Introduction to Structured VLSI Design VHDL IV Joachim

- Slides: 32

Introduction to Structured VLSI Design - VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

Overview • • Recap Datapath Memories Strictly Structured VHDL Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

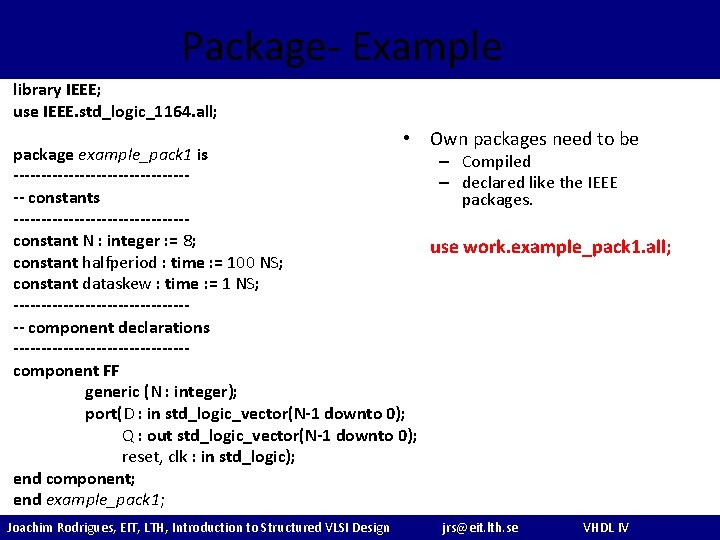

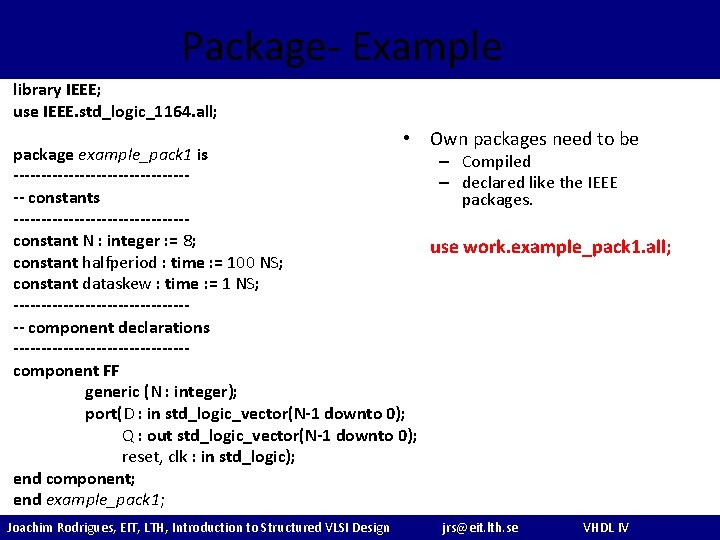

Package- Example library IEEE; use IEEE. std_logic_1164. all; • Own packages need to be package example_pack 1 is – Compiled ----------------– declared like the IEEE -- constants packages. ----------------constant N : integer : = 8; use work. example_pack 1. all; constant halfperiod : time : = 100 NS; constant dataskew : time : = 1 NS; ----------------- component declarations ----------------component FF generic (N : integer); port(D : in std_logic_vector(N-1 downto 0); Q : out std_logic_vector(N-1 downto 0); reset, clk : in std_logic); end component; end example_pack 1; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

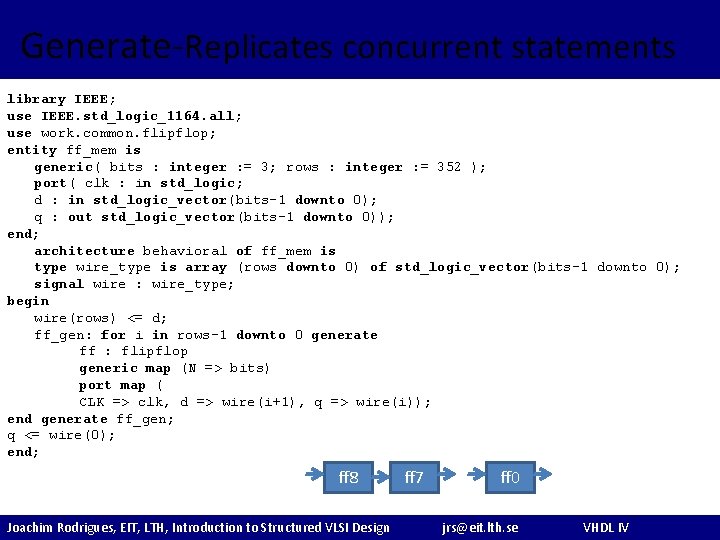

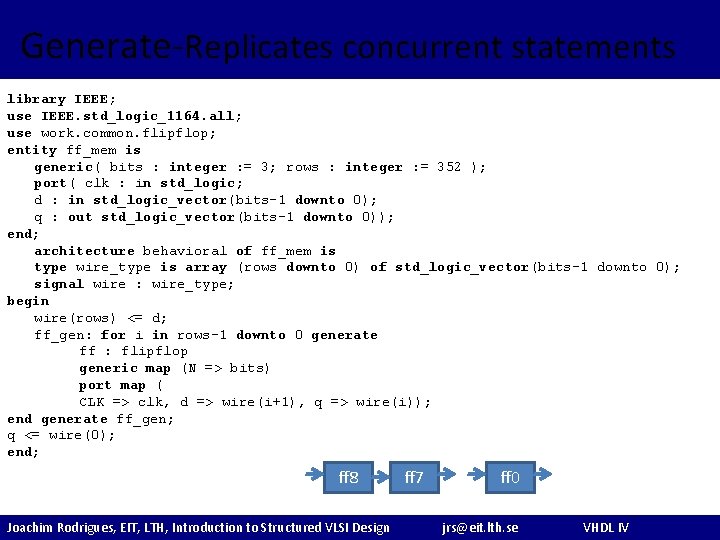

Generate-Replicates concurrent statements library IEEE; use IEEE. std_logic_1164. all; use work. common. flipflop; entity ff_mem is generic( bits : integer : = 3; rows : integer : = 352 ); port( clk : in std_logic; d : in std_logic_vector(bits-1 downto 0); q : out std_logic_vector(bits-1 downto 0)); end; architecture behavioral of ff_mem is type wire_type is array (rows downto 0) of std_logic_vector(bits-1 downto 0); signal wire : wire_type; begin wire(rows) <= d; ff_gen: for i in rows-1 downto 0 generate ff : flipflop generic map (N => bits) port map ( CLK => clk, d => wire(i+1), q => wire(i)); end generate ff_gen; q <= wire(0); end; ff 8 Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design ff 7 ff 0 jrs@eit. lth. se VHDL IV

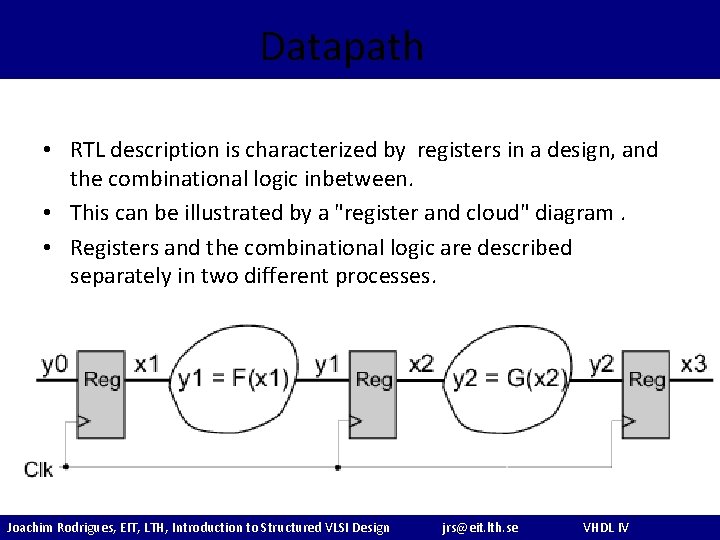

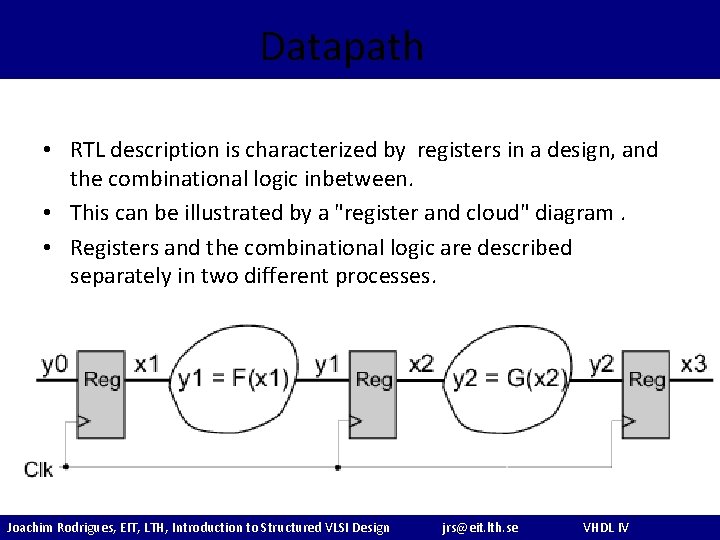

Datapath • RTL description is characterized by registers in a design, and the combinational logic inbetween. • This can be illustrated by a "register and cloud" diagram. • Registers and the combinational logic are described separately in two different processes. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

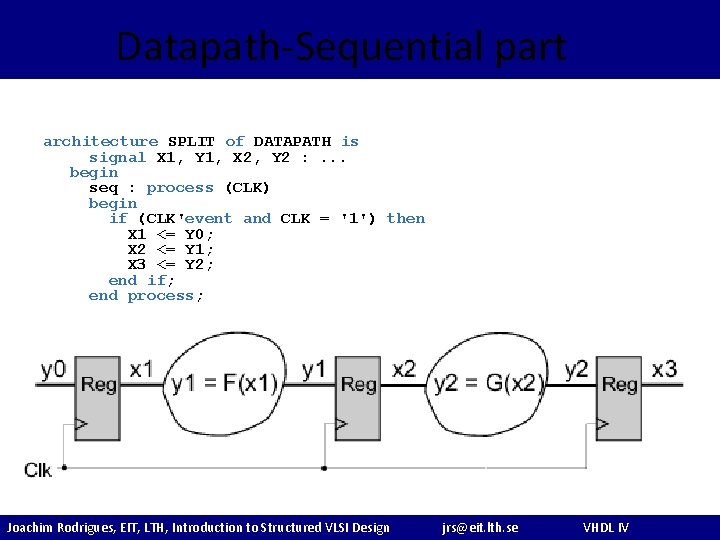

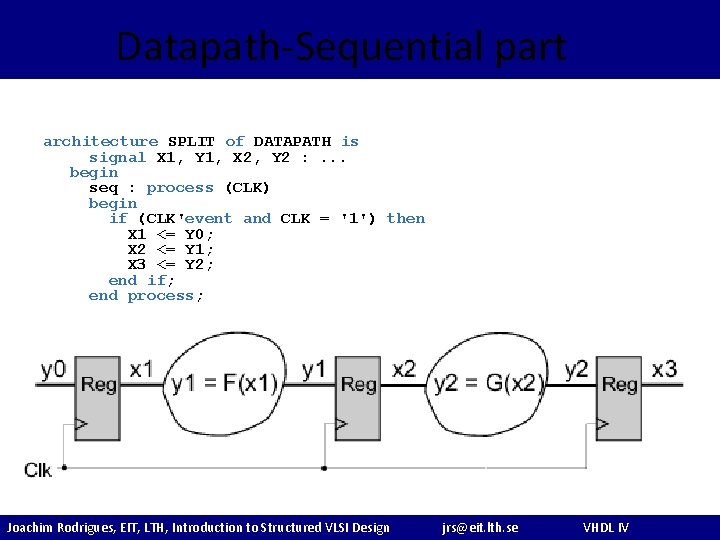

Datapath-Sequential part architecture SPLIT of DATAPATH is signal X 1, Y 1, X 2, Y 2 : . . . begin seq : process (CLK) begin if (CLK'event and CLK = '1') then X 1 <= Y 0; X 2 <= Y 1; X 3 <= Y 2; end if; end process; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

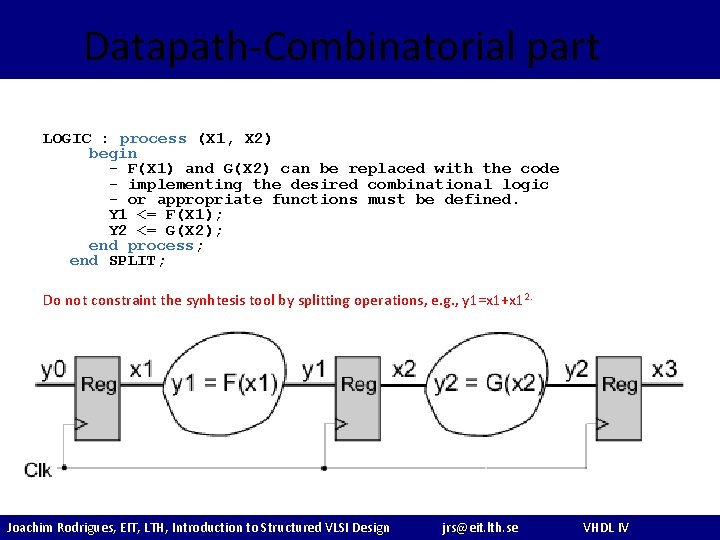

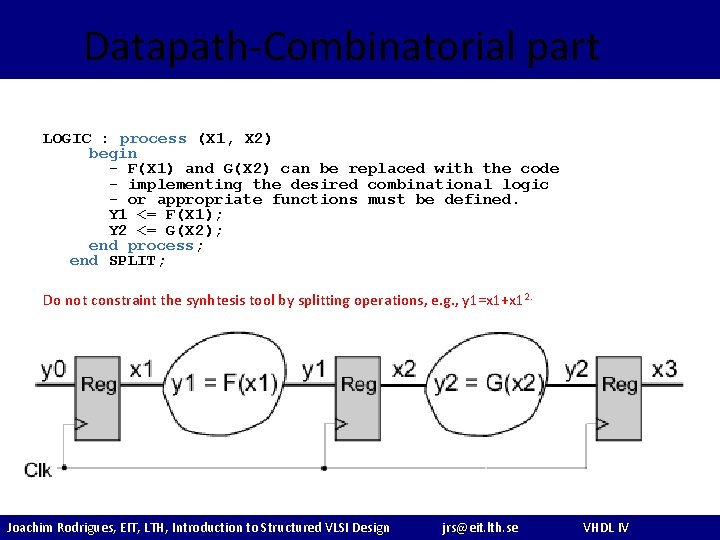

Datapath-Combinatorial part LOGIC : process (X 1, X 2) begin - F(X 1) and G(X 2) can be replaced with the code - implementing the desired combinational logic - or appropriate functions must be defined. Y 1 <= F(X 1); Y 2 <= G(X 2); end process; end SPLIT; Do not constraint the synhtesis tool by splitting operations, e. g. , y 1=x 1+x 1 2. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

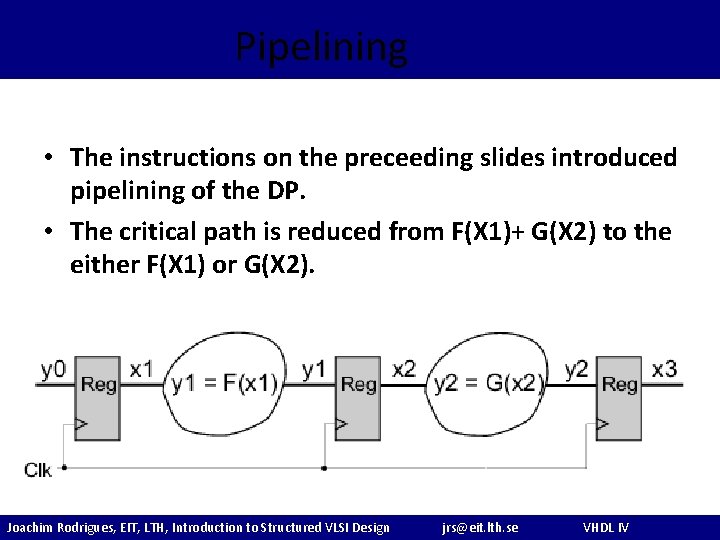

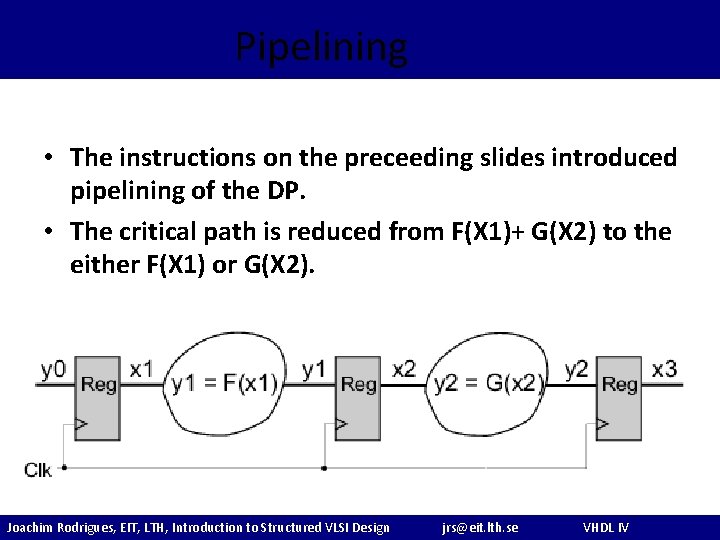

Pipelining • The instructions on the preceeding slides introduced pipelining of the DP. • The critical path is reduced from F(X 1)+ G(X 2) to the either F(X 1) or G(X 2). Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

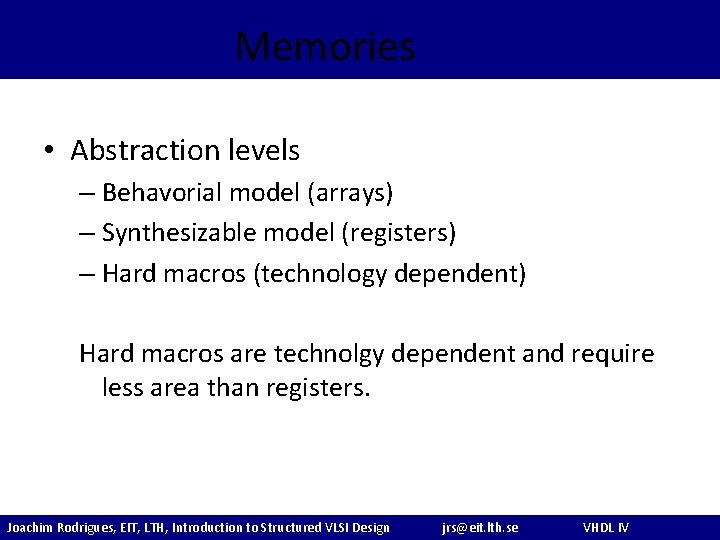

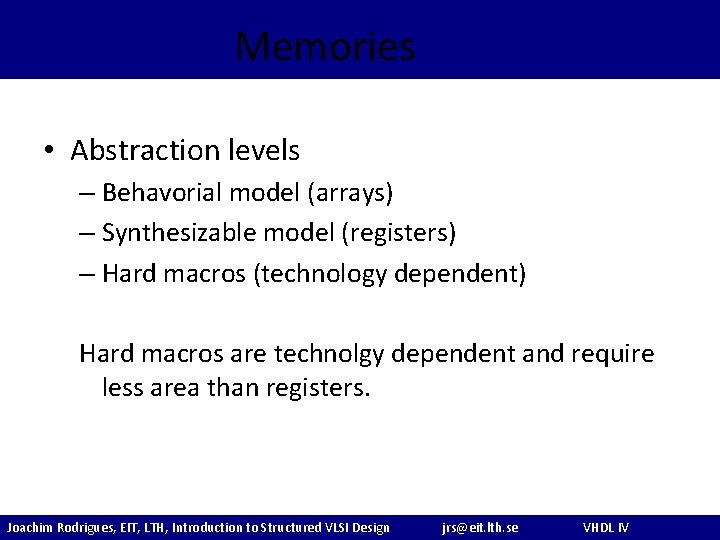

Memories • Abstraction levels – Behavorial model (arrays) – Synthesizable model (registers) – Hard macros (technology dependent) Hard macros are technolgy dependent and require less area than registers. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

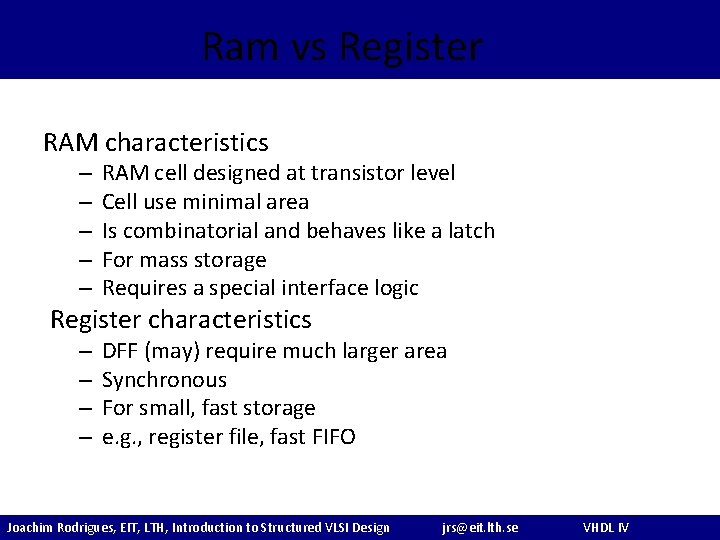

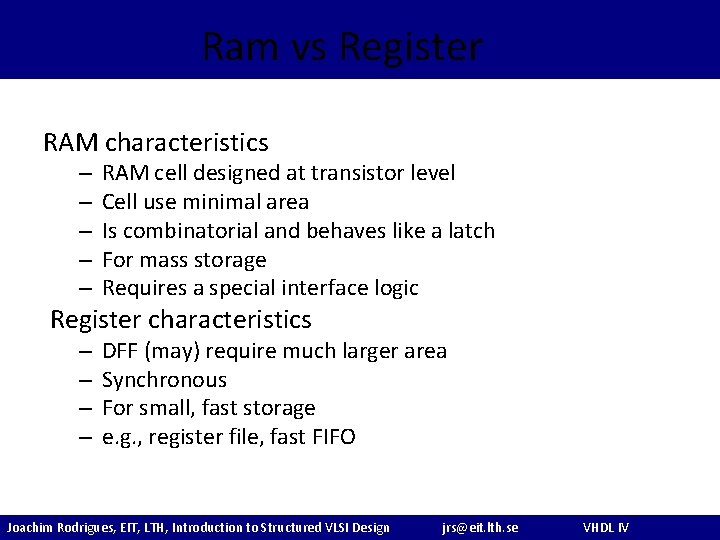

Ram vs Register RAM characteristics – – – RAM cell designed at transistor level Cell use minimal area Is combinatorial and behaves like a latch For mass storage Requires a special interface logic Register characteristics – – DFF (may) require much larger area Synchronous For small, fast storage e. g. , register file, fast FIFO Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

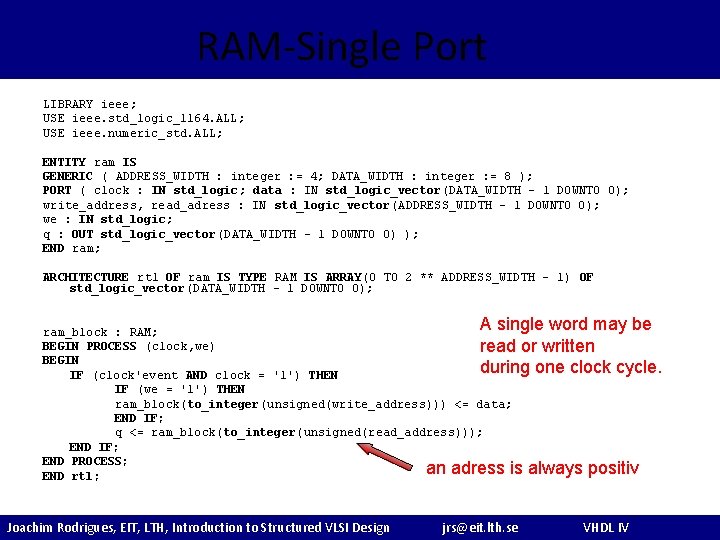

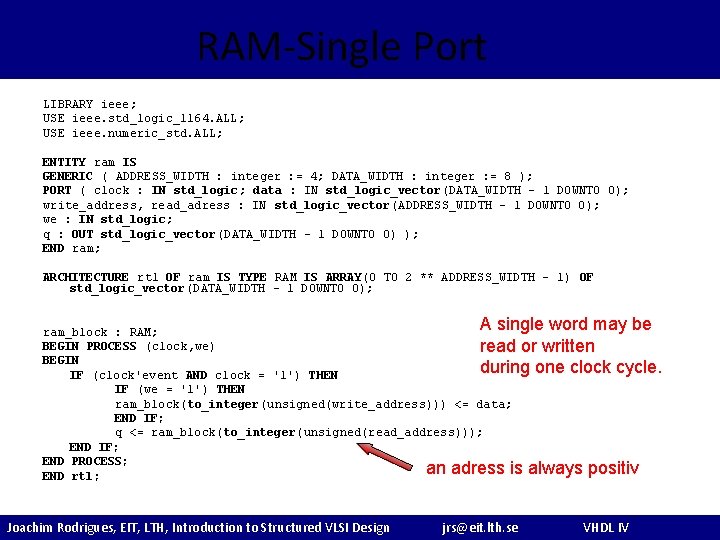

RAM-Single Port LIBRARY ieee; USE ieee. std_logic_1164. ALL; USE ieee. numeric_std. ALL; ENTITY ram IS GENERIC ( ADDRESS_WIDTH : integer : = 4; DATA_WIDTH : integer : = 8 ); PORT ( clock : IN std_logic; data : IN std_logic_vector(DATA_WIDTH - 1 DOWNTO 0); write_address, read_adress : IN std_logic_vector(ADDRESS_WIDTH - 1 DOWNTO 0); we : IN std_logic; q : OUT std_logic_vector(DATA_WIDTH - 1 DOWNTO 0) ); END ram; ARCHITECTURE rtl OF ram IS TYPE RAM IS ARRAY(0 TO 2 ** ADDRESS_WIDTH - 1) OF std_logic_vector(DATA_WIDTH - 1 DOWNTO 0); A single word may be ram_block : RAM; BEGIN PROCESS (clock, we) read or written BEGIN during one clock cycle. IF (clock'event AND clock = '1') THEN IF (we = '1') THEN ram_block(to_integer(unsigned(write_address))) <= data; END IF; q <= ram_block(to_integer(unsigned(read_address))); END IF; END PROCESS; an adress is always positiv END rtl; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

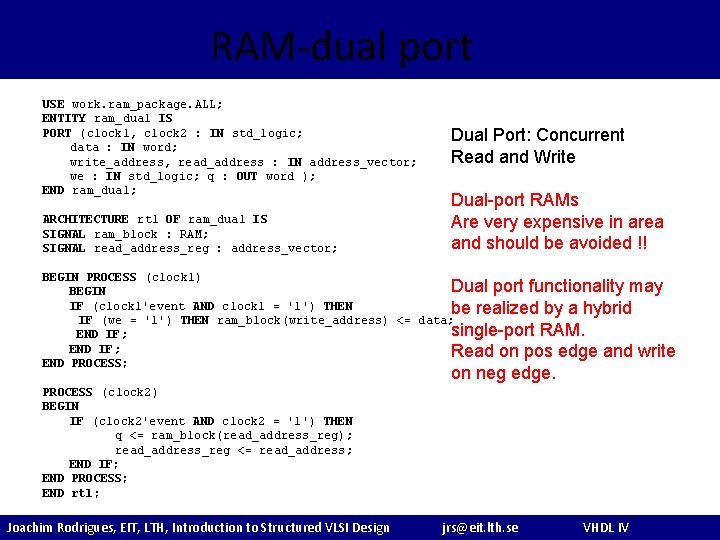

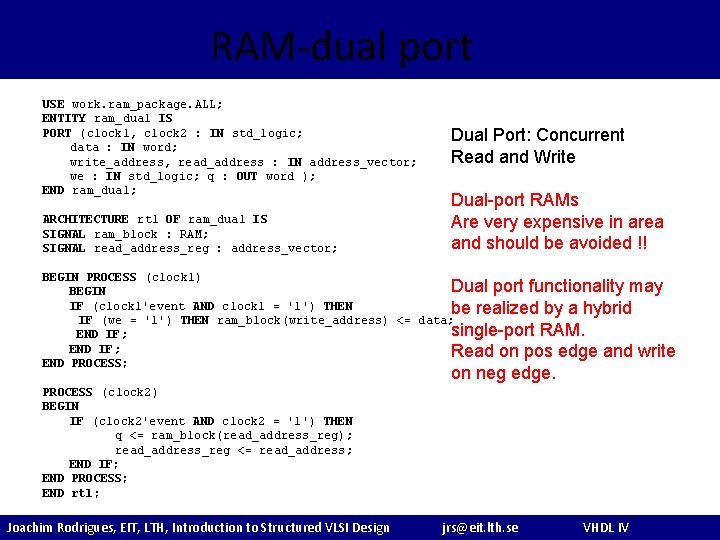

RAM-dual port USE work. ram_package. ALL; ENTITY ram_dual IS PORT (clock 1, clock 2 : IN std_logic; data : IN word; write_address, read_address : IN address_vector; we : IN std_logic; q : OUT word ); END ram_dual; ARCHITECTURE rtl OF ram_dual IS SIGNAL ram_block : RAM; SIGNAL read_address_reg : address_vector; Dual Port: Concurrent Read and Write Dual-port RAMs Are very expensive in area and should be avoided !! BEGIN PROCESS (clock 1) Dual port functionality may BEGIN IF (clock 1'event AND clock 1 = '1') THEN be realized by a hybrid IF (we = '1') THEN ram_block(write_address) <= data; single-port RAM. END IF; Read on pos edge and write END PROCESS; on neg edge. PROCESS (clock 2) BEGIN IF (clock 2'event AND clock 2 = '1') THEN q <= ram_block(read_address_reg); read_address_reg <= read_address; END IF; END PROCESS; END rtl; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

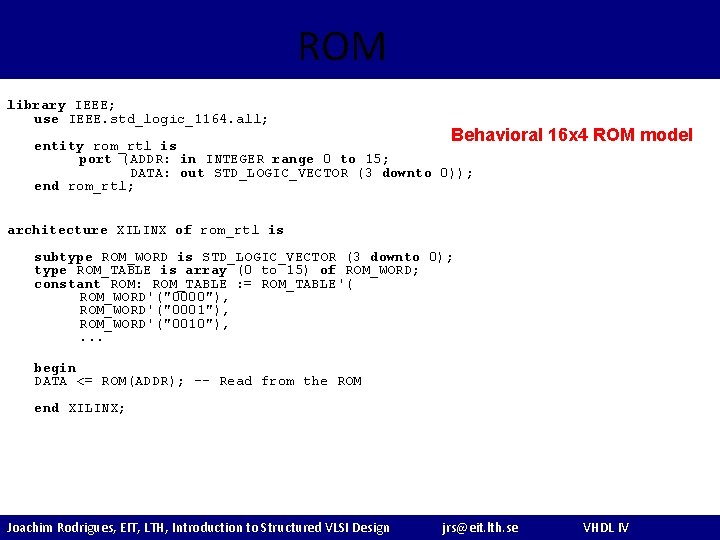

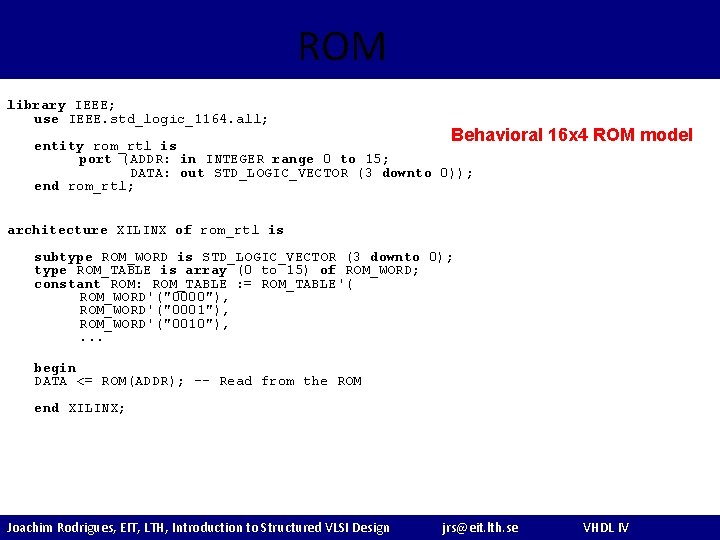

ROM library IEEE; use IEEE. std_logic_1164. all; Behavioral 16 x 4 ROM model entity rom_rtl is port (ADDR: in INTEGER range 0 to 15; DATA: out STD_LOGIC_VECTOR (3 downto 0)); end rom_rtl; architecture XILINX of rom_rtl is subtype ROM_WORD is STD_LOGIC_VECTOR (3 downto 0); type ROM_TABLE is array (0 to 15) of ROM_WORD; constant ROM: ROM_TABLE : = ROM_TABLE'( ROM_WORD'("0000"), ROM_WORD'("0001"), ROM_WORD'("0010"), . . . begin DATA <= ROM(ADDR); -- Read from the ROM end XILINX; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

Register File Registers are arranged as an 1 -d array • Each register is accessible with an address • Usually 1 write port (with write enable signal) • May have multiple read ports Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

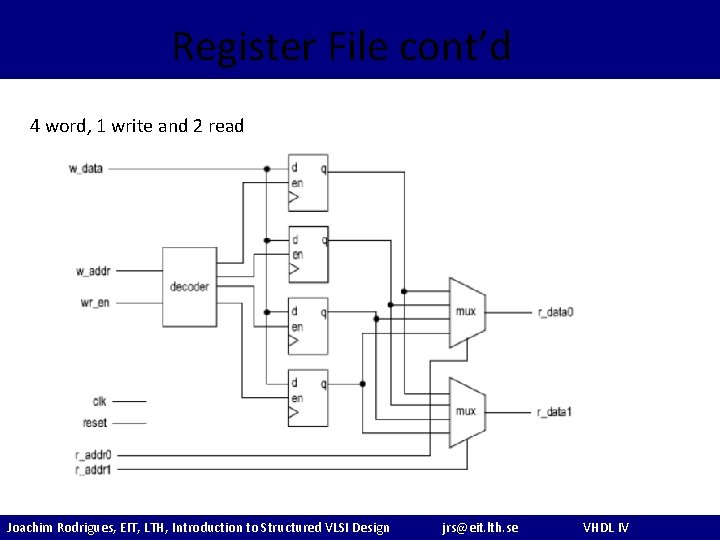

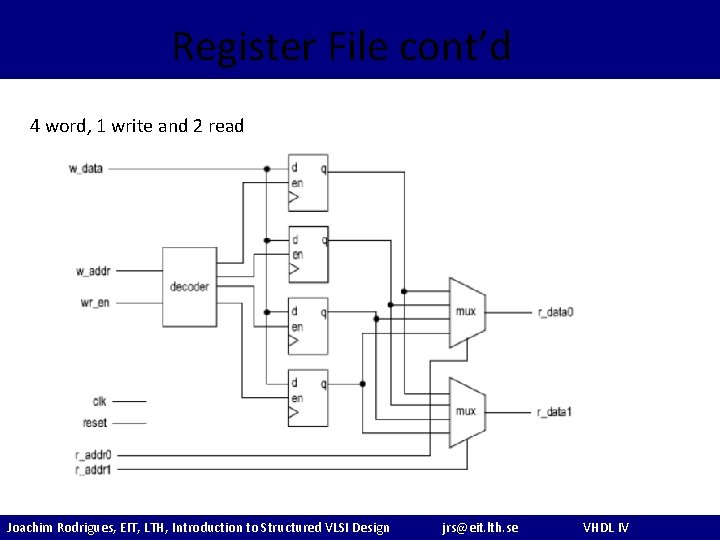

Register File cont’d 4 word, 1 write and 2 read Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

Strictly Structured VHDL “Gaisler’s method” is a design methodology (code style), which is summarized below: – Use records – Use case statements to model FSMs – Use synchronous reset – Apply strong hierarchies Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

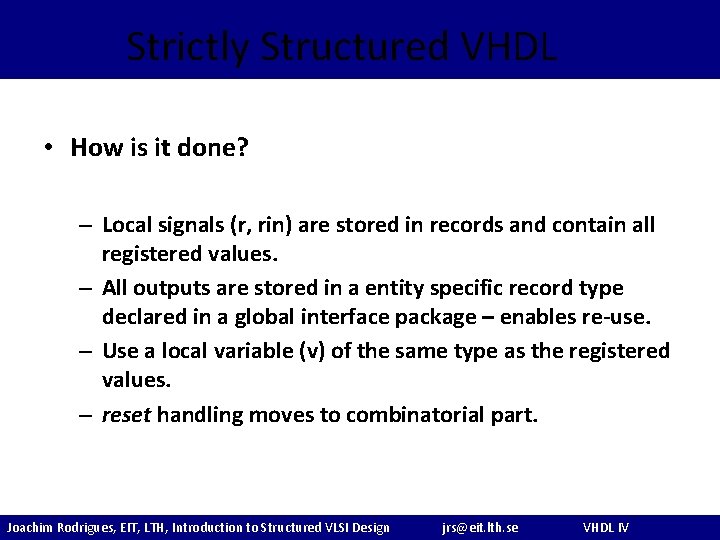

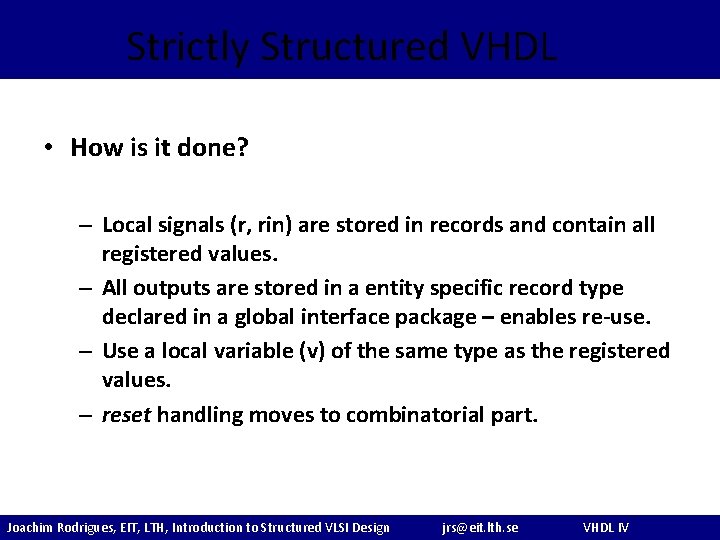

Strictly Structured VHDL • How is it done? – Local signals (r, rin) are stored in records and contain all registered values. – All outputs are stored in a entity specific record type declared in a global interface package – enables re-use. – Use a local variable (v) of the same type as the registered values. – reset handling moves to combinatorial part. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

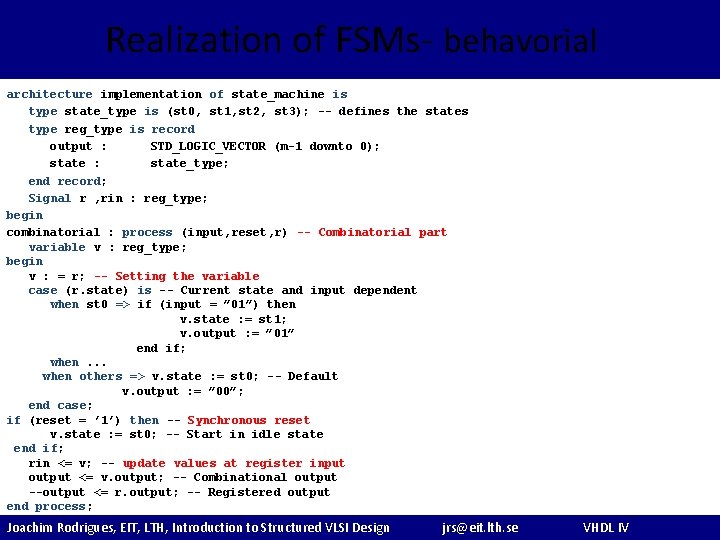

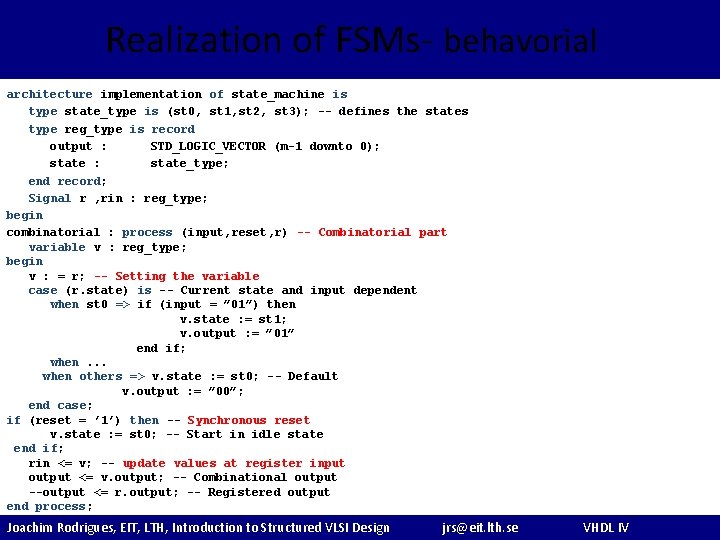

Realization of FSMs- behavorial architecture implementation of state_machine is type state_type is (st 0, st 1, st 2, st 3); -- defines the states type reg_type is record output : STD_LOGIC_VECTOR (m-1 downto 0); state : state_type; end record; Signal r , rin : reg_type; begin combinatorial : process (input, reset, r) -- Combinatorial part variable v : reg_type; begin v : = r; -- Setting the variable case (r. state) is -- Current state and input dependent when st 0 => if (input = ” 01”) then v. state : = st 1; v. output : = ” 01” end if; when. . . when others => v. state : = st 0; -- Default v. output : = ” 00”; end case; if (reset = ’ 1’) then -- Synchronous reset v. state : = st 0; -- Start in idle state end if; rin <= v; -- update values at register input output <= v. output; -- Combinational output --output <= r. output; -- Registered output end process; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

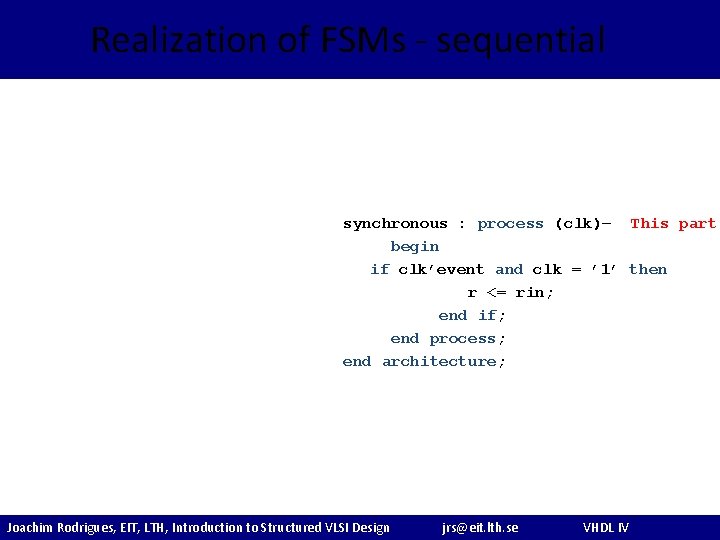

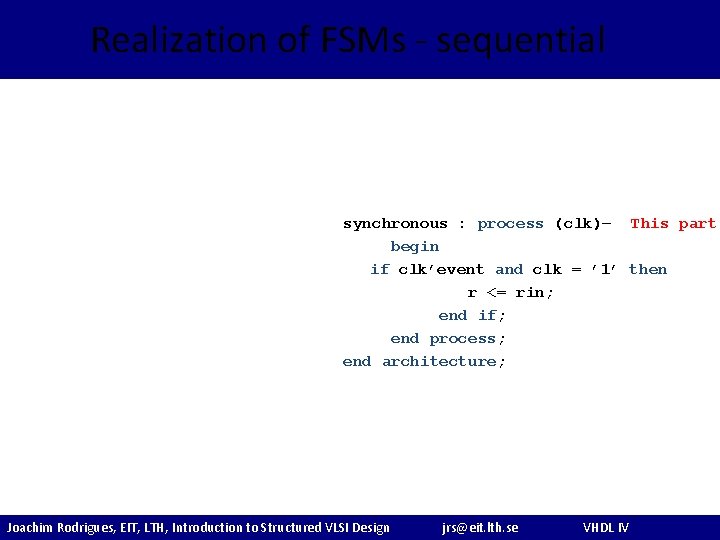

Realization of FSMs - sequential synchronous : process (clk)– This part begin if clk’event and clk = ’ 1’ then r <= rin; end if; end process; end architecture; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

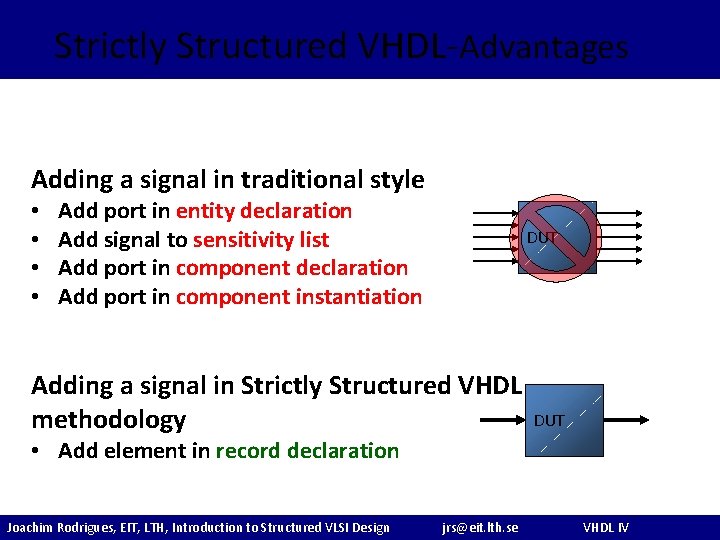

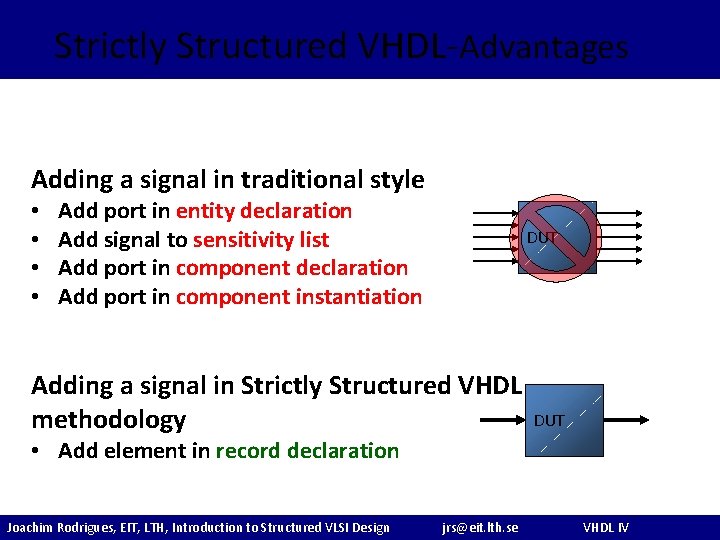

Strictly Structured VHDL-Advantages Adding a signal in traditional style • • Add port in entity declaration Add signal to sensitivity list Add port in component declaration Add port in component instantiation DUT Adding a signal in Strictly Structured VHDL methodology DUT • Add element in record declaration Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

Structured VHDL Obvious Advantages • Readability • Less written code • Maintainance and re-useability Hidden Advantages • Synthesizable • Synchronous reset • No need to update sensitivity lists • Faster simulation (less concurrent statements) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

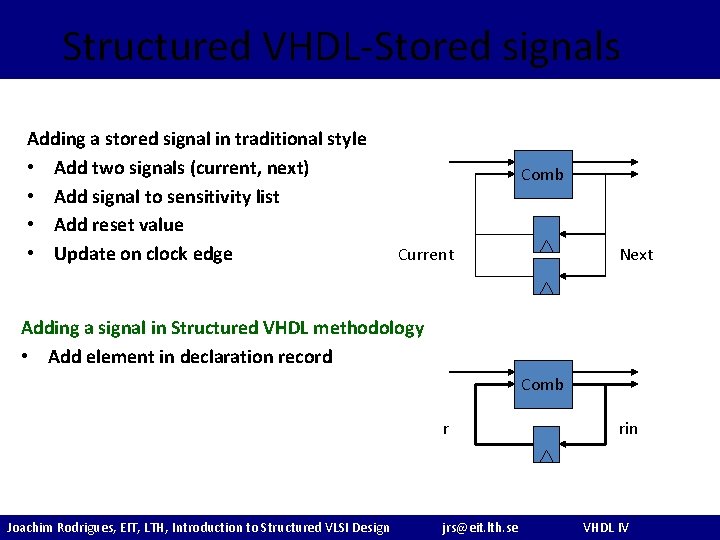

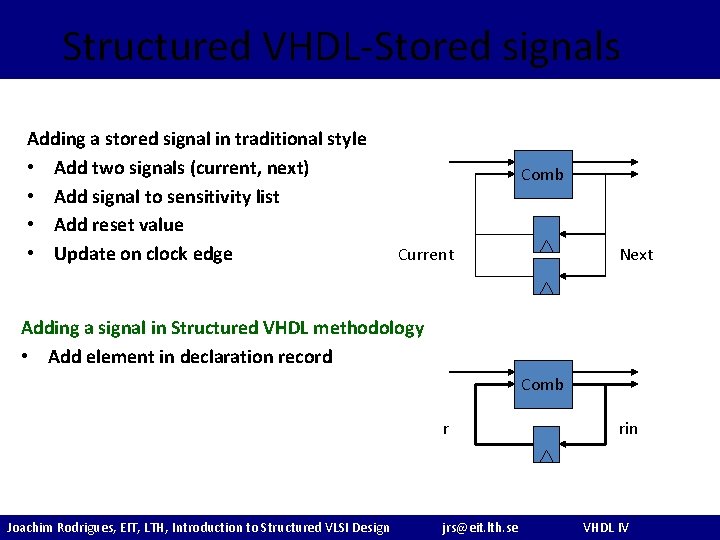

Structured VHDL-Stored signals Adding a stored signal in traditional style • Add two signals (current, next) • Add signal to sensitivity list • Add reset value • Update on clock edge Comb Current Next Adding a signal in Structured VHDL methodology • Add element in declaration record Comb r Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se rin VHDL IV

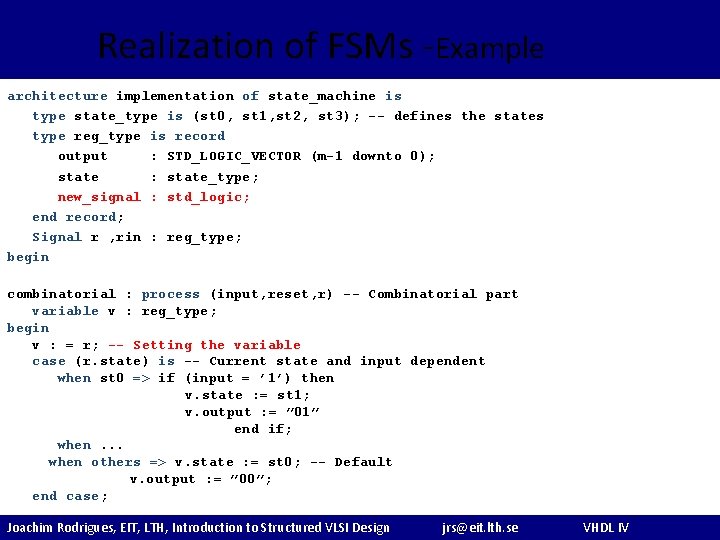

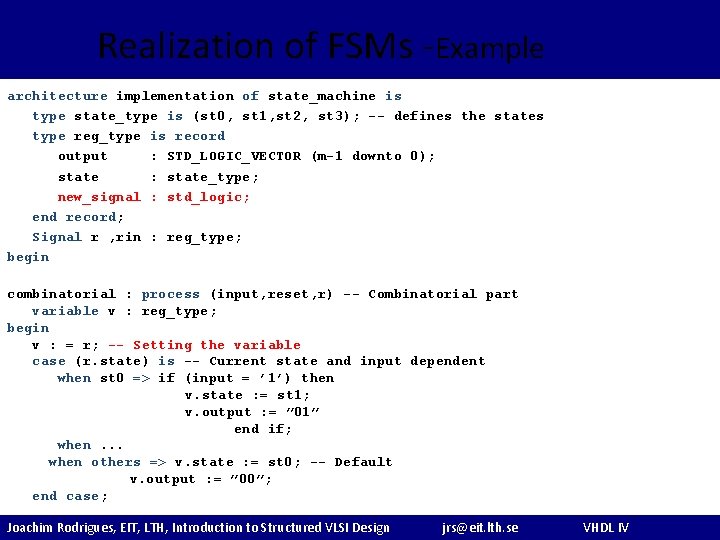

Realization of FSMs -Example architecture implementation of state_machine is type state_type is (st 0, st 1, st 2, st 3); -- defines the states type reg_type is record output : STD_LOGIC_VECTOR (m-1 downto 0); state : state_type; new_signal : std_logic; end record; Signal r , rin : reg_type; begin combinatorial : process (input, reset, r) -- Combinatorial part variable v : reg_type; begin v : = r; -- Setting the variable case (r. state) is -- Current state and input dependent when st 0 => if (input = ’ 1’) then v. state : = st 1; v. output : = ” 01” end if; when. . . when others => v. state : = st 0; -- Default v. output : = ” 00”; end case; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

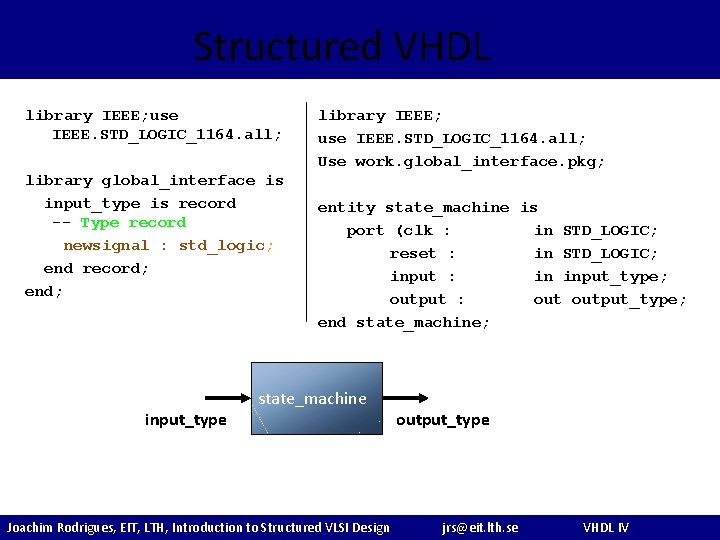

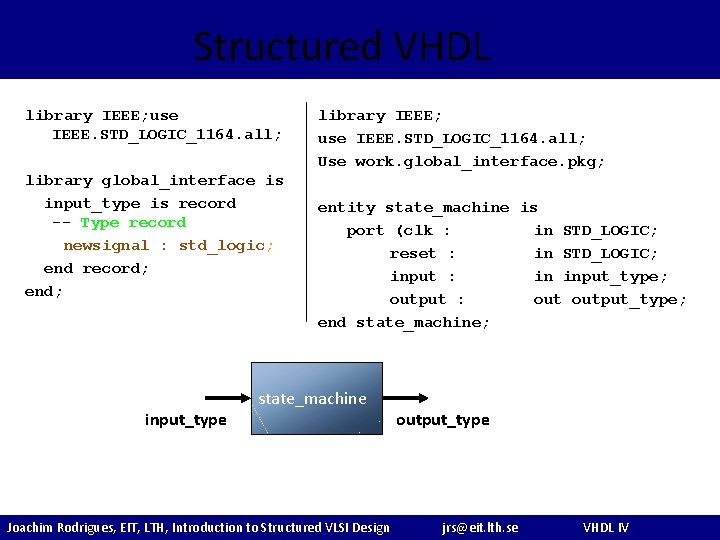

Structured VHDL library IEEE; use IEEE. STD_LOGIC_1164. all; Use work. global_interface. pkg; library global_interface is input_type is record entity state_machine is -- Type record port (clk : in STD_LOGIC; newsignal : std_logic; reset : in STD_LOGIC; end record; input : in input_type; end; output : output_type; end state_machine; input_type state_machine Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design output_type jrs@eit. lth. se VHDL IV

Conclusions Recommendations – – Use structured VHDL Use synchronous reset Use hierarchy (instantiation) extensively Let the testbench set the input signals and not the simulator (No signal forcing in Model. Sim) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

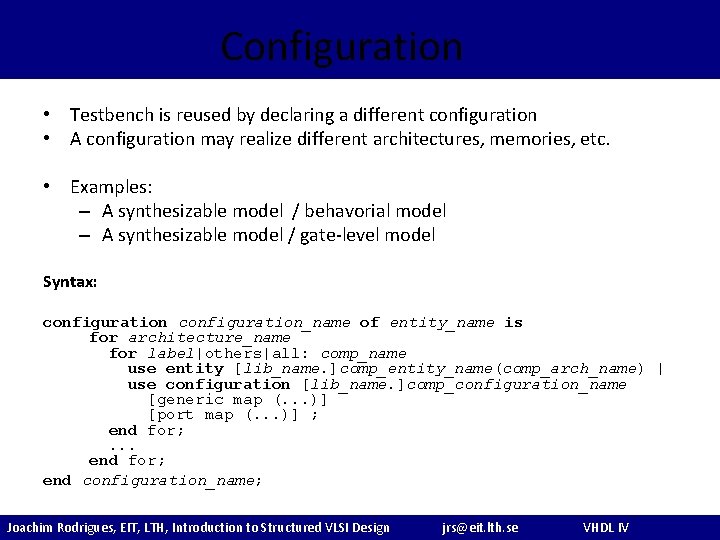

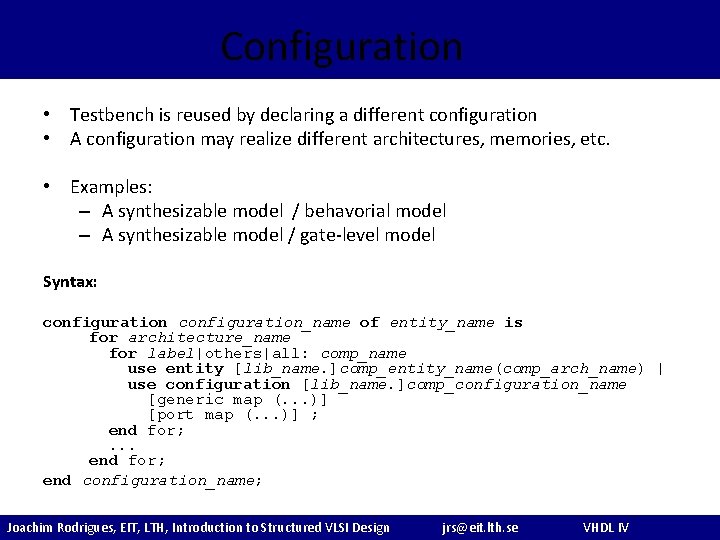

Configuration • Testbench is reused by declaring a different configuration • A configuration may realize different architectures, memories, etc. • Examples: – A synthesizable model / behavorial model – A synthesizable model / gate-level model Syntax: configuration_name of entity_name is for architecture_name for label|others|all: comp_name use entity [lib_name. ]comp_entity_name(comp_arch_name) | use configuration [lib_name. ]comp_configuration_name [generic map (. . . )] [port map (. . . )] ; end for; . . . end for; end configuration_name; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

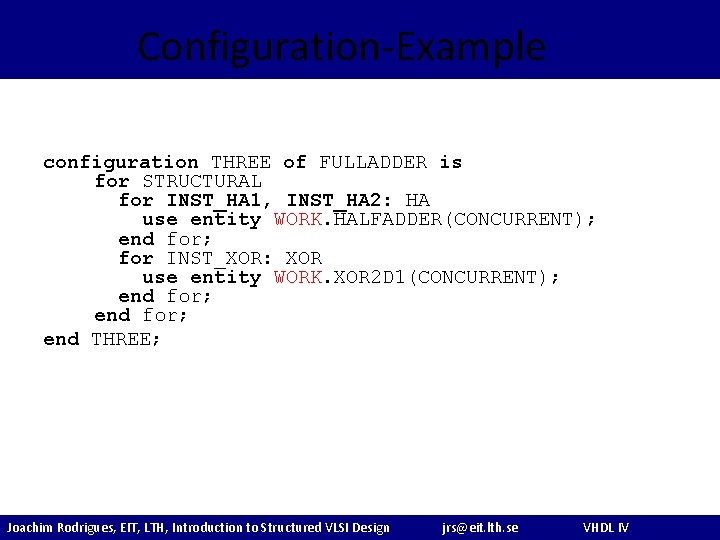

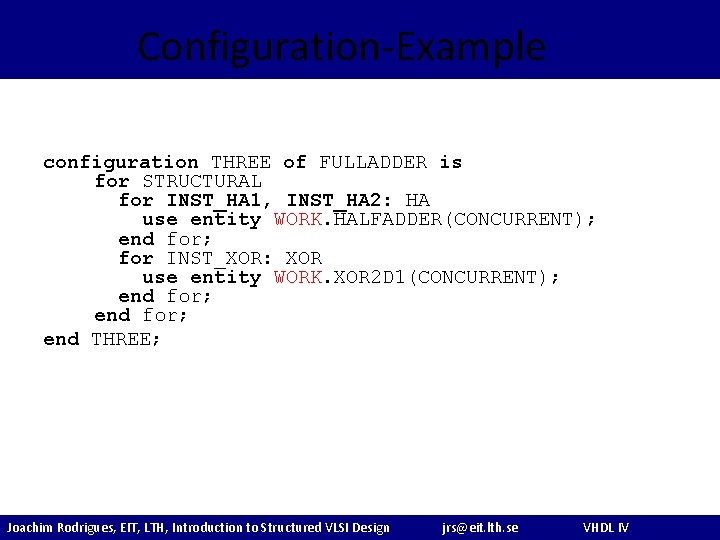

Configuration-Example configuration THREE of FULLADDER is for STRUCTURAL for INST_HA 1, INST_HA 2: HA use entity WORK. HALFADDER(CONCURRENT); end for; for INST_XOR: XOR use entity WORK. XOR 2 D 1(CONCURRENT); end for; end THREE; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

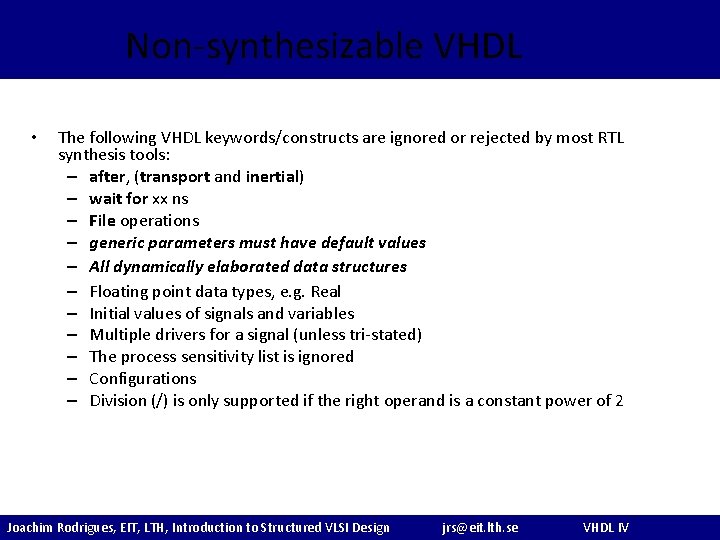

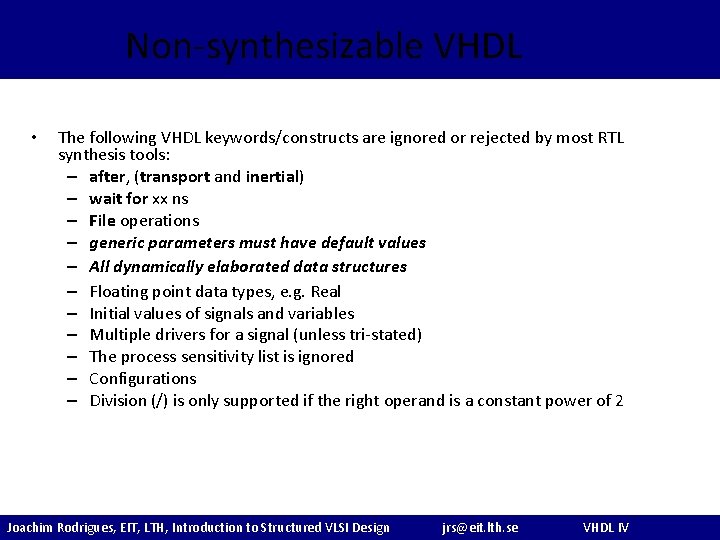

Non-synthesizable VHDL • The following VHDL keywords/constructs are ignored or rejected by most RTL synthesis tools: – after, (transport and inertial) – wait for xx ns – File operations – generic parameters must have default values – All dynamically elaborated data structures – Floating point data types, e. g. Real – Initial values of signals and variables – Multiple drivers for a signal (unless tri-stated) – The process sensitivity list is ignored – Configurations – Division (/) is only supported if the right operand is a constant power of 2 Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

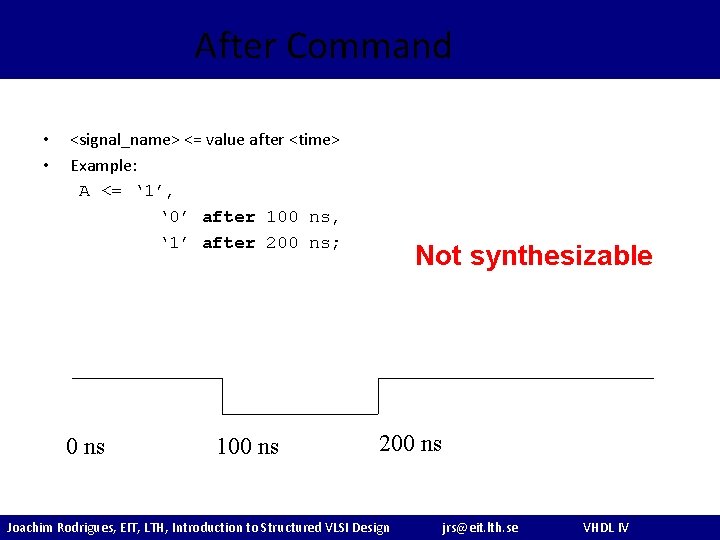

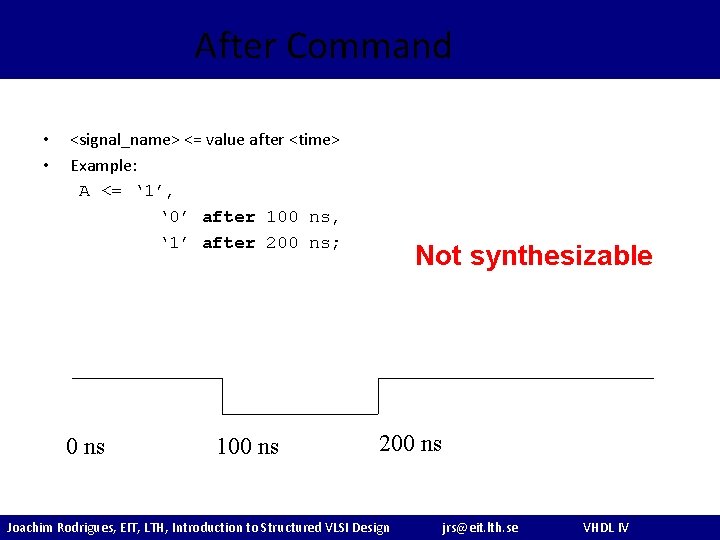

After Command • • <signal_name> <= value after <time> Example: A <= ‘ 1’, ‘ 0’ after 100 ns, ‘ 1’ after 200 ns; 0 ns 100 ns Not synthesizable 200 ns Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

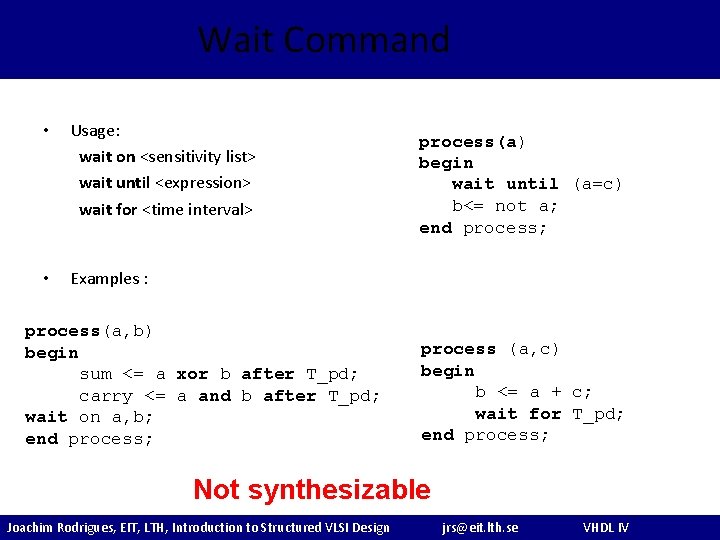

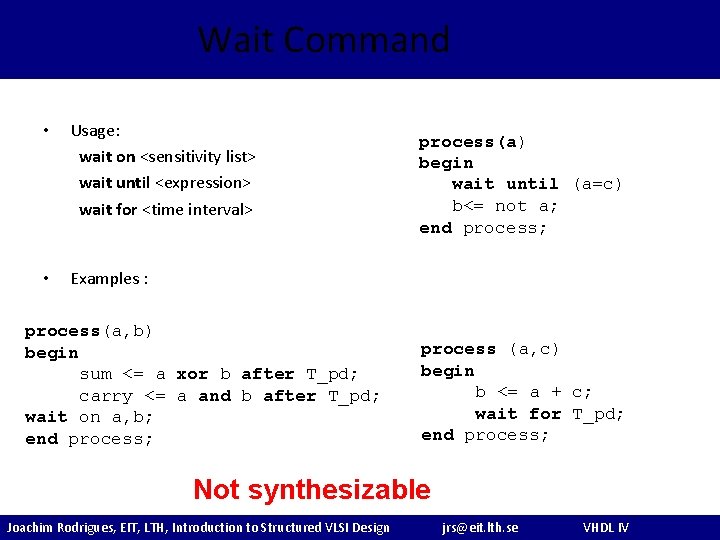

Wait Command • Usage: wait on <sensitivity list> wait until <expression> wait for <time interval> • Examples : process(a, b) begin sum <= a xor b after T_pd; carry <= a and b after T_pd; wait on a, b; end process; process(a) begin wait until (a=c) b<= not a; end process; process (a, c) begin b <= a + c; wait for T_pd; end process; Not synthesizable Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

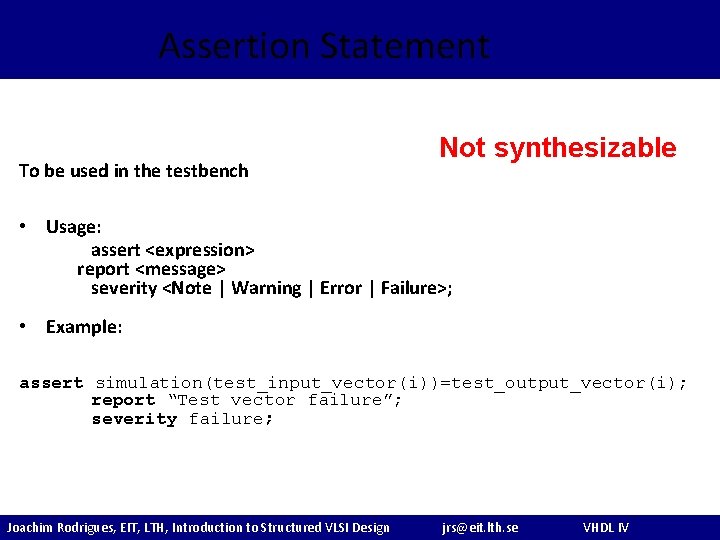

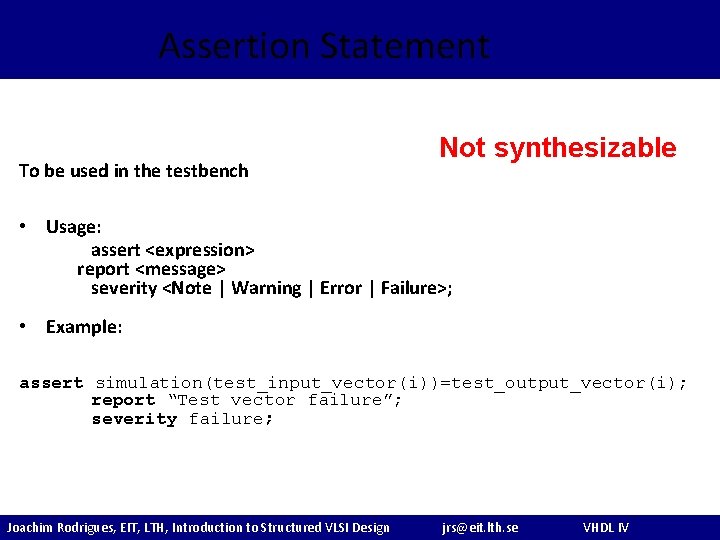

Assertion Statement To be used in the testbench Not synthesizable • Usage: assert <expression> report <message> severity <Note | Warning | Error | Failure>; • Example: assert simulation(test_input_vector(i))=test_output_vector(i); report “Test vector failure”; severity failure; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV

Watch out: Inferred Latches Already mentioned: get rid of any Latches. Check the synthesis report and correct eventual case/if instructions Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit. lth. se VHDL IV