Design and Implementation of VLSI Systems EN 1600

- Slides: 12

Design and Implementation of VLSI Systems (EN 1600 S 08) Lecture 12: Logical Effort (1/2) Prof. Sherief Reda Division of Engineering, Brown University Spring 2008 [sources: Weste/Addison Wesley – Rabaey/Pearson] S. Reda EN 1600 SP’ 08

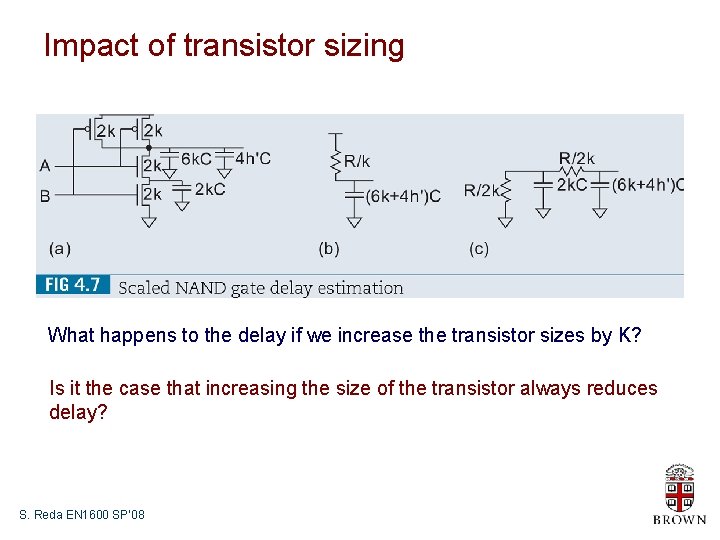

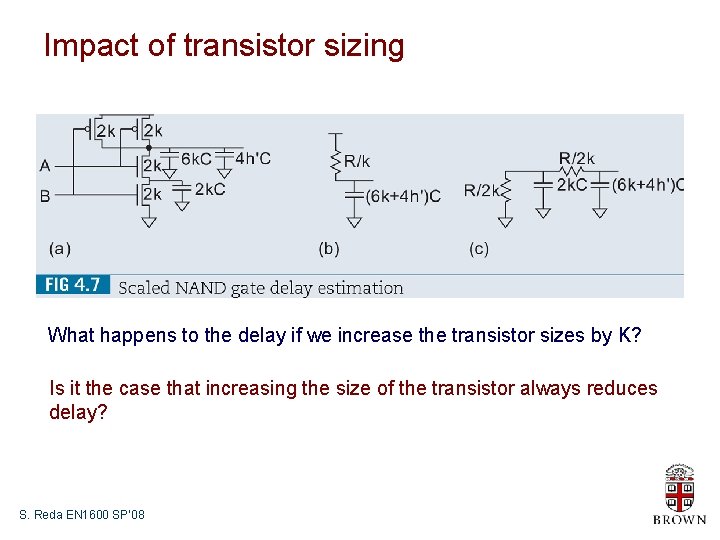

Impact of transistor sizing What happens to the delay if we increase the transistor sizes by K? Is it the case that increasing the size of the transistor always reduces delay? S. Reda EN 1600 SP’ 08

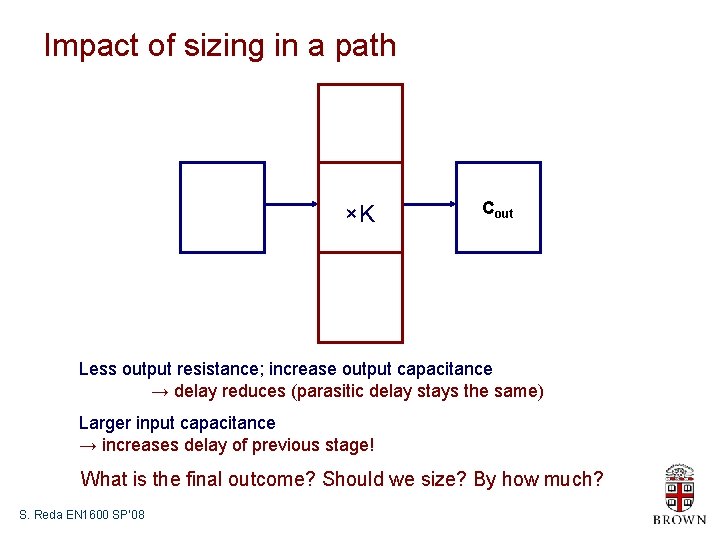

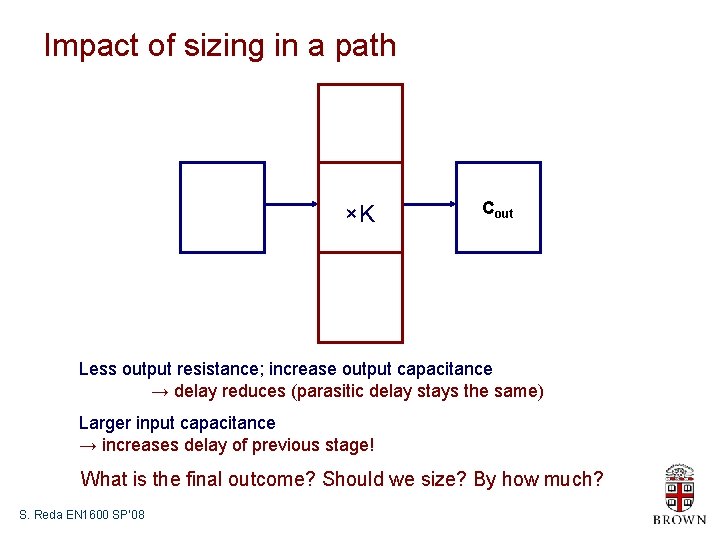

Impact of sizing in a path ×K Cout Less output resistance; increase output capacitance → delay reduces (parasitic delay stays the same) Larger input capacitance → increases delay of previous stage! What is the final outcome? Should we size? By how much? S. Reda EN 1600 SP’ 08

Impact of gate sizing If you decide to increase everything by a factor of k How about an inverter? Unloaded delay =3 RC 12 ps in 180 nm process 40 ps in 0. 6 mm process S. Reda EN 1600 SP’ 08

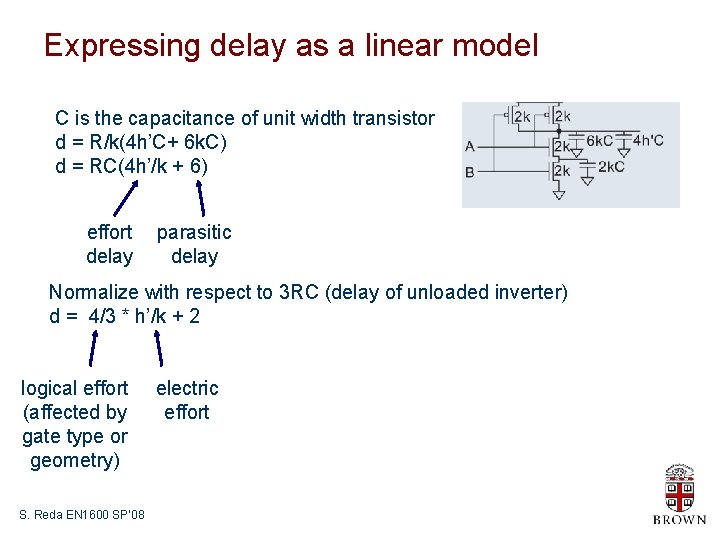

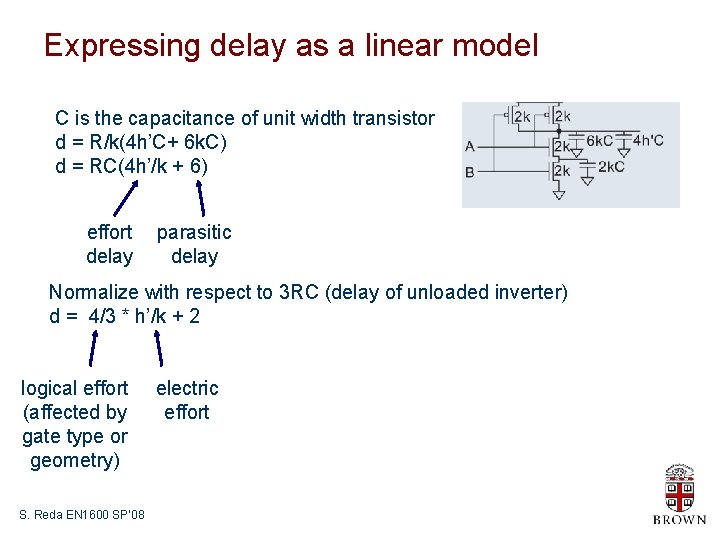

Expressing delay as a linear model C is the capacitance of unit width transistor d = R/k(4 h’C+ 6 k. C) d = RC(4 h’/k + 6) effort delay parasitic delay Normalize with respect to 3 RC (delay of unloaded inverter) d = 4/3 * h’/k + 2 logical effort (affected by gate type or geometry) S. Reda EN 1600 SP’ 08 electric effort

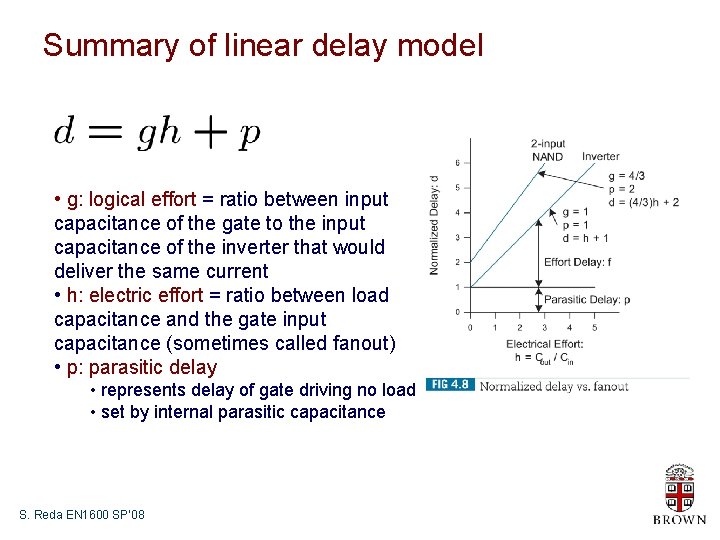

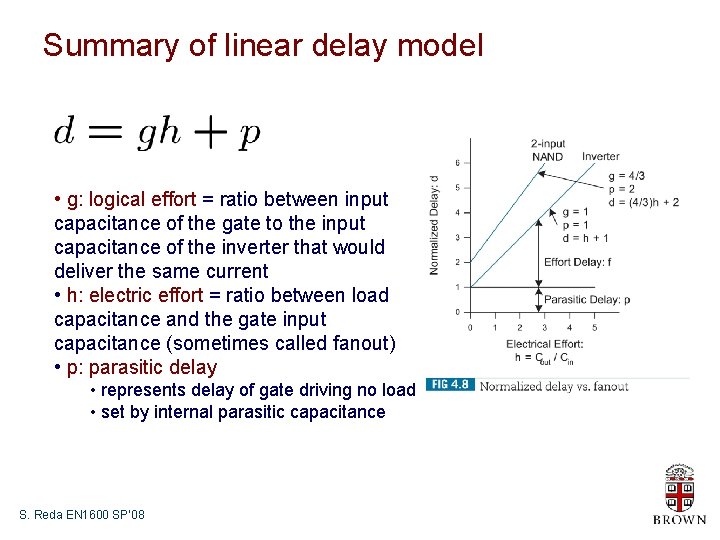

Summary of linear delay model • g: logical effort = ratio between input capacitance of the gate to the input capacitance of the inverter that would deliver the same current • h: electric effort = ratio between load capacitance and the gate input capacitance (sometimes called fanout) • p: parasitic delay • represents delay of gate driving no load • set by internal parasitic capacitance S. Reda EN 1600 SP’ 08

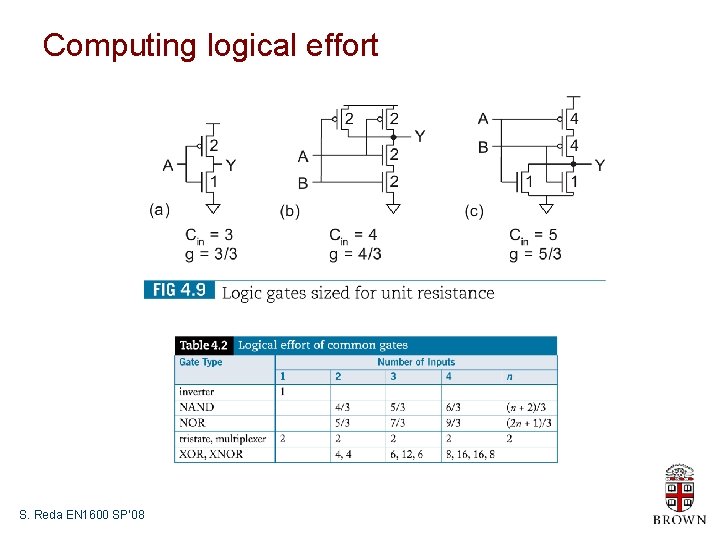

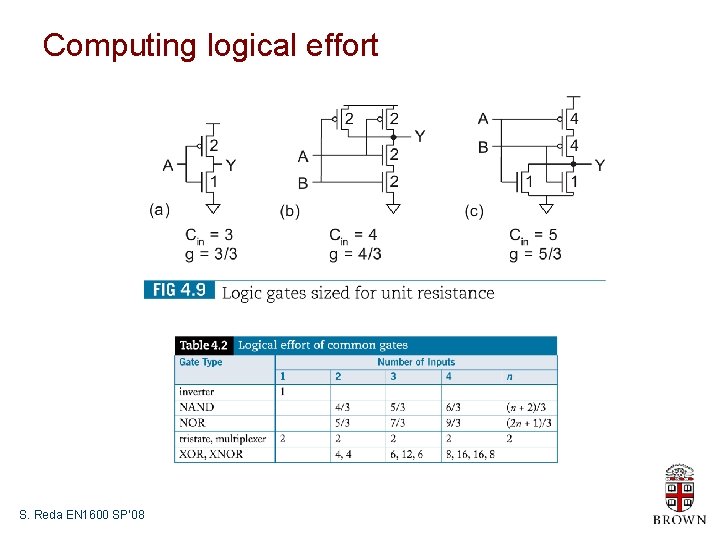

Computing logical effort S. Reda EN 1600 SP’ 08

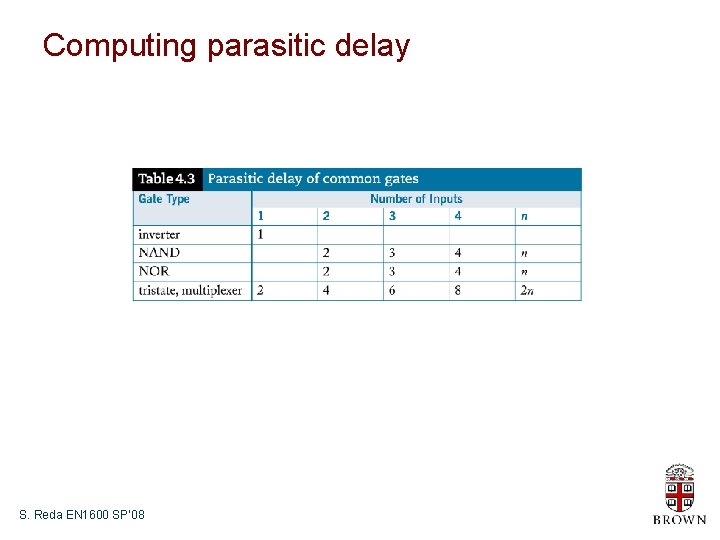

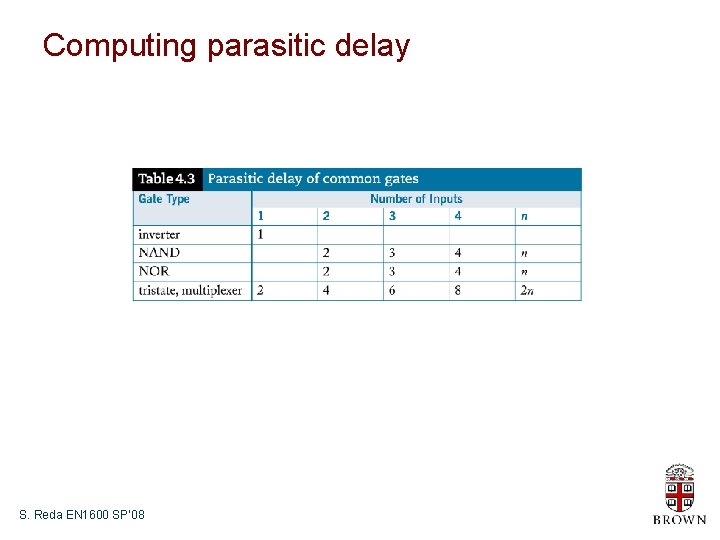

Computing parasitic delay S. Reda EN 1600 SP’ 08

Example: Ring oscillator • Estimate the frequency of an N-stage ring oscillator Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: Frequency: S. Reda EN 1600 SP’ 08 g= h= p= d= fosc =

Example: Ring oscillator • Estimate the frequency of an N-stage ring oscillator Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: Frequency: S. Reda EN 1600 SP’ 08 31 stage ring oscillator in g=1 0. 6 mm process has h=1 frequency of ~ 200 MHz p=1 d=2 fosc = 1/(2*N*d) = 1/4 N

Example: FO 4 Inverter • Estimate the delay of a fanout-of-4 (FO 4) inverter Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: S. Reda EN 1600 SP’ 08 g= h= p= d=

Example: FO 4 Inverter • Estimate the delay of a fanout-of-4 (FO 4) inverter Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: S. Reda EN 1600 SP’ 08 g=1 h=4 p=1 d=5 The FO 4 delay is about 200 ps in 0. 6 mm process 60 ps in a 180 nm process f/3 ns in an f mm process