VLSI SP Course 2001 FFT VLSI Implementation VLSI

- Slides: 15

VLSI SP Course 2001 FFT VLSI Implementation 台灣大學電機系 吳安宇 VLSI Signal Processing 1. 2. Shousheng He and Mats Torkelson, A new approach to pipeline FFT processor. IEEE Proc. Of IPPS, P 766 -770, 1996. E. Bidet, D. Castelain, C. Joanblanq, and P. Senn, A fast single-chip implementation of 8192 complex point FFT. IEEE J. Solid-State Circuits, P 300 -305, March 1995 Updated on 4/2/2001 台大電機吳安宇

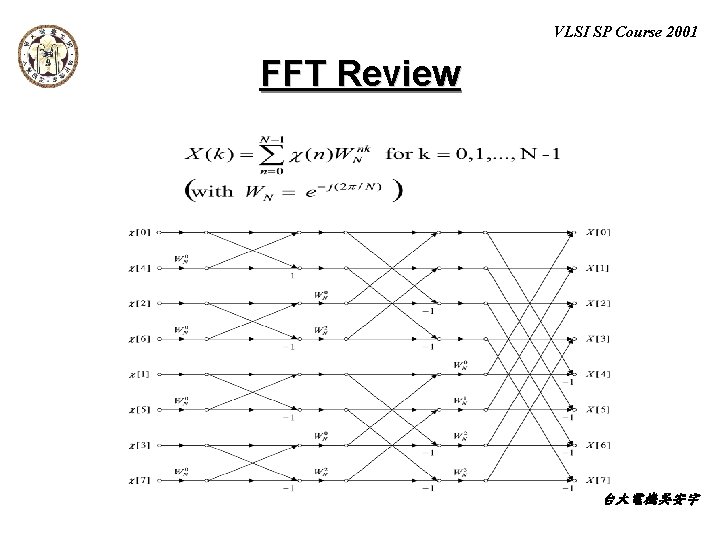

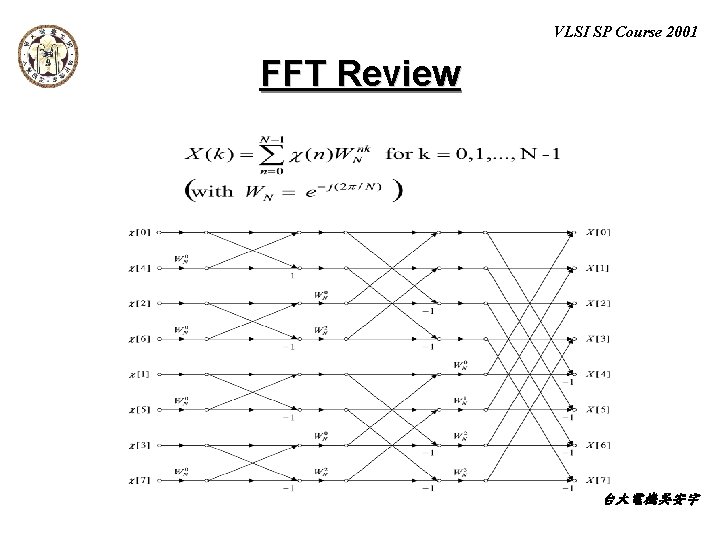

VLSI SP Course 2001 FFT Review 台大電機吳安宇

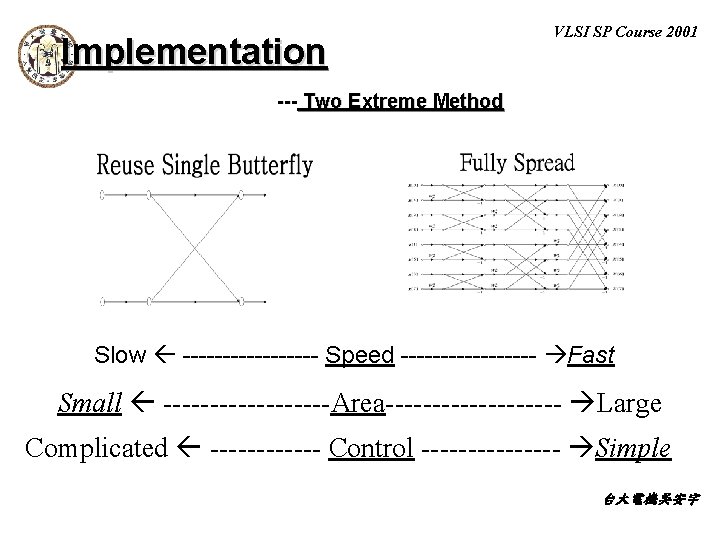

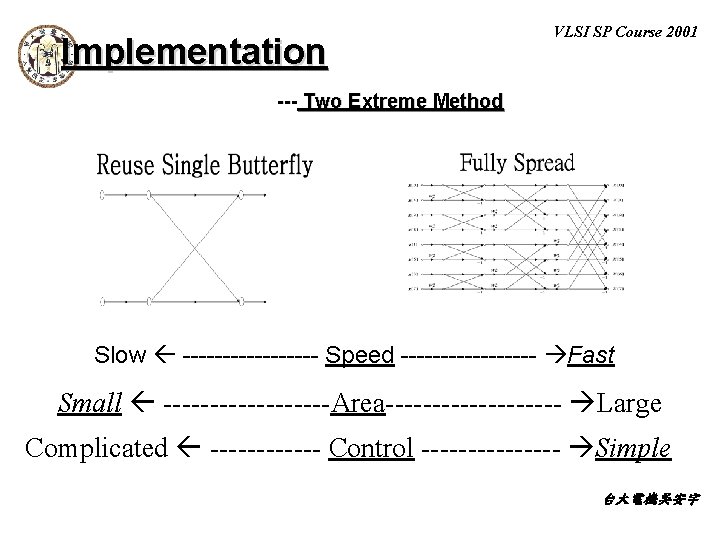

Implementation VLSI SP Course 2001 --- Two Extreme Method Slow --------- Speed --------- Fast Small ---------Area---------- Large Complicated ------ Control -------- Simple 台大電機吳安宇

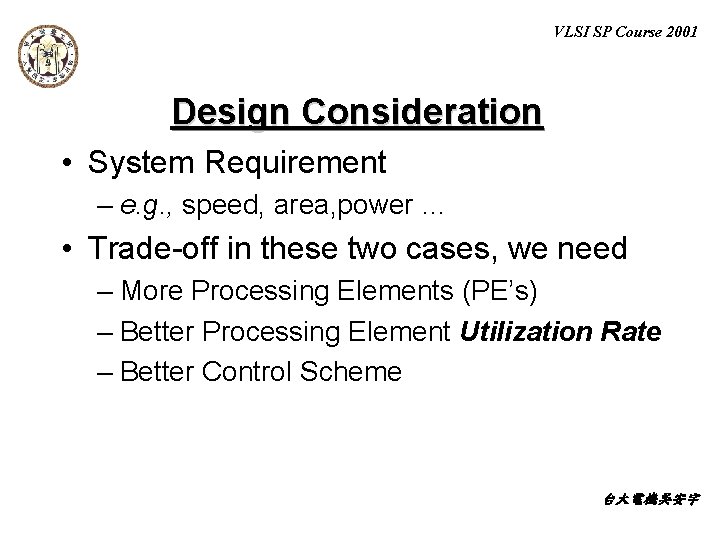

VLSI SP Course 2001 Design Consideration • System Requirement – e. g. , speed, area, power … • Trade-off in these two cases, we need – More Processing Elements (PE’s) – Better Processing Element Utilization Rate – Better Control Scheme 台大電機吳安宇

VLSI SP Course 2001 FFT Processor --- Block Diagram 台大電機吳安宇

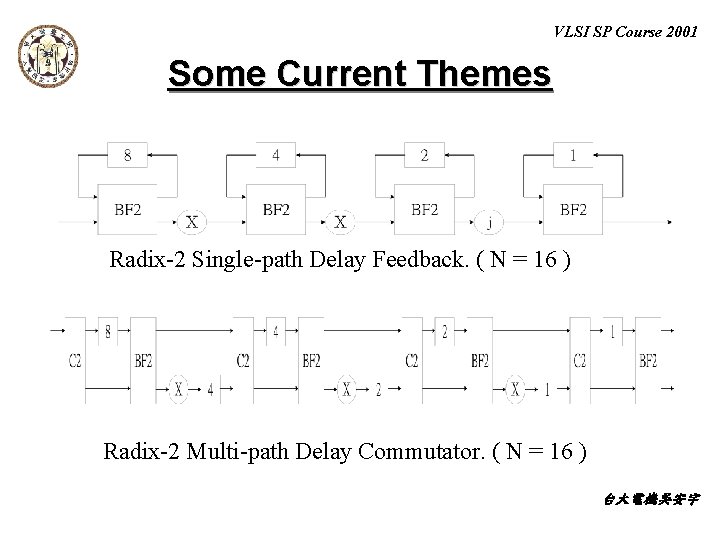

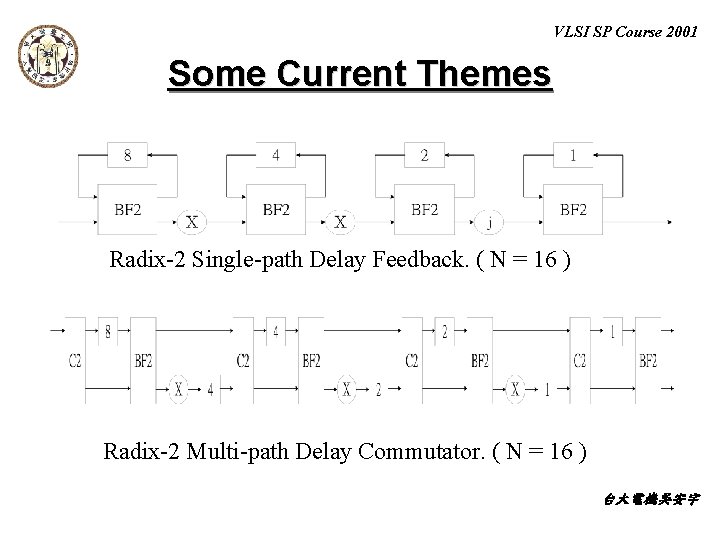

VLSI SP Course 2001 Some Current Themes Radix-2 Single-path Delay Feedback. ( N = 16 ) Radix-2 Multi-path Delay Commutator. ( N = 16 ) 台大電機吳安宇

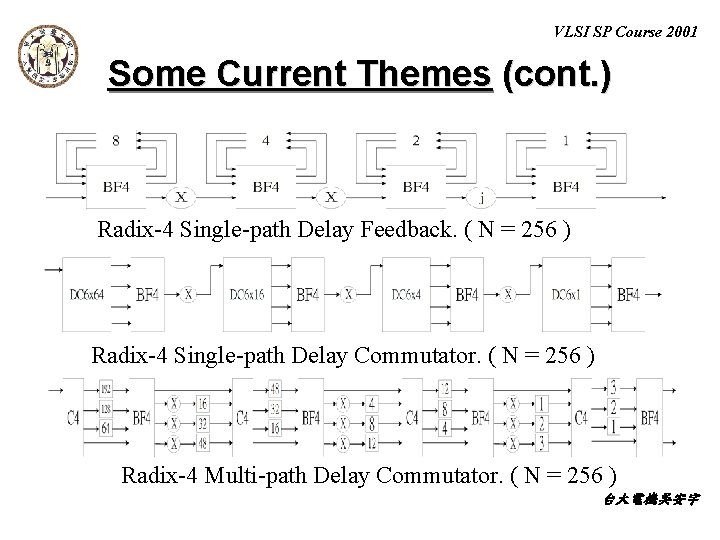

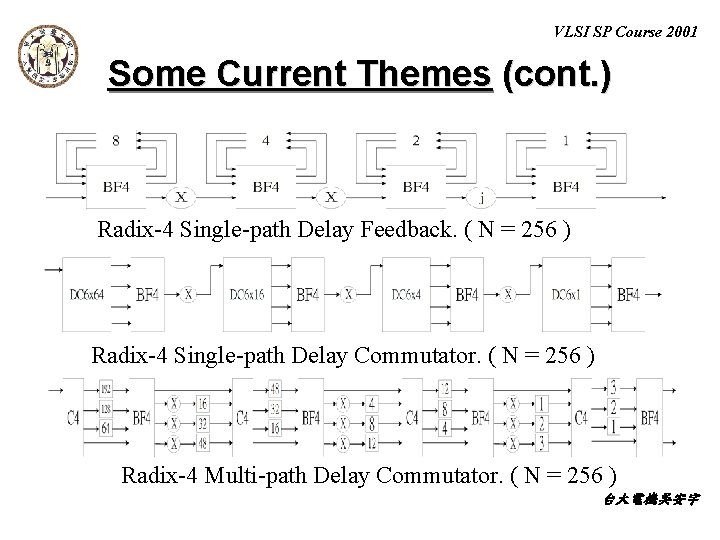

VLSI SP Course 2001 Some Current Themes (cont. ) Radix-4 Single-path Delay Feedback. ( N = 256 ) Radix-4 Single-path Delay Commutator. ( N = 256 ) Radix-4 Multi-path Delay Commutator. ( N = 256 ) 台大電機吳安宇

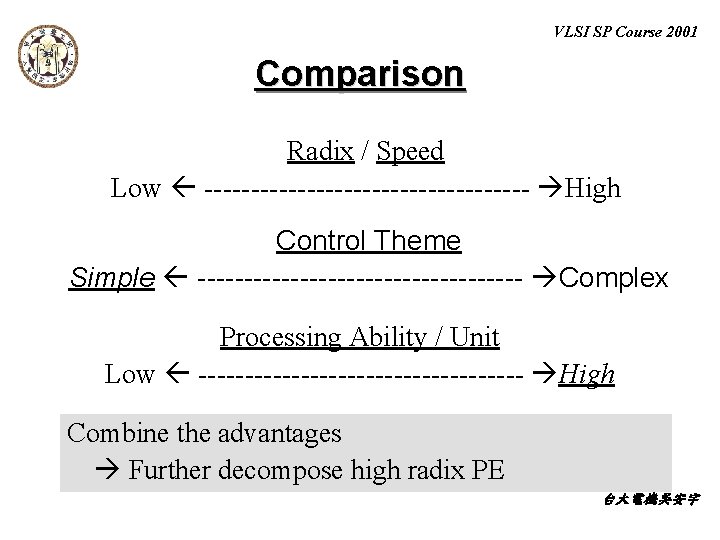

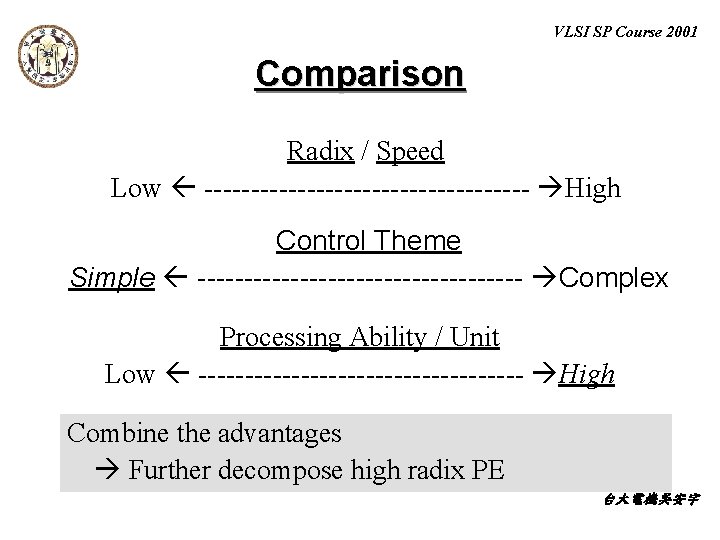

VLSI SP Course 2001 Comparison Radix / Speed Low ------------------ High Control Theme Simple ------------------ Complex Processing Ability / Unit Low ------------------ High Combine the advantages Further decompose high radix PE 台大電機吳安宇

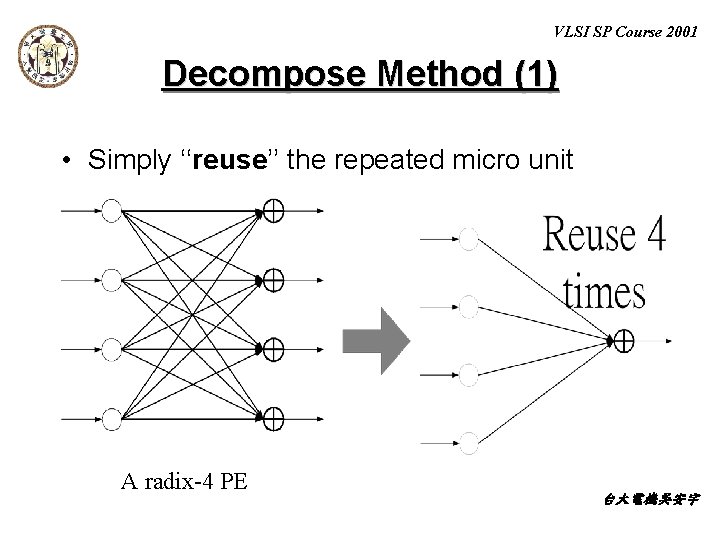

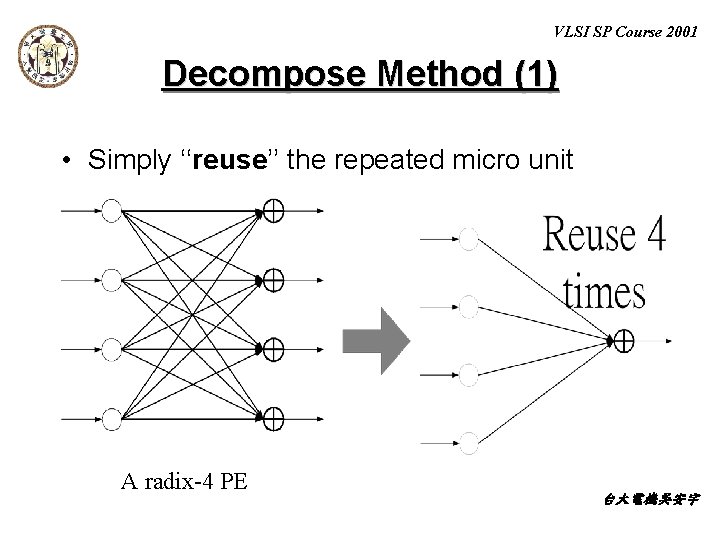

VLSI SP Course 2001 Decompose Method (1) • Simply ‘‘reuse’’ the repeated micro unit A radix-4 PE 台大電機吳安宇

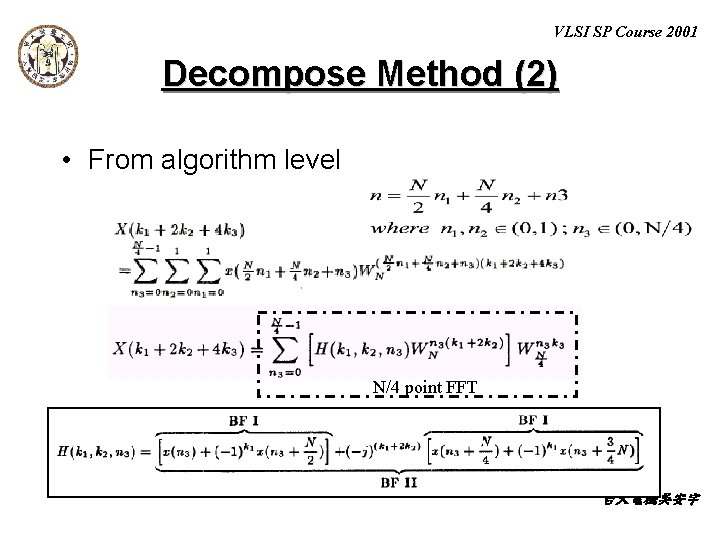

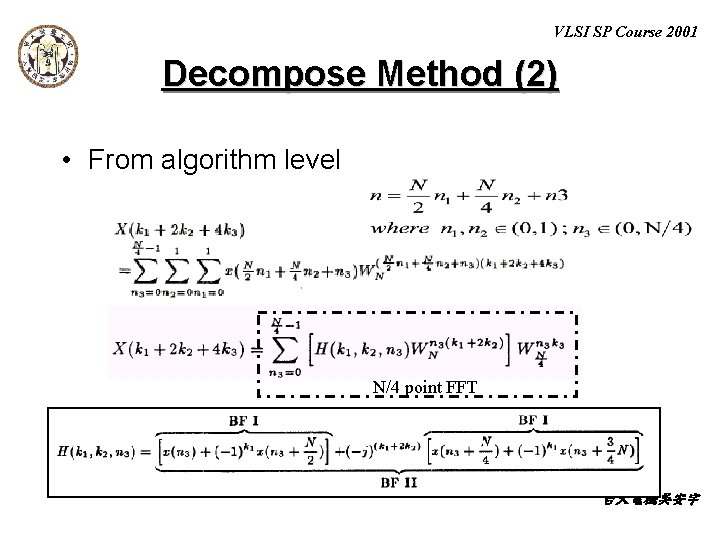

VLSI SP Course 2001 Decompose Method (2) • From algorithm level N/4 point FFT 台大電機吳安宇

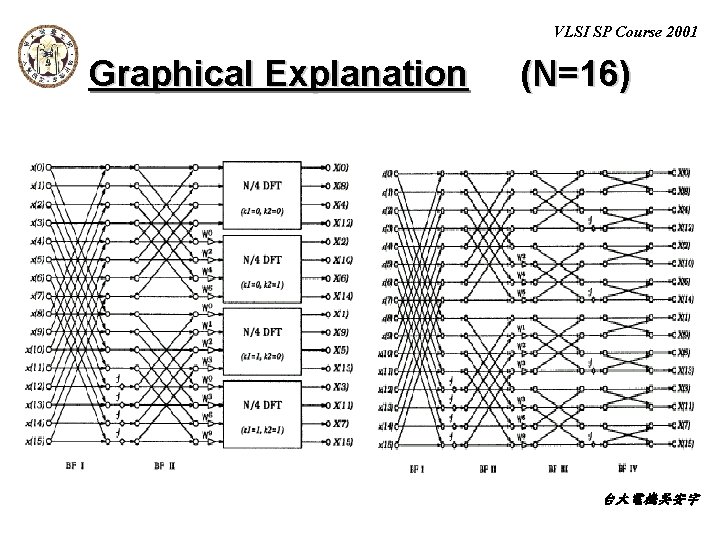

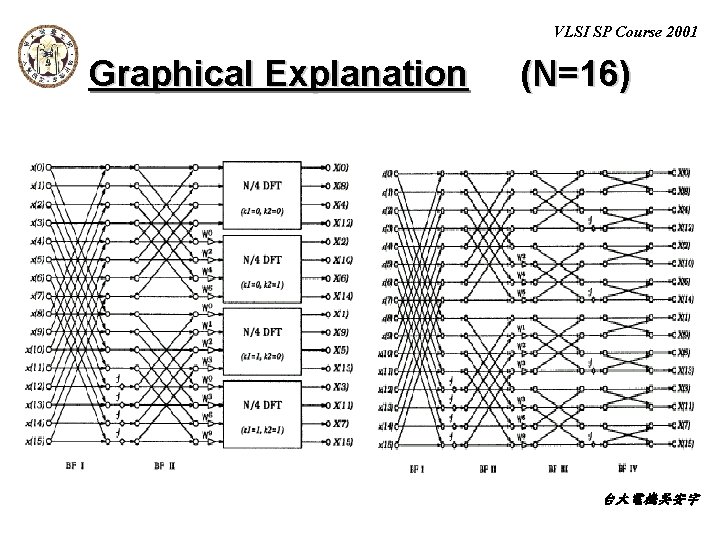

VLSI SP Course 2001 Graphical Explanation (N=16) 台大電機吳安宇

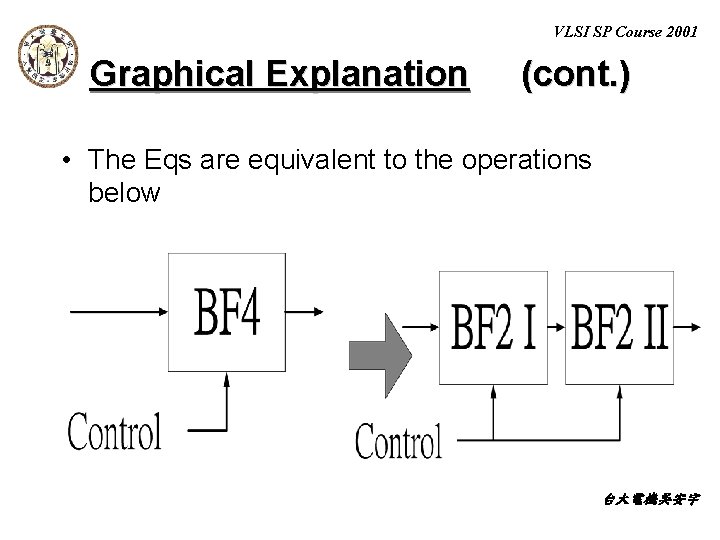

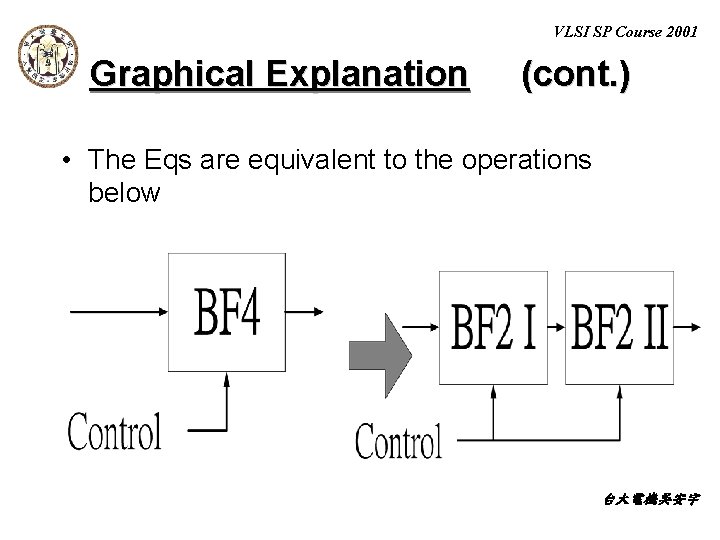

VLSI SP Course 2001 Graphical Explanation (cont. ) • The Eqs are equivalent to the operations below 台大電機吳安宇

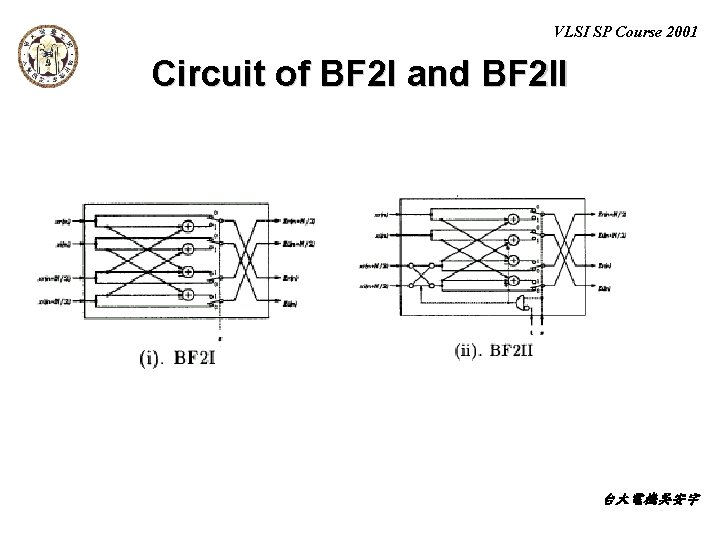

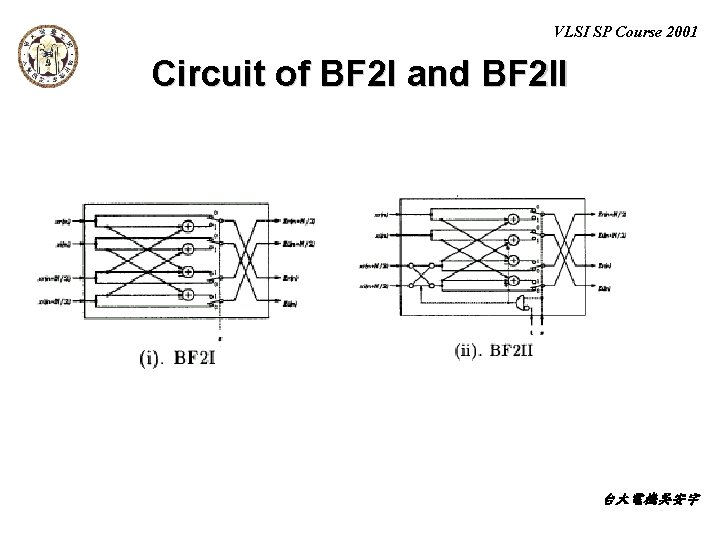

VLSI SP Course 2001 Circuit of BF 2 I and BF 2 II 台大電機吳安宇

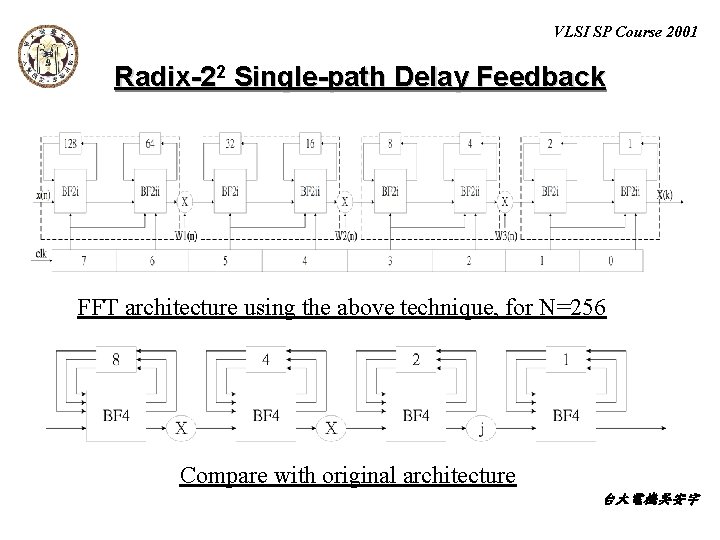

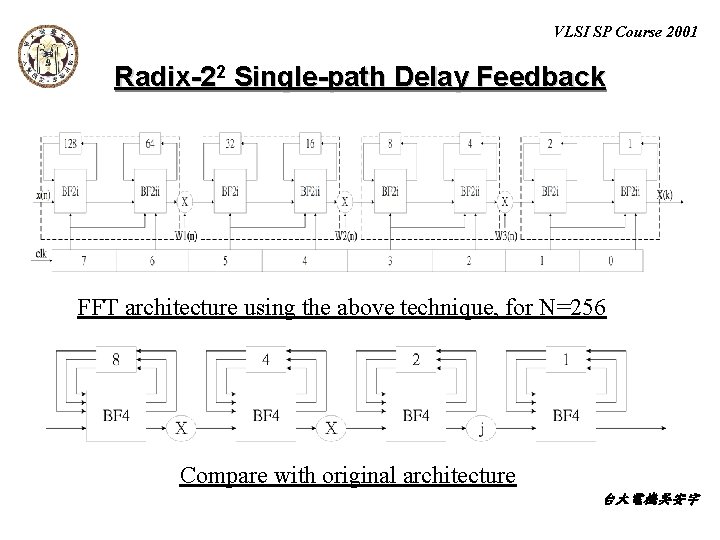

VLSI SP Course 2001 Radix-22 Single-path Delay Feedback FFT architecture using the above technique, for N=256 Compare with original architecture 台大電機吳安宇

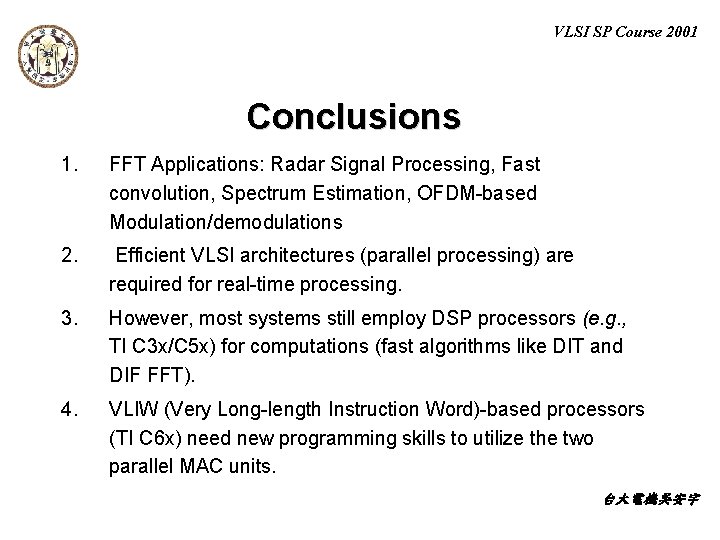

VLSI SP Course 2001 Conclusions 1. FFT Applications: Radar Signal Processing, Fast convolution, Spectrum Estimation, OFDM-based Modulation/demodulations 2. Efficient VLSI architectures (parallel processing) are required for real-time processing. 3. However, most systems still employ DSP processors (e. g. , TI C 3 x/C 5 x) for computations (fast algorithms like DIT and DIF FFT). 4. VLIW (Very Long-length Instruction Word)-based processors (TI C 6 x) need new programming skills to utilize the two parallel MAC units. 台大電機吳安宇