VHDL v What is VHDL An industry standard

- Slides: 109

VHDL v What is VHDL? § An industry standard language used to describe hardware from the abstract to the § concrete level VHSIC Hardware Description Language v VHSIC program § § Very High Speed Integrated Circuit Funded by the USA Department of Defense(DOD). Late 1970 s ~ early 1980 s Goal : To produce the next generation of integrated circuits 광운대학교 전자정보대학 - 2 - 4장. VHDL 개요

VHDL v History of VHDL § Proposed in 1981. • An offshoot of the VHSIC program § The DOD mandated that all digital electronic circuits should be described in VHDL. • F-22 advanced tactical fighter aircraft was one of the first major government programs to mandate the use of VHDL descriptions for all electronic subsystems in the project. § Adopted as the IEEE standard in December 1987. • Institute of Electrical and Electronics Engineers • IEEE 1076 -1987 Standard VHDL § Revised to IEEE 1076 -1993. 광운대학교 전자정보대학 - 3 - 4장. VHDL 개요

VHDL v Why proposed VHDL ? § The tools that were available to the designers were mostly based at the gate level. § The gate-level tools were inadequate for large designs. v Goals of VHDL § A language that could describe the complex circuits that the designers were trying § to describe A language that was a standard 광운대학교 전자정보대학 - 4 - 4장. VHDL 개요

VHDL v Applications of VHDL § Documentation § Simulation • The process of verifying the functional and/or timing characteristics of hardware models at any level of behavior from the abstract to the concrete level § Synthesis • The process of translating an abstract-level model of hardware into an optimized technology-specific gate-level implementation • Currently RTL(Register Transfer Level) synthesis 광운대학교 전자정보대학 - 5 - 4장. VHDL 개요

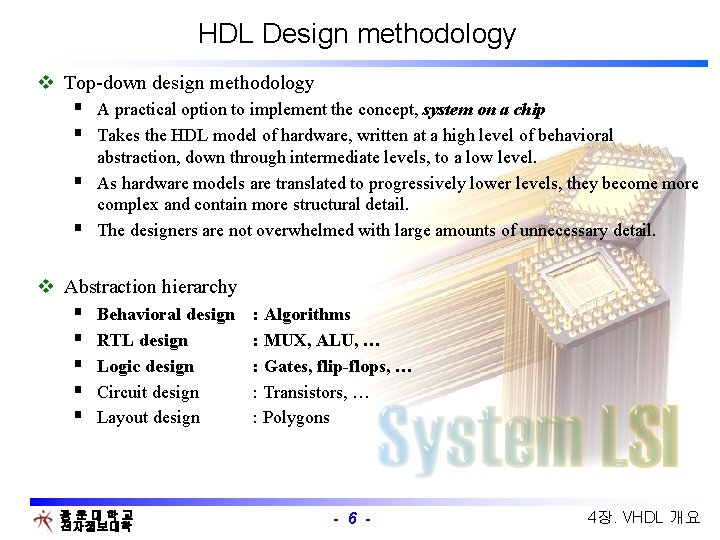

HDL Design methodology v Top-down design methodology § A practical option to implement the concept, system on a chip § Takes the HDL model of hardware, written at a high level of behavioral § § abstraction, down through intermediate levels, to a low level. As hardware models are translated to progressively lower levels, they become more complex and contain more structural detail. The designers are not overwhelmed with large amounts of unnecessary detail. v Abstraction hierarchy § § § Behavioral design RTL design Logic design Circuit design Layout design 광운대학교 전자정보대학 : Algorithms : MUX, ALU, … : Gates, flip-flops, … : Transistors, … : Polygons - 6 - 4장. VHDL 개요

Top-down Design v Advantages of top-down design methodology § Increased productivity yields shorter development cycles with more product § § § § features and reduced time to market. Reduced NRE (Non-Recurring Engineering) costs Design reuse is enabled. Increased flexibility to design changes Faster exploration of alternative architectures Faster exploration of alternative technology libraries Enables use of synthesis to rapidly sweep the design space of area and timing, and to automatically generate testable circuits. Better and easier design auditing and verification 광운대학교 전자정보대학 - 7 - 4장. VHDL 개요

FPGA 와 ASIC v FPGA and ASIC § Typical applications of top-down design methodology § The function is not fixed by the manufacturer. § The function is defined by the designer for a particular application. v FPGA (Field Programmable Gate Array) § A device that is completely manufactured, but that remains design independent § Each FPGA vendor manufactures devices with a proprietary architecture. § The architecture will include a number of logic blocks that are connected to § programmable switching matrices. The switching matrices are programmed to route signals between the individual logic blocks. 광운대학교 전자정보대학 - 8 - 4장. VHDL 개요

FPGA 와 ASIC v ASIC (Application Specific Integrated Circuit) § Partially manufactured by an ASIC vendor in generic form. § A chip with an array of unconnected transistors § The final manufacturing process of connecting the transistors is completed when a § chip designer has a specific design. An ASIC vendor can usually do the final process in a couple of weeks, known as the turn-around time. 광운대학교 전자정보대학 - 9 - 4장. VHDL 개요

ASIC Design v Traditional design flow for ASIC (schematic-based) § § § Schematic capture Netlist extraction Logic simulation Placement and routing Parasitic RC extraction and re-simulation (back annotation) Fabrication, assembly and test 광운대학교 전자정보대학 - 10 - 4장. VHDL 개요

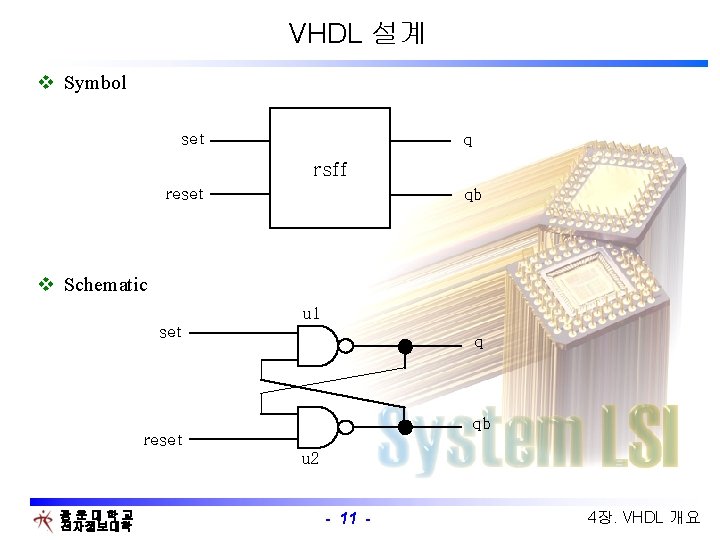

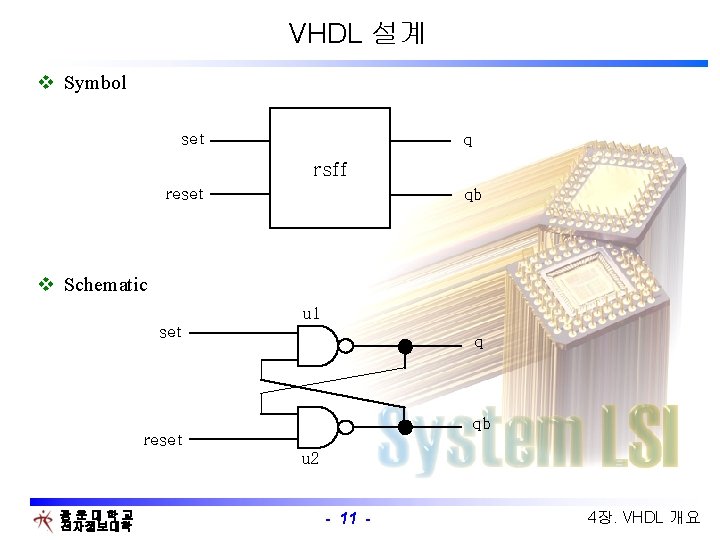

VHDL 설계 v Symbol set q rsff reset qb v Schematic u 1 set q qb reset u 2 광운대학교 전자정보대학 - 11 - 4장. VHDL 개요

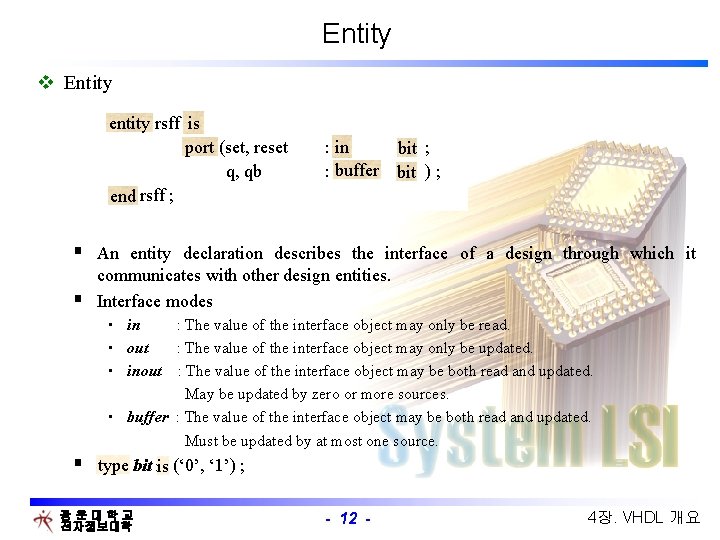

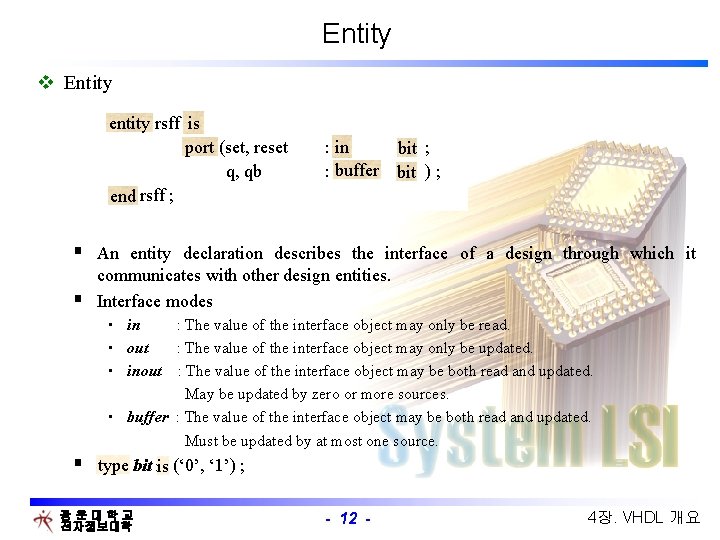

Entity v Entity entity is entity rsff is port (set, reset q, qb end rsff ; end : in in buffer : buffer bit ; bit ) ; bit § An entity declaration describes the interface of a design through which it § communicates with other design entities. Interface modes • in : The value of the interface object may only be read. • out : The value of the interface object may only be updated. • inout : The value of the interface object may be both read and updated. May be updated by zero or more sources. • buffer : The value of the interface object may be both read and updated. Must be updated by at most one source. type § type bit is (‘ 0’, ‘ 1’) ; is 광운대학교 전자정보대학 - 12 - 4장. VHDL 개요

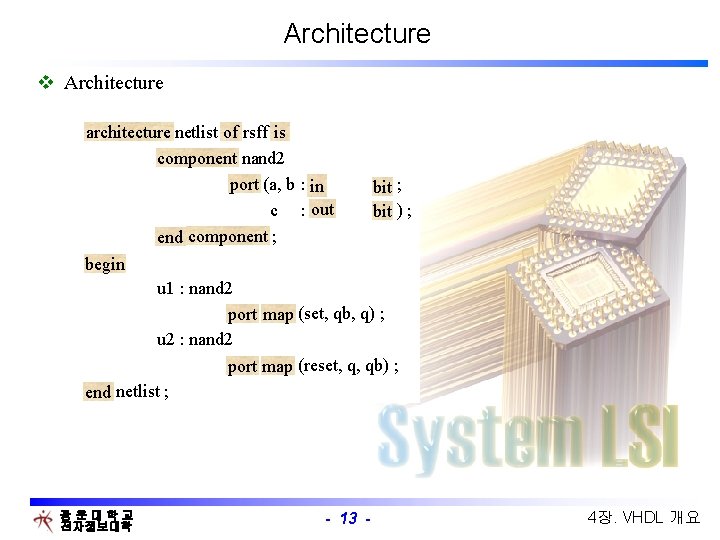

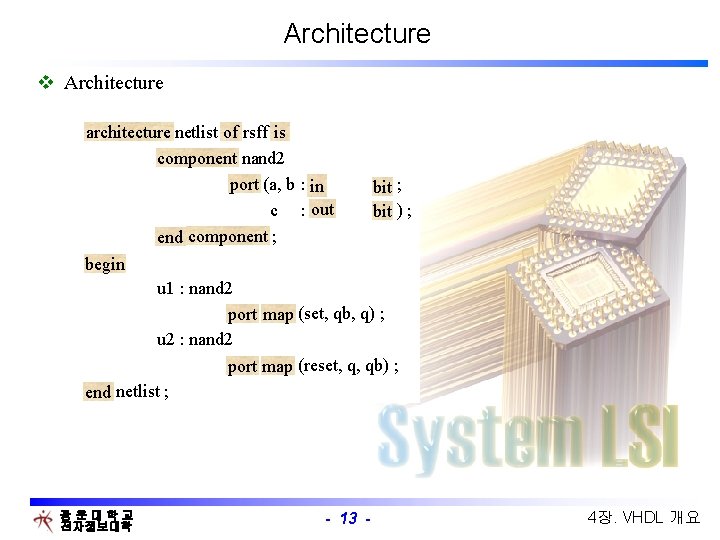

Architecture v Architecture architecture of is architecture netlist of rsff is component nand 2 component port (a, b : in bit ; port in bit out c : out bit ) ; bit end component ; end component begin u 1 : nand 2 port map (set, qb, q) ; port map u 2 : nand 2 port map (reset, q, qb) ; port map end netlist ; end 광운대학교 전자정보대학 - 13 - 4장. VHDL 개요

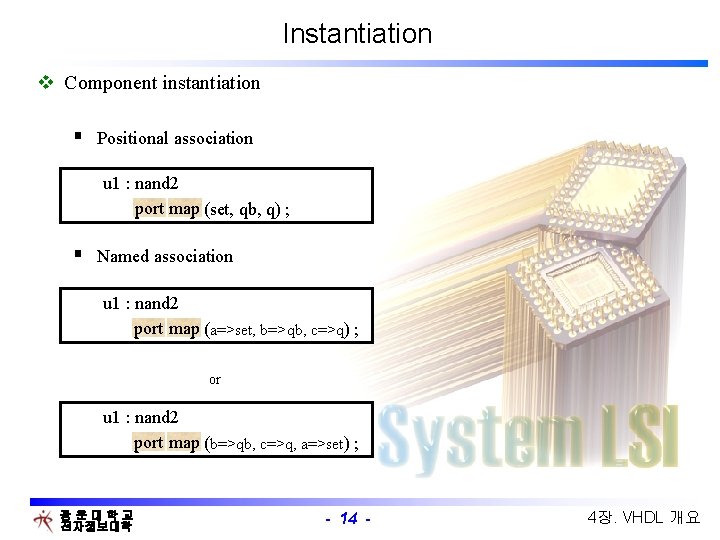

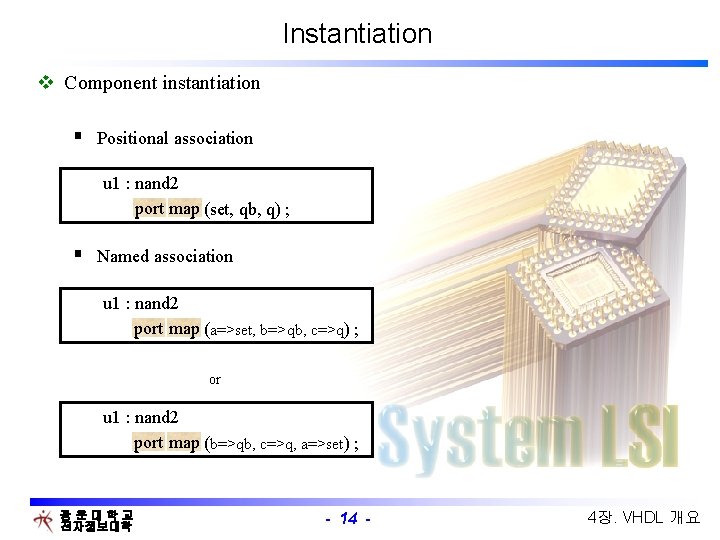

Instantiation v Component instantiation § Positional association u 1 : nand 2 port map (set, qb, q) ; § Named association u 1 : nand 2 port map a=>set, b=>qb, c=>q) ; port map ( or u 1 : nand 2 port map b=>qb, c=>q, a=>set) ; port map ( 광운대학교 전자정보대학 - 14 - 4장. VHDL 개요

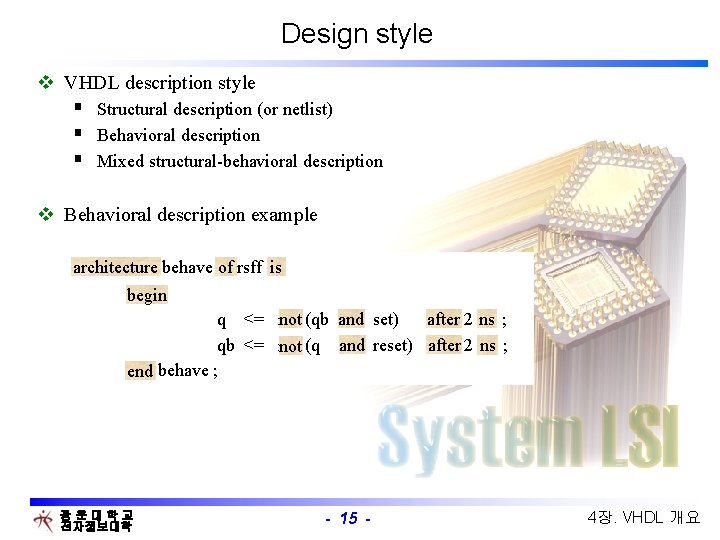

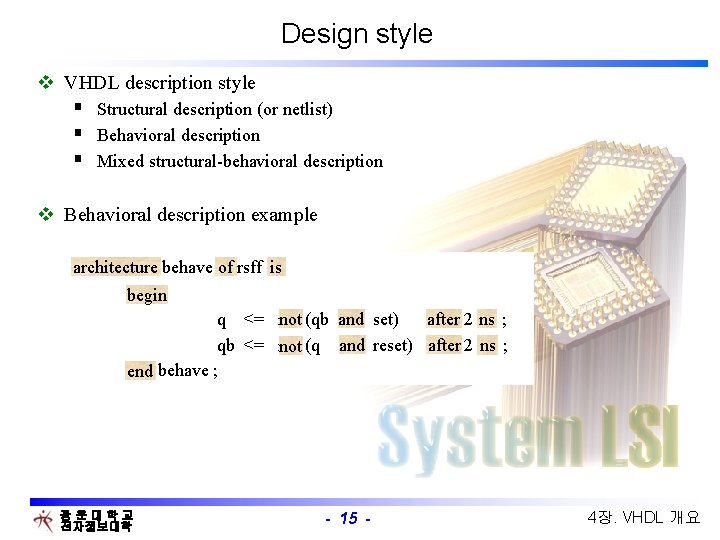

Design style v VHDL description style § Structural description (or netlist) § Behavioral description § Mixed structural-behavioral description v Behavioral description example architecture behave of rsff is architecture of is begin after ns q <= not (qb and set) after 2 ns ; not and qb <= not (q and reset) after 2 ns ; and after ns not end behave ; end 광운대학교 전자정보대학 - 15 - 4장. VHDL 개요

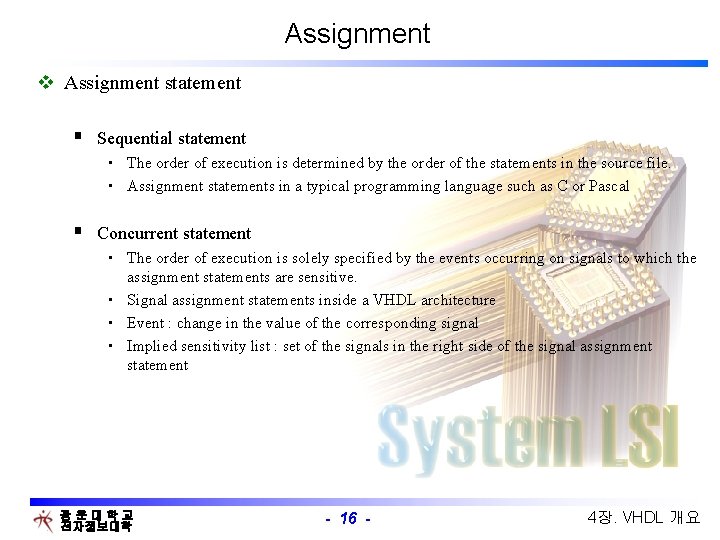

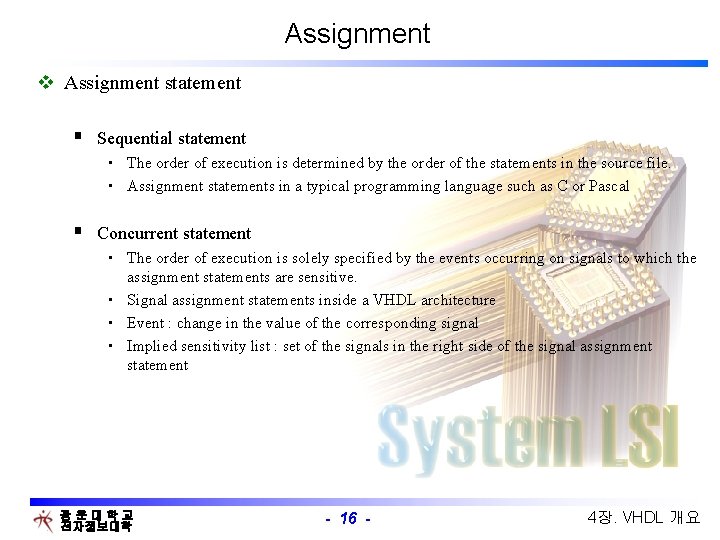

Assignment v Assignment statement § Sequential statement • The order of execution is determined by the order of the statements in the source file. • Assignment statements in a typical programming language such as C or Pascal § Concurrent statement • The order of execution is solely specified by the events occurring on signals to which the assignment statements are sensitive. • Signal assignment statements inside a VHDL architecture • Event : change in the value of the corresponding signal • Implied sensitivity list : set of the signals in the right side of the signal assignment statement 광운대학교 전자정보대학 - 16 - 4장. VHDL 개요

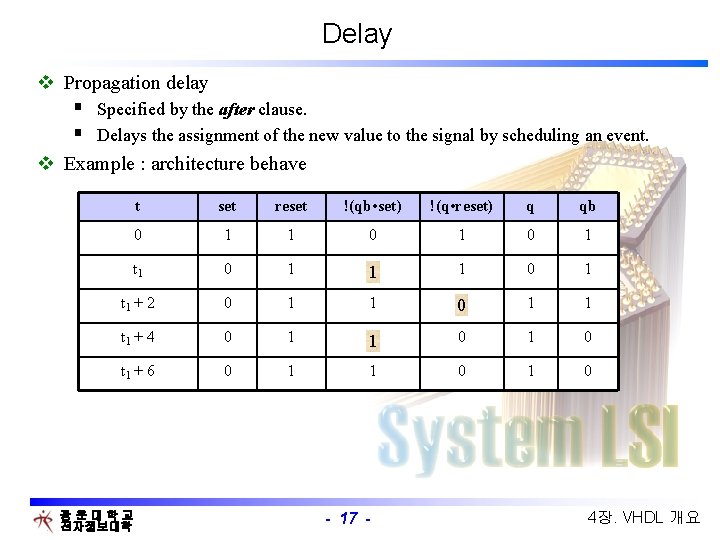

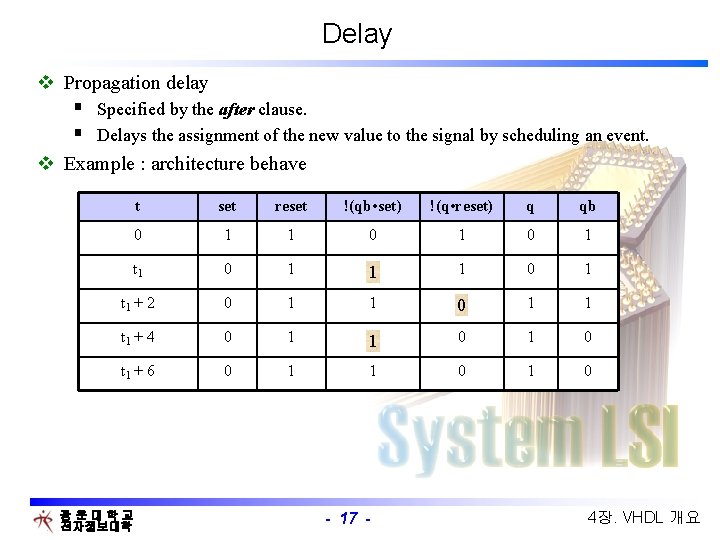

Delay v Propagation delay § Specified by the after clause. § Delays the assignment of the new value to the signal by scheduling an event. v Example : architecture behave t set reset !(qb • set) !(q • reset) q qb 0 1 1 0 1 t 1 0 1 11 1 0 1 t 1 + 2 0 1 1 00 1 1 t 1 + 4 0 1 11 0 t 1 + 6 0 1 1 0 광운대학교 전자정보대학 - 17 - 4장. VHDL 개요

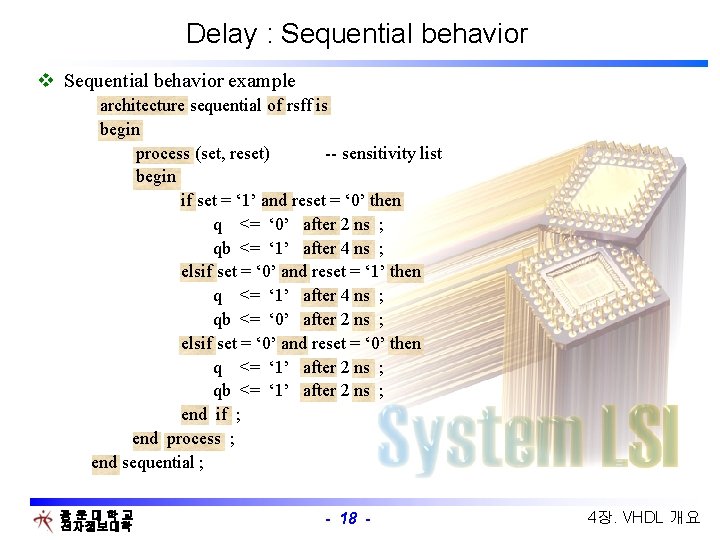

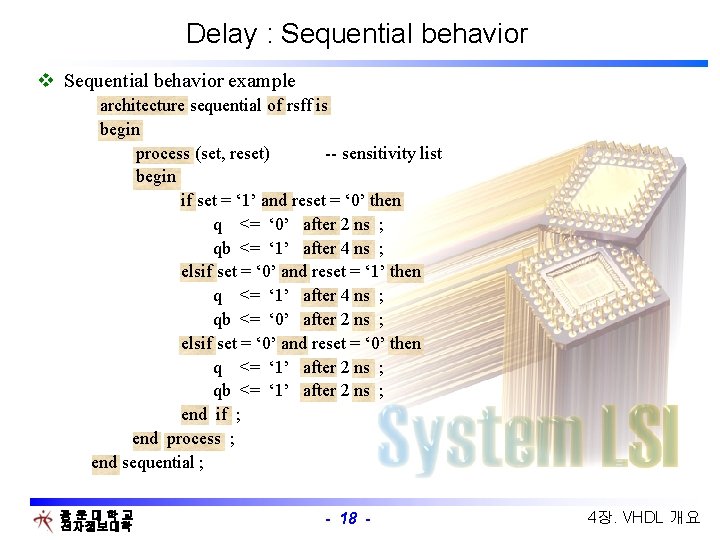

Delay : Sequential behavior v Sequential behavior example architecture sequential of rsff is begin process (set, reset) -- sensitivity list begin if set = ‘ 1’ and reset = ‘ 0’ then q <= ‘ 0’ after 2 ns ; qb <= ‘ 1’ after 4 ns ; elsif set = ‘ 0’ and reset = ‘ 1’ then q <= ‘ 1’ after 4 ns ; qb <= ‘ 0’ after 2 ns ; elsif set = ‘ 0’ and reset = ‘ 0’ then q <= ‘ 1’ after 2 ns ; qb <= ‘ 1’ after 2 ns ; end if ; end process ; end sequential ; 광운대학교 전자정보대학 - 18 - 4장. VHDL 개요

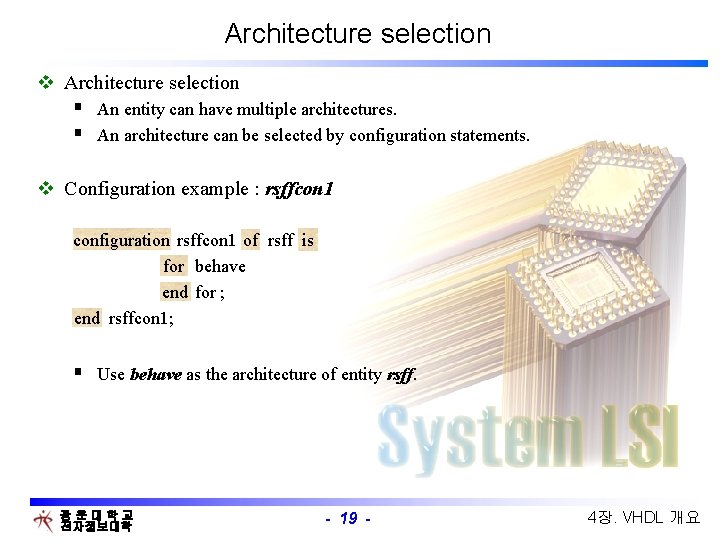

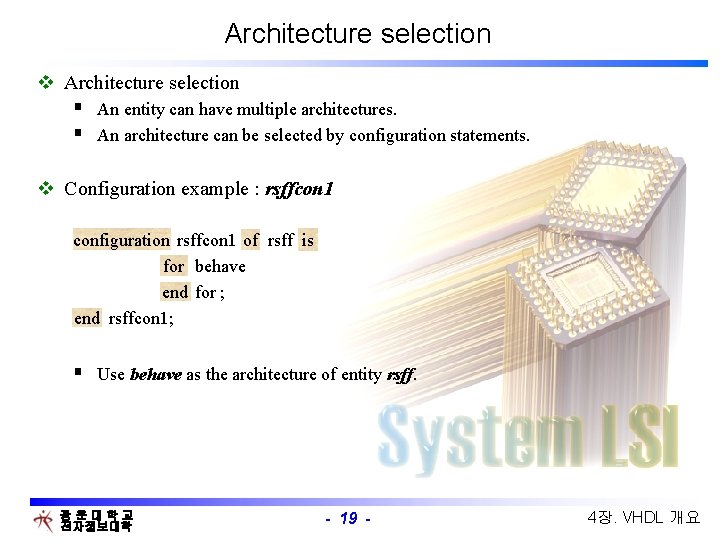

Architecture selection v Architecture selection § An entity can have multiple architectures. § An architecture can be selected by configuration statements. v Configuration example : rsffcon 1 configuration rsffcon 1 rsff of is for behave for ; end rsffcon 1; end § Use behave as the architecture of entity rsff. 광운대학교 전자정보대학 - 19 - 4장. VHDL 개요

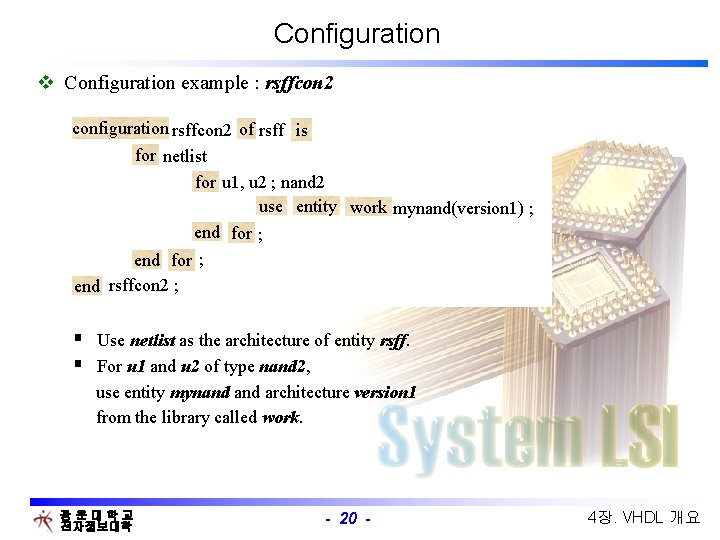

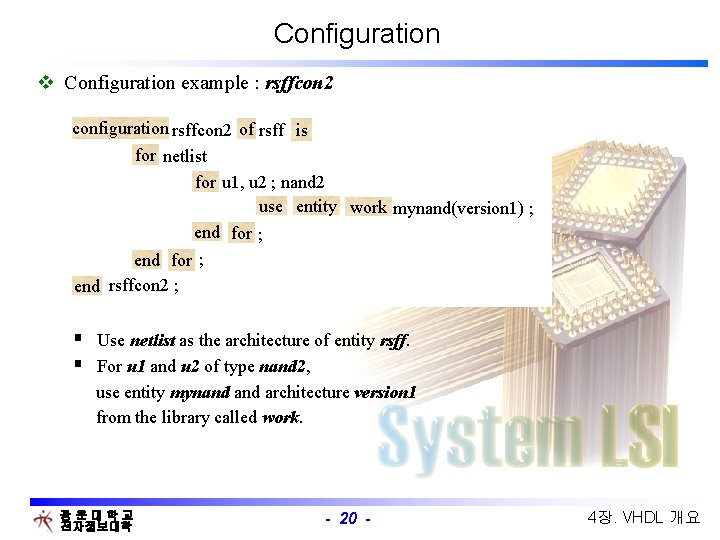

Configuration v Configuration example : rsffcon 2 configuration of rsffcon 2 rsff is for netlist u 1, u 2 ; nand 2 for use entity work mynand(version 1) ; end for ; end for rsffcon 2 ; end § Use netlist as the architecture of entity rsff. § For u 1 and u 2 of type nand 2, use entity mynand architecture version 1 from the library called work. 광운대학교 전자정보대학 - 20 - 4장. VHDL 개요

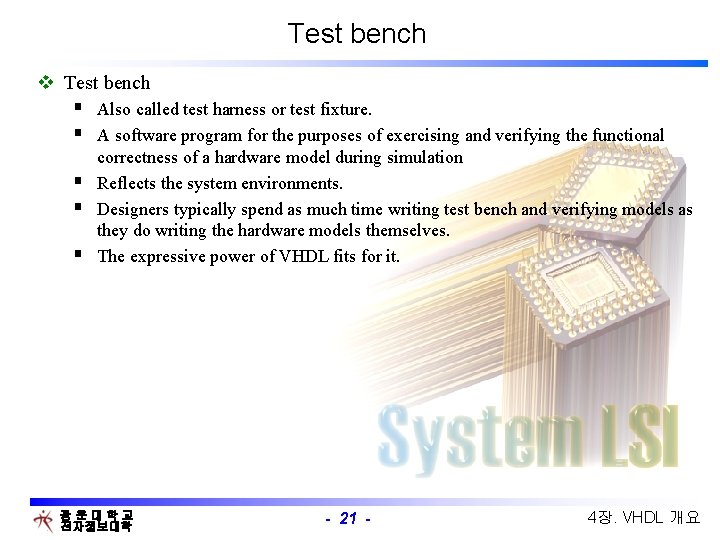

Test bench v Test bench § Also called test harness or test fixture. § A software program for the purposes of exercising and verifying the functional § § § correctness of a hardware model during simulation Reflects the system environments. Designers typically spend as much time writing test bench and verifying models as they do writing the hardware models themselves. The expressive power of VHDL fits for it. 광운대학교 전자정보대학 - 21 - 4장. VHDL 개요

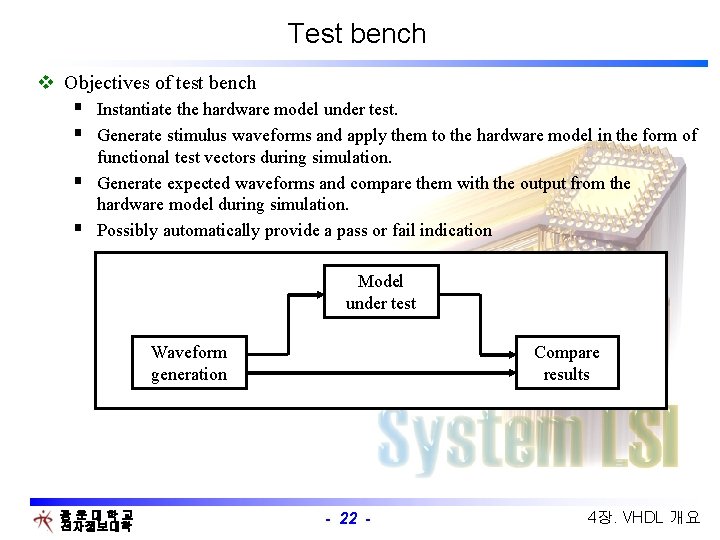

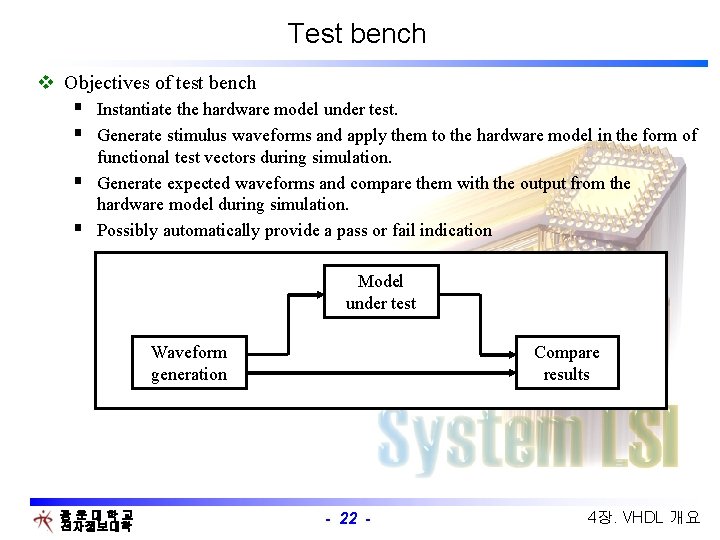

Test bench v Objectives of test bench § Instantiate the hardware model under test. § Generate stimulus waveforms and apply them to the hardware model in the form of § § functional test vectors during simulation. Generate expected waveforms and compare them with the output from the hardware model during simulation. Possibly automatically provide a pass or fail indication Model under test Waveform generation 광운대학교 전자정보대학 Compare results - 22 - 4장. VHDL 개요

Test bench v Advantages of writing a test bench in VHDL § There is no need to learn a special simulation tool or special language. § Since VHDL is an IEEE standardized language, models and their associated test § bench should be transportable across different design tools. VHDL has rich simulation semantics that can be fully exploited in a test bench 광운대학교 전자정보대학 - 23 - 4장. VHDL 개요

Test bench : Example v Clock waveform generation example entity clock_gen is entity is end clock_gen ; end architecture for_test_bench of clock_gen is architecture of is signal Clock. Fast, Clock. Med, Clock. Slow : bit : = ‘ 0’ ; signal bit begin Clock. Fast <= not Clock. Fast after 10 ns ; not after ns Clock. Med <= ‘ 1’ after 20 ns when Clock. Med = ‘ 0’ else after ns when else after ns ‘ 0’ after 20 ns ; process begin wait for ns wait for 30 ns ; Clock. Slow <= ‘ 1’ ; wait for 30 ns ; Clock. Slow <= ‘ 0’ ; wait for ns end process; end process end for_test_bench ; 광운대학교 전자정보대학 - 24 - 4장. VHDL 개요

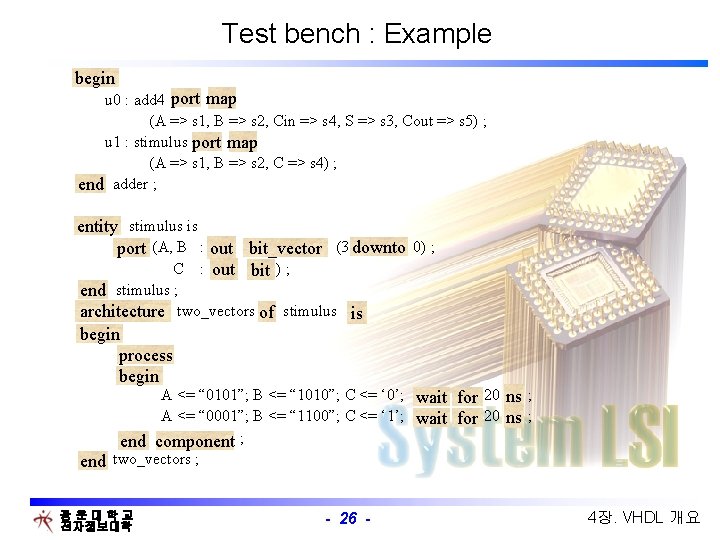

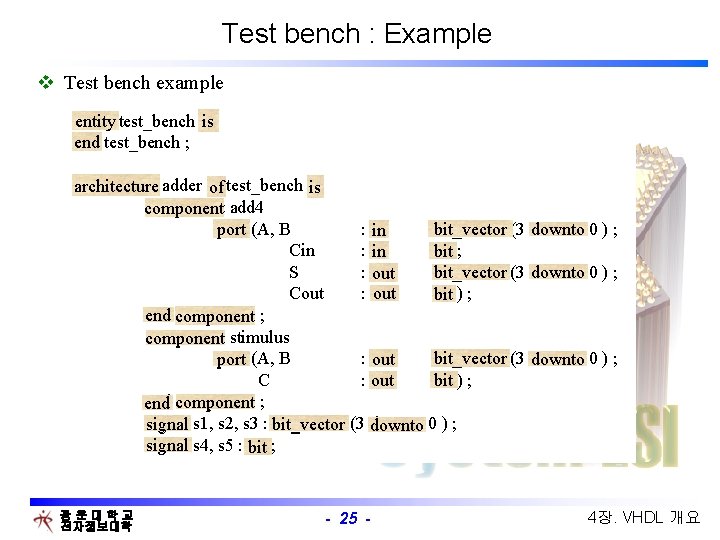

Test bench : Example v Test bench example entity test_bench is entity is end test_bench ; end architecture adder of test_bench is architecture is of component add 4 component port (A, B : in bit_vector (3 downto 0 ) ; port bit_vector downto in Cin : in bit ; in bit S : out bit_vector (3 downto 0 ) ; bit_vector downto out Cout : out bit ) ; out bit end component ; end component stimulus component port (A, B : out bit_vector (3 downto 0 ) ; bit_vector downto port out C : out bit ) ; bit out end component ; component end signal s 1, s 2, s 3 : bit_vector (3 downto 0 ) ; signal bit_vector downto signal s 4, s 5 : bit ; signal bit 광운대학교 전자정보대학 - 25 - 4장. VHDL 개요

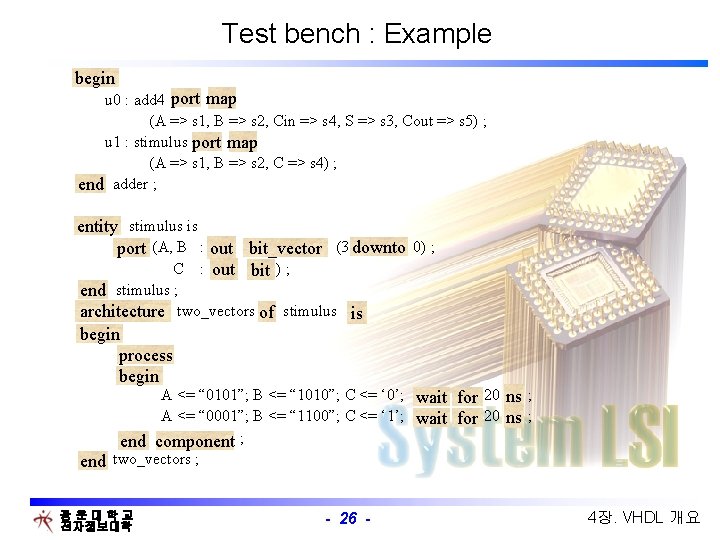

Test bench : Example begin u 0 : add 4 port map (A => s 1, B => s 2, Cin => s 4, S => s 3, Cout => s 5) ; u 1 : stimulus port map (A => s 1, B => s 2, C => s 4) ; adder ; end stimulus is entity (A, B : (3 0) ; downto out bit_vector port C : ) ; out bit stimulus ; end two_vectors stimulus architecture of is begin process begin A <= “ 0101”; B <= “ 1010”; C <= ‘ 0’; 20 ; ns wait for A <= “ 0001”; B <= “ 1100”; C <= ‘ 1’; 20 ; ns wait for ; end component two_vectors ; end 광운대학교 전자정보대학 - 26 - 4장. VHDL 개요

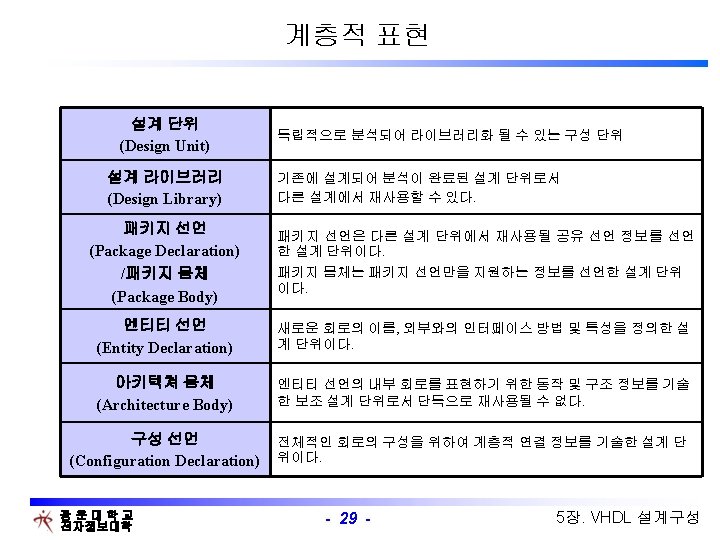

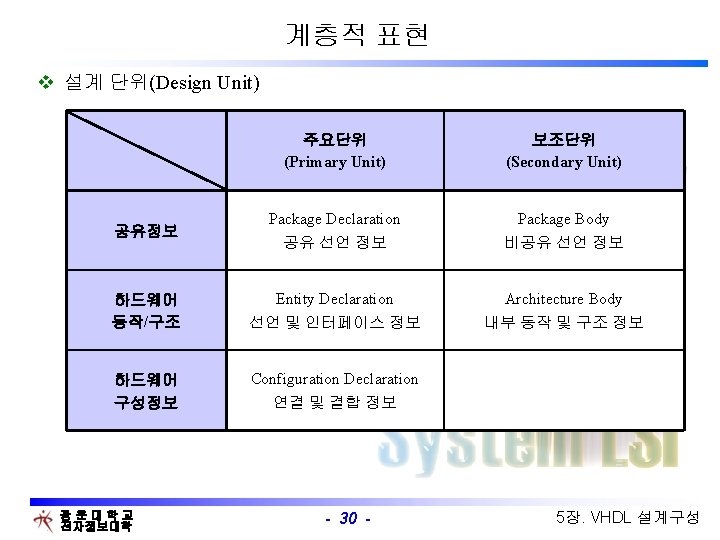

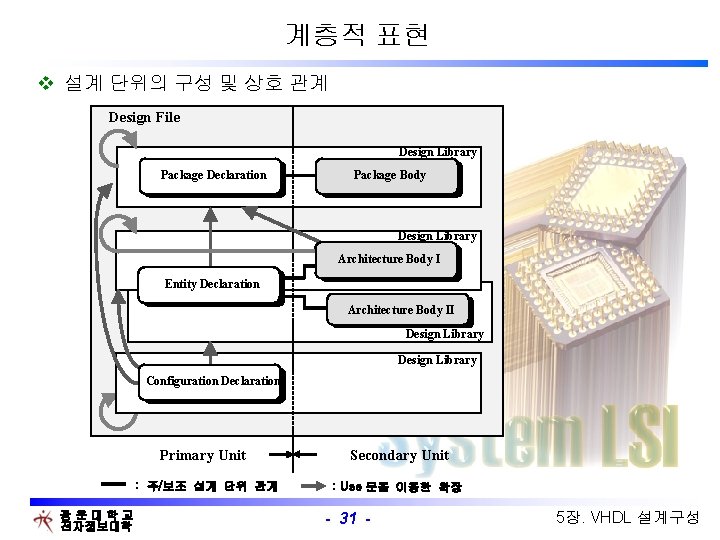

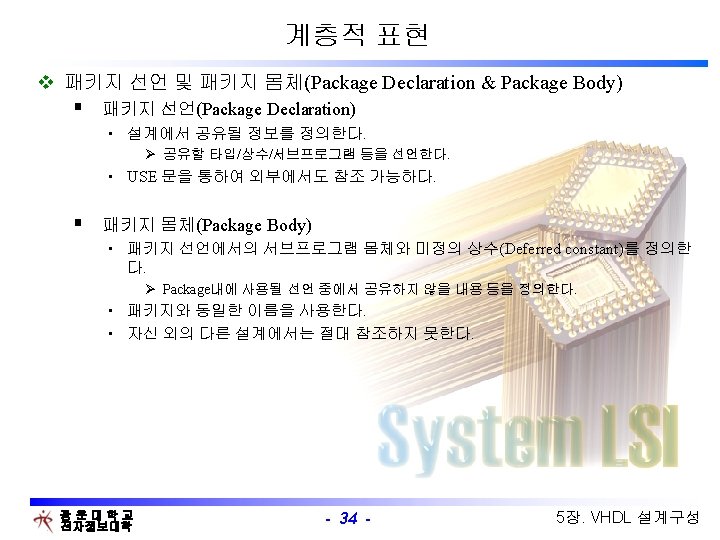

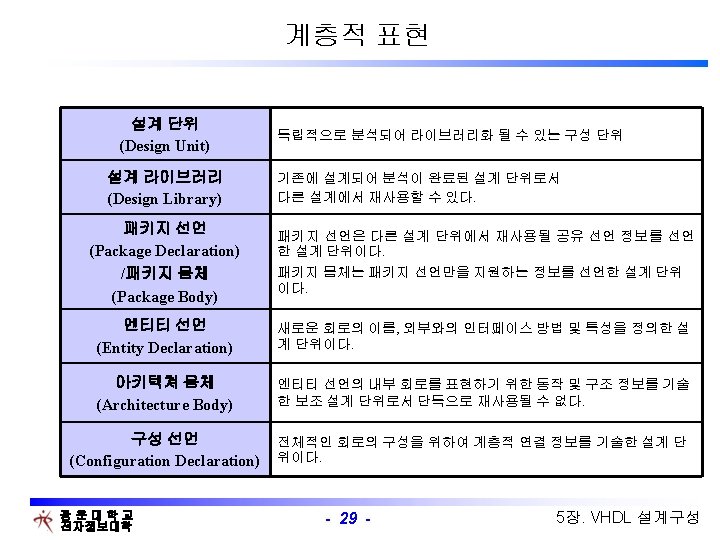

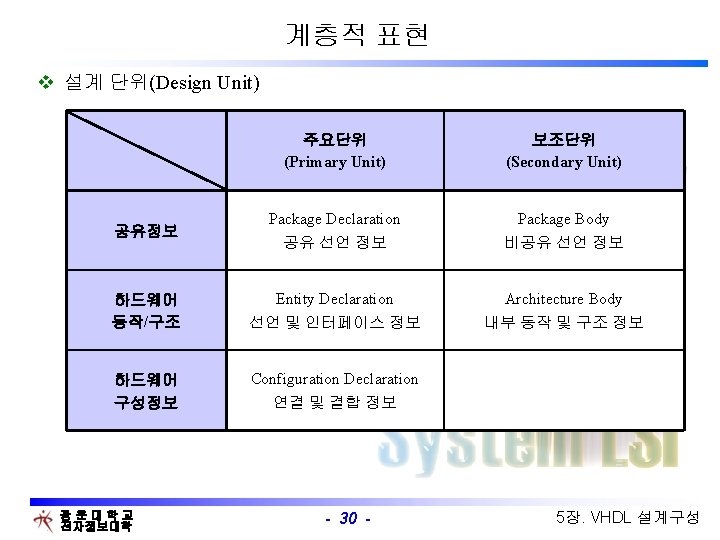

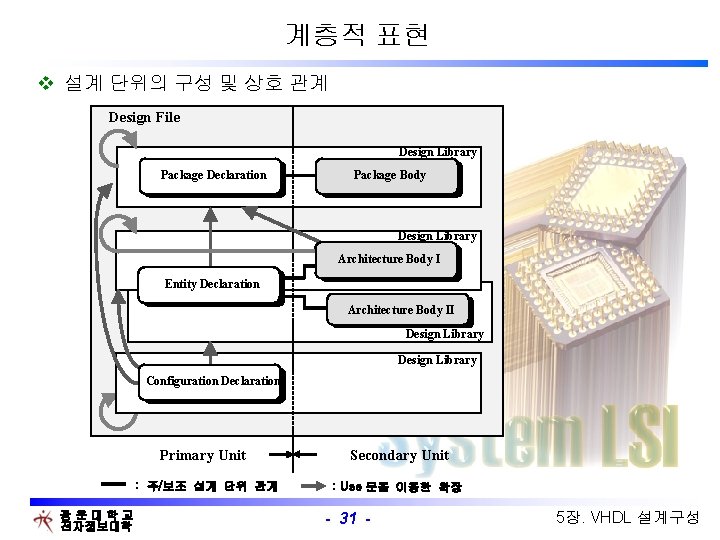

계층적 표현 v 설계 단위의 구성 및 상호 관계 Design File Design Library Package Declaration Package Body Design Library Architecture Body I Entity Declaration Architecture Body II Design Library Configuration Declaration Primary Unit : 주/보조 설계 단위 관계 광운대학교 전자정보대학 Secondary Unit : Use 문을 이용한 확장 - 31 - 5장. VHDL 설계구성

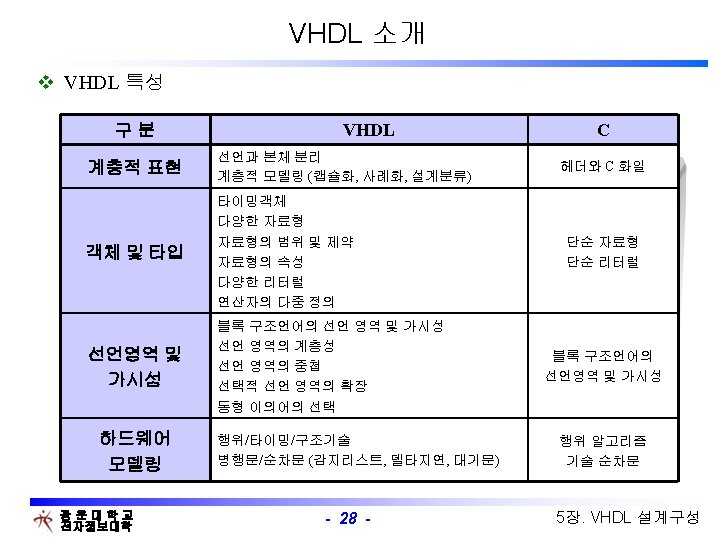

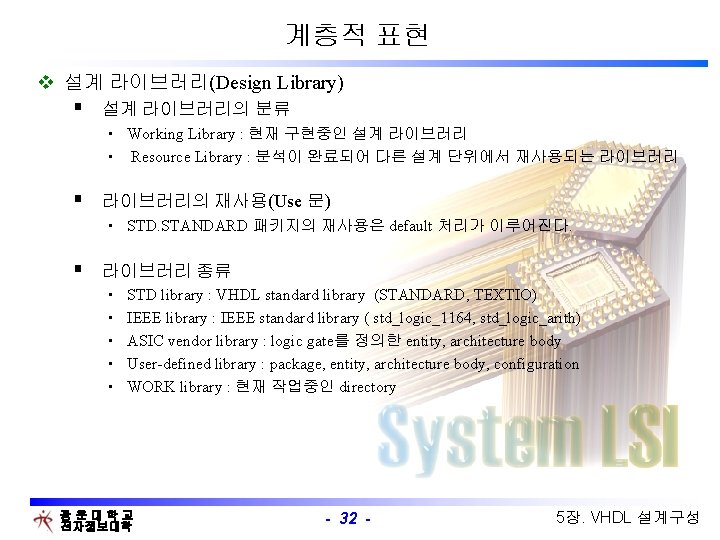

계층적 표현 v 설계 라이브러리(Design Library) § 설계 라이브러리의 분류 • Working Library : 현재 구현중인 설계 라이브러리 • Resource Library : 분석이 완료되어 다른 설계 단위에서 재사용되는 라이브러리 § 라이브러리의 재사용(Use 문) • STD. STANDARD 패키지의 재사용은 default 처리가 이루어진다. § 라이브러리 종류 • STD library : VHDL standard library (STANDARD, TEXTIO) • IEEE library : IEEE standard library ( std_logic_1164, std_logic_arith) • ASIC vendor library : logic gate를 정의한 entity, architecture body • User-defined library : package, entity, architecture body, configuration • WORK library : 현재 작업중인 directory 광운대학교 전자정보대학 - 32 - 5장. VHDL 설계구성

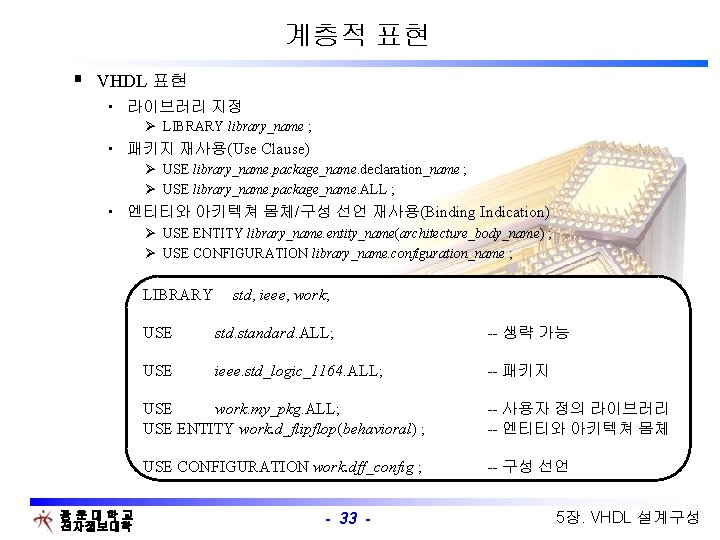

계층적 표현 § VHDL 표현 • 라이브러리 지정 Ø LIBRARY library_name ; • 패키지 재사용(Use Clause) Ø USE library_name. package_name. declaration_name ; Ø USE library_name. package_name. ALL ; • 엔티티와 아키텍쳐 몸체/구성 선언 재사용(Binding Indication) Ø USE ENTITY library_name. entity_name(architecture_body_name) ; Ø USE CONFIGURATION library_name. configuration_name ; LIBRARY std, ieee, work; USE std. standard. ALL; -- 생략 가능 USE ieee. std_logic_1164. ALL; -- 패키지 USE work. my_pkg. ALL; -- 사용자 정의 라이브러리 USE ENTITY work. d_flipflop(behavioral) ; -- 엔티티와 아키텍쳐 몸체 USE CONFIGURATION work. dff_config ; -- 구성 선언 광운대학교 전자정보대학 - 33 - 5장. VHDL 설계구성

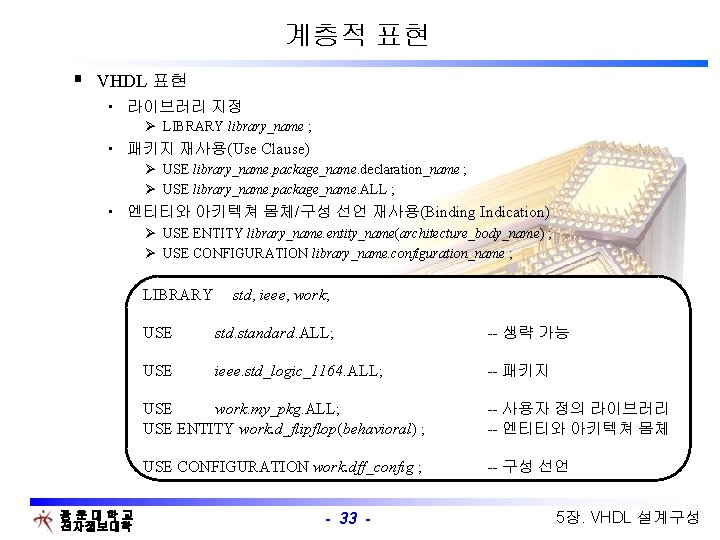

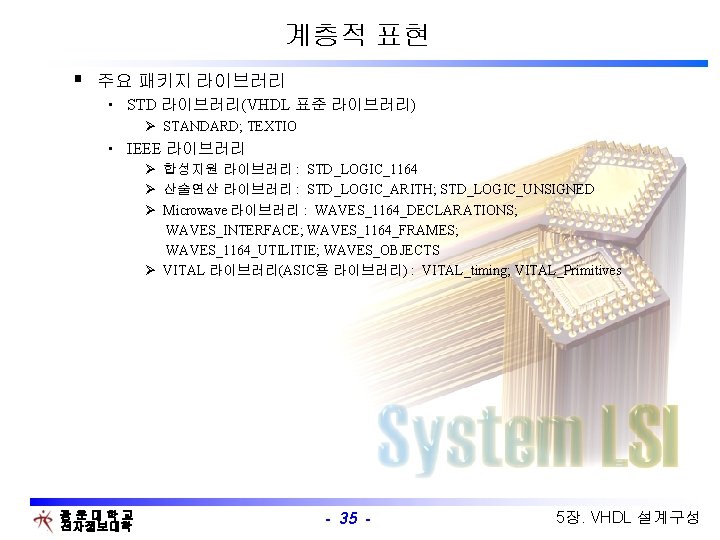

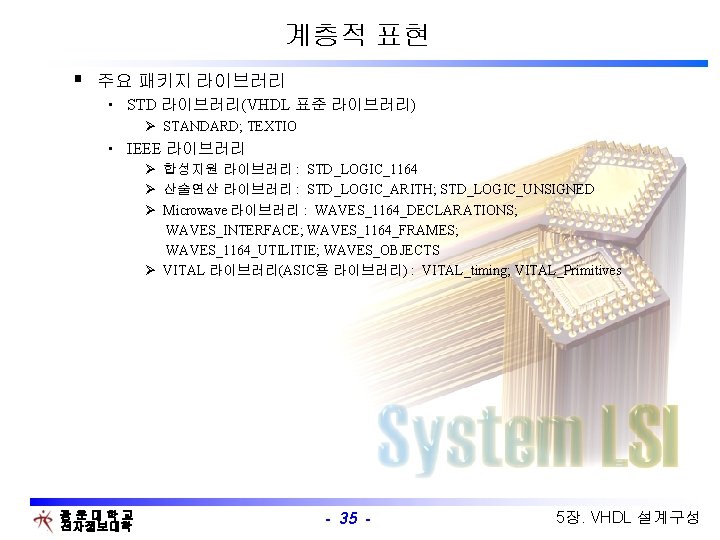

계층적 표현 § 주요 패키지 라이브러리 • STD 라이브러리(VHDL 표준 라이브러리) Ø STANDARD; TEXTIO • IEEE 라이브러리 Ø 합성지원 라이브러리 : STD_LOGIC_1164 Ø 산술연산 라이브러리 : STD_LOGIC_ARITH; STD_LOGIC_UNSIGNED Ø Microwave 라이브러리 : WAVES_1164_DECLARATIONS; WAVES_INTERFACE; WAVES_1164_FRAMES; WAVES_1164_UTILITIE; WAVES_OBJECTS Ø VITAL 라이브러리(ASIC용 라이브러리) : VITAL_timing; VITAL_Primitives 광운대학교 전자정보대학 - 35 - 5장. VHDL 설계구성

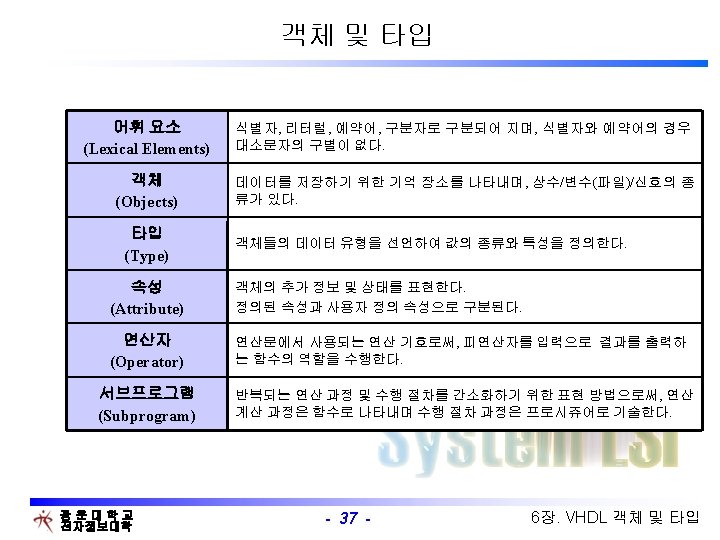

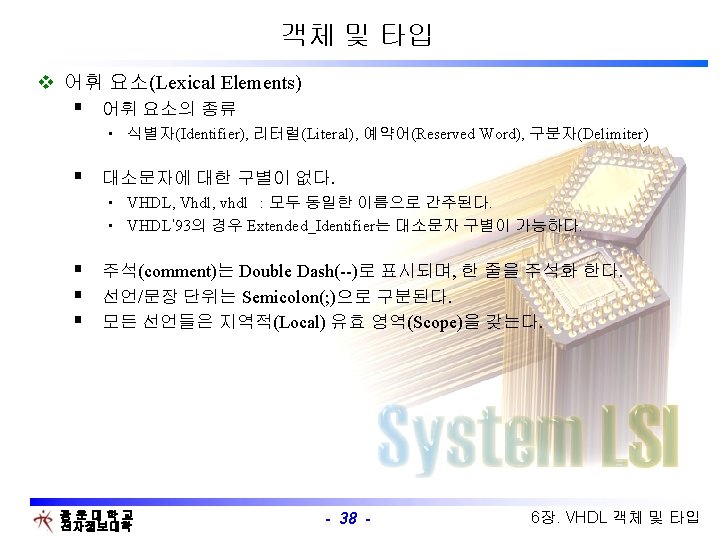

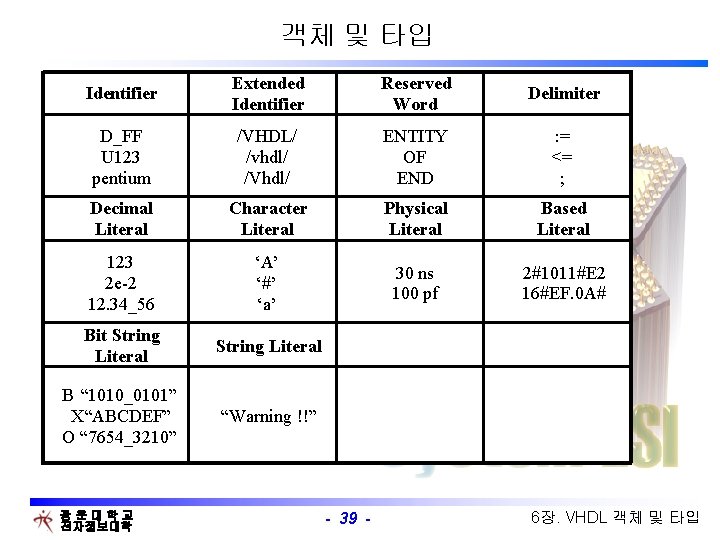

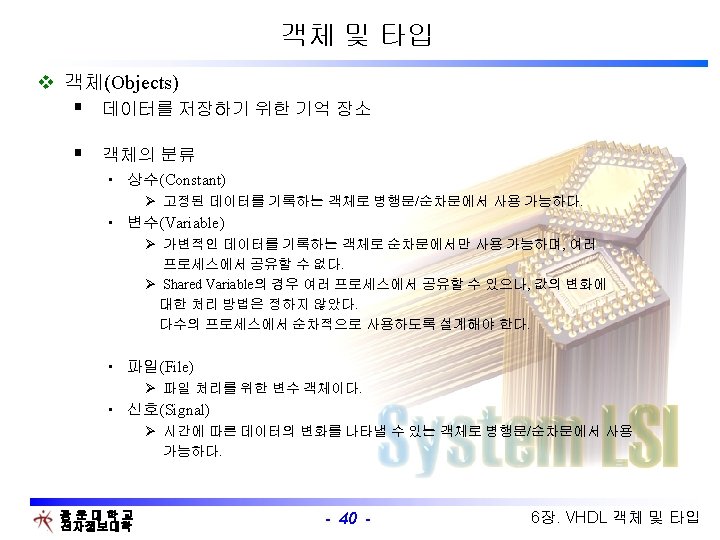

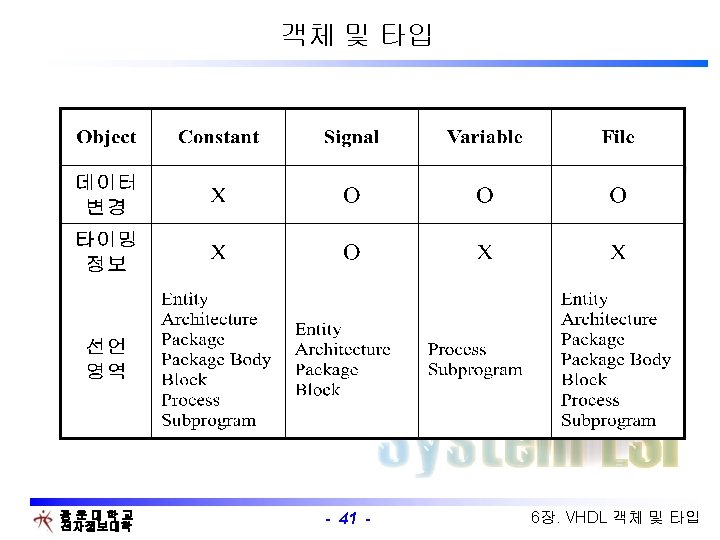

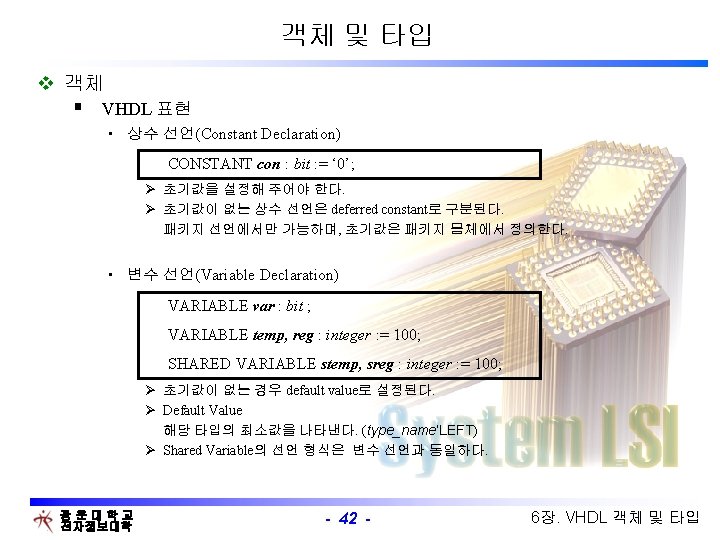

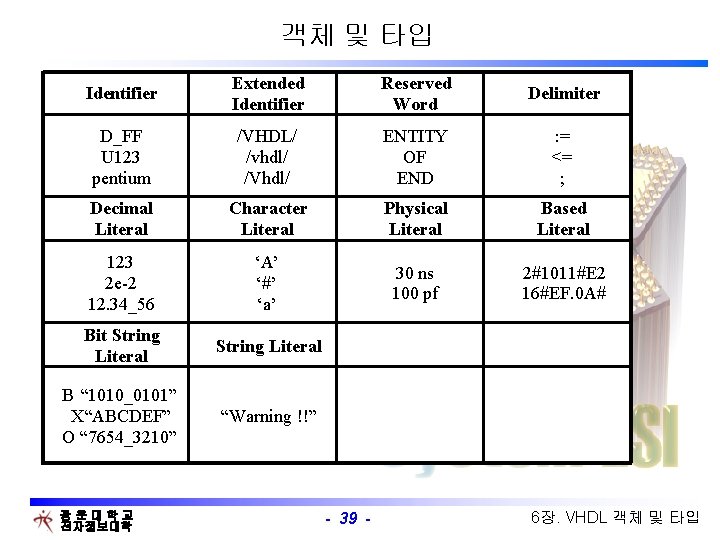

객체 및 타입 Identifier Extended Identifier Reserved Word Delimiter D_FF U 123 pentium /VHDL/ /vhdl/ /Vhdl/ ENTITY OF END : = <= ; Decimal Literal Character Literal Physical Literal Based Literal 123 2 e-2 12. 34_56 ‘A’ ‘#’ ‘a’ 30 ns 100 pf 2#1011#E 2 16#EF. 0 A# Bit String Literal B “ 1010_0101” X“ABCDEF” O “ 7654_3210” “Warning !!” 광운대학교 전자정보대학 - 39 - 6장. VHDL 객체 및 타입

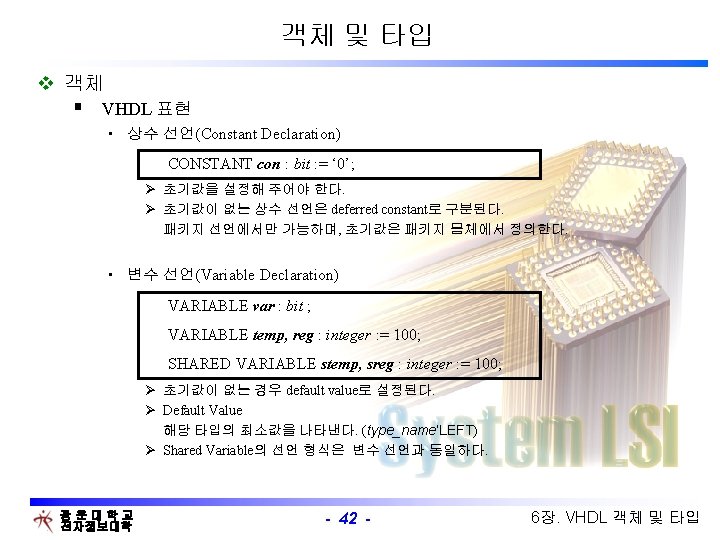

객체 및 타입 • 파일 선언(File Declaration) FILE input : text OPEN read_mode IS “STD_INPUT”; Ø READ_MODE/WRITE_MODE/APPEND_MODE 형식으로 파일을 처리한다. • 신호 선언(Signal Declaration) SIGNAL sig : bit_vector(7 DOWNTO 0) : = “ 00001111”; Ø 초기값이 없는 경우 default value로 설정된다. 광운대학교 전자정보대학 - 43 - 6장. VHDL 객체 및 타입

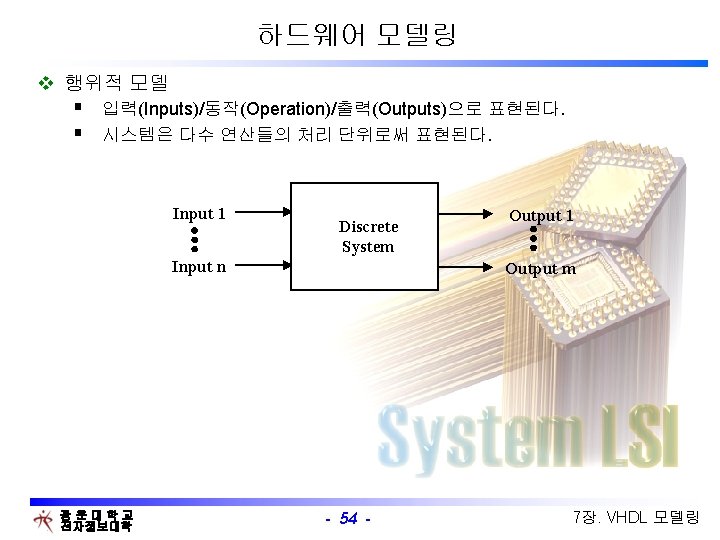

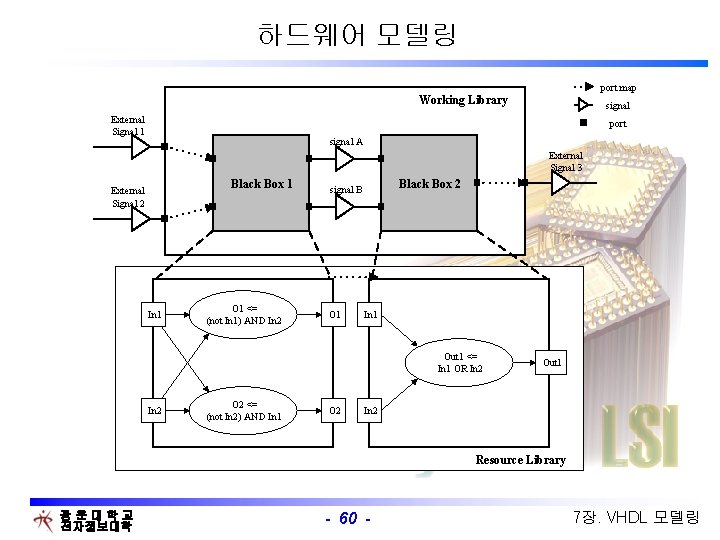

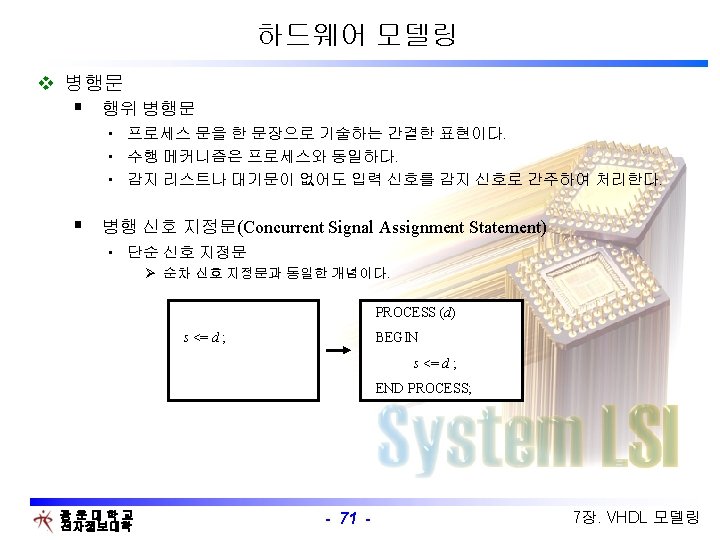

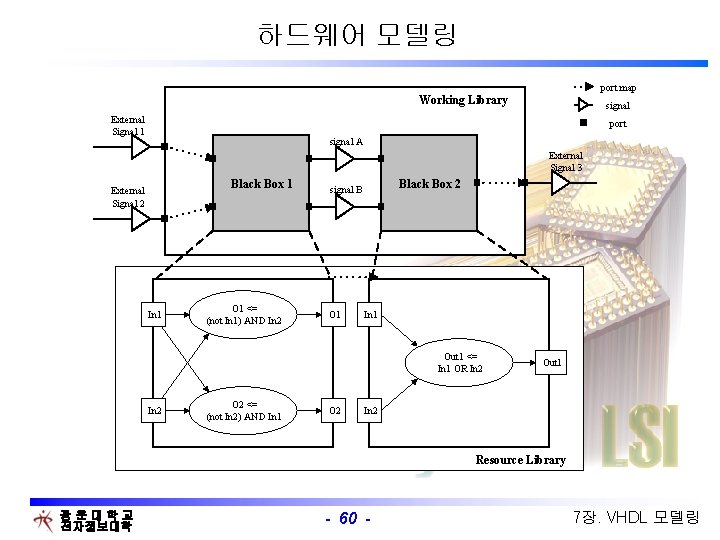

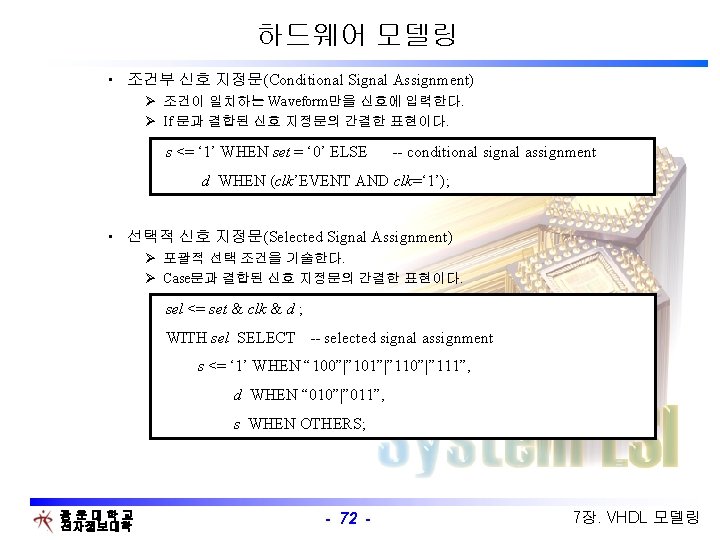

하드웨어 모델링 port map Working Library External Signal 1 signal port signal A External Signal 3 Black Box 1 External Signal 2 In 1 O 1 <= (not In 1) AND In 2 Black Box 2 signal B O 1 In 1 Out 1 <= In 1 OR In 2 O 2 <= (not In 2) AND In 1 O 2 Out 1 In 2 Resource Library 광운대학교 전자정보대학 - 60 - 7장. VHDL 모델링

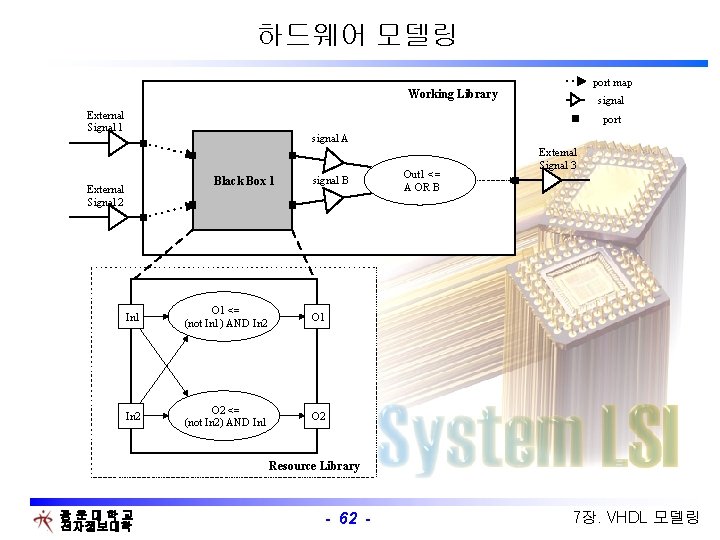

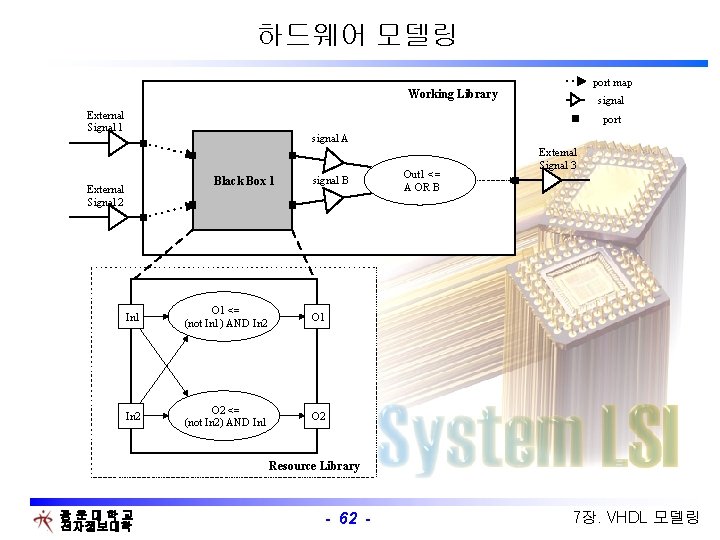

하드웨어 모델링 port map Working Library External Signal 1 signal port signal A Black Box 1 External Signal 2 signal B In 1 O 1 <= (not In 1) AND In 2 O 1 In 2 O 2 <= (not In 2) AND In 1 O 2 Out 1 <= A OR B External Signal 3 Resource Library 광운대학교 전자정보대학 - 62 - 7장. VHDL 모델링

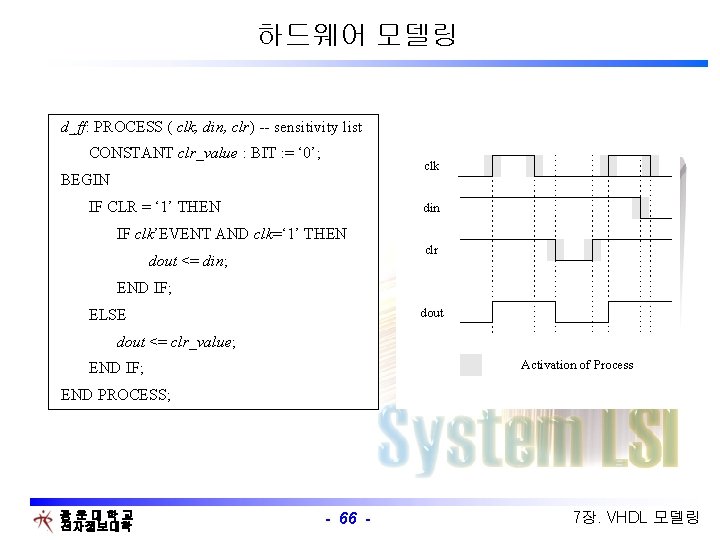

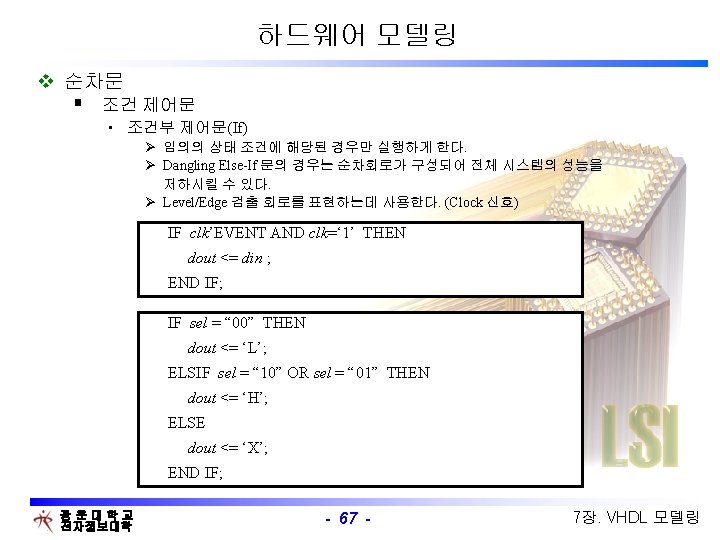

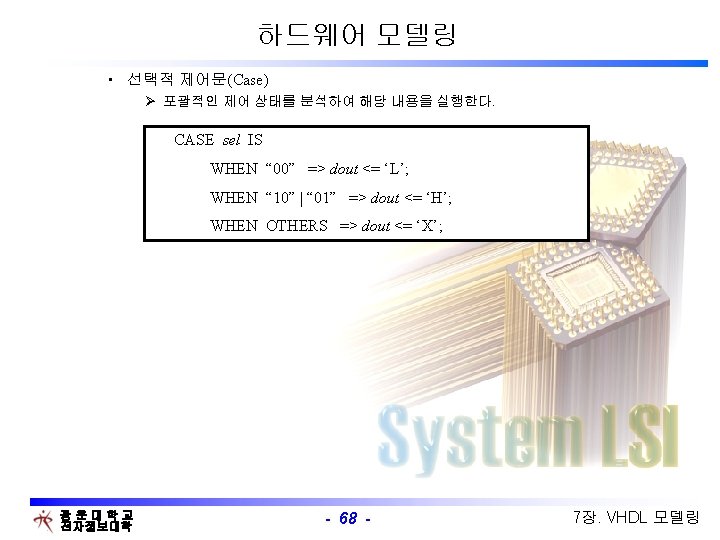

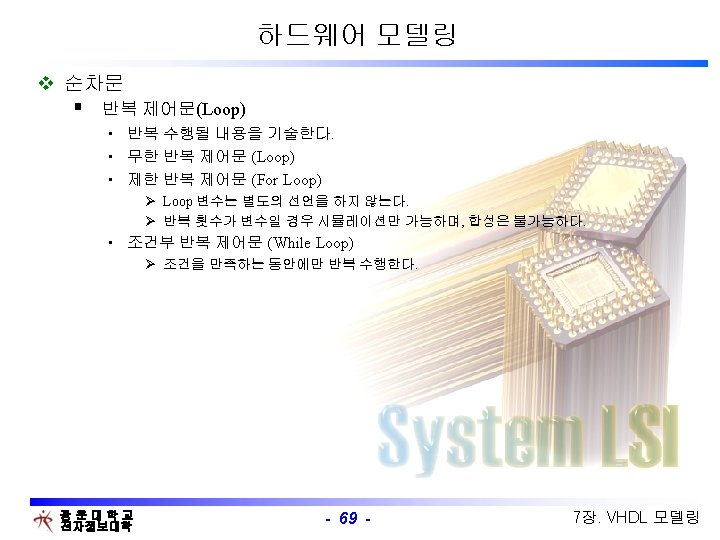

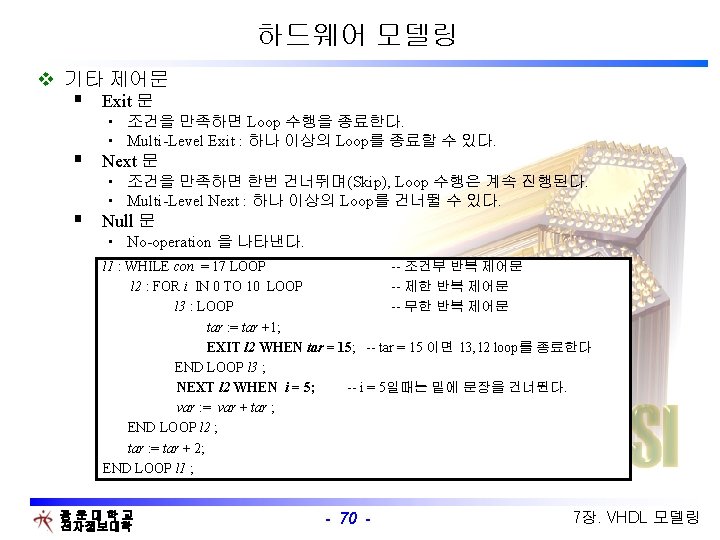

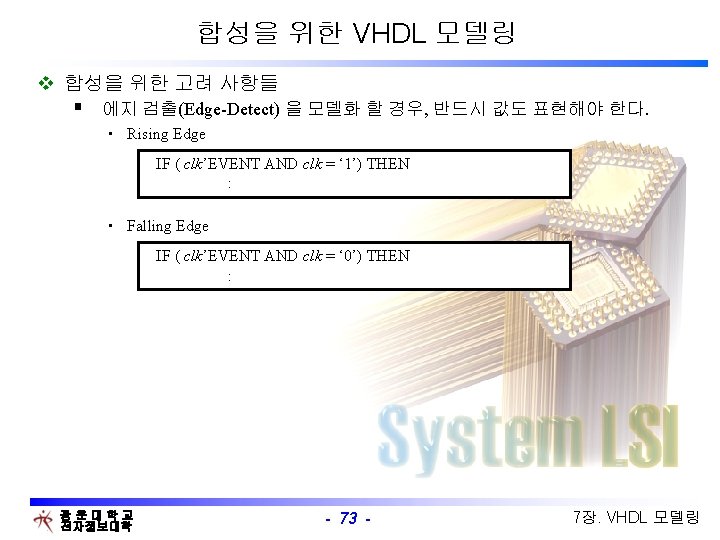

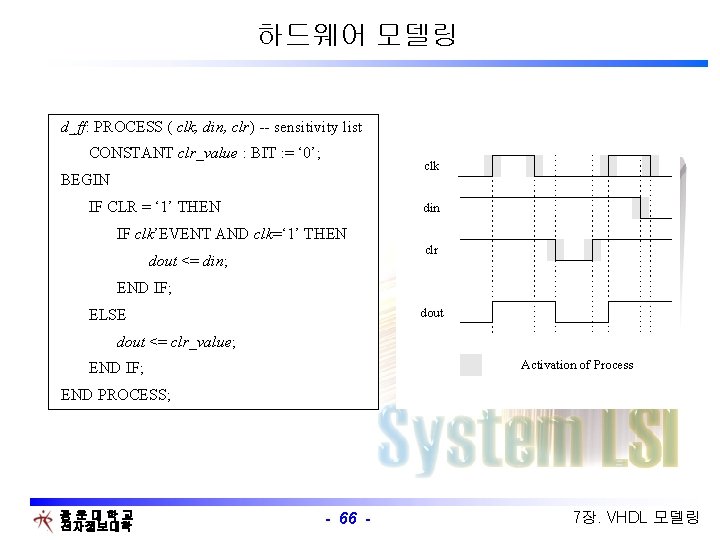

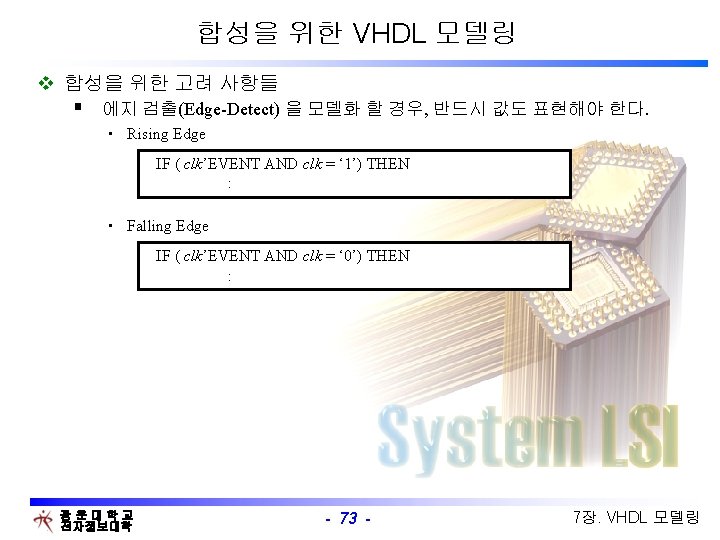

하드웨어 모델링 d_ff: PROCESS ( clk, din, clr) -- sensitivity list CONSTANT clr_value : BIT : = ‘ 0’; BEGIN IF CLR = ‘ 1’ THEN clk din IF clk’EVENT AND clk=‘ 1’ THEN clr dout <= din; END IF; ELSE dout dout <= clr_value; Activation of Process END IF; END PROCESS; 광운대학교 전자정보대학 - 66 - 7장. VHDL 모델링

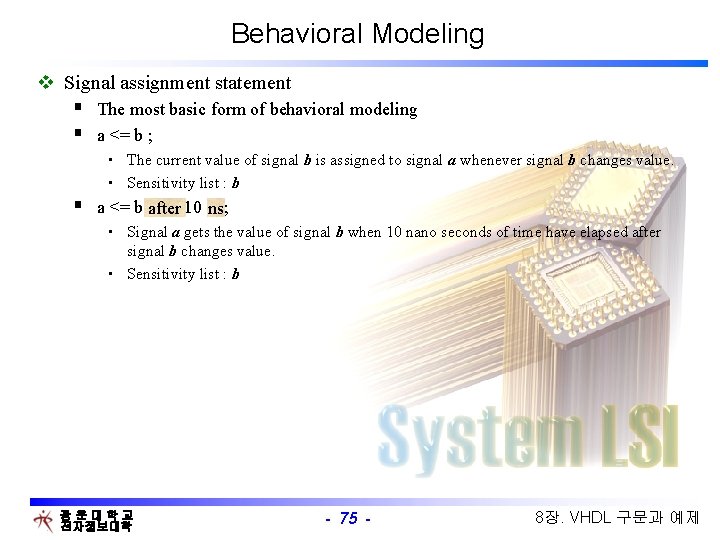

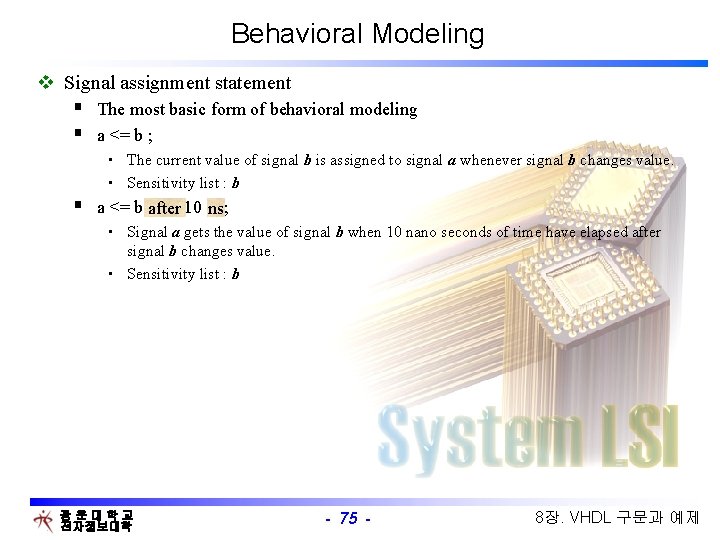

Behavioral Modeling v Signal assignment statement § The most basic form of behavioral modeling § a <= b ; • The current value of signal b is assigned to signal a whenever signal b changes value. • Sensitivity list : b § a <= b 10 ; after ns • Signal a gets the value of signal b when 10 nano seconds of time have elapsed after signal b changes value. • Sensitivity list : b 광운대학교 전자정보대학 - 75 - 8장. VHDL 구문과 예제

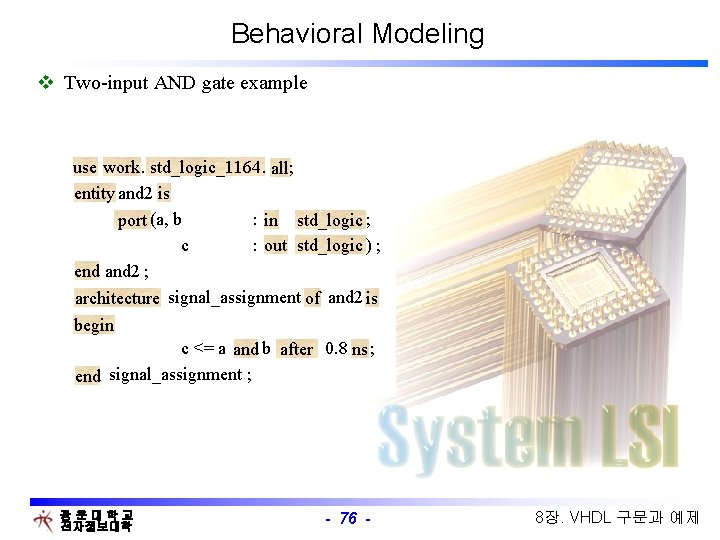

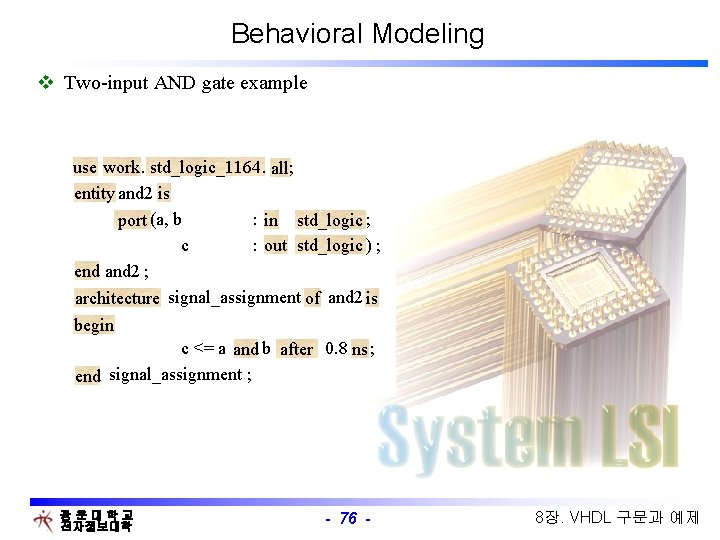

Behavioral Modeling v Two-input AND gate example . ; use work std_logic_1164 all and 2 entity is (a, b : ; port in std_logic c : ) ; out std_logic and 2 ; end signal_assignment and 2 architecture of is begin c <= a b 0. 8 ; and after ns signal_assignment ; end 광운대학교 전자정보대학 - 76 - 8장. VHDL 구문과 예제

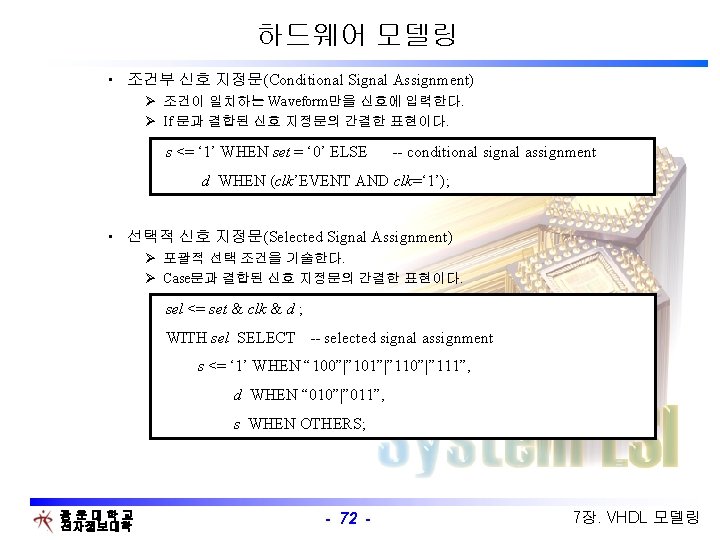

Behavioral Modeling v Signal assignment statement with conditions § Conditional signal assignment statement • assigns a value to the target signal based on conditions that are evaluated for each statement. § Selected signal assignment statement • Selects among a number of options to assign the correct value to the target signal. 광운대학교 전자정보대학 - 77 - 8장. VHDL 구문과 예제

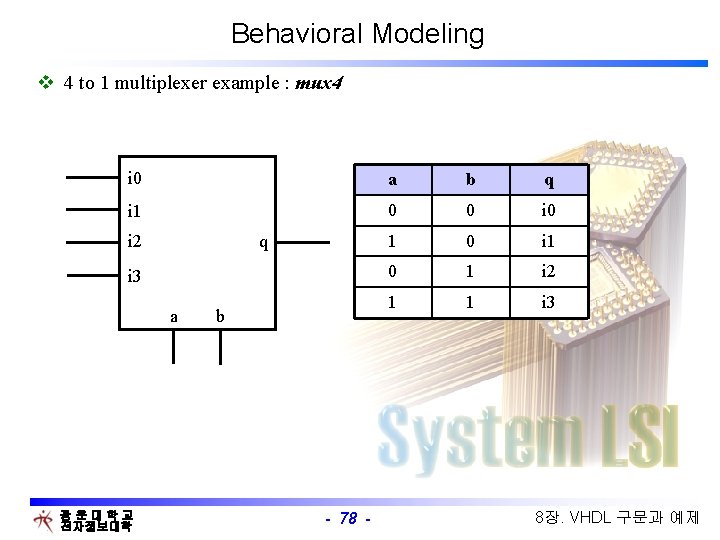

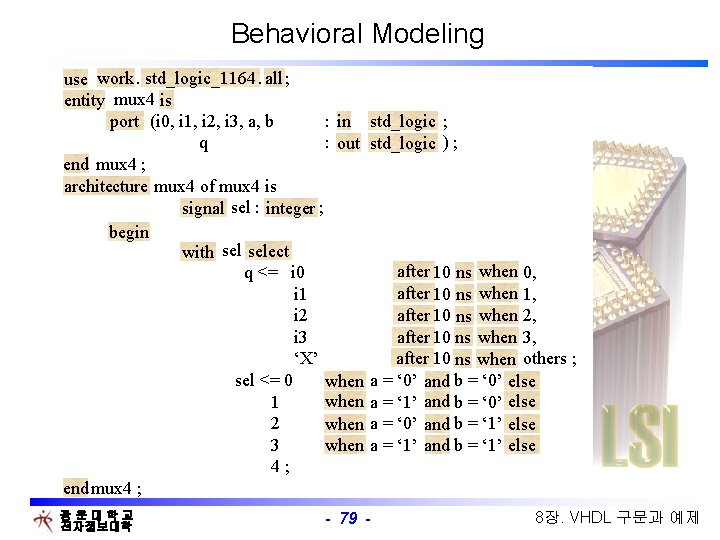

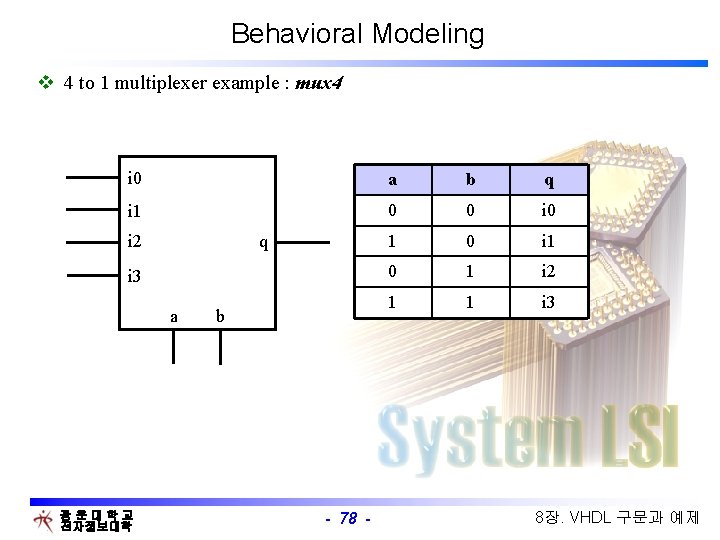

Behavioral Modeling v 4 to 1 multiplexer example : mux 4 i 0 a b q i 1 0 0 i 0 1 0 i 1 0 1 i 2 1 1 i 3 q i 2 i 3 a 광운대학교 전자정보대학 b - 78 - 8장. VHDL 구문과 예제

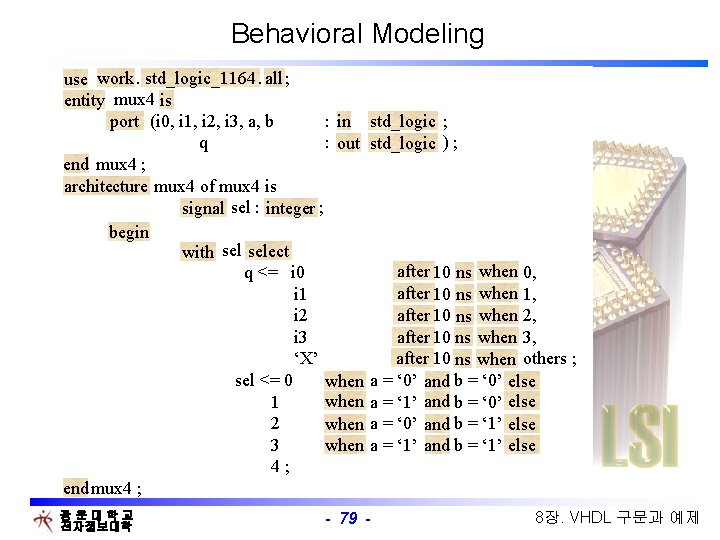

Behavioral Modeling . ; work std_logic_1164 all use mux 4 entity is in std_logic (i 0, i 1, i 2, i 3, a, b : ; port q : ) ; out std_logic mux 4 ; end mux 4 of mux 4 is architecture sel : ; signal integer begin select with after ns when q <= i 0 10 0, after ns when i 1 10 1, after ns when i 2 10 2, after i 3 10 3, ns when ‘X’ 10 others ; after ns when sel <= 0 a = ‘ 0’ b = ‘ 0’ when and else 1 a = ‘ 1’ b = ‘ 0’ 2 a = ‘ 0’ b = ‘ 1’ when and else 3 a = ‘ 1’ b = ‘ 1’ when and else 4 ; end mux 4 ; 광운대학교 전자정보대학 - 79 - 8장. VHDL 구문과 예제

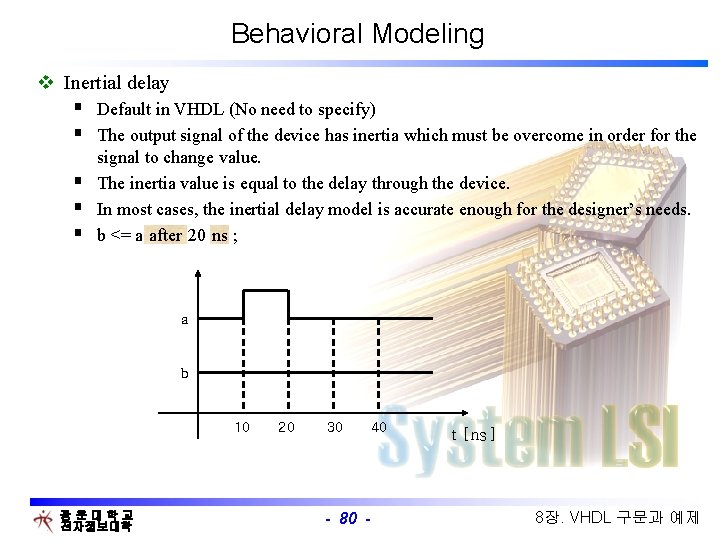

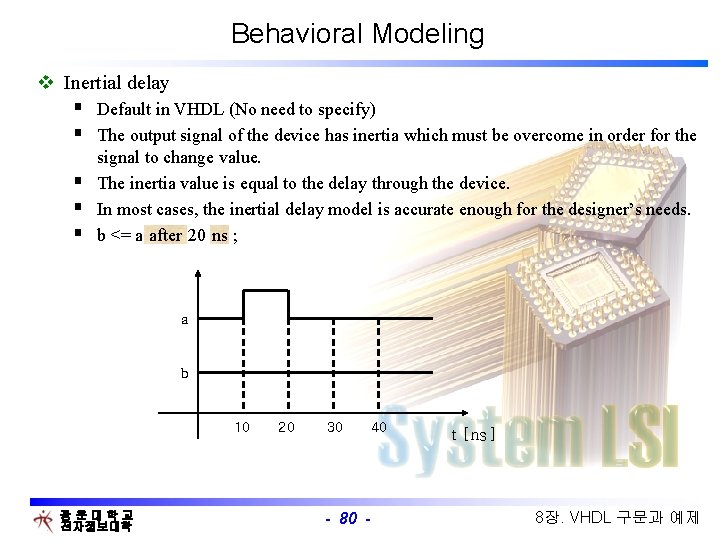

Behavioral Modeling v Inertial delay § Default in VHDL (No need to specify) § The output signal of the device has inertia which must be overcome in order for the § § § signal to change value. The inertia value is equal to the delay through the device. In most cases, the inertial delay model is accurate enough for the designer’s needs. b <= a 20 ; after ns a b 10 광운대학교 전자정보대학 20 30 40 - 80 - t [ns] 8장. VHDL 구문과 예제

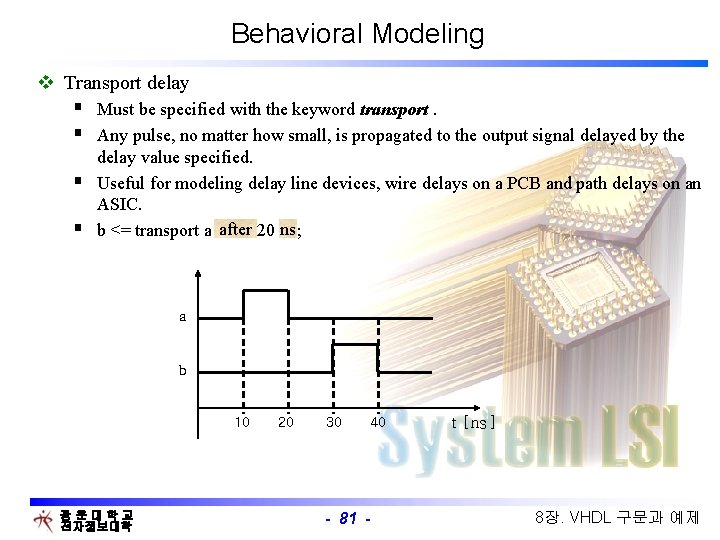

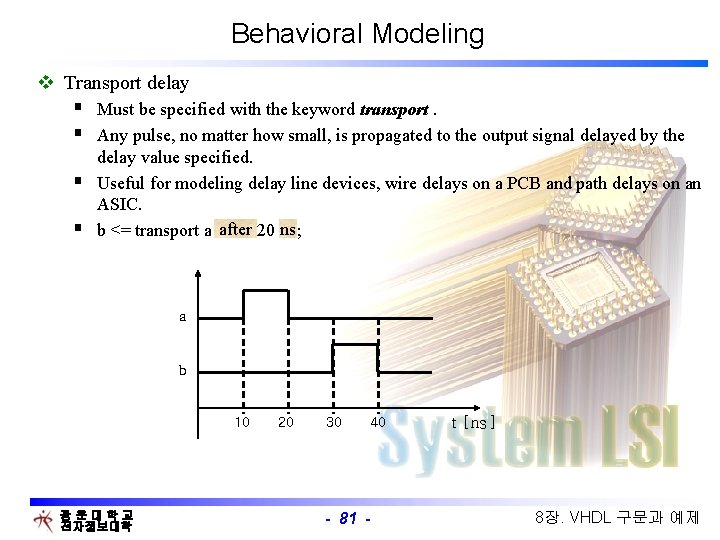

Behavioral Modeling v Transport delay § Must be specified with the keyword transport. § Any pulse, no matter how small, is propagated to the output signal delayed by the § § delay value specified. Useful for modeling delay line devices, wire delays on a PCB and path delays on an ASIC. after ns b <= transport a 20 ; a b 10 광운대학교 전자정보대학 20 30 40 - 81 - t [ns] 8장. VHDL 구문과 예제

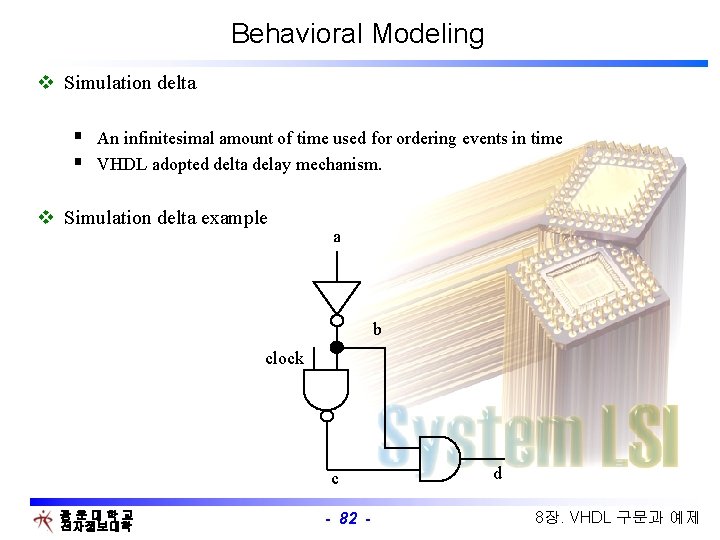

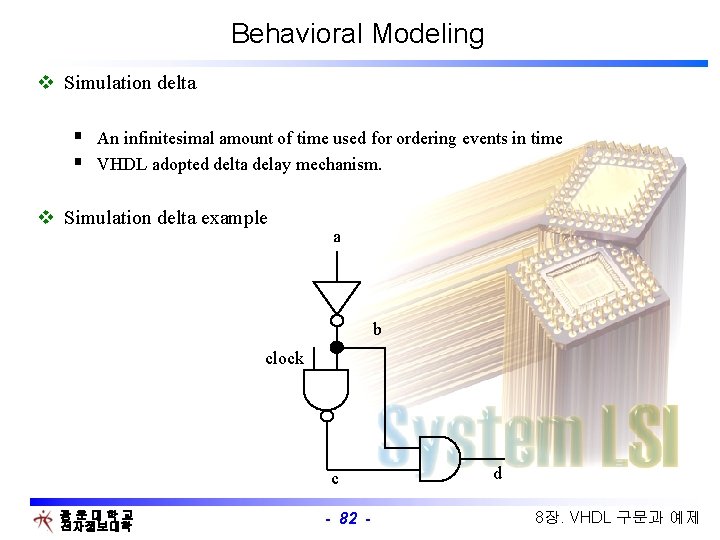

Behavioral Modeling v Simulation delta § An infinitesimal amount of time used for ordering events in time § VHDL adopted delta delay mechanism. v Simulation delta example a b clock c 광운대학교 전자정보대학 - 82 - d 8장. VHDL 구문과 예제

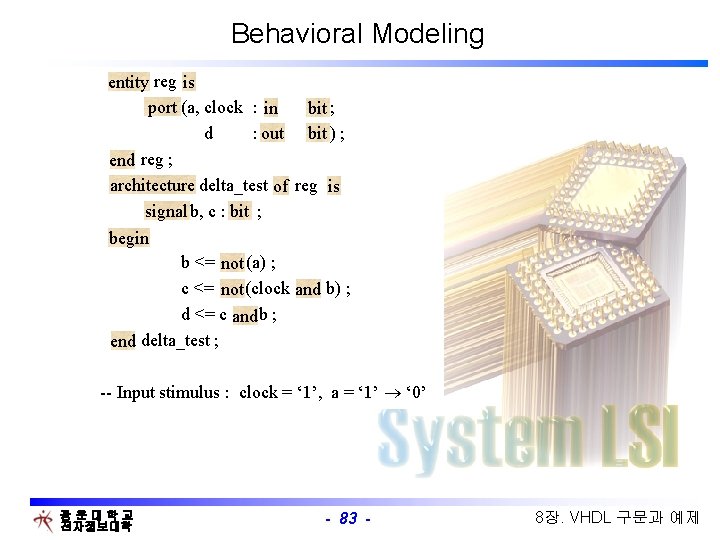

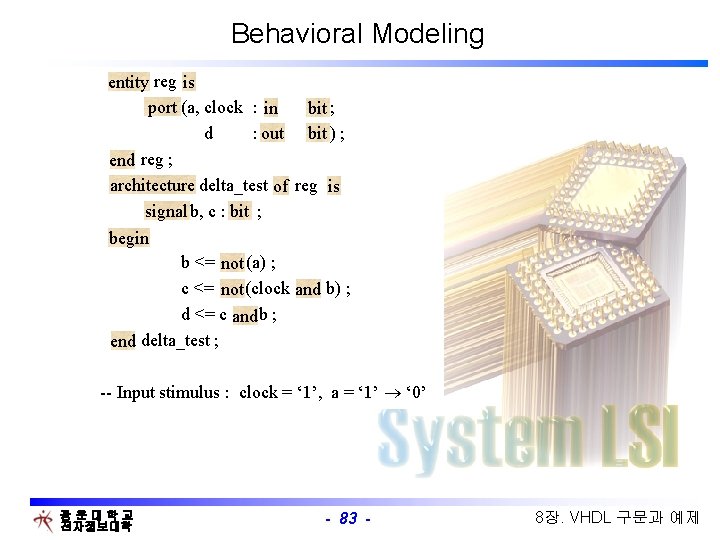

Behavioral Modeling reg is entity port (a, clock : ; in bit d : out bit ) ; reg ; end delta_test reg architecture of is b, c : ; signal bit begin b <= (a) ; not c <= (clock b) ; not and d <= c b ; and delta_test ; end -- Input stimulus : clock = ‘ 1’, a = ‘ 1’ ‘ 0’ 광운대학교 전자정보대학 - 83 - 8장. VHDL 구문과 예제

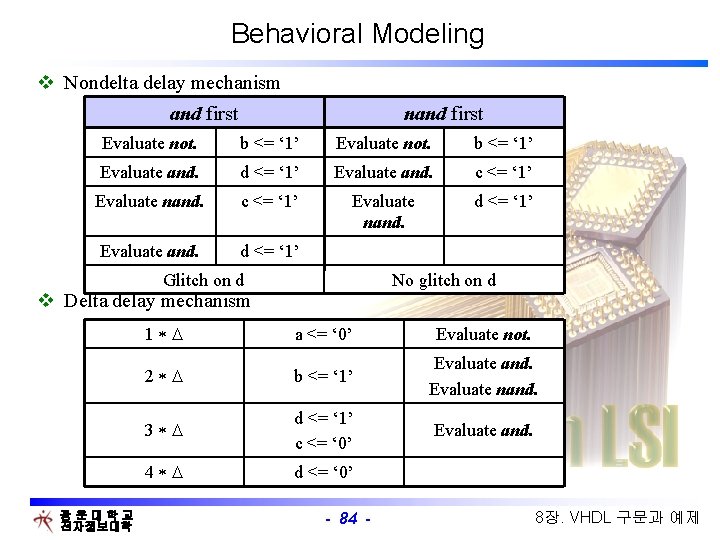

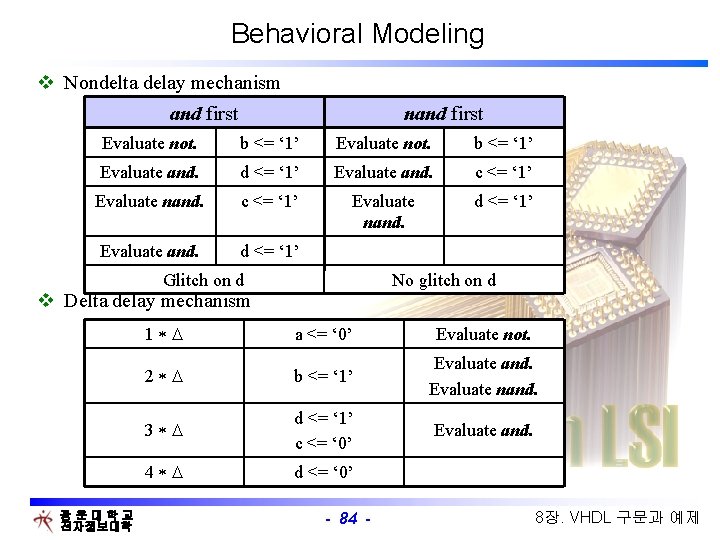

Behavioral Modeling v Nondelta delay mechanism and first nand first Evaluate not. b <= ‘ 1’ Evaluate and. d <= ‘ 1’ Evaluate and. c <= ‘ 1’ Evaluate nand. d <= ‘ 1’ Evaluate and. d <= ‘ 1’ Glitch on d No glitch on d v Delta delay mechanism 광운대학교 전자정보대학 1 a <= ‘ 0’ Evaluate not. 2 b <= ‘ 1’ Evaluate and. Evaluate nand. 3 d <= ‘ 1’ c <= ‘ 0’ Evaluate and. 4 d <= ‘ 0’ - 84 - 8장. VHDL 구문과 예제

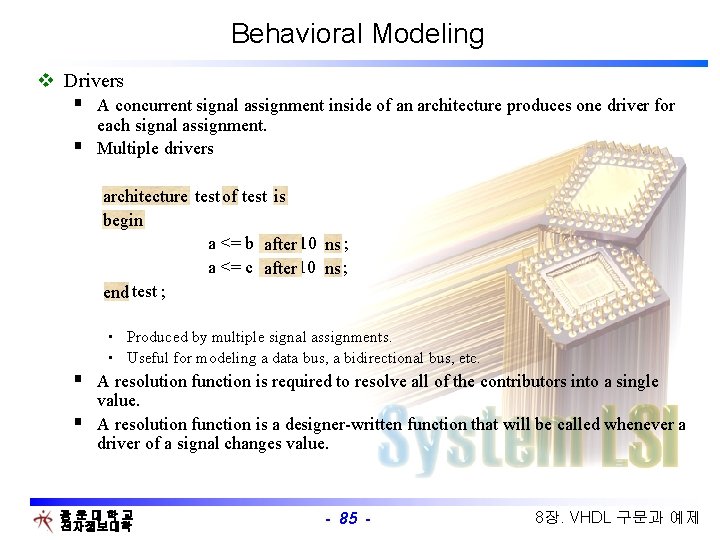

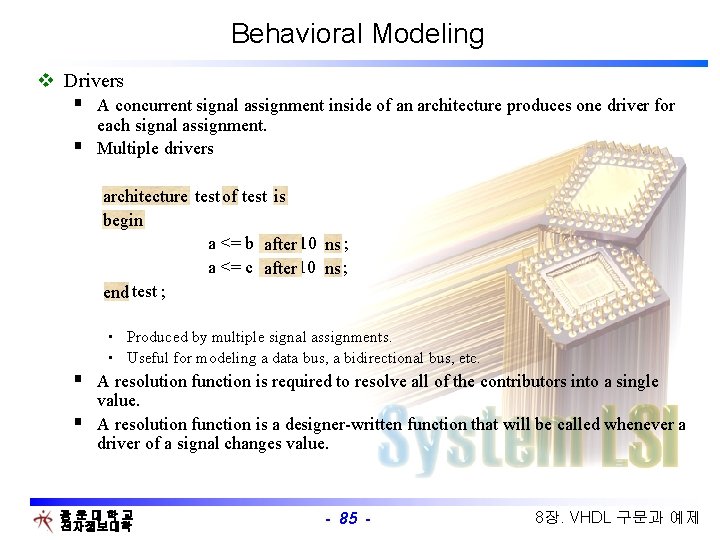

Behavioral Modeling v Drivers § A concurrent signal assignment inside of an architecture produces one driver for § each signal assignment. Multiple drivers is test architecture of begin a <= b 10 ; after ns a <= c 10 ; after ns test ; end • Produced by multiple signal assignments. • Useful for modeling a data bus, a bidirectional bus, etc. § A resolution function is required to resolve all of the contributors into a single § value. A resolution function is a designer-written function that will be called whenever a driver of a signal changes value. 광운대학교 전자정보대학 - 85 - 8장. VHDL 구문과 예제

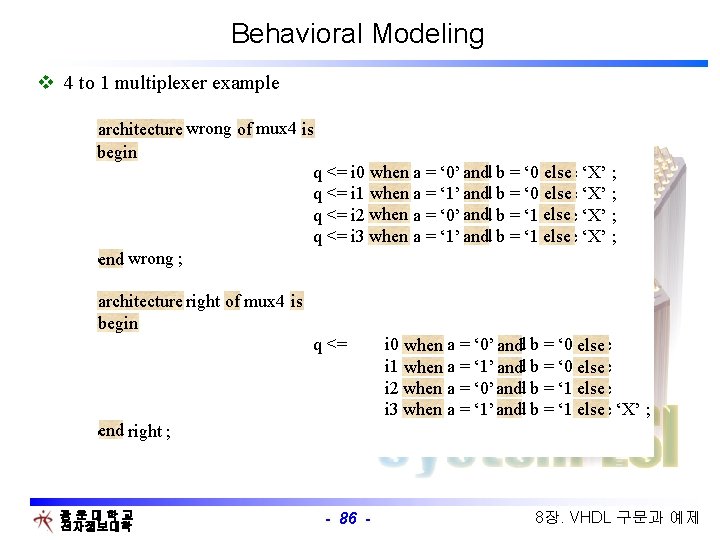

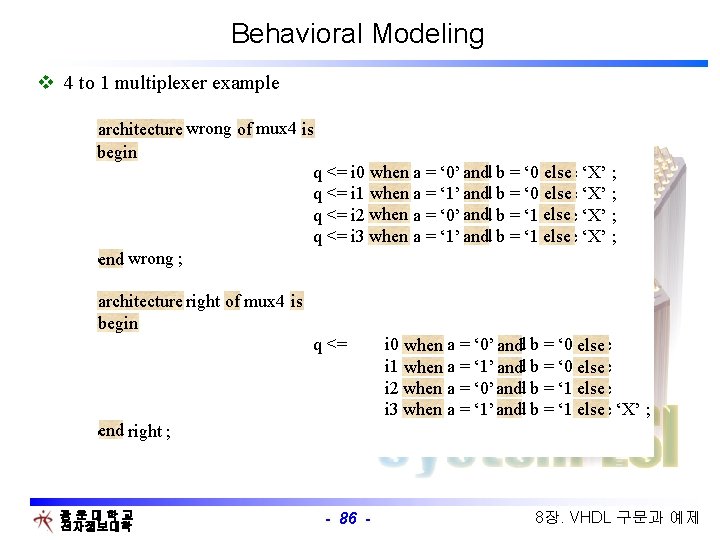

Behavioral Modeling v 4 to 1 multiplexer example architecture wrong of mux 4 is architecture of is begin q <= i 0 when a = ‘ 0’ and b = ‘ 0’ else ‘X’ ; when and else q <= i 1 when a = ‘ 1’ and b = ‘ 0’ else ‘X’ ; when and else q <= i 2 when a = ‘ 0’ and b = ‘ 1’ else ‘X’ ; when and else q <= i 3 when a = ‘ 1’ and b = ‘ 1’ else ‘X’ ; end wrong ; end architecture right of mux 4 is architecture of is begin q <= i 0 when a = ‘ 0’ and b = ‘ 0’ else when and else i 1 when a = ‘ 1’ and b = ‘ 0’ else when and else i 2 when a = ‘ 0’ and b = ‘ 1’ else i 3 when a = ‘ 1’ and b = ‘ 1’ else ‘X’ ; when and else end right ; 광운대학교 전자정보대학 - 86 - 8장. VHDL 구문과 예제

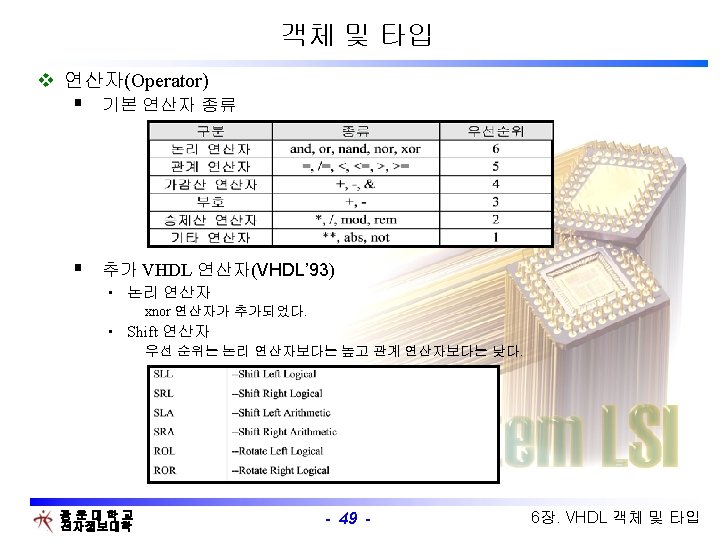

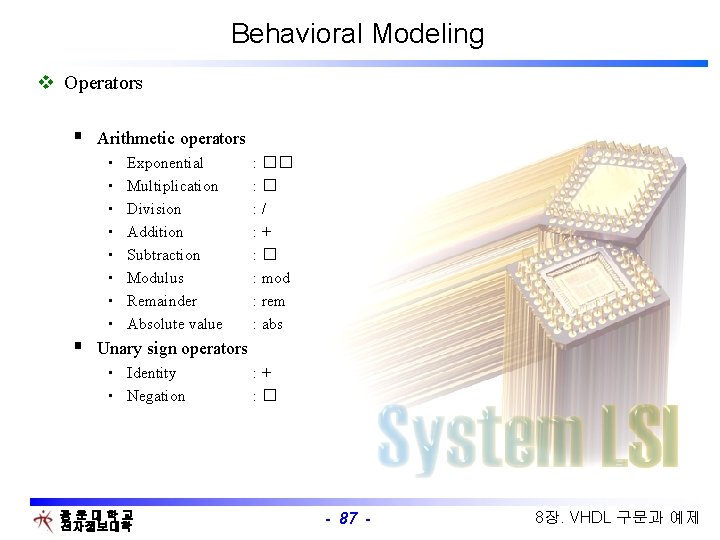

Behavioral Modeling v Operators § Arithmetic operators • Exponential • Multiplication • Division • Addition • Subtraction • Modulus • Remainder • Absolute value : �� : / : + : � : mod : rem : abs § Unary sign operators • Identity • Negation 광운대학교 전자정보대학 : + : � - 87 - 8장. VHDL 구문과 예제

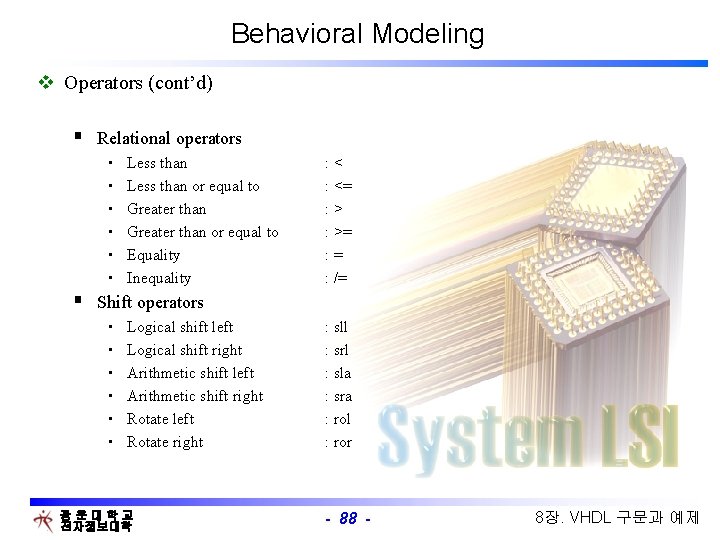

Behavioral Modeling v Operators (cont’d) § Relational operators • Less than or equal to • Greater than or equal to • Equality • Inequality : <= : >= : /= § Shift operators • Logical shift left • Logical shift right • Arithmetic shift left • Arithmetic shift right • Rotate left • Rotate right 광운대학교 전자정보대학 : sll : srl : sla : sra : rol : ror - 88 - 8장. VHDL 구문과 예제

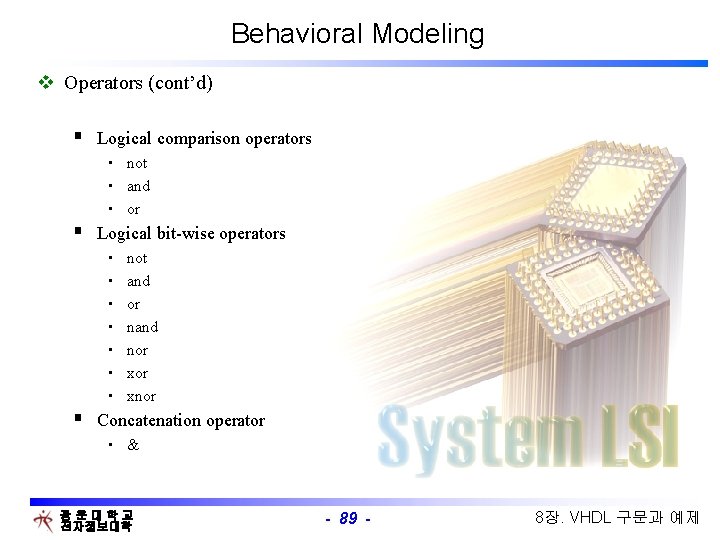

Behavioral Modeling v Operators (cont’d) § Logical comparison operators • not • and • or § Logical bit-wise operators • not • and • or • nand • nor • xnor § Concatenation operator • & 광운대학교 전자정보대학 - 89 - 8장. VHDL 구문과 예제

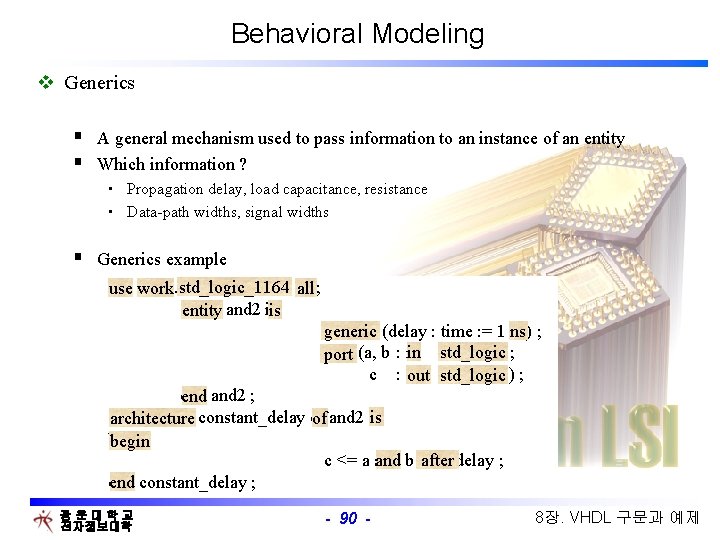

Behavioral Modeling v Generics § A general mechanism used to pass information to an instance of an entity § Which information ? • Propagation delay, load capacitance, resistance • Data-path widths, signal widths § Generics example use work. std_logic_1164. all ; use work std_logic_1164 all entity and 2 is is entity generic ns generic (delay : time : = 1 ns) ; port (a, b : in ; in std_logic port c : out ) ; out std_logic end and 2 ; end is architecture constant_delay of and 2 is architecture of begin c <= a and b after delay ; and after end constant_delay ; end 광운대학교 전자정보대학 - 90 - 8장. VHDL 구문과 예제

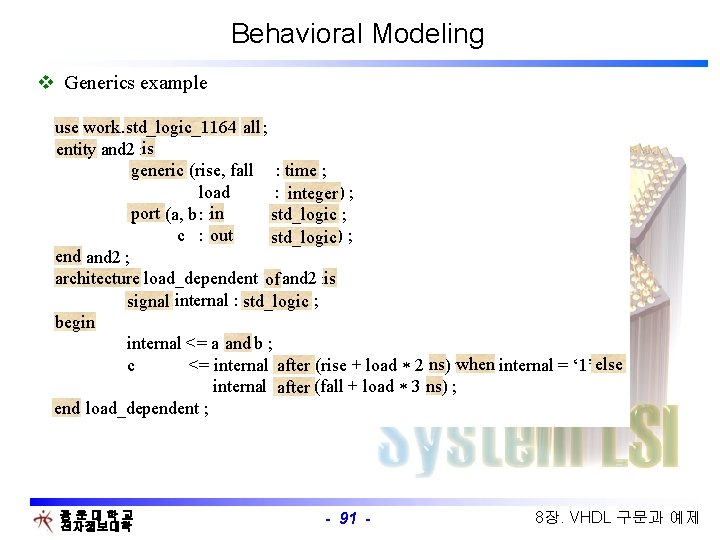

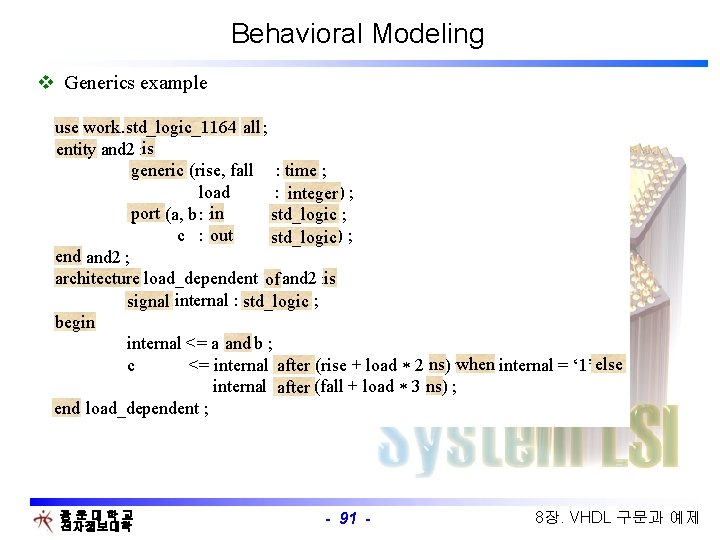

Behavioral Modeling v Generics example use work. std_logic_1164. all ; use work std_logic_1164 all is entity and 2 is entity generic time generic (rise, fall : time ; load : integer) ; integer port in port (a, b : in std_logic ; std_logic c : out std_logic) ; out std_logic end and 2 ; architecture is architecture load_dependent of and 2 is of signal internal : std_logic ; signal std_logic begin and internal <= a and b ; ns when else c <= internal after (rise + load 2 ns) when internal = ‘ 1’ else after ns internal after (fall + load 3 ns) ; after end load_dependent ; 광운대학교 전자정보대학 - 91 - 8장. VHDL 구문과 예제

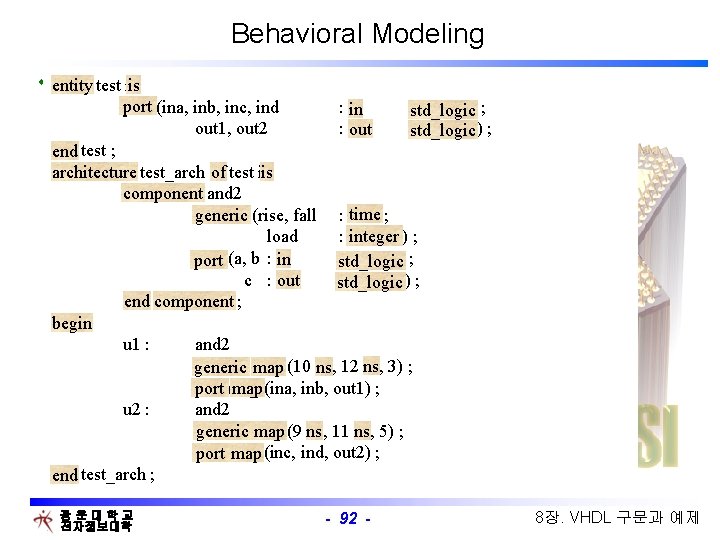

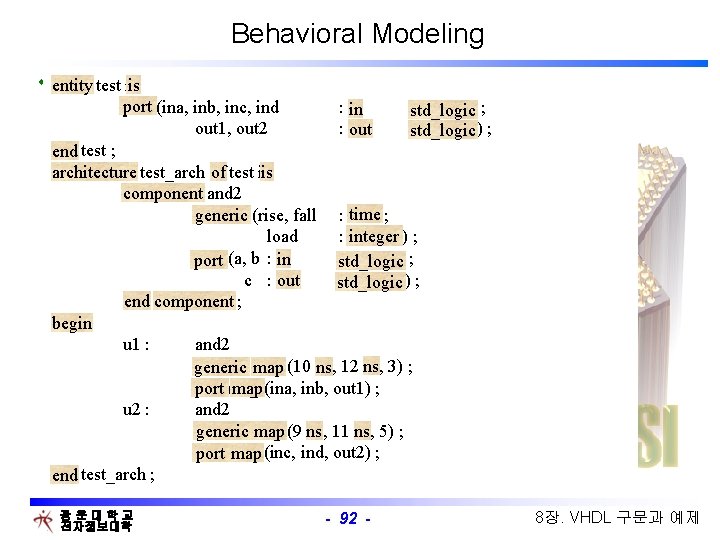

Behavioral Modeling ventity test is Behavioral Modeling entity is port (ina, inb, inc, ind out 1, out 2 : in in : out std_logic ; std_logic) ; std_logic end test ; end architecture test_arch of test is architecture of is component and 2 component time generic (rise, fall : time ; generic integer load : integer ) ; port (a, b : in std_logic ; in port std_logic c : out std_logic) ; out std_logic end component ; end component begin u 1 : and 2 ns generic map (10 ns, 12 ns, 3) ; generic map ns port map (ina, inb, out 1) ; port map u 2 : and 2 generic map (9 ns, 11 ns, 5) ; generic map ns ns port map (inc, ind, out 2) ; port map end test_arch ; end 광운대학교 전자정보대학 - 92 - 8장. VHDL 구문과 예제

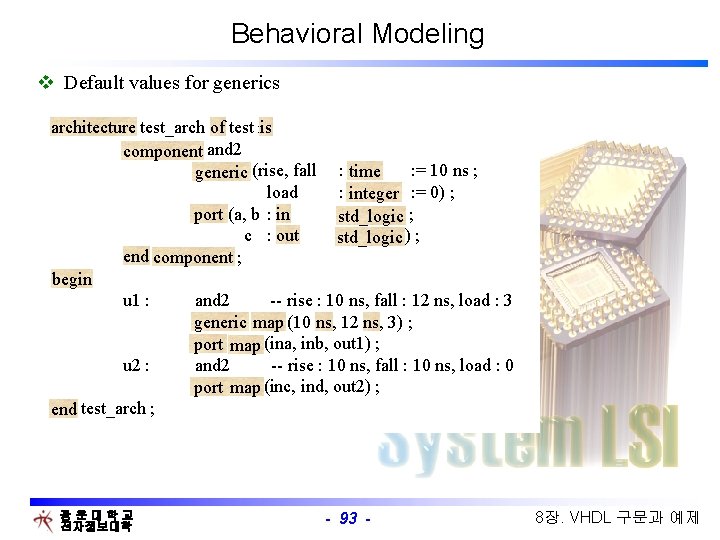

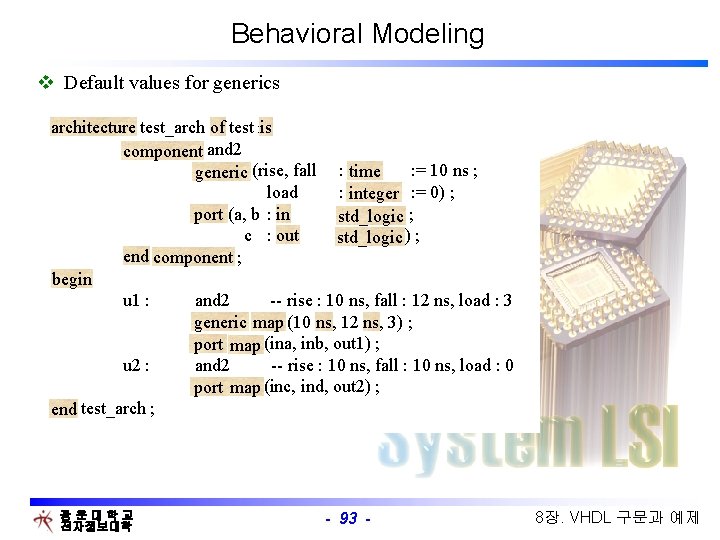

Behavioral Modeling v Default values for generics architecture test_arch of test is architecture of is component and 2 component generic (rise, fall : time : = 10 ns ; time generic load : integer : = 0) ; port (a, b : in std_logic ; in port std_logic out c : out std_logic) ; std_logic end component ; begin u 1 : and 2 -- rise : 10 ns, fall : 12 ns, load : 3 generic map (10 ns, 12 ns, 3) ; ns generic map ns port map (ina, inb, out 1) ; port map u 2 : and 2 -- rise : 10 ns, fall : 10 ns, load : 0 port map (inc, ind, out 2) ; port map end test_arch ; end 광운대학교 전자정보대학 - 93 - 8장. VHDL 구문과 예제

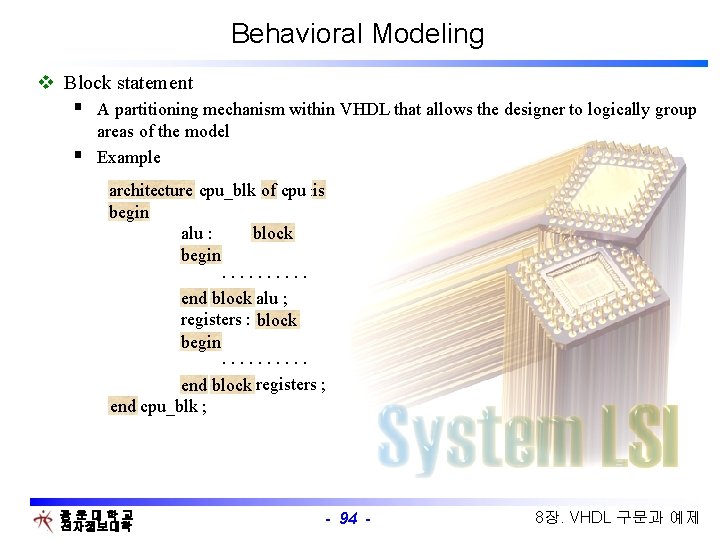

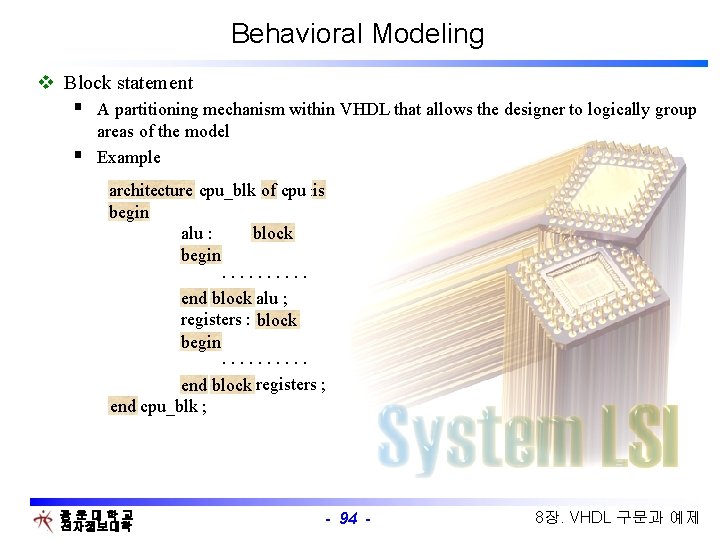

Behavioral Modeling v Block statement § A partitioning mechanism within VHDL that allows the designer to logically group § areas of the model Example architecture cpu_blk of cpu is architecture of is begin alu : block begin end block alu ; end block registers : block begin end block registers ; end block end cpu_blk ; 광운대학교 전자정보대학 - 94 - 8장. VHDL 구문과 예제

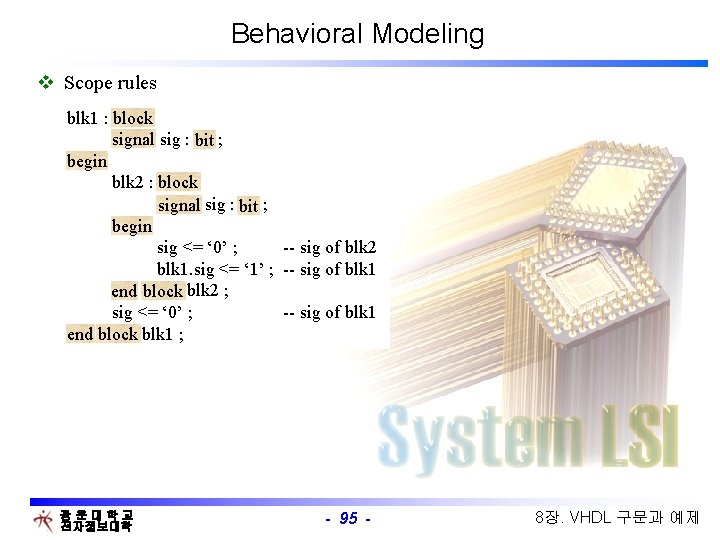

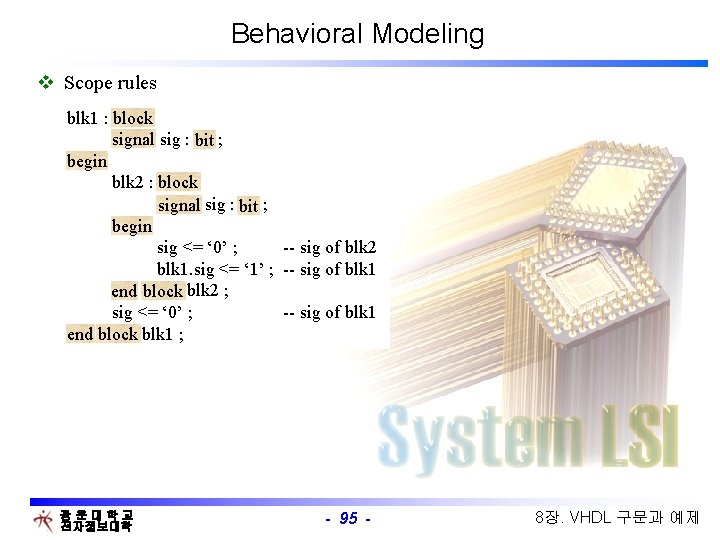

Behavioral Modeling v Scope rules blk 1 : block signal sig : bit ; signal bit begin block blk 2 : block signal sig : bit ; signal bit begin sig <= ‘ 0’ ; -- sig of blk 2 blk 1. sig <= ‘ 1’ ; -- sig of blk 1 end block blk 2 ; end block sig <= ‘ 0’ ; -- sig of blk 1 end block blk 1 ; end block 광운대학교 전자정보대학 - 95 - 8장. VHDL 구문과 예제

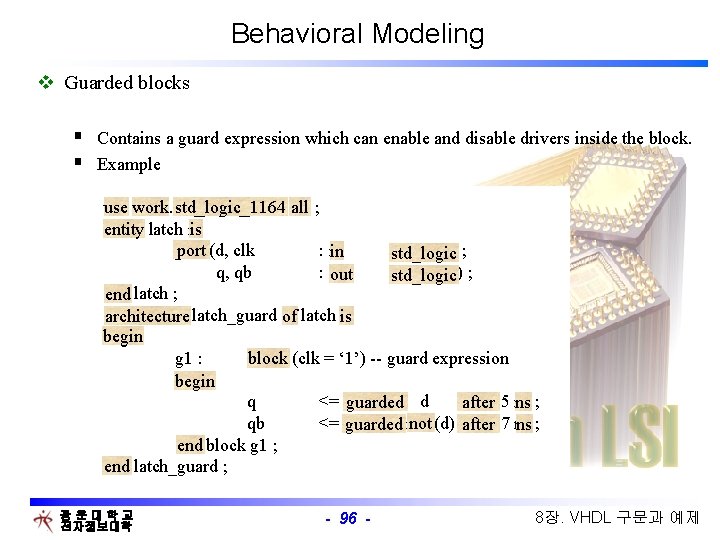

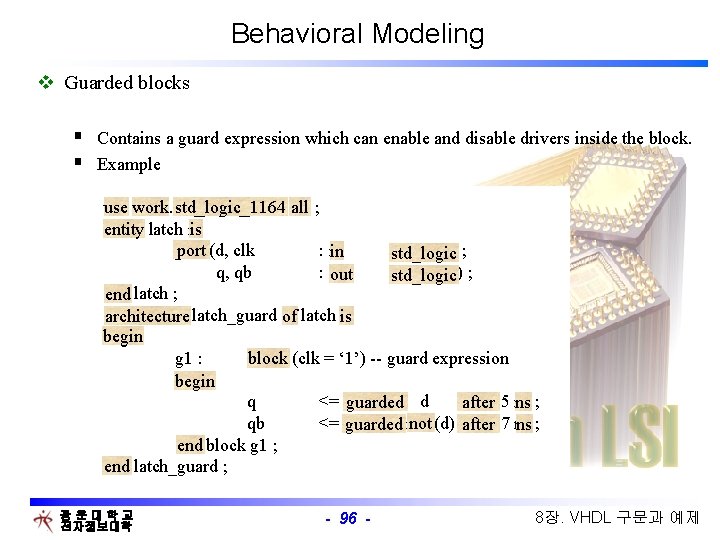

Behavioral Modeling v Guarded blocks § Contains a guard expression which can enable and disable drivers inside the block. § Example use work std_logic_1164 all use work. std_logic_1164. all ; entity latch is entity is port (d, clk : in std_logic ; port in std_logic q, qb : out std_logic) ; out std_logic end latch ; end architecture latch_guard of latch is architecture of is begin g 1 : block (clk = ‘ 1’) -- guard expression block begin q <= guarded d after 5 ns ; guarded after ns qb <= guarded not (d) after 7 ns ; guarded not after ns end block g 1 ; end end latch_guard ; 광운대학교 전자정보대학 - 96 - 8장. VHDL 구문과 예제

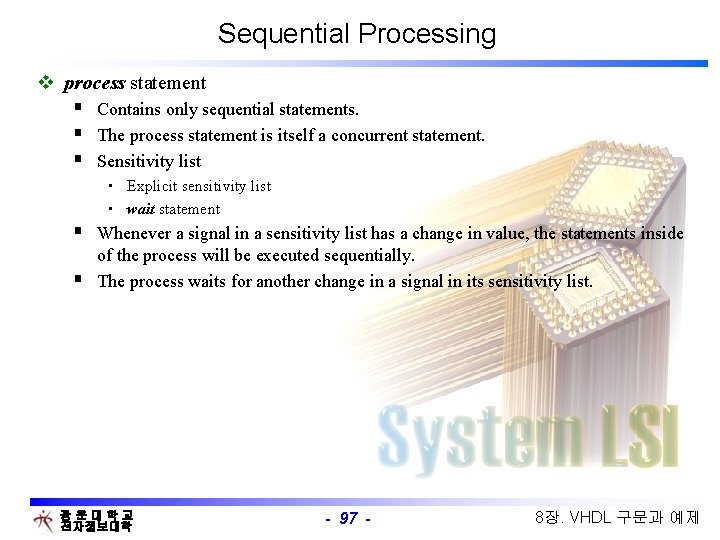

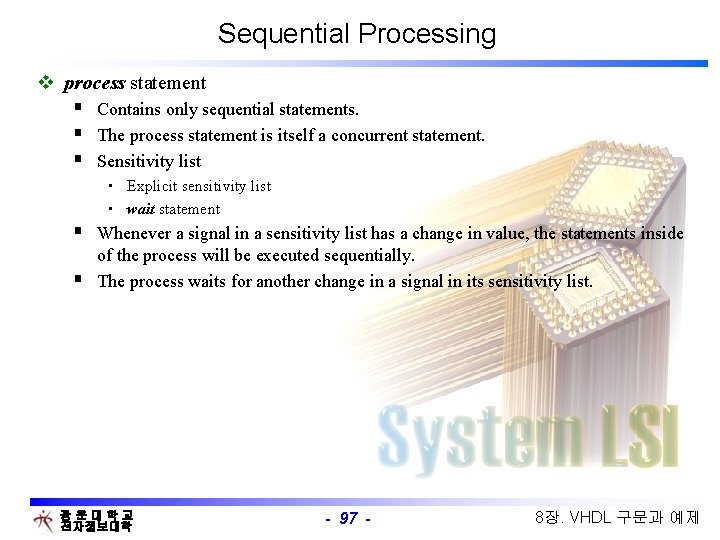

Sequential Processing v process statement § Contains only sequential statements. § The process statement is itself a concurrent statement. § Sensitivity list • Explicit sensitivity list • wait statement § Whenever a signal in a sensitivity list has a change in value, the statements inside § of the process will be executed sequentially. The process waits for another change in a signal in its sensitivity list. 광운대학교 전자정보대학 - 97 - 8장. VHDL 구문과 예제

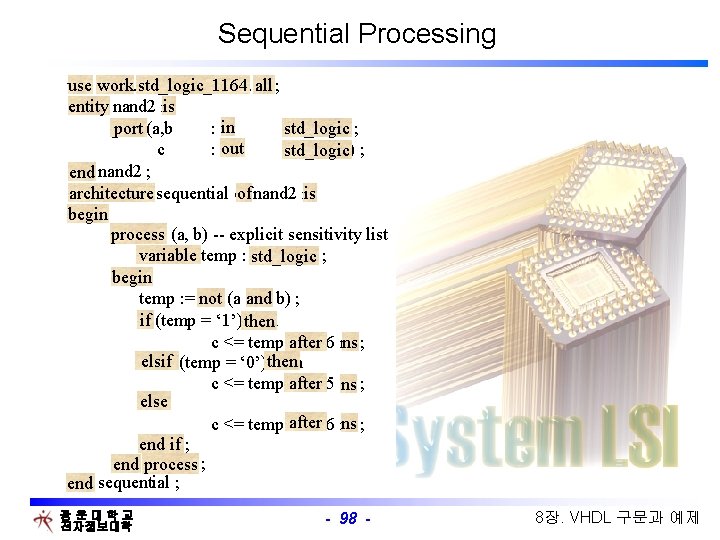

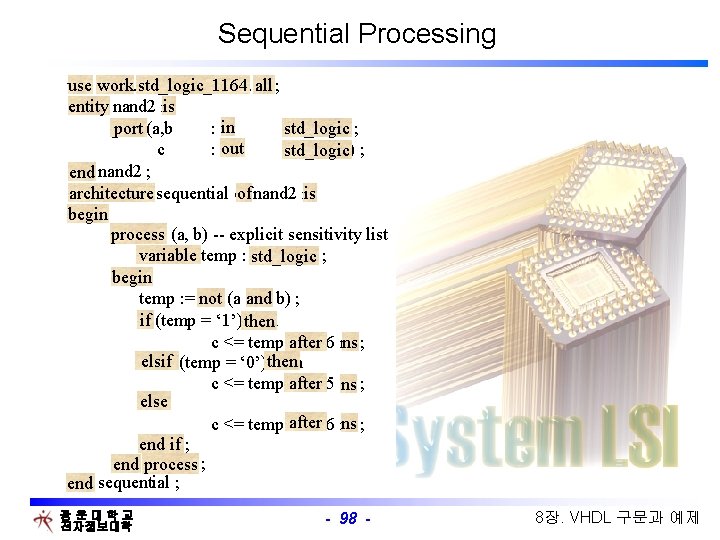

Sequential Processing use work std_logic_1164 all use work. std_logic_1164. all ; entity nand 2 is entity is in port (a, b : in std_logic ; port std_logic out c : out std_logic) ; std_logic end nand 2 ; end architecture of is architecture sequential of nand 2 is begin process (a, b) -- explicit sensitivity list process variable temp : std_logic ; std_logic begin not and temp : = not (a and b) ; if (temp = ‘ 1’) then if then c <= temp after 6 ns ; after ns elsif then elsif (temp = ‘ 0’) then c <= temp after 5 ns ; after ns else after ns c <= temp after 6 ns ; end if end process ; end process end sequential ; end 광운대학교 전자정보대학 - 98 - 8장. VHDL 구문과 예제

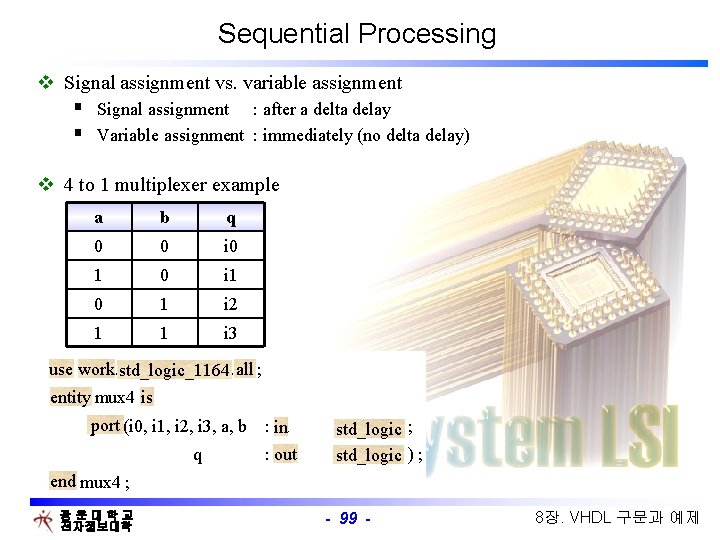

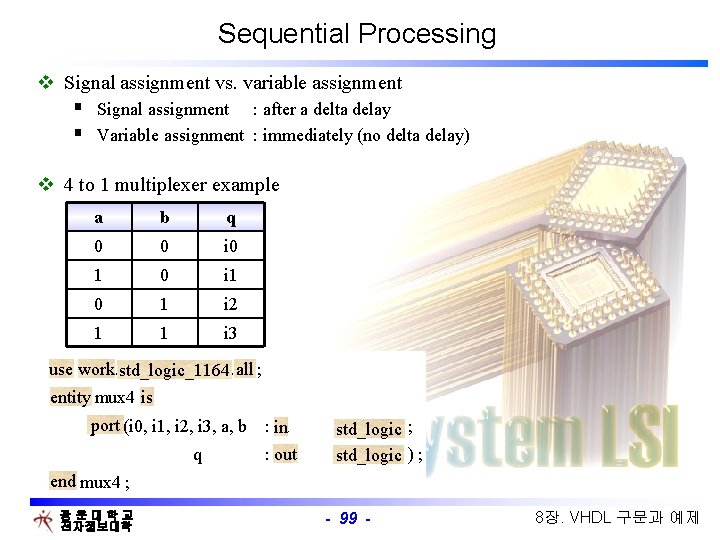

Sequential Processing v Signal assignment vs. variable assignment § Signal assignment : after a delta delay § Variable assignment : immediately (no delta delay) v 4 to 1 multiplexer example a b q 0 0 i 0 1 0 i 1 0 1 i 2 1 1 i 3 use work std_logic_1164 all use work. std_logic_1164. all ; entity is entity mux 4 is port (i 0, i 1, i 2, i 3, a, b q : in in out : out std_logic ; std_logic ) ; std_logic end mux 4 ; 광운대학교 전자정보대학 - 99 - 8장. VHDL 구문과 예제

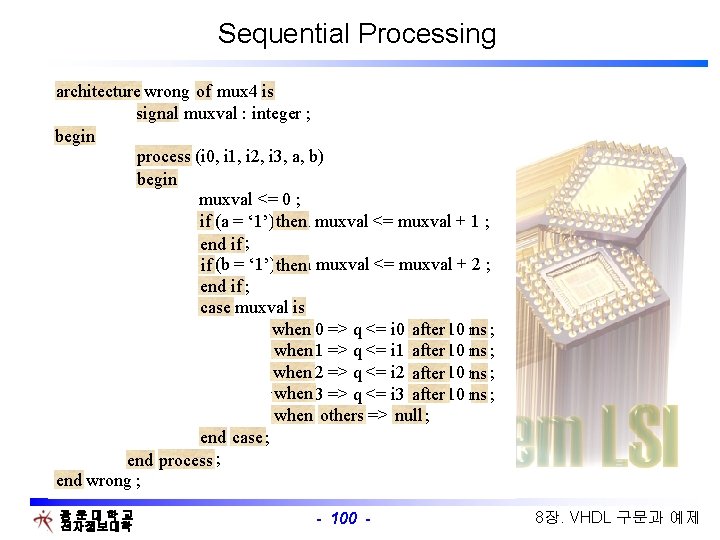

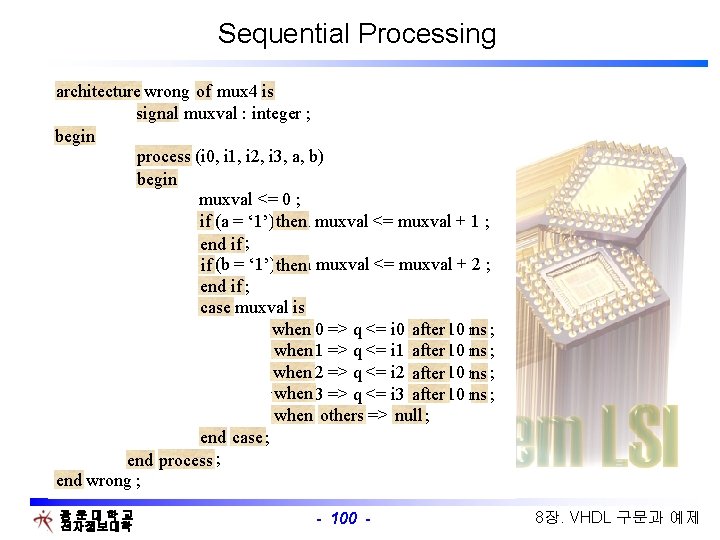

Sequential Processing architecture wrong o mux 4 is architecture of is signal muxval : integer ; signal begin process (i 0, i 1, i 2, i 3, a, b) begin muxval <= 0 ; if (a = ‘ 1’) then muxval <= muxval + 1 ; if then end if ; end if if (b = ‘ 1’) then muxval <= muxval + 2 ; if then end if ; end if case muxval is case is when 0 => q <= i 0 after 10 ns ; when after ns when 1 => q <= i 1 after 10 ns ; when 2 => q <= i 2 after 10 ns ; after ns when 3 => q <= i 3 after 10 ns ; when others => null ; when others null end case ; end case end process ; end process end wrong ; 광운대학교 전자정보대학 - 100 - 8장. VHDL 구문과 예제

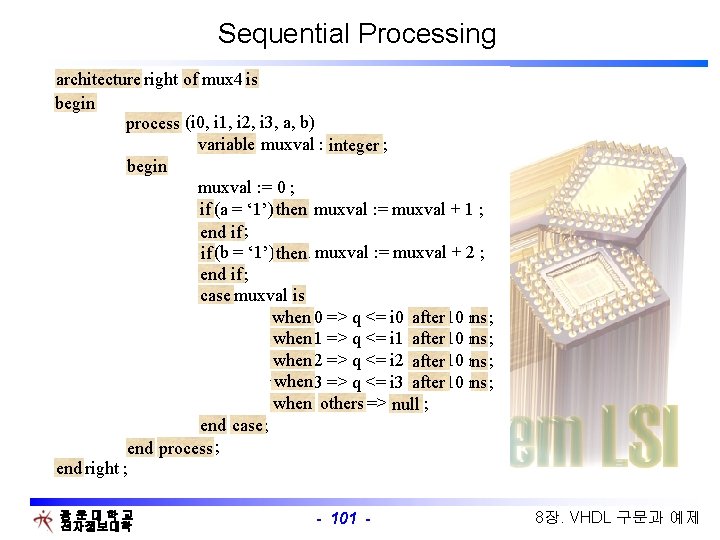

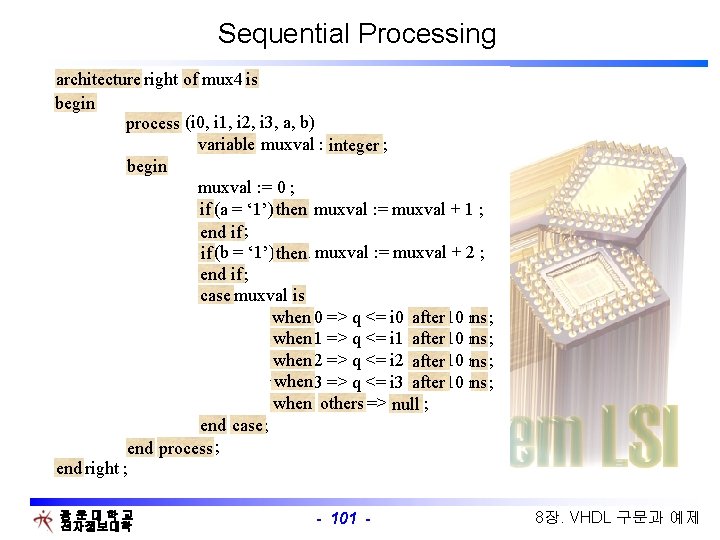

Sequential Processing architecture right of mux 4 is architecture of is begin process (i 0, i 1, i 2, i 3, a, b) process variable muxval : integer ; integer begin muxval : = 0 ; if (a = ‘ 1’) then muxval : = muxval + 1 ; if then end if ; end if if (b = ‘ 1’) then muxval : = muxval + 2 ; if then end if ; end if case muxval is case is when 0 => q <= i 0 after 10 ns ; when after ns when 1 => q <= i 1 after 10 ns ; when 2 => q <= i 2 after 10 ns ; after ns when 3 => q <= i 3 after 10 ns ; when others => null ; when others null end case ; end case end process ; end process end right ; 광운대학교 전자정보대학 - 101 - 8장. VHDL 구문과 예제

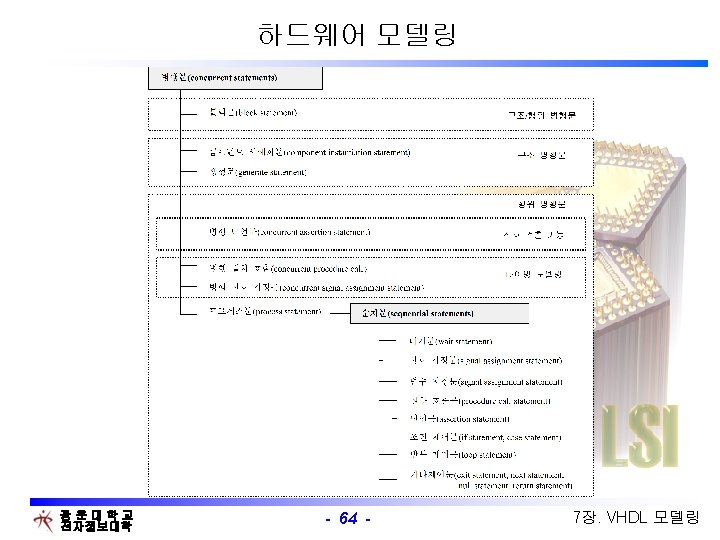

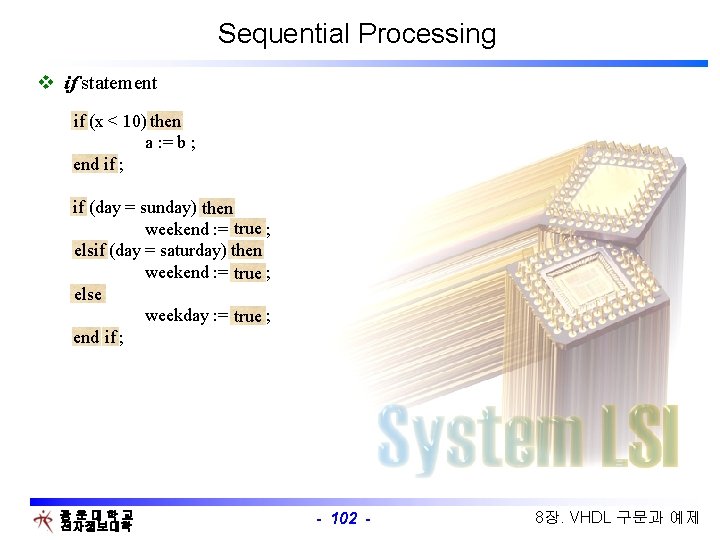

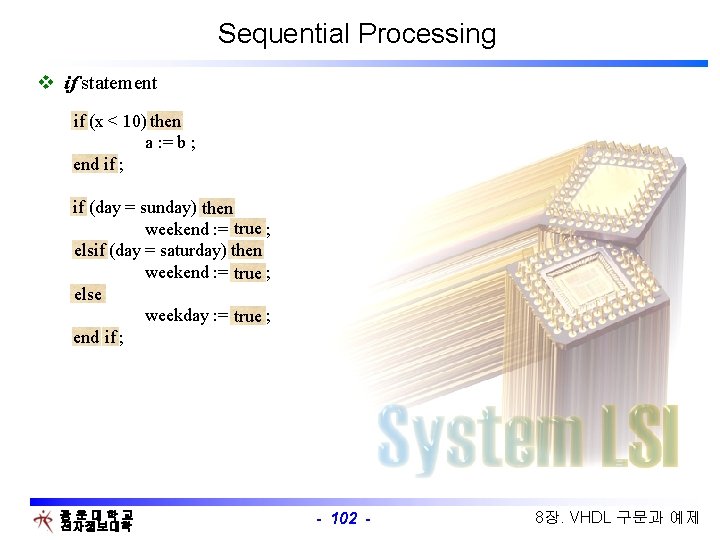

Sequential Processing v if statement if (x < 10) then if then a : = b ; end if if if (day = sunday) then true weekend : = true ; elsif (day = saturday) then weekend : = true ; true else weekday : = true ; true end if ; end if 광운대학교 전자정보대학 - 102 - 8장. VHDL 구문과 예제

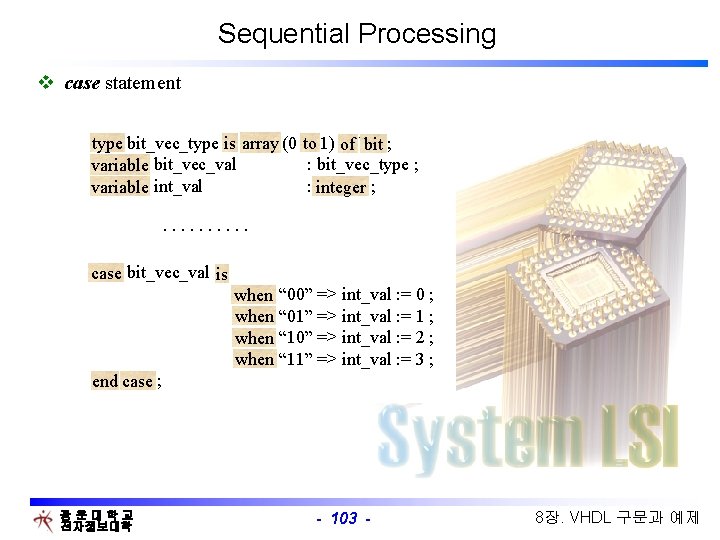

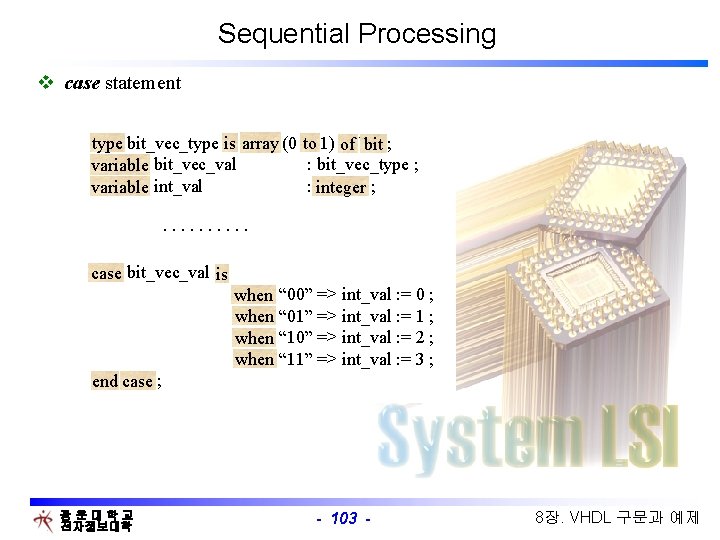

Sequential Processing v case statement type bit_vec_type is array (0 to 1) of bit ; type is array to of bit variable bit_vec_val : bit_vec_type ; variable int_val : integer ; variable integer case bit_vec_val is case is when “ 00” => int_val : = 0 ; when “ 01” => int_val : = 1 ; when “ 10” => int_val : = 2 ; when “ 11” => int_val : = 3 ; when end case ; end case 광운대학교 전자정보대학 - 103 - 8장. VHDL 구문과 예제

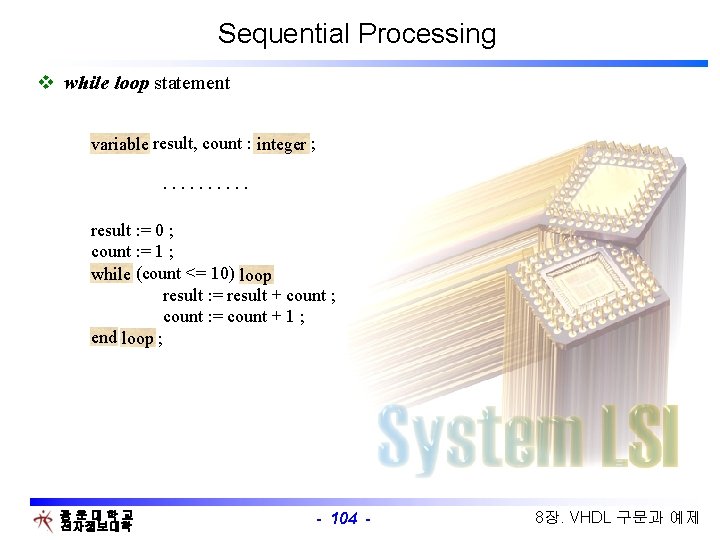

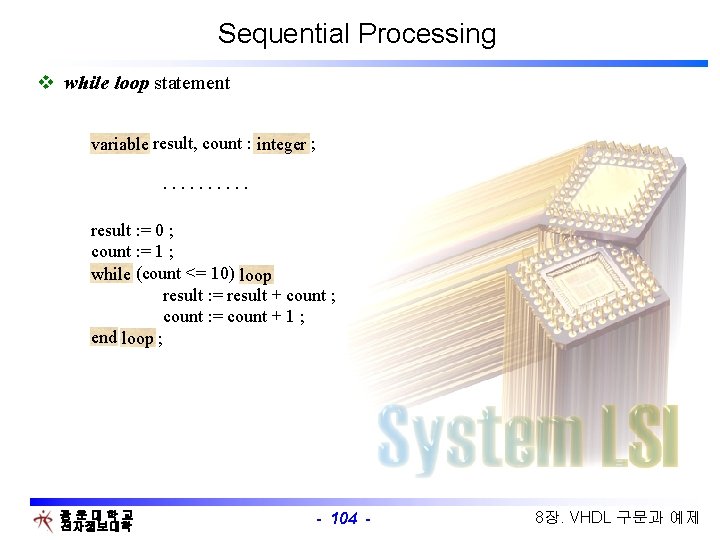

Sequential Processing v while loop statement variable result, count : integer ; variable integer result : = 0 ; count : = 1 ; while (count <= 10) loop while loop result : = result + count ; count : = count + 1 ; end loop ; 광운대학교 전자정보대학 - 104 - 8장. VHDL 구문과 예제

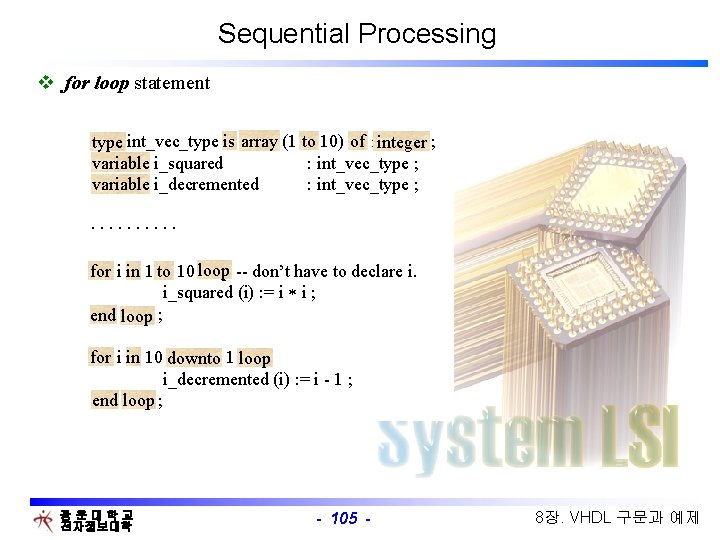

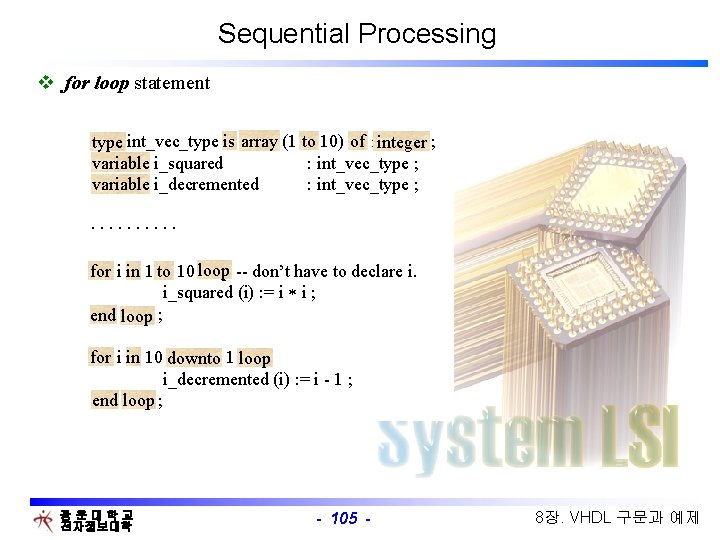

Sequential Processing v for loop statement is array to of integer type int_vec_type is array (1 to 10) of integer ; type varaible i_squared : int_vec_type ; variable varaible i_decremented : int_vec_type ; variable loop for i in 1 to 10 loop -- don’t have to declare i. for in to i_squared (i) : = i i ; end loop for in downto loop for i in 10 downto 1 loop i_decremented (i) : = i - 1 ; end loop ; 광운대학교 전자정보대학 - 105 - 8장. VHDL 구문과 예제

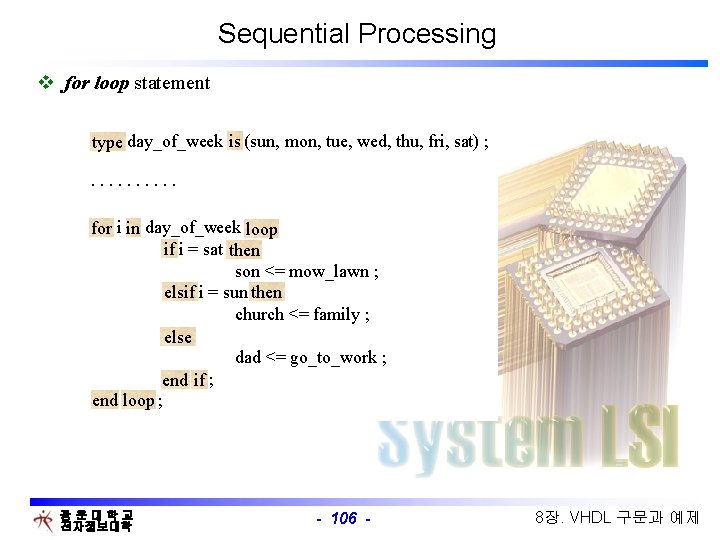

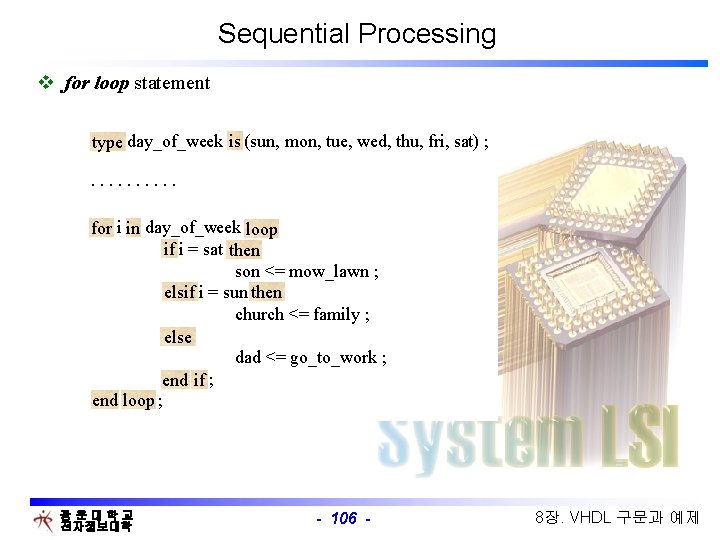

Sequential Processing v for loop statement is type day_of_week is (sun, mon, tue, wed, thu, fri, sat) ; type for i in day_of_week loop for in loop if if i = sat then son <= mow_lawn ; elsif i = sun then elsif then church <= family ; else dad <= go_to_work ; end if end loop ; 광운대학교 전자정보대학 - 106 - 8장. VHDL 구문과 예제

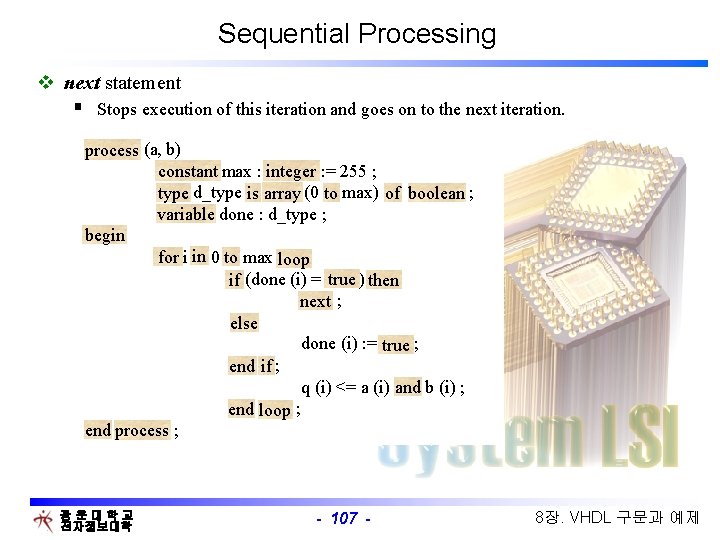

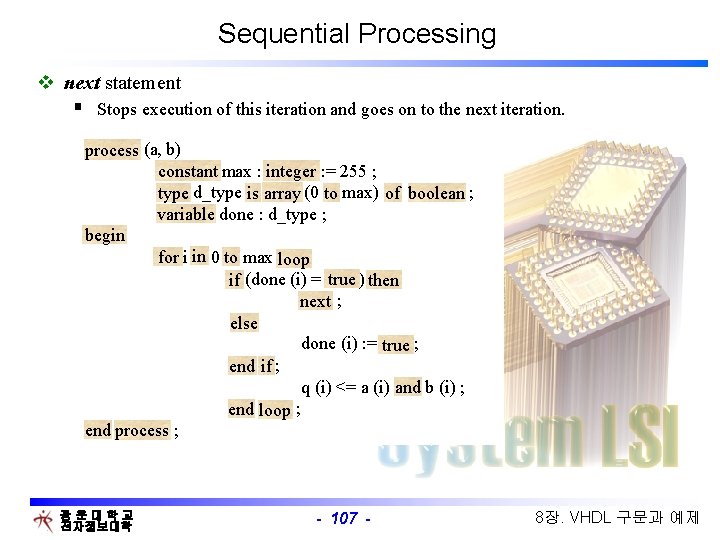

Sequential Processing v next statement § Stops execution of this iteration and goes on to the next iteration. process (a, b) process constant max : integer : = 255 ; constant integer type d_type is array (0 to max) of boolean ; is array to of boolean type variable done : d_type ; variable begin for i in 0 to max loop for in to loop if (done (i) = true ) then true then if next ; next else done (i) : = true ; true end if ; end if q (i) <= a (i) and b (i) ; and end loop ; end loop end process ; end process 광운대학교 전자정보대학 - 107 - 8장. VHDL 구문과 예제

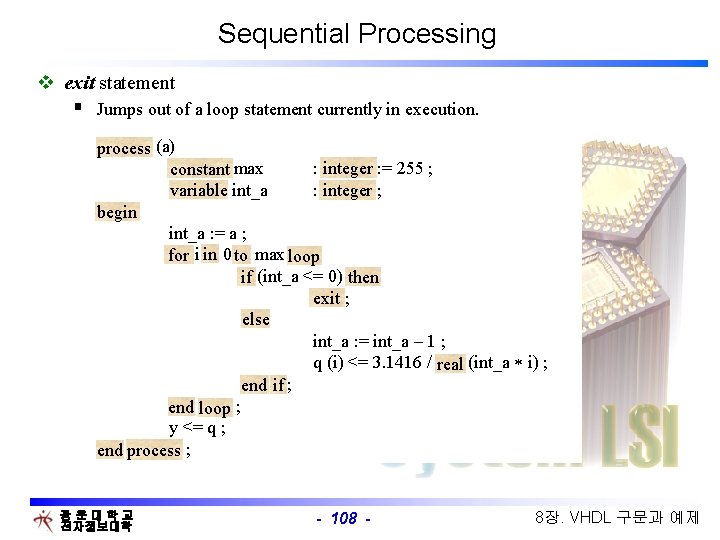

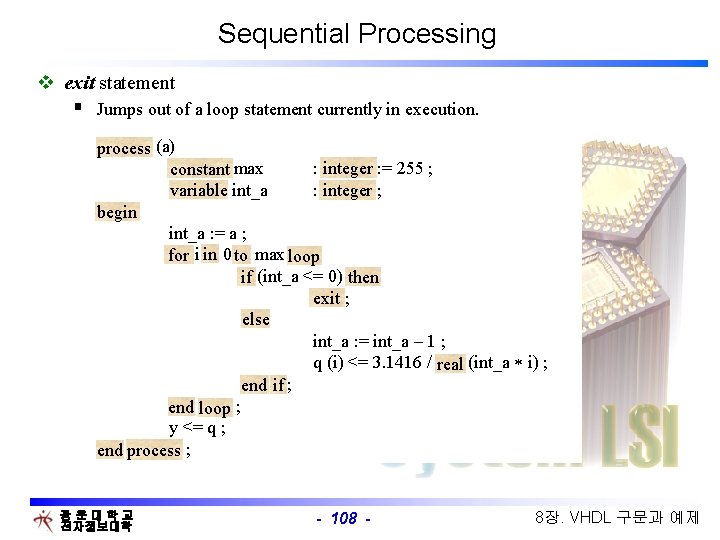

Sequential Processing v exit statement § Jumps out of a loop statement currently in execution. process (a) process integer constant max : integer : = 255 ; constant variable int_a : integer ; variable integer begin int_a : = a ; in to for i in 0 to max loop for loop if (int_a <= 0) then if then exit ; exit else int_a : = int_a – 1 ; q (i) <= 3. 1416 / real (int_a i) ; real end if ; end if end loop ; end loop y <= q ; end process 광운대학교 전자정보대학 - 108 - 8장. VHDL 구문과 예제

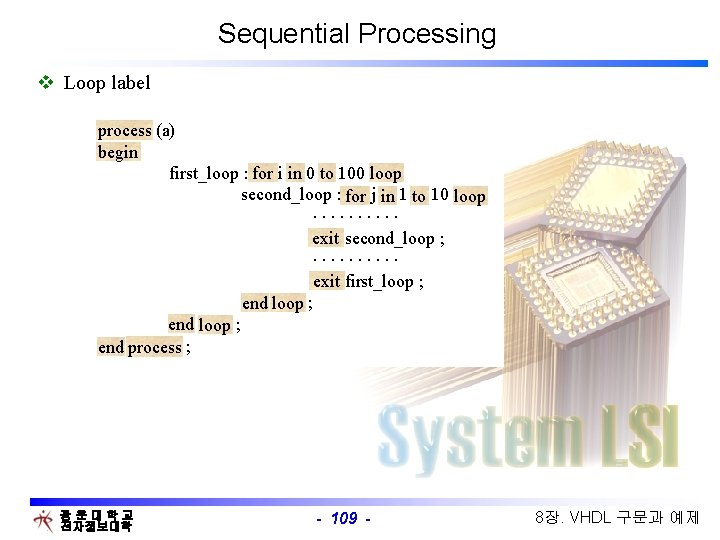

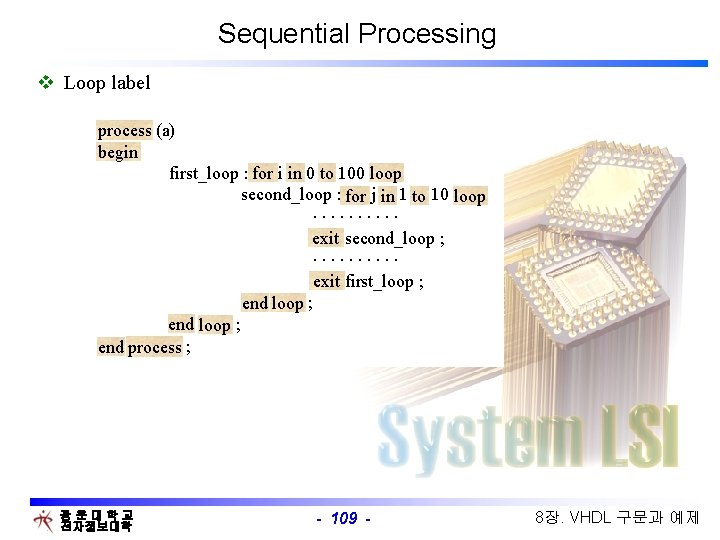

Sequential Processing v Loop label process (a) process begin first_loop : for i in 0 to 100 loop for in to loop second_loop : for j in 1 to 10 loop for in to loop exit second_loop ; exit exit first_loop ; exit end loop ; end loop ; loop end process ; end process 광운대학교 전자정보대학 - 109 - 8장. VHDL 구문과 예제