VHDL Introduction MSc Cristian Sisterna UNSJ Introduction Very

![Process Statement �Syntax process sensitivity_list [declarations; ] begin sequential_statements; end process; 64 DSDA - Process Statement �Syntax process sensitivity_list [declarations; ] begin sequential_statements; end process; 64 DSDA -](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-64.jpg)

![Process Statement [process_label: ] process [(sensitivity_list)] [is] [process_data_object_declarations] begin variable_assignment_statement signal_assignment_statement wait_statement if_statement case_statement Process Statement [process_label: ] process [(sensitivity_list)] [is] [process_data_object_declarations] begin variable_assignment_statement signal_assignment_statement wait_statement if_statement case_statement](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-65.jpg)

![if Statement �Syntax if <boolean_expression> then <sequential_statement(s)> [elsif <boolean_expression> then <sequential_statement(s)>] . . . if Statement �Syntax if <boolean_expression> then <sequential_statement(s)> [elsif <boolean_expression> then <sequential_statement(s)>] . . .](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-70.jpg)

![case Statement [case label: ]case <selector_expression> is when <choice_1> => <sequential_statements> -- branch #1 case Statement [case label: ]case <selector_expression> is when <choice_1> => <sequential_statements> -- branch #1](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-77.jpg)

![for-loop Statement [loop_label]: for identifier in discrete_range loop <sequential_statements> end loop [loop_label]; <identifier> • for-loop Statement [loop_label]: for identifier in discrete_range loop <sequential_statements> end loop [loop_label]; <identifier> •](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-83.jpg)

- Slides: 98

VHDL Introduction MSc Cristian Sisterna UNSJ

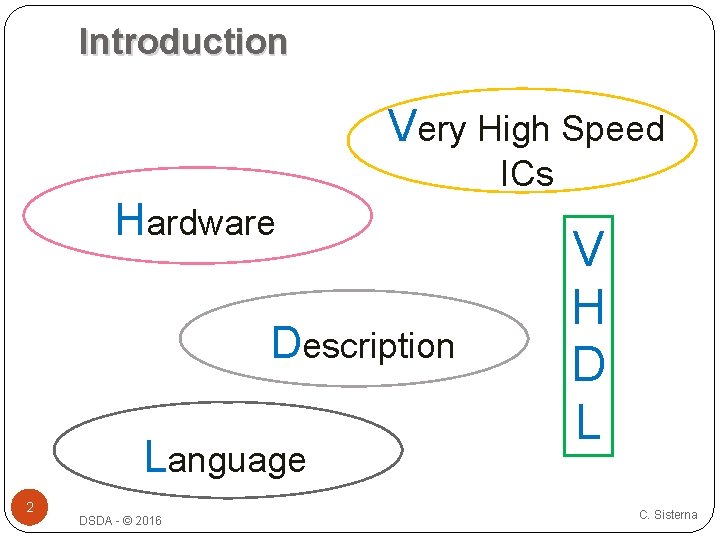

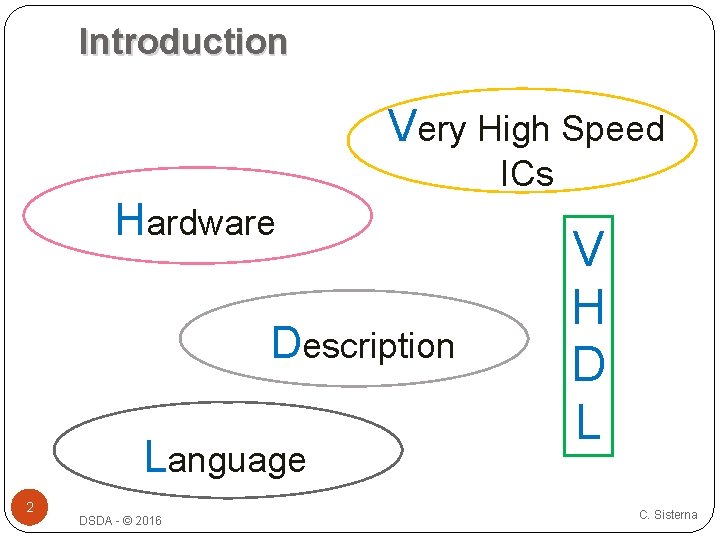

Introduction Very High Speed ICs Hardware Description Language 2 DSDA - © 2016 V H D L C. Sisterna

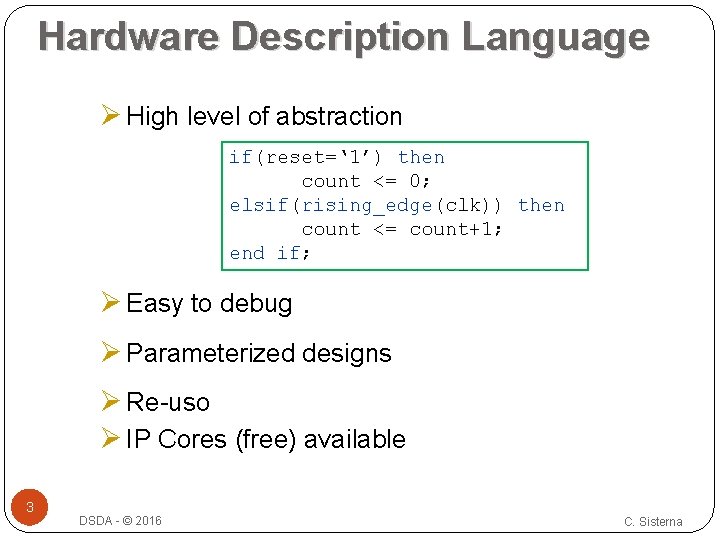

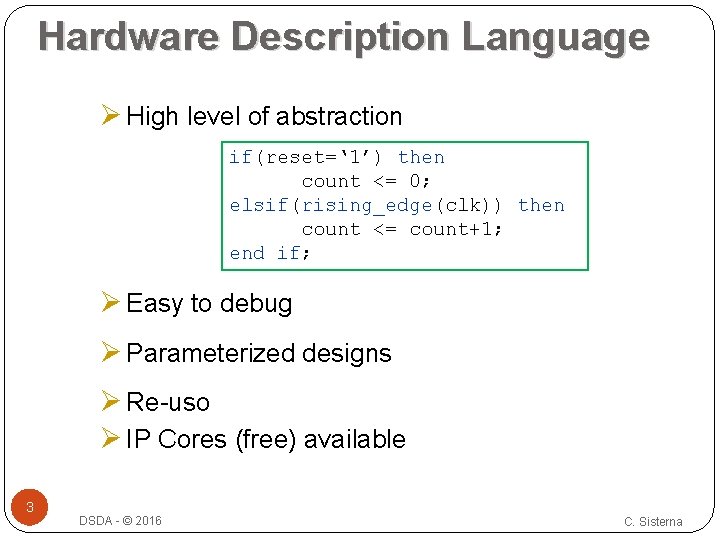

Hardware Description Language Ø High level of abstraction if(reset=‘ 1’) then count <= 0; elsif(rising_edge(clk)) then count <= count+1; end if; Ø Easy to debug Ø Parameterized designs Ø Re-uso Ø IP Cores (free) available 3 DSDA - © 2016 C. Sisterna

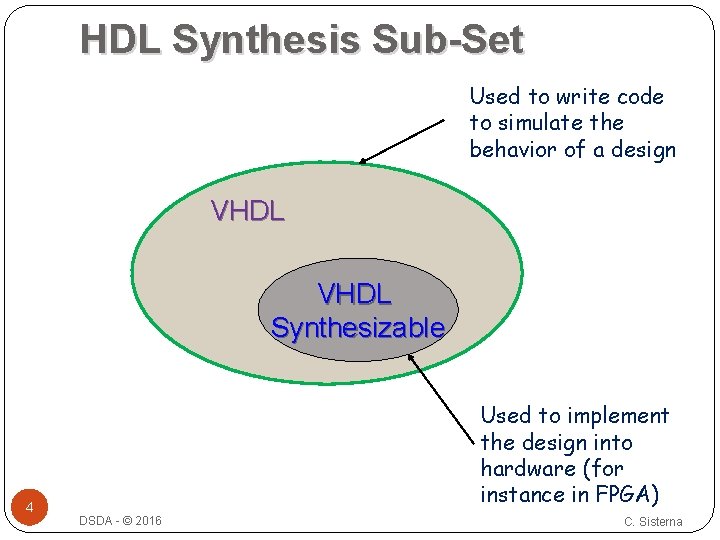

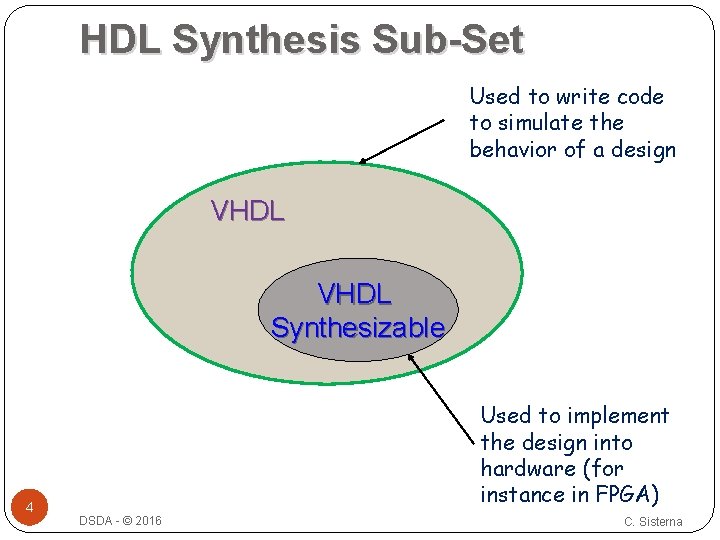

HDL Synthesis Sub-Set Used to write code to simulate the behavior of a design VHDL Synthesizable 4 Used to implement the design into hardware (for instance in FPGA) DSDA - © 2016 C. Sisterna

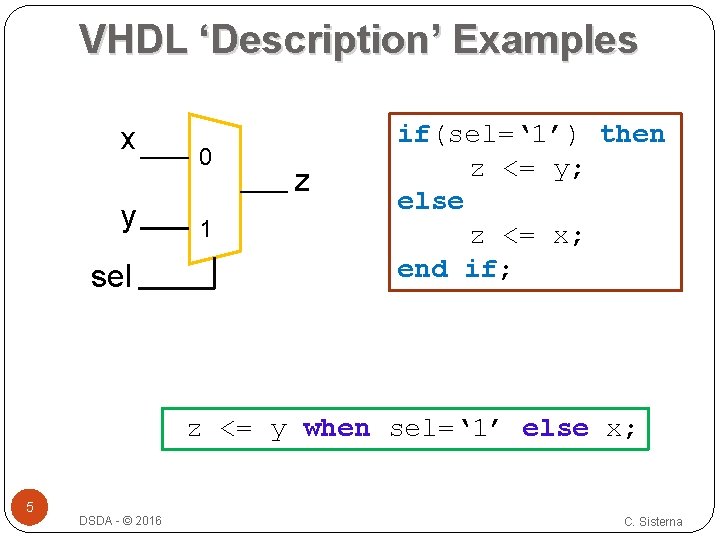

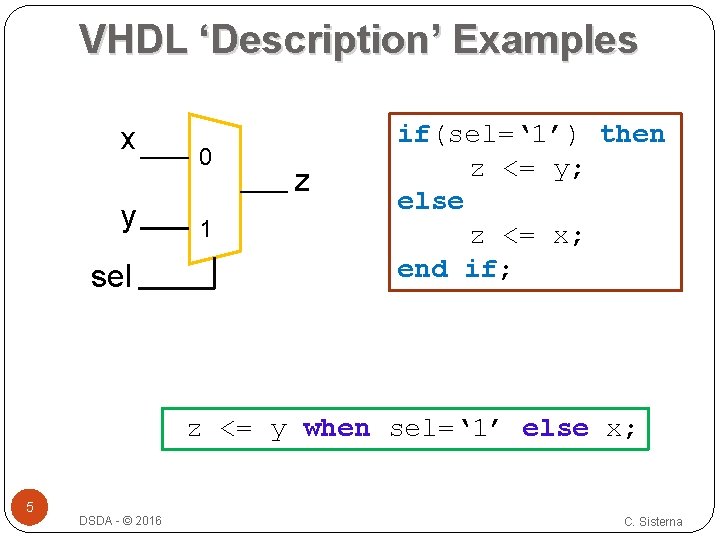

VHDL ‘Description’ Examples x y sel 0 1 z if(sel=‘ 1’) then z <= y; else z <= x; end if; z <= y when sel=‘ 1’ else x; 5 DSDA - © 2016 C. Sisterna

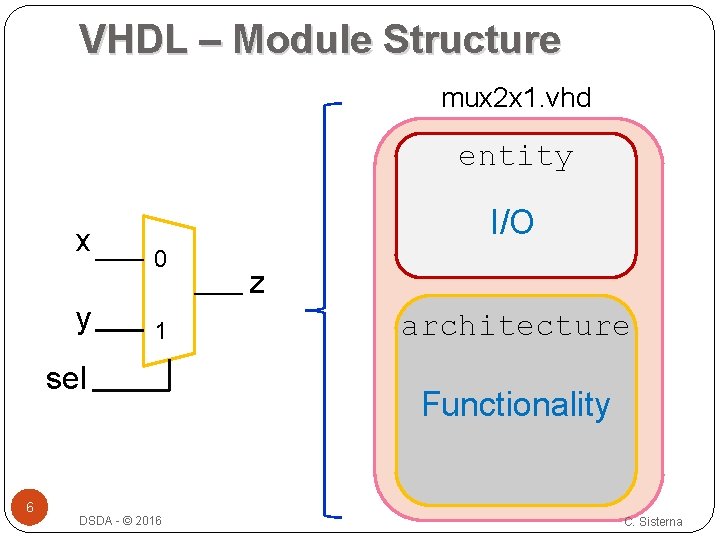

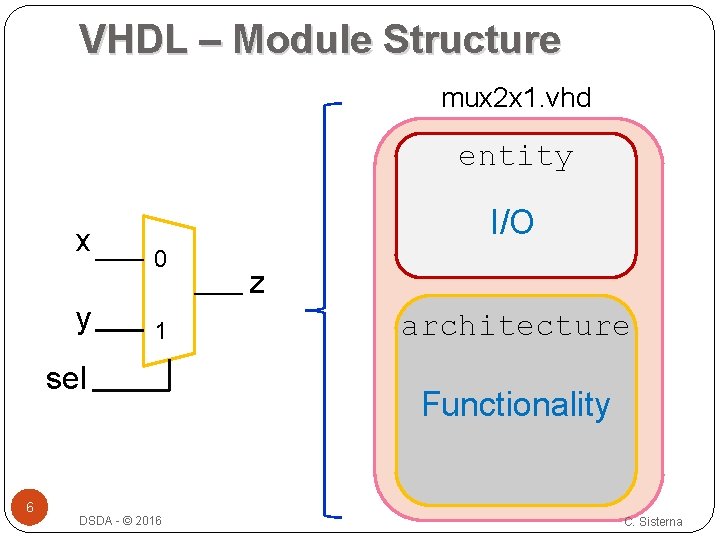

VHDL – Module Structure mux 2 x 1. vhd entity x y I/O 0 1 sel 6 DSDA - © 2016 z architecture Functionality C. Sisterna

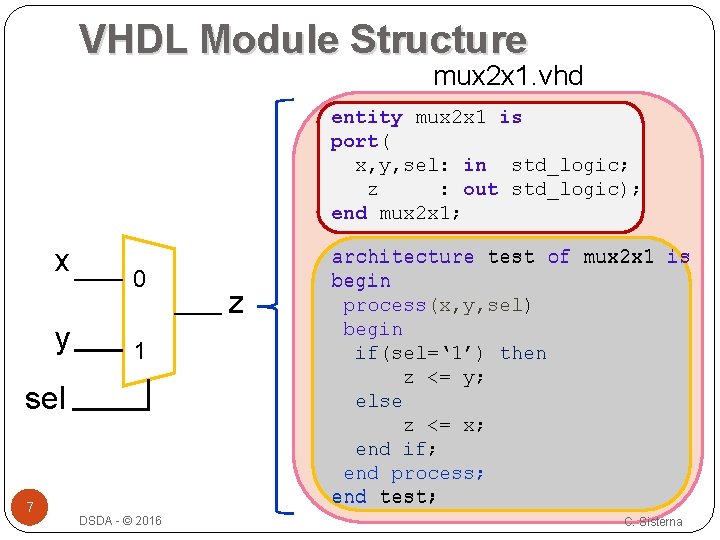

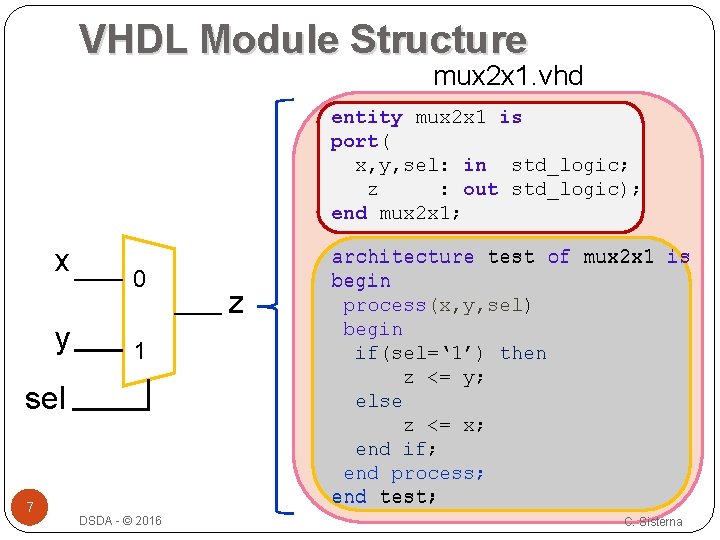

VHDL Module Structure mux 2 x 1. vhd entity mux 2 x 1 is port( x, y, sel: in std_logic; z : out std_logic); end mux 2 x 1; x y 0 1 sel 7 DSDA - © 2016 z architecture test of mux 2 x 1 is begin process(x, y, sel) begin if(sel=‘ 1’) then z <= y; else z <= x; end if; end process; end test; C. Sisterna

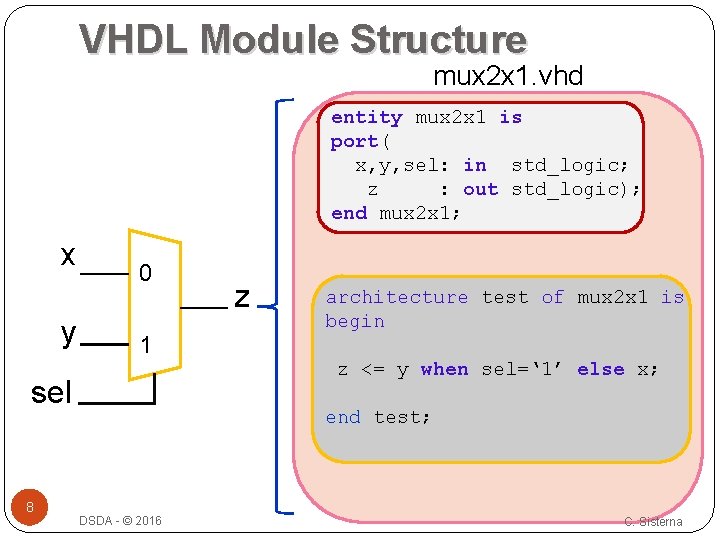

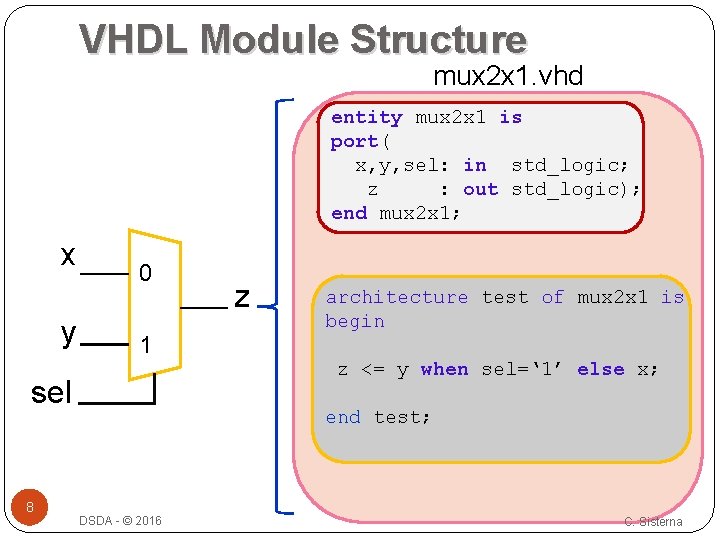

VHDL Module Structure mux 2 x 1. vhd entity mux 2 x 1 is port( x, y, sel: in std_logic; z : out std_logic); end mux 2 x 1; x y 0 1 sel 8 z architecture test of mux 2 x 1 is begin z <= y when sel=‘ 1’ else x; end test; DSDA - © 2016 C. Sisterna

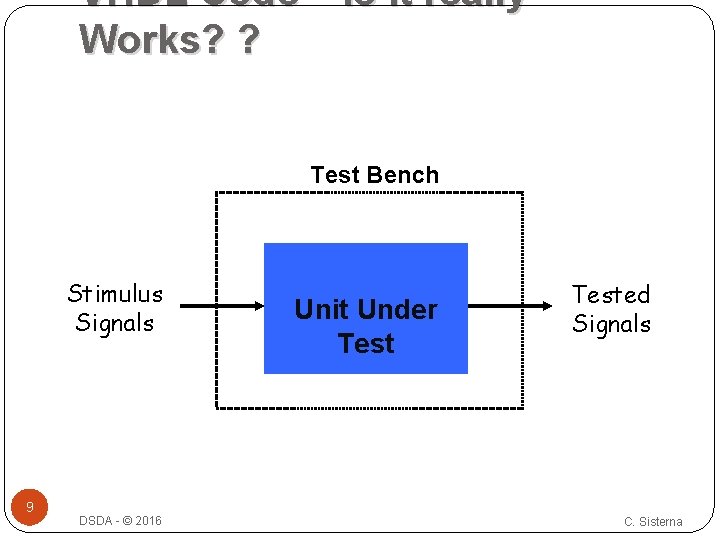

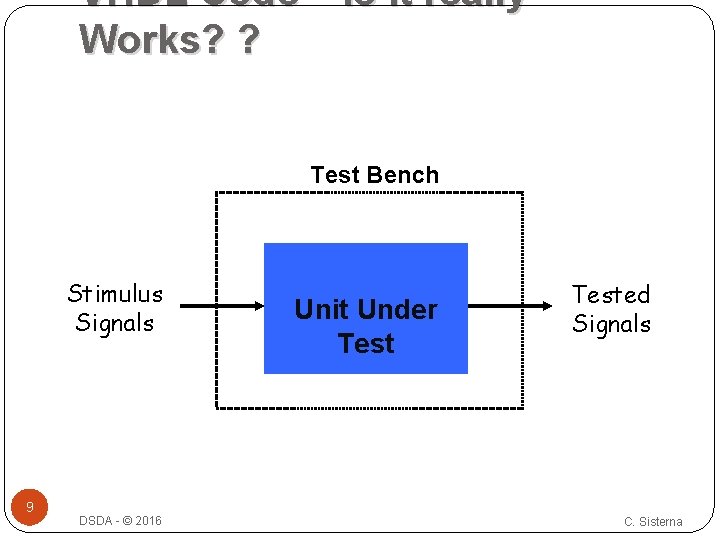

VHDL Code – Is it really Works? ? Test Bench Stimulus Signals 9 DSDA - © 2016 Unit Under Tested Signals C. Sisterna

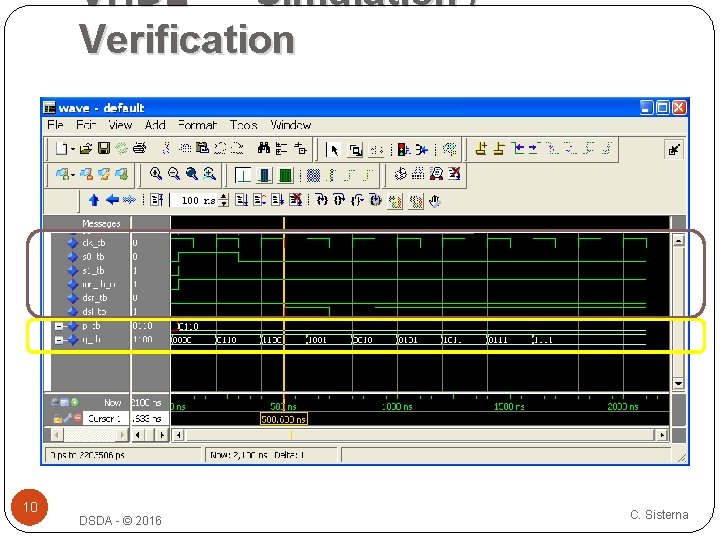

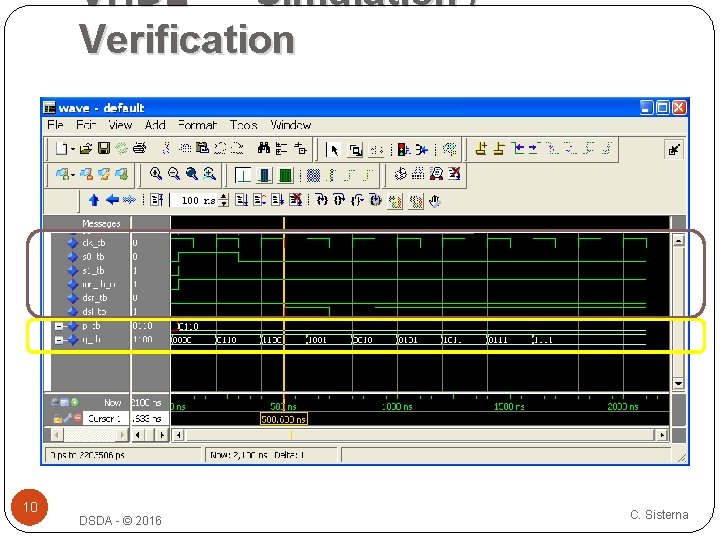

VHDL – Simulation / Verification 10 DSDA - © 2016 C. Sisterna

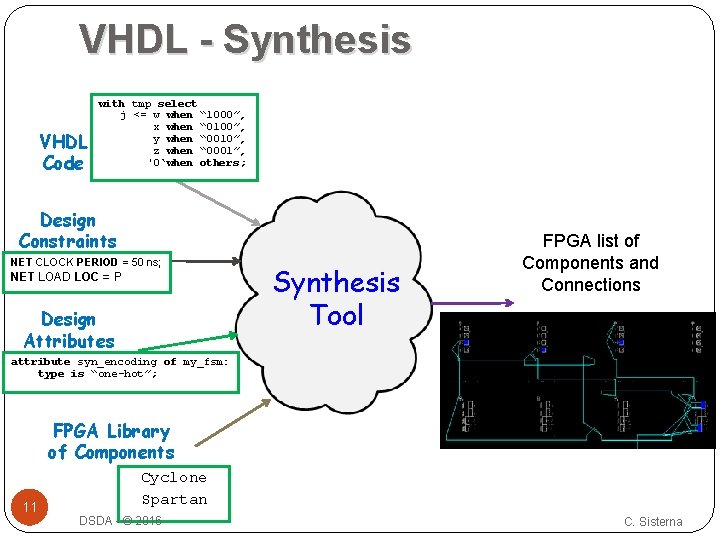

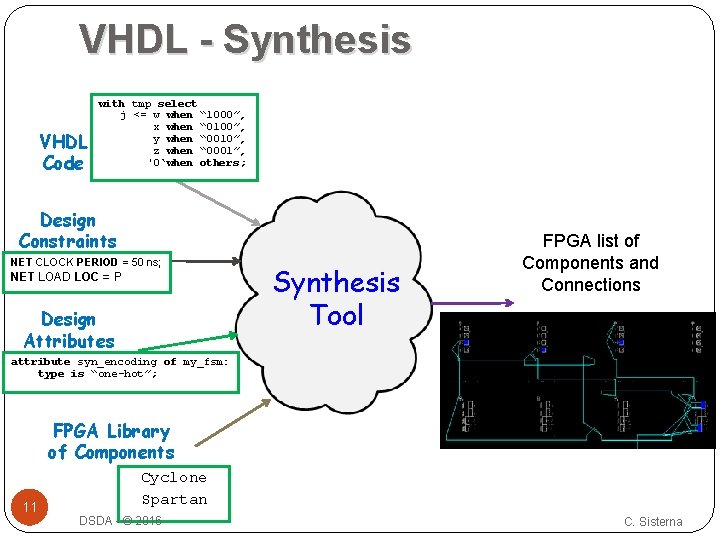

VHDL - Synthesis VHDL Code with tmp select j <= w when “ 1000”, x when “ 0100”, y when “ 0010”, z when “ 0001”, '0‘when others; Design Constraints NET CLOCK PERIOD = 50 ns; NET LOAD LOC = P Design Attributes Synthesis Tool FPGA list of Components and Connections attribute syn_encoding of my_fsm: type is “one-hot”; FPGA Library of Components 11 Cyclone Spartan DSDA - © 2016 C. Sisterna

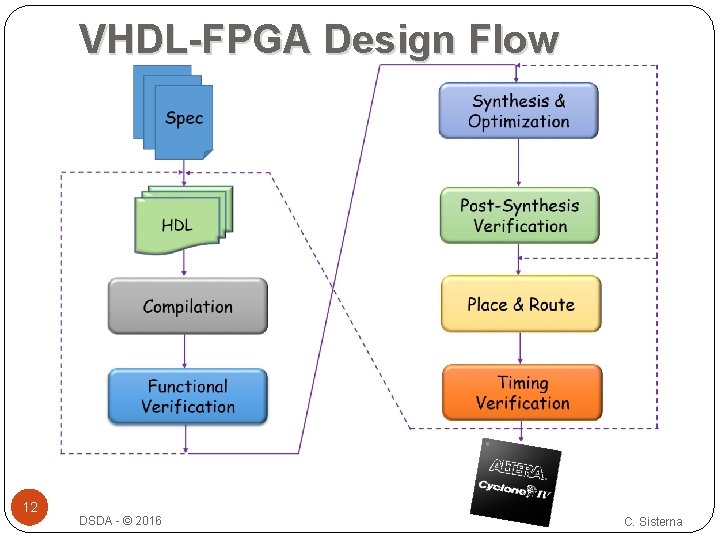

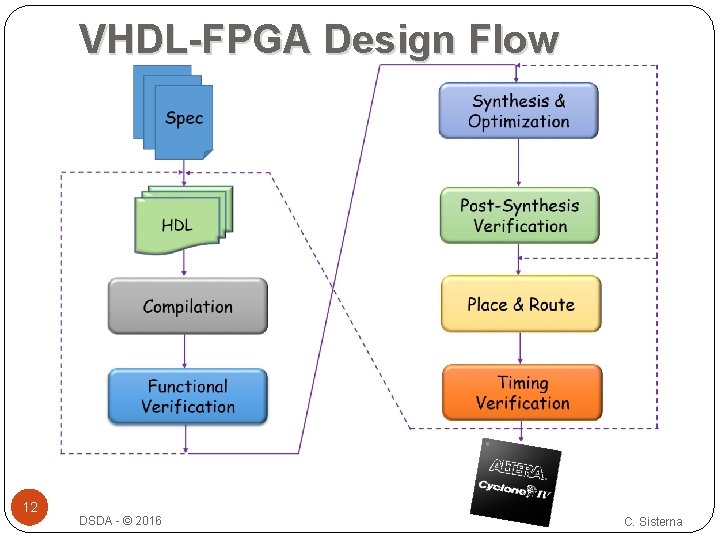

VHDL-FPGA Design Flow 12 DSDA - © 2016 C. Sisterna

Design Implemented in the FPGA 13 DSDA - © 2016 C. Sisterna

FPGA Kit – DE 2 -115 http: //www. terasic. com. tw/cgi-bin/page/archive. pl? Language=English&Category. No=165&No=502 14 DSDA - © 2016 C. Sisterna

VHDL Objects 15 DSDA - © 2016 C. Sisterna

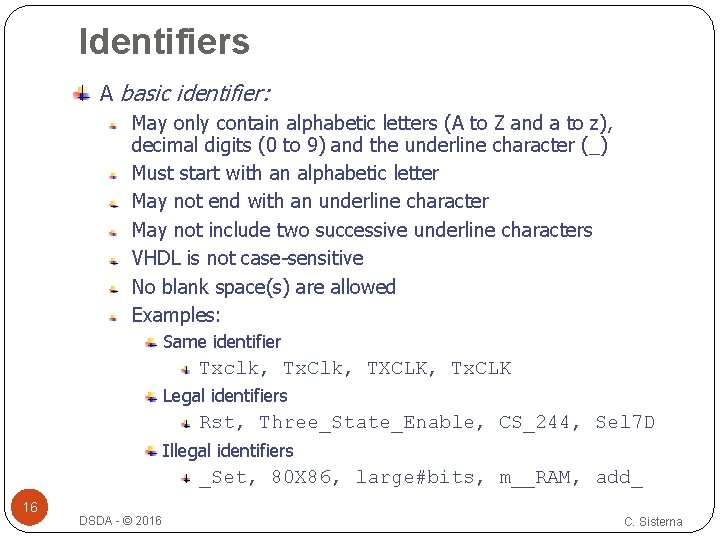

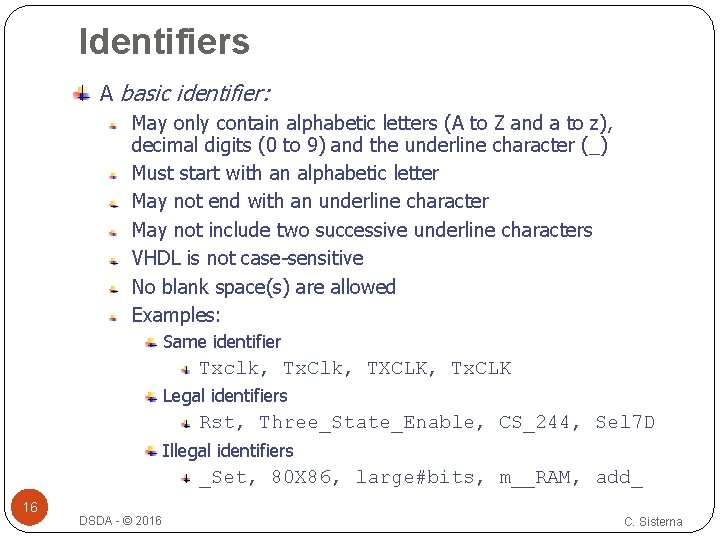

Identifiers A basic identifier: May only contain alphabetic letters (A to Z and a to z), decimal digits (0 to 9) and the underline character (_) Must start with an alphabetic letter May not end with an underline character May not include two successive underline characters VHDL is not case-sensitive No blank space(s) are allowed Examples: Same identifier Txclk, Tx. Clk, TXCLK, Tx. CLK Legal identifiers Rst, Three_State_Enable, CS_244, Sel 7 D Illegal identifiers _Set, 80 X 86, large#bits, m__RAM, add_ 16 DSDA - © 2016 C. Sisterna

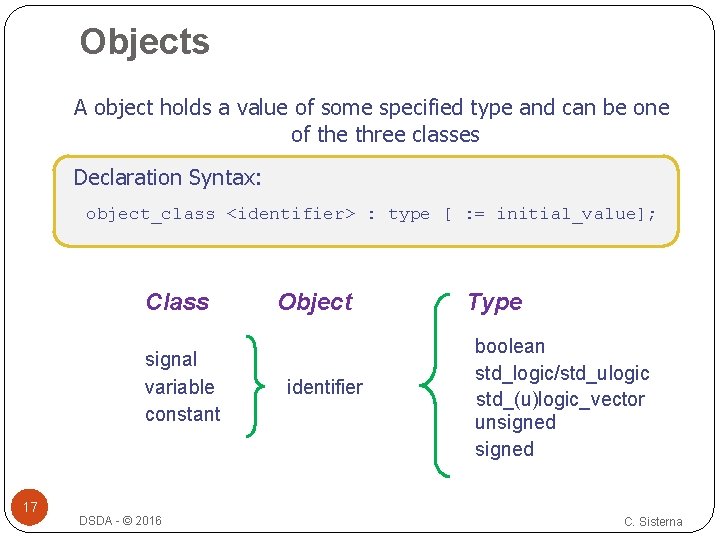

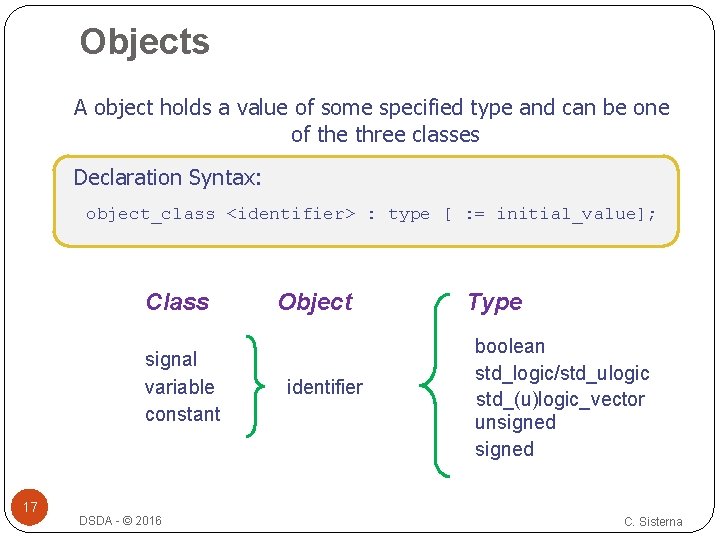

Objects A object holds a value of some specified type and can be one of the three classes Declaration Syntax: object_class <identifier> : type [ : = initial_value]; Class signal variable constant 17 DSDA - © 2016 Object identifier Type boolean std_logic/std_ulogic std_(u)logic_vector unsigned C. Sisterna

Objects Each object has a type and a class The type indicates what type of data can be hold by the data object The class indicates what can be done with the data object Constant Variable constant setup_time: time : = 3 ns; variable flag: boolean : = true; variable add_bus: std_logict_vector (12 downto 0); Classes Signal 18 constant data_bus: integer : = 32; signal reset : bit; signal my_start_up: std_logic; File DSDA - © 2016 C. Sisterna

Signal Declaration - Architecture Signal Declarations: A signal is declared in the declarative part of an architecture signal count_i: std_logic; Signal Name (identifier) 19 DSDA - © 2016 Signal Type boolean std_logic/std_ulogic std_(u)logic_vector unsigned integer C. Sisterna

Signal Declaration Entity Port declarations appear in the port section of an entity declaration. Each port declaration is seperated by semicolon from the others A port declaration has three parts: signal reset_n: in std_logic; Signal Name 20 Port Mode in out inout buffer DSDA - © 2016 Signal Type boolean std_(u)logic_vector unsigned integer C. Sisterna

Signal Declaration – Ports in the Entity 21 DSDA - © 2016 C. Sisterna

Signal Assignment count <= count + 1; carry_out <= (a and b) or (a and c) or (b and c); Z <= y; Left Hand Side (LHS) Target Signal LHS Signal Type 22 DSDA - © 2016 Right Hand Side (RHS) Source Signal(s) RHS Signal Type C. Sisterna

Signal – How to read an output An output port declared as mode out can not be read How to solve this problem? entity and_nand is port( a, b : in std_logic; entity and_nand is z, z_bar: out std_logic); port( end; a, b: in std_logic; z, z_bar: out std_logic); architecture bad of and_nand is end; begin z <= a and b; architecture bad of and_nand is z_bar <= not z; signal int_sig: std_logic; end; begin int_sig <= a and b; z <= int_sig; z_bar <= not int_sig; end; 23 DSDA - © 2016 C. Sisterna

Constant Declaration An Object of class constant holds a single value of a specific type The value is assigned to the constant during its declaration and the value can not be changed Constant declaration: constant <identifier>: type : = value; 24 DSDA - © 2016 C. Sisterna

Constant Declarations architecture behavioral of counterx 16 is constant Bus_Width: integer : = 16; constant GNDLogic: bit : = '0'; constant error_flag: boolean : = true; constant cnt_max: std_logic_vector(3 downto 0): =“ 1111”; signal count_tmp: std_logic_vector(3 downto 0); begin 25 DSDA - © 2016 C. Sisterna

VHDL Operators 26 DSDA - © 2016 C. Sisterna

Logic Operators 27 DSDA - © 2016 C. Sisterna

Boolean or Logic Operators � All boolean operators have the same precedence Parenthesis must always be used to separate out the different boolean operators in an expression carry <= a and b or a and c or b and c; -carry <= (a and b) or (a and c) or (b and c); -- The only exception is the not operator zout <= not a and b; -- equivalent to zout <= (not a) and b; 28 DSDA - © 2016 C. Sisterna

Boolean or Logic Operators The inversion operands nand nor are not associative y 1 <= a nand b nand c; -- illegal y 1 <= (a nand b) nand c; -y 1 <= a nand (b nand c); -- Non inversion operands are associative parity <= d 0 xor d 1 xor d 2 xor d 3 xor d 4 xor d 5 xor d 6 xor d 7; 29 DSDA - © 2016 C. Sisterna

Relational Operators 30 DSDA - © 2016 C. Sisterna

Relational Operators �All types have equality and inequality operators The result of relational operators is boolean type Boolean operators can be used with relational operators data <= a=0 and b=1; -- data is type? Relational operatos have higher precedence than boolean operators. However, it is a good VHDL style coding to use parenthesis: data <= (a=0) and (b=1); 31 DSDA - © 2016 C. Sisterna

Mathematical Operators 32 DSDA - © 2016 C. Sisterna

Mathematical Operators 33 DSDA - © 2016 C. Sisterna

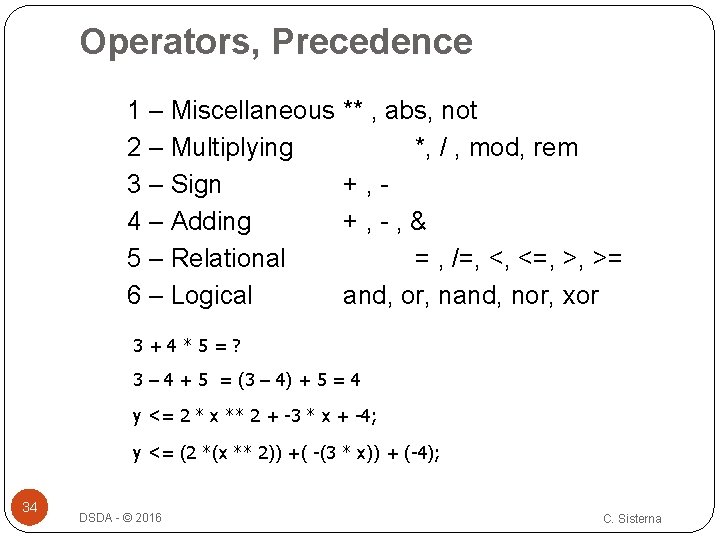

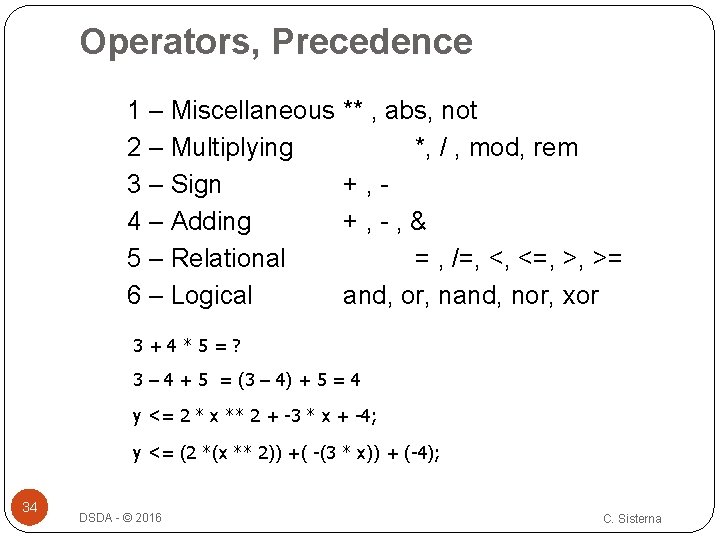

Operators, Precedence 1 – Miscellaneous 2 – Multiplying 3 – Sign 4 – Adding 5 – Relational 6 – Logical ** , abs, not *, / , mod, rem +, +, -, & = , /=, <, <=, >, >= and, or, nand, nor, xor 3+4*5=? 3 – 4 + 5 = (3 – 4) + 5 = 4 y <= 2 * x ** 2 + -3 * x + -4; y <= (2 *(x ** 2)) +( -(3 * x)) + (-4); 34 DSDA - © 2016 C. Sisterna

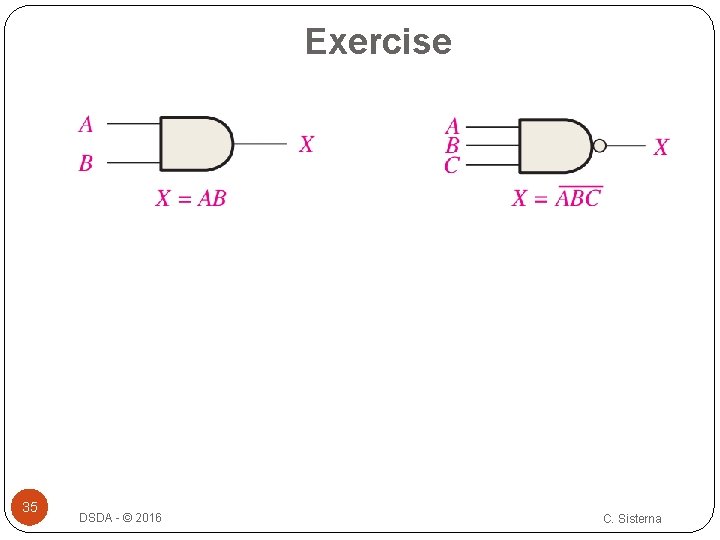

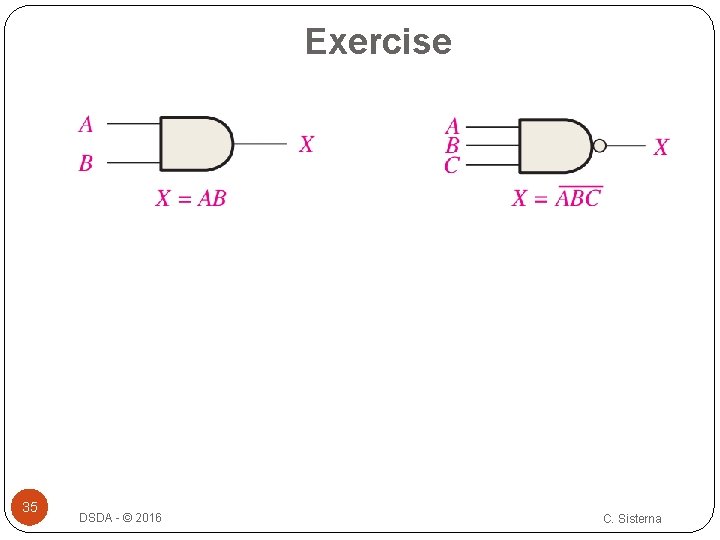

Exercise 35 DSDA - © 2016 C. Sisterna

VHDL Types 36 DSDA - © 2016 C. Sisterna

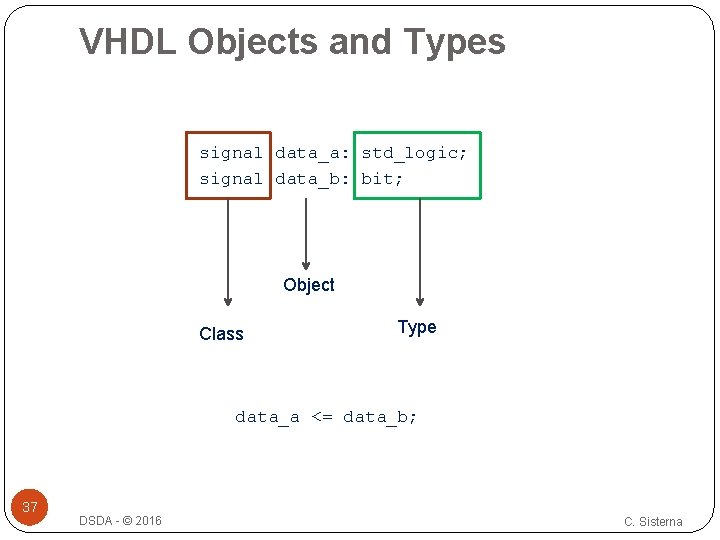

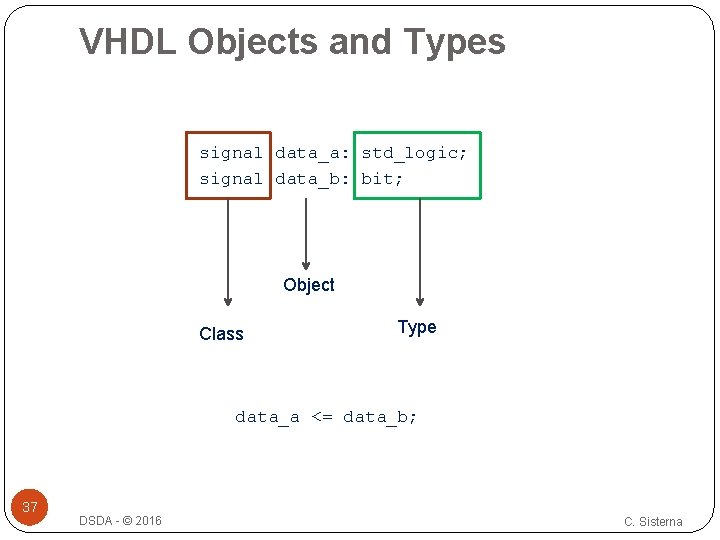

VHDL Objects and Types signal data_a: std_logic; signal data_b: bit; Object Class Type data_a <= data_b; 37 DSDA - © 2016 C. Sisterna

Boolean Type The VHDL standard defines boolean type as follow: type boolean is (false, true); Type boolean is the built-in comparison type in VHDL All the comparison results are of boolean type 38 DSDA - © 2016 C. Sisterna

Boolean Type signal sys_on : std_logic; signal sys_off: std_logic; . . . if (sys_on = sys_off) then std_logic boolean variable bandera: boolean; signal a, b : std_logic; . . bandera : = a < b; -- ? bandera : = a ; -- ? 39 DSDA - © 2016 C. Sisterna

std_logic Type PACKAGE std_logic_1164 IS ------------------------ -- logic state system (unresolved) ------------------------ TYPE std_ulogic IS ( 'U', -- Uninitialized 'X', -- Forcing Unknown '0', -- Forcing 0 '1', -- Forcing 1 'Z', -- High Impedance 'W', -- Weak Unknown 'L', -- Weak 0 'H', -- Weak 1 '-' -- Wild card ); SUBTYPE std_logic IS resolved std_ulogic; 40 DSDA - © 2016 C. Sisterna

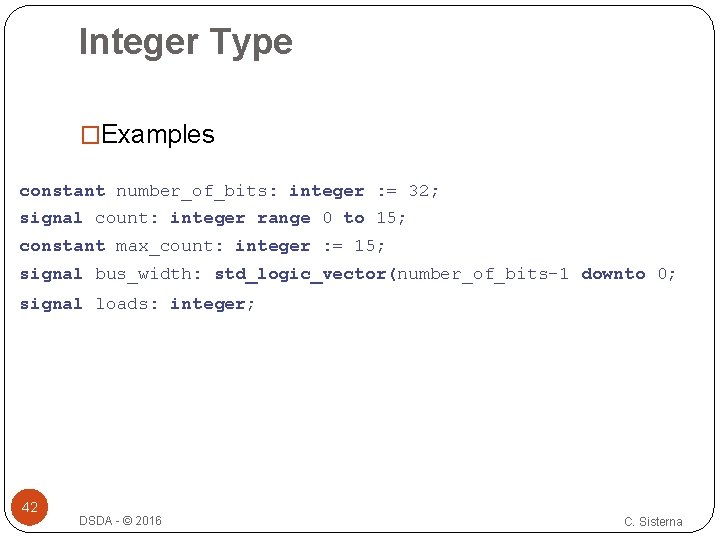

Integer Type An integer type defines a type whose set of values fall within a specified integer range Minimum range –(231 -1) to +(231 -1) VHDL standard defines integer type as follow: type integer is range -2147483648 to +2147483747; 41 DSDA - © 2016 C. Sisterna

Integer Type �Examples constant number_of_bits: integer : = 32; signal count: integer range 0 to 15; constant max_count: integer : = 15; signal bus_width: std_logic_vector(number_of_bits-1 downto 0; signal loads: integer; 42 DSDA - © 2016 C. Sisterna

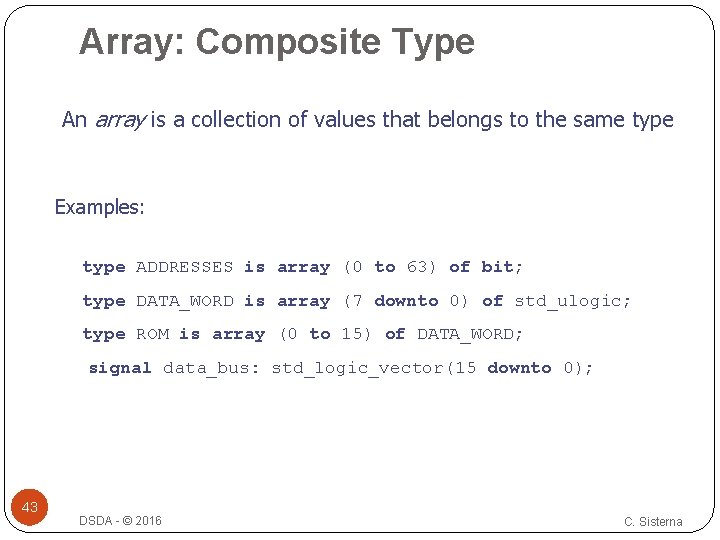

Array: Composite Type An array is a collection of values that belongs to the same type Examples: type ADDRESSES is array (0 to 63) of bit; type DATA_WORD is array (7 downto 0) of std_ulogic; type ROM is array (0 to 15) of DATA_WORD; signal data_bus: std_logic_vector(15 downto 0); 43 DSDA - © 2016 C. Sisterna

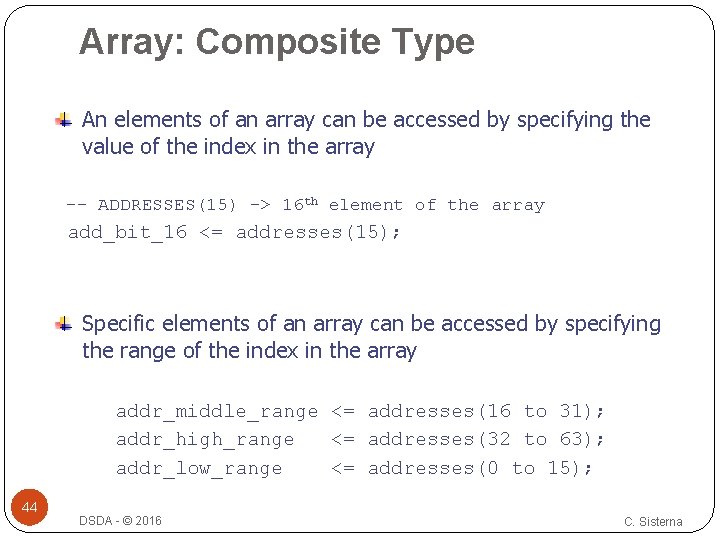

Array: Composite Type An elements of an array can be accessed by specifying the value of the index in the array -- ADDRESSES(15) -> 16 th element of the array add_bit_16 <= addresses(15); Specific elements of an array can be accessed by specifying the range of the index in the array addr_middle_range <= addresses(16 to 31); addr_high_range <= addresses(32 to 63); addr_low_range <= addresses(0 to 15); 44 DSDA - © 2016 C. Sisterna

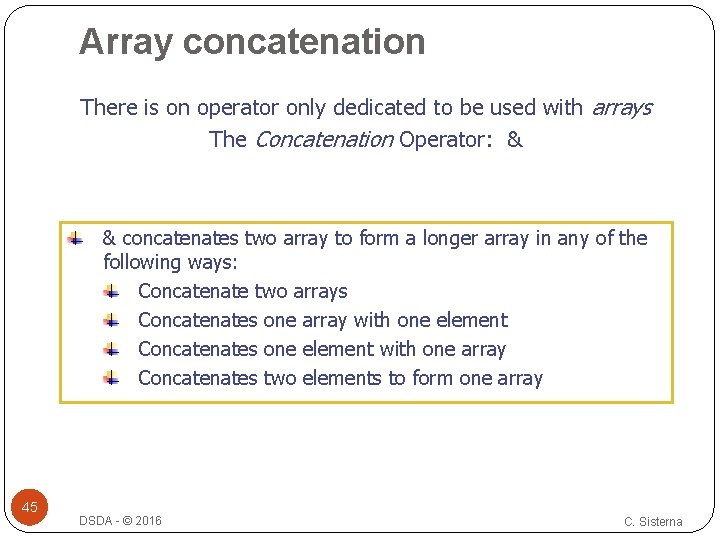

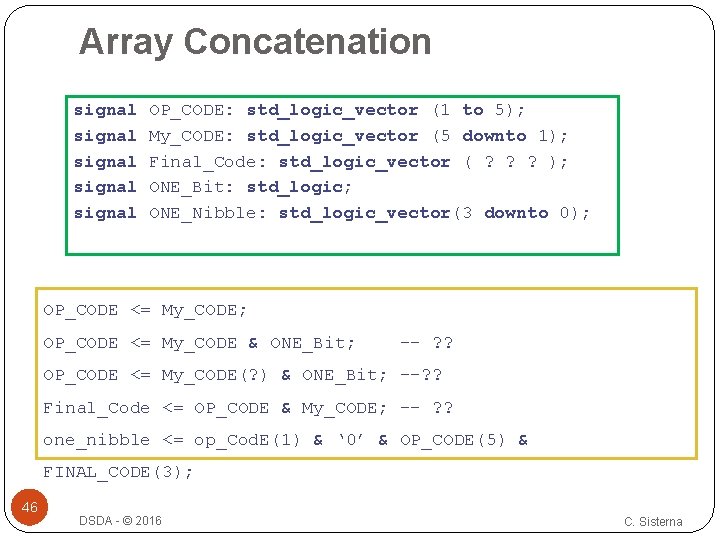

Array concatenation There is on operator only dedicated to be used with arrays The Concatenation Operator: & & concatenates two array to form a longer array in any of the following ways: Concatenate two arrays Concatenates one array with one element Concatenates one element with one array Concatenates two elements to form one array 45 DSDA - © 2016 C. Sisterna

Array Concatenation signal OP_CODE: std_logic_vector (1 to 5); signal My_CODE: std_logic_vector (5 downto 1); signal Final_Code: std_logic_vector ( ? ? ? ); signal ONE_Bit: std_logic; signal ONE_Nibble: std_logic_vector(3 downto 0); OP_CODE <= My_CODE; OP_CODE <= My_CODE & ONE_Bit; -- ? ? OP_CODE <= My_CODE(? ) & ONE_Bit; --? ? Final_Code <= OP_CODE & My_CODE; -- ? ? one_nibble <= op_Cod. E(1) & ‘ 0’ & OP_CODE(5) & FINAL_CODE(3); 46 DSDA - © 2016 C. Sisterna

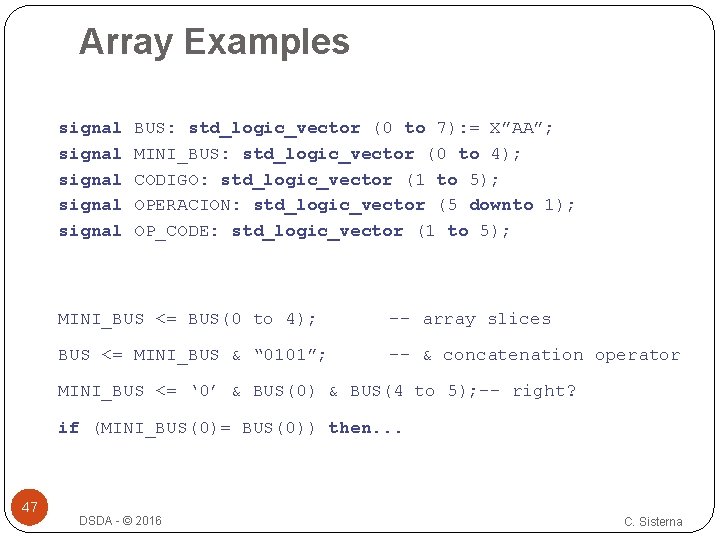

Array Examples signal BUS: std_logic_vector (0 to 7): = X”AA”; signal MINI_BUS: std_logic_vector (0 to 4); signal CODIGO: std_logic_vector (1 to 5); signal OPERACION: std_logic_vector (5 downto 1); signal OP_CODE: std_logic_vector (1 to 5); MINI_BUS <= BUS(0 to 4); -- array slices BUS <= MINI_BUS & “ 0101”; -- & concatenation operator MINI_BUS <= ‘ 0’ & BUS(0) & BUS(4 to 5); -- right? if (MINI_BUS(0)= BUS(0)) then. . . 47 DSDA - © 2016 C. Sisterna

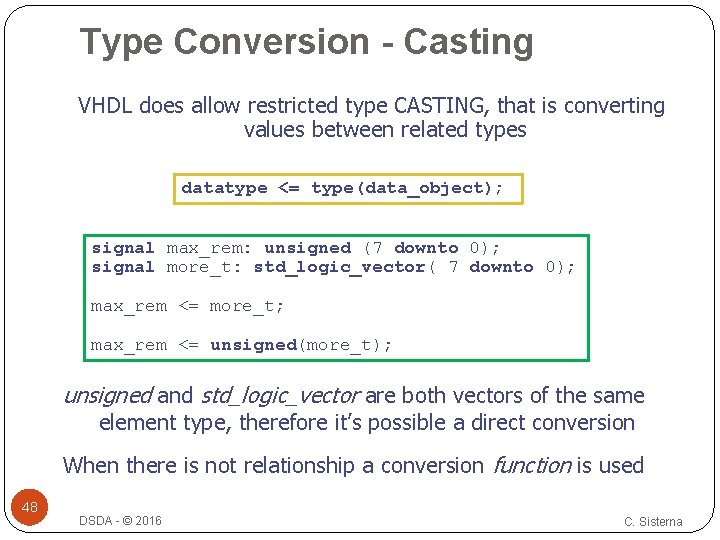

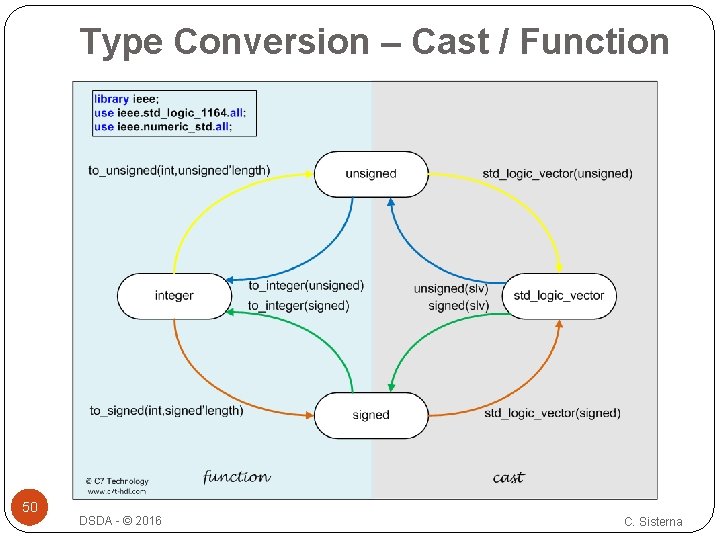

Type Conversion - Casting VHDL does allow restricted type CASTING, that is converting values between related types datatype <= type(data_object); signal max_rem: unsigned (7 downto 0); signal more_t: std_logic_vector( 7 downto 0); max_rem <= more_t; max_rem <= unsigned(more_t); unsigned and std_logic_vector are both vectors of the same element type, therefore it’s possible a direct conversion When there is not relationship a conversion function is used 48 DSDA - © 2016 C. Sisterna

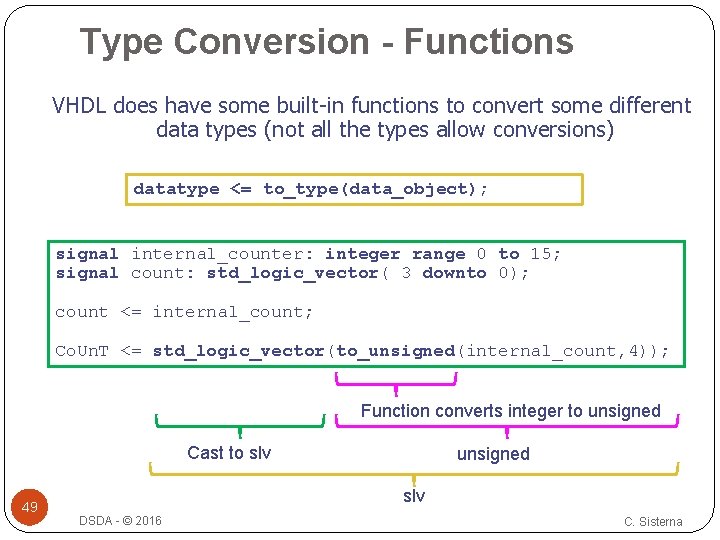

Type Conversion - Functions VHDL does have some built-in functions to convert some different data types (not all the types allow conversions) datatype <= to_type(data_object); signal internal_counter: integer range 0 to 15; signal count: std_logic_vector( 3 downto 0); count <= internal_count; Co. Un. T <= std_logic_vector(to_unsigned(internal_count, 4)); Function converts integer to unsigned Cast to slv 49 unsigned slv DSDA - © 2016 C. Sisterna

Type Conversion – Cast / Function 50 DSDA - © 2016 C. Sisterna

Describing Combinational Logic with VHDL 51 DSDA - © 2016 C. Sisterna

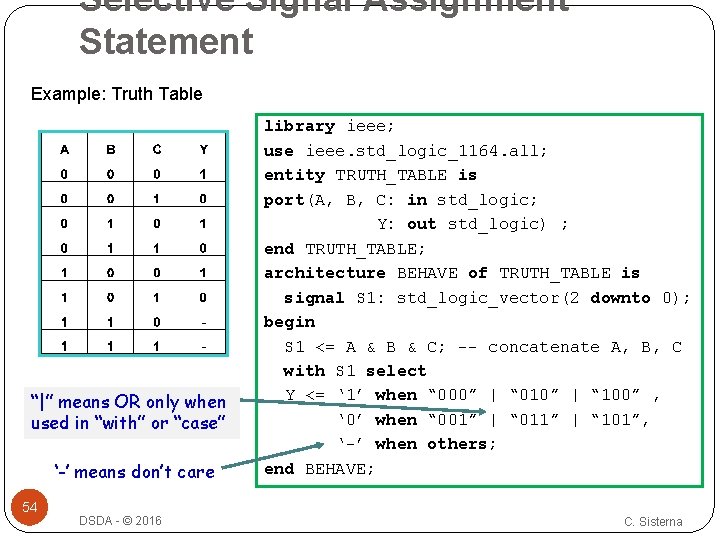

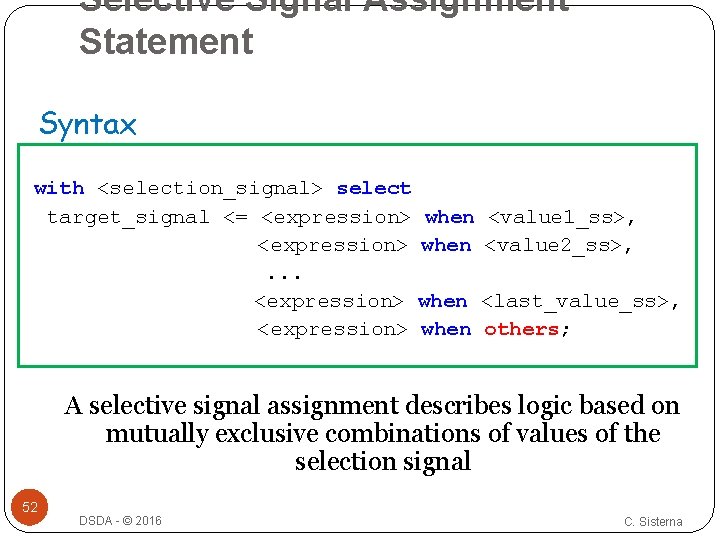

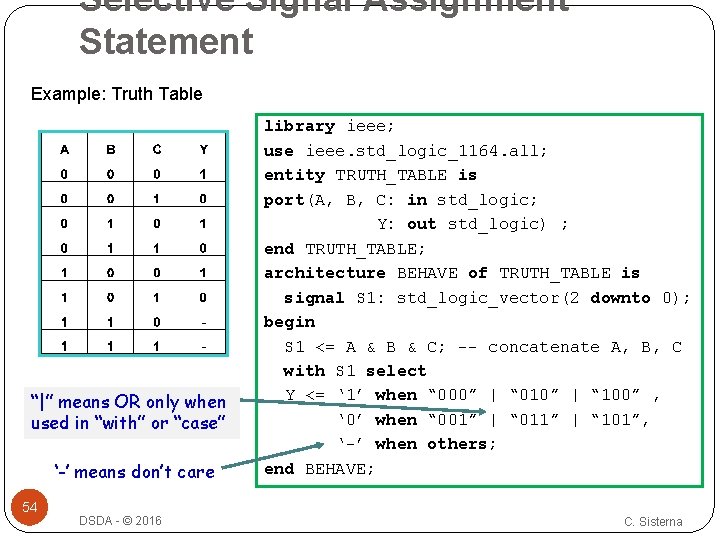

Selective Signal Assignment Statement Syntax with <selection_signal> select target_signal <= <expression> when <value 1_ss>, <expression> when <value 2_ss>, . . . <expression> when <last_value_ss>, <expression> when others; A selective signal assignment describes logic based on mutually exclusive combinations of values of the selection signal 52 DSDA - © 2016 C. Sisterna

Selective Signal Assignment Statement • There is no priority. Each branch has identical priority • All values of <selection_signal> must be listed in the when clauses and will be mutually exclusive • All the possible values of the expression are reachable • A branch can depend on a range of the possible values of <selection_signal> 53 DSDA - © 2016 C. Sisterna

Selective Signal Assignment Statement Example: Truth Table “|” means OR only when used in “with” or “case” ‘-’ means don’t care 54 DSDA - © 2016 library ieee; use ieee. std_logic_1164. all; entity TRUTH_TABLE is port(A, B, C: in std_logic; Y: out std_logic) ; end TRUTH_TABLE; architecture BEHAVE of TRUTH_TABLE is signal S 1: std_logic_vector(2 downto 0); begin S 1 <= A & B & C; -- concatenate A, B, C with S 1 select Y <= ‘ 1’ when “ 000” | “ 010” | “ 100” , ‘ 0’ when “ 001” | “ 011” | “ 101”, ‘-’ when others; end BEHAVE; C. Sisterna

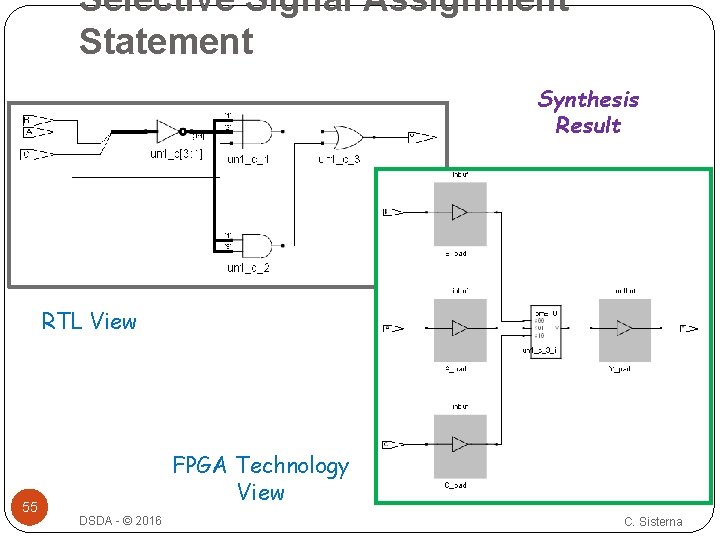

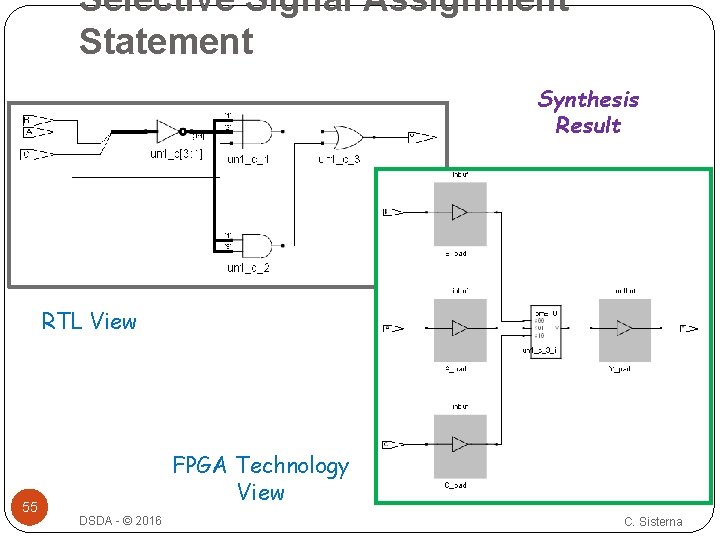

Selective Signal Assignment Statement Synthesis Result RTL View 55 FPGA Technology View DSDA - © 2016 C. Sisterna

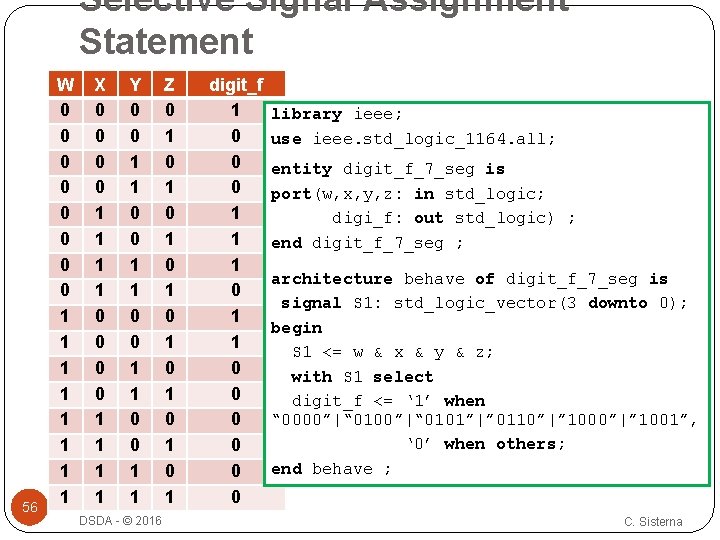

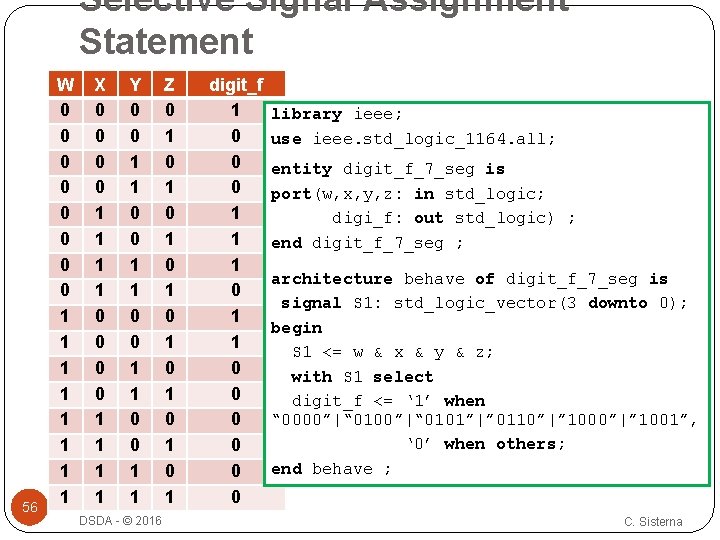

Selective Signal Assignment Statement 56 W 0 0 0 0 1 1 1 1 X 0 0 0 0 1 1 1 1 Y 0 0 1 1 DSDA - © 2016 Z 0 1 0 1 digit_f 1 0 0 0 1 1 1 0 0 0 0 library ieee; use ieee. std_logic_1164. all; entity digit_f_7_seg is port(w, x, y, z: in std_logic; digi_f: out std_logic) ; end digit_f_7_seg ; architecture behave of digit_f_7_seg is signal S 1: std_logic_vector(3 downto 0); begin S 1 <= w & x & y & z; with S 1 select digit_f <= ‘ 1’ when “ 0000”|“ 0101”|” 0110”|” 1001”, ‘ 0’ when others; end behave ; C. Sisterna

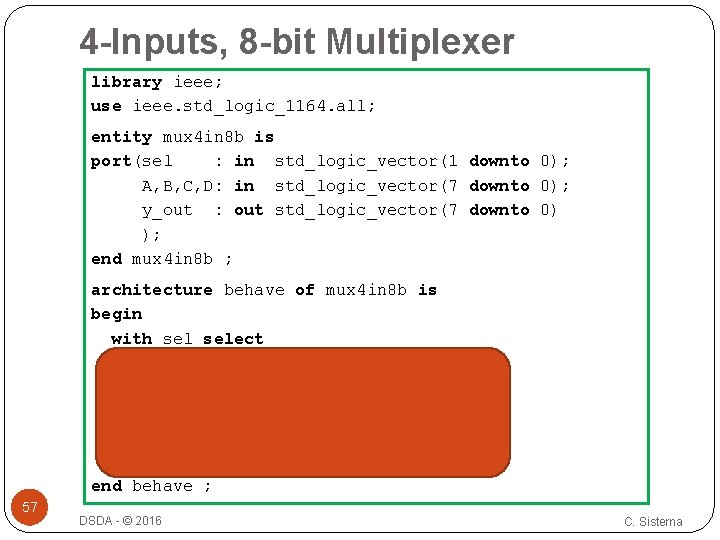

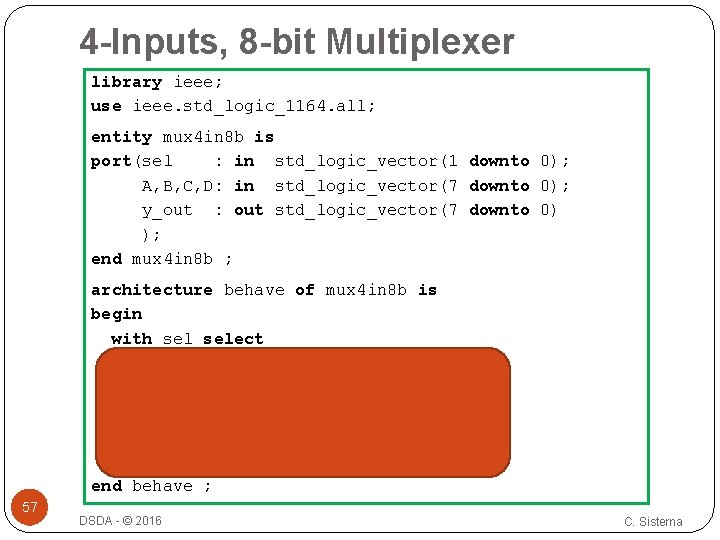

4 -Inputs, 8 -bit Multiplexer library ieee; use ieee. std_logic_1164. all; entity mux 4 in 8 b is port(sel : in std_logic_vector(1 downto 0); A, B, C, D: in std_logic_vector(7 downto 0); y_out : out std_logic_vector(7 downto 0) ); end mux 4 in 8 b ; architecture behave of mux 4 in 8 b is begin with select y_out <= A when “ 00”, (other=>‘-’) when others; end behave ; 57 DSDA - © 2016 C. Sisterna

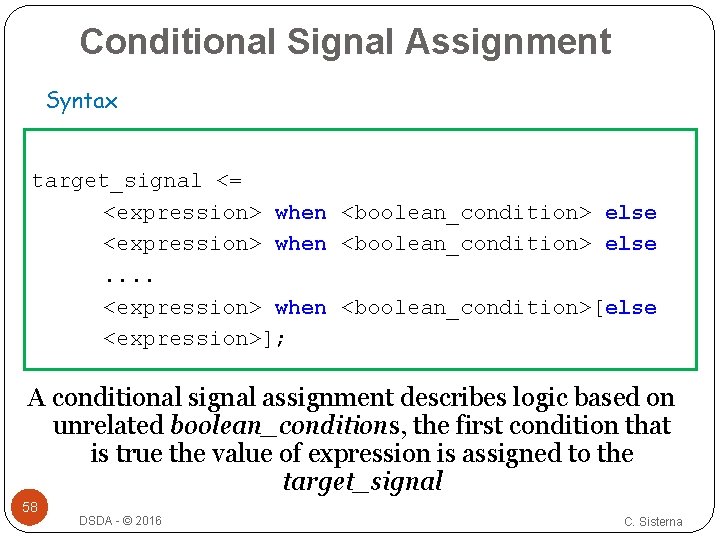

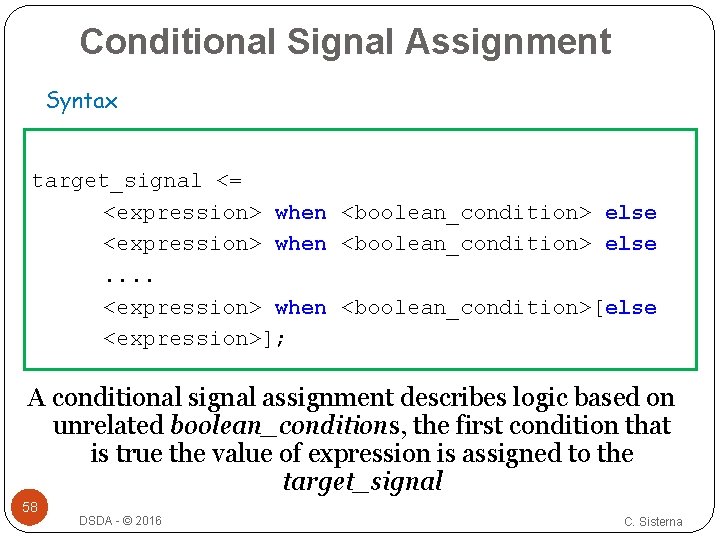

Conditional Signal Assignment Syntax target_signal <= <expression> when <boolean_condition> else . . <expression> when <boolean_condition>[else <expression>]; A conditional signal assignment describes logic based on unrelated boolean_conditions, the first condition that is true the value of expression is assigned to the target_signal 58 DSDA - © 2016 C. Sisterna

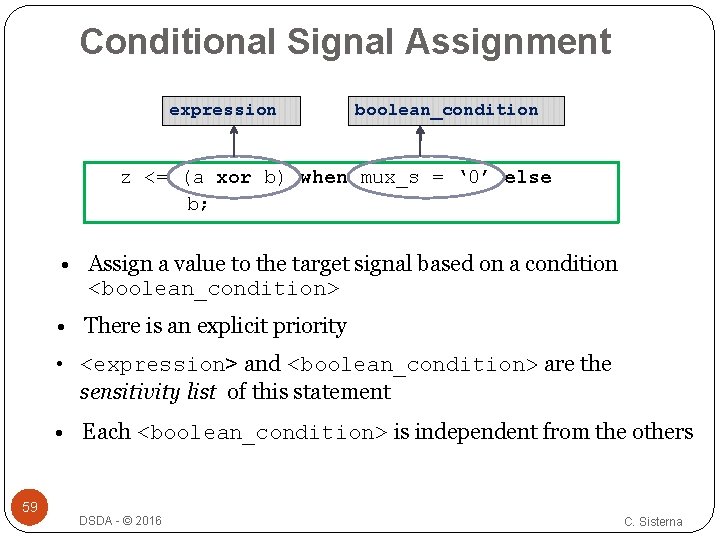

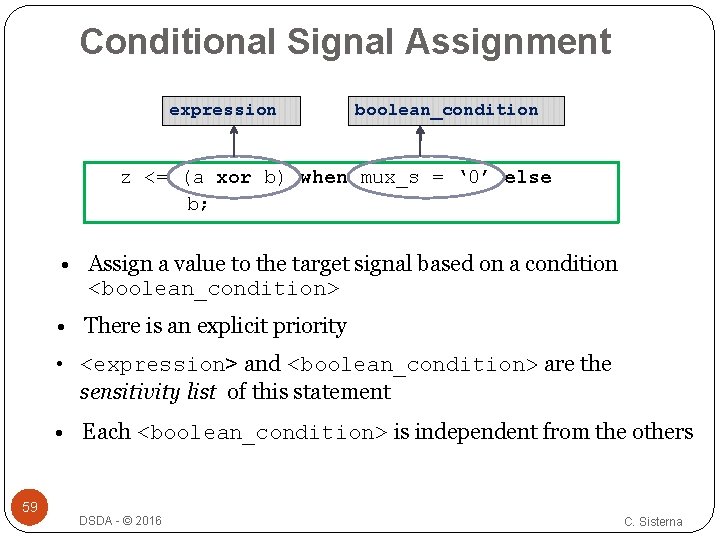

Conditional Signal Assignment expression boolean_condition z <= (a xor b) when mux_s = ‘ 0’ else b; • Assign a value to the target signal based on a condition <boolean_condition> • There is an explicit priority • <expression> and <boolean_condition> are the sensitivity list of this statement • Each <boolean_condition> is independent from the others 59 DSDA - © 2016 C. Sisterna

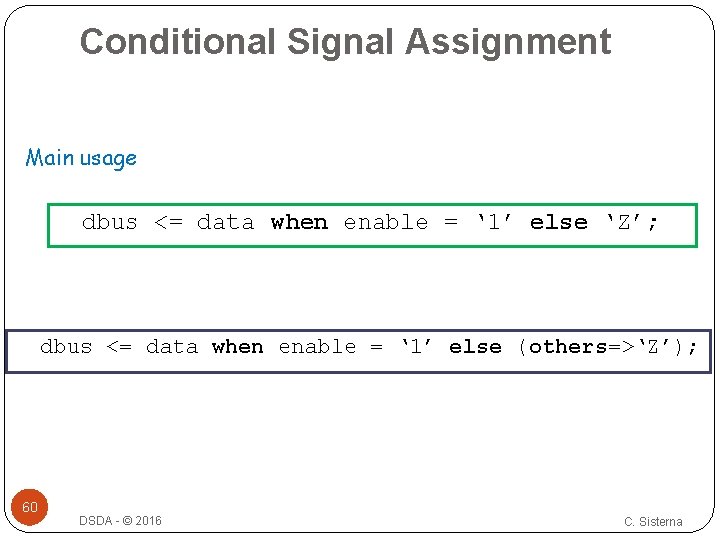

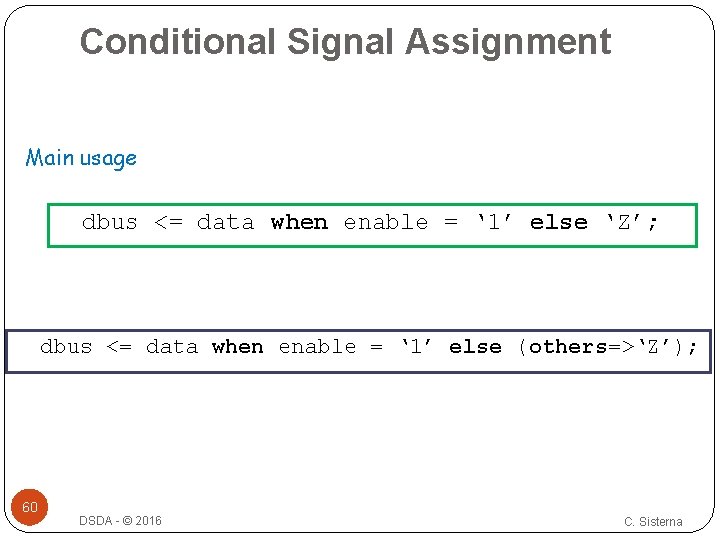

Conditional Signal Assignment Main usage dbus <= data when enable = ‘ 1’ else ‘Z’; dbus <= data when enable = ‘ 1’ else (others=>‘Z’); 60 DSDA - © 2016 C. Sisterna

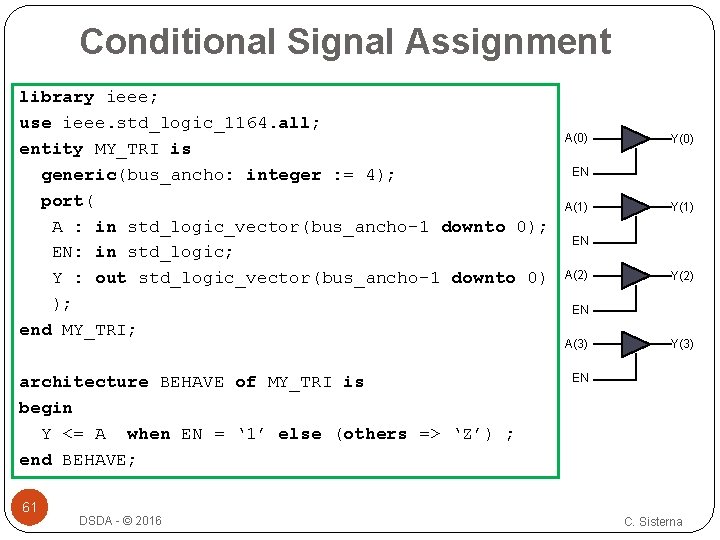

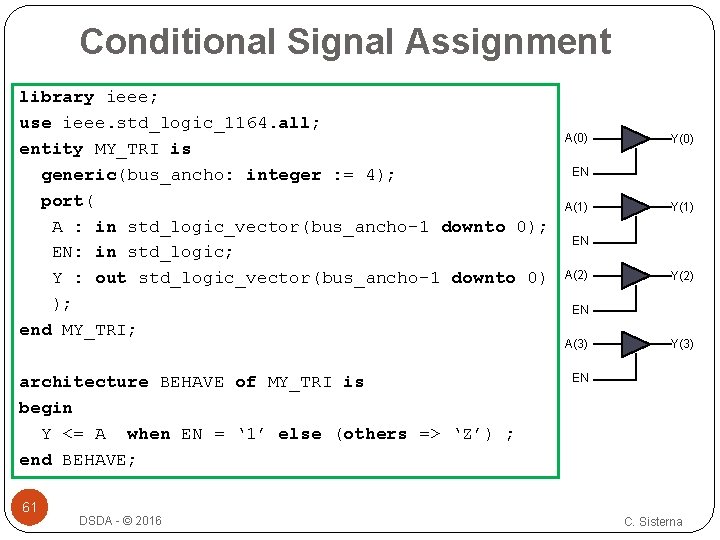

Conditional Signal Assignment library ieee; use ieee. std_logic_1164. all; entity MY_TRI is generic(bus_ancho: integer : = 4); port( A : in std_logic_vector(bus_ancho-1 downto 0); EN: in std_logic; Y : out std_logic_vector(bus_ancho-1 downto 0) ); end MY_TRI; architecture BEHAVE of MY_TRI is begin Y <= A when EN = ‘ 1’ else (others => ‘Z’) ; end BEHAVE; 61 DSDA - © 2016 A(0) Y(0) EN A(1) Y(1) EN A(2) Y(2) EN A(3) Y(3) EN C. Sisterna

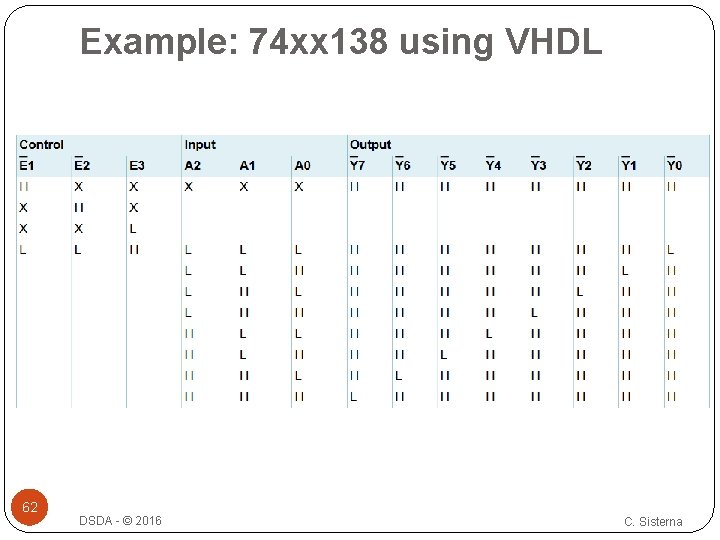

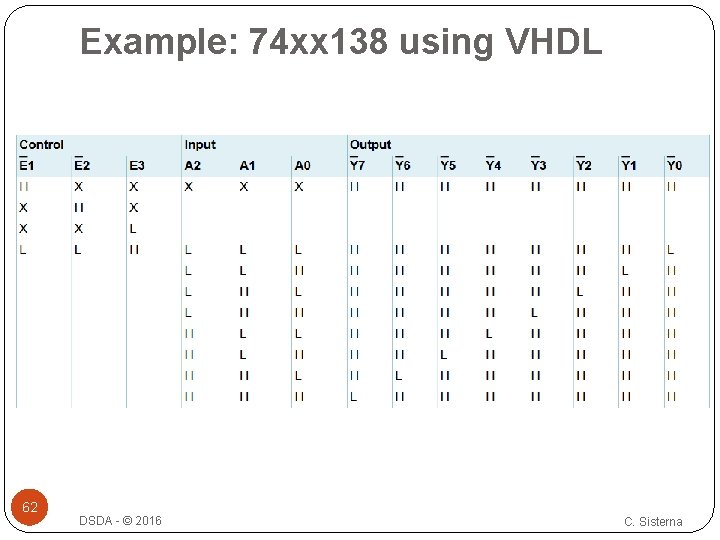

Example: 74 xx 138 using VHDL 62 DSDA - © 2016 C. Sisterna

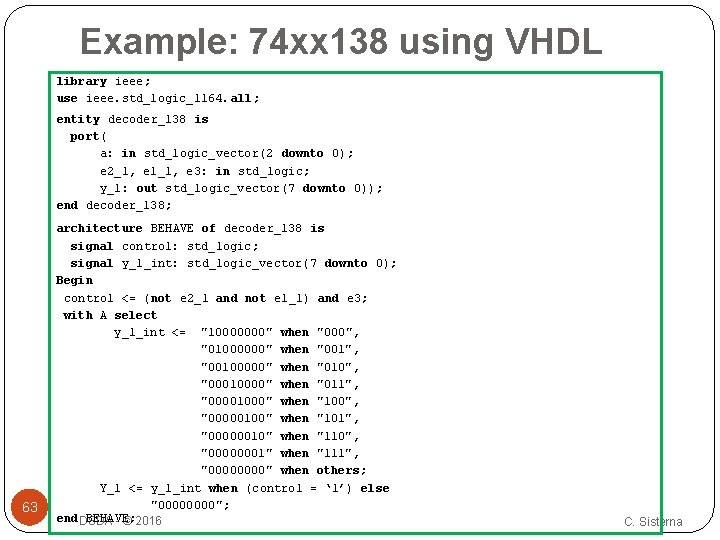

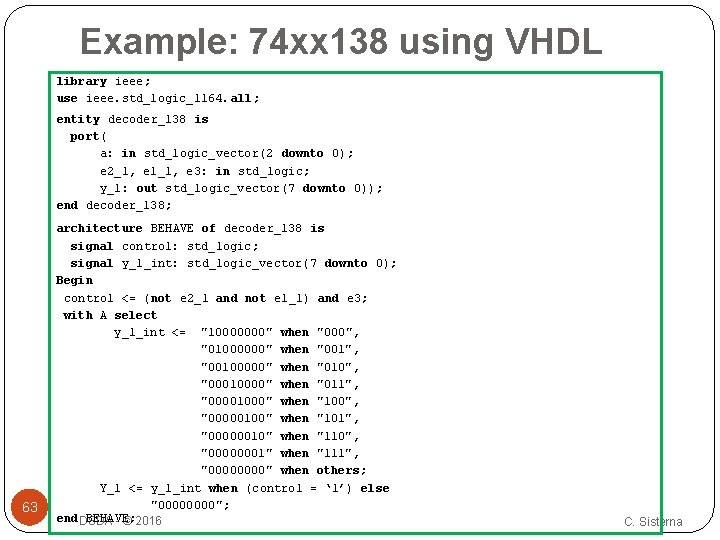

Example: 74 xx 138 using VHDL library ieee; use ieee. std_logic_1164. all; entity decoder_138 is port( a: in std_logic_vector(2 downto 0); e 2_l, e 1_l, e 3: in std_logic; y_l: out std_logic_vector(7 downto 0)); end decoder_138; 63 architecture BEHAVE of decoder_138 is signal control: std_logic; signal y_l_int: std_logic_vector(7 downto 0); Begin control <= (not e 2_l and not e 1_l) and e 3; with A select y_l_int <= "10000000" when "000", "01000000" when "001", "00100000" when "010", "00010000" when "011", "00001000" when "100", "00000100" when "101", "00000010" when "110", "00000001" when "111", "0000" when others; Y_l <= y_l_int when (control = ‘ 1’) else "0000"; end BEHAVE; DSDA - © 2016 C. Sisterna

![Process Statement Syntax process sensitivitylist declarations begin sequentialstatements end process 64 DSDA Process Statement �Syntax process sensitivity_list [declarations; ] begin sequential_statements; end process; 64 DSDA -](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-64.jpg)

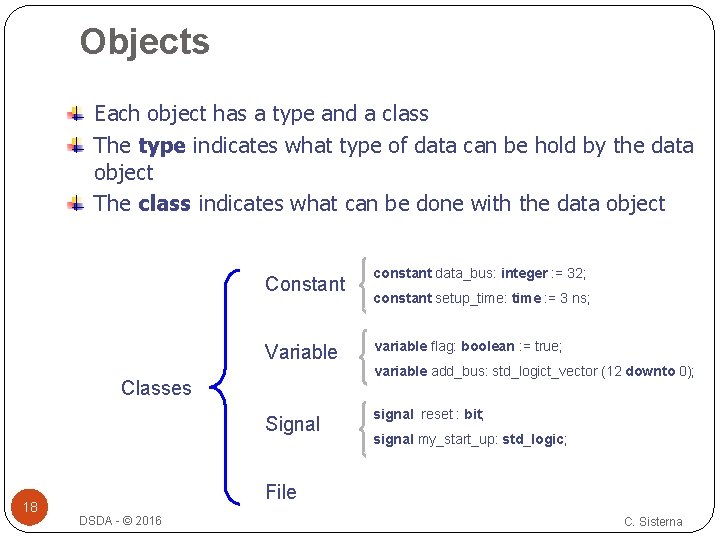

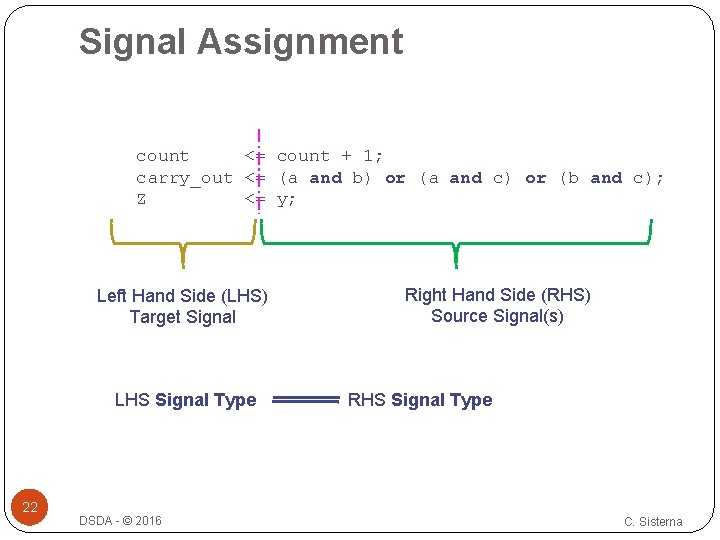

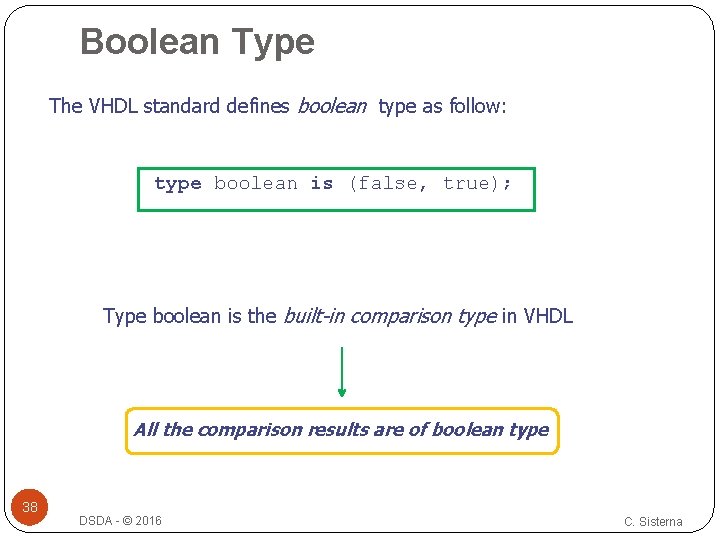

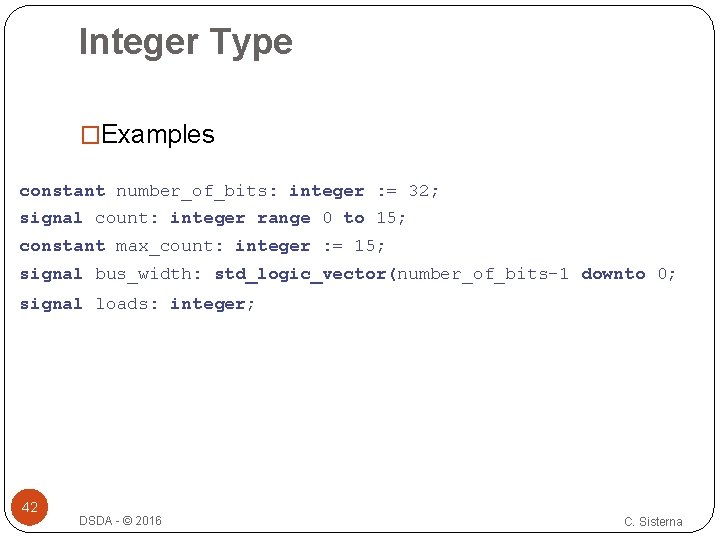

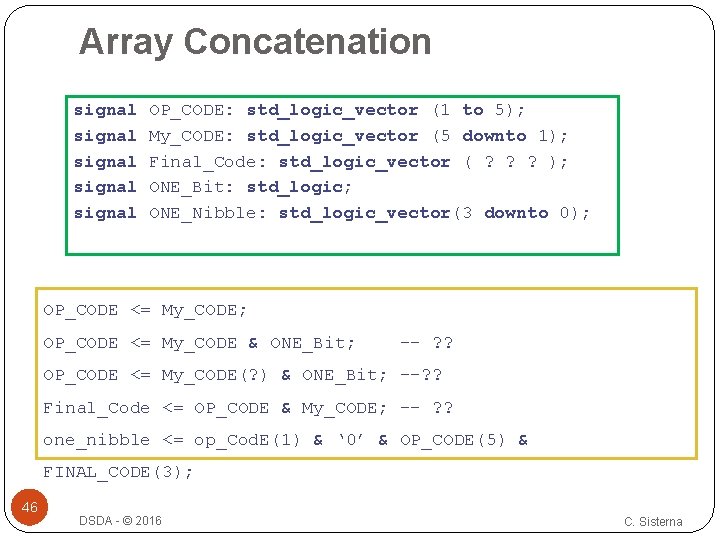

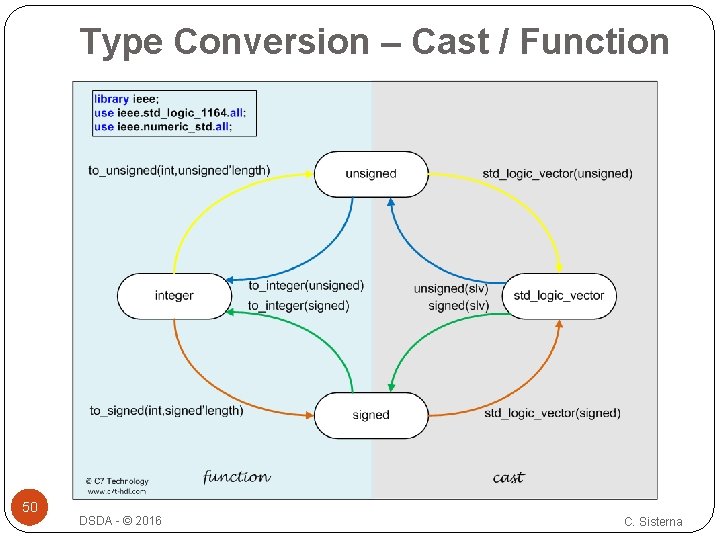

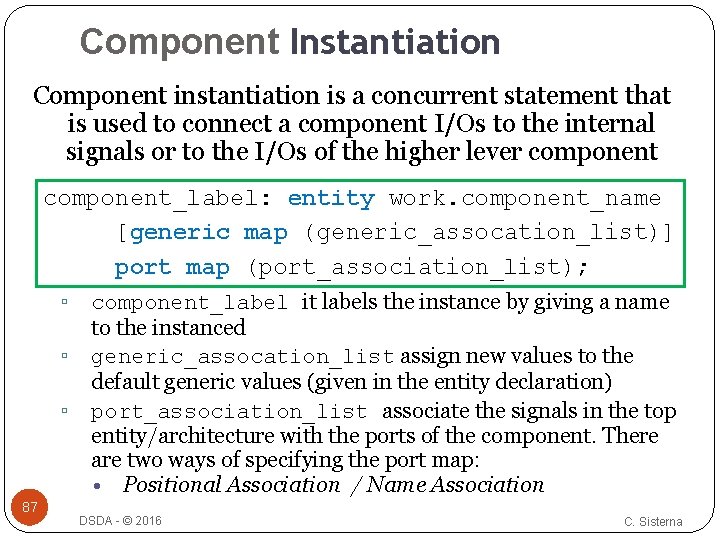

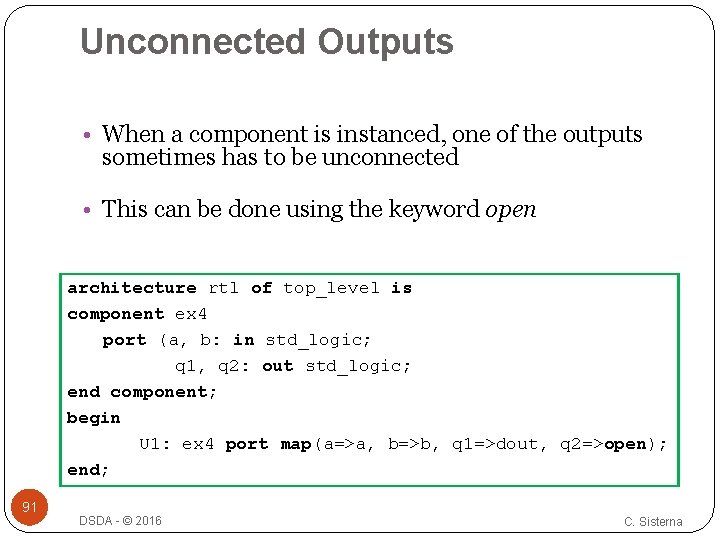

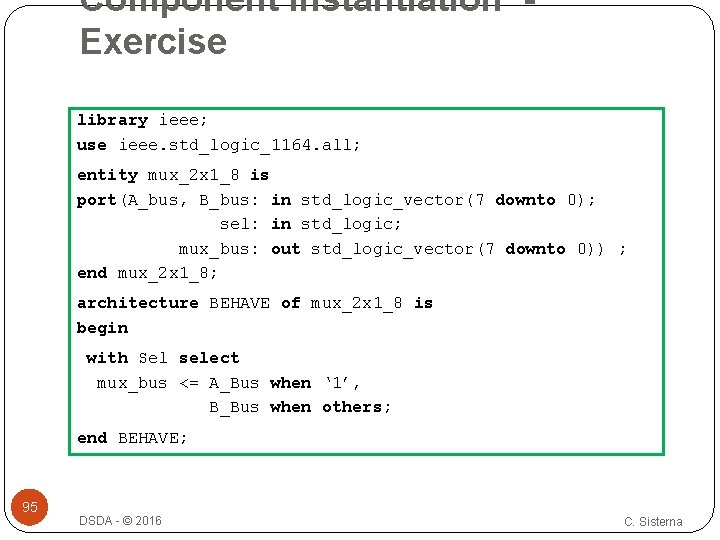

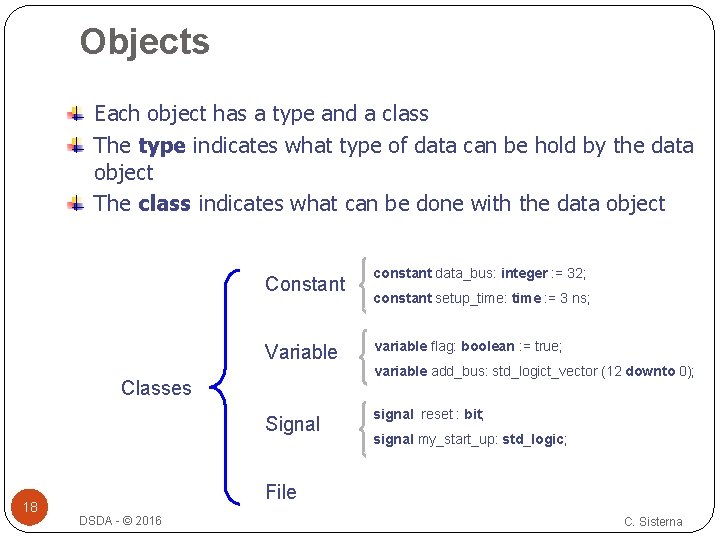

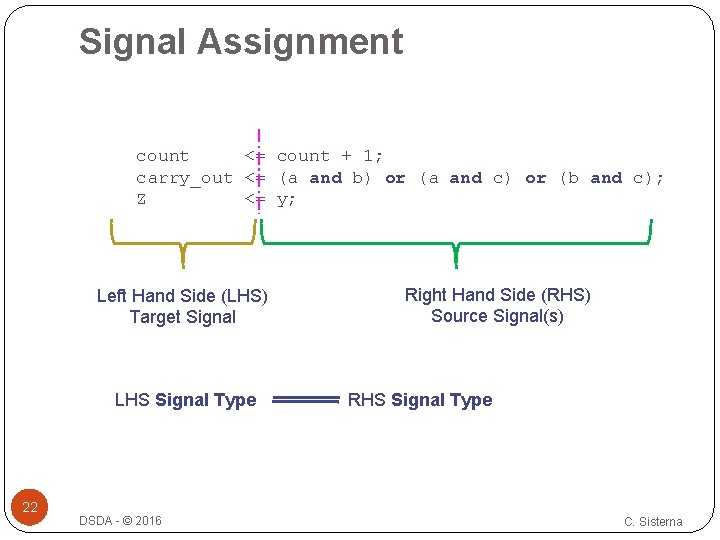

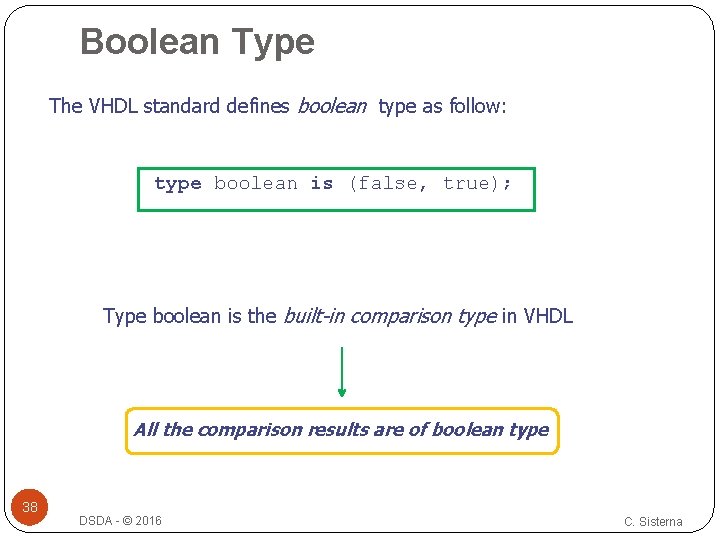

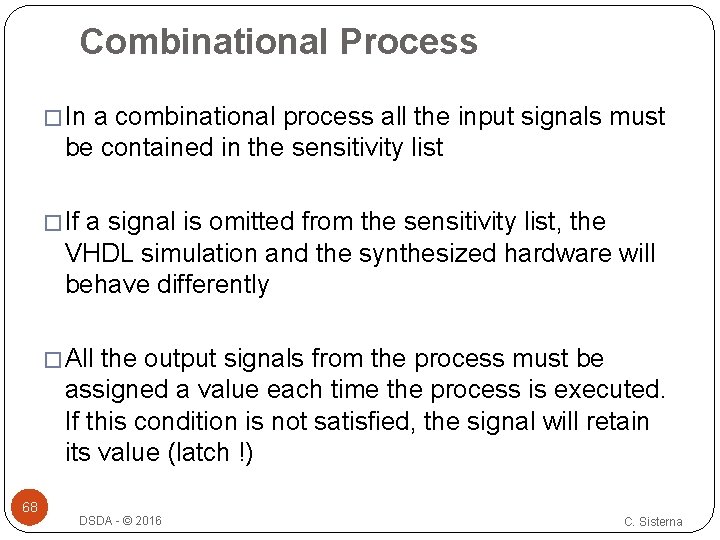

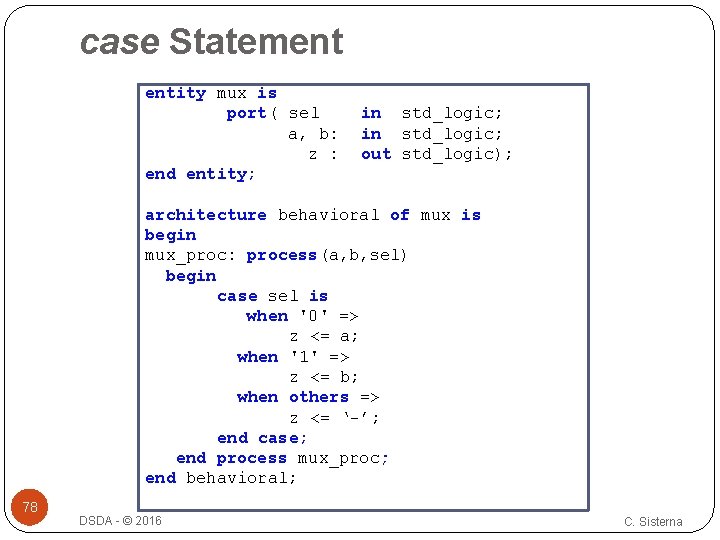

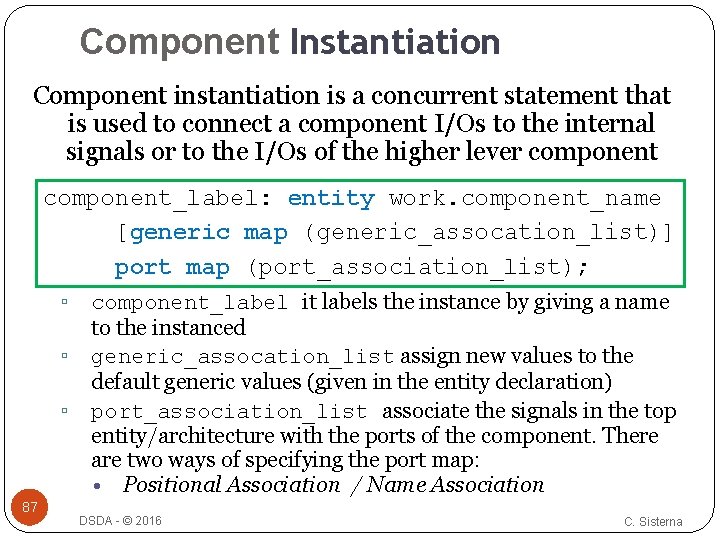

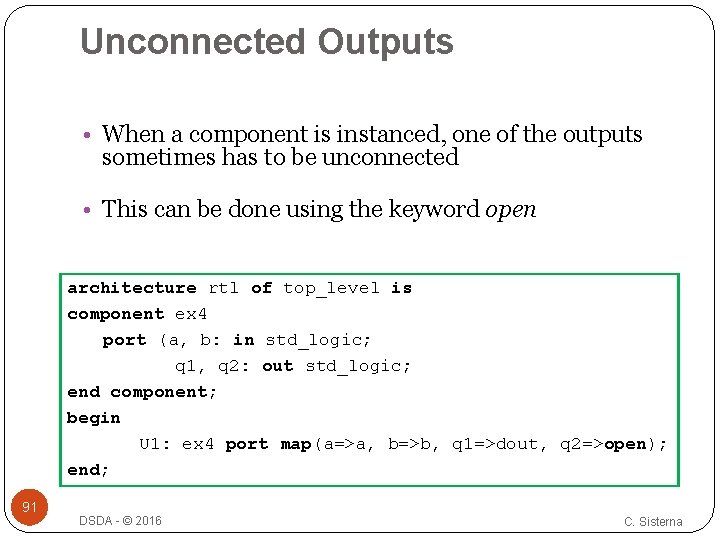

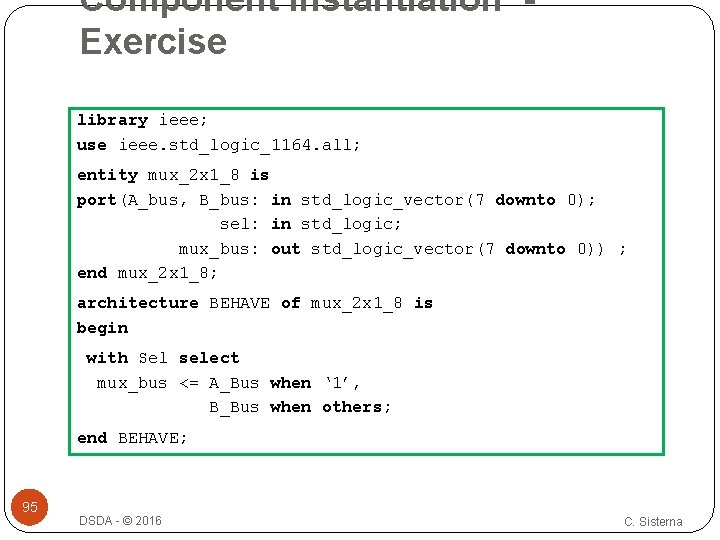

Process Statement �Syntax process sensitivity_list [declarations; ] begin sequential_statements; end process; 64 DSDA - © 2016 C. Sisterna

![Process Statement processlabel process sensitivitylist is processdataobjectdeclarations begin variableassignmentstatement signalassignmentstatement waitstatement ifstatement casestatement Process Statement [process_label: ] process [(sensitivity_list)] [is] [process_data_object_declarations] begin variable_assignment_statement signal_assignment_statement wait_statement if_statement case_statement](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-65.jpg)

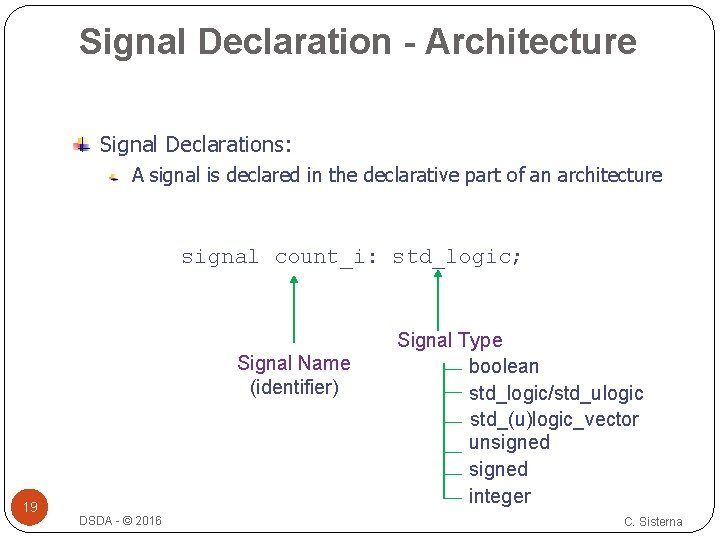

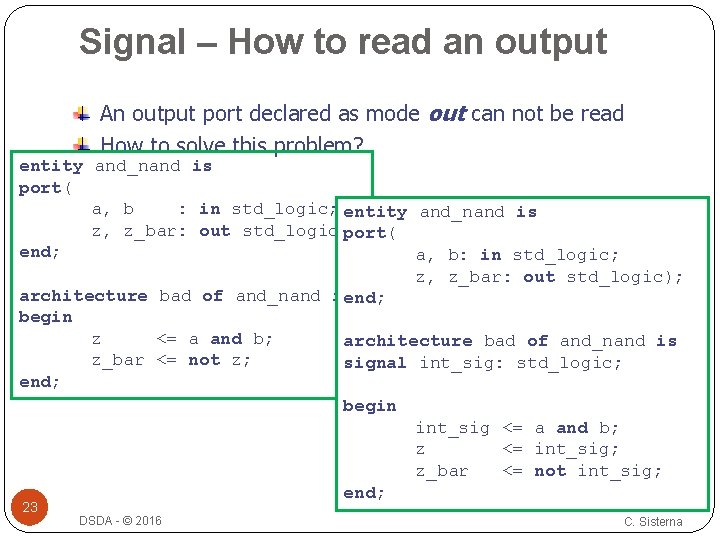

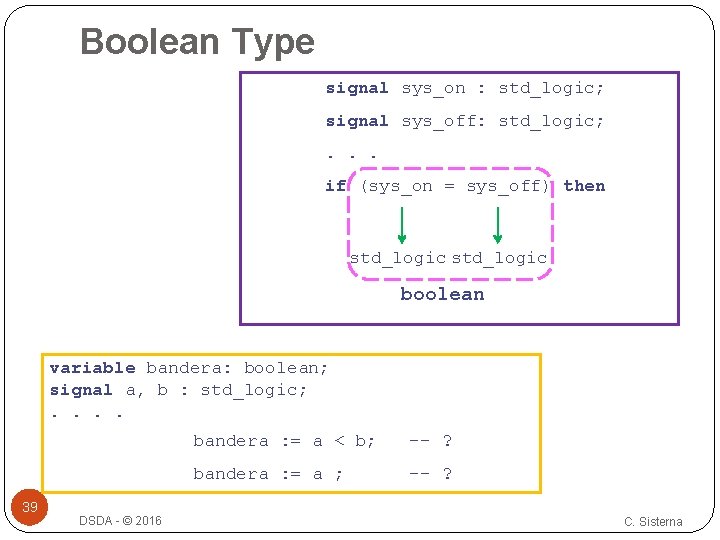

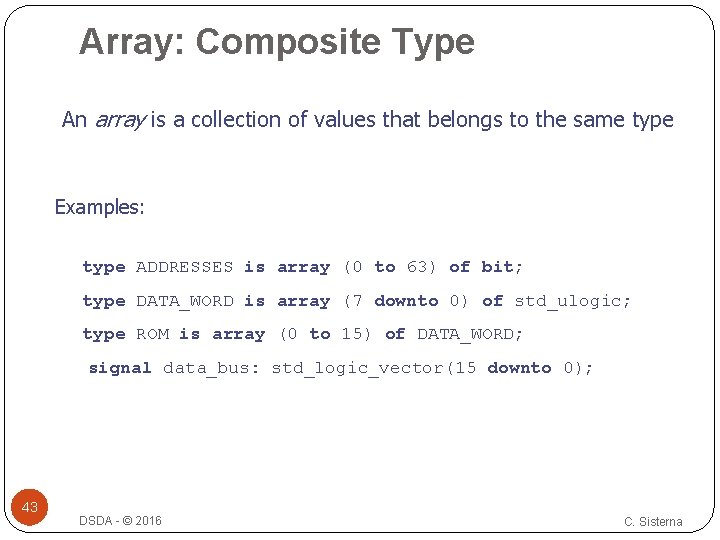

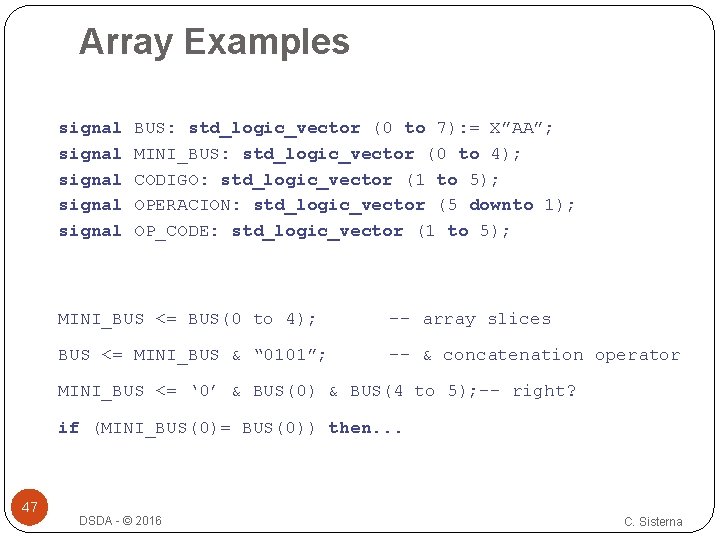

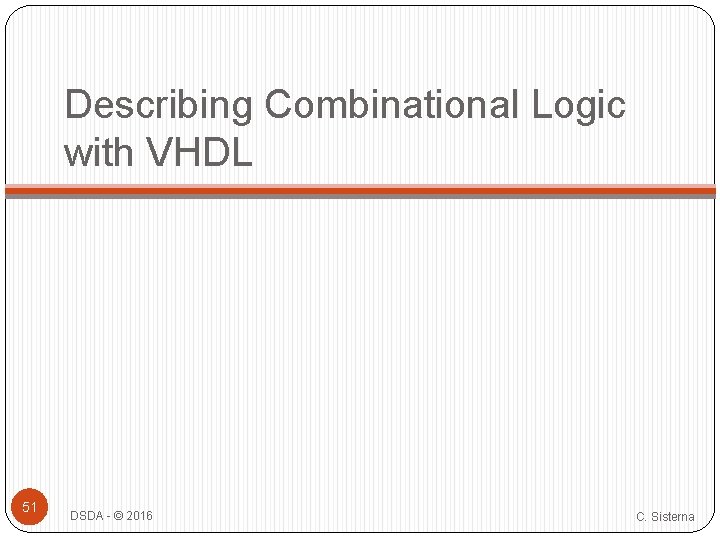

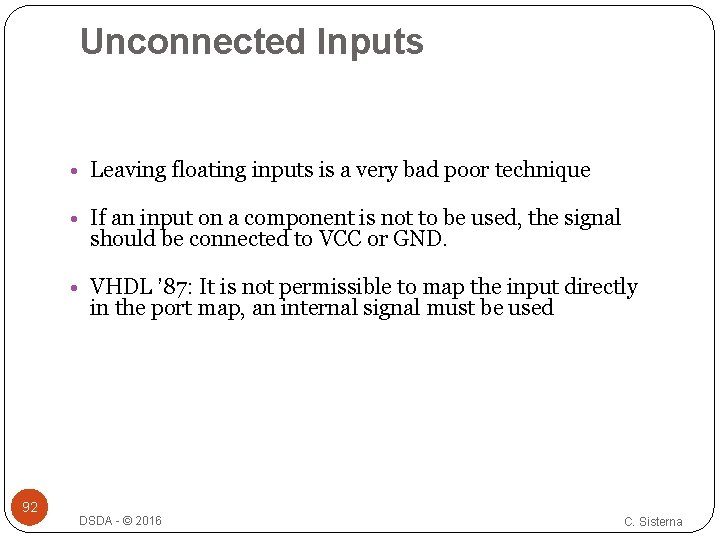

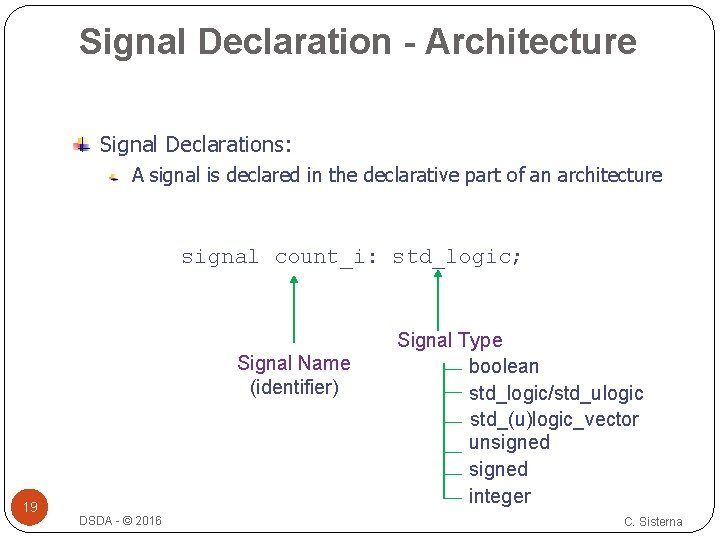

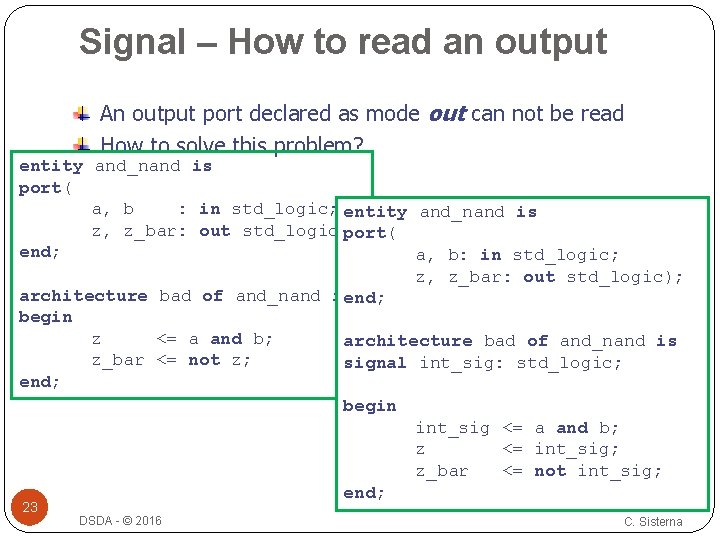

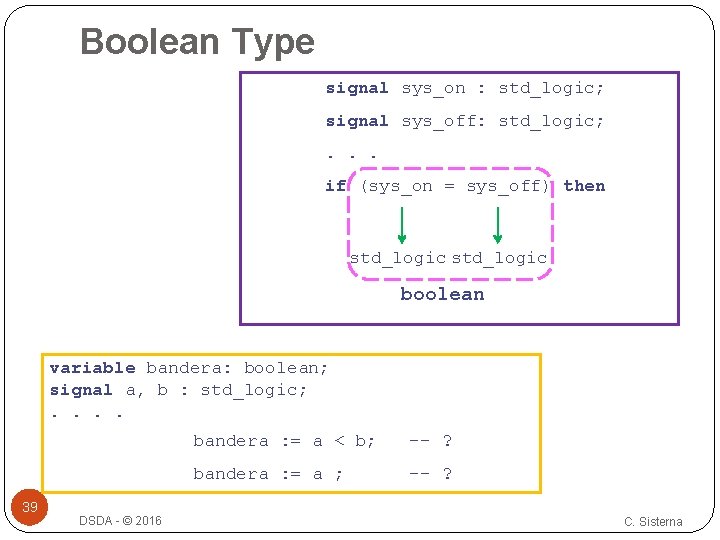

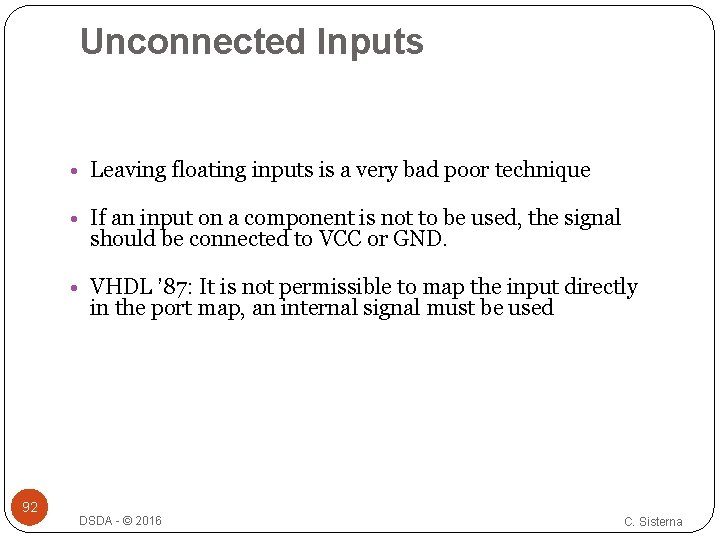

Process Statement [process_label: ] process [(sensitivity_list)] [is] [process_data_object_declarations] begin variable_assignment_statement signal_assignment_statement wait_statement if_statement case_statement loop_statement null_statement exit_statement next_statement assertion_statement report_statement procedure_call_statement return_statement [wait on sensitivity_list] end process [process_label]; 65 DSDA - © 2016 Sequential statements C. Sisterna

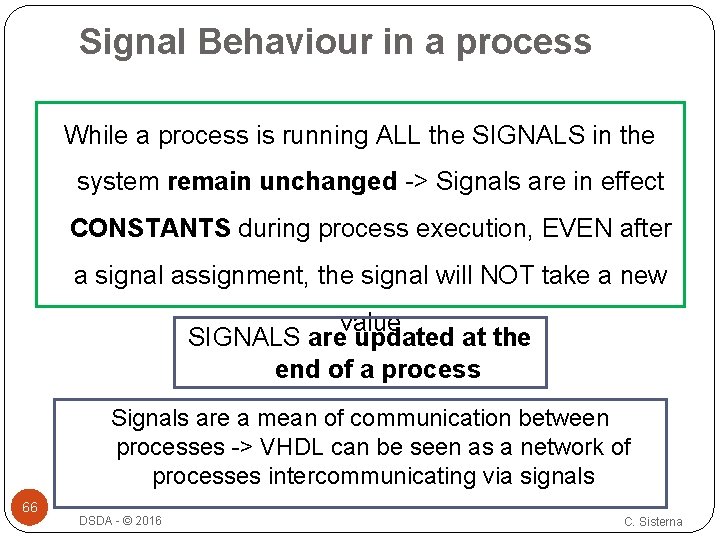

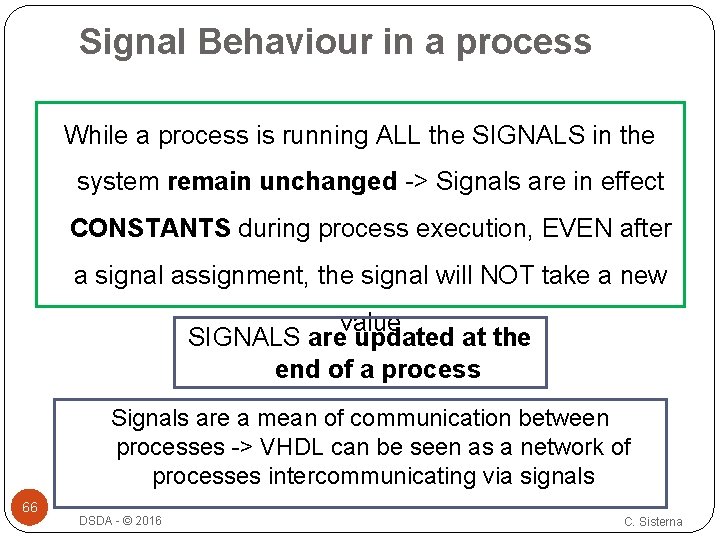

Signal Behaviour in a process While a process is running ALL the SIGNALS in the system remain unchanged -> Signals are in effect CONSTANTS during process execution, EVEN after a signal assignment, the signal will NOT take a new value SIGNALS are updated at the end of a process Signals are a mean of communication between processes -> VHDL can be seen as a network of processes intercommunicating via signals 66 DSDA - © 2016 C. Sisterna

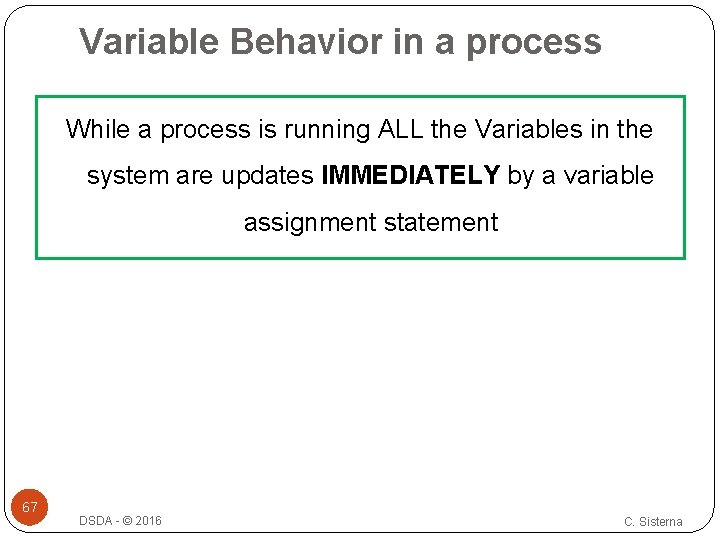

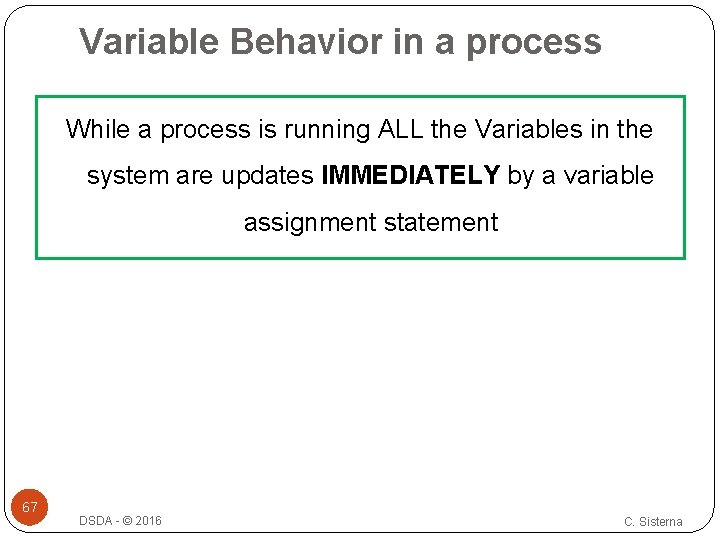

Variable Behavior in a process While a process is running ALL the Variables in the system are updates IMMEDIATELY by a variable assignment statement 67 DSDA - © 2016 C. Sisterna

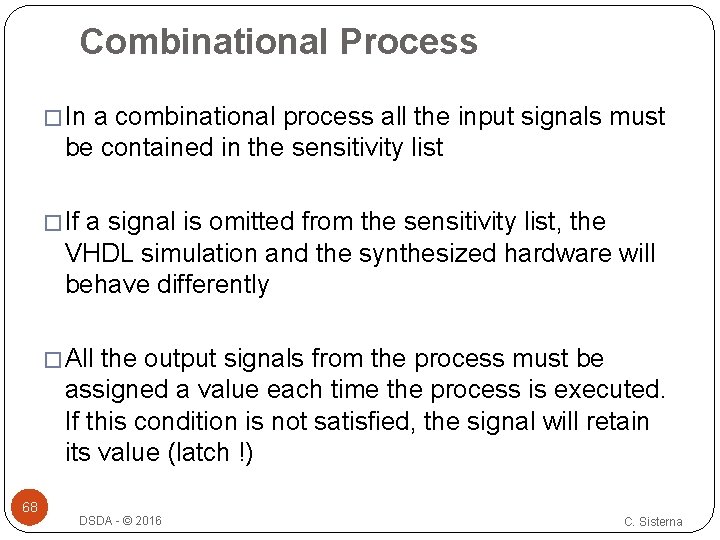

Combinational Process � In a combinational process all the input signals must be contained in the sensitivity list � If a signal is omitted from the sensitivity list, the VHDL simulation and the synthesized hardware will behave differently � All the output signals from the process must be assigned a value each time the process is executed. If this condition is not satisfied, the signal will retain its value (latch !) 68 DSDA - © 2016 C. Sisterna

Combinational Process a_process: process (a_in, b_in) begin c_out <= not(a_in and b_in); d_out <= not b_in; end process a_process; . . architecture rtl of com_ex is begin ex_c: process (a, b) begin z <= a and b; end process ex_c; end rtl; 69 DSDA - © 2016 C. Sisterna

![if Statement Syntax if booleanexpression then sequentialstatements elsif booleanexpression then sequentialstatements if Statement �Syntax if <boolean_expression> then <sequential_statement(s)> [elsif <boolean_expression> then <sequential_statement(s)>] . . .](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-70.jpg)

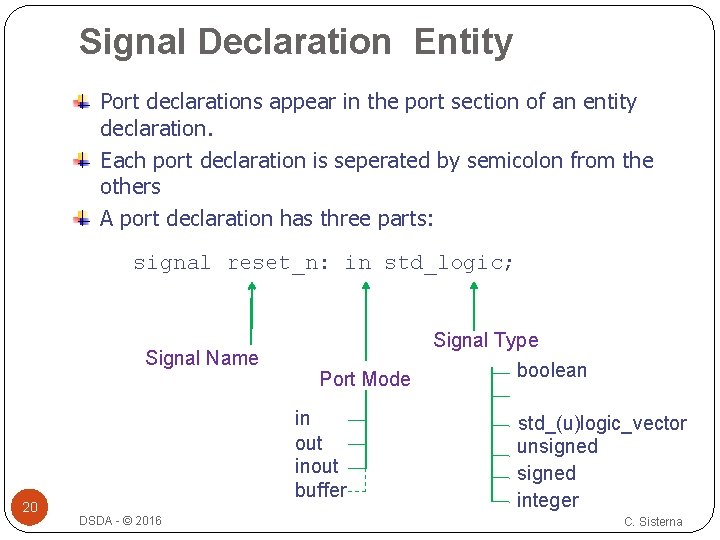

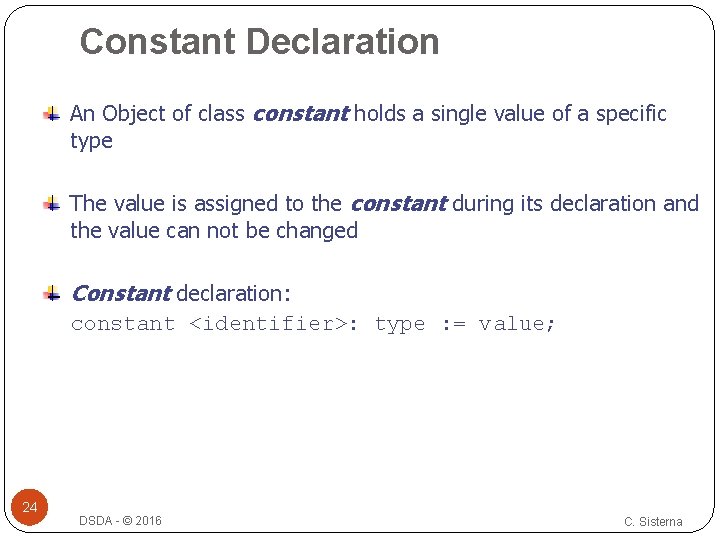

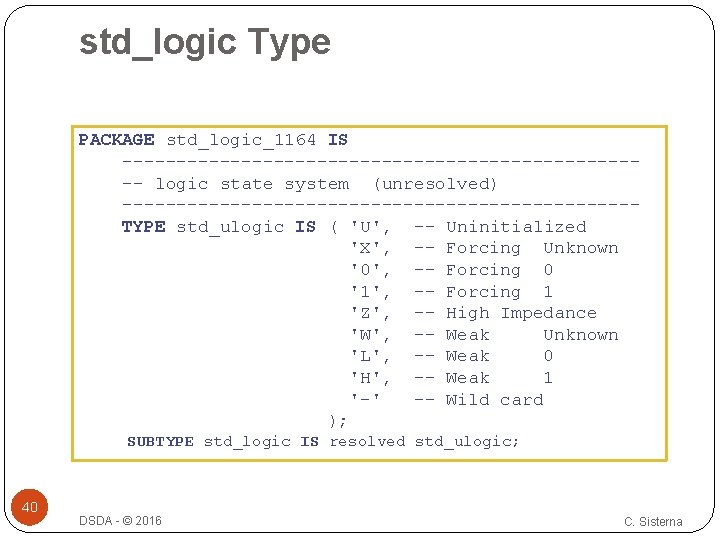

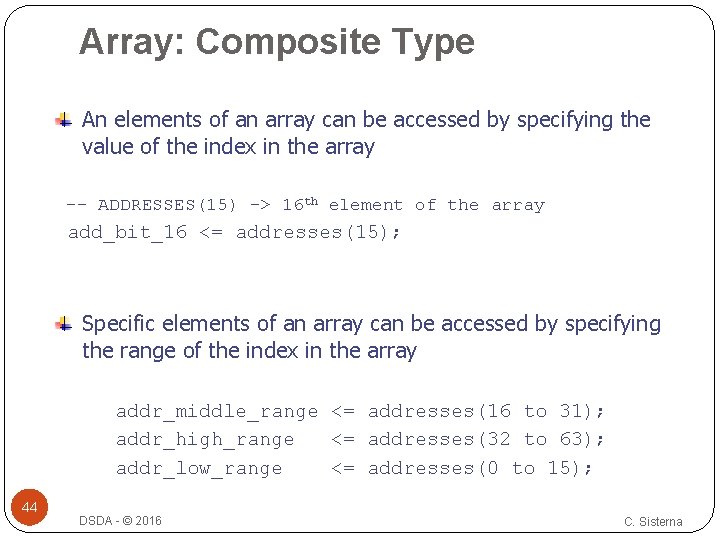

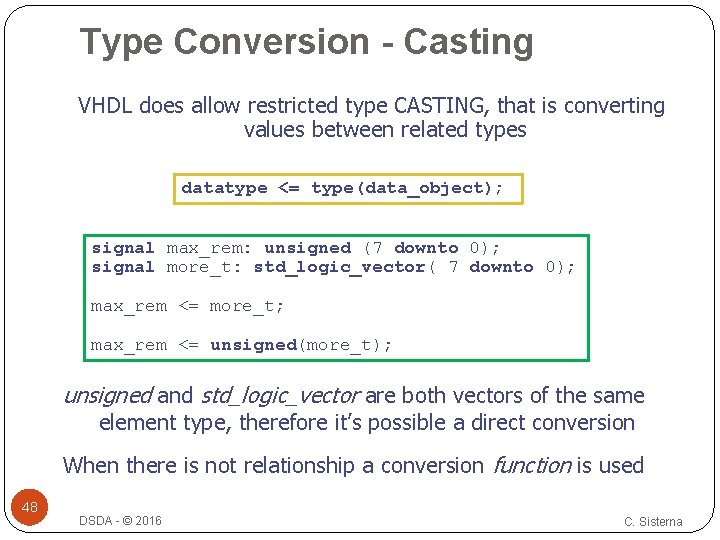

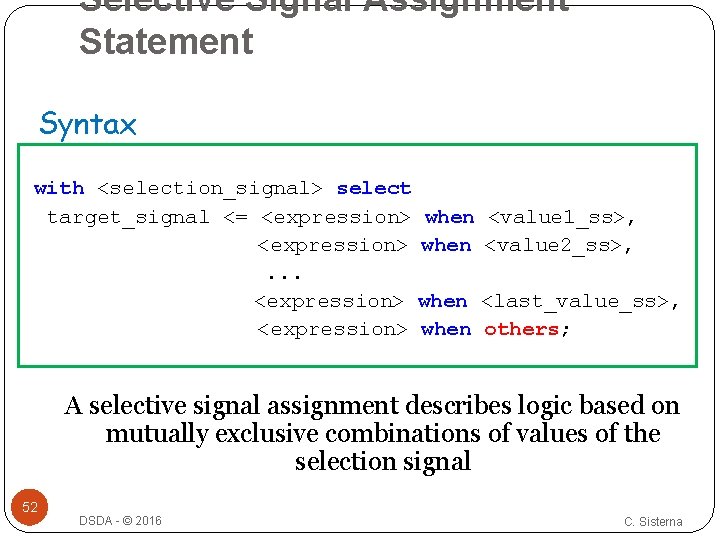

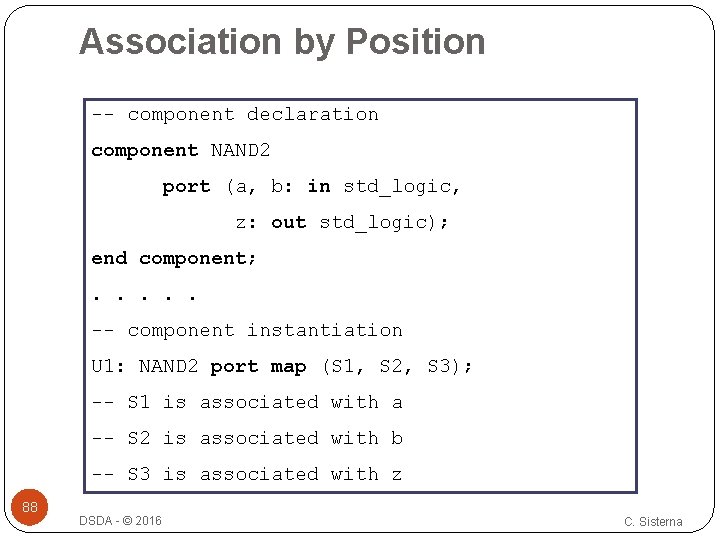

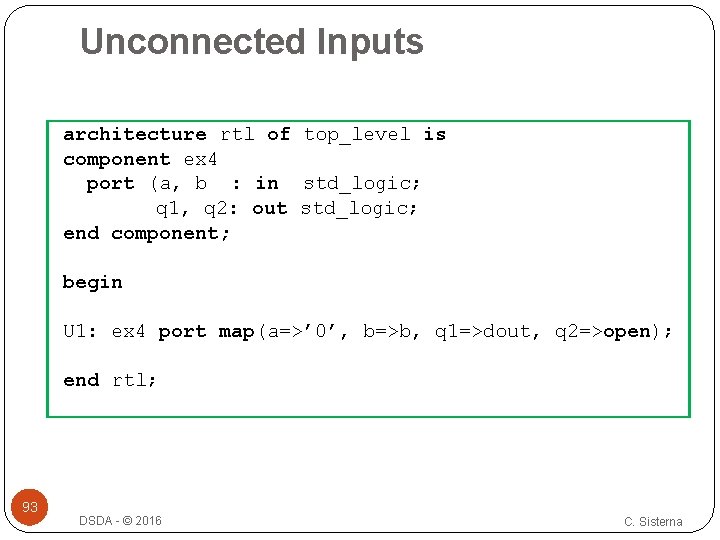

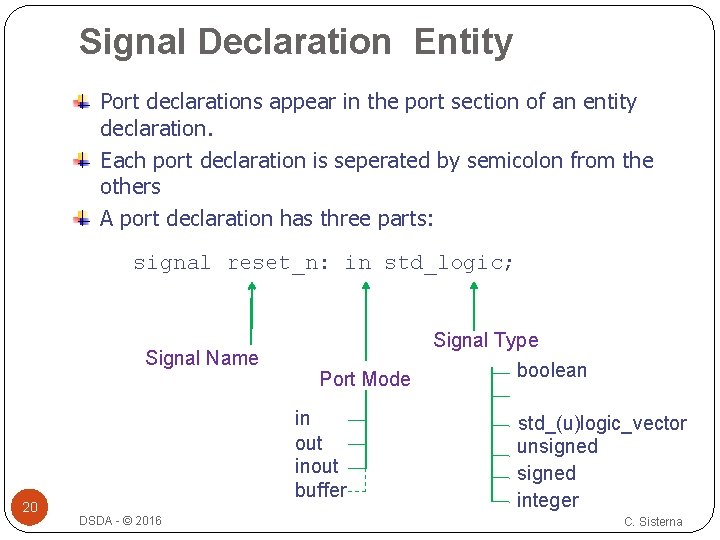

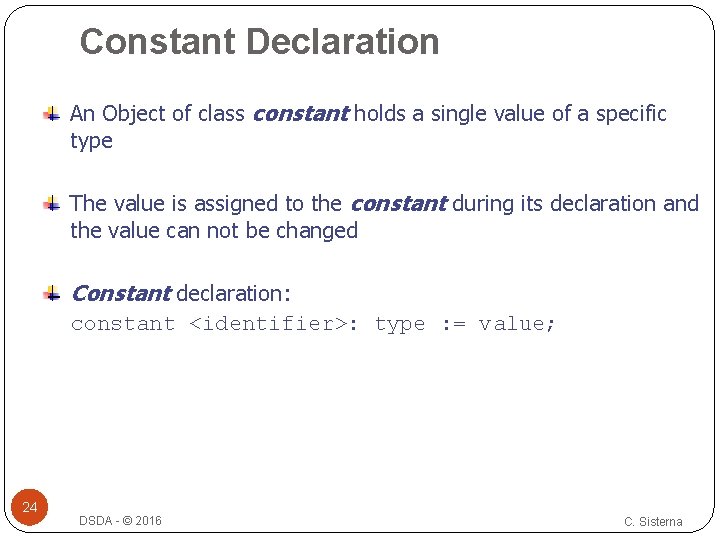

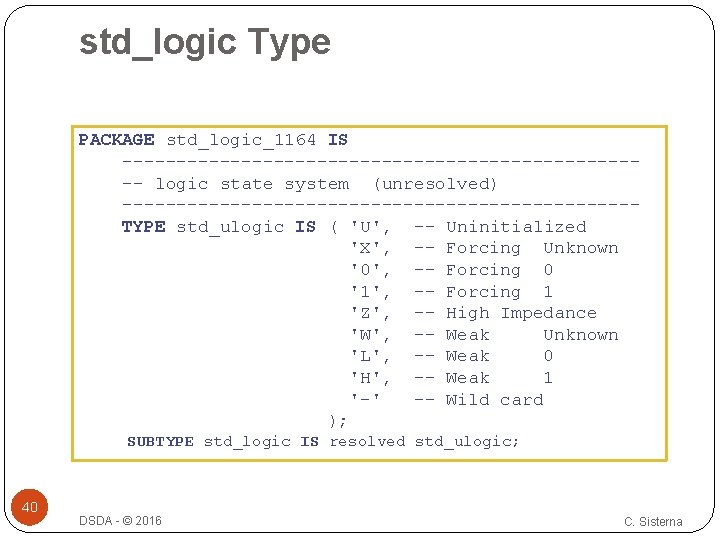

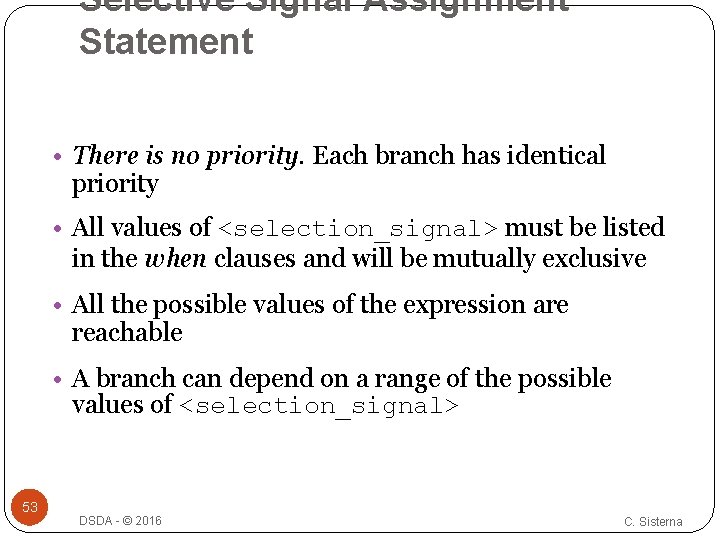

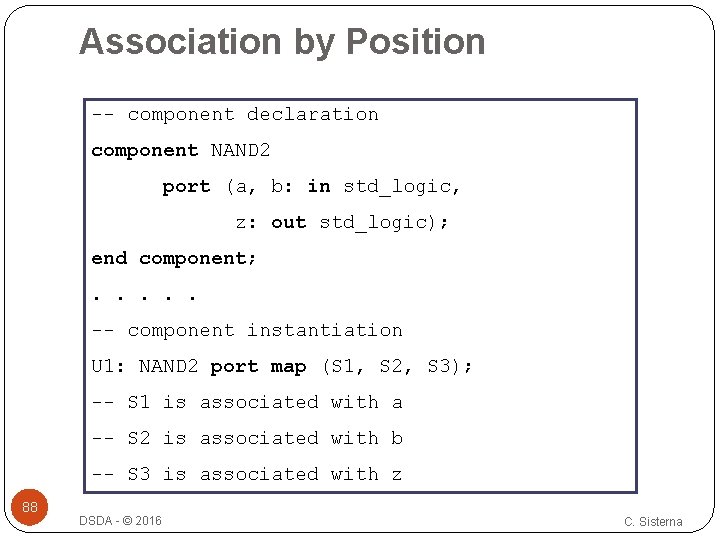

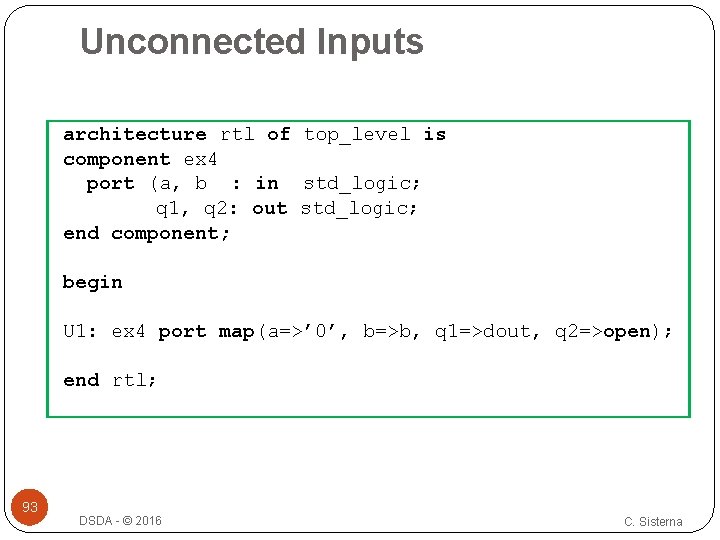

if Statement �Syntax if <boolean_expression> then <sequential_statement(s)> [elsif <boolean_expression> then <sequential_statement(s)>] . . . [else <sequential_statement(s)>] end if; 70 DSDA - © 2016 C. Sisterna

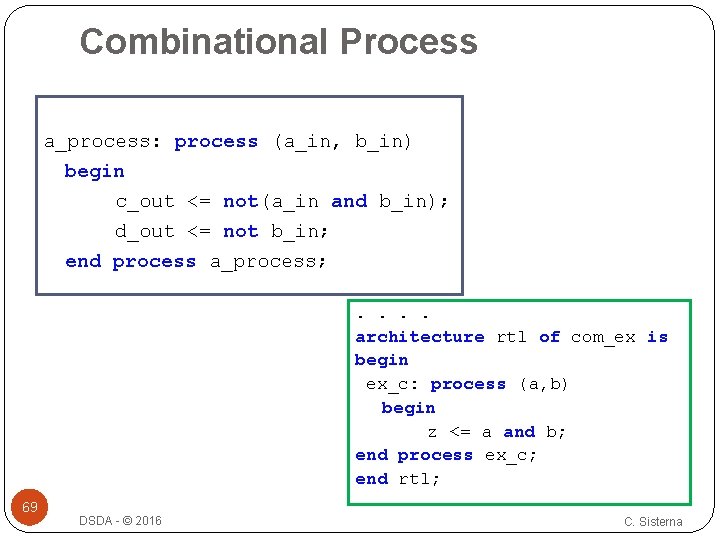

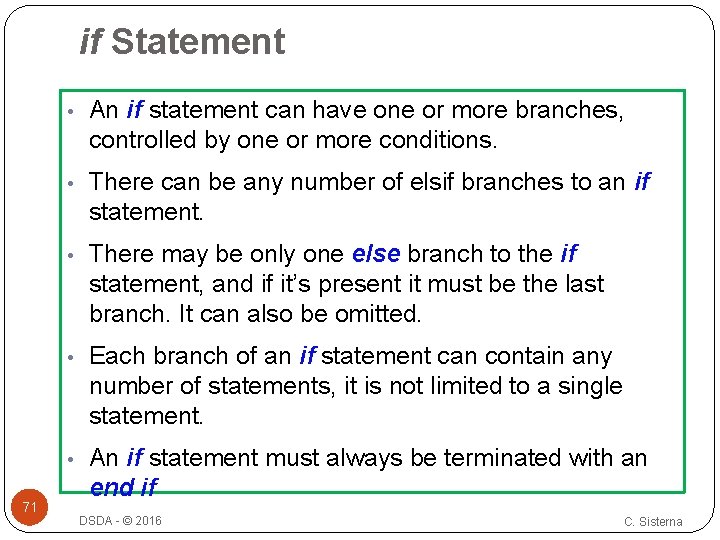

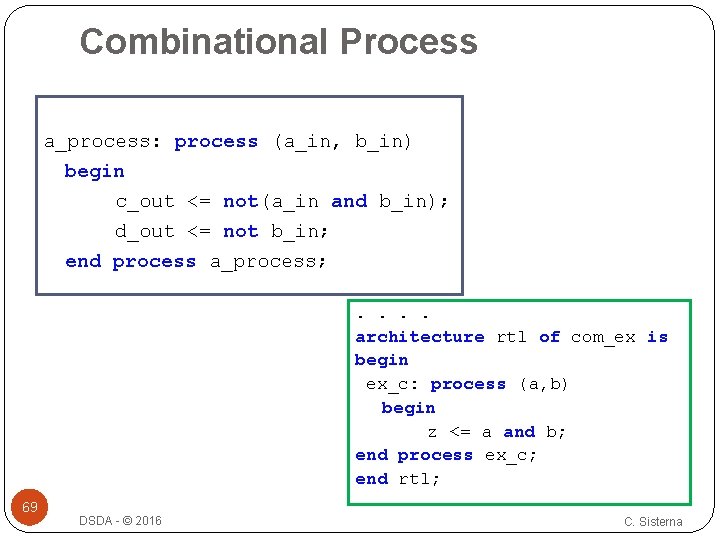

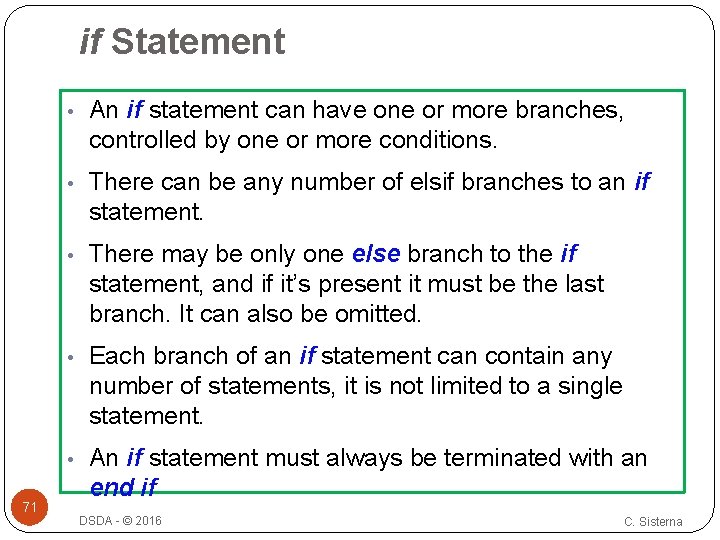

if Statement 71 • An if statement can have one or more branches, controlled by one or more conditions. • There can be any number of elsif branches to an if statement. • There may be only one else branch to the if statement, and if it’s present it must be the last branch. It can also be omitted. • Each branch of an if statement can contain any number of statements, it is not limited to a single statement. • An if statement must always be terminated with an end if DSDA - © 2016 C. Sisterna

if Statement entity if_example_1 is port( a, b: in std_logic_vector(7 downto 0); z : out std_logic); end entity; architecture rtl of if_example_1 is begin if_ex: process (a, b) begin if (a = b) then z <= ‘ 1’; else z <= ‘ 0’; end if; end process if_ex; end rtl; 72 DSDA - © 2016 C. Sisterna

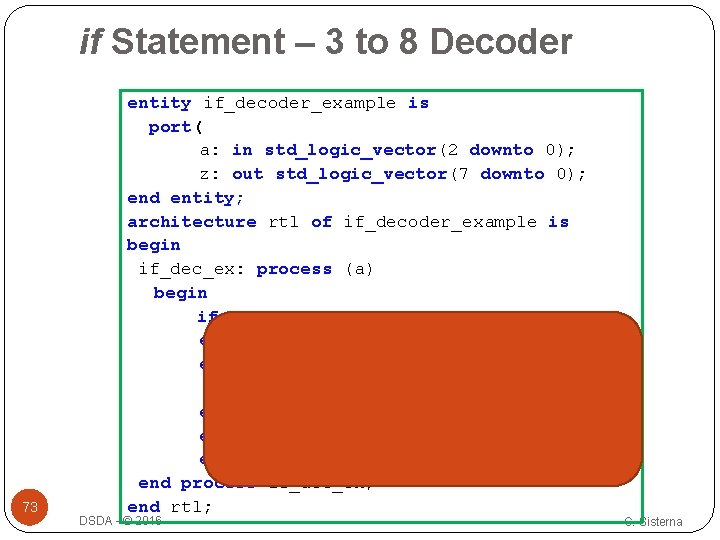

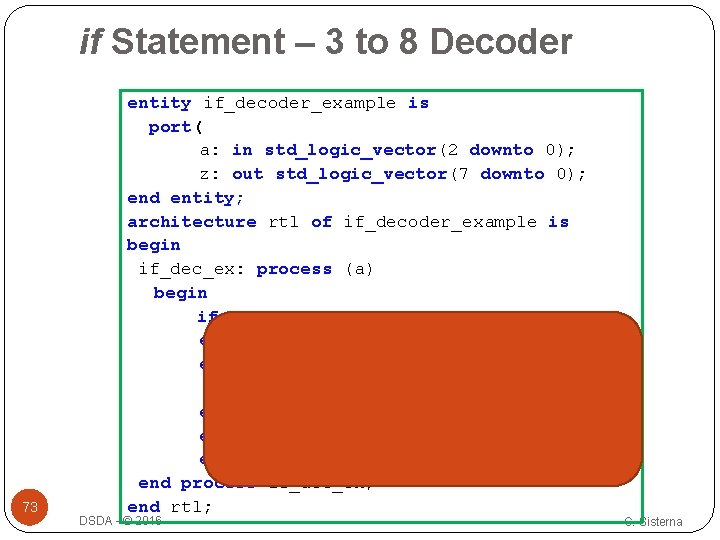

if Statement – 3 to 8 Decoder 73 entity if_decoder_example is port( a: in std_logic_vector(2 downto 0); z: out std_logic_vector(7 downto 0); end entity; architecture rtl of if_decoder_example is begin if_dec_ex: process (a) begin if (a = “ 000”) then z <= “ 00000001”; elsif (a = “ 001”) then z <= “ 00000010”; elsif (a = “ 010”) then z <= “ 00000100”; . . . elsif (a = “ 110”) then z <= “ 01000000”; else z <= “ 10000000”; end if; end process if_dec_ex; end rtl; DSDA - © 2016 C. Sisterna

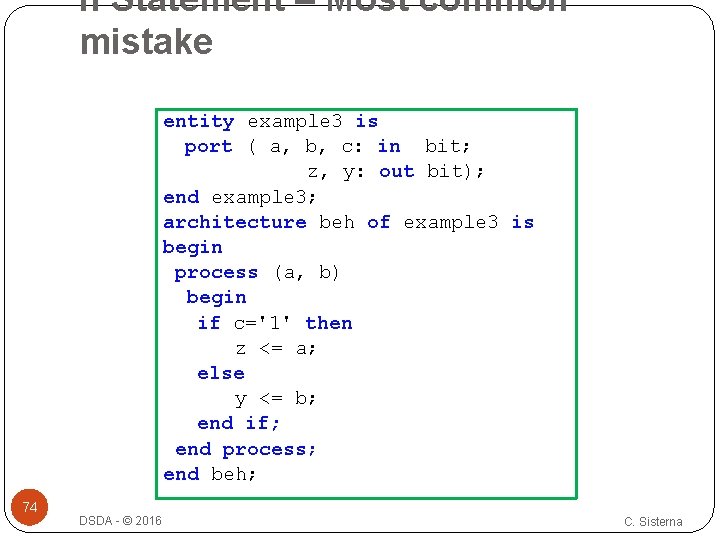

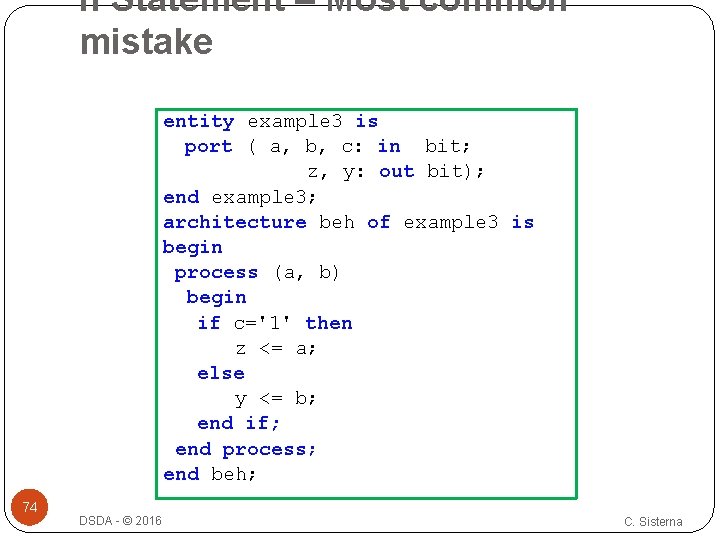

If Statement – Most common mistake entity example 3 is port ( a, b, c: in bit; z, y: out bit); end example 3; architecture beh of example 3 is begin process (a, b) begin if c='1' then z <= a; else y <= b; end if; end process; end beh; 74 DSDA - © 2016 C. Sisterna

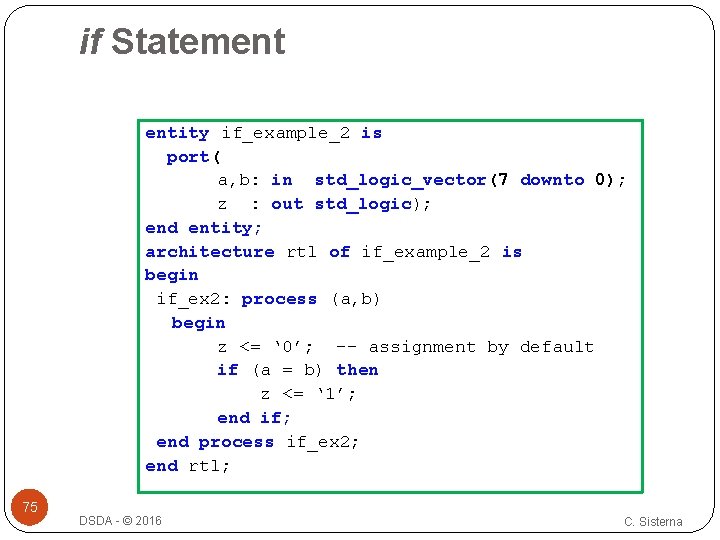

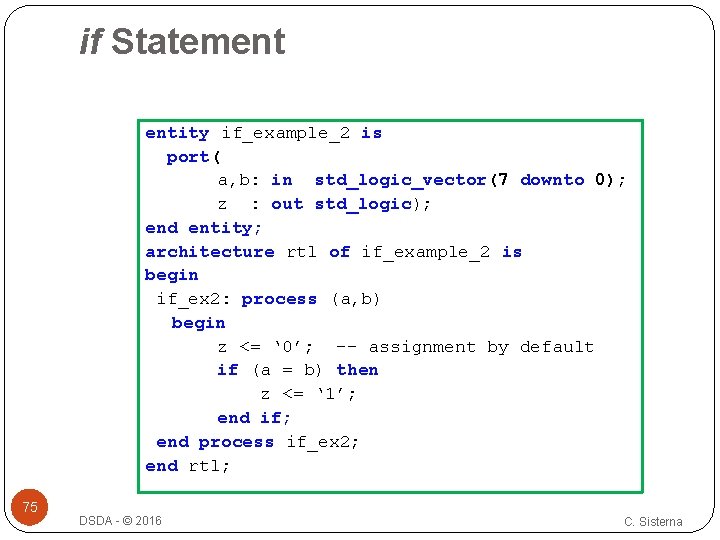

if Statement entity if_example_2 is port( a, b: in std_logic_vector(7 downto 0); z : out std_logic); end entity; architecture rtl of if_example_2 is begin if_ex 2: process (a, b) begin z <= ‘ 0’; -- assignment by default if (a = b) then z <= ‘ 1’; end if; end process if_ex 2; end rtl; 75 DSDA - © 2016 C. Sisterna

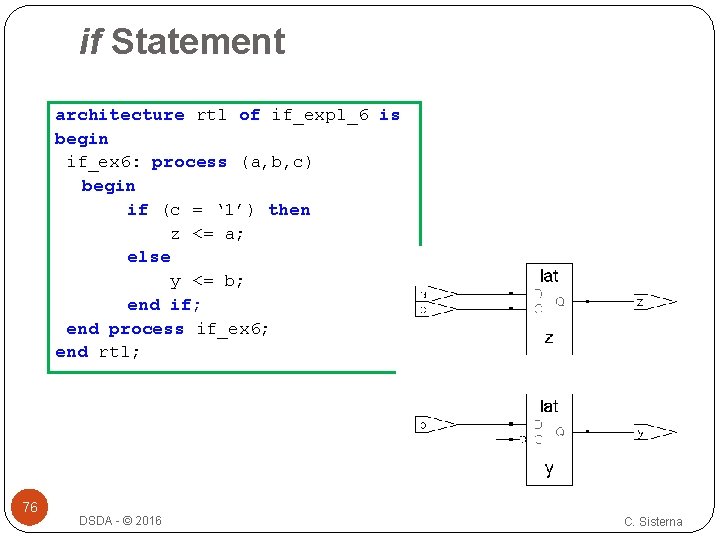

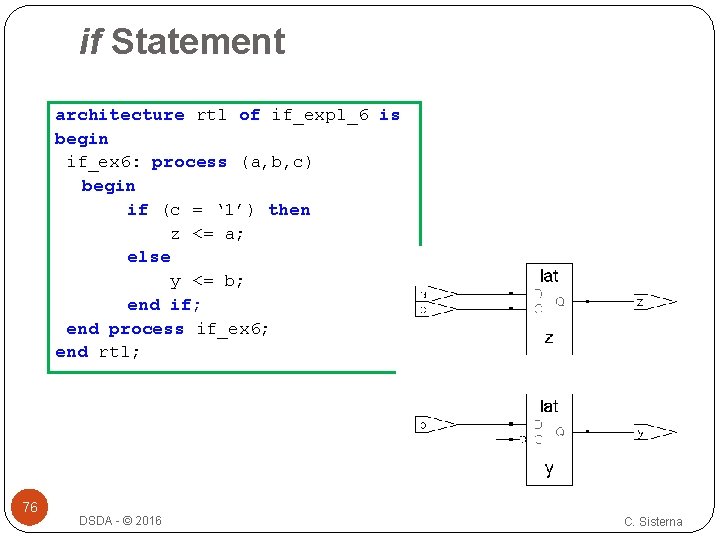

if Statement architecture rtl of if_expl_6 is begin if_ex 6: process (a, b, c) begin if (c = ‘ 1’) then z <= a; else y <= b; end if; end process if_ex 6; end rtl; 76 DSDA - © 2016 C. Sisterna

![case Statement case label case selectorexpression is when choice1 sequentialstatements branch 1 case Statement [case label: ]case <selector_expression> is when <choice_1> => <sequential_statements> -- branch #1](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-77.jpg)

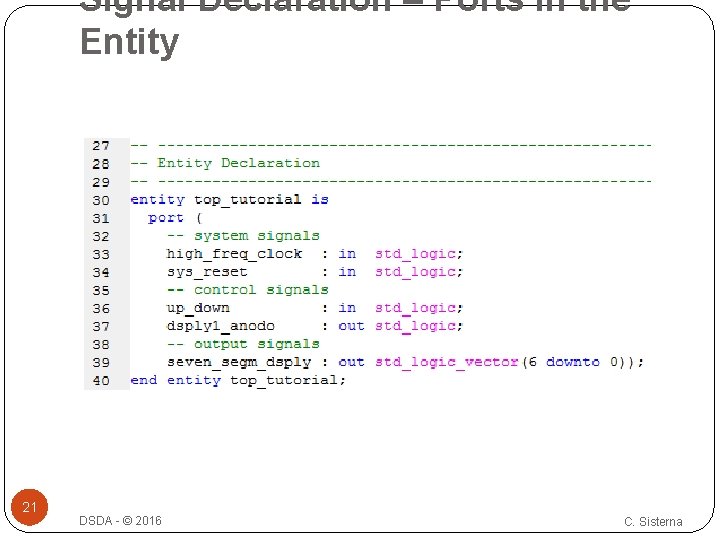

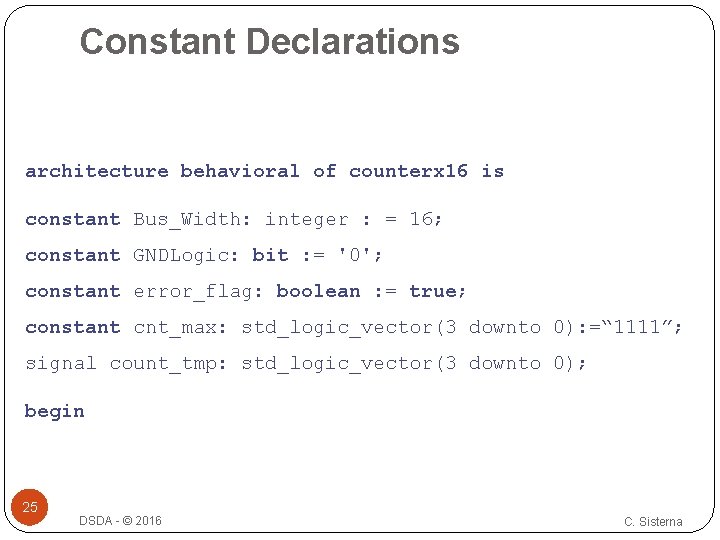

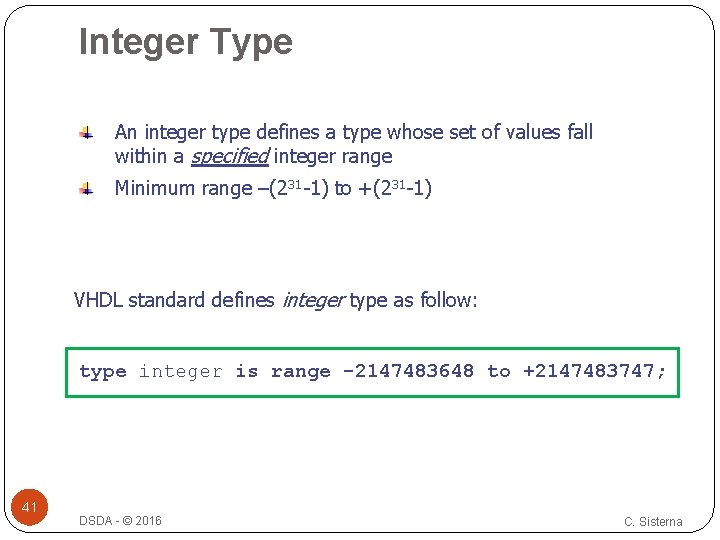

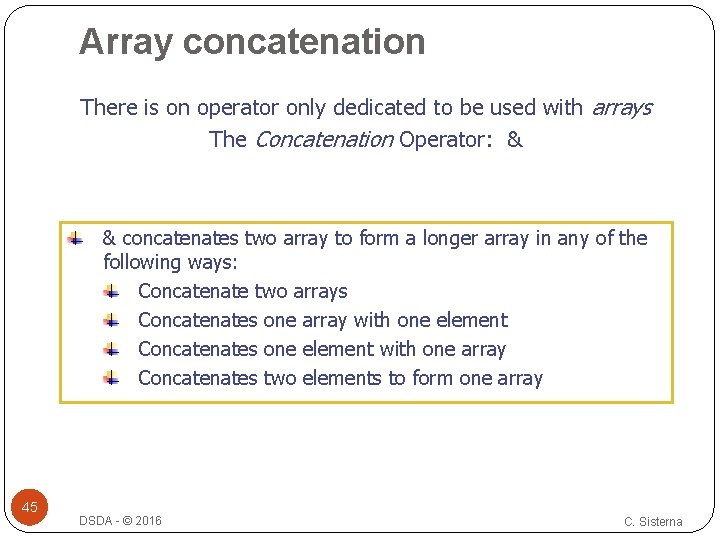

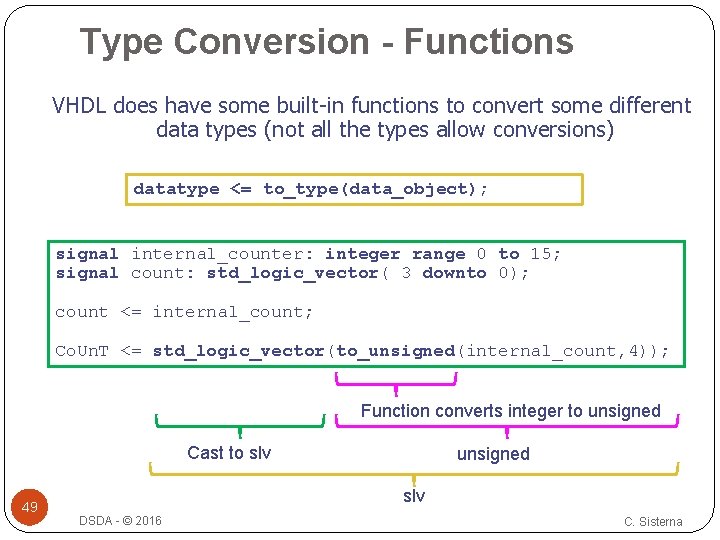

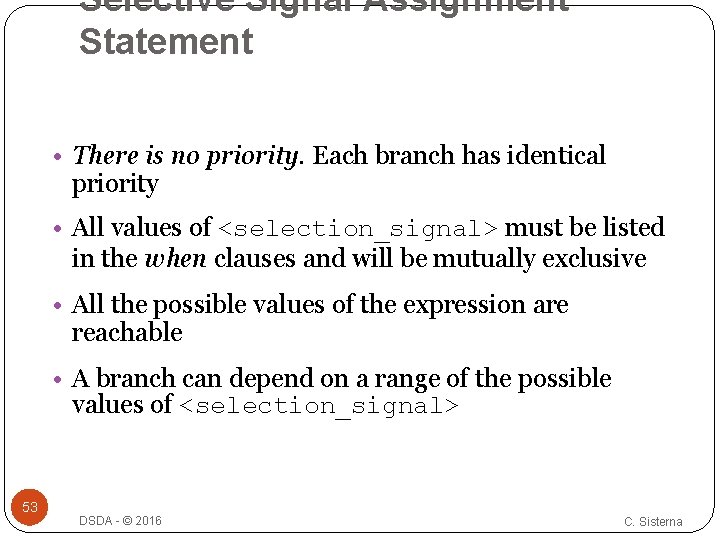

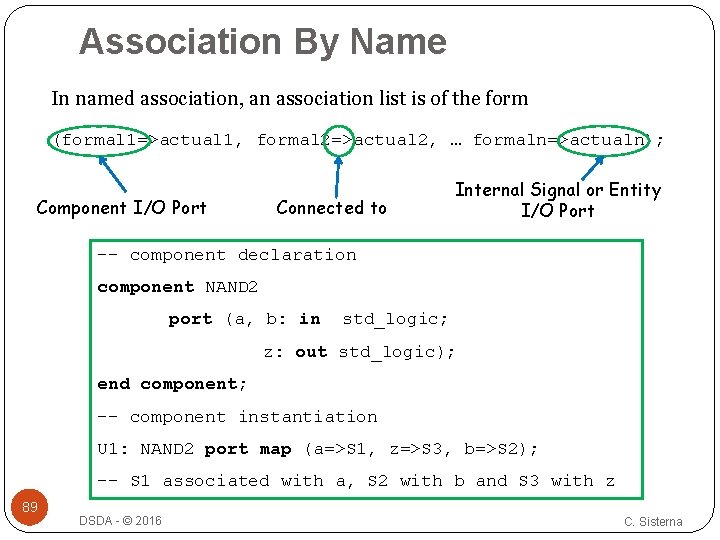

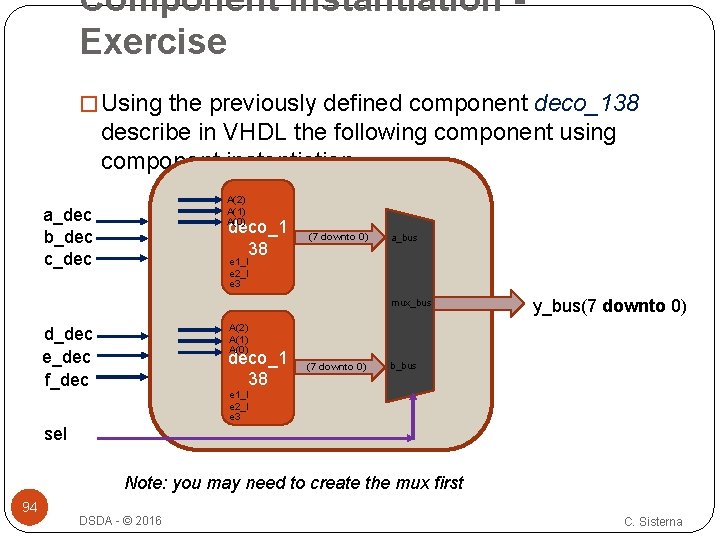

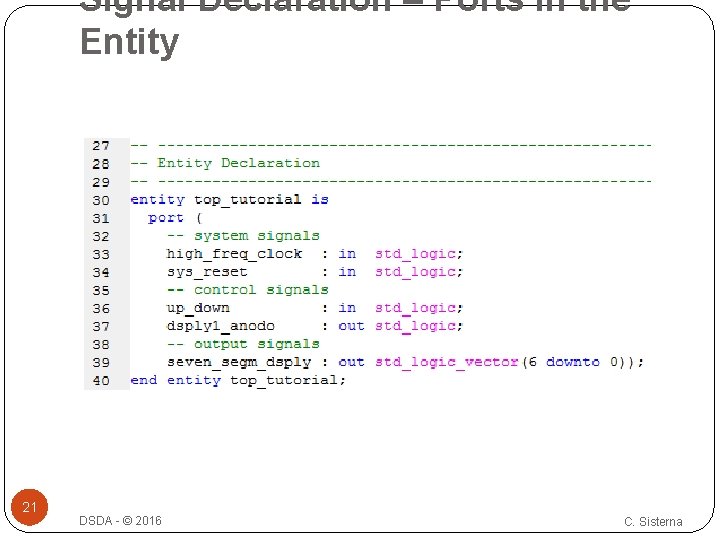

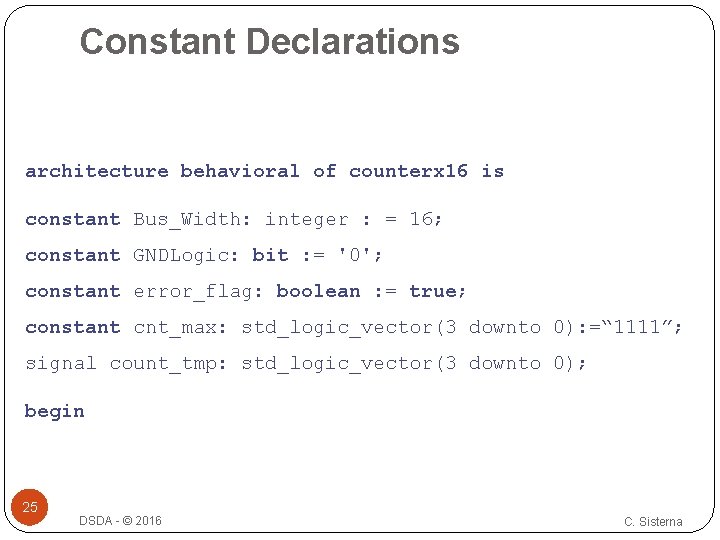

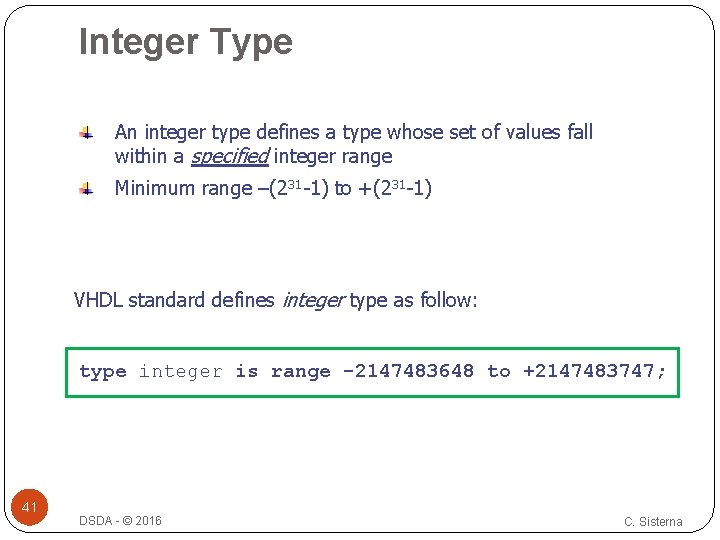

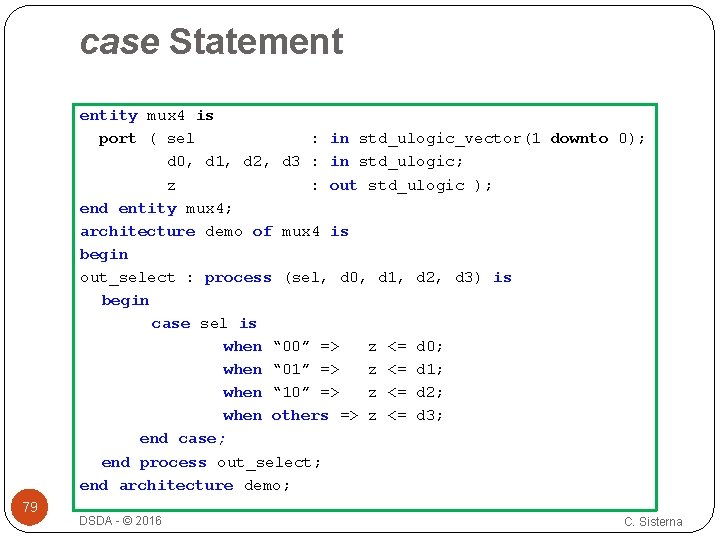

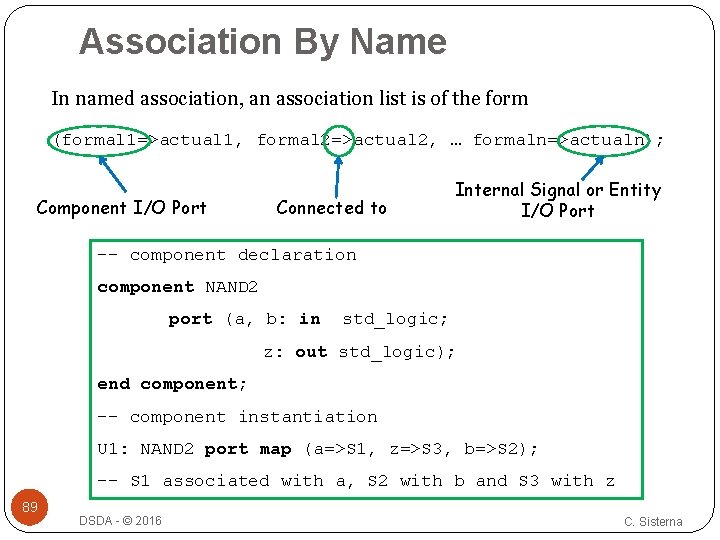

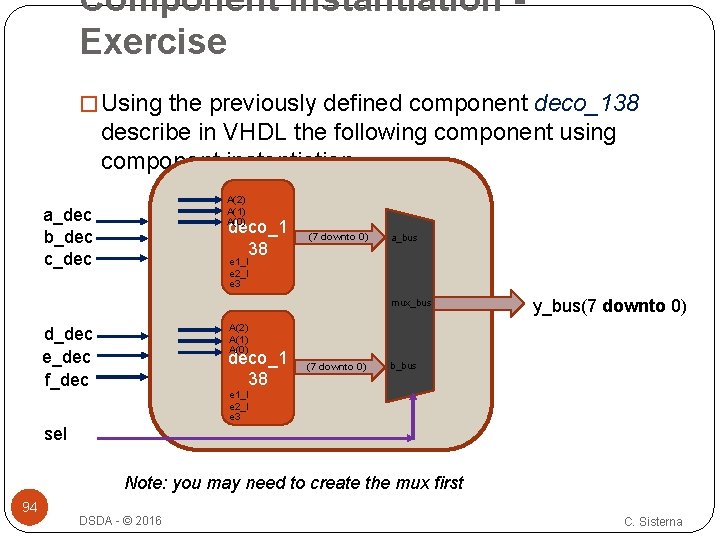

case Statement [case label: ]case <selector_expression> is when <choice_1> => <sequential_statements> -- branch #1 when <choice_2> => <sequential_statements> -- branch #2 . . . [when <choice_n to/downto choice_m > => <sequential_statements>] -- branch #n . . [when <choice_x | choice_y |. . . > => <sequential_statements>] -- branch #. . . [when others => <sequential_statements>]-- last branch end case [case_label]; 77 DSDA - © 2016 C. Sisterna

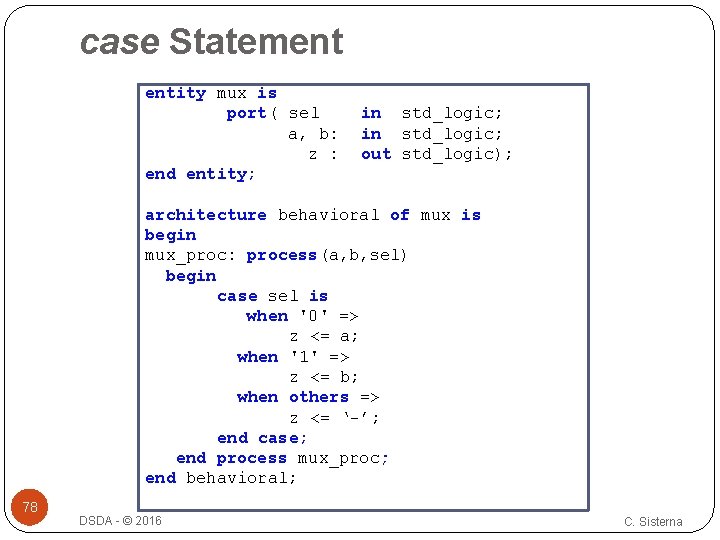

case Statement entity mux is port( sel in std_logic; a, b: in std_logic; z : out std_logic); end entity; architecture behavioral of mux is begin mux_proc: process(a, b, sel) begin case sel is when '0' => z <= a; when '1' => z <= b; when others => z <= ‘-’; end case; end process mux_proc; end behavioral; 78 DSDA - © 2016 C. Sisterna

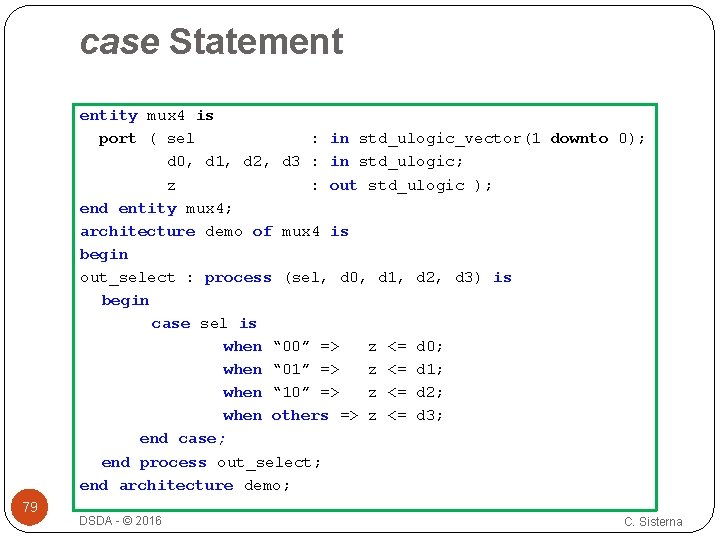

case Statement entity mux 4 is port ( sel : in std_ulogic_vector(1 downto 0); d 0, d 1, d 2, d 3 : in std_ulogic; z : out std_ulogic ); end entity mux 4; architecture demo of mux 4 is begin out_select : process (sel, d 0, d 1, d 2, d 3) is begin case sel is when “ 00” => z <= d 0; when “ 01” => z <= d 1; when “ 10” => z <= d 2; when others => z <= d 3; end case; end process out_select; end architecture demo; 79 DSDA - © 2016 C. Sisterna

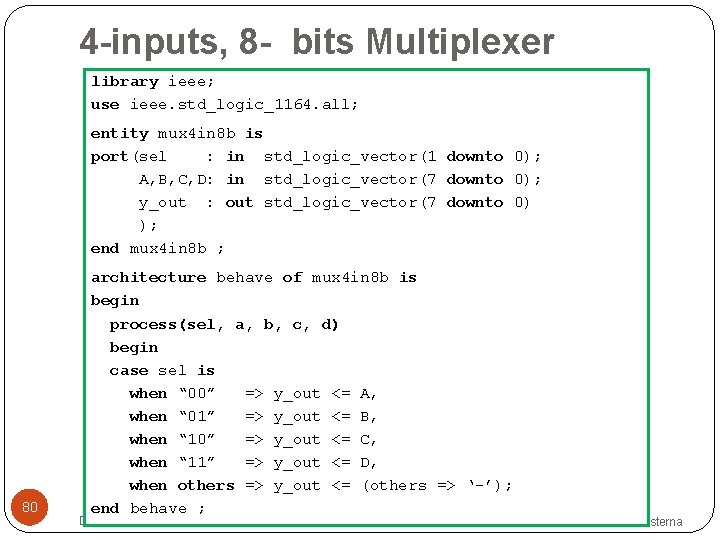

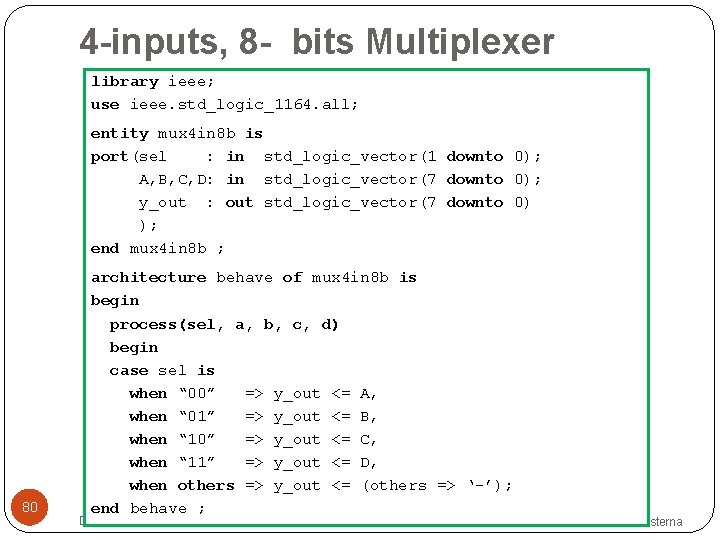

4 -inputs, 8 - bits Multiplexer library ieee; use ieee. std_logic_1164. all; entity mux 4 in 8 b is port(sel : in std_logic_vector(1 downto 0); A, B, C, D: in std_logic_vector(7 downto 0); y_out : out std_logic_vector(7 downto 0) ); end mux 4 in 8 b ; 80 architecture behave of mux 4 in 8 b is begin process(sel, a, b, c, d) begin case sel is when “ 00” => y_out <= A, when “ 01” => y_out <= B, when “ 10” => y_out <= C, when “ 11” => y_out <= D, when others => y_out <= (others => ‘-’); end behave ; DSDA - © 2016 C. Sisterna

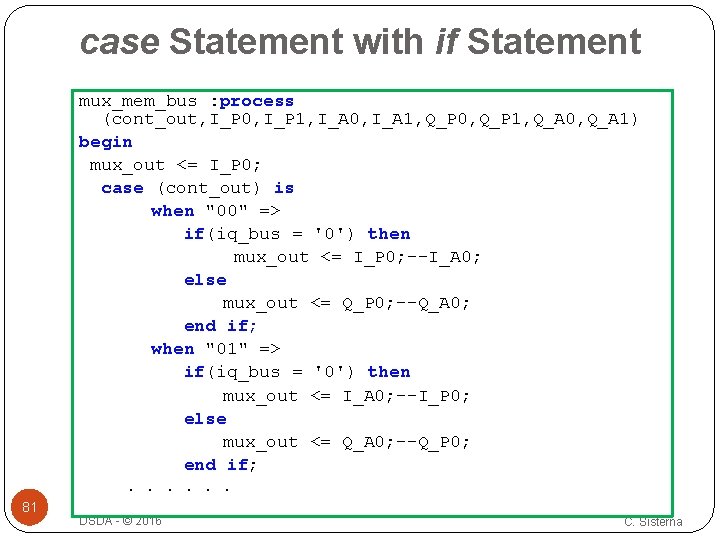

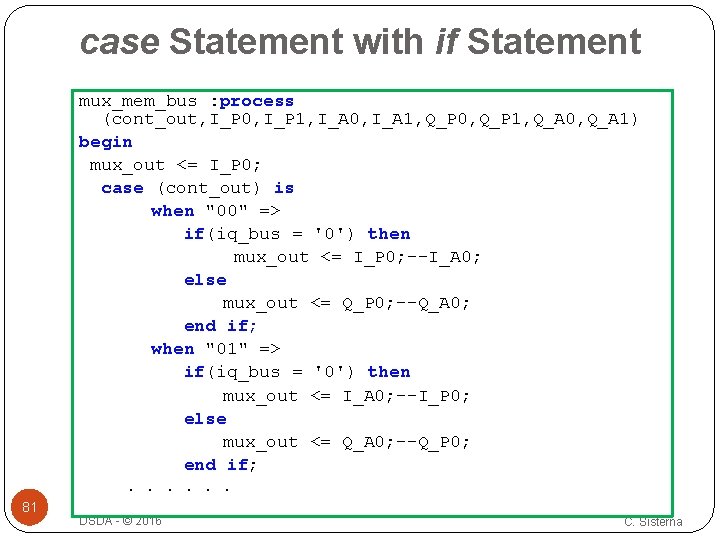

case Statement with if Statement mux_mem_bus : process (cont_out, I_P 0, I_P 1, I_A 0, I_A 1, Q_P 0, Q_P 1, Q_A 0, Q_A 1) begin mux_out <= I_P 0; case (cont_out) is when "00" => if(iq_bus = '0') then mux_out <= I_P 0; --I_A 0; else mux_out <= Q_P 0; --Q_A 0; end if; when "01" => if(iq_bus = '0') then mux_out <= I_A 0; --I_P 0; else mux_out <= Q_A 0; --Q_P 0; end if; . . . 81 DSDA - © 2016 C. Sisterna

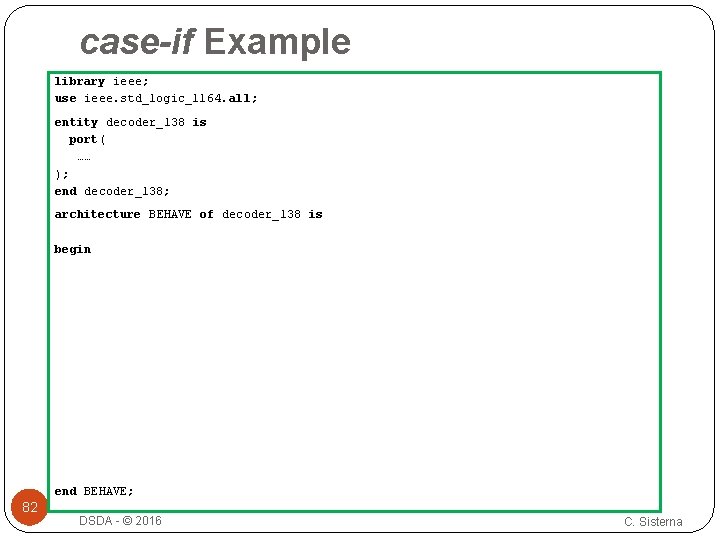

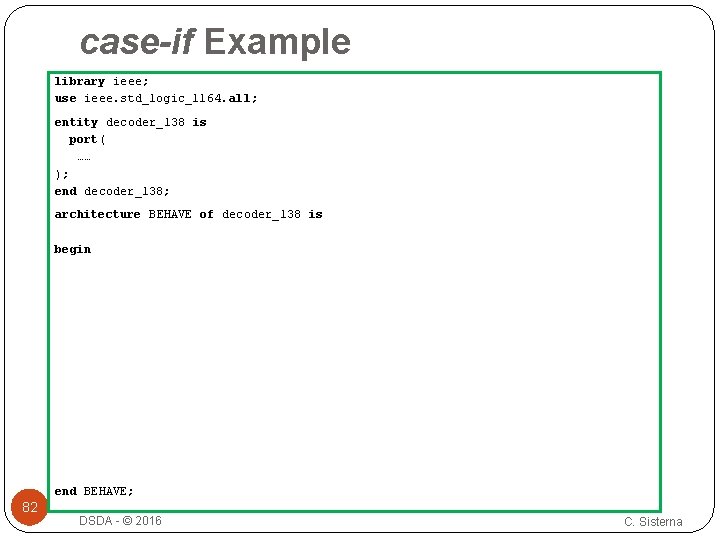

case-if Example library ieee; use ieee. std_logic_1164. all; entity decoder_138 is port( …… ); end decoder_138; architecture BEHAVE of decoder_138 is begin end BEHAVE; 82 DSDA - © 2016 C. Sisterna

![forloop Statement looplabel for identifier in discreterange loop sequentialstatements end loop looplabel identifier for-loop Statement [loop_label]: for identifier in discrete_range loop <sequential_statements> end loop [loop_label]; <identifier> •](https://slidetodoc.com/presentation_image/2ddf167a70142c475ed8688c831062fa/image-83.jpg)

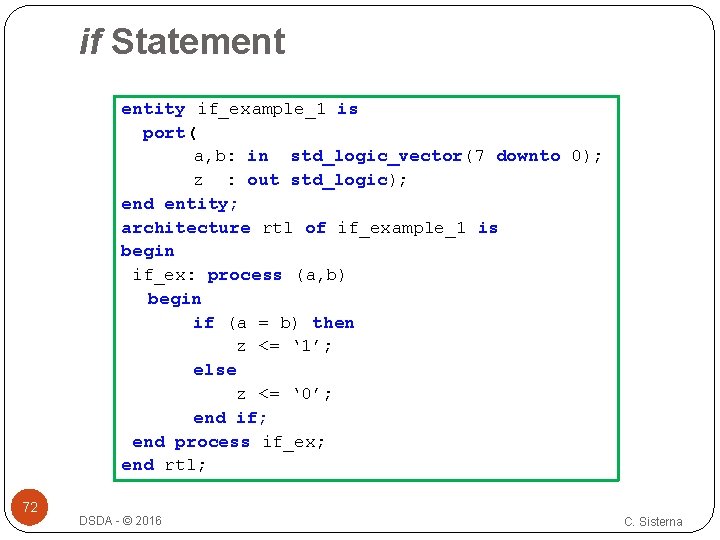

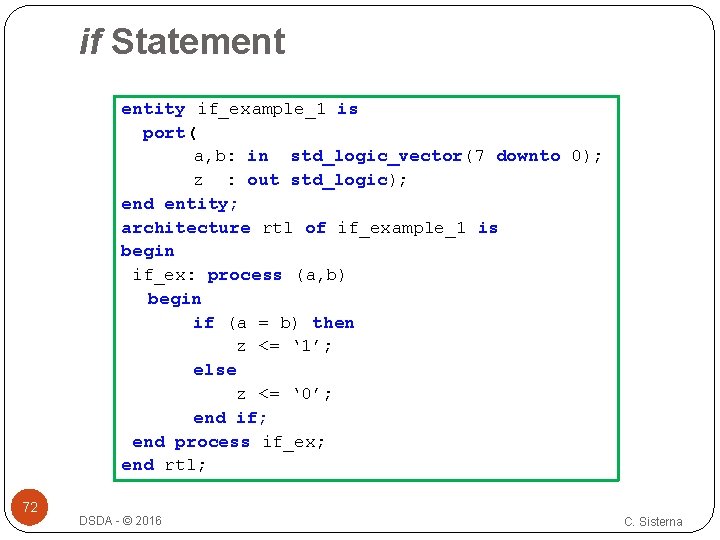

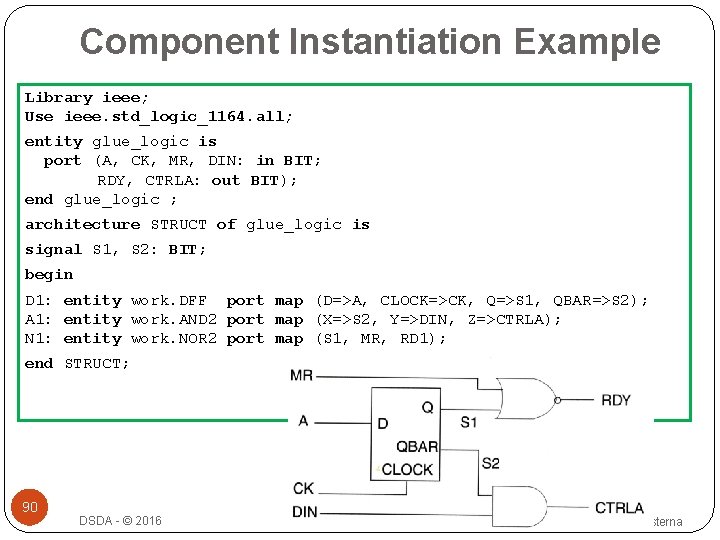

for-loop Statement [loop_label]: for identifier in discrete_range loop <sequential_statements> end loop [loop_label]; <identifier> • The identifier is called loop parameter, and for each iteration of the loop, it takes on successive values of the discrete range, starting from the left element • It is not necessary to declare the identifier • By default the type is integer • Only exists when the loop is executing 83 DSDA - © 2016 C. Sisterna

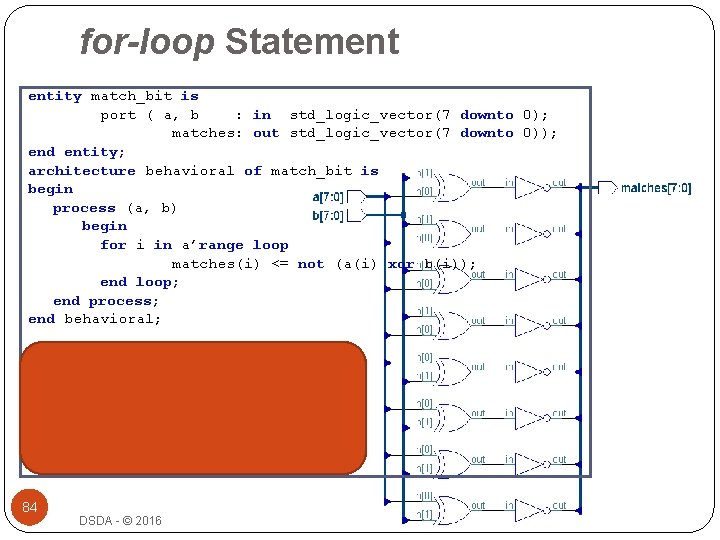

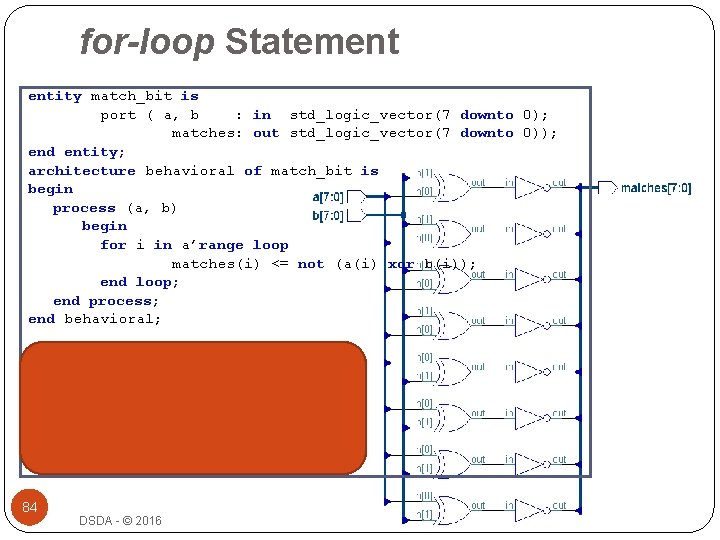

for-loop Statement entity match_bit is port ( a, b : in std_logic_vector(7 downto 0); matches: out std_logic_vector(7 downto 0)); end entity; architecture behavioral of match_bit is begin process (a, b) begin for i in a’range loop matches(i) <= not (a(i) xor b(i)); end loop; end process; end behavioral; -- process (a, b) -- begin -- matches(7) <= not (a(7) xor b(7)); -- matches(6) <= not (a(6) xor b(6)); --. . -- matches(0) <= not (a(0) xor b(0)); -- end process; 84 DSDA - © 2016 C. Sisterna

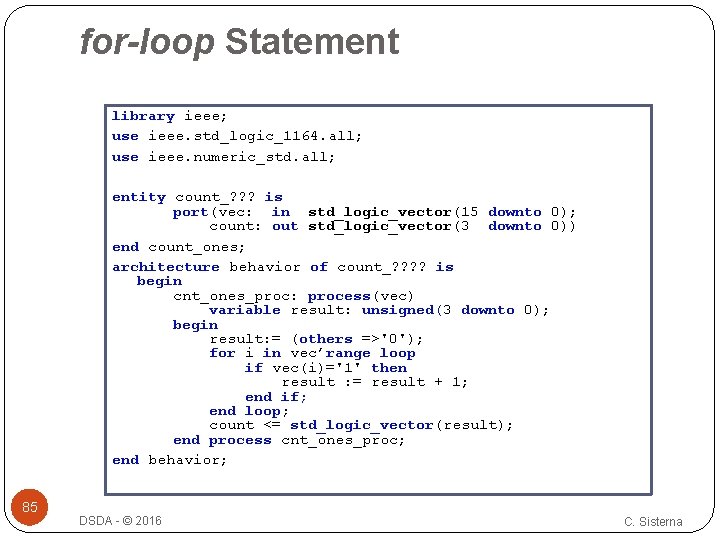

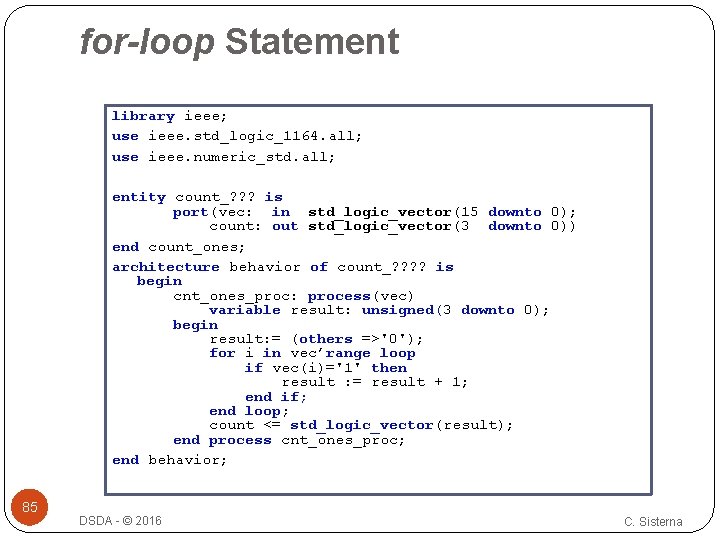

for-loop Statement library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity count_? ? ? is port(vec: in std_logic_vector(15 downto 0); count: out std_logic_vector(3 downto 0)) end count_ones; architecture behavior of count_? ? is begin cnt_ones_proc: process(vec) variable result: unsigned(3 downto 0); begin result: = (others =>'0'); for i in vec’range loop if vec(i)='1' then result : = result + 1; end if; end loop; count <= std_logic_vector(result); end process cnt_ones_proc; end behavior; 85 DSDA - © 2016 C. Sisterna

The Role of Componentes in VHDL Hierarchy in VHDL Components Divide & Conquer Each subcomponent can be designed and completely tested Create library of components (technology independent if possible) Third-party available components Code for reuse 86 DSDA - © 2016 C. Sisterna

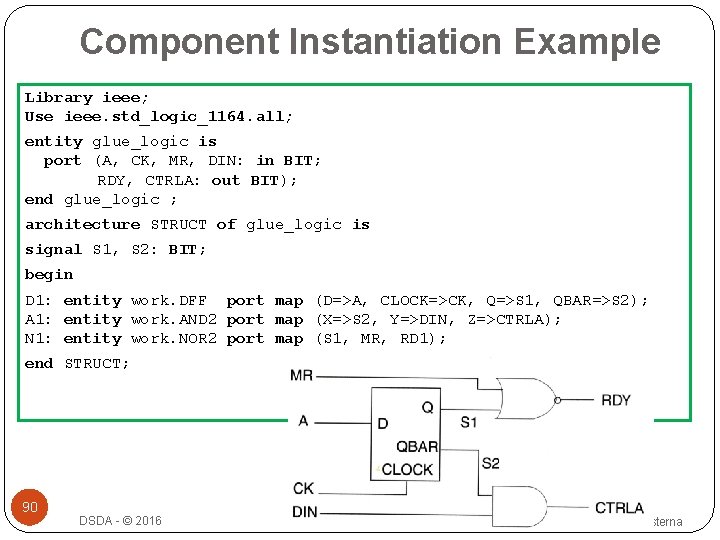

Component Instantiation Component instantiation is a concurrent statement that is used to connect a component I/Os to the internal signals or to the I/Os of the higher lever component_label: entity work. component_name [generic map (generic_assocation_list)] port map (port_association_list); ▫ component_label it labels the instance by giving a name to the instanced ▫ generic_assocation_list assign new values to the default generic values (given in the entity declaration) ▫ port_association_list associate the signals in the top entity/architecture with the ports of the component. There are two ways of specifying the port map: • Positional Association / Name Association 87 DSDA - © 2016 C. Sisterna

Association by Position -- component declaration component NAND 2 port (a, b: in std_logic, z: out std_logic); end component; . . . -- component instantiation U 1: NAND 2 port map (S 1, S 2, S 3); -- S 1 is associated with a -- S 2 is associated with b -- S 3 is associated with z 88 DSDA - © 2016 C. Sisterna

Association By Name In named association, an association list is of the form (formal 1=>actual 1, formal 2=>actual 2, … formaln=>actualn); Component I/O Port Connected to Internal Signal or Entity I/O Port -- component declaration component NAND 2 port (a, b: in std_logic; z: out std_logic); end component; -- component instantiation U 1: NAND 2 port map (a=>S 1, z=>S 3, b=>S 2); -- S 1 associated with a, S 2 with b and S 3 with z 89 DSDA - © 2016 C. Sisterna

Component Instantiation Example Library ieee; Use ieee. std_logic_1164. all; entity glue_logic is port (A, CK, MR, DIN: in BIT; RDY, CTRLA: out BIT); end glue_logic ; architecture STRUCT of glue_logic is signal S 1, S 2: BIT; begin D 1: entity work. DFF port map (D=>A, CLOCK=>CK, Q=>S 1, QBAR=>S 2); A 1: entity work. AND 2 port map (X=>S 2, Y=>DIN, Z=>CTRLA); N 1: entity work. NOR 2 port map (S 1, MR, RD 1); end STRUCT; 90 DSDA - © 2016 C. Sisterna

Unconnected Outputs • When a component is instanced, one of the outputs sometimes has to be unconnected • This can be done using the keyword open architecture rtl of top_level is component ex 4 port (a, b: in std_logic; q 1, q 2: out std_logic; end component; begin U 1: ex 4 port map(a=>a, b=>b, q 1=>dout, q 2=>open); end; 91 DSDA - © 2016 C. Sisterna

Unconnected Inputs • Leaving floating inputs is a very bad poor technique • If an input on a component is not to be used, the signal should be connected to VCC or GND. • VHDL ’ 87: It is not permissible to map the input directly in the port map, an internal signal must be used 92 DSDA - © 2016 C. Sisterna

Unconnected Inputs architecture rtl of top_level is component ex 4 port (a, b : in std_logic; q 1, q 2: out std_logic; end component; begin U 1: ex 4 port map(a=>’ 0’, b=>b, q 1=>dout, q 2=>open); end rtl; 93 DSDA - © 2016 C. Sisterna

Component Instantiation Exercise � Using the previously defined component deco_138 describe in VHDL the following component using component instantiation A(2) A(1) A(0) a_dec b_dec c_dec deco_1 38 (7 downto 0) a_bus e 1_l e 2_l e 3 mux_bus y_bus(7 downto 0) A(2) A(1) A(0) d_dec e_dec f_dec deco_1 38 (7 downto 0) b_bus e 1_l e 2_l e 3 sel Note: you may need to create the mux first 94 DSDA - © 2016 C. Sisterna

Component Instantiation Exercise library ieee; use ieee. std_logic_1164. all; entity mux_2 x 1_8 is port(A_bus, B_bus: in std_logic_vector(7 downto 0); sel: in std_logic; mux_bus: out std_logic_vector(7 downto 0)) ; end mux_2 x 1_8; architecture BEHAVE of mux_2 x 1_8 is begin with Sel select mux_bus <= A_Bus when ‘ 1’, B_Bus when others; end BEHAVE; 95 DSDA - © 2016 C. Sisterna

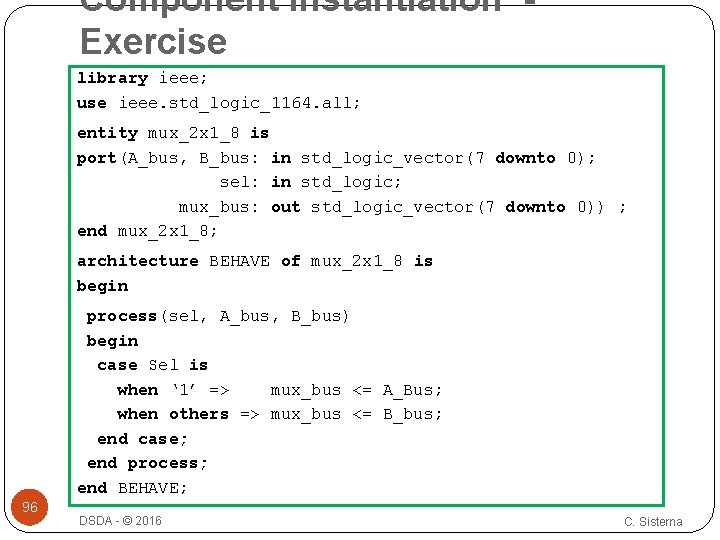

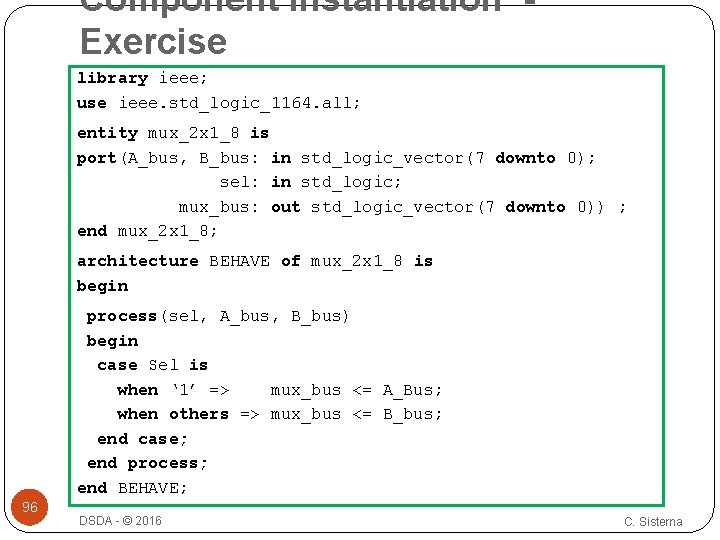

Component Instantiation Exercise library ieee; use ieee. std_logic_1164. all; entity mux_2 x 1_8 is port(A_bus, B_bus: in std_logic_vector(7 downto 0); sel: in std_logic; mux_bus: out std_logic_vector(7 downto 0)) ; end mux_2 x 1_8; architecture BEHAVE of mux_2 x 1_8 is begin process(sel, A_bus, B_bus) begin case Sel is when ‘ 1’ => mux_bus <= A_Bus; when others => mux_bus <= B_bus; end case; end process; end BEHAVE; 96 DSDA - © 2016 C. Sisterna

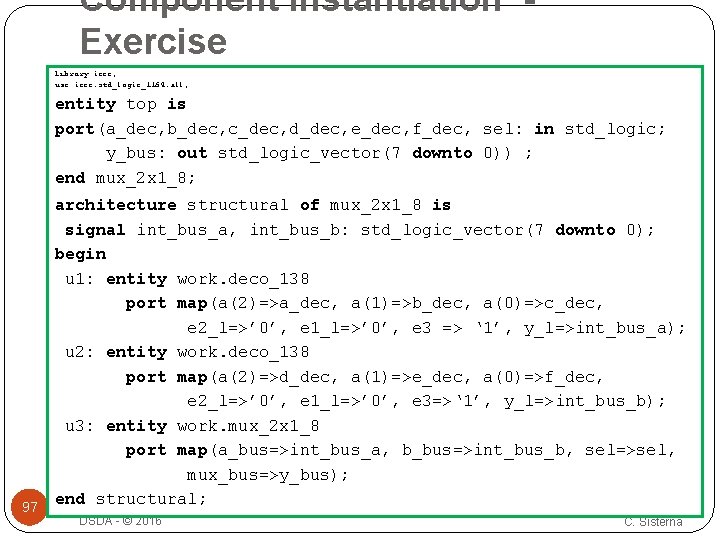

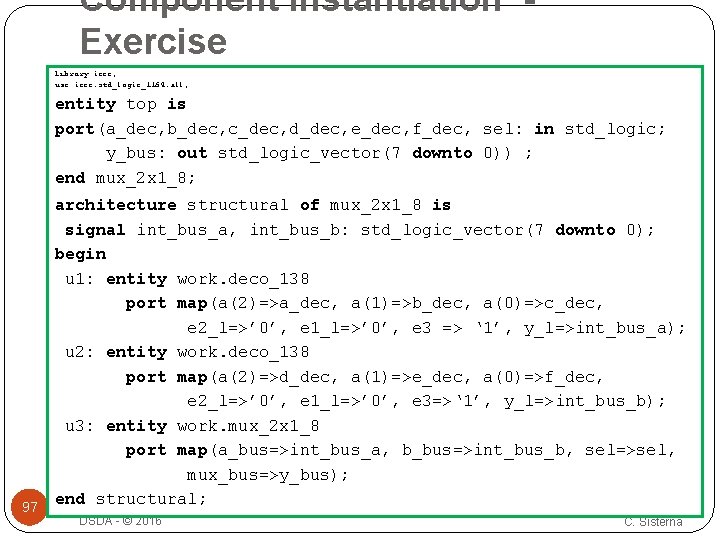

Component Instantiation Exercise library ieee; use ieee. std_logic_1164. all; entity top is port(a_dec, b_dec, c_dec, d_dec, e_dec, f_dec, sel: in std_logic; y_bus: out std_logic_vector(7 downto 0)) ; end mux_2 x 1_8; 97 architecture structural of mux_2 x 1_8 is signal int_bus_a, int_bus_b: std_logic_vector(7 downto 0); begin u 1: entity work. deco_138 port map(a(2)=>a_dec, a(1)=>b_dec, a(0)=>c_dec, e 2_l=>’ 0’, e 1_l=>’ 0’, e 3 => ‘ 1’, y_l=>int_bus_a); u 2: entity work. deco_138 port map(a(2)=>d_dec, a(1)=>e_dec, a(0)=>f_dec, e 2_l=>’ 0’, e 1_l=>’ 0’, e 3=>‘ 1’, y_l=>int_bus_b); u 3: entity work. mux_2 x 1_8 port map(a_bus=>int_bus_a, b_bus=>int_bus_b, sel=>sel, mux_bus=>y_bus); end structural; DSDA - © 2016 C. Sisterna

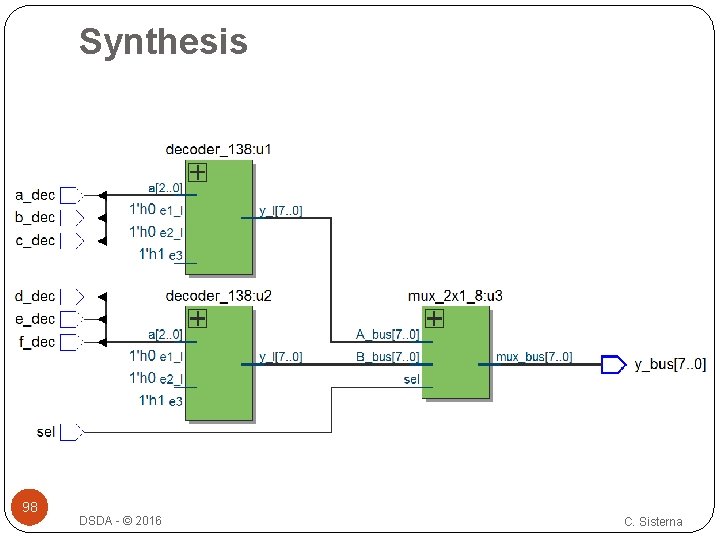

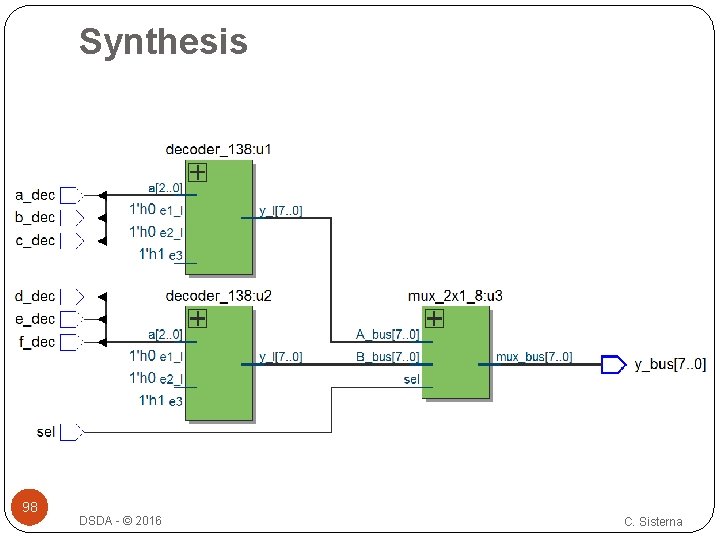

Synthesis 98 DSDA - © 2016 C. Sisterna