Logic Circuits and Computer Architecture Appendix A Digital

- Slides: 142

Logic Circuits and Computer Architecture Appendix A Digital Logic Circuits Part 1: Combinational Circuits and Minimization RLAC (2008 -09) by Luciano Gualà A 1 - 1

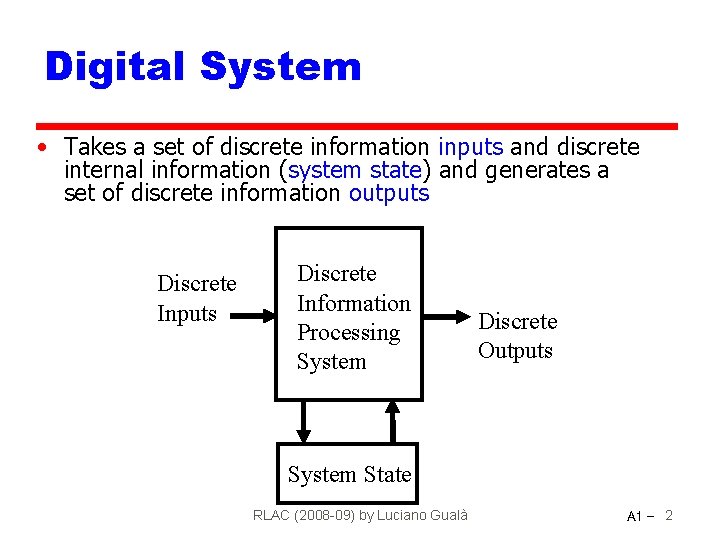

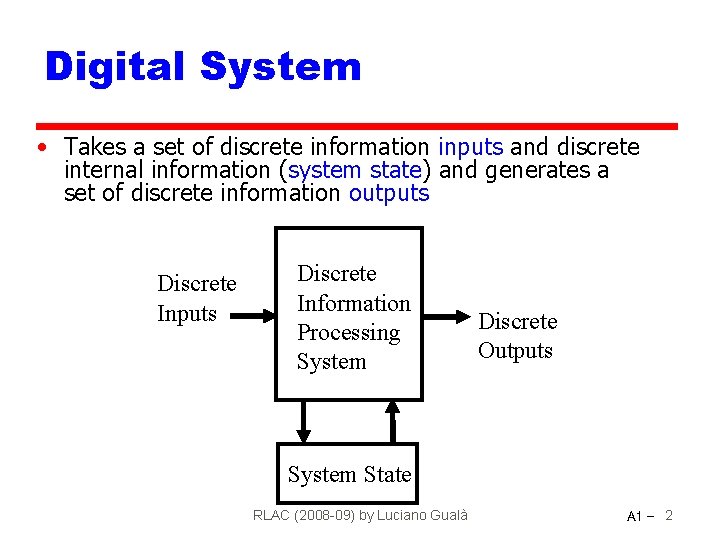

Digital System • Takes a set of discrete information inputs and discrete internal information (system state) and generates a set of discrete information outputs Discrete Information Processing System Discrete Outputs System State RLAC (2008 -09) by Luciano Gualà A 1 - 2

Basic circuits • Combinational § without memory, stateless § Output = Function(Input) • Sequential § § with memory, state dependent behaviour State = Function (State, Input) Output = Function (State) or Function (State, Input) It can be: • Synchronous: state updated at discrete times • Asynchronous: State updated at any times RLAC (2008 -09) by Luciano Gualà A 1 - 3

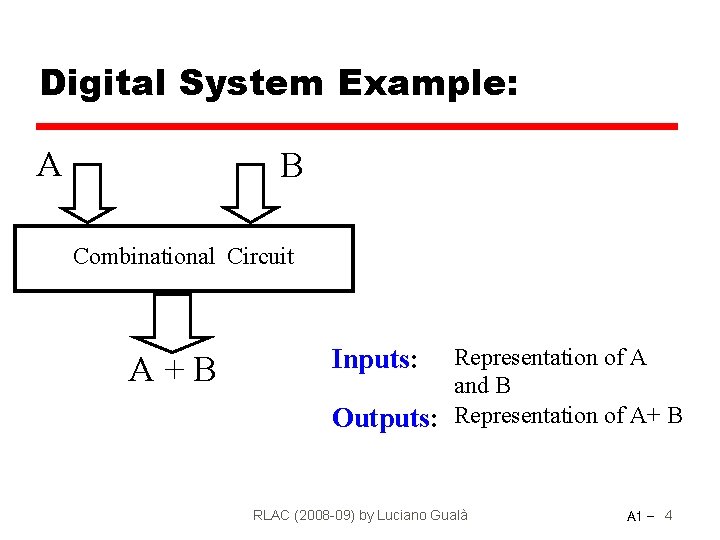

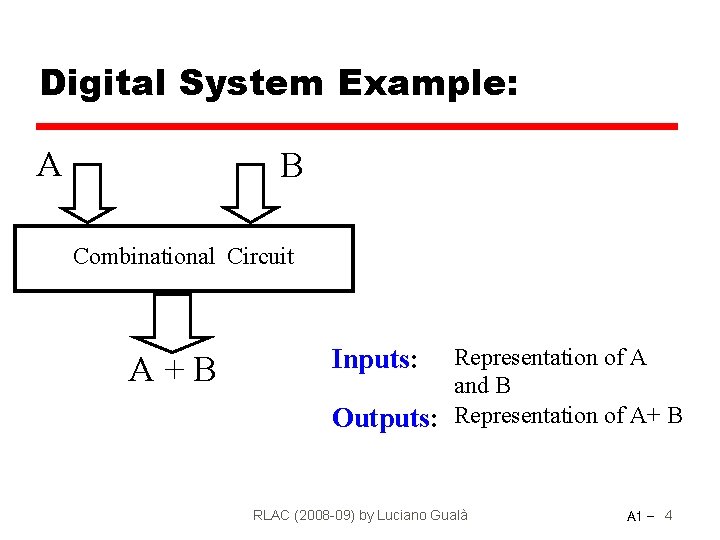

Digital System Example: A B Combinational Circuit A+B Representation of A and B Outputs: Representation of A+ B Inputs: RLAC (2008 -09) by Luciano Gualà A 1 - 4

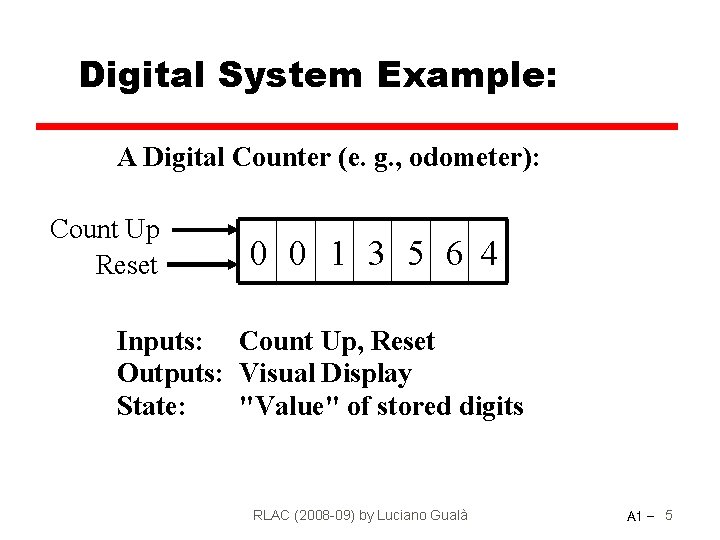

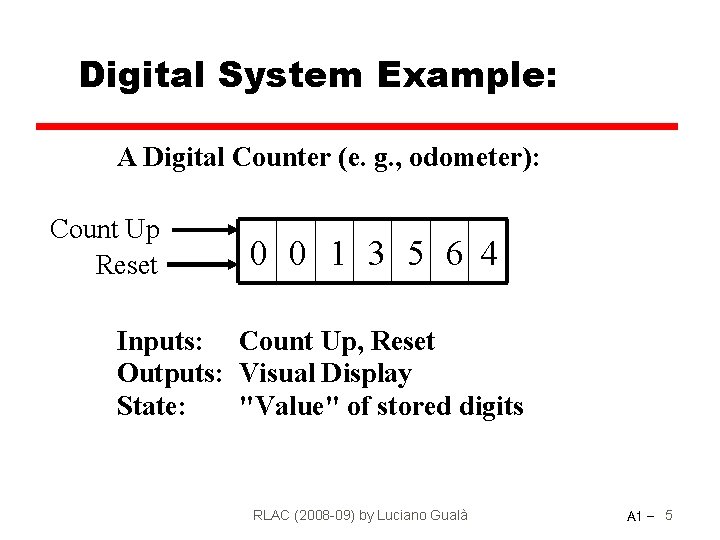

Digital System Example: A Digital Counter (e. g. , odometer): Count Up Reset 0 0 1 3 5 6 4 Inputs: Count Up, Reset Outputs: Visual Display "Value" of stored digits State: RLAC (2008 -09) by Luciano Gualà A 1 - 5

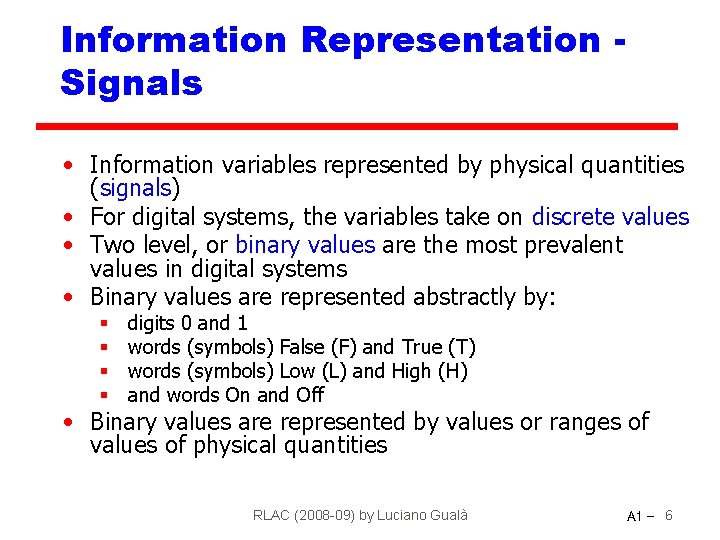

Information Representation Signals • Information variables represented by physical quantities (signals) • For digital systems, the variables take on discrete values • Two level, or binary values are the most prevalent values in digital systems • Binary values are represented abstractly by: § § digits 0 and 1 words (symbols) False (F) and True (T) words (symbols) Low (L) and High (H) and words On and Off • Binary values are represented by values or ranges of values of physical quantities RLAC (2008 -09) by Luciano Gualà A 1 - 6

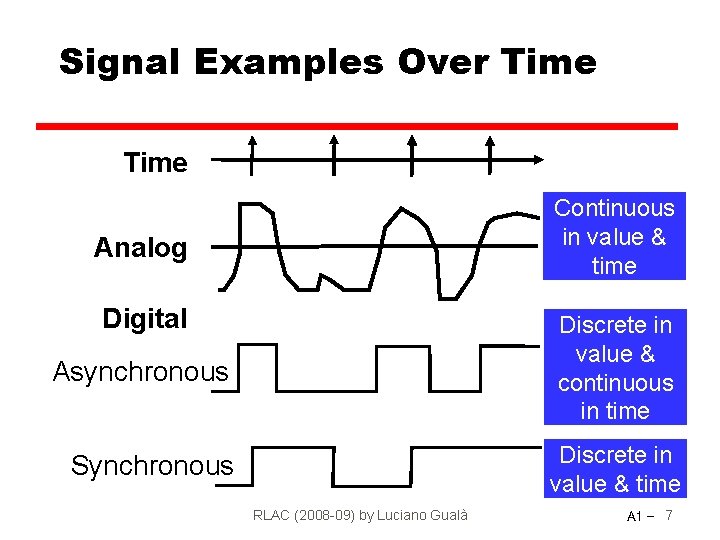

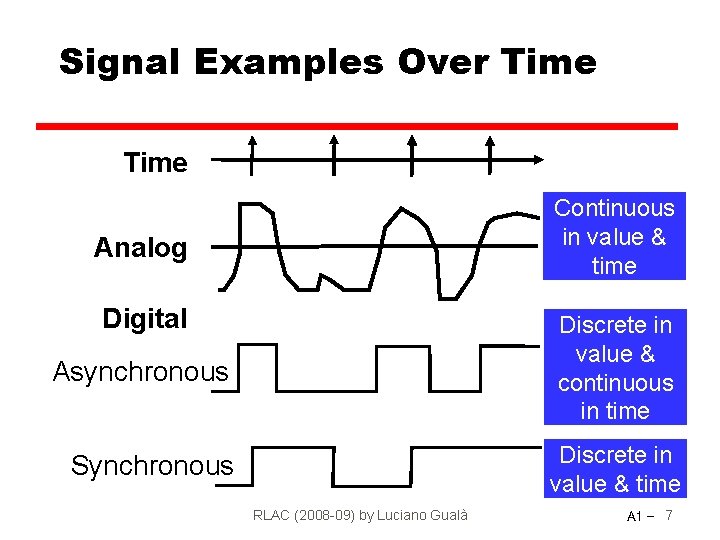

Signal Examples Over Time Continuous in value & time Analog Digital Discrete in value & continuous in time Asynchronous Discrete in value & time Synchronous RLAC (2008 -09) by Luciano Gualà A 1 - 7

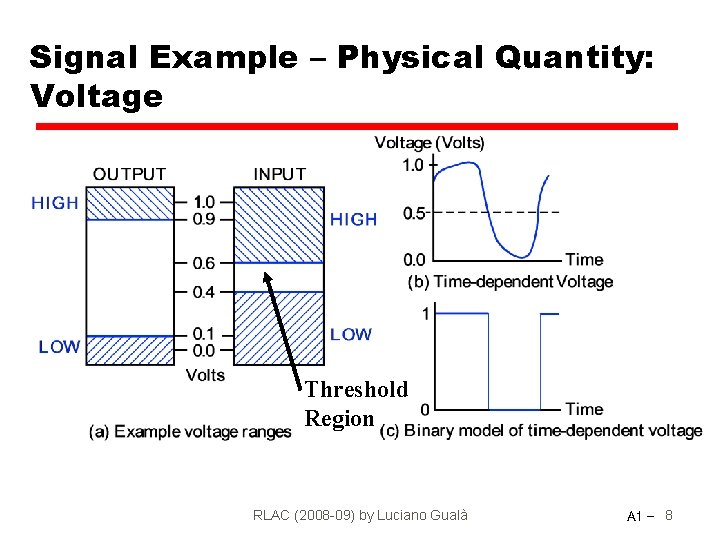

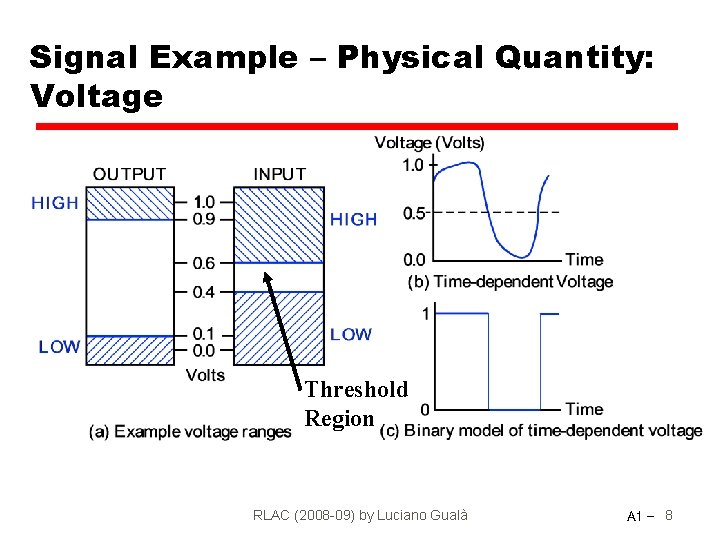

Signal Example – Physical Quantity: Voltage Threshold Region RLAC (2008 -09) by Luciano Gualà A 1 - 8

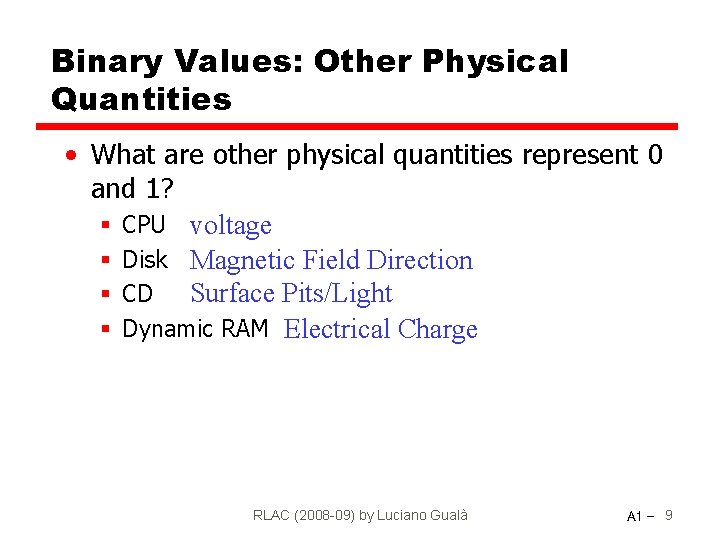

Binary Values: Other Physical Quantities • What are other physical quantities represent 0 and 1? § CPU voltage § Disk Magnetic Field Direction § CD Surface Pits/Light § Dynamic RAM Electrical Charge RLAC (2008 -09) by Luciano Gualà A 1 - 9

Information processing • by means of boolean gates • a boolean gate implements simple boolean operations (see later) • basic gates: § AND, OR, NOT • gates are used to build circuits RLAC (2008 -09) by Luciano Gualà A 1 - 10

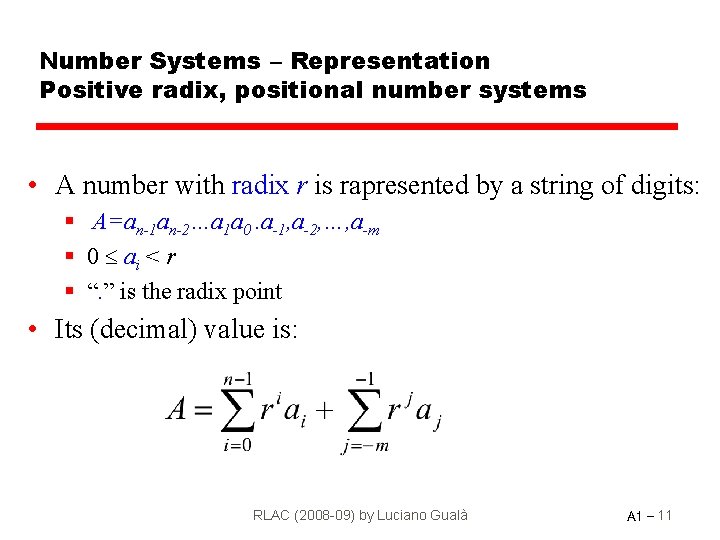

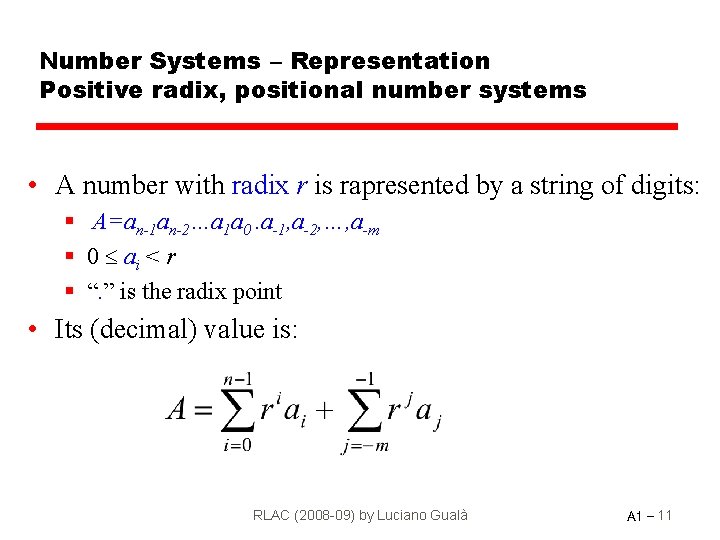

Number Systems – Representation Positive radix, positional number systems • A number with radix r is rapresented by a string of digits: § A=an-1 an-2…a 1 a 0. a-1, a-2, …, a-m § 0 ai < r § “. ” is the radix point • Its (decimal) value is: RLAC (2008 -09) by Luciano Gualà A 1 - 11

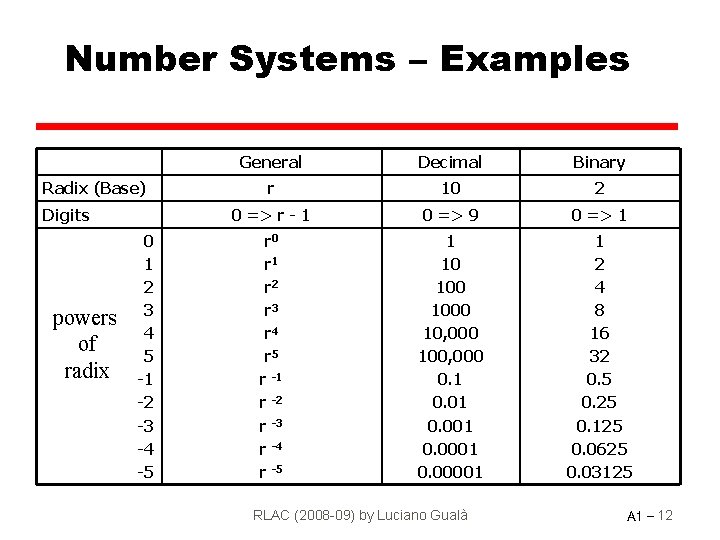

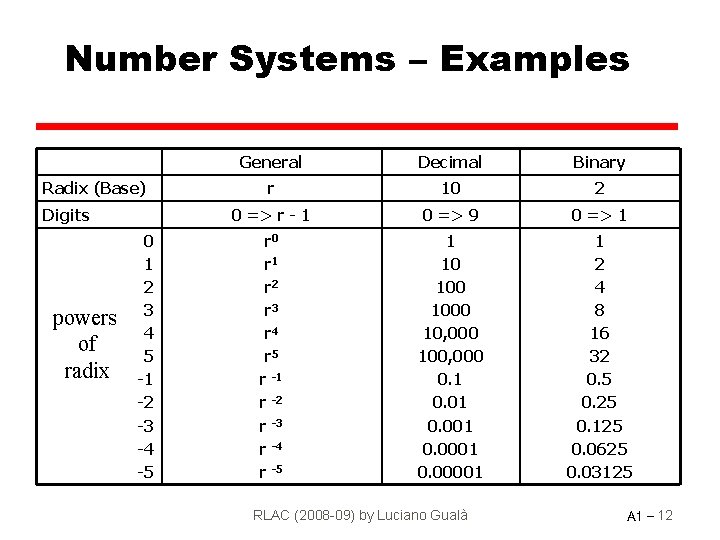

Number Systems – Examples Radix (Base) Digits powers of radix 0 1 2 3 4 5 -1 -2 -3 -4 -5 General Decimal Binary r 10 2 0 => r - 1 0 => 9 0 => 1 r 0 r 1 r 2 r 3 r 4 r 5 r -1 r -2 r -3 r -4 r -5 1 10 1000 10, 000 100, 000 0. 1 0. 001 0. 00001 1 2 4 8 16 32 0. 5 0. 25 0. 125 0. 0625 0. 03125 RLAC (2008 -09) by Luciano Gualà A 1 - 12

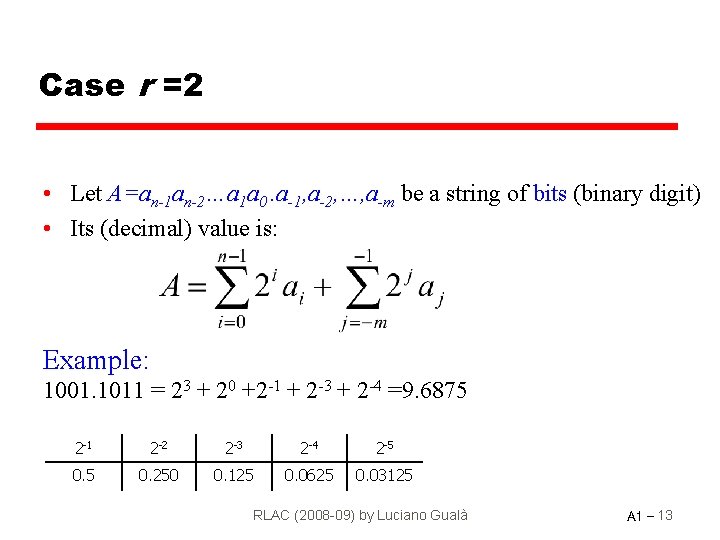

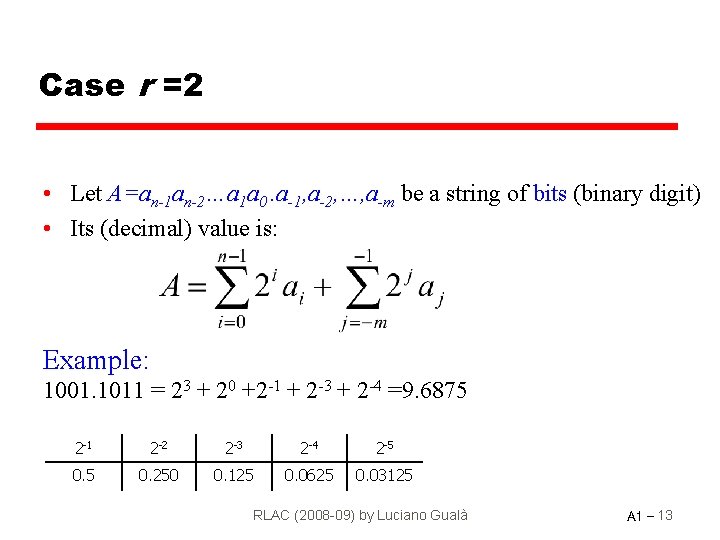

Case r =2 • Let A=an-1 an-2…a 1 a 0. a-1, a-2, …, a-m be a string of bits (binary digit) • Its (decimal) value is: Example: 1001. 1011 = 23 + 20 +2 -1 + 2 -3 + 2 -4 =9. 6875 2 -1 2 -2 2 -3 2 -4 2 -5 0. 250 0. 125 0. 0625 0. 03125 RLAC (2008 -09) by Luciano Gualà A 1 - 13

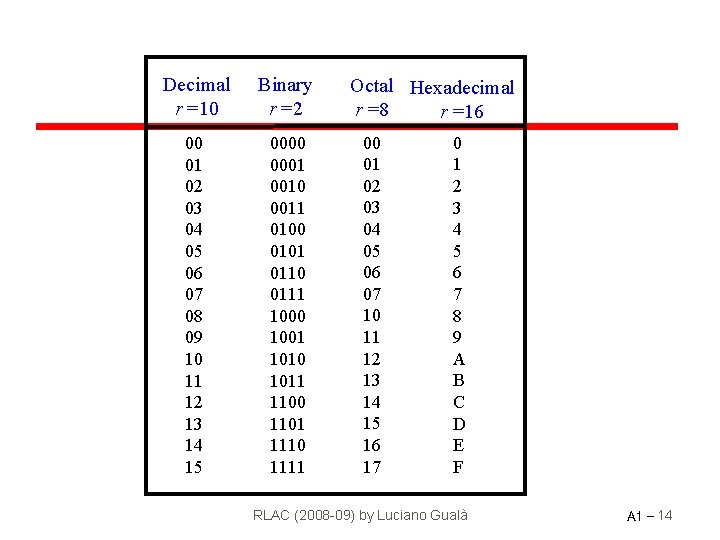

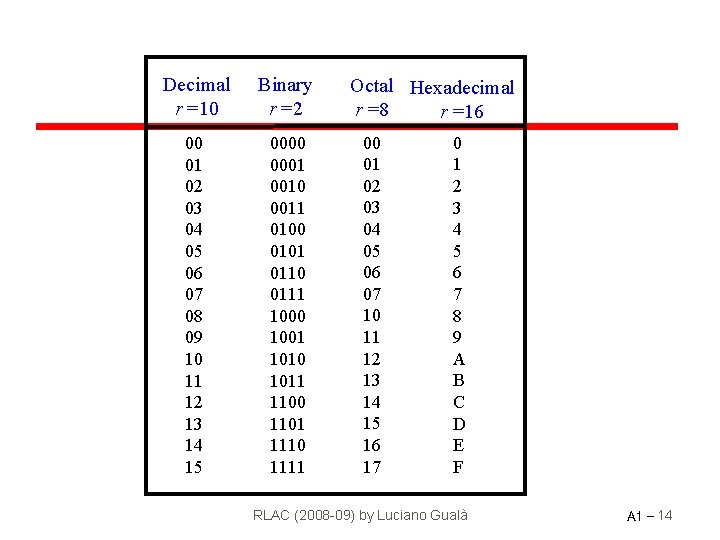

Decimal r =10 Binary r =2 00 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Octal Hexadecimal r =8 r =16 00 01 02 03 04 05 06 07 10 11 12 13 14 15 16 17 0 1 2 3 4 5 6 7 8 9 A B C D E F RLAC (2008 -09) by Luciano Gualà A 1 - 14

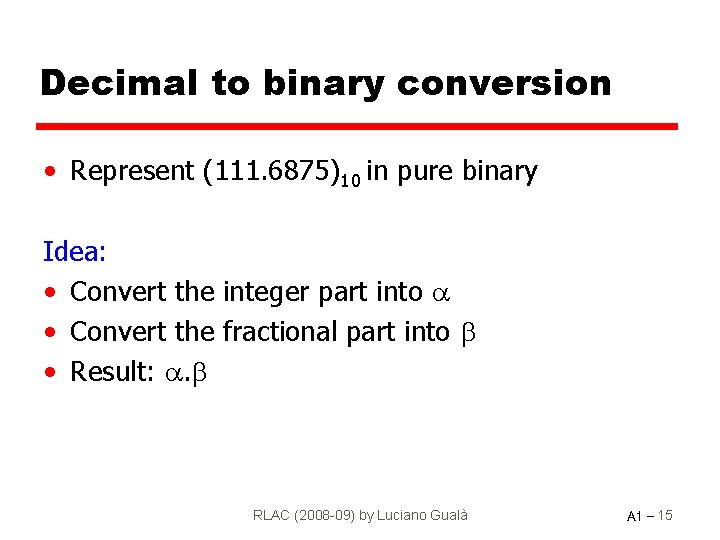

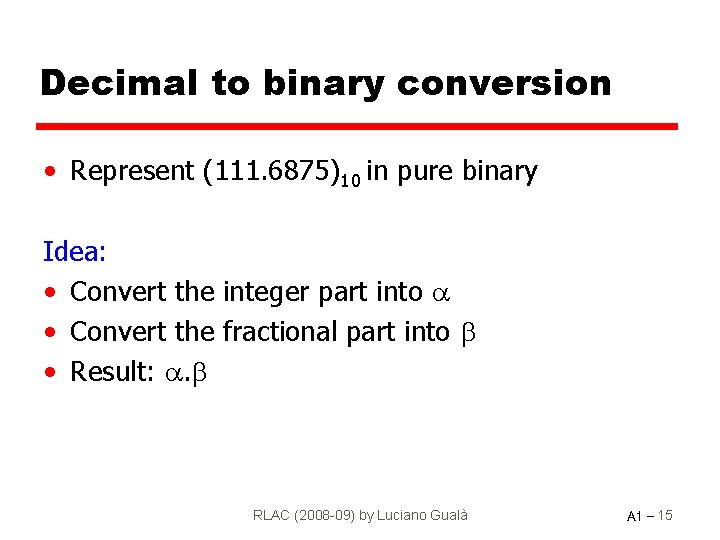

Decimal to binary conversion • Represent (111. 6875)10 in pure binary Idea: • Convert the integer part into • Convert the fractional part into • Result: . RLAC (2008 -09) by Luciano Gualà A 1 - 15

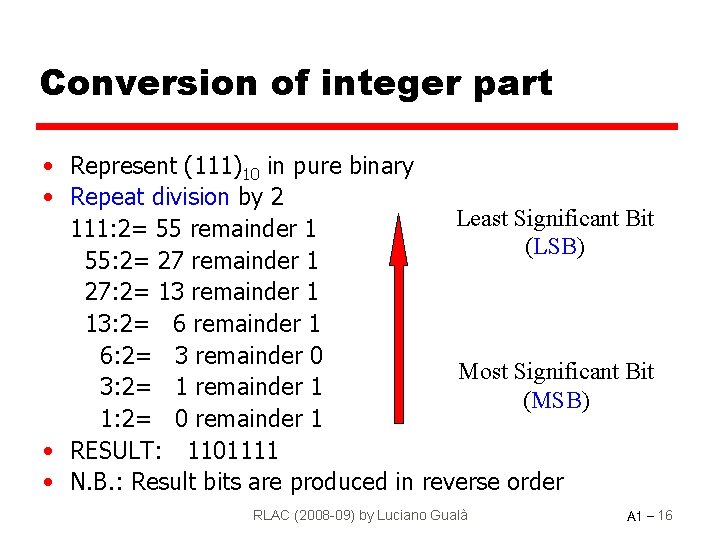

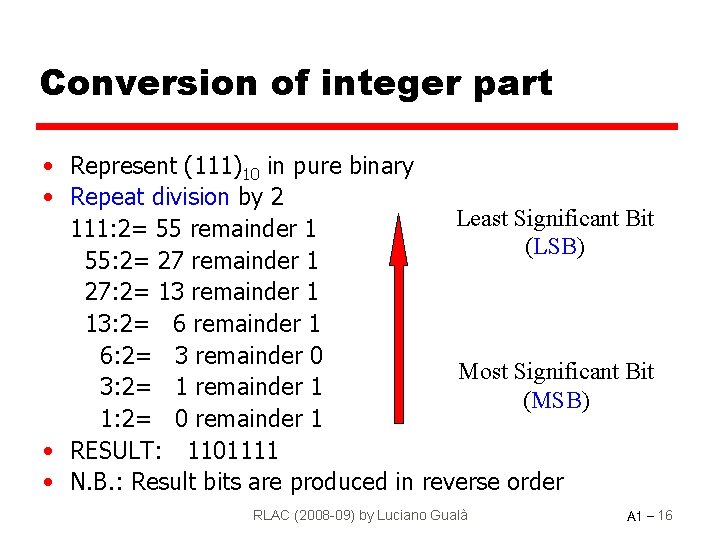

Conversion of integer part • Represent (111)10 in pure binary • Repeat division by 2 Least Significant Bit 111: 2= 55 remainder 1 (LSB) 55: 2= 27 remainder 1 27: 2= 13 remainder 1 13: 2= 6 remainder 1 6: 2= 3 remainder 0 Most Significant Bit 3: 2= 1 remainder 1 (MSB) 1: 2= 0 remainder 1 • RESULT: 1101111 • N. B. : Result bits are produced in reverse order RLAC (2008 -09) by Luciano Gualà A 1 - 16

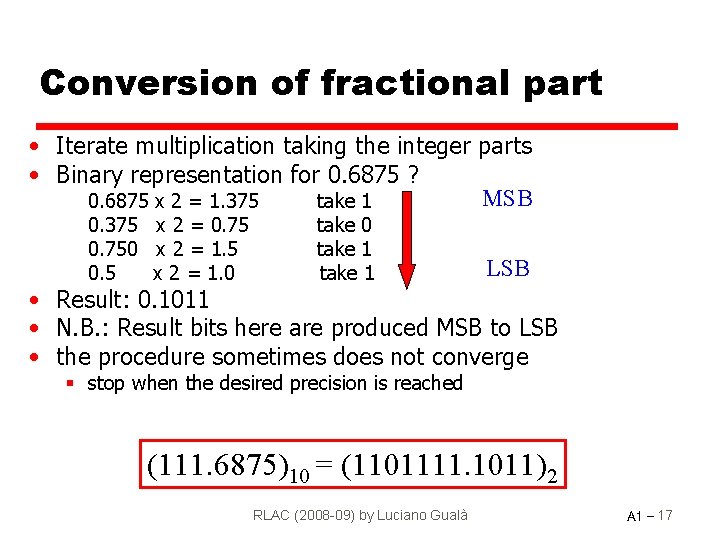

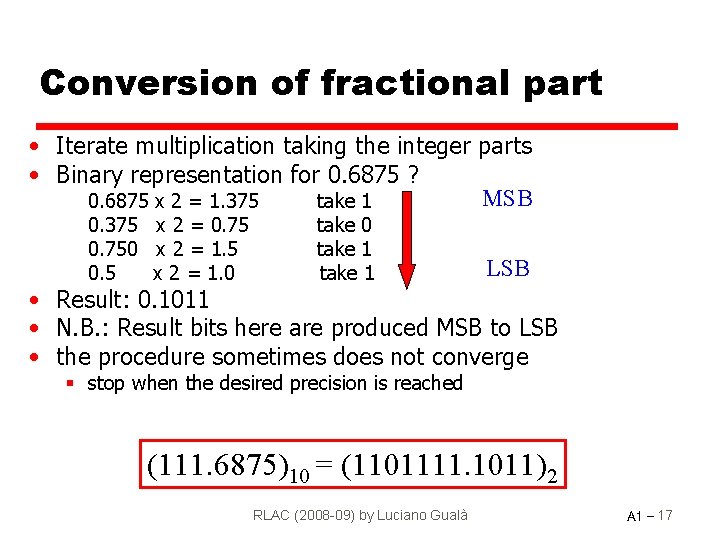

Conversion of fractional part • Iterate multiplication taking the integer parts • Binary representation for 0. 6875 ? MSB 0. 6875 x 2 = 1. 375 take 1 0. 375 x 2 = 0. 750 x 2 = 1. 5 0. 5 x 2 = 1. 0 take 1 LSB • Result: 0. 1011 • N. B. : Result bits here are produced MSB to LSB • the procedure sometimes does not converge § stop when the desired precision is reached (111. 6875)10 = (1101111. 1011)2 RLAC (2008 -09) by Luciano Gualà A 1 - 17

Boolean Algebra • A useful mathematical system for specifying and transforming logic functions • We study Boolean algebra as a foundation for designing and analyzing digital systems! • Named from George Boole RLAC (2008 -09) by Luciano Gualà A 1 - 18

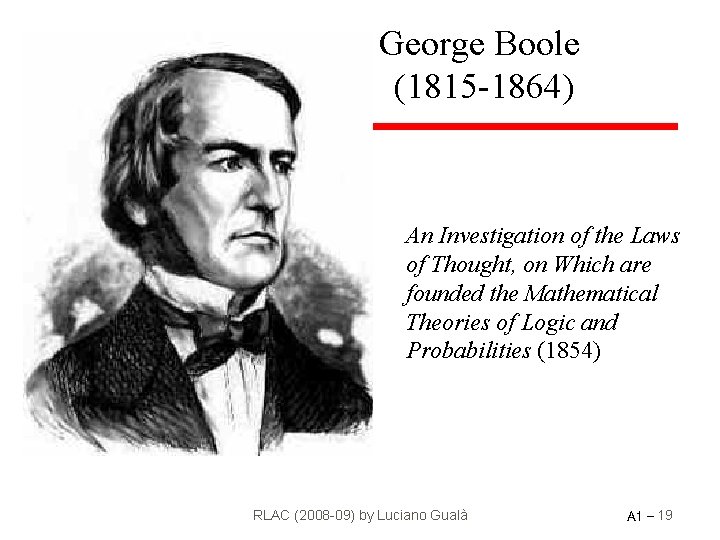

George Boole (1815 -1864) An Investigation of the Laws of Thought, on Which are founded the Mathematical Theories of Logic and Probabilities (1854) RLAC (2008 -09) by Luciano Gualà A 1 - 19

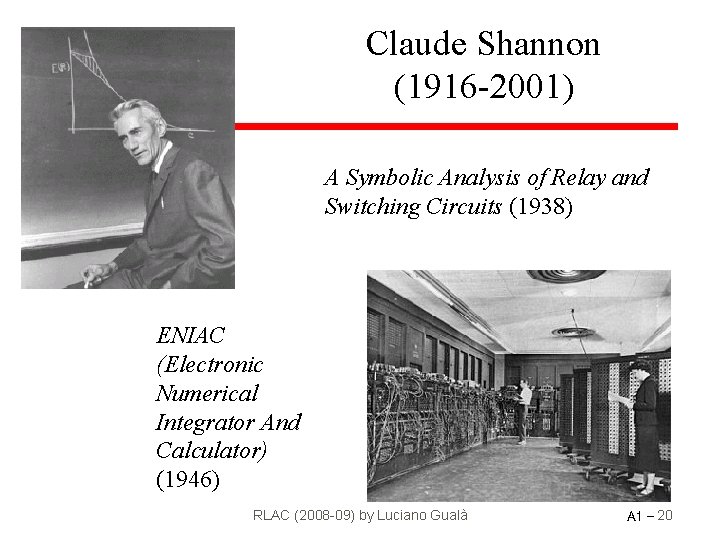

Claude Shannon (1916 -2001) A Symbolic Analysis of Relay and Switching Circuits (1938) ENIAC (Electronic Numerical Integrator And Calculator) (1946) RLAC (2008 -09) by Luciano Gualà A 1 - 20

Boolean Algebra • Boolean Algebra deals with § Binary variables take on one of two values. § Logical operators operate on binary values and binary variables • the two binary values have different names: § § True/False On/Off Yes/No 1/0 • Basic logical operators are the logic functions AND, OR and NOT • Logic gates implement logic functions RLAC (2008 -09) by Luciano Gualà A 1 - 21

Logical Operations • The three basic logical operations are: § AND , OR, NOT • AND is denoted by a dot (·). • OR is denoted by a plus (+). • NOT is denoted by an overbar ( ¯ ), a single quote mark (') after, or (~) before the variable • Intended meaning (for humans - Laws of Thought) § AND: both inputs are true § OR: at least one input is true § NOT: negate the input RLAC (2008 -09) by Luciano Gualà A 1 - 22

Notation Examples • Examples: § Y = A B is read “Y is equal to A AND B. ” § z = x+y is read “z is equal to x OR y. ” § X=A’ is read “X is equal to NOT A. ” § Note: The statement: 1 + 1 = 2 (read “one plus one equals two”) is not the same as 1 + 1 = 1 (read “ 1 or 1 equals 1”). RLAC (2008 -09) by Luciano Gualà A 1 - 23

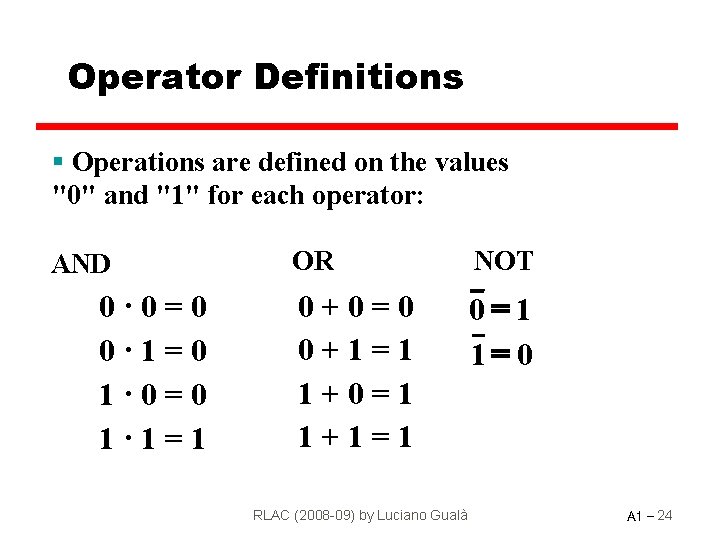

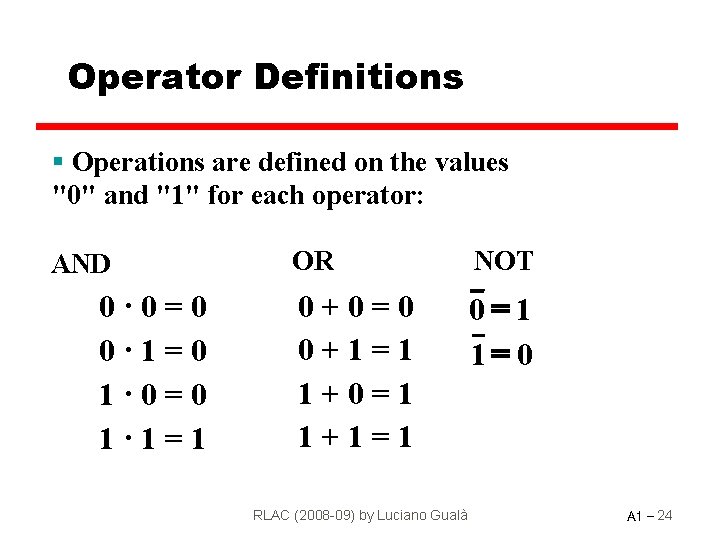

Operator Definitions § Operations are defined on the values "0" and "1" for each operator: AND 0· 0=0 0· 1=0 1· 0=0 1· 1=1 OR NOT 0+0=0 0+1=1 1+0=1 1+1=1 0=1 1=0 RLAC (2008 -09) by Luciano Gualà A 1 - 24

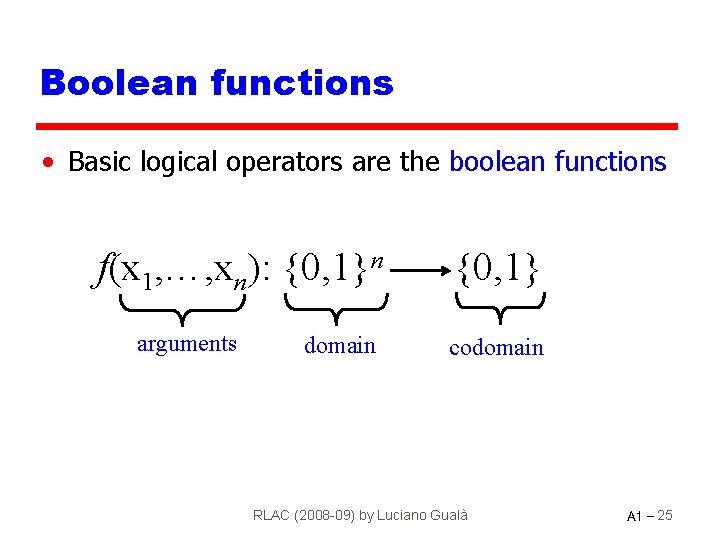

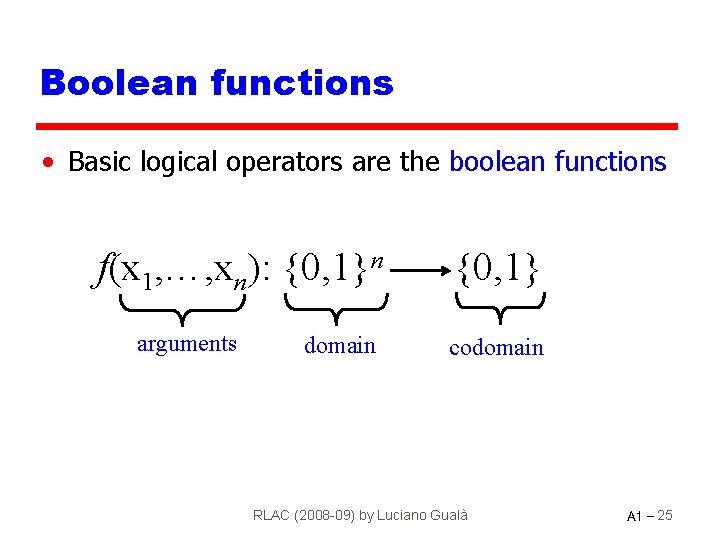

Boolean functions • Basic logical operators are the boolean functions f(x 1, …, xn): {0, 1}n arguments domain {0, 1} codomain RLAC (2008 -09) by Luciano Gualà A 1 - 25

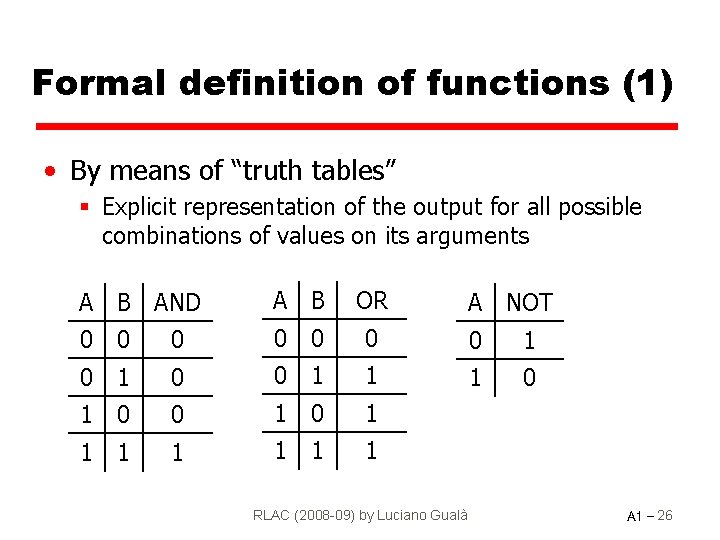

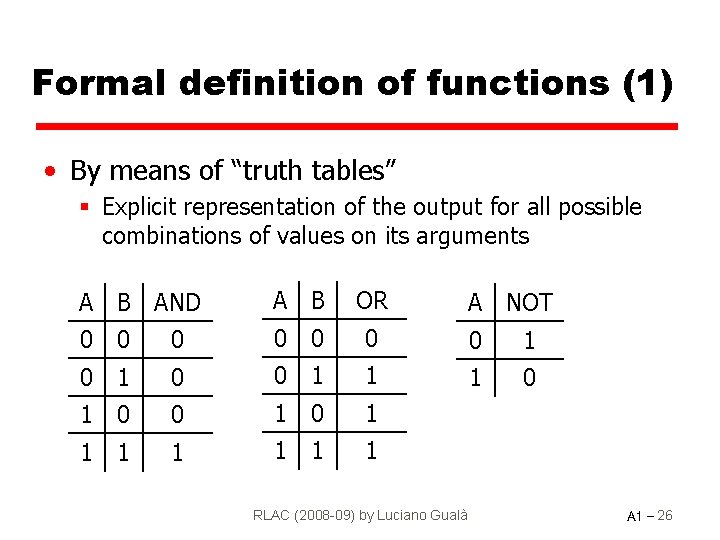

Formal definition of functions (1) • By means of “truth tables” § Explicit representation of the output for all possible combinations of values on its arguments A B AND A B OR 0 0 0 0 1 1 1 0 0 1 1 1 1 RLAC (2008 -09) by Luciano Gualà A NOT A 1 - 26

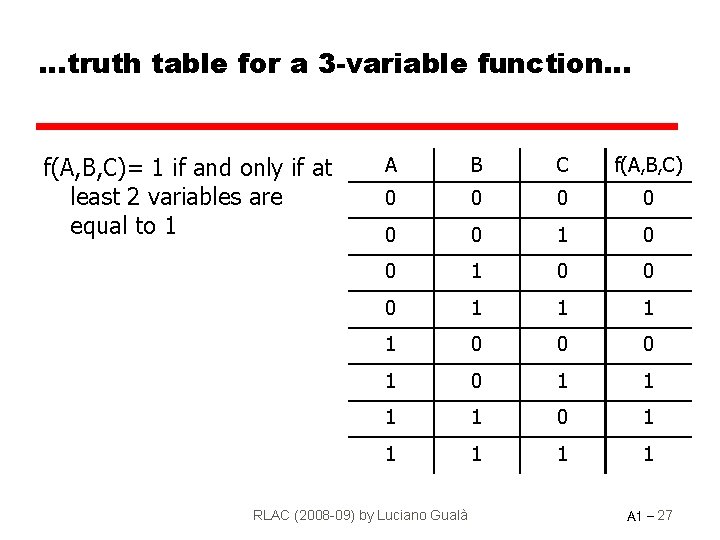

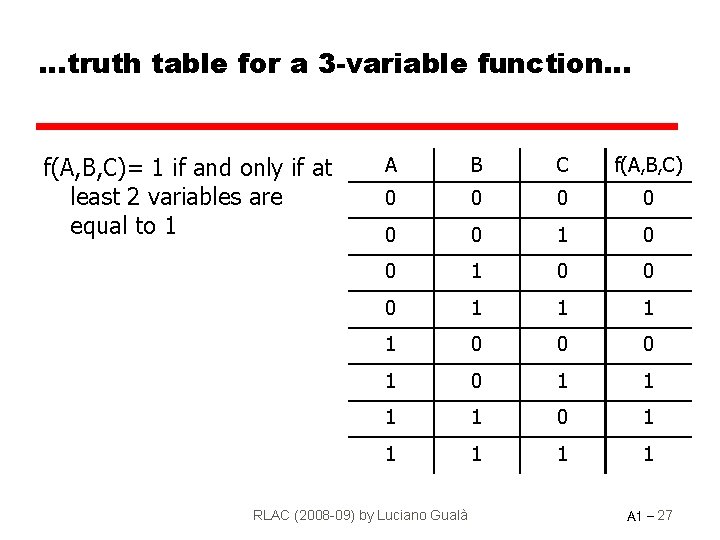

…truth table for a 3 -variable function… f(A, B, C)= 1 if and only if at least 2 variables are equal to 1 A B C f(A, B, C) 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 1 RLAC (2008 -09) by Luciano Gualà A 1 - 27

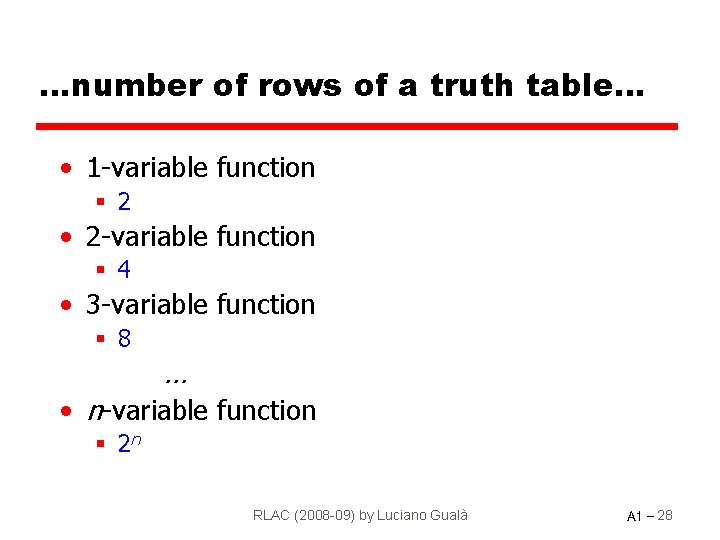

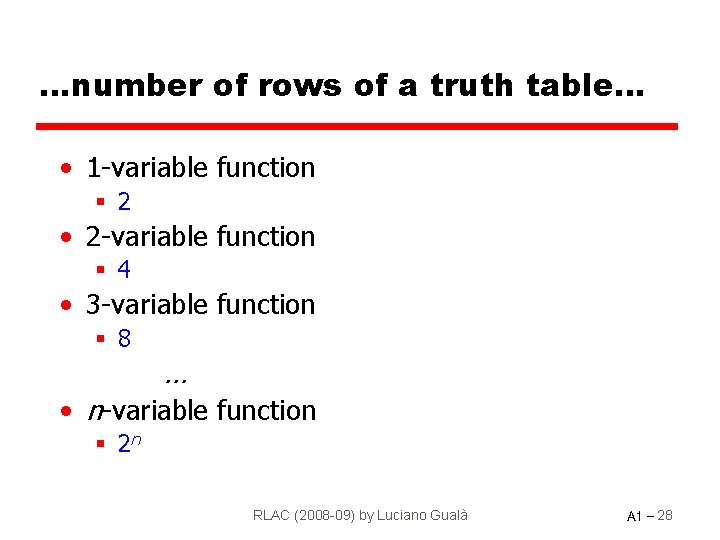

…number of rows of a truth table… • 1 -variable function § 2 • 2 -variable function § 4 • 3 -variable function § 8 … • n-variable function § 2 n RLAC (2008 -09) by Luciano Gualà A 1 - 28

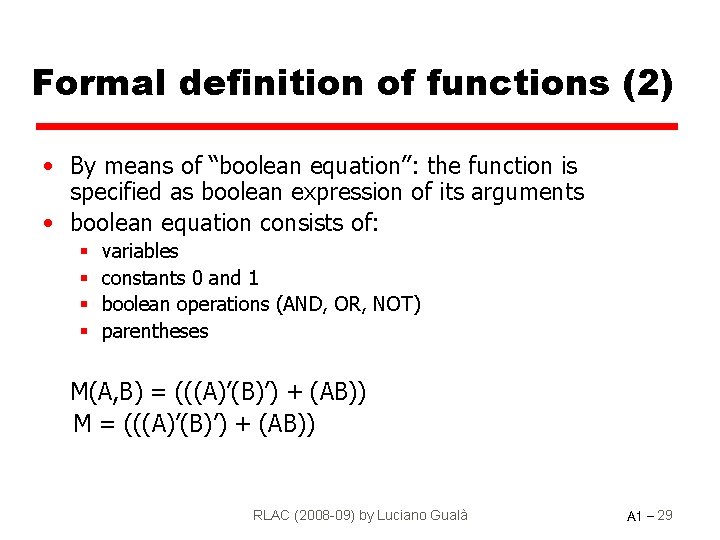

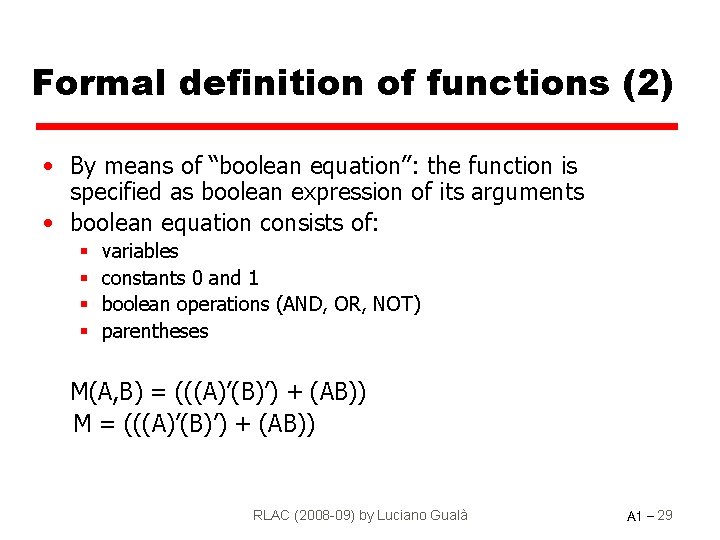

Formal definition of functions (2) • By means of “boolean equation”: the function is specified as boolean expression of its arguments • boolean equation consists of: § § variables constants 0 and 1 boolean operations (AND, OR, NOT) parentheses M(A, B) = (((A)’(B)’) + (AB)) M = (((A)’(B)’) + (AB)) RLAC (2008 -09) by Luciano Gualà A 1 - 29

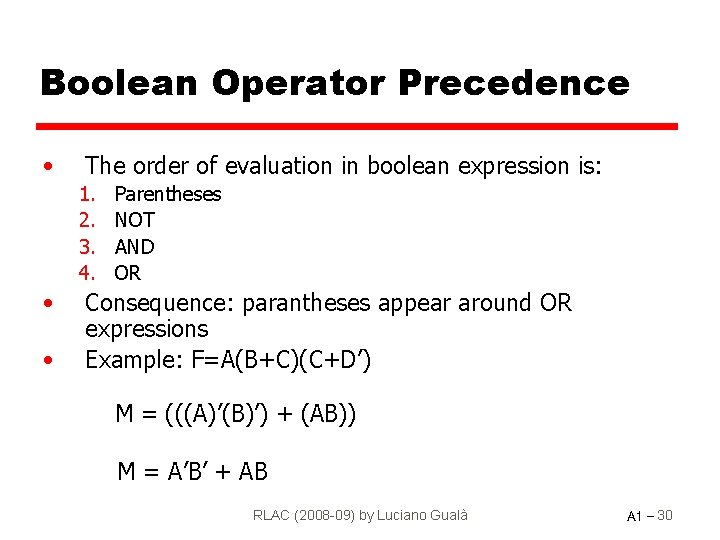

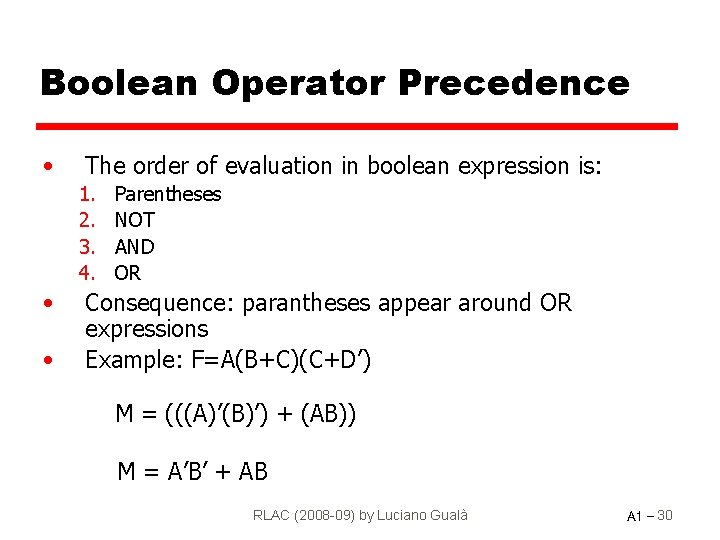

Boolean Operator Precedence • The order of evaluation in boolean expression is: 1. 2. 3. 4. • • Parentheses NOT AND OR Consequence: parantheses appear around OR expressions Example: F=A(B+C)(C+D’) M = (((A)’(B)’) + (AB)) M = A’B’ + AB RLAC (2008 -09) by Luciano Gualà A 1 - 30

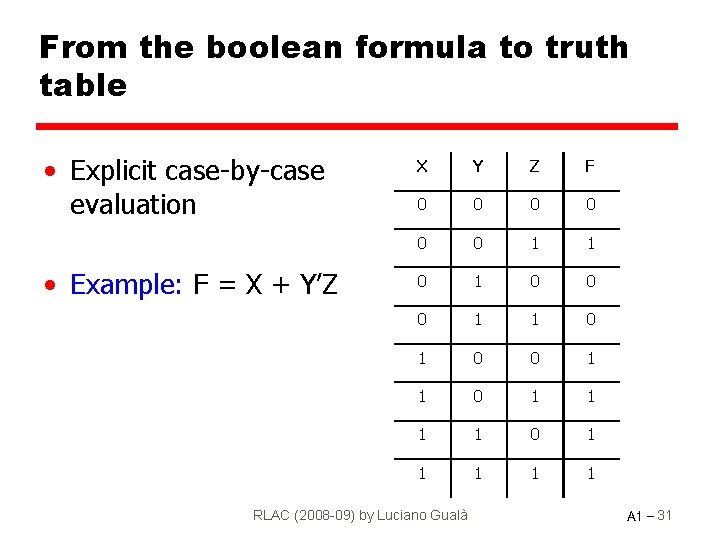

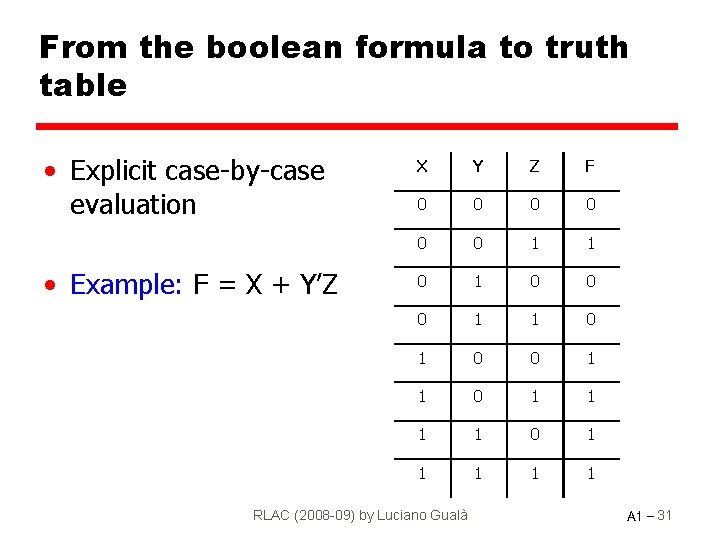

From the boolean formula to truth table • Explicit case-by-case evaluation • Example: F = X + Y’Z X Y Z F 0 0 0 1 1 0 1 1 1 1 0 1 1 1 RLAC (2008 -09) by Luciano Gualà A 1 - 31

Logic gates • A logic gate implements simple boolean operation • basic gates: § AND, OR, NOT • gates are used to build circuits RLAC (2008 -09) by Luciano Gualà A 1 - 32

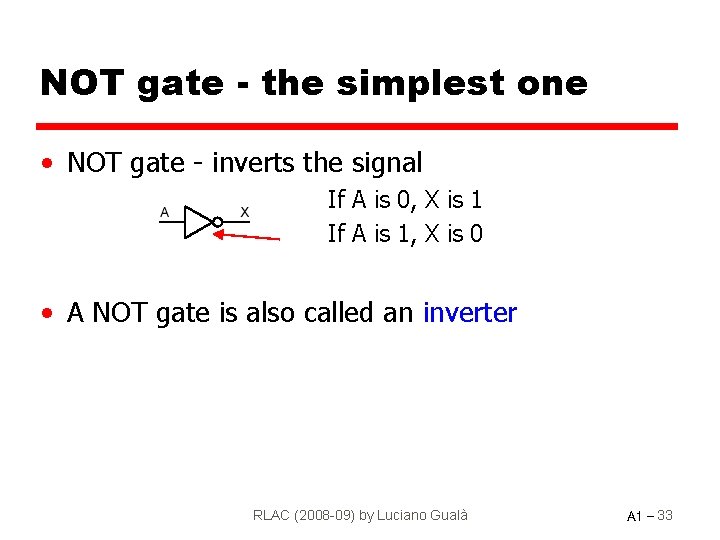

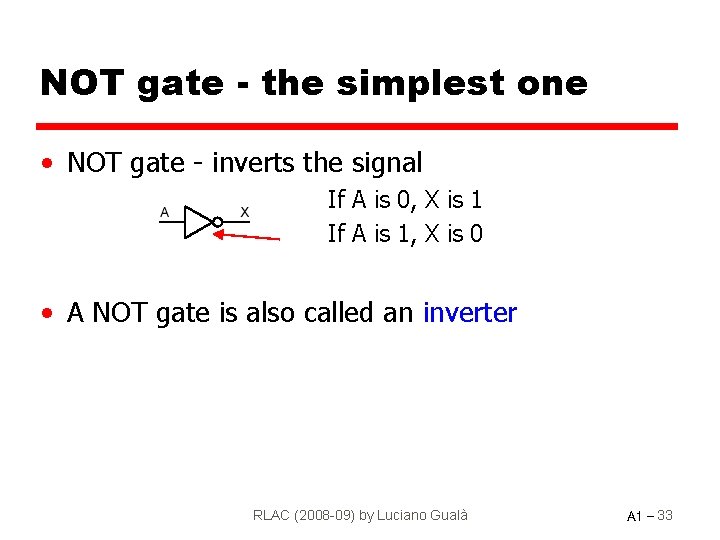

NOT gate - the simplest one • NOT gate - inverts the signal If A is 0, X is 1 If A is 1, X is 0 • A NOT gate is also called an inverter RLAC (2008 -09) by Luciano Gualà A 1 - 33

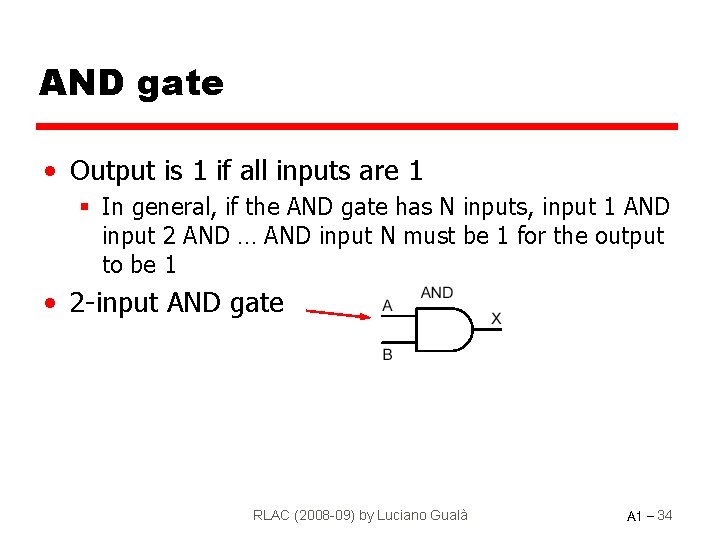

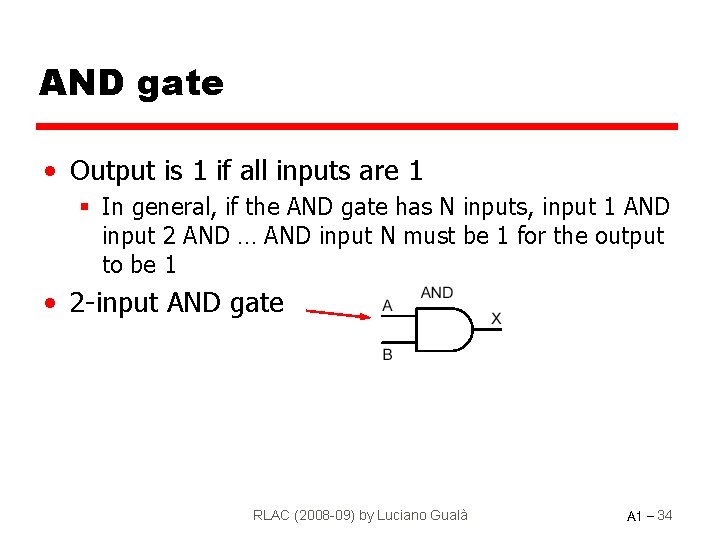

AND gate • Output is 1 if all inputs are 1 § In general, if the AND gate has N inputs, input 1 AND input 2 AND … AND input N must be 1 for the output to be 1 • 2 -input AND gate RLAC (2008 -09) by Luciano Gualà A 1 - 34

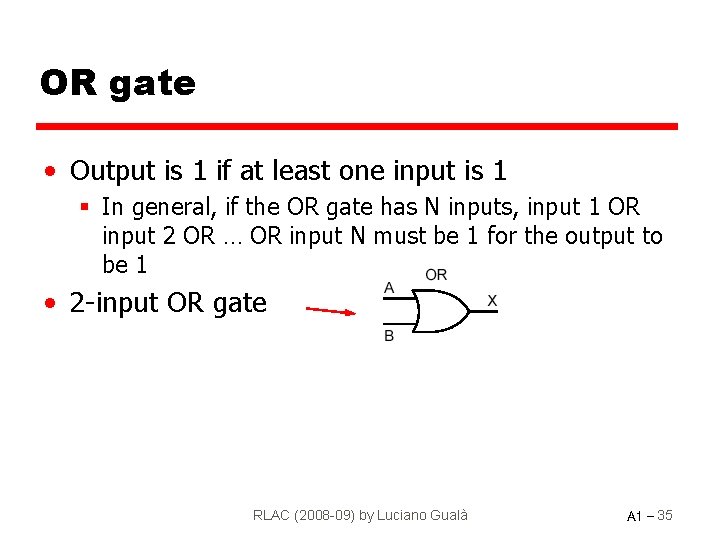

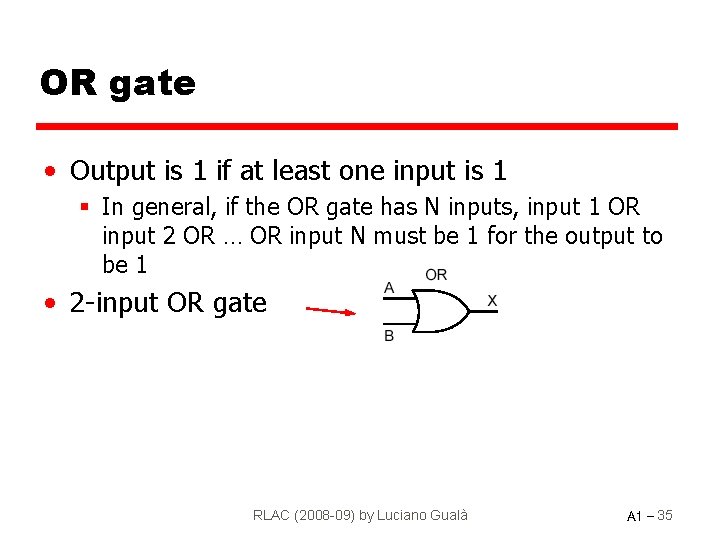

OR gate • Output is 1 if at least one input is 1 § In general, if the OR gate has N inputs, input 1 OR input 2 OR … OR input N must be 1 for the output to be 1 • 2 -input OR gate RLAC (2008 -09) by Luciano Gualà A 1 - 35

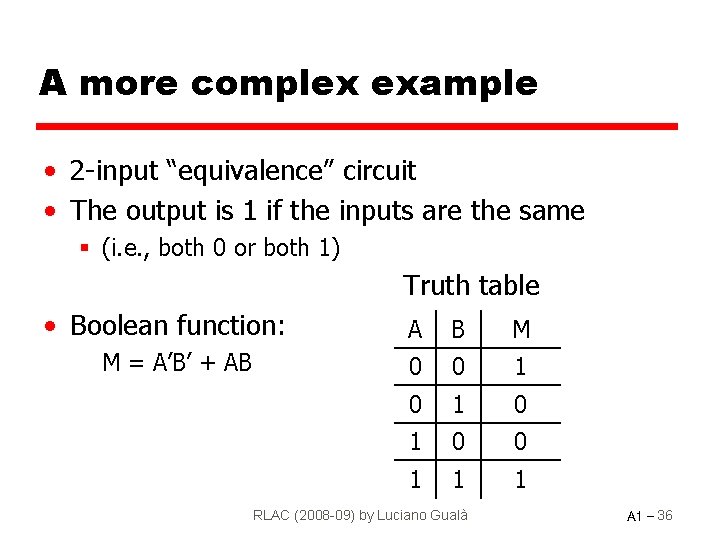

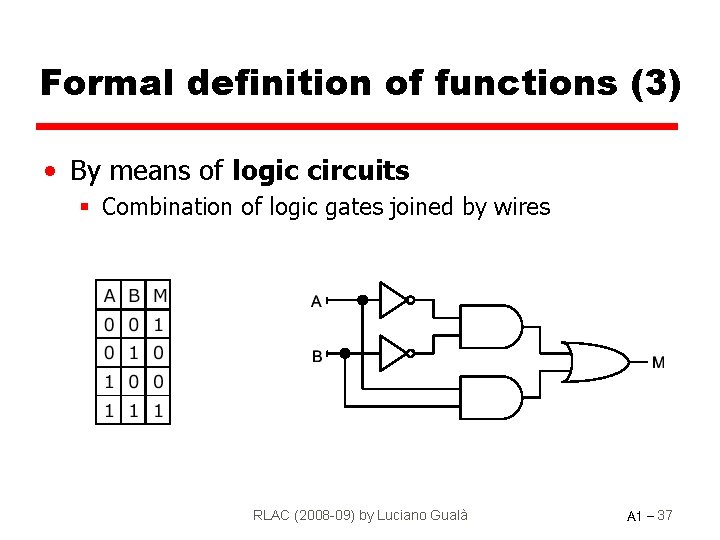

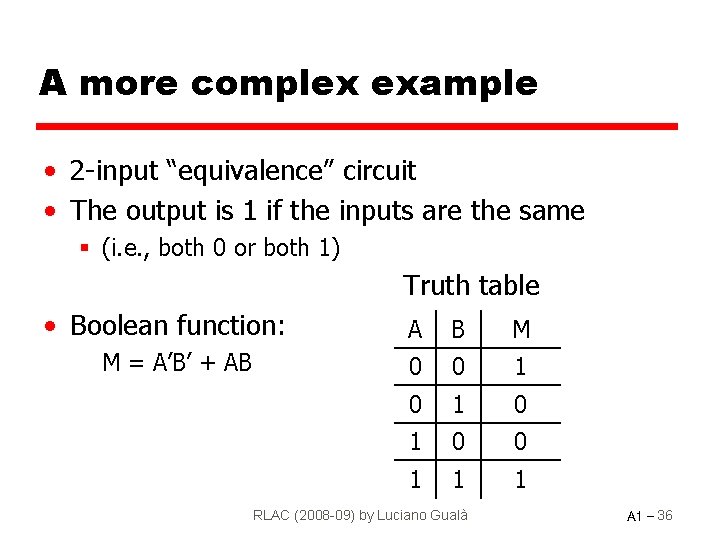

A more complex example • 2 -input “equivalence” circuit • The output is 1 if the inputs are the same § (i. e. , both 0 or both 1) Truth table • Boolean function: M = A’B’ + AB A B M 0 0 1 0 1 0 0 1 1 1 RLAC (2008 -09) by Luciano Gualà A 1 - 36

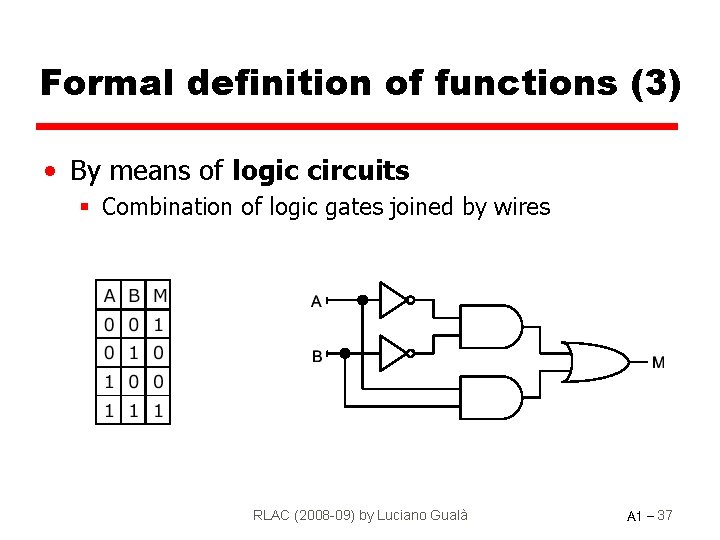

Formal definition of functions (3) • By means of logic circuits § Combination of logic gates joined by wires RLAC (2008 -09) by Luciano Gualà A 1 - 37

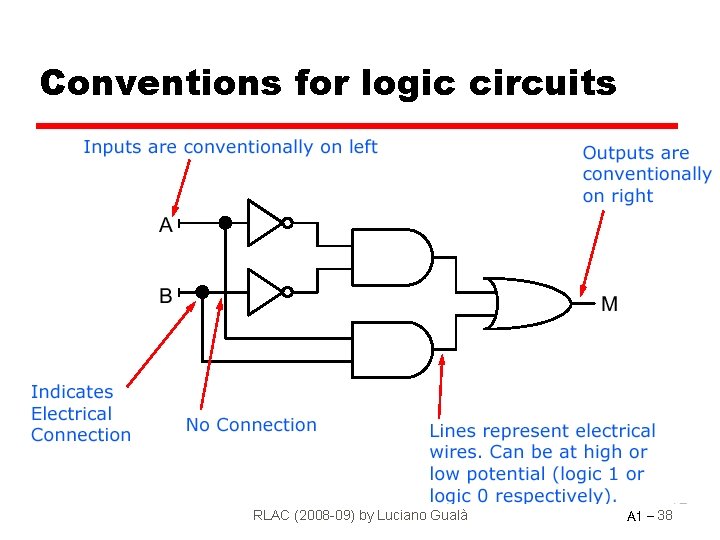

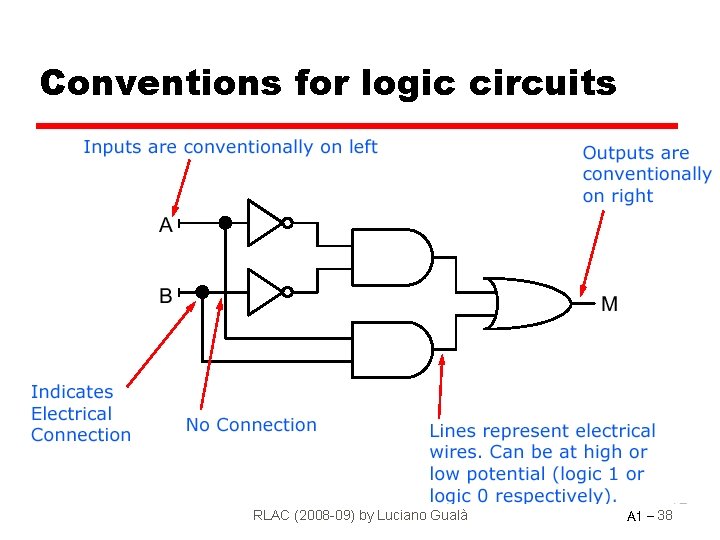

Conventions for logic circuits RLAC (2008 -09) by Luciano Gualà A 1 - 38

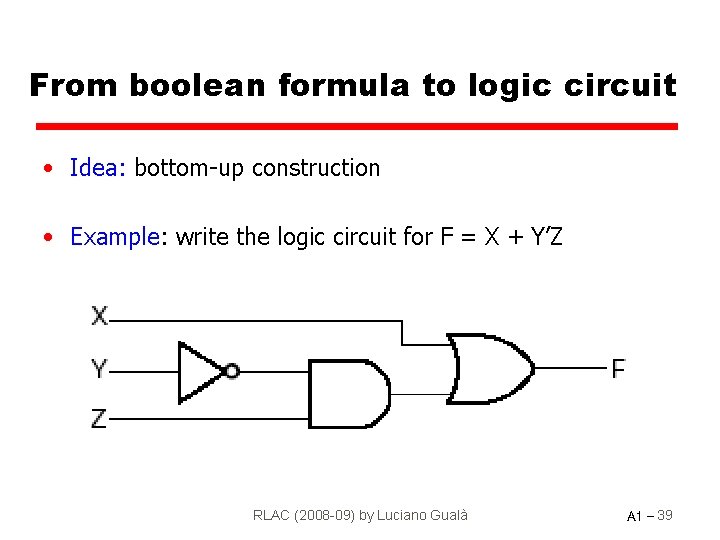

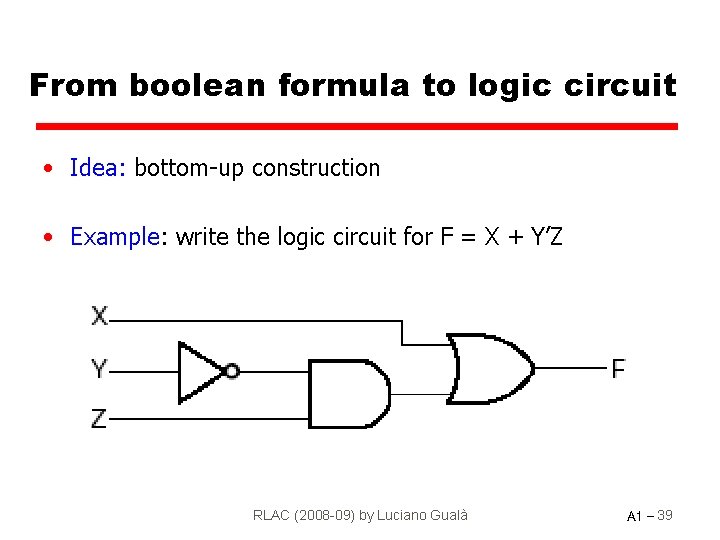

From boolean formula to logic circuit • Idea: bottom-up construction • Example: write the logic circuit for F = X + Y’Z RLAC (2008 -09) by Luciano Gualà A 1 - 39

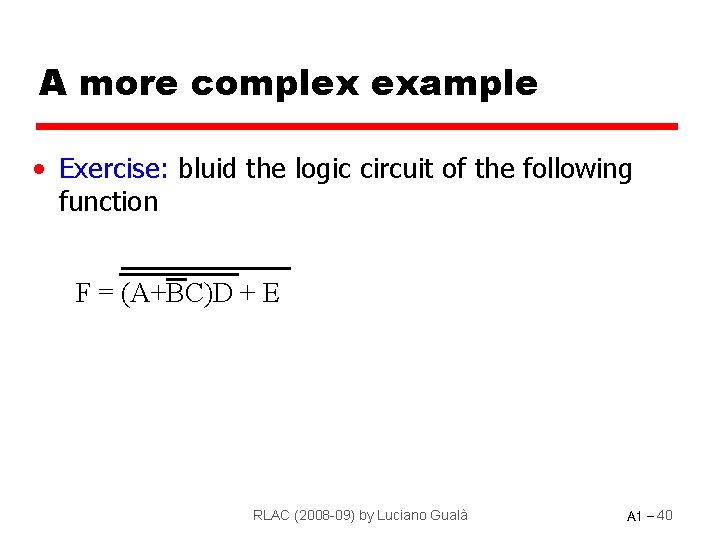

A more complex example • Exercise: bluid the logic circuit of the following function F = (A+BC)D + E RLAC (2008 -09) by Luciano Gualà A 1 - 40

From logic circuit to… • …truth table § explicit case-by-case computation • …boolean formula § left-to-right inspection RLAC (2008 -09) by Luciano Gualà A 1 - 41

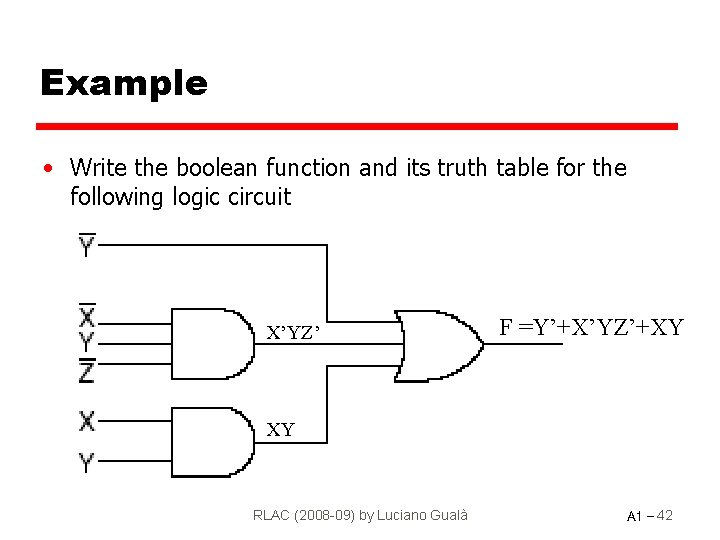

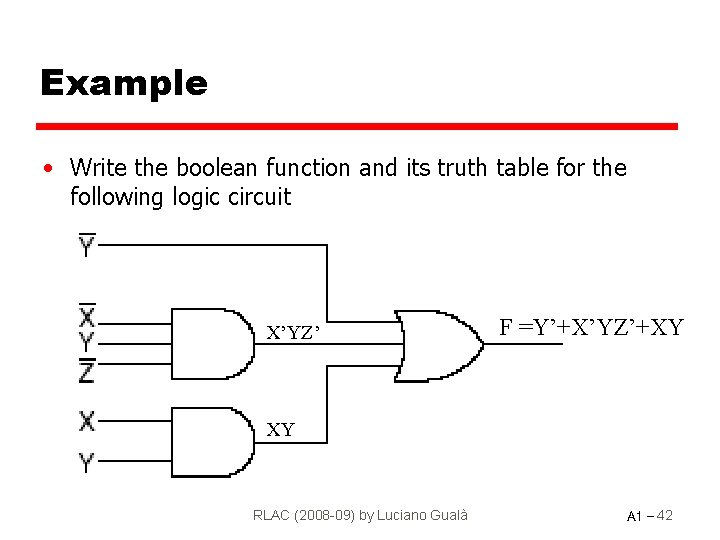

Example • Write the boolean function and its truth table for the following logic circuit X’YZ’ F =Y’+X’YZ’+XY XY RLAC (2008 -09) by Luciano Gualà A 1 - 42

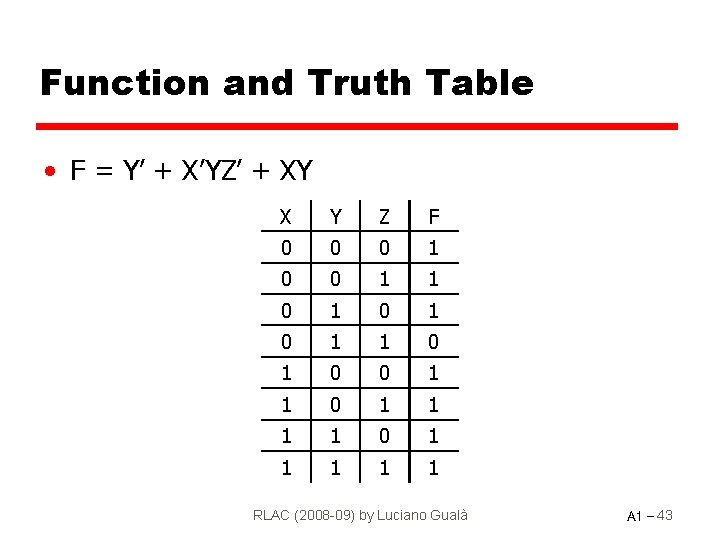

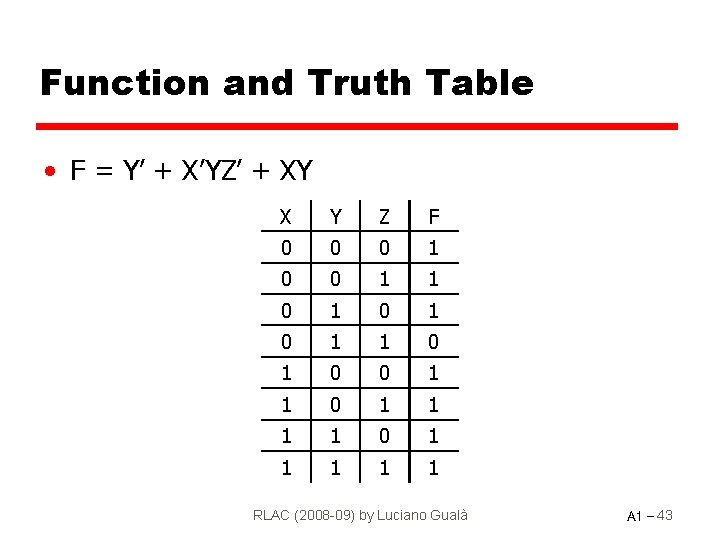

Function and Truth Table • F = Y’ + X’YZ’ + XY X Y Z F 0 0 0 1 1 0 1 0 1 0 0 1 1 1 1 0 1 1 1 RLAC (2008 -09) by Luciano Gualà A 1 - 43

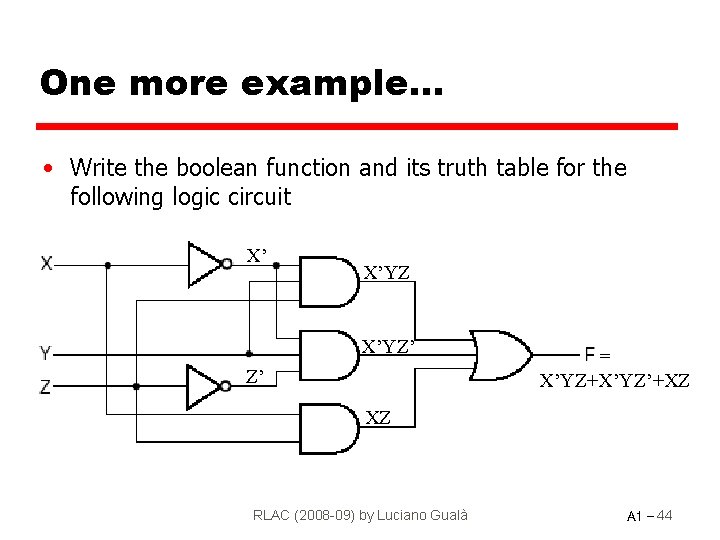

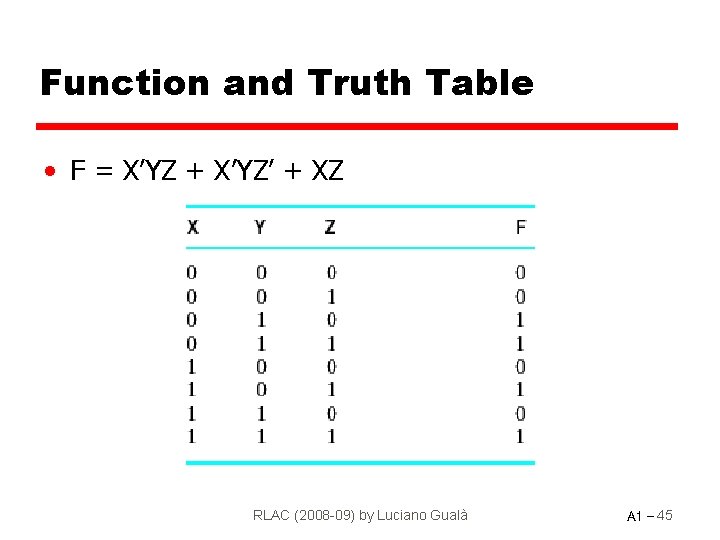

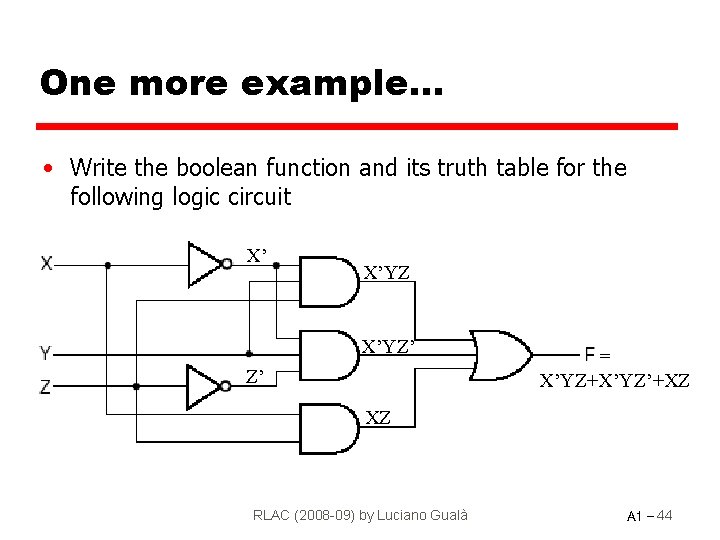

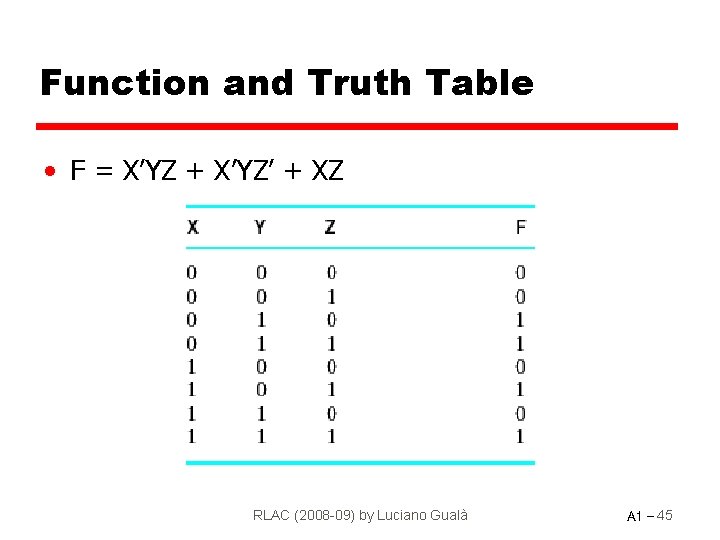

One more example… • Write the boolean function and its truth table for the following logic circuit X’ X’YZ’ Z’ = X’YZ+X’YZ’+XZ XZ RLAC (2008 -09) by Luciano Gualà A 1 - 44

Function and Truth Table • F = X’YZ + X’YZ’ + XZ RLAC (2008 -09) by Luciano Gualà A 1 - 45

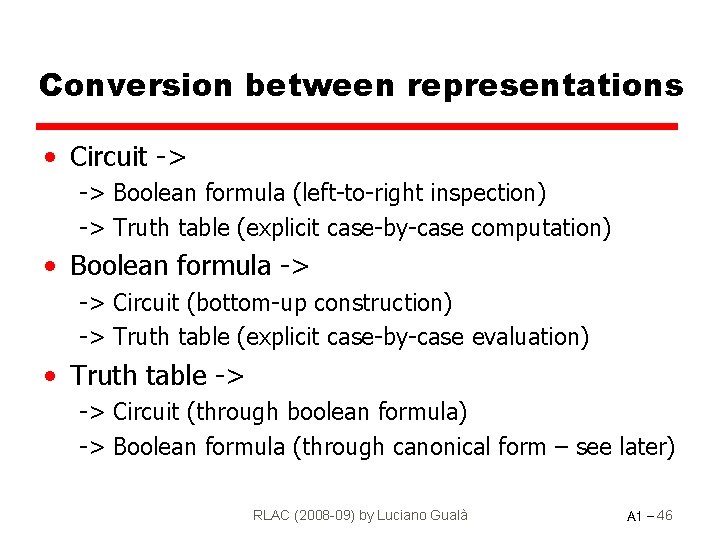

Conversion between representations • Circuit -> -> Boolean formula (left-to-right inspection) -> Truth table (explicit case-by-case computation) • Boolean formula -> -> Circuit (bottom-up construction) -> Truth table (explicit case-by-case evaluation) • Truth table -> -> Circuit (through boolean formula) -> Boolean formula (through canonical form – see later) RLAC (2008 -09) by Luciano Gualà A 1 - 46

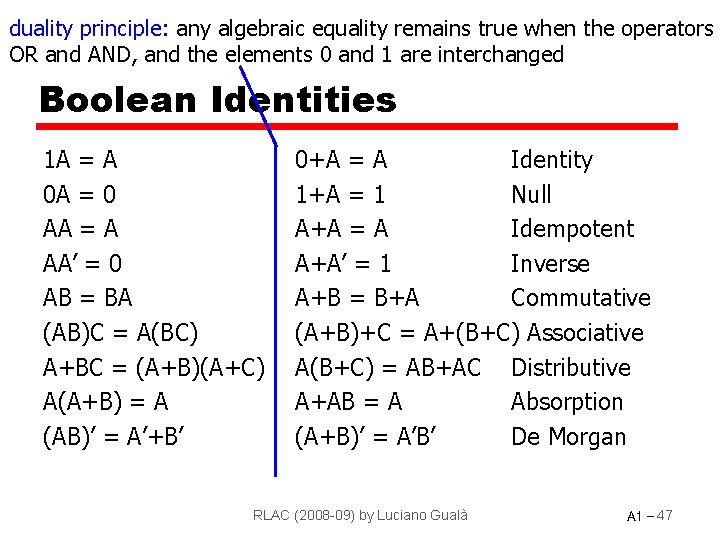

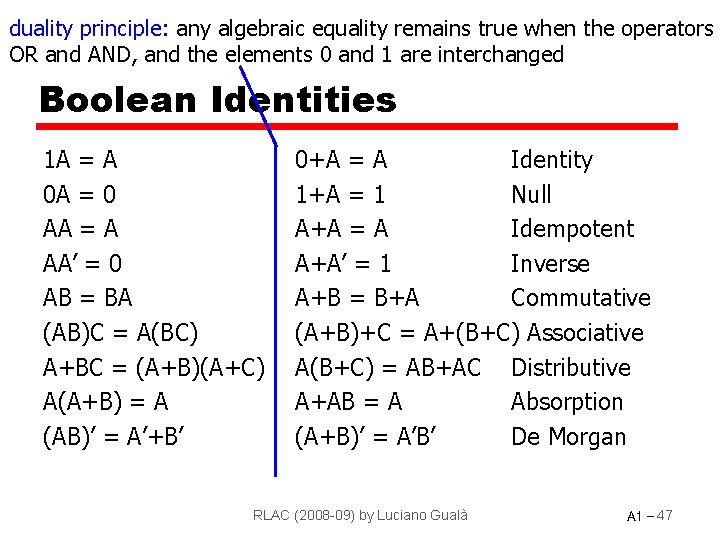

duality principle: any algebraic equality remains true when the operators OR and AND, and the elements 0 and 1 are interchanged Boolean Identities 1 A = A 0 A = 0 AA = A AA’ = 0 AB = BA (AB)C = A(BC) A+BC = (A+B)(A+C) A(A+B) = A (AB)’ = A’+B’ 0+A = A Identity 1+A = 1 Null A+A = A Idempotent A+A’ = 1 Inverse A+B = B+A Commutative (A+B)+C = A+(B+C) Associative A(B+C) = AB+AC Distributive A+AB = A Absorption (A+B)’ = A’B’ De Morgan RLAC (2008 -09) by Luciano Gualà A 1 - 47

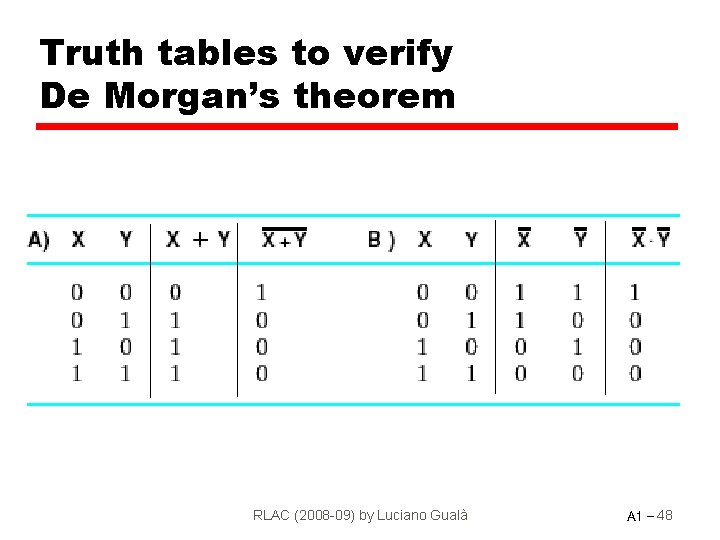

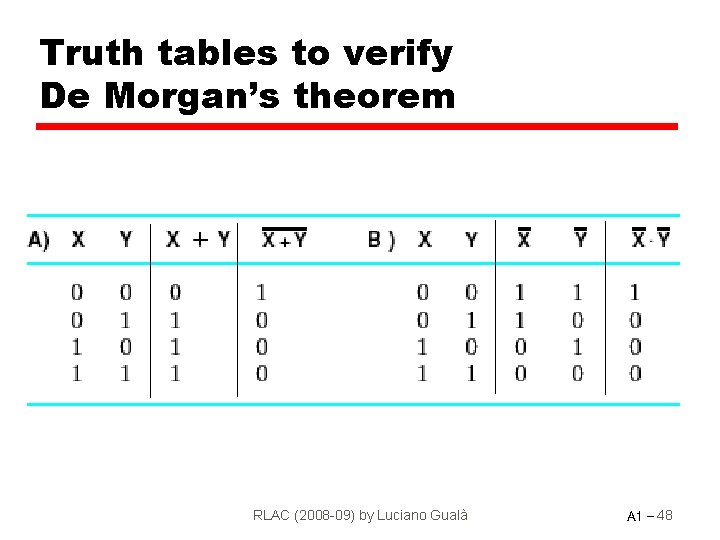

Truth tables to verify De Morgan’s theorem RLAC (2008 -09) by Luciano Gualà A 1 - 48

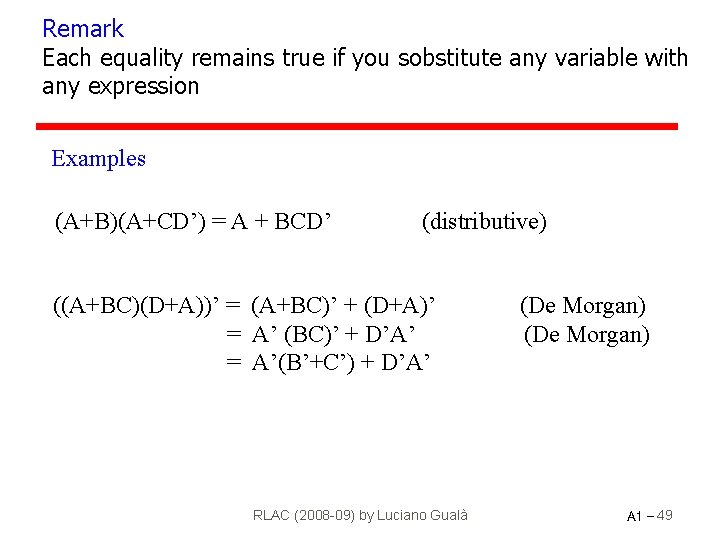

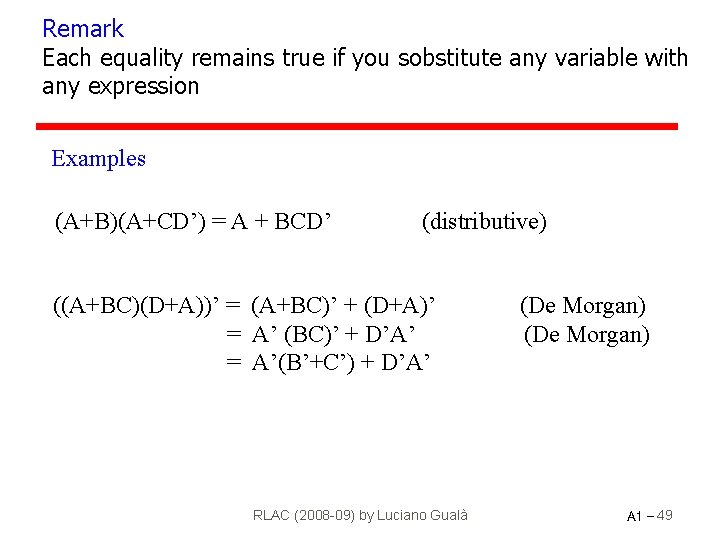

Remark Each equality remains true if you sobstitute any variable with any expression Examples (A+B)(A+CD’) = A + BCD’ (distributive) ((A+BC)(D+A))’ = (A+BC)’ + (D+A)’ = A’ (BC)’ + D’A’ = A’(B’+C’) + D’A’ RLAC (2008 -09) by Luciano Gualà (De Morgan) A 1 - 49

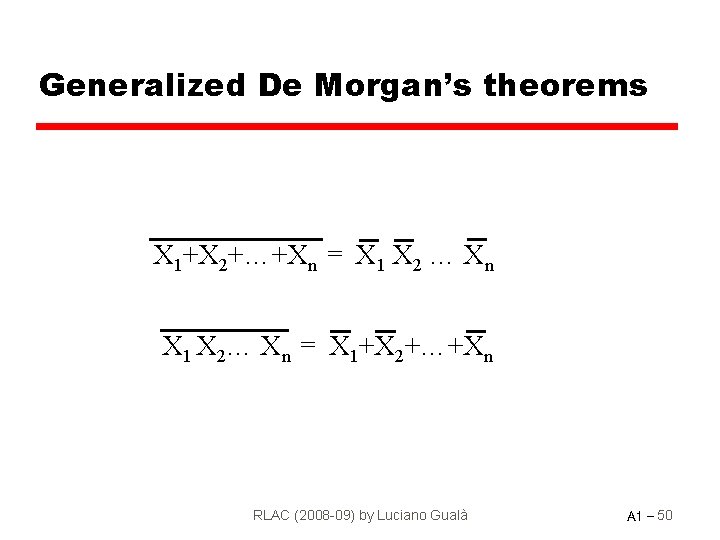

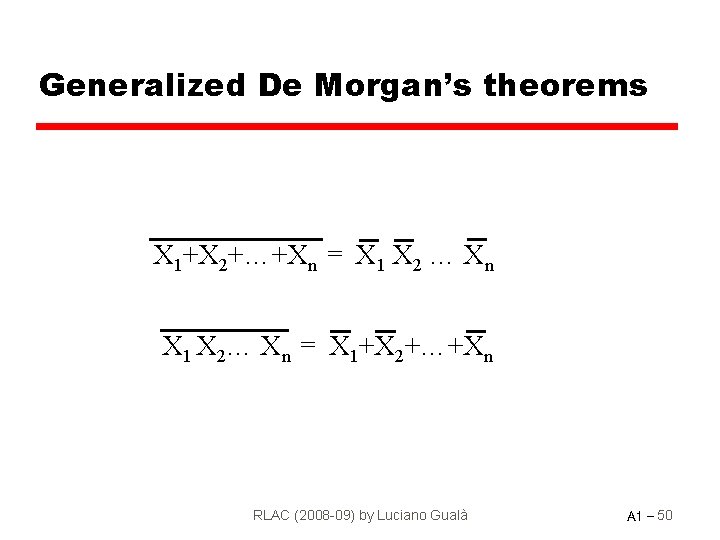

Generalized De Morgan’s theorems X 1+X 2+…+Xn = X 1 X 2 … Xn X 1 X 2… Xn = X 1+X 2+…+Xn RLAC (2008 -09) by Luciano Gualà A 1 - 50

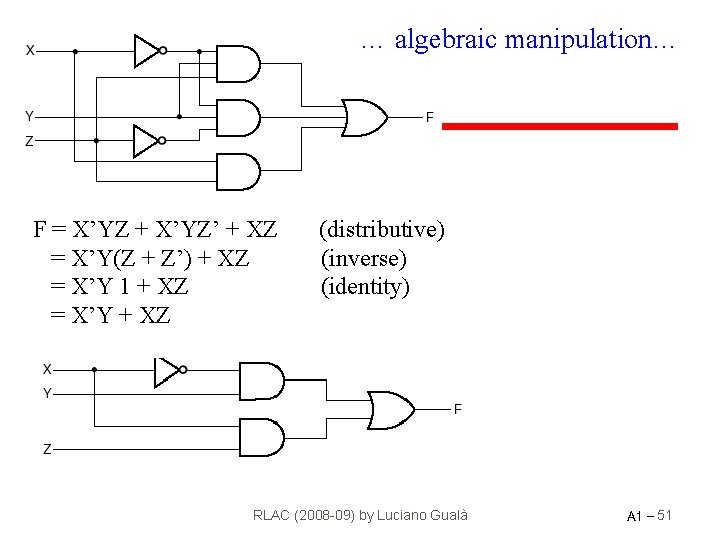

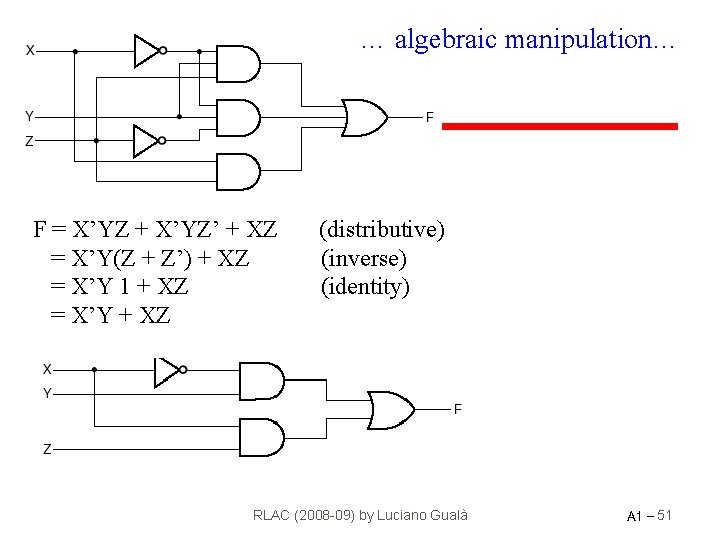

… algebraic manipulation… F = X’YZ + X’YZ’ + XZ = X’Y(Z + Z’) + XZ = X’Y 1 + XZ = X’Y + XZ (distributive) (inverse) (identity) RLAC (2008 -09) by Luciano Gualà A 1 - 51

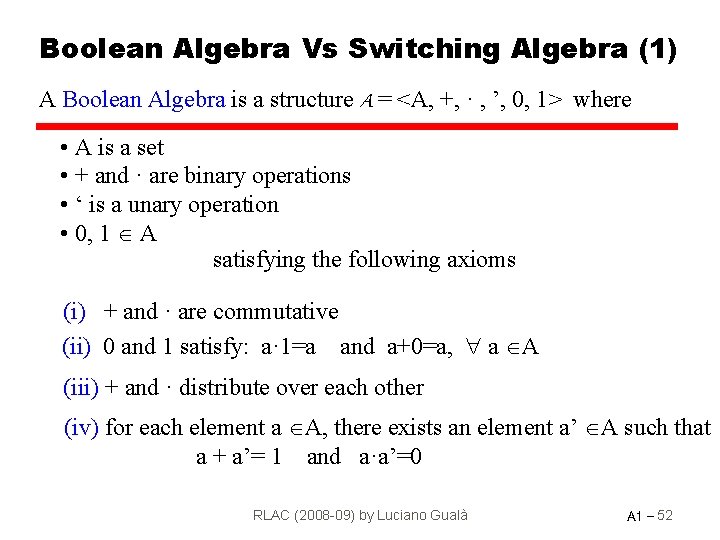

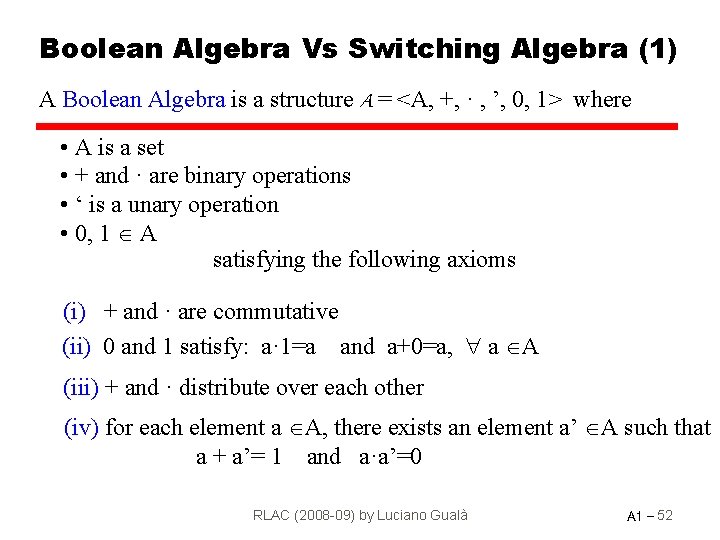

Boolean Algebra Vs Switching Algebra (1) A Boolean Algebra is a structure A = <A, +, · , ’, 0, 1> where • A is a set • + and · are binary operations • ‘ is a unary operation • 0, 1 A satisfying the following axioms (i) + and · are commutative (ii) 0 and 1 satisfy: a· 1=a and a+0=a, a A (iii) + and · distribute over each other (iv) for each element a A, there exists an element a’ A such that a + a’= 1 and a·a’=0 RLAC (2008 -09) by Luciano Gualà A 1 - 52

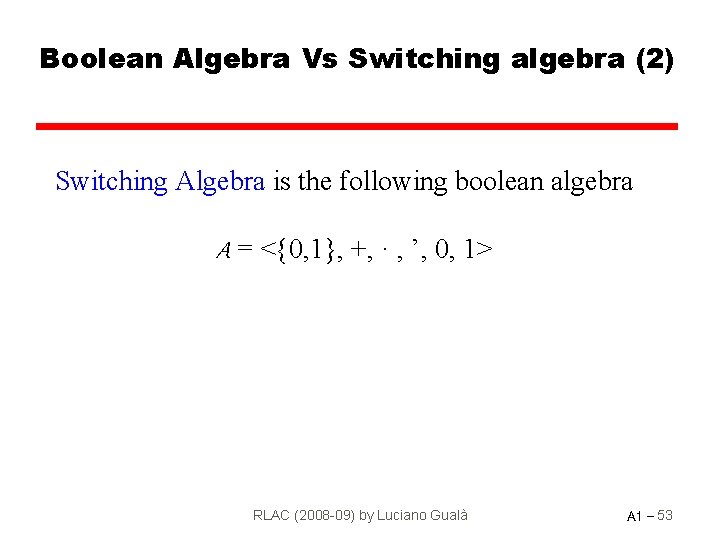

Boolean Algebra Vs Switching algebra (2) Switching Algebra is the following boolean algebra A = <{0, 1}, +, · , ’, 0, 1> RLAC (2008 -09) by Luciano Gualà A 1 - 53

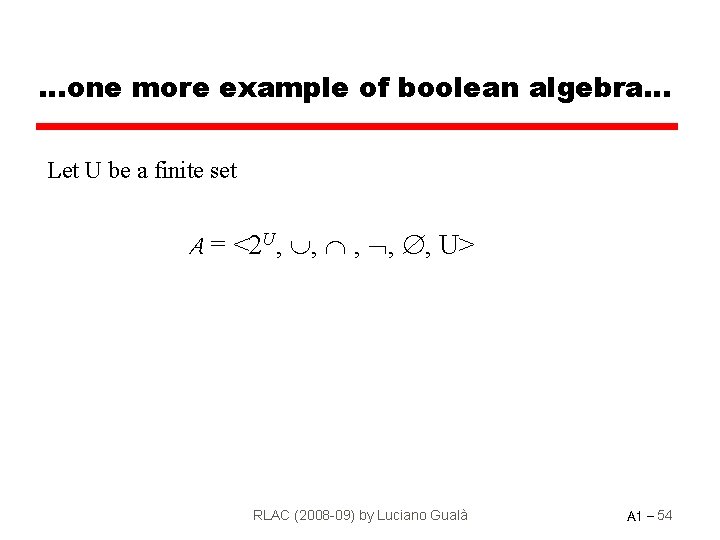

…one more example of boolean algebra… Let U be a finite set A = <2 U, , , U> RLAC (2008 -09) by Luciano Gualà A 1 - 54

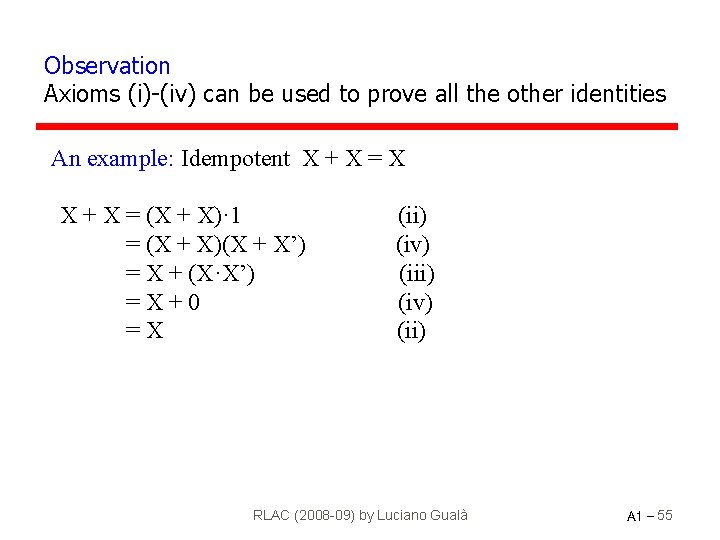

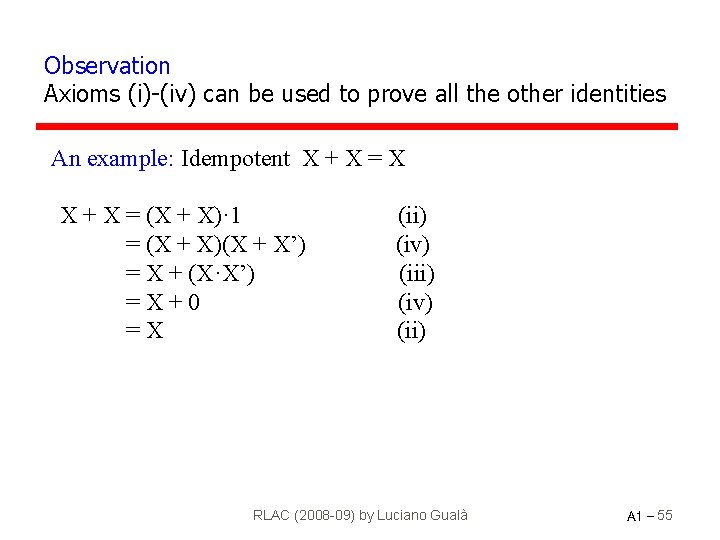

Observation Axioms (i)-(iv) can be used to prove all the other identities An example: Idempotent X + X = X X + X = (X + X)· 1 = (X + X)(X + X’) = X + (X·X’) =X+0 =X (ii) (iv) (ii) RLAC (2008 -09) by Luciano Gualà A 1 - 55

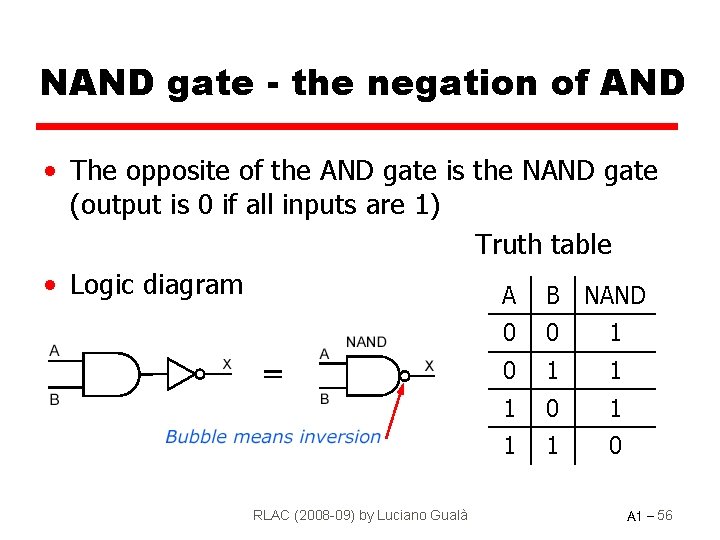

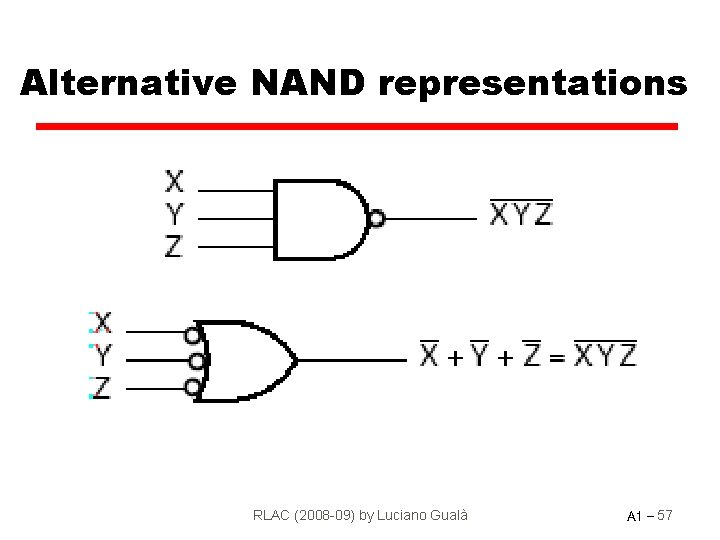

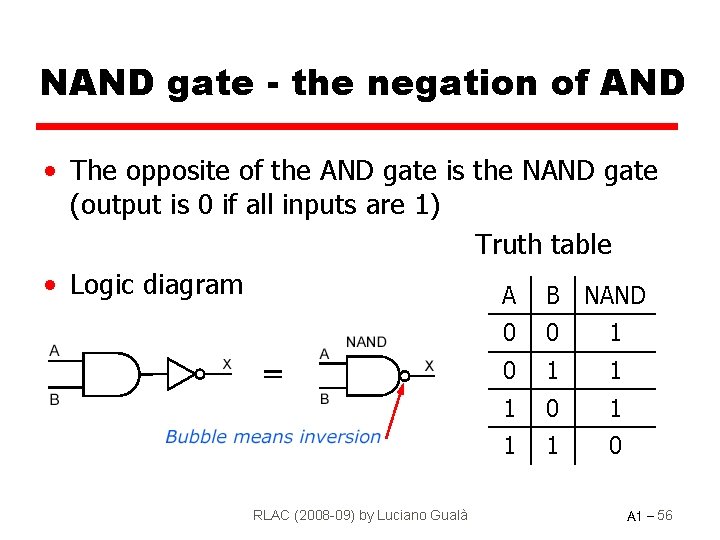

NAND gate - the negation of AND • The opposite of the AND gate is the NAND gate (output is 0 if all inputs are 1) Truth table • Logic diagram A B NAND RLAC (2008 -09) by Luciano Gualà 0 0 1 1 1 0 A 1 - 56

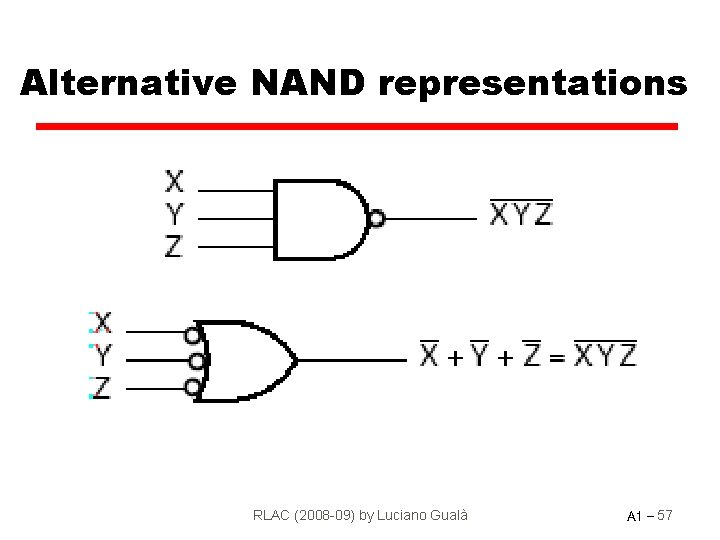

Alternative NAND representations RLAC (2008 -09) by Luciano Gualà A 1 - 57

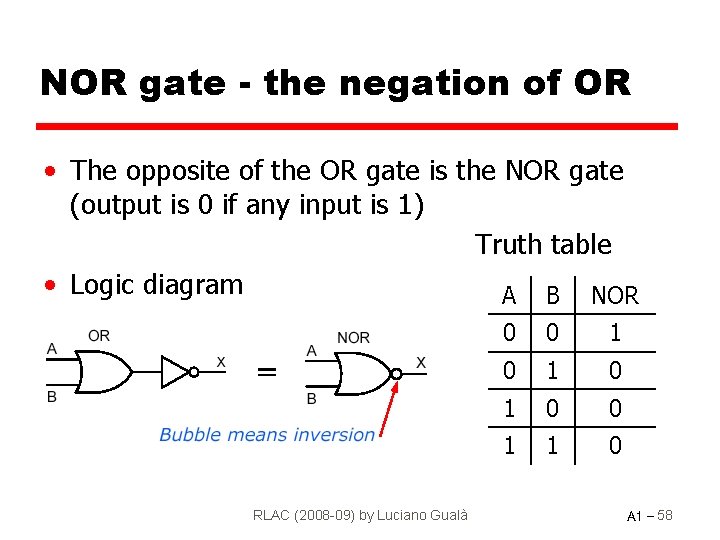

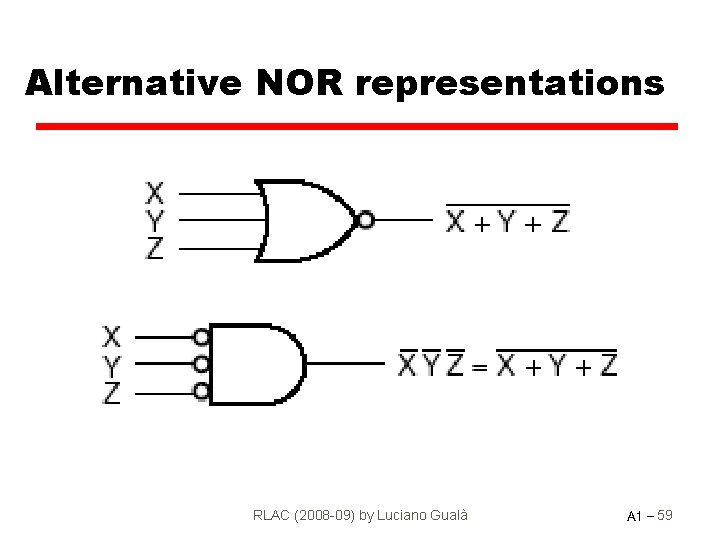

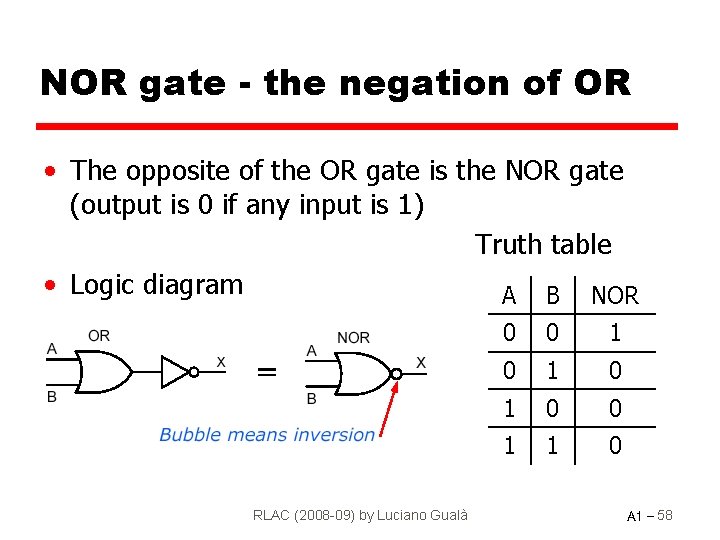

NOR gate - the negation of OR • The opposite of the OR gate is the NOR gate (output is 0 if any input is 1) Truth table • Logic diagram A B NOR RLAC (2008 -09) by Luciano Gualà 0 0 1 0 1 0 0 1 1 0 A 1 - 58

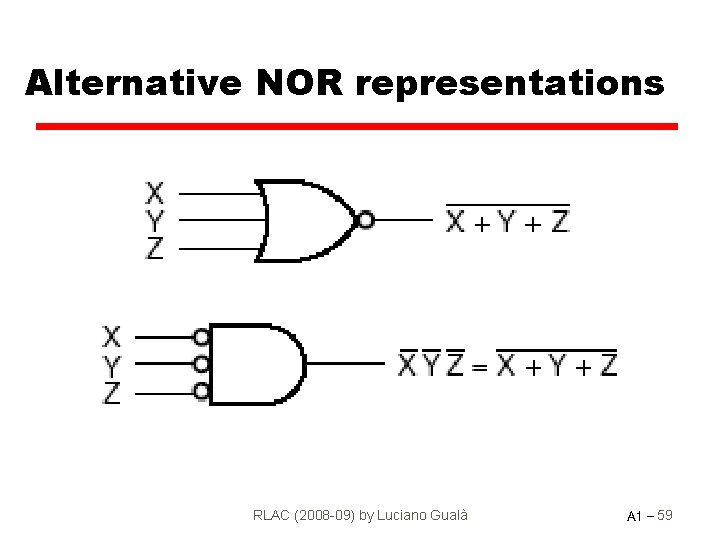

Alternative NOR representations RLAC (2008 -09) by Luciano Gualà A 1 - 59

Exercise • Write the truth table for: § a 3 input NAND gate § a 3 input NOR gate RLAC (2008 -09) by Luciano Gualà A 1 - 60

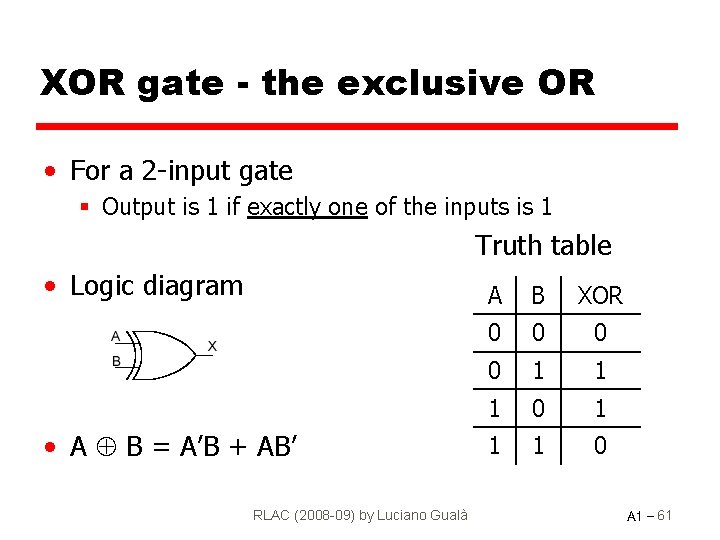

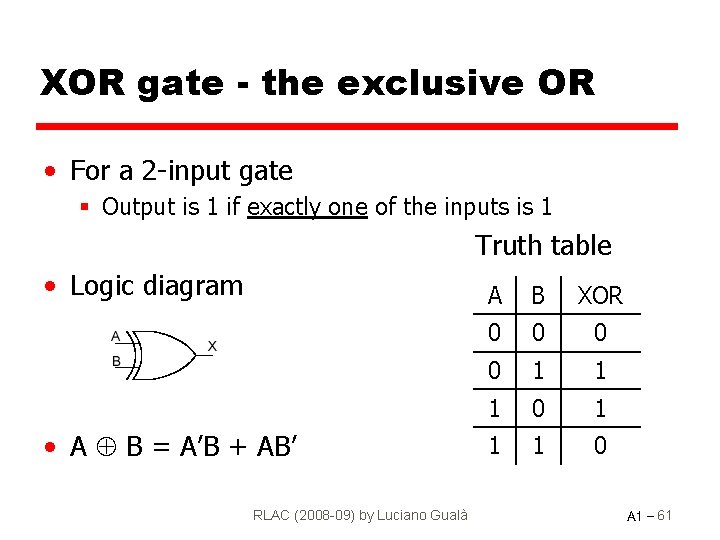

XOR gate - the exclusive OR • For a 2 -input gate § Output is 1 if exactly one of the inputs is 1 Truth table • Logic diagram • A B = A’B + AB’ RLAC (2008 -09) by Luciano Gualà A B XOR 0 0 1 1 1 0 A 1 - 61

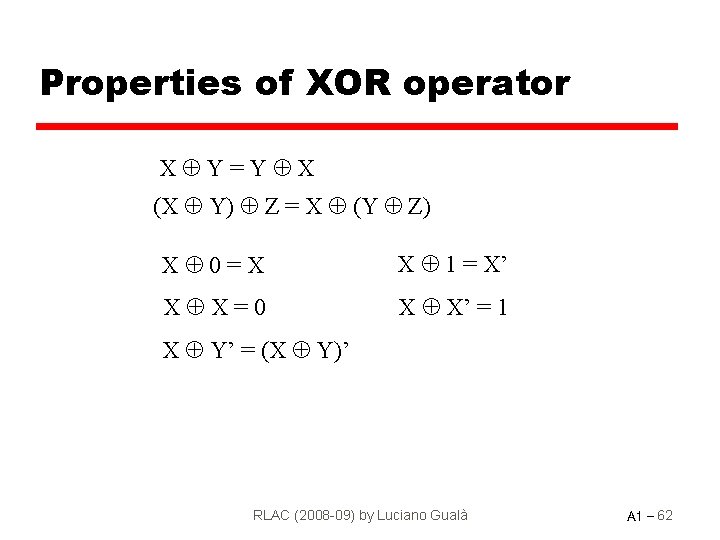

Properties of XOR operator X Y=Y X (X Y) Z = X (Y Z) X 0=X X 1 = X’ X X=0 X X’ = 1 X Y’ = (X Y)’ RLAC (2008 -09) by Luciano Gualà A 1 - 62

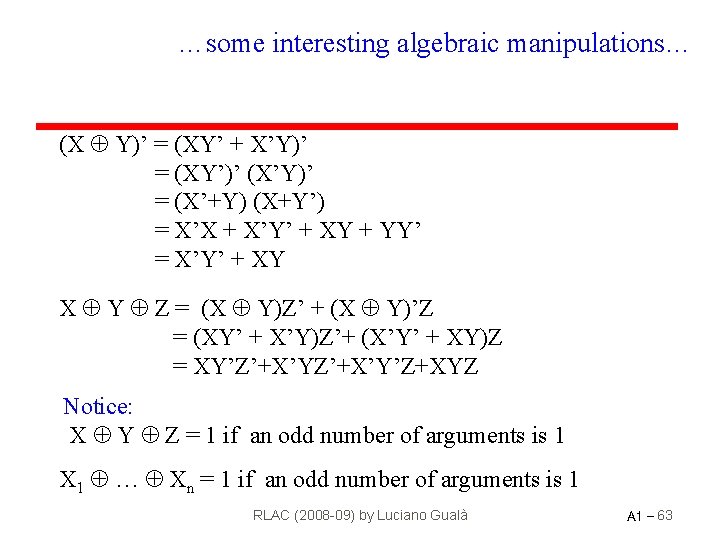

…some interesting algebraic manipulations… (X Y)’ = (XY’ + X’Y)’ = (XY’)’ (X’Y)’ = (X’+Y) (X+Y’) = X’X + X’Y’ + XY + YY’ = X’Y’ + XY X Y Z = (X Y)Z’ + (X Y)’Z = (XY’ + X’Y)Z’+ (X’Y’ + XY)Z = XY’Z’+X’Y’Z+XYZ Notice: X Y Z = 1 if an odd number of arguments is 1 X 1 … Xn = 1 if an odd number of arguments is 1 RLAC (2008 -09) by Luciano Gualà A 1 - 63

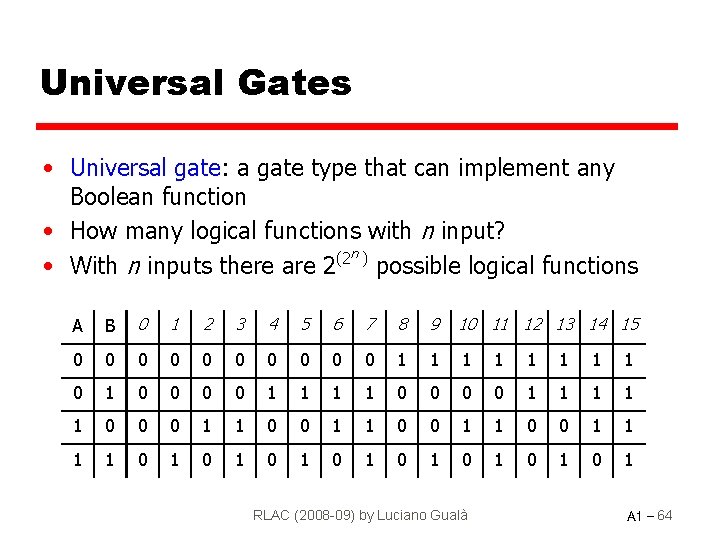

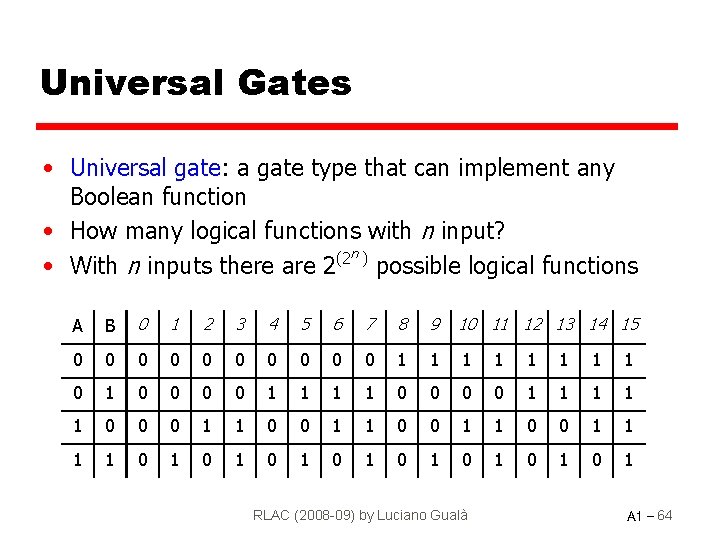

Universal Gates • Universal gate: a gate type that can implement any Boolean function • How many logical functions with n input? (2 n ) • With n inputs there are 2 possible logical functions A B 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 0 0 1 1 1 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 1 0 1 0 1 RLAC (2008 -09) by Luciano Gualà A 1 - 64

Universal Gates (2) • AND, OR, NOT can generate all possible boolean functions (see later) • Is it possible to use fewer basic operations? • AND, NOT are enough ! • OR, NOT are enough ! • Even NAND alone or NOR alone are enough ! RLAC (2008 -09) by Luciano Gualà A 1 - 65

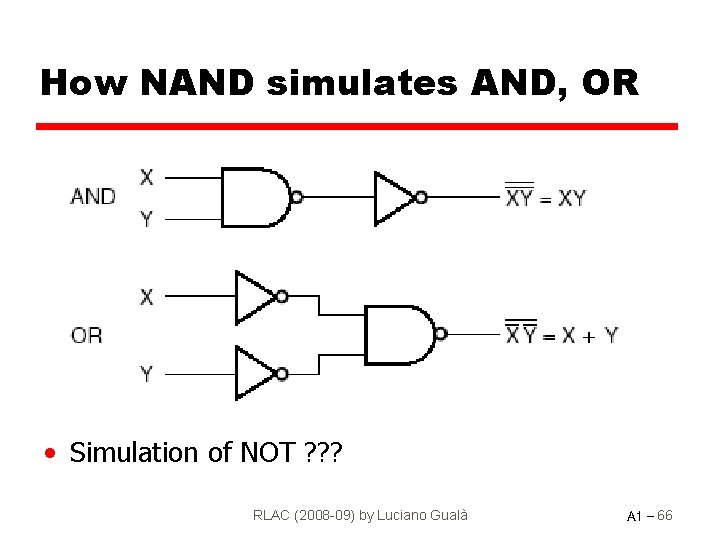

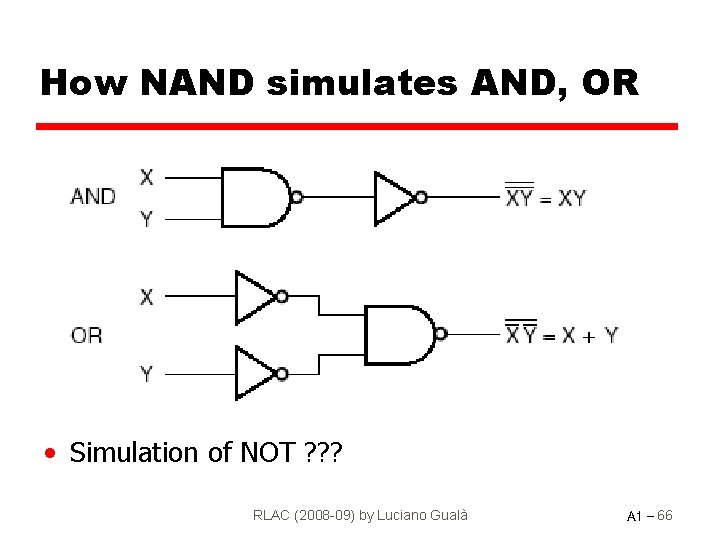

How NAND simulates AND, OR • Simulation of NOT ? ? ? RLAC (2008 -09) by Luciano Gualà A 1 - 66

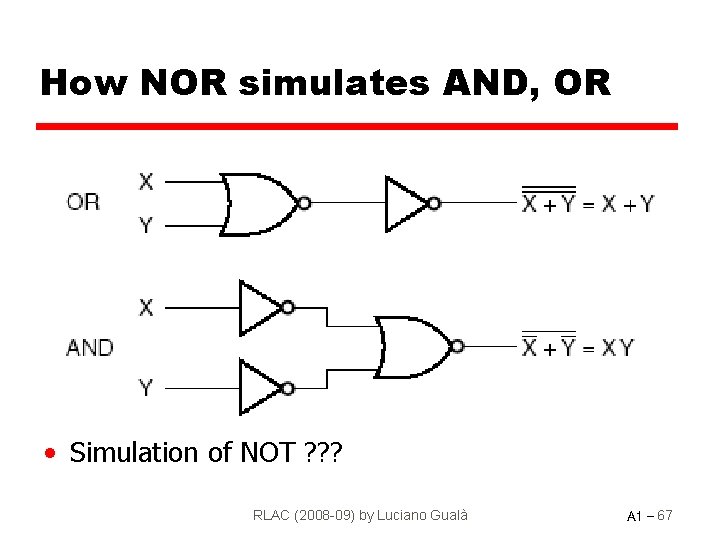

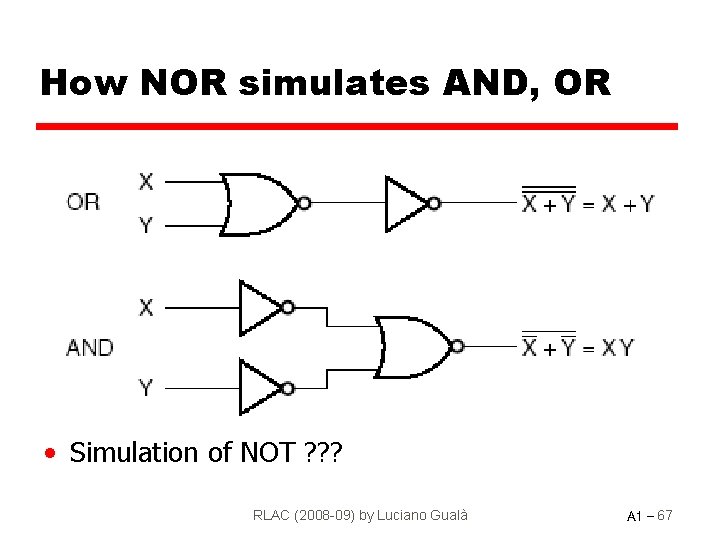

How NOR simulates AND, OR • Simulation of NOT ? ? ? RLAC (2008 -09) by Luciano Gualà A 1 - 67

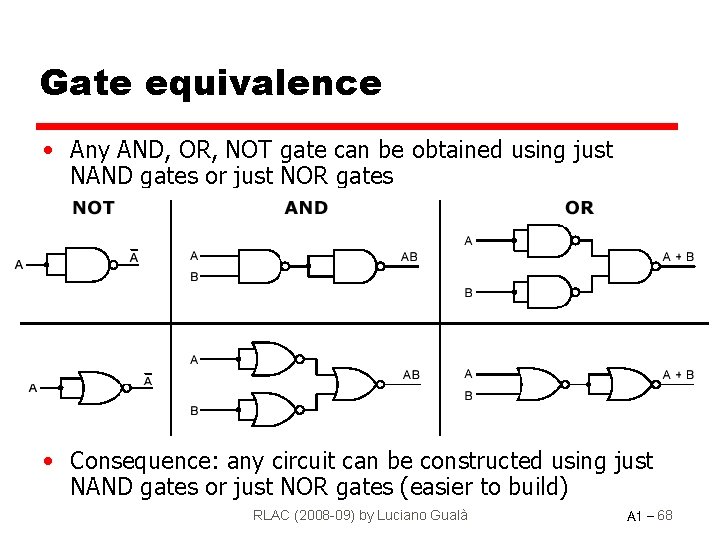

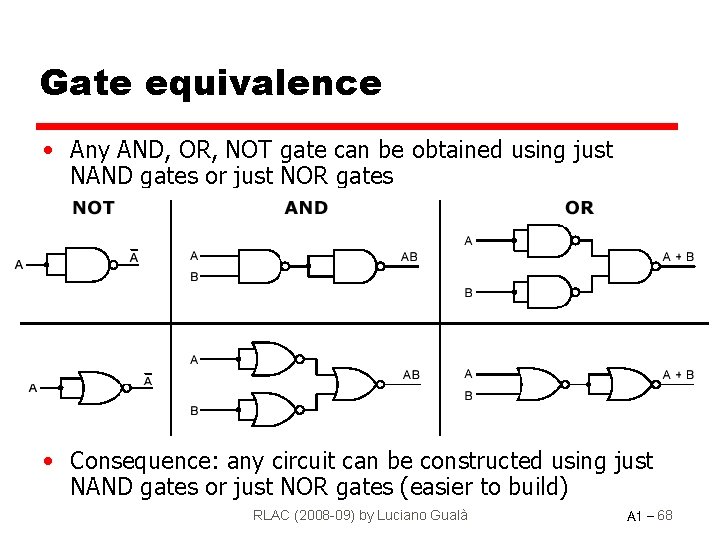

Gate equivalence • Any AND, OR, NOT gate can be obtained using just NAND gates or just NOR gates • Consequence: any circuit can be constructed using just NAND gates or just NOR gates (easier to build) RLAC (2008 -09) by Luciano Gualà A 1 - 68

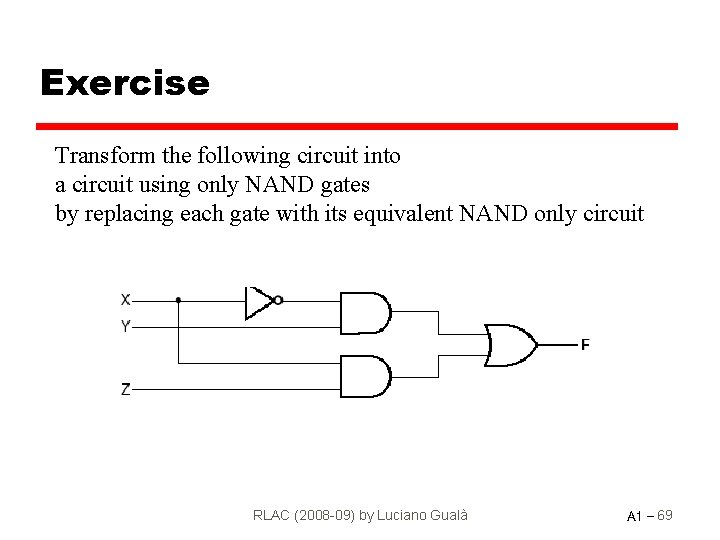

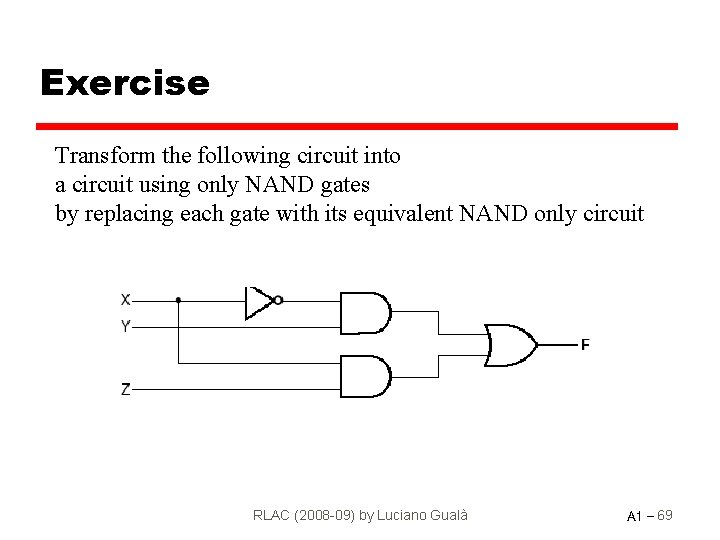

Exercise Transform the following circuit into a circuit using only NAND gates by replacing each gate with its equivalent NAND only circuit RLAC (2008 -09) by Luciano Gualà A 1 - 69

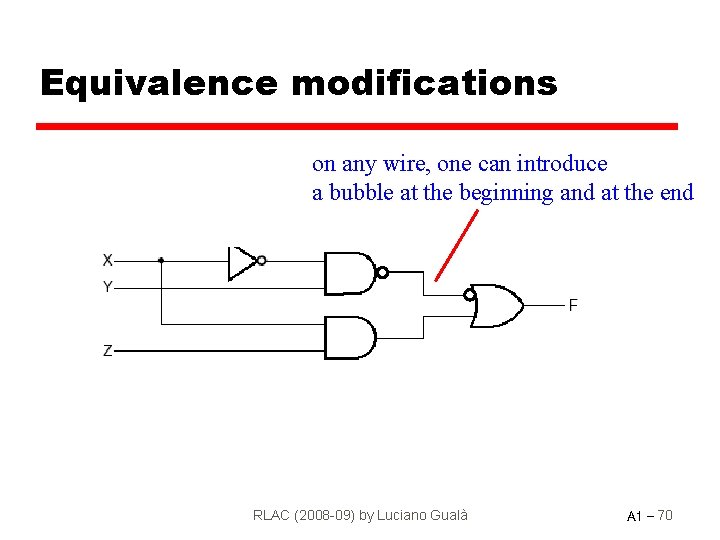

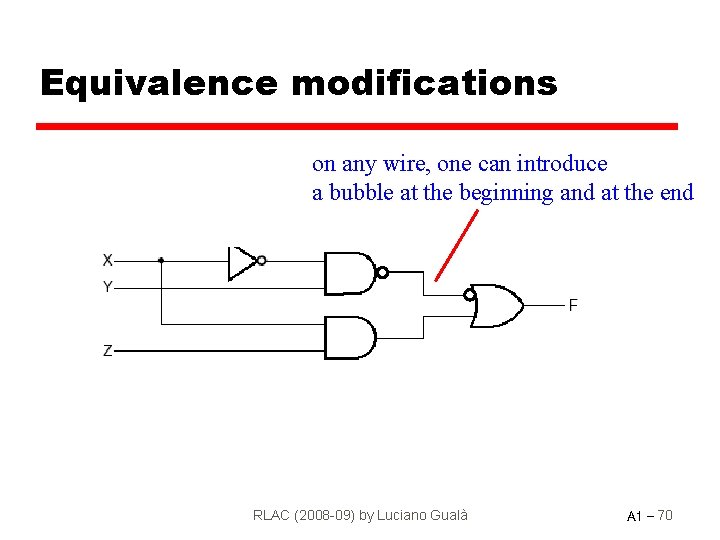

Equivalence modifications on any wire, one can introduce a bubble at the beginning and at the end RLAC (2008 -09) by Luciano Gualà A 1 - 70

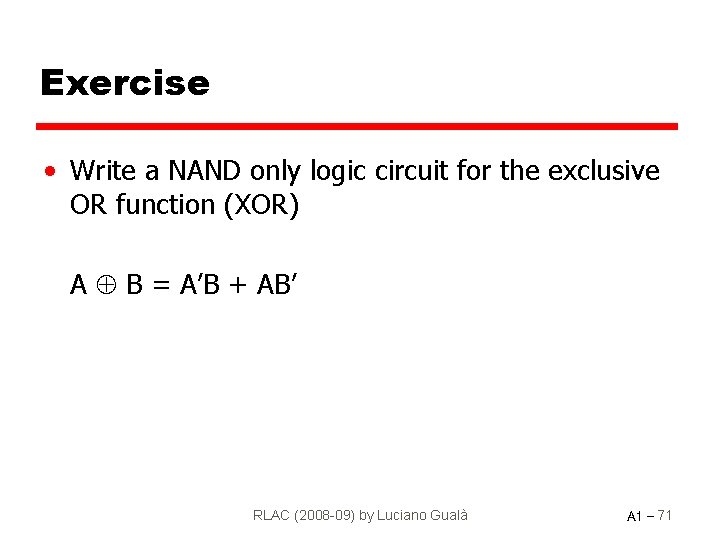

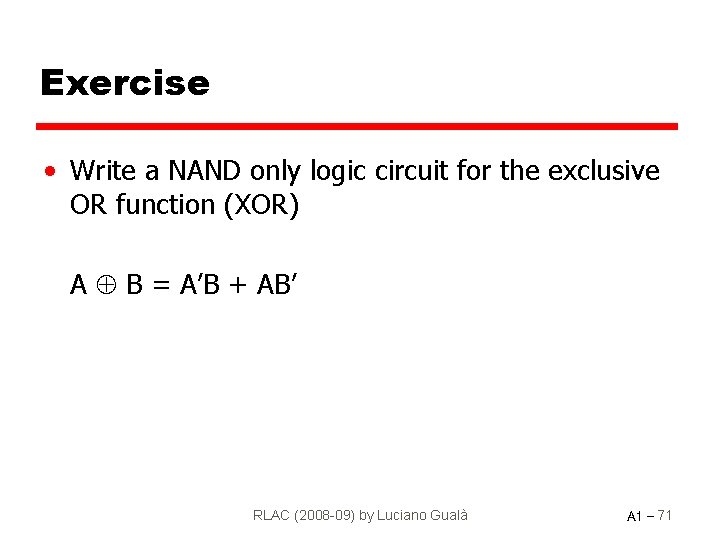

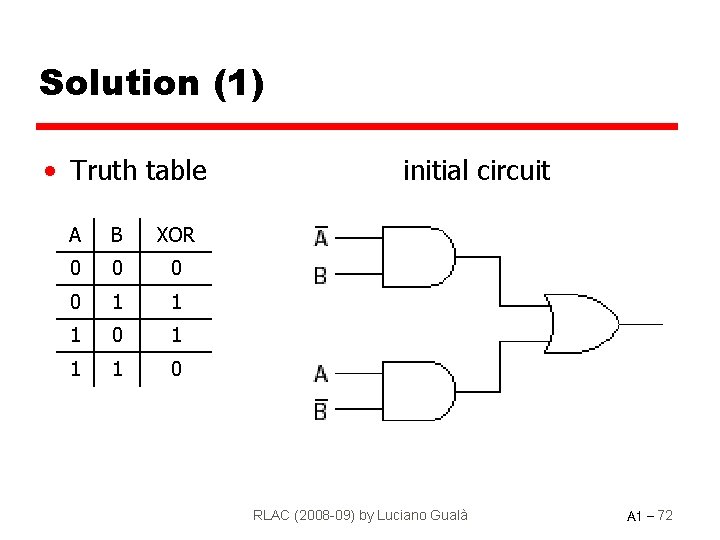

Exercise • Write a NAND only logic circuit for the exclusive OR function (XOR) A B = A’B + AB’ RLAC (2008 -09) by Luciano Gualà A 1 - 71

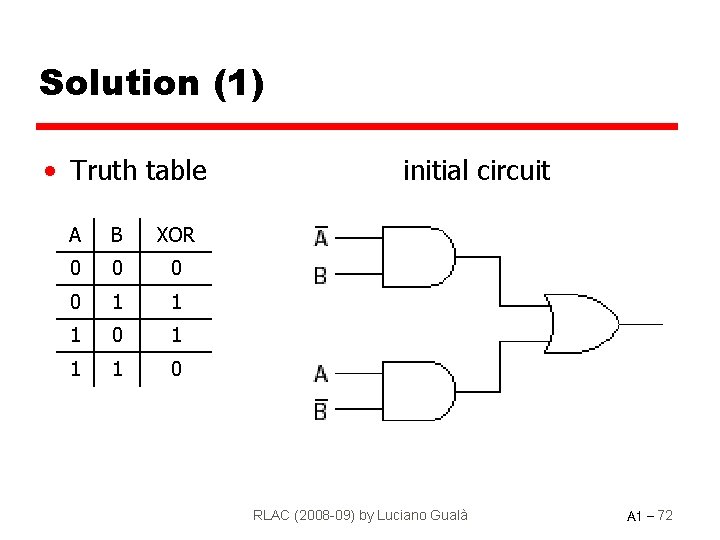

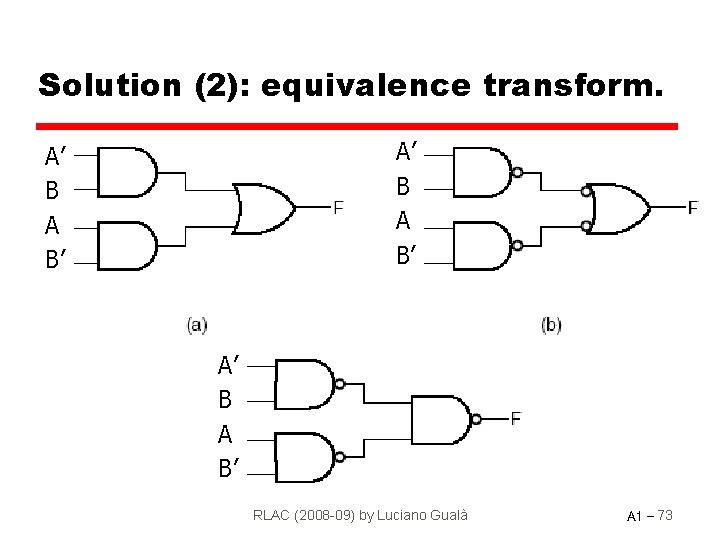

Solution (1) • Truth table A B XOR 0 0 1 1 1 0 initial circuit RLAC (2008 -09) by Luciano Gualà A 1 - 72

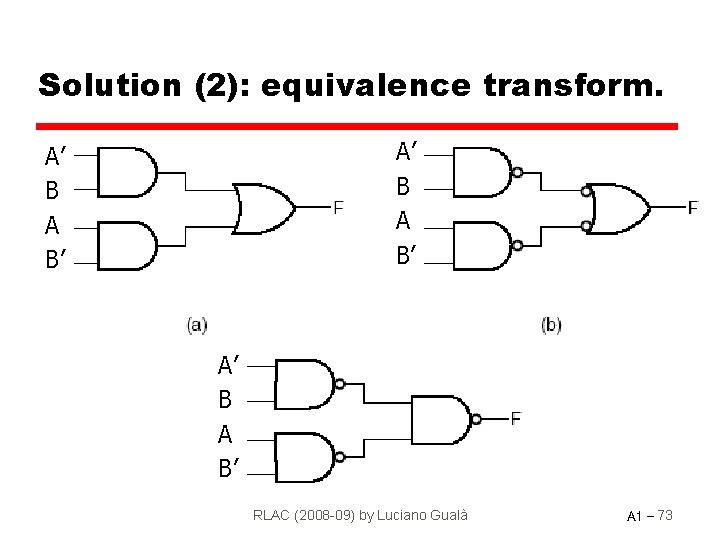

Solution (2): equivalence transform. A’ B A B’ RLAC (2008 -09) by Luciano Gualà A 1 - 73

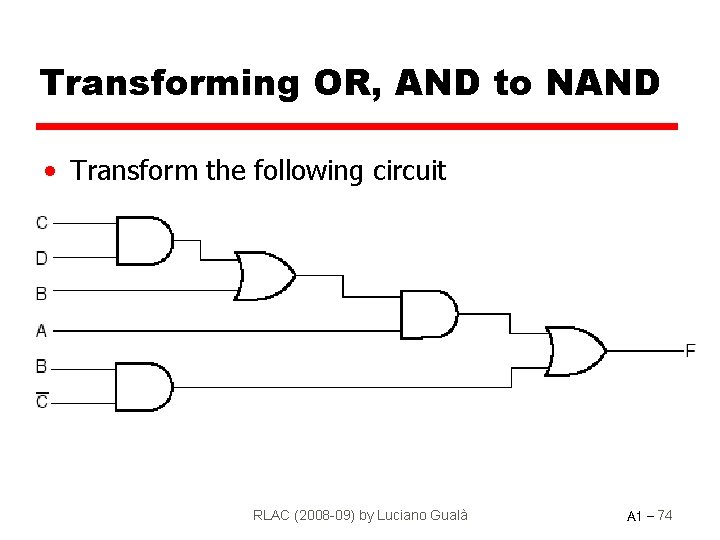

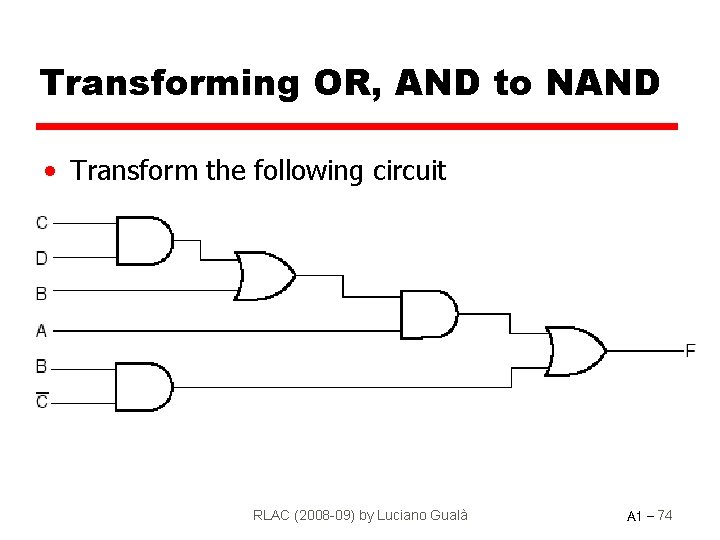

Transforming OR, AND to NAND • Transform the following circuit RLAC (2008 -09) by Luciano Gualà A 1 - 74

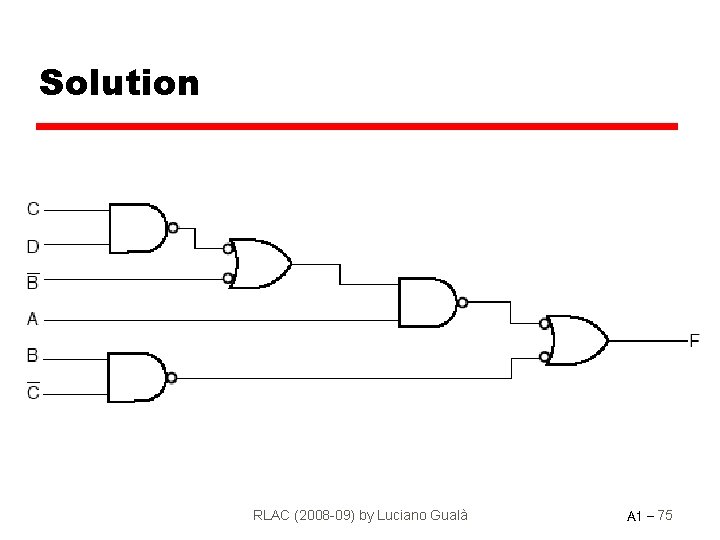

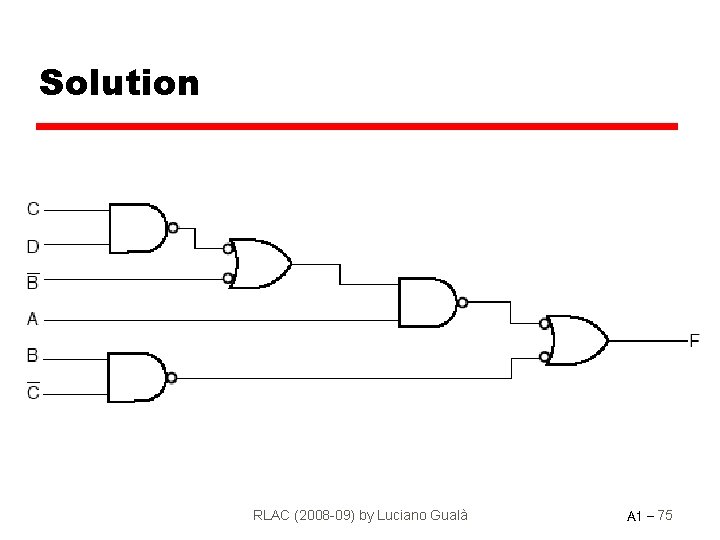

Solution RLAC (2008 -09) by Luciano Gualà A 1 - 75

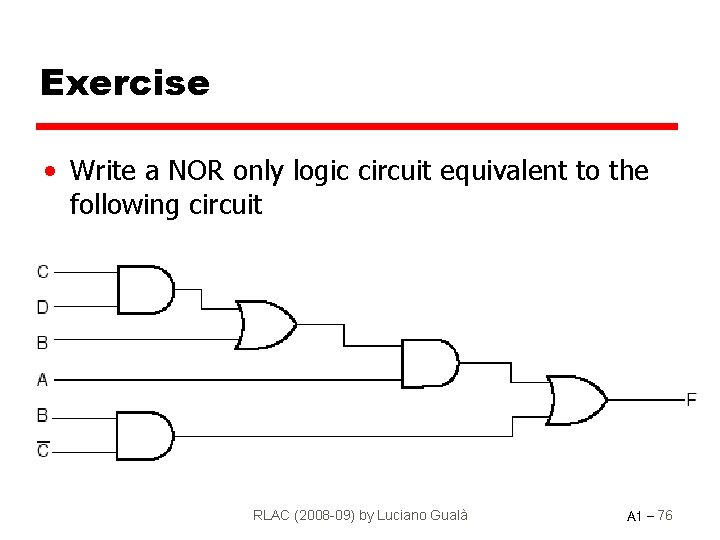

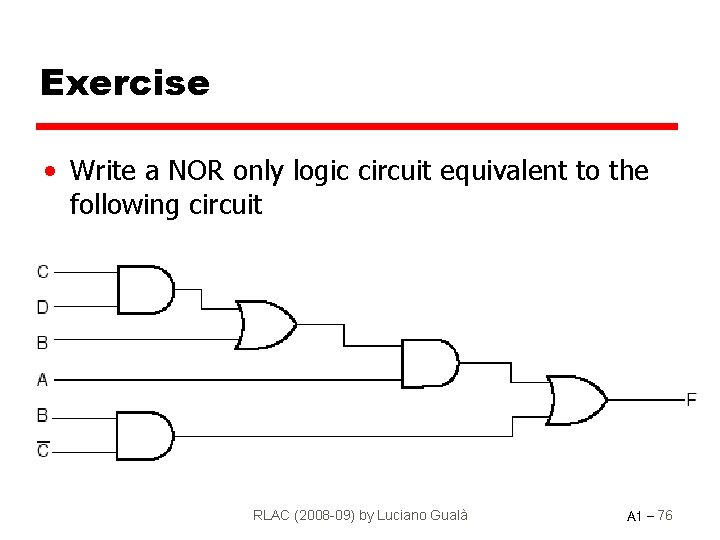

Exercise • Write a NOR only logic circuit equivalent to the following circuit RLAC (2008 -09) by Luciano Gualà A 1 - 76

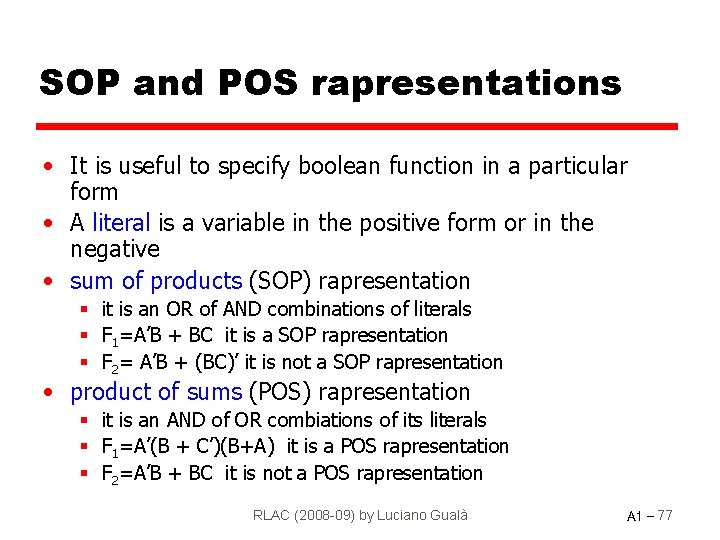

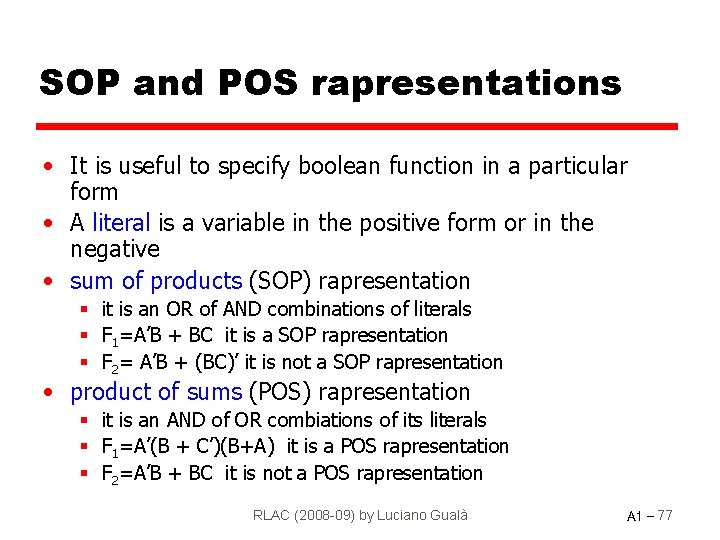

SOP and POS rapresentations • It is useful to specify boolean function in a particular form • A literal is a variable in the positive form or in the negative • sum of products (SOP) rapresentation § it is an OR of AND combinations of literals § F 1=A’B + BC it is a SOP rapresentation § F 2= A’B + (BC)’ it is not a SOP rapresentation • product of sums (POS) rapresentation § it is an AND of OR combiations of its literals § F 1=A’(B + C’)(B+A) it is a POS rapresentation § F 2=A’B + BC it is not a POS rapresentation RLAC (2008 -09) by Luciano Gualà A 1 - 77

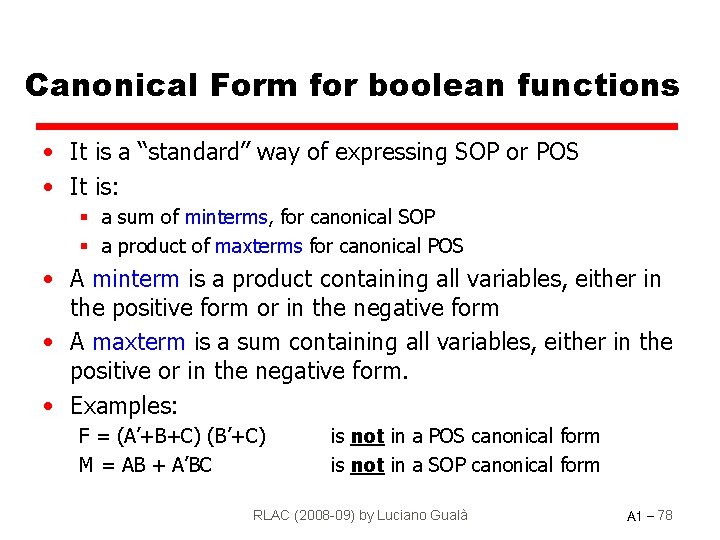

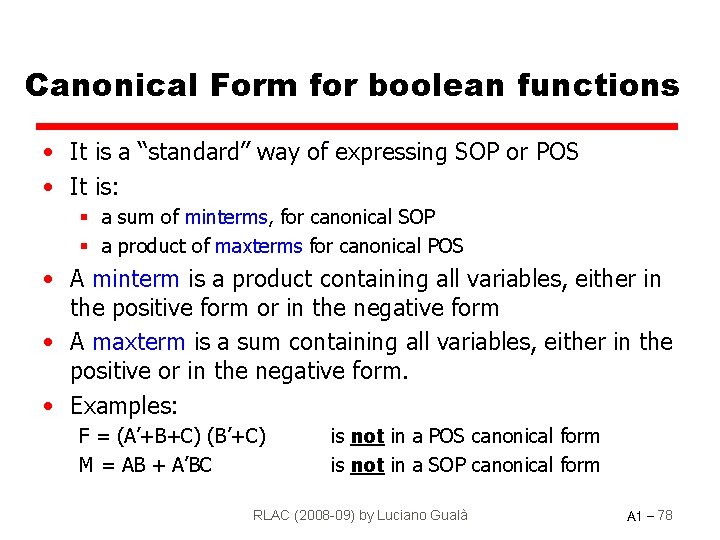

Canonical Form for boolean functions • It is a “standard” way of expressing SOP or POS • It is: § a sum of minterms, for canonical SOP § a product of maxterms for canonical POS • A minterm is a product containing all variables, either in the positive form or in the negative form • A maxterm is a sum containing all variables, either in the positive or in the negative form. • Examples: F = (A’+B+C) (B’+C) M = AB + A’BC is not in a POS canonical form is not in a SOP canonical form RLAC (2008 -09) by Luciano Gualà A 1 - 78

Minterms • Given that each variable may appear normal (e. g. X) or complemented (e. g. X’), there are 2 n minterms for n variables • Example: Two variables (X and Y) produce 4 combinations: § § XY X’Y XY’ X’Y’ • Thus there are 4 minterms of 2 variables RLAC (2008 -09) by Luciano Gualà A 1 - 79

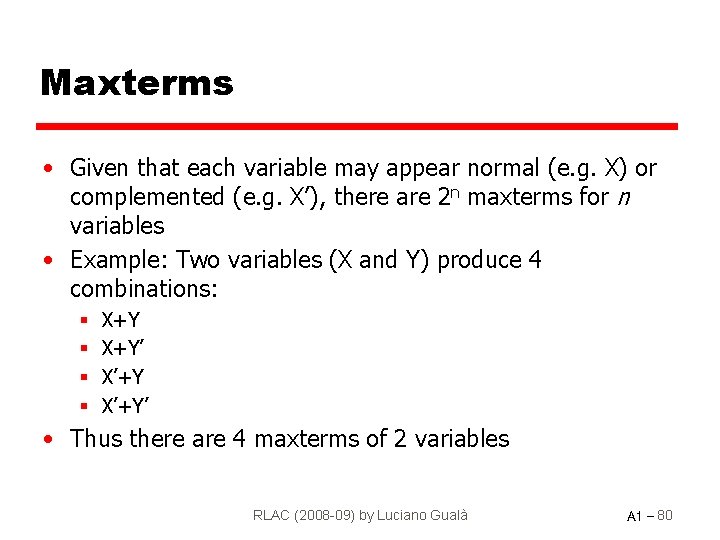

Maxterms • Given that each variable may appear normal (e. g. X) or complemented (e. g. X’), there are 2 n maxterms for n variables • Example: Two variables (X and Y) produce 4 combinations: § § X+Y’ X’+Y’ • Thus there are 4 maxterms of 2 variables RLAC (2008 -09) by Luciano Gualà A 1 - 80

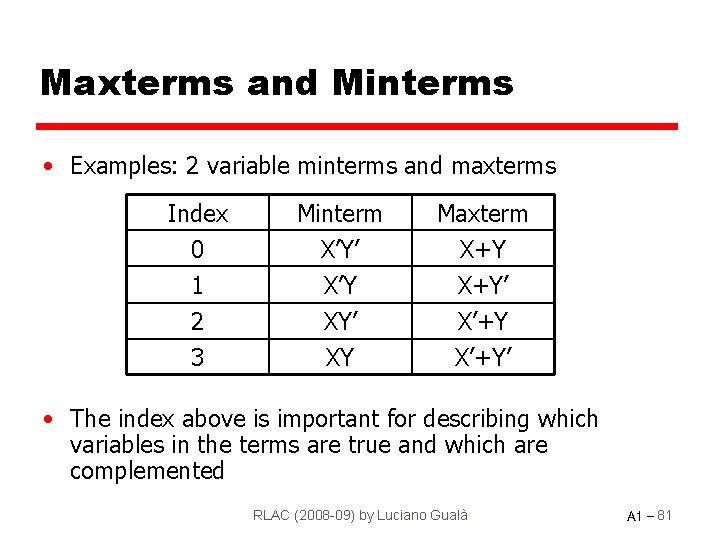

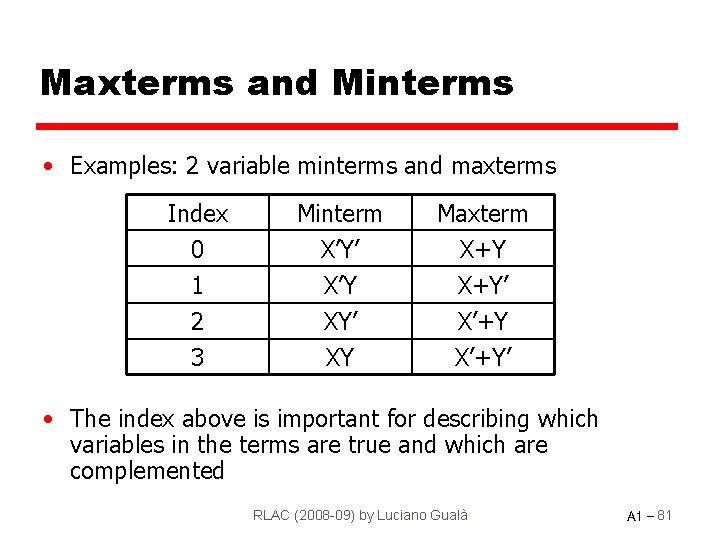

Maxterms and Minterms • Examples: 2 variable minterms and maxterms Index Minterm Maxterm 0 X’Y’ X+Y 1 X’Y X+Y’ 2 XY’ X’+Y 3 XY X’+Y’ • The index above is important for describing which variables in the terms are true and which are complemented RLAC (2008 -09) by Luciano Gualà A 1 - 81

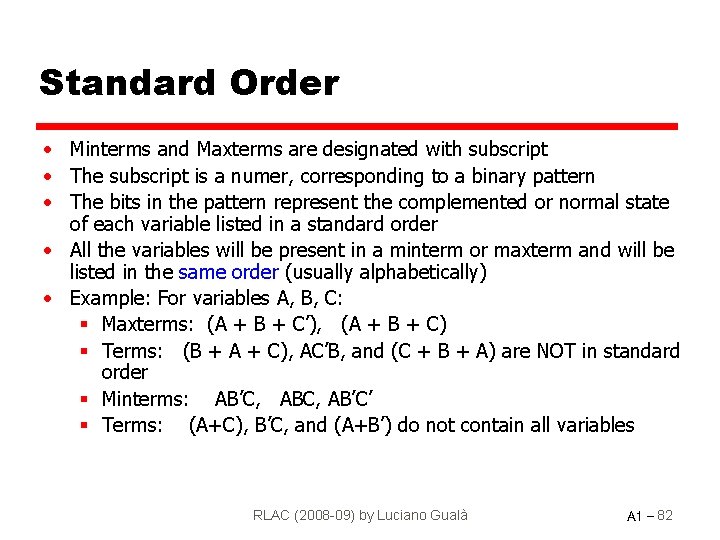

Standard Order • Minterms and Maxterms are designated with subscript • The subscript is a numer, corresponding to a binary pattern • The bits in the pattern represent the complemented or normal state of each variable listed in a standard order • All the variables will be present in a minterm or maxterm and will be listed in the same order (usually alphabetically) • Example: For variables A, B, C: § Maxterms: (A + B + C’), (A + B + C) § Terms: (B + A + C), AC’B, and (C + B + A) are NOT in standard order § Minterms: AB’C, AB’C’ § Terms: (A+C), B’C, and (A+B’) do not contain all variables RLAC (2008 -09) by Luciano Gualà A 1 - 82

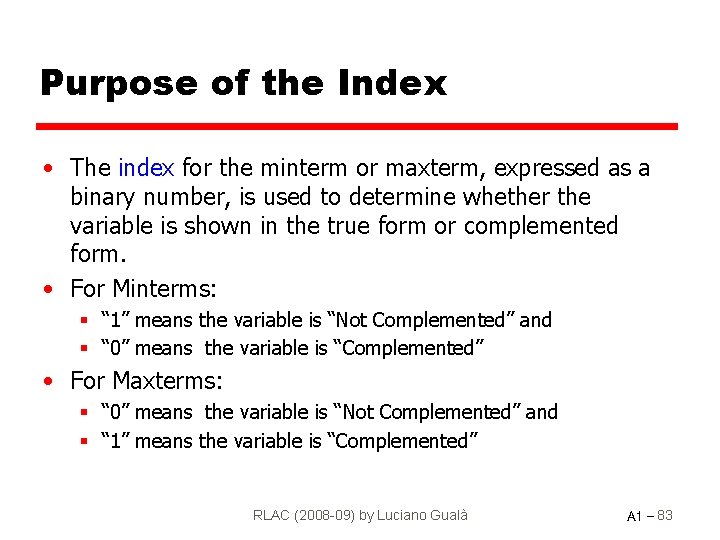

Purpose of the Index • The index for the minterm or maxterm, expressed as a binary number, is used to determine whether the variable is shown in the true form or complemented form. • For Minterms: § “ 1” means the variable is “Not Complemented” and § “ 0” means the variable is “Complemented” • For Maxterms: § “ 0” means the variable is “Not Complemented” and § “ 1” means the variable is “Complemented” RLAC (2008 -09) by Luciano Gualà A 1 - 83

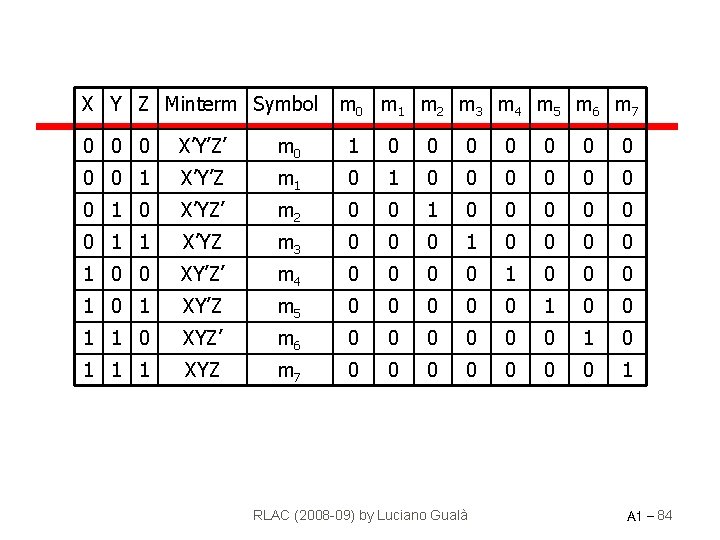

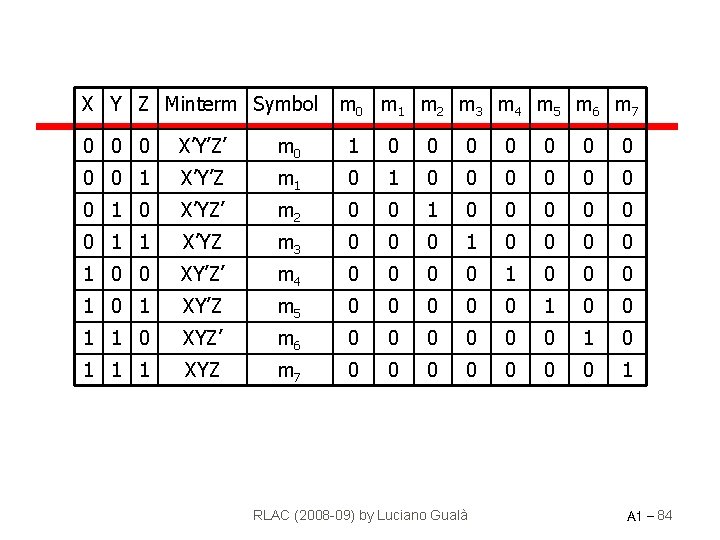

X Y Z Minterm Symbol m 0 m 1 m 2 m 3 m 4 m 5 m 6 m 7 0 0 0 X’Y’Z’ m 0 1 0 0 0 0 0 1 X’Y’Z m 1 0 0 0 0 1 0 X’YZ’ m 2 0 0 1 0 0 0 1 1 X’YZ m 3 0 0 0 1 0 0 XY’Z’ m 4 0 0 1 0 0 0 1 XY’Z m 5 0 0 0 1 1 0 XYZ’ m 6 0 0 0 1 0 1 1 1 XYZ m 7 0 0 0 0 1 RLAC (2008 -09) by Luciano Gualà A 1 - 84

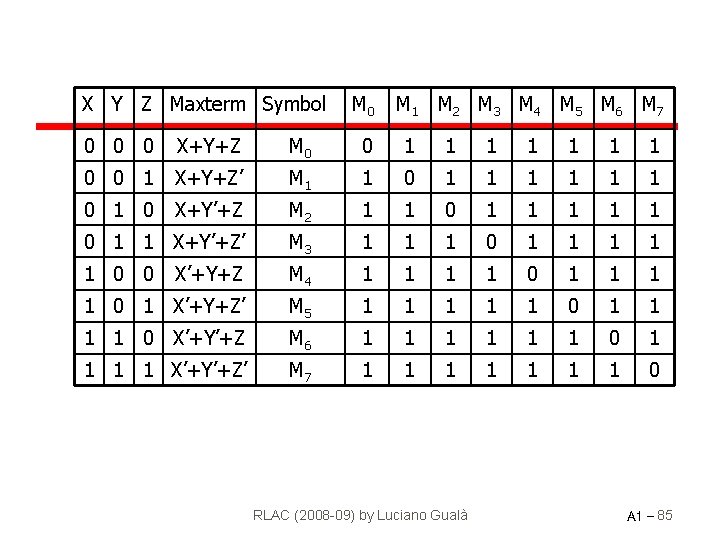

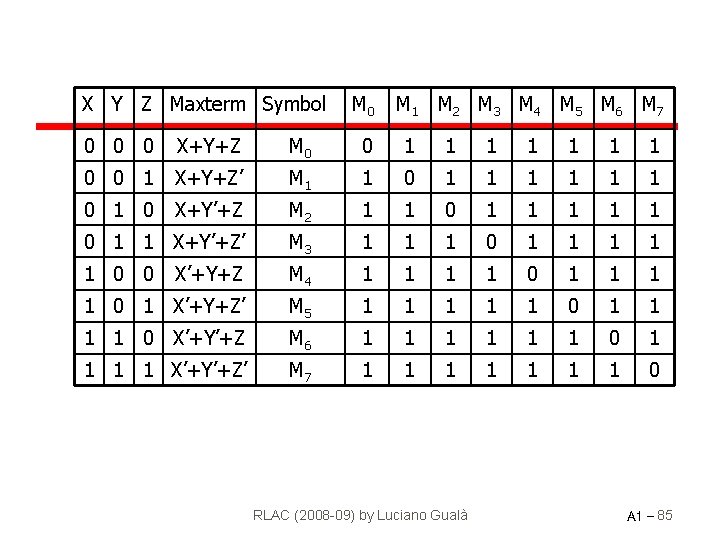

X Y Z Maxterm Symbol M 0 M 1 M 2 M 3 M 4 M 5 M 6 M 7 0 0 0 X+Y+Z M 0 0 1 1 1 1 0 0 1 X+Y+Z’ M 1 1 0 1 0 X+Y’+Z M 2 1 1 0 1 1 X+Y’+Z’ M 3 1 1 1 0 0 X’+Y+Z M 4 1 1 1 1 0 1 X’+Y+Z’ M 5 1 1 1 0 X’+Y’+Z M 6 1 1 1 0 1 1 X’+Y’+Z’ M 7 1 1 1 1 0 RLAC (2008 -09) by Luciano Gualà A 1 - 85

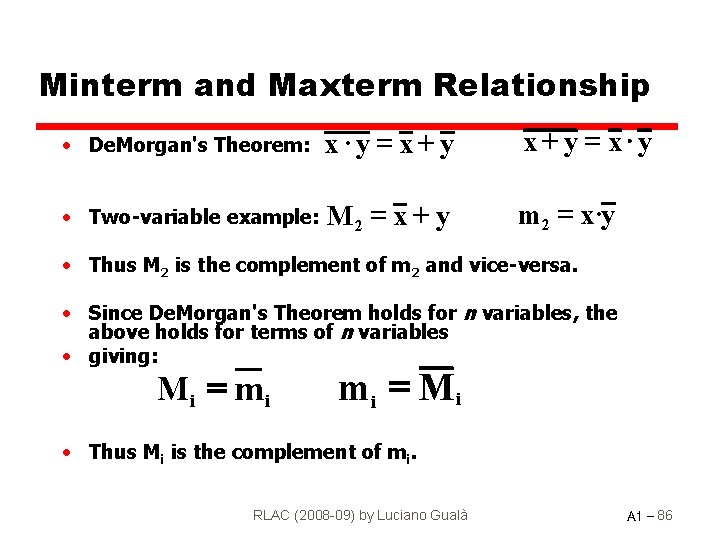

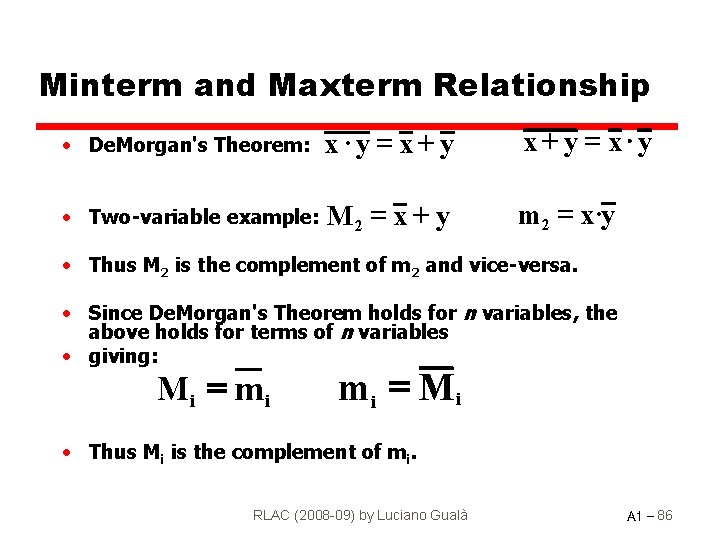

Minterm and Maxterm Relationship • De. Morgan's Theorem: x ·y = x + y = x×y • Two-variable example: M 2 = x + y m 2 = x·y • Thus M 2 is the complement of m 2 and vice-versa. • Since De. Morgan's Theorem holds for n variables, the above holds for terms of n variables • giving: Mi = mi mi = M i • Thus Mi is the complement of mi. RLAC (2008 -09) by Luciano Gualà A 1 - 86

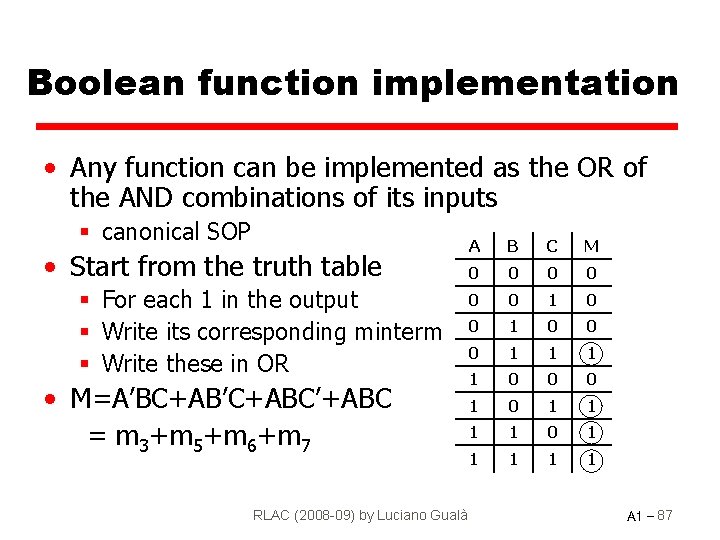

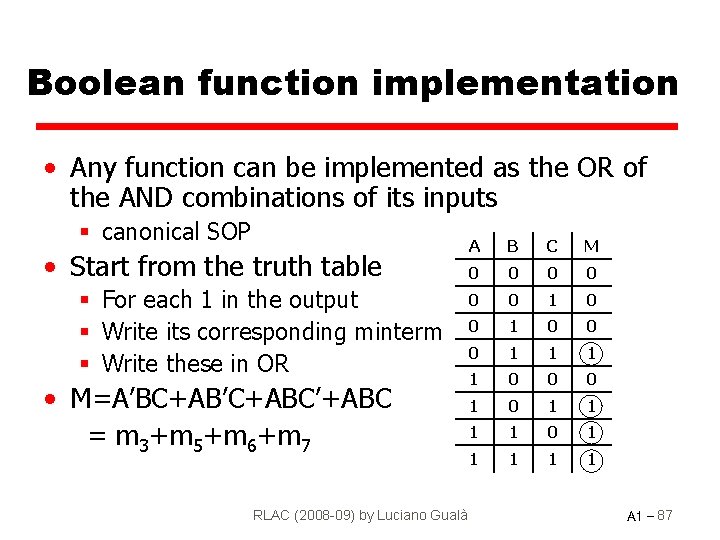

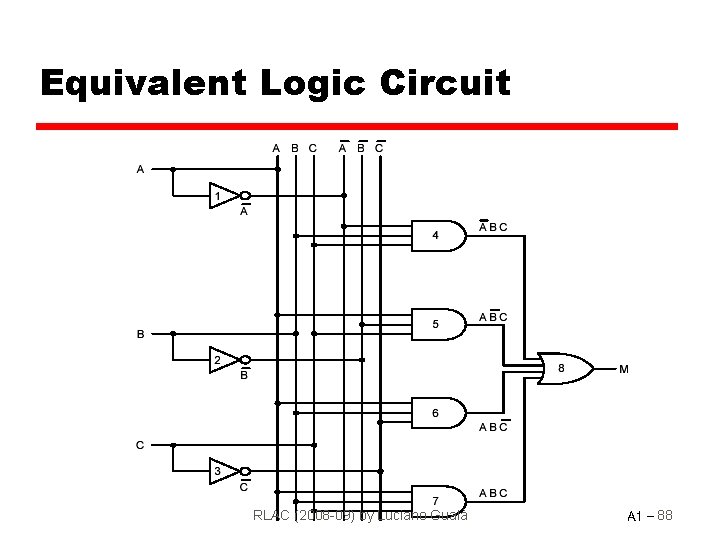

Boolean function implementation • Any function can be implemented as the OR of the AND combinations of its inputs § canonical SOP • Start from the truth table § For each 1 in the output § Write its corresponding minterm § Write these in OR • M=A’BC+AB’C+ABC’+ABC = m 3+m 5+m 6+m 7 RLAC (2008 -09) by Luciano Gualà A B C M 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 1 A 1 - 87

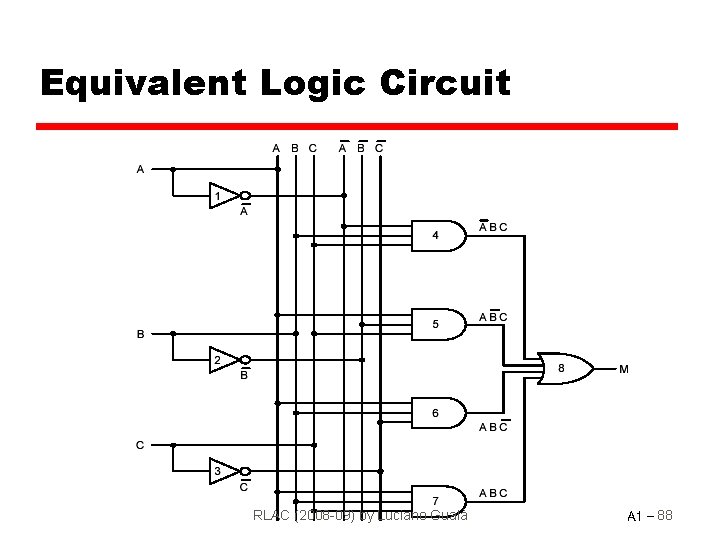

Equivalent Logic Circuit RLAC (2008 -09) by Luciano Gualà A 1 - 88

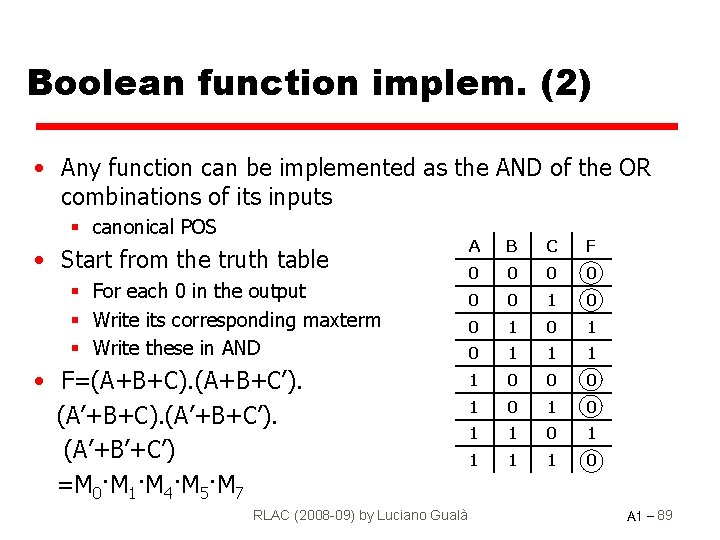

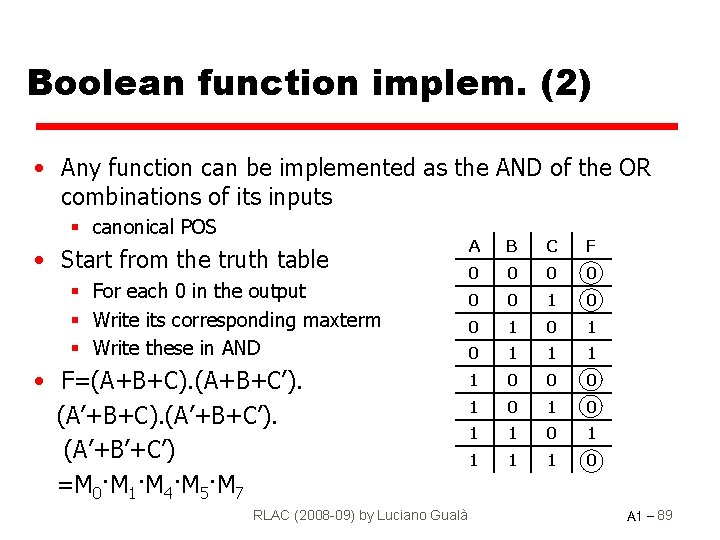

Boolean function implem. (2) • Any function can be implemented as the AND of the OR combinations of its inputs § canonical POS • Start from the truth table § For each 0 in the output § Write its corresponding maxterm § Write these in AND • F=(A+B+C). (A+B+C’). (A’+B+C’). (A’+B’+C’) =M 0·M 1·M 4·M 5·M 7 RLAC (2008 -09) by Luciano Gualà A B C F 0 0 0 1 0 1 1 0 0 0 1 0 1 1 1 1 0 A 1 - 89

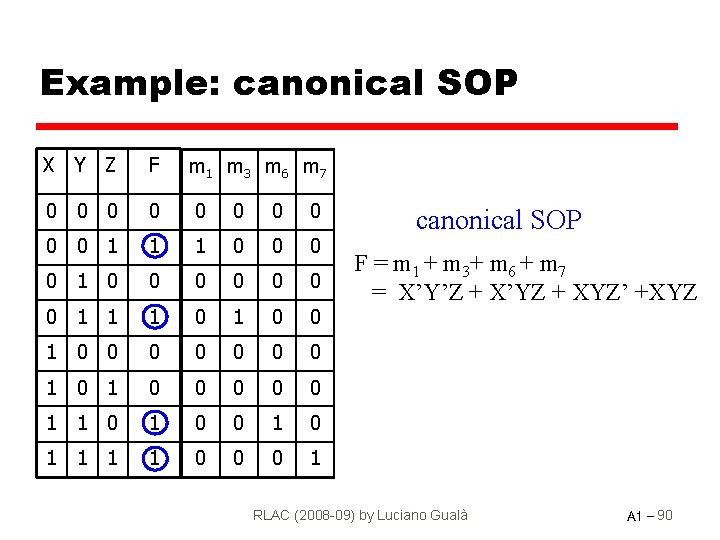

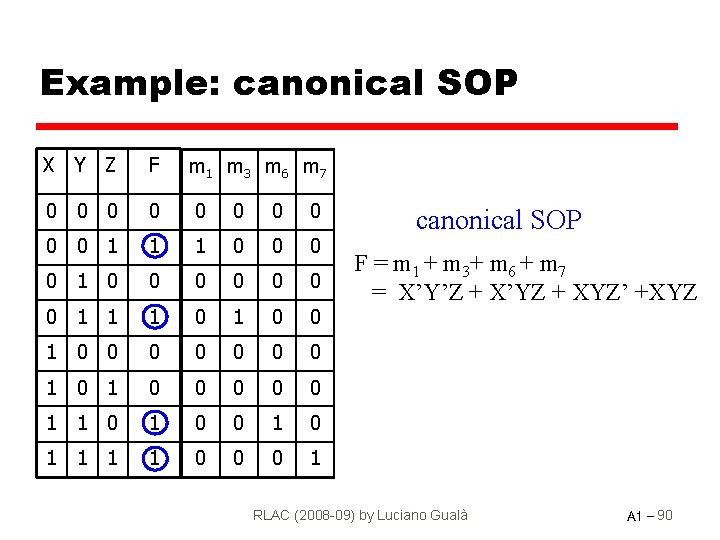

Example: canonical SOP X Y Z F 0 0 0 0 0 1 1 1 0 0 1 0 0 0 0 1 1 0 0 1 1 1 1 0 0 0 1 m 3 m 6 m 7 canonical SOP F = m 1 + m 3+ m 6 + m 7 = X’Y’Z + X’YZ + XYZ’ +XYZ RLAC (2008 -09) by Luciano Gualà A 1 - 90

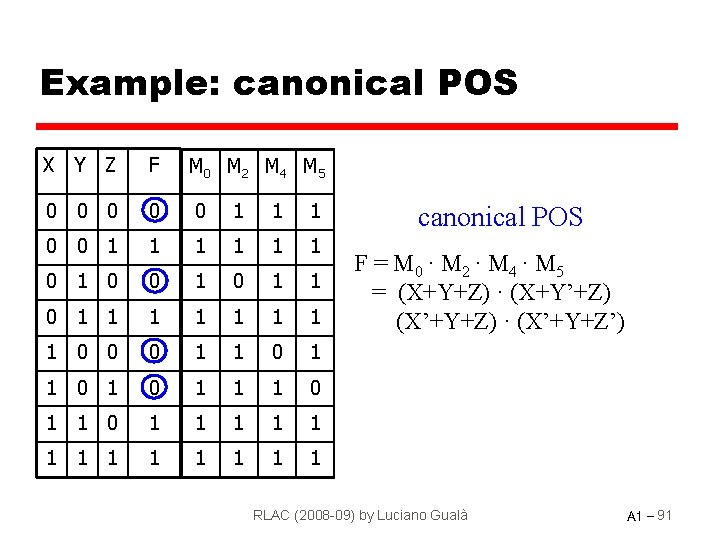

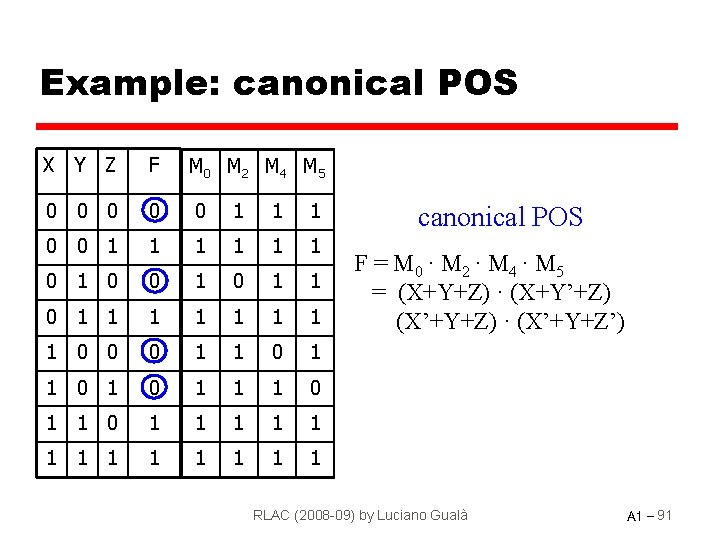

Example: canonical POS X Y Z F 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 1 1 1 0 1 1 1 1 M 0 M 2 M 4 M 5 canonical POS F = M 0 · M 2 · M 4 · M 5 = (X+Y+Z) · (X+Y’+Z) (X’+Y+Z) · (X’+Y+Z’) RLAC (2008 -09) by Luciano Gualà A 1 - 91

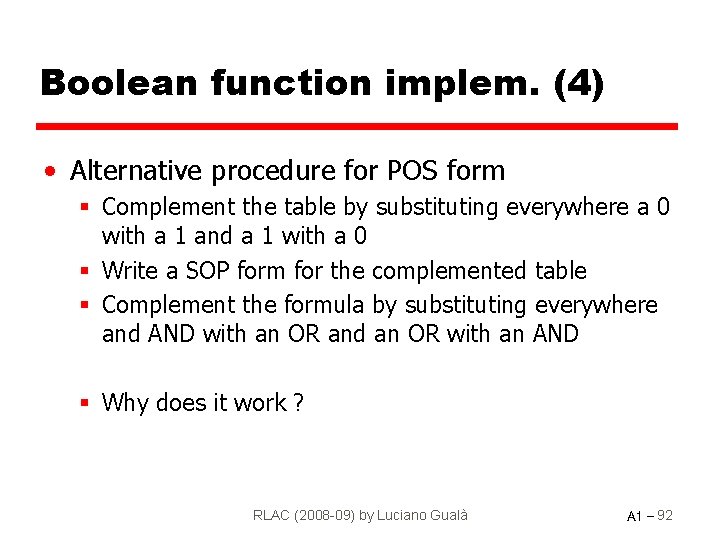

Boolean function implem. (4) • Alternative procedure for POS form § Complement the table by substituting everywhere a 0 with a 1 and a 1 with a 0 § Write a SOP form for the complemented table § Complement the formula by substituting everywhere and AND with an OR and an OR with an AND § Why does it work ? RLAC (2008 -09) by Luciano Gualà A 1 - 92

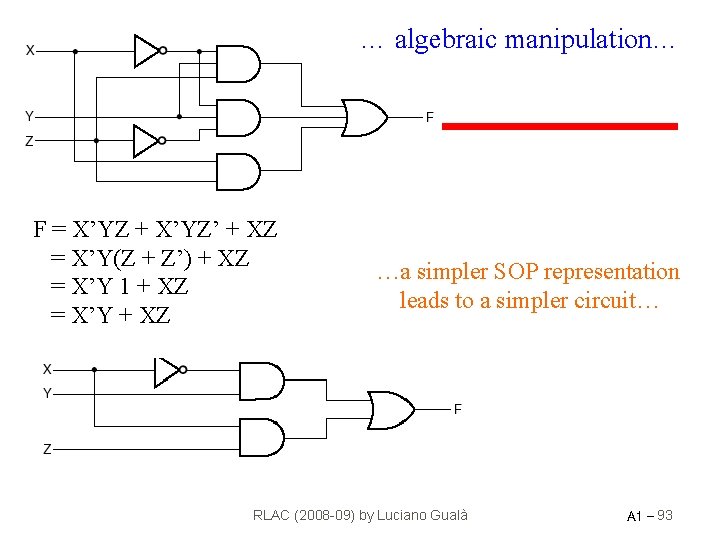

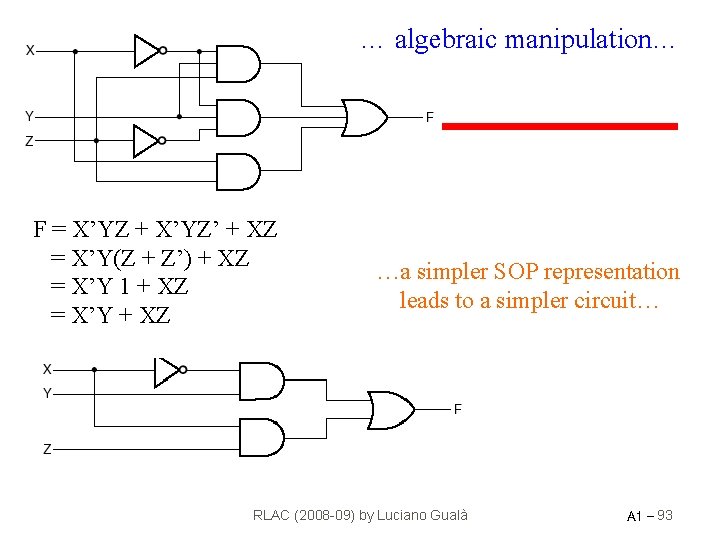

… algebraic manipulation… F = X’YZ + X’YZ’ + XZ = X’Y(Z + Z’) + XZ = X’Y 1 + XZ = X’Y + XZ …a simpler SOP representation leads to a simpler circuit… RLAC (2008 -09) by Luciano Gualà A 1 - 93

Circuit Optimization • Goal: To obtain the simplest implementation for a given function • Optimization is a more formal approach to simplification that is performed using a specific procedure or algorithm • Optimization requires a cost criterion to measure the simplicity of a circuit • Distinct cost criteria we will use: § Literal cost (L) § Gate input cost (G) § Gate input cost with NOTs (GN) RLAC (2008 -09) by Luciano Gualà A 1 - 94

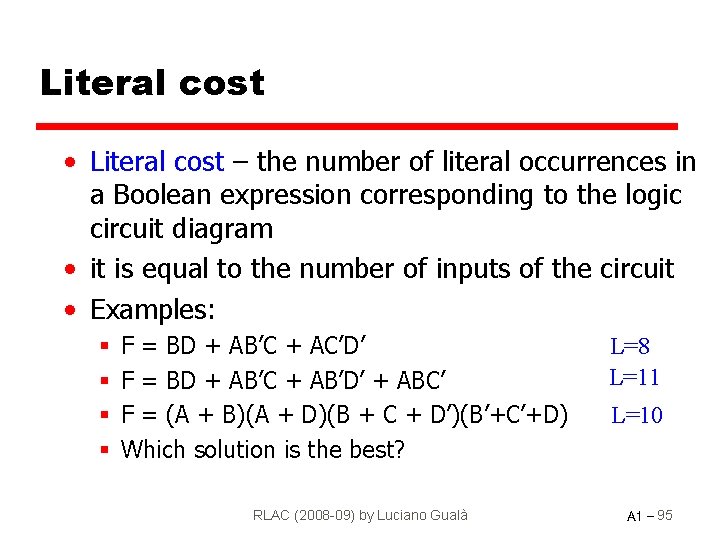

Literal cost • Literal cost – the number of literal occurrences in a Boolean expression corresponding to the logic circuit diagram • it is equal to the number of inputs of the circuit • Examples: § § F = BD + AB’C + AC’D’ F = BD + AB’C + AB’D’ + ABC’ F = (A + B)(A + D)(B + C + D’)(B’+C’+D) Which solution is the best? RLAC (2008 -09) by Luciano Gualà L=8 L=11 L=10 A 1 - 95

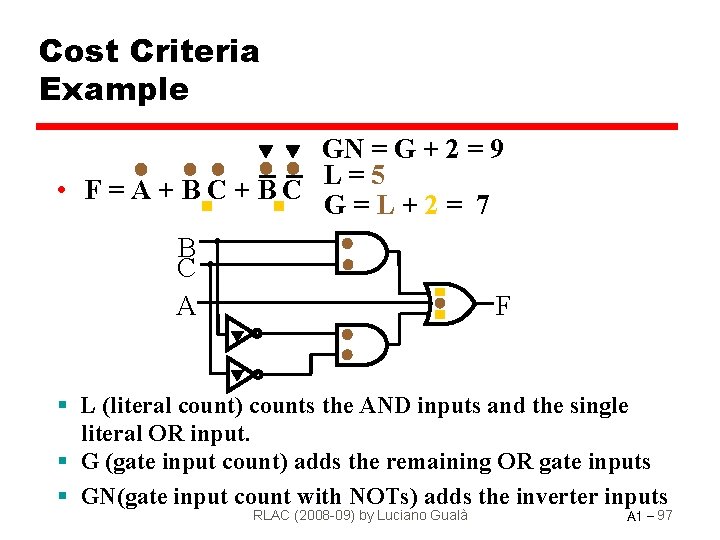

Gate input cost • Gate input cost: the number of inputs to the gates in the circuit corresponding exactly to the furmula § G - inverters not counted, GN - inverters counted • For SOP and POS equations, it can be found from the equation(s) by finding the sum of: § all literal occurrences § the number of terms excluding single literal terms (G) § optionally, the number of distinct complemented single literals (GN) RLAC (2008 -09) by Luciano Gualà A 1 - 96

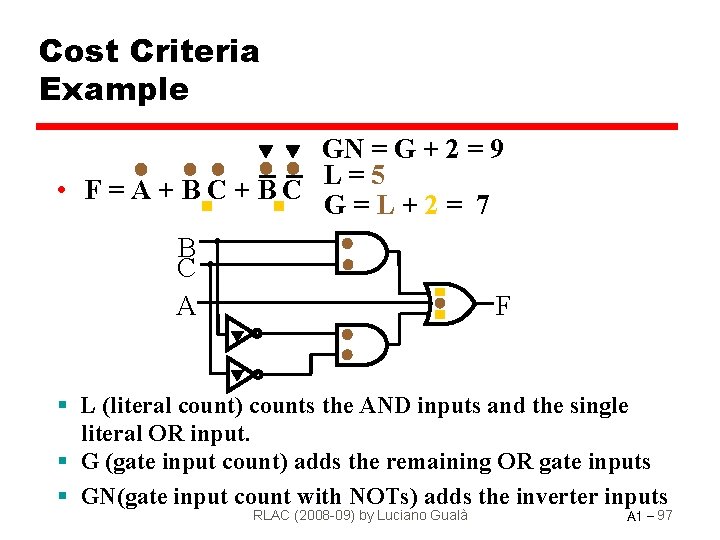

Cost Criteria Example GN = G + 2 = 9 L=5 • F=A+BC+ BC G=L+2= 7 B C A F § L (literal count) counts the AND inputs and the single literal OR input. § G (gate input count) adds the remaining OR gate inputs § GN(gate input count with NOTs) adds the inverter inputs RLAC (2008 -09) by Luciano Gualà A 1 - 97

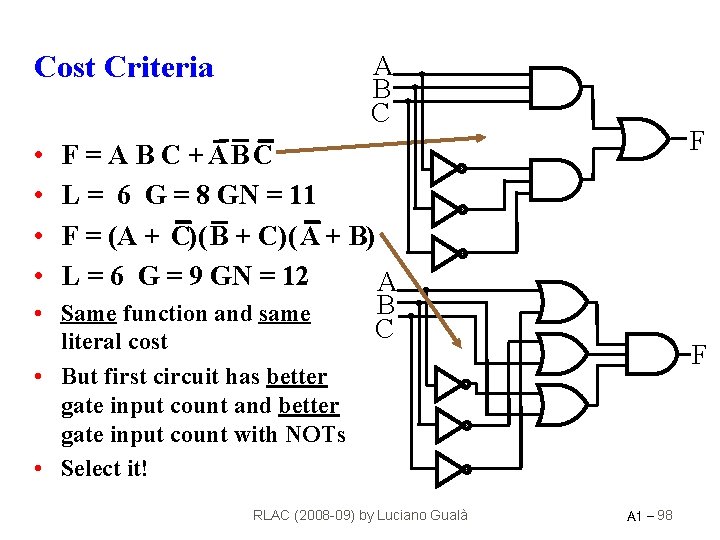

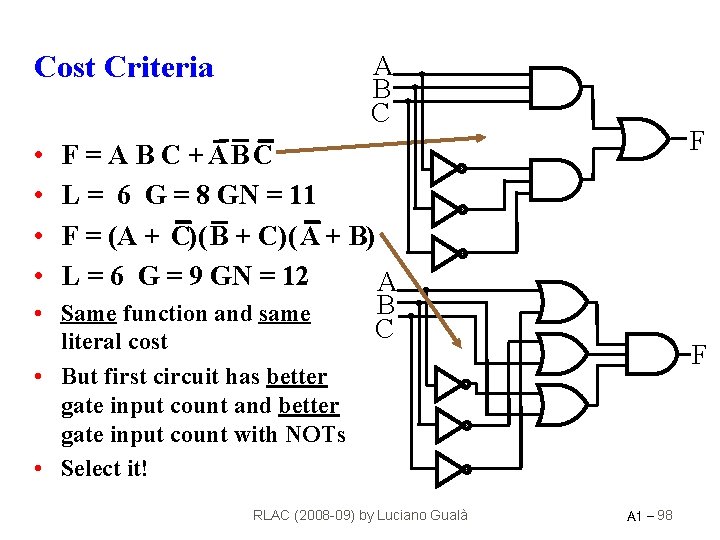

Cost Criteria • • • A B C F F = A B C + AB C L = 6 G = 8 GN = 11 F = (A + C)( B + C)( A + B) L = 6 G = 9 GN = 12 A B Same function and same C literal cost F • But first circuit has better gate input count and better gate input count with NOTs • Select it! RLAC (2008 -09) by Luciano Gualà A 1 - 98

Minimal SOP and POS • Optimization for two-level (SOP and POS) circuits: § minimal SOP • minimum number of pruduct terms • minimum number of literals for each product term § minimal POS • minimum number of sum terms • minimum number of literals for each sum term RLAC (2008 -09) by Luciano Gualà A 1 - 99

Minimization procedures • Karnaugh’s maps (by hand) § Used to minimize boolean functions of up to 4 input variables • Quine-Mc. Kluskey (programmable) § For more variables • Practical Optimization: Espresso § sub-optimal heuristic method RLAC (2008 -09) by Luciano Gualà A 1 -100

Karnaugh’s Maps (KM) • Grid-like representation for boolean functions • Each cell represents a minterm • The K-map can be viewed as a reorganized version of the truth table • Minterms with just one variable different occupies adjacent cells • Alternative algebraic expressions for the same function are derived by recognizing patterns of squares • Consider only 1 s in the representation (focusing on a SOP representation) • IDEA: if 2 adjacent cells have a 1 the function can be simplified RLAC (2008 -09) by Luciano Gualà A 1 -101

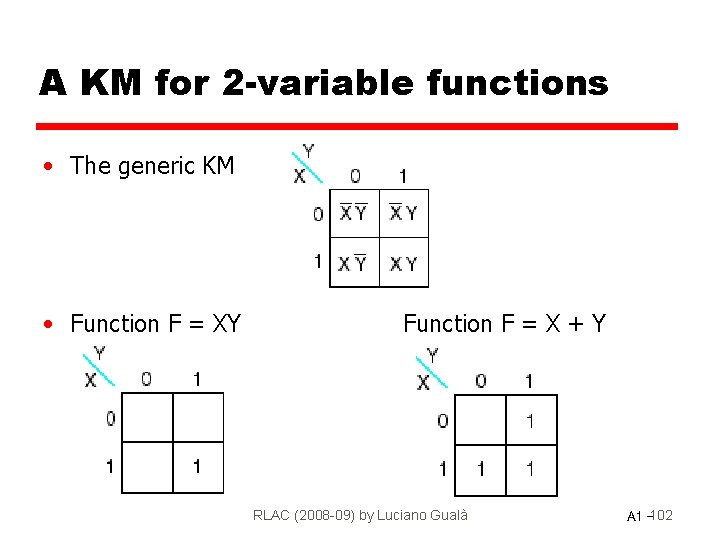

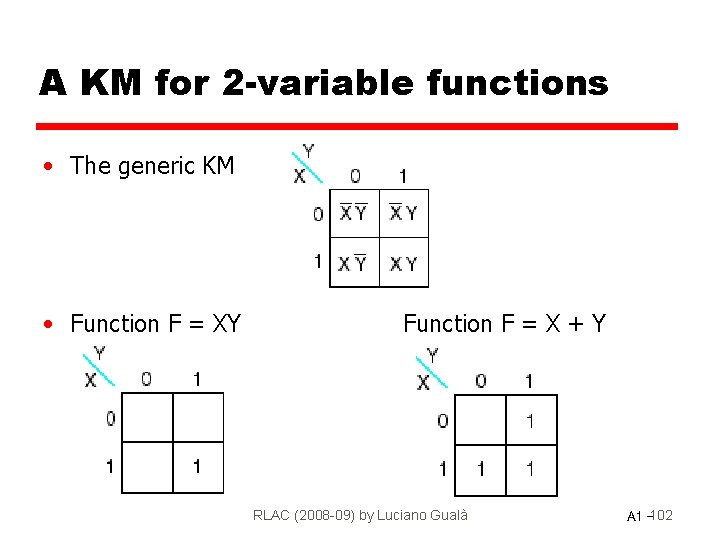

A KM for 2 -variable functions • The generic KM • Function F = XY Function F = X + Y RLAC (2008 -09) by Luciano Gualà A 1 -102

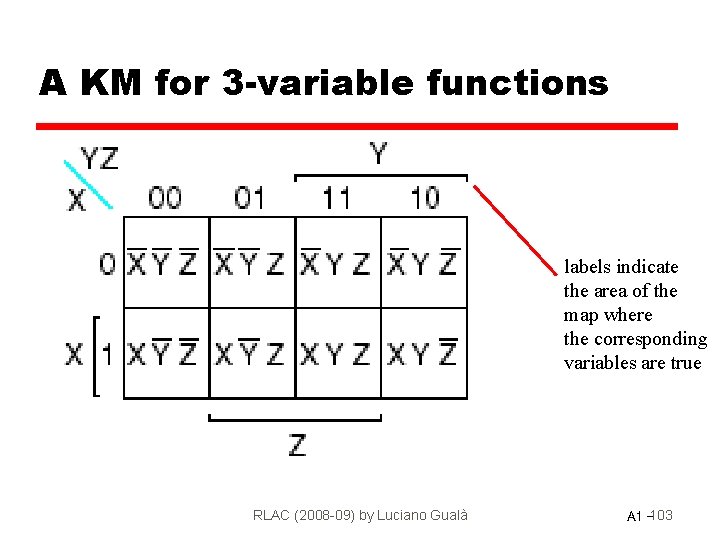

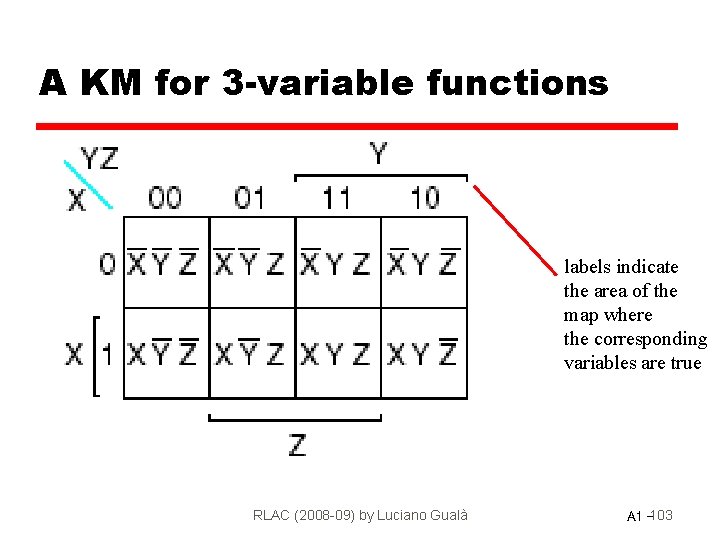

A KM for 3 -variable functions labels indicate the area of the map where the corresponding variables are true RLAC (2008 -09) by Luciano Gualà A 1 -103

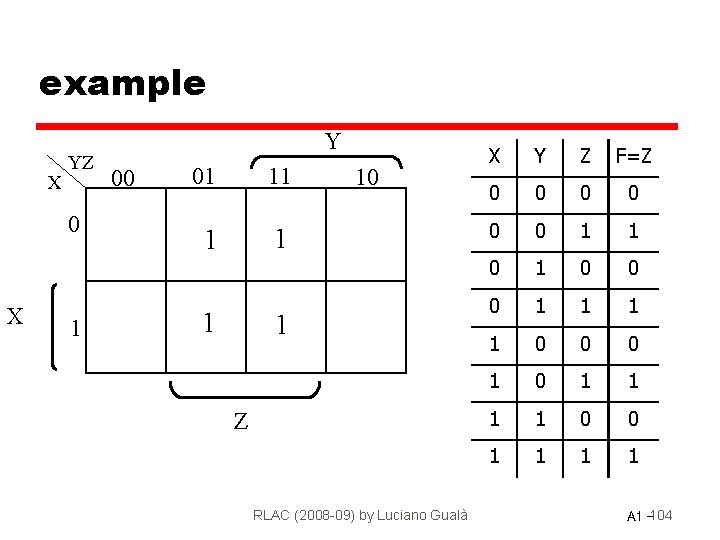

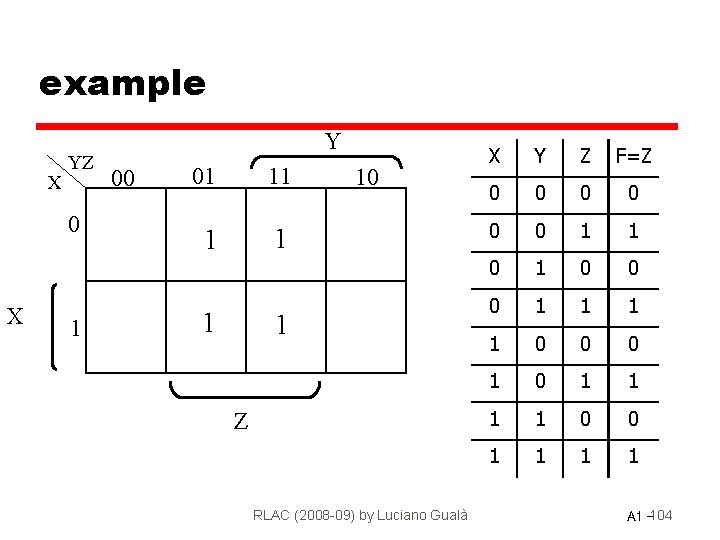

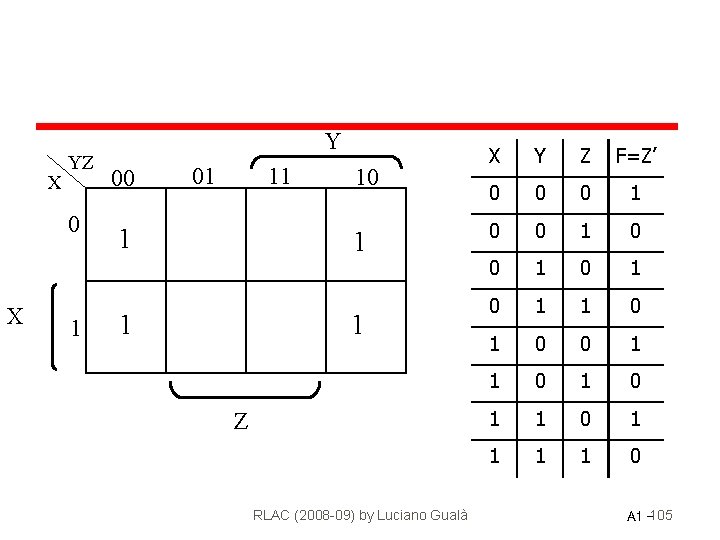

example X YZ 0 X 1 Y 00 01 11 1 10 1 Z RLAC (2008 -09) by Luciano Gualà X Y Z F=Z 0 0 0 1 1 0 0 0 1 1 1 1 0 0 1 1 A 1 -104

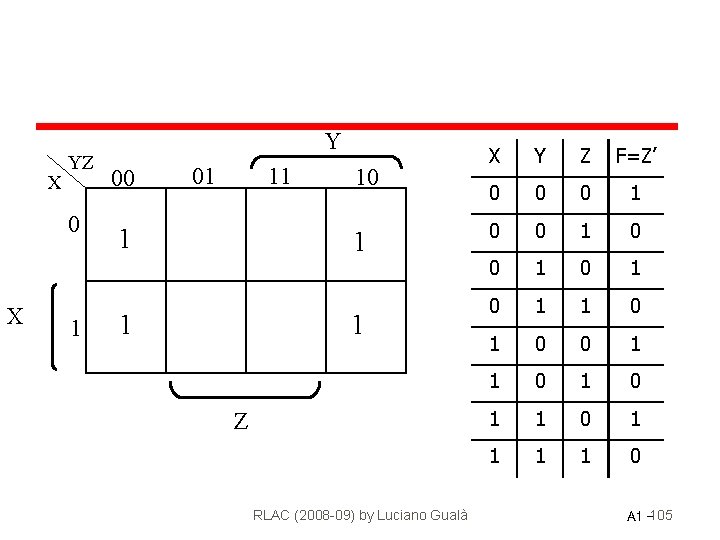

X YZ 0 X 1 Y 00 01 11 1 10 1 1 1 Z RLAC (2008 -09) by Luciano Gualà X Y Z F=Z’ 0 0 0 1 0 1 1 0 1 1 0 A 1 -105

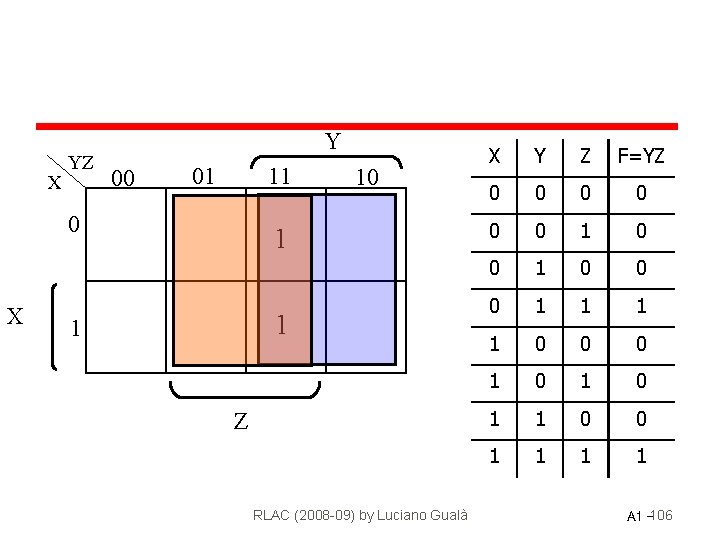

X YZ Y 00 01 11 0 X 10 1 1 1 Z RLAC (2008 -09) by Luciano Gualà X Y Z F=YZ 0 0 0 1 1 0 0 0 1 0 1 1 0 0 1 1 A 1 -106

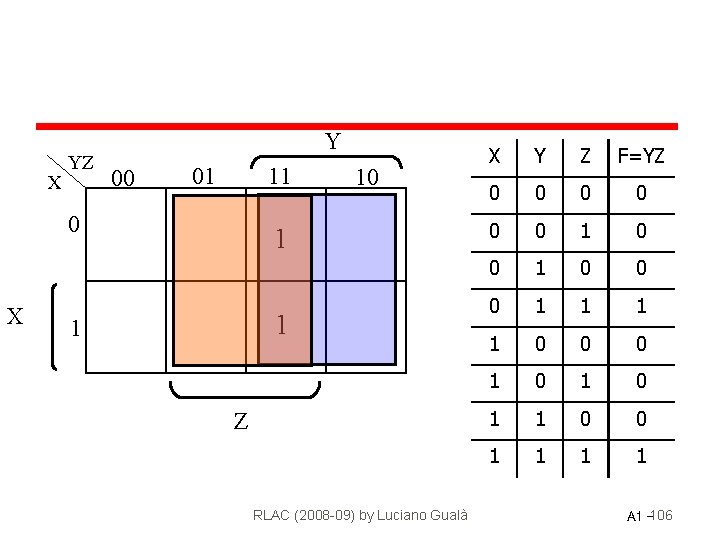

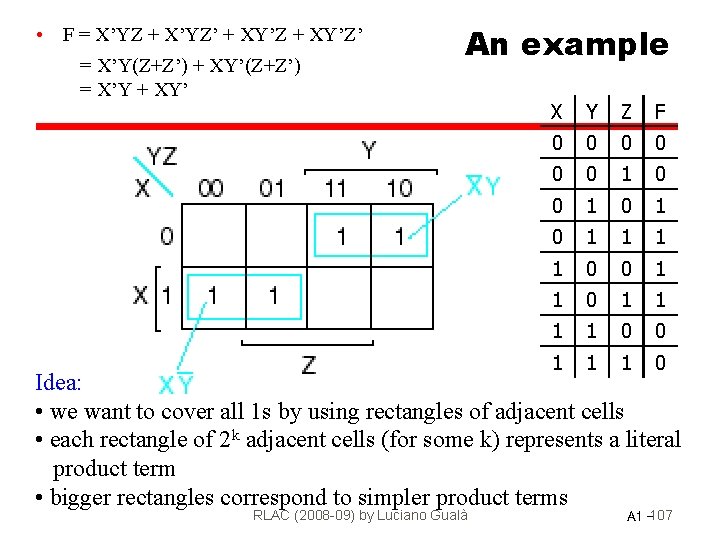

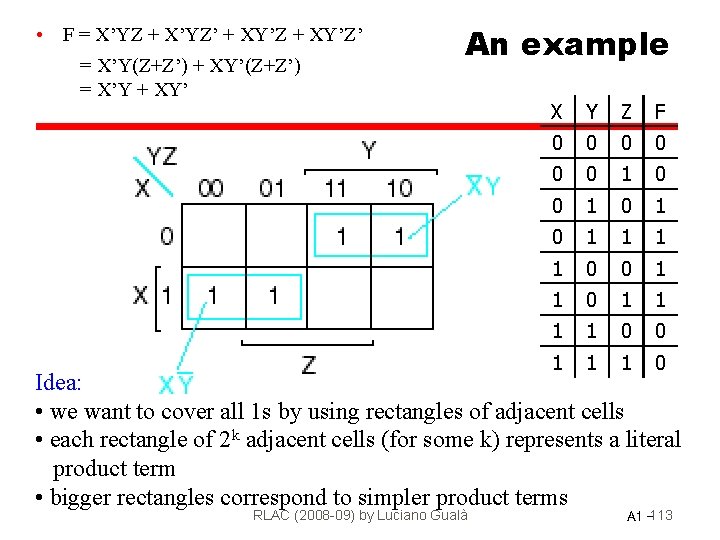

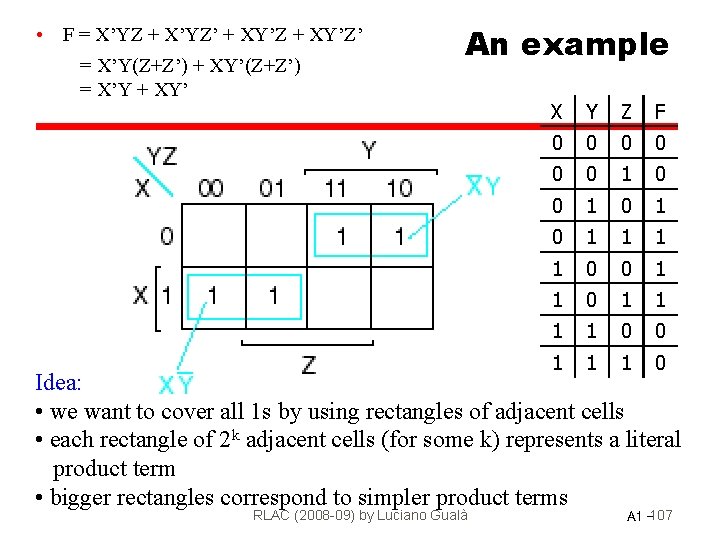

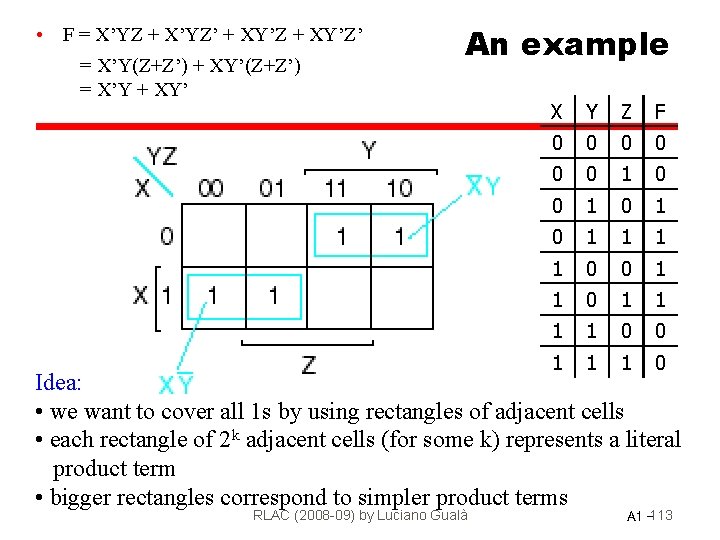

• F = X’YZ + X’YZ’ + XY’Z’ = X’Y(Z+Z’) + XY’(Z+Z’) = X’Y + XY’ An example X Y Z F 0 0 0 1 0 1 1 1 1 0 0 1 1 1 0 Idea: • we want to cover all 1 s by using rectangles of adjacent cells • each rectangle of 2 k adjacent cells (for some k) represents a literal product term • bigger rectangles correspond to simpler product terms RLAC (2008 -09) by Luciano Gualà A 1 -107

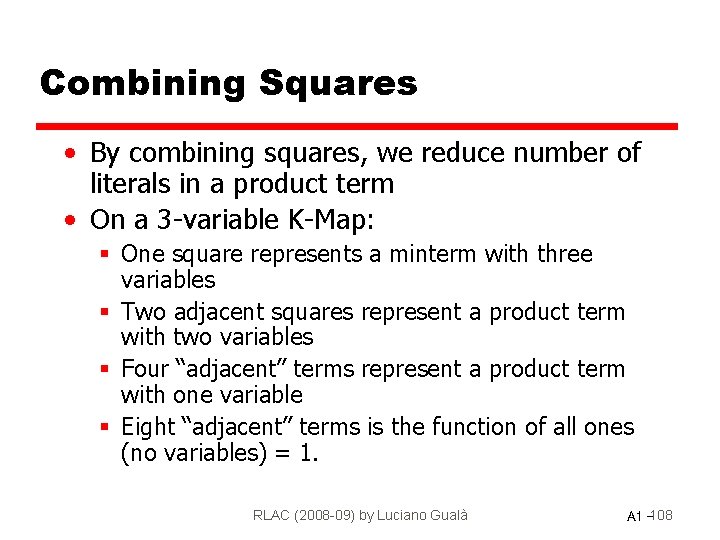

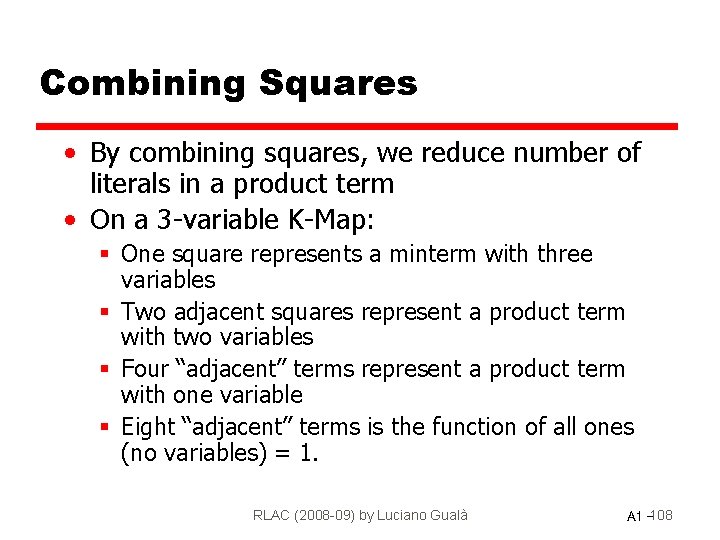

Combining Squares • By combining squares, we reduce number of literals in a product term • On a 3 -variable K-Map: § One square represents a minterm with three variables § Two adjacent squares represent a product term with two variables § Four “adjacent” terms represent a product term with one variable § Eight “adjacent” terms is the function of all ones (no variables) = 1. RLAC (2008 -09) by Luciano Gualà A 1 -108

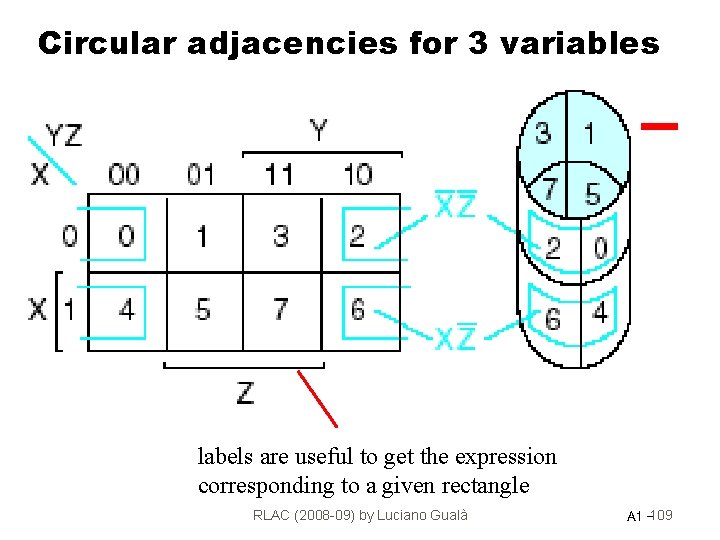

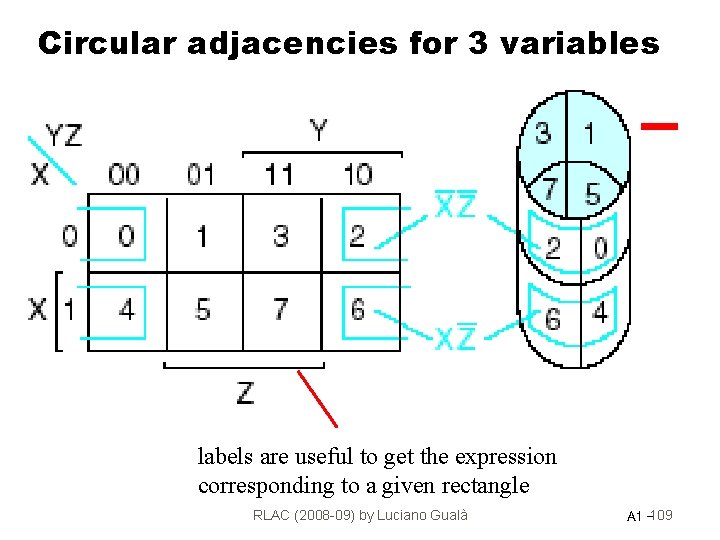

Circular adjacencies for 3 variables labels are useful to get the expression corresponding to a given rectangle RLAC (2008 -09) by Luciano Gualà A 1 -109

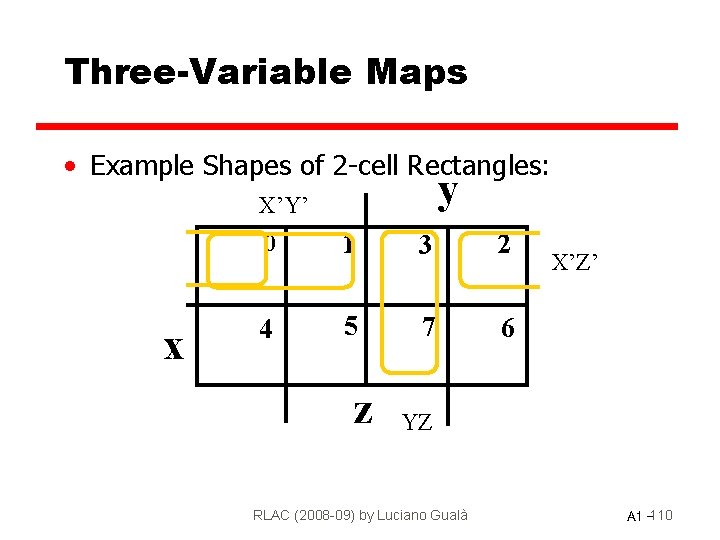

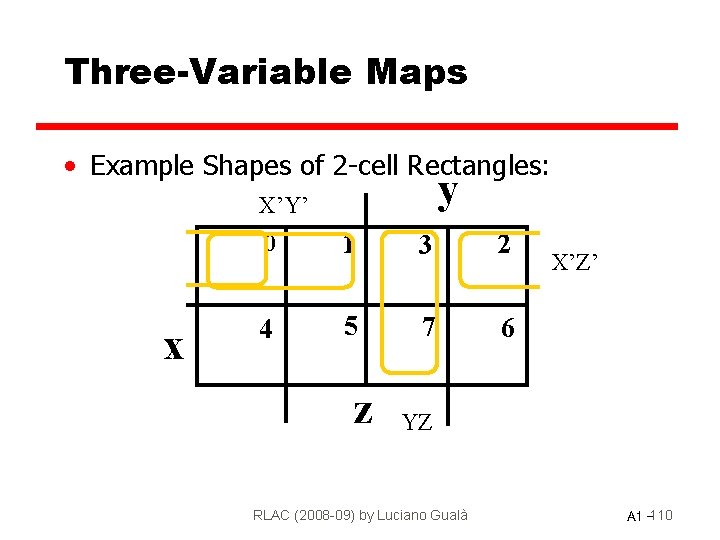

Three-Variable Maps • Example Shapes of 2 -cell Rectangles: y X’Y’ x 0 1 3 2 4 5 7 6 z X’Z’ YZ RLAC (2008 -09) by Luciano Gualà A 1 -110

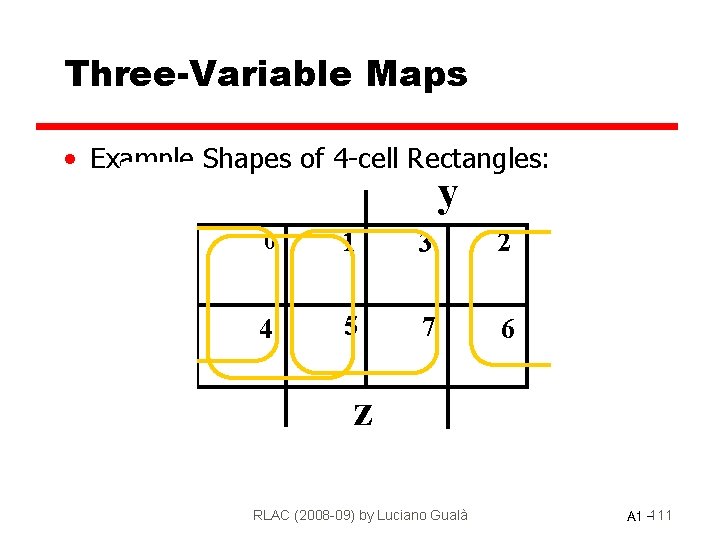

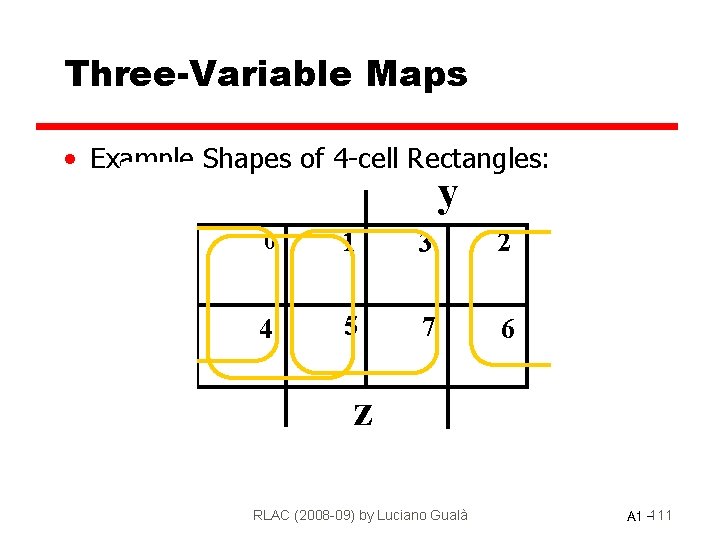

Three-Variable Maps • Example Shapes of 4 -cell Rectangles: y x 0 1 3 2 4 5 7 6 z RLAC (2008 -09) by Luciano Gualà A 1 -111

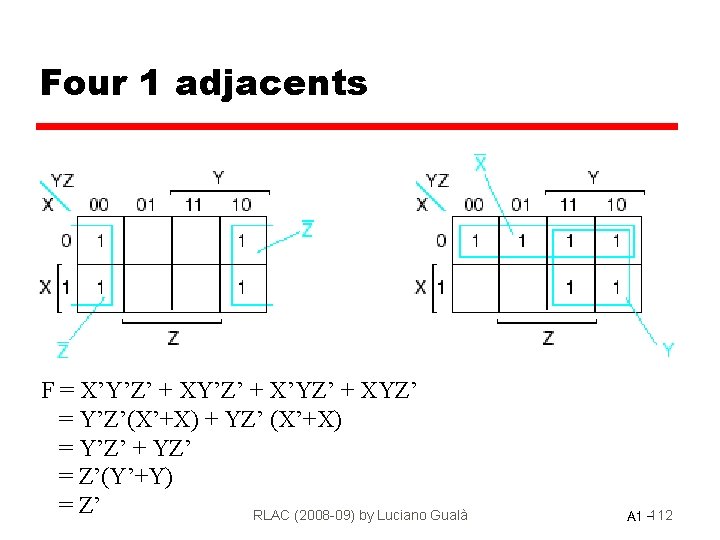

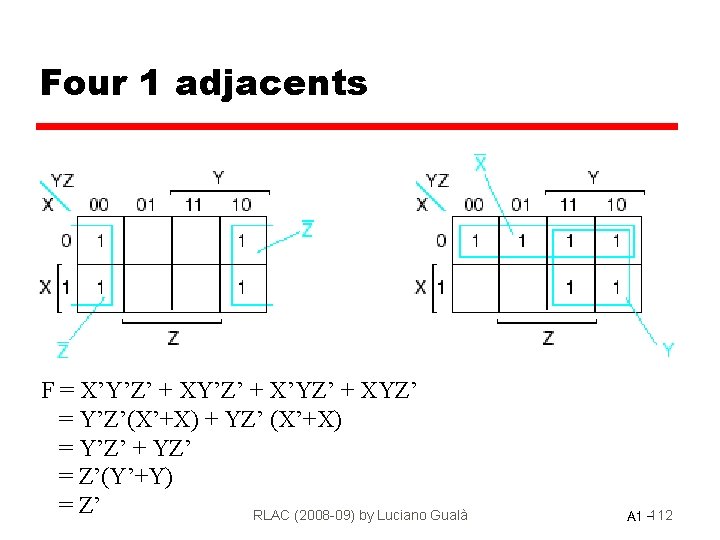

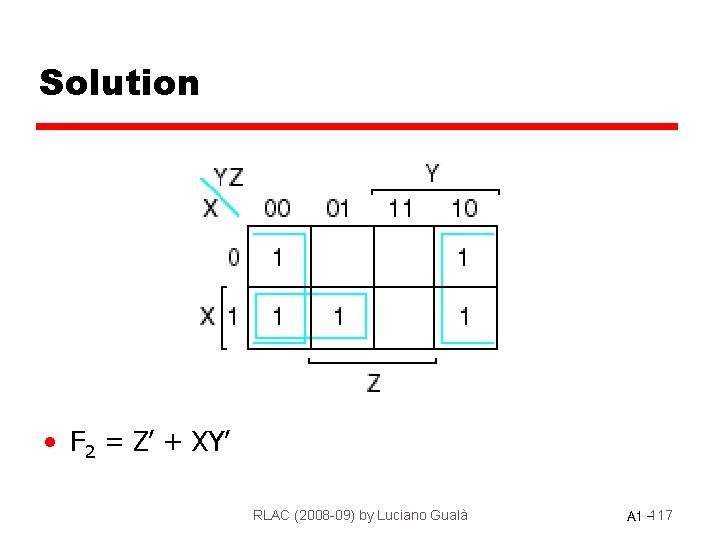

Four 1 adjacents F = X’Y’Z’ + X’YZ’ + XYZ’ = Y’Z’(X’+X) + YZ’ (X’+X) = Y’Z’ + YZ’ = Z’(Y’+Y) = Z’ RLAC (2008 -09) by Luciano Gualà A 1 -112

• F = X’YZ + X’YZ’ + XY’Z’ = X’Y(Z+Z’) + XY’(Z+Z’) = X’Y + XY’ An example X Y Z F 0 0 0 1 0 1 1 1 1 0 0 1 1 1 0 Idea: • we want to cover all 1 s by using rectangles of adjacent cells • each rectangle of 2 k adjacent cells (for some k) represents a literal product term • bigger rectangles correspond to simpler product terms RLAC (2008 -09) by Luciano Gualà A 1 -113

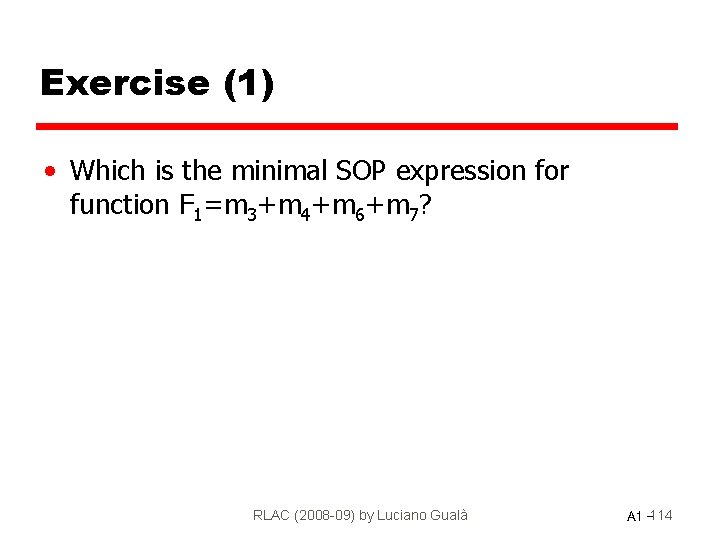

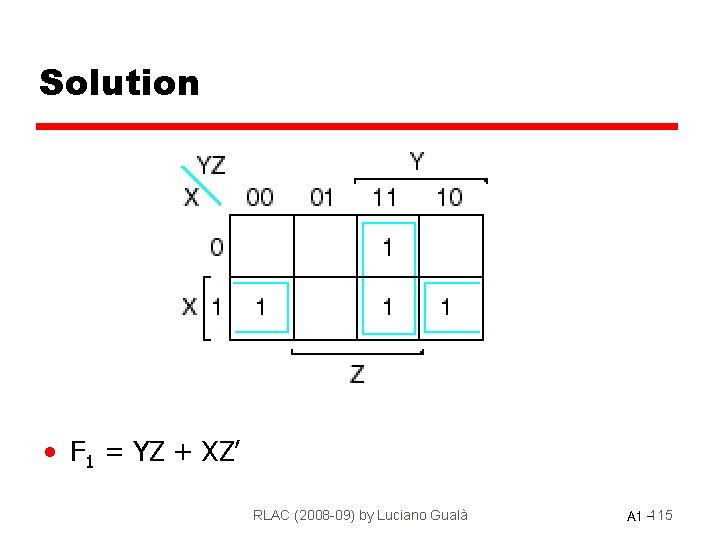

Exercise (1) • Which is the minimal SOP expression for function F 1=m 3+m 4+m 6+m 7? RLAC (2008 -09) by Luciano Gualà A 1 -114

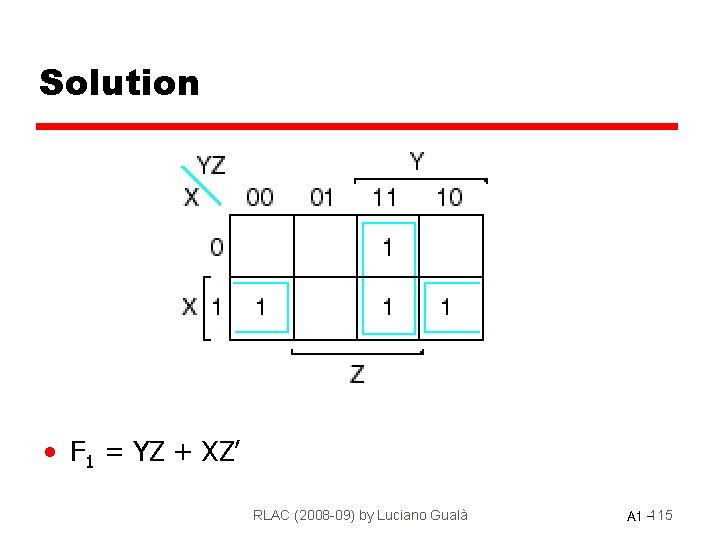

Solution • F 1 = YZ + XZ’ RLAC (2008 -09) by Luciano Gualà A 1 -115

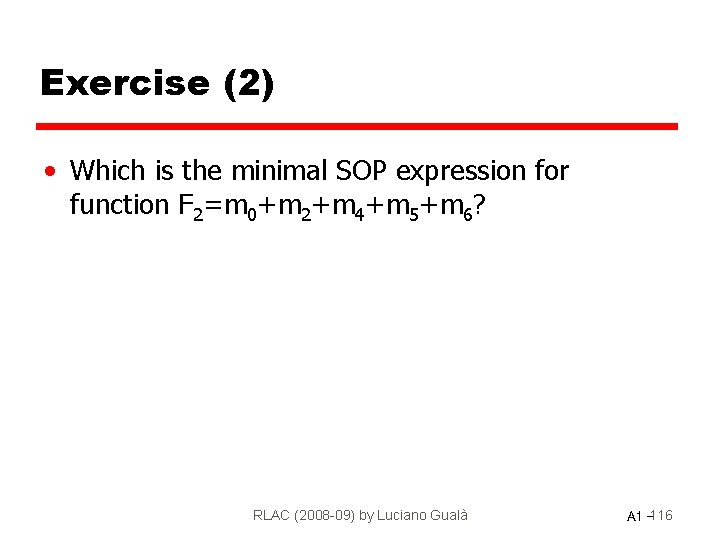

Exercise (2) • Which is the minimal SOP expression for function F 2=m 0+m 2+m 4+m 5+m 6? RLAC (2008 -09) by Luciano Gualà A 1 -116

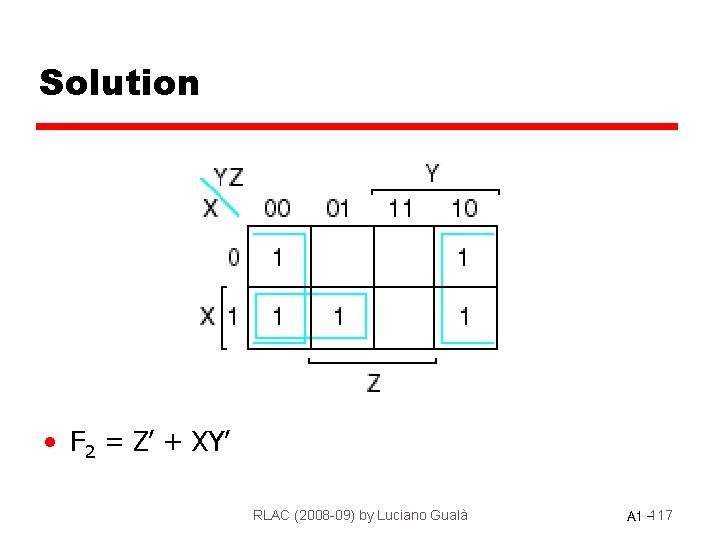

Solution • F 2 = Z’ + XY’ RLAC (2008 -09) by Luciano Gualà A 1 -117

k-cube of 1 s • • • Is a set of 2 k adjacent cells 0 -cube, 1 cell, a minterm 1 -cube, 2 adjacent cells 2 -cube, 4 adjacent cells 3 -cube, 8 adjacent cells …. RLAC (2008 -09) by Luciano Gualà A 1 -118

Prime implicants • a product term P is said to be an implicant for a function F if P implies F, i. e. if P is true then F is true • The product term corresponding to a k-cube is an implicant • An implicant is said to be a prime implicant for F if it does not imply any other implicant of F • A prime implicant can be chosen by selecting a maximal kcube, i. e. a k-cube in the KM which is not contained in any larger h-cube (h>k) RLAC (2008 -09) by Luciano Gualà A 1 -119

Minimal representation F = P 1 + P 2 + P 3 +. . . has a minimal SOP representation if: 1. Each Pi is a prime implicant 2. There is a minimum number of them RLAC (2008 -09) by Luciano Gualà A 1 -120

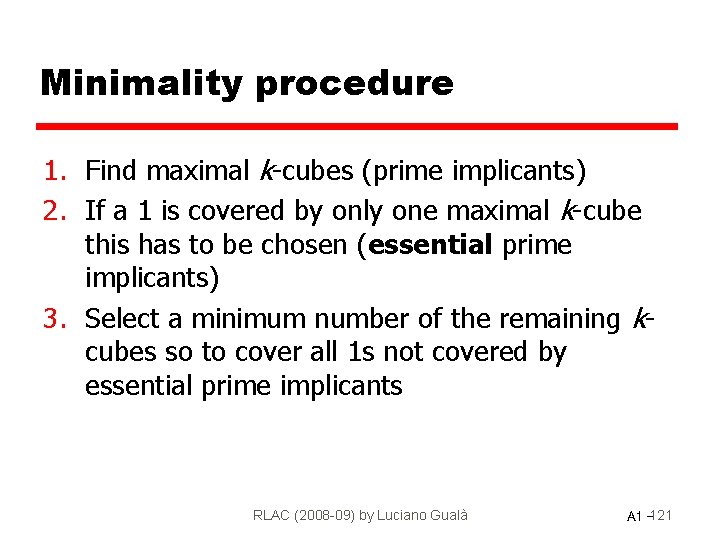

Minimality procedure 1. Find maximal k-cubes (prime implicants) 2. If a 1 is covered by only one maximal k-cube this has to be chosen (essential prime implicants) 3. Select a minimum number of the remaining kcubes so to cover all 1 s not covered by essential prime implicants RLAC (2008 -09) by Luciano Gualà A 1 -121

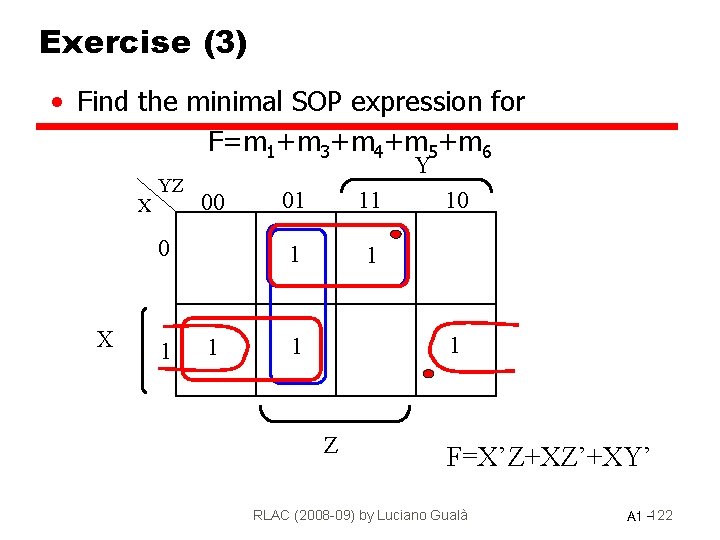

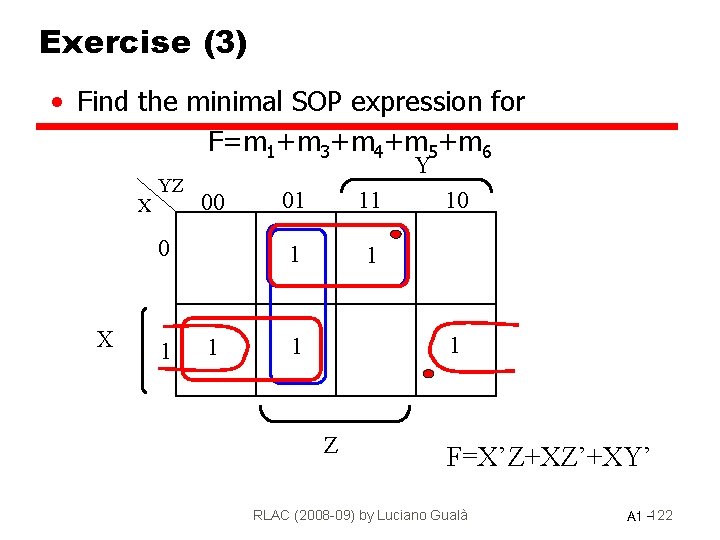

Exercise (3) • Find the minimal SOP expression for F=m 1+m 3+m 4+m 5+m 6 X YZ Y 00 0 X 1 1 01 11 1 1 10 1 1 Z F=X’Z+XZ’+XY’ RLAC (2008 -09) by Luciano Gualà A 1 -122

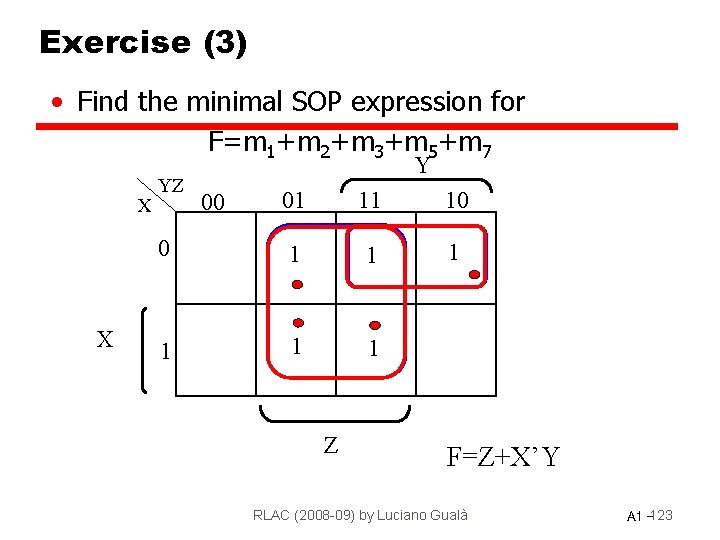

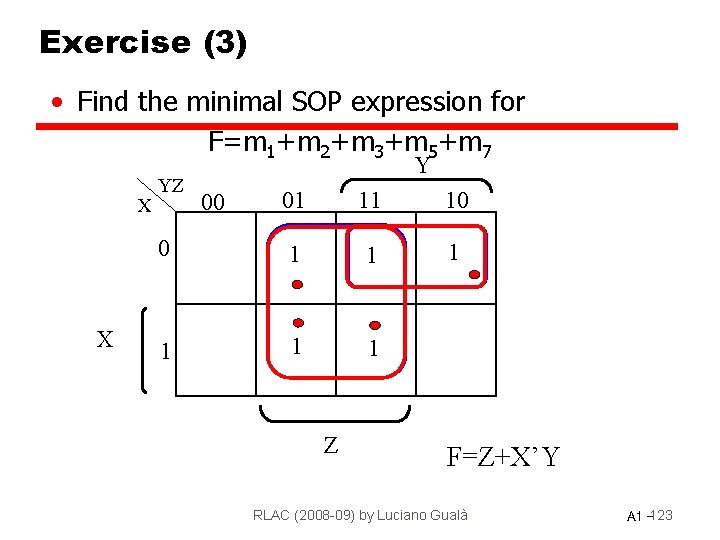

Exercise (3) • Find the minimal SOP expression for F=m 1+m 2+m 3+m 5+m 7 X X YZ Y 01 11 10 0 1 1 1 00 Z F=Z+X’Y RLAC (2008 -09) by Luciano Gualà A 1 -123

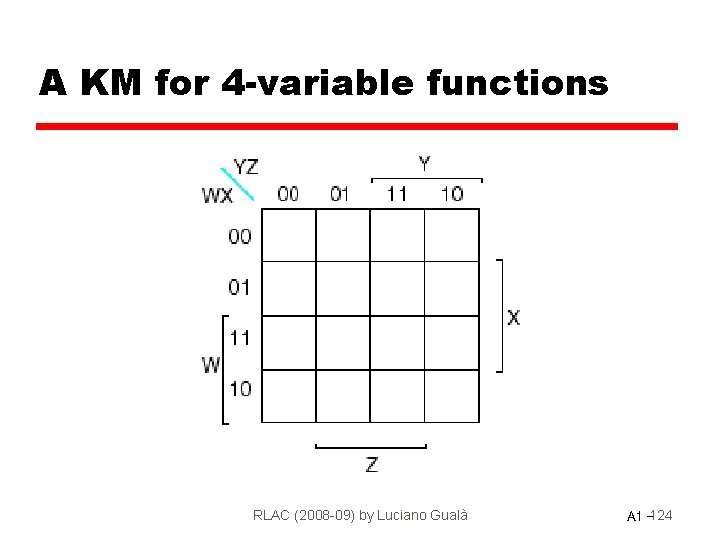

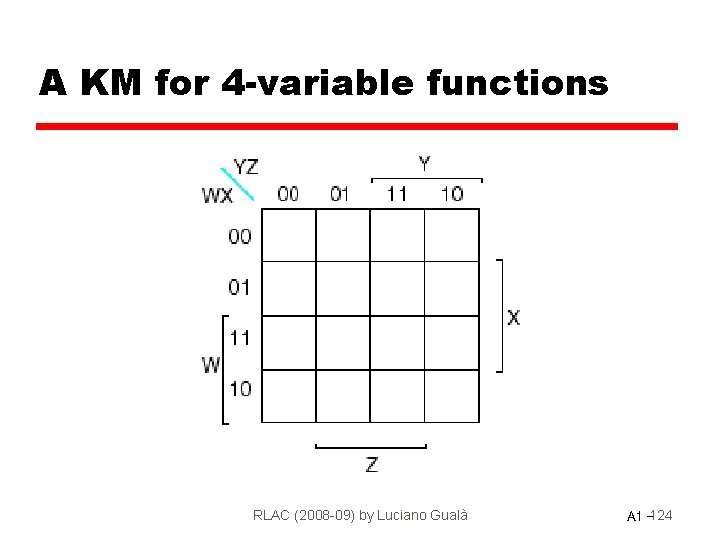

A KM for 4 -variable functions RLAC (2008 -09) by Luciano Gualà A 1 -124

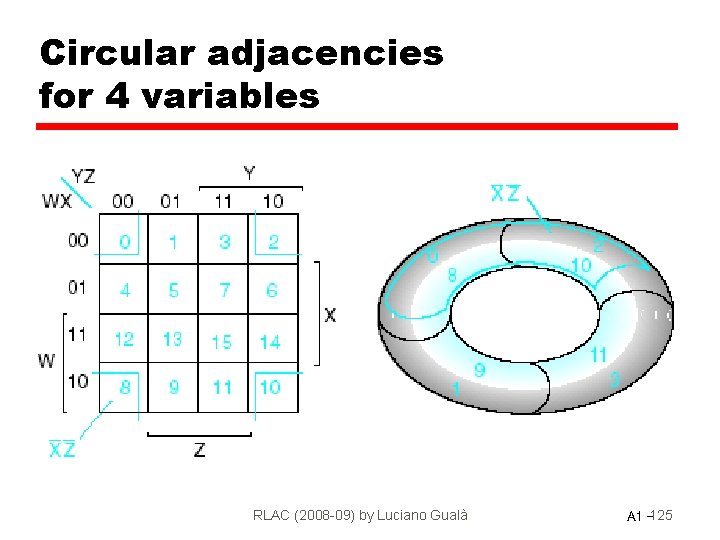

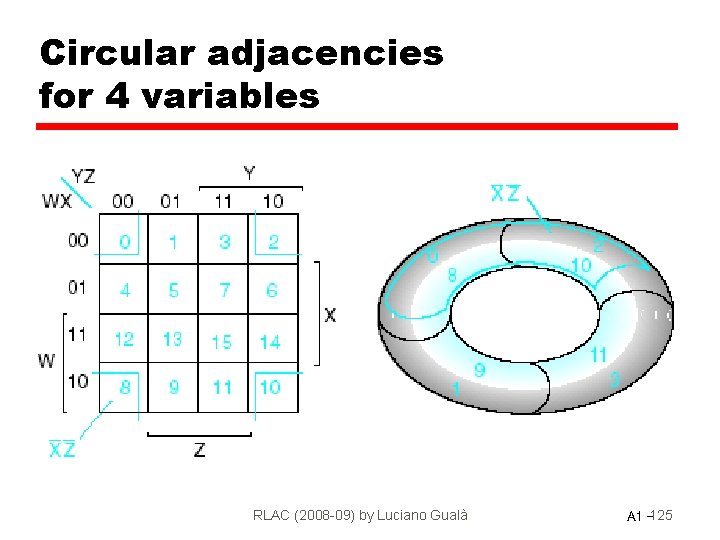

Circular adjacencies for 4 variables RLAC (2008 -09) by Luciano Gualà A 1 -125

Four Variable Terms § Four variable maps can have rectangles corresponding to: • A single 1 = 4 variables, (i. e. Minterm) • Two 1 s = 3 variables, • Four 1 s = 2 variables • Eight 1 s = 1 variable, • Sixteen 1 s = zero variables (i. e. Constant "1") RLAC (2008 -09) by Luciano Gualà A 1 -126

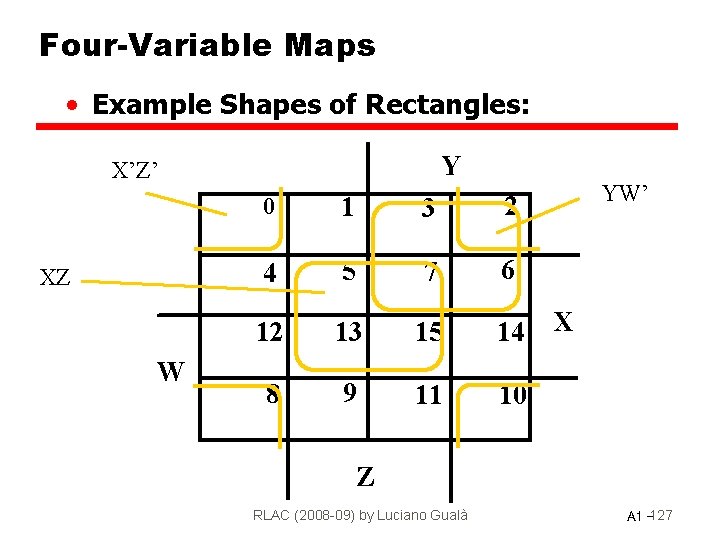

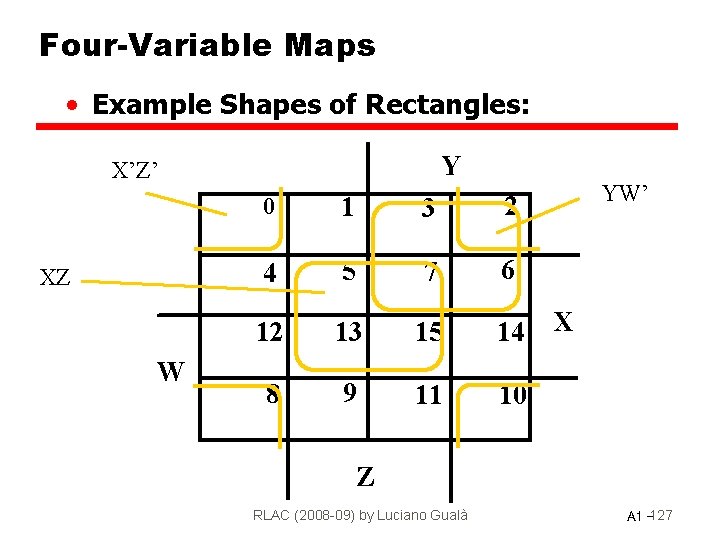

Four-Variable Maps • Example Shapes of Rectangles: Y X’Z’ XZ W 0 1 3 2 4 5 7 6 12 13 15 14 8 9 11 10 YW’ X Z RLAC (2008 -09) by Luciano Gualà A 1 -127

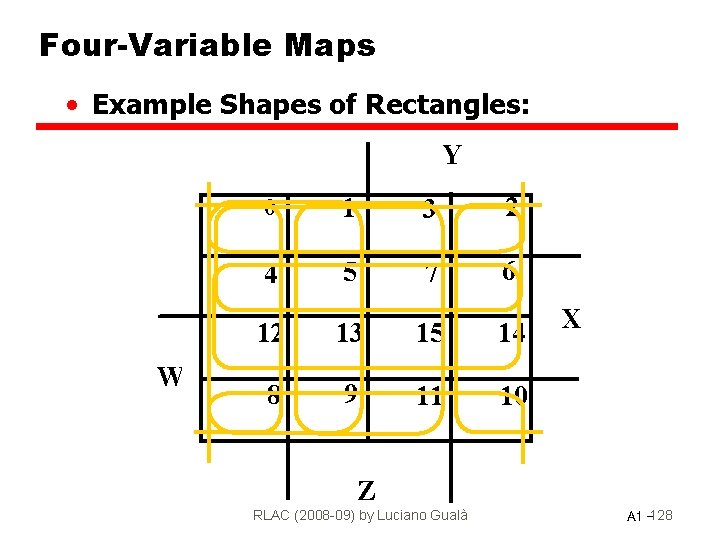

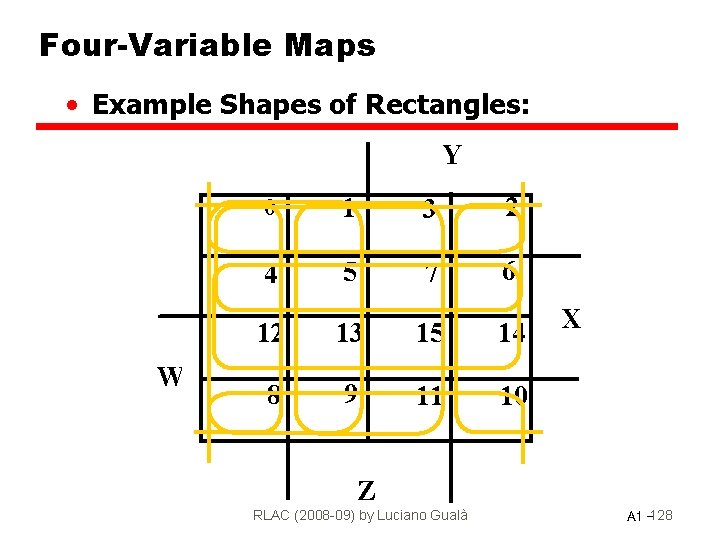

Four-Variable Maps • Example Shapes of Rectangles: Y W 0 1 3 2 4 5 7 6 12 13 15 14 8 9 11 10 X Z RLAC (2008 -09) by Luciano Gualà A 1 -128

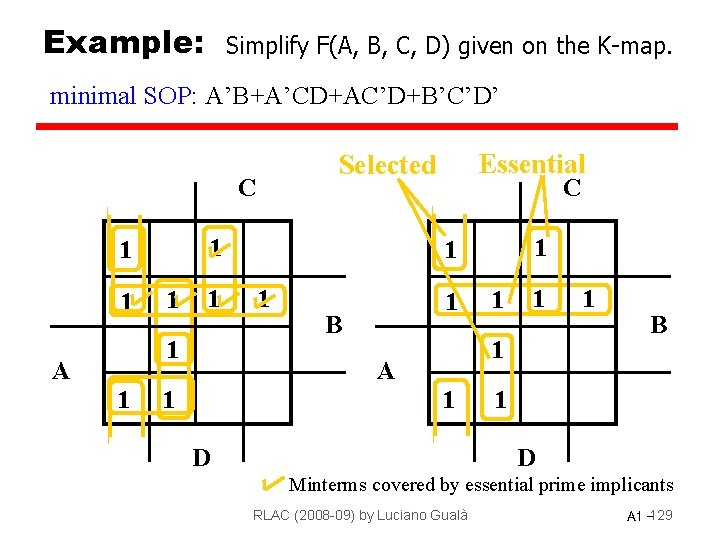

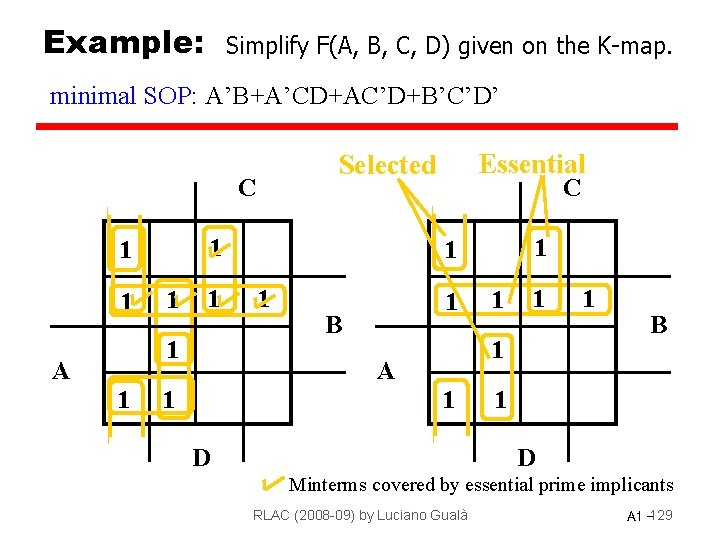

Example: Simplify F(A, B, C, D) given on the K-map. minimal SOP: A’B+A’CD+AC’D+B’C’D’ C 1 1 1 A 1 Essential Selected C 1 1 B 1 1 1 A 1 1 D 1 B 1 D Minterms covered by essential prime implicants RLAC (2008 -09) by Luciano Gualà A 1 -129

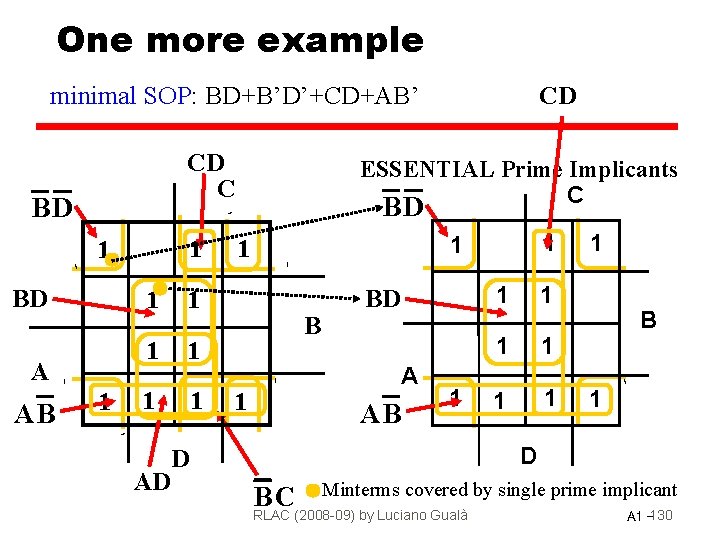

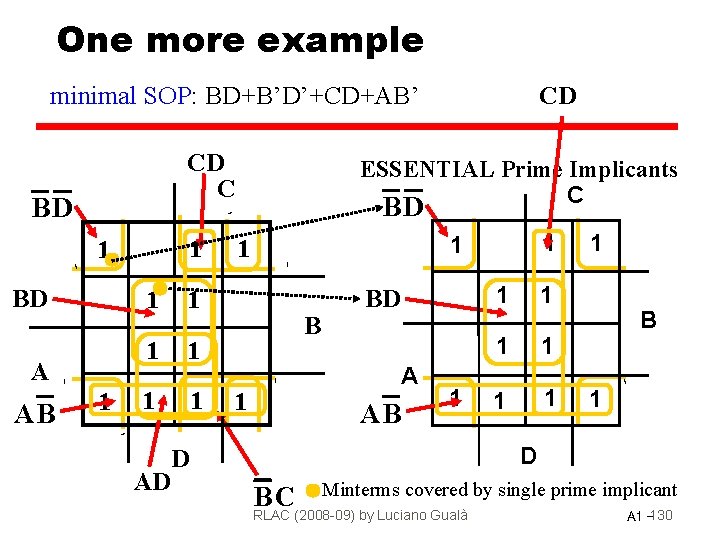

One more example CD minimal SOP: BD+B’D’+CD+AB’ CD C BD 1 1 BD A AB 1 1 1 1 D AD ESSENTIAL Prime Implicants C BD B 1 1 1 BD 1 B A AB 1 1 1 1 D Minterms covered by single prime implicant B C RLAC (2008 -09) by Luciano Gualà 130 A 1 -

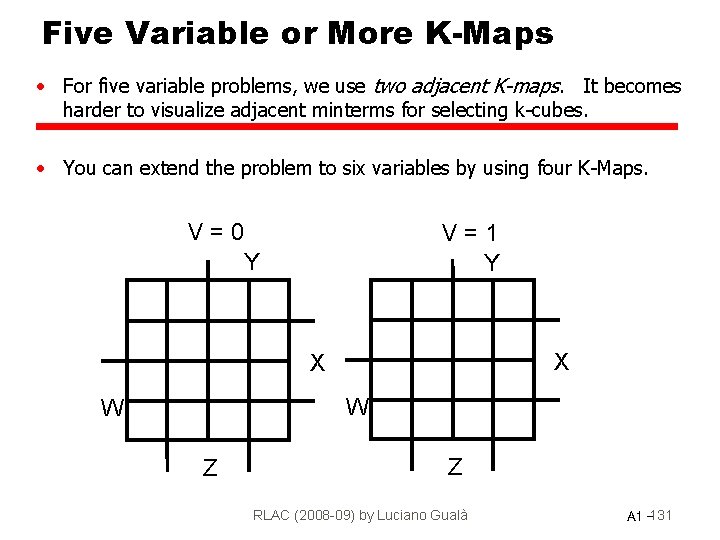

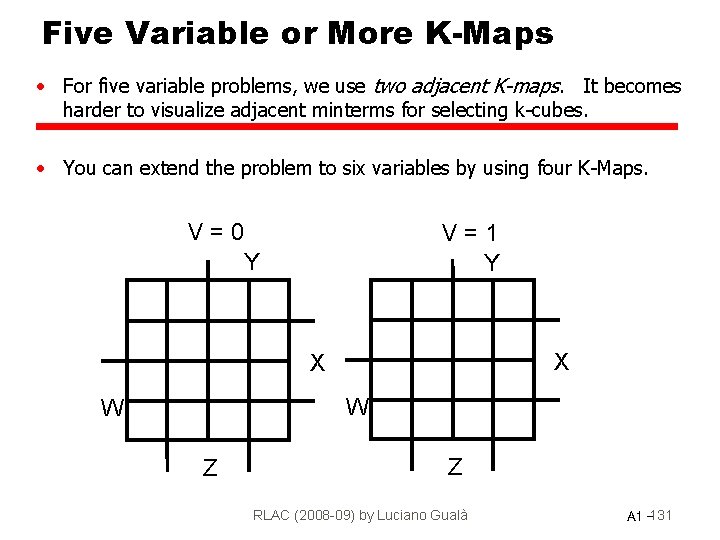

Five Variable or More K-Maps • For five variable problems, we use two adjacent K-maps. It becomes harder to visualize adjacent minterms for selecting k-cubes. • You can extend the problem to six variables by using four K-Maps. V=0 Y V=1 Y X X W W Z Z RLAC (2008 -09) by Luciano Gualà A 1 -131

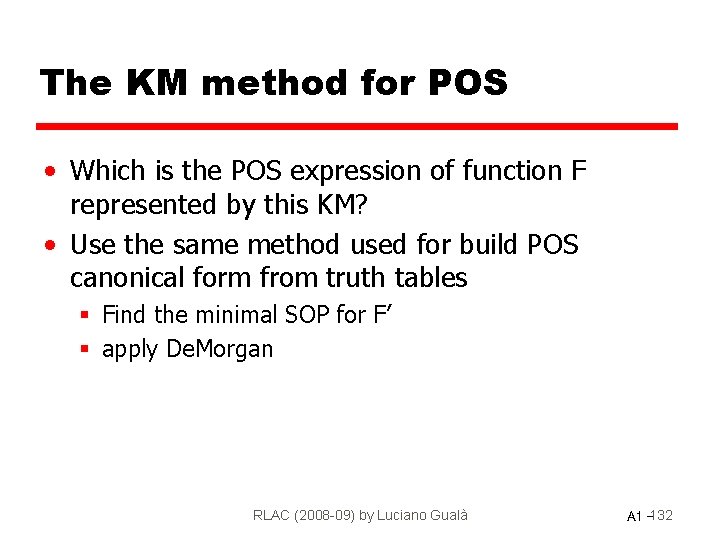

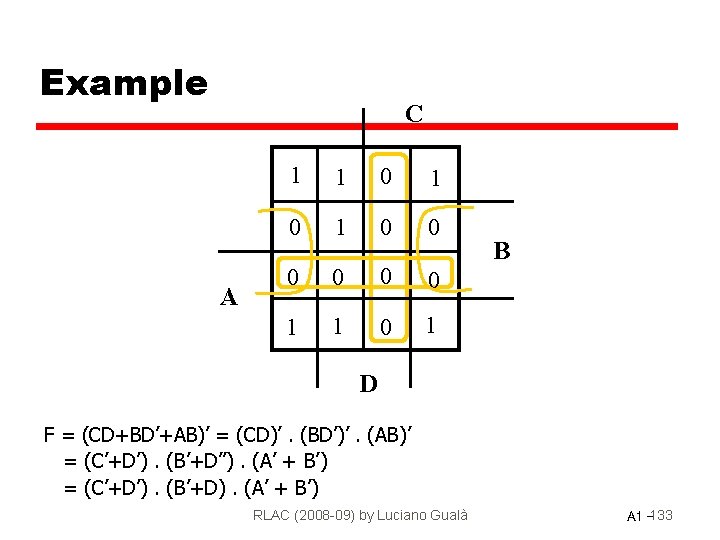

The KM method for POS • Which is the POS expression of function F represented by this KM? • Use the same method used for build POS canonical form from truth tables § Find the minimal SOP for F’ § apply De. Morgan RLAC (2008 -09) by Luciano Gualà A 1 -132

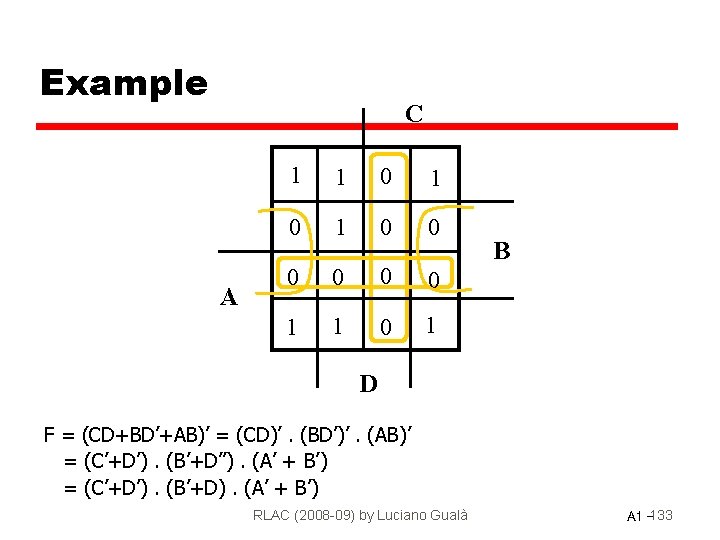

Example C A 1 1 0 1 0 0 0 1 1 0 1 B D F = (CD+BD’+AB)’ = (CD)’. (BD’)’. (AB)’ = (C’+D’). (B’+D’’). (A’ + B’) = (C’+D’). (B’+D). (A’ + B’) RLAC (2008 -09) by Luciano Gualà A 1 -133

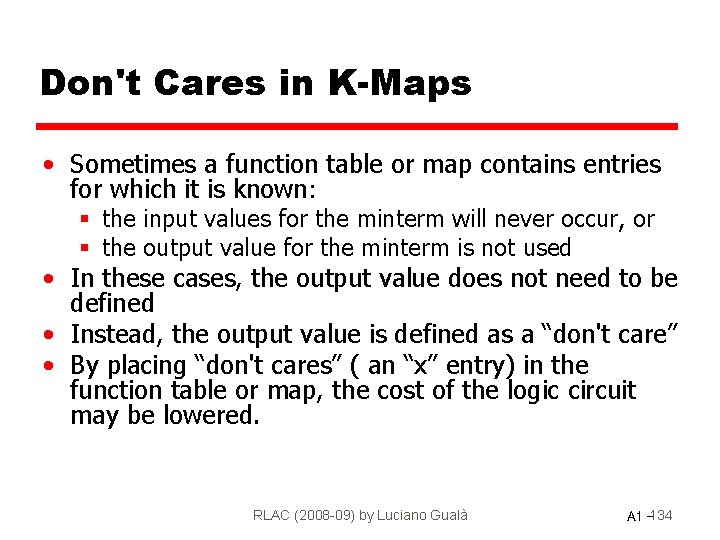

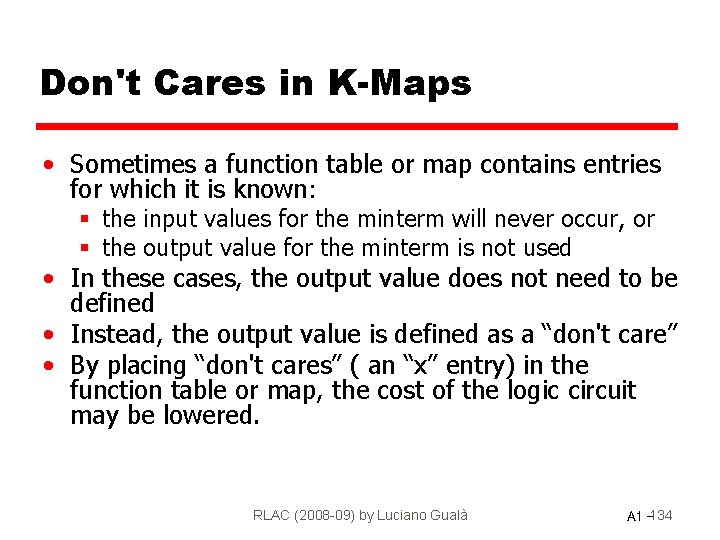

Don't Cares in K-Maps • Sometimes a function table or map contains entries for which it is known: § the input values for the minterm will never occur, or § the output value for the minterm is not used • In these cases, the output value does not need to be defined • Instead, the output value is defined as a “don't care” • By placing “don't cares” ( an “x” entry) in the function table or map, the cost of the logic circuit may be lowered. RLAC (2008 -09) by Luciano Gualà A 1 -134

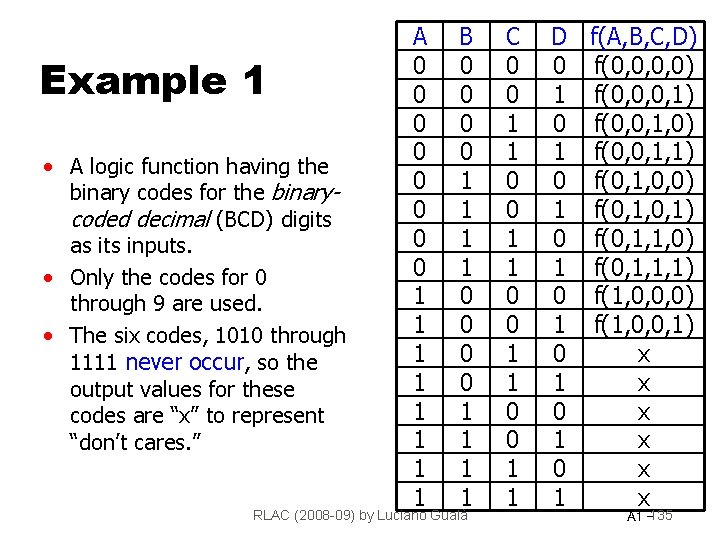

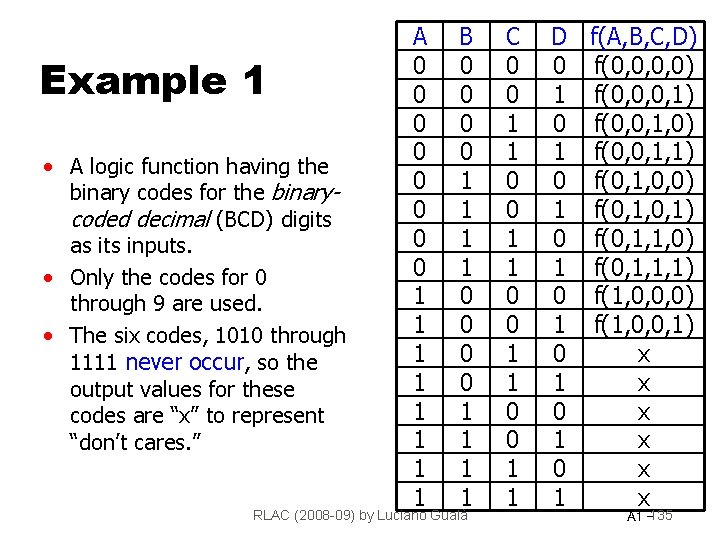

Example 1 • A logic function having the binary codes for the binarycoded decimal (BCD) digits as its inputs. • Only the codes for 0 through 9 are used. • The six codes, 1010 through 1111 never occur, so the output values for these codes are “x” to represent “don’t cares. ” A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 RLAC (2008 -09) by Luciano Gualà C 0 0 1 1 D f(A, B, C, D) 0 f(0, 0, 0, 0) 1 f(0, 0, 0, 1) 0 f(0, 0, 1, 0) 1 f(0, 0, 1, 1) 0 f(0, 1, 0, 0) 1 f(0, 1, 0, 1) 0 f(0, 1, 1, 0) 1 f(0, 1, 1, 1) 0 f(1, 0, 0, 0) 1 f(1, 0, 0, 1) 0 x 1 x A 1 -135

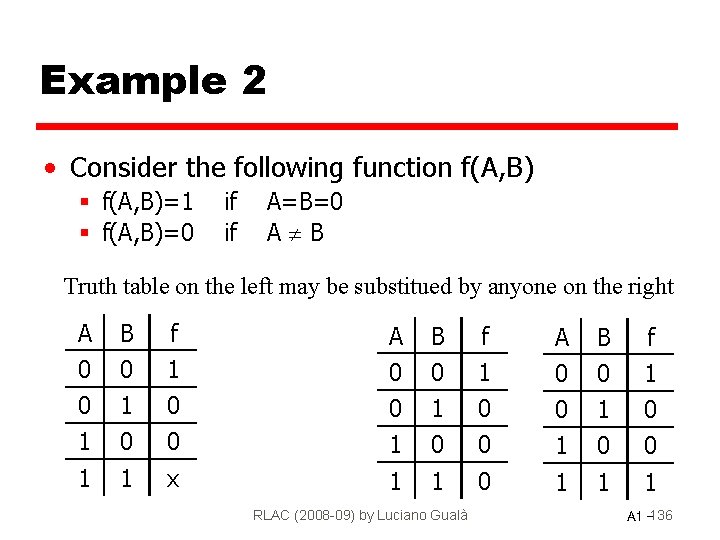

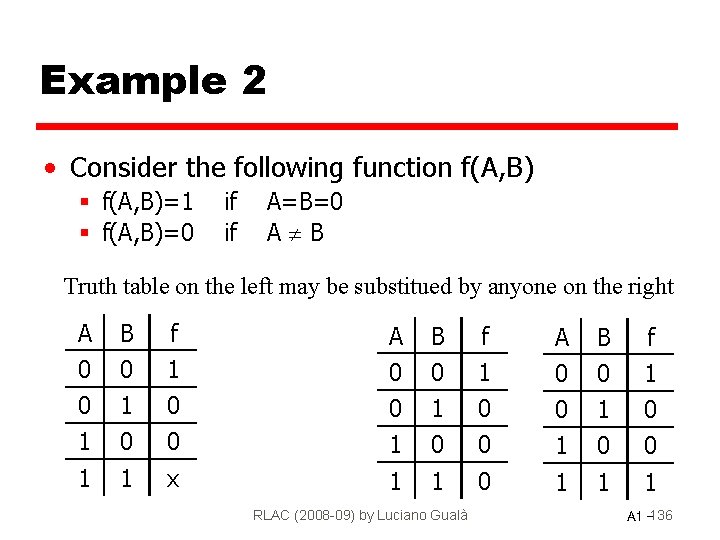

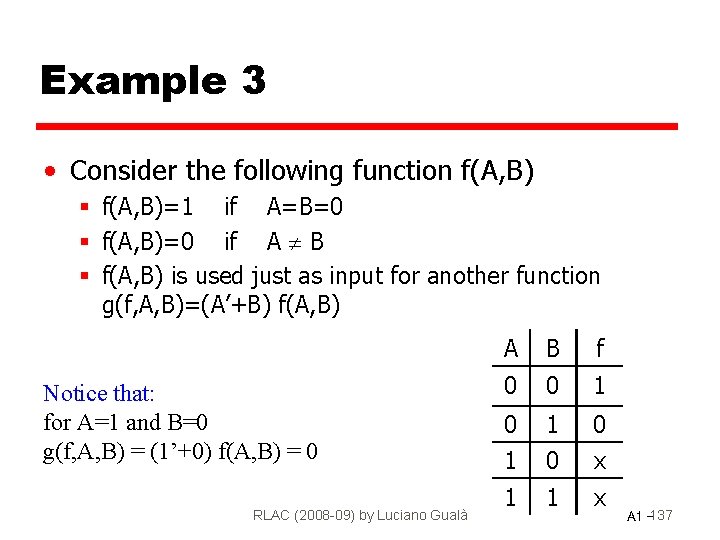

Example 2 • Consider the following function f(A, B) § f(A, B)=1 § f(A, B)=0 if if A=B=0 A B Truth table on the left may be substitued by anyone on the right A B f 0 0 1 0 1 0 0 1 1 x 1 1 0 1 1 1 RLAC (2008 -09) by Luciano Gualà A 1 -136

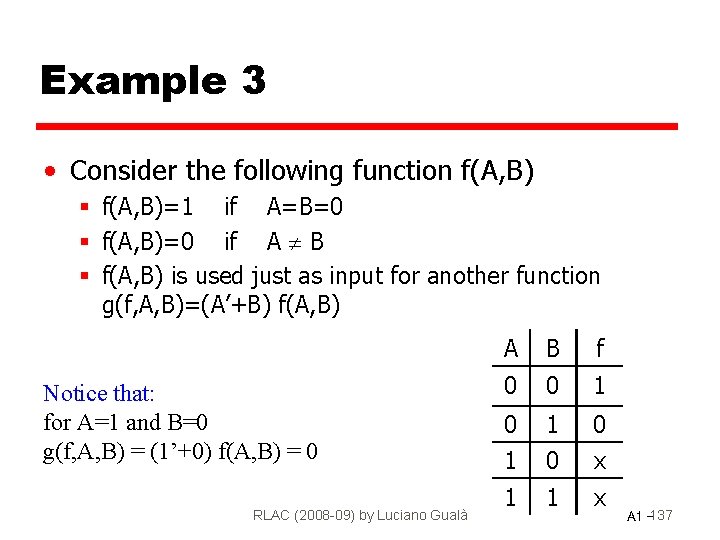

Example 3 • Consider the following function f(A, B) § f(A, B)=1 if A=B=0 § f(A, B)=0 if A B § f(A, B) is used just as input for another function g(f, A, B)=(A’+B) f(A, B) Notice that: for A=1 and B=0 g(f, A, B) = (1’+0) f(A, B) = 0 RLAC (2008 -09) by Luciano Gualà A B f 0 0 1 0 1 0 x 1 1 x A 1 -137

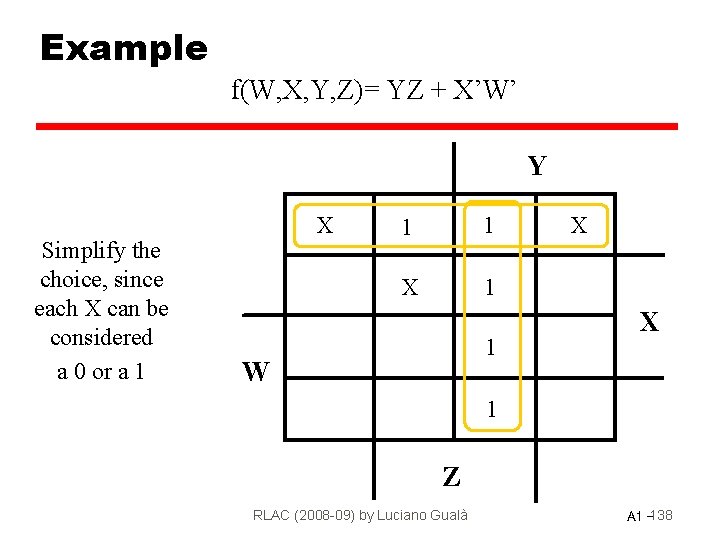

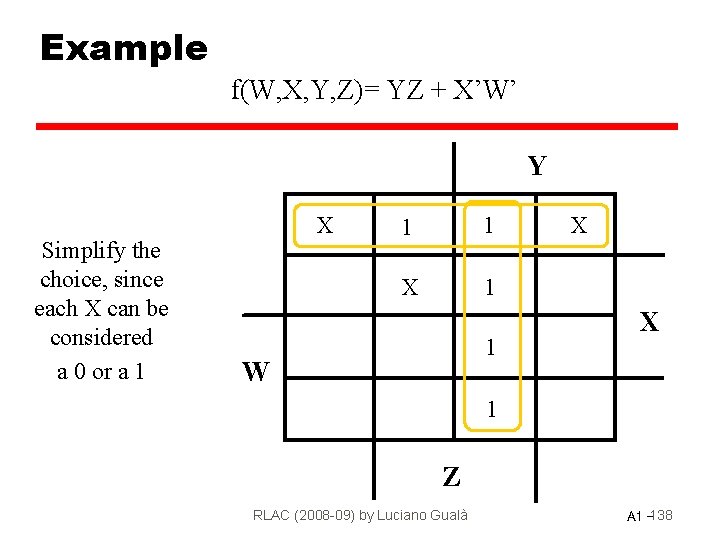

Example f(W, X, Y, Z)= YZ + X’W’ Y Simplify the choice, since each X can be considered a 0 or a 1 X 1 1 W X X 1 Z RLAC (2008 -09) by Luciano Gualà A 1 -138

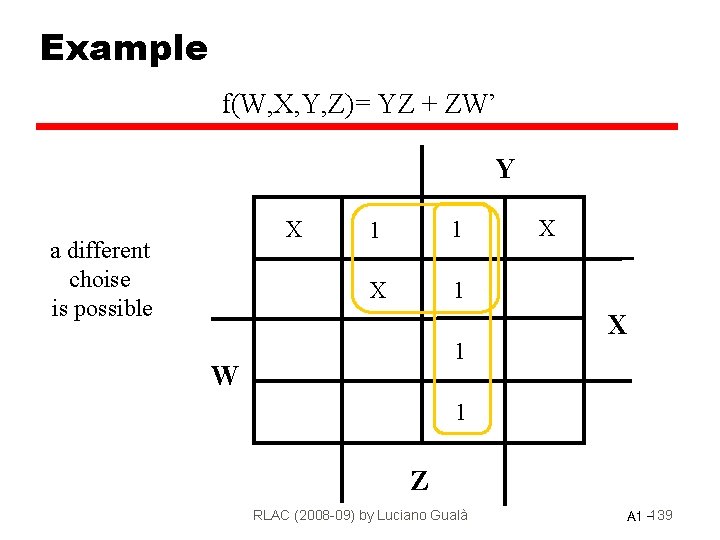

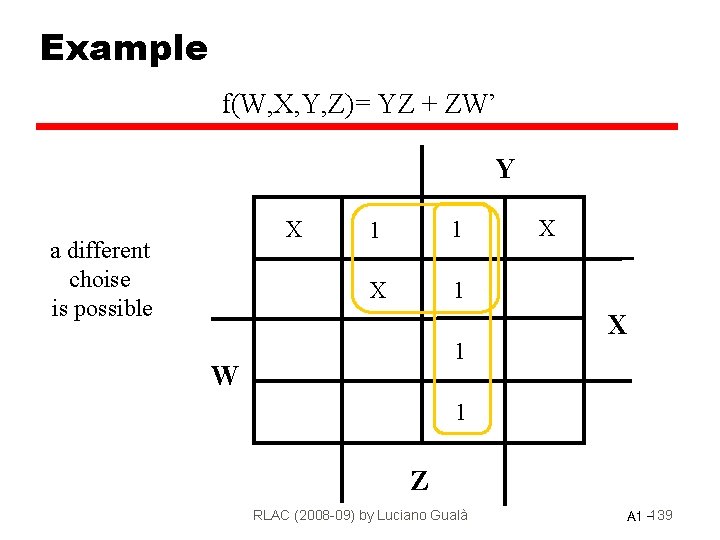

Example f(W, X, Y, Z)= YZ + ZW’ Y X a different choise is possible 1 1 X 1 1 W X X 1 Z RLAC (2008 -09) by Luciano Gualà A 1 -139

Multiple-Level Optimization • Multiple-level circuits - circuits that are not twolevel • Multiple-level circuits can have reduced gate input cost compared to two-level (SOP and POS) circuits • Multiple-level optimization is performed by applying transformations to circuits represented by equations while evaluating cost RLAC (2008 -09) by Luciano Gualà A 1 -140

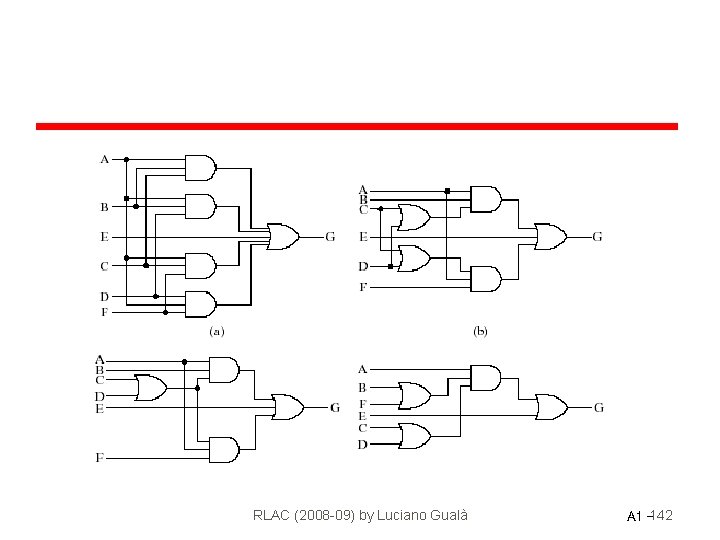

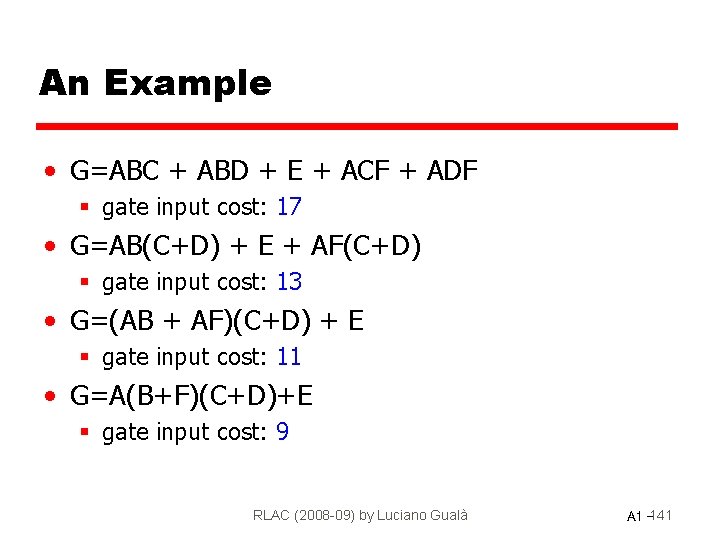

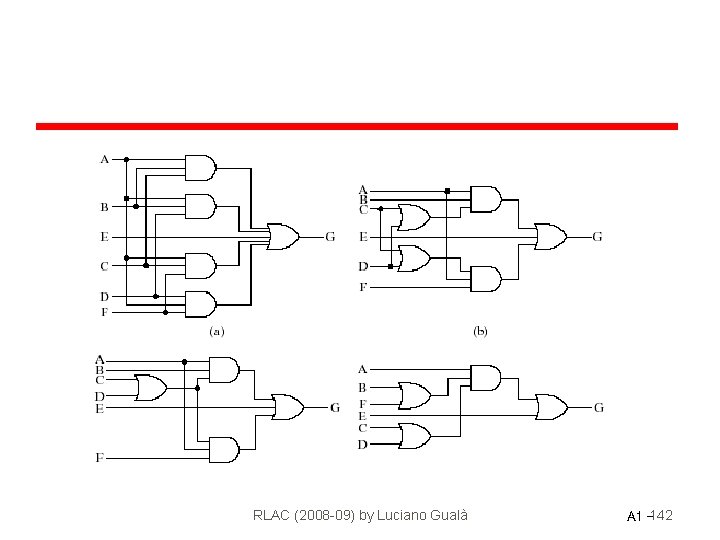

An Example • G=ABC + ABD + E + ACF + ADF § gate input cost: 17 • G=AB(C+D) + E + AF(C+D) § gate input cost: 13 • G=(AB + AF)(C+D) + E § gate input cost: 11 • G=A(B+F)(C+D)+E § gate input cost: 9 RLAC (2008 -09) by Luciano Gualà A 1 -141

RLAC (2008 -09) by Luciano Gualà A 1 -142