Combinational Logic Design Combinational Circuits A combinational logic

Combinational Logic Design

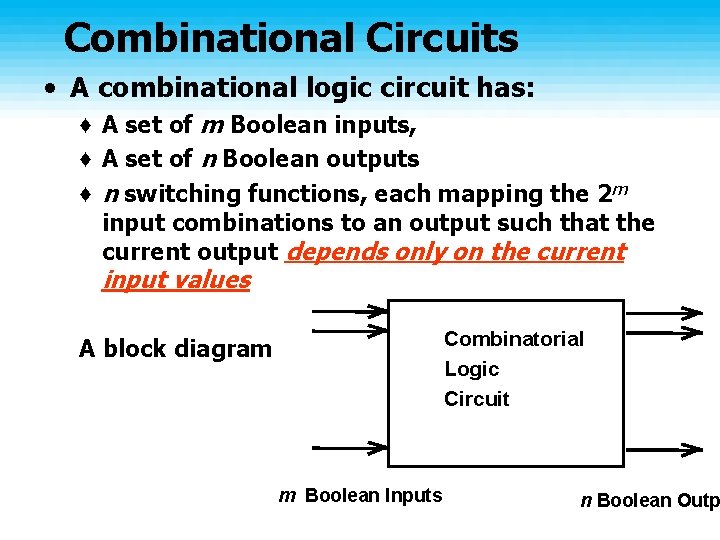

Combinational Circuits • A combinational logic circuit has: ♦ A set of m Boolean inputs, ♦ A set of n Boolean outputs ♦ n switching functions, each mapping the 2 m input combinations to an output such that the current output depends only on the current input values Combinatorial Logic Circuit A block diagram m Boolean Inputs n Boolean Outp

Design Procedure 1. Specification • Write a specification for the circuit if one is not already available 2. Formulation • Derive a truth table or initial Boolean equations that define the required relationships between the inputs and outputs, if not in the specification • Apply hierarchical design if appropriate (more later) 3

Design Procedure 3. Optimization • Apply 2 -level and multiple-level optimization • Draw a logic diagram for the resulting circuit using ANDs, ORs, and inverters 4

Design Procedure 4. Technology Mapping • Map the logic diagram or netlist to the implementation technology selected 5. Verification • Verify the correctness of the final design manually or using simulation 5

Hierarchical Design § Objective: To control the complexity of each function which is mapping inputs to outputs • Decompose the function into smaller pieces called blocks • Decompose each block’s function into smaller blocks, repeating as necessary until all blocks are small enough • Any block not decomposed is called a primitive block • The collection of all blocks including the decomposed ones is a hierarchy 6

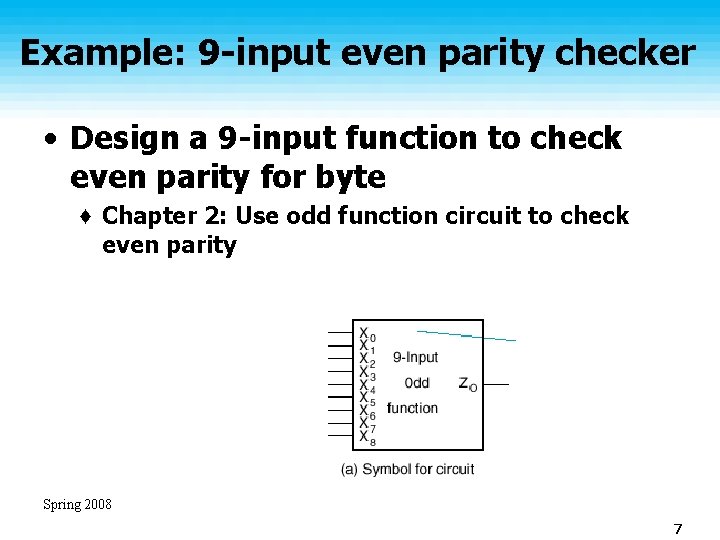

Example: 9 -input even parity checker • Design a 9 -input function to check even parity for byte ♦ Chapter 2: Use odd function circuit to check even parity Spring 2008 7

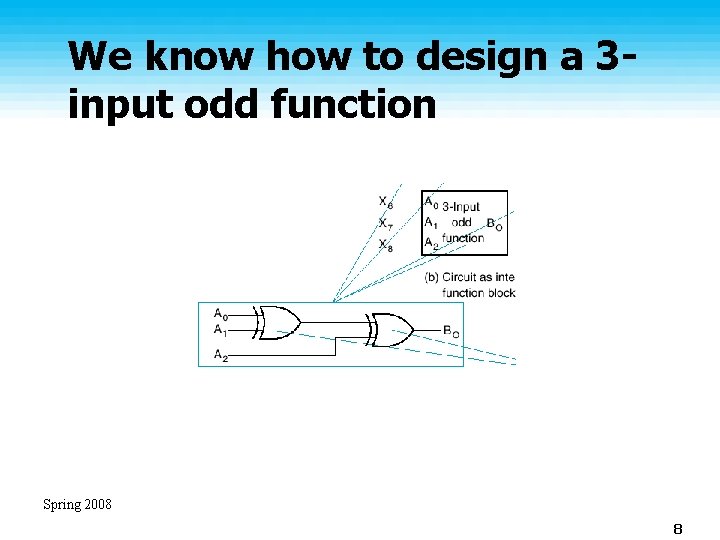

We know how to design a 3 input odd function Spring 2008 8

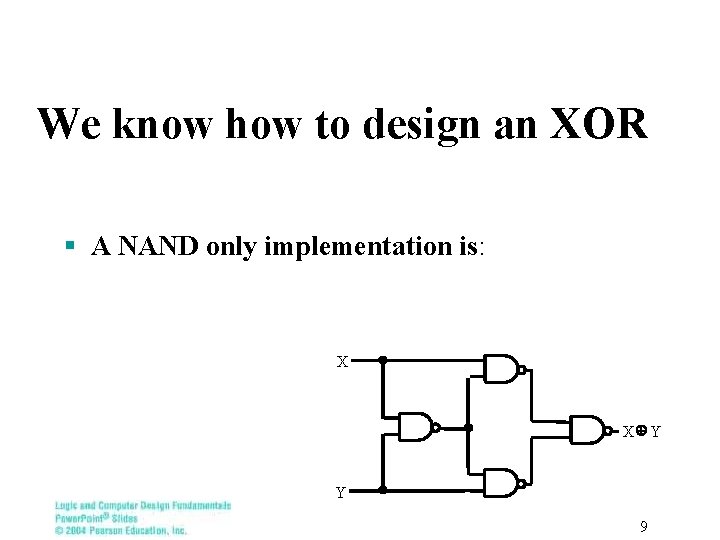

We know how to design an XOR § A NAND only implementation is: X X Y Y 9

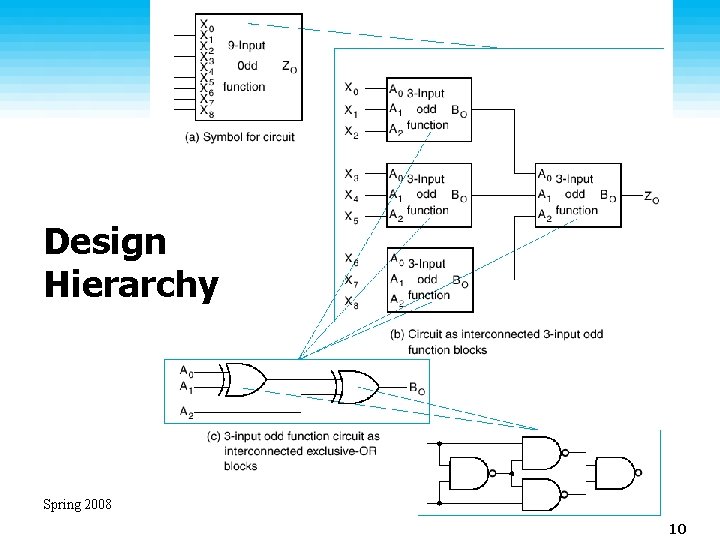

Design Hierarchy Spring 2008 10

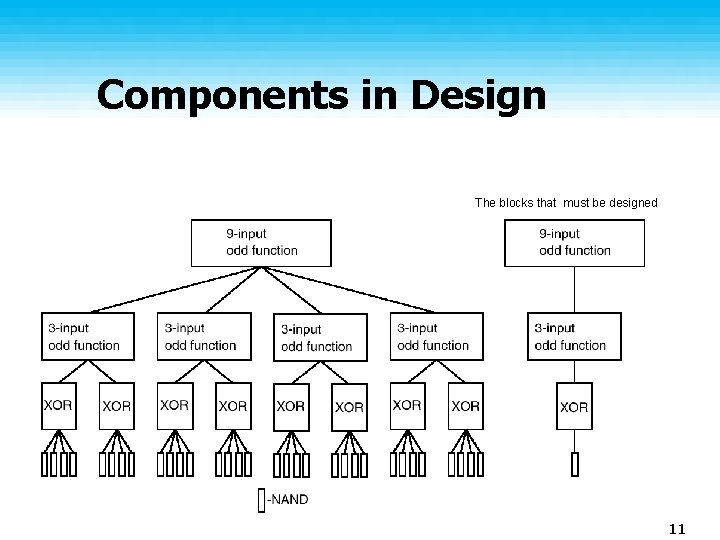

Components in Design The blocks that must be designed Spring 2008 11

9 -input parity tree (continued) • Top Level: 9 inputs, one output • 2 nd Level: Four 3 -bit odd funcions in two levels • 3 rd Level: Two 2 -bit exclusive-OR functions • Primitive block, XOR gate: Four 2 input NAND gates • Design requires {4 X (2 X 4)} = 32 2 -input NAND gates Spring 2008 12

Top Down Design • Ideally you specify top level of design and work your way down • Real life isn’t that way ♦ ♦ Work some at top Build/test some low-level blocks Go back to top level Just like real software programs • Big projects (like Pentium) done with architecture and levels of simulators Spring 2008 13

- Slides: 13