MC 542 Organizao de Computadores Teoria e Prtica

![Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-36.jpg)

![Array // high-level code int array[5]; array[0] = array[0] * 2; array[1] = array[1] Array // high-level code int array[5]; array[0] = array[0] * 2; array[1] = array[1]](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-87.jpg)

![Array Usando For // high-level code int array[1000]; int i; for (i=0; i < Array Usando For // high-level code int array[1000]; int i; for (i=0; i <](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-88.jpg)

- Slides: 132

MC 542 Organização de Computadores Teoria e Prática 2007 Prof. Paulo Cesar Centoducatte@ic. unicamp. br www. ic. unicamp. br/~ducatte MC 542 A-1. 1

MC 542 Arquitetura de Computadores Introdução; Conjunto de Instruções “DDCA” - (Capítulo 6) “COD” - (Capítulo ) MC 542 A-1. 2

Arquitetura de Computadores Sumário • Introdução – O que é arquitetura de computadores – Tendências » » • Lei de Moore Capacidade Microprocessadores Desempenho dos processadores Capacidade e Velocidade das Memórias Conjuntos de Instruções – Introdução MC 542 A-1. 3

O que é Arquitetura de Computadores? • 1950 s a 1960 s: Cursos de AC Aritmética Computacional • 1970 s a meados anos 1980 s: Cursos de AC Projeto do Conjunto de Instruções (ISA), especialmente voltado para compiladores • 1990 s a 2000 s: Cursos de AC Projeto de CPU, Sistemas de Memórias, Sistemas de I/O, Multiprocessadores. MC 542 A-1. 4

Tendências • Gordon Moore (fundador da Intel), em 1965 observou que o número de transistores em um chip dobrava a cada ano (Lei de Moore) Continua valida até os dias de hoje (porém está encontrando a barreira térmica) • O desempenho dos processadores, medidos por diversos benchmarks, também tem crescido de forma acelerada. • A capacidade das memórias tem aumentado significativamente nos últimos 20 anos (E o custo reduzido) • MC 542 A-1. 5

Qual a Razão Desta Evolução nos Últimos Anos? • Desempenho – Avanços tecnológicos » Domínio de CMOS sobre as tecnologias mais antigas (TTL, ECL) em custo e desempenho – Avanços nas arquiteturas » RISC, superscalar, VLIW, RAID, … • Preço: Baixo custo devido – Desenvolvimento mais simples » CMOS VLSI: sistemas menores, menos componentes – Alto volume (escala) • . . . MC 542 A-1. 6

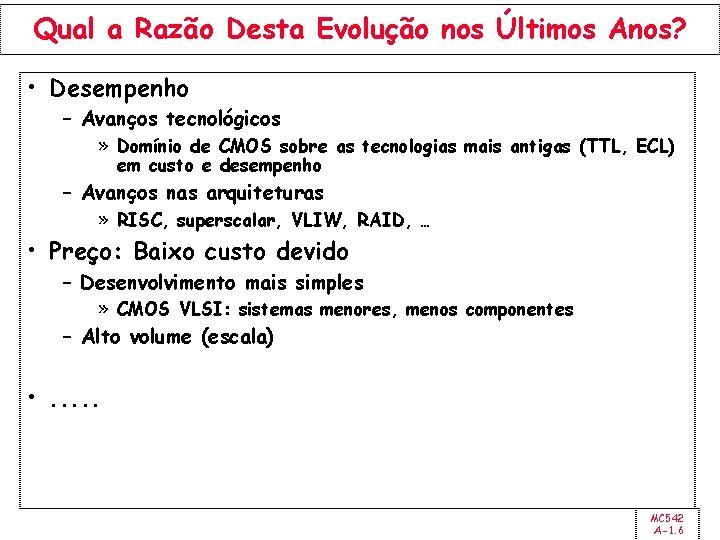

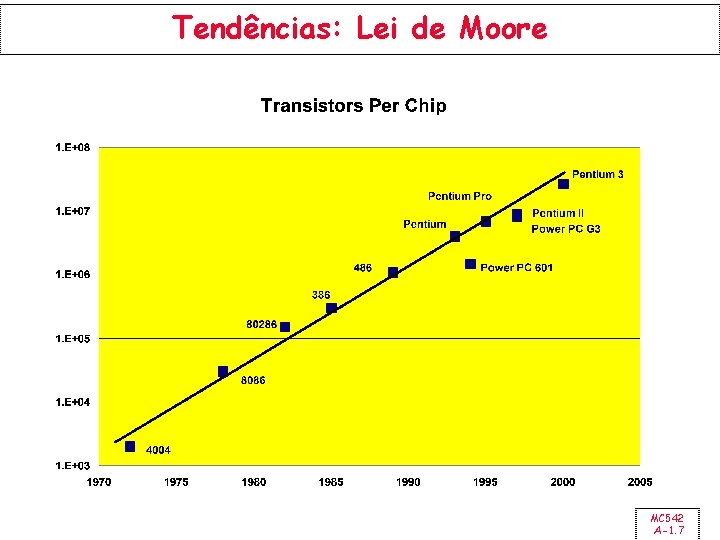

Tendências: Lei de Moore MC 542 A-1. 7

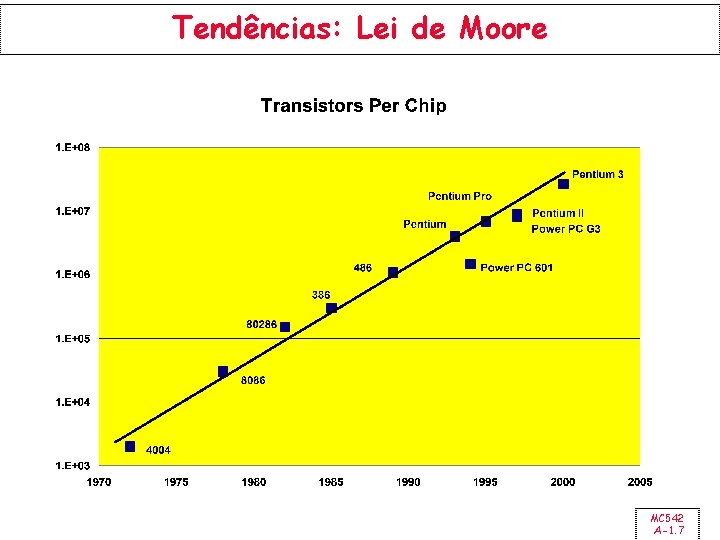

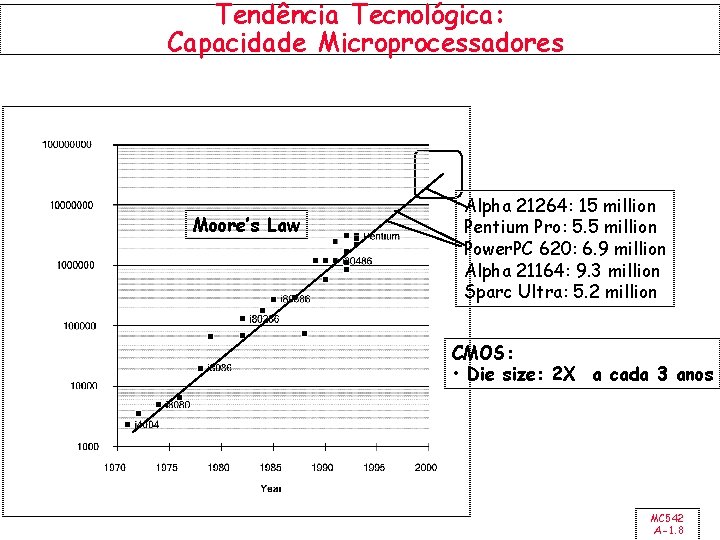

Tendência Tecnológica: Capacidade Microprocessadores Moore’s Law Alpha 21264: 15 million Pentium Pro: 5. 5 million Power. PC 620: 6. 9 million Alpha 21164: 9. 3 million Sparc Ultra: 5. 2 million CMOS: • Die size: 2 X a cada 3 anos MC 542 A-1. 8

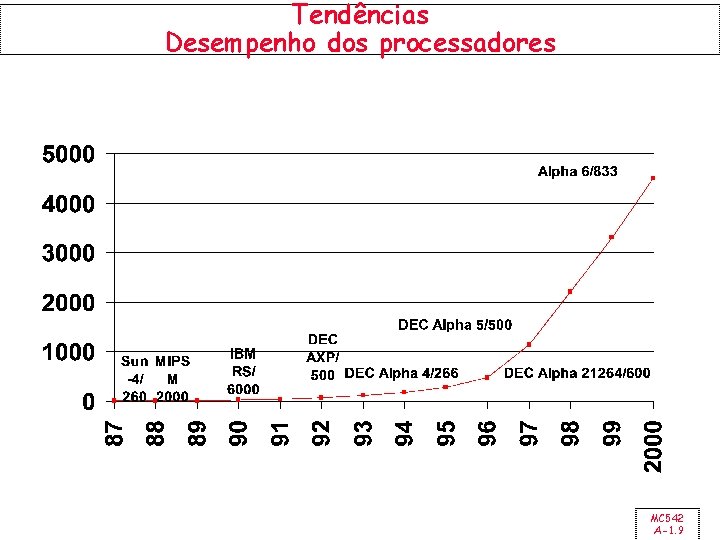

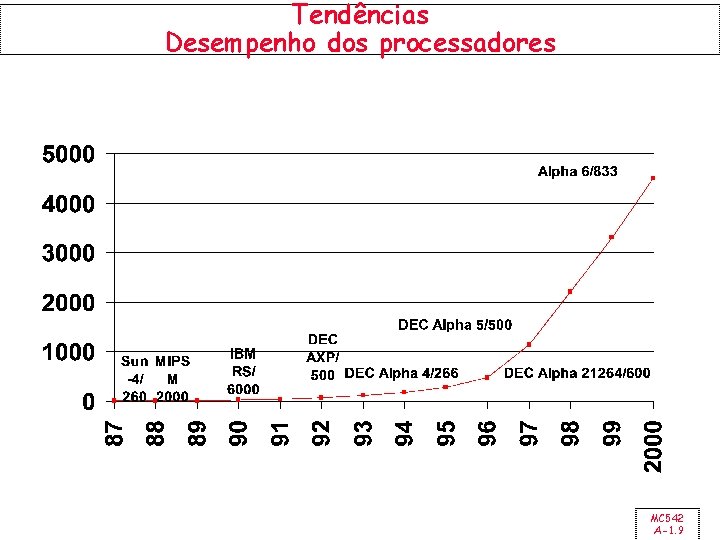

Tendências Desempenho dos processadores MC 542 A-1. 9

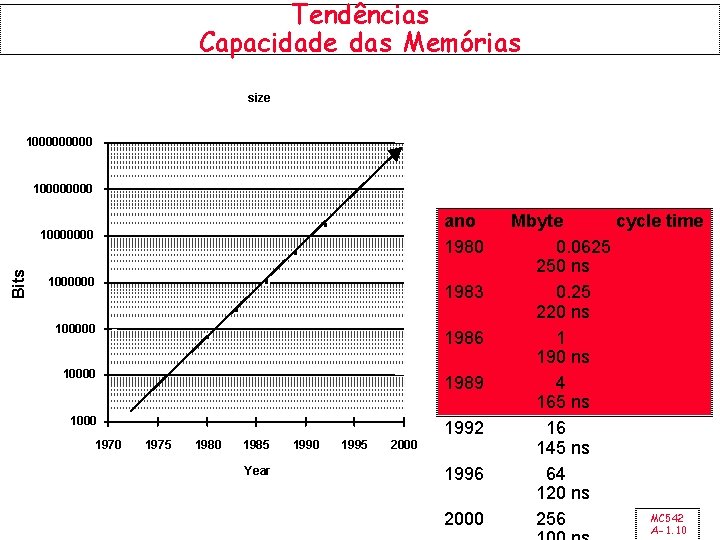

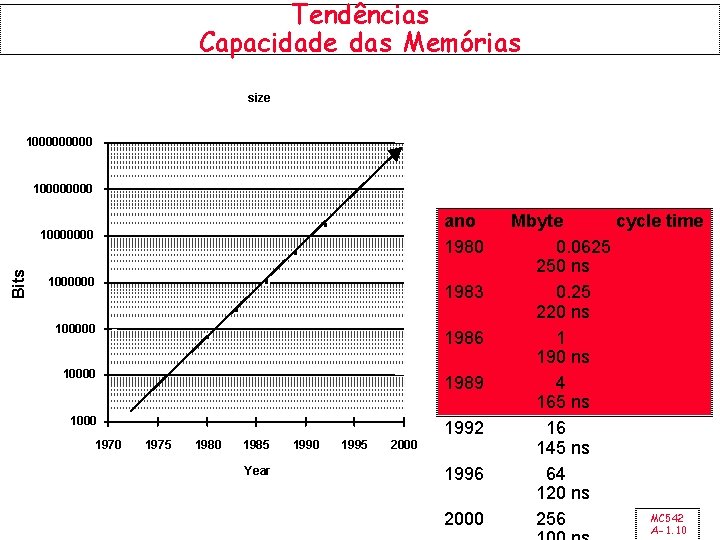

Tendências Capacidade das Memórias size 100000 10000 ano 1980 Bits 10000000 1983 100000 1986 10000 1989 1000 1992 1970 1975 1980 1985 Year 1990 1995 2000 1996 2000 Mbyte cycle time 0. 0625 250 ns 0. 25 220 ns 1 190 ns 4 165 ns 16 145 ns 64 120 ns MC 542 256 A-1. 10

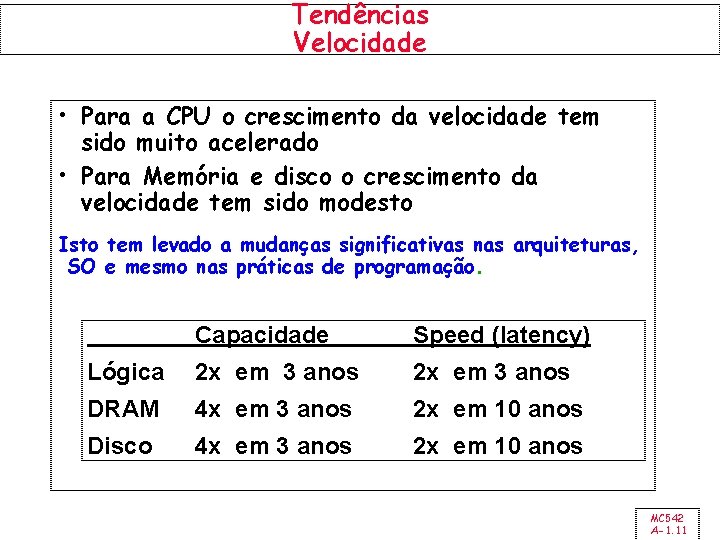

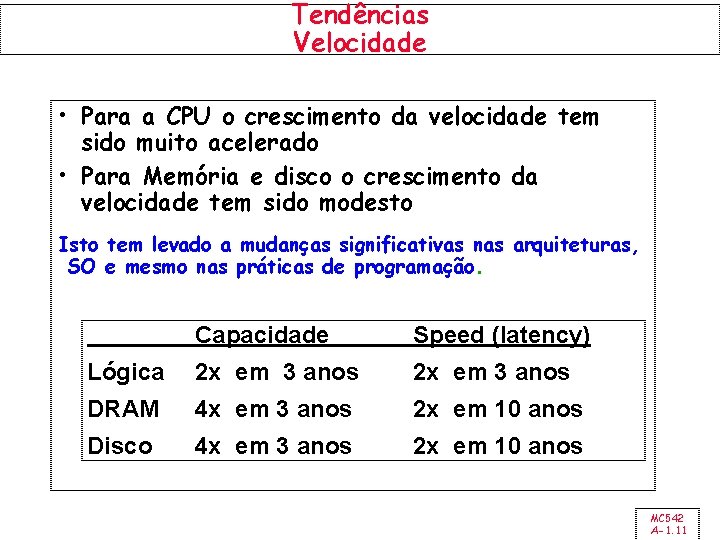

Tendências Velocidade • Para a CPU o crescimento da velocidade tem sido muito acelerado • Para Memória e disco o crescimento da velocidade tem sido modesto Isto tem levado a mudanças significativas nas arquiteturas, SO e mesmo nas práticas de programação. Capacidade Speed (latency) Lógica 2 x em 3 anos DRAM 4 x em 3 anos 2 x em 10 anos Disco 4 x em 3 anos 2 x em 10 anos MC 542 A-1. 11

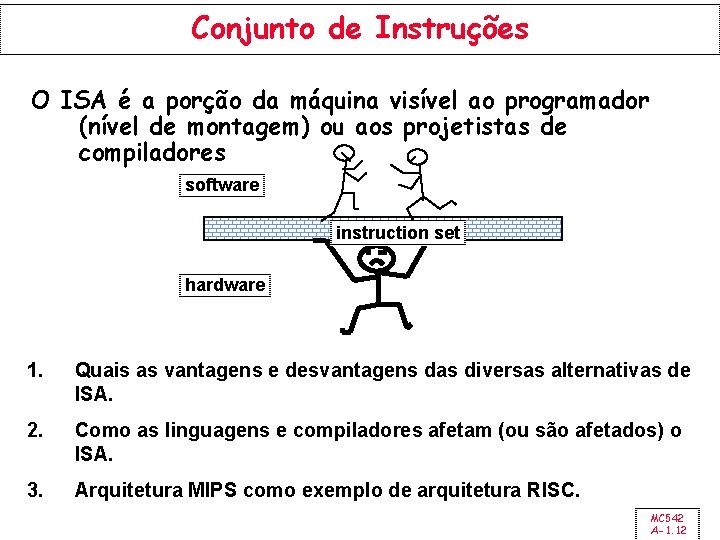

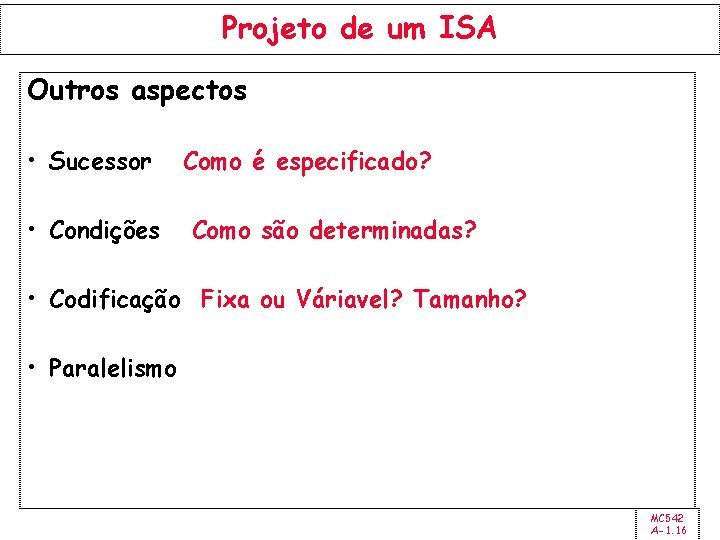

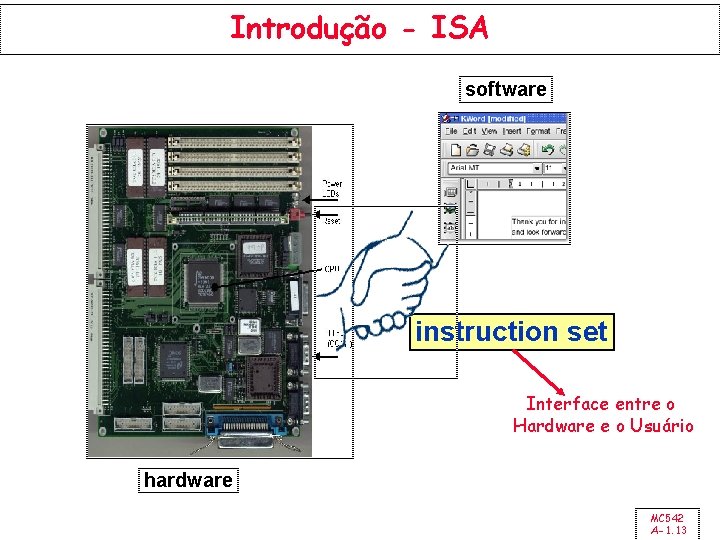

Conjunto de Instruções O ISA é a porção da máquina visível ao programador (nível de montagem) ou aos projetistas de compiladores software instruction set hardware 1. Quais as vantagens e desvantagens das diversas alternativas de ISA. 2. Como as linguagens e compiladores afetam (ou são afetados) o ISA. 3. Arquitetura MIPS como exemplo de arquitetura RISC. MC 542 A-1. 12

Introdução - ISA software instruction set Interface entre o Hardware e o Usuário hardware MC 542 A-1. 13

Evolução dos ISAs • As maiores vantagens em uma arquitetura, em geral, são associadas com as mudanças do ISA – Ex: Stack vs General Purpose Registers (GPR) • Decisões de projeto que devem ser levadas em consideração: – tecnologia – – organização linguagens de programação tecnologia em compiladores sistemas operacionais MC 542 A-1. 14

Projeto de um ISA 5 aspectos principais • Número de operandos (explícitos) (0, 1, 2, 3) • Armazenamento do Operando. Aonde ele está? • Endereço Efetivo. Como é especificado? • Tipo & Tamanho dos operandos. byte, int, float, … como eles são especificados? • Operações add, sub, mul, … como são especificadas? MC 542 A-1. 15

Projeto de um ISA Outros aspectos • Sucessor • Condições Como é especificado? Como são determinadas? • Codificação Fixa ou Váriavel? Tamanho? • Paralelismo MC 542 A-1. 16

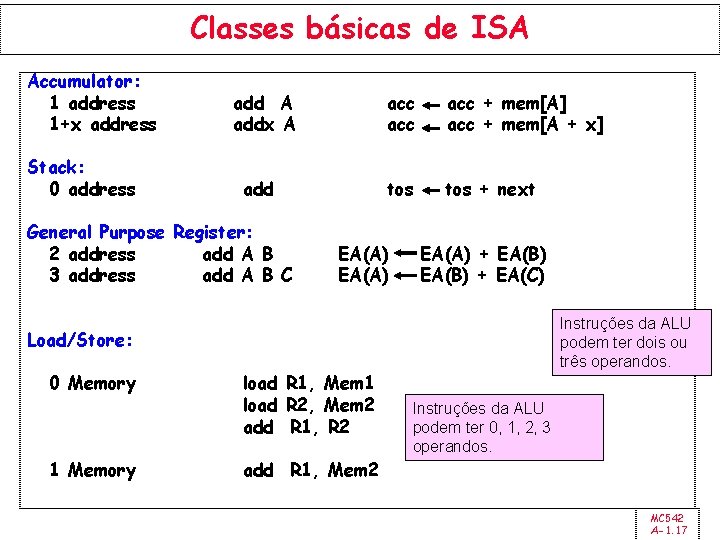

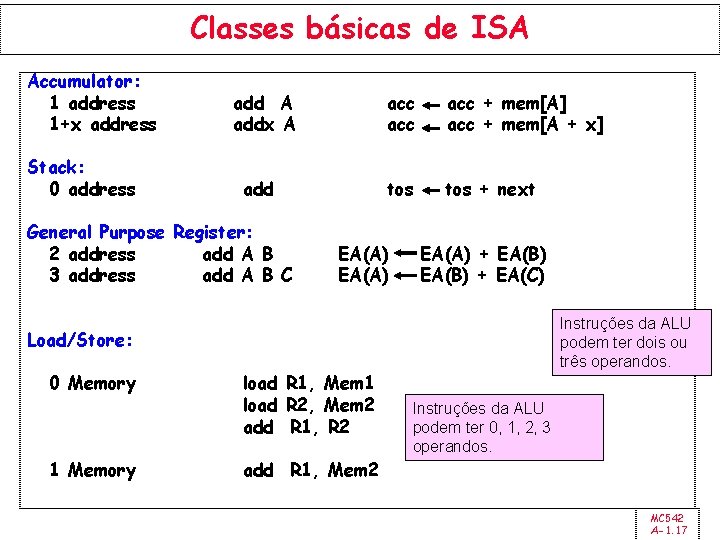

Classes básicas de ISA Accumulator: 1 address 1+x address Stack: 0 address add A addx A add General Purpose Register: 2 address add A B 3 address add A B C acc acc + mem[A] acc + mem[A + x] tos + next EA(A) + EA(B) + EA(C) Instruções da ALU podem ter dois ou três operandos. Load/Store: 0 Memory 1 Memory load R 1, Mem 1 load R 2, Mem 2 add R 1, R 2 Instruções da ALU podem ter 0, 1, 2, 3 operandos. add R 1, Mem 2 MC 542 A-1. 17

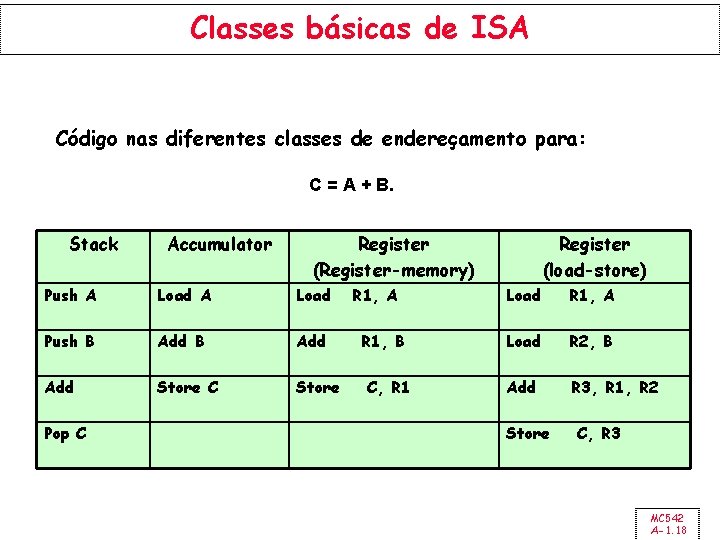

Classes básicas de ISA Código nas diferentes classes de endereçamento para: C = A + B. Stack Accumulator Register (Register-memory) Push A Load Push B Add Add Store C Store Pop C R 1, A R 1, B C, R 1 Register (load-store) Load R 1, A Load R 2, B Add R 3, R 1, R 2 Store C, R 3 MC 542 A-1. 18

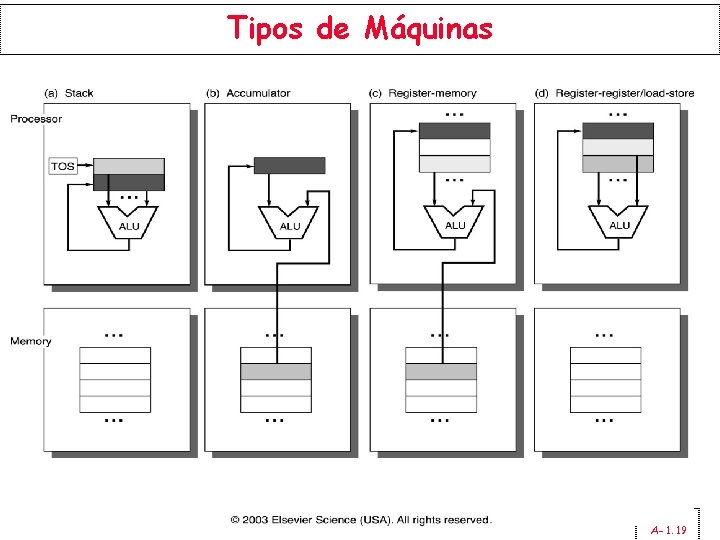

Tipos de Máquinas MC 542 A-1. 19

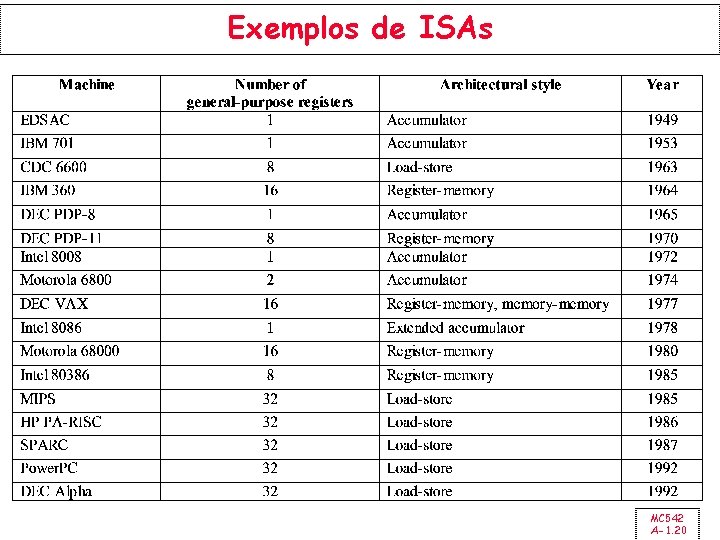

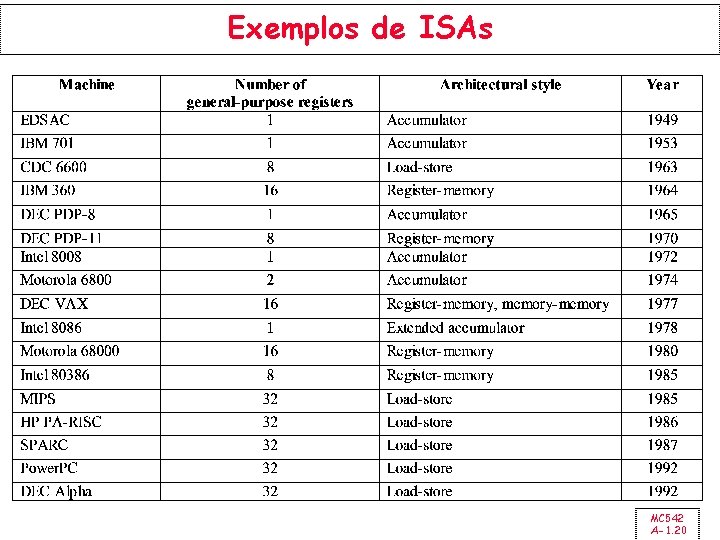

Exemplos de ISAs MC 542 A-1. 20

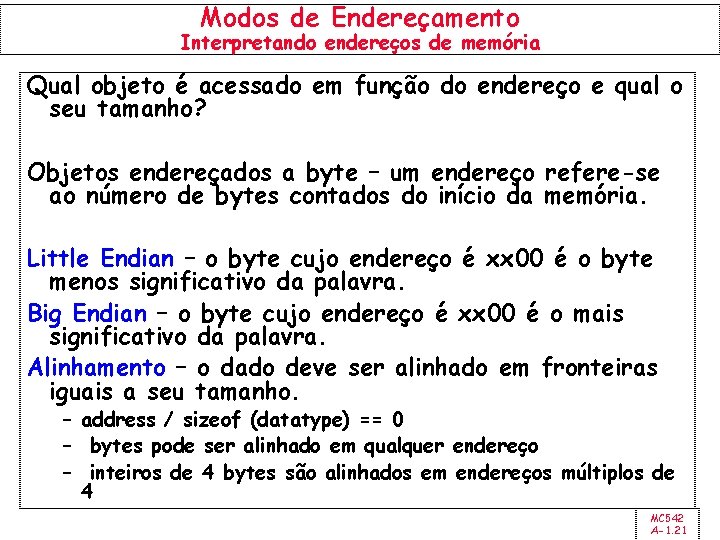

Modos de Endereçamento Interpretando endereços de memória Qual objeto é acessado em função do endereço e qual o seu tamanho? Objetos endereçados a byte – um endereço refere-se ao número de bytes contados do início da memória. Little Endian – o byte cujo endereço é xx 00 é o byte menos significativo da palavra. Big Endian – o byte cujo endereço é xx 00 é o mais significativo da palavra. Alinhamento – o dado deve ser alinhado em fronteiras iguais a seu tamanho. – address / sizeof (datatype) == 0 – bytes pode ser alinhado em qualquer endereço – inteiros de 4 bytes são alinhados em endereços múltiplos de 4 MC 542 A-1. 21

Modos de Endereçamento • • • Register direct Immediate (literal) Direct (absolute) Register indirect Base+Displacement Base+Index Scaled Index Autoincrement Autodecrement Memory indirect Ri v M[v] M[Ri +v] M[Ri + Rj*d +v] M[Ri++] reg. file M[Ri--] M[ M[Ri] ] memória MC 542 A-1. 22

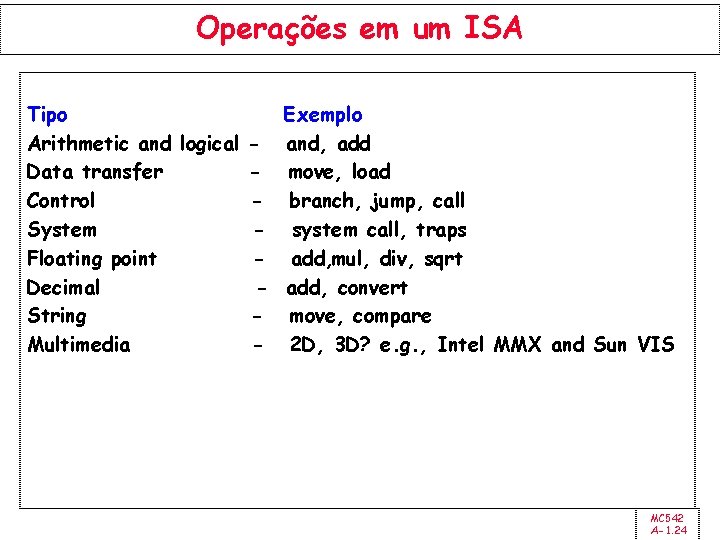

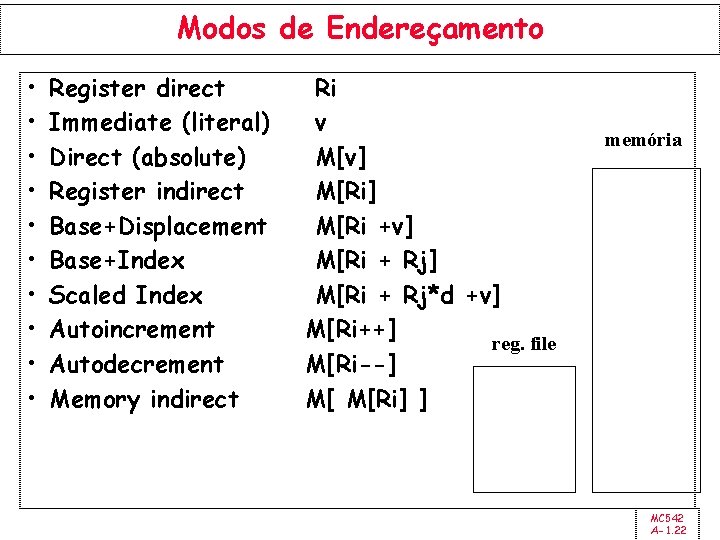

Modos de Endereçamento MC 542 A-1. 23

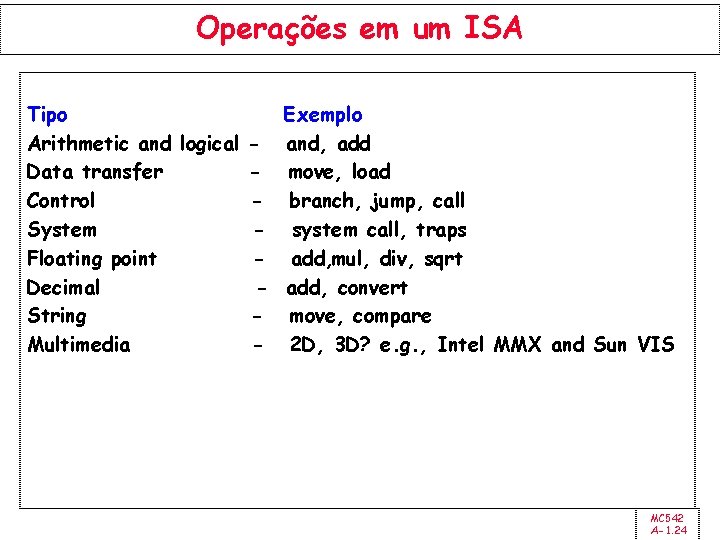

Operações em um ISA Tipo Arithmetic and logical Data transfer Control System Floating point Decimal String Multimedia - Exemplo and, add move, load branch, jump, call system call, traps add, mul, div, sqrt add, convert move, compare 2 D, 3 D? e. g. , Intel MMX and Sun VIS MC 542 A-1. 24

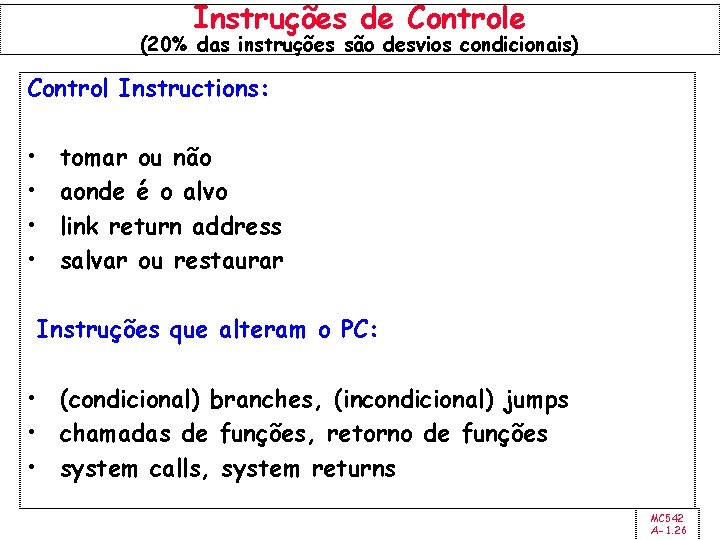

Uso de Operações em um ISA MC 542 A-1. 25

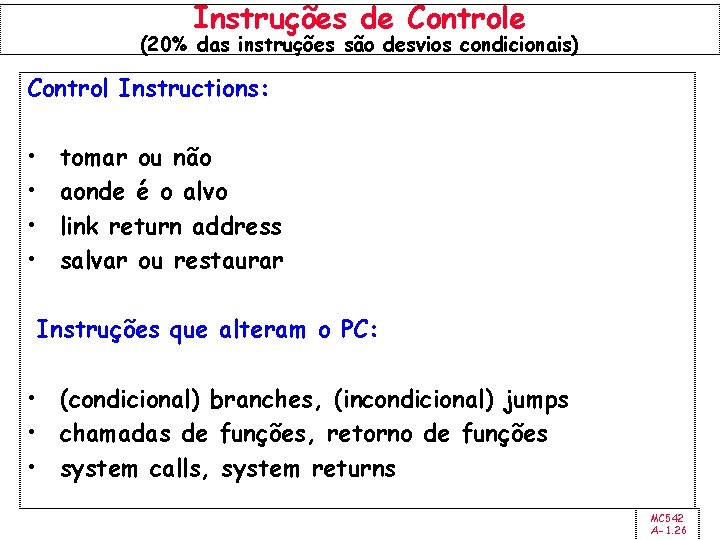

Instruções de Controle (20% das instruções são desvios condicionais) Control Instructions: • • tomar ou não aonde é o alvo link return address salvar ou restaurar Instruções que alteram o PC: • (condicional) branches, (incondicional) jumps • chamadas de funções, retorno de funções • system calls, system returns MC 542 A-1. 26

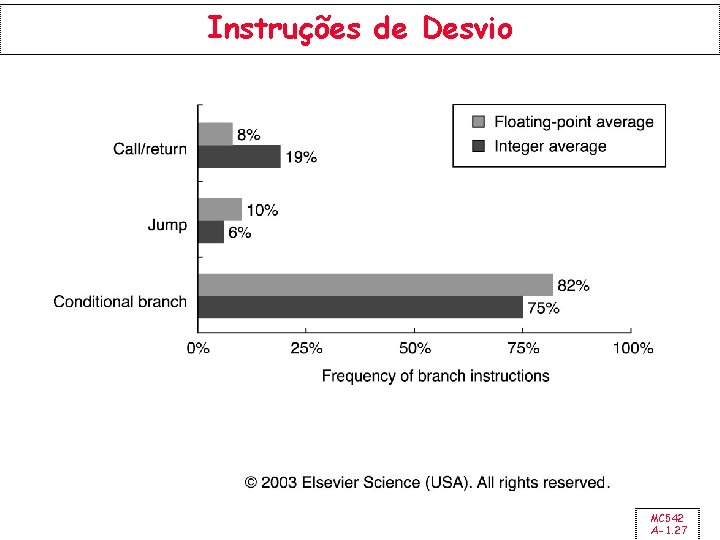

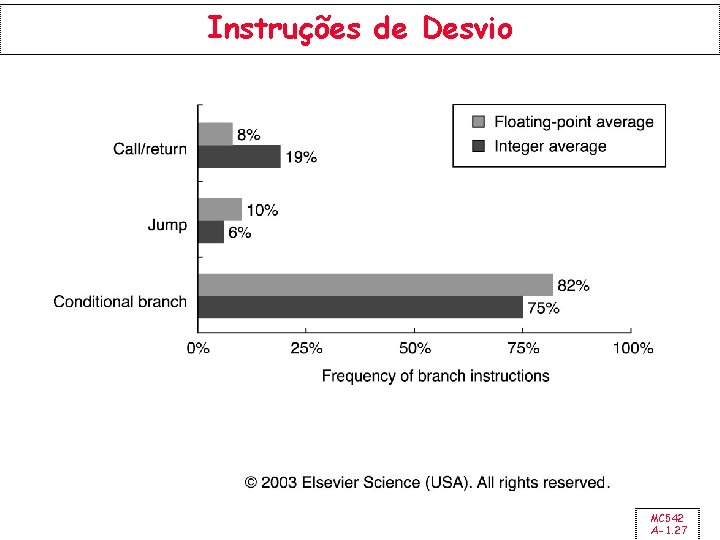

Instruções de Desvio MC 542 A-1. 27

Tipos e Tamanhos dos Operandos O tipo do operando, em geral, é codificado no opcode – LDW significa “ loading of a word”. Tamanhos típicos são: – – – Character (1 byte) Half word (16 bits) Word (32 bits) Single Precision Floating Point (1 Word) Double Precision Floating Point (2 Words) Inteiros são representados em complemento de dois. Floating point, em geral, usa o padrão IEEE 754. Algumas linguagens (como COBOL) usam packed decimal. MC 542 A-1. 28

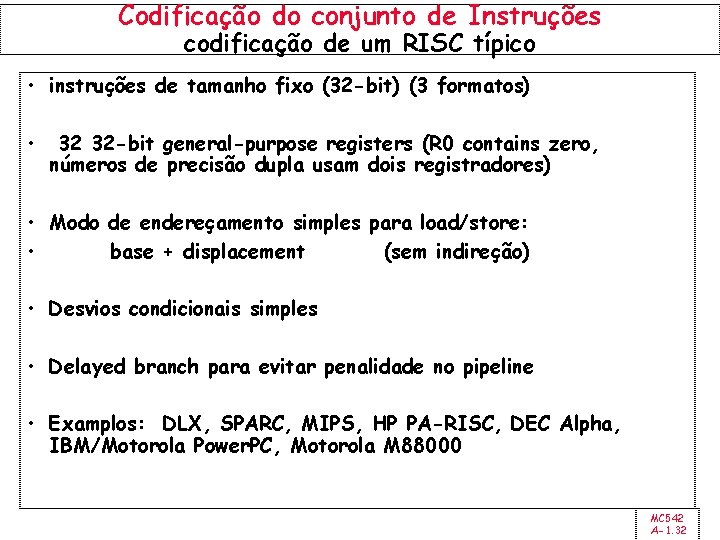

RISC vs CISC RISC = Reduced Instruction Set Computer • • Conjunto de Instruções pequeno Instruções de tamanho fixo Operações executadas somente em registradores Chip simples, em geral, executam com velocidade de clock elevada. CISC = Complex Instruction Set Computer • Conjunto de Instruções grande • Instruções Complexas e de tamanho variável • Operações Memória-Memória MC 542 A-1. 29

Projeto CISC premissas • Conjunto de Instruções farto pode simplificar o compilador. • Conjunto de Instruções farto pode aliviar o software. • Conjunto de Instruções farto pode dar qualidade a arquitetura. – Se o tempo de execução for proporcional ao tamanho do programa, técnicas de arquitetura que levem a programas menores também levam a computadores mais rápidos. MC 542 A-1. 30

Projeto RISC premissas • As funções devem ser simples, a menos que haja uma razão muito forte em contrário. • Decodificação simples e execução pipelined são mais importantes que o tamanho do programa. • Tecnologias de compiladores podem ser usadas para simplificar as instruções ao invés de produzirem instruções complexas. MC 542 A-1. 31

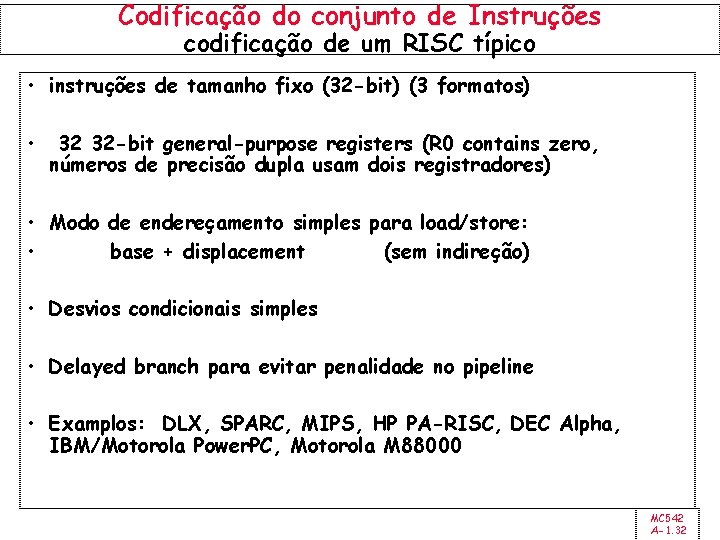

Codificação do conjunto de Instruções codificação de um RISC típico • instruções de tamanho fixo (32 -bit) (3 formatos) • 32 32 -bit general-purpose registers (R 0 contains zero, números de precisão dupla usam dois registradores) • Modo de endereçamento simples para load/store: • base + displacement (sem indireção) • Desvios condicionais simples • Delayed branch para evitar penalidade no pipeline • Examplos: DLX, SPARC, MIPS, HP PA-RISC, DEC Alpha, IBM/Motorola Power. PC, Motorola M 88000 MC 542 A-1. 32

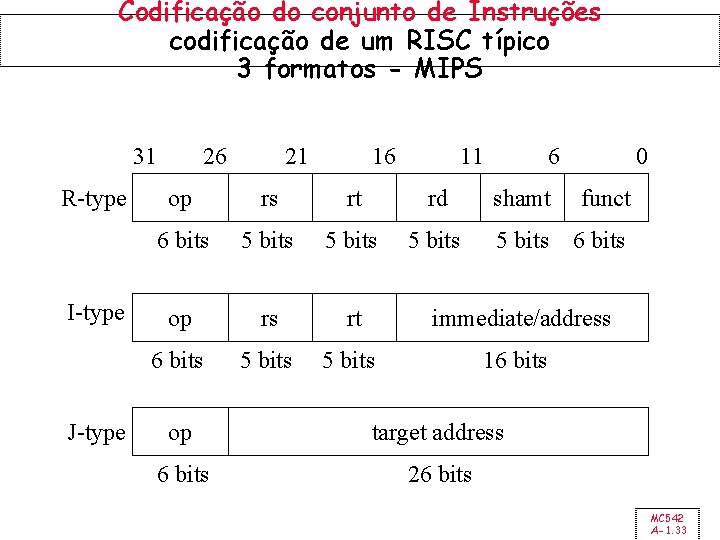

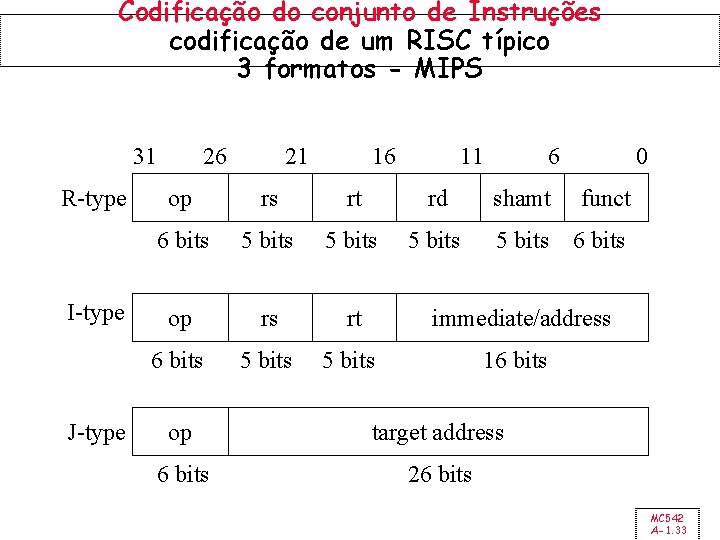

Codificação do conjunto de Instruções codificação de um RISC típico 3 formatos - MIPS 31 R-type I-type J-type 26 21 16 11 6 0 op rs rt rd shamt funct 6 bits 5 bits 6 bits op rs rt immediate/address 6 bits 5 bits 16 bits op target address 6 bits 26 bits MC 542 A-1. 33

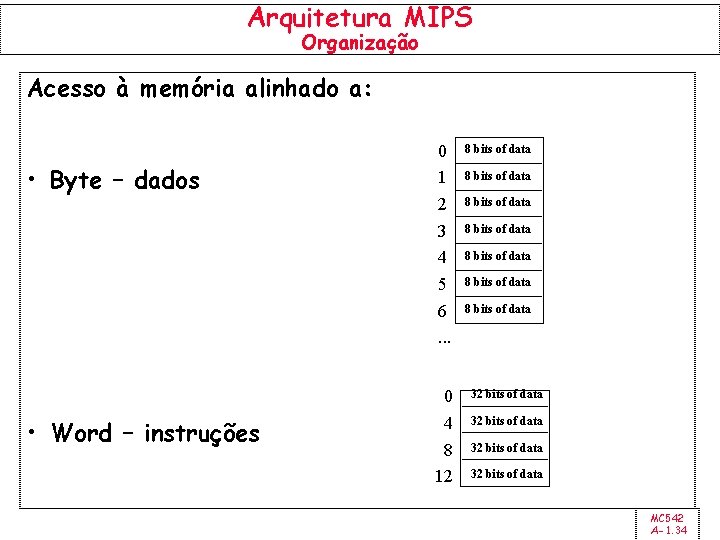

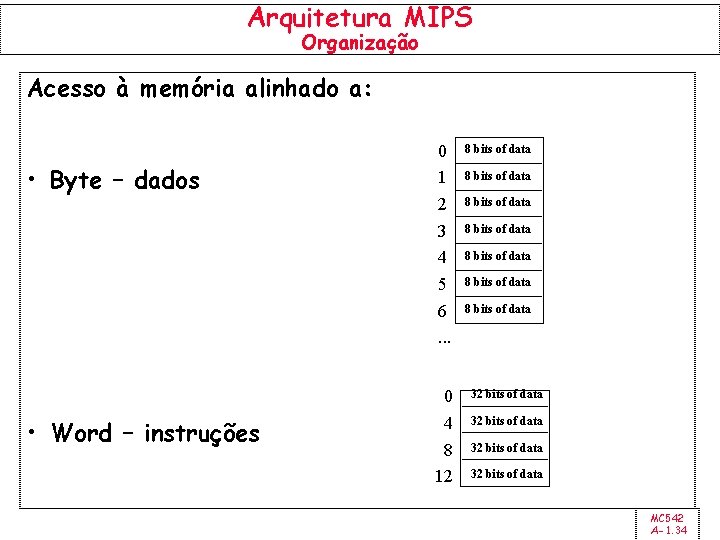

Arquitetura MIPS Organização Acesso à memória alinhado a: • Byte – dados • Word – instruções 0 1 2 3 4 5 6. . . 0 4 8 12 8 bits of data 8 bits of data 32 bits of data MC 542 A-1. 34

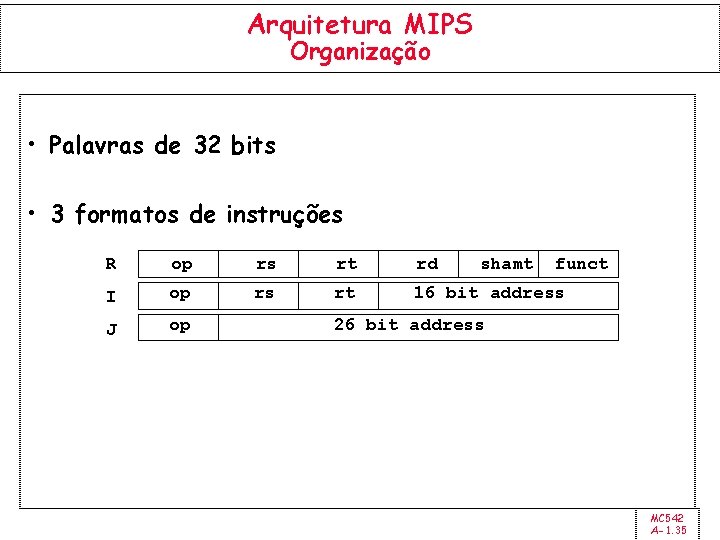

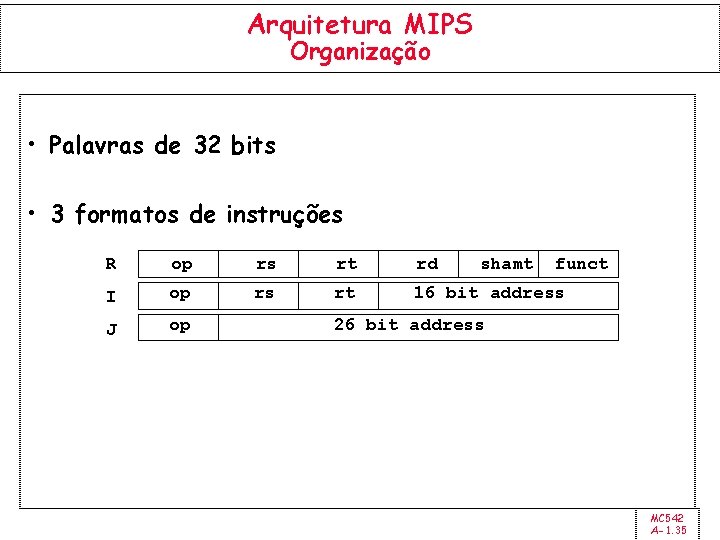

Arquitetura MIPS Organização • Palavras de 32 bits • 3 formatos de instruções R op rs rt rd I op rs rt 16 bit address J op shamt funct 26 bit address MC 542 A-1. 35

![Arquitetura MIPS Organização Código C A300 h A300 Código MIPS lw t Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-36.jpg)

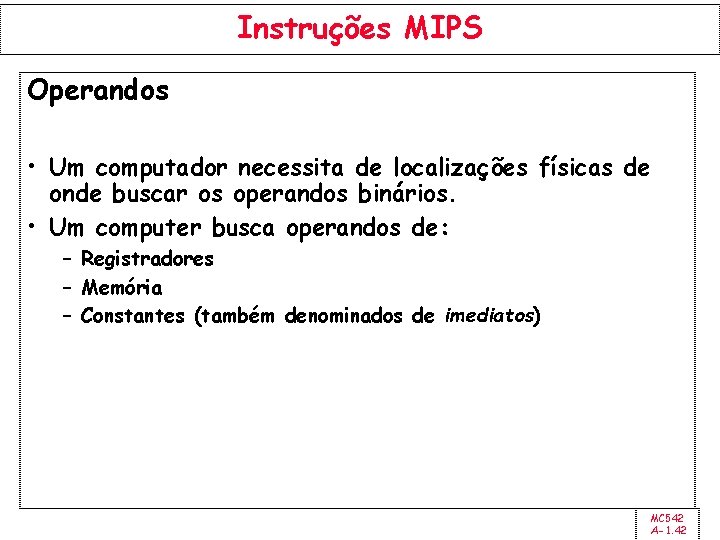

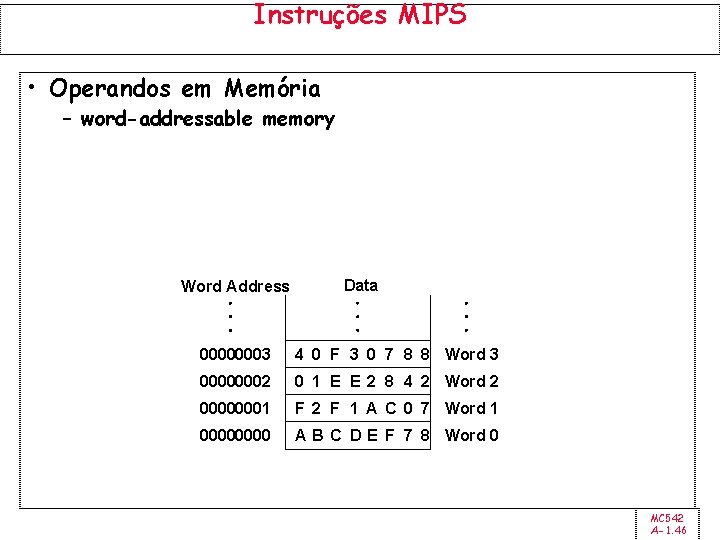

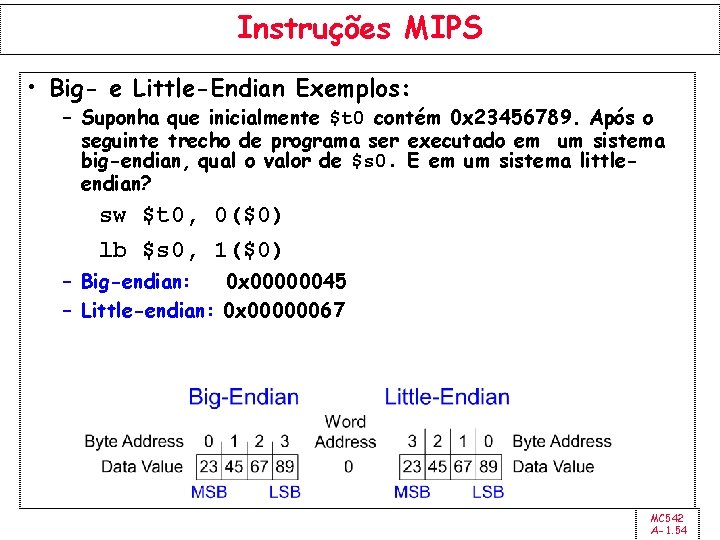

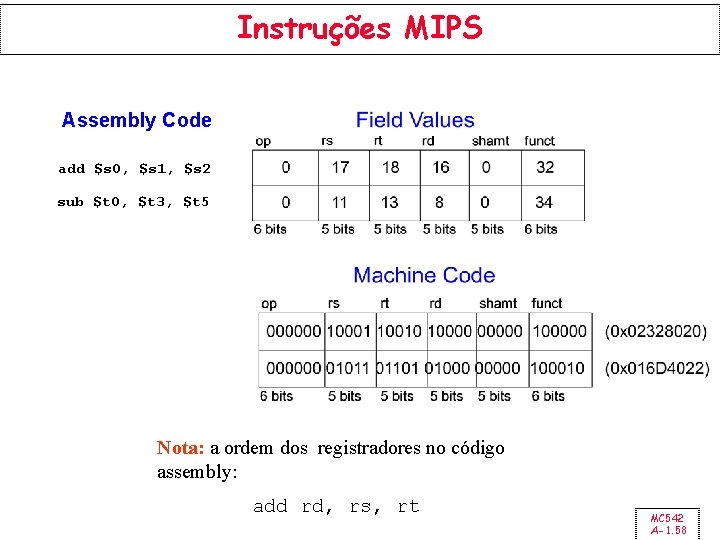

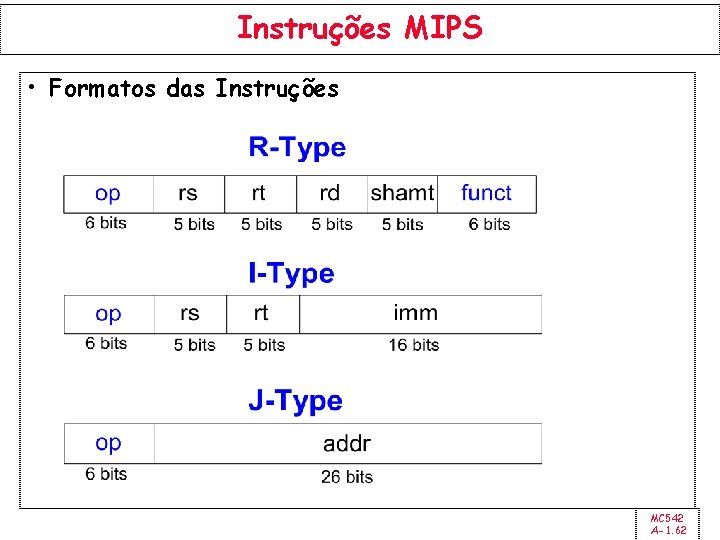

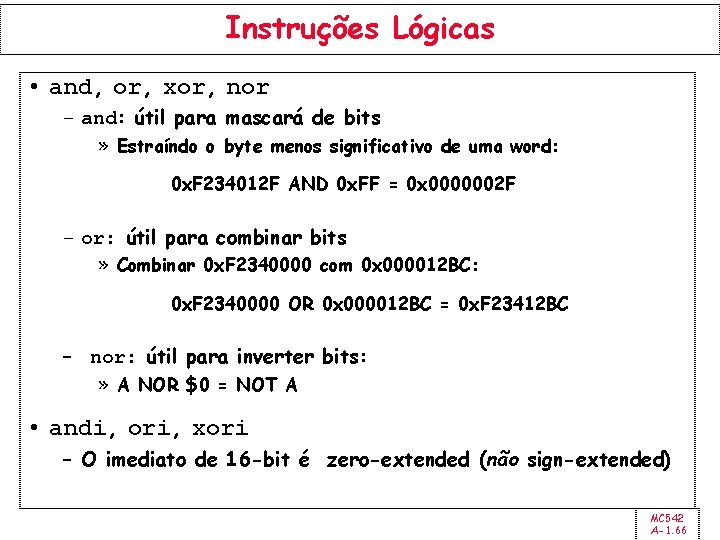

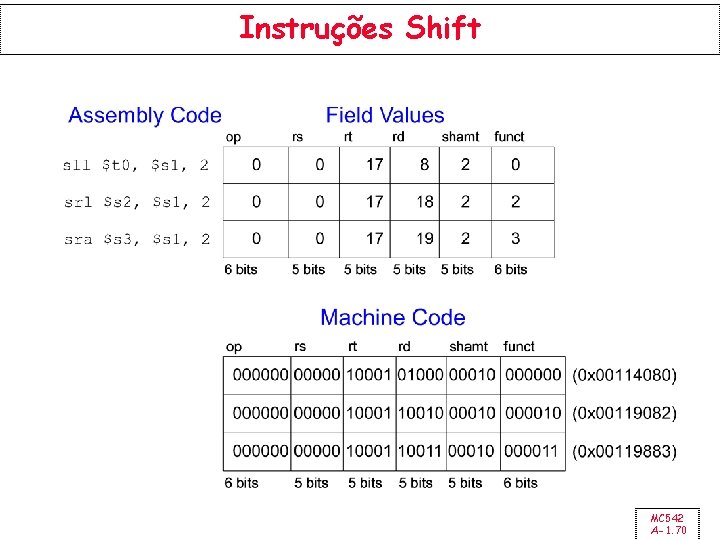

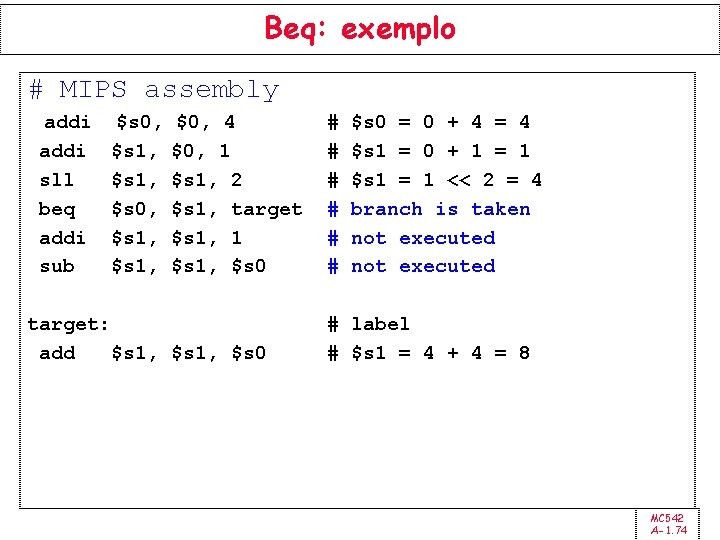

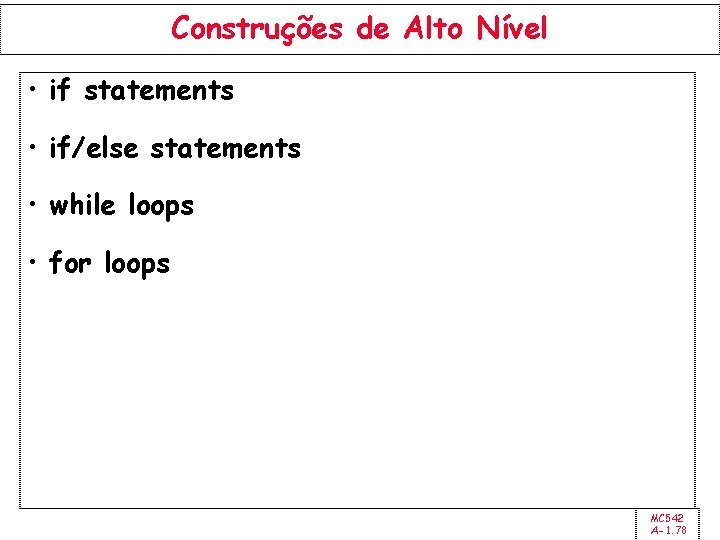

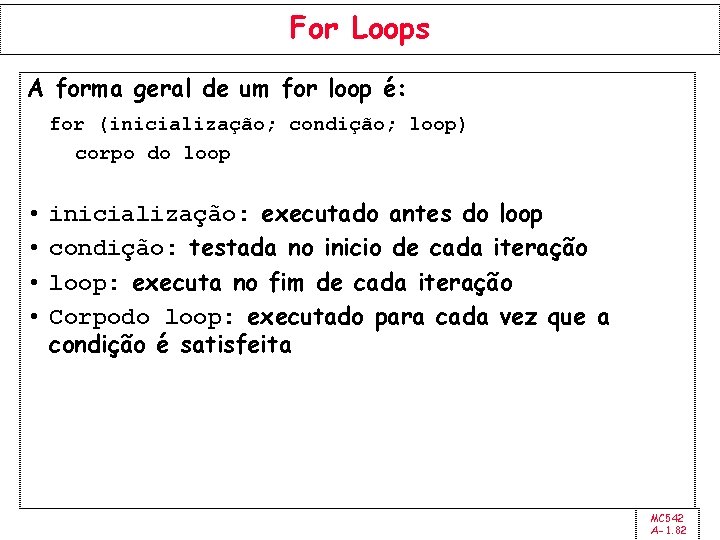

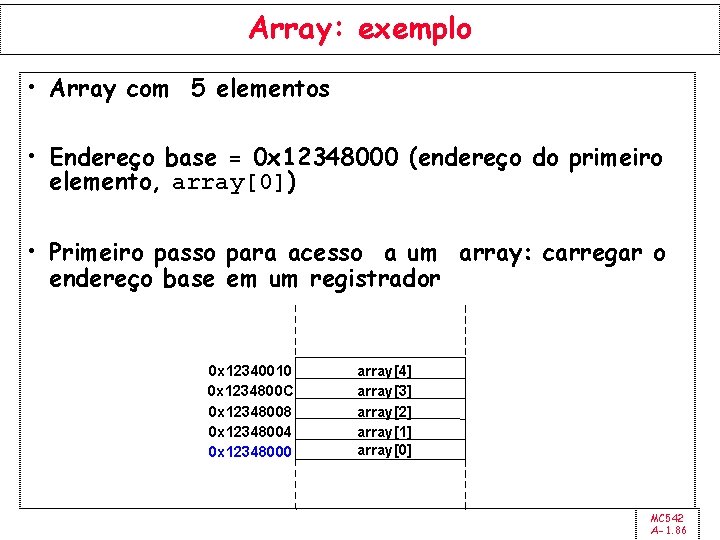

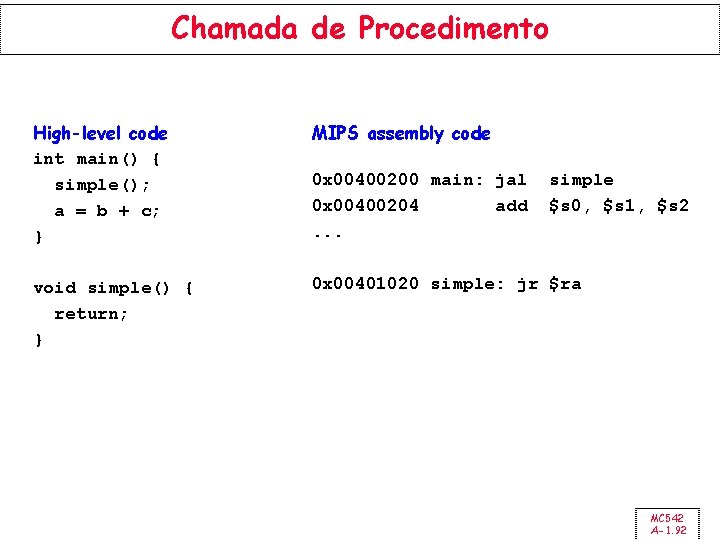

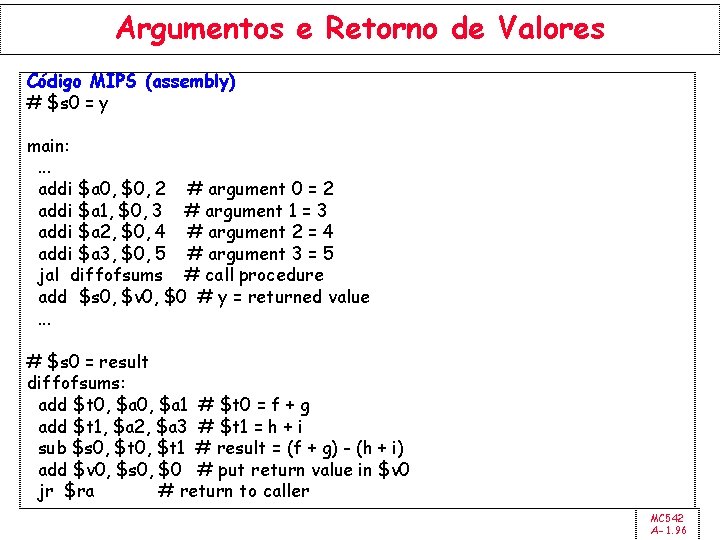

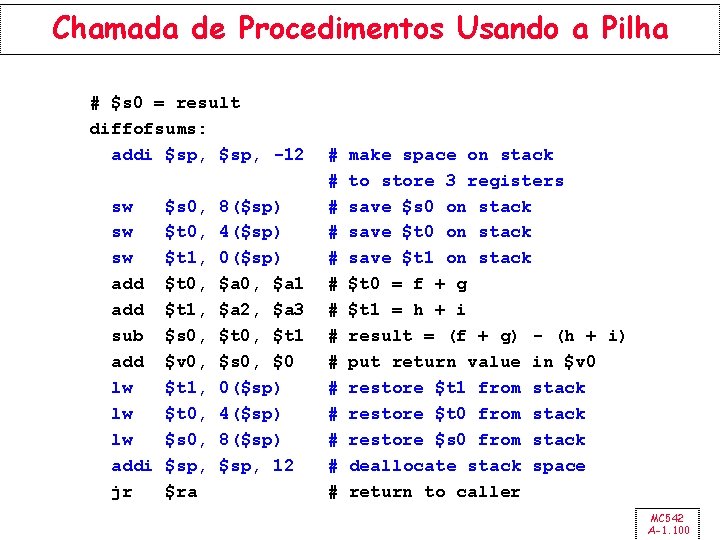

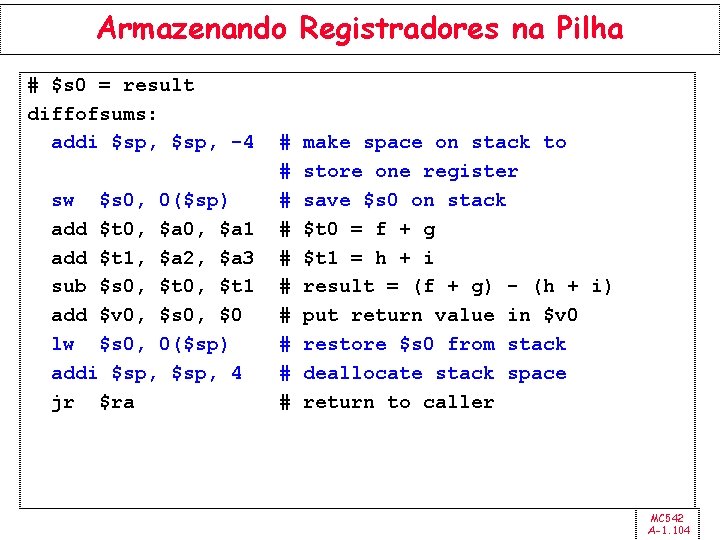

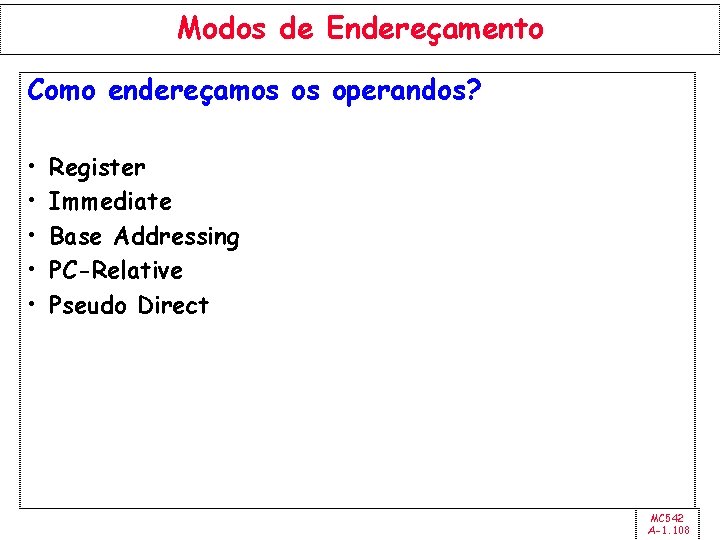

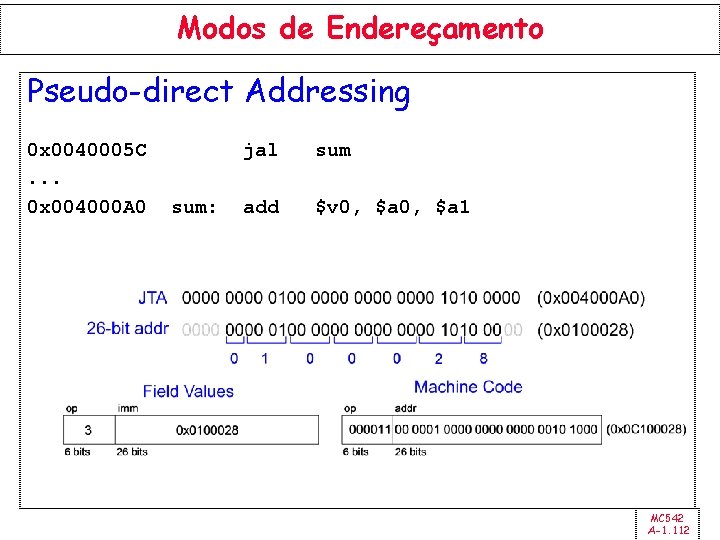

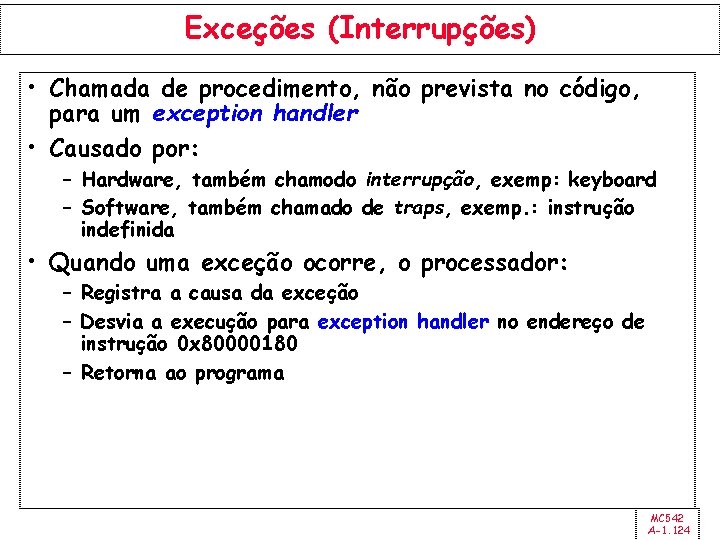

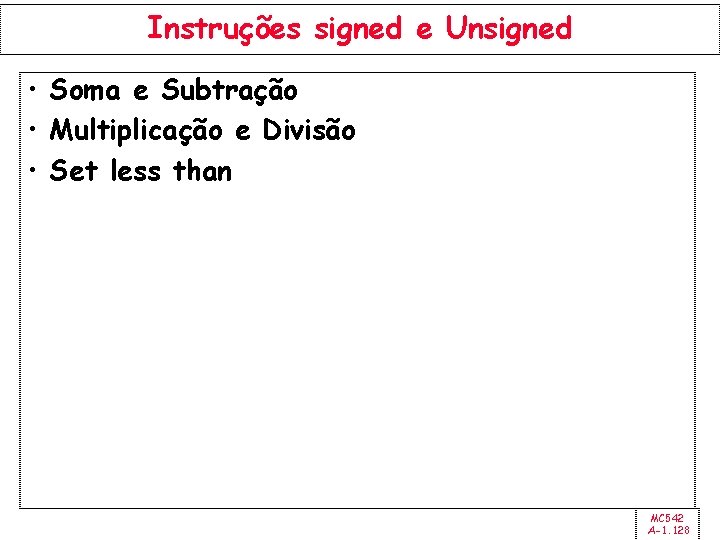

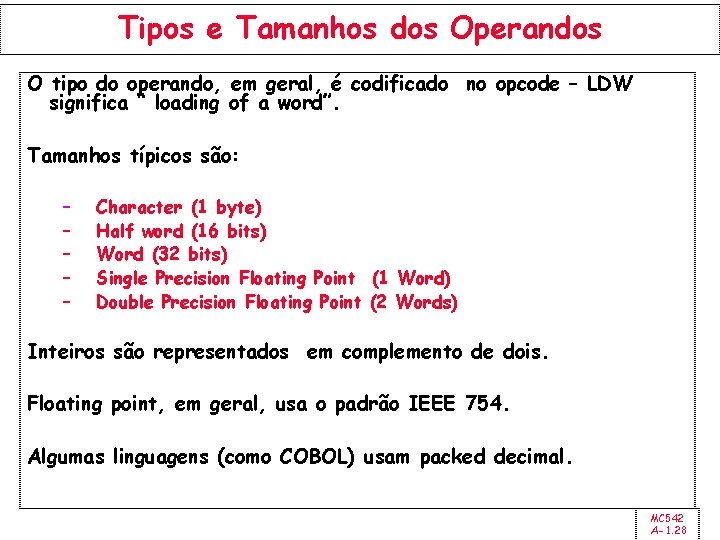

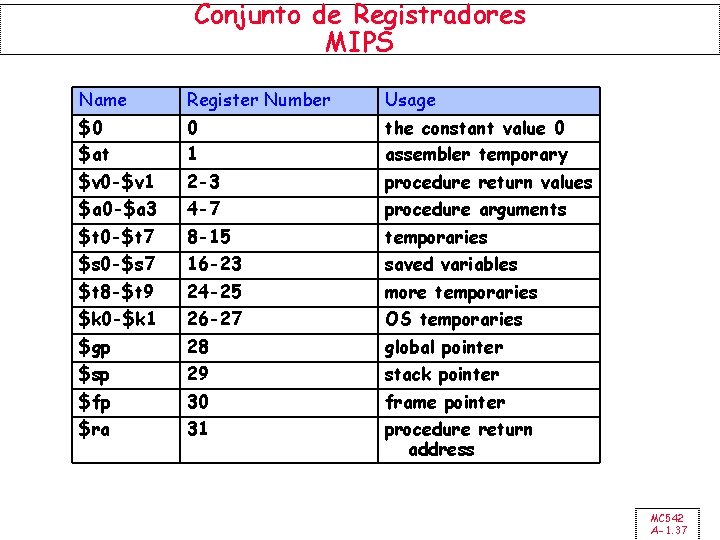

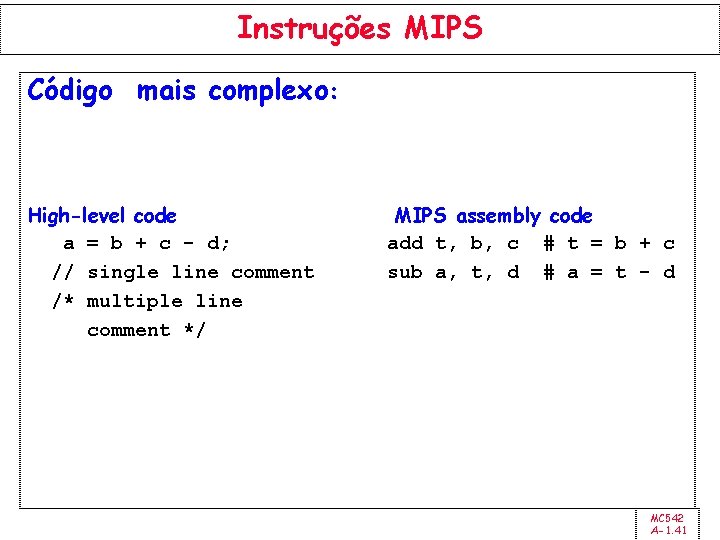

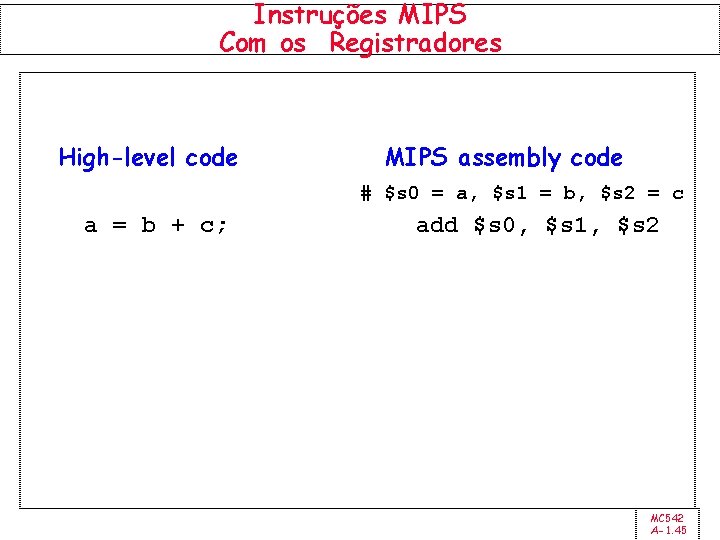

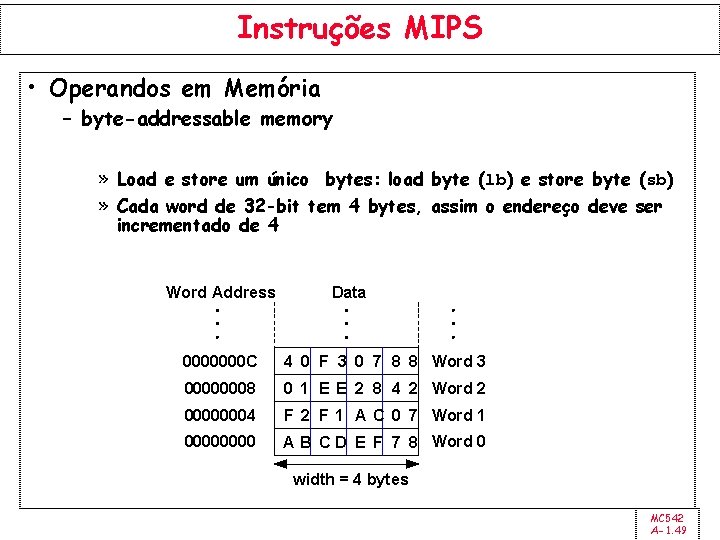

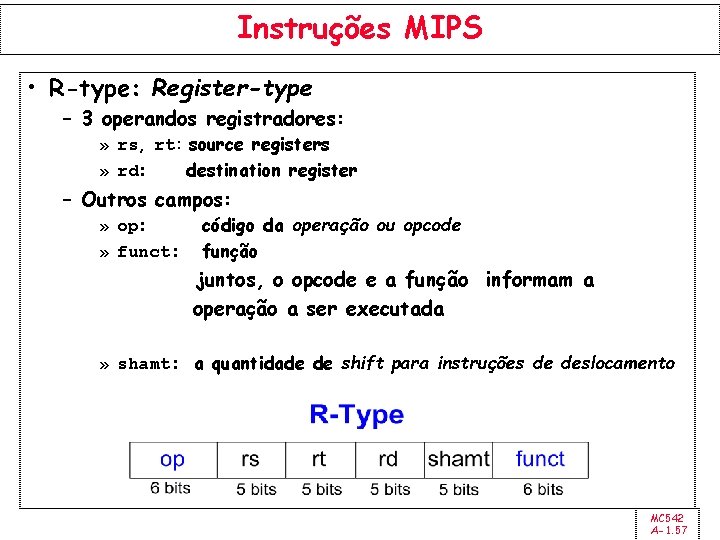

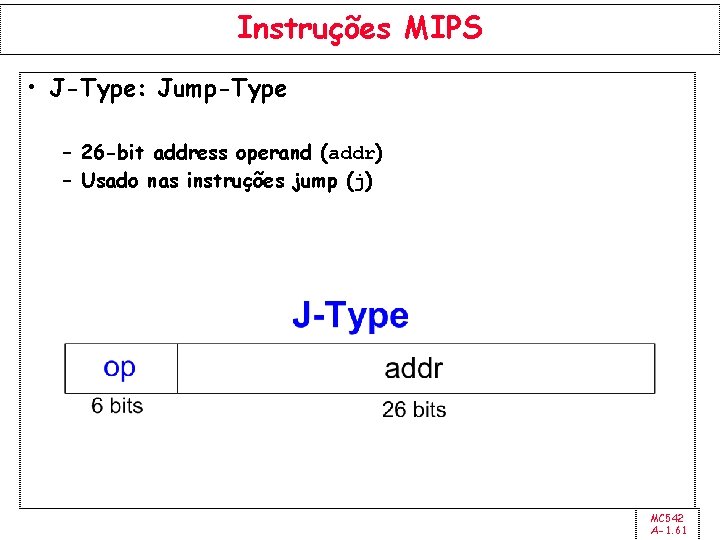

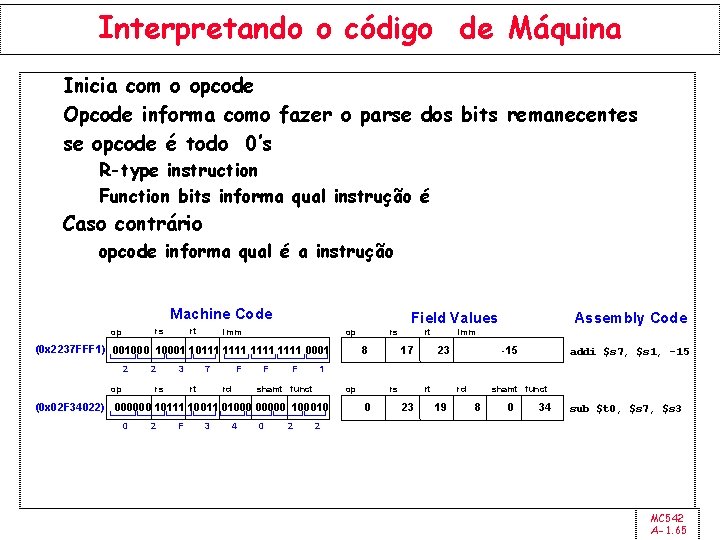

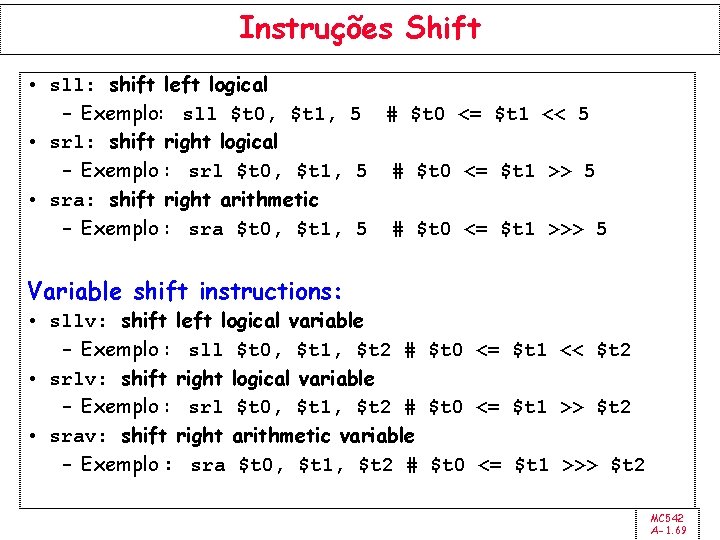

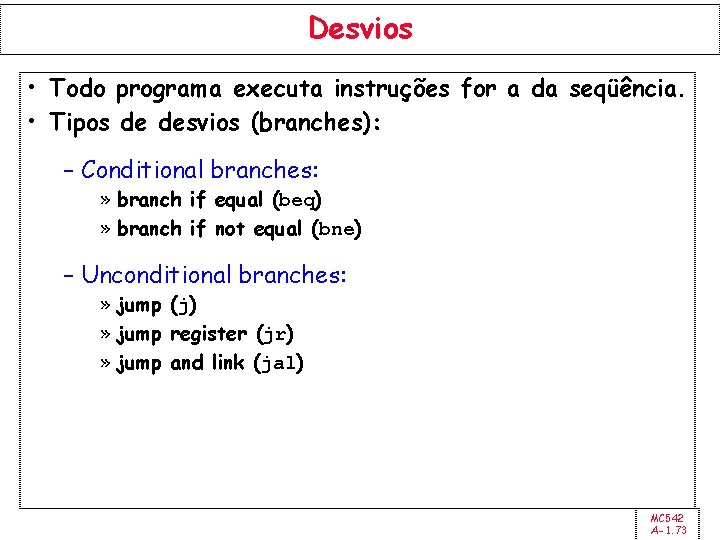

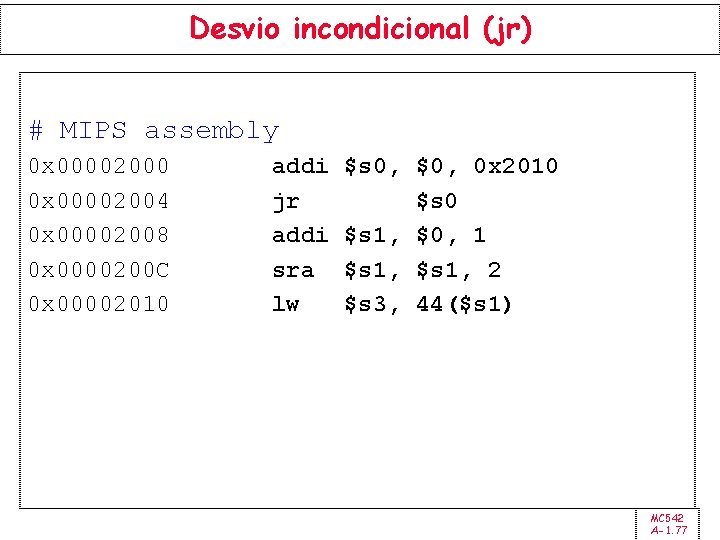

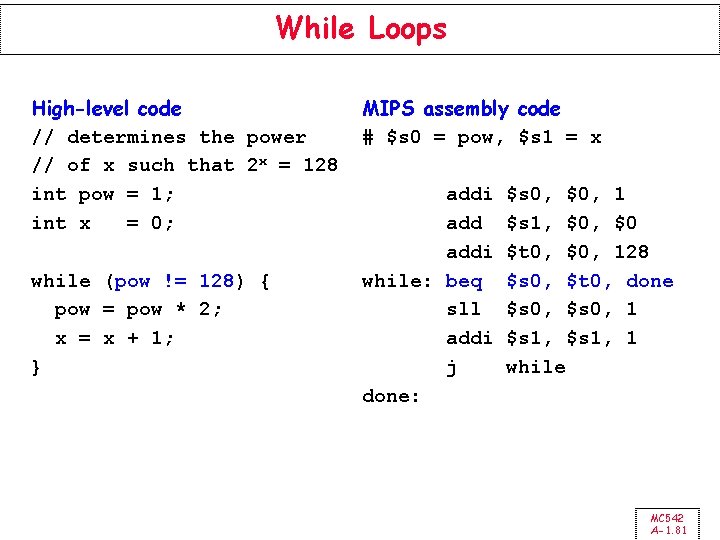

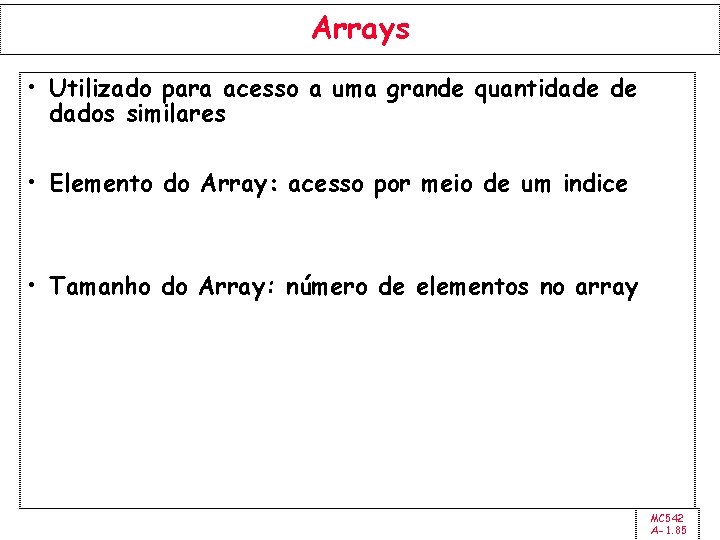

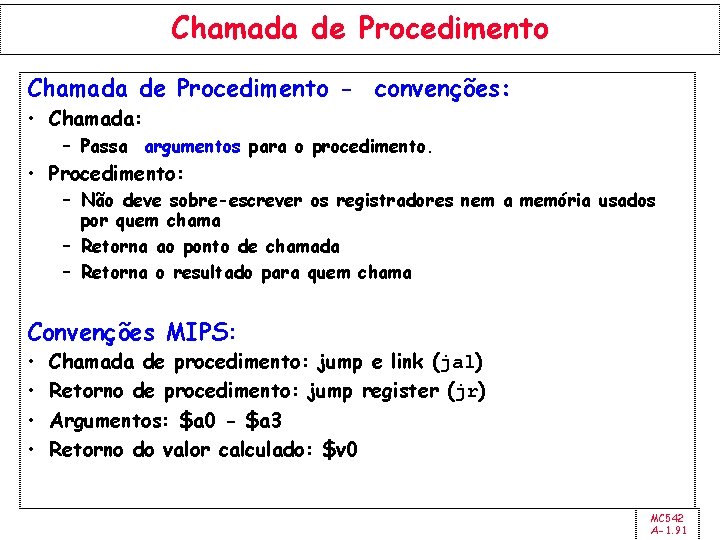

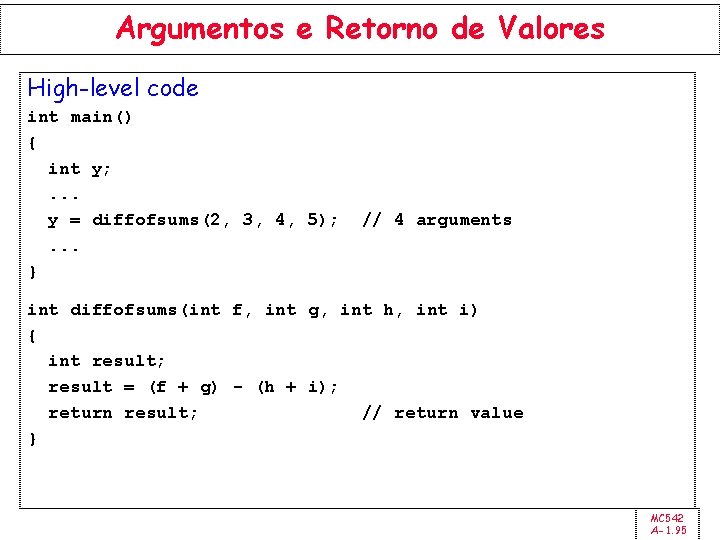

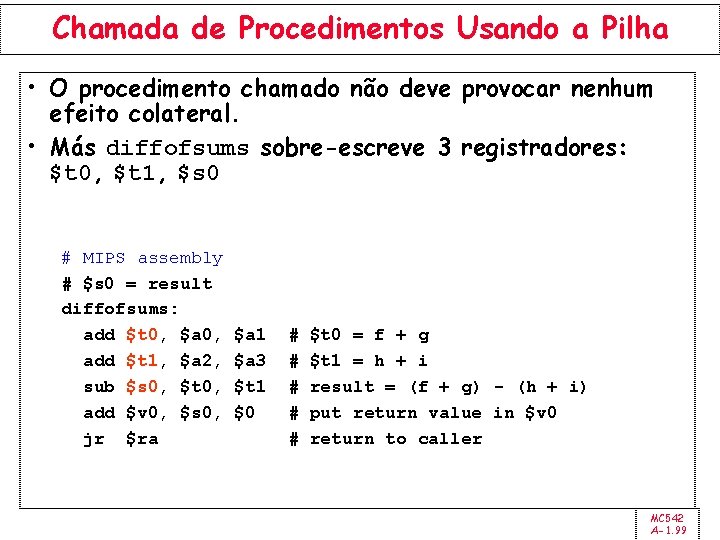

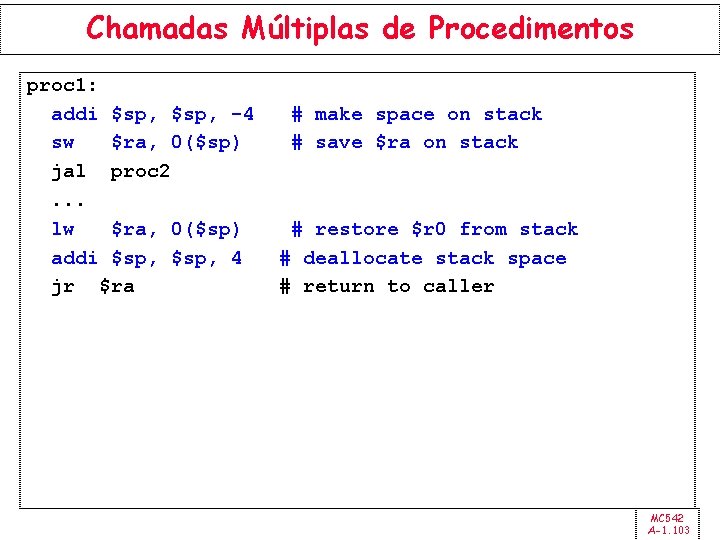

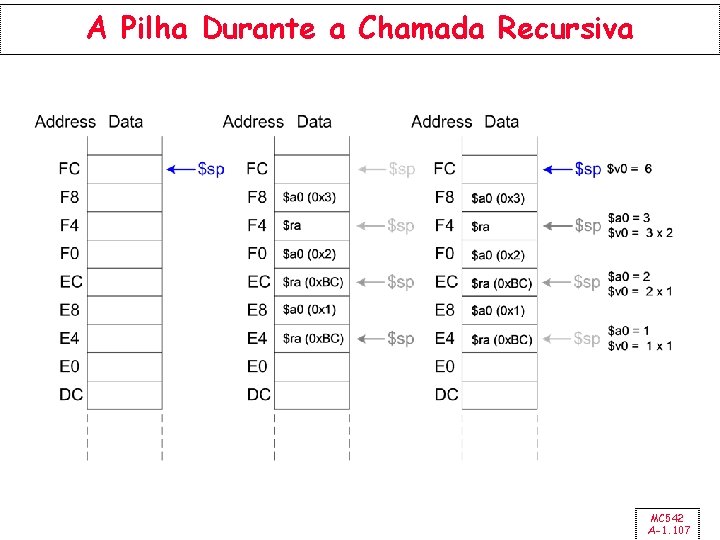

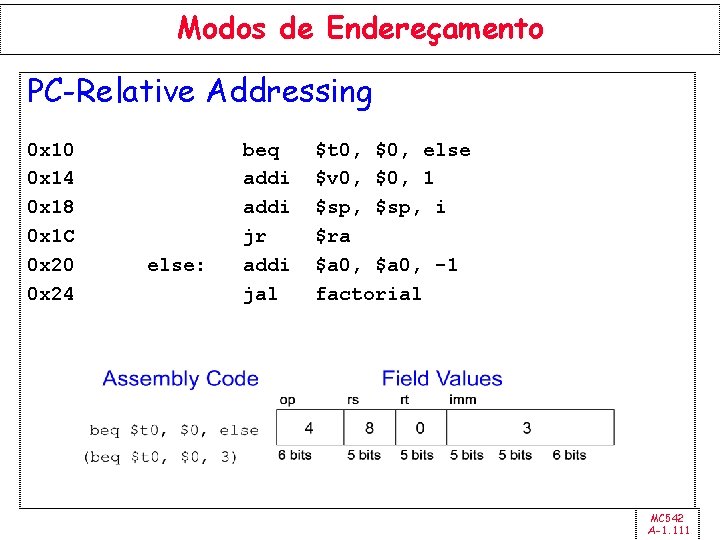

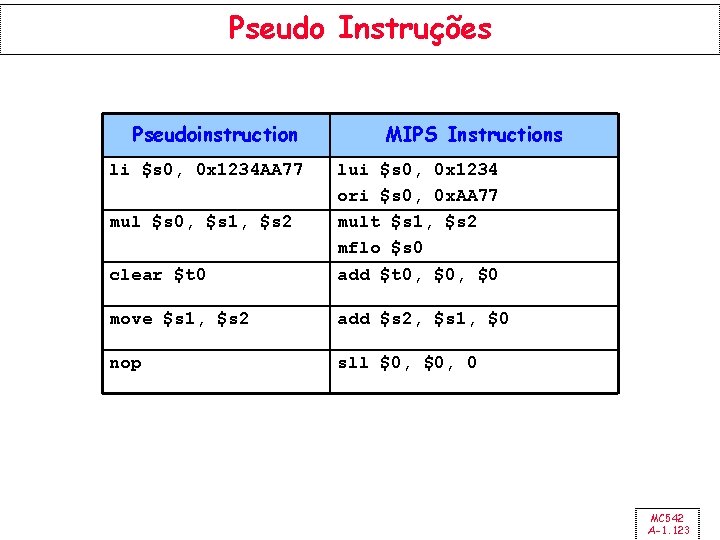

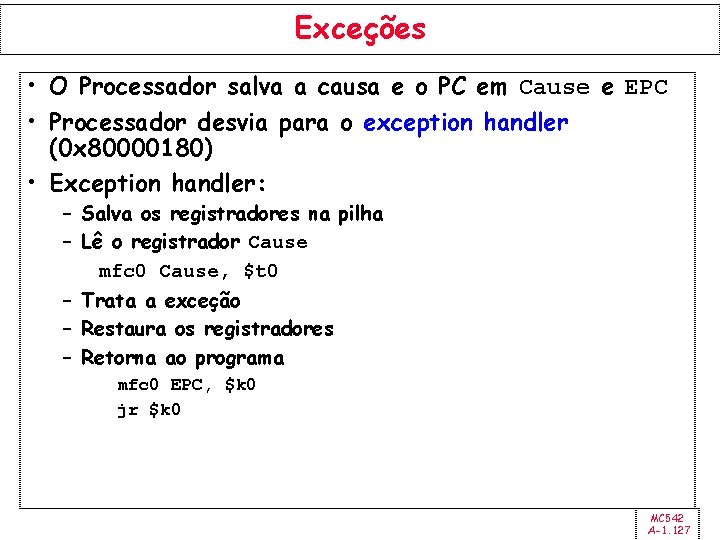

Arquitetura MIPS Organização Código C: A[300] = h + A[300]; Código MIPS: lw $t 0, 1200($t 1) add $t 0, $s 2, $t 0 sw $t 0, 1200($t 1) MC 542 A-1. 36

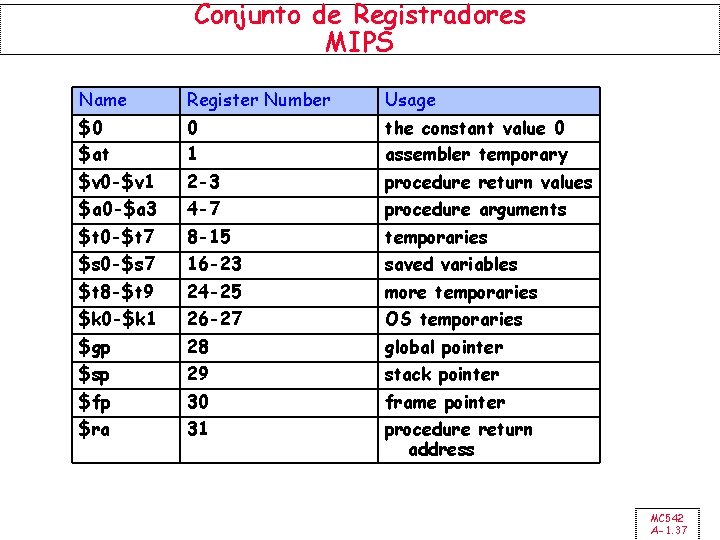

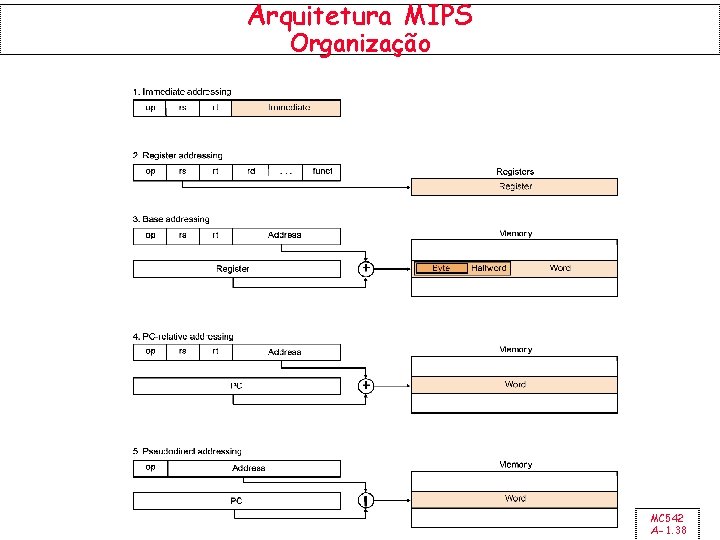

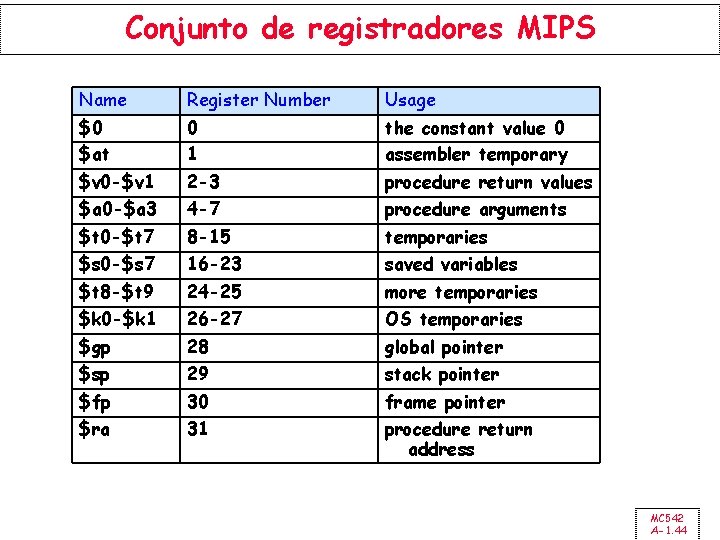

Conjunto de Registradores MIPS Name Register Number Usage $0 $at 0 1 the constant value 0 assembler temporary $v 0 -$v 1 2 -3 procedure return values $a 0 -$a 3 4 -7 procedure arguments $t 0 -$t 7 8 -15 temporaries $s 0 -$s 7 16 -23 saved variables $t 8 -$t 9 24 -25 more temporaries $k 0 -$k 1 26 -27 OS temporaries $gp 28 global pointer $sp 29 stack pointer $fp 30 frame pointer $ra 31 procedure return address MC 542 A-1. 37

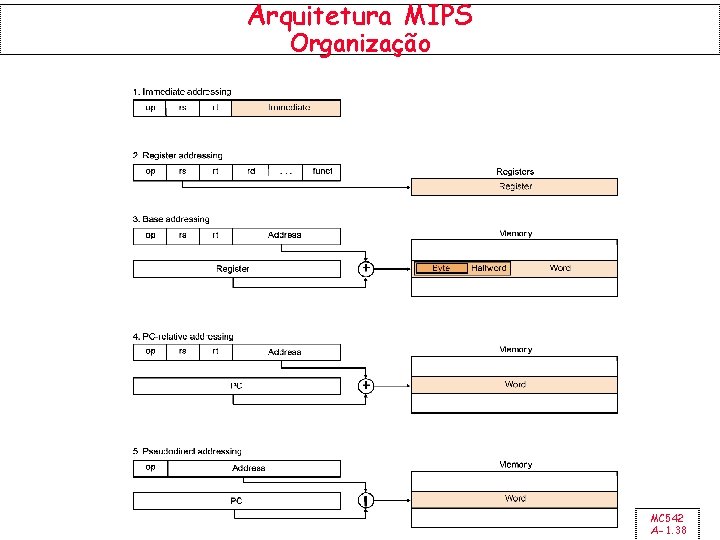

Arquitetura MIPS Organização MC 542 A-1. 38

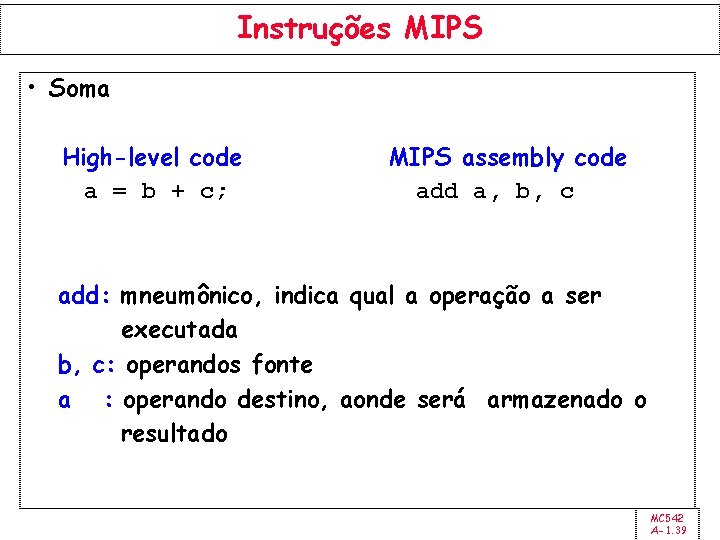

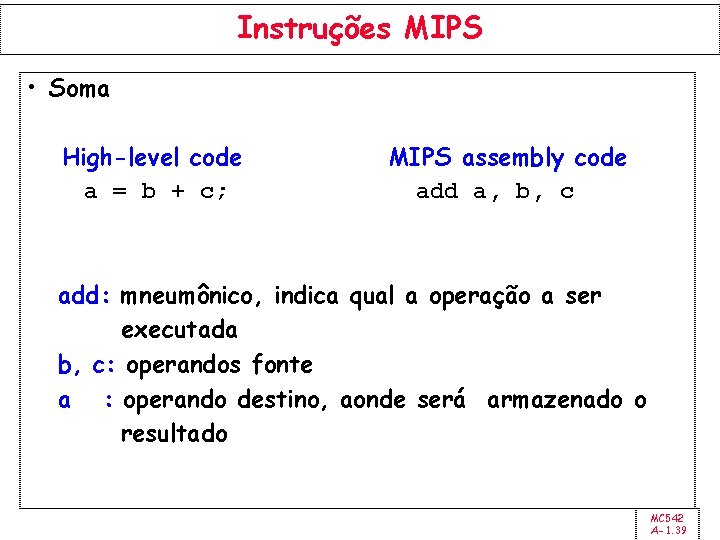

Instruções MIPS • Soma High-level code a = b + c; MIPS assembly code add a, b, c add: mneumônico, indica qual a operação a ser executada b, c: operandos fonte a : operando destino, aonde será armazenado o resultado MC 542 A-1. 39

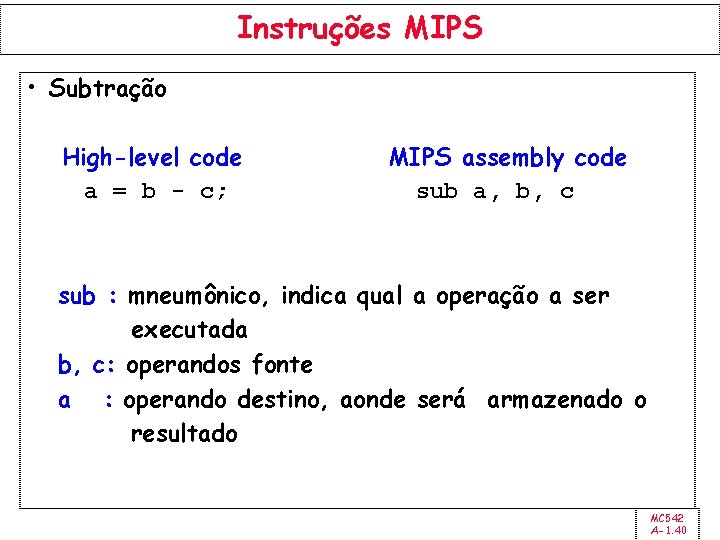

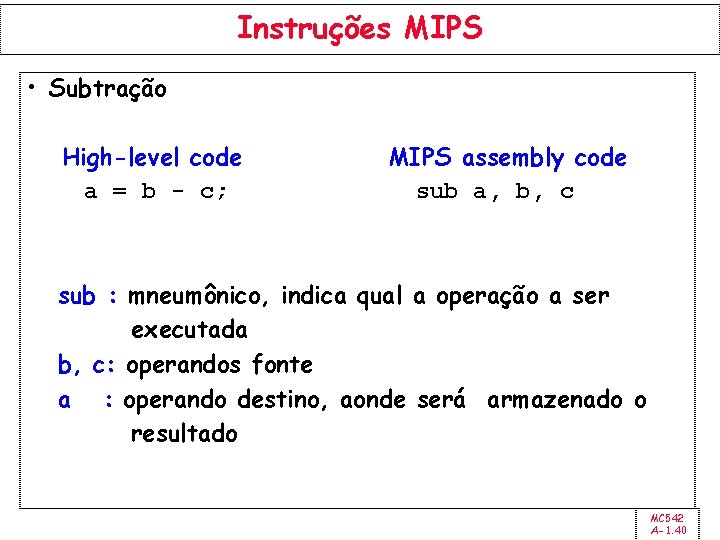

Instruções MIPS • Subtração High-level code a = b - c; MIPS assembly code sub a, b, c sub : mneumônico, indica qual a operação a ser executada b, c: operandos fonte a : operando destino, aonde será armazenado o resultado MC 542 A-1. 40

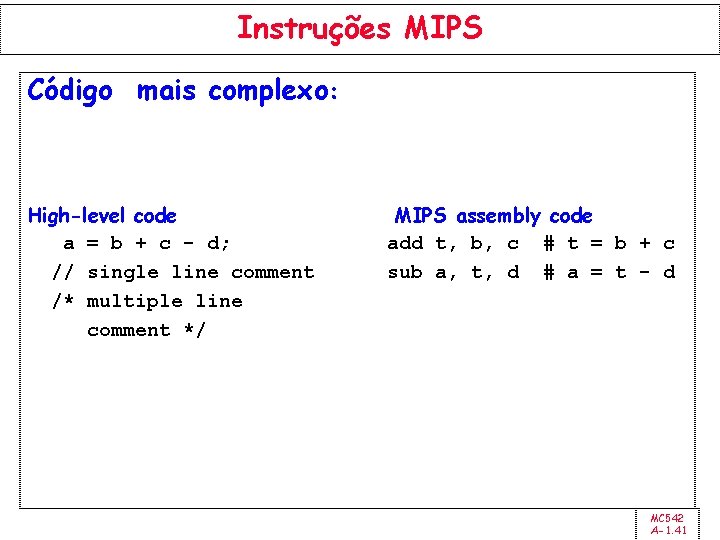

Instruções MIPS Código mais complexo: High-level code a = b + c - d; // single line comment /* multiple line comment */ MIPS assembly code add t, b, c # t = b + c sub a, t, d # a = t - d MC 542 A-1. 41

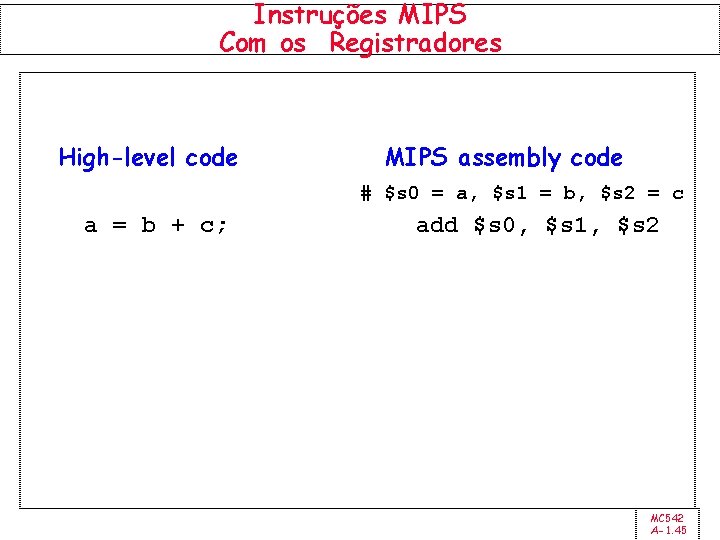

Instruções MIPS Operandos • Um computador necessita de localizações físicas de onde buscar os operandos binários. • Um computer busca operandos de: – Registradores – Memória – Constantes (também denominados de imediatos) MC 542 A-1. 42

Instruções MIPS Operandos • Memória é lenta. • Muitas arquiteturas possuem um conjunto pequeno de registradores (rápidos). • MIPS tem trinta e dois registradores de 32 -bit. • MIPS é chamado de arquitetura de 32 -bit devido seus operandos serem dados de 32 -bit. (Uma versão MIPS de 64 -bit também existe. ) MC 542 A-1. 43

Conjunto de registradores MIPS Name Register Number Usage $0 $at 0 1 the constant value 0 assembler temporary $v 0 -$v 1 2 -3 procedure return values $a 0 -$a 3 4 -7 procedure arguments $t 0 -$t 7 8 -15 temporaries $s 0 -$s 7 16 -23 saved variables $t 8 -$t 9 24 -25 more temporaries $k 0 -$k 1 26 -27 OS temporaries $gp 28 global pointer $sp 29 stack pointer $fp 30 frame pointer $ra 31 procedure return address MC 542 A-1. 44

Instruções MIPS Com os Registradores High-level code MIPS assembly code # $s 0 = a, $s 1 = b, $s 2 = c a = b + c; add $s 0, $s 1, $s 2 MC 542 A-1. 45

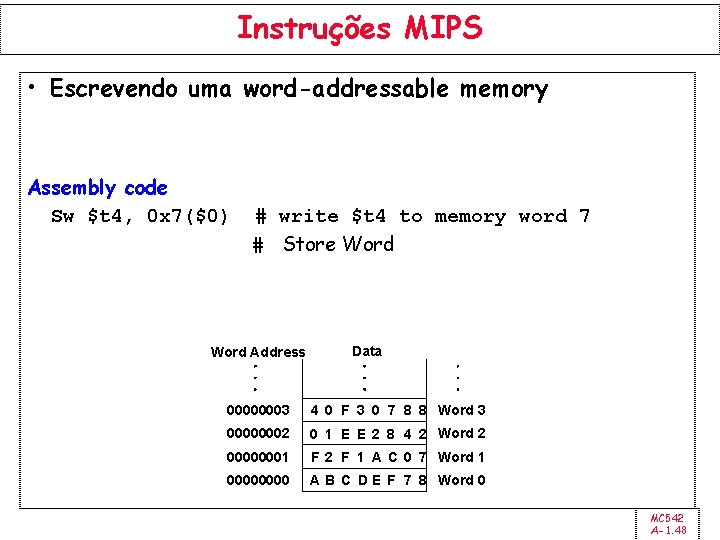

Instruções MIPS • Operandos em Memória – word-addressable memory Word Address Data 00000003 4 0 F 3 0 7 8 8 Word 3 00000002 0 1 E E 2 8 4 2 Word 2 00000001 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 MC 542 A-1. 46

Instruções MIPS • Lendo uma word-addressable memory Assembly code lw $s 3, 1($0) # read memory word 1 into $s 3 # Load Word Address Data 00000003 4 0 F 3 0 7 8 8 Word 3 00000002 0 1 E E 2 8 4 2 Word 2 00000001 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 MC 542 A-1. 47

Instruções MIPS • Escrevendo uma word-addressable memory Assembly code Sw $t 4, 0 x 7($0) # write $t 4 to memory word 7 # Store Word Address Data 00000003 4 0 F 3 0 7 8 8 Word 3 00000002 0 1 E E 2 8 4 2 Word 2 00000001 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 MC 542 A-1. 48

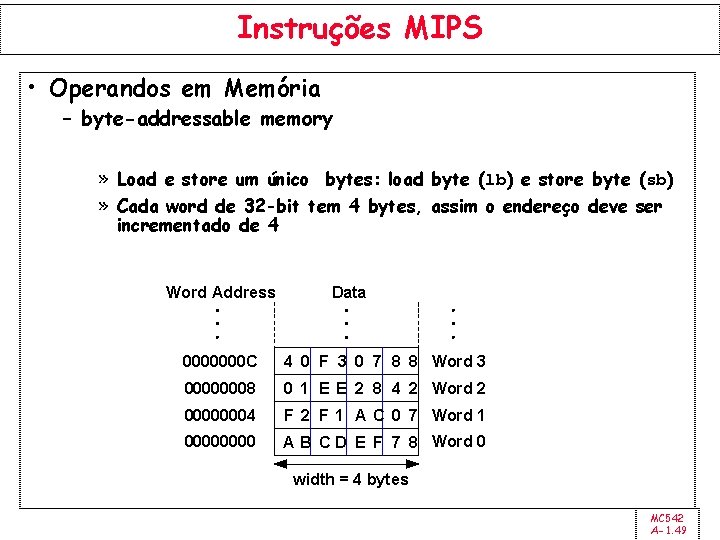

Instruções MIPS • Operandos em Memória – byte-addressable memory » Load e store um único bytes: load byte (lb) e store byte (sb) » Cada word de 32 -bit tem 4 bytes, assim o endereço deve ser incrementado de 4 Word Address Data 0000000 C 4 0 F 3 0 7 8 8 Word 3 00000008 0 1 E E 2 8 4 2 Word 2 00000004 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 width = 4 bytes MC 542 A-1. 49

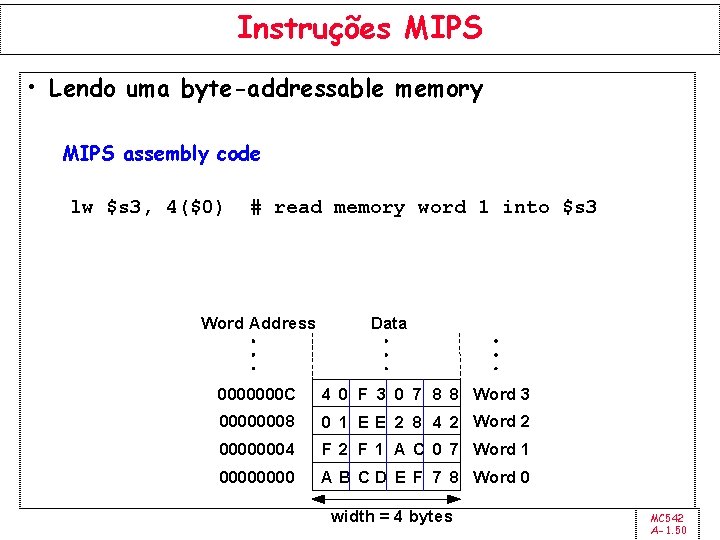

Instruções MIPS • Lendo uma byte-addressable memory MIPS assembly code lw $s 3, 4($0) # read memory word 1 into $s 3 Word Address Data 0000000 C 4 0 F 3 0 7 8 8 Word 3 00000008 0 1 E E 2 8 4 2 Word 2 00000004 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 width = 4 bytes MC 542 A-1. 50

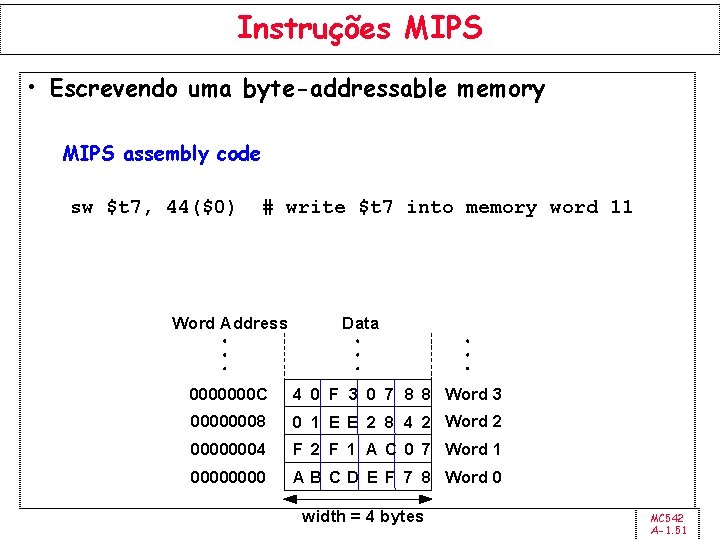

Instruções MIPS • Escrevendo uma byte-addressable memory MIPS assembly code sw $t 7, 44($0) # write $t 7 into memory word 11 Word Address Data 0000000 C 4 0 F 3 0 7 8 8 Word 3 00000008 0 1 E E 2 8 4 2 Word 2 00000004 F 2 F 1 A C 0 7 Word 1 0000 A B C D E F 7 8 Word 0 width = 4 bytes MC 542 A-1. 51

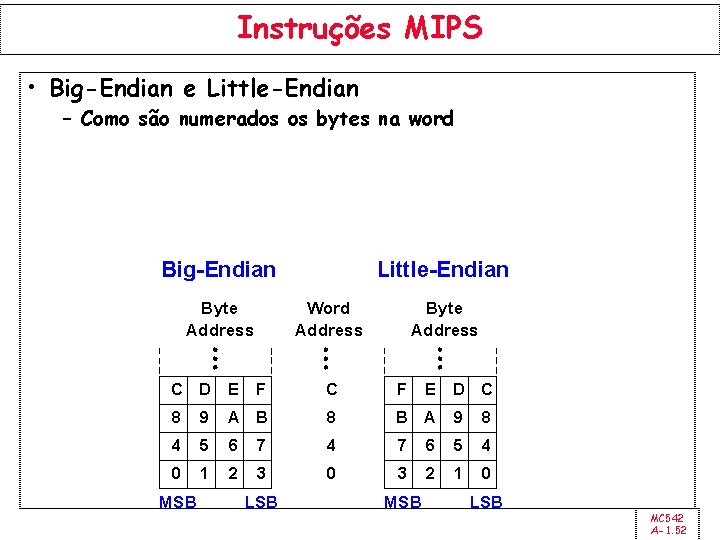

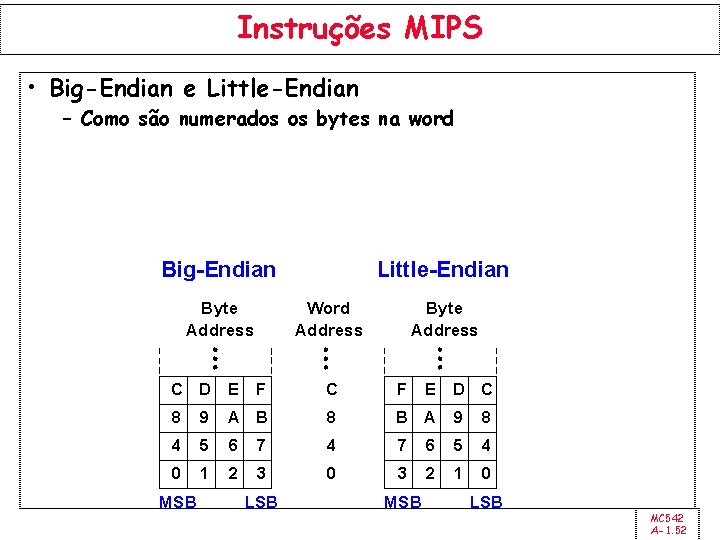

Instruções MIPS • Big-Endian e Little-Endian – Como são numerados os bytes na word Big-Endian Little-Endian Byte Address Word Address C D E F C F 8 9 A B 8 B A 9 8 4 5 6 7 4 7 6 5 4 0 1 2 3 0 3 2 1 0 MSB LSB Byte Address MSB E D C LSB MC 542 A-1. 52

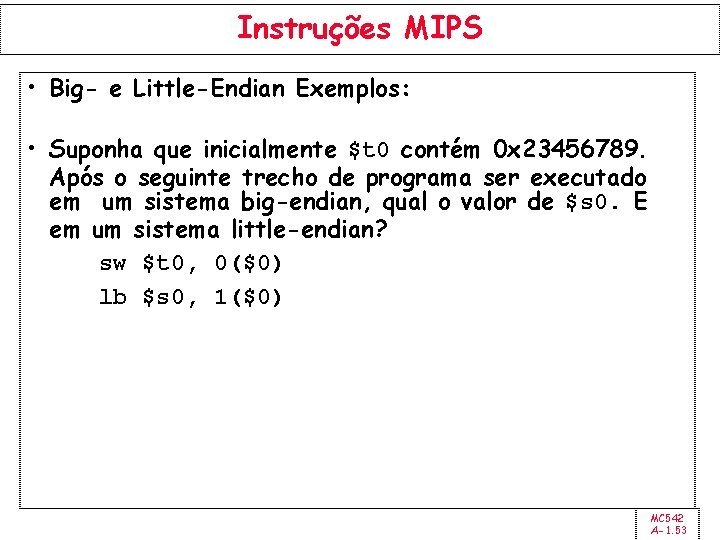

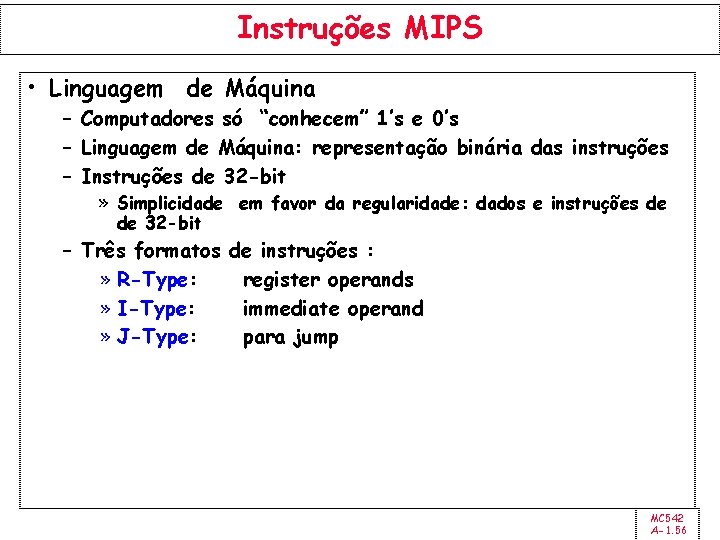

Instruções MIPS • Big- e Little-Endian Exemplos: • Suponha que inicialmente $t 0 contém 0 x 23456789. Após o seguinte trecho de programa ser executado em um sistema big-endian, qual o valor de $s 0. E em um sistema little-endian? sw $t 0, 0($0) lb $s 0, 1($0) MC 542 A-1. 53

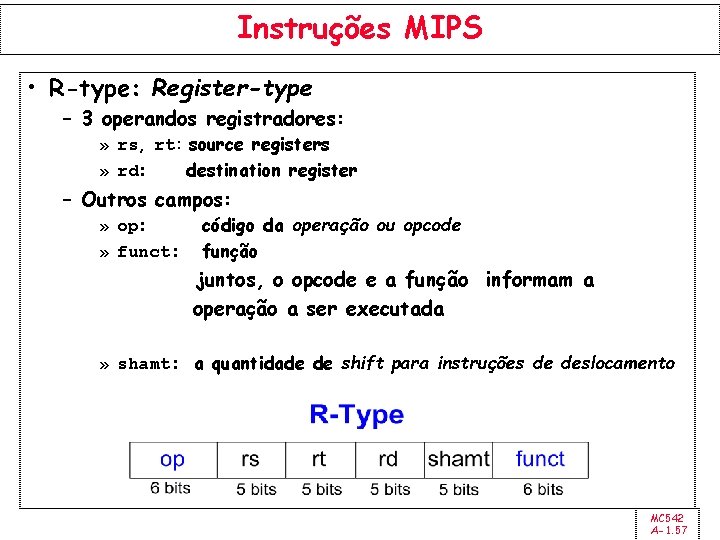

Instruções MIPS • Big- e Little-Endian Exemplos: – Suponha que inicialmente $t 0 contém 0 x 23456789. Após o seguinte trecho de programa ser executado em um sistema big-endian, qual o valor de $s 0. E em um sistema littleendian? sw $t 0, 0($0) lb $s 0, 1($0) – Big-endian: 0 x 00000045 – Little-endian: 0 x 00000067 MC 542 A-1. 54

Instruções MIPS • Operandos: Constantes/Imediatos – Um imediato é um número de 16 -bit em complemento de dois. High-level code a = a + 4; b = a – 12; MIPS assembly code # $s 0 = a, $s 1 = b addi $s 0, 4 addi $s 1, $s 0, -12 MC 542 A-1. 55

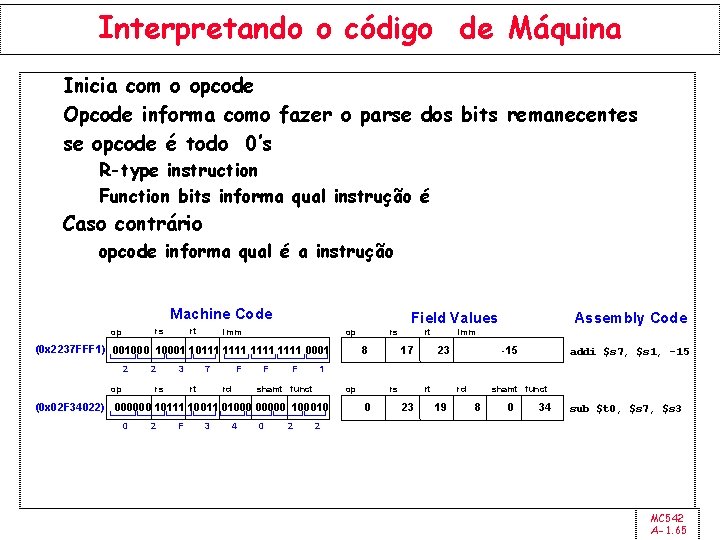

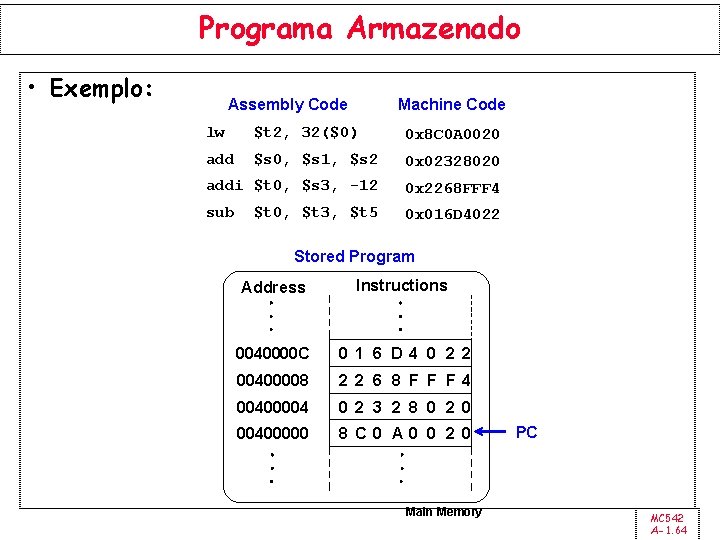

Instruções MIPS • Linguagem de Máquina – Computadores só “conhecem” 1’s e 0’s – Linguagem de Máquina: representação binária das instruções – Instruções de 32 -bit » Simplicidade em favor da regularidade: dados e instruções de de 32 -bit – Três formatos de instruções : » R-Type: register operands » I-Type: immediate operand » J-Type: para jump MC 542 A-1. 56

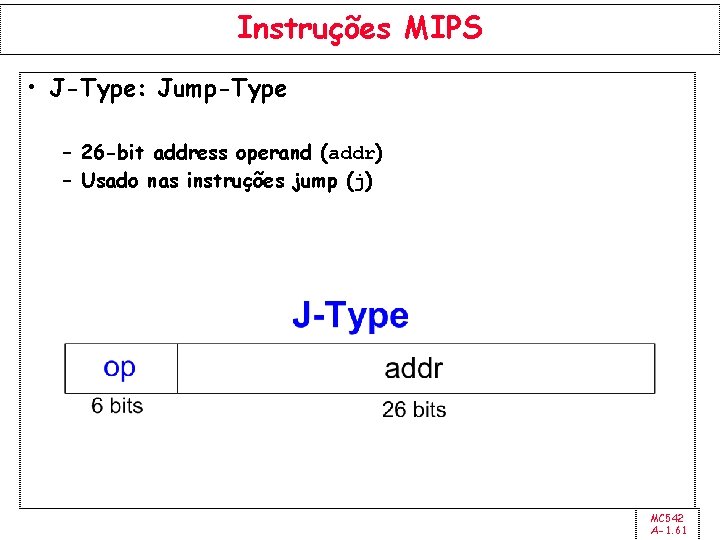

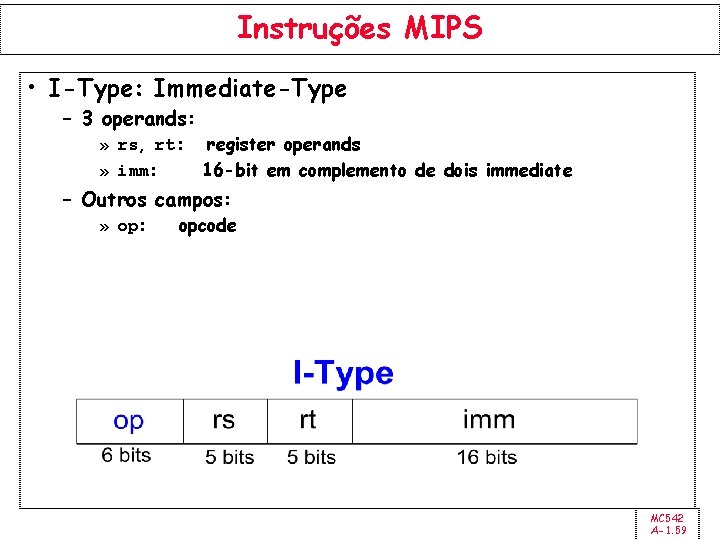

Instruções MIPS • R-type: Register-type – 3 operandos registradores: » rs, rt: source registers » rd: destination register – Outros campos: » op: » funct: código da operação ou opcode função juntos, o opcode e a função informam a operação a ser executada » shamt: a quantidade de shift para instruções de deslocamento MC 542 A-1. 57

Instruções MIPS Assembly Code add $s 0, $s 1, $s 2 sub $t 0, $t 3, $t 5 Nota: a ordem dos registradores no código assembly: add rd, rs, rt MC 542 A-1. 58

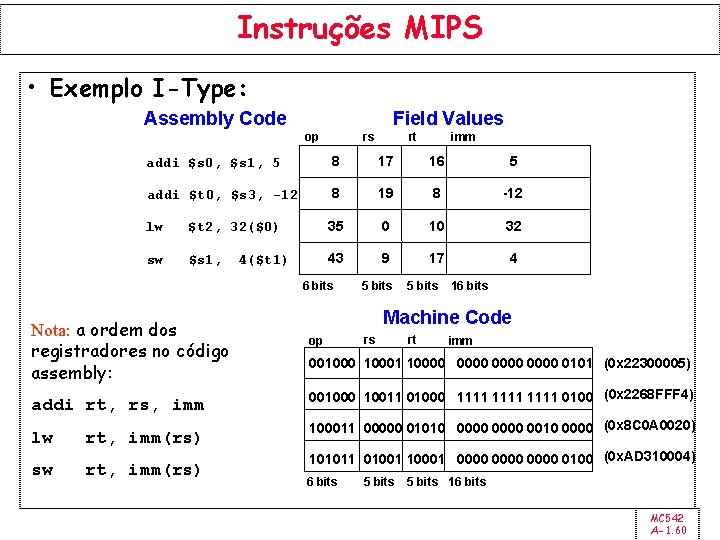

Instruções MIPS • I-Type: Immediate-Type – 3 operands: » rs, rt: » imm: register operands 16 -bit em complemento de dois immediate – Outros campos: » op: opcode MC 542 A-1. 59

Instruções MIPS • Exemplo I-Type: Assembly Code Field Values rs op rt imm addi $s 0, $s 1, 5 8 17 16 5 addi $t 0, $s 3, -12 8 19 8 -12 lw $t 2, 32($0) 35 0 10 32 sw $s 1, 43 9 17 4 4($t 1) 6 bits Nota: a ordem dos registradores no código assembly: addi rt, rs, imm lw rt, imm(rs) sw rt, imm(rs) 5 bits 16 bits Machine Code op rs rt imm 0010001 10000 0101 (0 x 22300005) 001000 10011 01000 1111 0100 (0 x 2268 FFF 4) 100011 00000 01010 0000 0010 0000 (0 x 8 C 0 A 0020) 101011 01001 10001 0000 0100 (0 x. AD 310004) 6 bits 5 bits 16 bits MC 542 A-1. 60

Instruções MIPS • J-Type: Jump-Type – 26 -bit address operand (addr) – Usado nas instruções jump (j) MC 542 A-1. 61

Instruções MIPS • Formatos das Instruções MC 542 A-1. 62

Programa Armazenado • Instruções e dados de 32 -bit armazenados na memória • Seqüência de instruções: é a única diferença entre dois programas • Execuçãode um novo programa: – Simplismente armazene o novo programa na memória • Execução do programa pelo hardware do processador: – fetches (reads) as instruções da memória em seqüência – Executa a operação especificada • Um program counter (PC) indica a instrução corrente (ou a próxima instrução). • no MIPS, programas tipicamente iniciam no endereço de memória 0 x 00400000. MC 542 A-1. 63

Programa Armazenado • Exemplo: Assembly Code Machine Code lw $t 2, 32($0) 0 x 8 C 0 A 0020 add $s 0, $s 1, $s 2 0 x 02328020 addi $t 0, $s 3, -12 0 x 2268 FFF 4 sub 0 x 016 D 4022 $t 0, $t 3, $t 5 Stored Program Address Instructions 0040000 C 0 1 6 D 4 0 2 2 00400008 2 2 6 8 F F F 4 00400004 0 2 3 2 8 0 2 0 00400000 8 C 0 A 0 0 2 0 Main Memory PC MC 542 A-1. 64

Interpretando o código de Máquina Inicia com o opcode Opcode informa como fazer o parse dos bits remanecentes se opcode é todo 0’s R-type instruction Function bits informa qual instrução é Caso contrário opcode informa qual é a instrução Machine Code rs op rt Field Values imm op (0 x 2237 FFF 1) 0010001 10111 1111 0001 2 op 2 3 rs 7 rt F rd F F 2 F 3 shamt funct 4 0 2 8 rt 17 Assembly Code imm 23 -15 addi $s 7, $s 1, -15 1 rs op (0 x 02 F 34022) 000000 10111 10011 01000 00000 100010 0 rs 0 rt 23 rd 19 shamt funct 8 0 34 sub $t 0, $s 7, $s 3 2 MC 542 A-1. 65

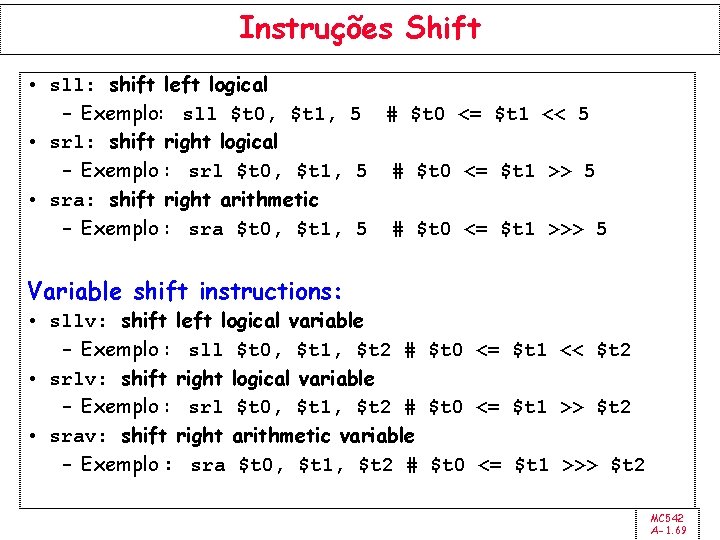

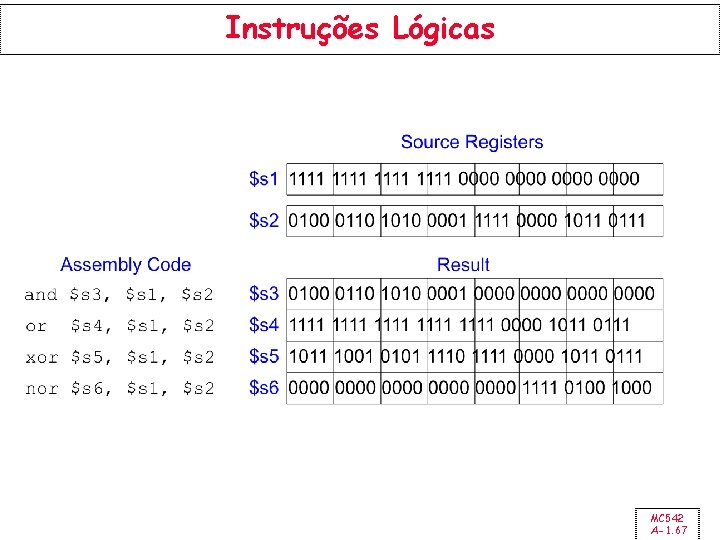

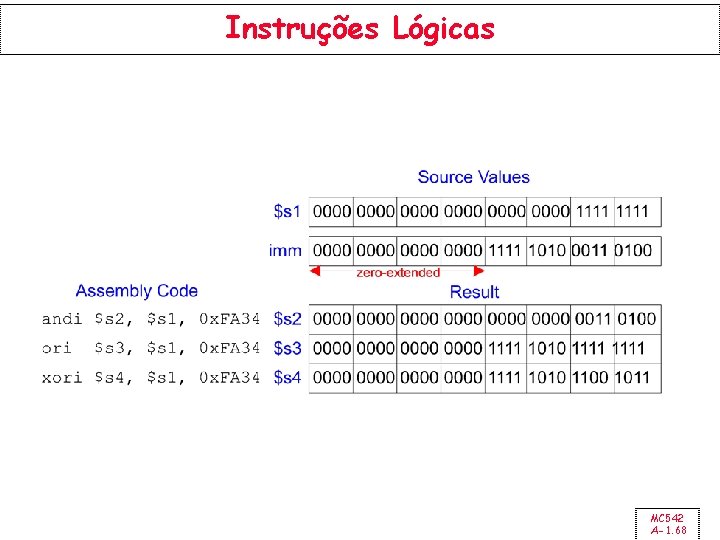

Instruções Lógicas • and, or, xor, nor – and: útil para mascará de bits » Estraíndo o byte menos significativo de uma word: 0 x. F 234012 F AND 0 x. FF = 0 x 0000002 F – or: útil para combinar bits » Combinar 0 x. F 2340000 com 0 x 000012 BC: 0 x. F 2340000 OR 0 x 000012 BC = 0 x. F 23412 BC – nor: útil para inverter bits: » A NOR $0 = NOT A • andi, ori, xori – O imediato de 16 -bit é zero-extended (não sign-extended) MC 542 A-1. 66

Instruções Lógicas MC 542 A-1. 67

Instruções Lógicas MC 542 A-1. 68

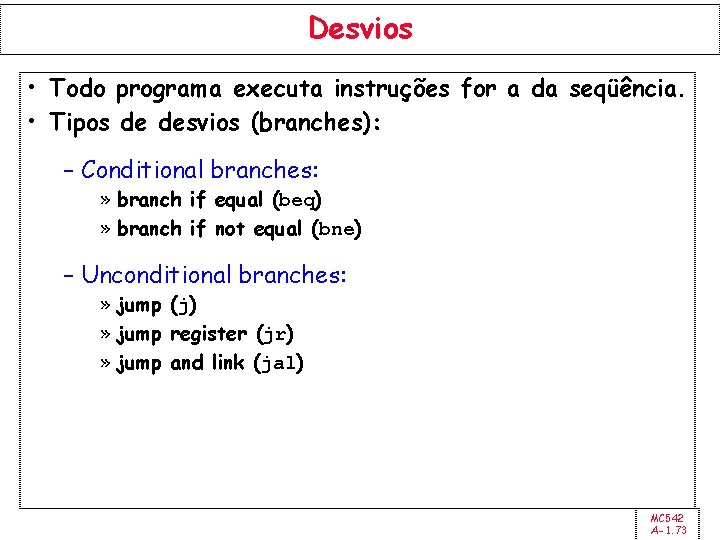

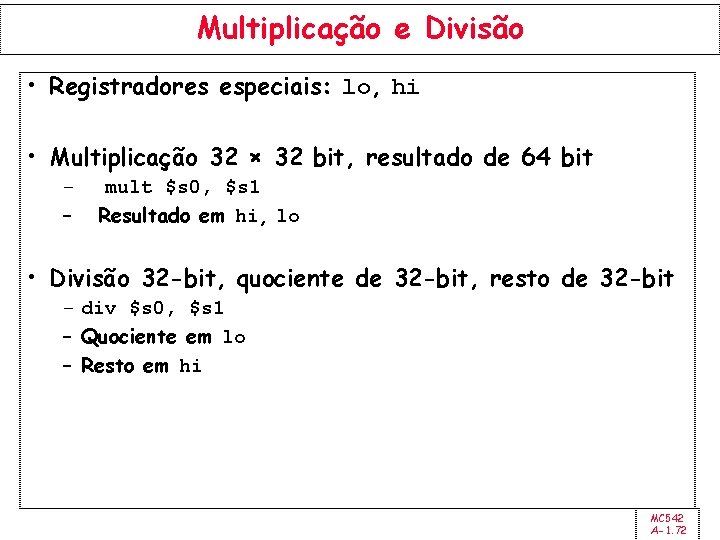

Instruções Shift • sll: shift left logical – Exemplo: sll $t 0, $t 1, 5 # $t 0 <= $t 1 << 5 • srl: shift right logical – Exemplo : srl $t 0, $t 1, 5 # $t 0 <= $t 1 >> 5 • sra: shift right arithmetic – Exemplo : sra $t 0, $t 1, 5 # $t 0 <= $t 1 >>> 5 Variable shift instructions: • sllv: shift left logical variable – Exemplo : sll $t 0, $t 1, $t 2 # $t 0 <= $t 1 << $t 2 • srlv: shift right logical variable – Exemplo : srl $t 0, $t 1, $t 2 # $t 0 <= $t 1 >> $t 2 • srav: shift right arithmetic variable – Exemplo : sra $t 0, $t 1, $t 2 # $t 0 <= $t 1 >>> $t 2 MC 542 A-1. 69

Instruções Shift MC 542 A-1. 70

Gerando Constantes • Constantes de 16 -bit usando addi: High-level code // int is a 32 -bit signed word int a = 0 x 4 f 3 c; MIPS assembly code # $s 0 = a addi $s 0, $0, 0 x 4 f 3 c • Constantes de 32 -bit usando load upper immediate (lui) e ori: (lui loads o imediato de 16 -bit na metade mais significativa do registrador seta a menos significativa com 0. ) High-level code int a = 0 x. FEDC 8765; MIPS assembly code # $s 0 = a lui $s 0, 0 x. FEDC ori $s 0, 0 x 8765 MC 542 A-1. 71

Multiplicação e Divisão • Registradores especiais: lo, hi • Multiplicação 32 × 32 bit, resultado de 64 bit – – mult $s 0, $s 1 Resultado em hi, lo • Divisão 32 -bit, quociente de 32 -bit, resto de 32 -bit – div $s 0, $s 1 – Quociente em lo – Resto em hi MC 542 A-1. 72

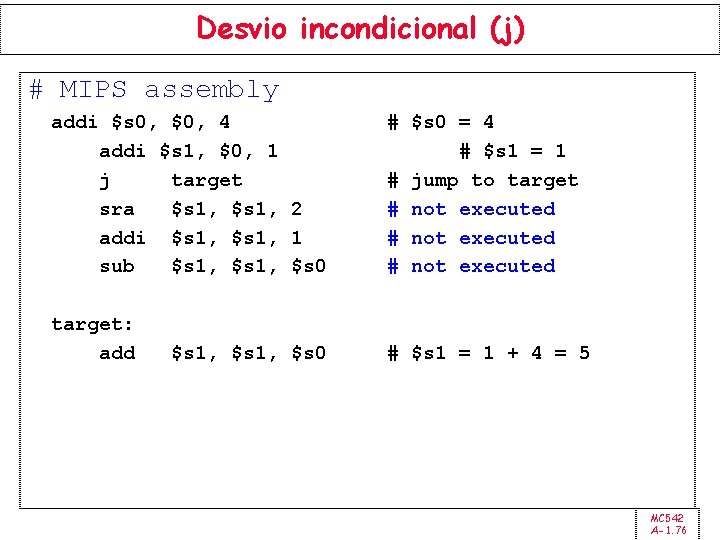

Desvios • Todo programa executa instruções for a da seqüência. • Tipos de desvios (branches): – Conditional branches: » branch if equal (beq) » branch if not equal (bne) – Unconditional branches: » jump (j) » jump register (jr) » jump and link (jal) MC 542 A-1. 73

Beq: exemplo # MIPS assembly addi sll beq addi sub $s 0, $s 1, $0, 4 $0, 1 $s 1, 2 $s 1, target $s 1, 1 $s 1, $s 0 target: add $s 1, $s 0 # # # $s 0 = 0 + 4 = 4 $s 1 = 0 + 1 = 1 $s 1 = 1 << 2 = 4 branch is taken not executed # label # $s 1 = 4 + 4 = 8 MC 542 A-1. 74

Bne: exemplo # MIPS assembly addi sll bne addi sub target: add $s 0, $s 1, $0, 4 $0, 1 $s 1, 2 $s 1, target $s 1, 1 $s 1, $s 0 # # # $s 0 = 0 + 4 = 4 $s 1 = 0 + 1 = 1 $s 1 = 1 << 2 = 4 branch not taken $s 1 = 4 + 1 = 5 $s 1 = 5 – 4 = 1 # $s 1 = 1 + 4 = 5 MC 542 A-1. 75

Desvio incondicional (j) # MIPS assembly addi $s 0, $0, 4 addi $s 1, $0, 1 j target sra $s 1, 2 addi $s 1, 1 sub $s 1, $s 0 # $s 0 = 4 # $s 1 = 1 # jump to target # not executed target: add # $s 1 = 1 + 4 = 5 $s 1, $s 0 MC 542 A-1. 76

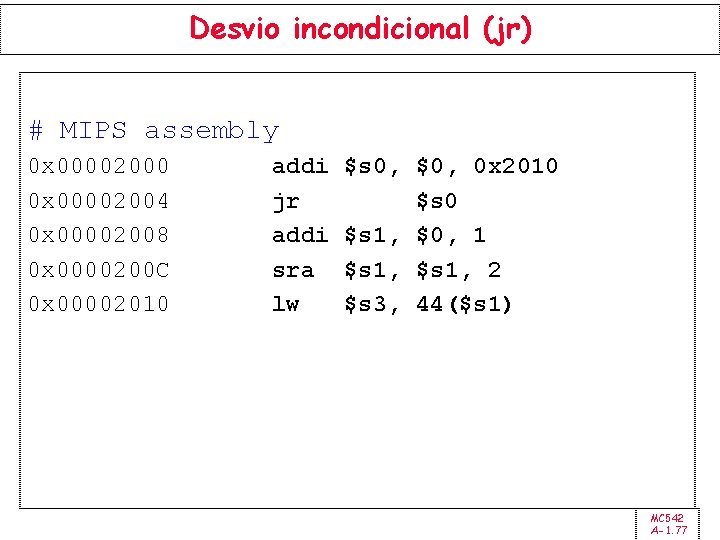

Desvio incondicional (jr) # MIPS assembly 0 x 00002000 0 x 00002004 0 x 00002008 0 x 0000200 C 0 x 00002010 addi jr addi sra lw $s 0, $0, 0 x 2010 $s 1, $0, 1 $s 1, 2 $s 3, 44($s 1) MC 542 A-1. 77

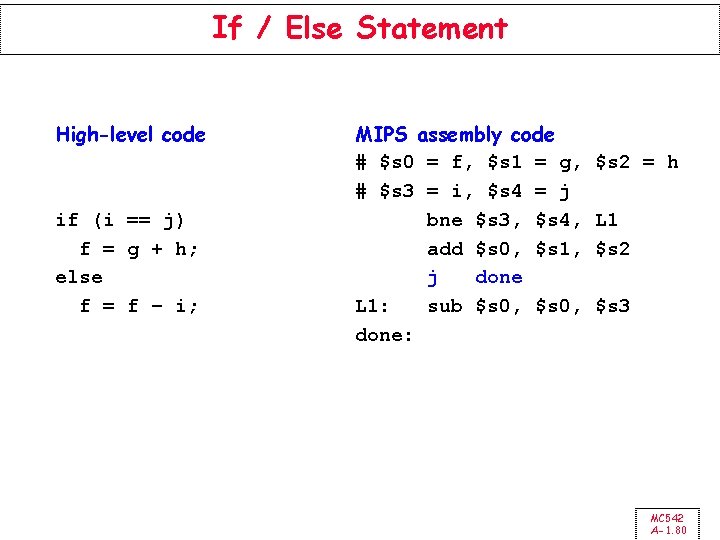

Construções de Alto Nível • if statements • if/else statements • while loops • for loops MC 542 A-1. 78

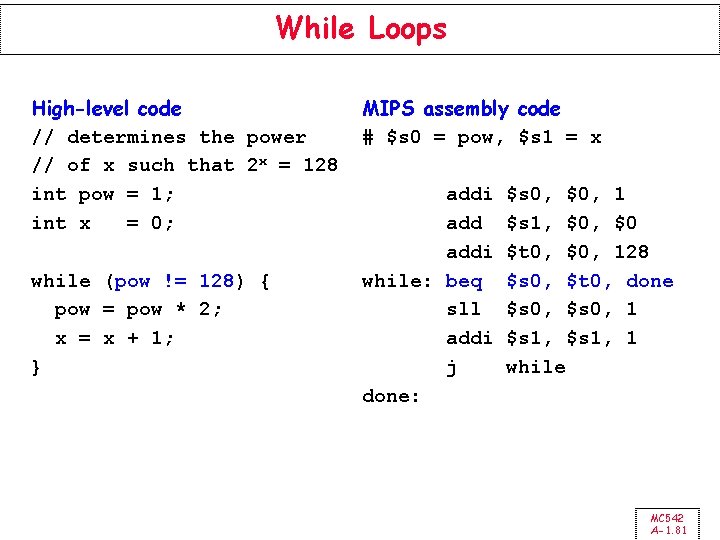

If Statement High-level code if (i == j) f = g + h; MIPS assembly code # $s 0 = f, $s 1 = g, $s 2 = h # $s 3 = i, $s 4 = j bne $s 3, $s 4, L 1 add $s 0, $s 1, $s 2 f = f – i; L 1: sub $s 0, $s 3 Note que em assembly o teste é o oposto (i != j) do teste em alto nível (i == j). MC 542 A-1. 79

If / Else Statement High-level code if (i == j) f = g + h; else f = f – i; MIPS assembly code # $s 0 = f, $s 1 = g, # $s 3 = i, $s 4 = j bne $s 3, $s 4, add $s 0, $s 1, j done L 1: sub $s 0, done: $s 2 = h L 1 $s 2 $s 3 MC 542 A-1. 80

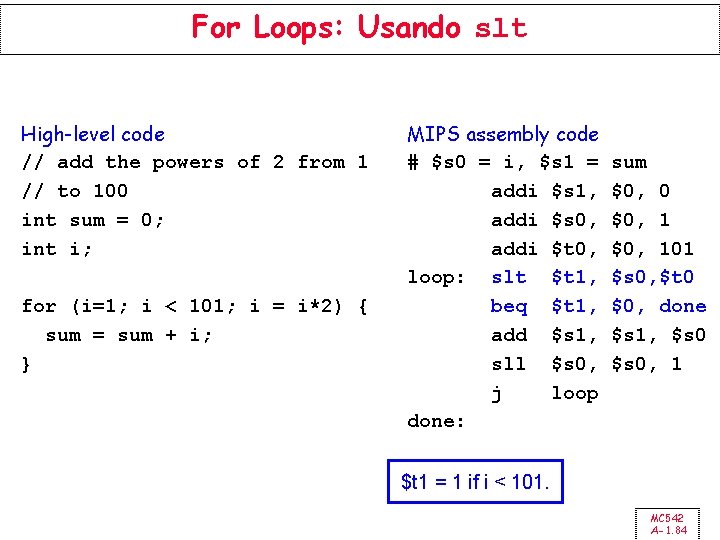

While Loops High-level code // determines the power // of x such that 2 x = 128 int pow = 1; int x = 0; while (pow != 128) { pow = pow * 2; x = x + 1; } MIPS assembly code # $s 0 = pow, $s 1 = x addi while: beq sll addi j done: $s 0, $0, 1 $s 1, $0 $t 0, $0, 128 $s 0, $t 0, done $s 0, 1 $s 1, 1 while MC 542 A-1. 81

For Loops A forma geral de um for loop é: for (inicialização; condição; loop) corpo do loop • • inicialização: executado antes do loop condição: testada no inicio de cada iteração loop: executa no fim de cada iteração Corpodo loop: executado para cada vez que a condição é satisfeita MC 542 A-1. 82

For Loops High-level code MIPS assembly code // add the numbers from 0 to 9 # $s 0 = i, $s 1 = int sum = 0; addi $s 1, int i; add $s 0, addi $t 0, for (i=0; i!=10; i = i+1) { for: beq $s 0, sum = sum + i; add $s 1, } addi $s 0, j for done: sum $0, 0 $0, $0 $0, 10 $t 0, done $s 1, $s 0, 1 MC 542 A-1. 83

For Loops: Usando slt High-level code // add the powers of 2 from 1 // to 100 int sum = 0; int i; for (i=1; i < 101; i = i*2) { sum = sum + i; } MIPS assembly code # $s 0 = i, $s 1 = addi $s 1, addi $s 0, addi $t 0, loop: slt $t 1, beq $t 1, add $s 1, sll $s 0, j loop done: sum $0, 0 $0, 101 $s 0, $t 0 $0, done $s 1, $s 0, 1 $t 1 = 1 if i < 101. MC 542 A-1. 84

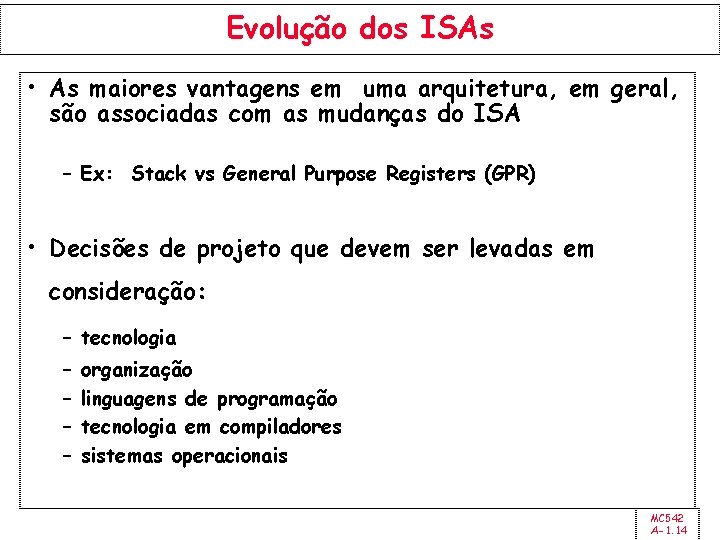

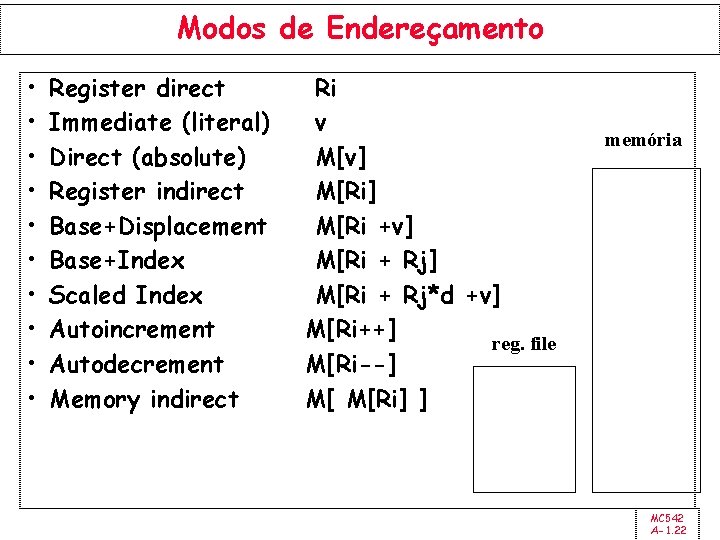

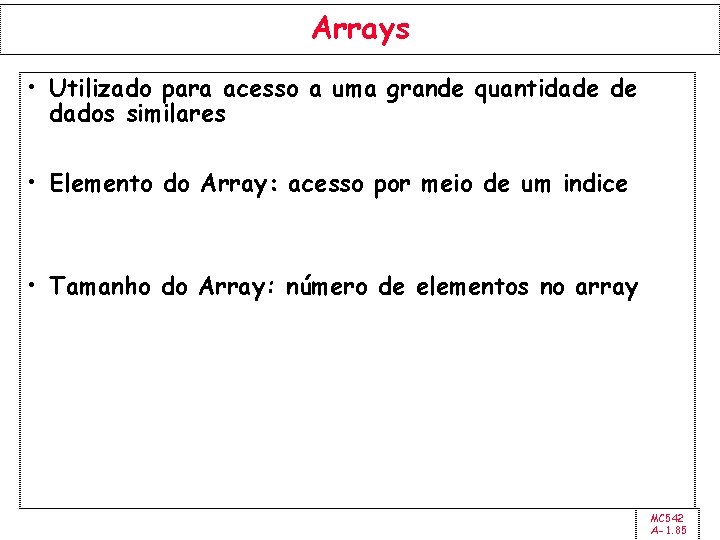

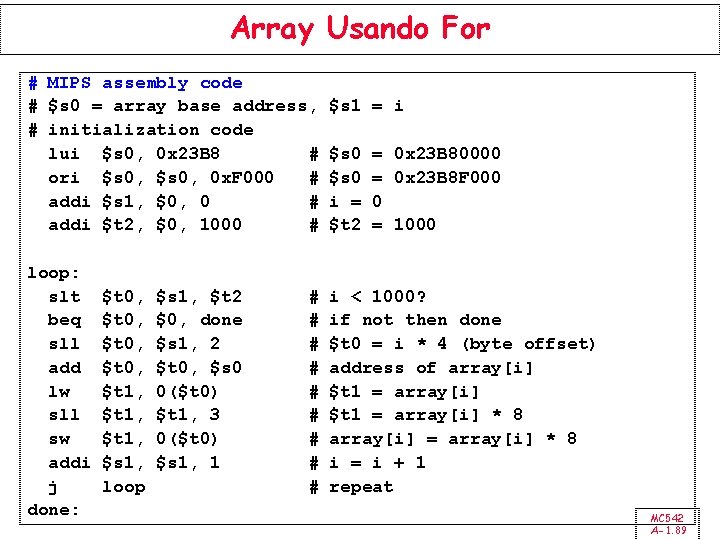

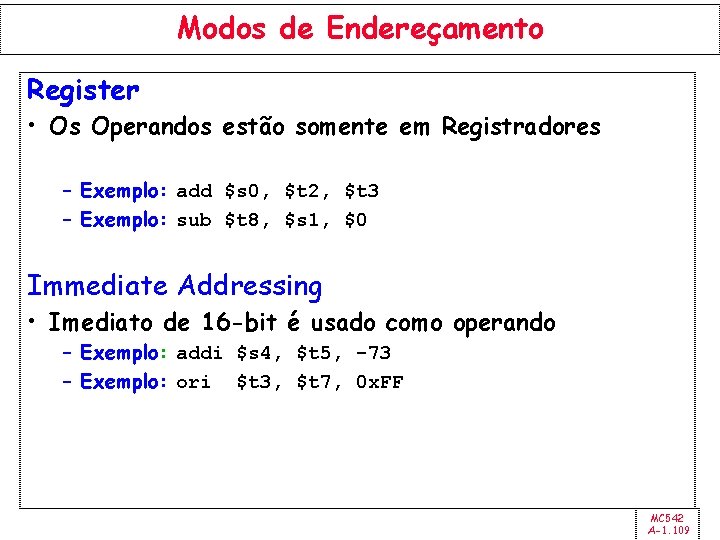

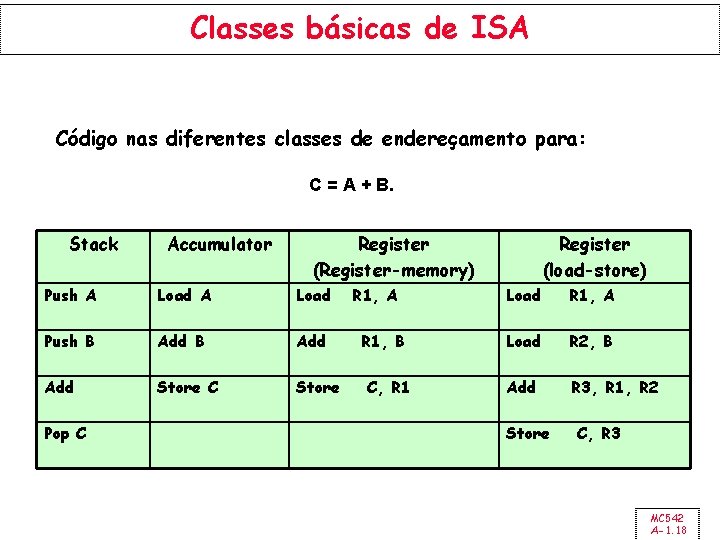

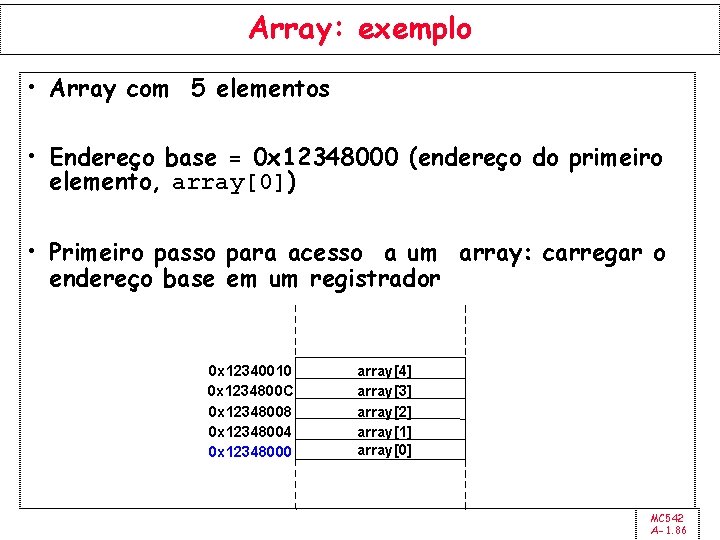

Arrays • Utilizado para acesso a uma grande quantidade de dados similares • Elemento do Array: acesso por meio de um indice • Tamanho do Array: número de elementos no array MC 542 A-1. 85

Array: exemplo • Array com 5 elementos • Endereço base = 0 x 12348000 (endereço do primeiro elemento, array[0]) • Primeiro passo para acesso a um array: carregar o endereço base em um registrador 0 x 12340010 0 x 1234800 C 0 x 12348008 0 x 12348004 0 x 12348000 array[4] array[3] array[2] array[1] array[0] MC 542 A-1. 86

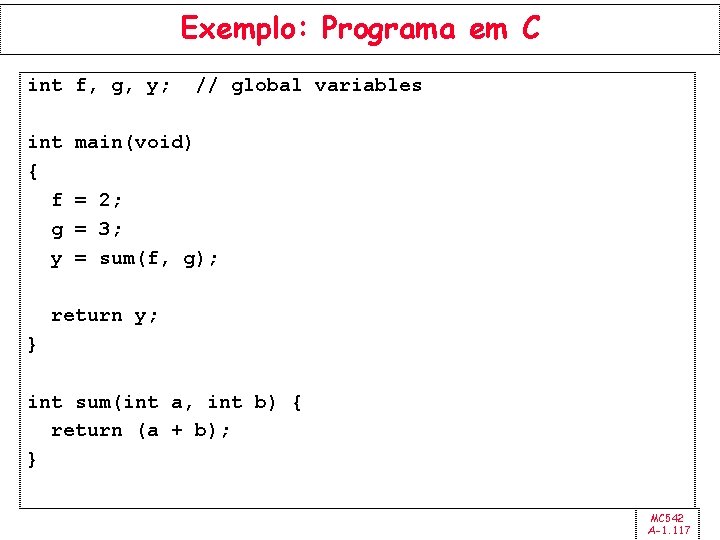

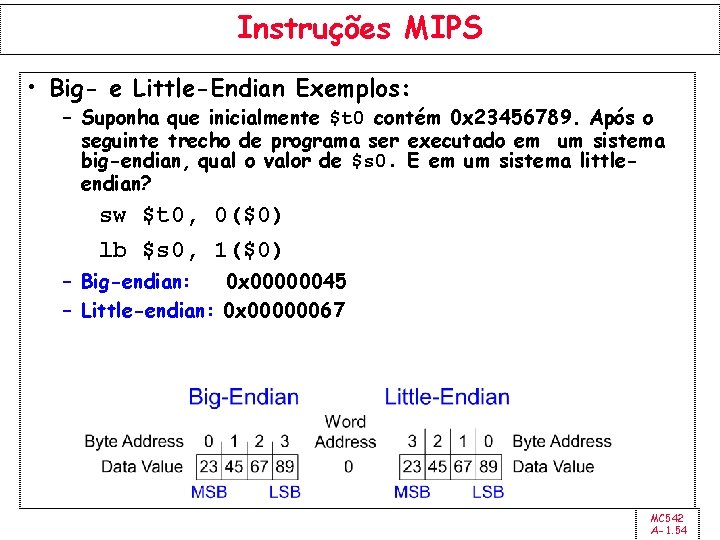

![Array highlevel code int array5 array0 array0 2 array1 array1 Array // high-level code int array[5]; array[0] = array[0] * 2; array[1] = array[1]](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-87.jpg)

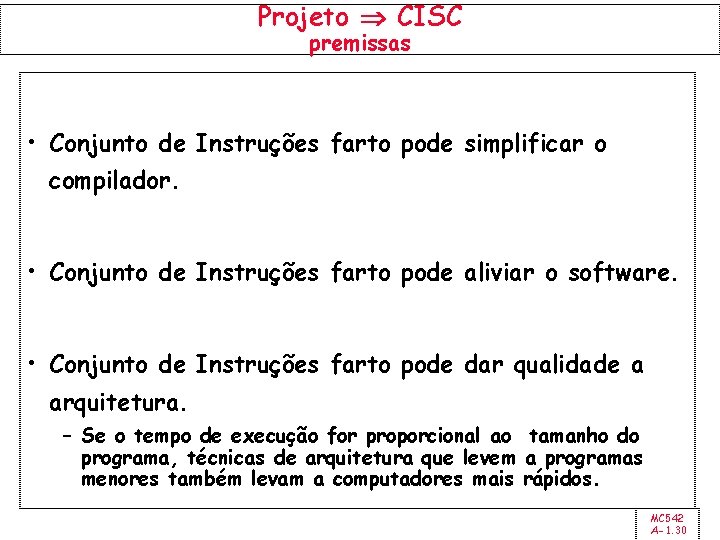

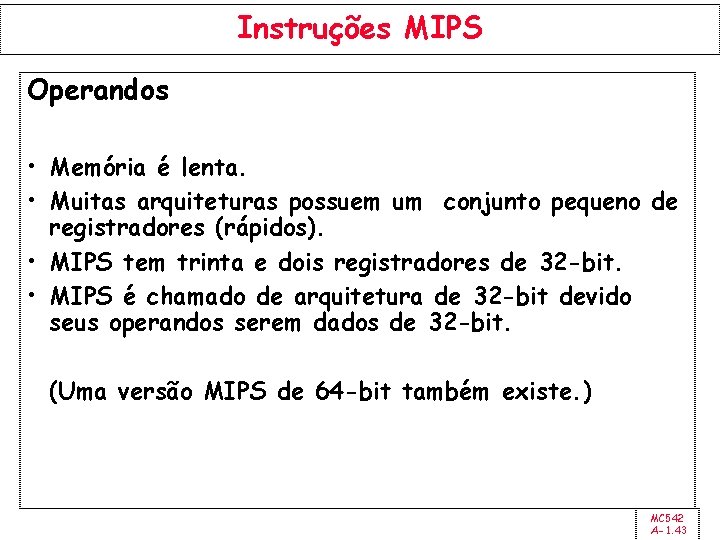

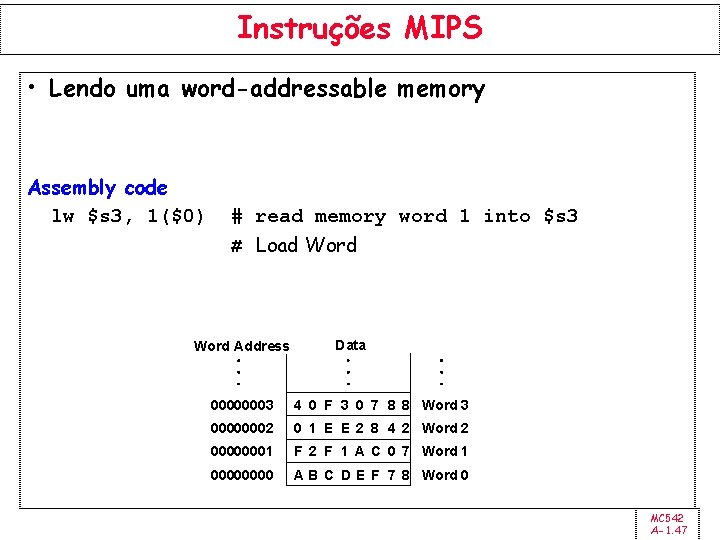

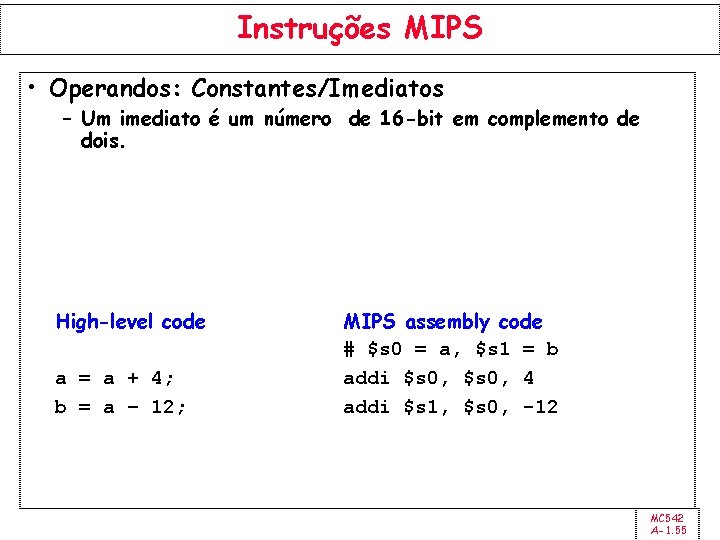

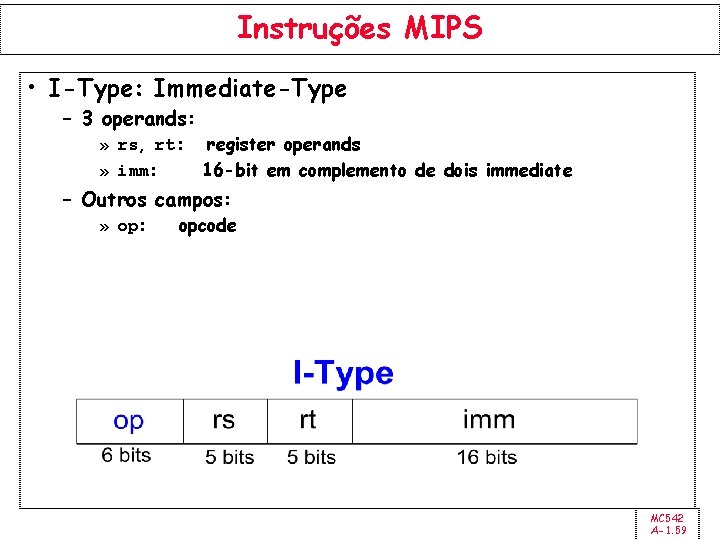

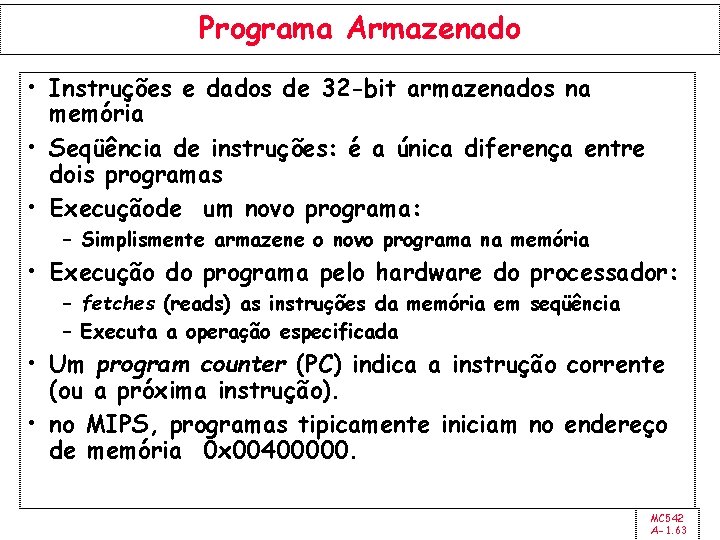

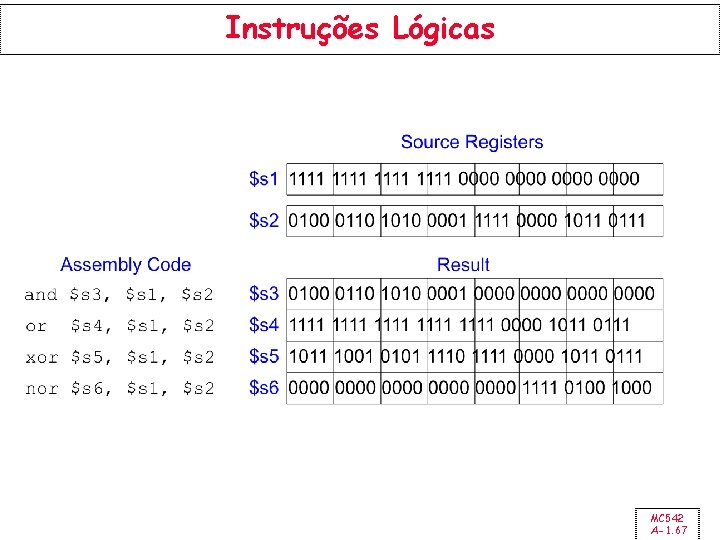

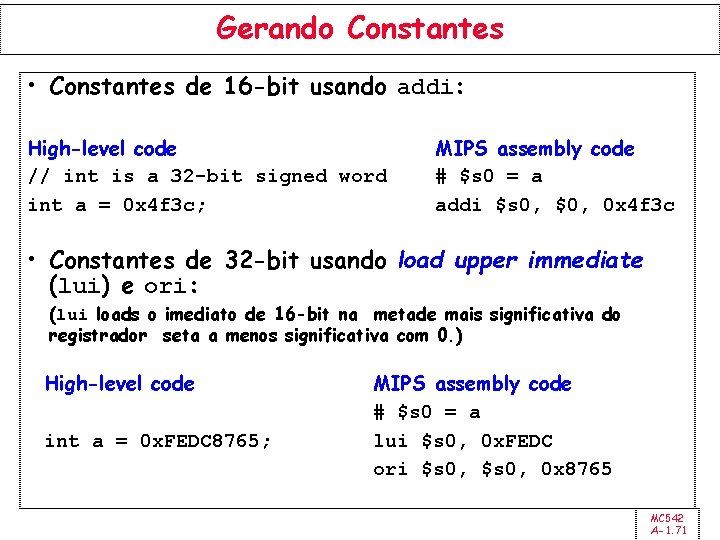

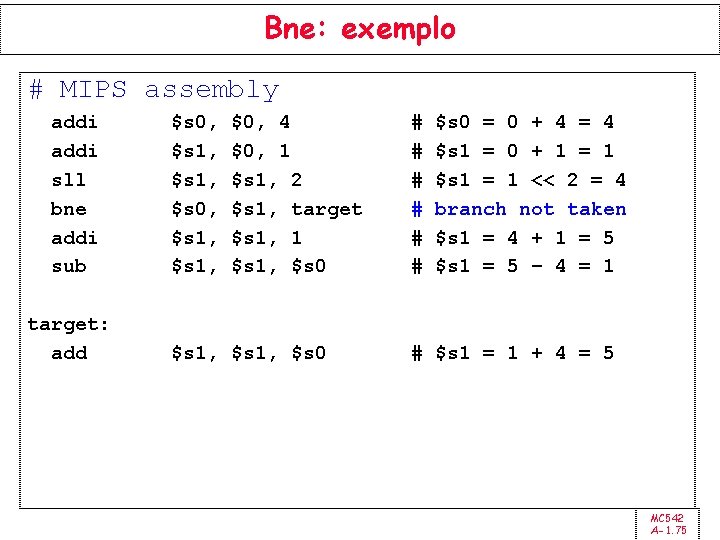

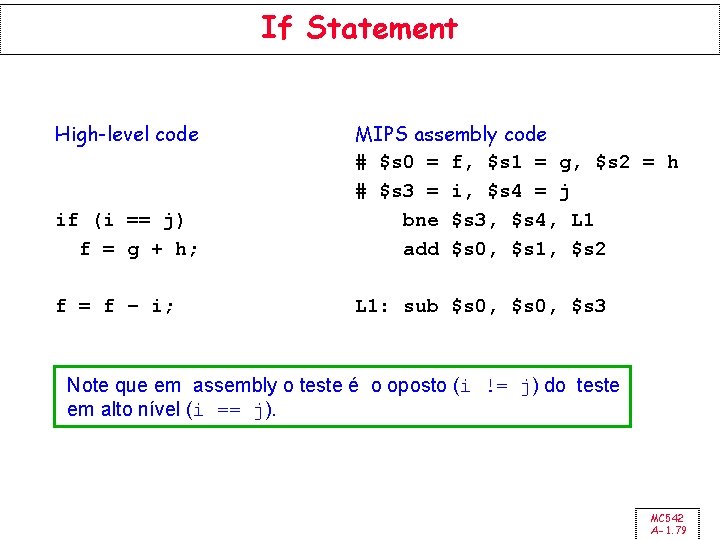

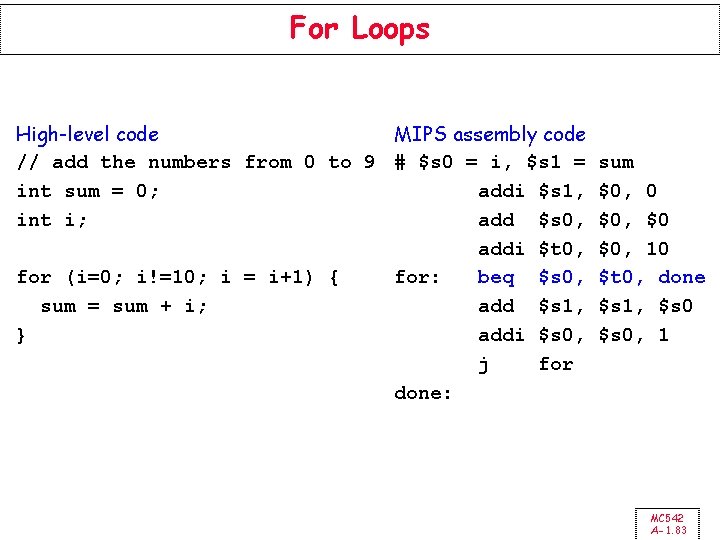

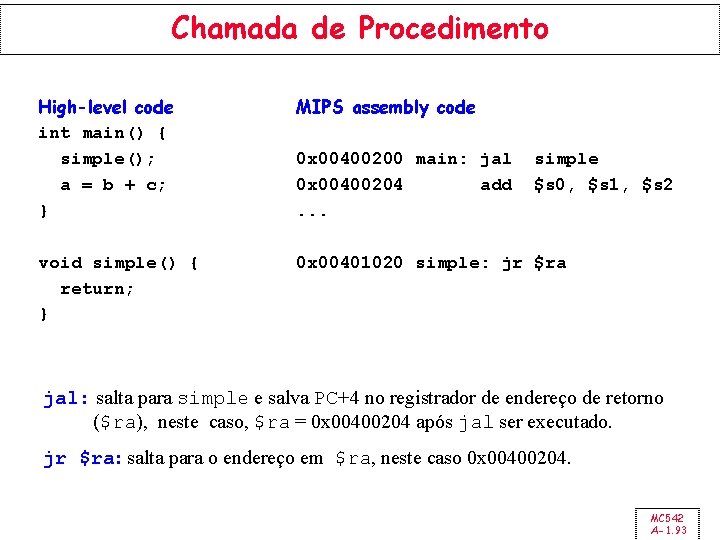

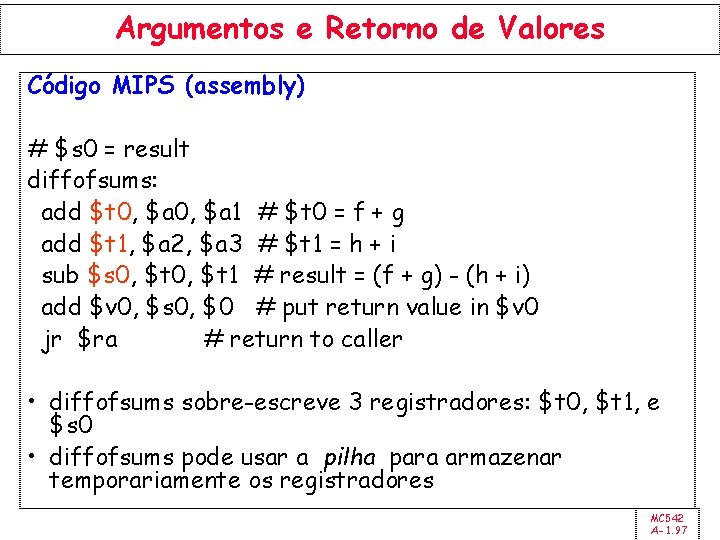

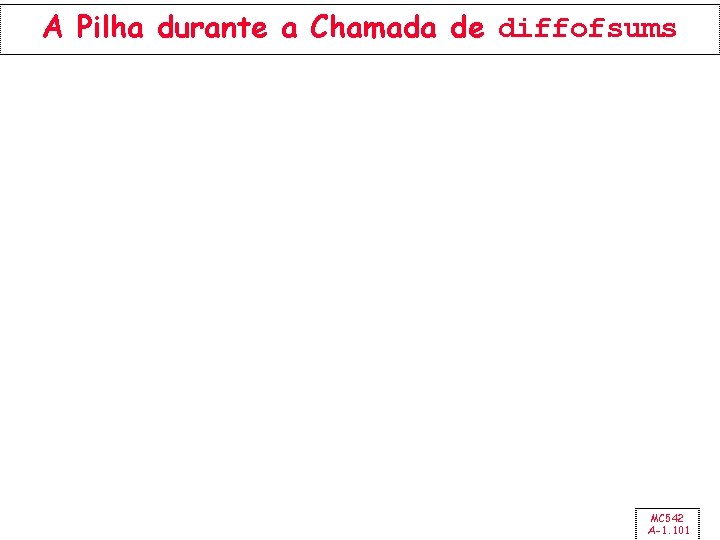

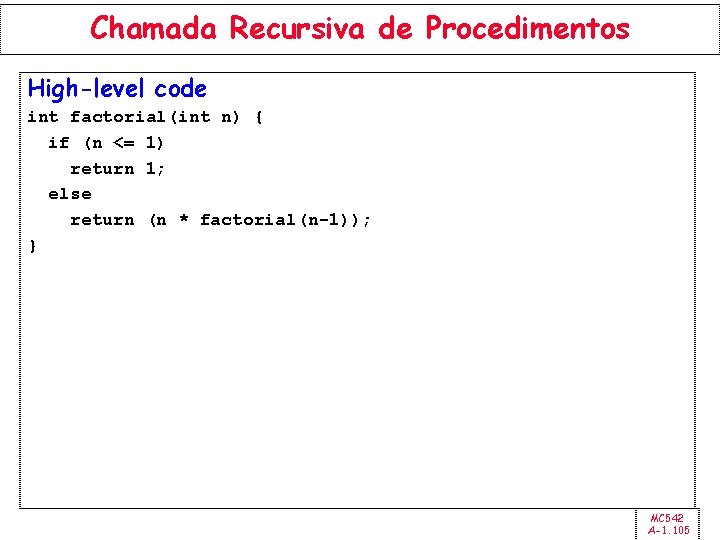

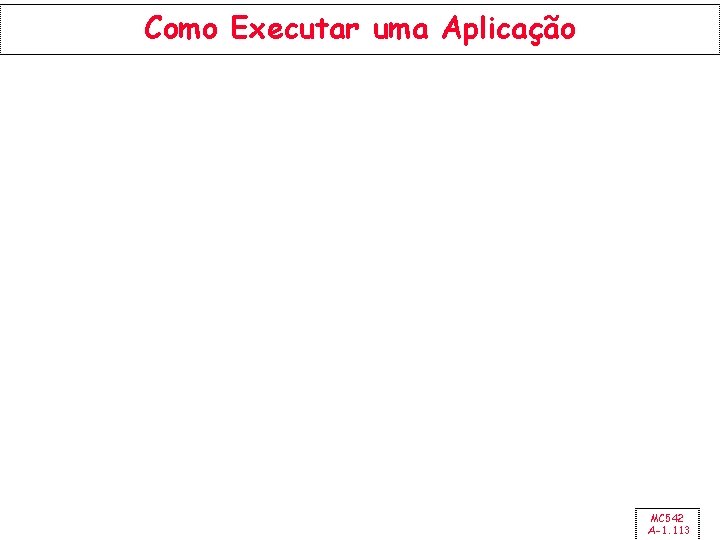

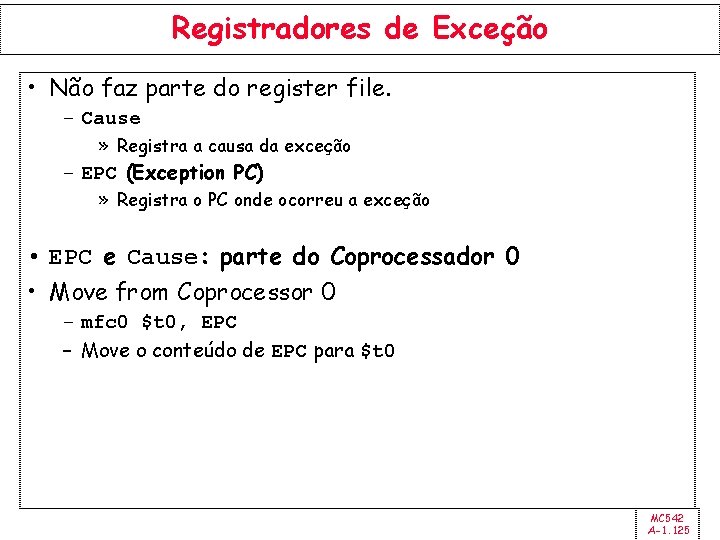

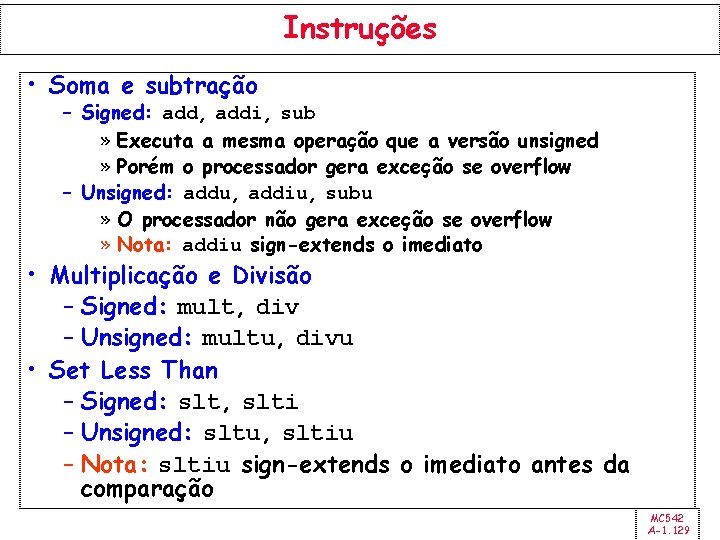

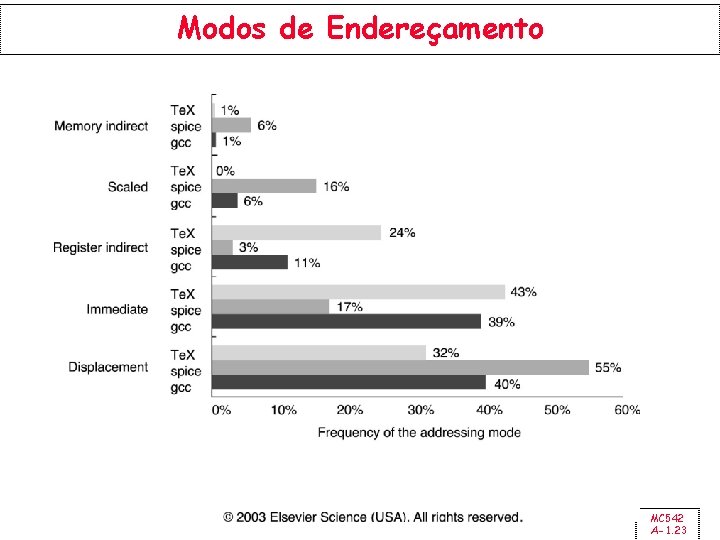

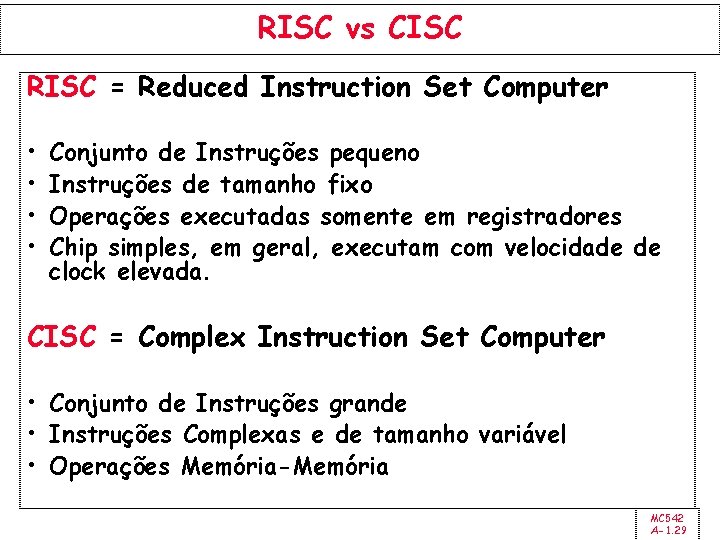

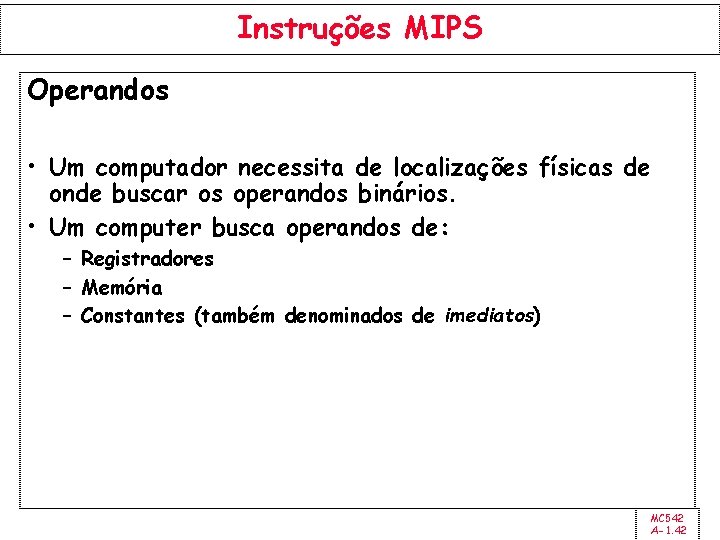

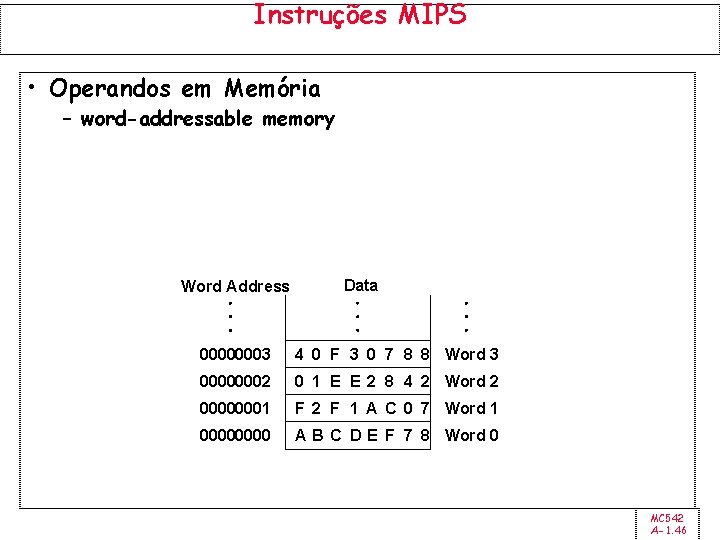

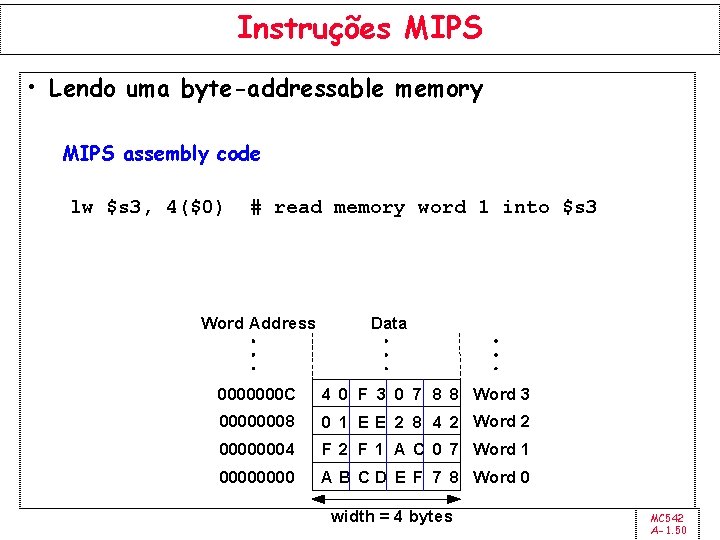

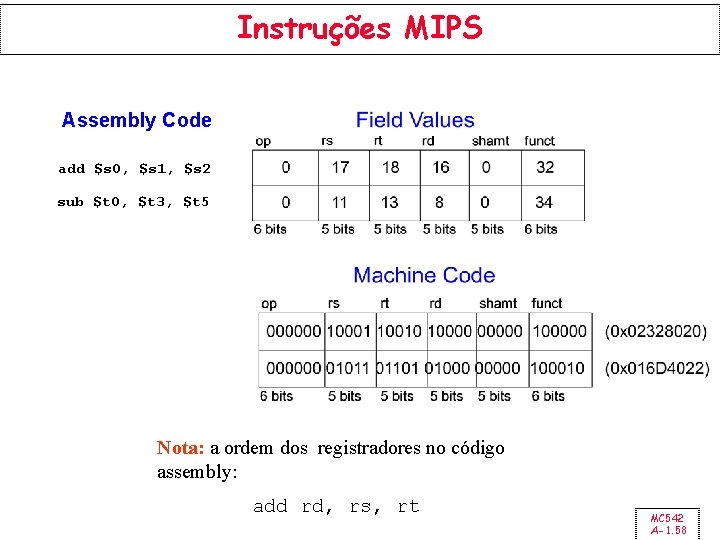

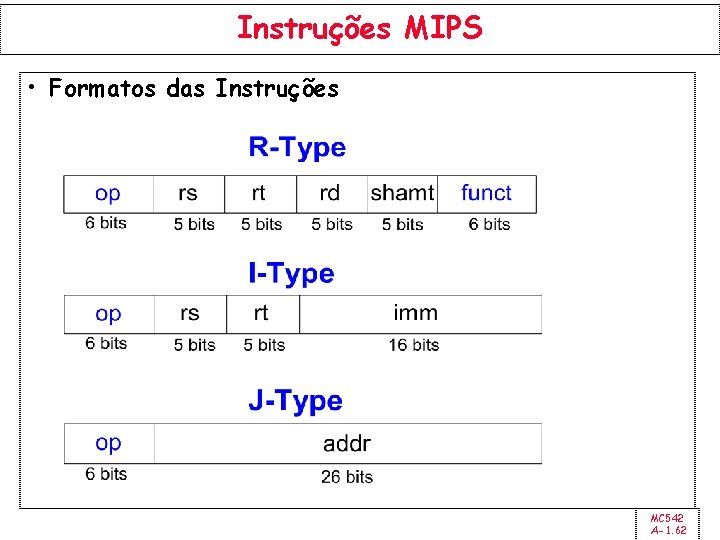

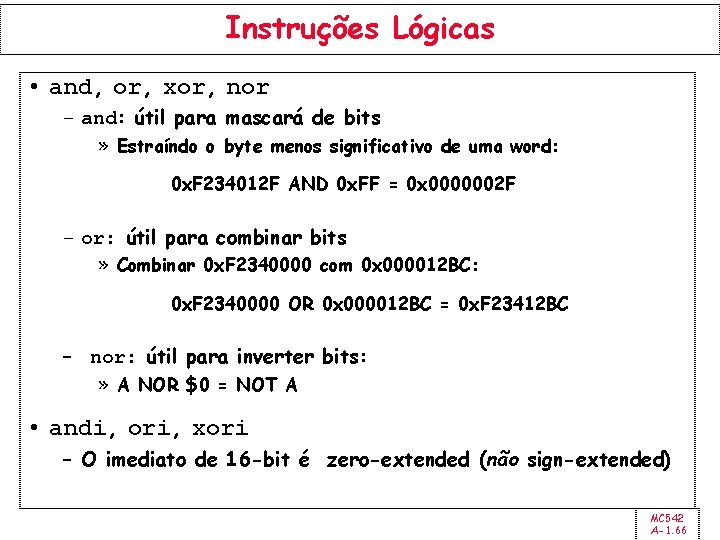

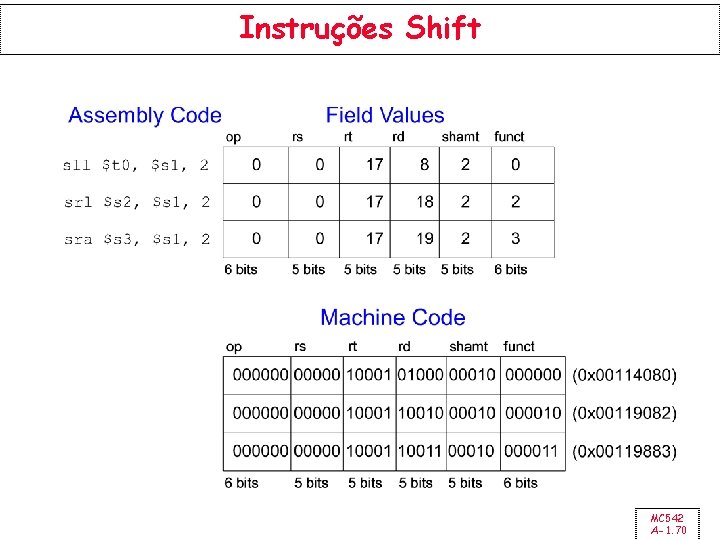

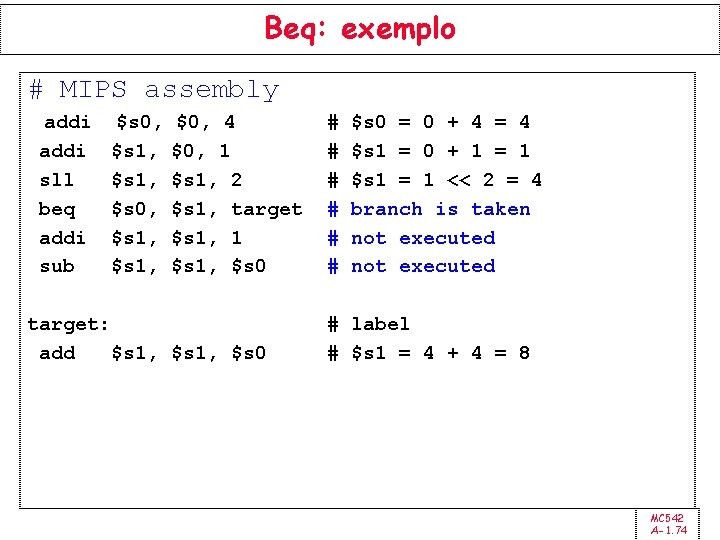

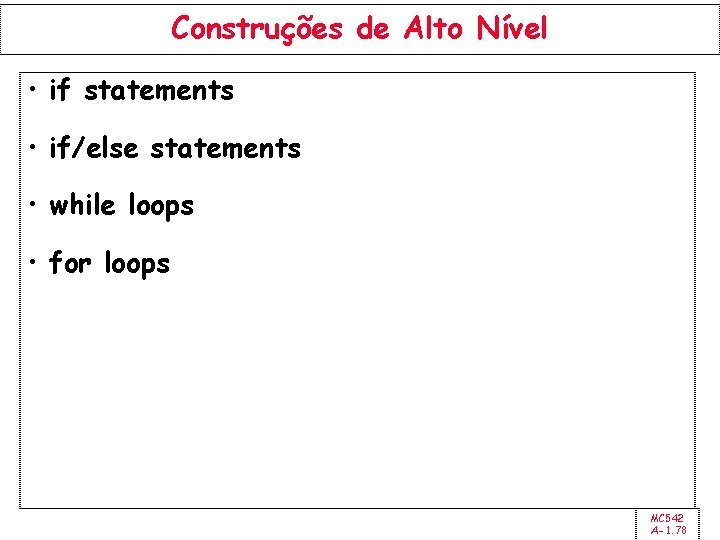

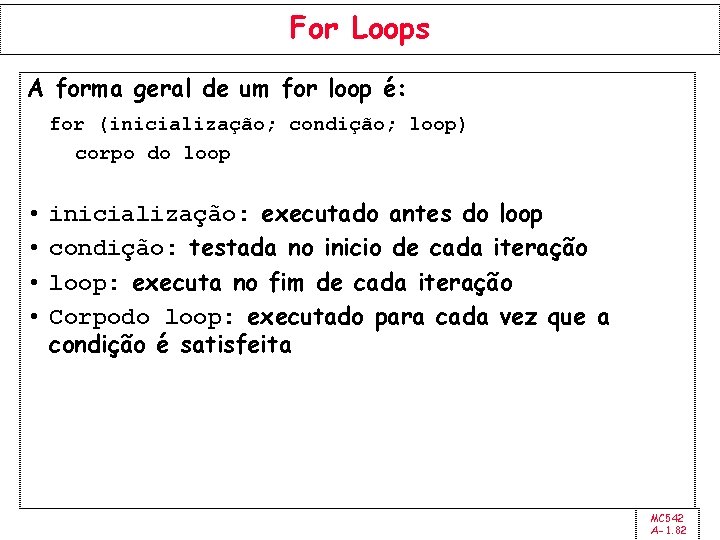

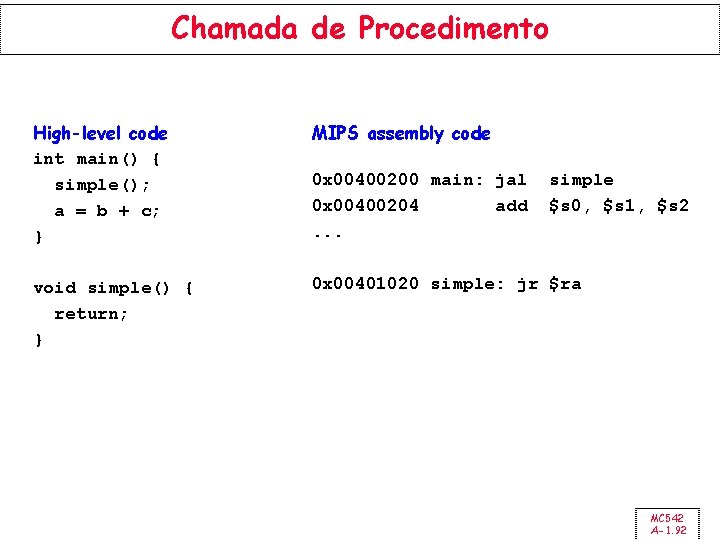

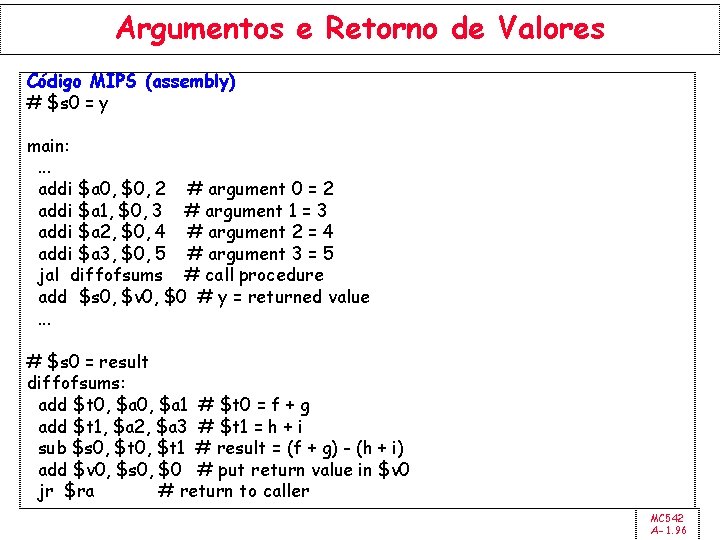

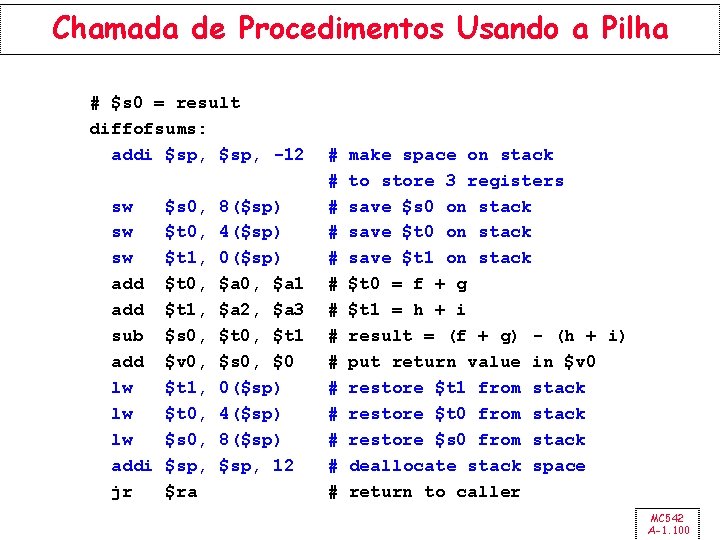

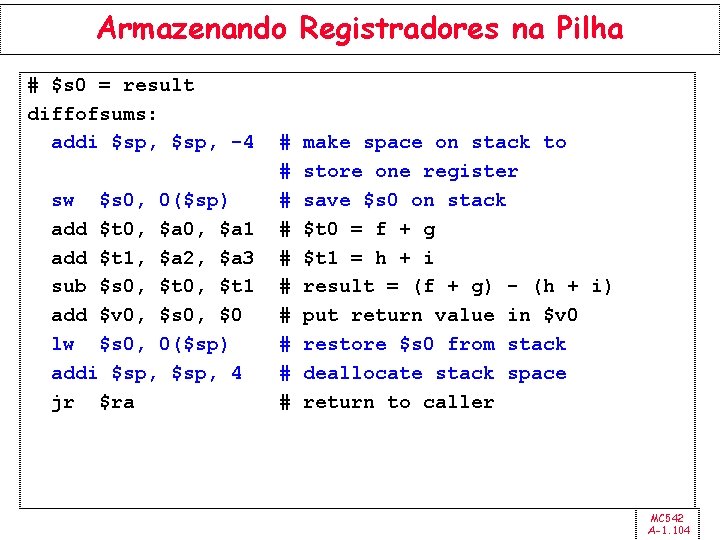

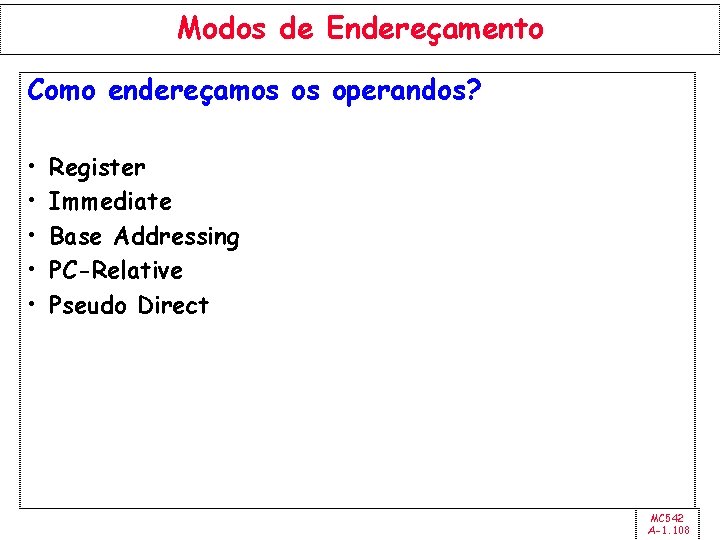

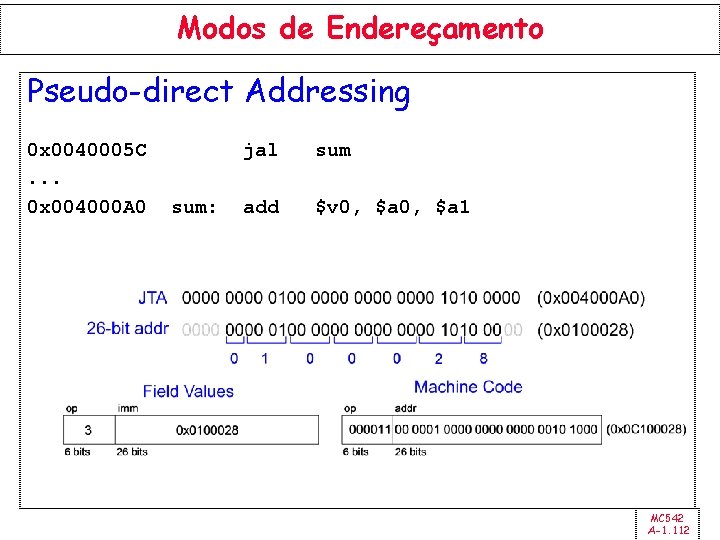

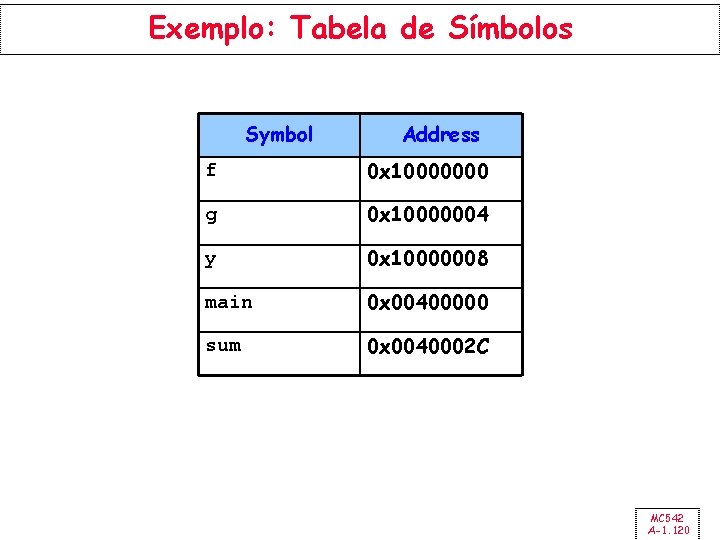

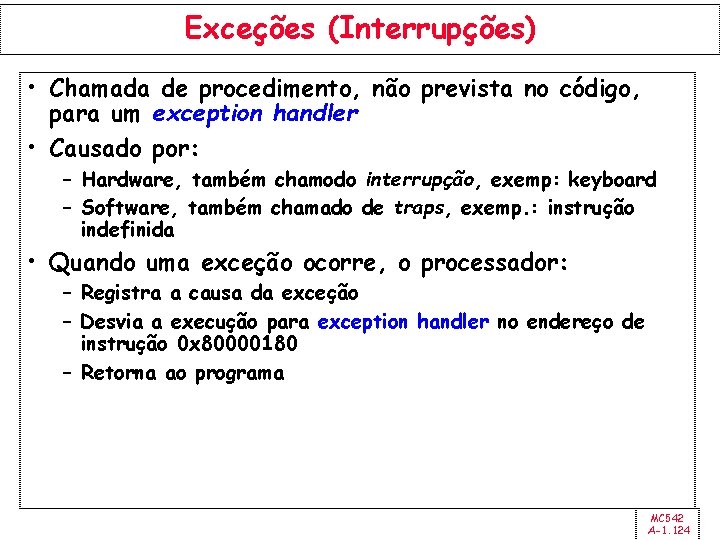

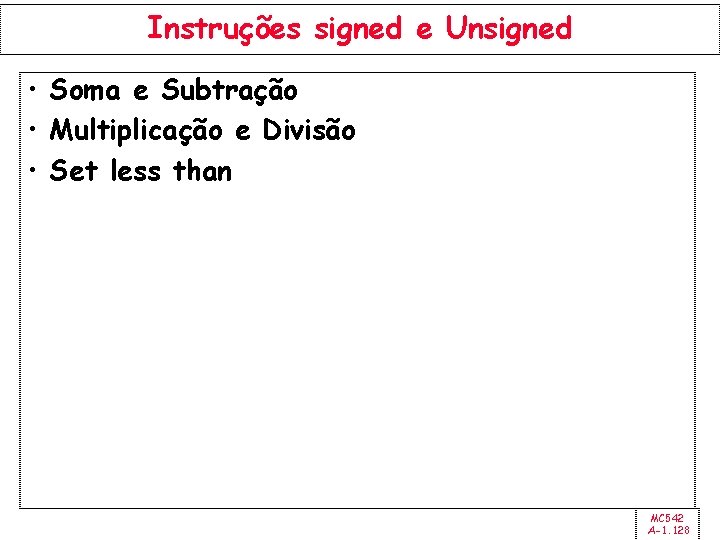

Array // high-level code int array[5]; array[0] = array[0] * 2; array[1] = array[1] * 2; # MIPS assembly code # array base address = $s 0 lui $s 0, 0 x 1234 ori $s 0, 0 x 8000 # put 0 x 1234 in upper half of $S 0 # put 0 x 8000 in lower half of $s 0 lw $t 1, 0($s 0) sll $t 1, 1 sw $t 1, 0($s 0) # $t 1 = array[0] # $t 1 = $t 1 * 2 # array[0] = $t 1 lw $t 1, 4($s 0) sll $t 1, 1 sw $t 1, 4($s 0) # $t 1 = array[1] # $t 1 = $t 1 * 2 # array[1] = $t 1 MC 542 A-1. 87

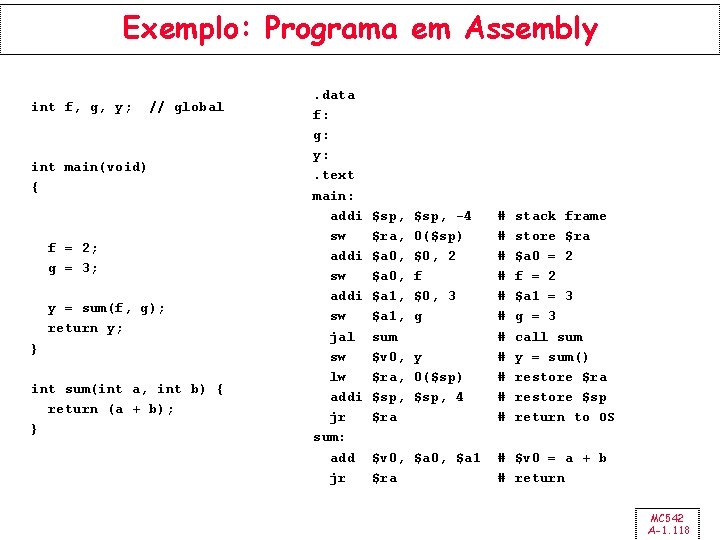

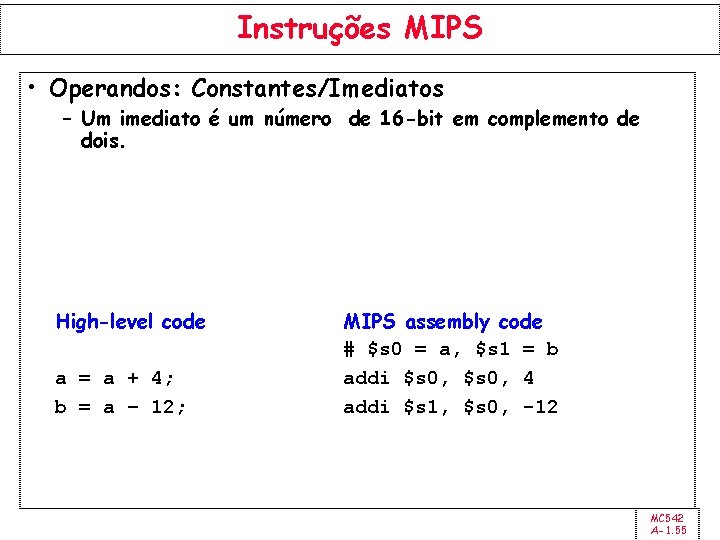

![Array Usando For highlevel code int array1000 int i for i0 i Array Usando For // high-level code int array[1000]; int i; for (i=0; i <](https://slidetodoc.com/presentation_image/22e24f50370a8b86246893907b43285a/image-88.jpg)

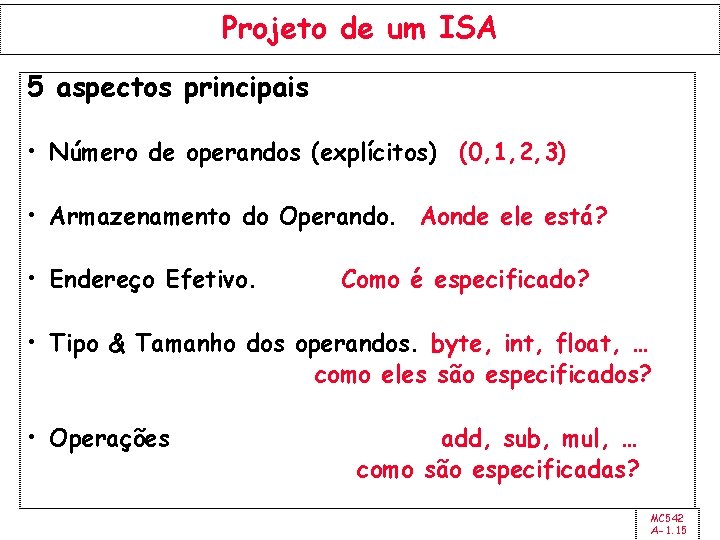

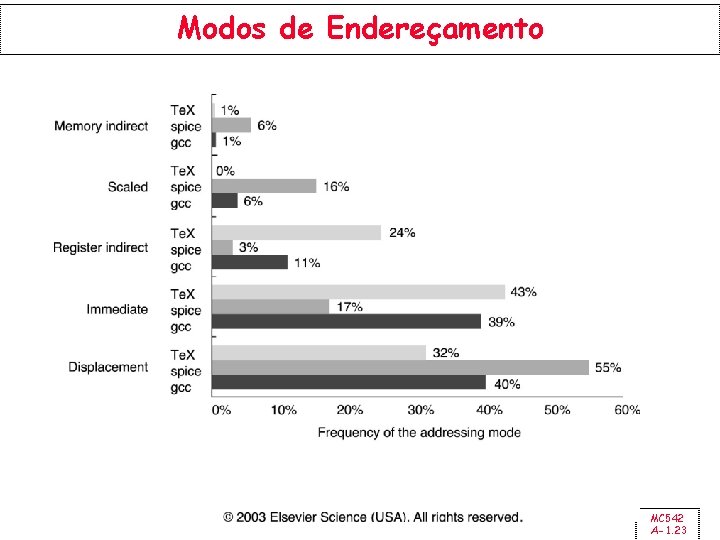

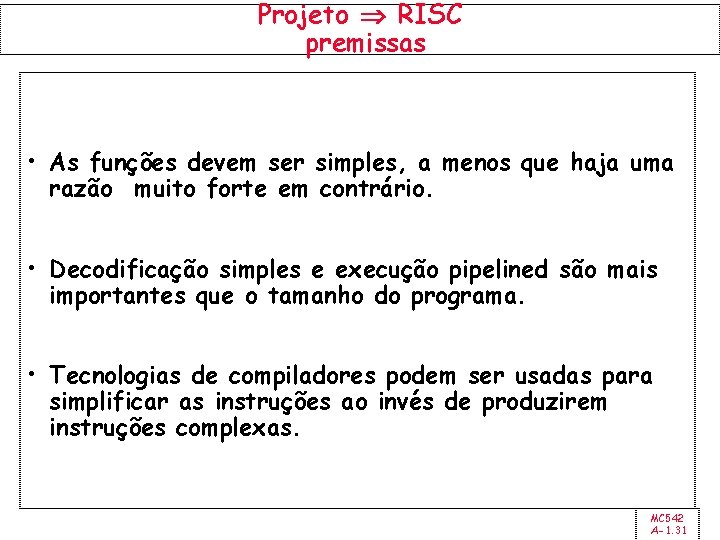

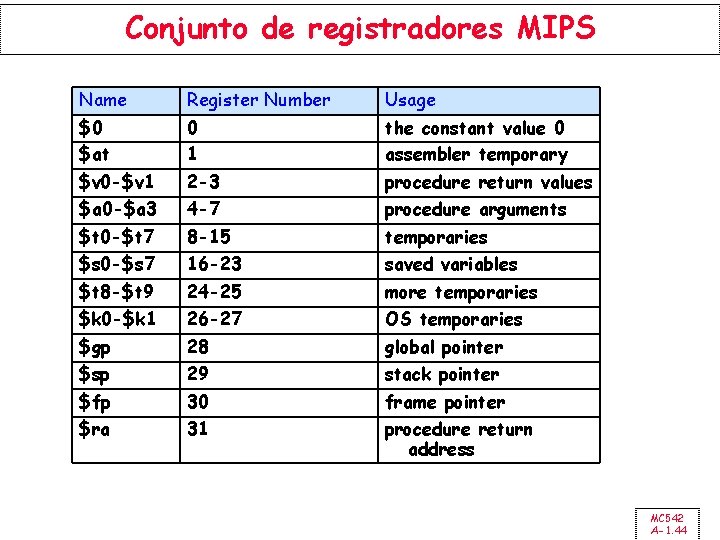

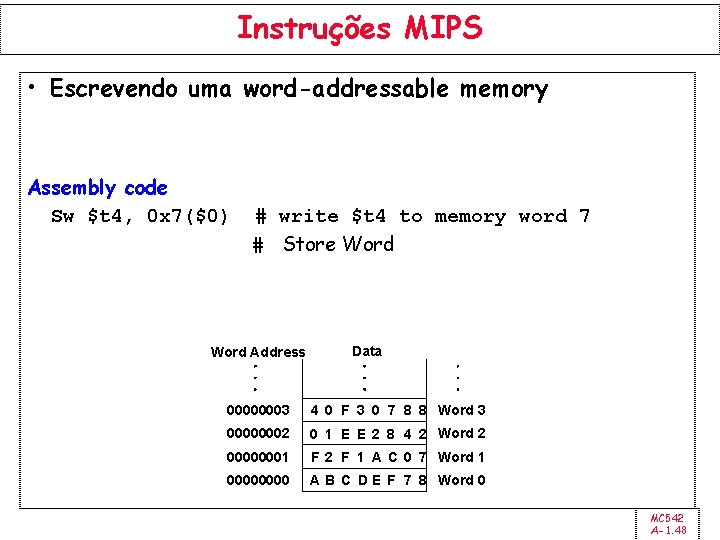

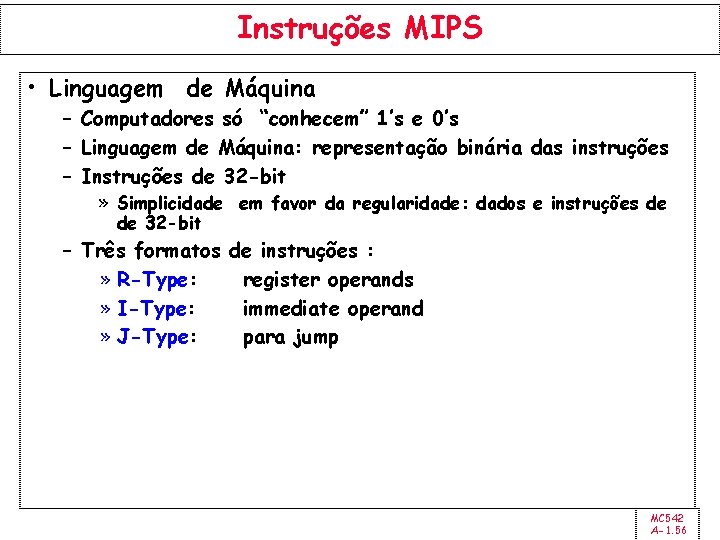

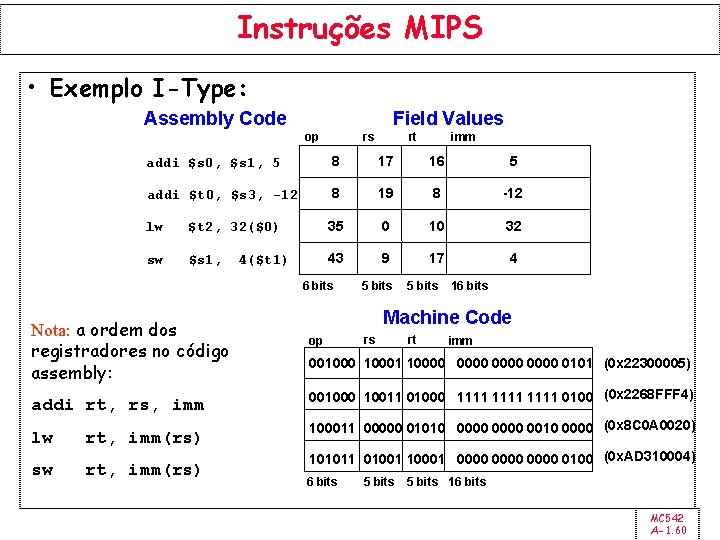

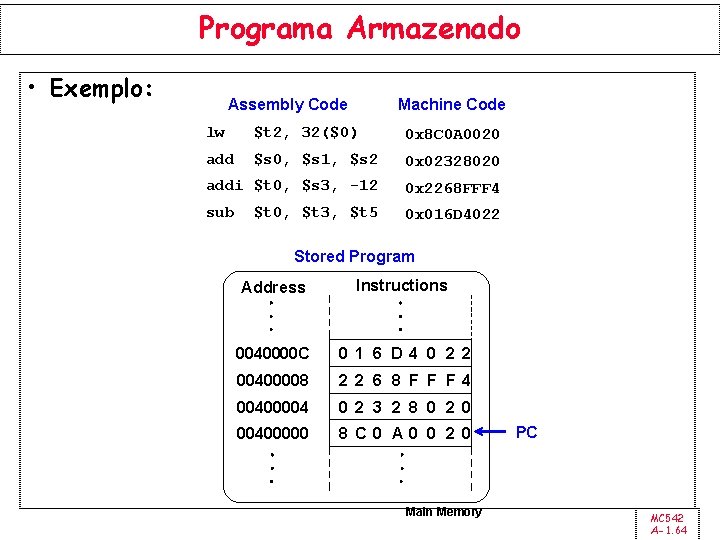

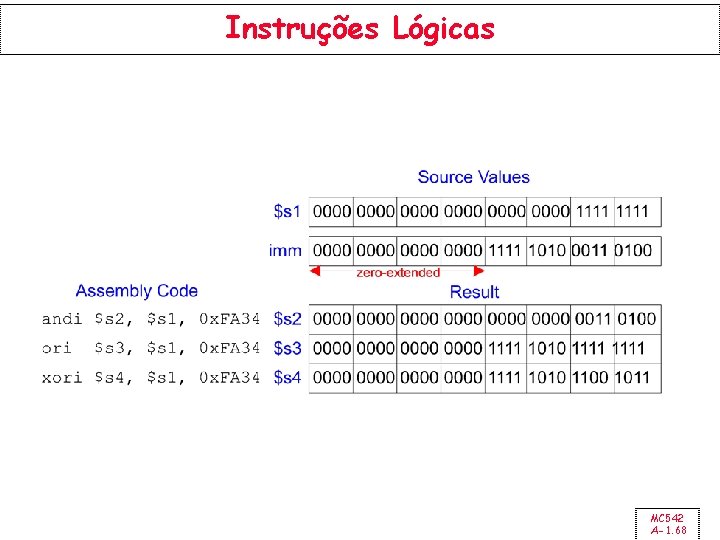

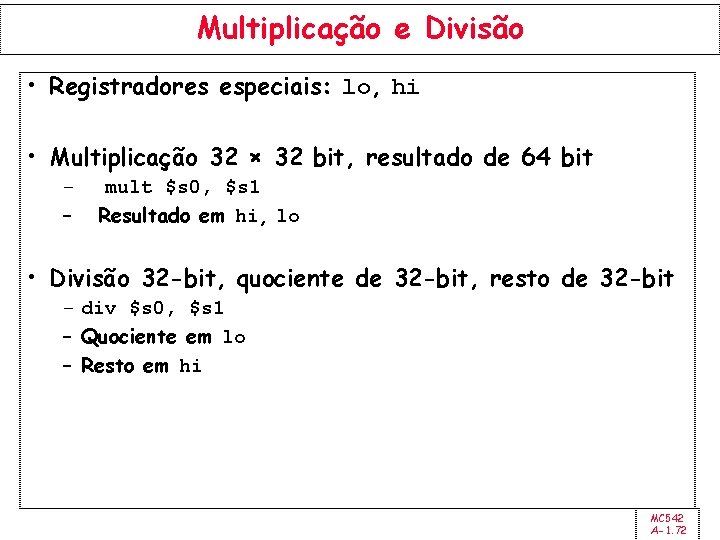

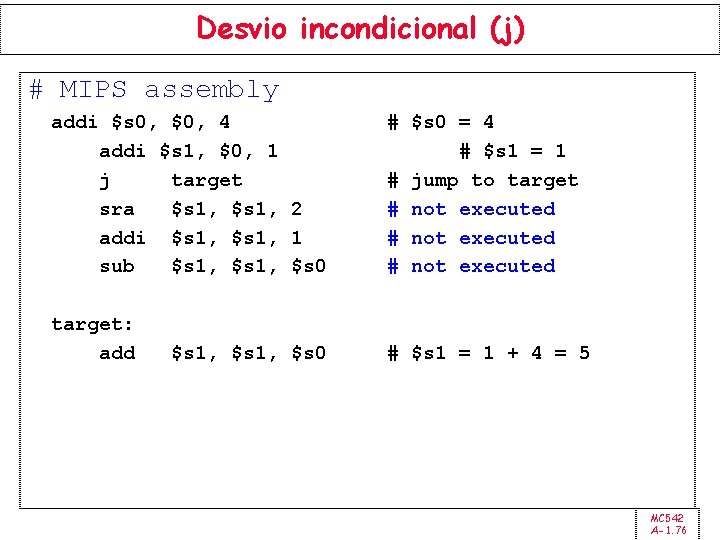

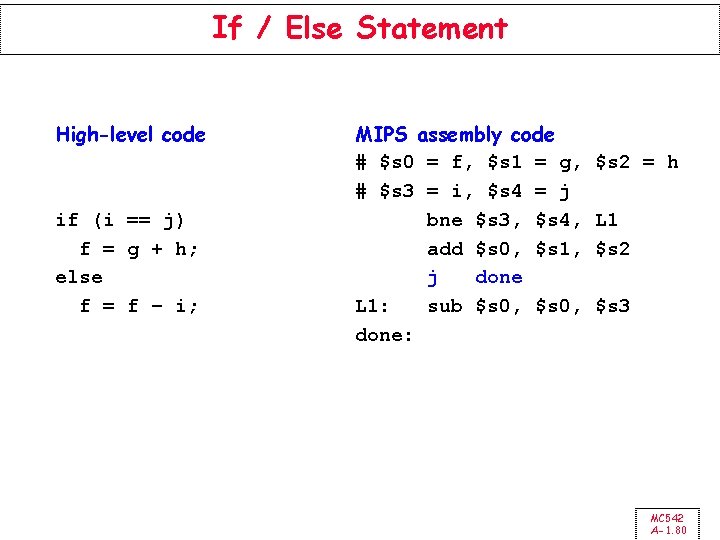

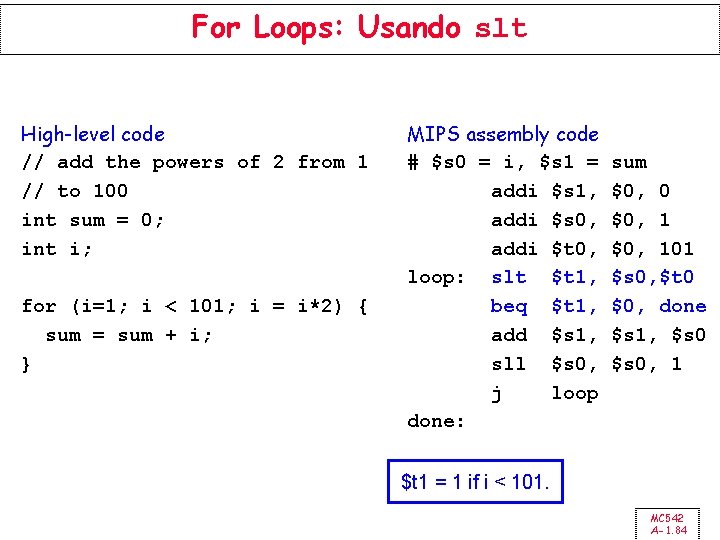

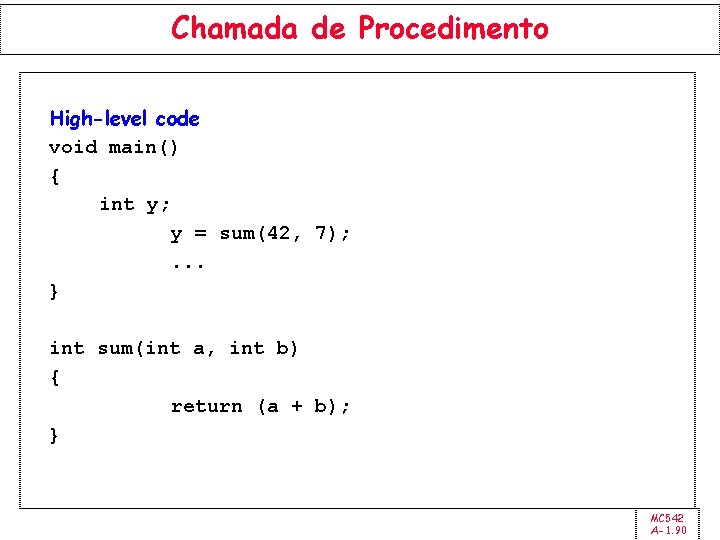

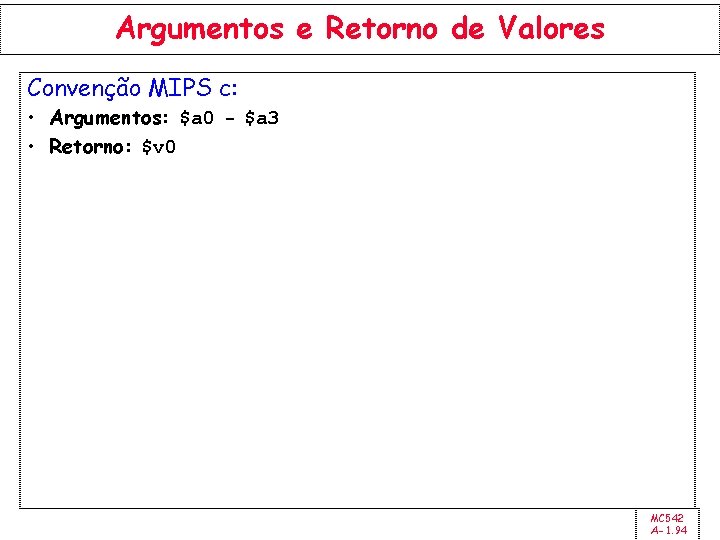

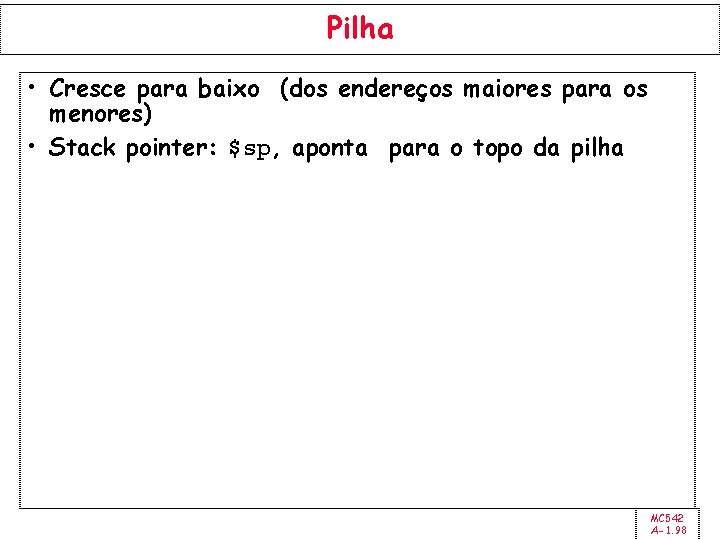

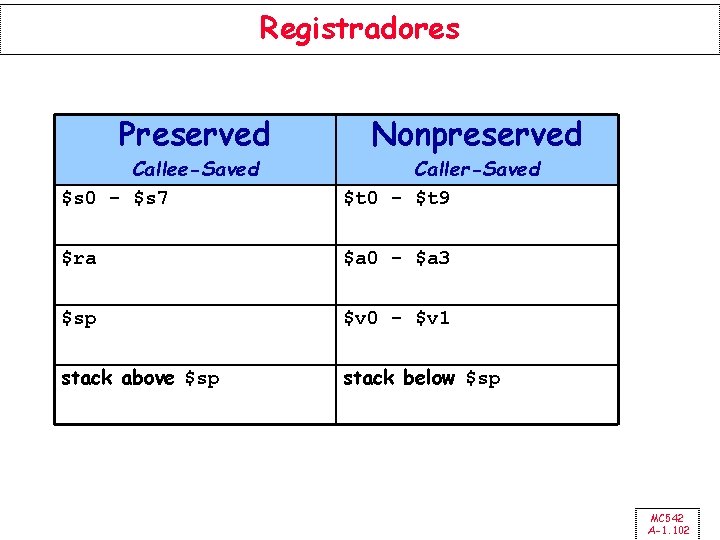

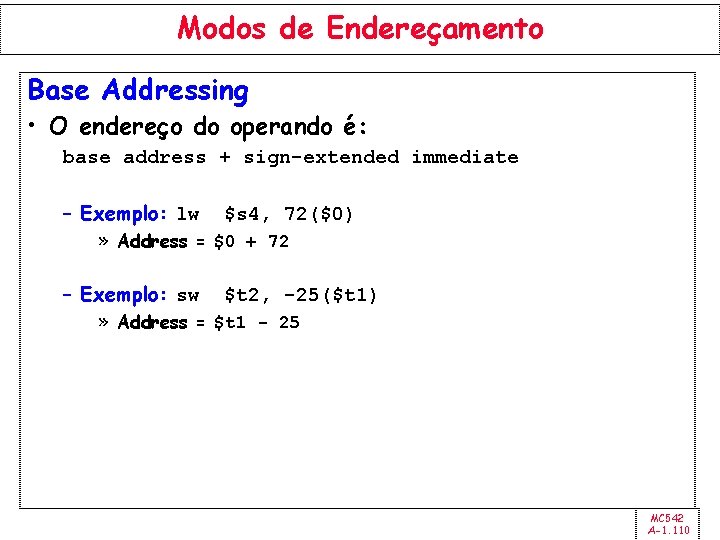

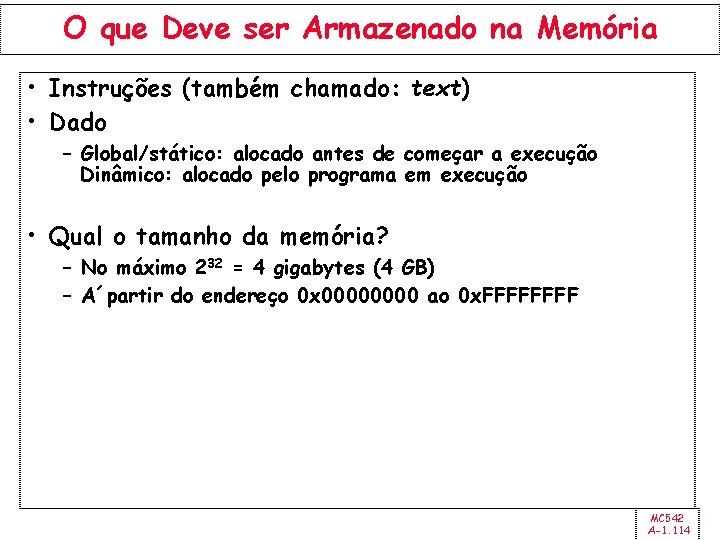

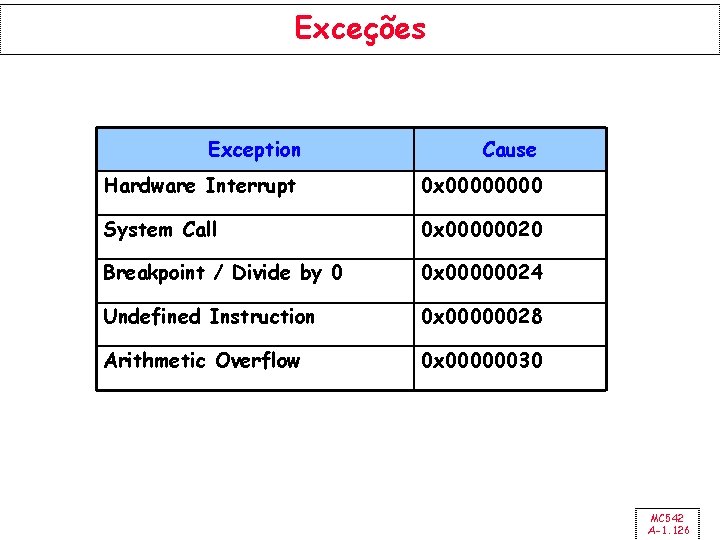

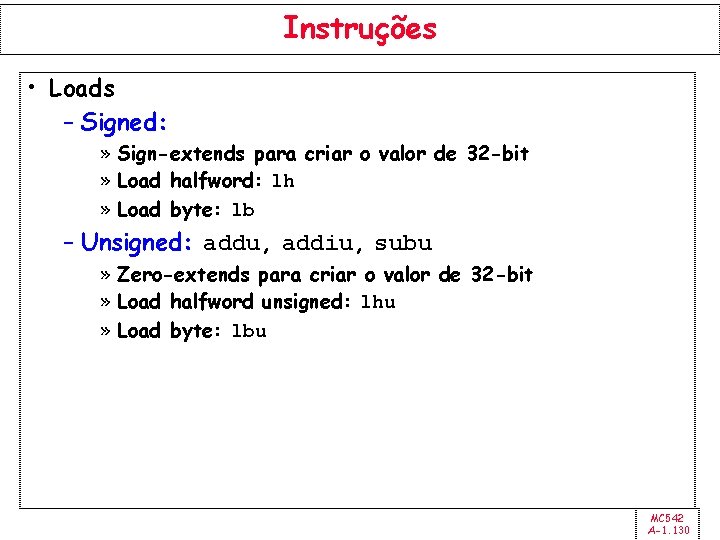

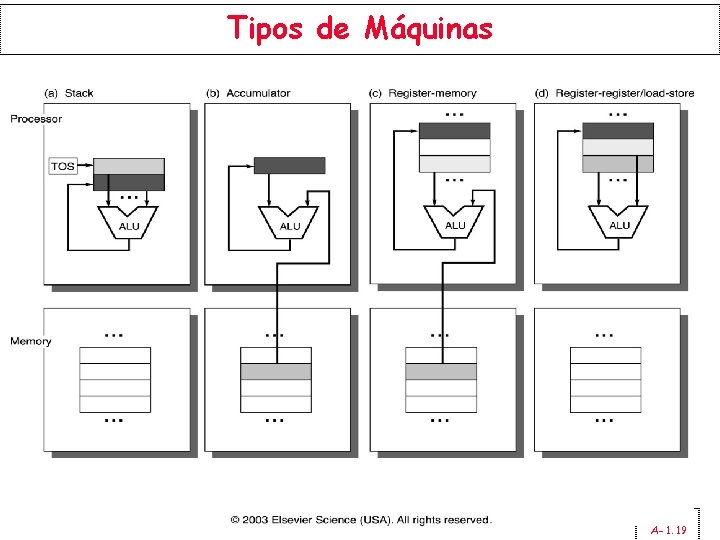

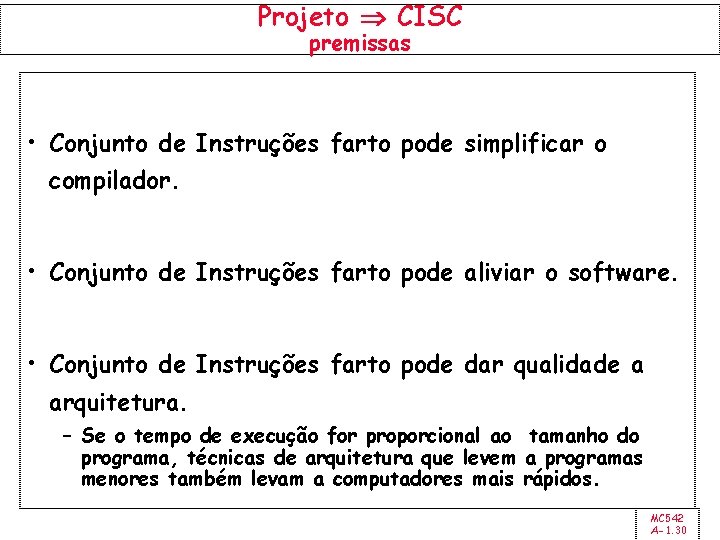

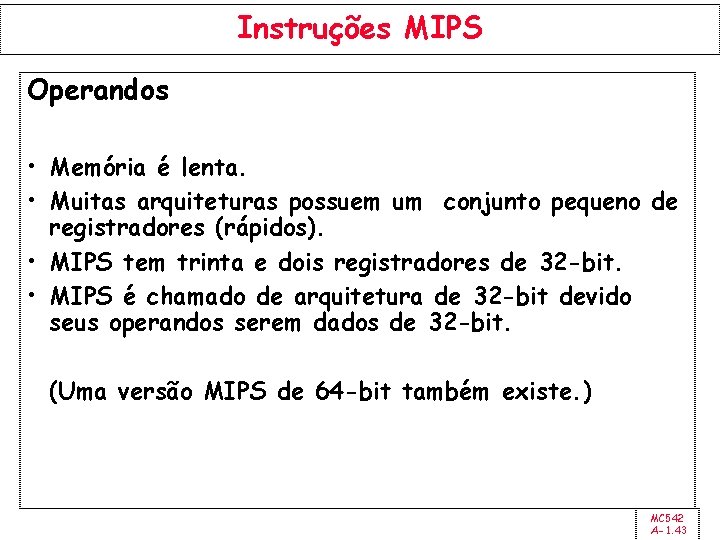

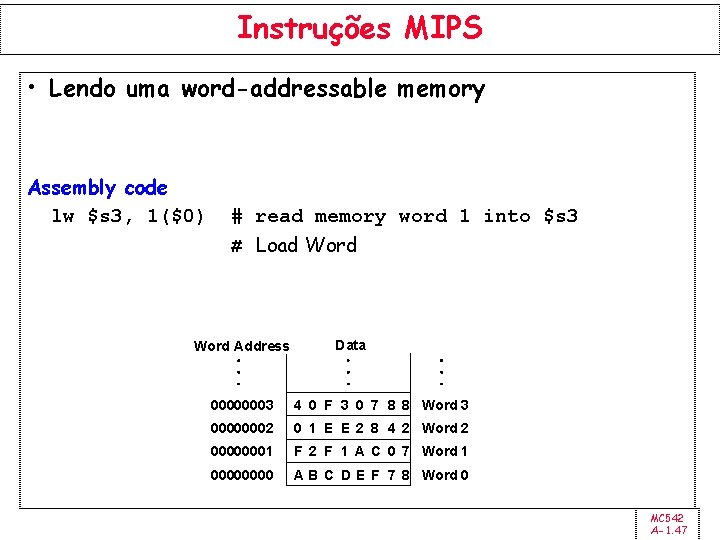

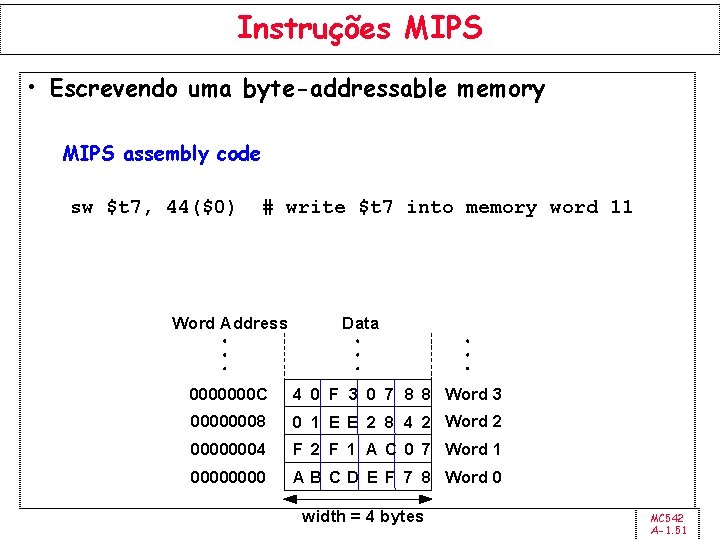

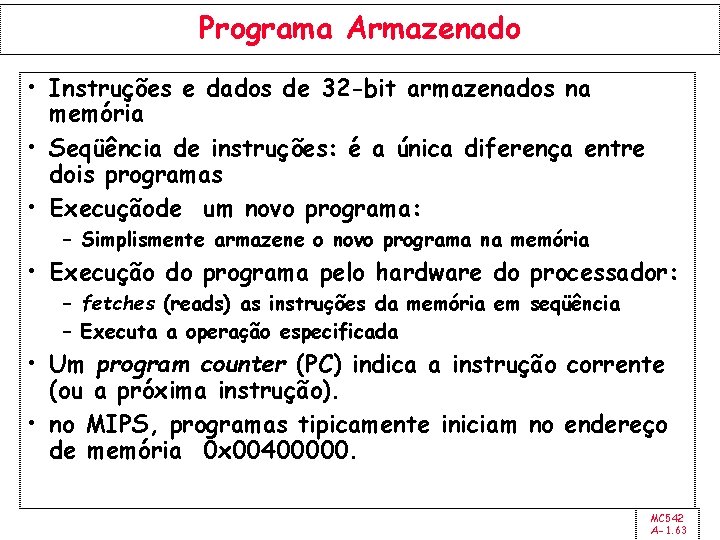

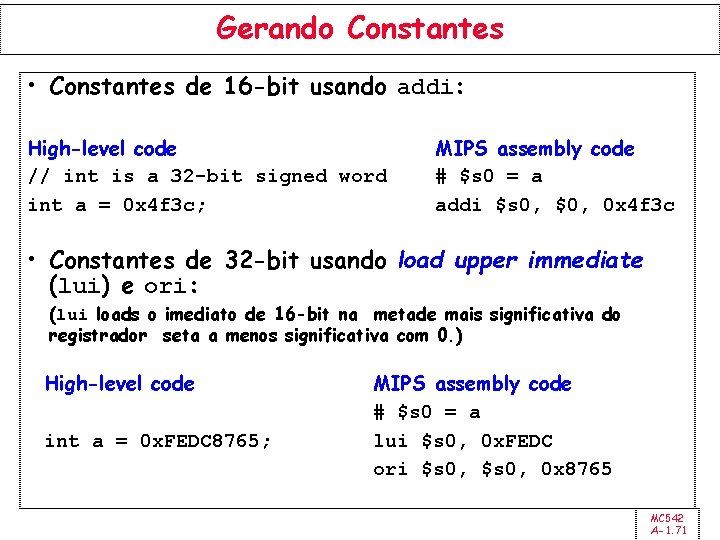

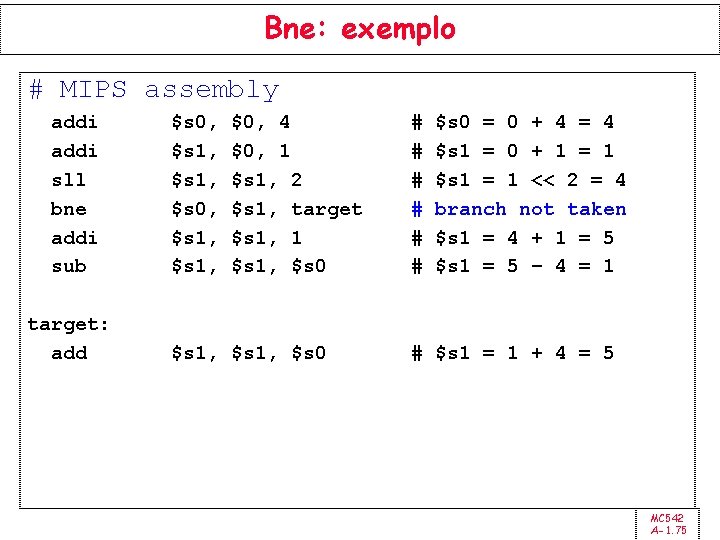

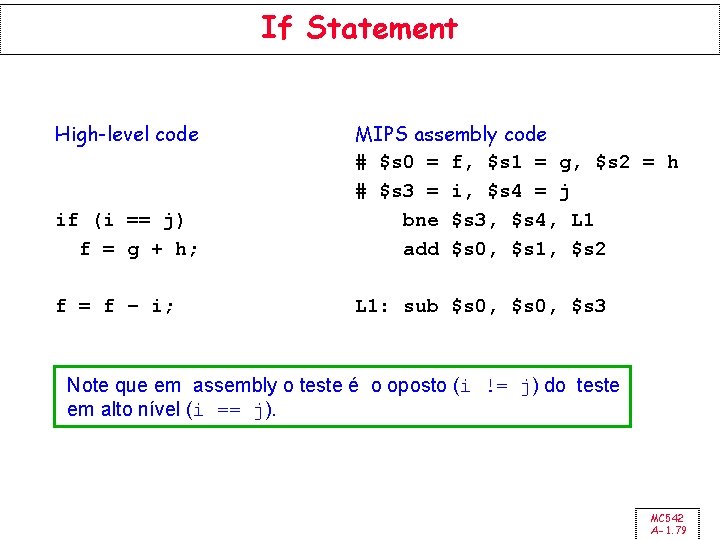

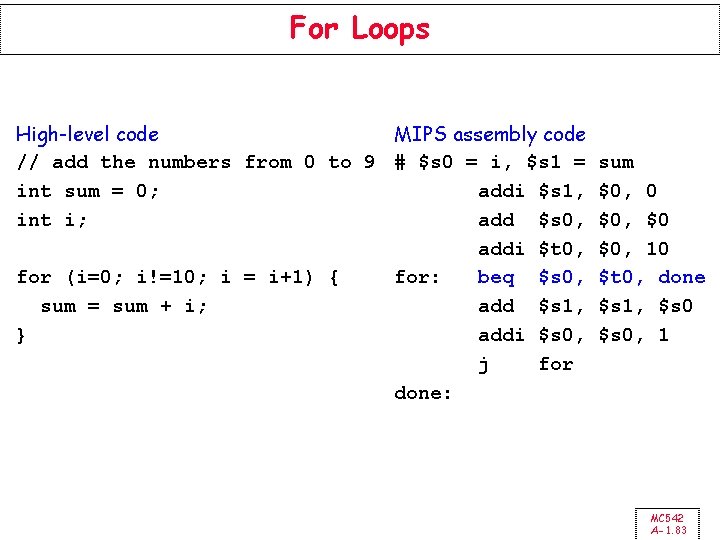

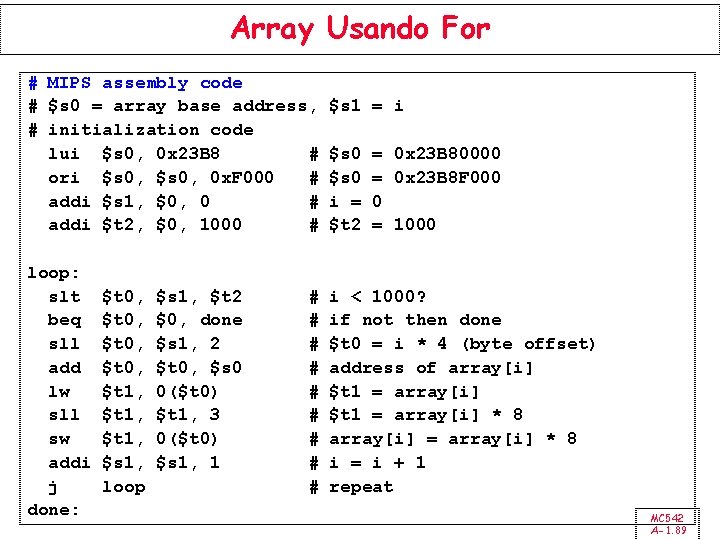

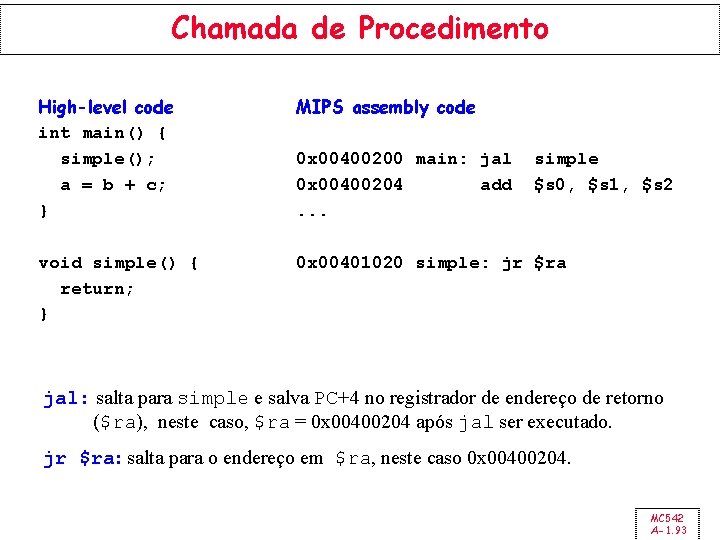

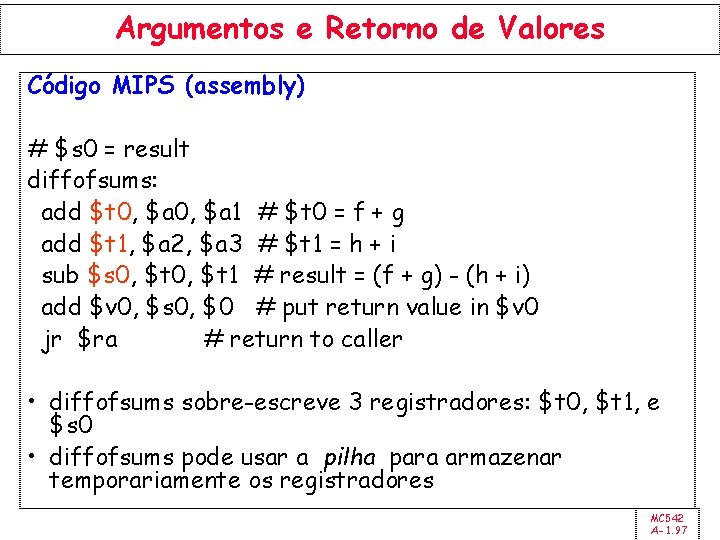

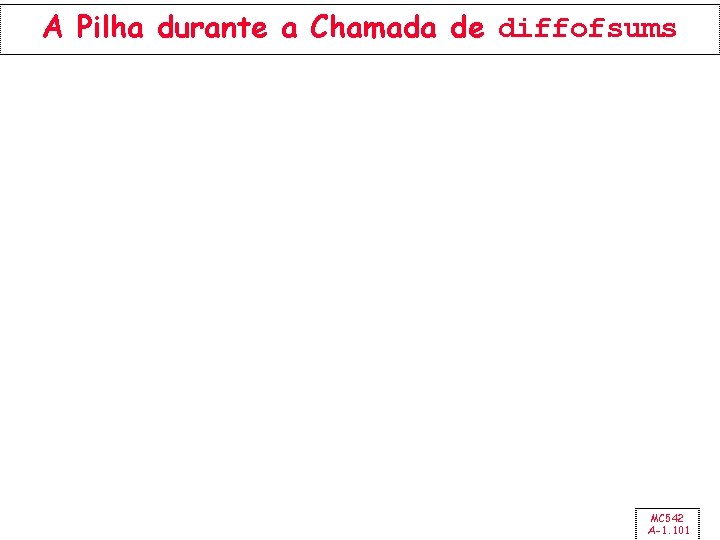

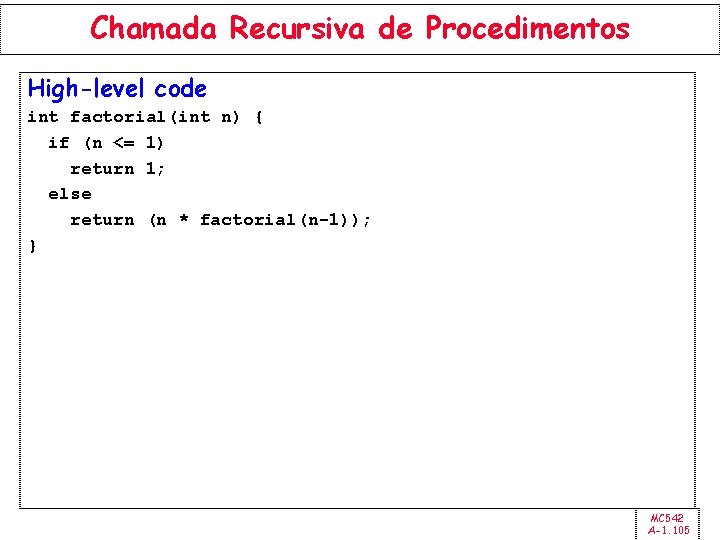

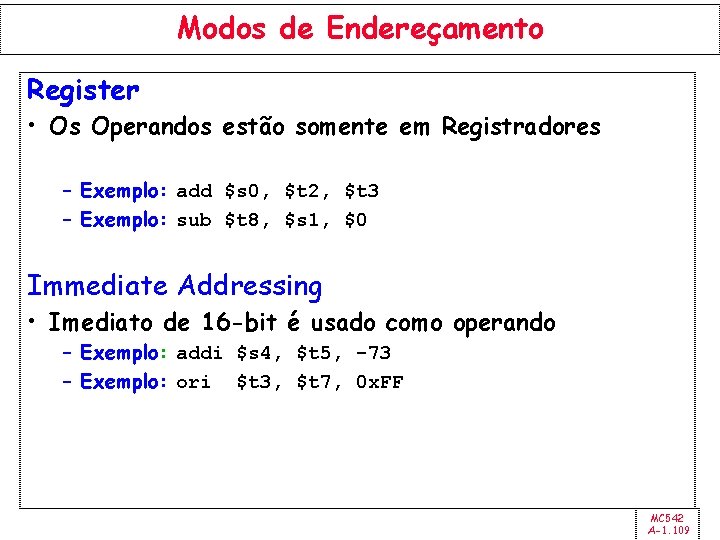

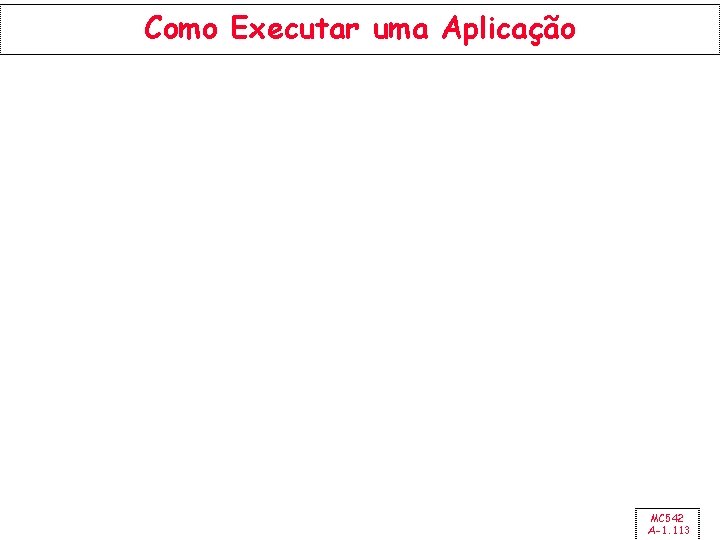

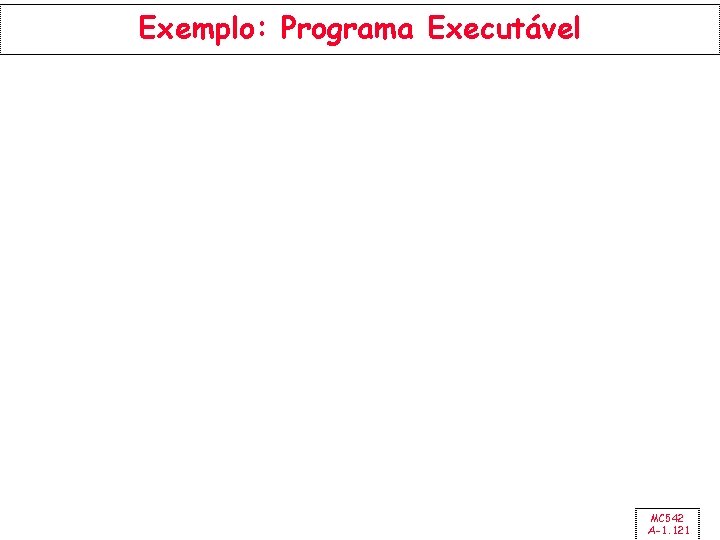

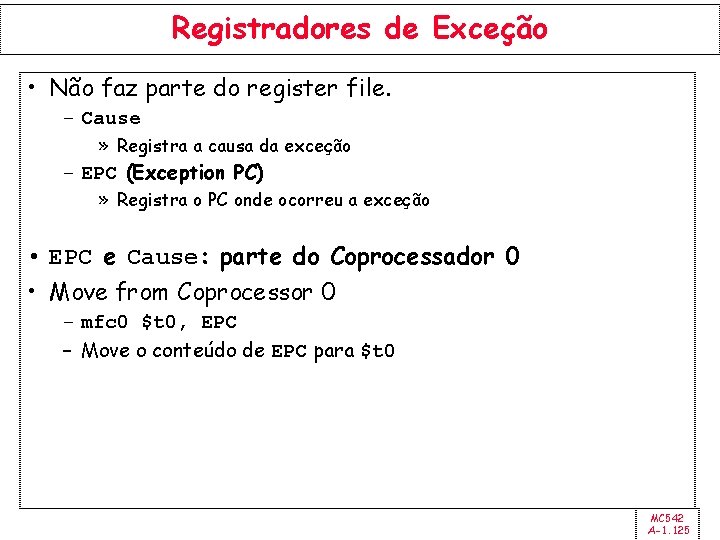

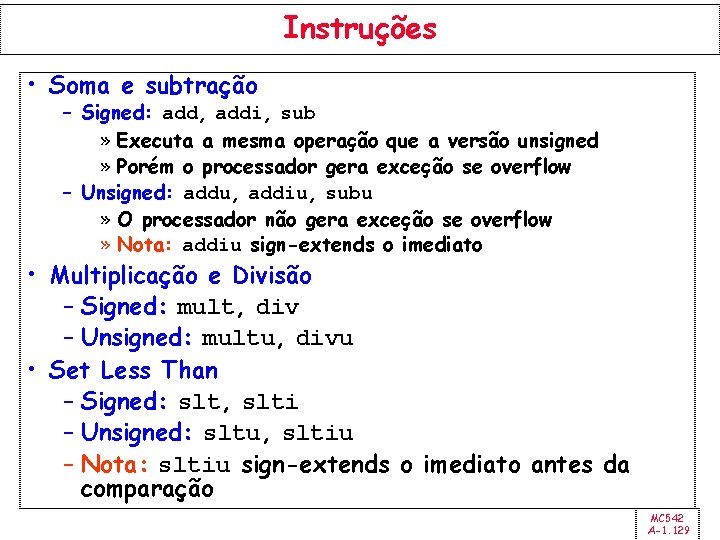

Array Usando For // high-level code int array[1000]; int i; for (i=0; i < 1000; i = i + 1) array[i] = array[i] * 8; MC 542 A-1. 88

Array Usando For # MIPS assembly code # $s 0 = array base address, # initialization code lui $s 0, 0 x 23 B 8 # ori $s 0, 0 x. F 000 # addi $s 1, $0, 0 # addi $t 2, $0, 1000 # loop: slt beq sll add lw sll sw addi j done: $t 0, $t 1, $s 1, loop $s 1, $t 2 $0, done $s 1, 2 $t 0, $s 0 0($t 0) $t 1, 3 0($t 0) $s 1, 1 # # # # # $s 1 = i $s 0 i = $t 2 = 0 x 23 B 80000 = 0 x 23 B 8 F 000 0 = 1000 i < 1000? if not then done $t 0 = i * 4 (byte offset) address of array[i] $t 1 = array[i] * 8 array[i] = array[i] * 8 i = i + 1 repeat MC 542 A-1. 89

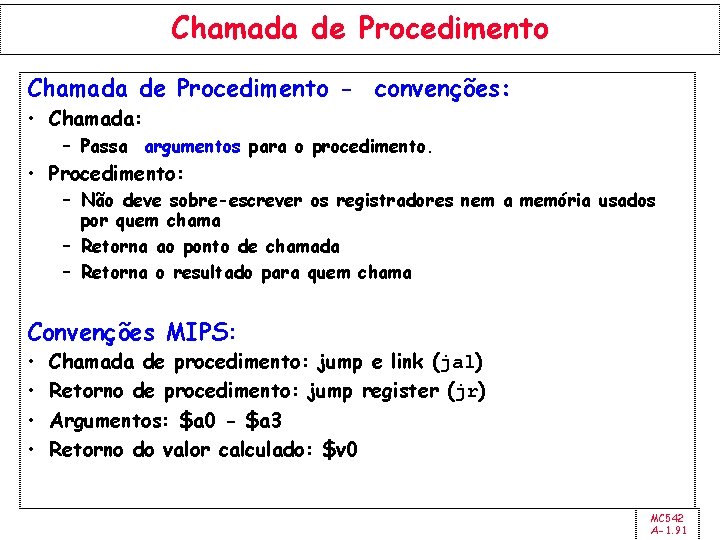

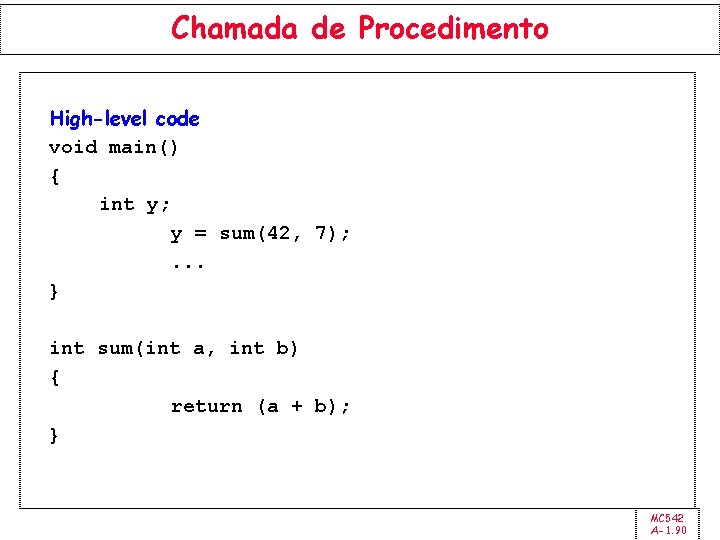

Chamada de Procedimento High-level code void main() { int y; y = sum(42, 7); . . . } int sum(int a, int b) { return (a + b); } MC 542 A-1. 90

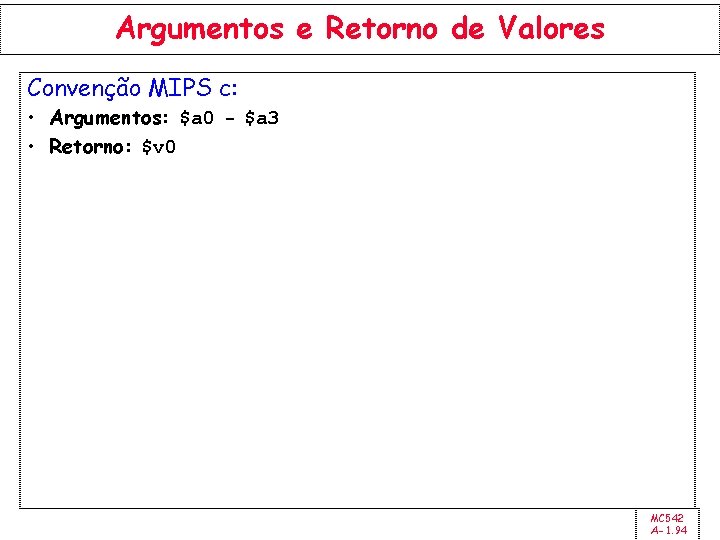

Chamada de Procedimento - convenções: • Chamada: – Passa argumentos para o procedimento. • Procedimento: – Não deve sobre-escrever os registradores nem a memória usados por quem chama – Retorna ao ponto de chamada – Retorna o resultado para quem chama Convenções MIPS: • • Chamada de procedimento: jump e link (jal) Retorno de procedimento: jump register (jr) Argumentos: $a 0 - $a 3 Retorno do valor calculado: $v 0 MC 542 A-1. 91

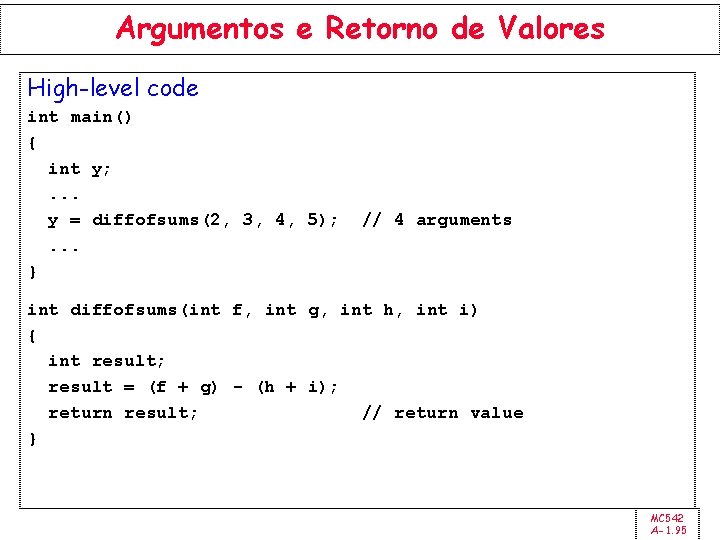

Chamada de Procedimento High-level code int main() { simple(); a = b + c; } MIPS assembly code void simple() { return; } 0 x 00401020 simple: jr $ra 0 x 00400200 main: jal 0 x 00400204 add. . . simple $s 0, $s 1, $s 2 MC 542 A-1. 92

Chamada de Procedimento High-level code int main() { simple(); a = b + c; } MIPS assembly code void simple() { return; } 0 x 00401020 simple: jr $ra 0 x 00400200 main: jal 0 x 00400204 add. . . simple $s 0, $s 1, $s 2 jal: salta para simple e salva PC+4 no registrador de endereço de retorno ($ra), neste caso, $ra = 0 x 00400204 após jal ser executado. jr $ra: salta para o endereço em $ra, neste caso 0 x 00400204. MC 542 A-1. 93

Argumentos e Retorno de Valores Convenção MIPS c: • Argumentos: $a 0 - $a 3 • Retorno: $v 0 MC 542 A-1. 94

Argumentos e Retorno de Valores High-level code int main() { int y; . . . y = diffofsums(2, 3, 4, 5); . . . } // 4 arguments int diffofsums(int f, int g, int h, int i) { int result; result = (f + g) - (h + i); return result; // return value } MC 542 A-1. 95

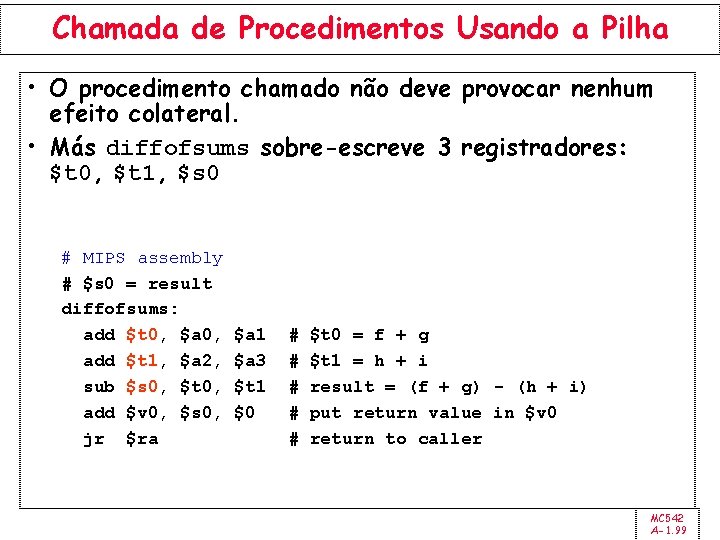

Argumentos e Retorno de Valores Código MIPS (assembly) # $s 0 = y main: . . . addi $a 0, $0, 2 # argument 0 = 2 addi $a 1, $0, 3 # argument 1 = 3 addi $a 2, $0, 4 # argument 2 = 4 addi $a 3, $0, 5 # argument 3 = 5 jal diffofsums # call procedure add $s 0, $v 0, $0 # y = returned value. . . # $s 0 = result diffofsums: add $t 0, $a 1 # $t 0 = f + g add $t 1, $a 2, $a 3 # $t 1 = h + i sub $s 0, $t 1 # result = (f + g) - (h + i) add $v 0, $s 0, $0 # put return value in $v 0 jr $ra # return to caller MC 542 A-1. 96

Argumentos e Retorno de Valores Código MIPS (assembly) # $s 0 = result diffofsums: add $t 0, $a 1 # $t 0 = f + g add $t 1, $a 2, $a 3 # $t 1 = h + i sub $s 0, $t 1 # result = (f + g) - (h + i) add $v 0, $s 0, $0 # put return value in $v 0 jr $ra # return to caller • diffofsums sobre-escreve 3 registradores: $t 0, $t 1, e $s 0 • diffofsums pode usar a pilha para armazenar temporariamente os registradores MC 542 A-1. 97

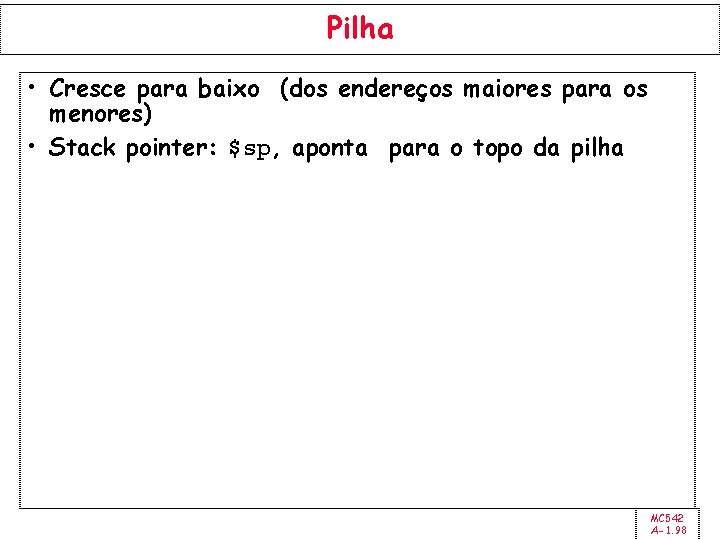

Pilha • Cresce para baixo (dos endereços maiores para os menores) • Stack pointer: $sp, aponta para o topo da pilha MC 542 A-1. 98

Chamada de Procedimentos Usando a Pilha • O procedimento chamado não deve provocar nenhum efeito colateral. • Más diffofsums sobre-escreve 3 registradores: $t 0, $t 1, $s 0 # MIPS assembly # $s 0 = result diffofsums: add $t 0, $a 0, add $t 1, $a 2, sub $s 0, $t 0, add $v 0, $s 0, jr $ra $a 1 $a 3 $t 1 $0 # # # $t 0 = f + g $t 1 = h + i result = (f + g) - (h + i) put return value in $v 0 return to caller MC 542 A-1. 99

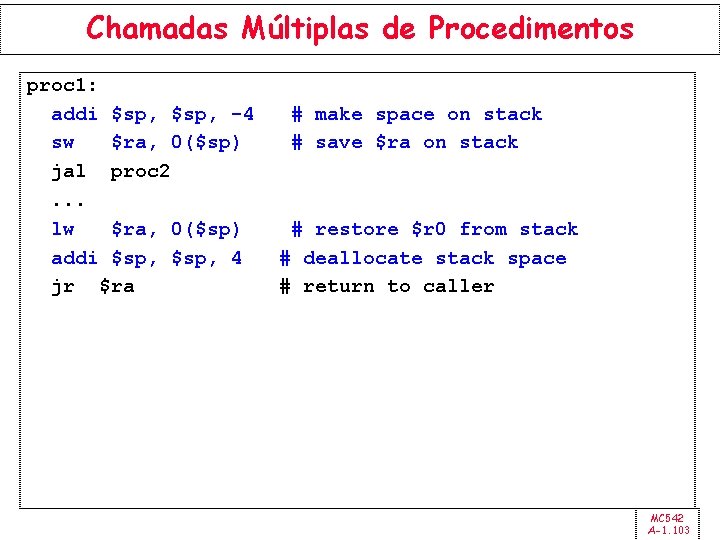

Chamada de Procedimentos Usando a Pilha # $s 0 = result diffofsums: addi $sp, -12 sw sw sw add sub add lw lw lw addi jr $s 0, $t 1, $t 0, $t 1, $s 0, $v 0, $t 1, $t 0, $sp, $ra 8($sp) 4($sp) 0($sp) $a 0, $a 1 $a 2, $a 3 $t 0, $t 1 $s 0, $0 0($sp) 4($sp) 8($sp) $sp, 12 # # # # make space on stack to store 3 registers save $s 0 on stack save $t 1 on stack $t 0 = f + g $t 1 = h + i result = (f + g) - (h + i) put return value in $v 0 restore $t 1 from stack restore $t 0 from stack restore $s 0 from stack deallocate stack space return to caller MC 542 A-1. 100

A Pilha durante a Chamada de diffofsums MC 542 A-1. 101

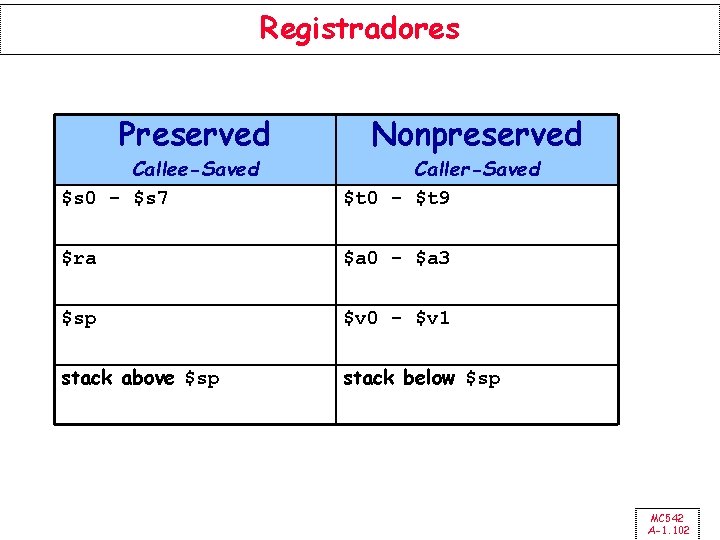

Registradores Preserved Nonpreserved Callee-Saved $s 0 - $s 7 Caller-Saved $t 0 - $t 9 $ra $a 0 - $a 3 $sp $v 0 - $v 1 stack above $sp stack below $sp MC 542 A-1. 102

Chamadas Múltiplas de Procedimentos proc 1: addi $sp, -4 sw $ra, 0($sp) jal proc 2. . . lw $ra, 0($sp) addi $sp, 4 jr $ra # make space on stack # save $ra on stack # restore $r 0 from stack # deallocate stack space # return to caller MC 542 A-1. 103

Armazenando Registradores na Pilha # $s 0 = result diffofsums: addi $sp, -4 sw $s 0, 0($sp) add $t 0, $a 1 add $t 1, $a 2, $a 3 sub $s 0, $t 1 add $v 0, $s 0, $0 lw $s 0, 0($sp) addi $sp, 4 jr $ra # # # # # make space on stack to store one register save $s 0 on stack $t 0 = f + g $t 1 = h + i result = (f + g) - (h + i) put return value in $v 0 restore $s 0 from stack deallocate stack space return to caller MC 542 A-1. 104

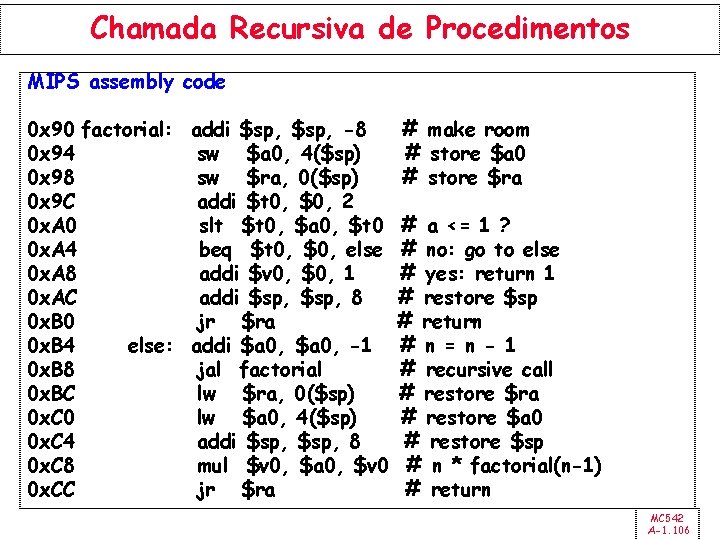

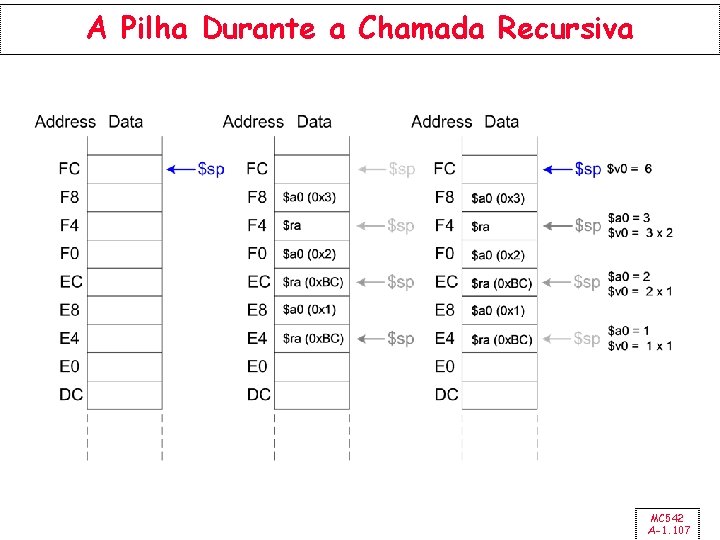

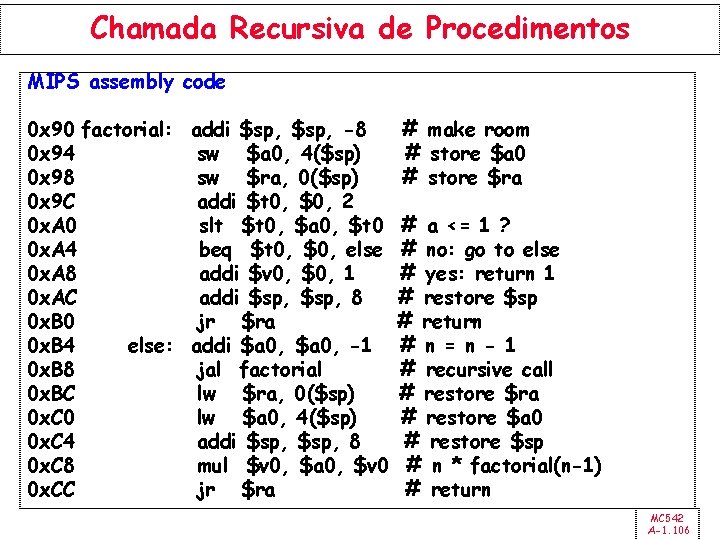

Chamada Recursiva de Procedimentos High-level code int factorial(int n) { if (n <= 1) return 1; else return (n * factorial(n-1)); } MC 542 A-1. 105

Chamada Recursiva de Procedimentos MIPS assembly code 0 x 90 factorial: addi $sp, -8 0 x 94 sw $a 0, 4($sp) 0 x 98 sw $ra, 0($sp) 0 x 9 C addi $t 0, $0, 2 0 x. A 0 slt $t 0, $a 0, $t 0 0 x. A 4 beq $t 0, $0, else 0 x. A 8 addi $v 0, $0, 1 0 x. AC addi $sp, 8 0 x. B 0 jr $ra 0 x. B 4 else: addi $a 0, -1 0 x. B 8 jal factorial 0 x. BC lw $ra, 0($sp) 0 x. C 0 lw $a 0, 4($sp) 0 x. C 4 addi $sp, 8 0 x. C 8 mul $v 0, $a 0, $v 0 0 x. CC jr $ra # make room # store $a 0 # store $ra # a <= 1 ? # no: go to else # yes: return 1 # restore $sp # return # n = n - 1 # recursive call # restore $ra # restore $a 0 # restore $sp # n * factorial(n-1) # return MC 542 A-1. 106

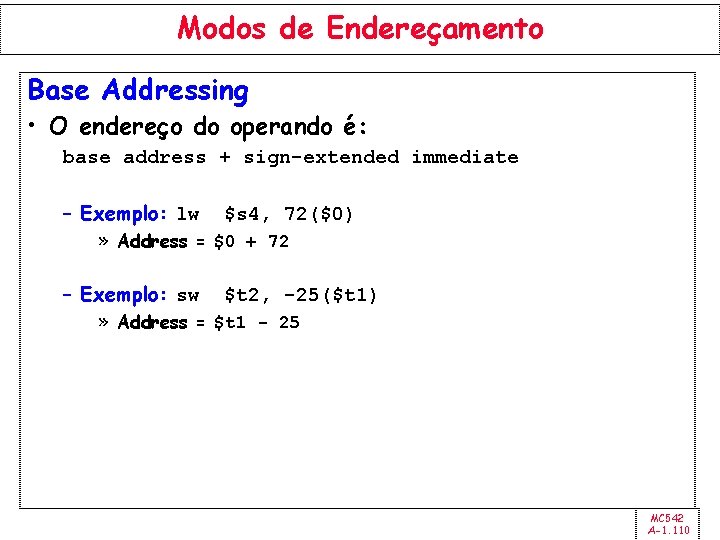

A Pilha Durante a Chamada Recursiva MC 542 A-1. 107

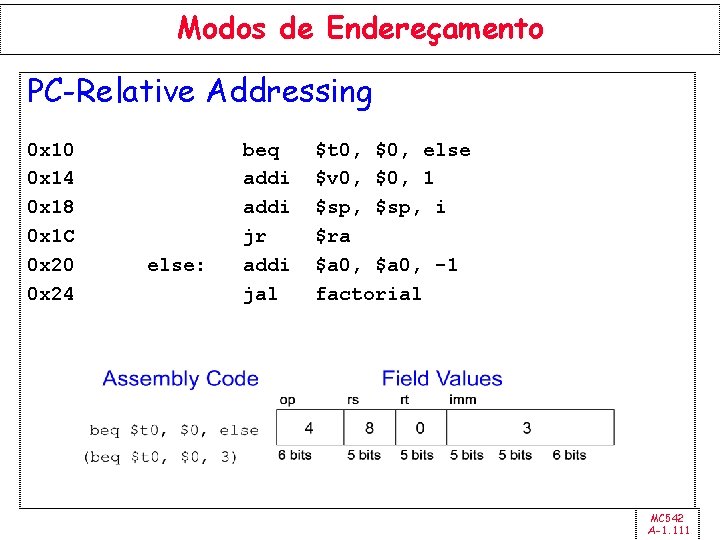

Modos de Endereçamento Como endereçamos os operandos? • • • Register Immediate Base Addressing PC-Relative Pseudo Direct MC 542 A-1. 108

Modos de Endereçamento Register • Os Operandos estão somente em Registradores – Exemplo: add $s 0, $t 2, $t 3 – Exemplo: sub $t 8, $s 1, $0 Immediate Addressing • Imediato de 16 -bit é usado como operando – Exemplo: addi $s 4, $t 5, -73 – Exemplo: ori $t 3, $t 7, 0 x. FF MC 542 A-1. 109

Modos de Endereçamento Base Addressing • O endereço do operando é: base address + sign-extended immediate – Exemplo: lw $s 4, 72($0) » Address = $0 + 72 – Exemplo: sw $t 2, -25($t 1) » Address = $t 1 - 25 MC 542 A-1. 110

Modos de Endereçamento PC-Relative Addressing 0 x 10 0 x 14 0 x 18 0 x 1 C 0 x 20 0 x 24 else: beq addi jr addi jal $t 0, $0, else $v 0, $0, 1 $sp, i $ra $a 0, -1 factorial MC 542 A-1. 111

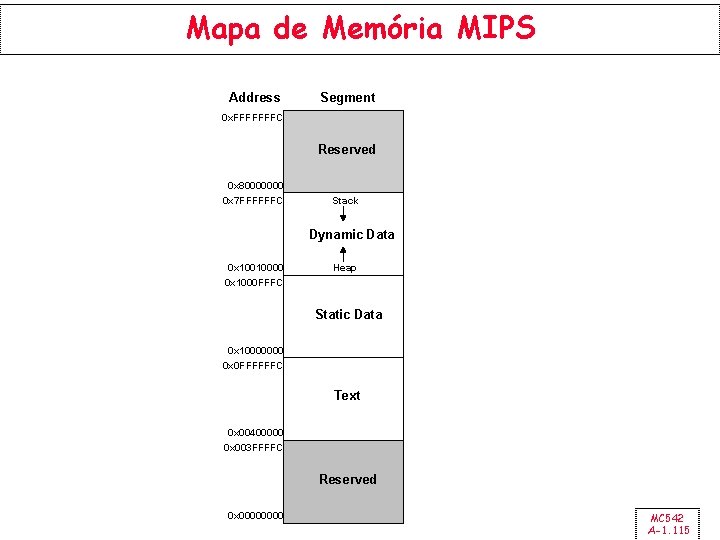

Modos de Endereçamento Pseudo-direct Addressing 0 x 0040005 C. . . 0 x 004000 A 0 sum: jal sum add $v 0, $a 1 MC 542 A-1. 112

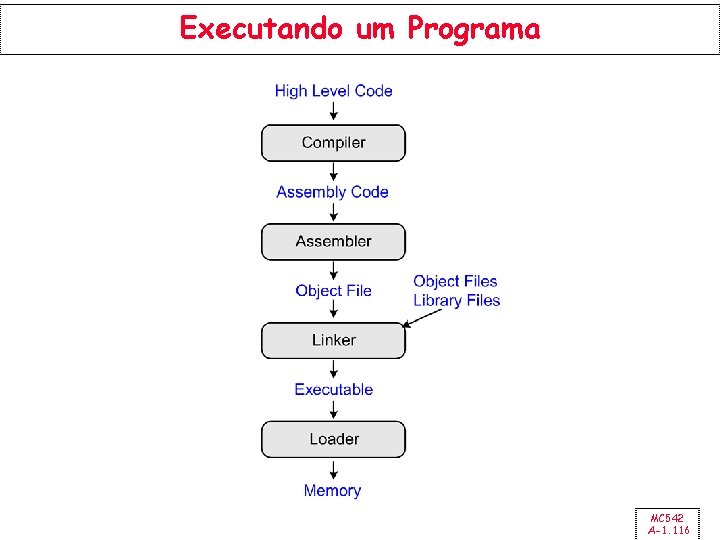

Como Executar uma Aplicação MC 542 A-1. 113

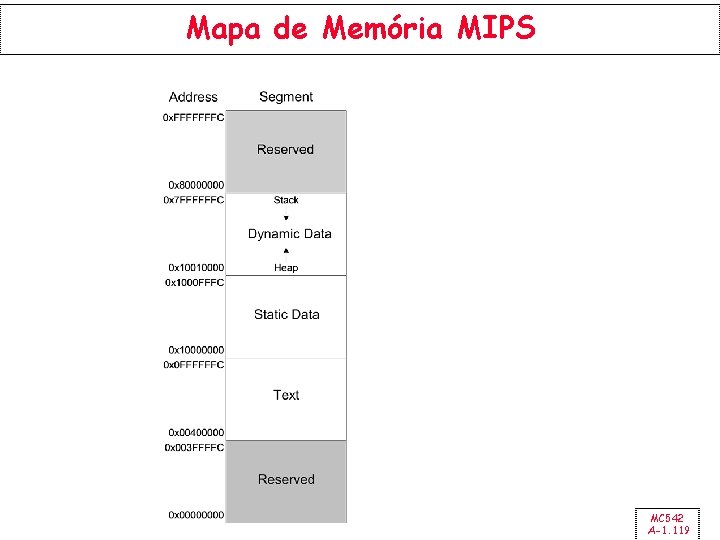

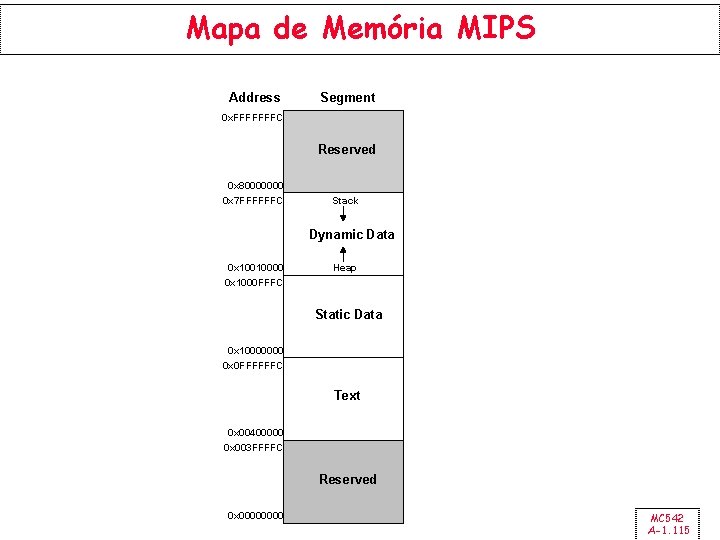

O que Deve ser Armazenado na Memória • Instruções (também chamado: text) • Dado – Global/stático: alocado antes de começar a execução Dinâmico: alocado pelo programa em execução • Qual o tamanho da memória? – No máximo 232 = 4 gigabytes (4 GB) – A´partir do endereço 0 x 0000 ao 0 x. FFFF MC 542 A-1. 114

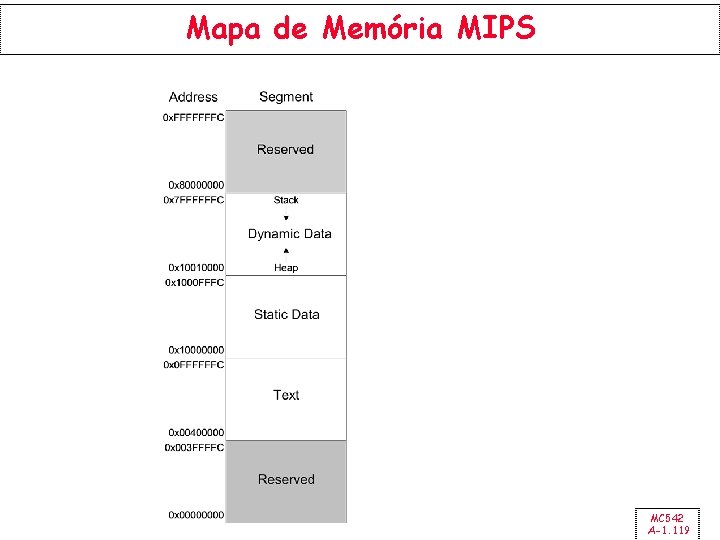

Mapa de Memória MIPS Address Segment 0 x. FFFFFFFC Reserved 0 x 80000000 0 x 7 FFFFFFC Stack Dynamic Data 0 x 10010000 0 x 1000 FFFC Heap Static Data 0 x 10000000 0 x 0 FFFFFFC Text 0 x 00400000 0 x 003 FFFFC Reserved 0 x 0000 MC 542 A-1. 115

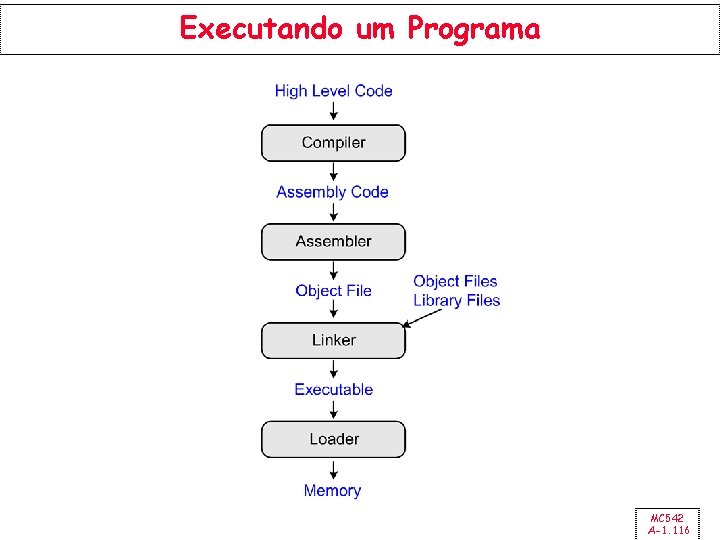

Executando um Programa MC 542 A-1. 116

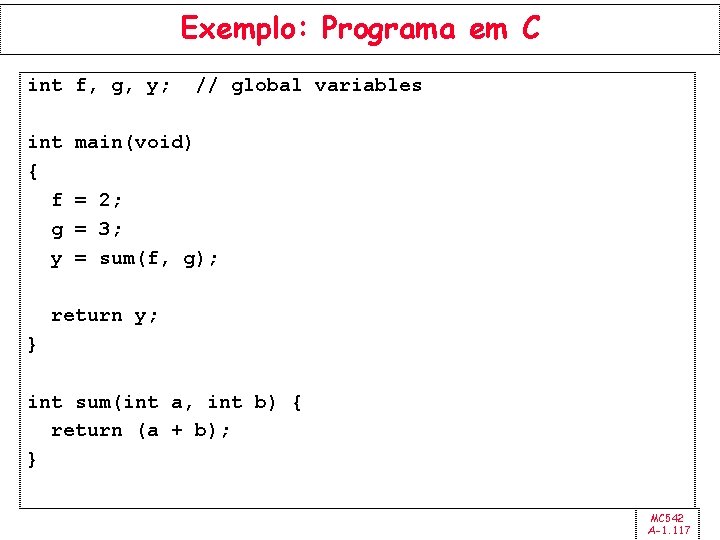

Exemplo: Programa em C int f, g, y; int { f g y // global variables main(void) = 2; = 3; = sum(f, g); return y; } int sum(int a, int b) { return (a + b); } MC 542 A-1. 117

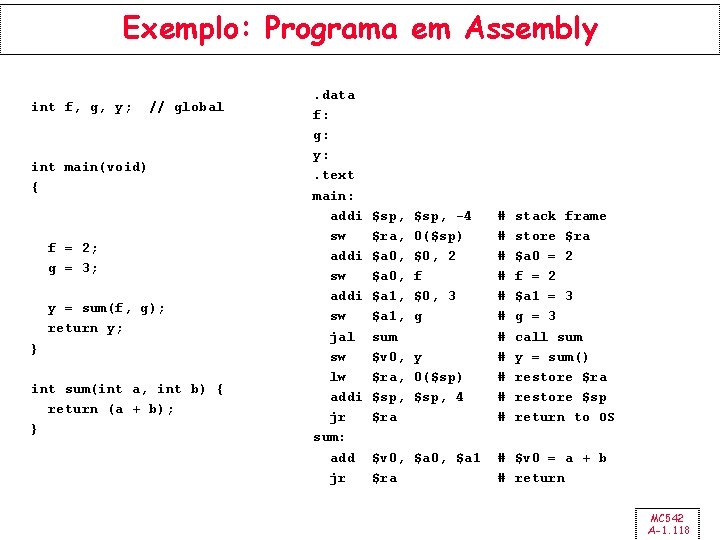

Exemplo: Programa em Assembly int f, g, y; // global int main(void) { f = 2; g = 3; y = sum(f, g); return y; } int sum(int a, int b) { return (a + b); } . data f: g: y: . text main: addi sw jal sw lw addi jr sum: add jr $sp, $ra, $a 0, $a 1, sum $v 0, $ra, $sp, $ra $sp, -4 0($sp) $0, 2 f $0, 3 g y 0($sp) $sp, 4 $v 0, $a 1 $ra # # # stack frame store $ra $a 0 = 2 f = 2 $a 1 = 3 g = 3 call sum y = sum() restore $ra restore $sp return to OS # $v 0 = a + b # return MC 542 A-1. 118

Mapa de Memória MIPS MC 542 A-1. 119

Exemplo: Tabela de Símbolos Symbol Address f 0 x 10000000 g 0 x 10000004 y 0 x 10000008 main 0 x 00400000 sum 0 x 0040002 C MC 542 A-1. 120

Exemplo: Programa Executável MC 542 A-1. 121

Exemplo: Programa na Memória MC 542 A-1. 122

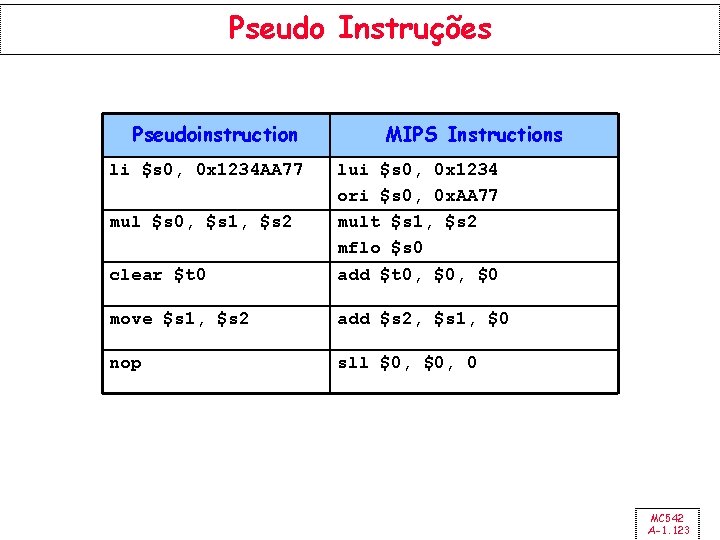

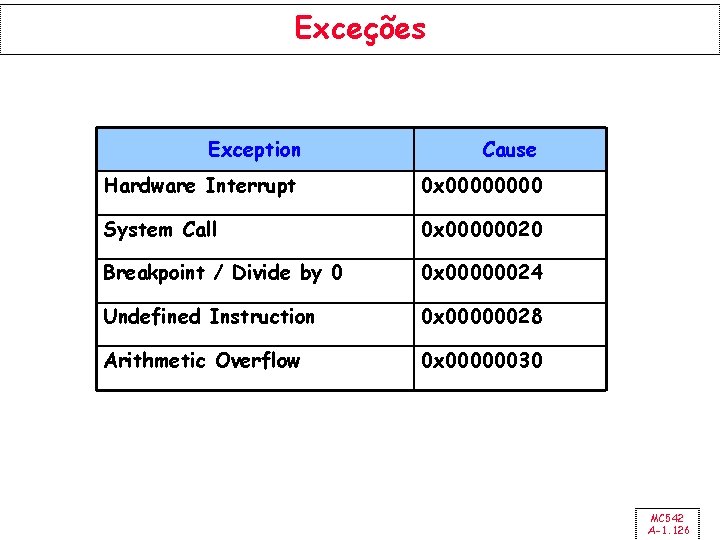

Pseudo Instruções Pseudoinstruction li $s 0, 0 x 1234 AA 77 MIPS Instructions clear $t 0 lui $s 0, 0 x 1234 ori $s 0, 0 x. AA 77 mult $s 1, $s 2 mflo $s 0 add $t 0, $0 move $s 1, $s 2 add $s 2, $s 1, $0 nop sll $0, 0 mul $s 0, $s 1, $s 2 MC 542 A-1. 123

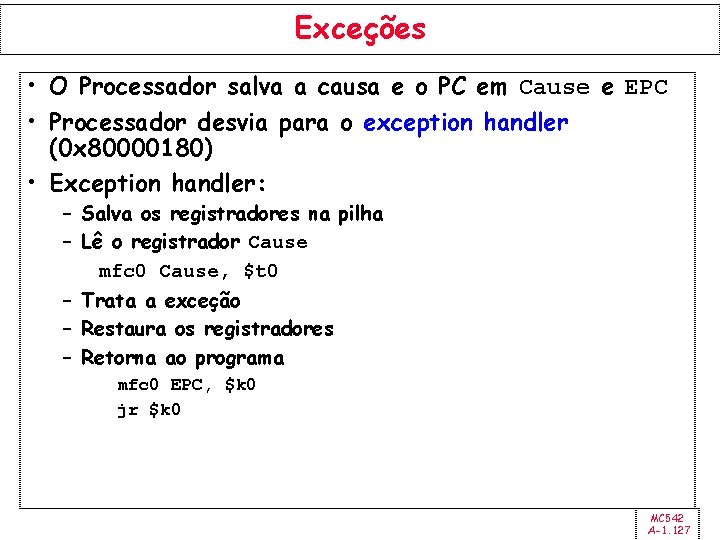

Exceções (Interrupções) • Chamada de procedimento, não prevista no código, para um exception handler • Causado por: – Hardware, também chamodo interrupção, exemp: keyboard – Software, também chamado de traps, exemp. : instrução indefinida • Quando uma exceção ocorre, o processador: – Registra a causa da exceção – Desvia a execução para exception handler no endereço de instrução 0 x 80000180 – Retorna ao programa MC 542 A-1. 124

Registradores de Exceção • Não faz parte do register file. – Cause » Registra a causa da exceção – EPC (Exception PC) » Registra o PC onde ocorreu a exceção • EPC e Cause: parte do Coprocessador 0 • Move from Coprocessor 0 – mfc 0 $t 0, EPC – Move o conteúdo de EPC para $t 0 MC 542 A-1. 125

Exceções Exception Cause Hardware Interrupt 0 x 0000 System Call 0 x 00000020 Breakpoint / Divide by 0 0 x 00000024 Undefined Instruction 0 x 00000028 Arithmetic Overflow 0 x 00000030 MC 542 A-1. 126

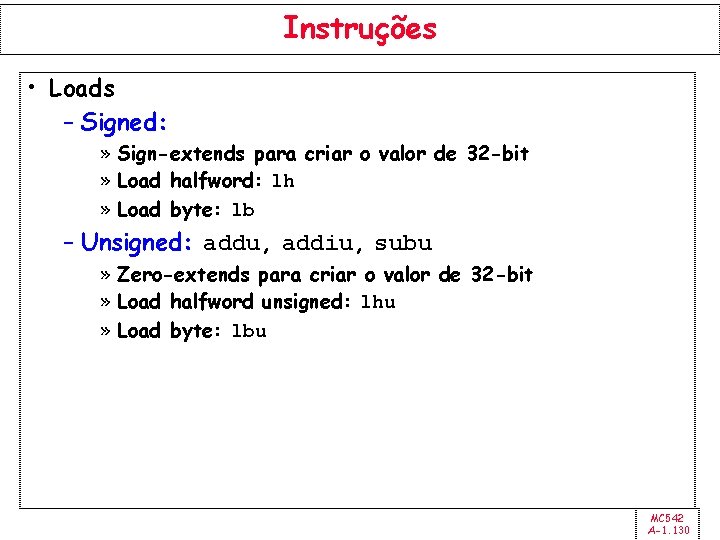

Exceções • O Processador salva a causa e o PC em Cause e EPC • Processador desvia para o exception handler (0 x 80000180) • Exception handler: – Salva os registradores na pilha – Lê o registrador Cause mfc 0 Cause, $t 0 – Trata a exceção – Restaura os registradores – Retorna ao programa mfc 0 EPC, $k 0 jr $k 0 MC 542 A-1. 127

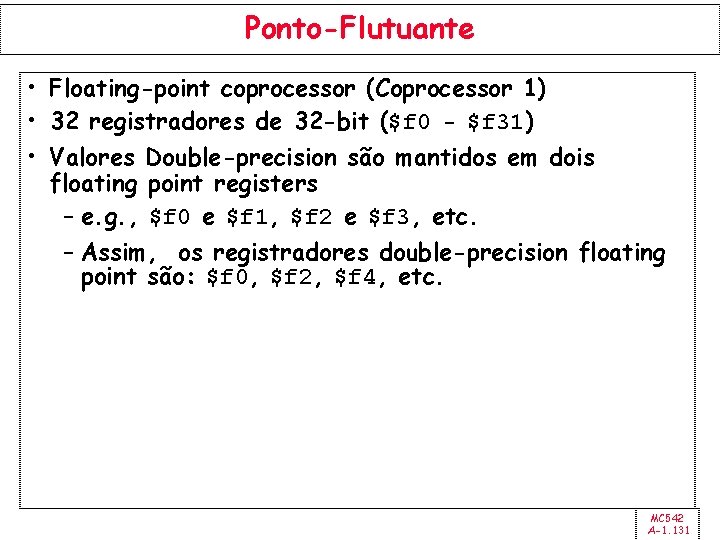

Instruções signed e Unsigned • Soma e Subtração • Multiplicação e Divisão • Set less than MC 542 A-1. 128

Instruções • Soma e subtração – Signed: add, addi, sub » Executa a mesma operação que a versão unsigned » Porém o processador gera exceção se overflow – Unsigned: addu, addiu, subu » O processador não gera exceção se overflow » Nota: addiu sign-extends o imediato • Multiplicação e Divisão – Signed: mult, div – Unsigned: multu, divu • Set Less Than – Signed: slt, slti – Unsigned: sltu, sltiu – Nota: sltiu sign-extends o imediato antes da comparação MC 542 A-1. 129

Instruções • Loads – Signed: » Sign-extends para criar o valor de 32 -bit » Load halfword: lh » Load byte: lb – Unsigned: addu, addiu, subu » Zero-extends para criar o valor de 32 -bit » Load halfword unsigned: lhu » Load byte: lbu MC 542 A-1. 130

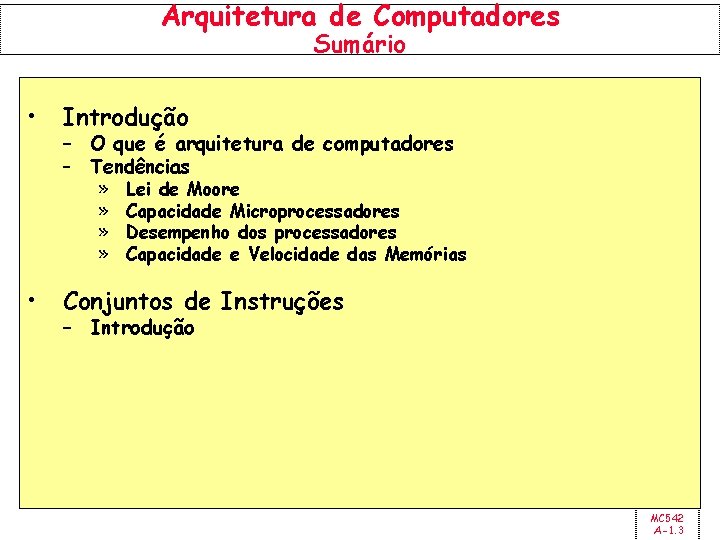

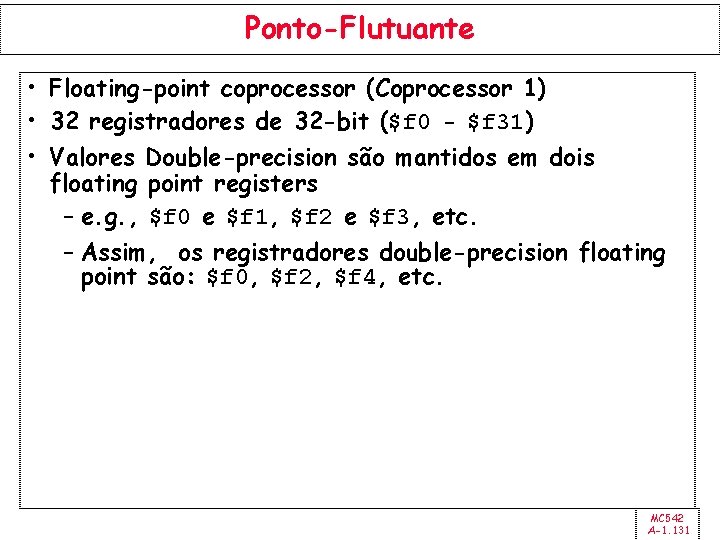

Ponto-Flutuante • Floating-point coprocessor (Coprocessor 1) • 32 registradores de 32 -bit ($f 0 - $f 31) • Valores Double-precision são mantidos em dois floating point registers – e. g. , $f 0 e $f 1, $f 2 e $f 3, etc. – Assim, os registradores double-precision floating point são: $f 0, $f 2, $f 4, etc. MC 542 A-1. 131

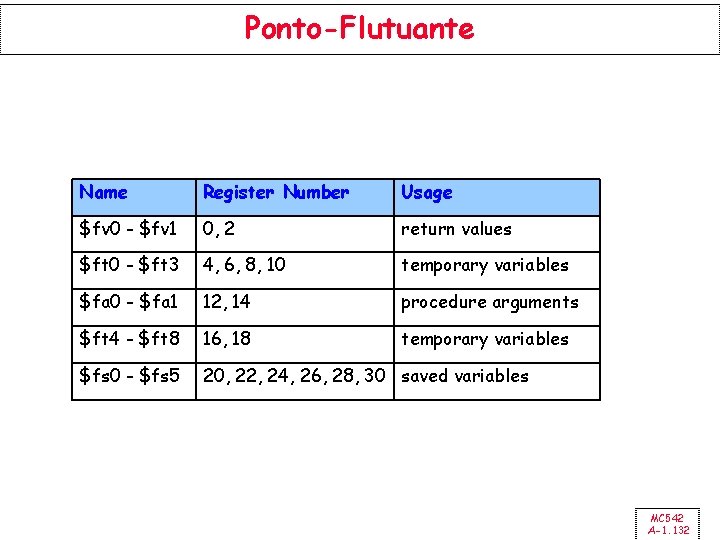

Ponto-Flutuante Name Register Number Usage $fv 0 - $fv 1 0, 2 return values $ft 0 - $ft 3 4, 6, 8, 10 temporary variables $fa 0 - $fa 1 12, 14 procedure arguments $ft 4 - $ft 8 16, 18 temporary variables $fs 0 - $fs 5 20, 22, 24, 26, 28, 30 saved variables MC 542 A-1. 132