MC 542 Organizao de Computadores Teoria e Prtica

- Slides: 44

MC 542 Organização de Computadores Teoria e Prática 2006 Prof. Paulo Cesar Centoducatte@ic. unicamp. br www. ic. unicamp. br/~ducatte Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 1

MC 542 Arquitetura de Computadores Processador MIPS Pipeline (continuação) “Computer Organization and Design: The Hardware/Software Interface” (Capítulo 6) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 2

Sumário • Dependências – Soluçãopor Softwarwe – Solução por Hardware • Forwarding • Condições para determinar se há Hazard de dados • Datapath sem Forwarding • Datapath com Forwarding • Detecção e Controle de Hazard • Datapath Modificado para Fowarding • Exemplo de Execução de instruções com Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 3

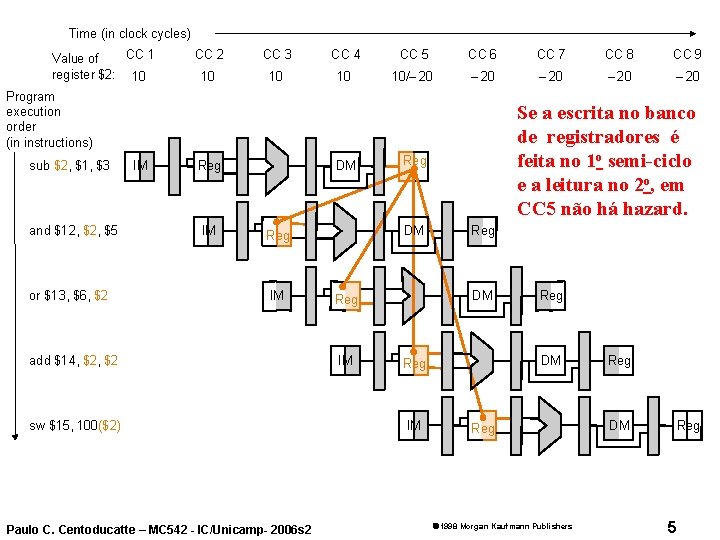

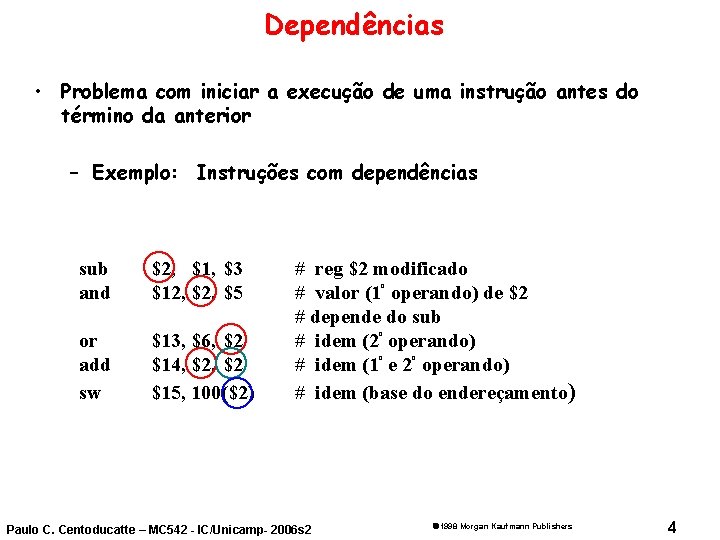

Dependências • Problema com iniciar a execução de uma instrução antes do término da anterior – Exemplo: Instruções com dependências sub and $2, $1, $3 $12, $5 or add sw $13, $6, $2 $14, $2 $15, 100($2) # reg $2 modificado # valor (1º operando) de $2 # depende do sub # idem (2º operando) # idem (1º e 2º operando) # idem (base do endereçamento) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 4

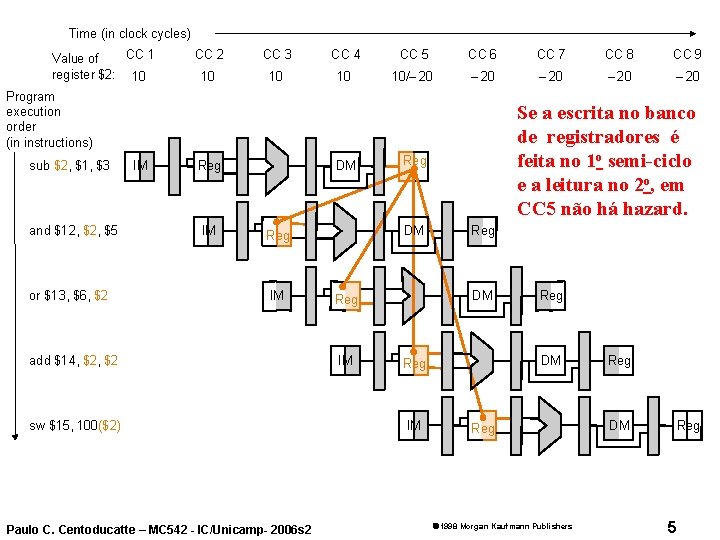

Time (in clock cycles) CC 1 Value of register $2: 10 CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 10 10/– 20 – 20 Program execution order (in instructions) sub $2, $1, $3 and $12, $5 or $13, $6, $2 IM Reg IM DM IM add $14, $2 sw $15, 100($2) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 Reg DM Reg IM Se a escrita no banco de registradores é feita no 1 o semi-ciclo e a leitura no 2 o, em CC 5 não há hazard. DM Reg IM Reg 1998 Morgan Kaufmann Publishers Reg DM Reg 5

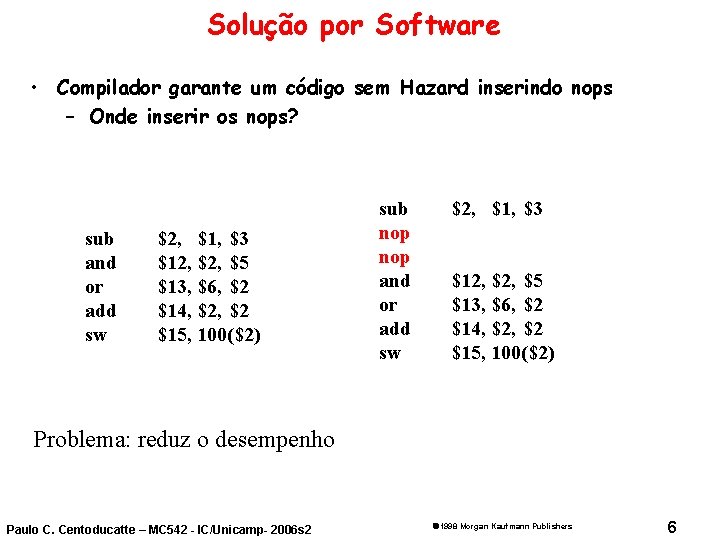

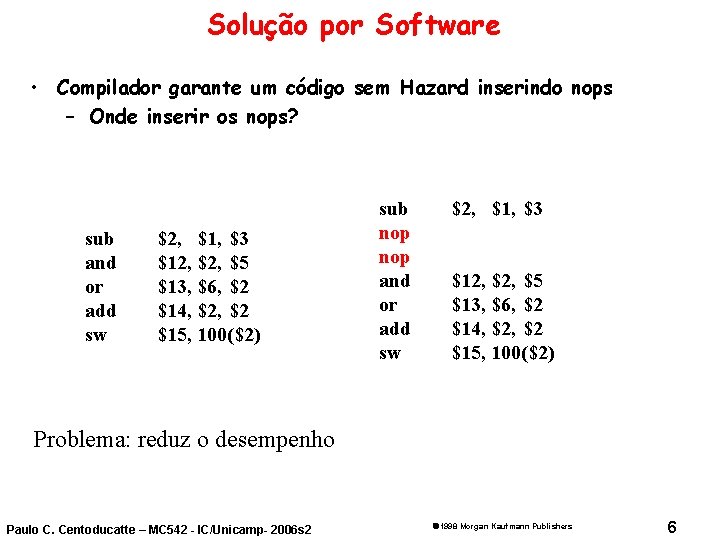

Solução por Software • Compilador garante um código sem Hazard inserindo nops – Onde inserir os nops? sub and or add sw $2, $1, $3 $12, $5 $13, $6, $2 $14, $2 $15, 100($2) sub nop and or add sw $2, $1, $3 $12, $5 $13, $6, $2 $14, $2 $15, 100($2) Problema: reduz o desempenho Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 6

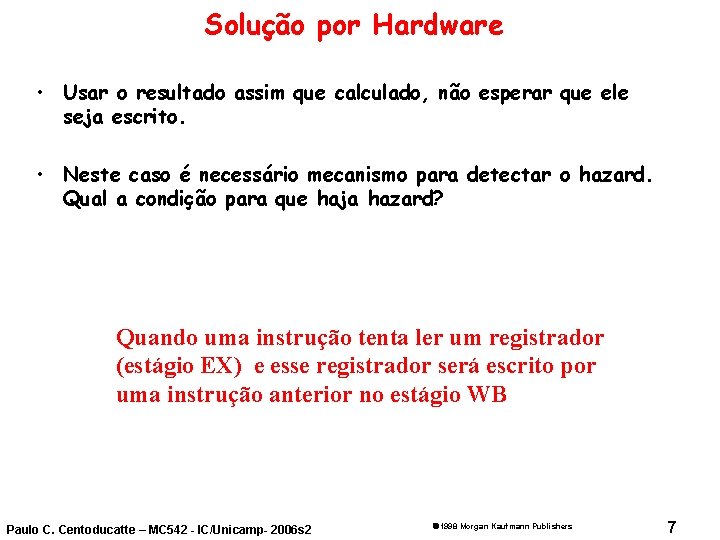

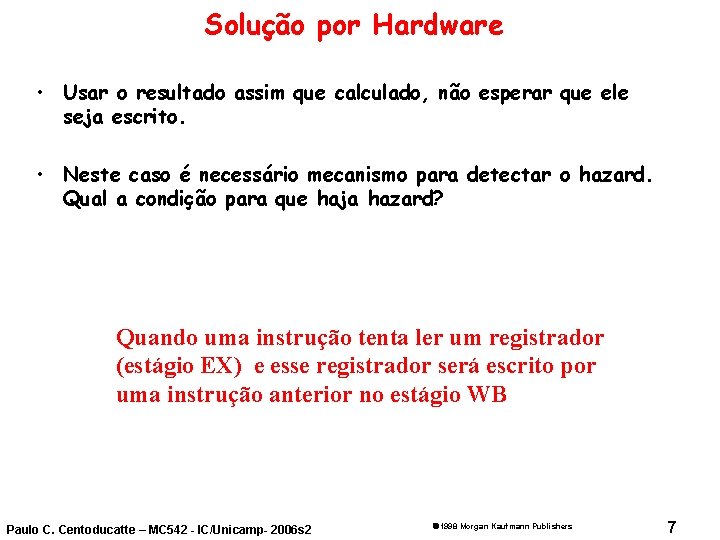

Solução por Hardware • Usar o resultado assim que calculado, não esperar que ele seja escrito. • Neste caso é necessário mecanismo para detectar o hazard. Qual a condição para que haja hazard? Quando uma instrução tenta ler um registrador (estágio EX) e esse registrador será escrito por uma instrução anterior no estágio WB Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 7

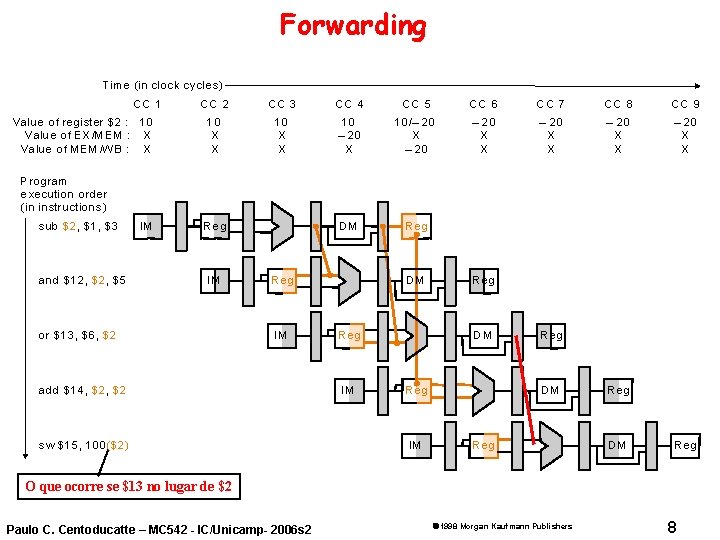

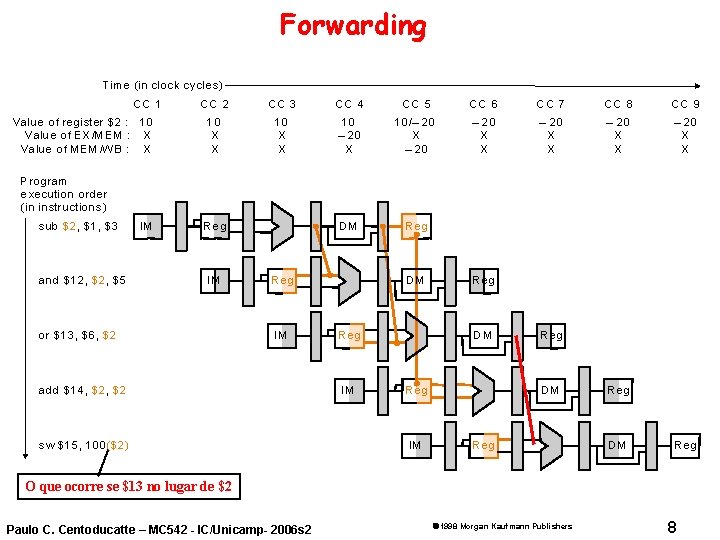

Forwarding Time (in clock cycles) CC 1 Value of register $ 2 : 10 Valu e of EX/M EM : X Valu e of M EM /W B : X CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 10 X X 10 – 20 X 10/– 20 X X – 20 X X DM R eg Prog ram e xecution order (in instru ctio ns) sub $ 2, $1, $ 3 a nd $ 12, $5 IM Re g IM o r $13, $ 6, $2 R eg IM a dd $ 14, $2 sw $15, 1 00($2) DM R eg IM R eg DM R eg IM Reg DM R eg Reg DM Re g O que ocorre se $13 no lugar de $2 Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 8

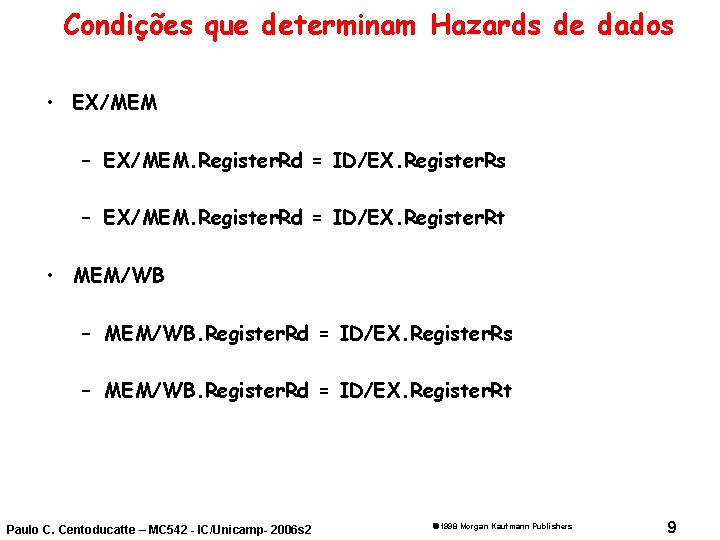

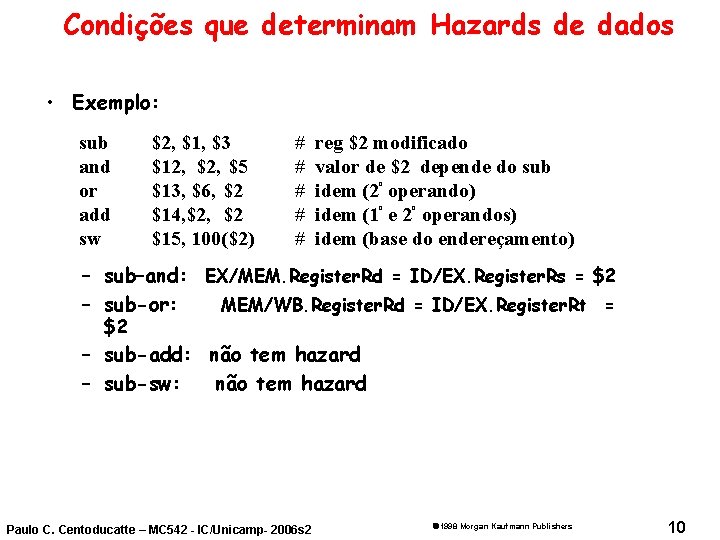

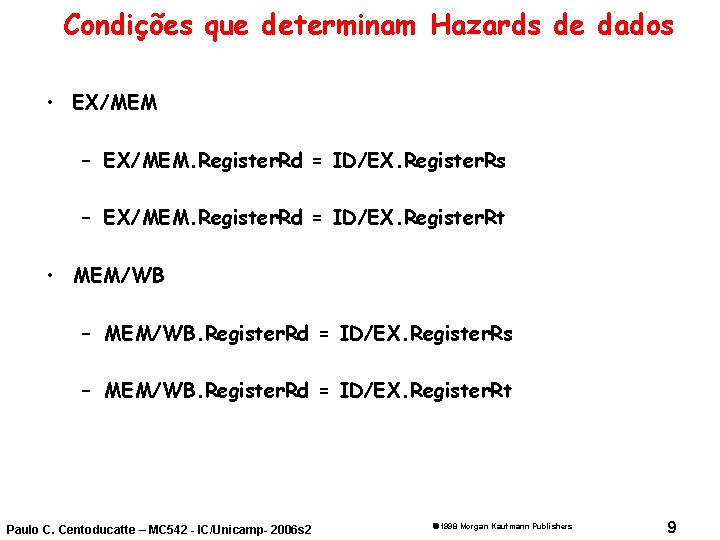

Condições que determinam Hazards de dados • EX/MEM – EX/MEM. Register. Rd = ID/EX. Register. Rs – EX/MEM. Register. Rd = ID/EX. Register. Rt • MEM/WB – MEM/WB. Register. Rd = ID/EX. Register. Rs – MEM/WB. Register. Rd = ID/EX. Register. Rt Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 9

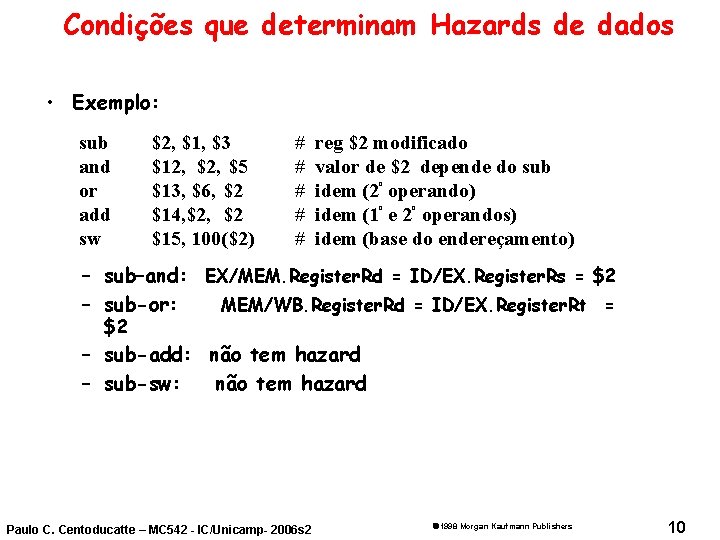

Condições que determinam Hazards de dados • Exemplo: sub and or add sw $2, $1, $3 $12, $5 $13, $6, $2 $14, $2 $15, 100($2) # # # reg $2 modificado valor de $2 depende do sub idem (2º operando) idem (1º e 2º operandos) idem (base do endereçamento) – sub–and: EX/MEM. Register. Rd = ID/EX. Register. Rs = $2 – sub-or: MEM/WB. Register. Rd = ID/EX. Register. Rt = $2 – sub-add: não tem hazard – sub-sw: não tem hazard Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 10

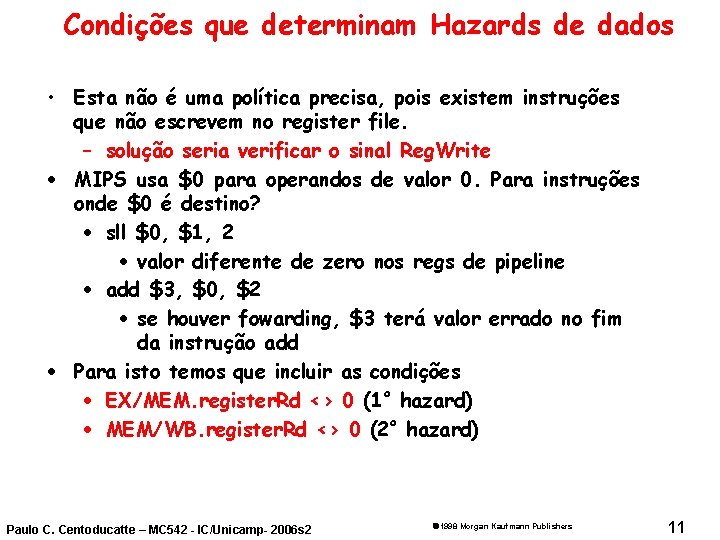

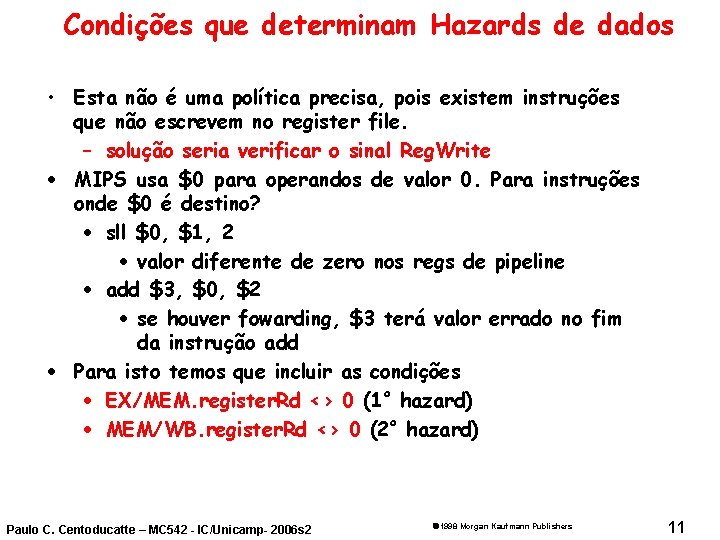

Condições que determinam Hazards de dados • Esta não é uma política precisa, pois existem instruções que não escrevem no register file. – solução seria verificar o sinal Reg. Write · MIPS usa $0 para operandos de valor 0. Para instruções onde $0 é destino? · sll $0, $1, 2 · valor diferente de zero nos regs de pipeline · add $3, $0, $2 · se houver fowarding, $3 terá valor errado no fim da instrução add · Para isto temos que incluir as condições · EX/MEM. register. Rd <> 0 (1º hazard) · MEM/WB. register. Rd <> 0 (2º hazard) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 11

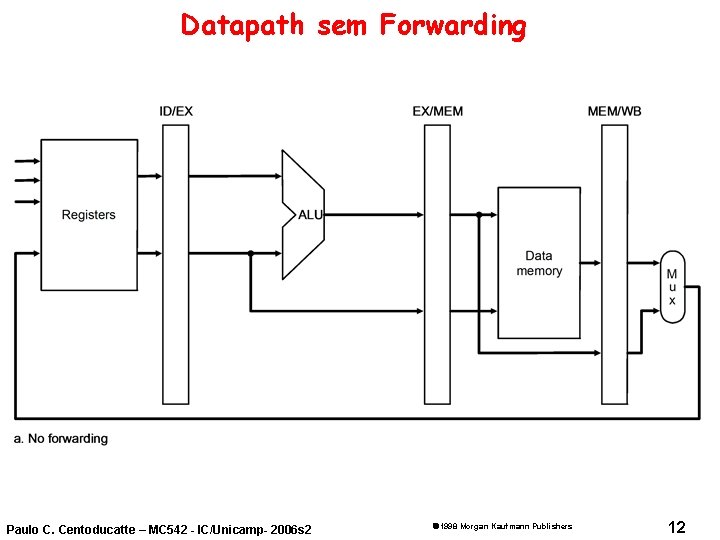

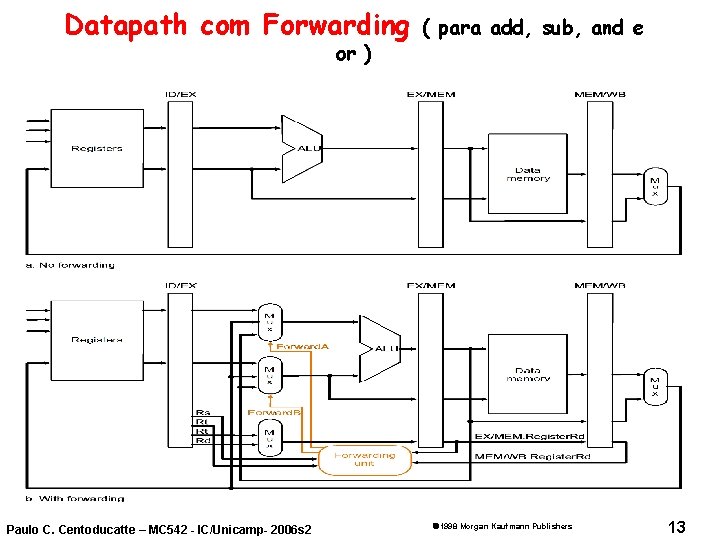

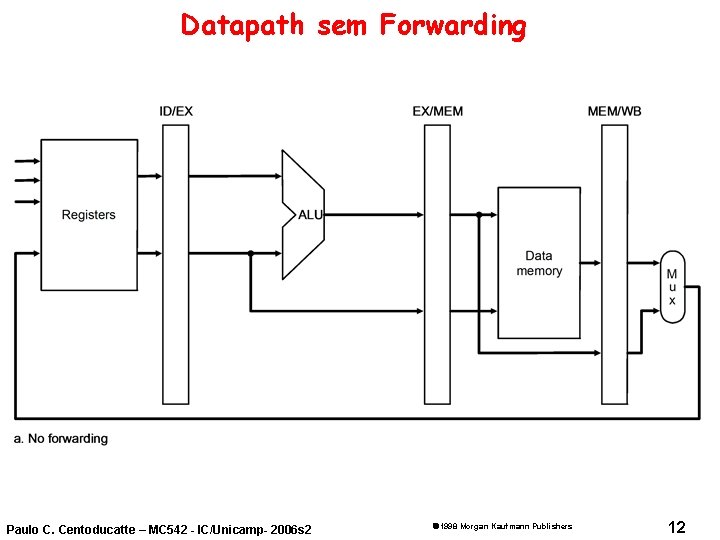

Datapath sem Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 12

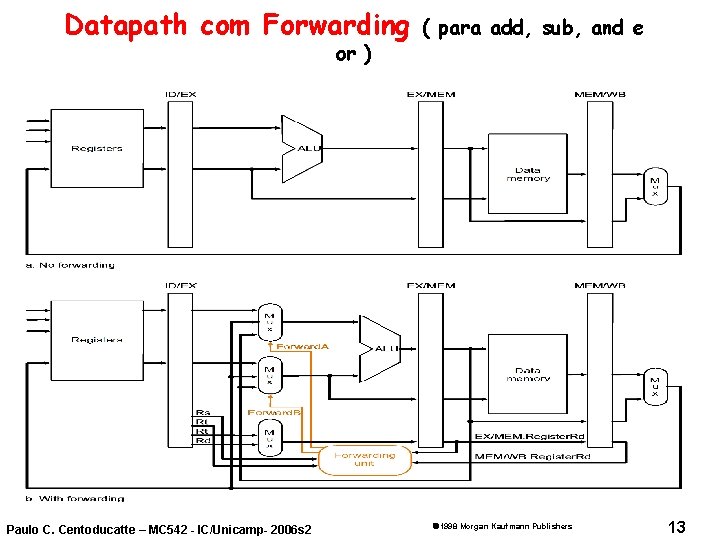

Datapath com Forwarding or ) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 ( para add, sub, and e 1998 Morgan Kaufmann Publishers 13

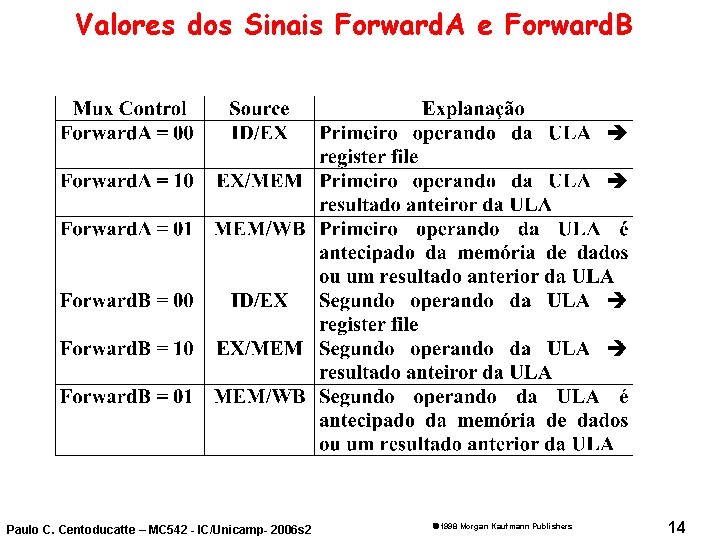

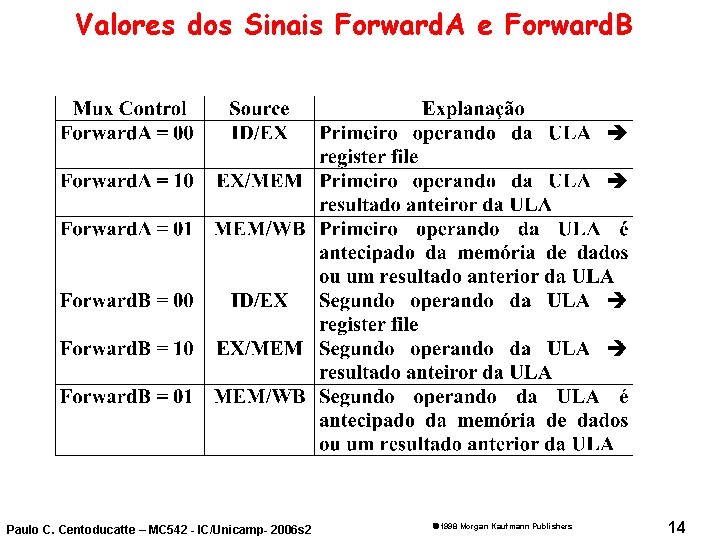

Valores dos Sinais Forward. A e Forward. B Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 14

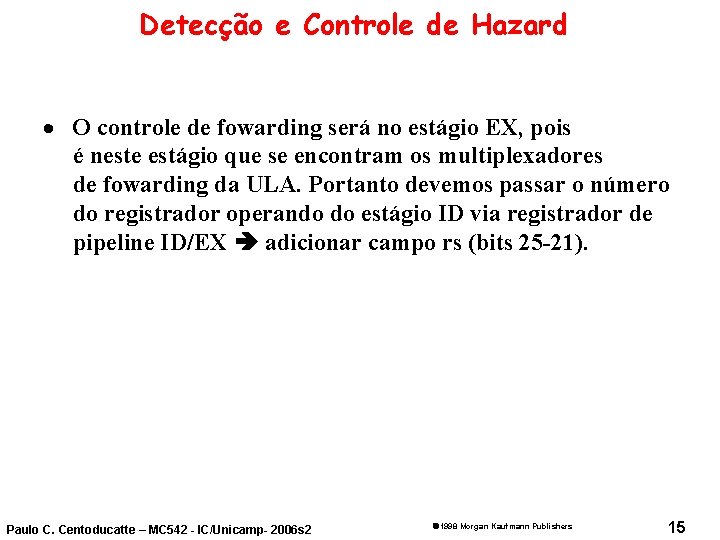

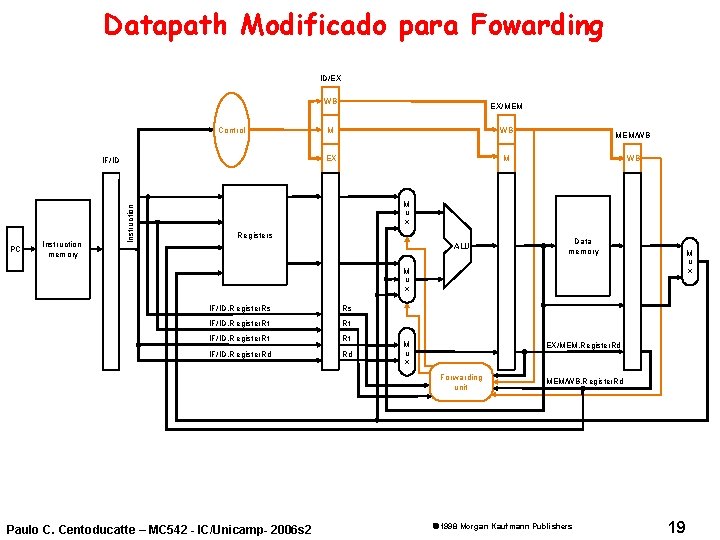

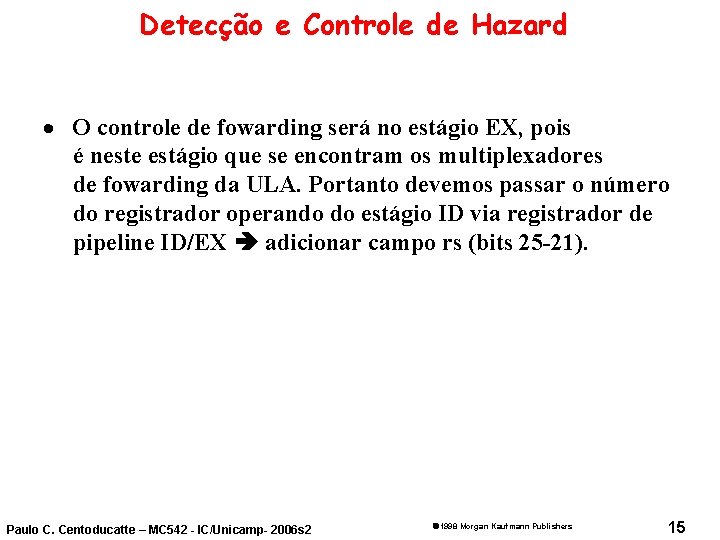

Detecção e Controle de Hazard · O controle de fowarding será no estágio EX, pois é neste estágio que se encontram os multiplexadores de fowarding da ULA. Portanto devemos passar o número do registrador operando do estágio ID via registrador de pipeline ID/EX adicionar campo rs (bits 25 -21). Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 15

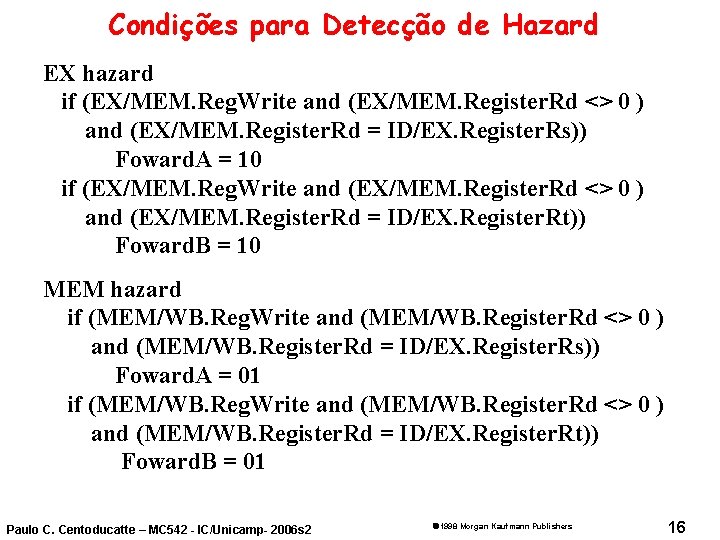

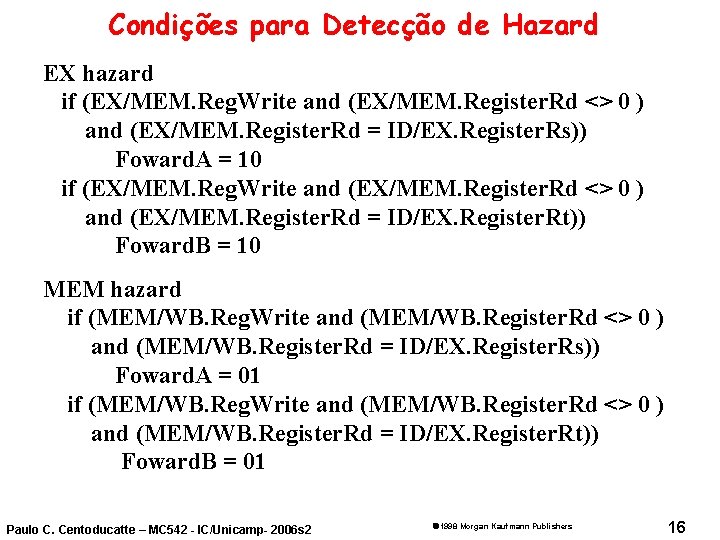

Condições para Detecção de Hazard EX hazard if (EX/MEM. Reg. Write and (EX/MEM. Register. Rd <> 0 ) and (EX/MEM. Register. Rd = ID/EX. Register. Rs)) Foward. A = 10 if (EX/MEM. Reg. Write and (EX/MEM. Register. Rd <> 0 ) and (EX/MEM. Register. Rd = ID/EX. Register. Rt)) Foward. B = 10 MEM hazard if (MEM/WB. Reg. Write and (MEM/WB. Register. Rd <> 0 ) and (MEM/WB. Register. Rd = ID/EX. Register. Rs)) Foward. A = 01 if (MEM/WB. Reg. Write and (MEM/WB. Register. Rd <> 0 ) and (MEM/WB. Register. Rd = ID/EX. Register. Rt)) Foward. B = 01 Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 16

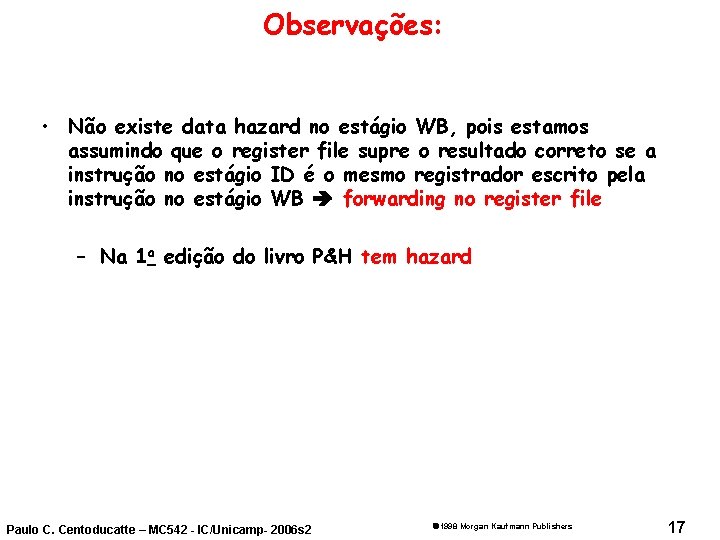

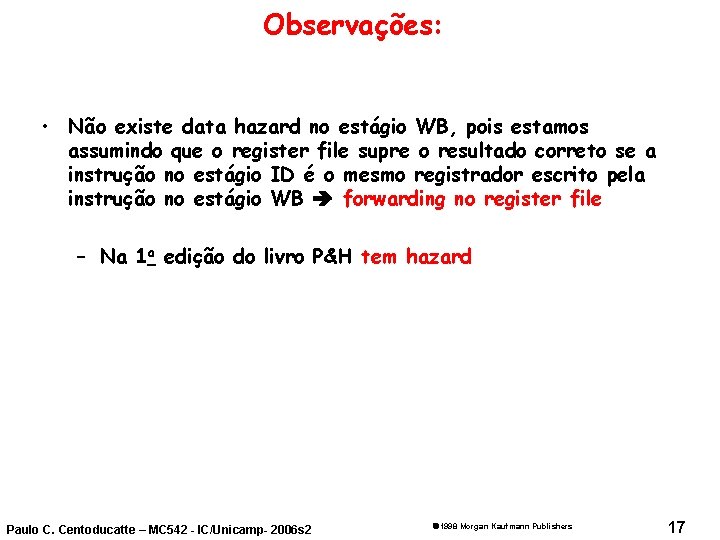

Observações: • Não existe data hazard no estágio WB, pois estamos assumindo que o register file supre o resultado correto se a instrução no estágio ID é o mesmo registrador escrito pela instrução no estágio WB forwarding no register file – Na 1 a edição do livro P&H tem hazard Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 17

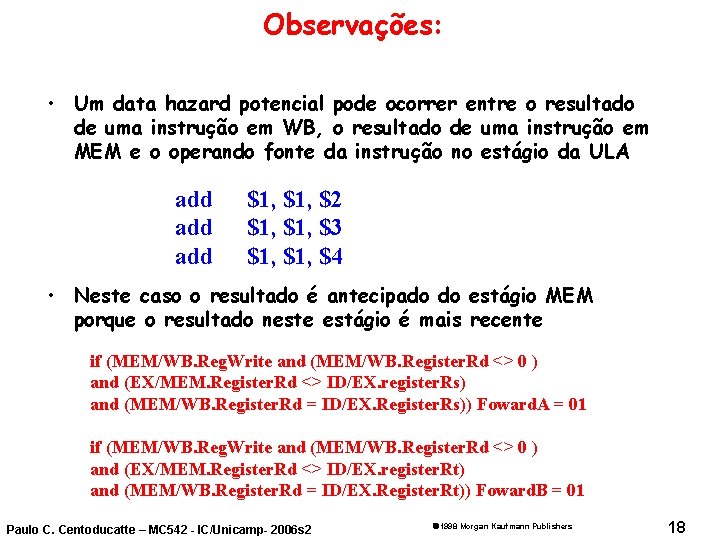

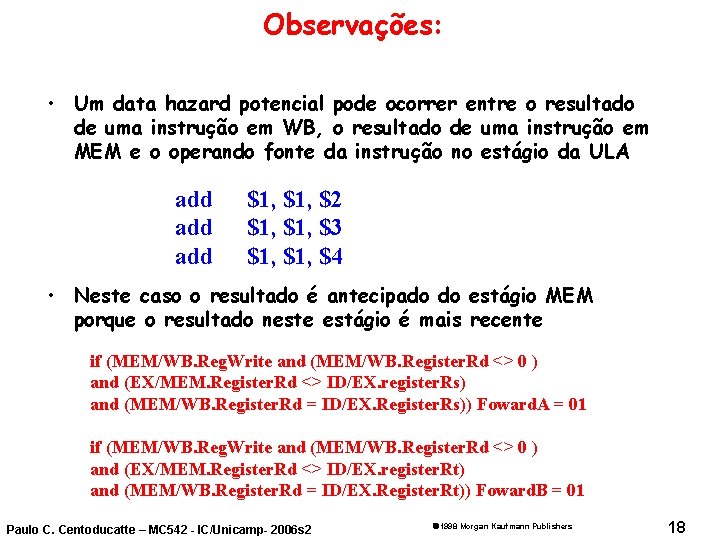

Observações: • Um data hazard potencial pode ocorrer entre o resultado de uma instrução em WB, o resultado de uma instrução em MEM e o operando fonte da instrução no estágio da ULA add add $1, $2 $1, $3 $1, $4 • Neste caso o resultado é antecipado do estágio MEM porque o resultado neste estágio é mais recente if (MEM/WB. Reg. Write and (MEM/WB. Register. Rd <> 0 ) and (EX/MEM. Register. Rd <> ID/EX. register. Rs) and (MEM/WB. Register. Rd = ID/EX. Register. Rs)) Foward. A = 01 if (MEM/WB. Reg. Write and (MEM/WB. Register. Rd <> 0 ) and (EX/MEM. Register. Rd <> ID/EX. register. Rt) and (MEM/WB. Register. Rd = ID/EX. Register. Rt)) Foward. B = 01 Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 18

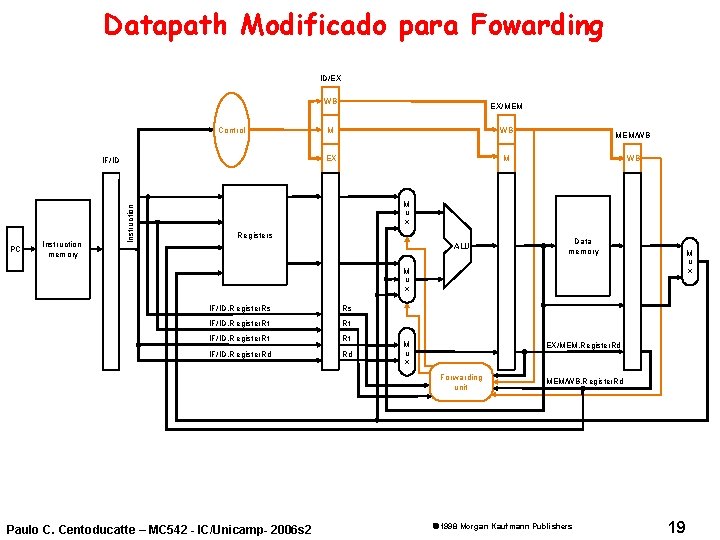

Datapath Modificado para Fowarding ID/EX WB Control PC Instruction memory Instruction IF/ID EX/MEM M WB EX M MEM/WB WB M u x Registers ALU Data memory M u x IF/ID. Register. Rs Rs IF/ID. Register. Rt Rt IF/ID. Register. Rd Rd M u x EX/MEM. Register. Rd Forwarding unit Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 MEM/WB. Register. Rd 1998 Morgan Kaufmann Publishers 19

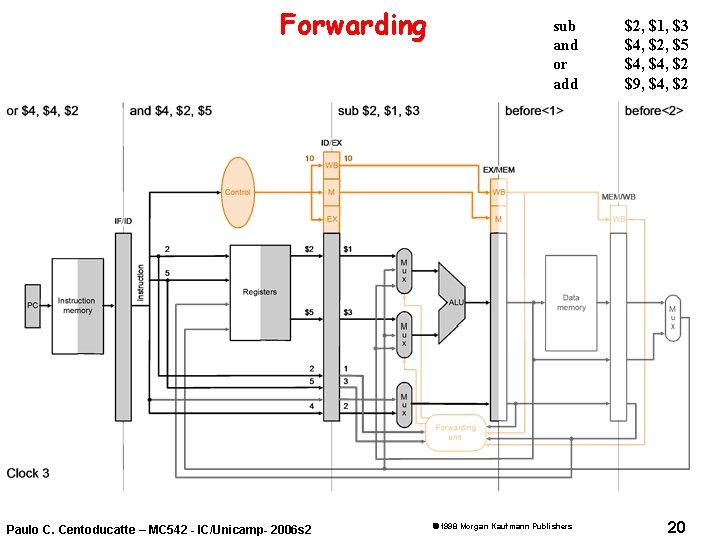

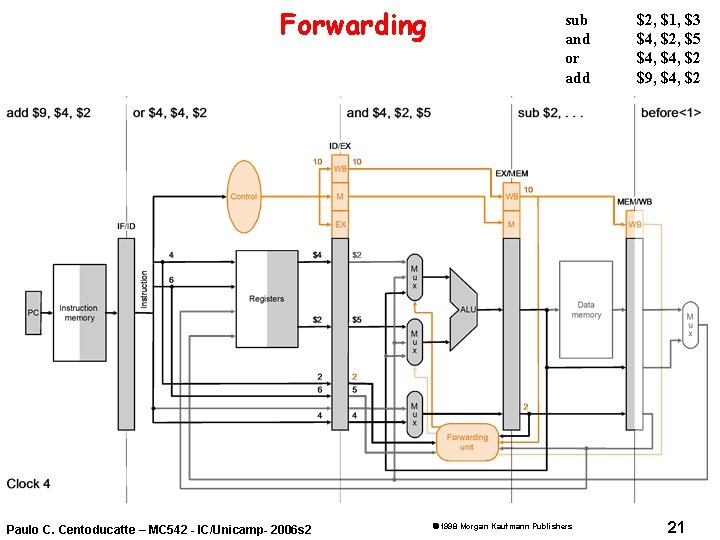

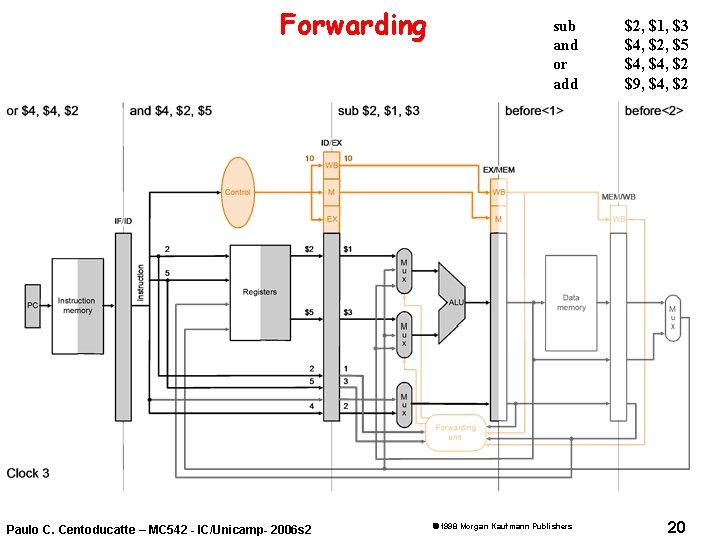

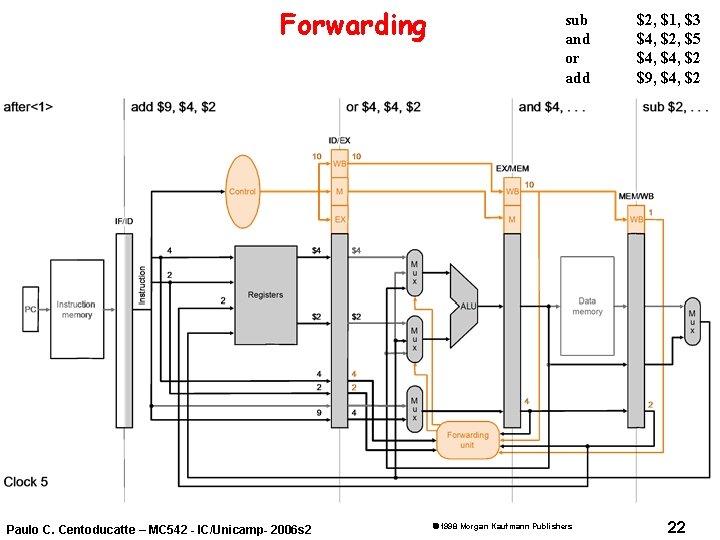

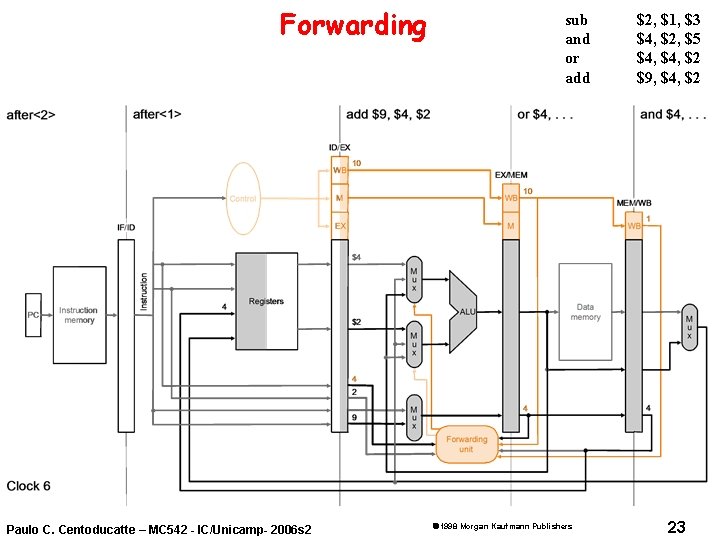

Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 sub and or add 1998 Morgan Kaufmann Publishers $2, $1, $3 $4, $2, $5 $4, $2 $9, $4, $2 20

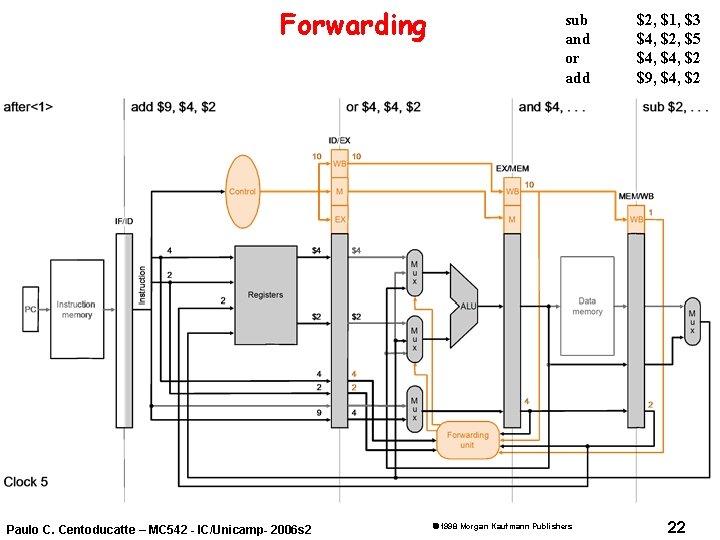

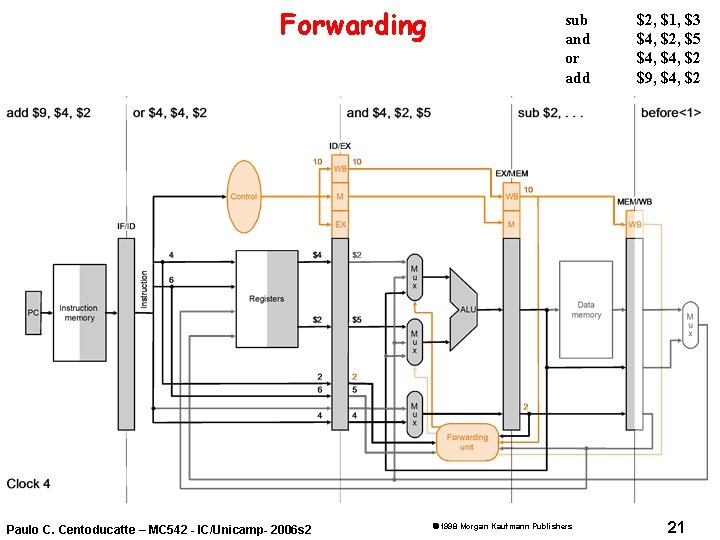

Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 sub and or add 1998 Morgan Kaufmann Publishers $2, $1, $3 $4, $2, $5 $4, $2 $9, $4, $2 21

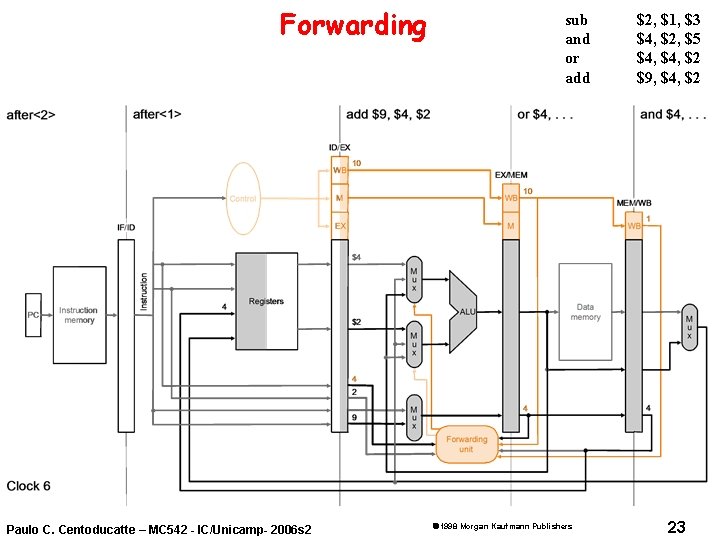

Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 sub and or add 1998 Morgan Kaufmann Publishers $2, $1, $3 $4, $2, $5 $4, $2 $9, $4, $2 22

Forwarding Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 sub and or add 1998 Morgan Kaufmann Publishers $2, $1, $3 $4, $2, $5 $4, $2 $9, $4, $2 23

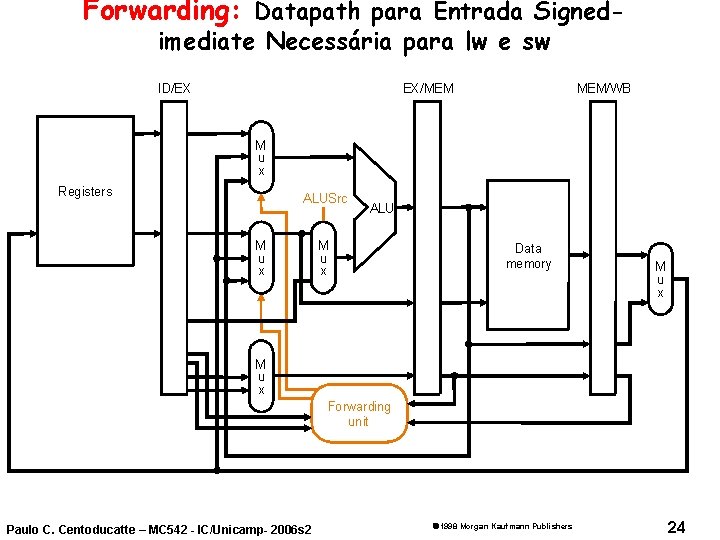

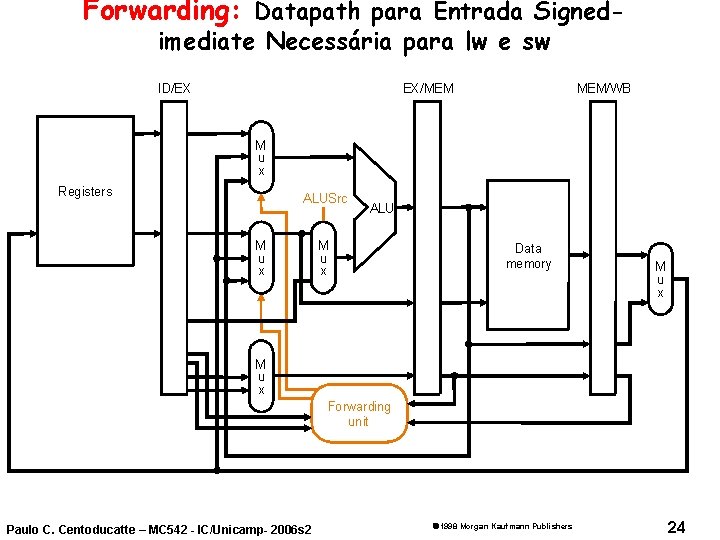

Forwarding: Datapath para Entrada Signedimediate Necessária para lw e sw ID/EX EX/MEM MEM/WB M u x Registers ALUSrc M u x ALU M u x Data memory M u x Forwarding unit Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 24

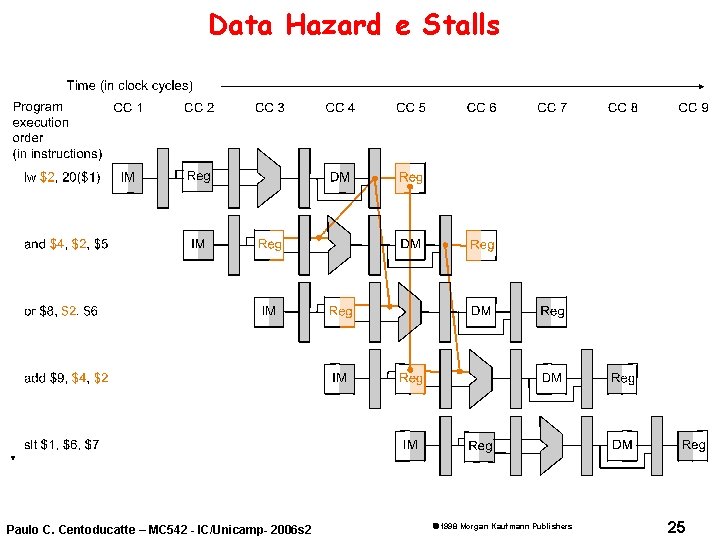

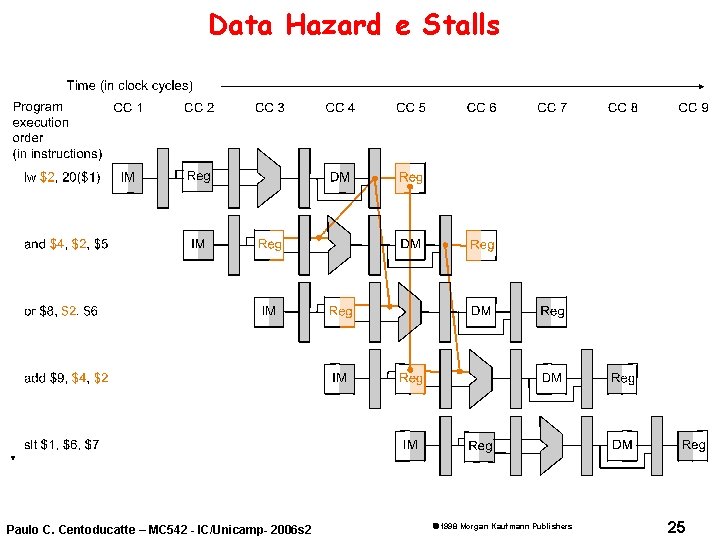

Data Hazard e Stalls Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 25

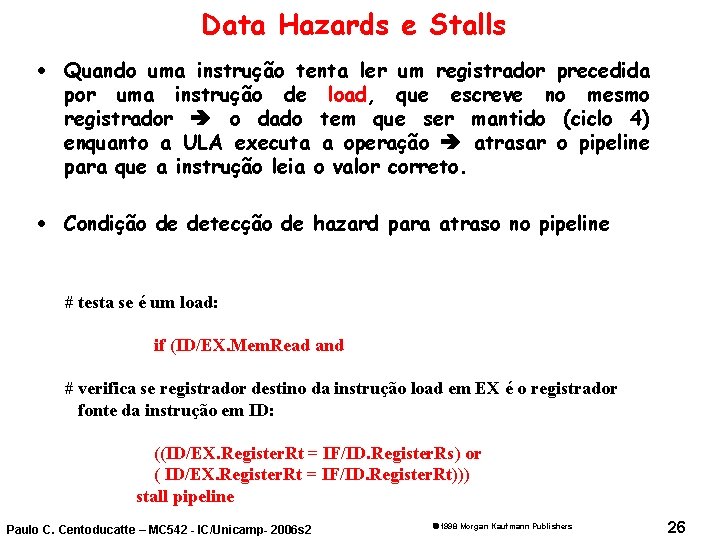

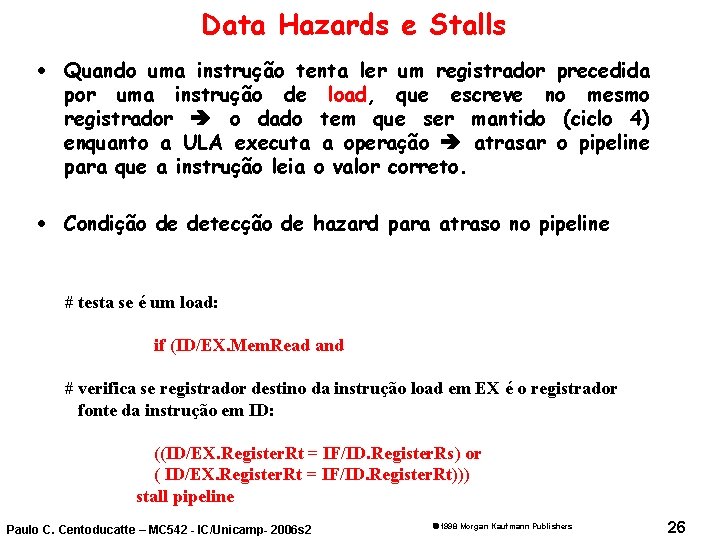

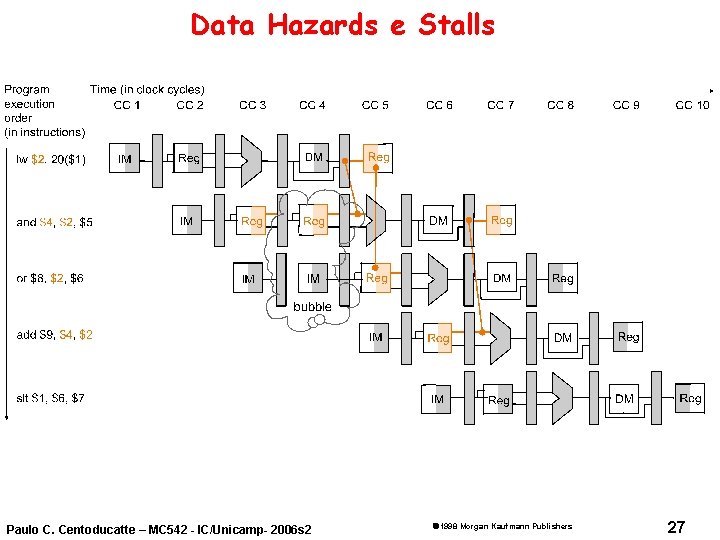

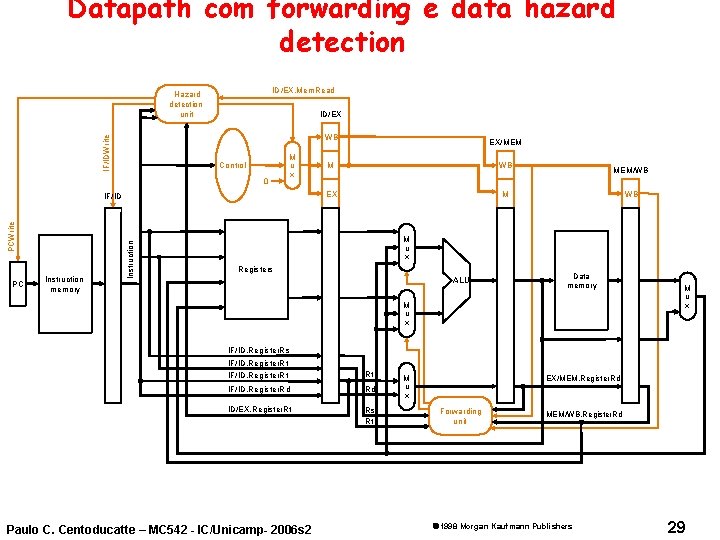

Data Hazards e Stalls · Quando uma instrução tenta ler um registrador precedida por uma instrução de load, que escreve no mesmo registrador o dado tem que ser mantido (ciclo 4) enquanto a ULA executa a operação atrasar o pipeline para que a instrução leia o valor correto. · Condição de detecção de hazard para atraso no pipeline # testa se é um load: if (ID/EX. Mem. Read and # verifica se registrador destino da instrução load em EX é o registrador fonte da instrução em ID: ((ID/EX. Register. Rt = IF/ID. Register. Rs) or ( ID/EX. Register. Rt = IF/ID. Register. Rt))) stall pipeline Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 26

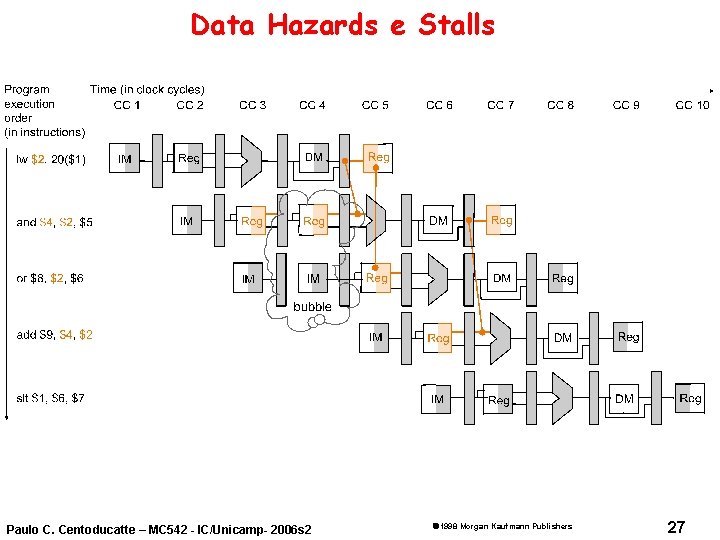

Data Hazards e Stalls Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 27

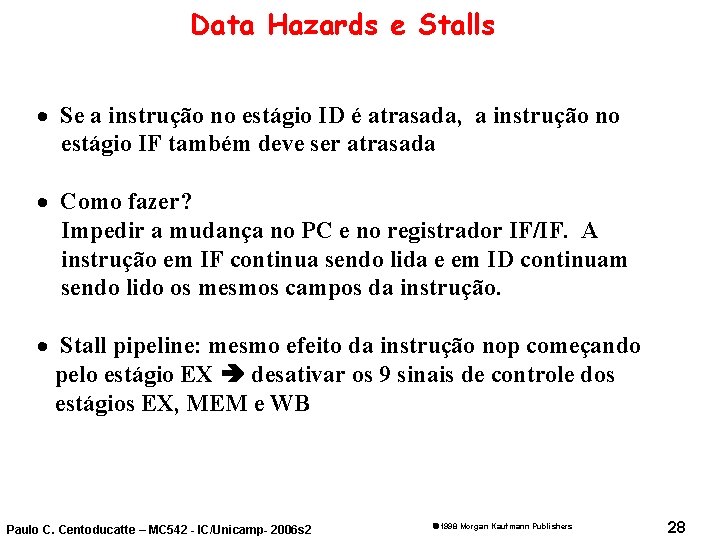

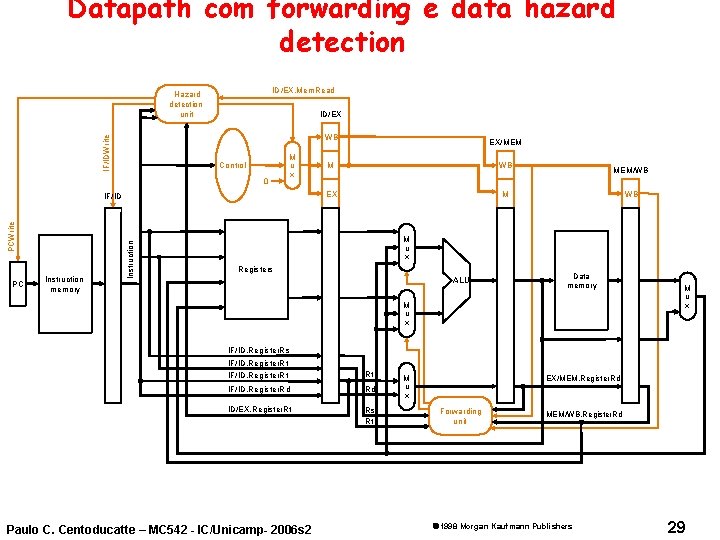

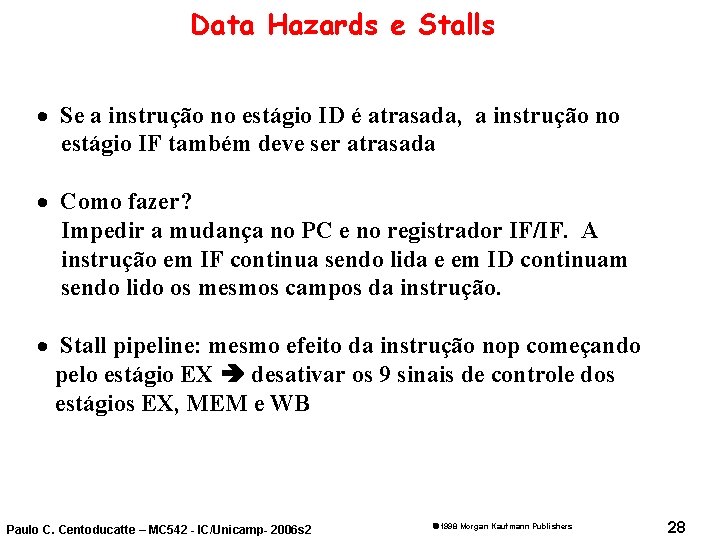

Data Hazards e Stalls · Se a instrução no estágio ID é atrasada, a instrução no estágio IF também deve ser atrasada · Como fazer? Impedir a mudança no PC e no registrador IF/IF. A instrução em IF continua sendo lida e em ID continuam sendo lido os mesmos campos da instrução. · Stall pipeline: mesmo efeito da instrução nop começando pelo estágio EX desativar os 9 sinais de controle dos estágios EX, MEM e WB Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 28

Datapath com forwarding e data hazard detection ID/EX. Mem. Read Hazard detection unit ID/EX IF/IDWrite WB Control 0 M u x PC Instruction memory Instruction PCWrite IF/ID EX/MEM M WB EX M MEM/WB WB M u x Registers ALU Data memory M u x IF/ID. Register. Rs IF/ID. Register. Rt Rt IF/ID. Register. Rd Rd ID/EX. Register. Rt Rs Rt Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 M u x EX/MEM. Register. Rd Forwarding unit MEM/WB. Register. Rd 1998 Morgan Kaufmann Publishers 29

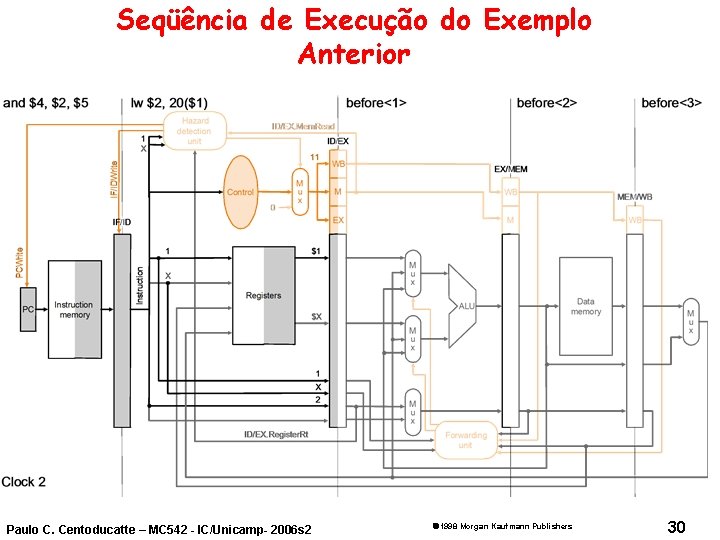

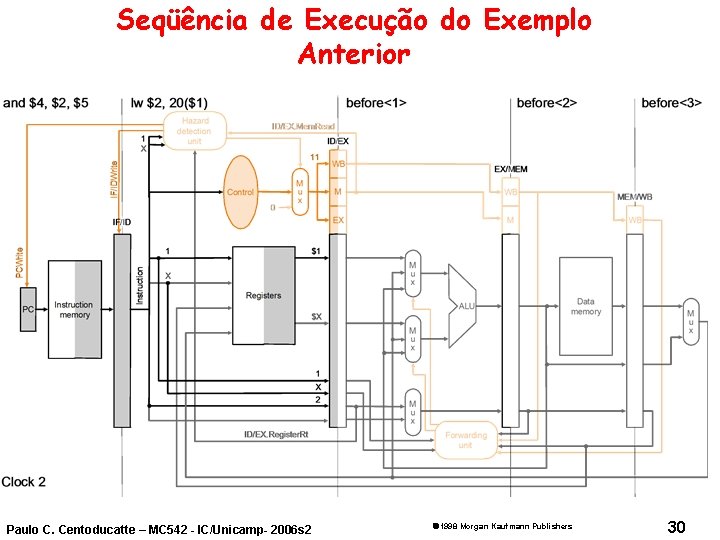

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 30

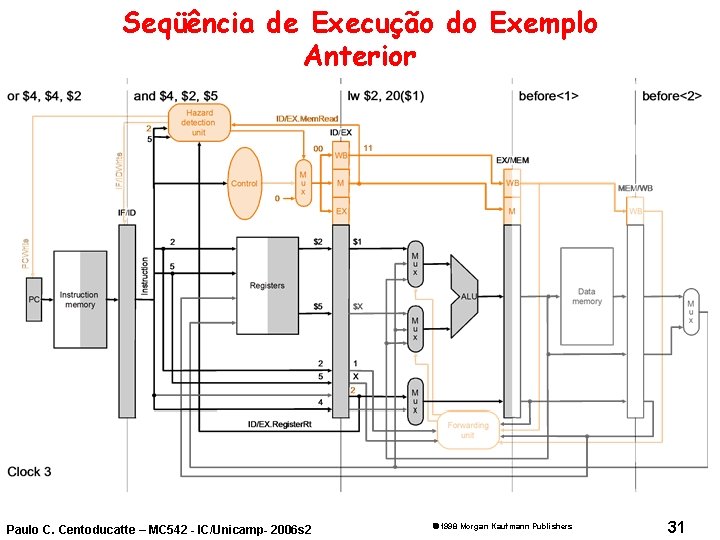

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 31

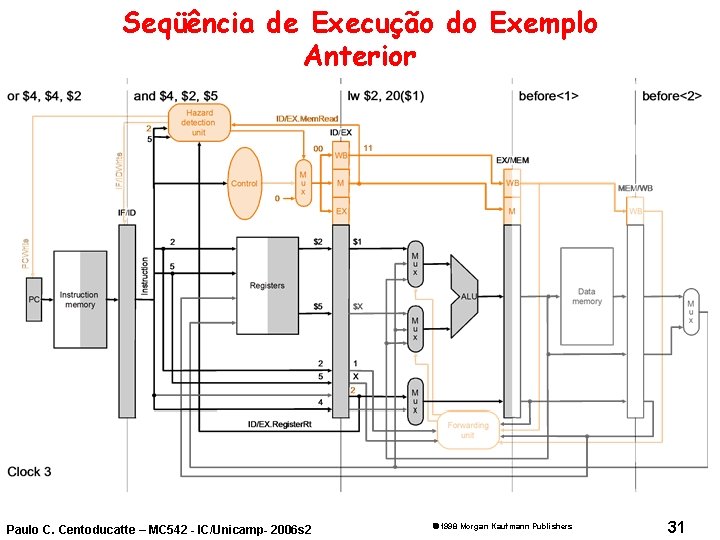

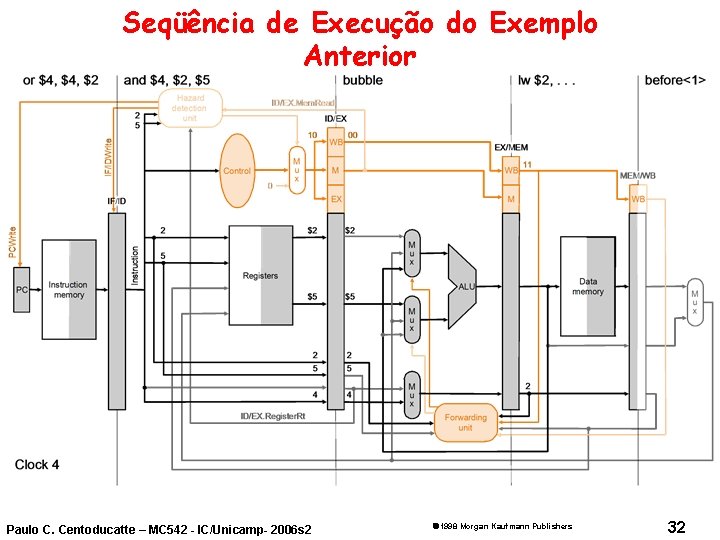

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 32

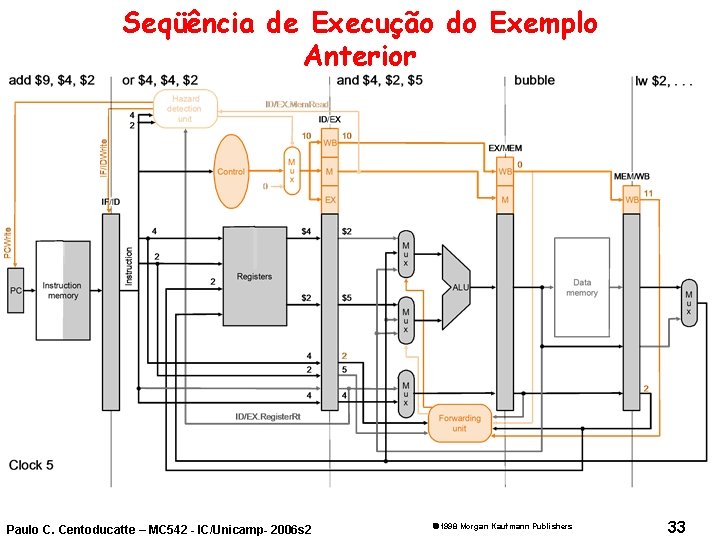

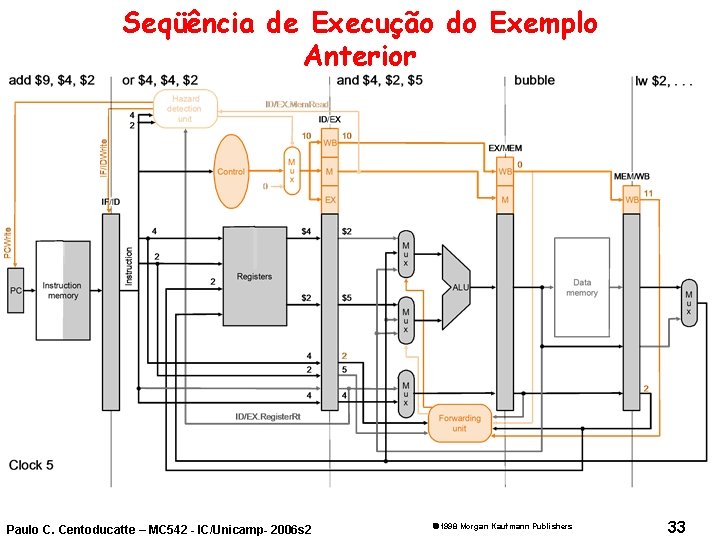

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 33

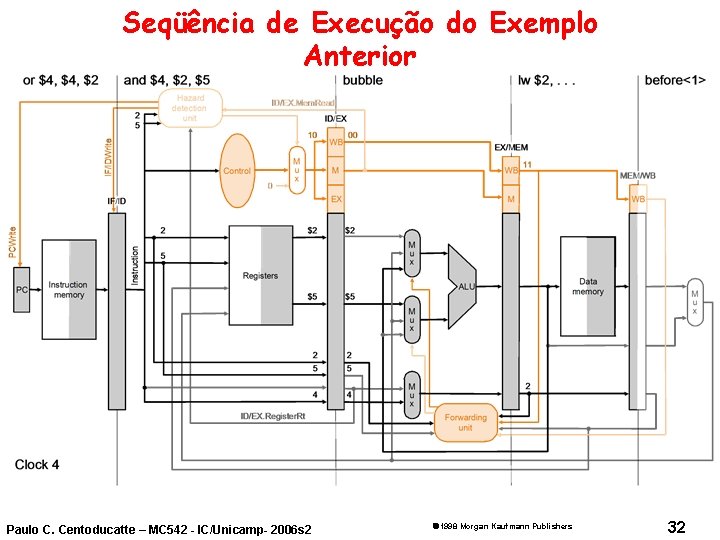

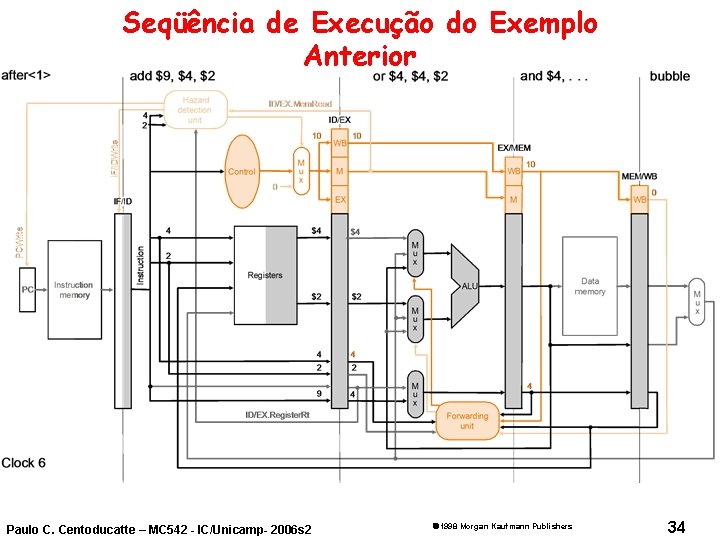

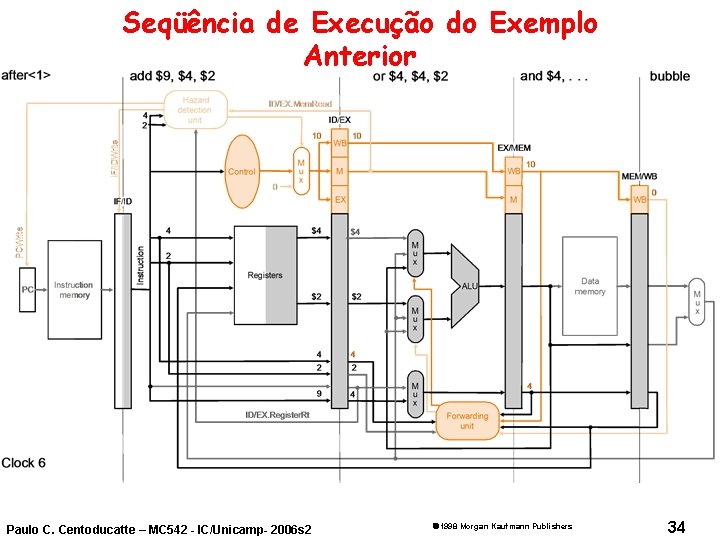

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 34

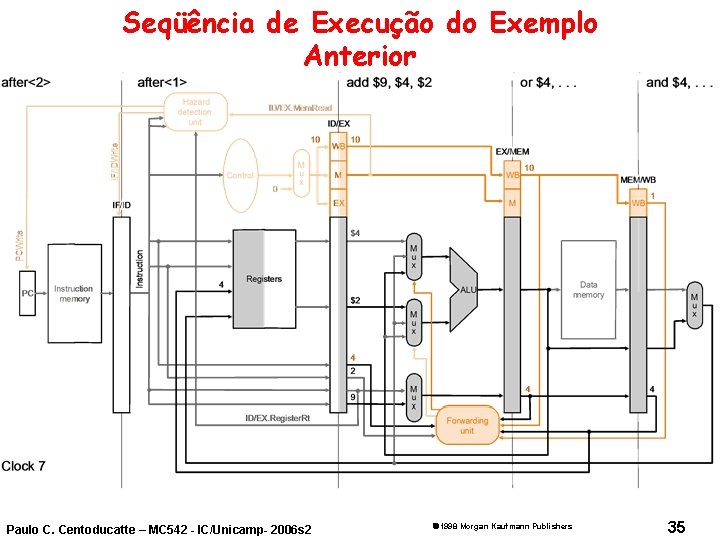

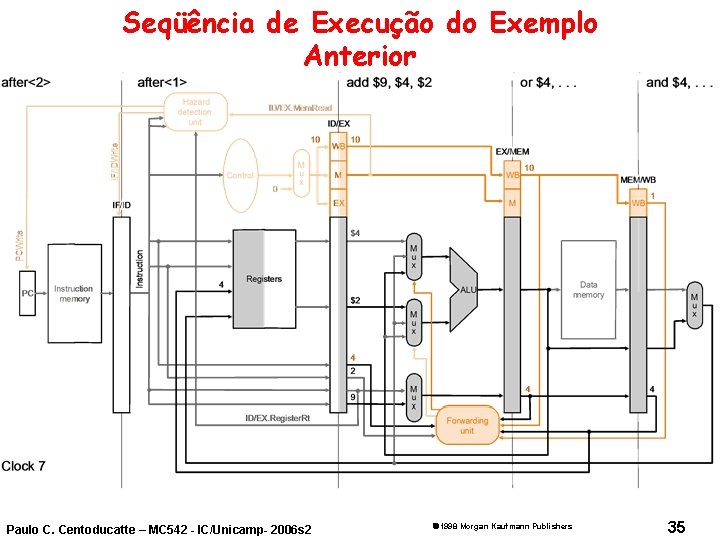

Seqüência de Execução do Exemplo Anterior Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 35

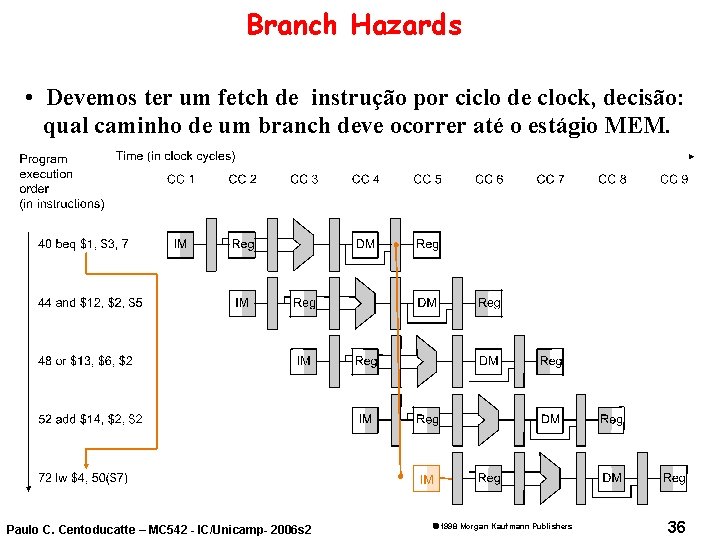

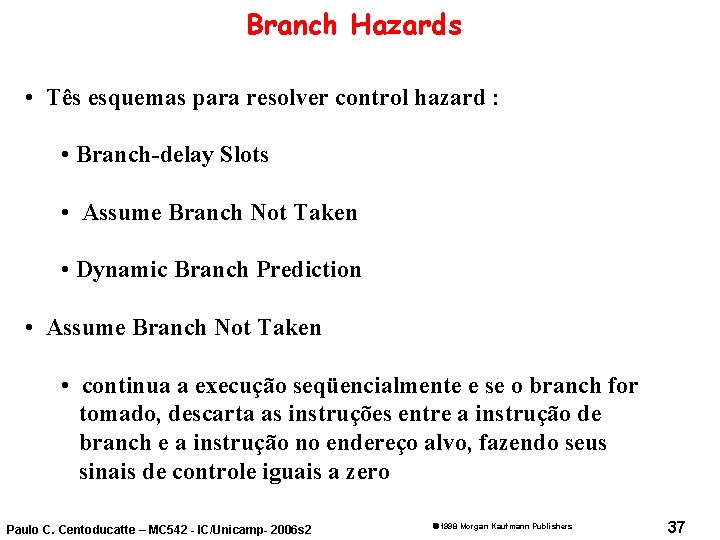

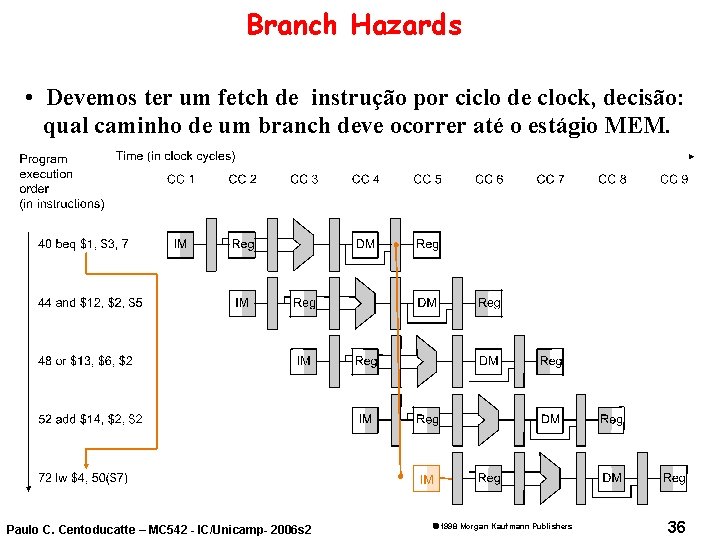

Branch Hazards • Devemos ter um fetch de instrução por ciclo de clock, decisão: qual caminho de um branch deve ocorrer até o estágio MEM. Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 36

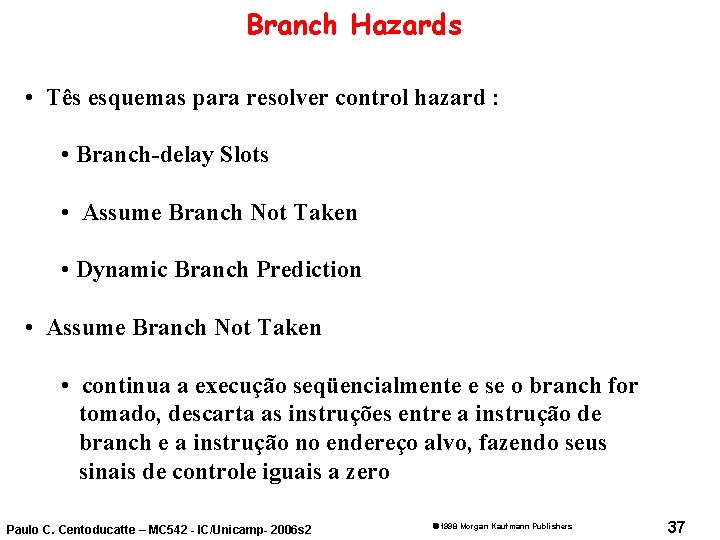

Branch Hazards • Tês esquemas para resolver control hazard : • Branch-delay Slots • Assume Branch Not Taken • Dynamic Branch Prediction • Assume Branch Not Taken • continua a execução seqüencialmente e se o branch for tomado, descarta as instruções entre a instrução de branch e a instrução no endereço alvo, fazendo seus sinais de controle iguais a zero Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 37

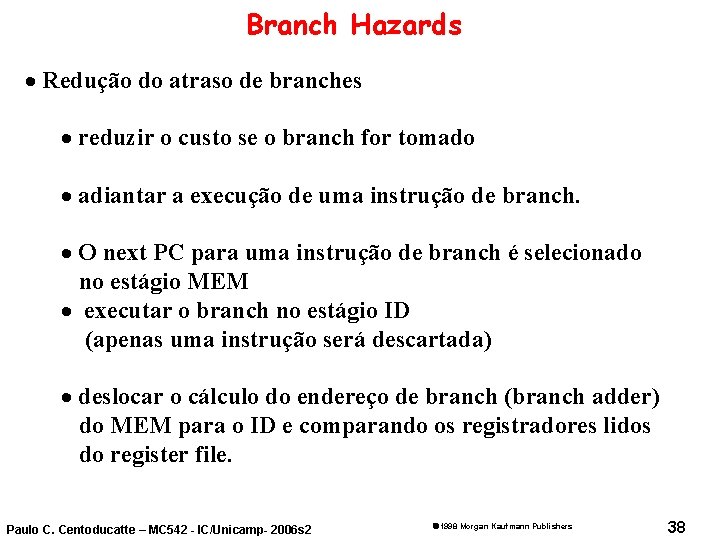

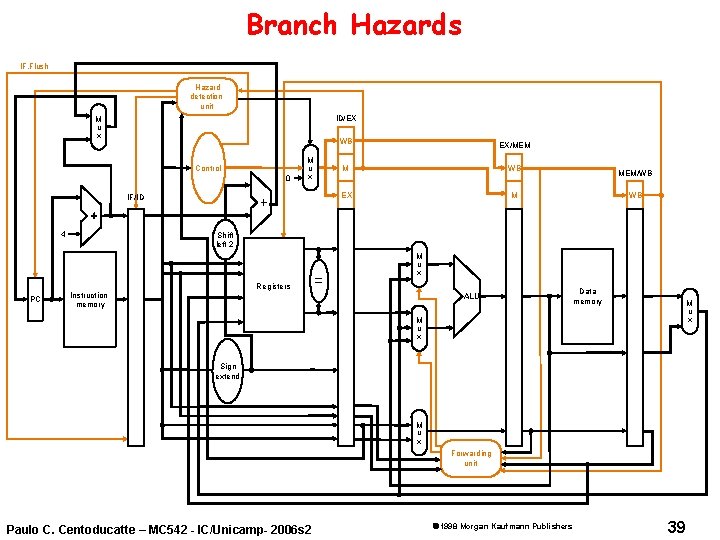

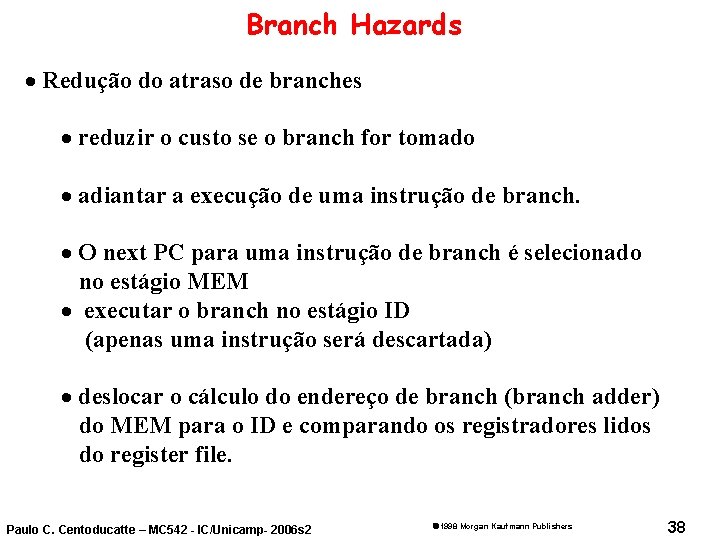

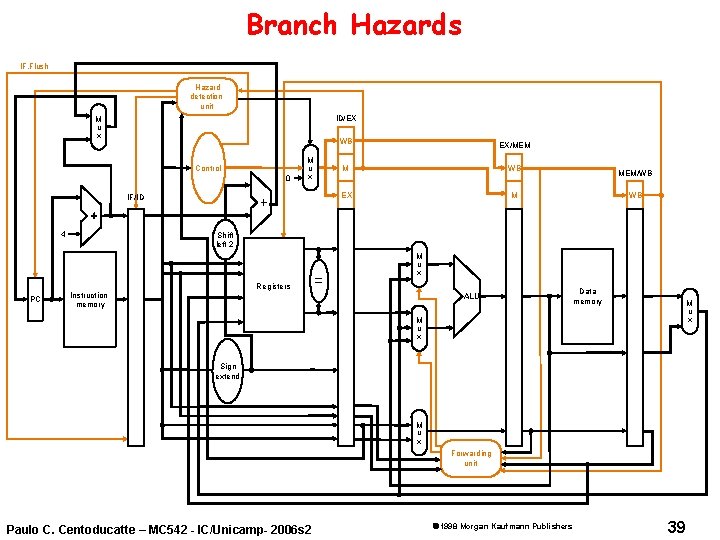

Branch Hazards · Redução do atraso de branches · reduzir o custo se o branch for tomado · adiantar a execução de uma instrução de branch. · O next PC para uma instrução de branch é selecionado no estágio MEM · executar o branch no estágio ID (apenas uma instrução será descartada) · deslocar o cálculo do endereço de branch (branch adder) do MEM para o ID e comparando os registradores lidos do register file. Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 38

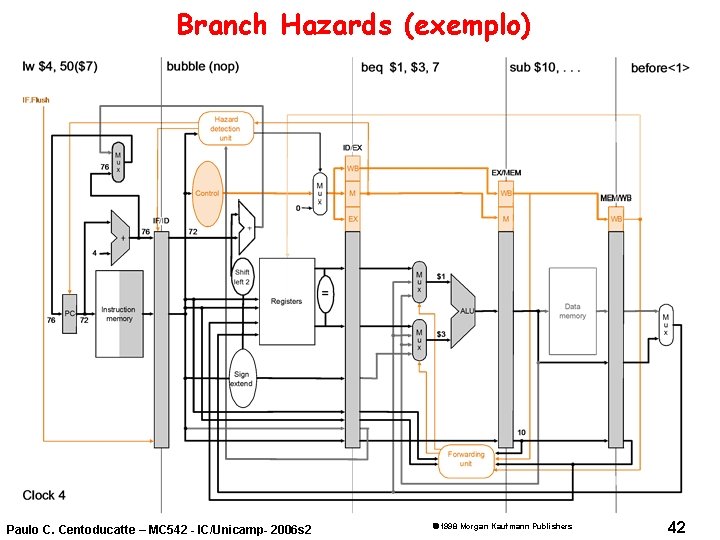

Branch Hazards IF. Flush Hazard detection unit ID/EX M u x WB Control 0 M u x IF/ID 4 PC EX/MEM M WB EX M MEM/WB WB Shift left 2 Registers Instruction memory = M u x ALU Data memory M u x Sign extend M u x Forwarding unit Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 39

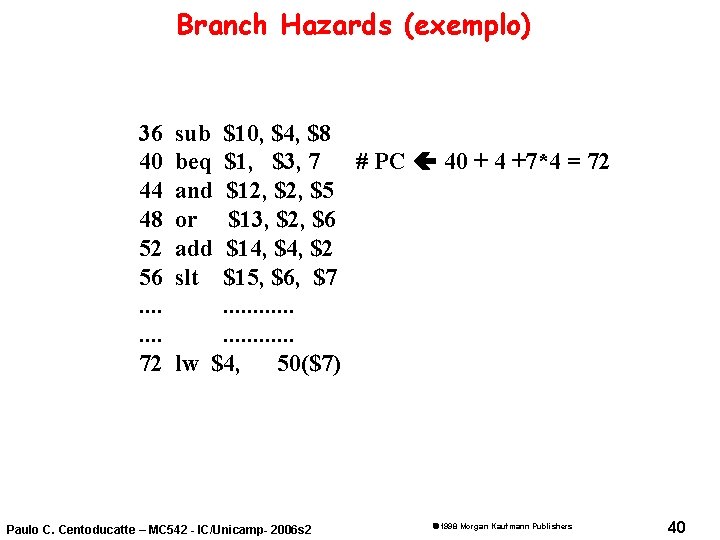

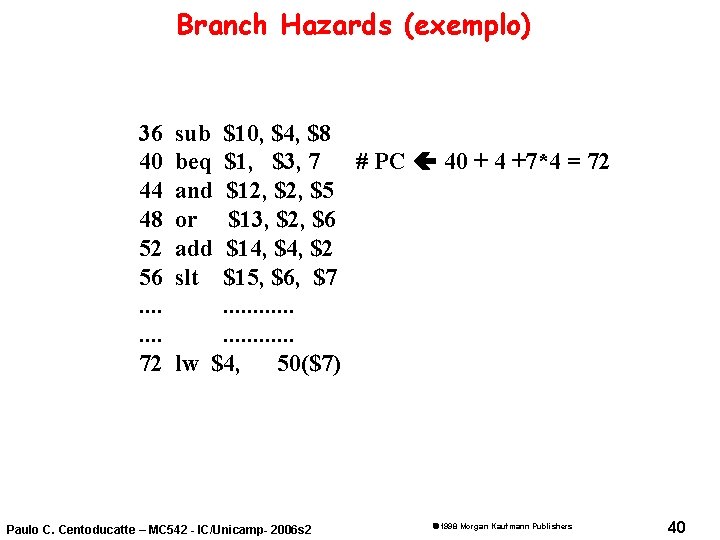

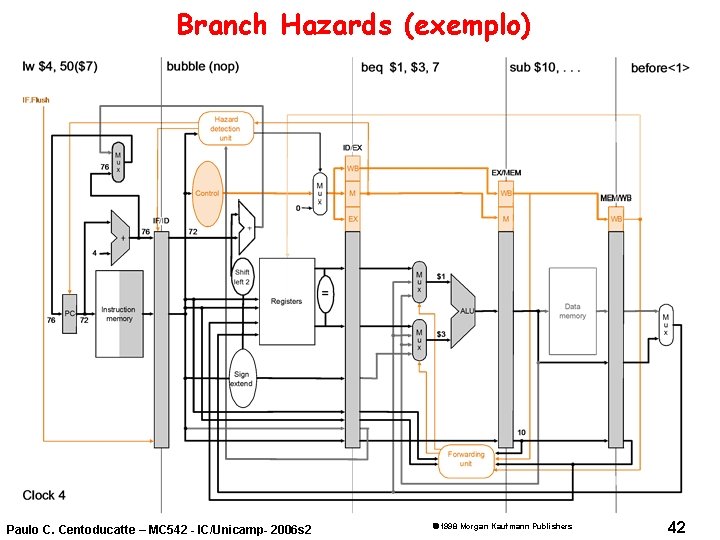

Branch Hazards (exemplo) 36 40 44 48 52 56. . . . 72 sub beq and or add slt $10, $4, $8 $1, $3, 7 # PC 40 + 4 +7*4 = 72 $12, $5 $13, $2, $6 $14, $2 $15, $6, $7. . . lw $4, 50($7) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 40

Branch Hazards (exemplo) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 41

Branch Hazards (exemplo) Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 42

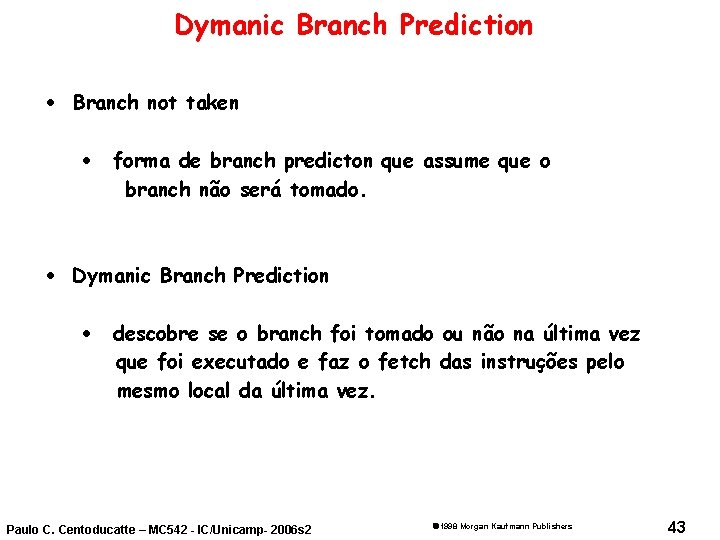

Dymanic Branch Prediction · Branch not taken · forma de branch predicton que assume que o branch não será tomado. · Dymanic Branch Prediction · descobre se o branch foi tomado ou não na última vez que foi executado e faz o fetch das instruções pelo mesmo local da última vez. Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 43

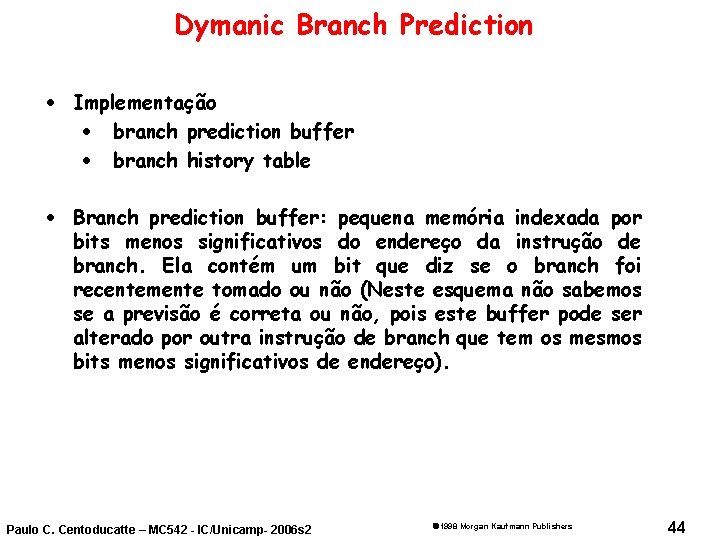

Dymanic Branch Prediction · Implementação · branch prediction buffer · branch history table · Branch prediction buffer: pequena memória indexada por bits menos significativos do endereço da instrução de branch. Ela contém um bit que diz se o branch foi recentemente tomado ou não (Neste esquema não sabemos se a previsão é correta ou não, pois este buffer pode ser alterado por outra instrução de branch que tem os mesmos bits menos significativos de endereço). Paulo C. Centoducatte – MC 542 - IC/Unicamp- 2006 s 2 1998 Morgan Kaufmann Publishers 44