PUCRS Faculdade de Engenharia DISPOSITIVO LGICO PROGRAMVEL FPGA

- Slides: 110

PUCRS Faculdade de Engenharia DISPOSITIVO LÓGICO PROGRAMÁVEL (FPGA) LINGUAGEM DE DESCRIÇÃO DE HARDWARE (VHDL) Prof. Anderson Royes Terroso Abril, 2000.

FPGA & VHDL Tópicos 1 - Dispositivos Programáveis (FPGA) – 1. 1 Introdução – 1. 2 Estrutura da FPGA – 1. 3 Tipos de FPGA – 1. 4 Técnicas de programação 2 - Linguagem de Descrição de Hardware (VHDL) – 2. 1 Introdução • 2. 1. 1 O que é VHDL terroso@ee. pucrs. br sisc-l@ee. pucrs. br http: //www. ee. pucrs. br/~terroso http: //www. ee. pucrs. br/~sisc 2

• 2. 1. 2 O que significa VHDL • 2. 1. 3 O que significa uma Linguagem de Descrição de Hardware • 2. 1. 4 Breve Histórico • 2. 1. 5 Vantagens e Desvantagens de se utilizar VHDL – 2. 2 Componentes de um projeto VHDL • • 2. 2. 1 Package 2. 2. 2 Entity 2. 2. 3 Architecture 2. 2. 4 Configuration – 2. 3 Semântica da Linguagem • 2. 3. 1 Elementos Léxicos – Comentários, Identificadores, tipos de dados não lógicos, expressões e operadores 3

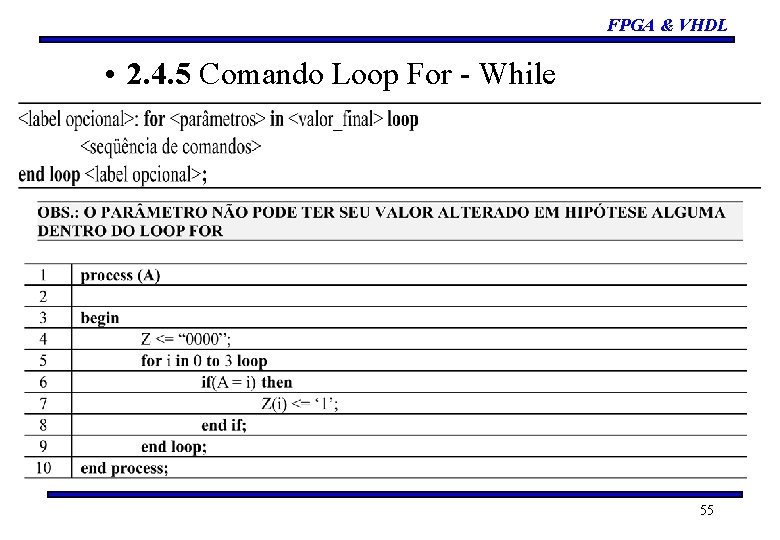

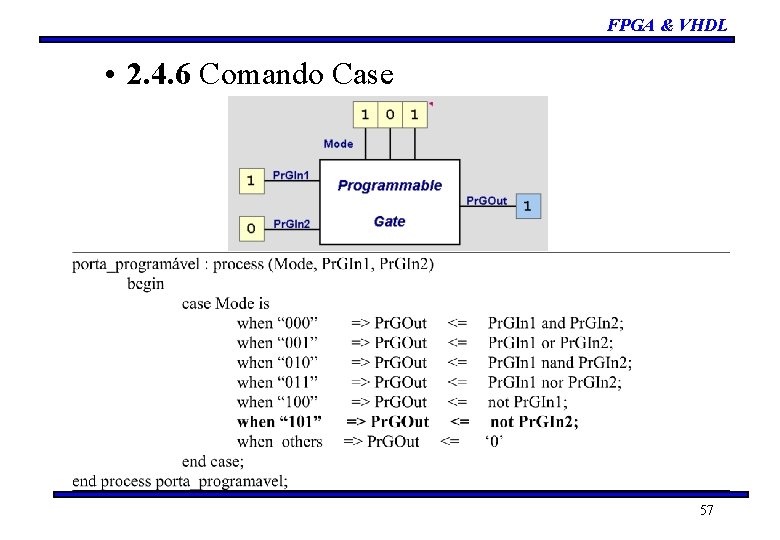

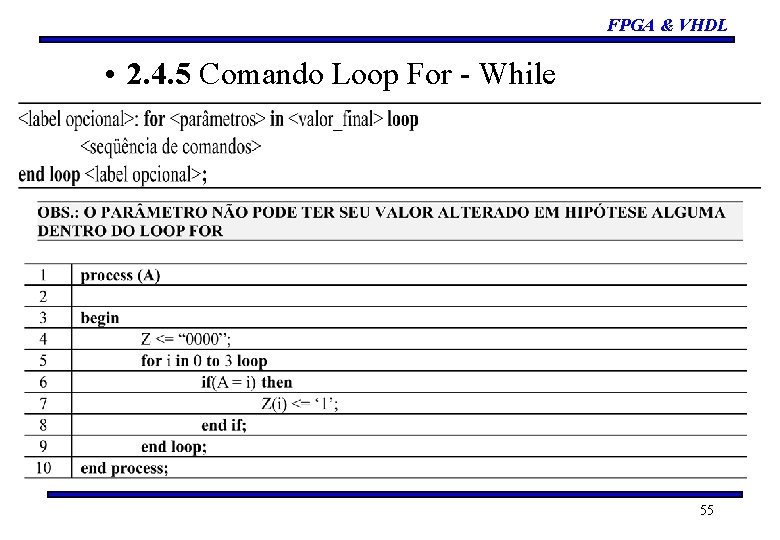

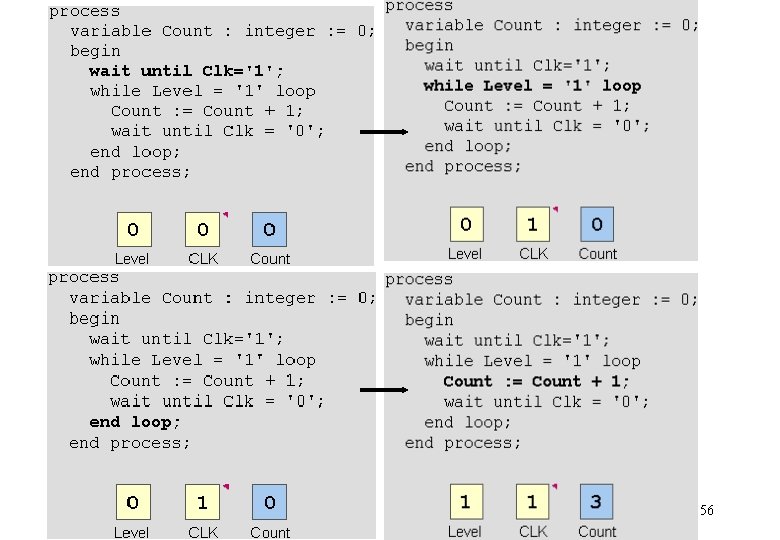

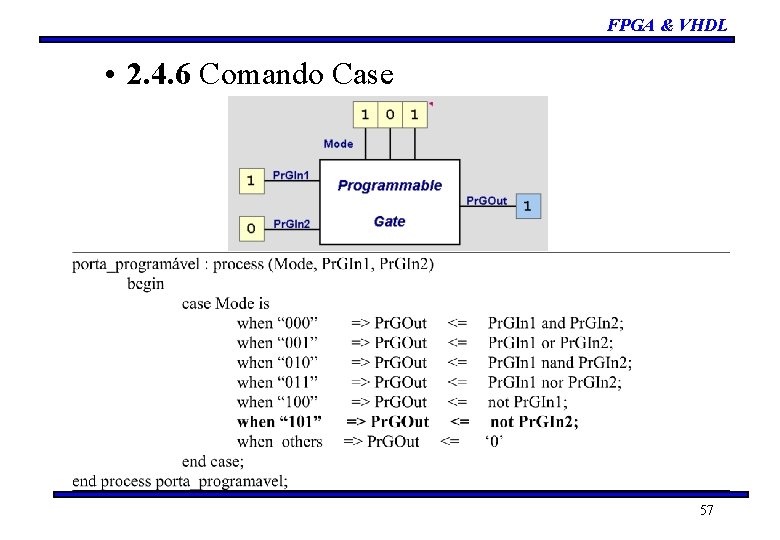

– 2. 4 Comandos Seqüênciais • • • 2. 4. 1 Atribuição de Variáveis 2. 4. 2 Atribuição de Sinais 2. 4. 3 Comando Wait 2. 4. 4 Comando If - Then - Else 2. 4. 5 Comando Loop For - While 2. 4. 6 Comando Case – 2. 5 Especificando a Estrutura de um Sistema – 2. 6 Exemplos de Circuitos Digitais utilizando a ferramenta MAX PLUS II – 2. 7 Placa University Program ALTERA • Exemplos práticos – 2. 8 Bibliografia 4

OBJETIVO CKT ESQUEMÁTICO E/OU VHDL PROTOTIPAGEM EM FPGA 5

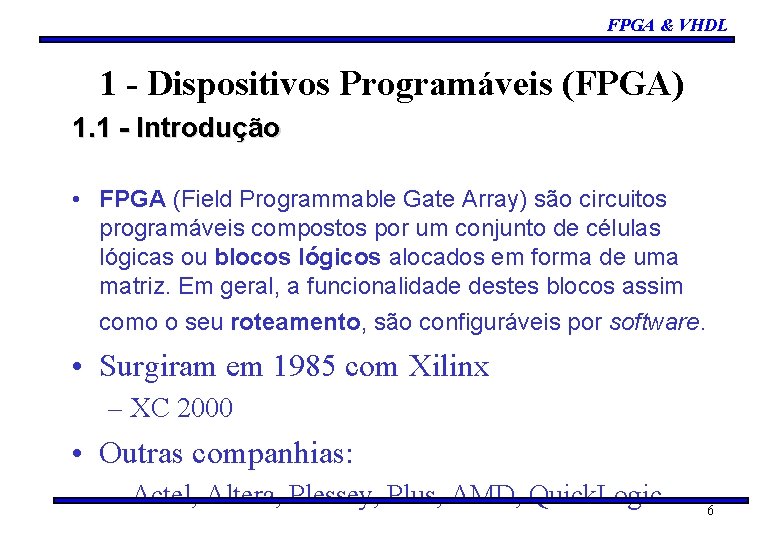

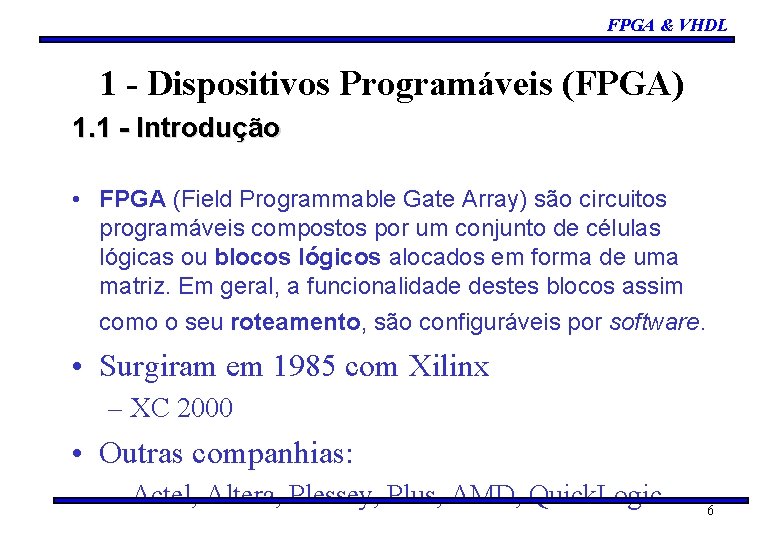

FPGA & VHDL 1 - Dispositivos Programáveis (FPGA) 1. 1 - Introdução • FPGA (Field Programmable Gate Array) são circuitos programáveis compostos por um conjunto de células lógicas ou blocos lógicos alocados em forma de uma matriz. Em geral, a funcionalidade destes blocos assim como o seu roteamento, são configuráveis por software. • Surgiram em 1985 com Xilinx – XC 2000 • Outras companhias: – Actel, Altera, Plessey, Plus, AMD, Quick. Logic 6

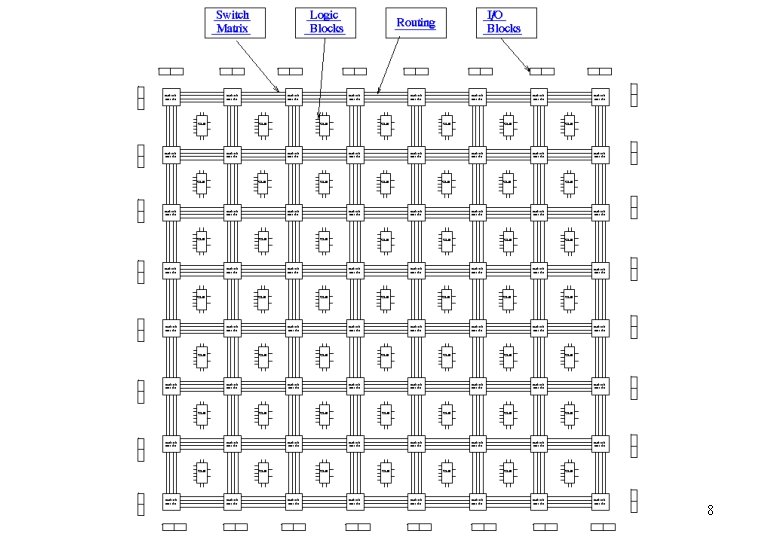

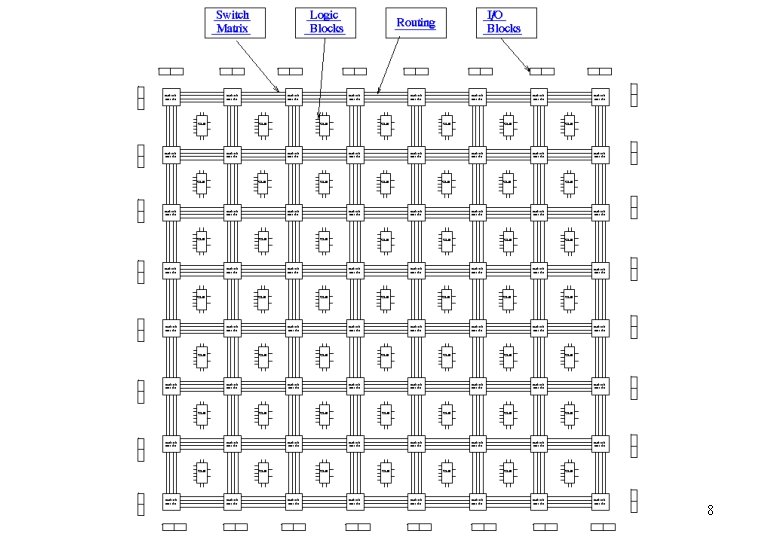

FPGA & VHDL 1. 2 - Estrutura da FPGA • Três elementos básicos: – CLB’s (Configurable Logic Block): Blocos Lógicos Configuráveis; – IOB’s (In/Out Block): Blocos de entrada e saída; – SB’s (Switch Box): Caixa de conexão; 7

8

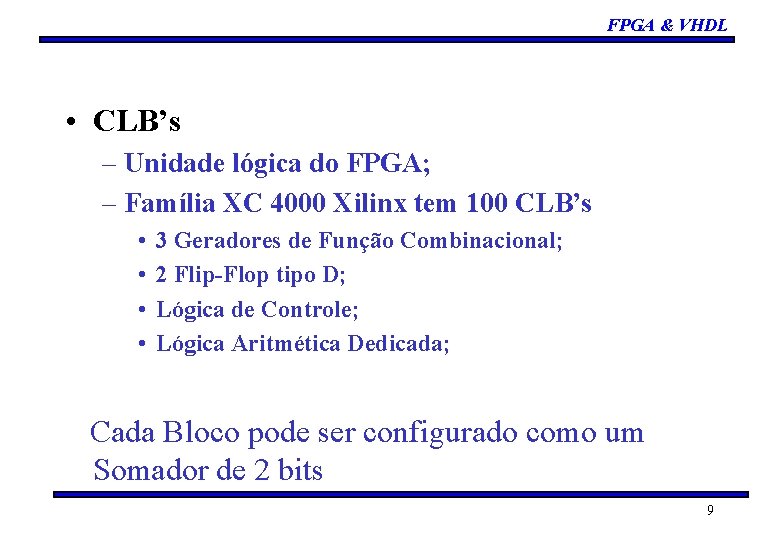

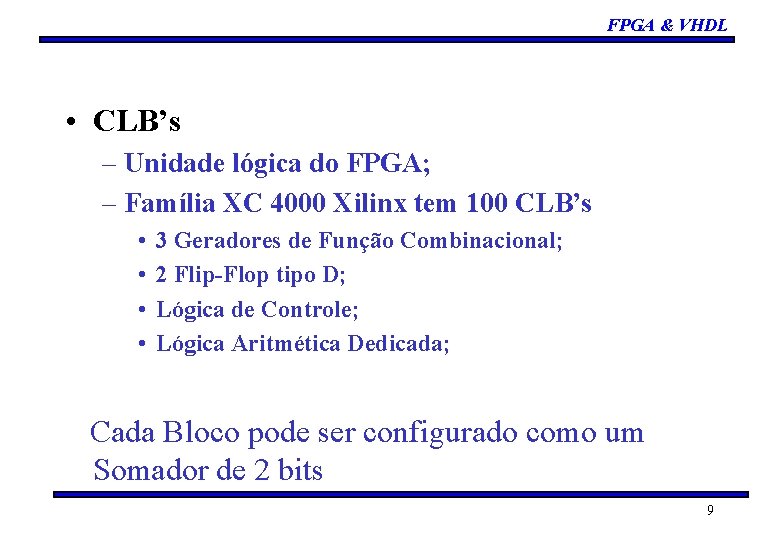

FPGA & VHDL • CLB’s – Unidade lógica do FPGA; – Família XC 4000 Xilinx tem 100 CLB’s • • 3 Geradores de Função Combinacional; 2 Flip-Flop tipo D; Lógica de Controle; Lógica Aritmética Dedicada; Cada Bloco pode ser configurado como um Somador de 2 bits 9

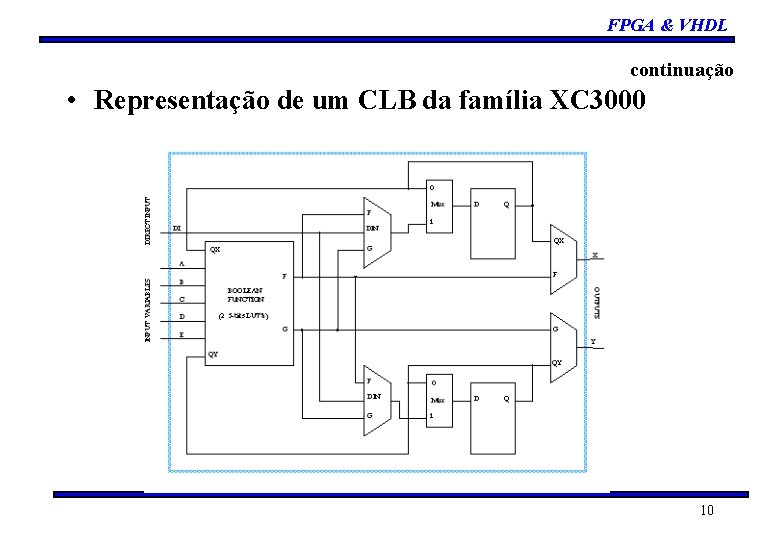

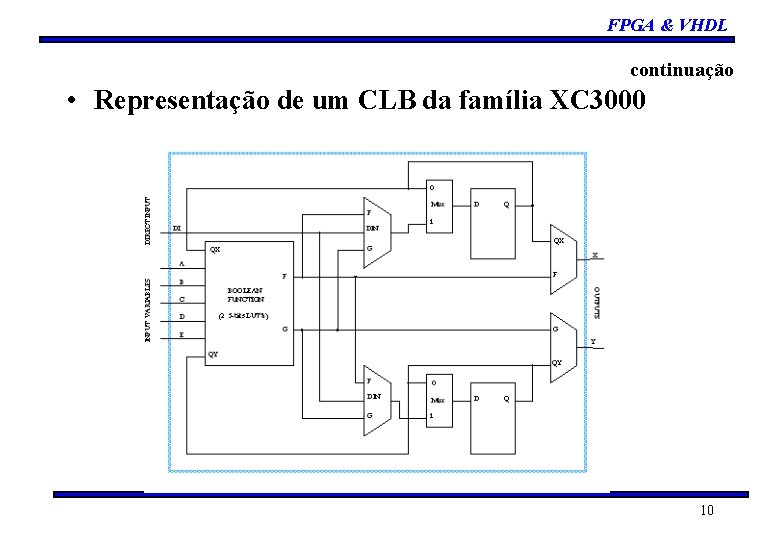

FPGA & VHDL continuação • Representação de um CLB da família XC 3000 10

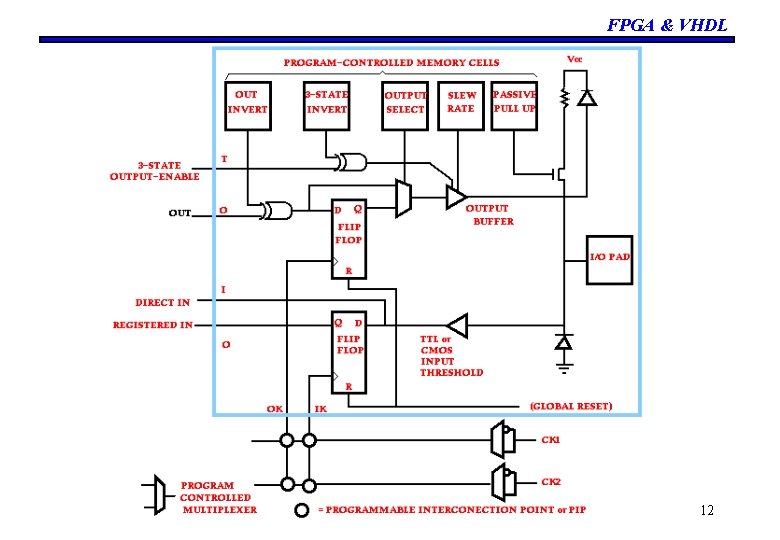

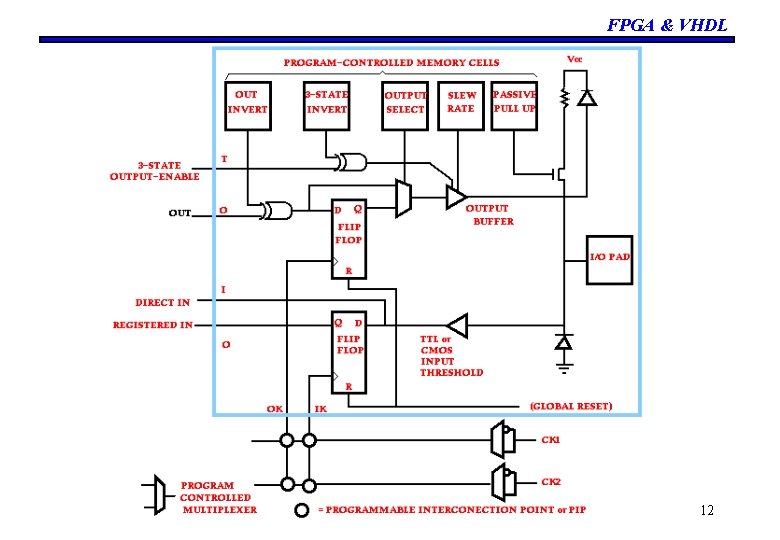

FPGA & VHDL continuação • IOB’s – Interface entre uma FPGA e o resto do sistema; – O FPGA XC 4003 Xilinx tem 80 IOB’s – Localizam na periferia do chip; 11

FPGA & VHDL 12

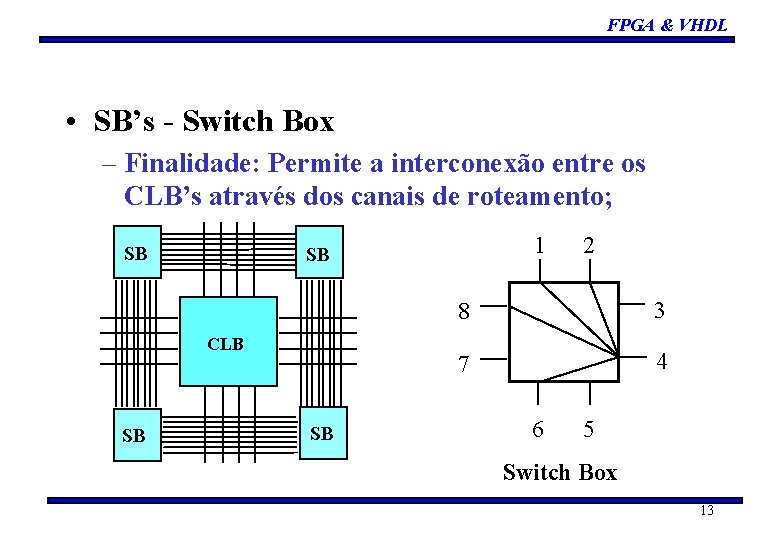

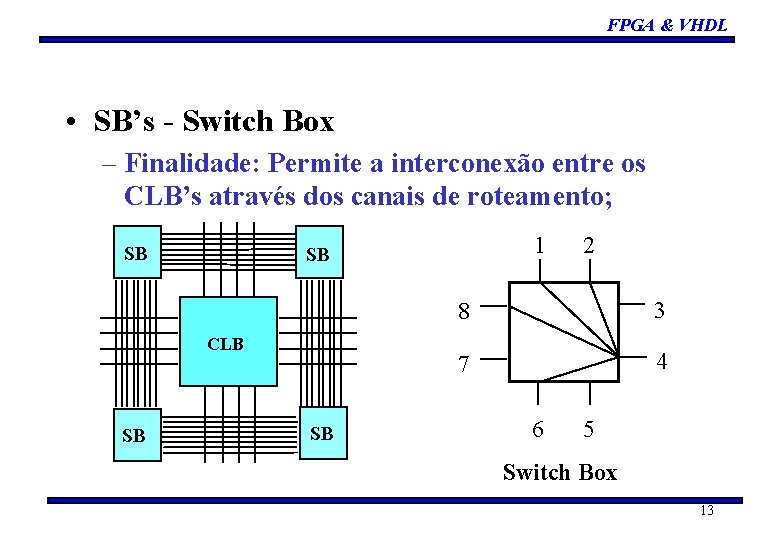

FPGA & VHDL • SB’s - Switch Box – Finalidade: Permite a interconexão entre os CLB’s através dos canais de roteamento; SB CLB SB 1 SB SB 2 8 3 7 4 6 5 Switch Box 13

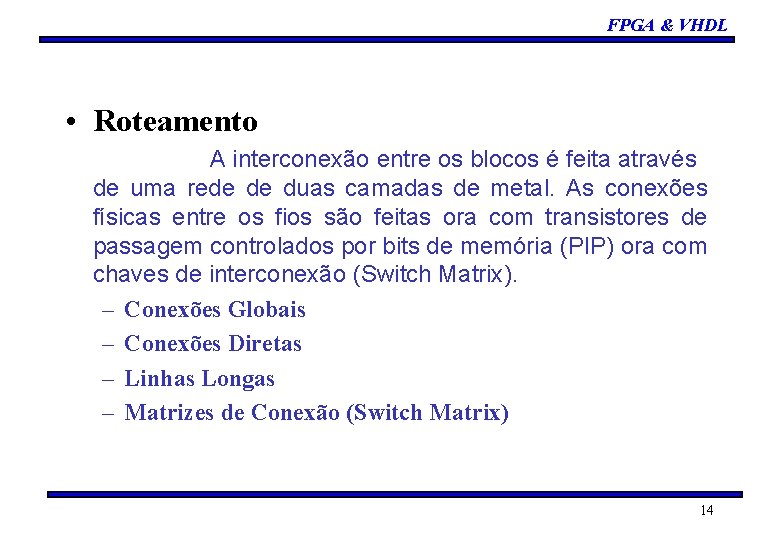

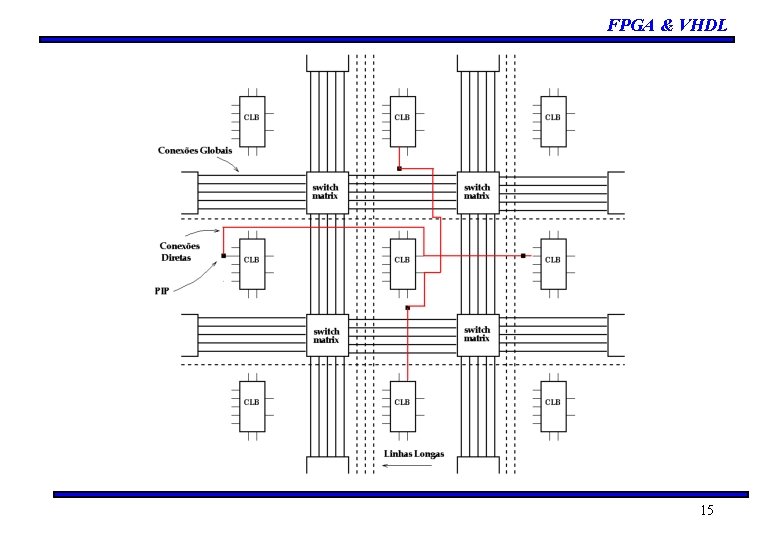

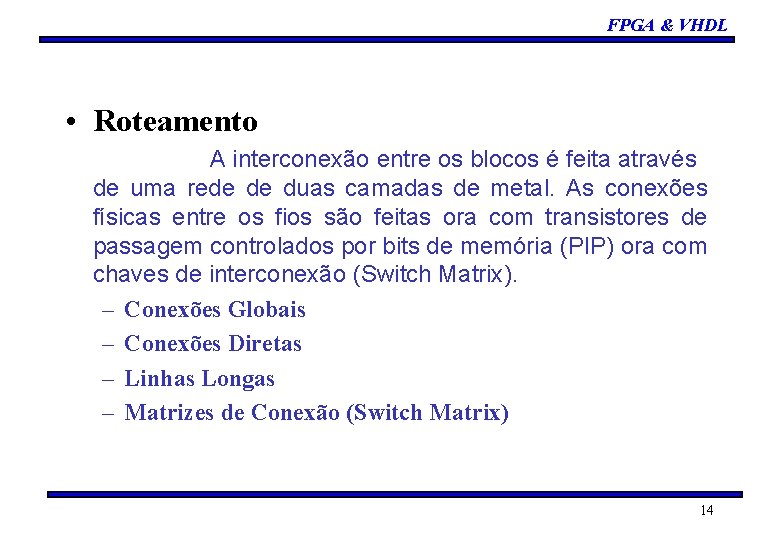

FPGA & VHDL • Roteamento A interconexão entre os blocos é feita através de uma rede de duas camadas de metal. As conexões físicas entre os fios são feitas ora com transistores de passagem controlados por bits de memória (PIP) ora com chaves de interconexão (Switch Matrix). – Conexões Globais – Conexões Diretas – Linhas Longas – Matrizes de Conexão (Switch Matrix) 14

FPGA & VHDL 15

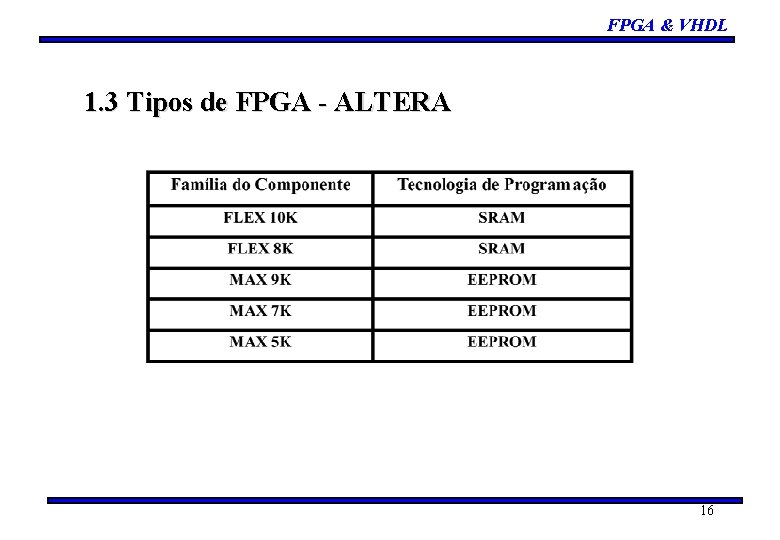

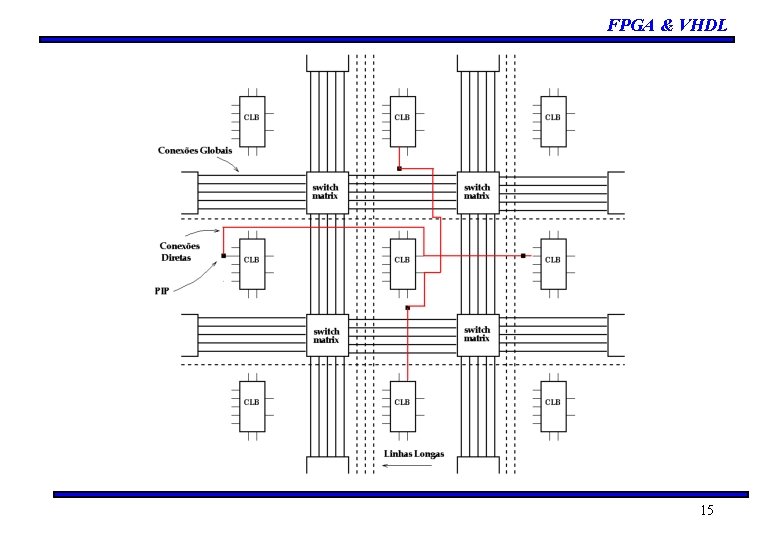

FPGA & VHDL 1. 3 Tipos de FPGA - ALTERA 16

FPGA & VHDL 1. 4 Técnicas de programação • Esquemático • VHDL • AHDL • Handel C 17

MAX+PLUS II - SOFTWARE QUE PERMITE O PROJETO AO NÍVEL DE ESQUEMÁTICO E VHDL. 18

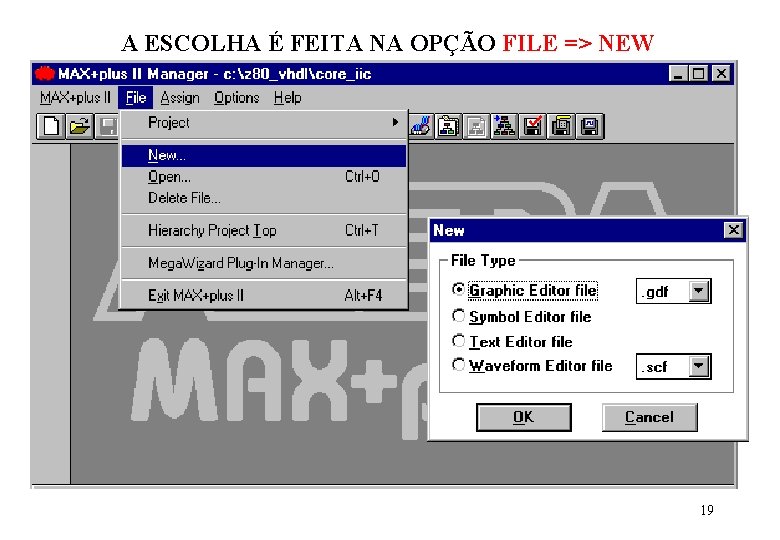

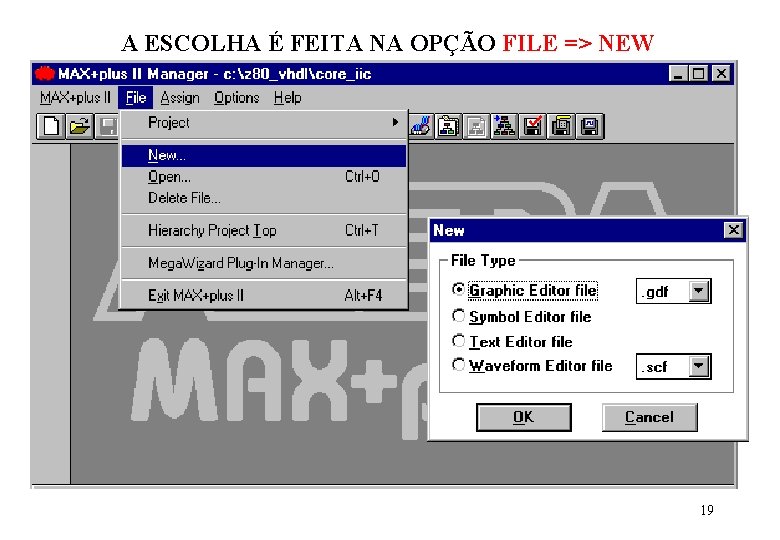

A ESCOLHA É FEITA NA OPÇÃO FILE => NEW 19

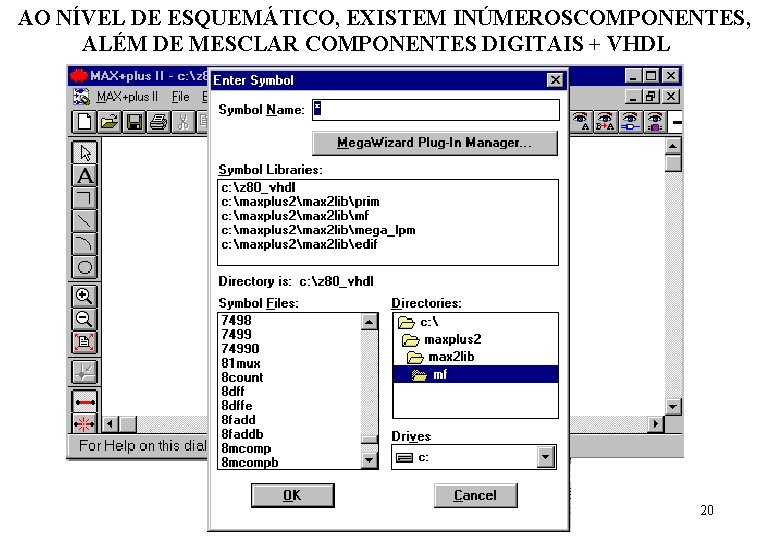

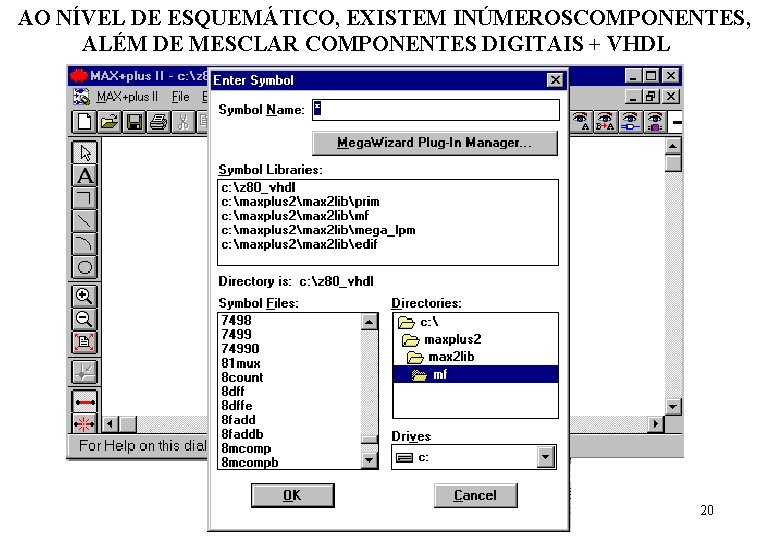

AO NÍVEL DE ESQUEMÁTICO, EXISTEM INÚMEROSCOMPONENTES, ALÉM DE MESCLAR COMPONENTES DIGITAIS + VHDL 20

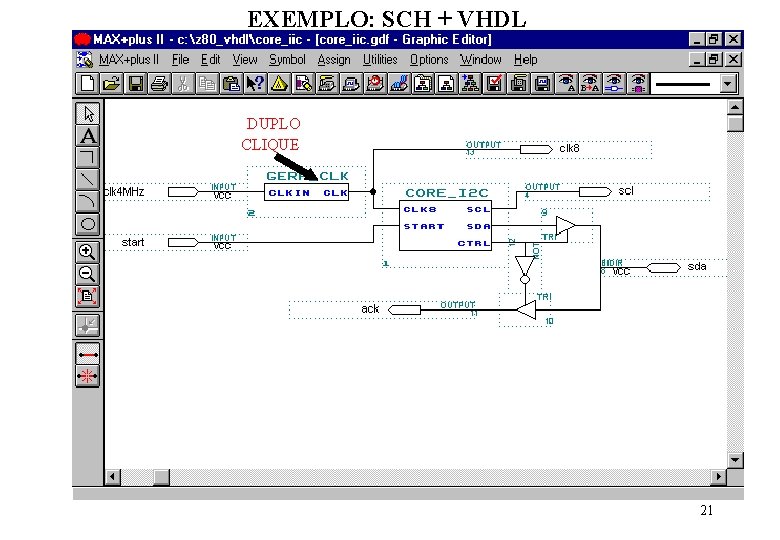

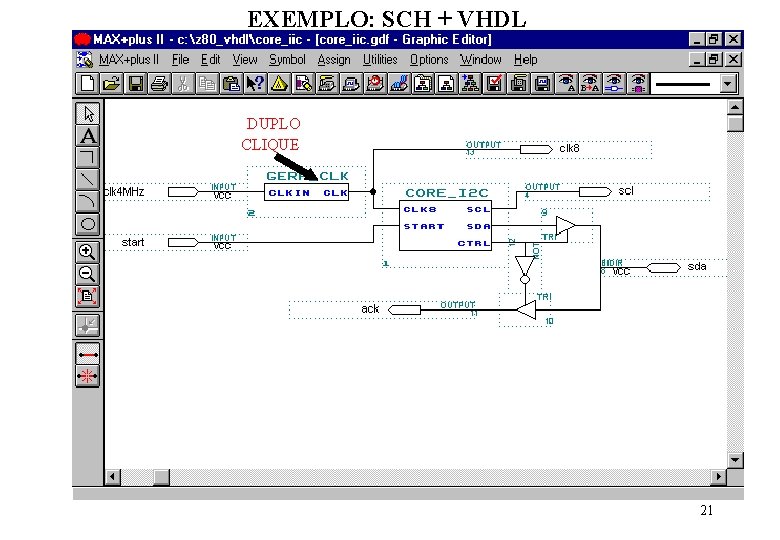

EXEMPLO: SCH + VHDL DUPLO CLIQUE 21

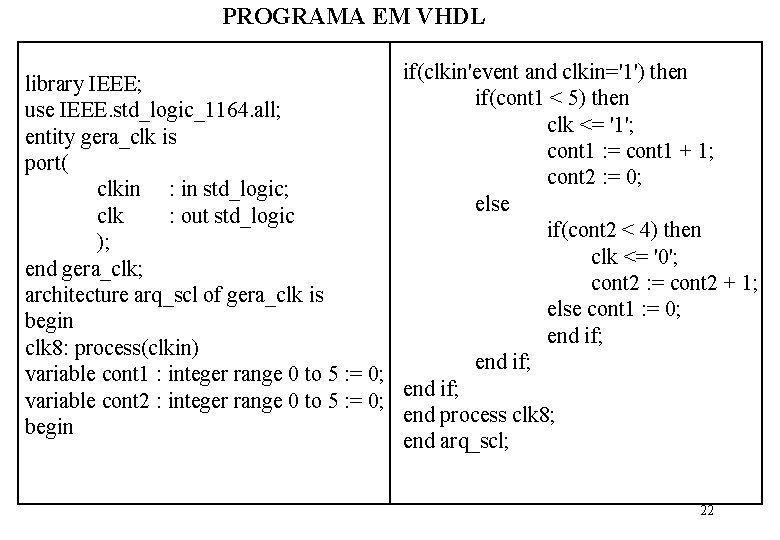

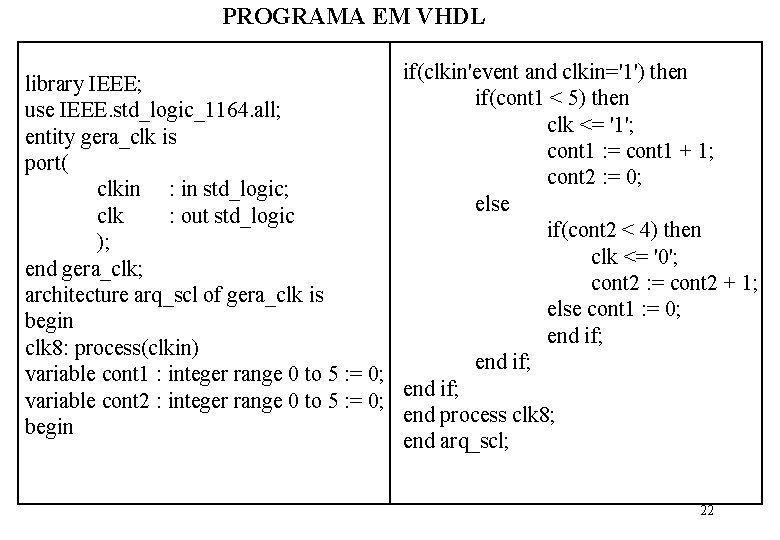

PROGRAMA EM VHDL if(clkin'event and clkin='1') then library IEEE; if(cont 1 < 5) then use IEEE. std_logic_1164. all; clk <= '1'; entity gera_clk is cont 1 : = cont 1 + 1; port( cont 2 : = 0; clkin : in std_logic; else clk : out std_logic if(cont 2 < 4) then ); clk <= '0'; end gera_clk; cont 2 : = cont 2 + 1; architecture arq_scl of gera_clk is else cont 1 : = 0; begin end if; clk 8: process(clkin) end if; variable cont 1 : integer range 0 to 5 : = 0; end if; variable cont 2 : integer range 0 to 5 : = 0; end process clk 8; begin end arq_scl; 22

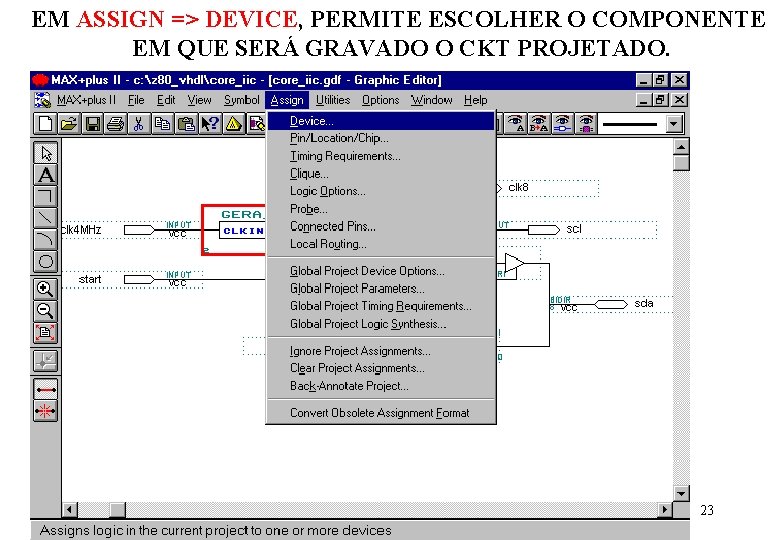

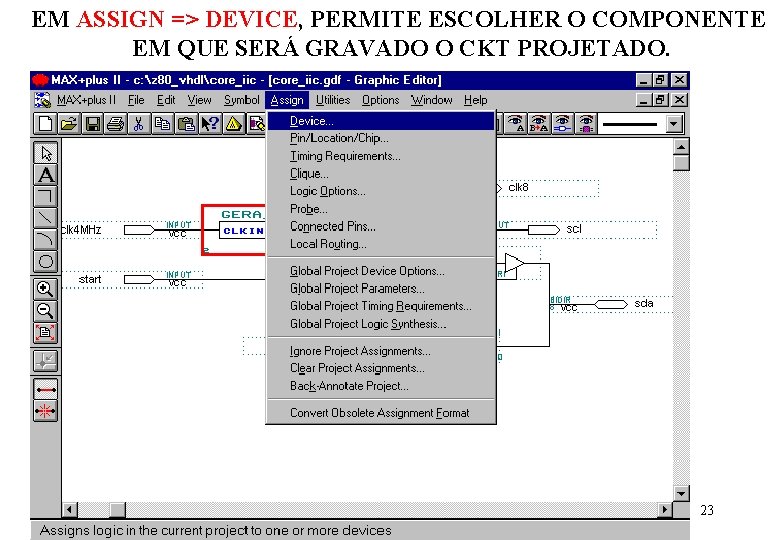

EM ASSIGN => DEVICE, PERMITE ESCOLHER O COMPONENTE EM QUE SERÁ GRAVADO O CKT PROJETADO. 23

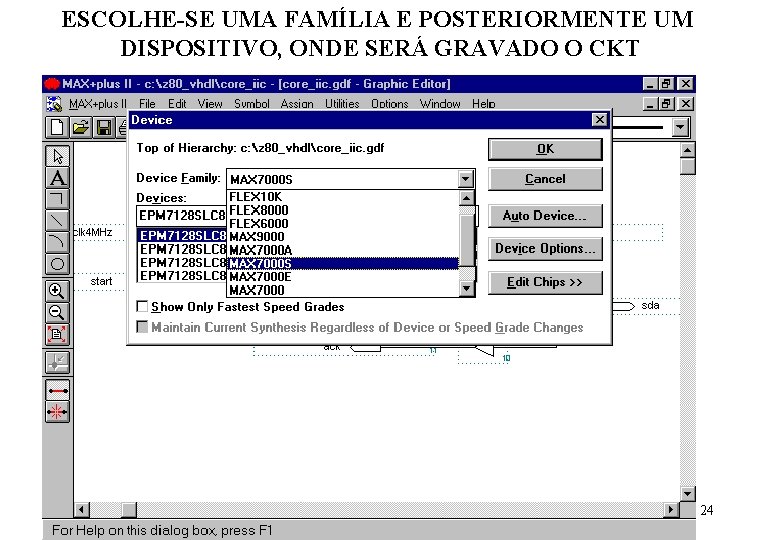

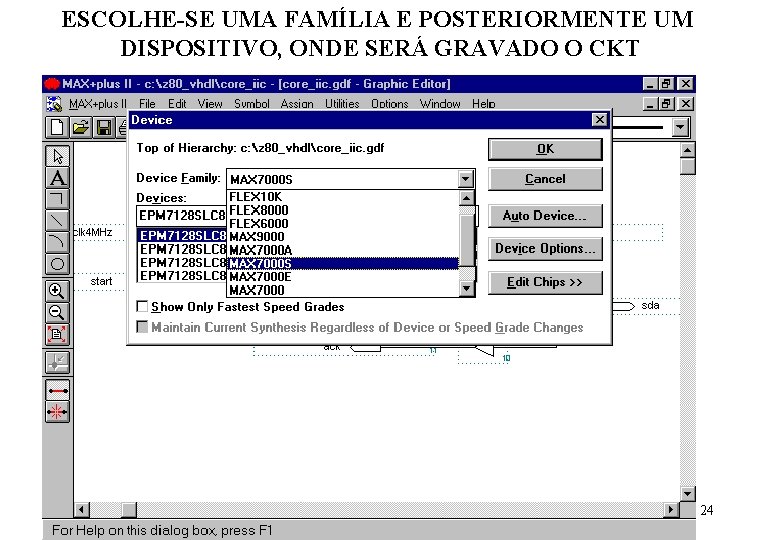

ESCOLHE-SE UMA FAMÍLIA E POSTERIORMENTE UM DISPOSITIVO, ONDE SERÁ GRAVADO O CKT 24

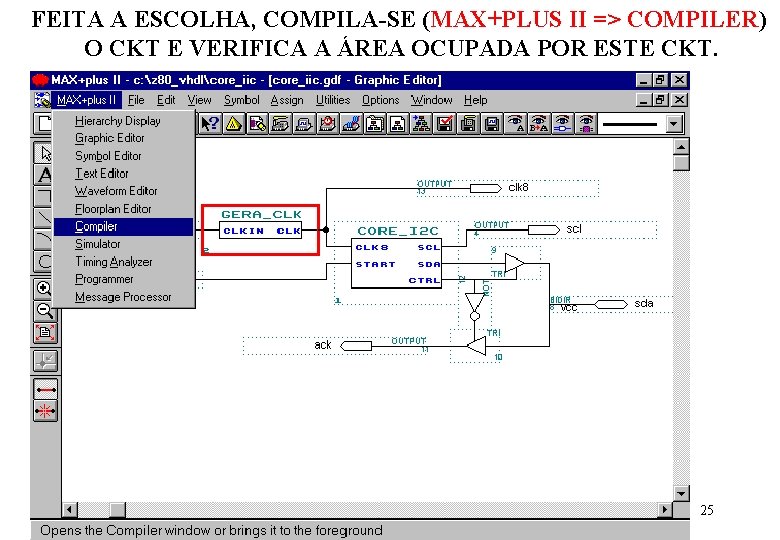

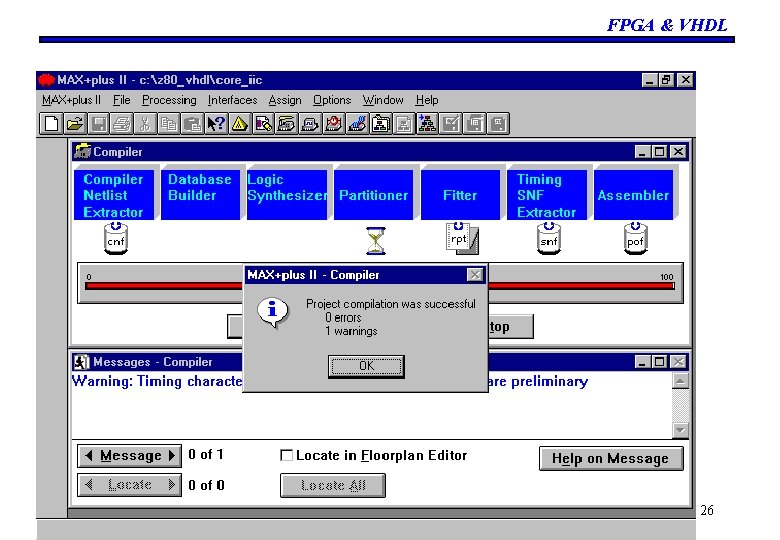

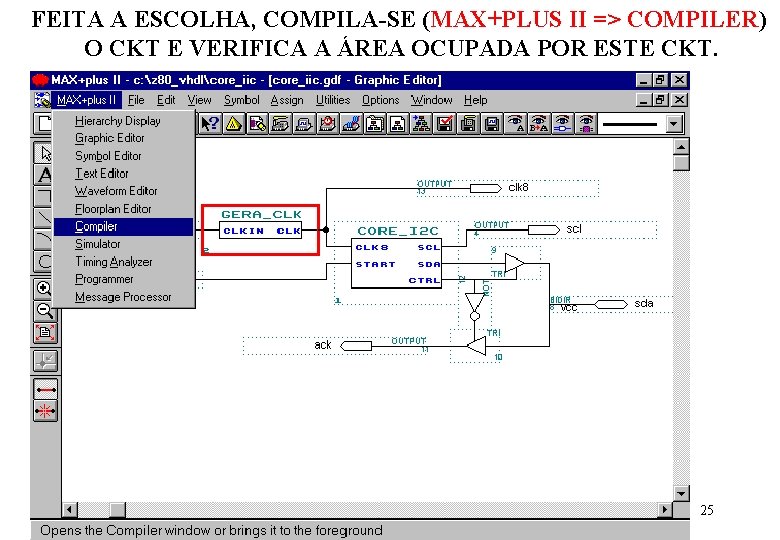

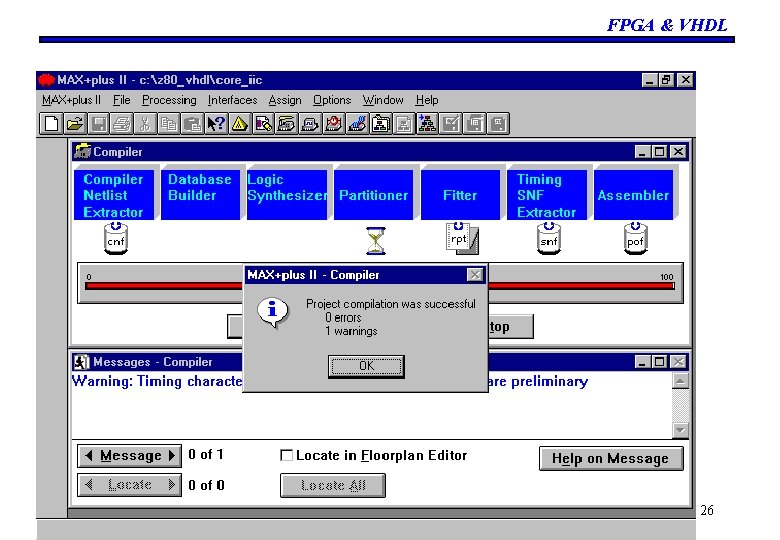

FEITA A ESCOLHA, COMPILA-SE (MAX+PLUS II => COMPILER) O CKT E VERIFICA A ÁREA OCUPADA POR ESTE CKT. 25

FPGA & VHDL 26

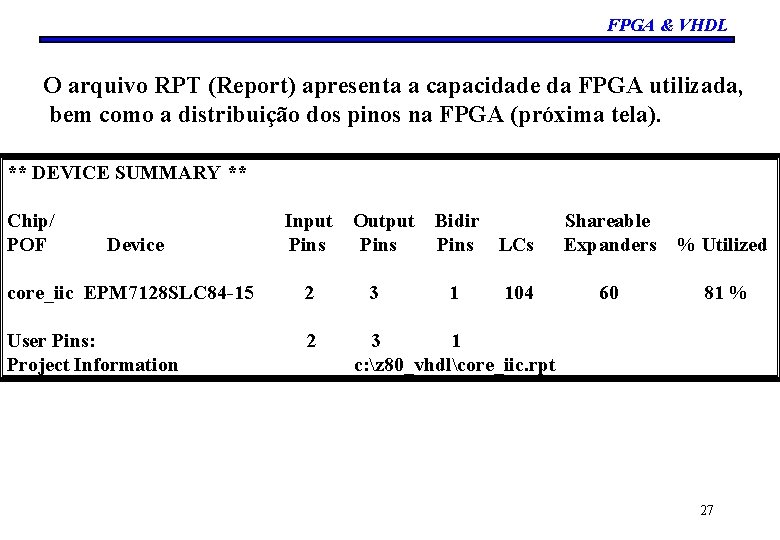

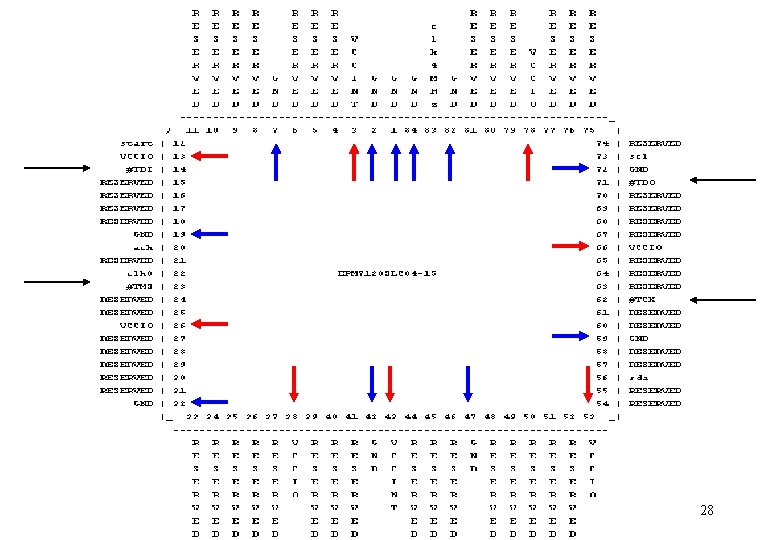

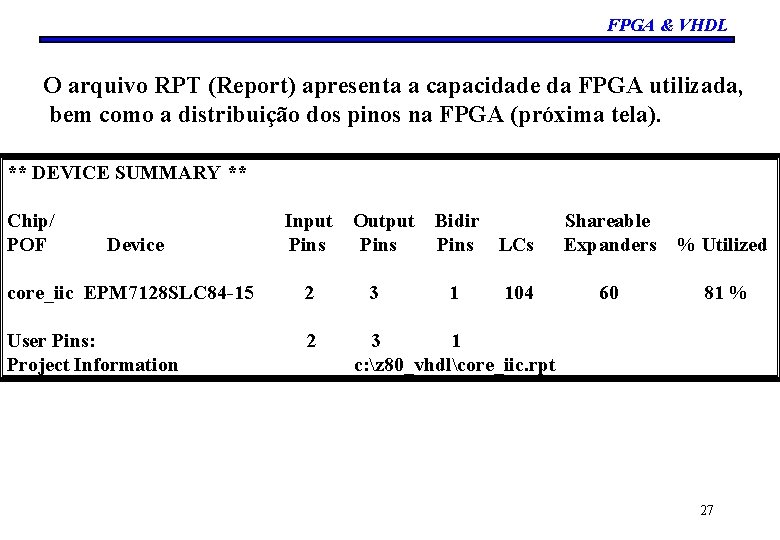

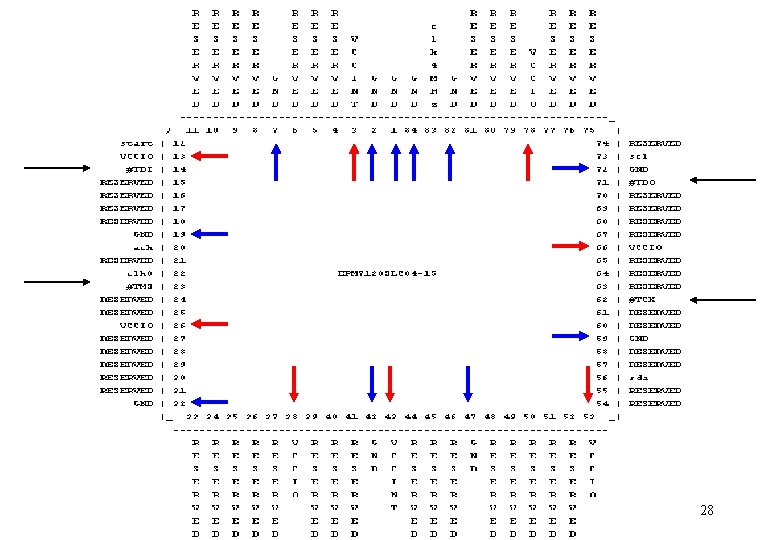

FPGA & VHDL O arquivo RPT (Report) apresenta a capacidade da FPGA utilizada, bem como a distribuição dos pinos na FPGA (próxima tela). ** DEVICE SUMMARY ** Chip/ POF Device Input Pins core_iic EPM 7128 SLC 84 -15 2 User Pins: Project Information 2 Output Pins 3 Bidir Pins LCs 1 104 Shareable Expanders % Utilized 60 81 % 3 1 c: z 80_vhdlcore_iic. rpt 27

28

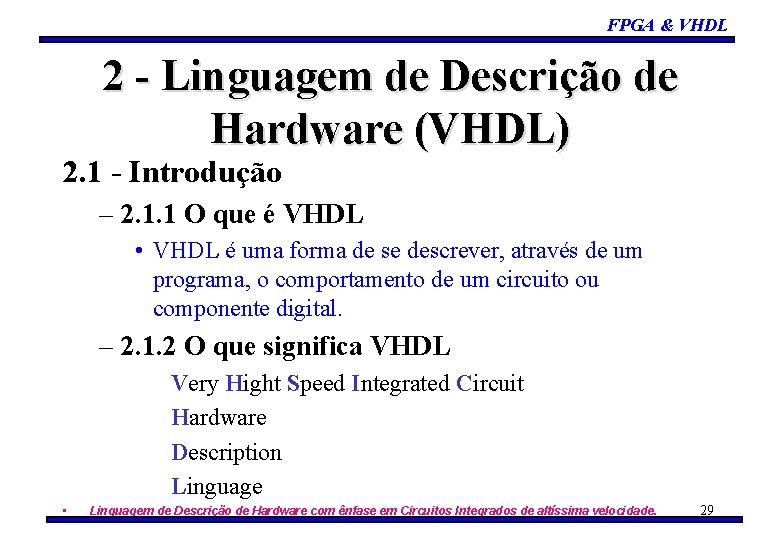

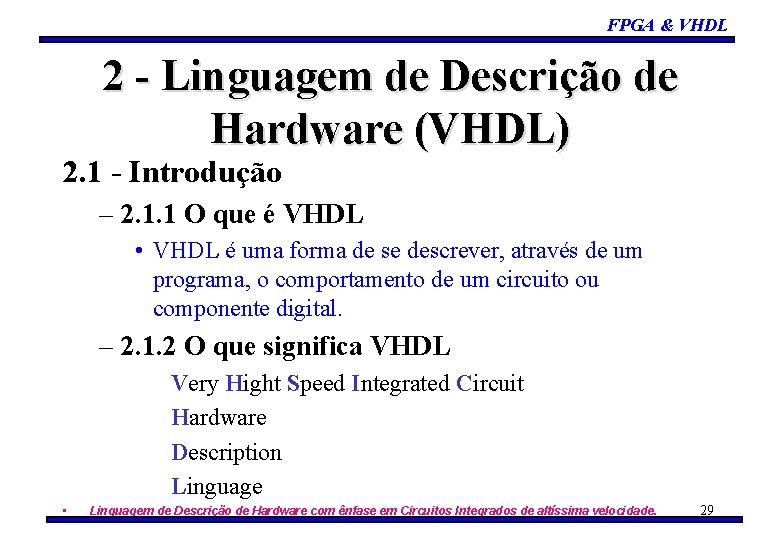

FPGA & VHDL 2 - Linguagem de Descrição de Hardware (VHDL) 2. 1 - Introdução – 2. 1. 1 O que é VHDL • VHDL é uma forma de se descrever, através de um programa, o comportamento de um circuito ou componente digital. – 2. 1. 2 O que significa VHDL Very Hight Speed Integrated Circuit Hardware Description Linguage • Linguagem de Descrição de Hardware com ênfase em Circuitos Integrados de altíssima velocidade. 29

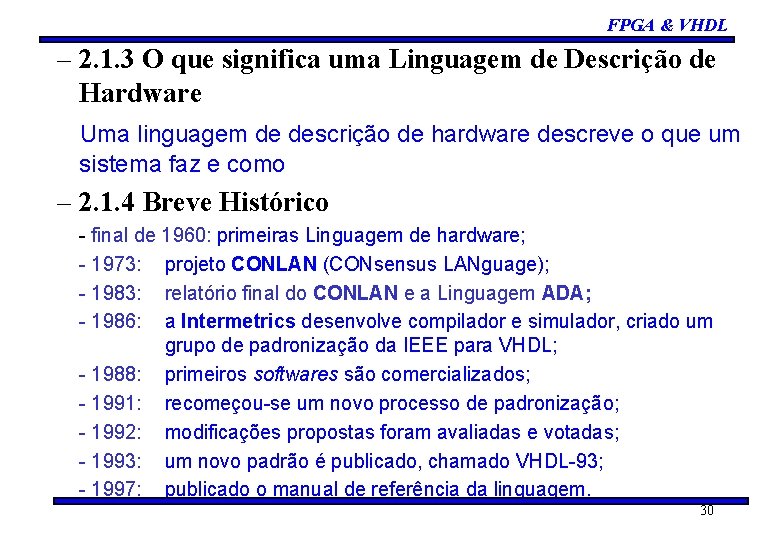

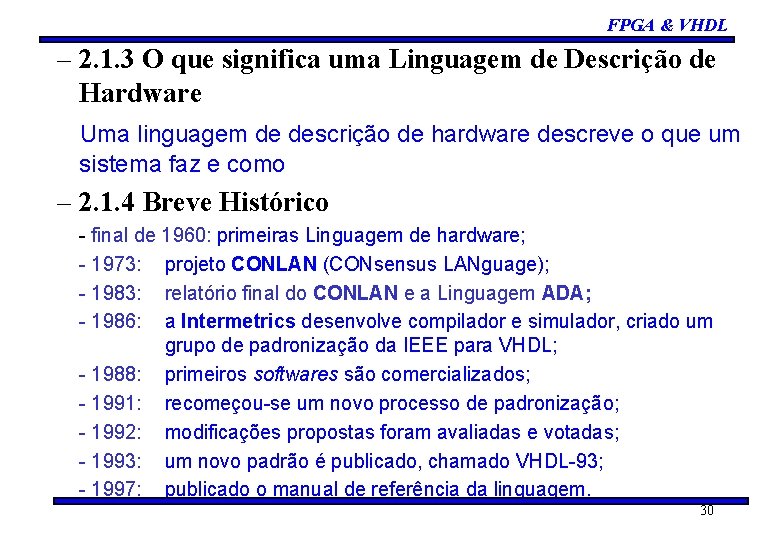

FPGA & VHDL – 2. 1. 3 O que significa uma Linguagem de Descrição de Hardware Uma linguagem de descrição de hardware descreve o que um sistema faz e como – 2. 1. 4 Breve Histórico - final de 1960: primeiras Linguagem de hardware; - 1973: projeto CONLAN (CONsensus LANguage); - 1983: relatório final do CONLAN e a Linguagem ADA; - 1986: a Intermetrics desenvolve compilador e simulador, criado um grupo de padronização da IEEE para VHDL; - 1988: primeiros softwares são comercializados; - 1991: recomeçou-se um novo processo de padronização; - 1992: modificações propostas foram avaliadas e votadas; - 1993: um novo padrão é publicado, chamado VHDL-93; - 1997: publicado o manual de referência da linguagem. 30

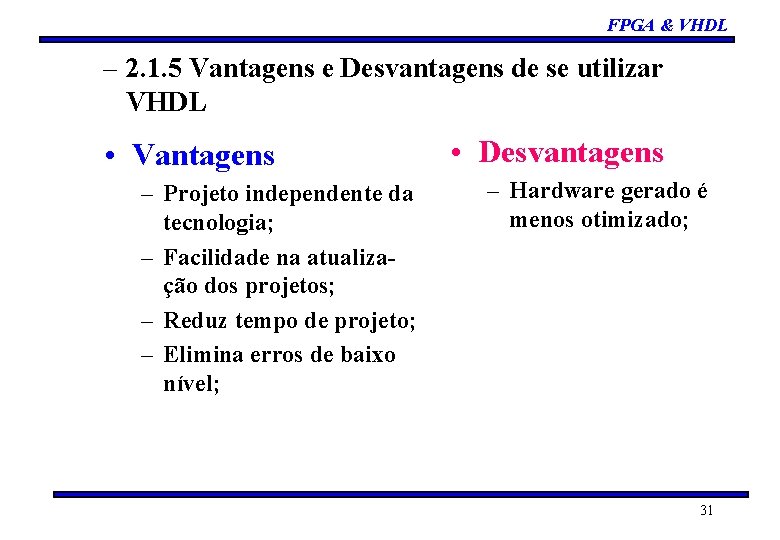

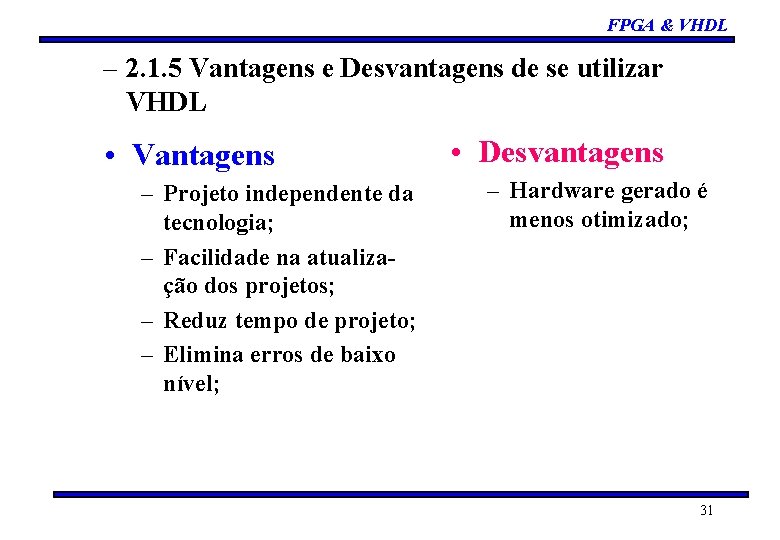

FPGA & VHDL – 2. 1. 5 Vantagens e Desvantagens de se utilizar VHDL • Vantagens – Projeto independente da tecnologia; – Facilidade na atualização dos projetos; – Reduz tempo de projeto; – Elimina erros de baixo nível; • Desvantagens – Hardware gerado é menos otimizado; 31

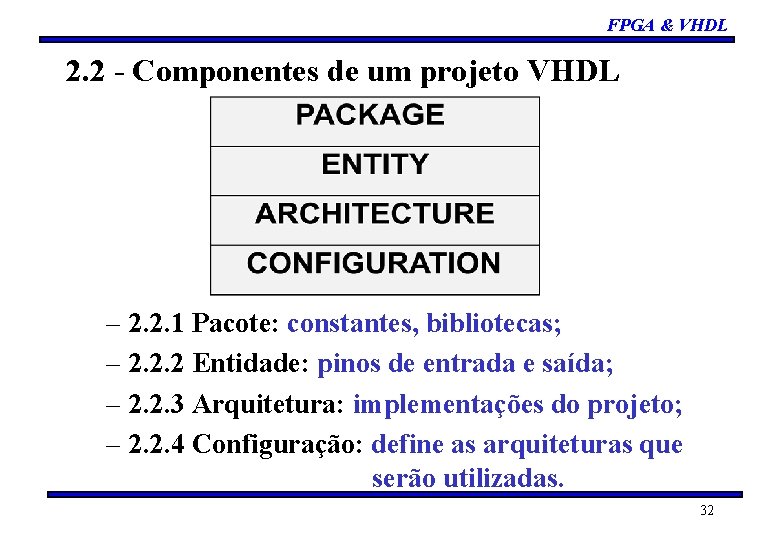

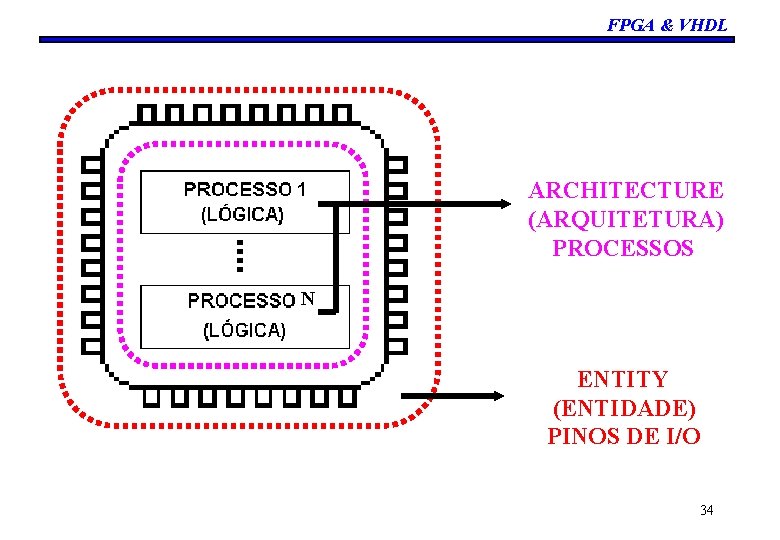

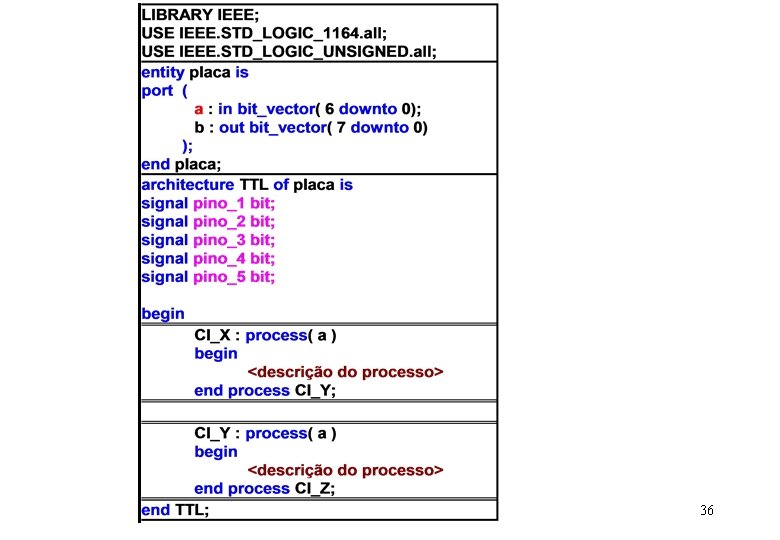

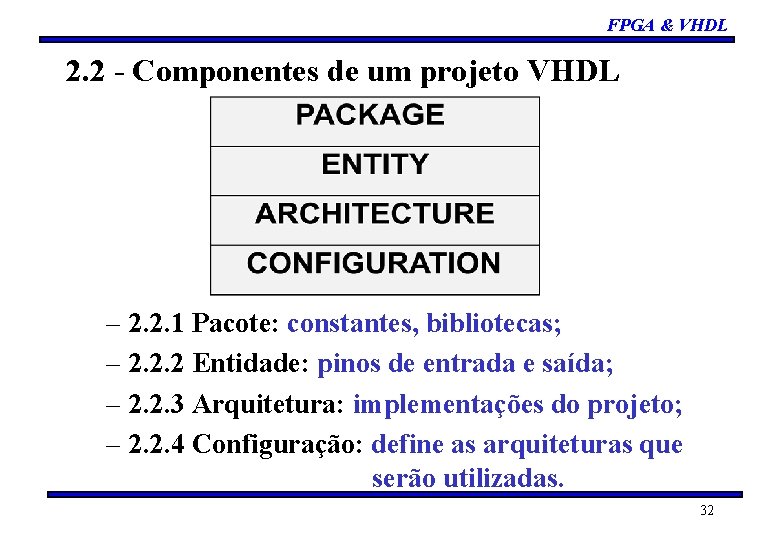

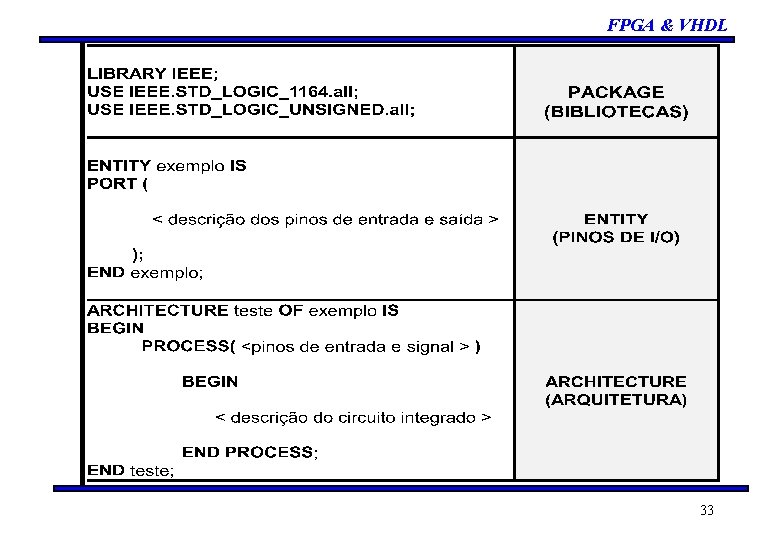

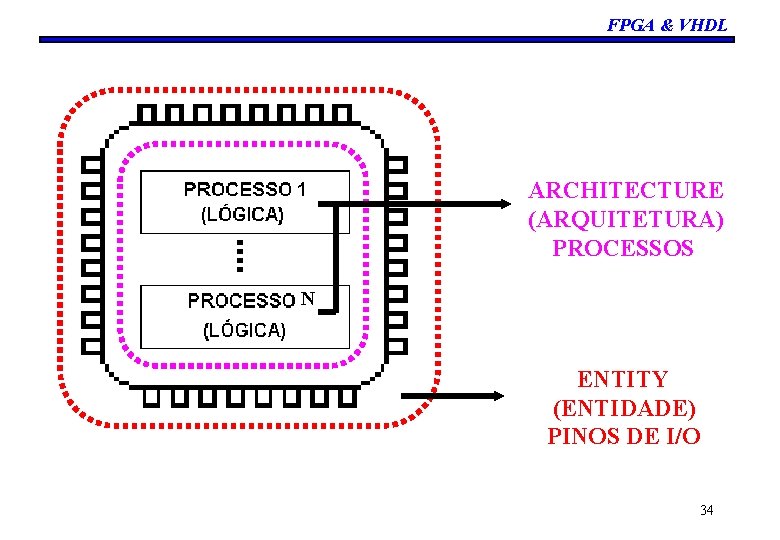

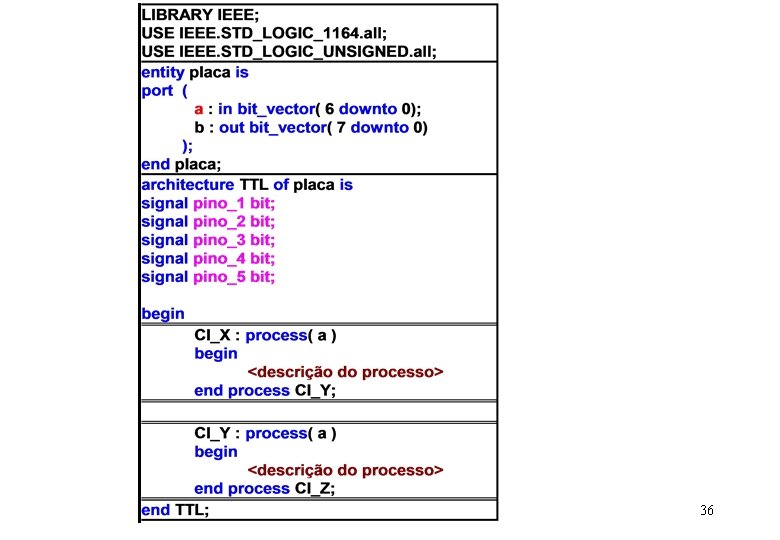

FPGA & VHDL 2. 2 - Componentes de um projeto VHDL – 2. 2. 1 Pacote: constantes, bibliotecas; – 2. 2. 2 Entidade: pinos de entrada e saída; – 2. 2. 3 Arquitetura: implementações do projeto; – 2. 2. 4 Configuração: define as arquiteturas que serão utilizadas. 32

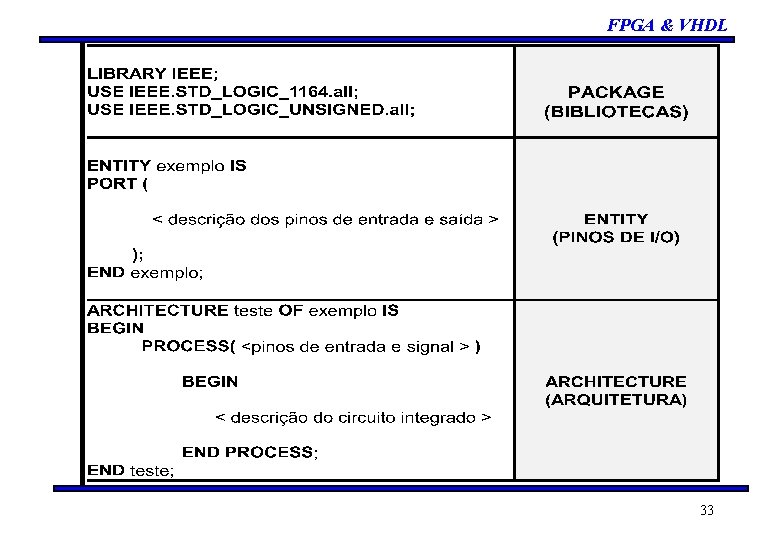

FPGA & VHDL 33

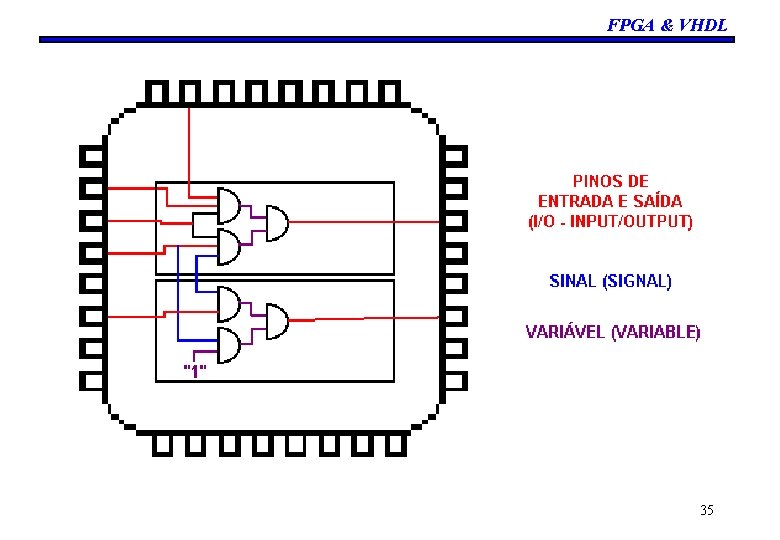

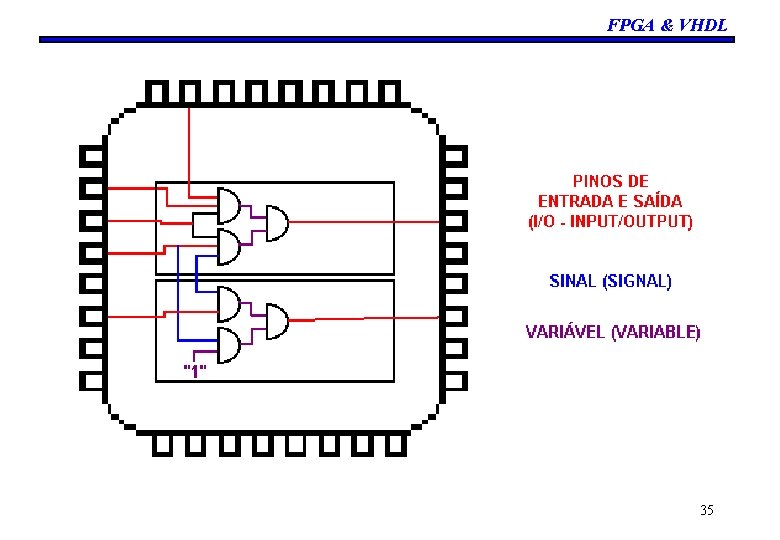

FPGA & VHDL ARCHITECTURE (ARQUITETURA) PROCESSOS N ENTITY (ENTIDADE) PINOS DE I/O 34

FPGA & VHDL 35

36

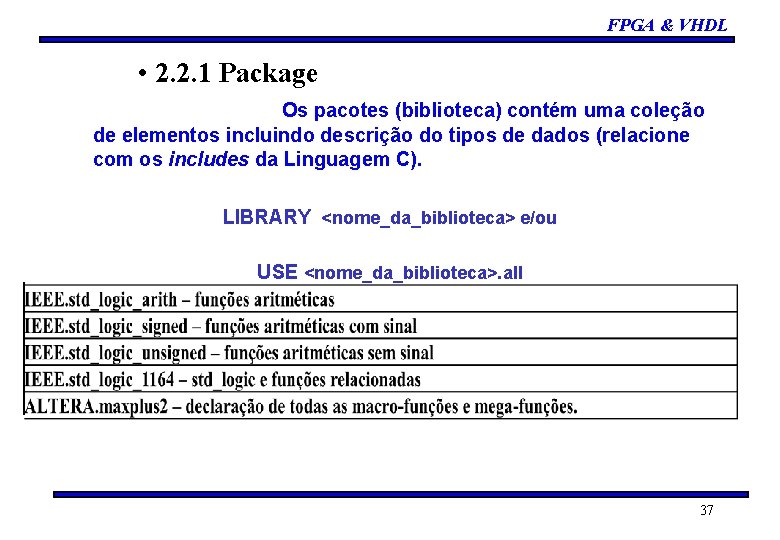

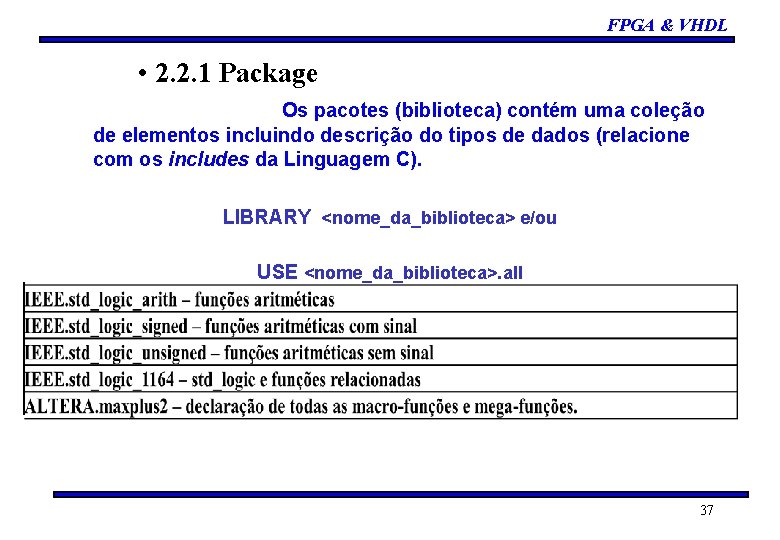

FPGA & VHDL • 2. 2. 1 Package Os pacotes (biblioteca) contém uma coleção de elementos incluindo descrição do tipos de dados (relacione com os includes da Linguagem C). LIBRARY <nome_da_biblioteca> e/ou USE <nome_da_biblioteca>. all 37

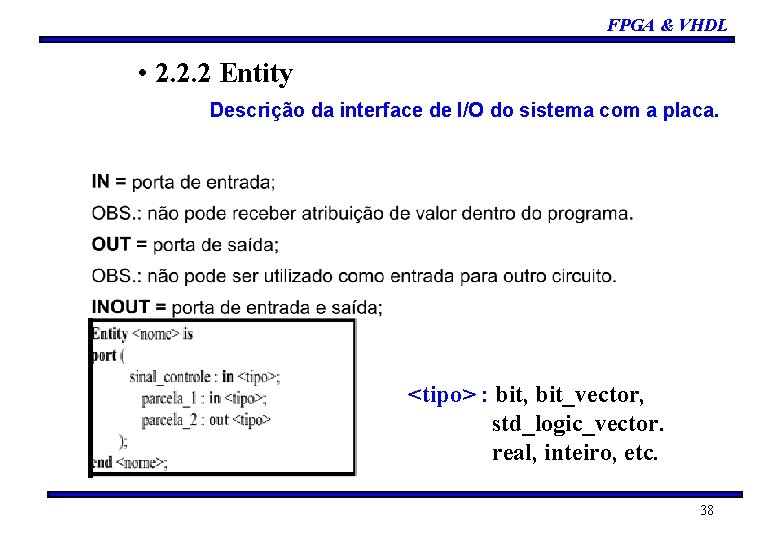

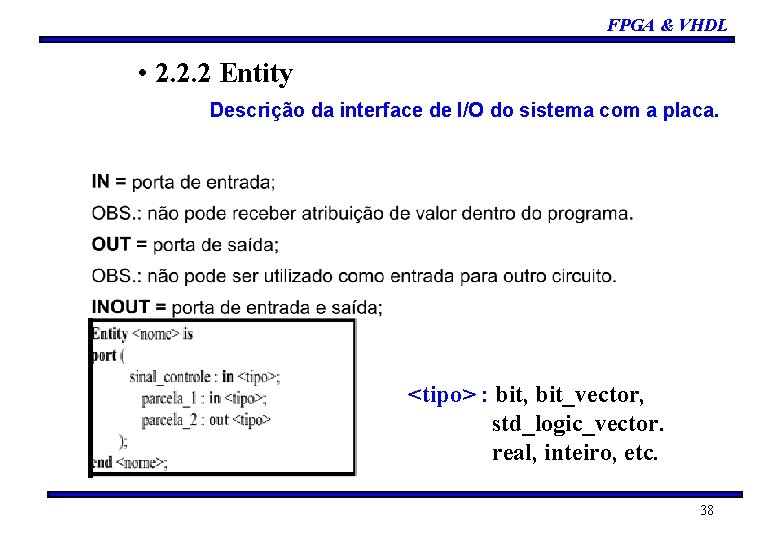

FPGA & VHDL • 2. 2. 2 Entity Descrição da interface de I/O do sistema com a placa. <tipo> : bit, bit_vector, std_logic_vector. real, inteiro, etc. 38

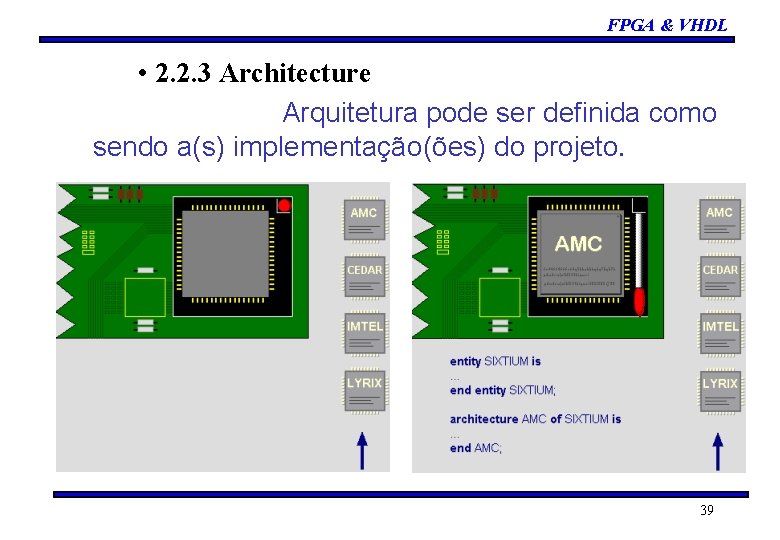

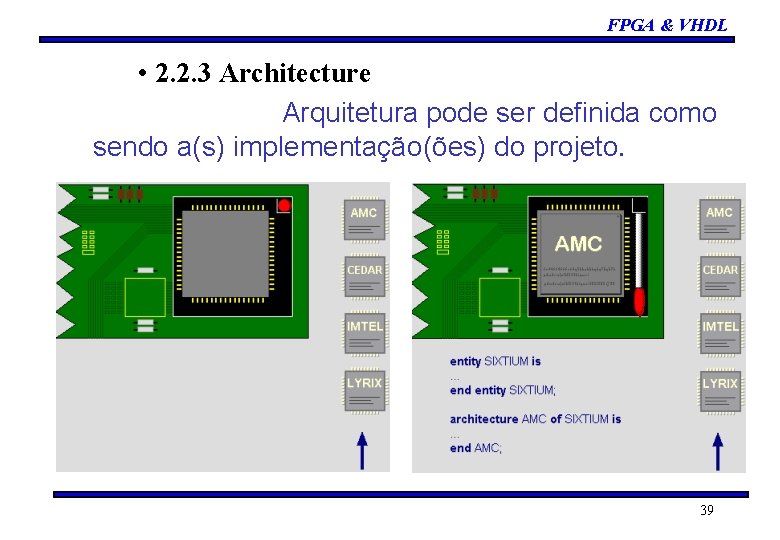

FPGA & VHDL • 2. 2. 3 Architecture Arquitetura pode ser definida como sendo a(s) implementação(ões) do projeto. 39

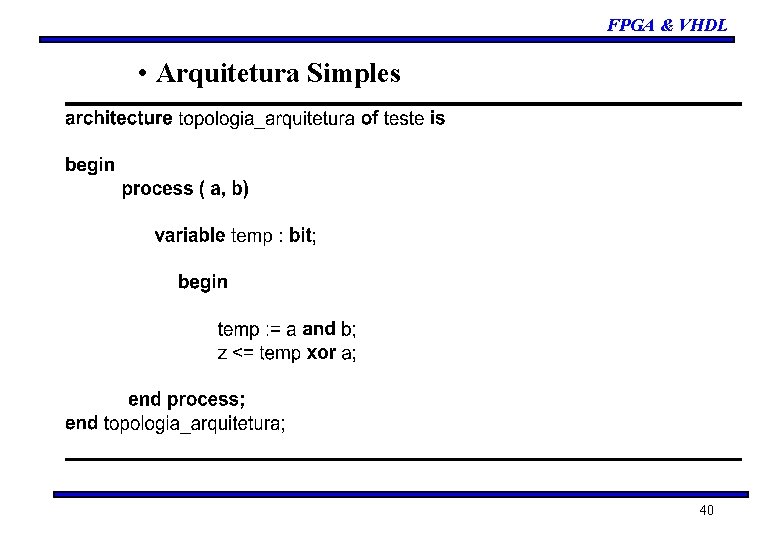

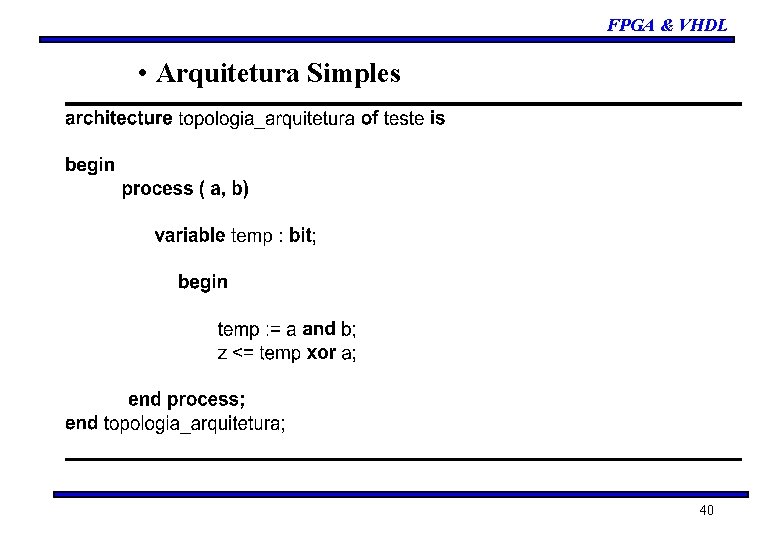

FPGA & VHDL • Arquitetura Simples 40

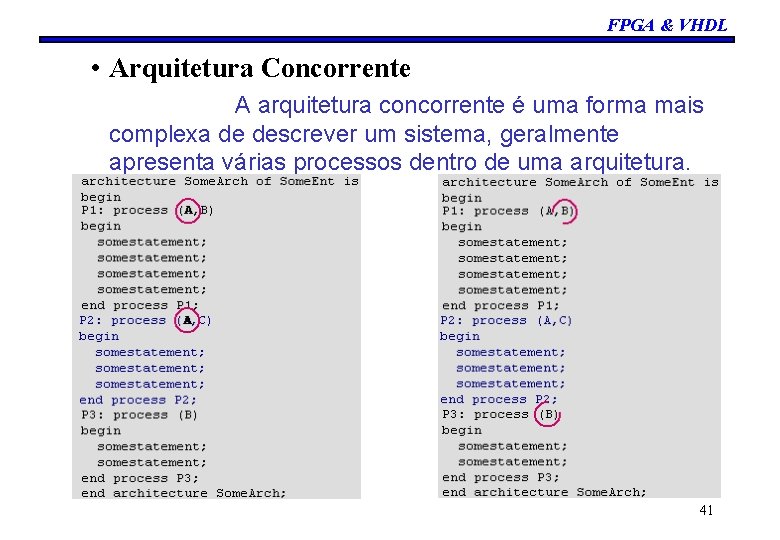

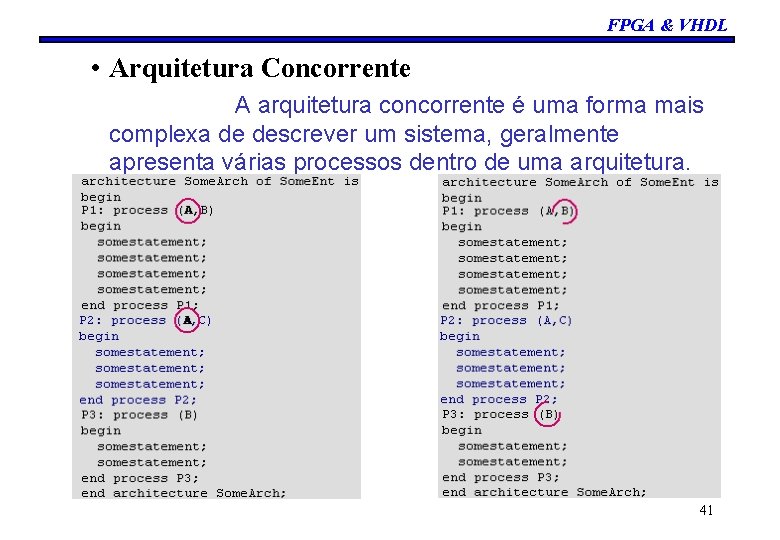

FPGA & VHDL • Arquitetura Concorrente A arquitetura concorrente é uma forma mais complexa de descrever um sistema, geralmente apresenta várias processos dentro de uma arquitetura. 41

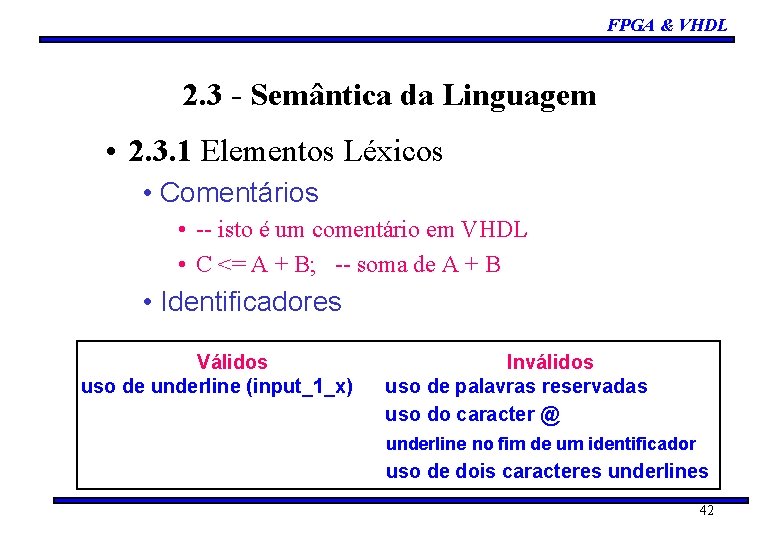

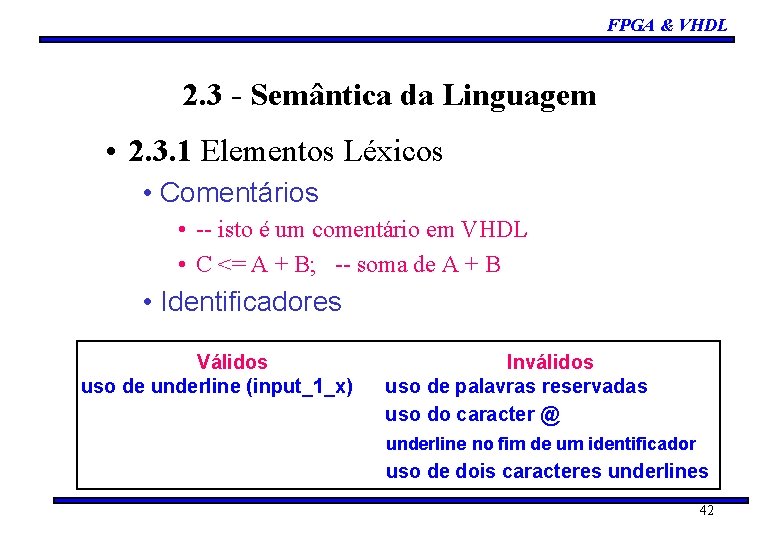

FPGA & VHDL 2. 3 - Semântica da Linguagem • 2. 3. 1 Elementos Léxicos • Comentários • -- isto é um comentário em VHDL • C <= A + B; -- soma de A + B • Identificadores Válidos uso de underline (input_1_x) Inválidos uso de palavras reservadas uso do caracter @ underline no fim de um identificador uso de dois caracteres underlines 42

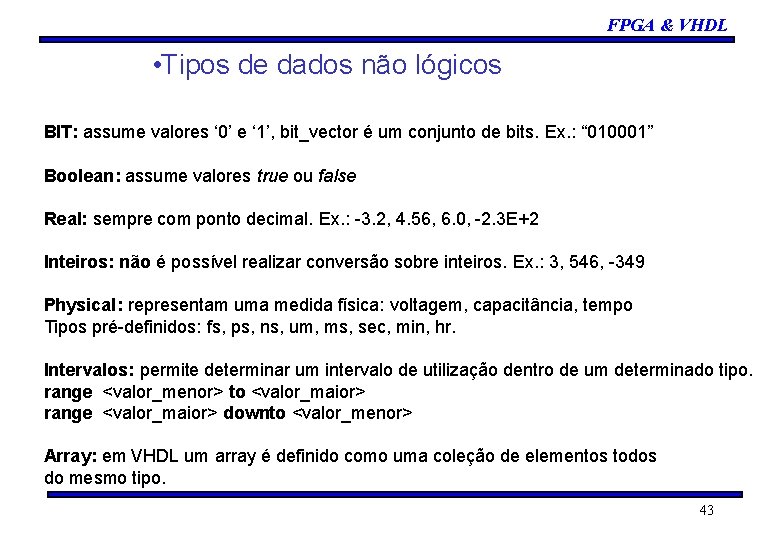

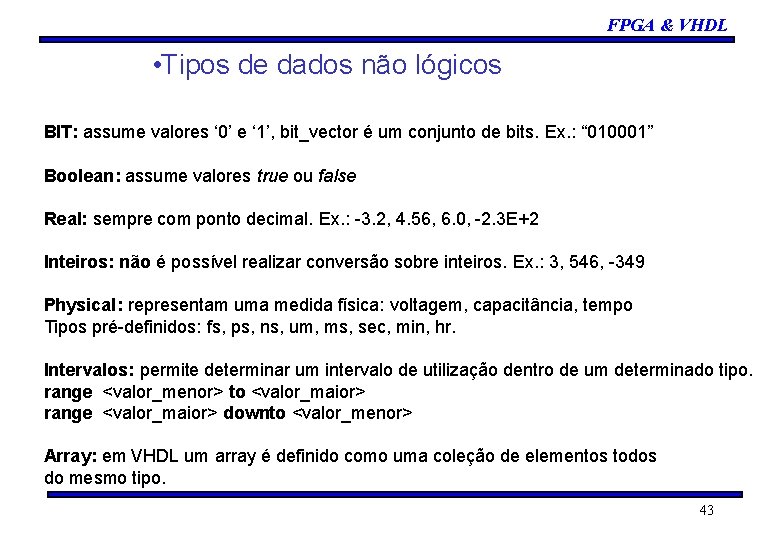

FPGA & VHDL • Tipos de dados não lógicos BIT: assume valores ‘ 0’ e ‘ 1’, bit_vector é um conjunto de bits. Ex. : “ 010001” Boolean: assume valores true ou false Real: sempre com ponto decimal. Ex. : -3. 2, 4. 56, 6. 0, -2. 3 E+2 Inteiros: não é possível realizar conversão sobre inteiros. Ex. : 3, 546, -349 Physical: representam uma medida física: voltagem, capacitância, tempo Tipos pré-definidos: fs, ps, ns, um, ms, sec, min, hr. Intervalos: permite determinar um intervalo de utilização dentro de um determinado tipo. range <valor_menor> to <valor_maior> range <valor_maior> downto <valor_menor> Array: em VHDL um array é definido como uma coleção de elementos todos do mesmo tipo. 43

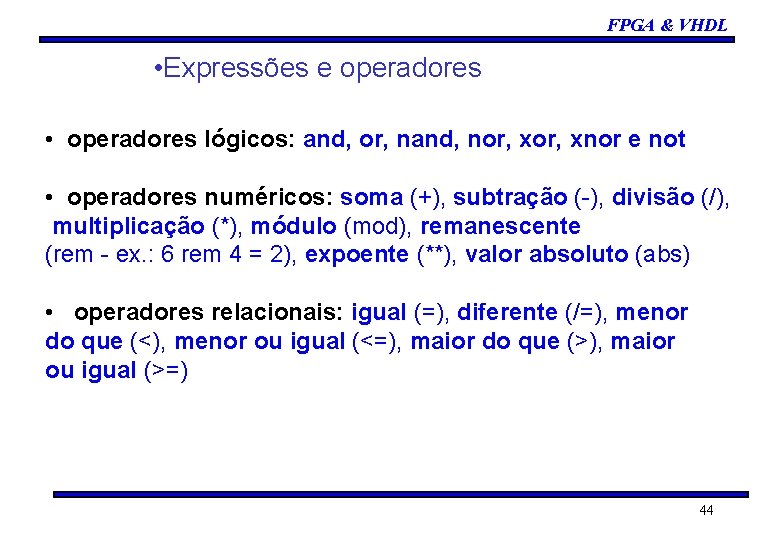

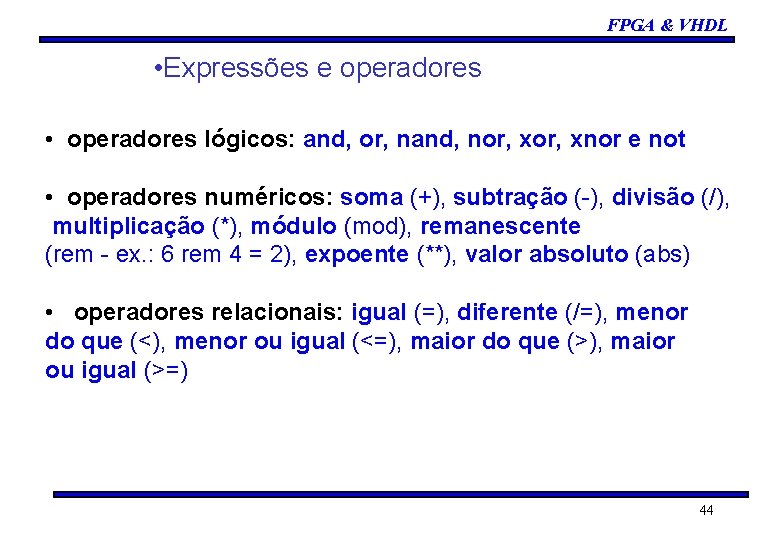

FPGA & VHDL • Expressões e operadores • operadores lógicos: and, or, nand, nor, xnor e not • operadores numéricos: soma (+), subtração (-), divisão (/), multiplicação (*), módulo (mod), remanescente (rem - ex. : 6 rem 4 = 2), expoente (**), valor absoluto (abs) • operadores relacionais: igual (=), diferente (/=), menor do que (<), menor ou igual (<=), maior do que (>), maior ou igual (>=) 44

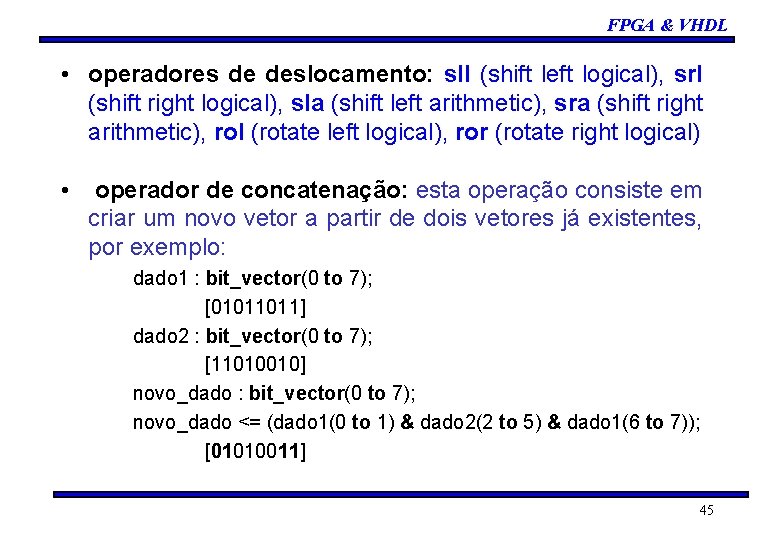

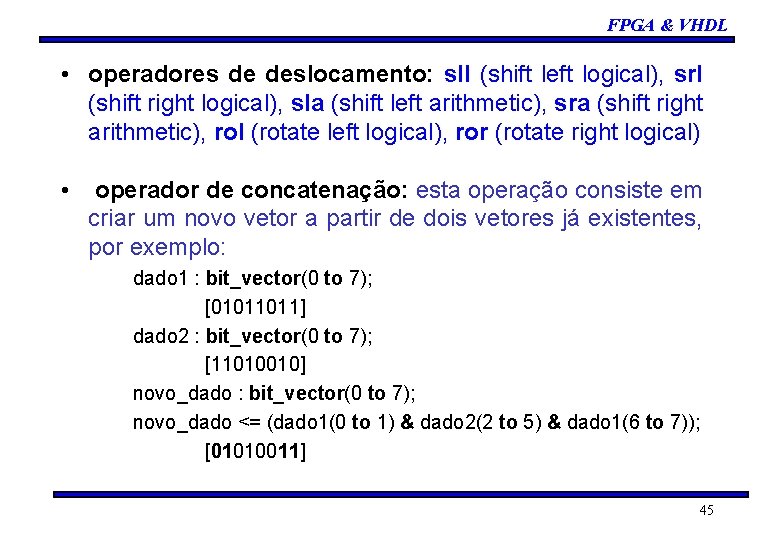

FPGA & VHDL • operadores de deslocamento: sll (shift left logical), srl (shift right logical), sla (shift left arithmetic), sra (shift right arithmetic), rol (rotate left logical), ror (rotate right logical) • operador de concatenação: esta operação consiste em criar um novo vetor a partir de dois vetores já existentes, por exemplo: dado 1 : bit_vector(0 to 7); [01011011] dado 2 : bit_vector(0 to 7); [11010010] novo_dado : bit_vector(0 to 7); novo_dado <= (dado 1(0 to 1) & dado 2(2 to 5) & dado 1(6 to 7)); [01010011] 45

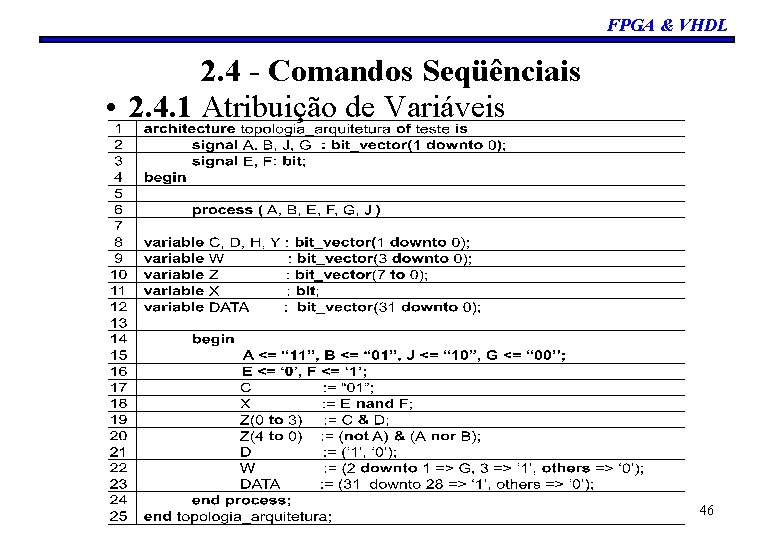

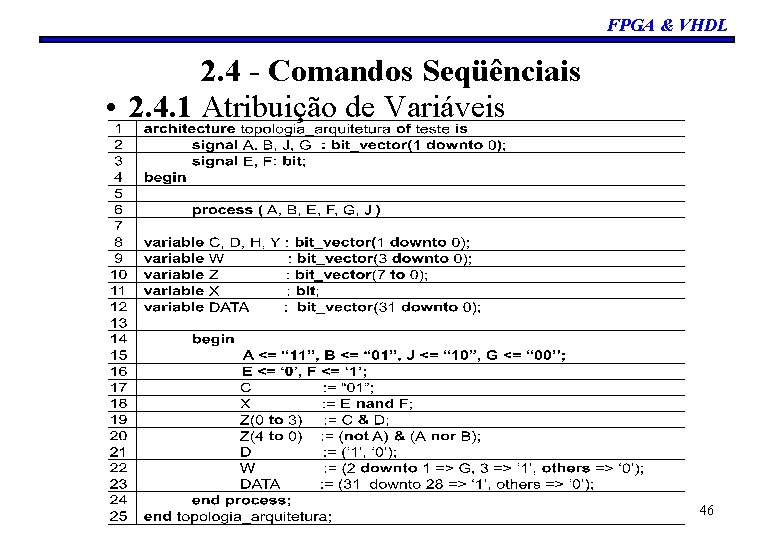

FPGA & VHDL 2. 4 - Comandos Seqüênciais • 2. 4. 1 Atribuição de Variáveis 46

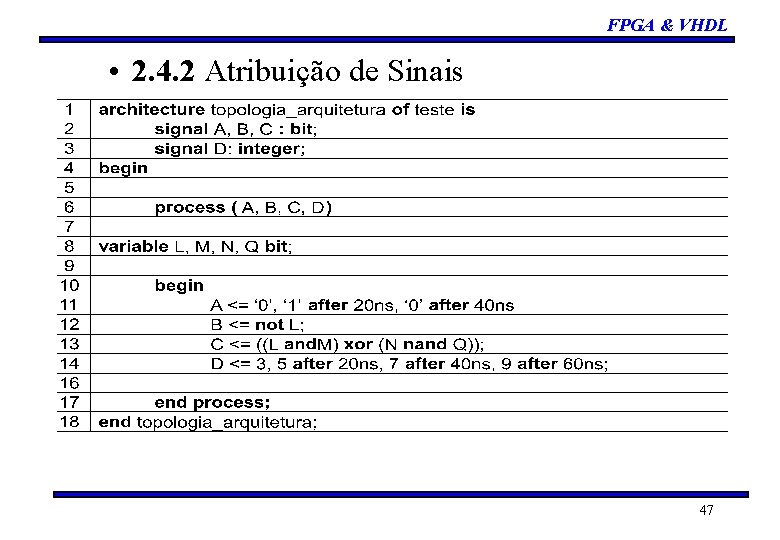

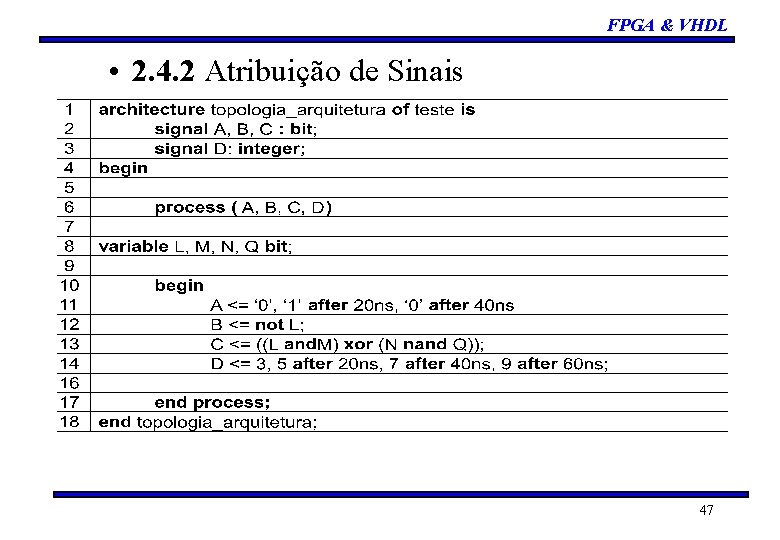

FPGA & VHDL • 2. 4. 2 Atribuição de Sinais 47

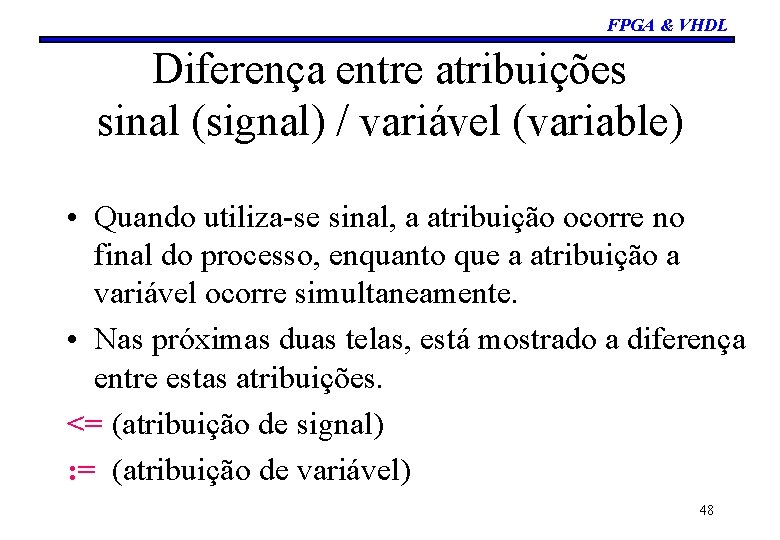

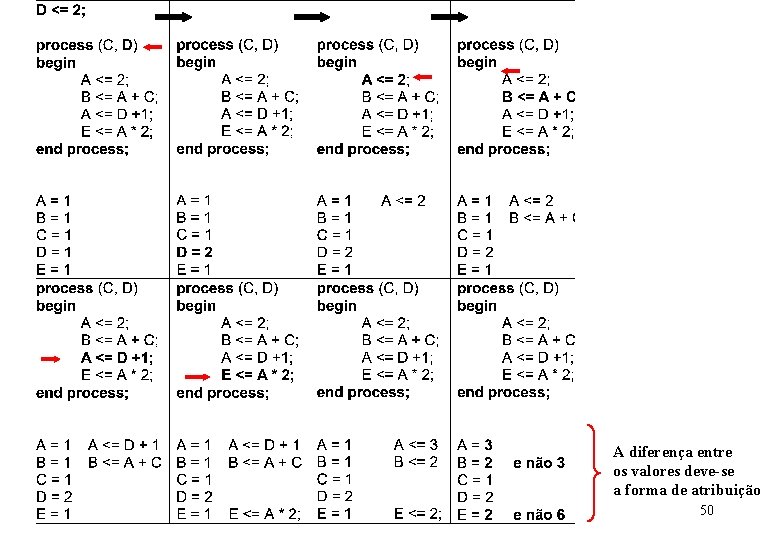

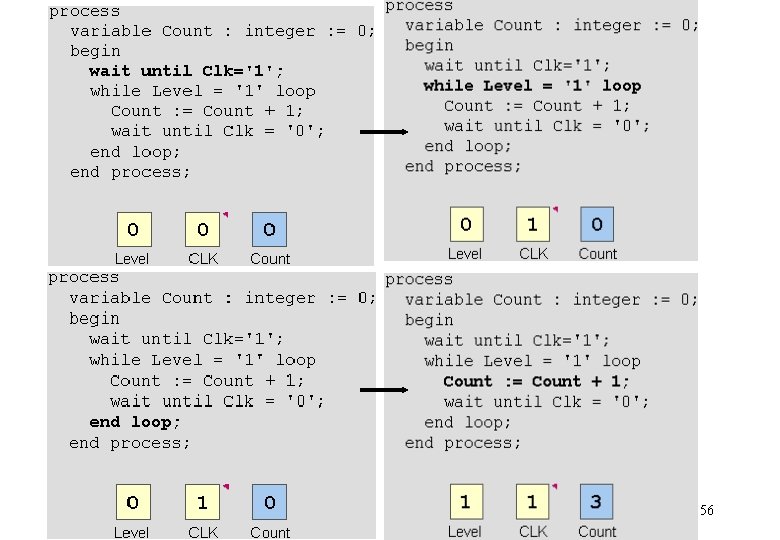

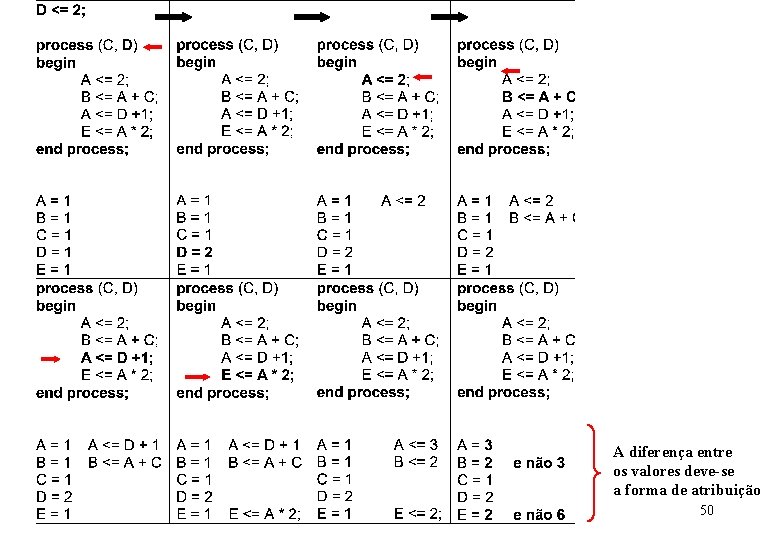

FPGA & VHDL Diferença entre atribuições sinal (signal) / variável (variable) • Quando utiliza-se sinal, a atribuição ocorre no final do processo, enquanto que a atribuição a variável ocorre simultaneamente. • Nas próximas duas telas, está mostrado a diferença entre estas atribuições. <= (atribuição de signal) : = (atribuição de variável) 48

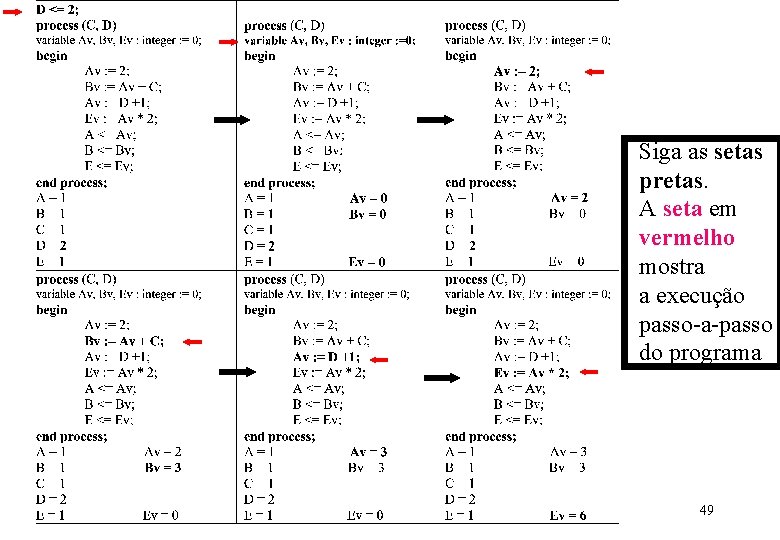

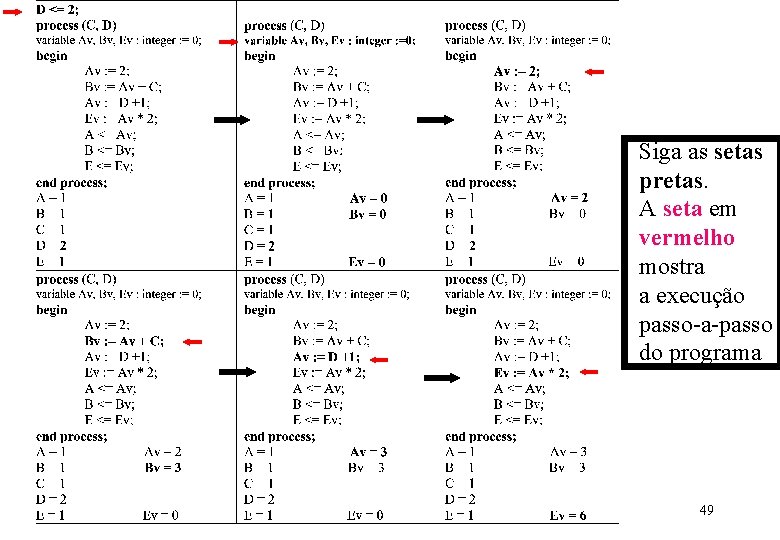

Siga as setas pretas. A seta em vermelho mostra a execução passo-a-passo do programa 49

A diferença entre os valores deve-se a forma de atribuição 50

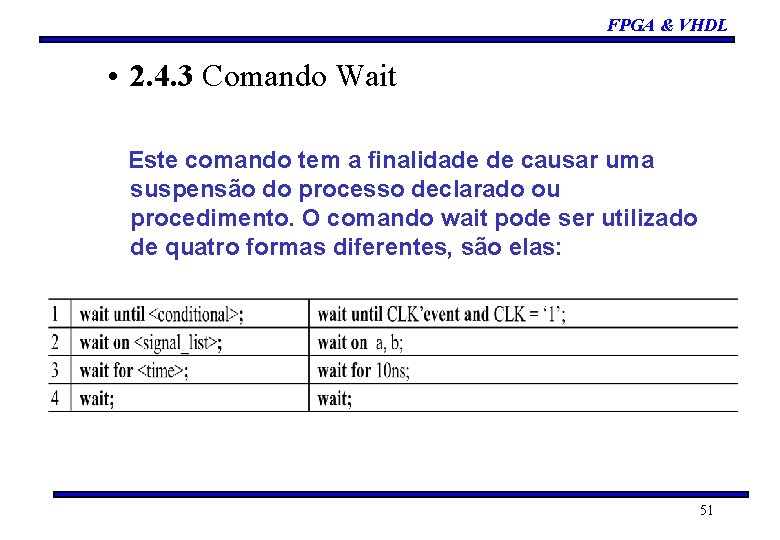

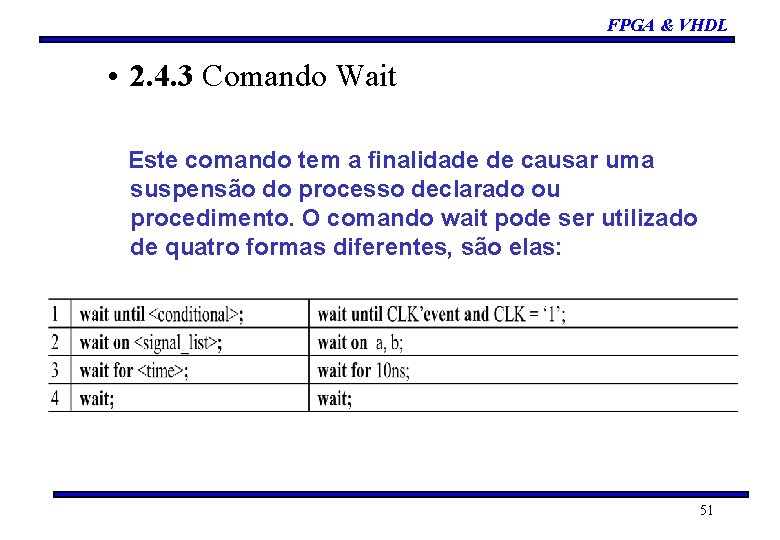

FPGA & VHDL • 2. 4. 3 Comando Wait Este comando tem a finalidade de causar uma suspensão do processo declarado ou procedimento. O comando wait pode ser utilizado de quatro formas diferentes, são elas: 51

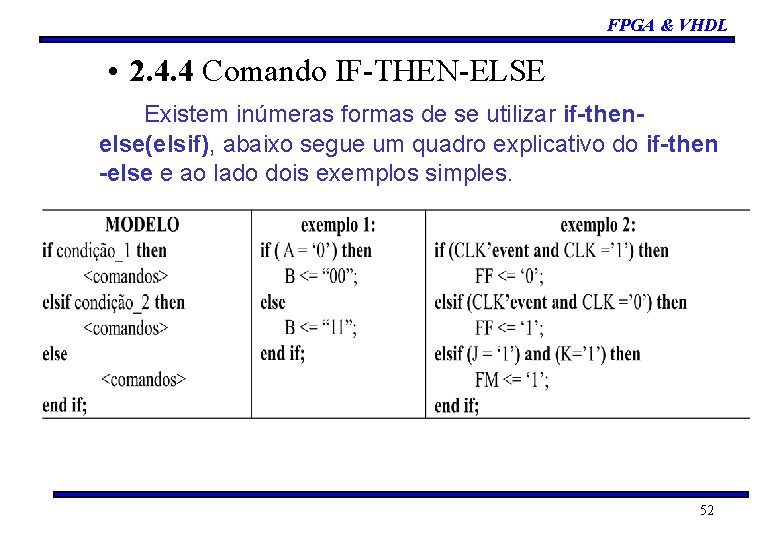

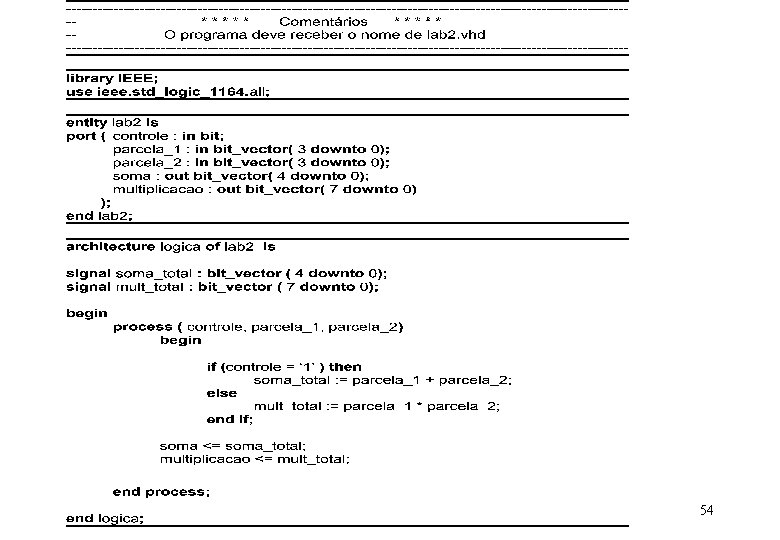

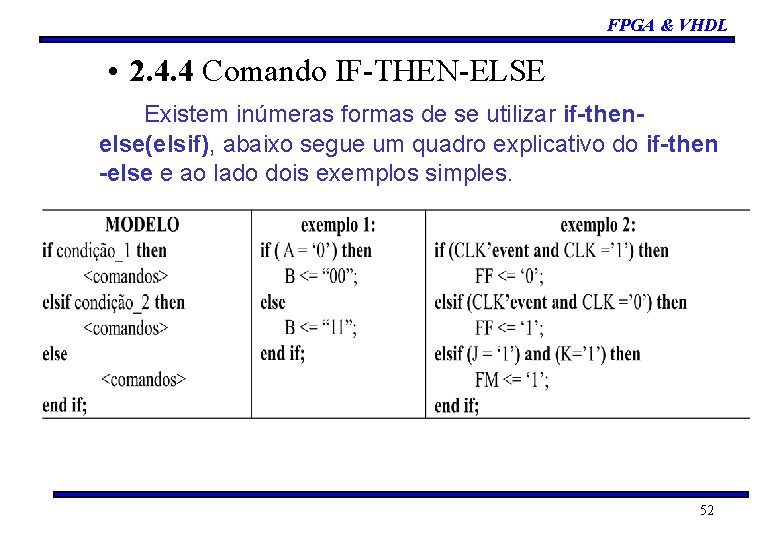

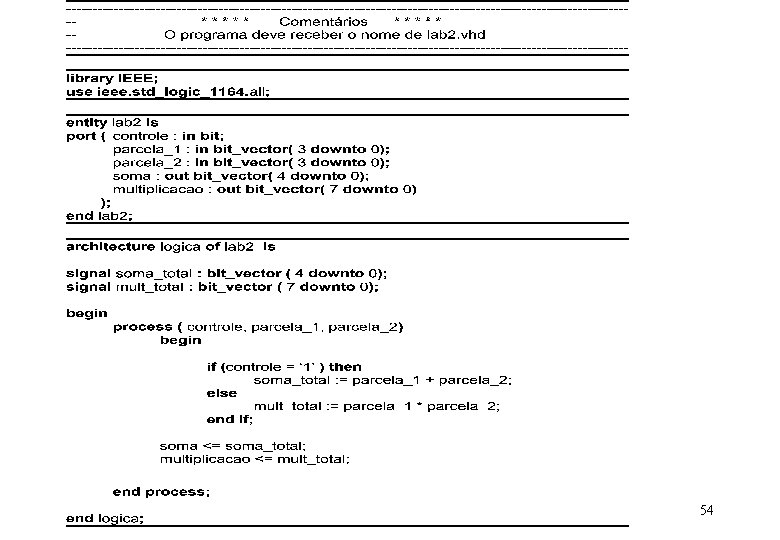

FPGA & VHDL • 2. 4. 4 Comando IF-THEN-ELSE Existem inúmeras formas de se utilizar if-thenelse(elsif), abaixo segue um quadro explicativo do if-then -else e ao lado dois exemplos simples. 52

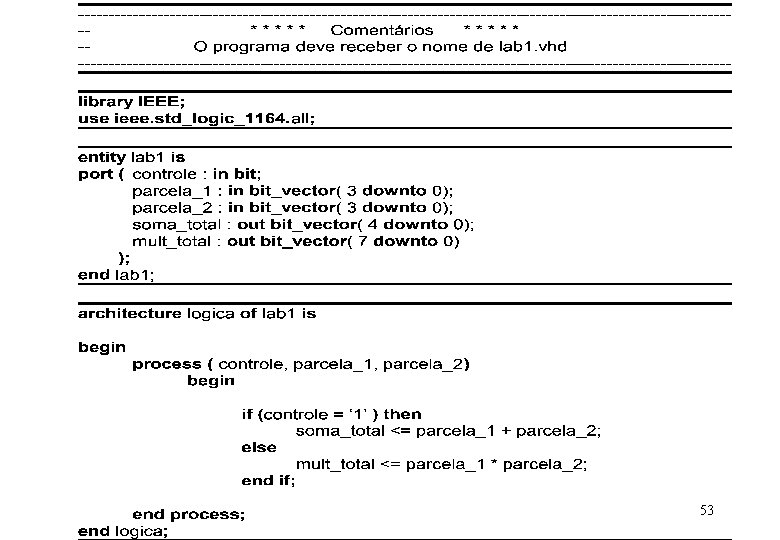

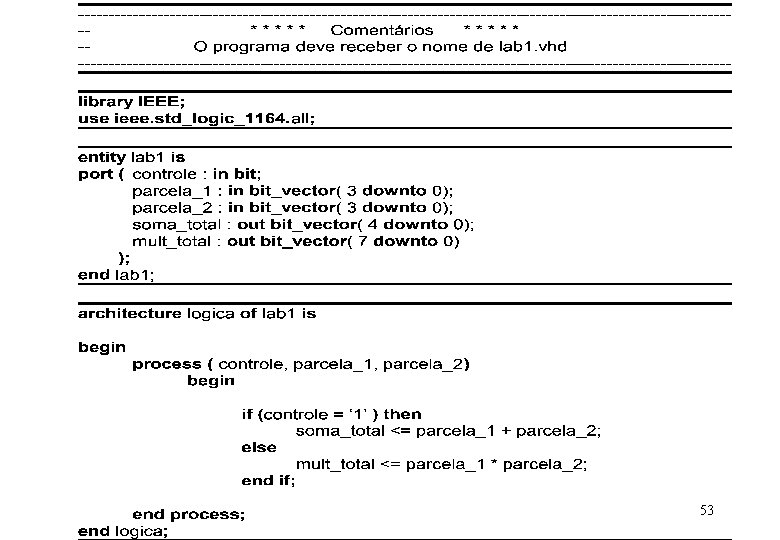

53

54

FPGA & VHDL • 2. 4. 5 Comando Loop For - While 55

56

FPGA & VHDL • 2. 4. 6 Comando Case 57

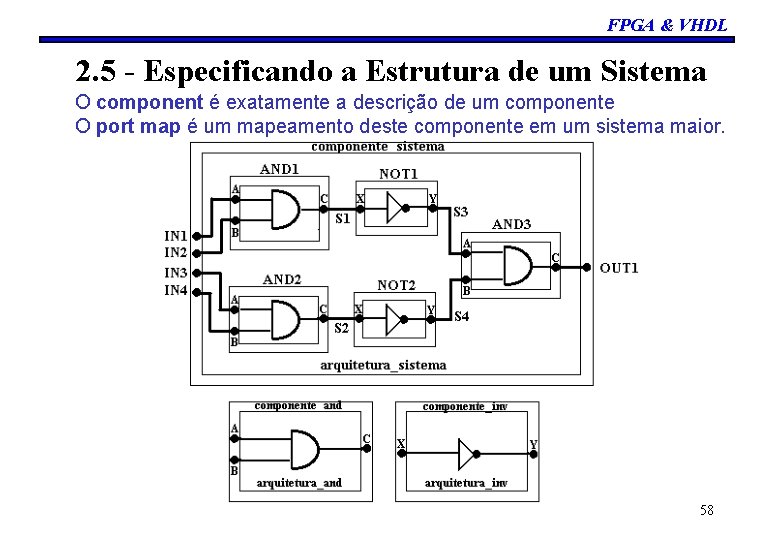

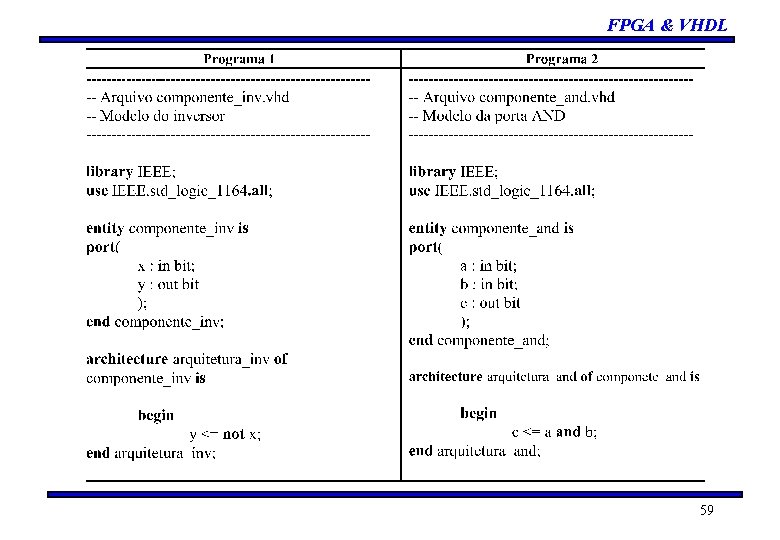

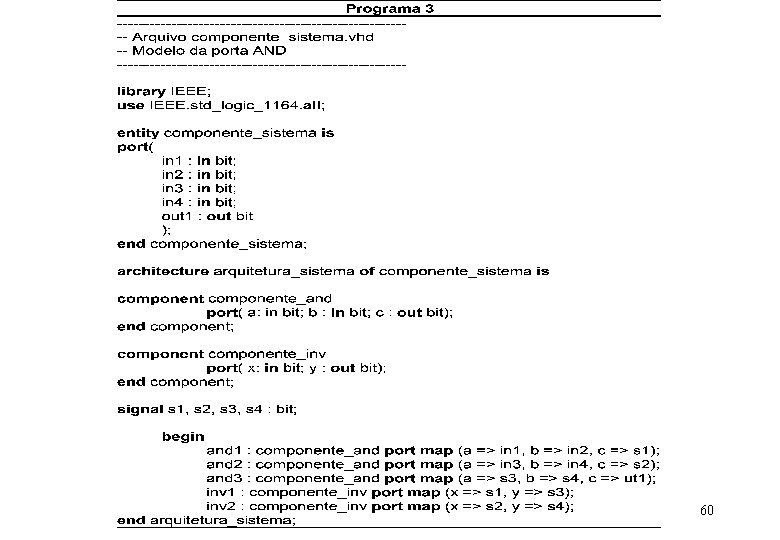

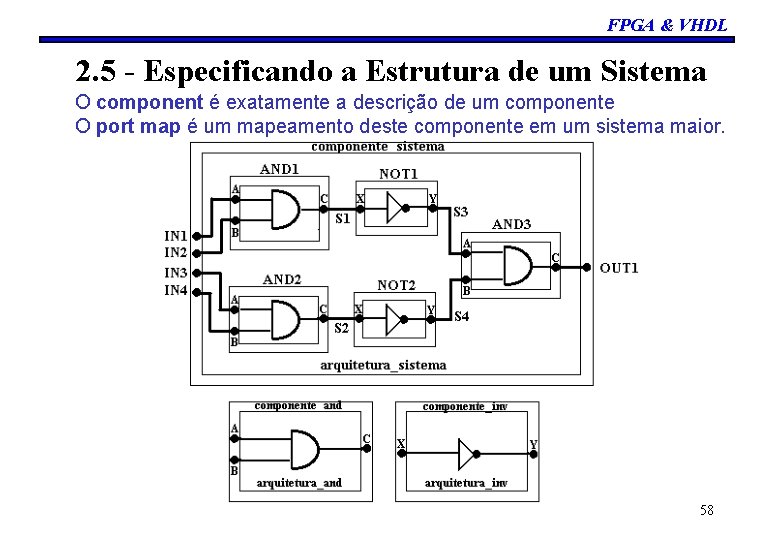

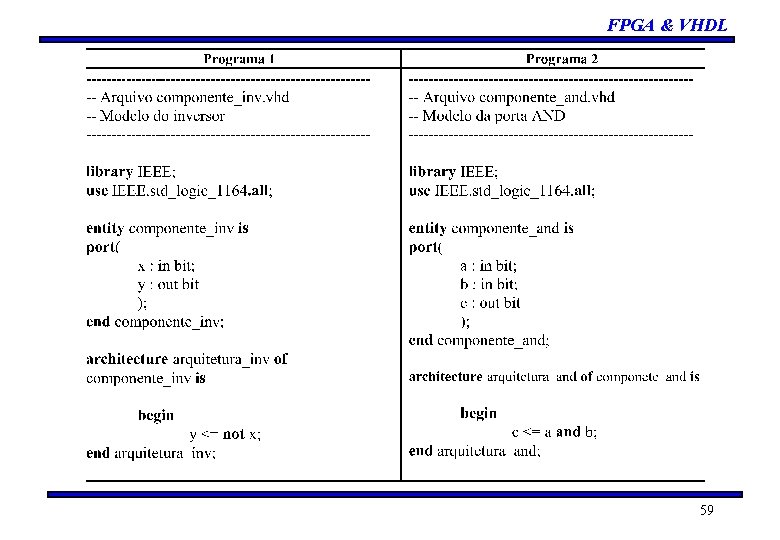

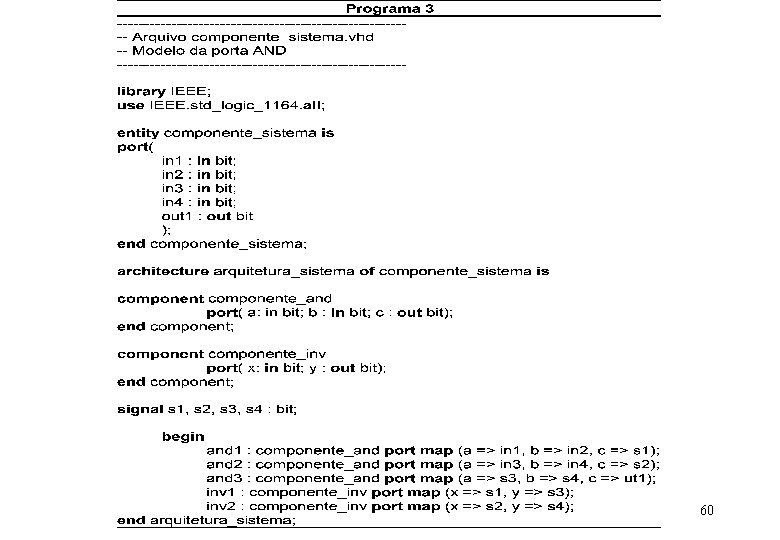

FPGA & VHDL 2. 5 - Especificando a Estrutura de um Sistema O component é exatamente a descrição de um componente O port map é um mapeamento deste componente em um sistema maior. 58

FPGA & VHDL 59

60

FPGA & VHDL Exemplos de circuitos descritos em VHDL Anderson Royes Terroso http: //www. ee. pucrs. br/~terroso

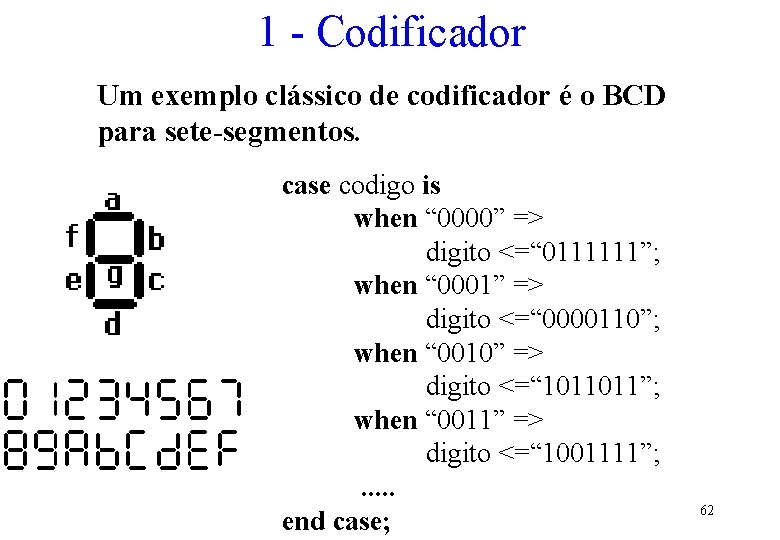

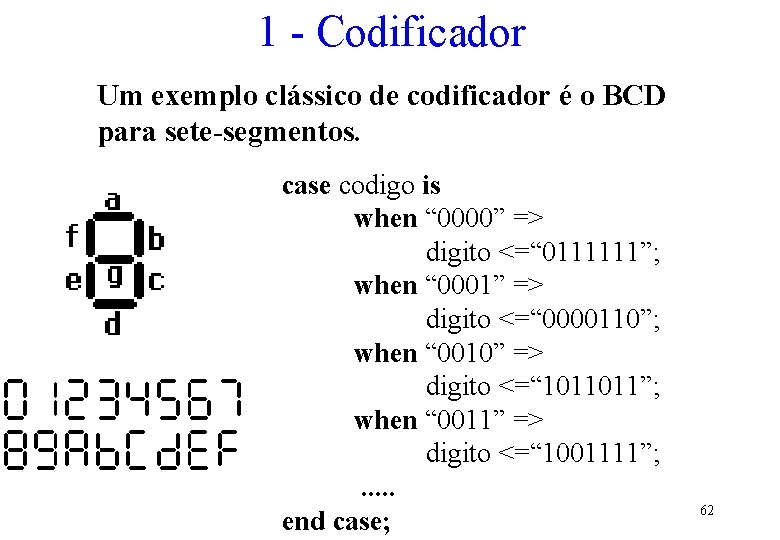

1 - Codificador Um exemplo clássico de codificador é o BCD para sete-segmentos. case codigo is when “ 0000” => digito <=“ 0111111”; when “ 0001” => digito <=“ 0000110”; when “ 0010” => digito <=“ 1011011”; when “ 0011” => digito <=“ 1001111”; . . . end case; 62

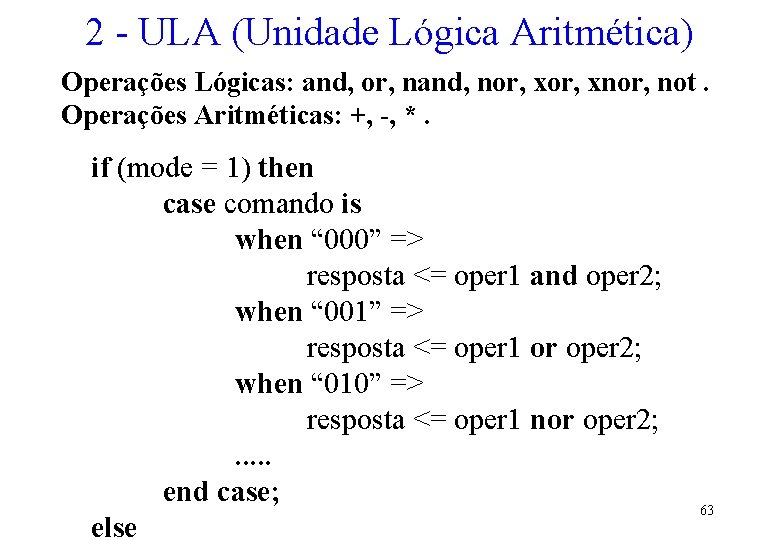

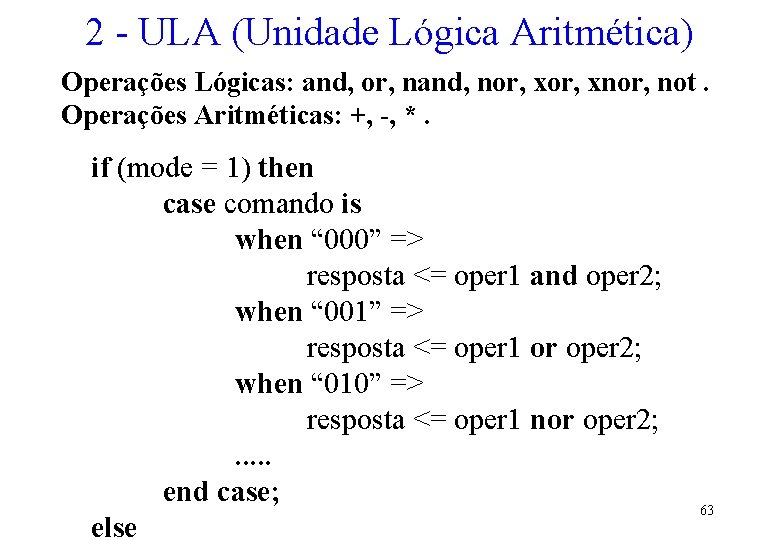

2 - ULA (Unidade Lógica Aritmética) Operações Lógicas: and, or, nand, nor, xnor, not. Operações Aritméticas: +, -, *. if (mode = 1) then case comando is when “ 000” => resposta <= oper 1 and oper 2; when “ 001” => resposta <= oper 1 or oper 2; when “ 010” => resposta <= oper 1 nor oper 2; . . . end case; else 63

-- continuação do else case comando is when “ 000” => resp_aritm <= oper 1 + oper 2; when “ 001” => resp_aritm <= oper 1 - oper 2; . . . when others => resp_aritm <= X’ 0’; end case; end if; 64

3 - Gerador do Código de Hamming Tarefa: Implementar o gerador do código de Hamming. 65

ALTERA MAX-PLUS II

FINALIDADE: • ESQUEMÁTICO; • VHDL; • AHDL; ------------------------------------ • COMPILAR PARA UM DETERMINADO CHIP • SIMULAR • FAZER O DOWNLOAD DO CÓDIGO PARA FPGA 67

68

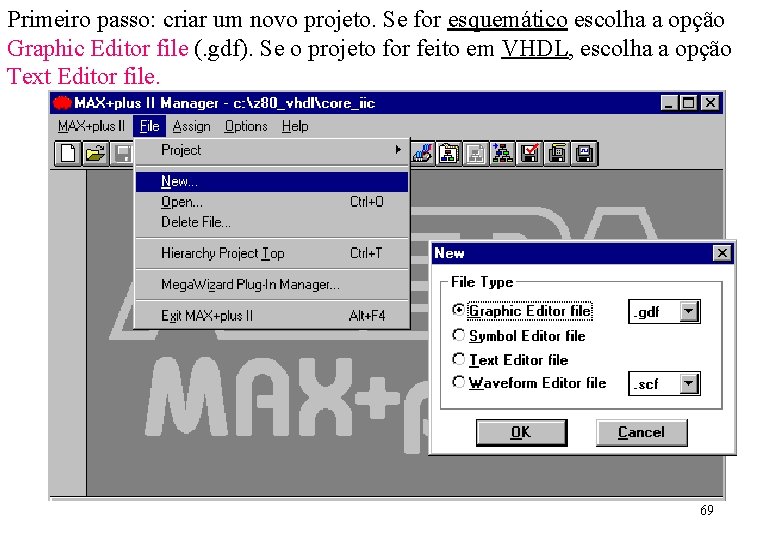

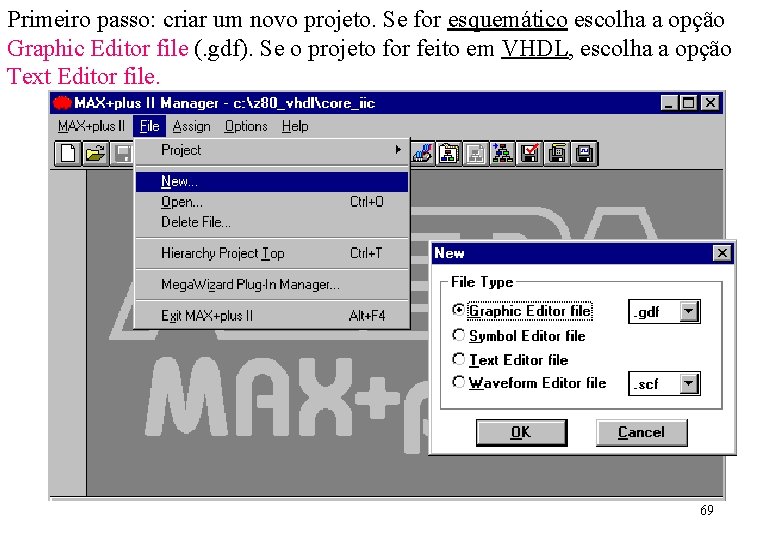

Primeiro passo: criar um novo projeto. Se for esquemático escolha a opção Graphic Editor file (. gdf). Se o projeto for feito em VHDL, escolha a opção Text Editor file. 69

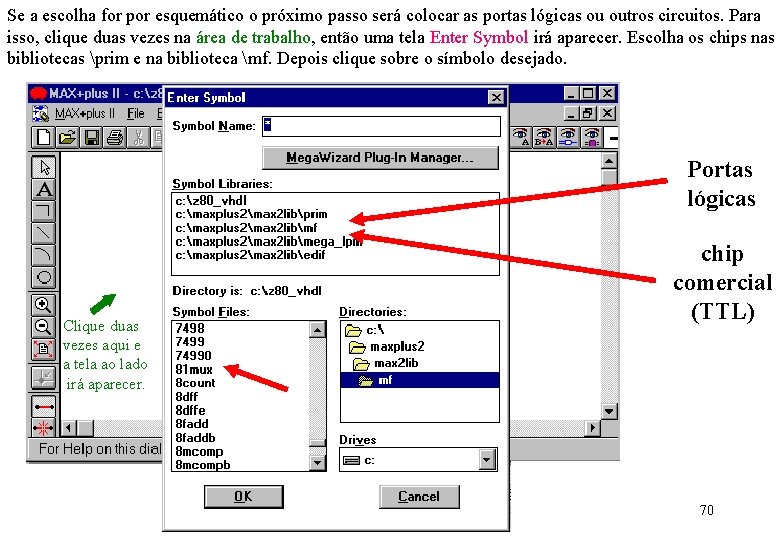

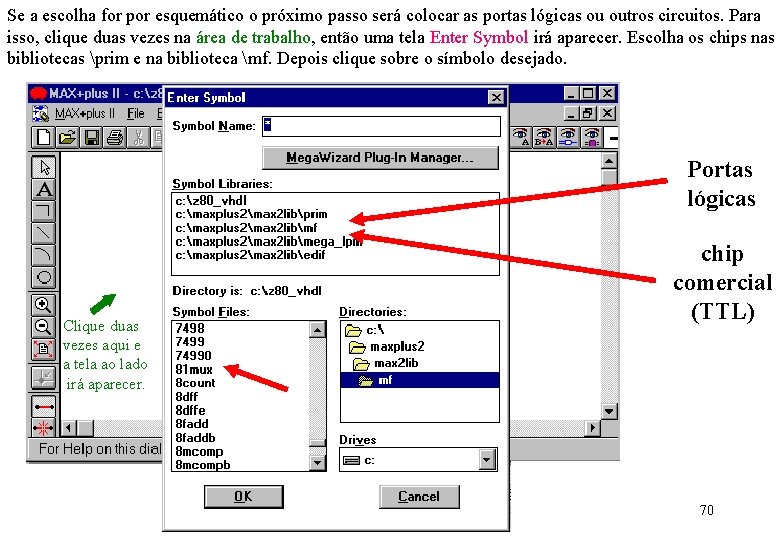

Se a escolha for por esquemático o próximo passo será colocar as portas lógicas ou outros circuitos. Para isso, clique duas vezes na área de trabalho, então uma tela Enter Symbol irá aparecer. Escolha os chips nas bibliotecas prim e na biblioteca mf. Depois clique sobre o símbolo desejado. Portas lógicas Clique duas vezes aqui e a tela ao lado irá aparecer. chip comercial (TTL) 70

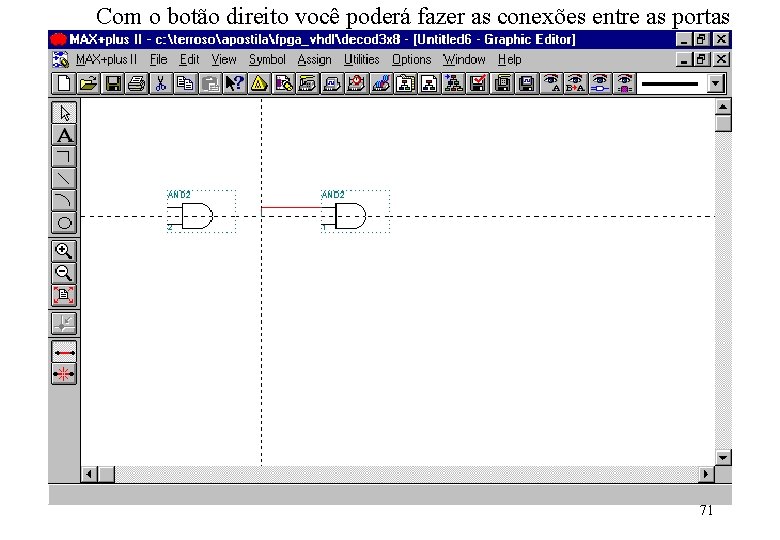

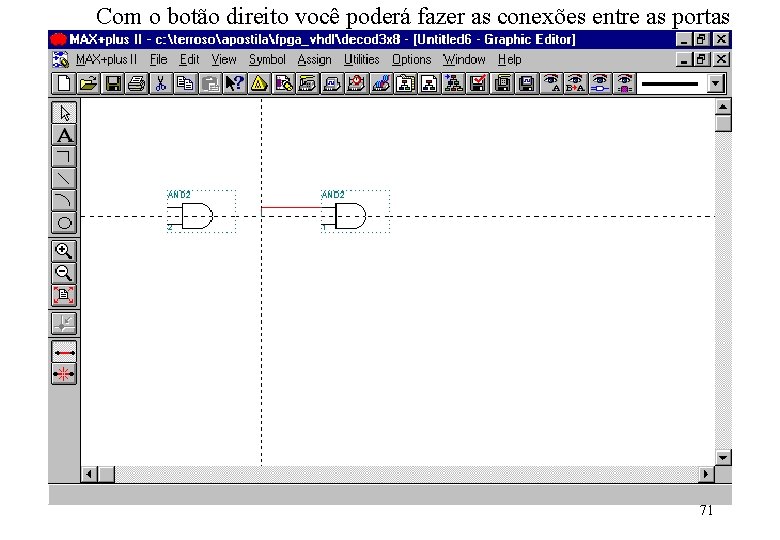

Com o botão direito você poderá fazer as conexões entre as portas 71

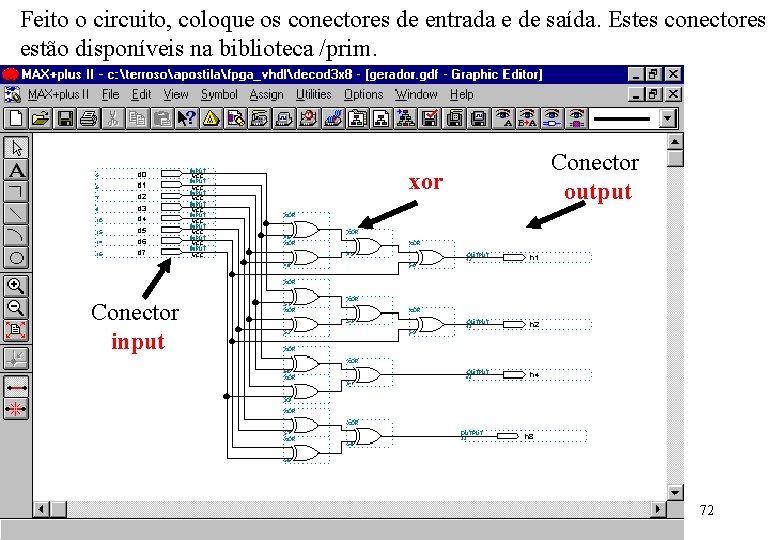

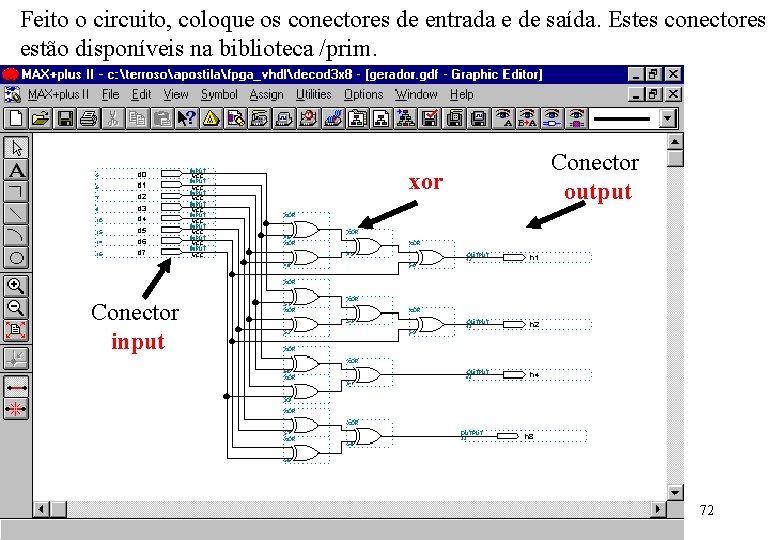

Feito o circuito, coloque os conectores de entrada e de saída. Estes conectores estão disponíveis na biblioteca /prim. xor Conector output Conector input 72

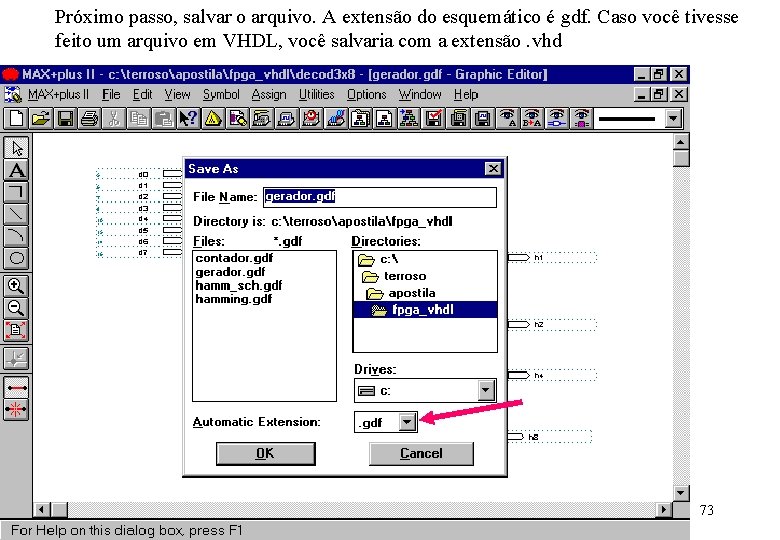

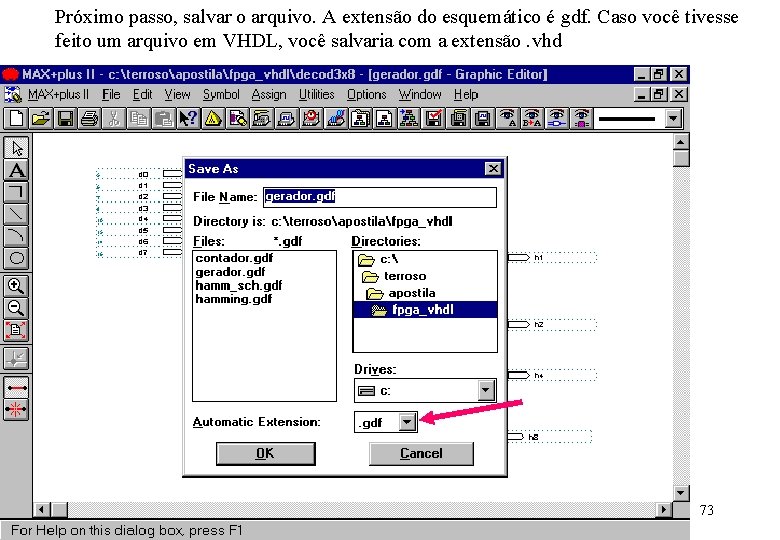

Próximo passo, salvar o arquivo. A extensão do esquemático é gdf. Caso você tivesse feito um arquivo em VHDL, você salvaria com a extensão. vhd 73

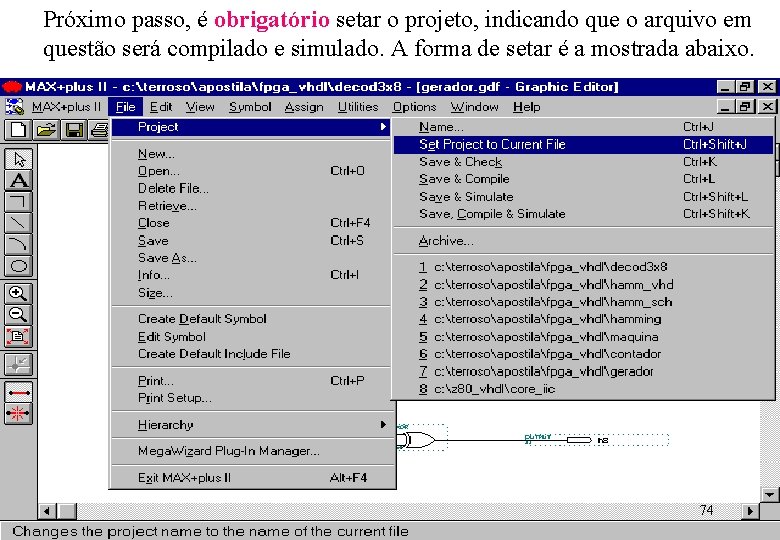

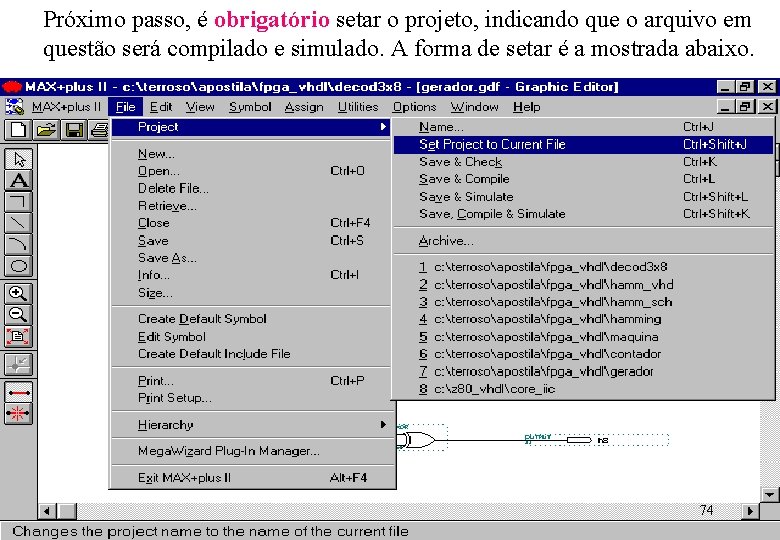

Próximo passo, é obrigatório setar o projeto, indicando que o arquivo em questão será compilado e simulado. A forma de setar é a mostrada abaixo. 74

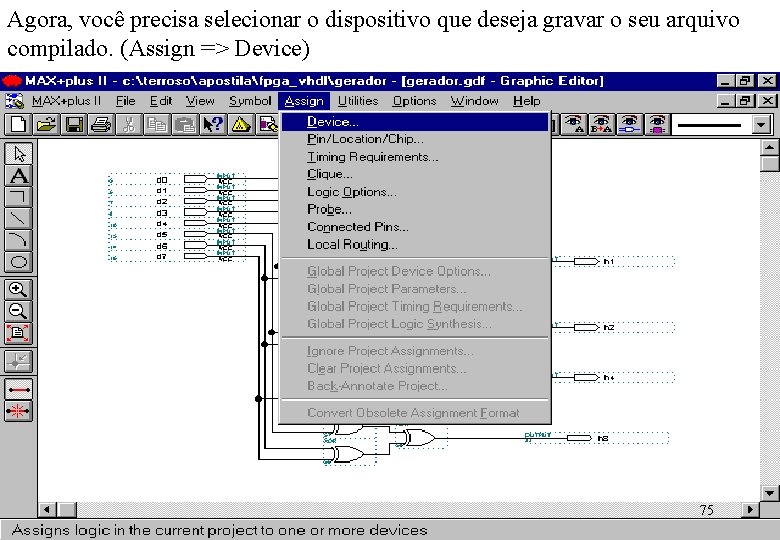

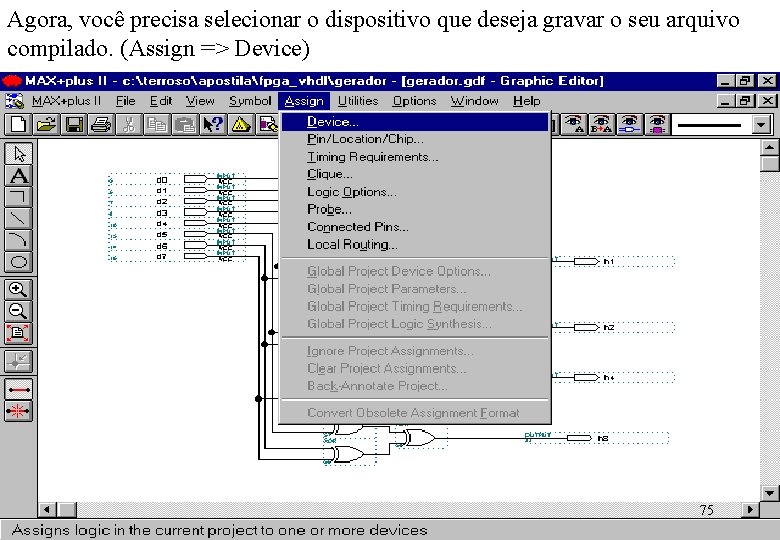

Agora, você precisa selecionar o dispositivo que deseja gravar o seu arquivo compilado. (Assign => Device) 75

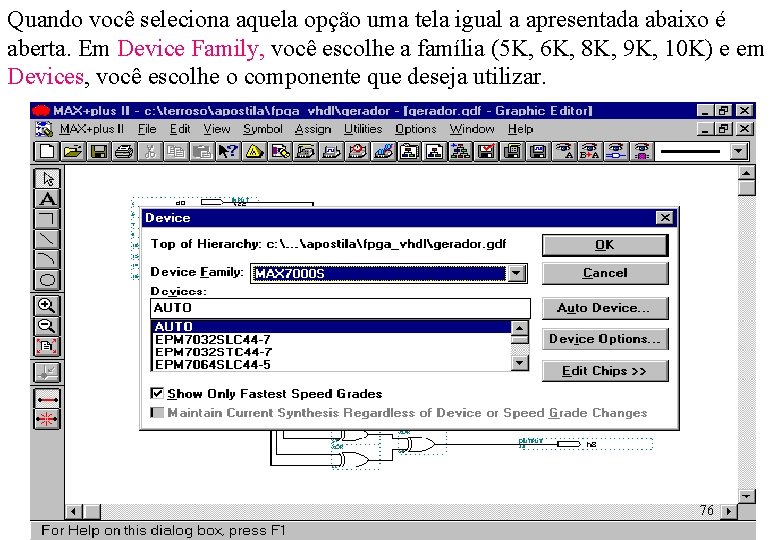

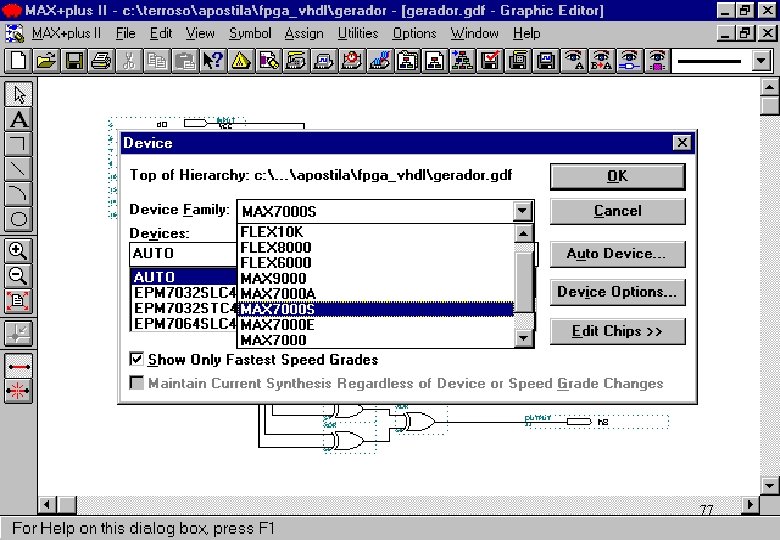

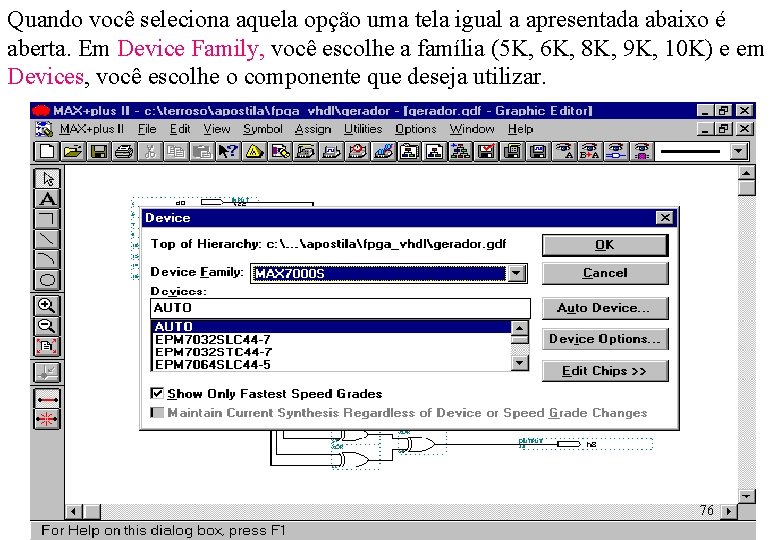

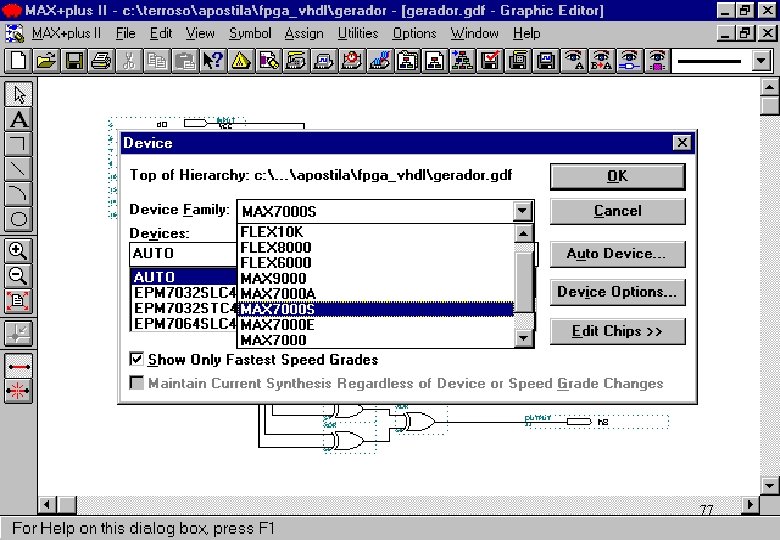

Quando você seleciona aquela opção uma tela igual a apresentada abaixo é aberta. Em Device Family, você escolhe a família (5 K, 6 K, 8 K, 9 K, 10 K) e em Devices, você escolhe o componente que deseja utilizar. 76

77

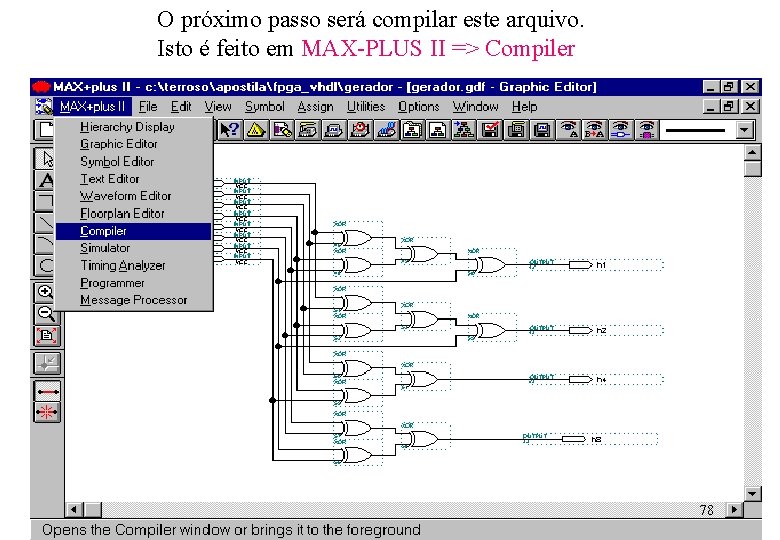

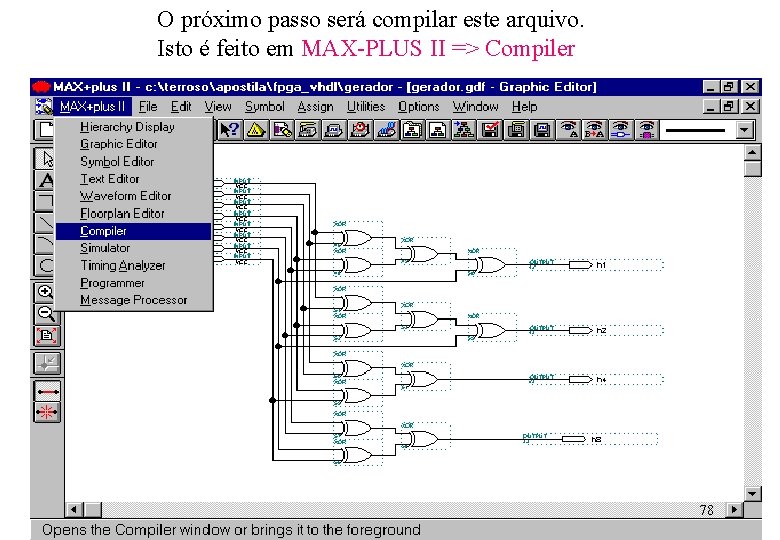

O próximo passo será compilar este arquivo. Isto é feito em MAX-PLUS II => Compiler 78

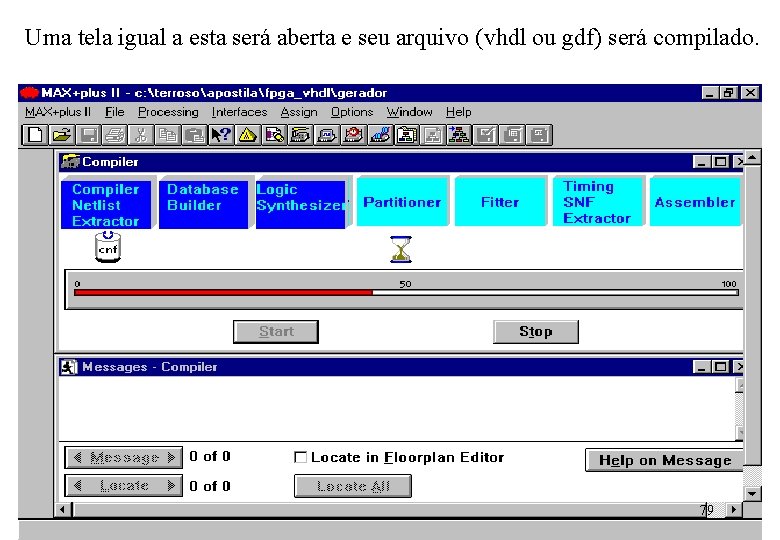

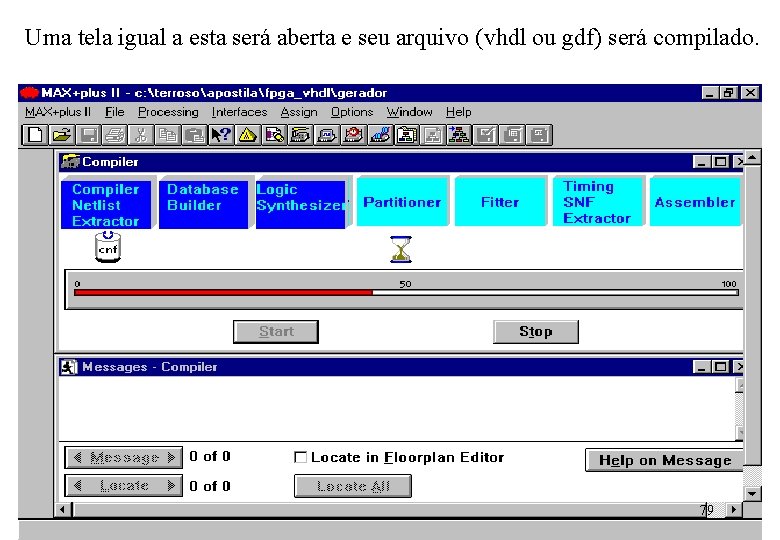

Uma tela igual a esta será aberta e seu arquivo (vhdl ou gdf) será compilado. 79

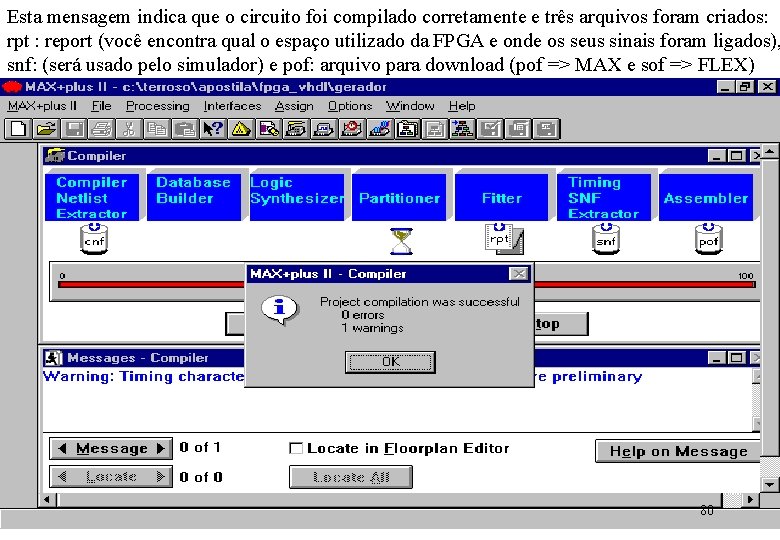

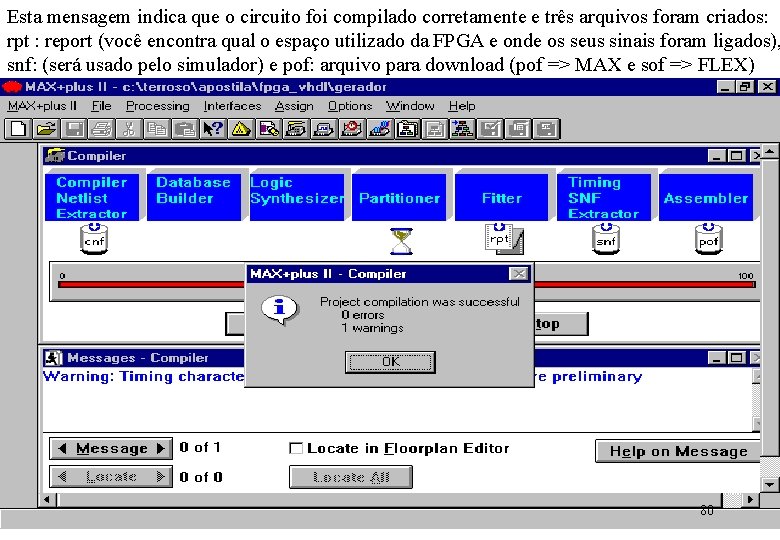

Esta mensagem indica que o circuito foi compilado corretamente e três arquivos foram criados: rpt : report (você encontra qual o espaço utilizado da FPGA e onde os seus sinais foram ligados), snf: (será usado pelo simulador) e pof: arquivo para download (pof => MAX e sof => FLEX) 80

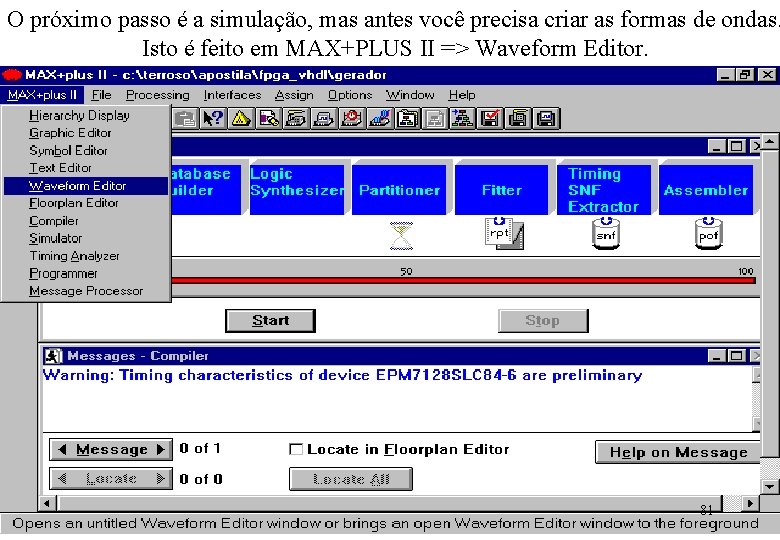

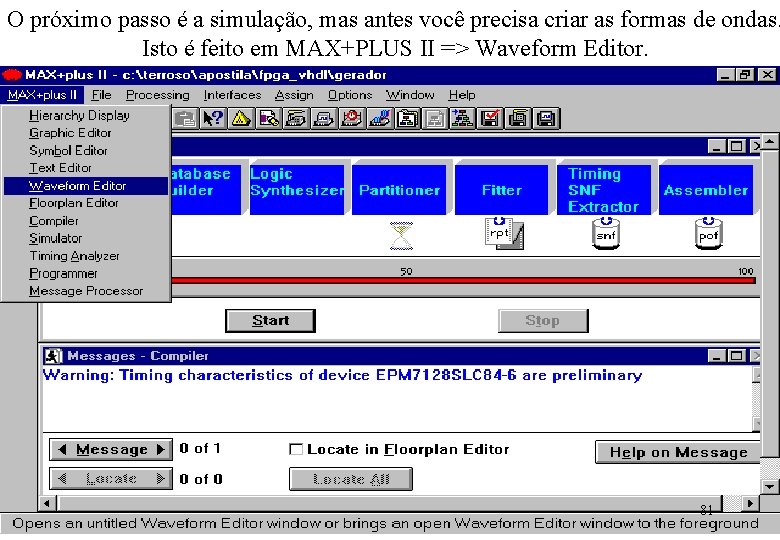

O próximo passo é a simulação, mas antes você precisa criar as formas de ondas. Isto é feito em MAX+PLUS II => Waveform Editor. 81

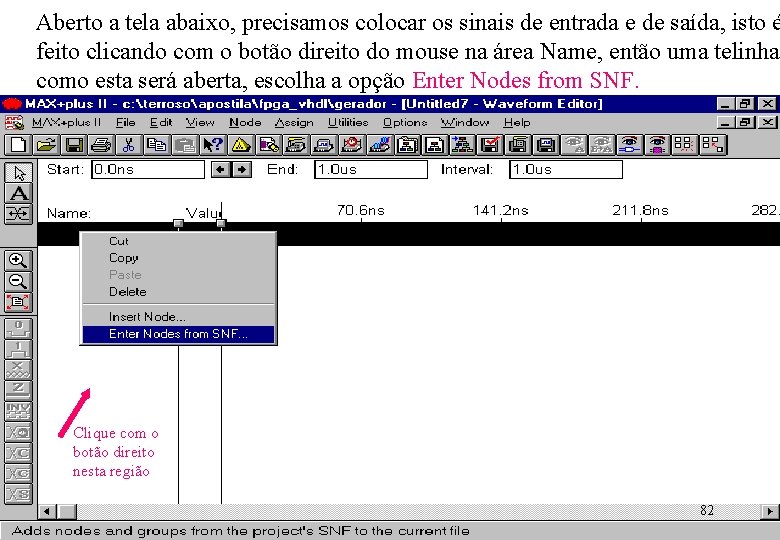

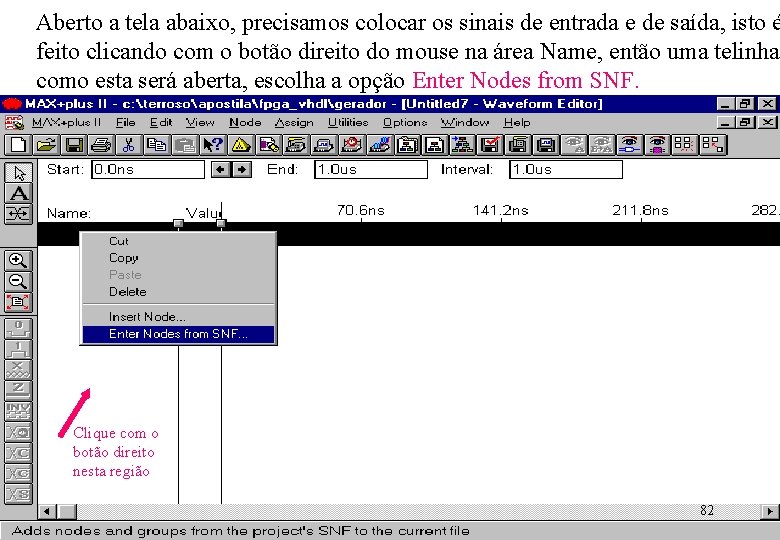

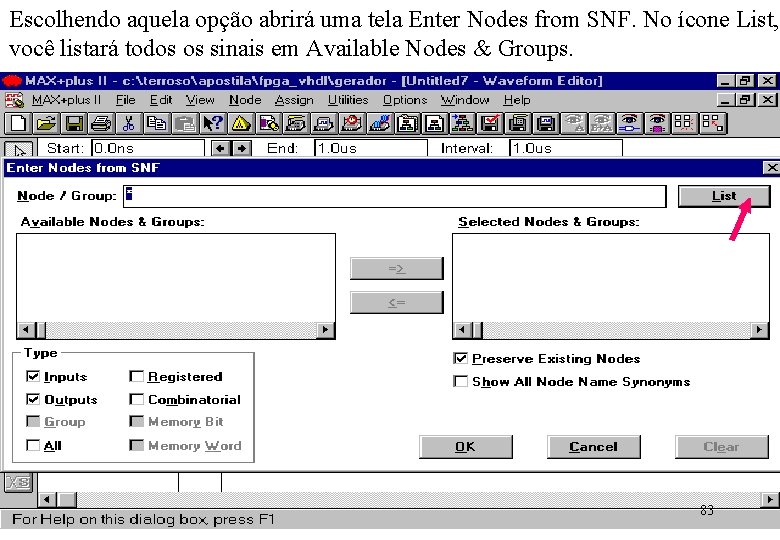

Aberto a tela abaixo, precisamos colocar os sinais de entrada e de saída, isto é feito clicando com o botão direito do mouse na área Name, então uma telinha como esta será aberta, escolha a opção Enter Nodes from SNF. Clique com o botão direito nesta região 82

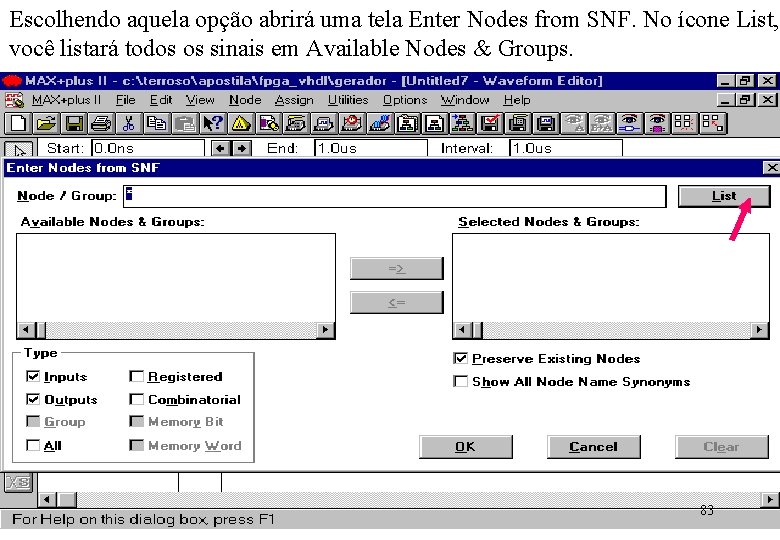

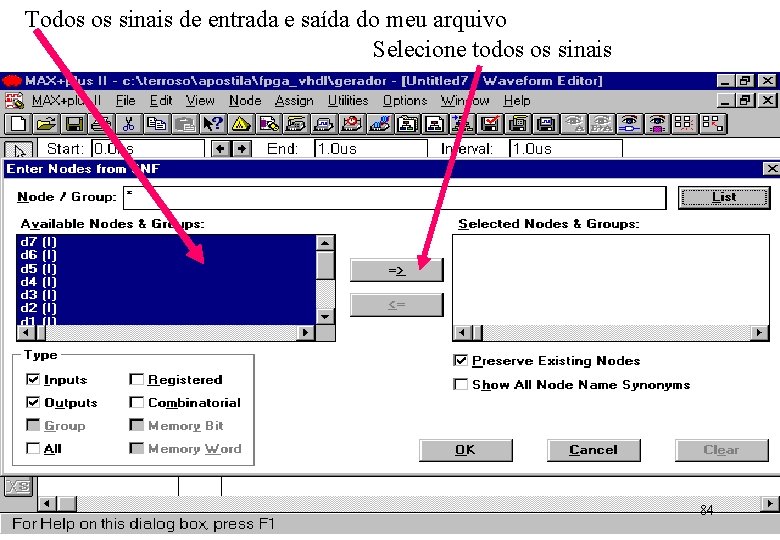

Escolhendo aquela opção abrirá uma tela Enter Nodes from SNF. No ícone List, você listará todos os sinais em Available Nodes & Groups. 83

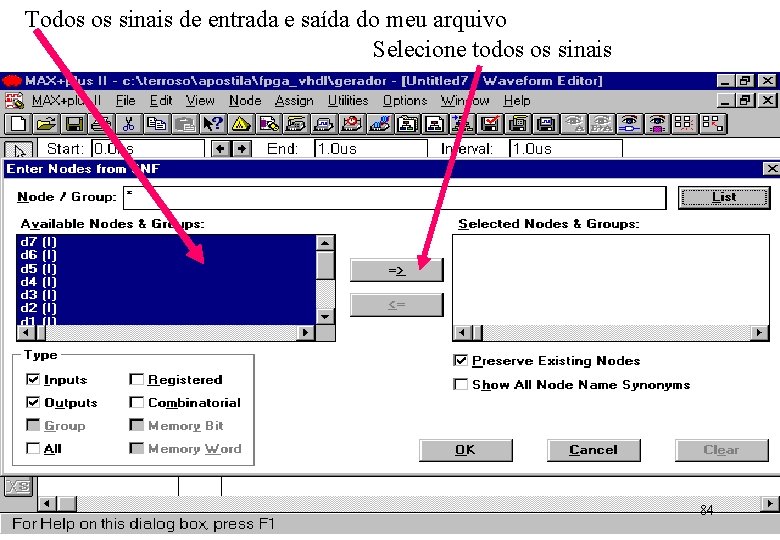

Todos os sinais de entrada e saída do meu arquivo Selecione todos os sinais 84

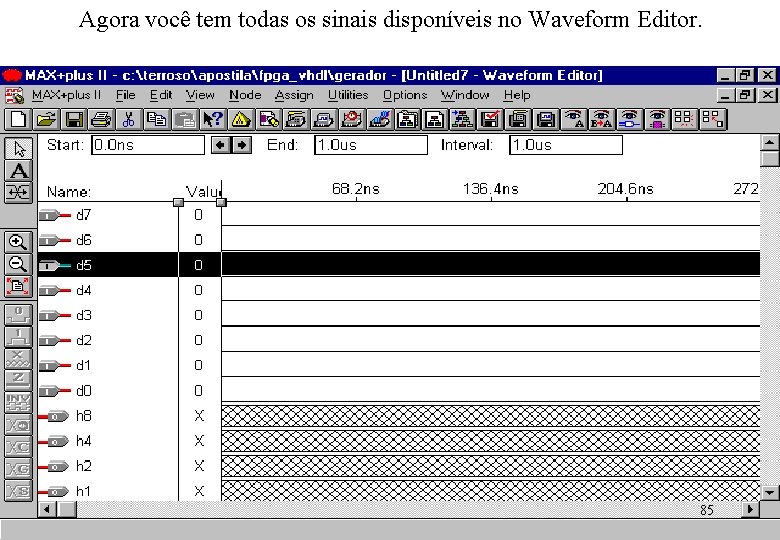

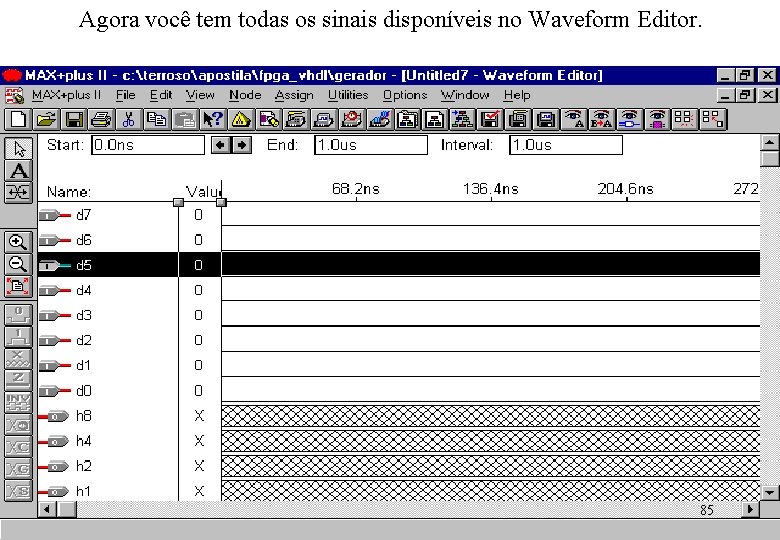

Agora você tem todas os sinais disponíveis no Waveform Editor. 85

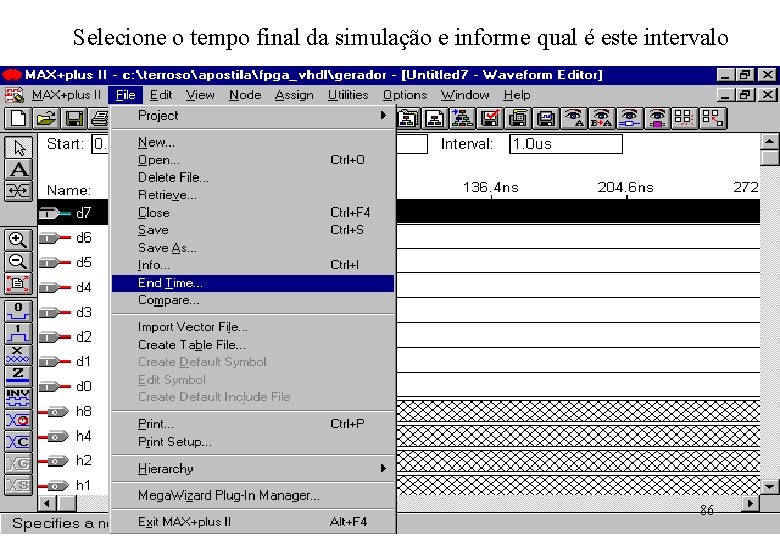

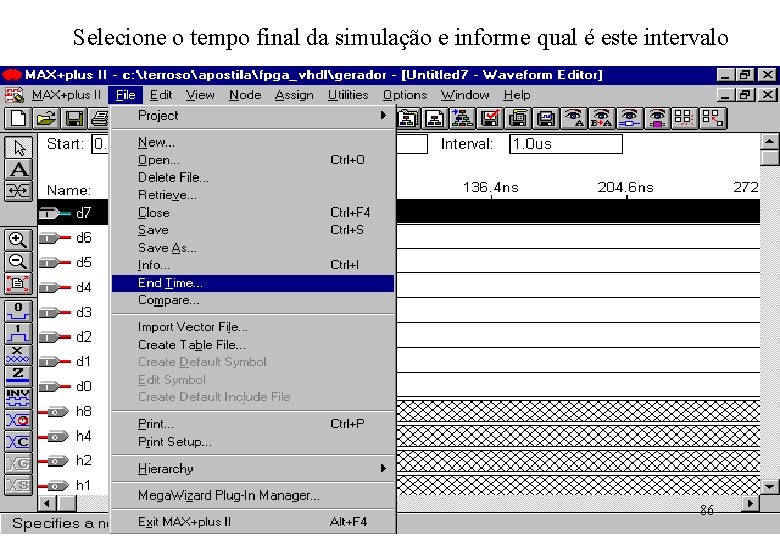

Selecione o tempo final da simulação e informe qual é este intervalo 86

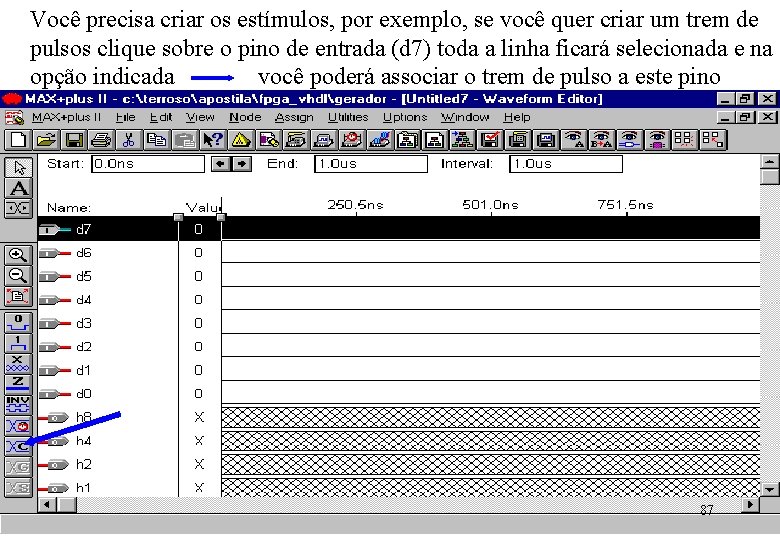

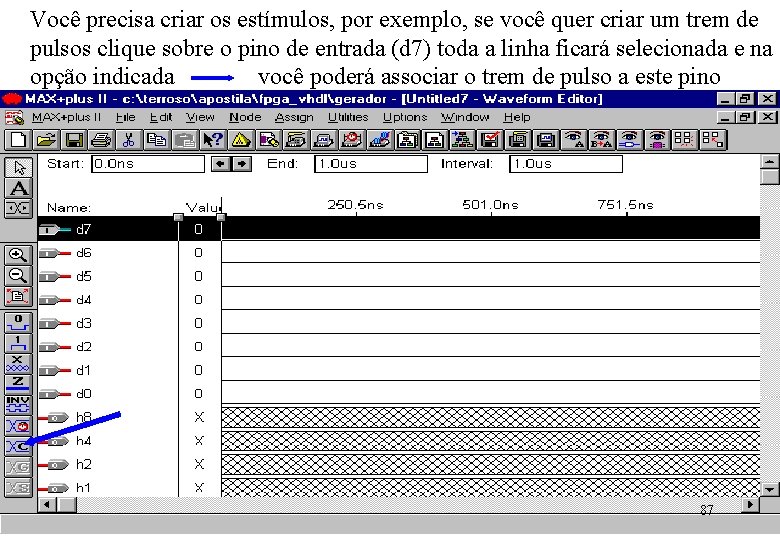

Você precisa criar os estímulos, por exemplo, se você quer criar um trem de pulsos clique sobre o pino de entrada (d 7) toda a linha ficará selecionada e na opção indicada você poderá associar o trem de pulso a este pino 87

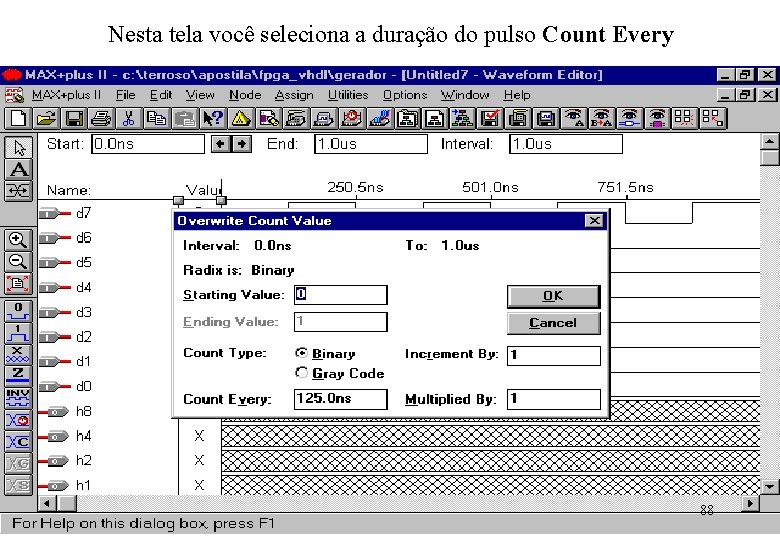

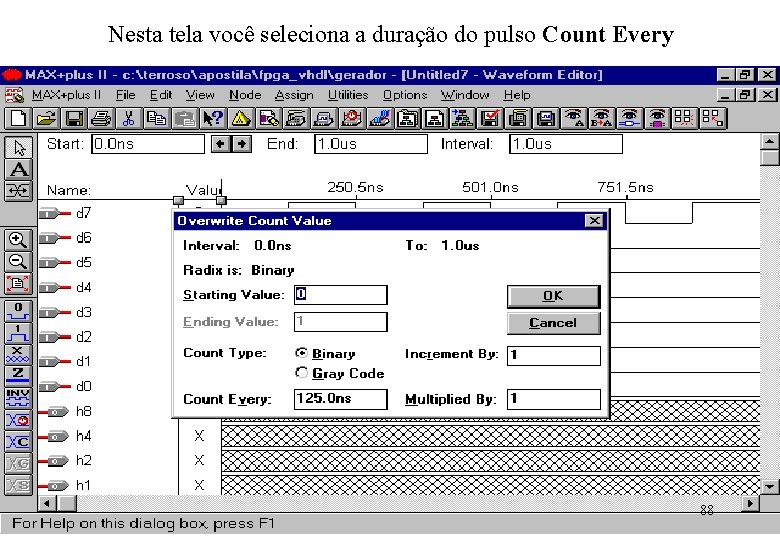

Nesta tela você seleciona a duração do pulso Count Every 88

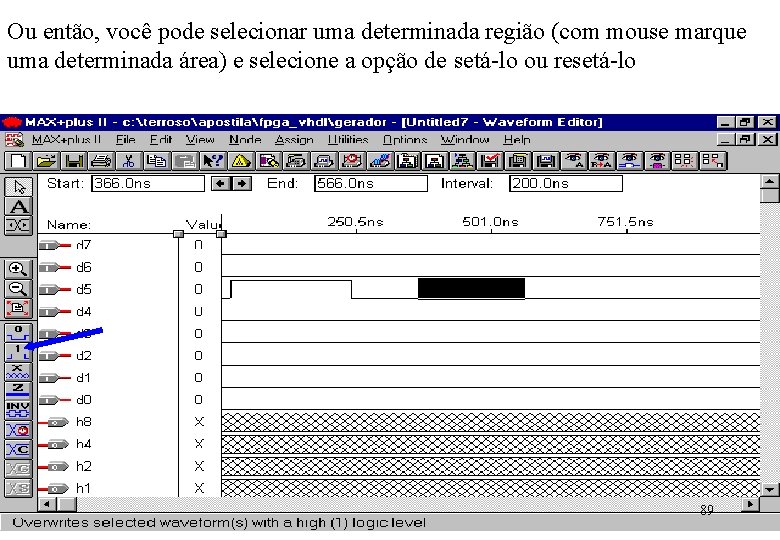

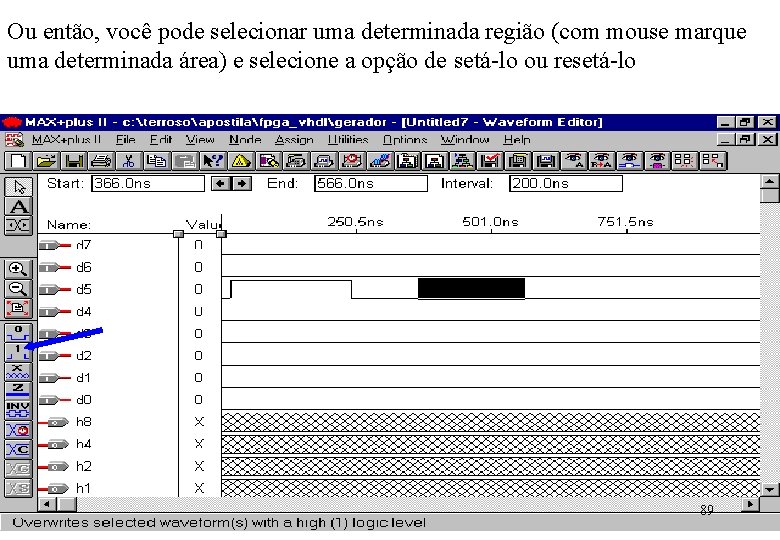

Ou então, você pode selecionar uma determinada região (com mouse marque uma determinada área) e selecione a opção de setá-lo ou resetá-lo 89

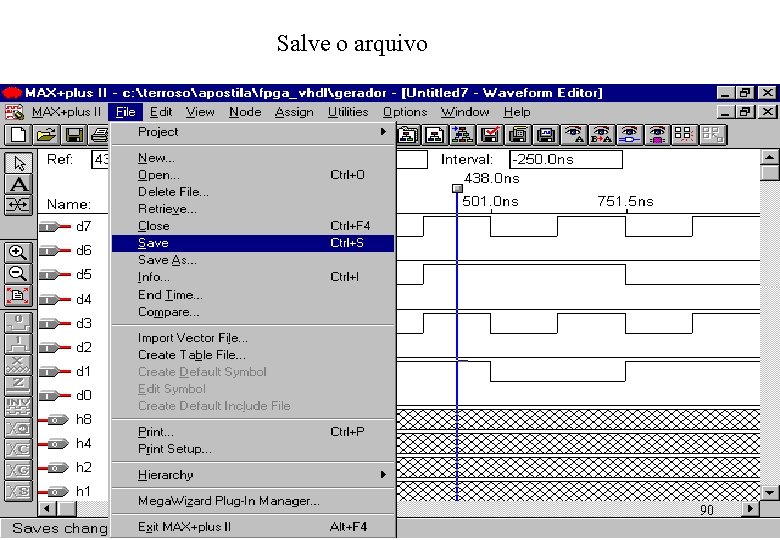

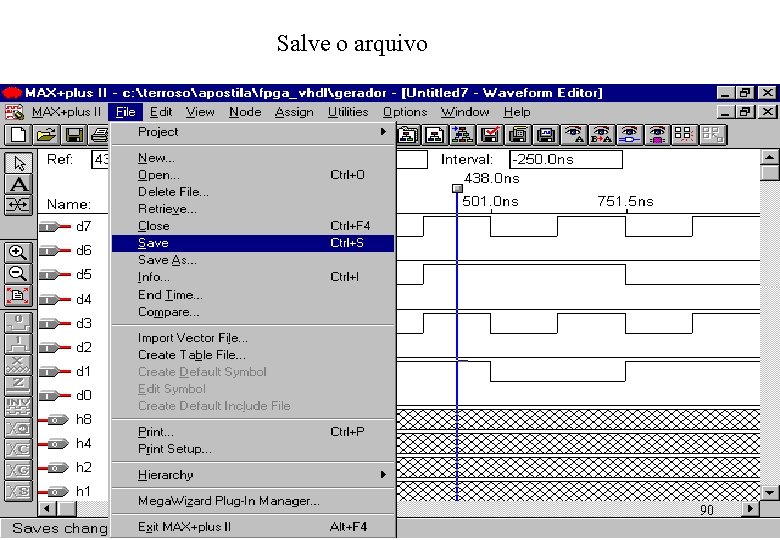

Salve o arquivo 90

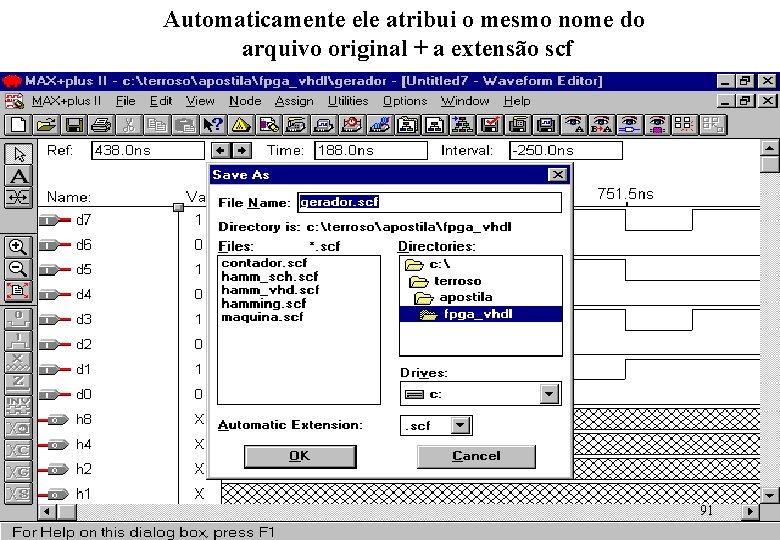

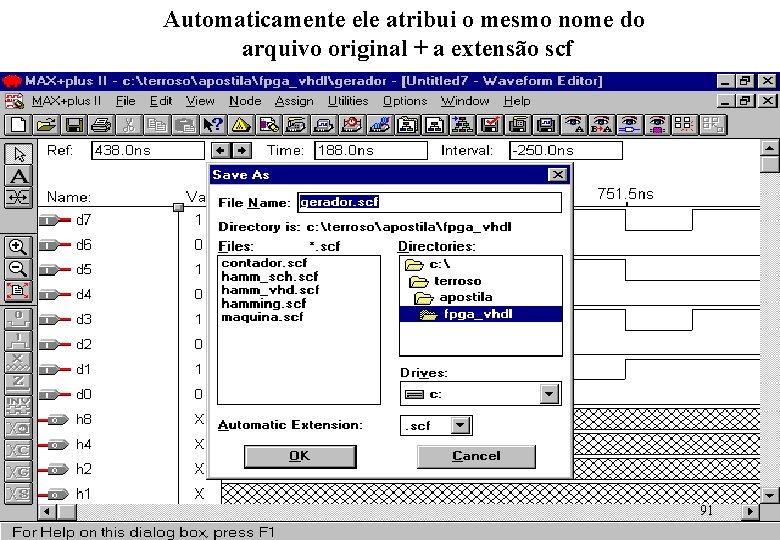

Automaticamente ele atribui o mesmo nome do arquivo original + a extensão scf 91

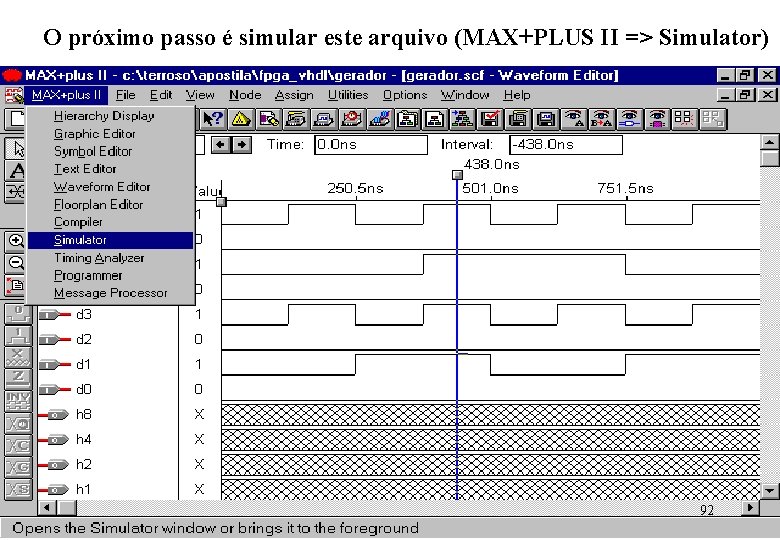

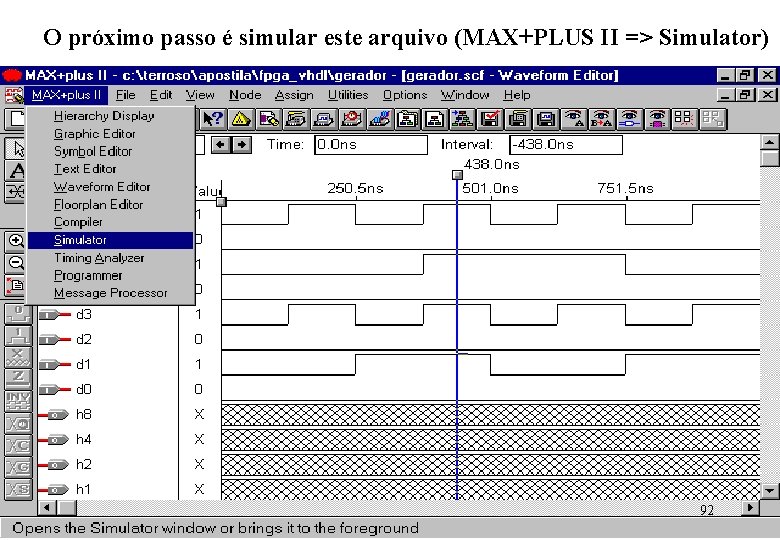

O próximo passo é simular este arquivo (MAX+PLUS II => Simulator) 92

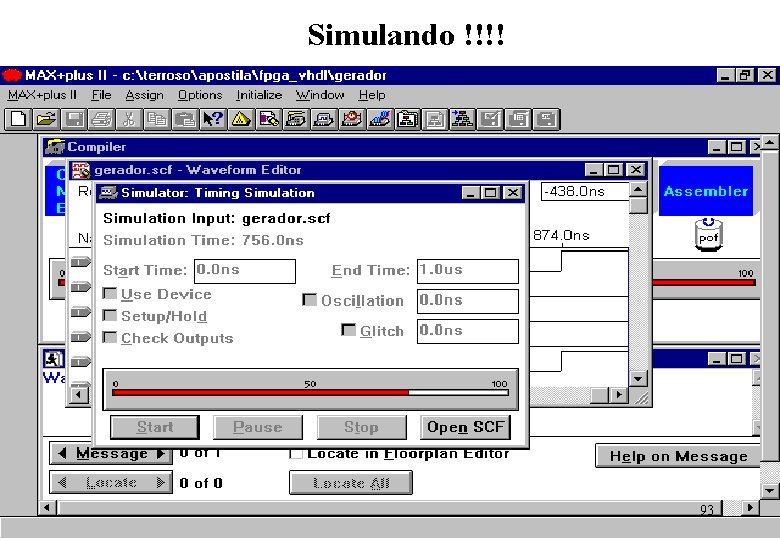

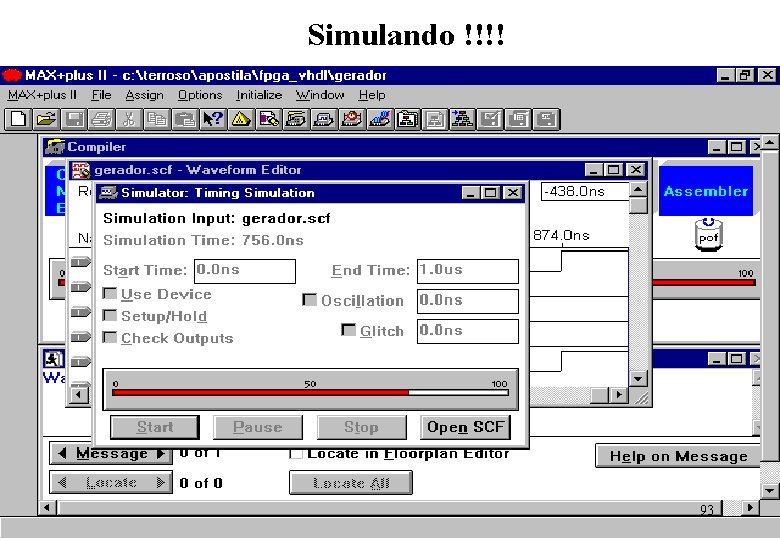

Simulando !!!! 93

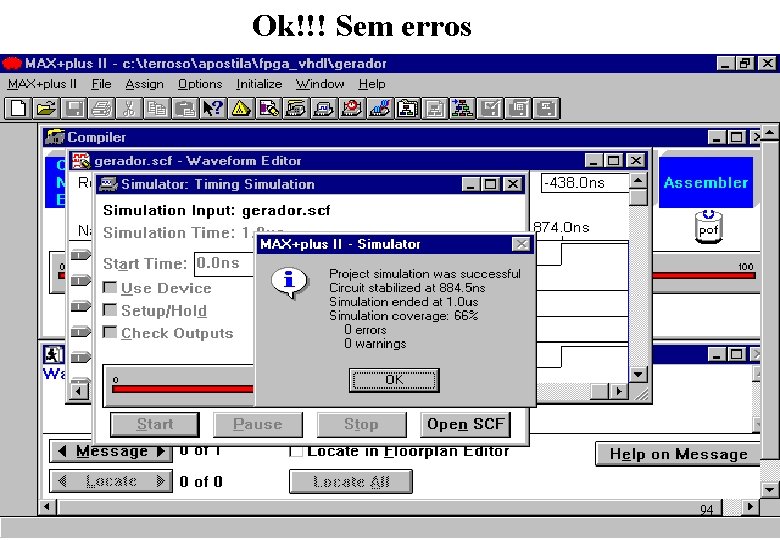

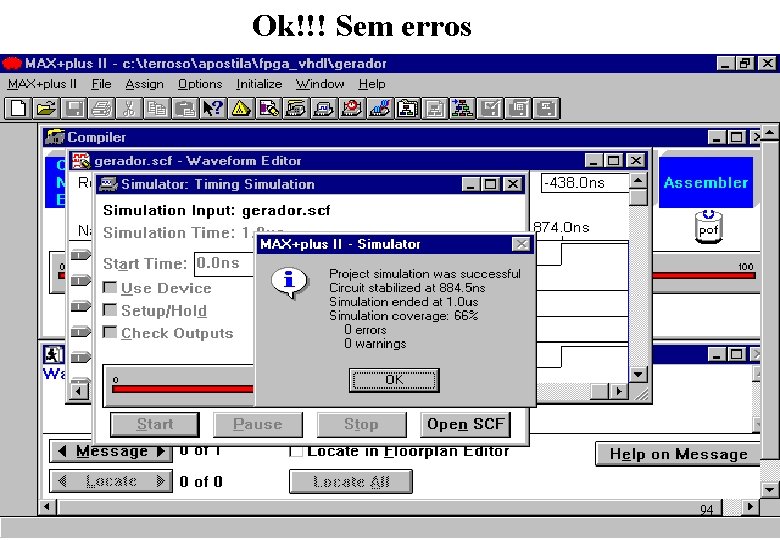

Ok!!! Sem erros 94

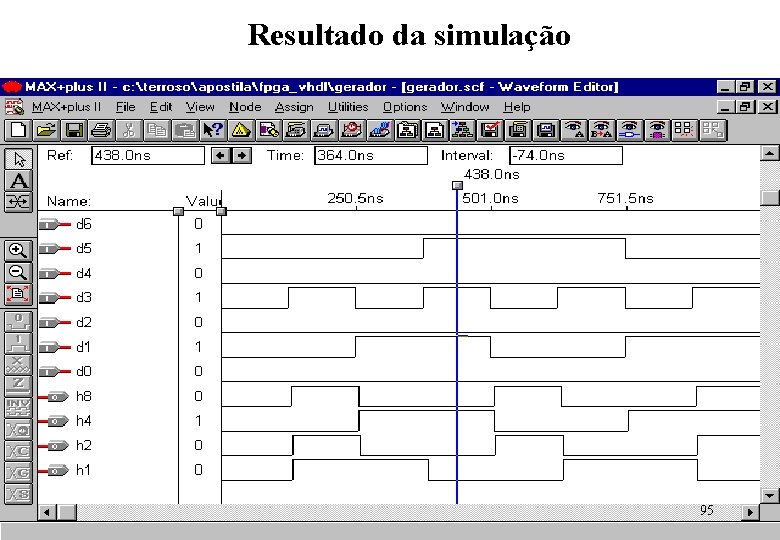

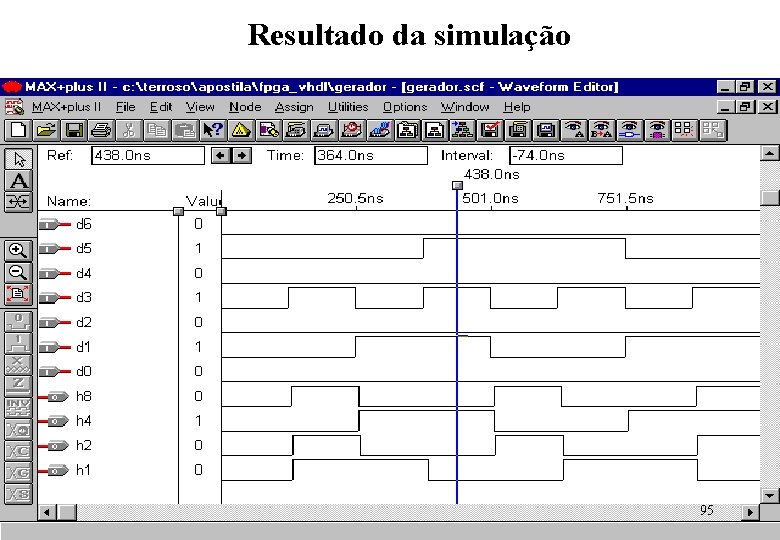

Resultado da simulação 95

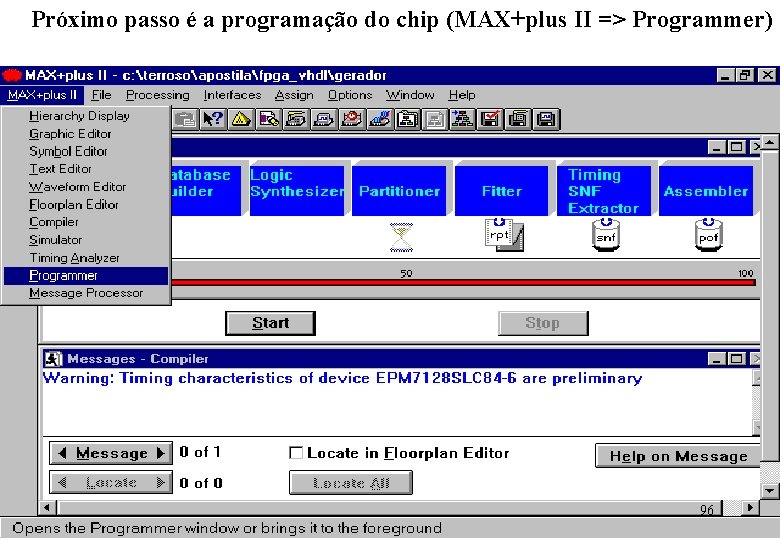

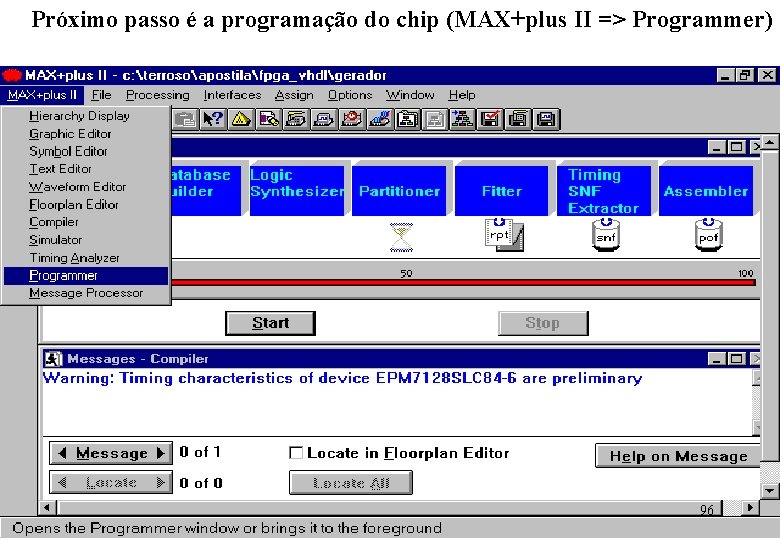

Próximo passo é a programação do chip (MAX+plus II => Programmer) 96

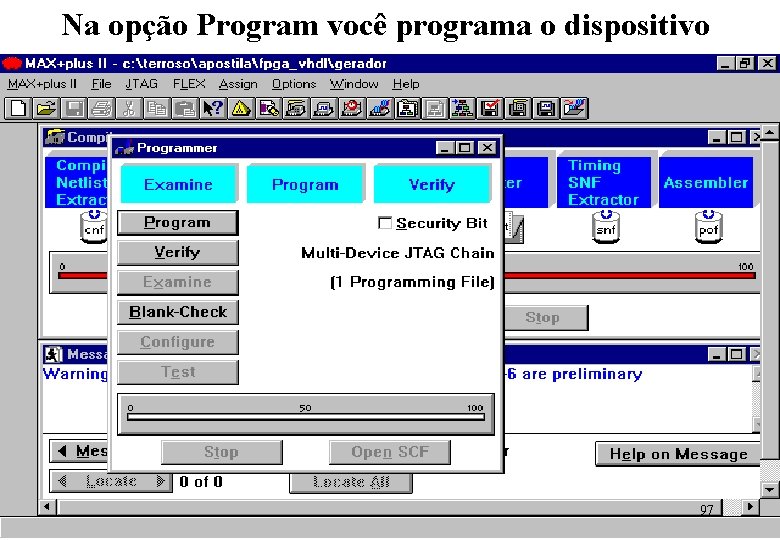

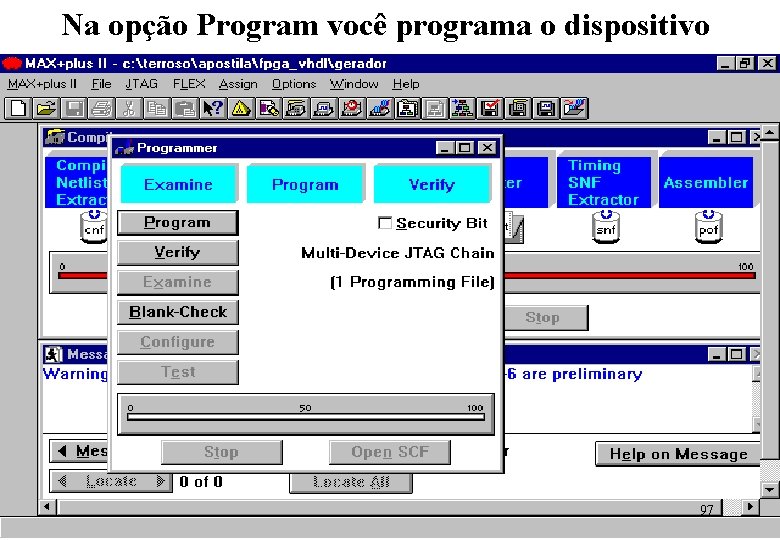

Na opção Program você programa o dispositivo 97

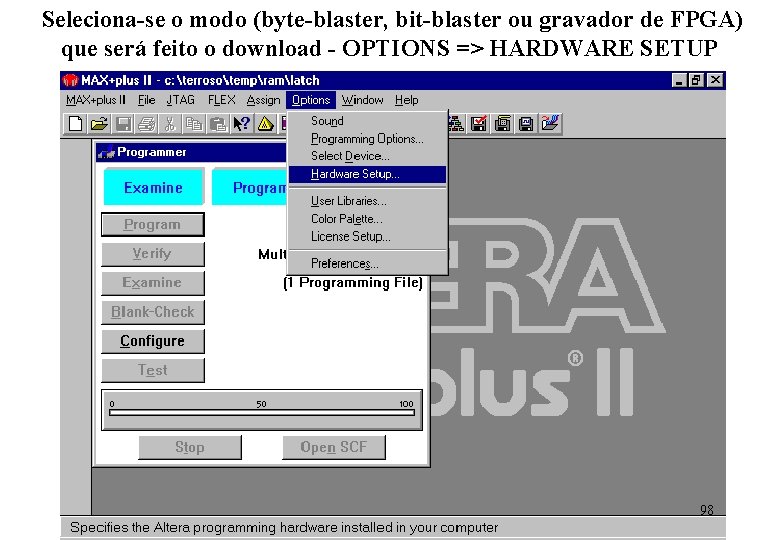

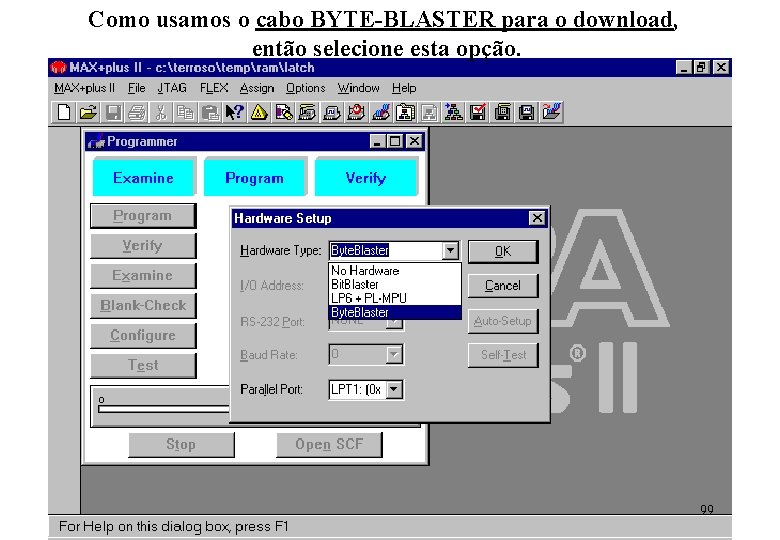

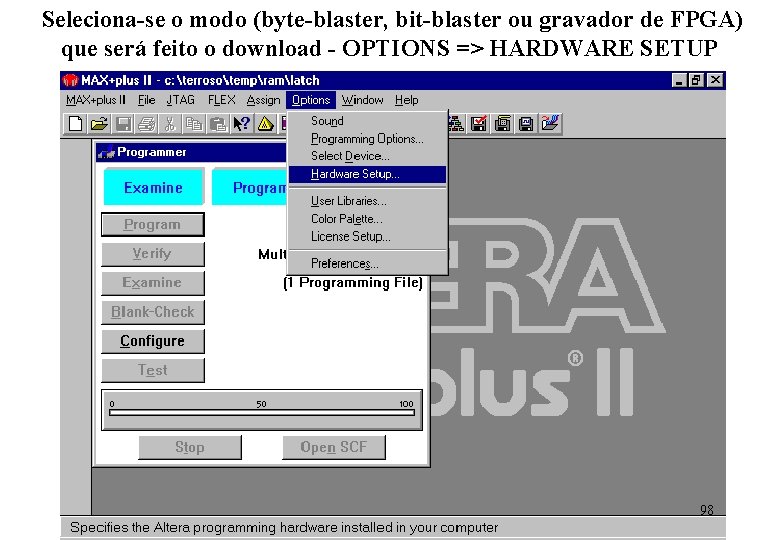

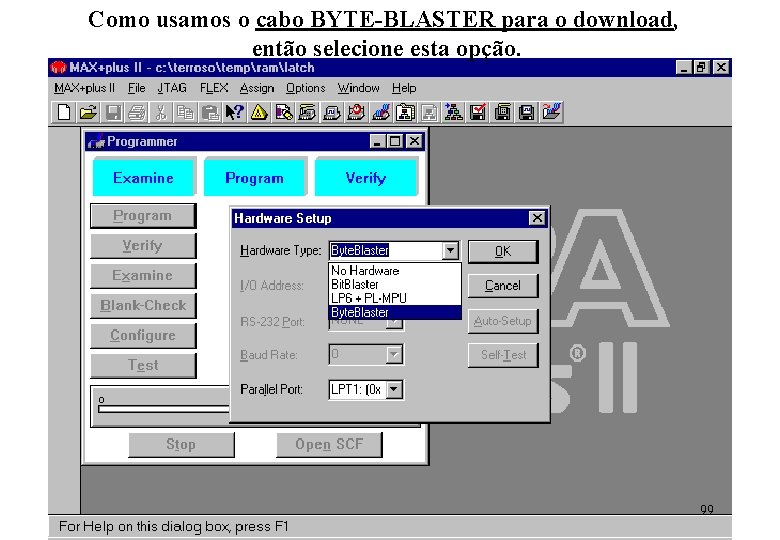

Seleciona-se o modo (byte-blaster, bit-blaster ou gravador de FPGA) que será feito o download - OPTIONS => HARDWARE SETUP 98

Como usamos o cabo BYTE-BLASTER para o download, então selecione esta opção. 99

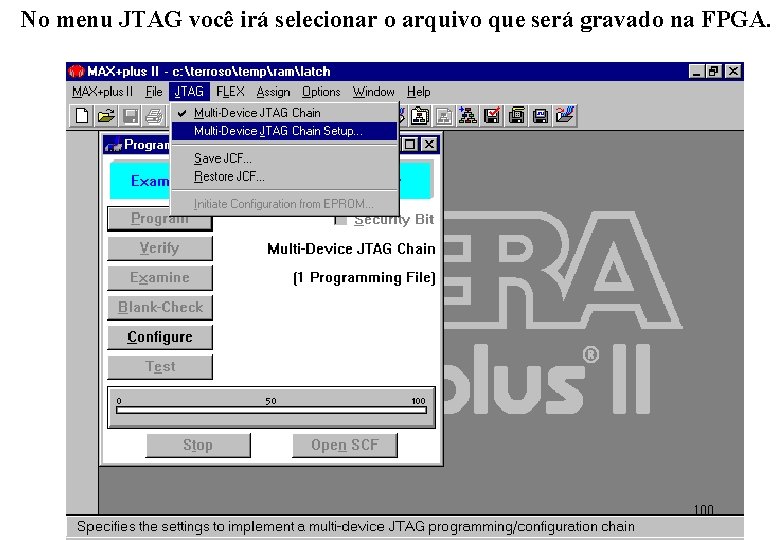

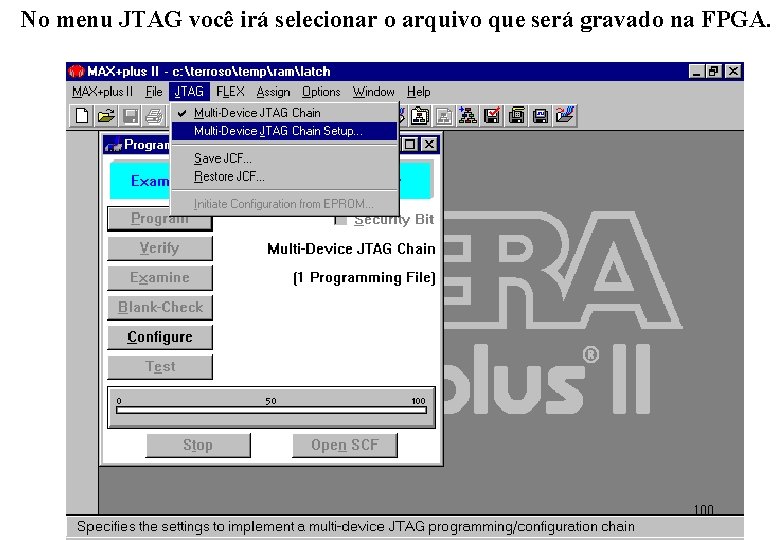

No menu JTAG você irá selecionar o arquivo que será gravado na FPGA. 100

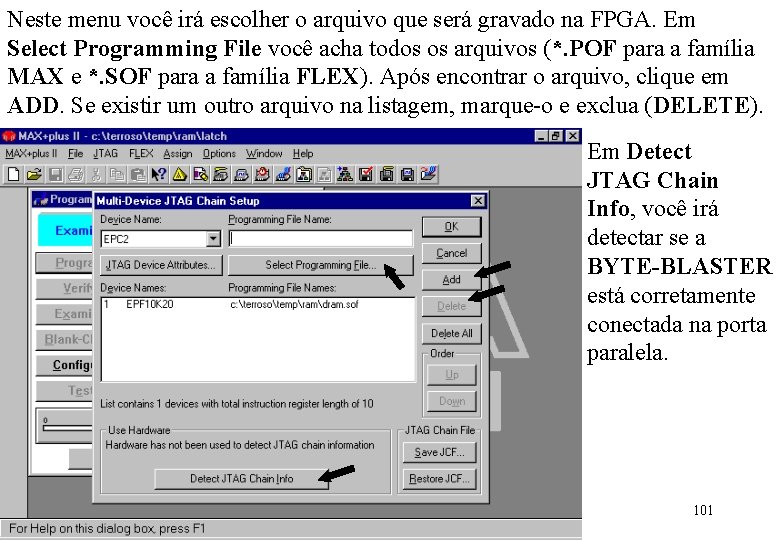

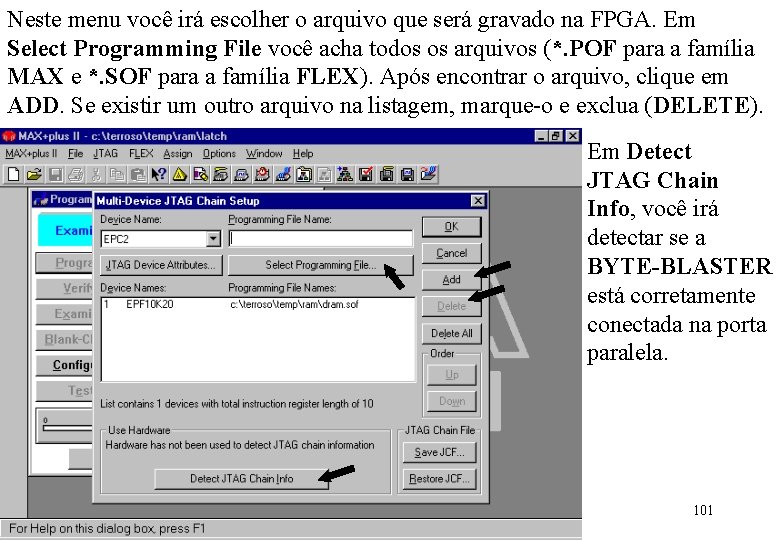

Neste menu você irá escolher o arquivo que será gravado na FPGA. Em Select Programming File você acha todos os arquivos (*. POF para a família MAX e *. SOF para a família FLEX). Após encontrar o arquivo, clique em ADD. Se existir um outro arquivo na listagem, marque-o e exclua (DELETE). Em Detect JTAG Chain Info, você irá detectar se a BYTE-BLASTER está corretamente conectada na porta paralela. 101

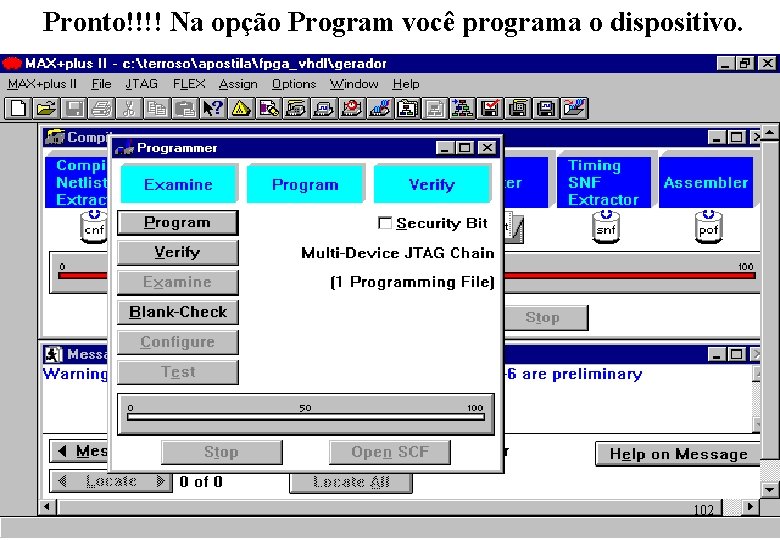

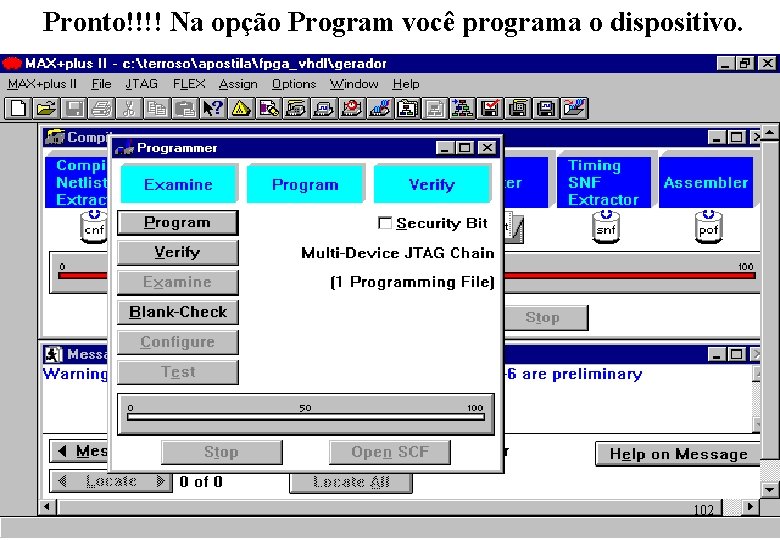

Pronto!!!! Na opção Program você programa o dispositivo. 102

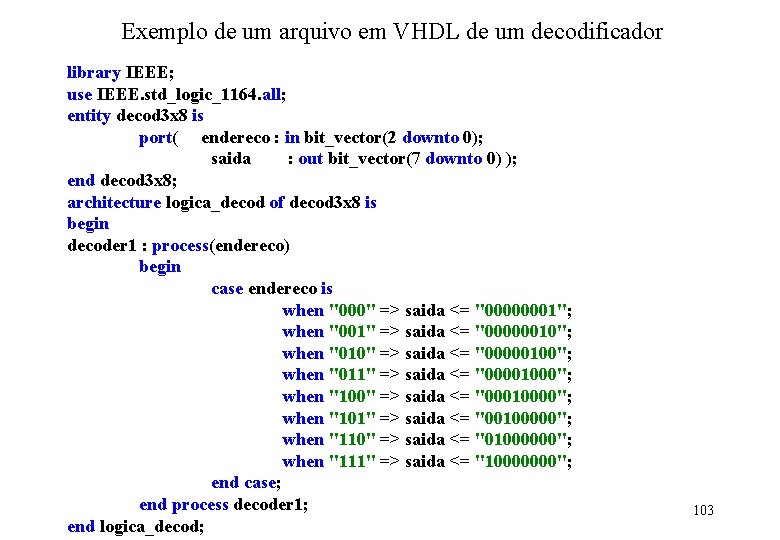

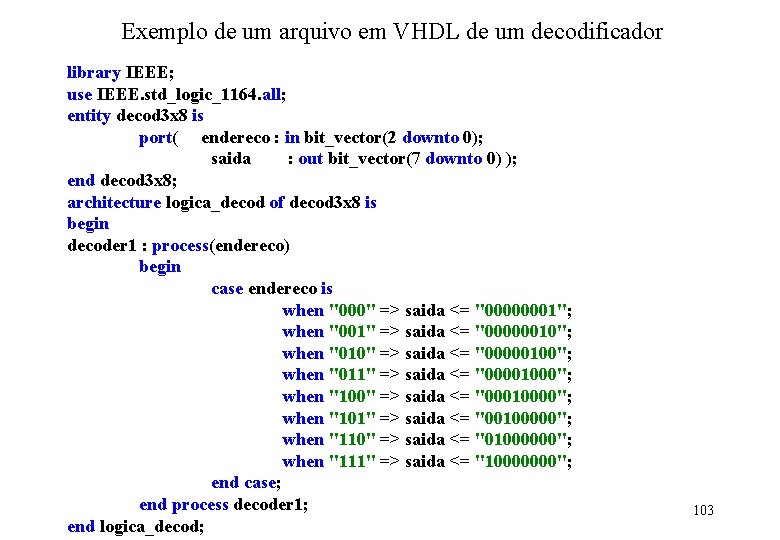

Exemplo de um arquivo em VHDL de um decodificador library IEEE; use IEEE. std_logic_1164. all; entity decod 3 x 8 is port( endereco : in bit_vector(2 downto 0); saida : out bit_vector(7 downto 0) ); end decod 3 x 8; architecture logica_decod of decod 3 x 8 is begin decoder 1 : process(endereco) begin case endereco is when "000" => saida <= "00000001"; when "001" => saida <= "00000010"; when "010" => saida <= "00000100"; when "011" => saida <= "00001000"; when "100" => saida <= "00010000"; when "101" => saida <= "00100000"; when "110" => saida <= "01000000"; when "111" => saida <= "10000000"; end case; end process decoder 1; end logica_decod; 103

CABO BYTE-BLASTER

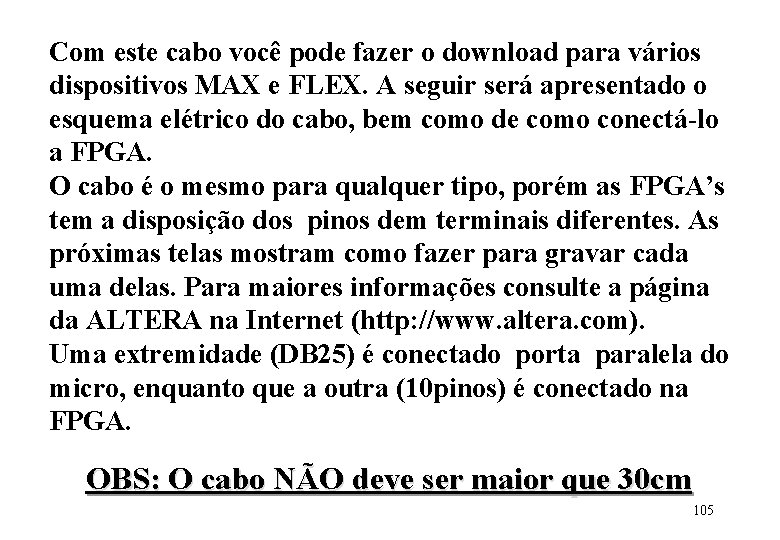

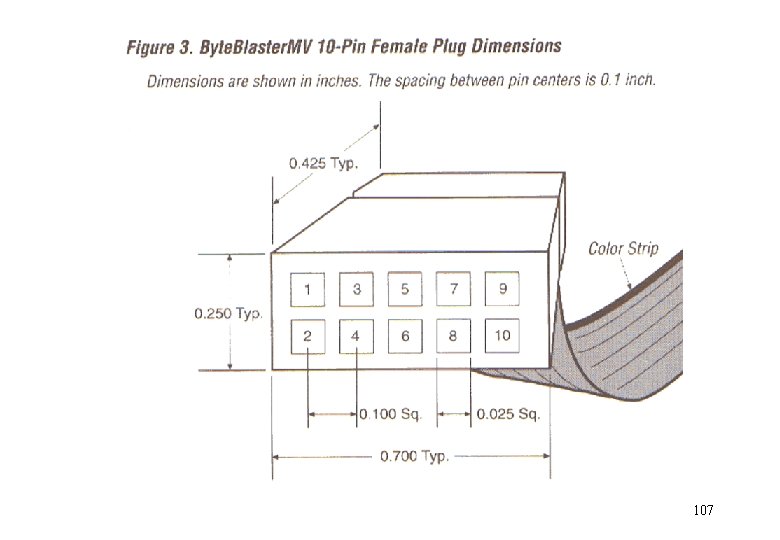

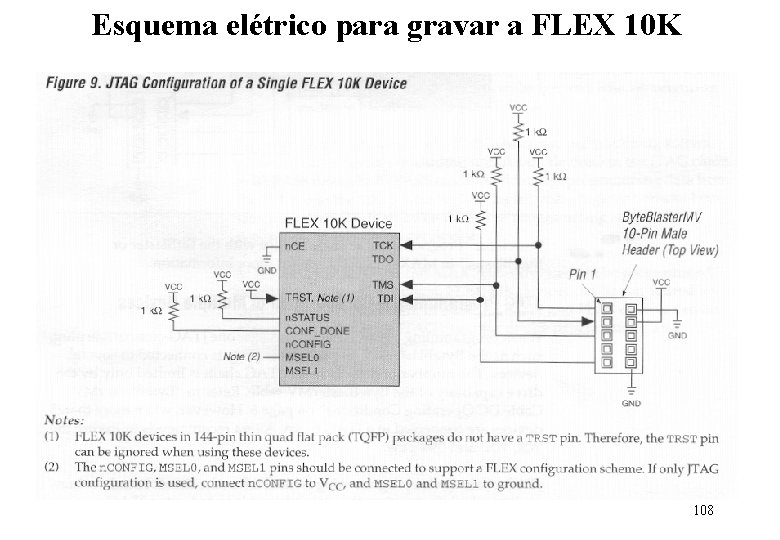

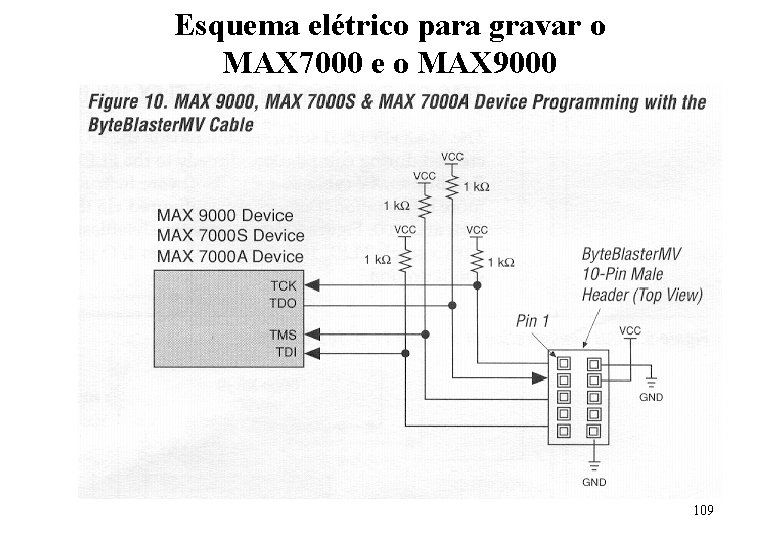

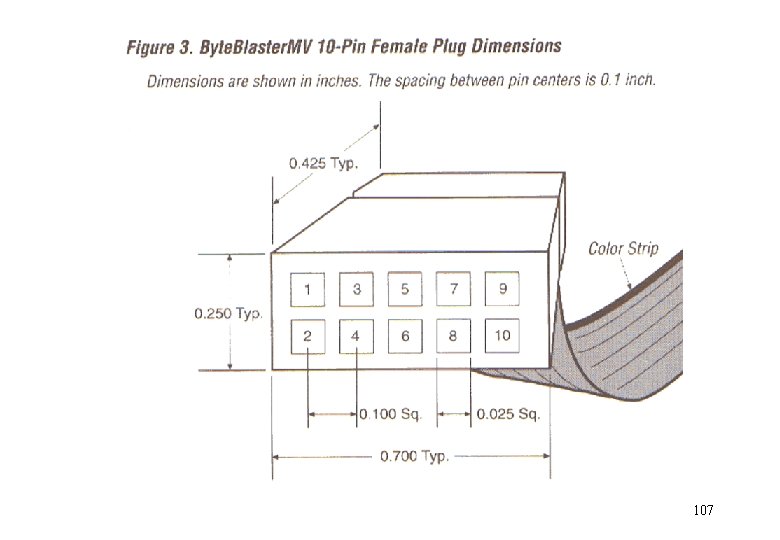

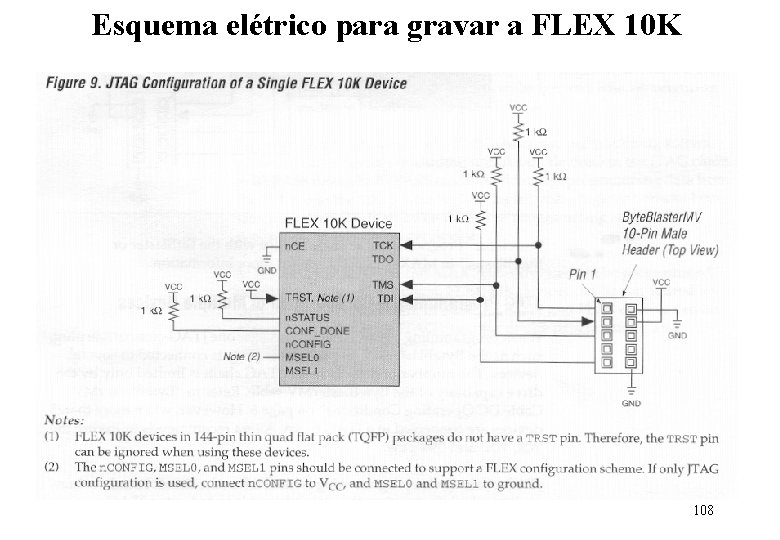

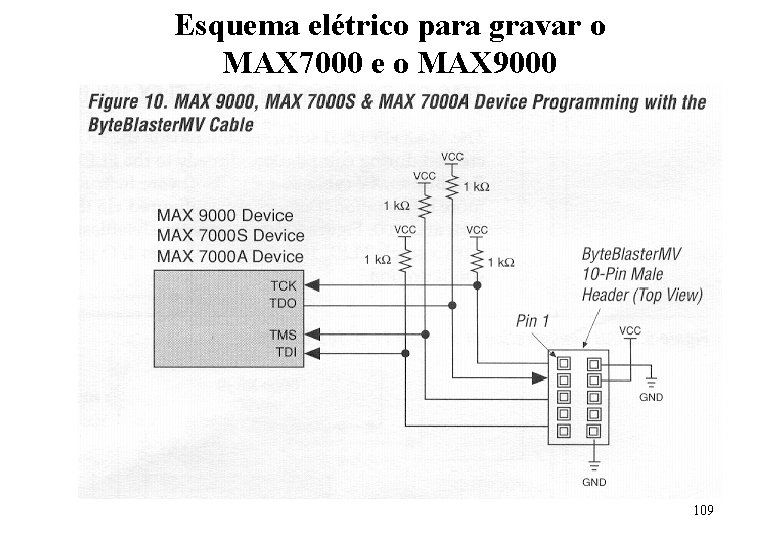

Com este cabo você pode fazer o download para vários dispositivos MAX e FLEX. A seguir será apresentado o esquema elétrico do cabo, bem como de como conectá-lo a FPGA. O cabo é o mesmo para qualquer tipo, porém as FPGA’s tem a disposição dos pinos dem terminais diferentes. As próximas telas mostram como fazer para gravar cada uma delas. Para maiores informações consulte a página da ALTERA na Internet (http: //www. altera. com). Uma extremidade (DB 25) é conectado porta paralela do micro, enquanto que a outra (10 pinos) é conectado na FPGA. OBS: O cabo NÃO deve ser maior que 30 cm 105

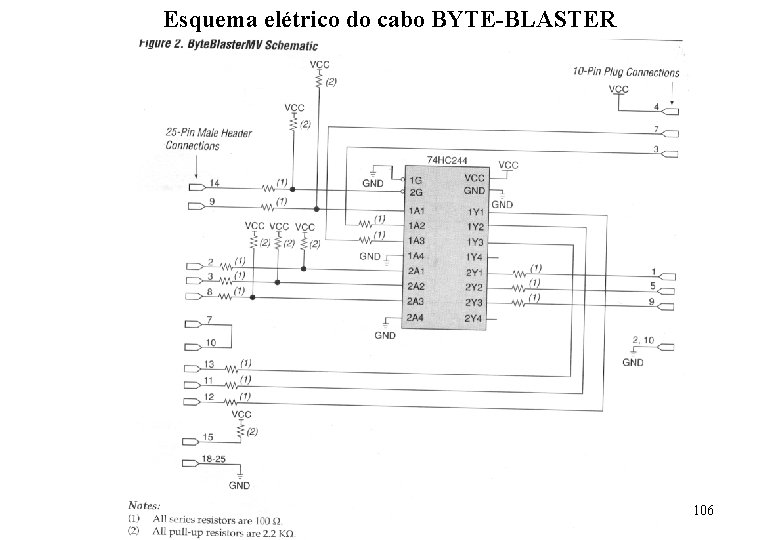

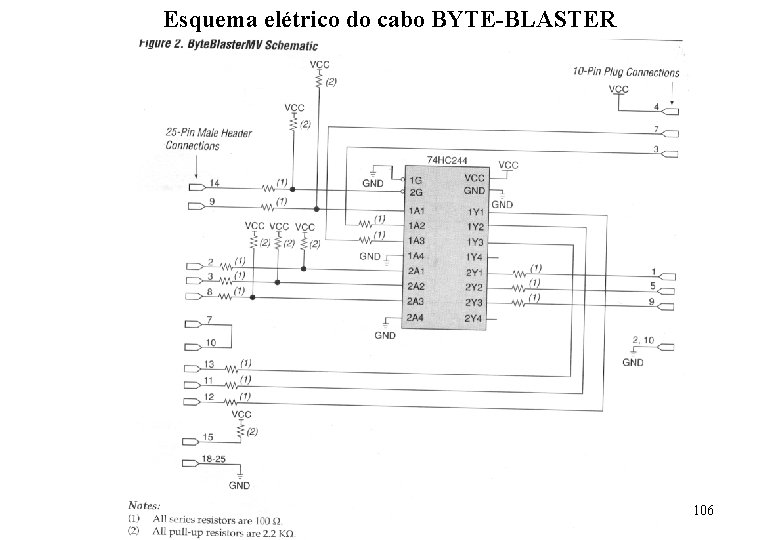

Esquema elétrico do cabo BYTE-BLASTER 106

107

Esquema elétrico para gravar a FLEX 10 K 108

Esquema elétrico para gravar o MAX 7000 e o MAX 9000 109

2. 8 BIBLIOGRAFIA Bostock, Geoff, FPGAs and programmable LSI : a designer's handbook. Oxford : Butterworth-Heinemann, 1996. 216 p. Hachtel, Gary D. ; Somenzi, Fabio, Logic synthesis and verification algorithms. Boston : Kluwer Academic, 1996. 564 p. Brown, Stephen D. et al. Field-programmable gate arrays. Boston : Kluwer Academic, 1992. 206 p. Trimberger, Stephen M. (Ed). Field-programmable gate array technology. Boston : Kluwer Academic, 1994. 258 p. Grünbacher, Herbert ; Hartenstein, Reiner W. (Ed. ). Field-programmable gate arrays : architectures and tools for rapid prototyping. Berlin : Springer, 1993. 220 p. IEEE Workshop on FPGAs for Custom Computing Machines (1993 : Napa) Proceedings. ; Buell, Duncan A. ; Pocek, Kenneth L. (Ed. ). Los Alamitos, CA : IEEE Computer Society Press, 1993. 212 p. CHANG, K. C. , Digital Design and Modeling with VHDL and Synthesis. IEEE Computer Society Press, 1997 AIRIAU, R. et all. VHDL du langage à la modélisation. Presses Polytechniques Universitaires Romandes, 1990. MAX+PLUS II & VHDL, Customer Training - ALTERA. MAX+PLUS II, Programmable Logic Development System - Getting Started. ALTERA, Version 6. 0, 1995. VHDL Reference Guide, ACTIVE-VHDL Series Book 1. ALDEC, 1998. INTERNET: ftp: //ftp. cs. adelaide. edu. au/pub/VHDL http: //www. altera. com http: //www. aldec. com 110