Quartus II IT Cook Book VHDL FPGA Section

오브젝트 Quartus II 사용 IT Cook. Book, VHDL을 이용한 FPGA 디지털 설계

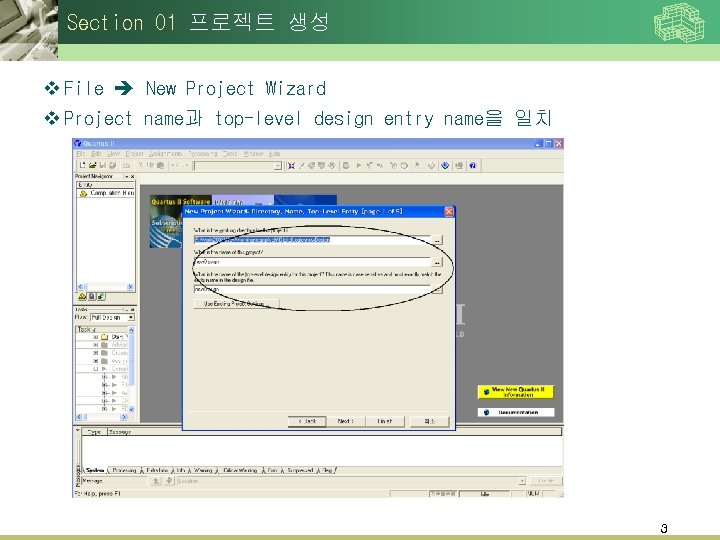

Section 01 프로젝트 생성 v File New Project Wizard v Project name과 top-level design entry name을 일치 3

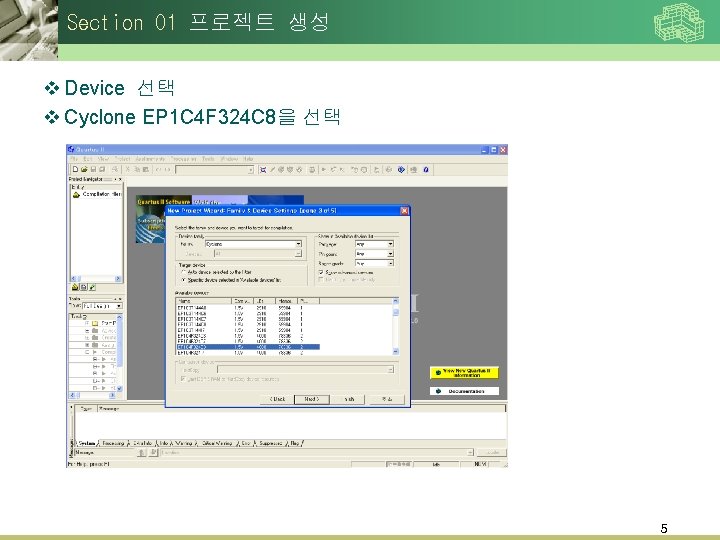

Section 01 프로젝트 생성 v Device 선택 v Cyclone EP 1 C 4 F 324 C 8을 선택 5

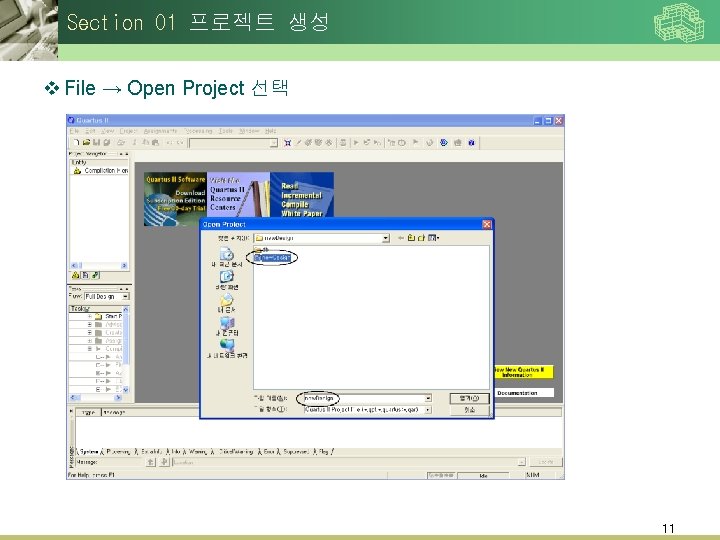

Section 01 프로젝트 생성 v File → Open Project 선택 11

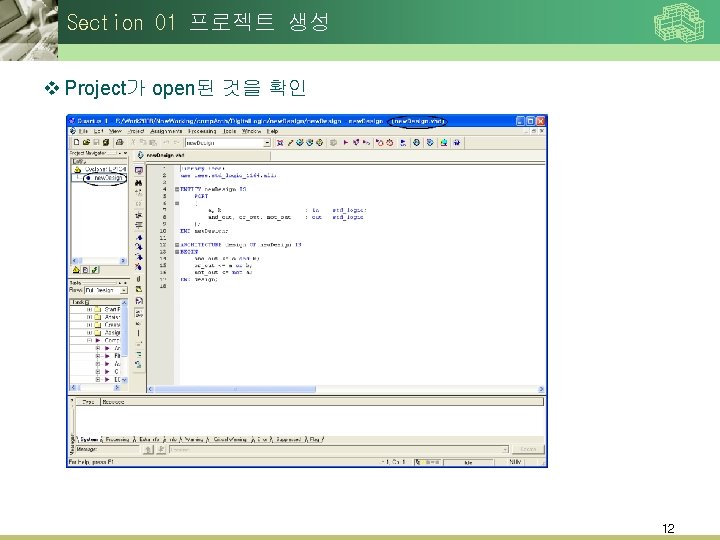

Section 01 프로젝트 생성 v Project가 open된 것을 확인 12

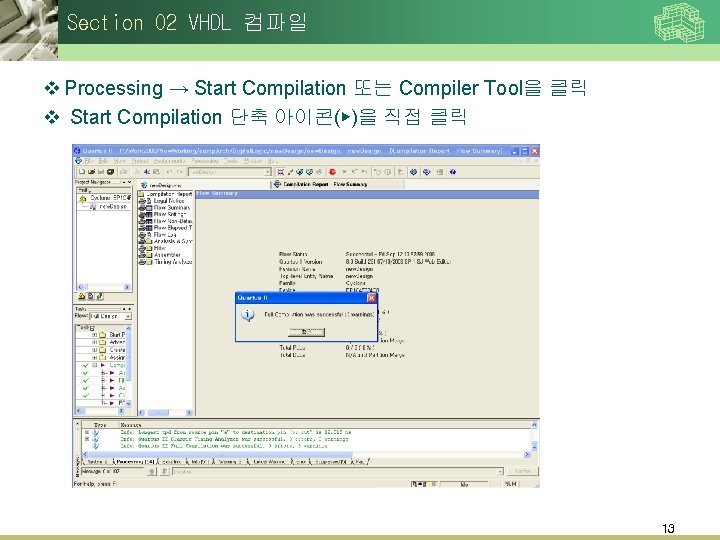

Section 02 VHDL 컴파일 v Processing → Start Compilation 또는 Compiler Tool을 클릭 v Start Compilation 단축 아이콘(▶)을 직접 클릭 13

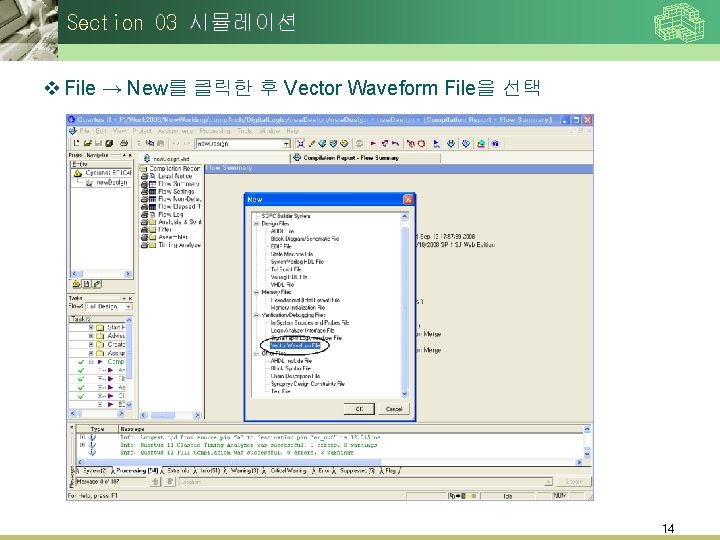

Section 03 시뮬레이션 v File → New를 클릭한 후 Vector Waveform File을 선택 14

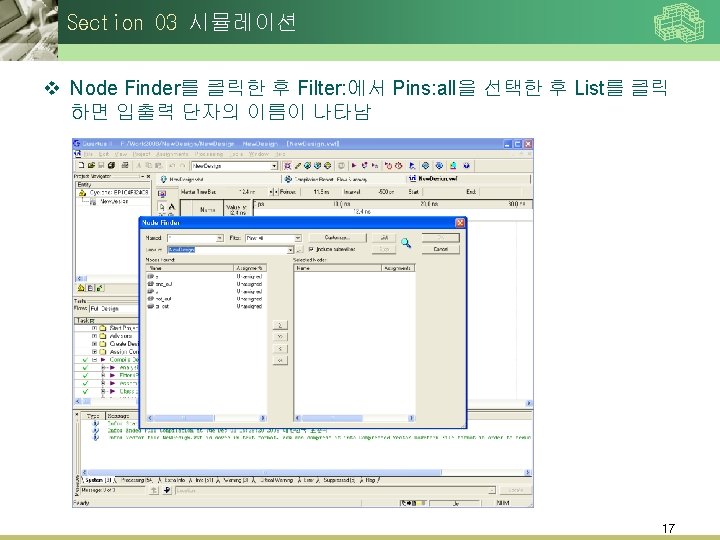

Section 03 시뮬레이션 v Processing → Start Simulation Tool을 클릭 v 단축 아이콘( )을 직접 클릭 20

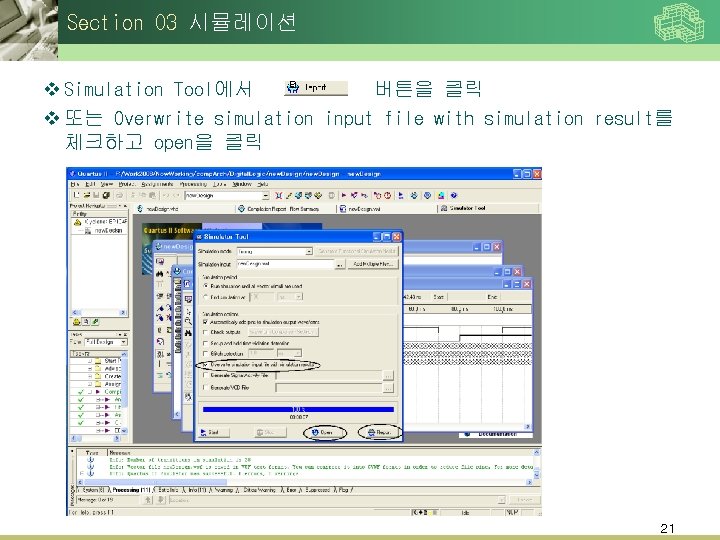

Section 03 시뮬레이션 v Simulation Tool에서 버튼을 클릭 v 또는 Overwrite simulation input file with simulation result를 체크하고 open을 클릭 21

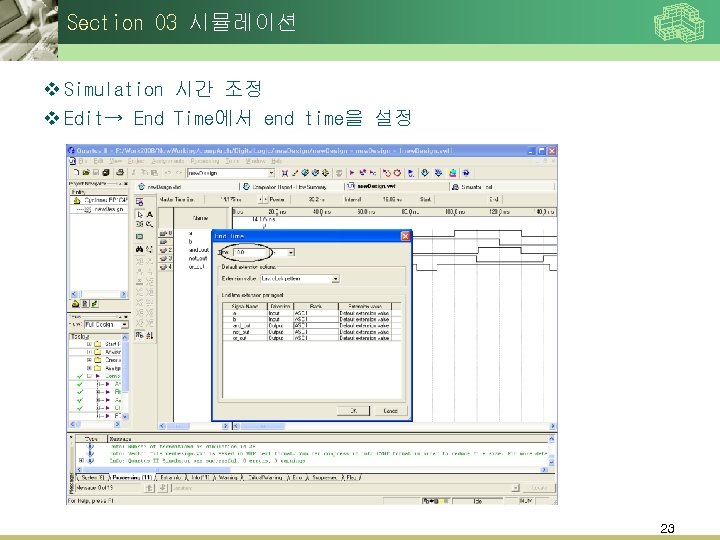

Section 03 시뮬레이션 v Simulation 시간 조정 v Edit→ End Time에서 end time을 설정 23

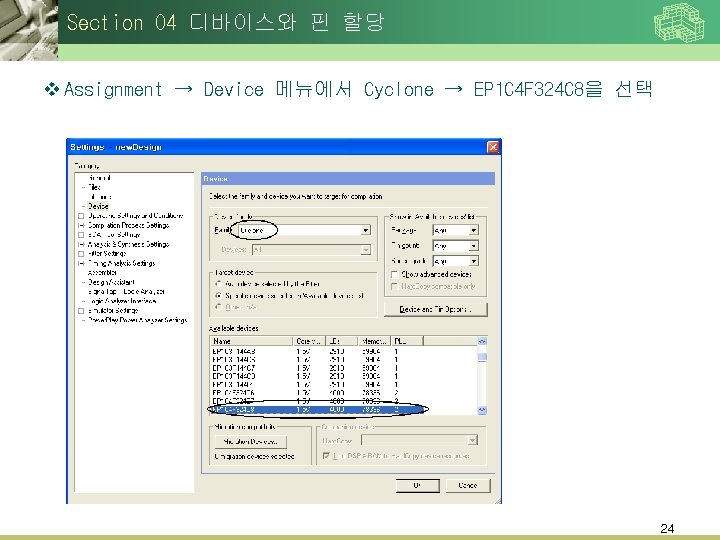

Section 04 디바이스와 핀 할당 v Assignment → Device 메뉴에서 Cyclone → EP 1 C 4 F 324 C 8을 선택 24

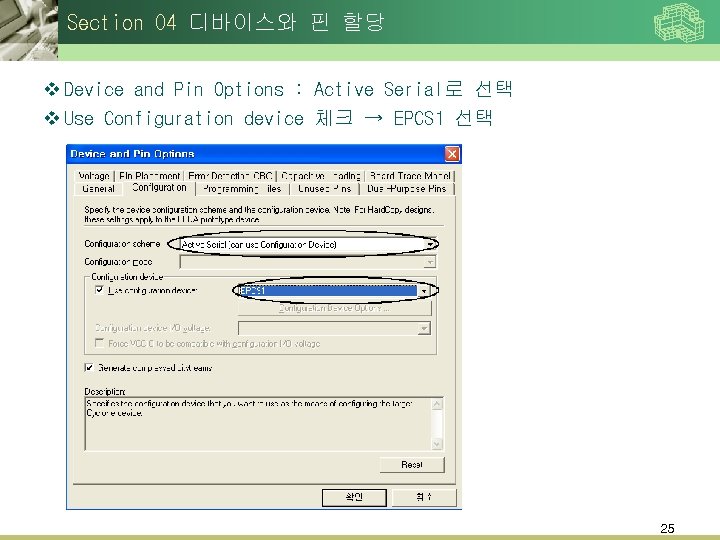

Section 04 디바이스와 핀 할당 v Device and Pin Options : Active Serial로 선택 v Use Configuration device 체크 → EPCS 1 선택 25

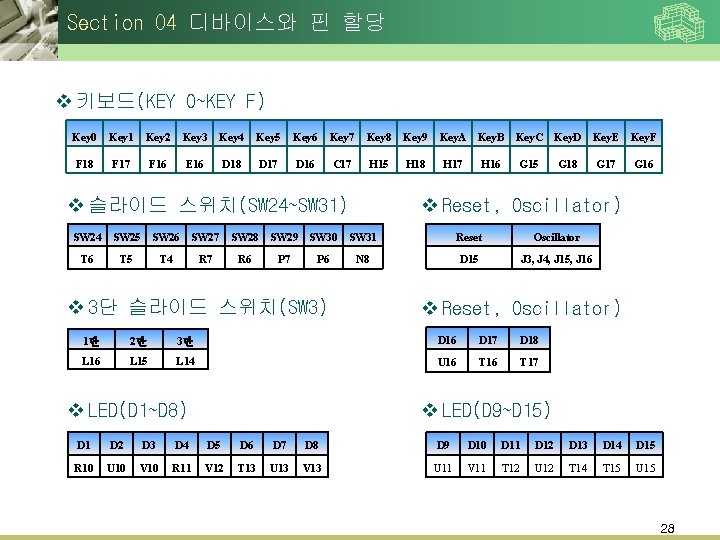

Section 04 디바이스와 핀 할당 v 키보드(KEY 0~KEY F) Key 0 Key 1 Key 2 Key 3 Key 4 Key 5 Key 6 Key 7 Key 8 Key 9 Key. A Key. B Key. C Key. D Key. E Key. F F 18 F 17 F 16 E 16 D 18 D 17 D 16 C 17 H 15 H 18 H 17 H 16 G 15 G 18 G 17 G 16 v 슬라이드 스위치(SW 24~SW 31) v Reset, Oscillator) SW 24 SW 25 SW 26 SW 27 SW 28 SW 29 SW 30 SW 31 Reset Oscillator T 6 T 5 T 4 R 7 R 6 P 7 P 6 N 8 D 15 J 3, J 4, J 15, J 16 v 3단 슬라이드 스위치(SW 3) v Reset, Oscillator) 1단 2단 3단 D 16 D 17 D 18 L 16 L 15 L 14 U 16 T 17 v LED(D 1~D 8) v LED(D 9~D 15) D 1 D 2 D 3 D 4 D 5 D 6 D 7 D 8 D 9 D 10 D 11 D 12 D 13 D 14 D 15 R 10 U 10 V 10 R 11 V 12 T 13 U 13 V 13 U 11 V 11 T 12 U 12 T 14 T 15 U 15 28

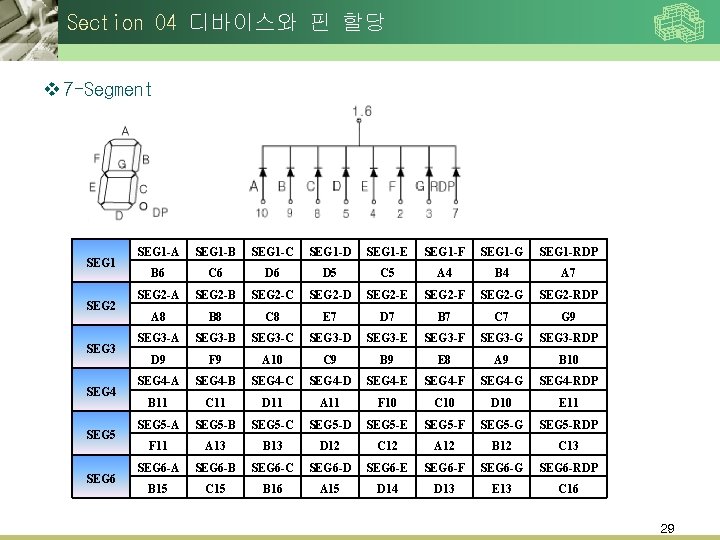

Section 04 디바이스와 핀 할당 v 7 -Segment SEG 1 SEG 2 SEG 3 SEG 4 SEG 5 SEG 6 SEG 1 -A SEG 1 -B SEG 1 -C SEG 1 -D SEG 1 -E SEG 1 -F SEG 1 -G SEG 1 -RDP B 6 C 6 D 5 C 5 A 4 B 4 A 7 SEG 2 -A SEG 2 -B SEG 2 -C SEG 2 -D SEG 2 -E SEG 2 -F SEG 2 -G SEG 2 -RDP A 8 B 8 C 8 E 7 D 7 B 7 C 7 G 9 SEG 3 -A SEG 3 -B SEG 3 -C SEG 3 -D SEG 3 -E SEG 3 -F SEG 3 -G SEG 3 -RDP D 9 F 9 A 10 C 9 B 9 E 8 A 9 B 10 SEG 4 -A SEG 4 -B SEG 4 -C SEG 4 -D SEG 4 -E SEG 4 -F SEG 4 -G SEG 4 -RDP B 11 C 11 D 11 A 11 F 10 C 10 D 10 E 11 SEG 5 -A SEG 5 -B SEG 5 -C SEG 5 -D SEG 5 -E SEG 5 -F SEG 5 -G SEG 5 -RDP F 11 A 13 B 13 D 12 C 12 A 12 B 12 C 13 SEG 6 -A SEG 6 -B SEG 6 -C SEG 6 -D SEG 6 -E SEG 6 -F SEG 6 -G SEG 6 -RDP B 15 C 15 B 16 A 15 D 14 D 13 E 13 C 16 29

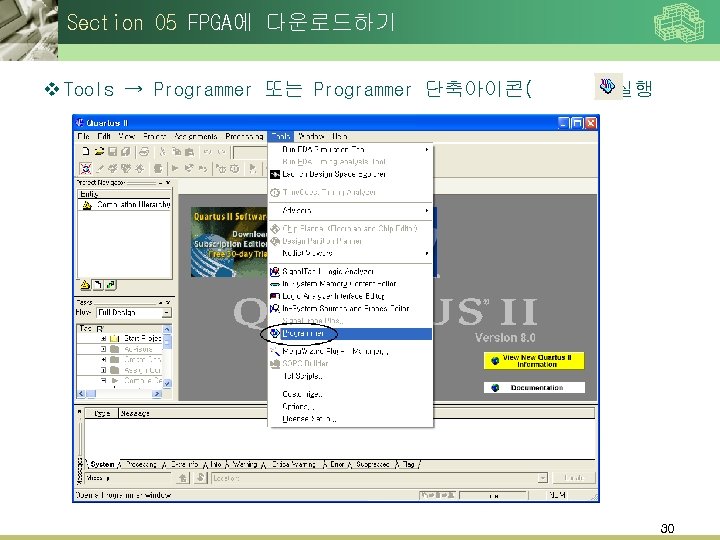

Section 05 FPGA에 다운로드하기 v Tools → Programmer 또는 Programmer 단축아이콘( ) 실행 30

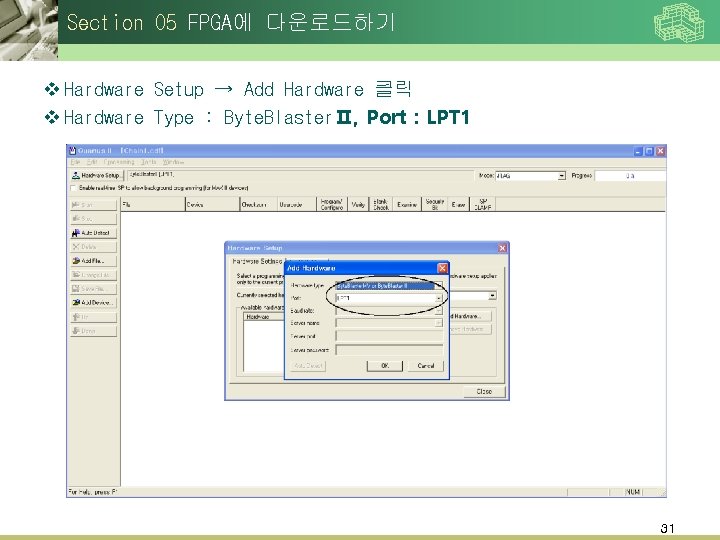

Section 05 FPGA에 다운로드하기 v Hardware Setup → Add Hardware 클릭 v Hardware Type : Byte. BlasterⅡ, Port : LPT 1 31

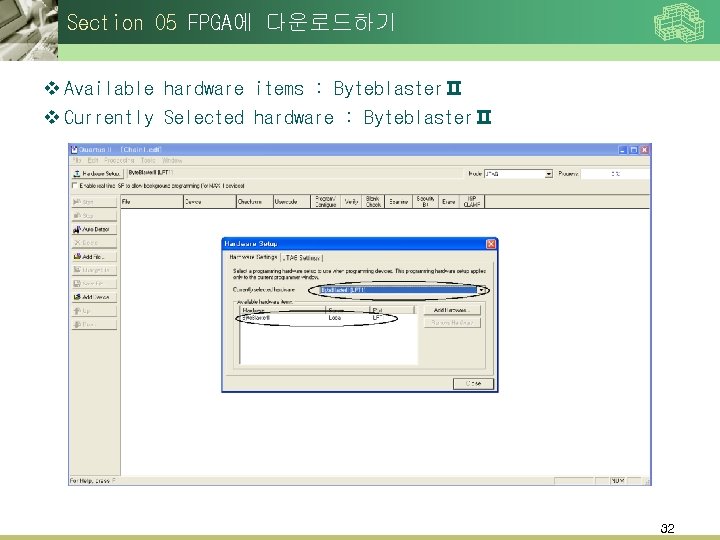

Section 05 FPGA에 다운로드하기 v Available hardware items : ByteblasterⅡ v Currently Selected hardware : ByteblasterⅡ 32

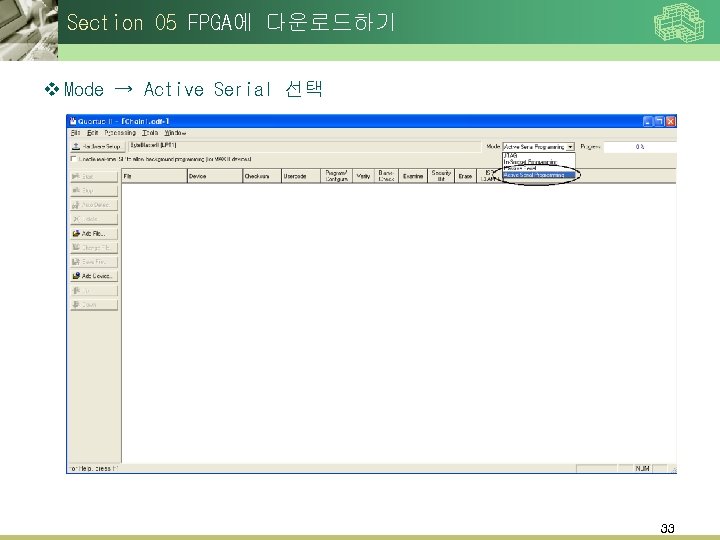

Section 05 FPGA에 다운로드하기 v Mode → Active Serial 선택 33

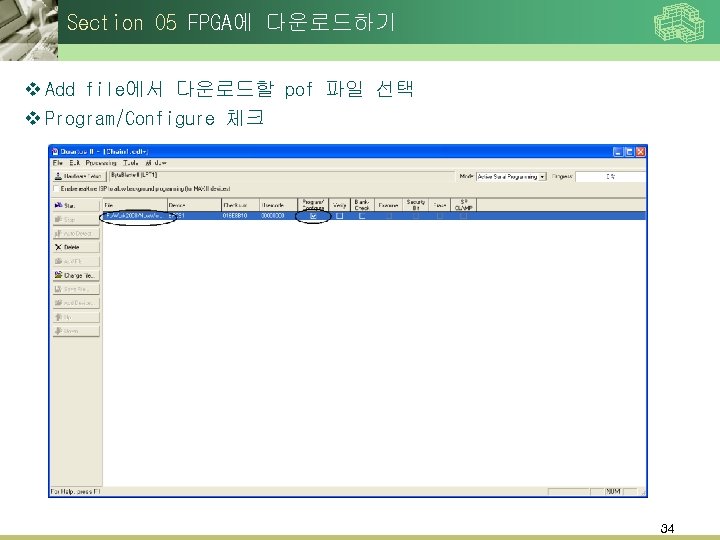

Section 05 FPGA에 다운로드하기 v Add file에서 다운로드할 pof 파일 선택 v Program/Configure 체크 34

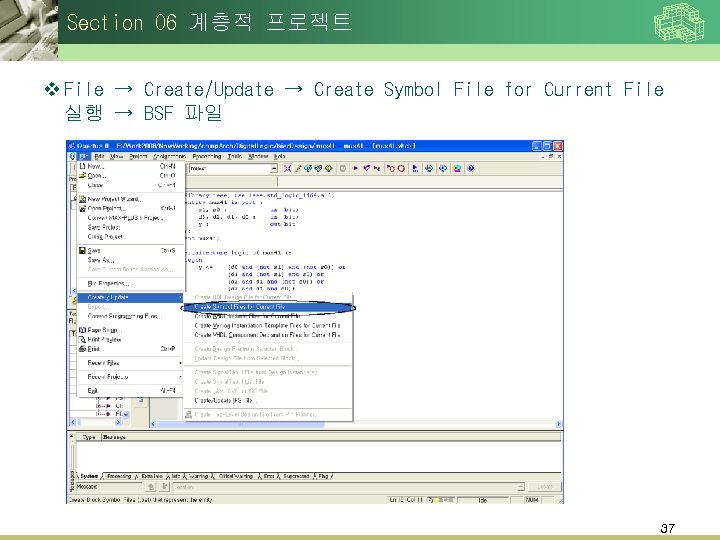

Section 06 계층적 프로젝트 v File → Create/Update → Create Symbol File for Current File 실행 → BSF 파일 37

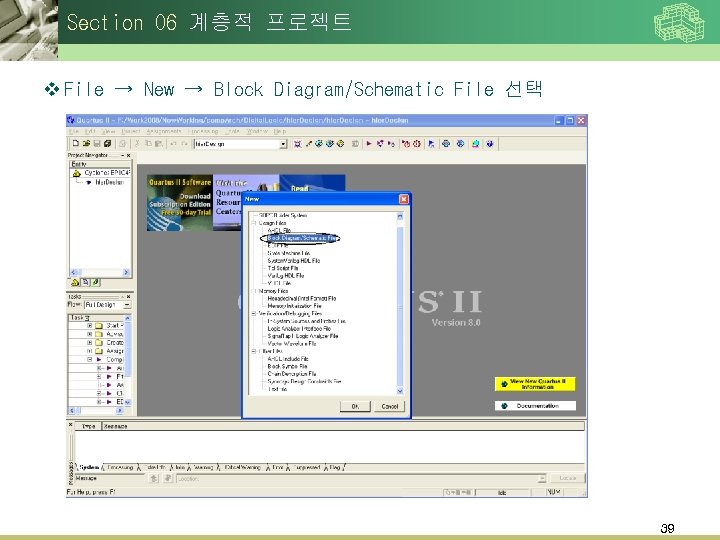

Section 06 계층적 프로젝트 v File → New → Block Diagram/Schematic File 선택 39

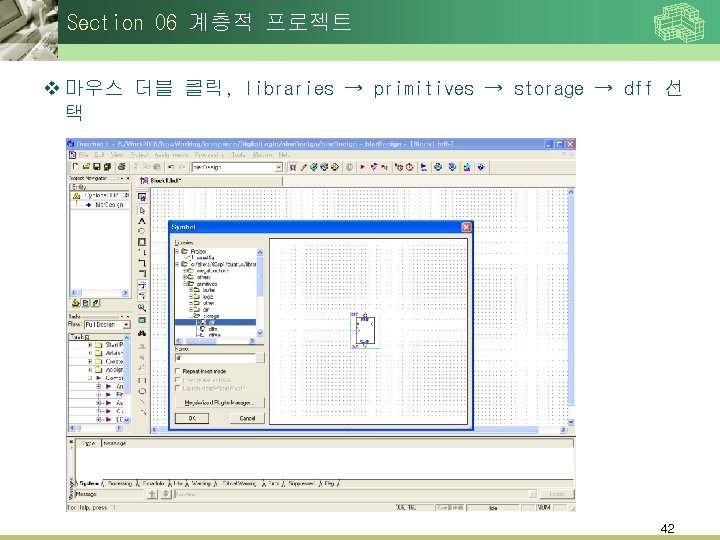

Section 06 계층적 프로젝트 v 마우스 더블 클릭, libraries → primitives → storage → dff 선 택 42

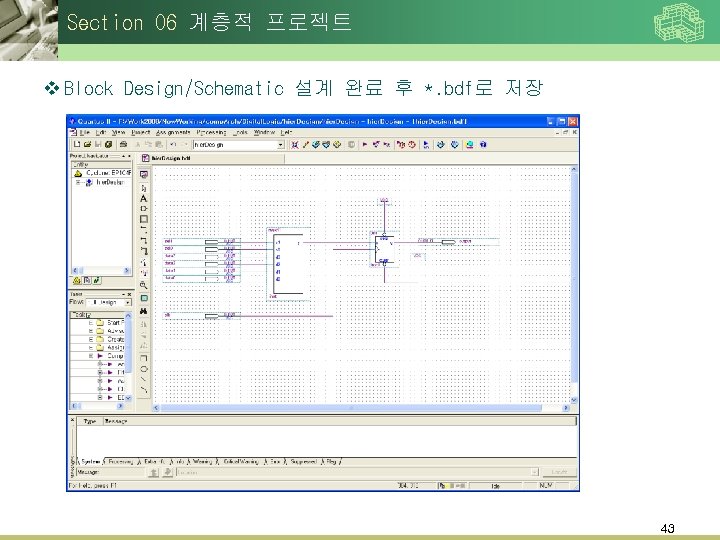

Section 06 계층적 프로젝트 v Block Design/Schematic 설계 완료 후 *. bdf로 저장 43

- Slides: 45