Verilog HDL Hardware Description LanguageHDL 6182021 1 HDL

- Slides: 53

Verilog HDL硬件描述语言 Hardware Description Language(HDL) 6/18/2021 西安理 大学电子 程系 1

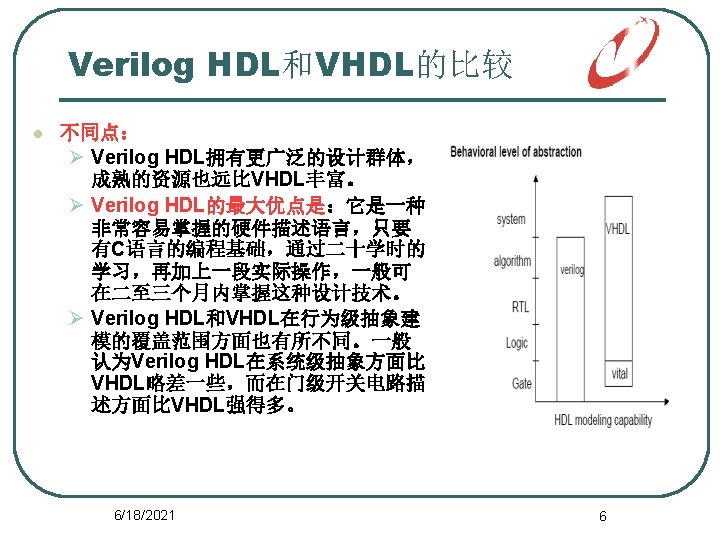

HDL的来历 l l HDL是“硬件描述语言”Hardware Description Language的 缩写(不是“硬件设计语言”Hardware Design Language的缩 写)。 VHDL(VHSIC HDL) Ø 1980年开始在美国国防部Department of Defense (DOD) VHSIC (Very High Speed Integration Circuit)计划的指 导下开发,完成于1983年,1987 VHDL成为标准, IEEE 1076 -1987。 Ø美国国防部要求所有的电子设计使用VHDL描述,并决定 在YF-22战斗机项目中使用VHDL。 6/18/2021 2

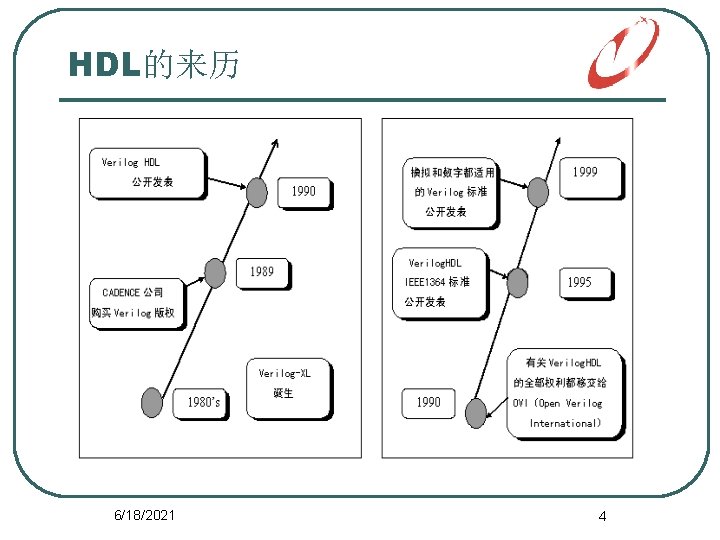

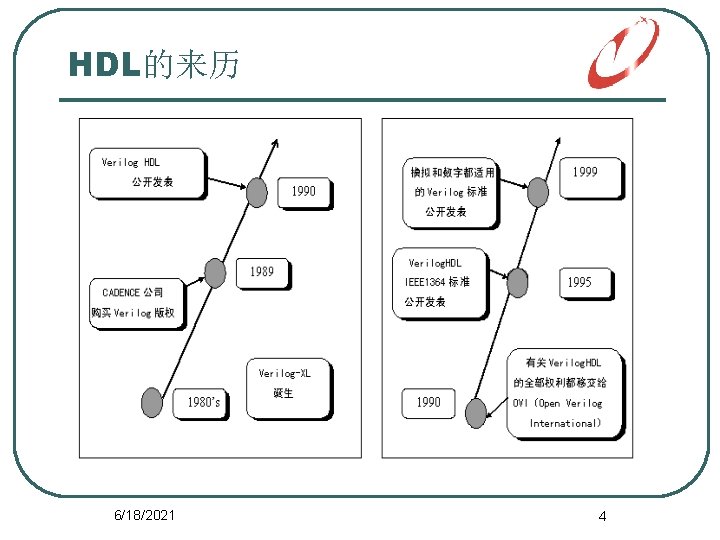

HDL的来历 l Verilog HDL ØVerilog HDL是在 1983年由Gateway Design Automation 公司的Phil Moorby首创的。 Ø在 1984 -1985年,Moorby设计出了第一个关于Verilog-XL的 仿真器。 Ø 1986年,他对Verilog HDL的发展又作出了另一个巨大贡献: 即提出了用于快速门级仿真的XL算法。 Ø 1989年,Cadence公司收购了GDA公司,Verilog HDL语言 成为Cadence公司的私有财产。 Ø 1990年,Cadence公司决定公开Verilog HDL语言,于是成 立了OVI(Open Verilog International)组织来负责Verilog HDL语言的发展。 Ø基于Verilog HDL的优越性,IEEE于1995年制定了Verilog HDL的IEEE标准,即Verilog HDL 1364 -1995。 6/18/2021 3

HDL的来历 6/18/2021 4

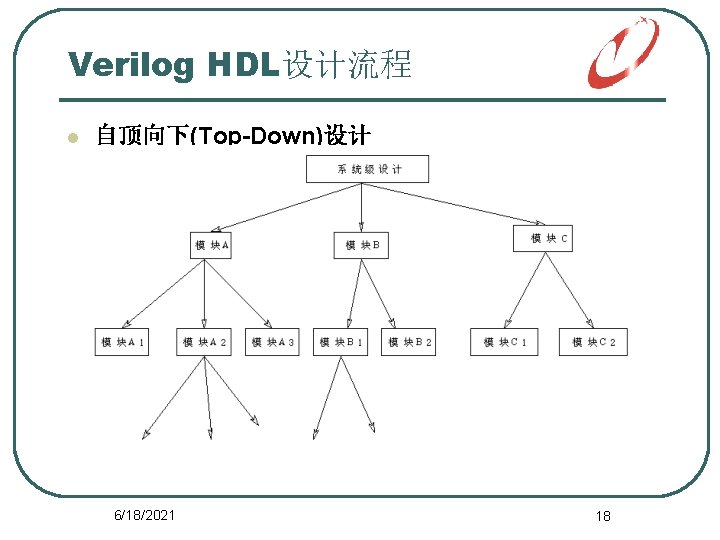

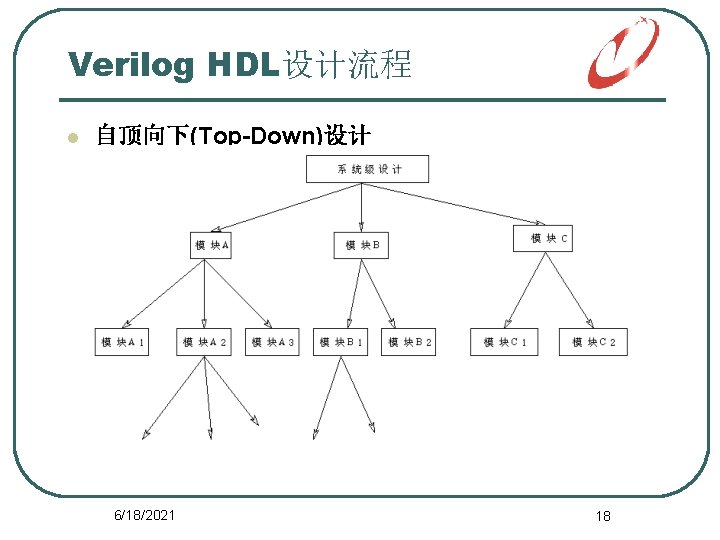

Verilog HDL设计流程 l 自顶向下(Top-Down)设计 6/18/2021 18

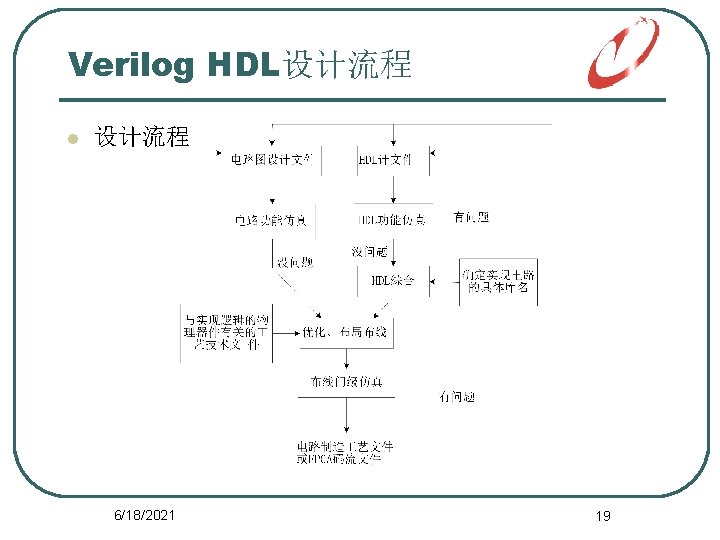

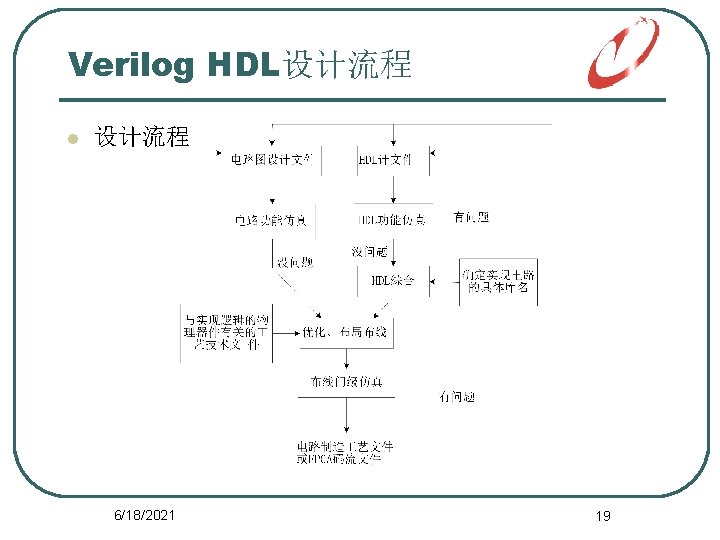

Verilog HDL设计流程 l 设计流程 6/18/2021 19

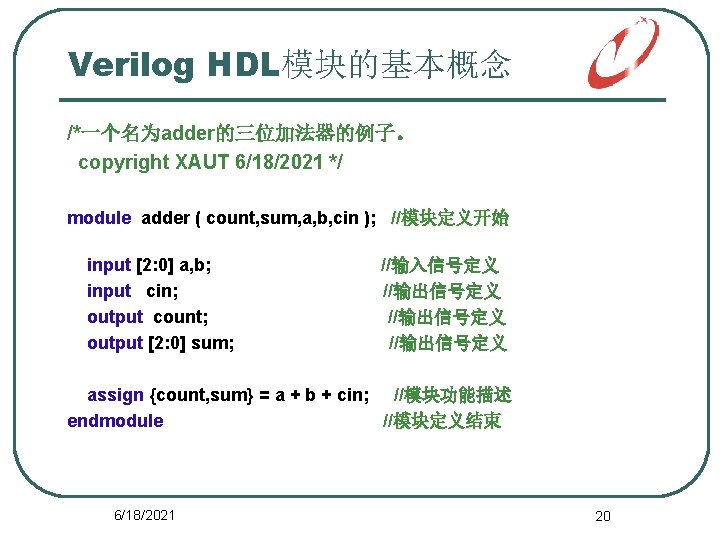

Verilog HDL模块的基本概念 /*一个名为adder的三位加法器的例子。 copyright XAUT 6/18/2021 */ module adder ( count, sum, a, b, cin ); //模块定义开始 input [2: 0] a, b; input cin; output count; output [2: 0] sum; //输入信号定义 //输出信号定义 assign {count, sum} = a + b + cin; //模块功能描述 endmodule //模块定义结束 6/18/2021 20

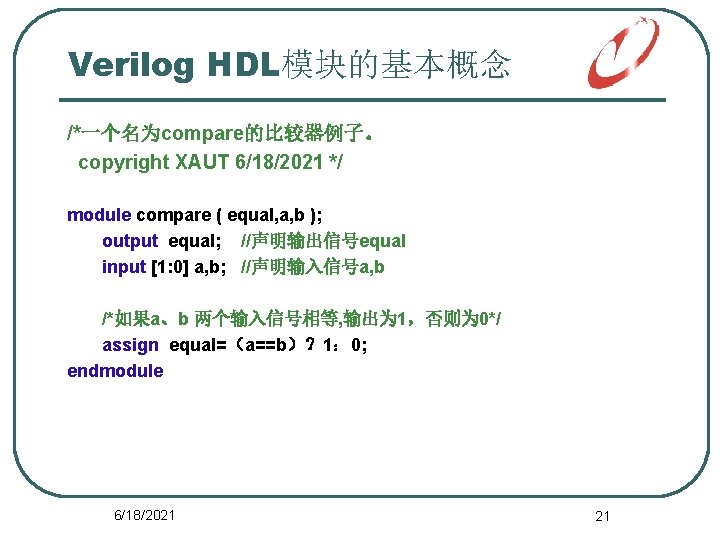

Verilog HDL模块的基本概念 /*一个名为compare的比较器例子。 copyright XAUT 6/18/2021 */ module compare ( equal, a, b ); output equal; //声明输出信号equal input [1: 0] a, b; //声明输入信号a, b /*如果a、b 两个输入信号相等, 输出为 1,否则为 0*/ assign equal=(a==b)? 1: 0; endmodule 6/18/2021 21

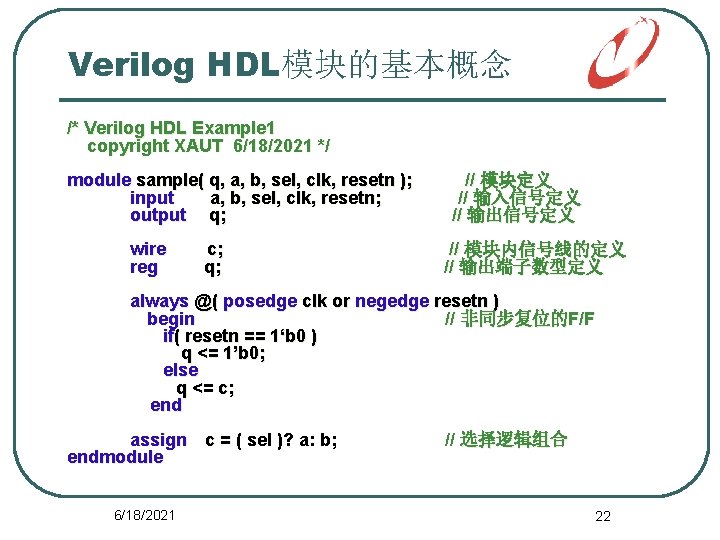

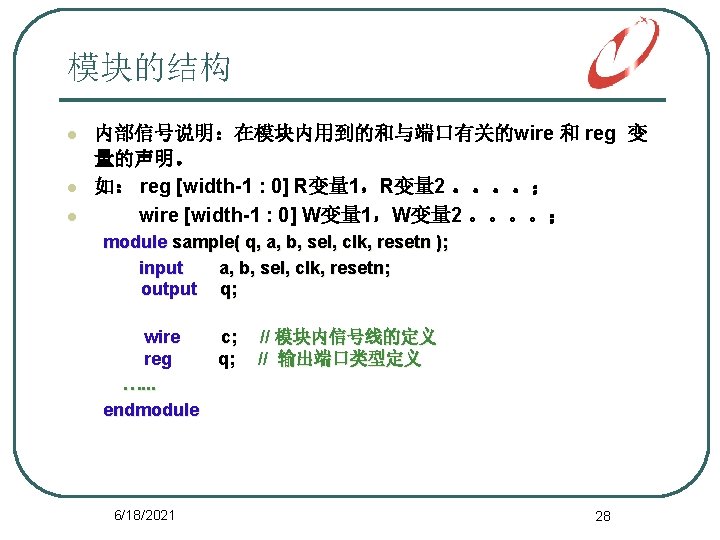

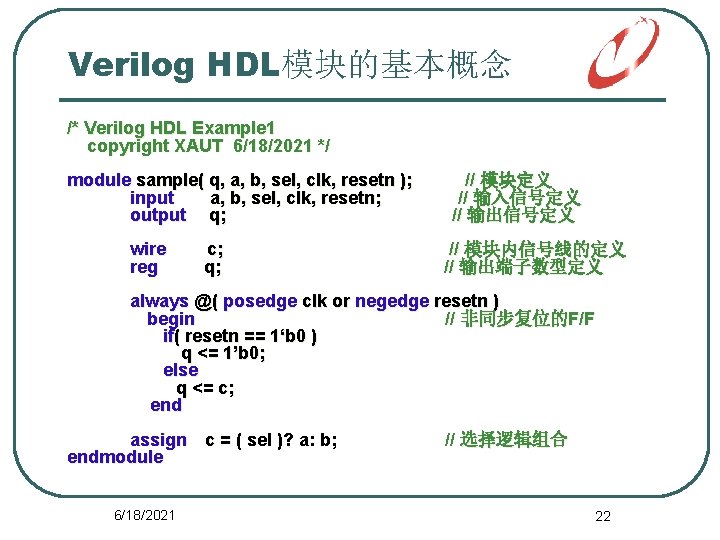

Verilog HDL模块的基本概念 /* Verilog HDL Example 1 copyright XAUT 6/18/2021 */ module sample( q, a, b, sel, clk, resetn ); input a, b, sel, clk, resetn; output q; wire reg c; q; // 模块定义 // 输入信号定义 // 输出信号定义 // 模块内信号线的定义 // 输出端子数型定义 always @( posedge clk or negedge resetn ) begin // 非同步复位的F/F if( resetn == 1‘b 0 ) q <= 1’b 0; else q <= c; end assign c = ( sel )? a: b; endmodule 6/18/2021 // 选择逻辑组合 22

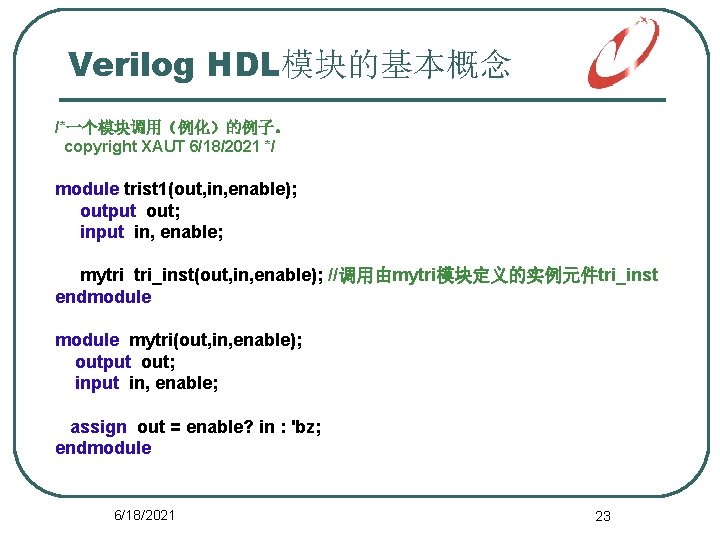

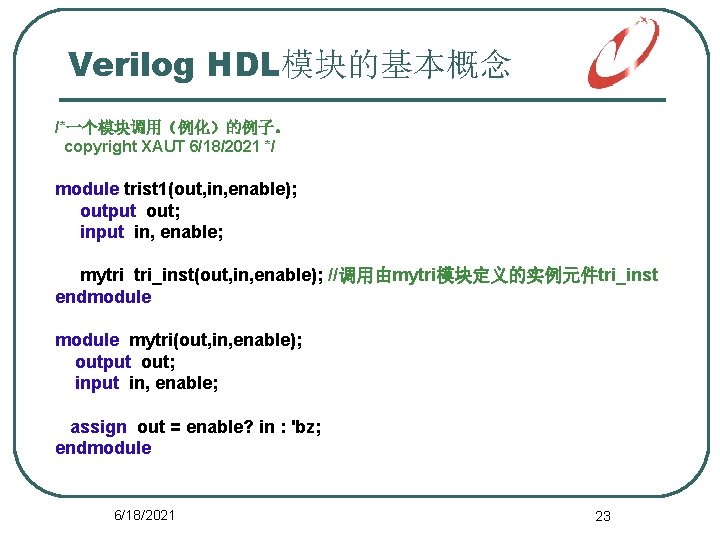

Verilog HDL模块的基本概念 /*一个模块调用(例化)的例子。 copyright XAUT 6/18/2021 */ module trist 1(out, in, enable); output out; input in, enable; mytri tri_inst(out, in, enable); //调用由mytri模块定义的实例元件tri_inst endmodule mytri(out, in, enable); output out; input in, enable; assign out = enable? in : 'bz; endmodule 6/18/2021 23

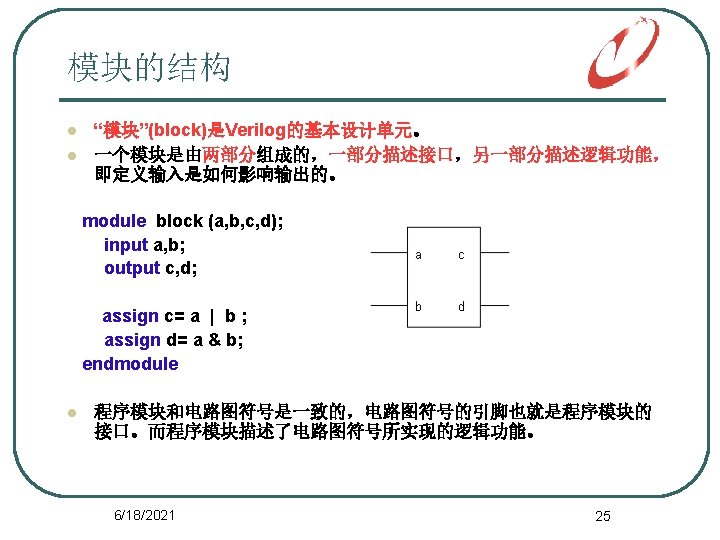

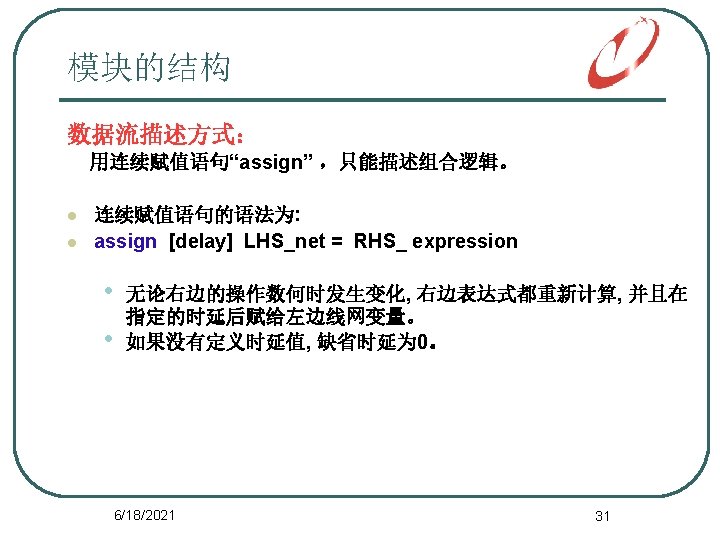

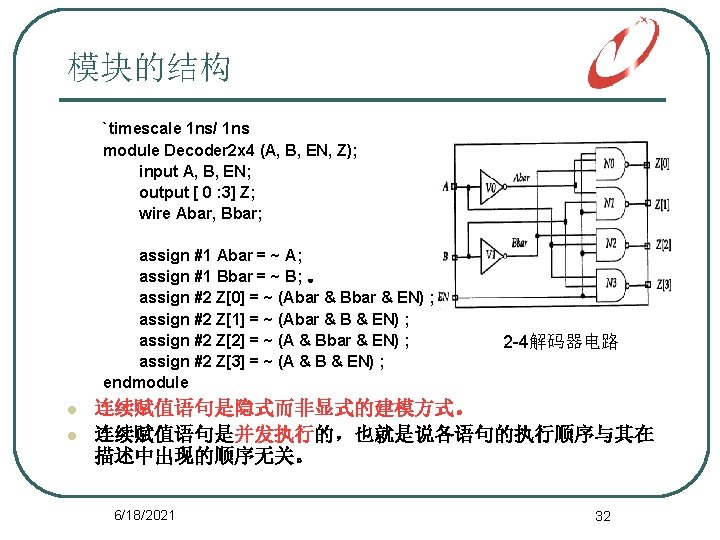

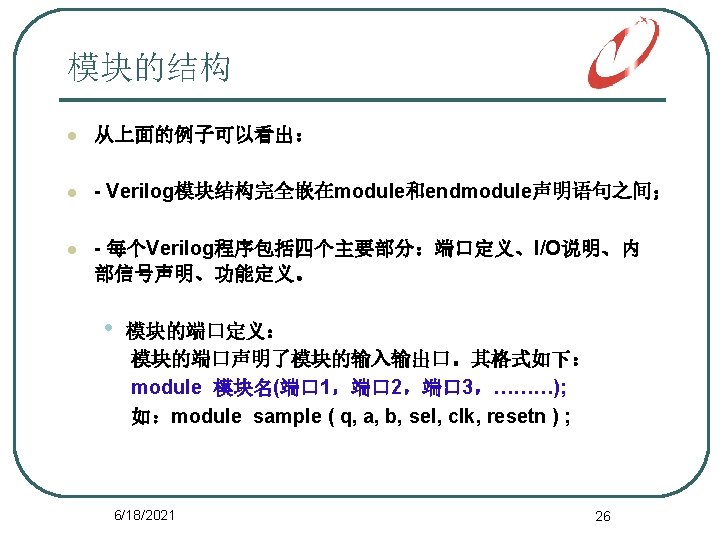

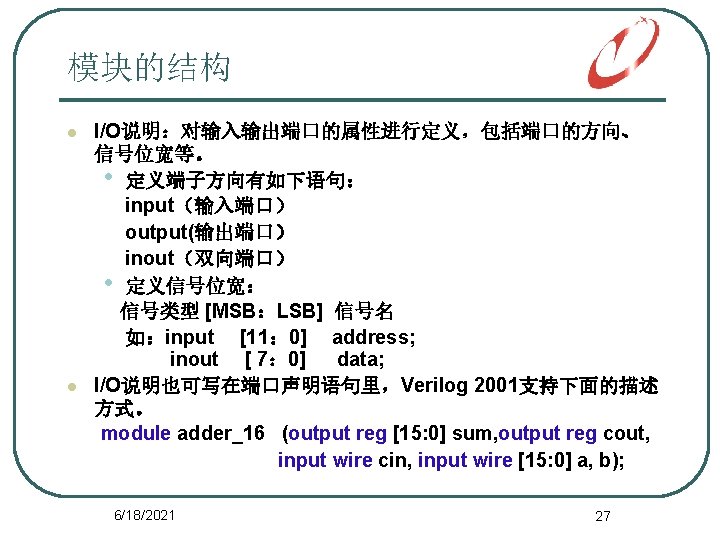

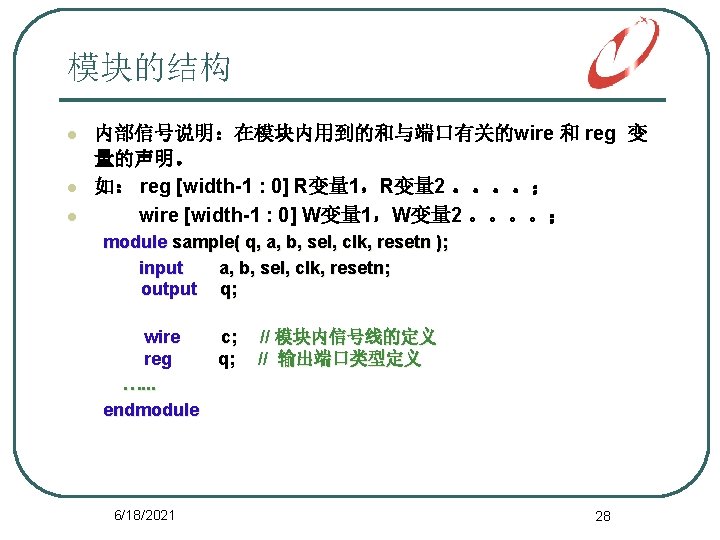

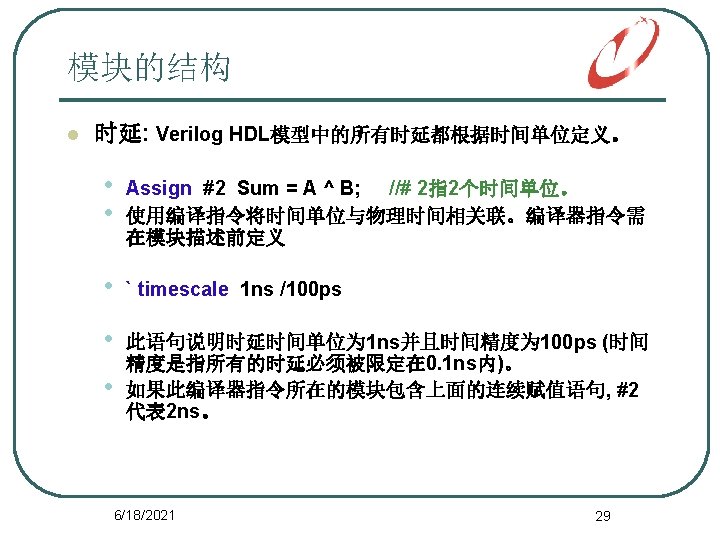

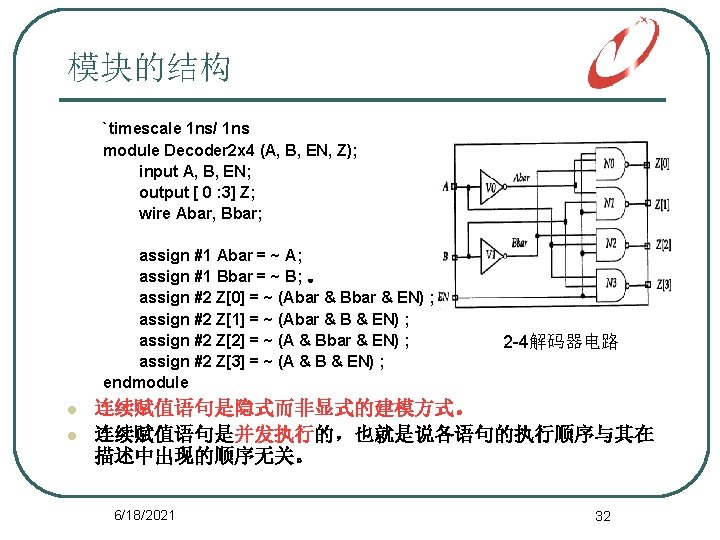

模块的结构 `timescale 1 ns/ 1 ns module Decoder 2 x 4 (A, B, EN, Z); input A, B, EN; output [ 0 : 3] Z; wire Abar, Bbar; assign #1 Abar = ~ A; assign #1 Bbar = ~ B; 。 assign #2 Z[0] = ~ (Abar & Bbar & EN) ; assign #2 Z[1] = ~ (Abar & B & EN) ; assign #2 Z[2] = ~ (A & Bbar & EN) ; assign #2 Z[3] = ~ (A & B & EN) ; endmodule l l 2 -4解码器电路 连续赋值语句是隐式而非显式的建模方式。 连续赋值语句是并发执行的,也就是说各语句的执行顺序与其在 描述中出现的顺序无关。 6/18/2021 32

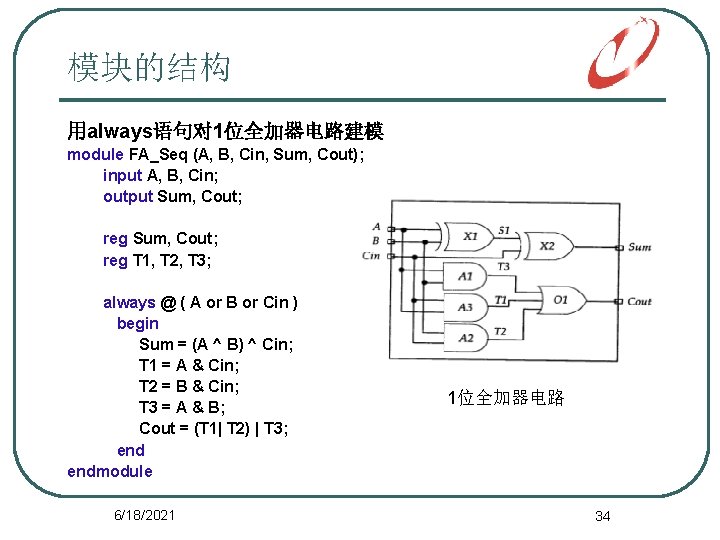

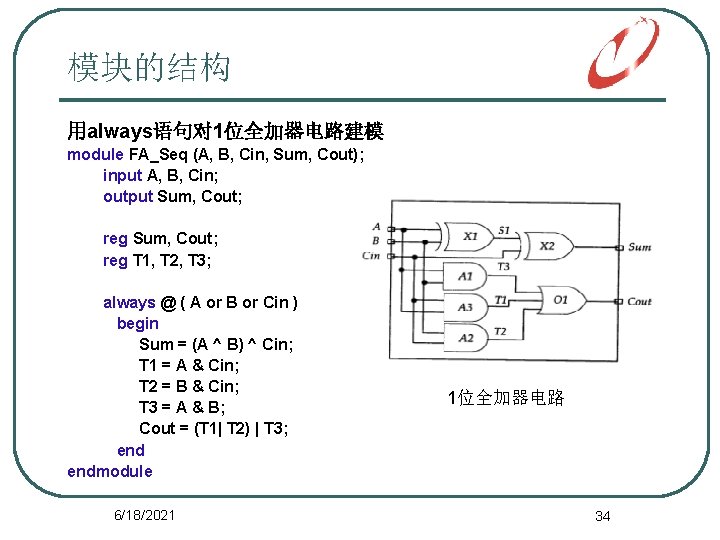

模块的结构 用always语句对 1位全加器电路建模 module FA_Seq (A, B, Cin, Sum, Cout); input A, B, Cin; output Sum, Cout; reg T 1, T 2, T 3; always @ ( A or B or Cin ) begin Sum = (A ^ B) ^ Cin; T 1 = A & Cin; T 2 = B & Cin; T 3 = A & B; Cout = (T 1| T 2) | T 3; endmodule 6/18/2021 1位全加器电路 34

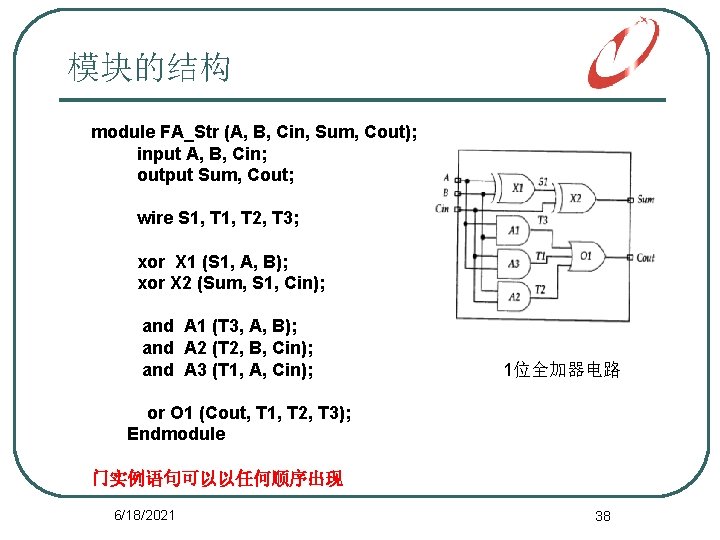

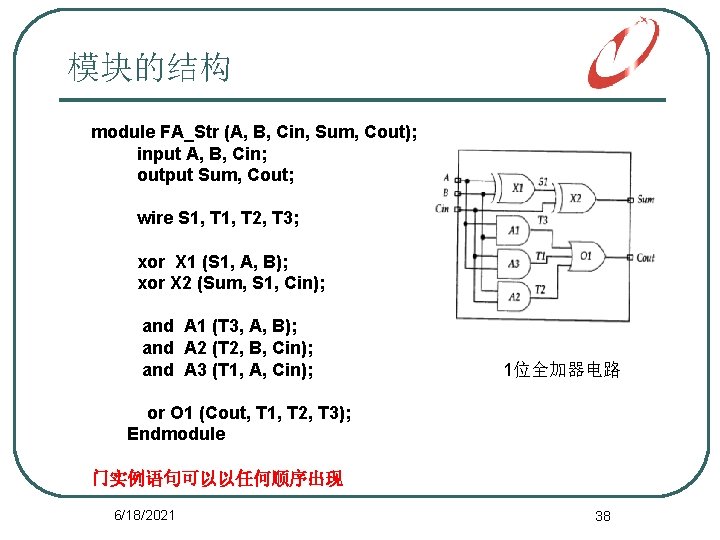

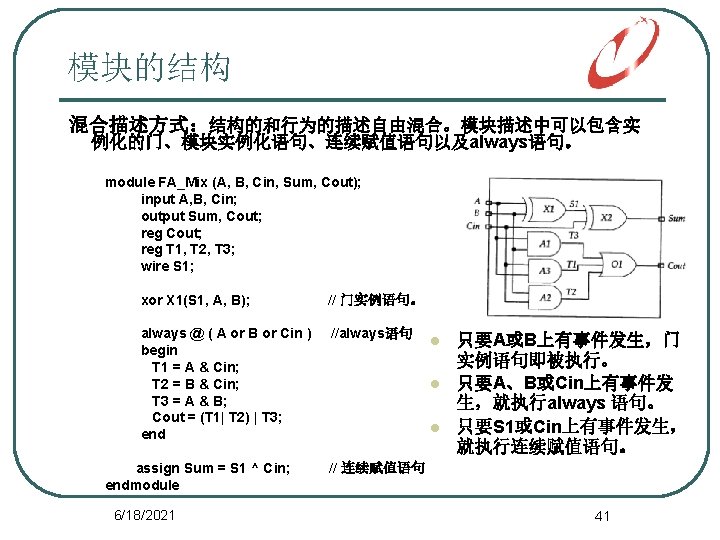

模块的结构 module FA_Str (A, B, Cin, Sum, Cout); input A, B, Cin; output Sum, Cout; wire S 1, T 2, T 3; xor X 1 (S 1, A, B); xor X 2 (Sum, S 1, Cin); and A 1 (T 3, A, B); and A 2 (T 2, B, Cin); and A 3 (T 1, A, Cin); 1位全加器电路 or O 1 (Cout, T 1, T 2, T 3); Endmodule 门实例语句可以以任何顺序出现 6/18/2021 38

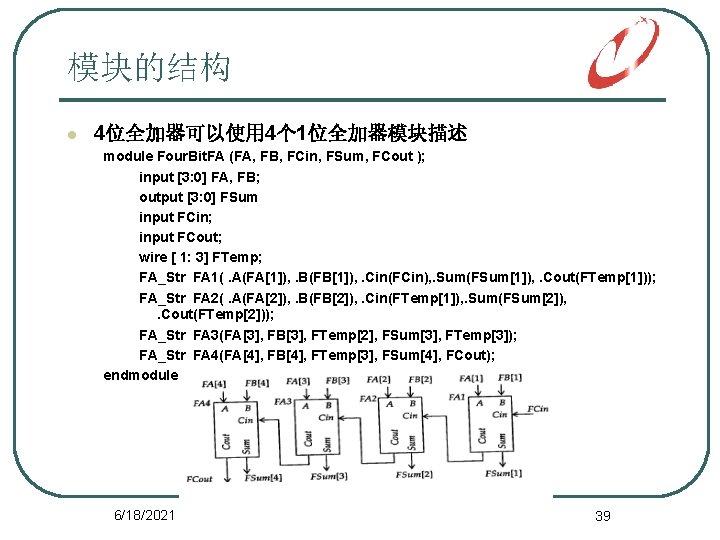

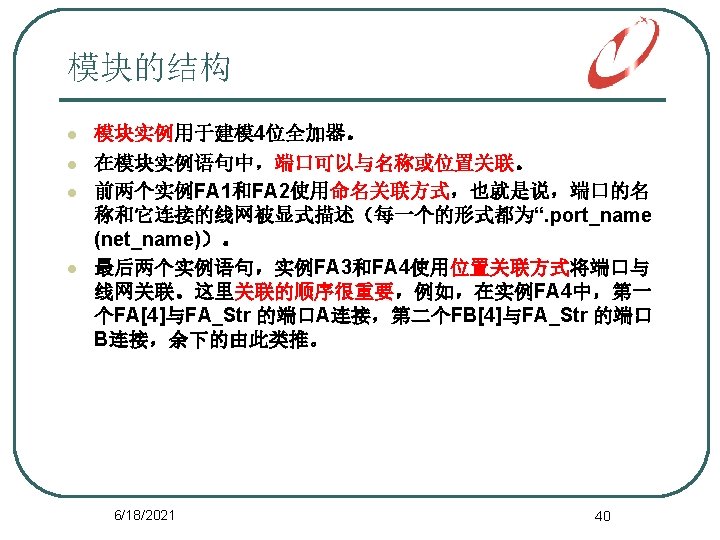

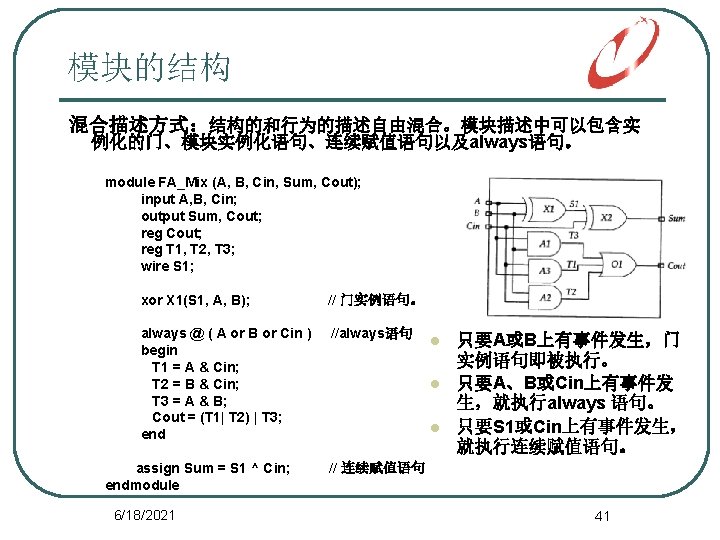

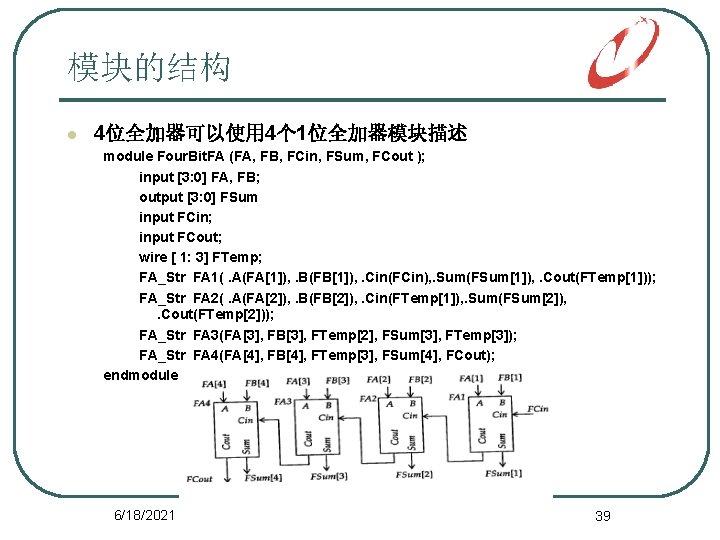

模块的结构 l 4位全加器可以使用 4个 1位全加器模块描述 module Four. Bit. FA (FA, FB, FCin, FSum, FCout ); input [3: 0] FA, FB; output [3: 0] FSum input FCin; input FCout; wire [ 1: 3] FTemp; FA_Str FA 1(. A(FA[1]), . B(FB[1]), . Cin(FCin), . Sum(FSum[1]), . Cout(FTemp[1])); FA_Str FA 2(. A(FA[2]), . B(FB[2]), . Cin(FTemp[1]), . Sum(FSum[2]), . Cout(FTemp[2])); FA_Str FA 3(FA[3], FB[3], FTemp[2], FSum[3], FTemp[3]); FA_Str FA 4(FA[4], FB[4], FTemp[3], FSum[4], FCout); endmodule 6/18/2021 39

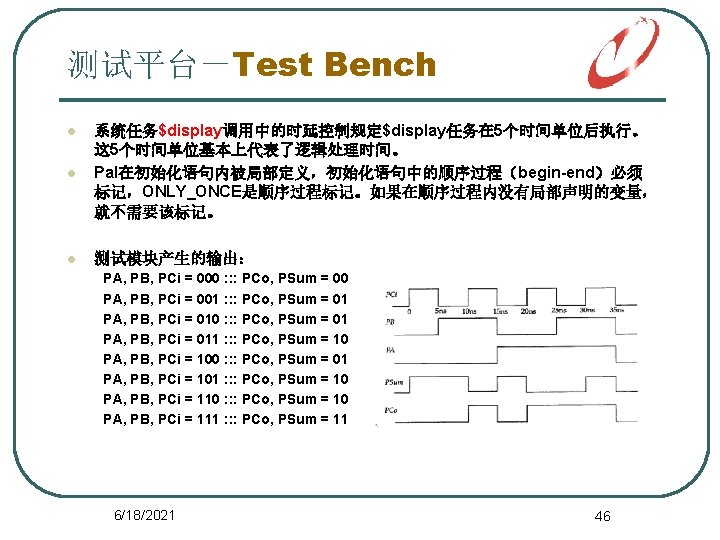

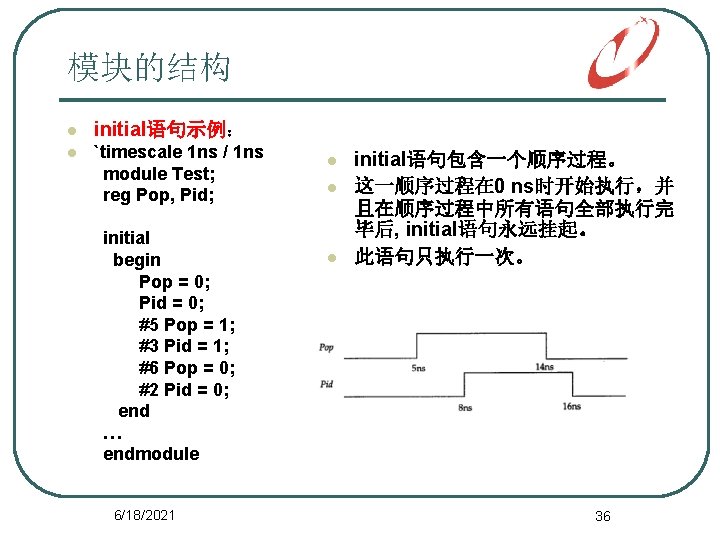

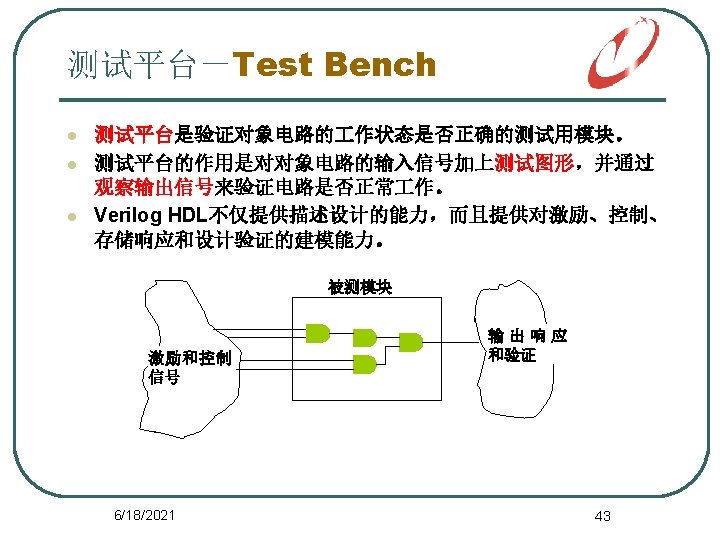

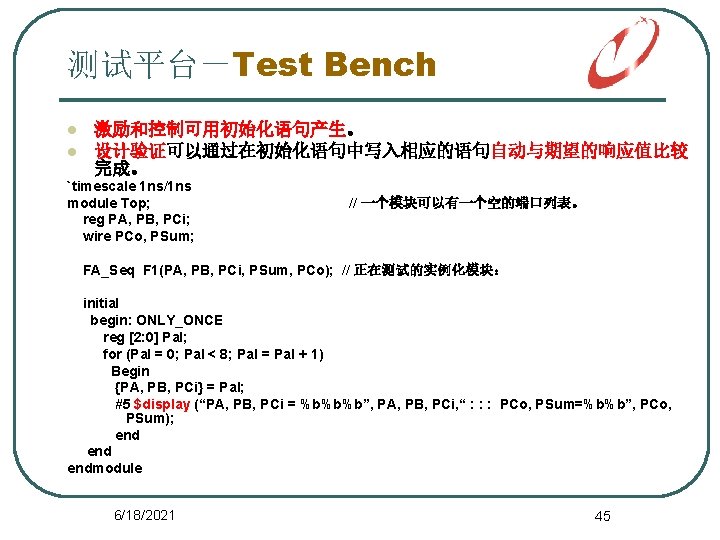

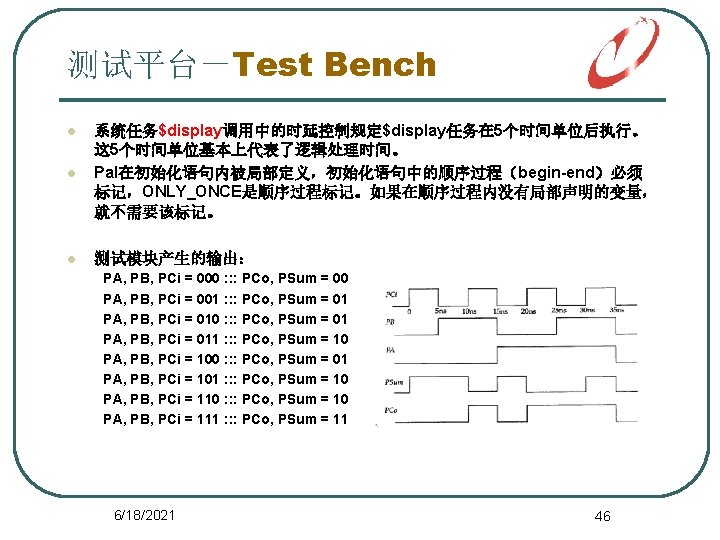

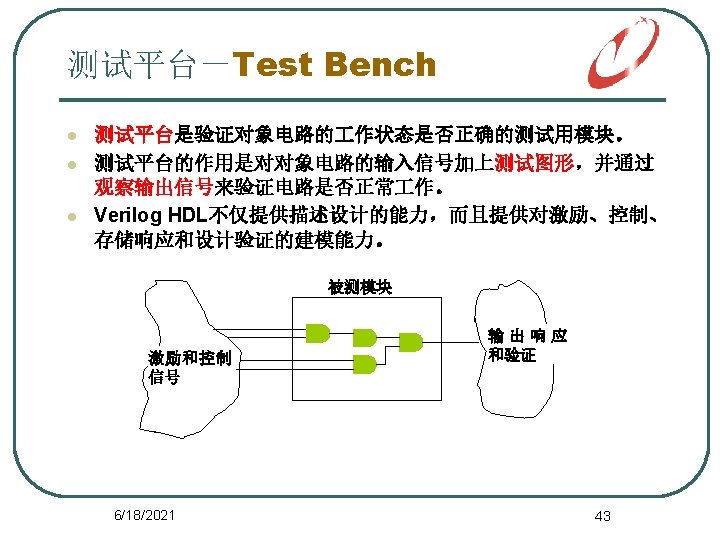

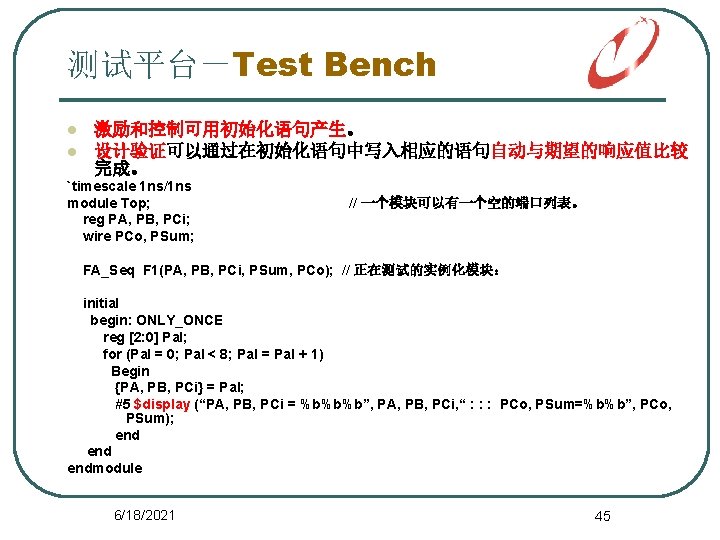

测试平台-Test Bench l l 激励和控制可用初始化语句产生。 设计验证可以通过在初始化语句中写入相应的语句自动与期望的响应值比较 完成。 `timescale 1 ns/1 ns module Top; reg PA, PB, PCi; wire PCo, PSum; // 一个模块可以有一个空的端口列表。 FA_Seq F 1(PA, PB, PCi, PSum, PCo); // 正在测试的实例化模块: initial begin: ONLY_ONCE reg [2: 0] Pal; for (Pal = 0; Pal < 8; Pal = Pal + 1) Begin {PA, PB, PCi} = Pal; #5 $display (“PA, PB, PCi = %b%b%b”, PA, PB, PCi, “ : : : PCo, PSum=%b%b”, PCo, PSum); end endmodule 6/18/2021 45