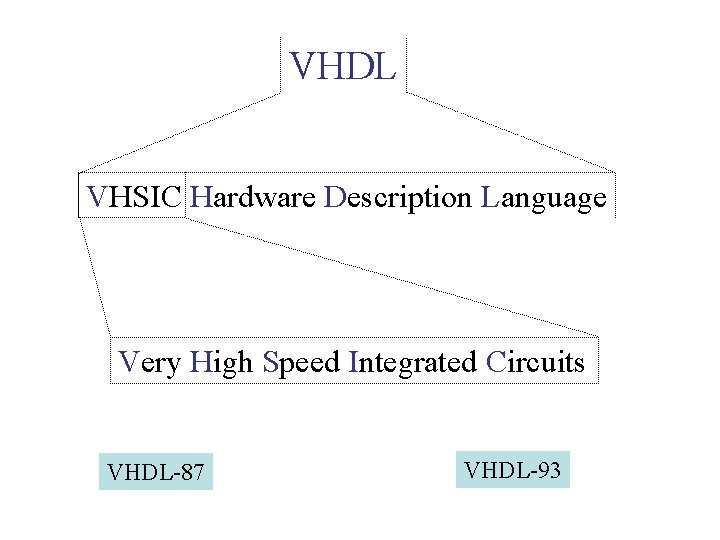

VHDL VHSIC Hardware Description Language Very High Speed

- Slides: 19

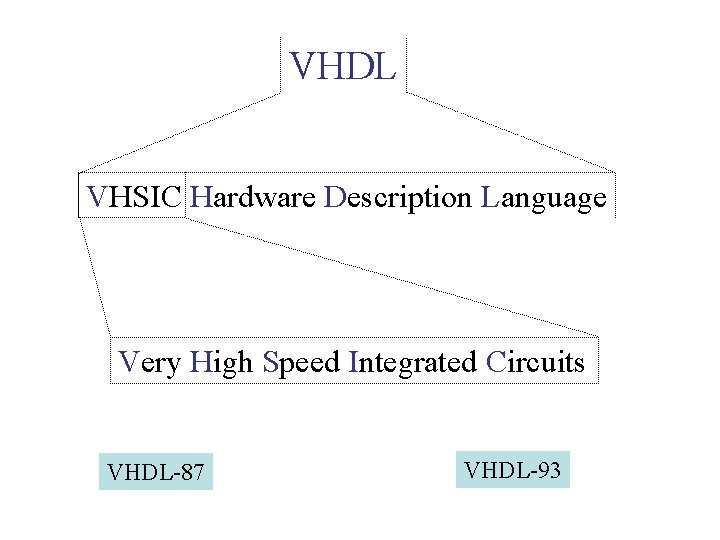

VHDL VHSIC Hardware Description Language Very High Speed Integrated Circuits VHDL-87 VHDL-93

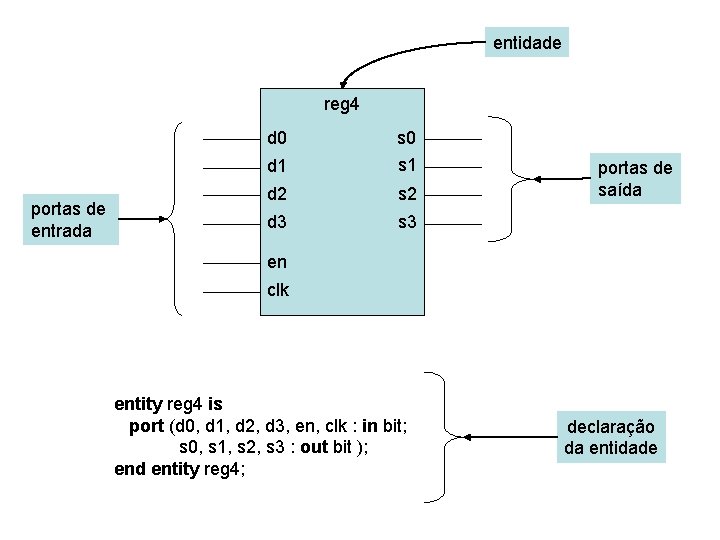

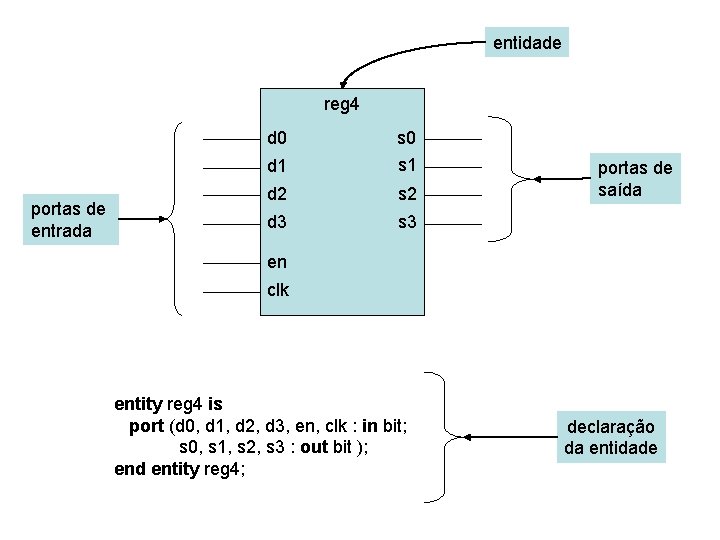

entidade reg 4 portas de entrada d 0 s 0 d 1 s 1 d 2 s 2 d 3 s 3 portas de saída en clk entity reg 4 is port (d 0, d 1, d 2, d 3, en, clk : in bit; s 0, s 1, s 2, s 3 : out bit ); end entity reg 4; declaração da entidade

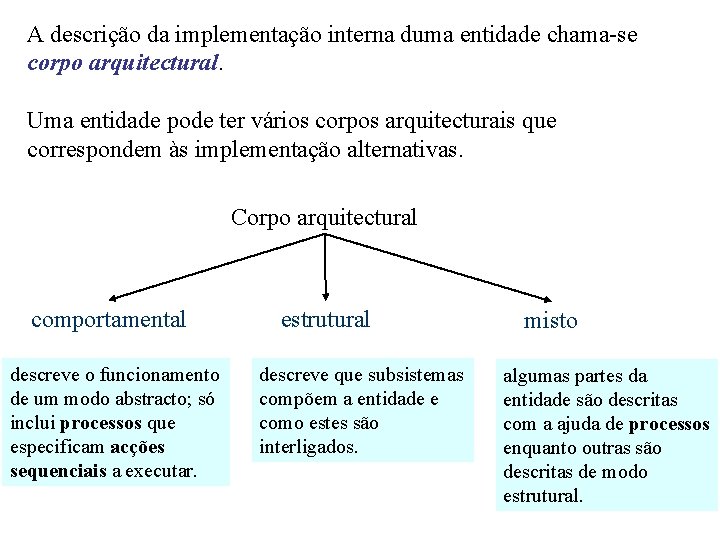

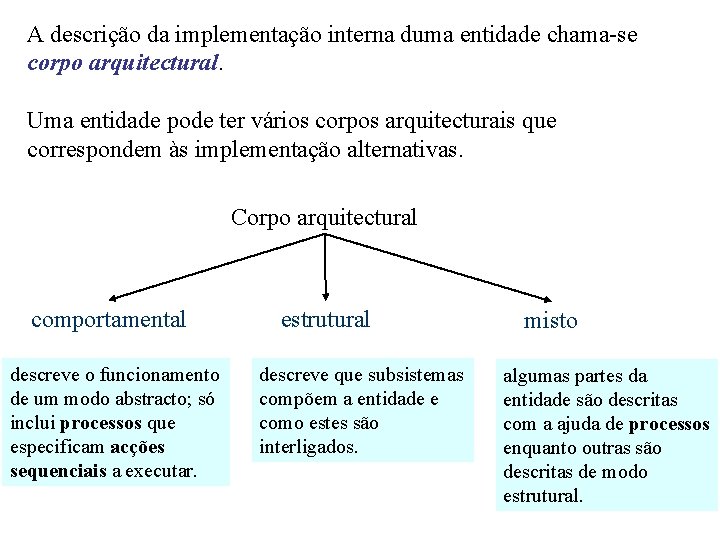

A descrição da implementação interna duma entidade chama-se corpo arquitectural. Uma entidade pode ter vários corpos arquitecturais que correspondem às implementação alternativas. Corpo arquitectural comportamental descreve o funcionamento de um modo abstracto; só inclui processos que especificam acções sequenciais a executar. estrutural descreve que subsistemas compõem a entidade e como estes são interligados. misto algumas partes da entidade são descritas com a ajuda de processos enquanto outras são descritas de modo estrutural.

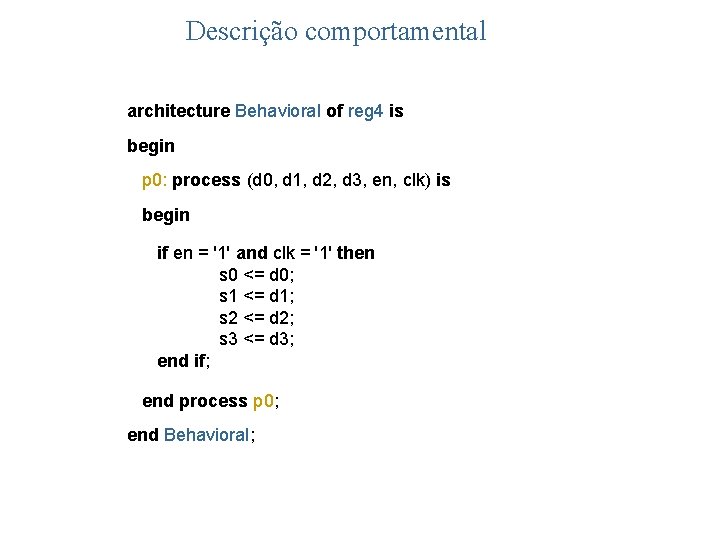

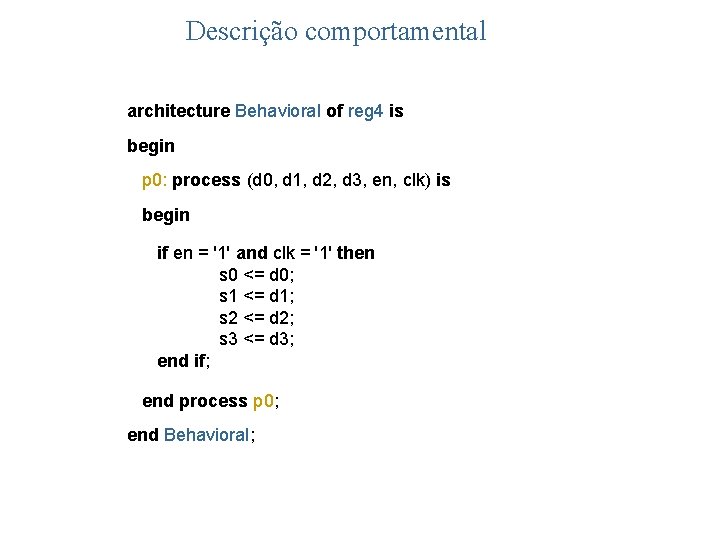

Descrição comportamental architecture Behavioral of reg 4 is begin p 0: process (d 0, d 1, d 2, d 3, en, clk) is begin if en = '1' and clk = '1' then s 0 <= d 0; s 1 <= d 1; s 2 <= d 2; s 3 <= d 3; end if; end process p 0; end Behavioral;

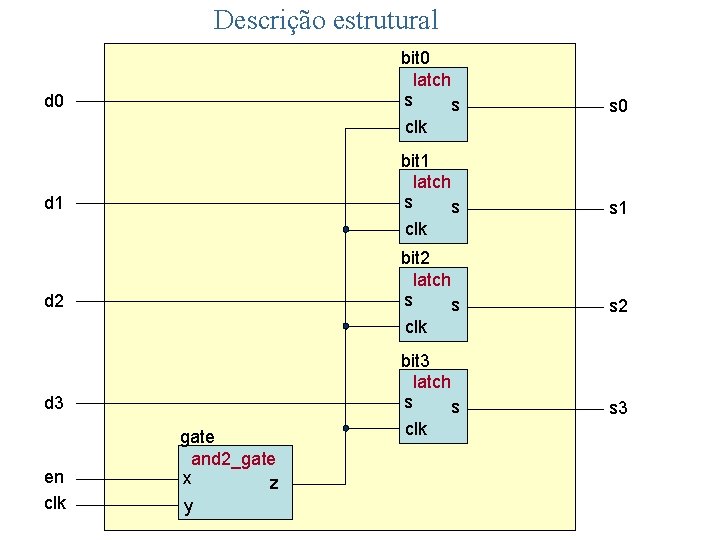

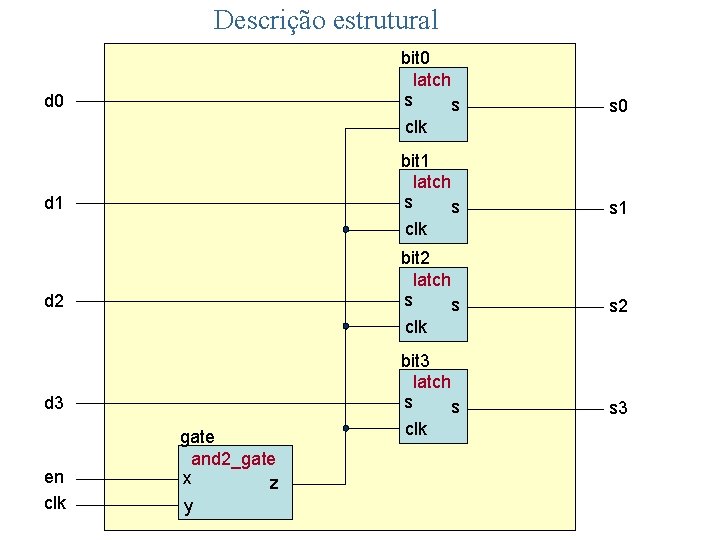

Descrição estrutural bit 0 latch s s d 0 s 0 clk bit 1 latch s s d 1 s 1 clk bit 2 latch s s d 2 s 2 clk bit 3 latch s s d 3 en clk gate and 2_gate x z y clk s 3

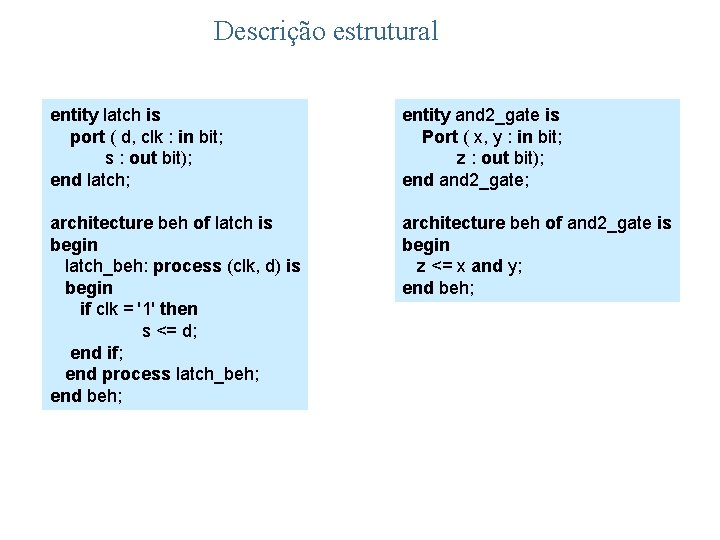

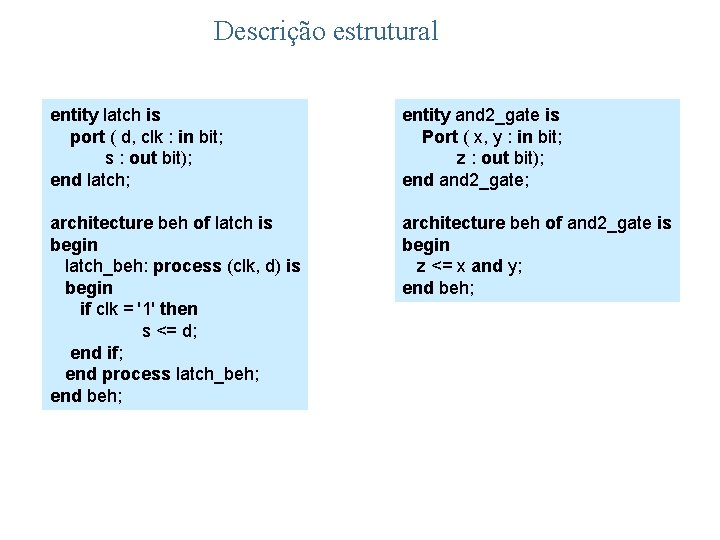

Descrição estrutural entity latch is port ( d, clk : in bit; s : out bit); end latch; entity and 2_gate is Port ( x, y : in bit; z : out bit); end and 2_gate; architecture beh of latch is begin latch_beh: process (clk, d) is begin if clk = '1' then s <= d; end if; end process latch_beh; end beh; architecture beh of and 2_gate is begin z <= x and y; end beh;

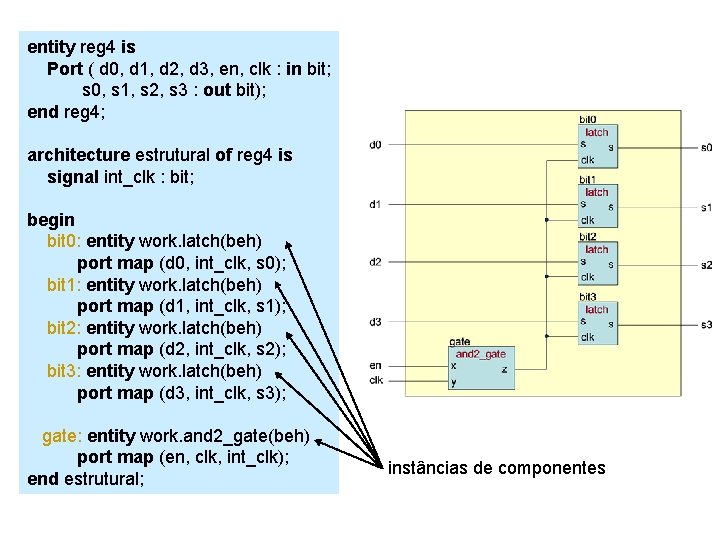

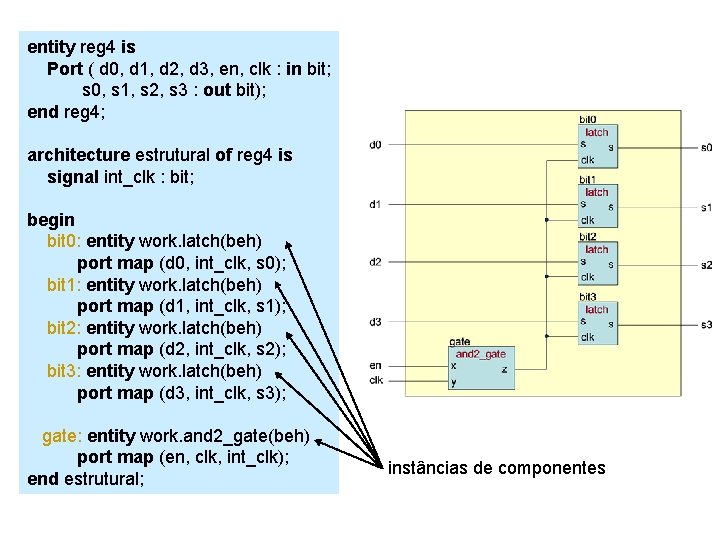

entity reg 4 is Port ( d 0, d 1, d 2, d 3, en, clk : in bit; s 0, s 1, s 2, s 3 : out bit); end reg 4; architecture estrutural of reg 4 is signal int_clk : bit; begin bit 0: entity work. latch(beh) port map (d 0, int_clk, s 0); bit 1: entity work. latch(beh) port map (d 1, int_clk, s 1); bit 2: entity work. latch(beh) port map (d 2, int_clk, s 2); bit 3: entity work. latch(beh) port map (d 3, int_clk, s 3); gate: entity work. and 2_gate(beh) port map (en, clk, int_clk); end estrutural; instâncias de componentes

----- Uncomment the following lines to use the declarations that are provided for instantiating Xilinx primitive components. library UNISIM; use UNISIM. VComponents. all;

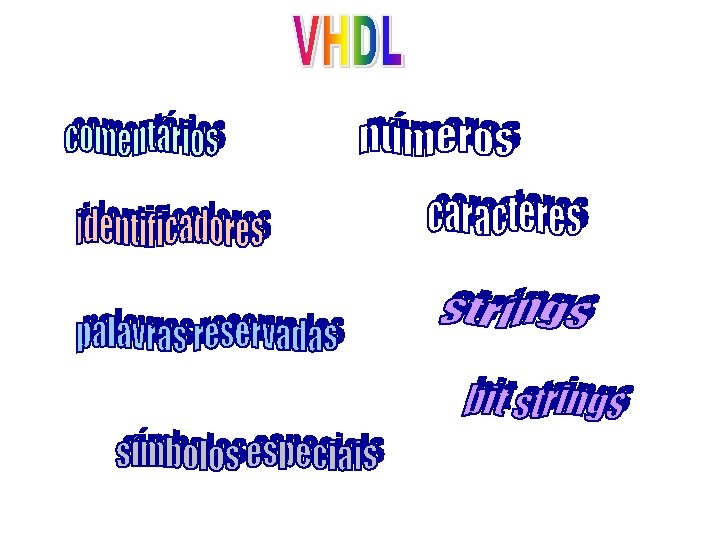

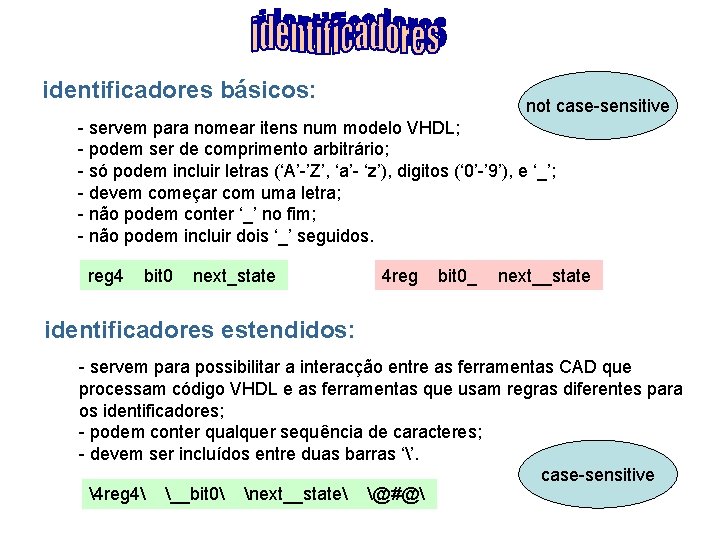

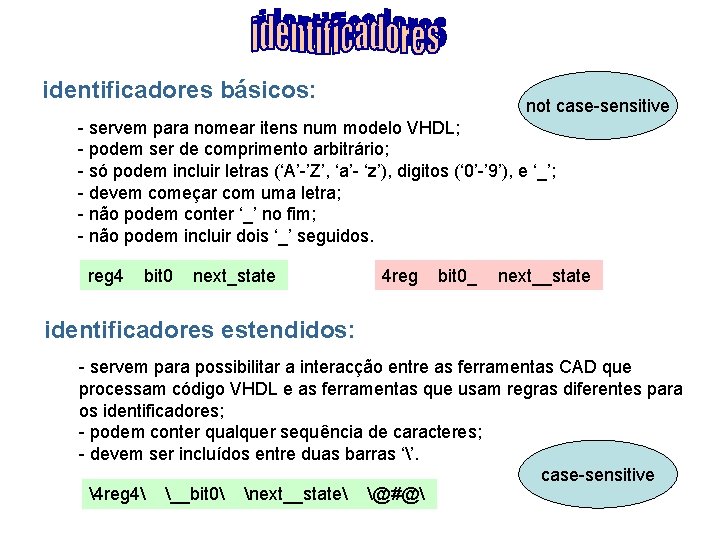

identificadores básicos: not case-sensitive - servem para nomear itens num modelo VHDL; - podem ser de comprimento arbitrário; - só podem incluir letras (‘A’-’Z’, ‘a’- ‘z’), digitos (‘ 0’-’ 9’), e ‘_’; - devem começar com uma letra; - não podem conter ‘_’ no fim; - não podem incluir dois ‘_’ seguidos. reg 4 bit 0 next_state 4 reg bit 0_ next__state identificadores estendidos: - servem para possibilitar a interacção entre as ferramentas CAD que processam código VHDL e as ferramentas que usam regras diferentes para os identificadores; - podem conter qualquer sequência de caracteres; - devem ser incluídos entre duas barras ‘’. case-sensitive 4 reg 4 __bit 0 next__state @#@

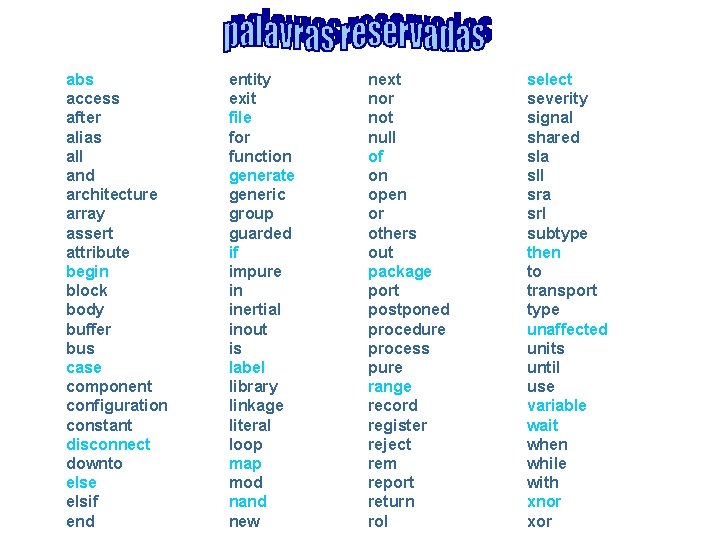

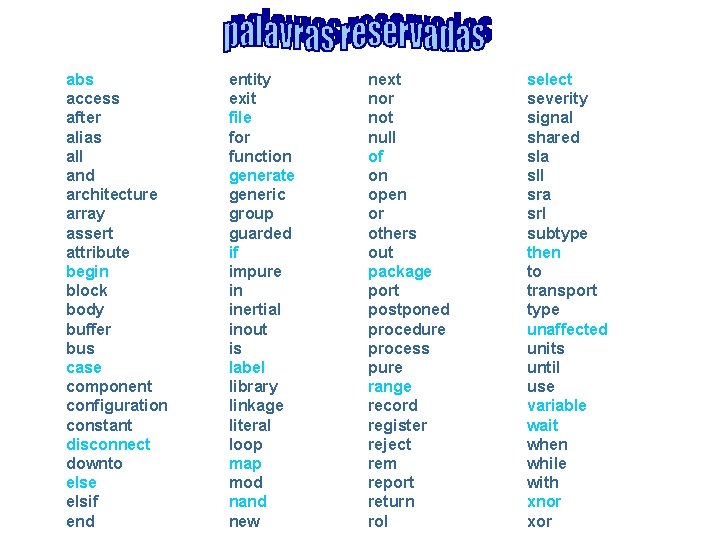

abs access after alias all and architecture array assert attribute begin block body buffer bus case component configuration constant disconnect downto else elsif end entity exit file for function generate generic group guarded if impure in inertial inout is label library linkage literal loop map mod nand new next nor not null of on open or others out package port postponed procedure process pure range record register reject rem report return rol select severity signal shared sla sll sra srl subtype then to transport type unaffected units until use variable wait when while with xnor xor

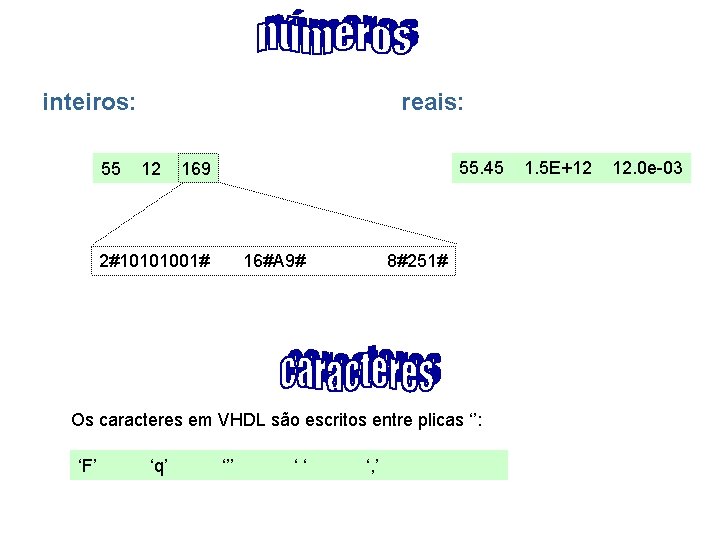

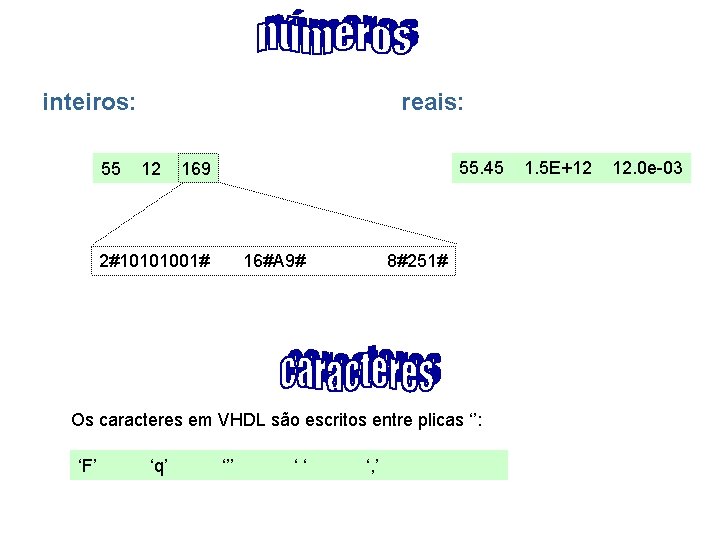

reais: inteiros: 55 12 55. 45 169 2#10101001# 16#A 9# 8#251# Os caracteres em VHDL são escritos entre plicas ‘’: ‘F’ ‘q’ ‘’’ ‘‘ ‘, ’ 1. 5 E+12 12. 0 e-03

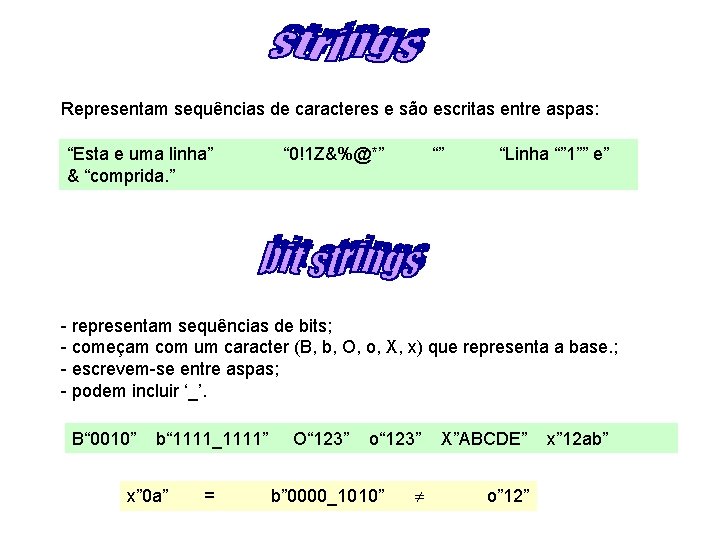

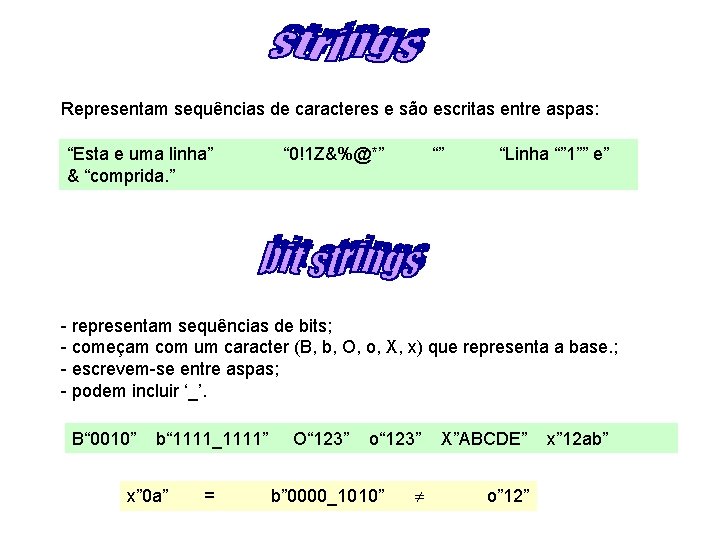

Representam sequências de caracteres e são escritas entre aspas: “Esta e uma linha” & “comprida. ” “ 0!1 Z&%@*” “” “Linha “” 1”” e” - representam sequências de bits; - começam com um caracter (B, b, O, o, X, x) que representa a base. ; - escrevem-se entre aspas; - podem incluir ‘_’. B“ 0010” b“ 1111_1111” x” 0 a” = O“ 123” o“ 123” X”ABCDE” o” 12” b” 0000_1010” x” 12 ab”

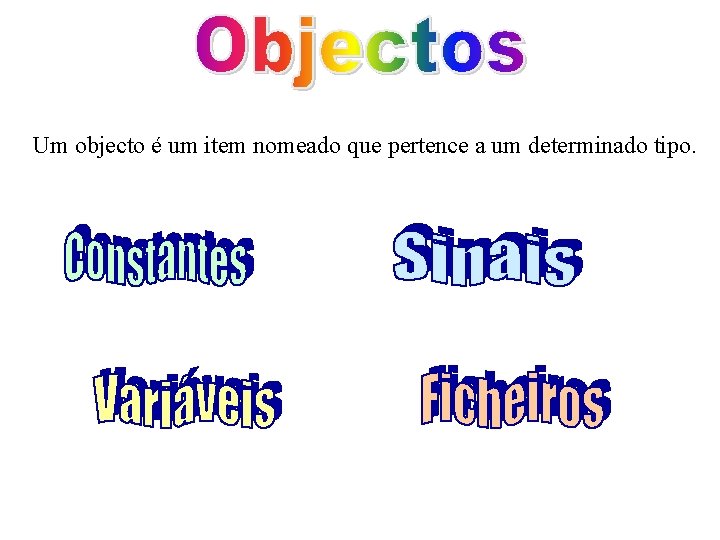

Um objecto é um item nomeado que pertence a um determinado tipo.

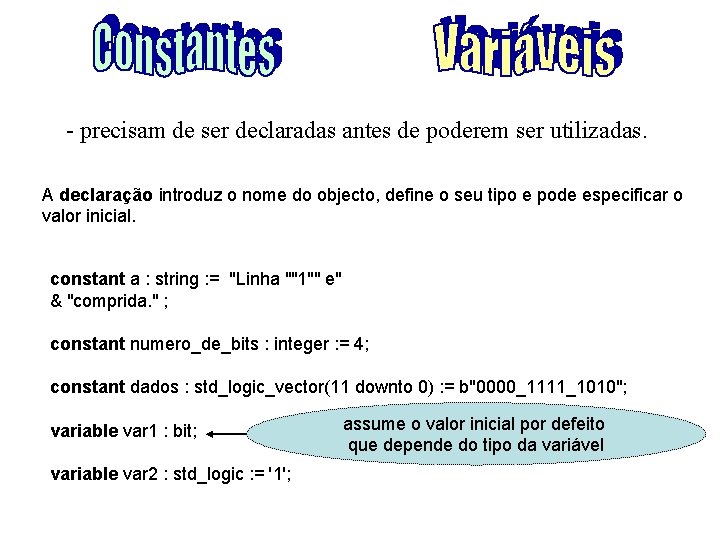

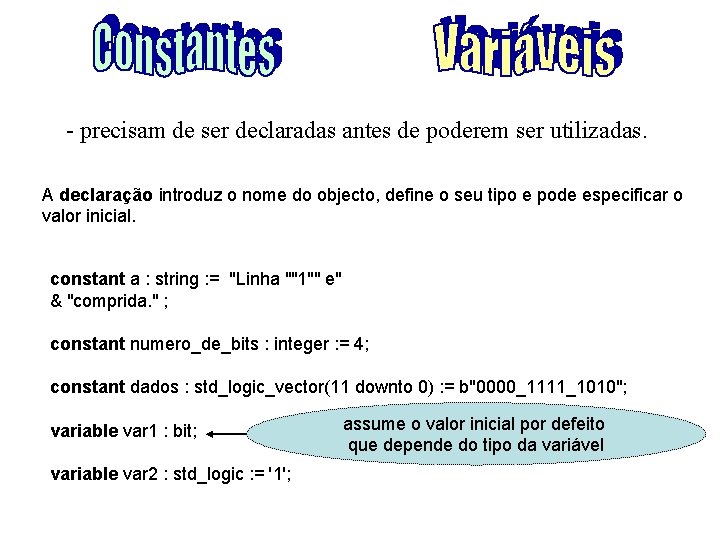

- precisam de ser declaradas antes de poderem ser utilizadas. A declaração introduz o nome do objecto, define o seu tipo e pode especificar o valor inicial. constant a : string : = "Linha ""1"" e" & "comprida. " ; constant numero_de_bits : integer : = 4; constant dados : std_logic_vector(11 downto 0) : = b"0000_1111_1010"; variable var 1 : bit; variable var 2 : std_logic : = '1'; assume o valor inicial por defeito que depende do tipo da variável

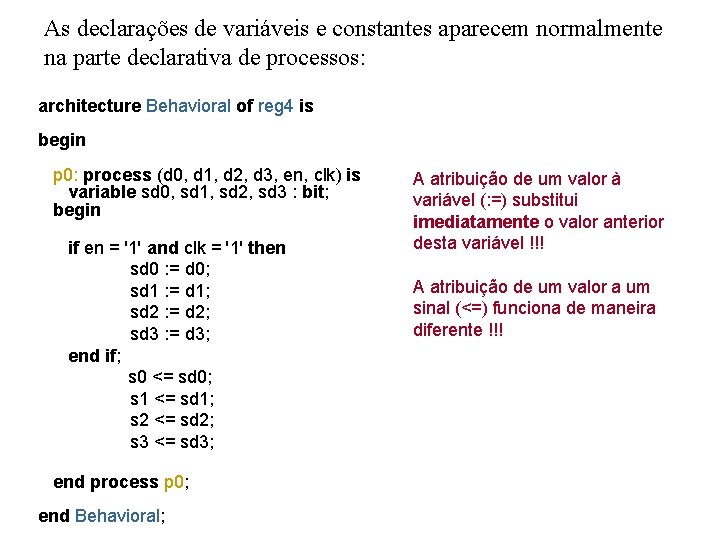

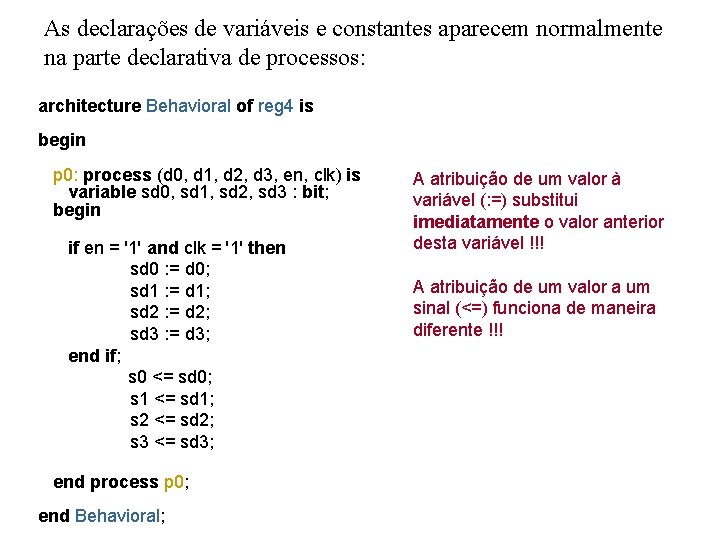

As declarações de variáveis e constantes aparecem normalmente na parte declarativa de processos: architecture Behavioral of reg 4 is begin p 0: process (d 0, d 1, d 2, d 3, en, clk) is variable sd 0, sd 1, sd 2, sd 3 : bit; begin if en = '1' and clk = '1' then sd 0 : = d 0; sd 1 : = d 1; sd 2 : = d 2; sd 3 : = d 3; end if; s 0 <= sd 0; s 1 <= sd 1; s 2 <= sd 2; s 3 <= sd 3; end process p 0; end Behavioral; A atribuição de um valor à variável (: =) substitui imediatamente o valor anterior desta variável !!! A atribuição de um valor a um sinal (<=) funciona de maneira diferente !!!

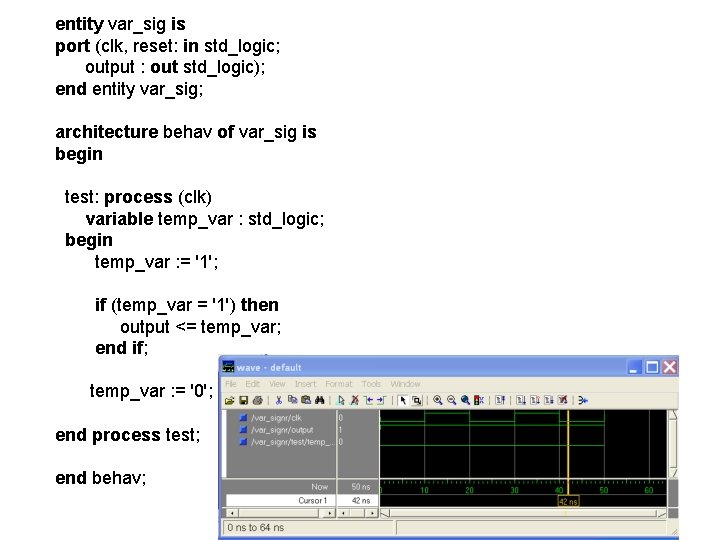

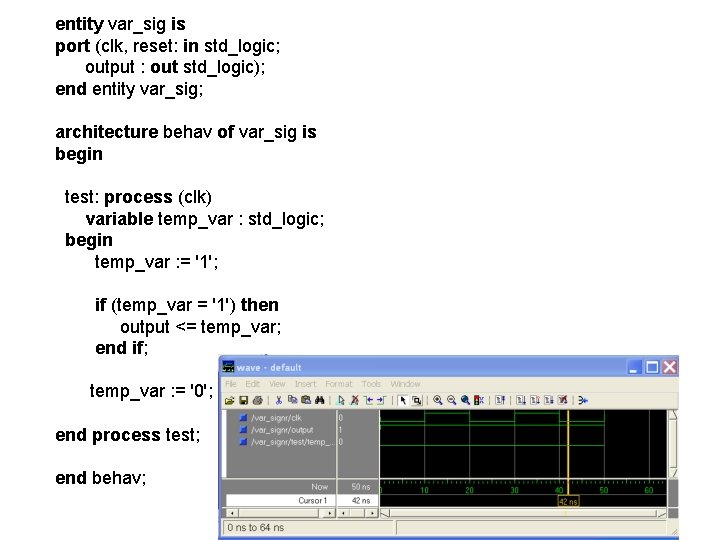

entity var_sig is port (clk, reset: in std_logic; output : out std_logic); end entity var_sig; architecture behav of var_sig is begin test: process (clk) variable temp_var : std_logic; begin temp_var : = '1'; if (temp_var = '1') then output <= temp_var; end if; temp_var : = '0'; end process test; end behav;

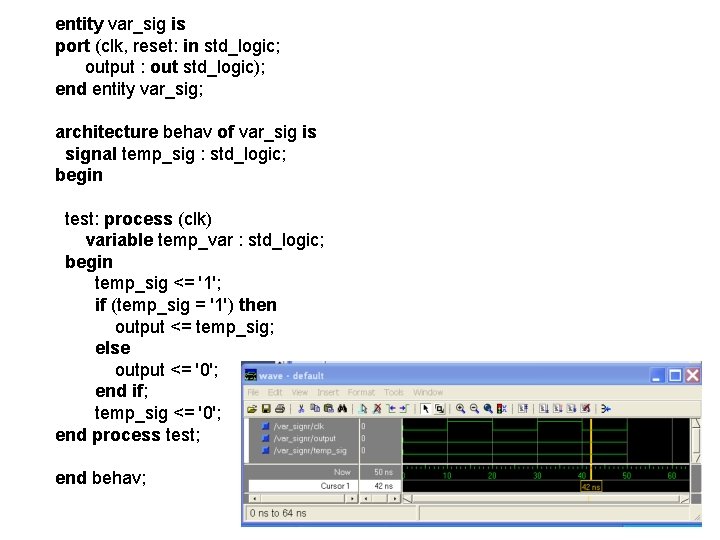

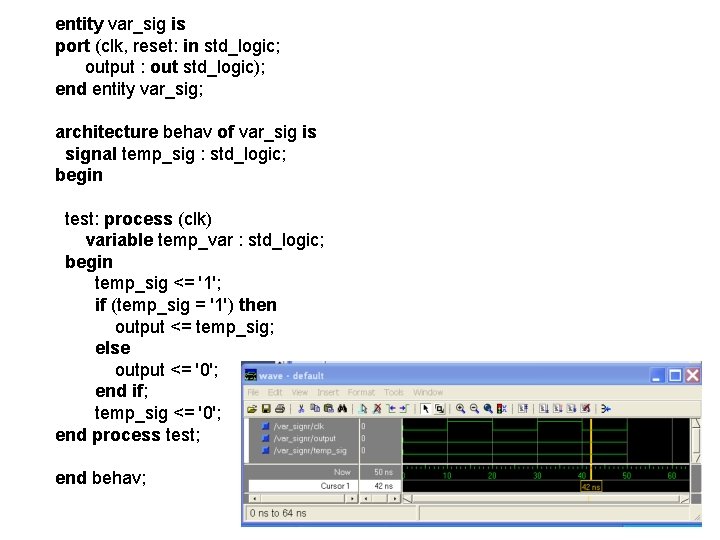

entity var_sig is port (clk, reset: in std_logic; output : out std_logic); end entity var_sig; architecture behav of var_sig is signal temp_sig : std_logic; begin test: process (clk) variable temp_var : std_logic; begin temp_sig <= '1'; if (temp_sig = '1') then output <= temp_sig; else output <= '0'; end if; temp_sig <= '0'; end process test; end behav;