VHDL VHSIC Hardware Description Language VHSIC Very High

![• Syntax of PROCESS [label: ] PROCESS (sensitivity list) [VARIABLE name type [range] • Syntax of PROCESS [label: ] PROCESS (sensitivity list) [VARIABLE name type [range]](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-58.jpg)

![• WHILE/LOOP (loop is repeated until a condition no longer holds) [label: ] • WHILE/LOOP (loop is repeated until a condition no longer holds) [label: ]](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-67.jpg)

![• NEXT (used for skipping loop steps) [label: ] NEXT [loop_label] [WHEN condition]; • NEXT (used for skipping loop steps) [label: ] NEXT [loop_label] [WHEN condition];](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-68.jpg)

- Slides: 71

VHDL VHSIC Hardware Description Language VHSIC- Very High Speed Integrated Circuits

• Hardware Description Language • It is intended for circuit synthesis and circuit simulation • It is a standard, technology/vendor independent language, and therefore portable and usable • Applications of VHDL- in the field of Programmable logic devices (CPLD and FPGA), ASICs. • Statements in VHDL are concurrent (parallel). Hence it is usually referred to as a code.

EDA tools • Several tools available for circuit synthesis, implementation and simulation using VHDL. • Tools: Altera’s Quartus II Xilinx’s ISE Suite

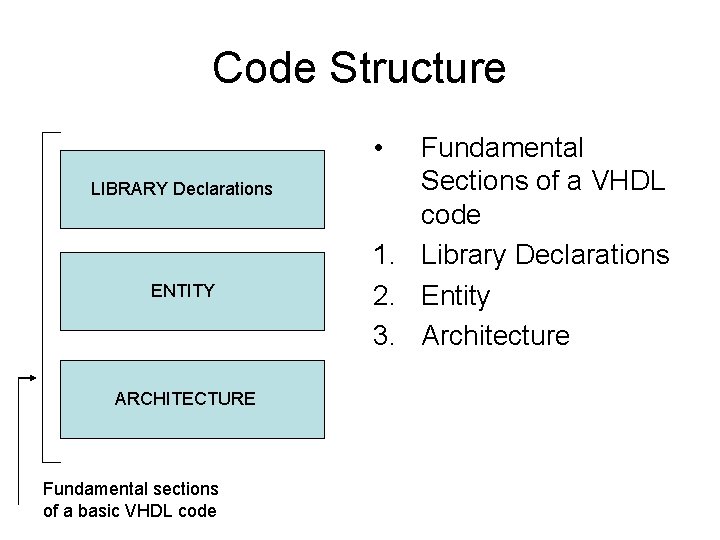

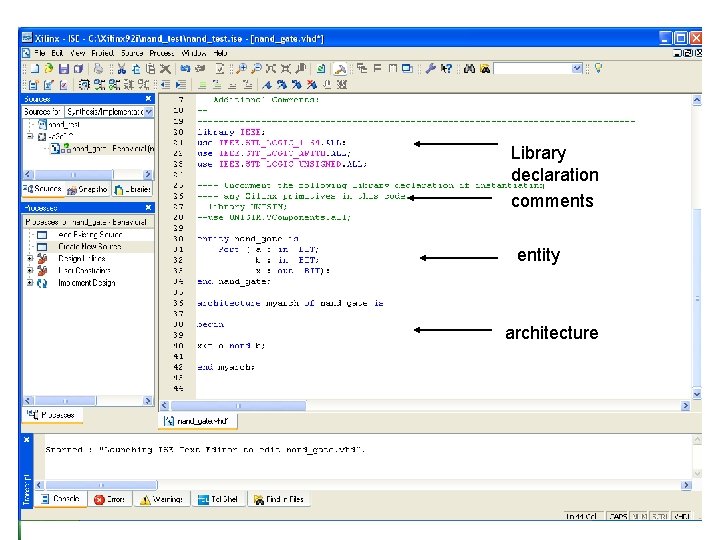

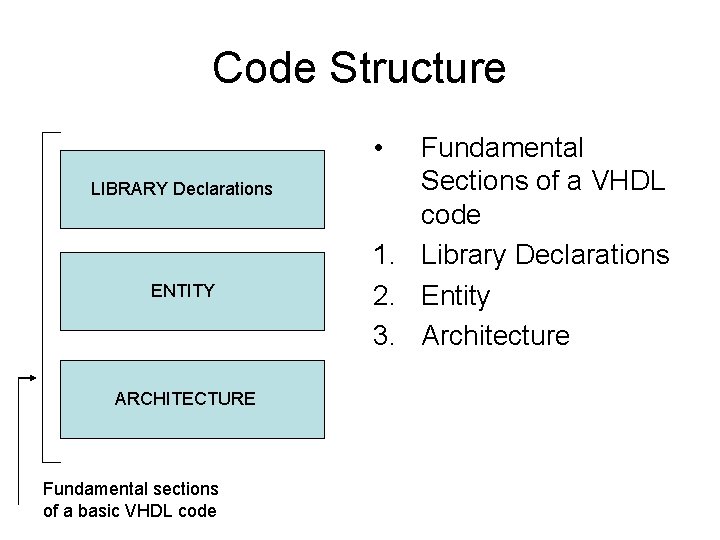

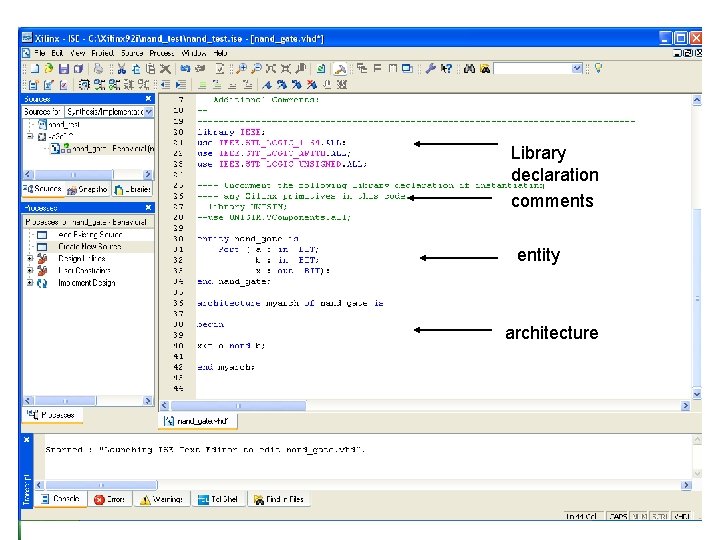

Code Structure • LIBRARY Declarations ENTITY ARCHITECTURE Fundamental sections of a basic VHDL code Fundamental Sections of a VHDL code 1. Library Declarations 2. Entity 3. Architecture

Library Declarations • Contains a list of all libraries to be used in the design • Examples: ieee, std, work etc. • Declaration of library LIBRARY library_name; USE library_name. package_parts;

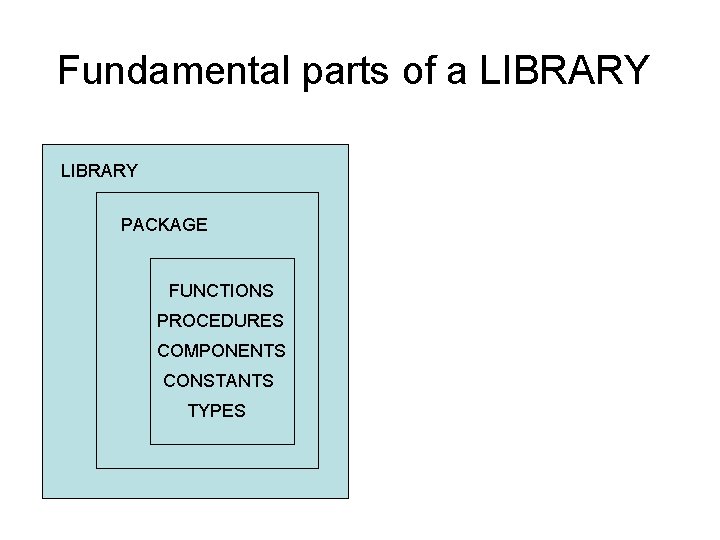

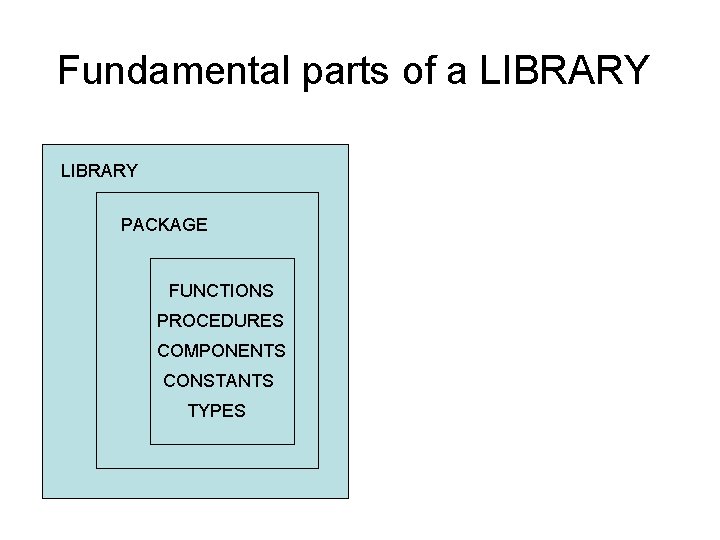

Fundamental parts of a LIBRARY PACKAGE FUNCTIONS PROCEDURES COMPONENTS CONSTANTS TYPES

• At least three packages from three different libraries are needed in a design: ieee. std_logic_1164 (from ieee library) standard (from the std library) work (work library)

Their declarations LIBRARY ieee; USE ieee. std_logic_1164. all; LIBRARY std; USE std. standard. all; LIBRARY work; USE work. all;

What is the purpose of the three packages/libraries mentioned above? ? ? • Std_logic_1164 package of ieee libraryspecifies a multi level logic system • Std is a resource library (data types, text i/o, etc. ) for the VHDL design environment • Work library is where we save our design (. vhd file, plus all files created by the compiler, simulator, etc. )

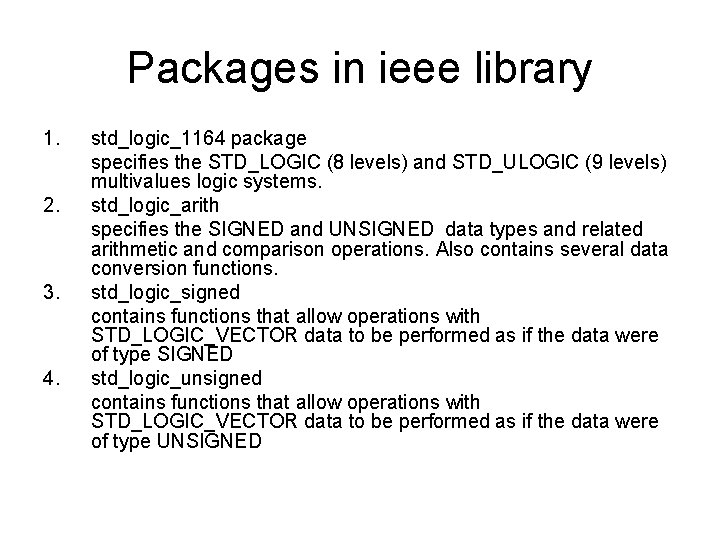

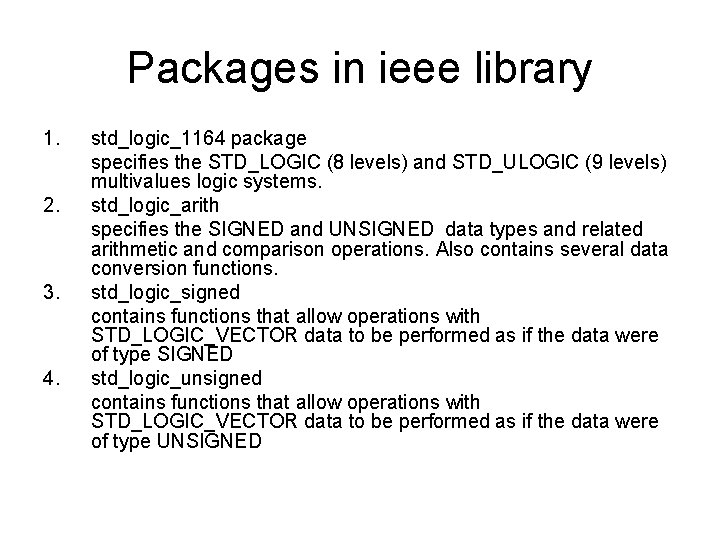

Packages in ieee library 1. 2. 3. 4. std_logic_1164 package specifies the STD_LOGIC (8 levels) and STD_ULOGIC (9 levels) multivalues logic systems. std_logic_arith specifies the SIGNED and UNSIGNED data types and related arithmetic and comparison operations. Also contains several data conversion functions. std_logic_signed contains functions that allow operations with STD_LOGIC_VECTOR data to be performed as if the data were of type SIGNED std_logic_unsigned contains functions that allow operations with STD_LOGIC_VECTOR data to be performed as if the data were of type UNSIGNED

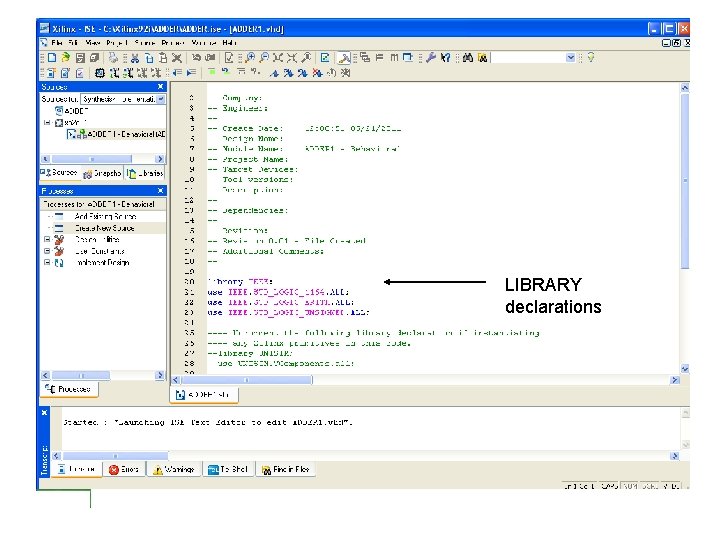

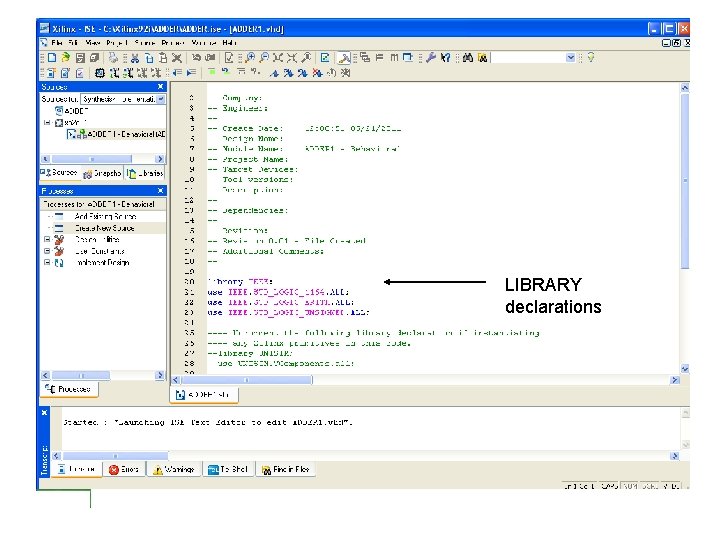

LIBRARY declarations

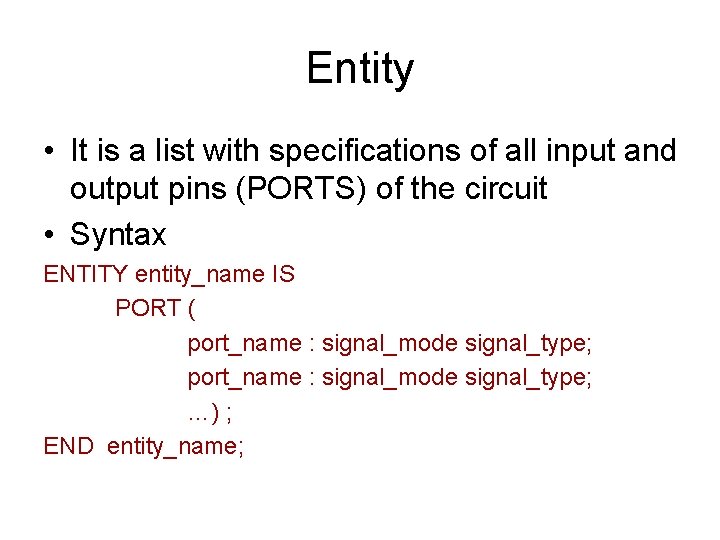

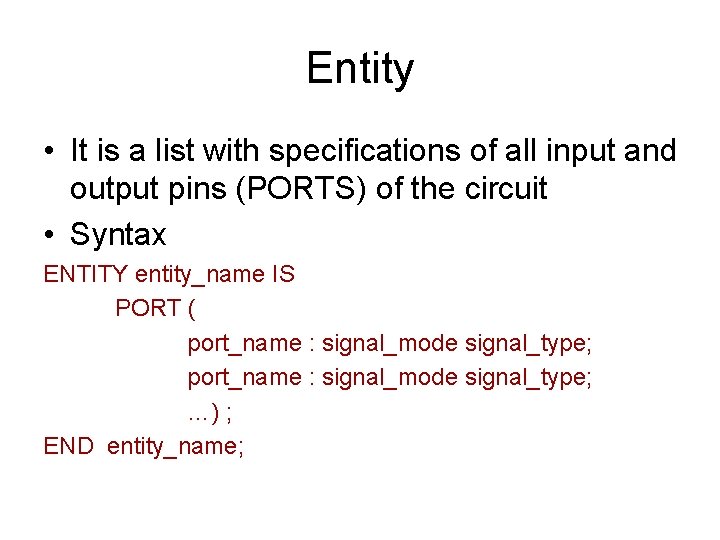

Entity • It is a list with specifications of all input and output pins (PORTS) of the circuit • Syntax ENTITY entity_name IS PORT ( port_name : signal_mode signal_type; …) ; END entity_name;

• 1. 2. 3. 4. Signal mode: IN (unidirectional pin) OUT (unidirectional pin) INOUT (bidirectional) BUFFER (employed when the output signal must be read internally) OUT IN INOUT CIRCUIT BUFFER

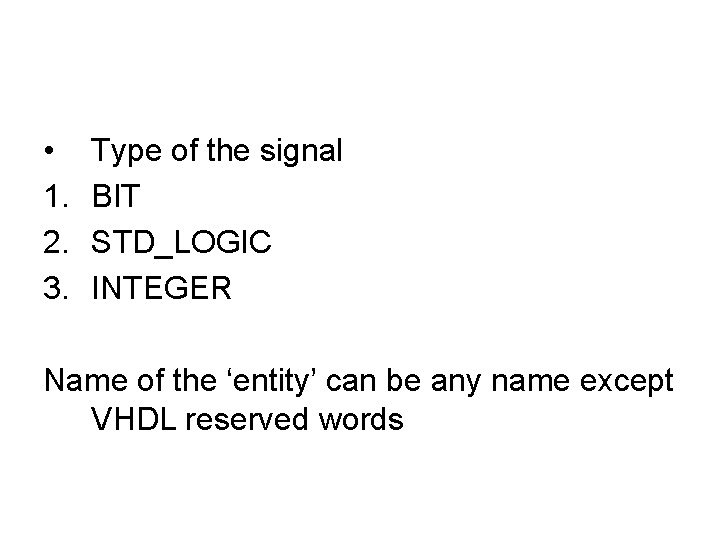

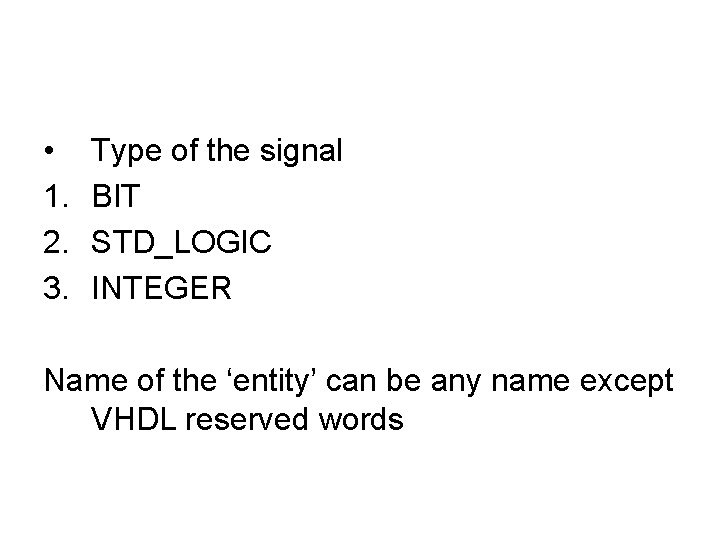

• 1. 2. 3. Type of the signal BIT STD_LOGIC INTEGER Name of the ‘entity’ can be any name except VHDL reserved words

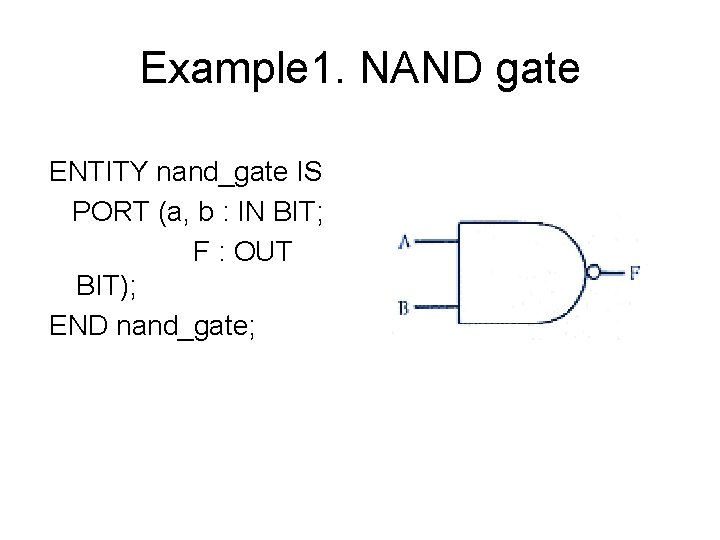

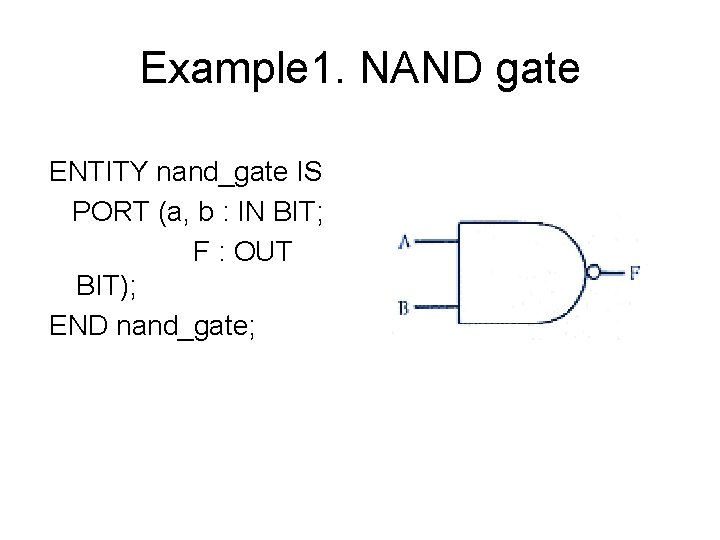

Example 1. NAND gate ENTITY nand_gate IS PORT (a, b : IN BIT; F : OUT BIT); END nand_gate;

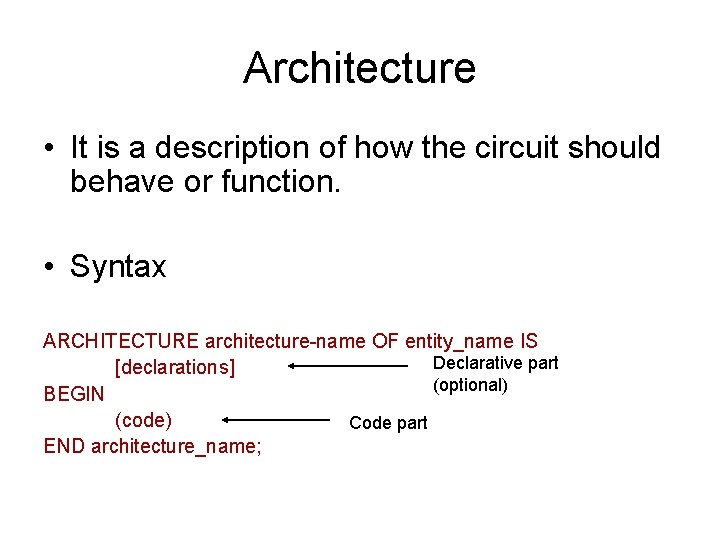

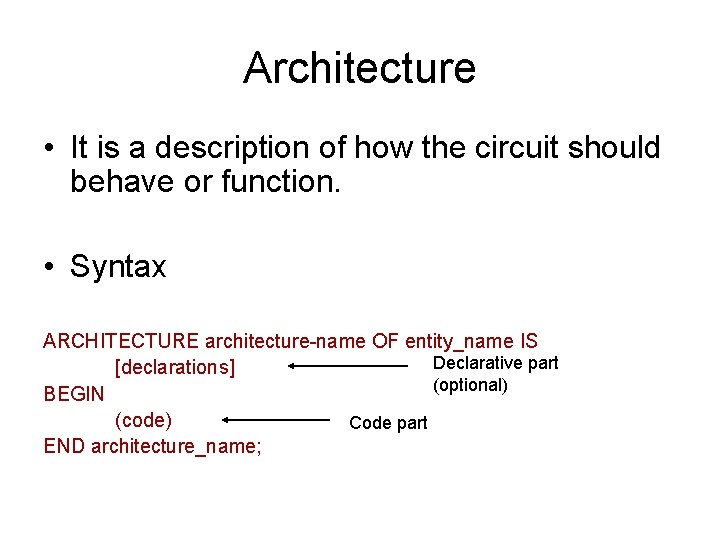

Architecture • It is a description of how the circuit should behave or function. • Syntax ARCHITECTURE architecture-name OF entity_name IS Declarative part [declarations] (optional) BEGIN (code) Code part END architecture_name;

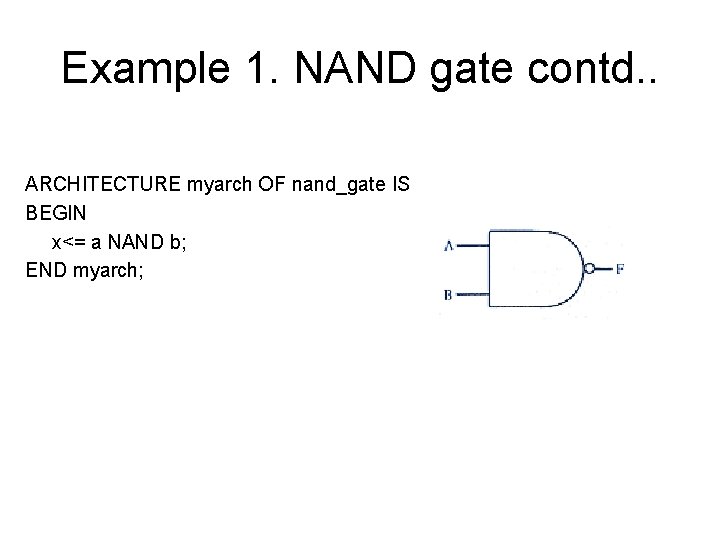

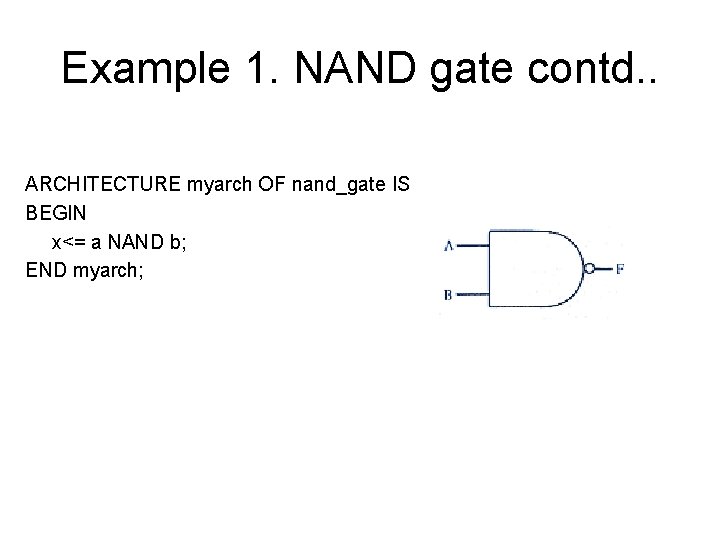

Example 1. NAND gate contd. . ARCHITECTURE myarch OF nand_gate IS BEGIN x<= a NAND b; END myarch;

Library declaration comments entity architecture

Is VHDL case sensitive? ? ? IT IS NOT CASE SENSITIVE To add comments: “--” indicates a comment. Used only to better organize the design

Data Types • Pre-defined Data types VHDL contains a series of pre-defined data types, specified through the IEEE 1076 and IEEE 1164 standards Data type definitions can be found in the following packages/libraries:

• Package standard of library std Defines BIT, BOOLEAN, INTEGER, and REAL data types • Package std_logic_1164 of library ieee Defines STD_LOGIC, STD_ULOGIC data types • Package std_logic_arith of library ieee Defines SIGNED, UNSIGNED, data conversion functions • Packages std_logic_signed and std_logic_unsigned of library ieee Contains functions that allow operations with STD_LOGIC_VECTOR data to be performed as if the data were of type SIGNED or UNSIGNED resp.

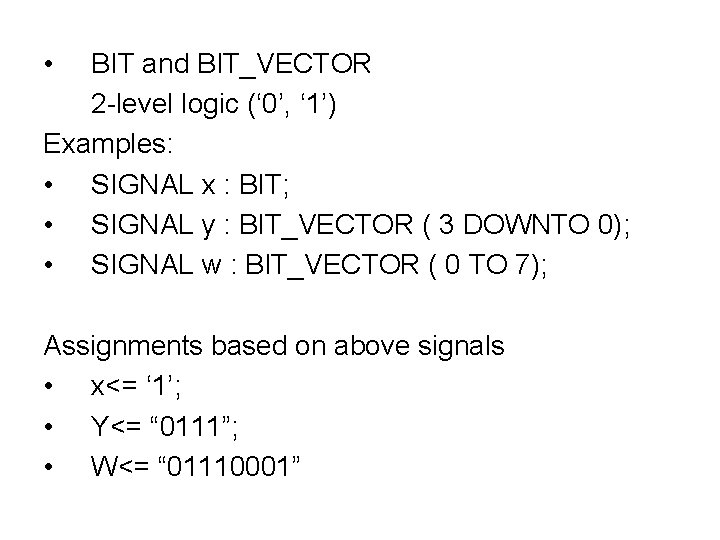

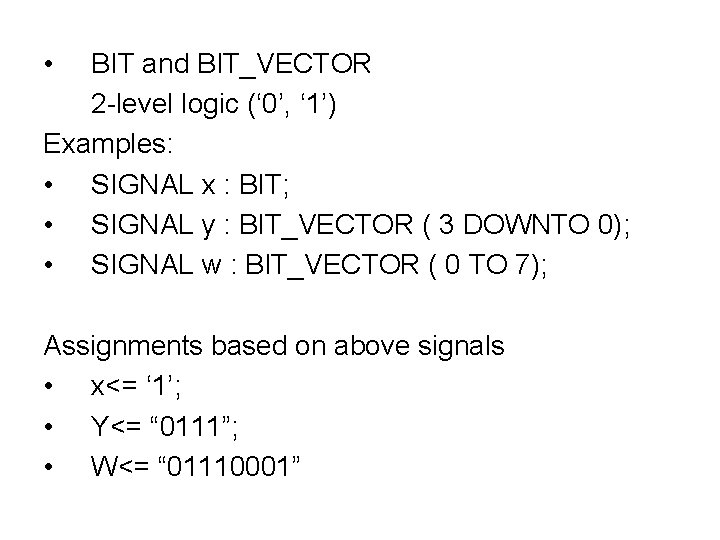

• BIT and BIT_VECTOR 2 -level logic (‘ 0’, ‘ 1’) Examples: • SIGNAL x : BIT; • SIGNAL y : BIT_VECTOR ( 3 DOWNTO 0); • SIGNAL w : BIT_VECTOR ( 0 TO 7); Assignments based on above signals • x<= ‘ 1’; • Y<= “ 0111”; • W<= “ 01110001”

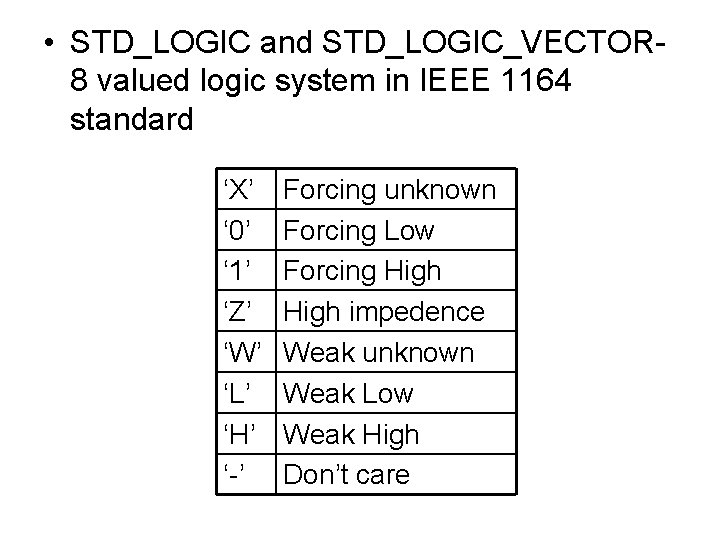

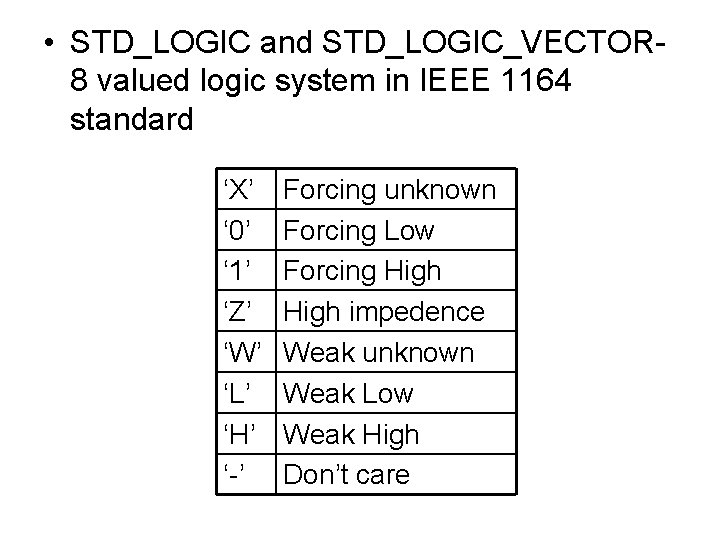

• STD_LOGIC and STD_LOGIC_VECTOR 8 valued logic system in IEEE 1164 standard ‘X’ ‘ 0’ ‘ 1’ ‘Z’ ‘W’ ‘L’ ‘H’ ‘-’ Forcing unknown Forcing Low Forcing High impedence Weak unknown Weak Low Weak High Don’t care

1. SIGNAL x : STD_LOGIC; 2. SIGNAL Y : STD_LOGIC_VECTOR ( 3 DOWNTO 0) : = “ 0001”; (‘: =‘ used to establish the initial value)

• STD_ULOGIC 9 -level logic system introduced in IEEE 1164 standard. It includes an extra logic value ‘U’unresolved

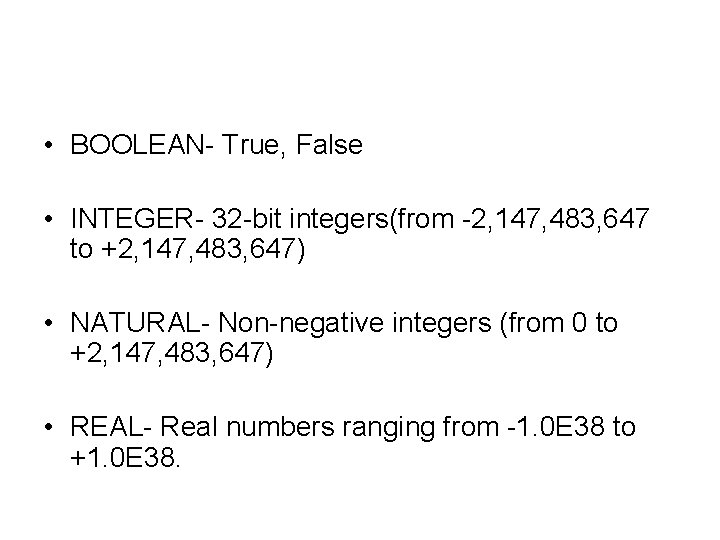

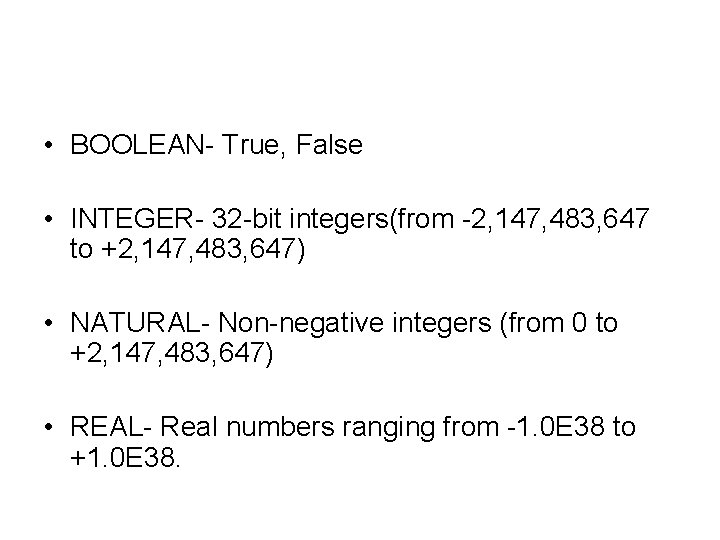

• BOOLEAN- True, False • INTEGER- 32 -bit integers(from -2, 147, 483, 647 to +2, 147, 483, 647) • NATURAL- Non-negative integers (from 0 to +2, 147, 483, 647) • REAL- Real numbers ranging from -1. 0 E 38 to +1. 0 E 38.

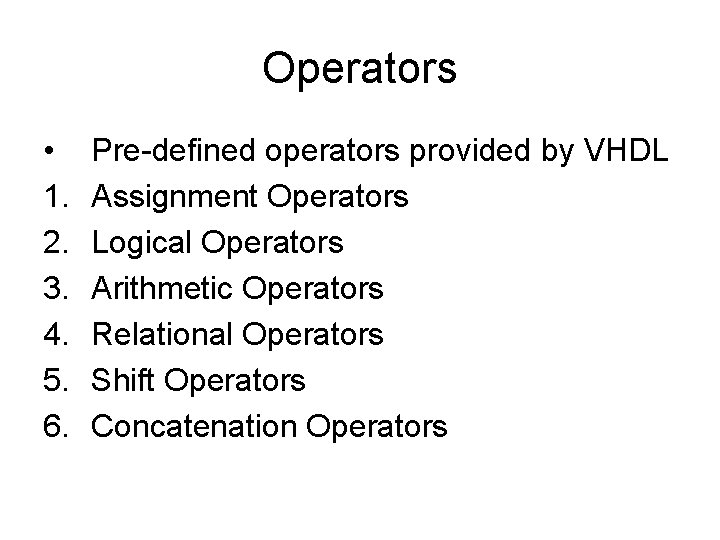

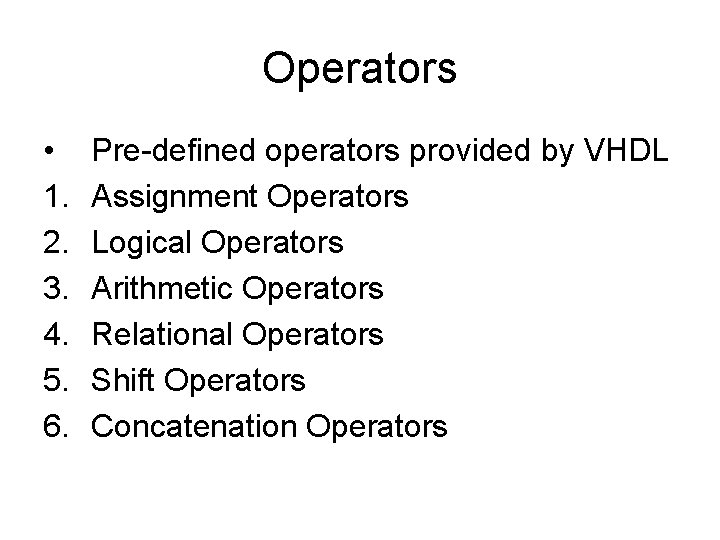

Operators • 1. 2. 3. 4. 5. 6. Pre-defined operators provided by VHDL Assignment Operators Logical Operators Arithmetic Operators Relational Operators Shift Operators Concatenation Operators

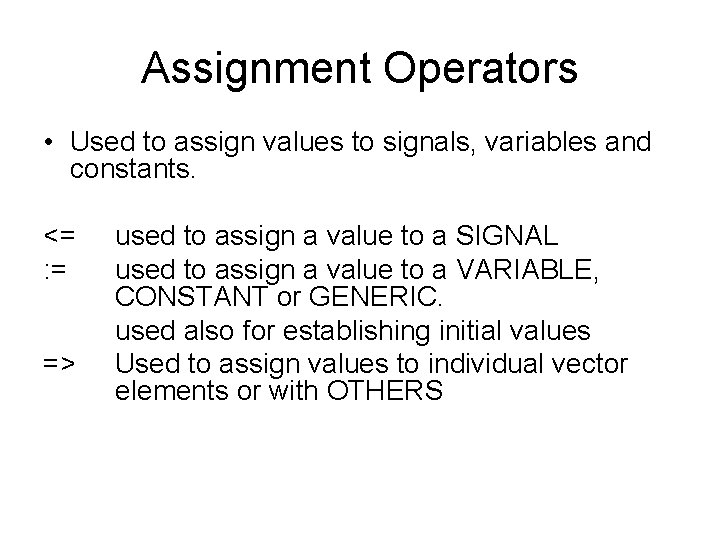

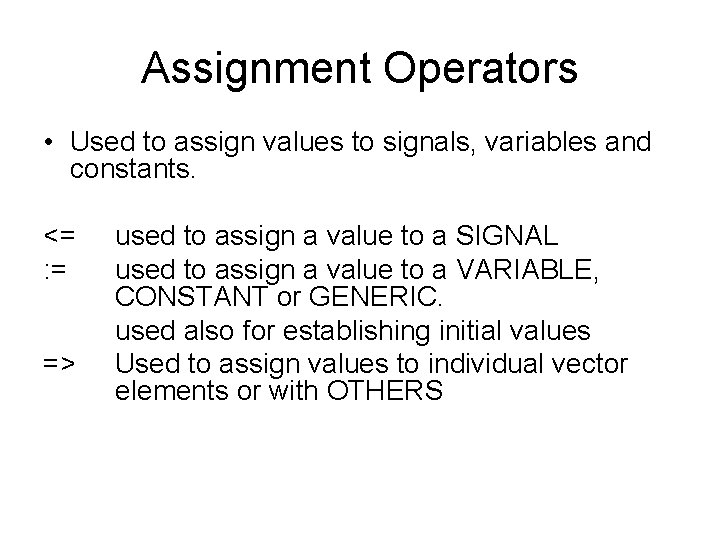

Assignment Operators • Used to assign values to signals, variables and constants. <= : = => used to assign a value to a SIGNAL used to assign a value to a VARIABLE, CONSTANT or GENERIC. used also for establishing initial values Used to assign values to individual vector elements or with OTHERS

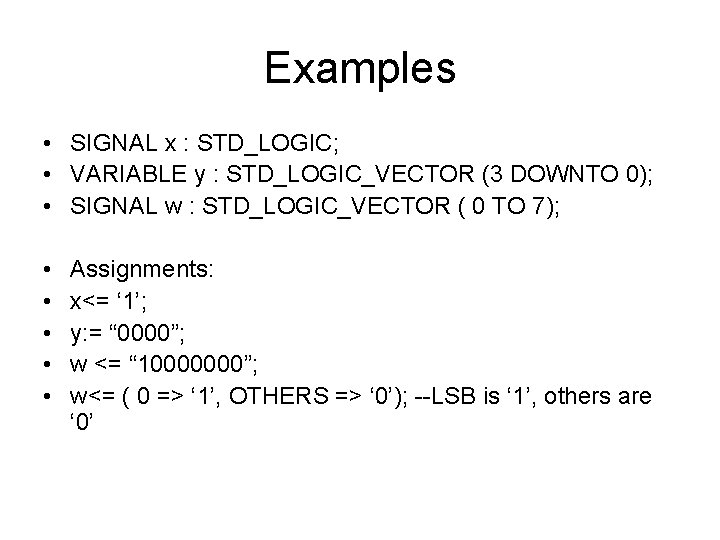

Examples • SIGNAL x : STD_LOGIC; • VARIABLE y : STD_LOGIC_VECTOR (3 DOWNTO 0); • SIGNAL w : STD_LOGIC_VECTOR ( 0 TO 7); • • • Assignments: x<= ‘ 1’; y: = “ 0000”; w <= “ 10000000”; w<= ( 0 => ‘ 1’, OTHERS => ‘ 0’); --LSB is ‘ 1’, others are ‘ 0’

Logical Operators • Used to perform logical operations • Data must be of type BIT, STD_LOGIC or STD_ULOGIC, BIT_VECTOR, STD_ULOGIC_VECTOR

• 1. 2. 3. 4. 5. 6. 7. Logical Operators NOT AND OR NAND NOR XNOR

Examples • y <= NOT a AND b; • y <= NOT (a AND b); • y <= a NAND b;

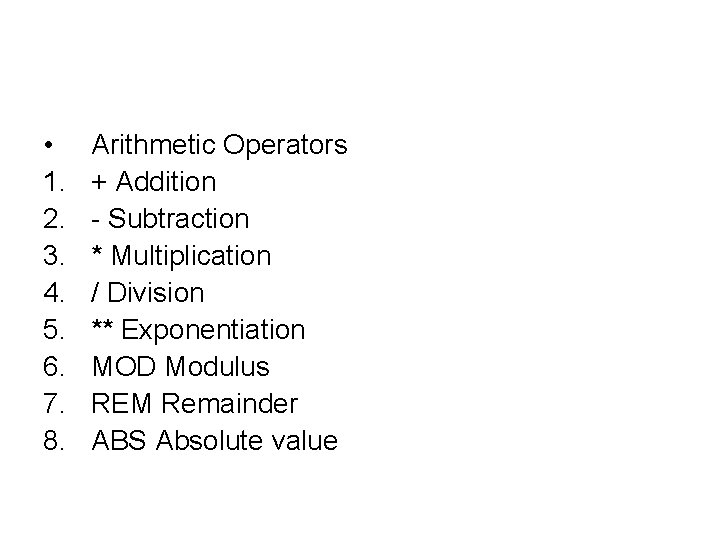

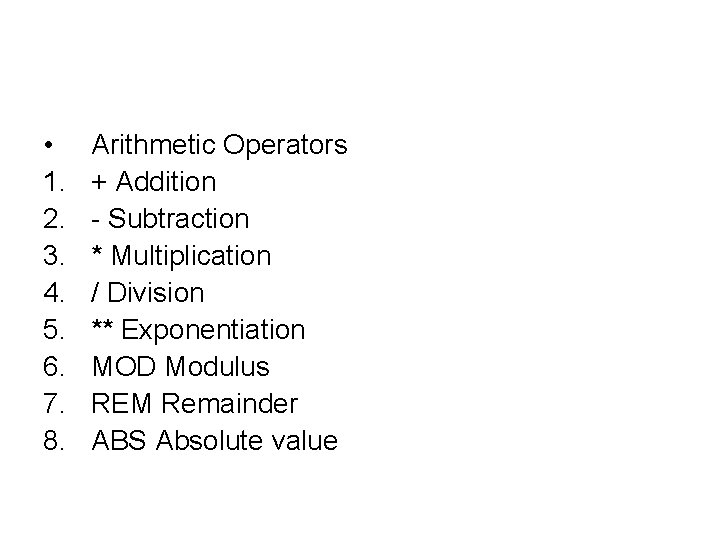

Arithmetic Operators • Used to perform arithmetic operations • Data type can be INTEGER, SIGNED, UNSIGNED or REAL

• 1. 2. 3. 4. 5. 6. 7. 8. Arithmetic Operators + Addition - Subtraction * Multiplication / Division ** Exponentiation MOD Modulus REM Remainder ABS Absolute value

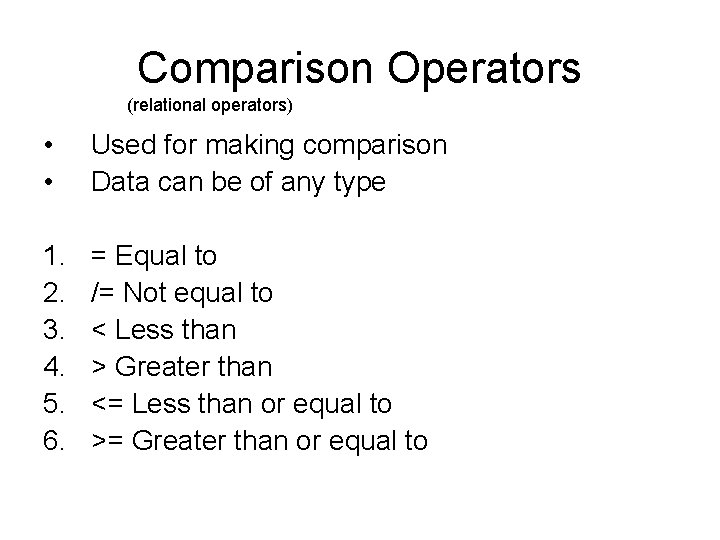

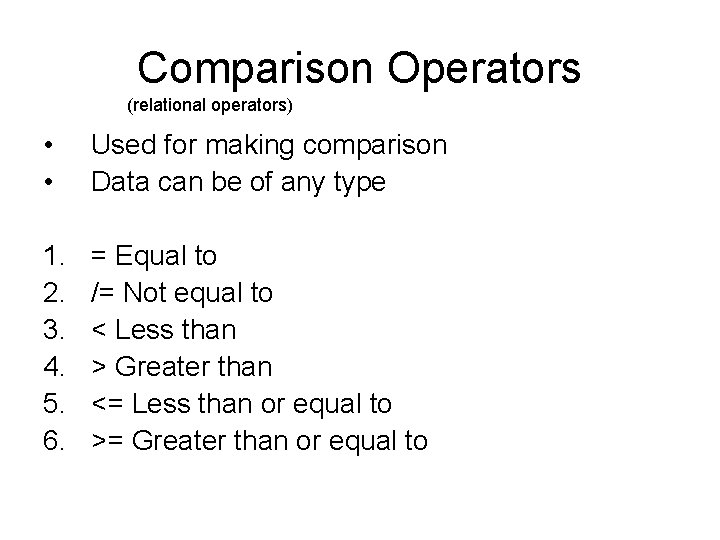

Comparison Operators (relational operators) • • Used for making comparison Data can be of any type 1. 2. 3. 4. 5. 6. = Equal to /= Not equal to < Less than > Greater than <= Less than or equal to >= Greater than or equal to

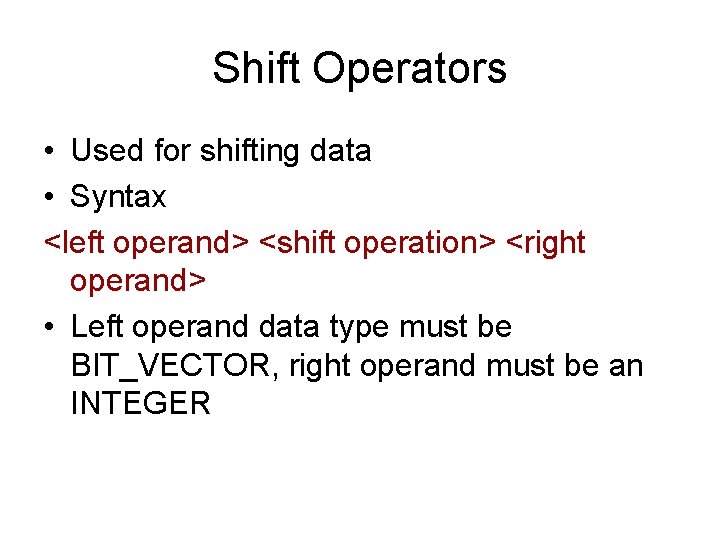

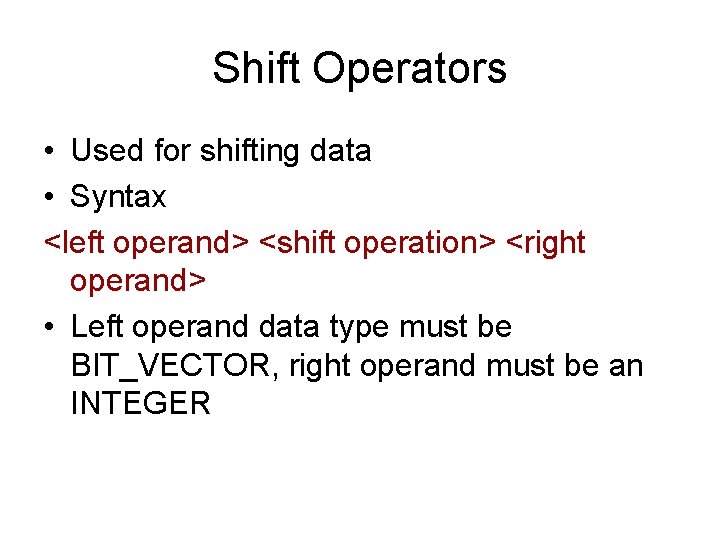

Shift Operators • Used for shifting data • Syntax <left operand> <shift operation> <right operand> • Left operand data type must be BIT_VECTOR, right operand must be an INTEGER

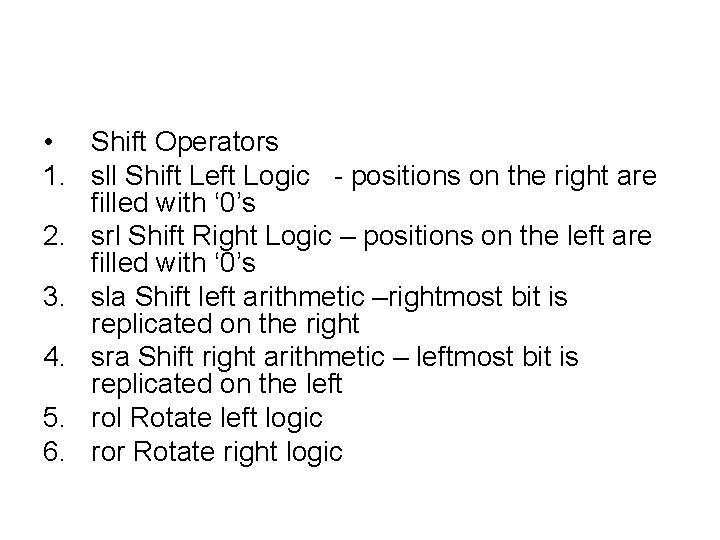

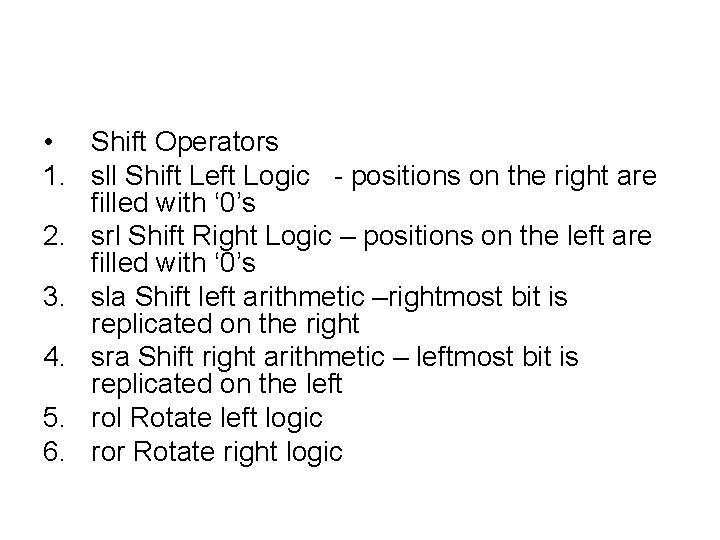

• Shift Operators 1. sll Shift Left Logic - positions on the right are filled with ‘ 0’s 2. srl Shift Right Logic – positions on the left are filled with ‘ 0’s 3. sla Shift left arithmetic –rightmost bit is replicated on the right 4. sra Shift right arithmetic – leftmost bit is replicated on the left 5. rol Rotate left logic 6. ror Rotate right logic

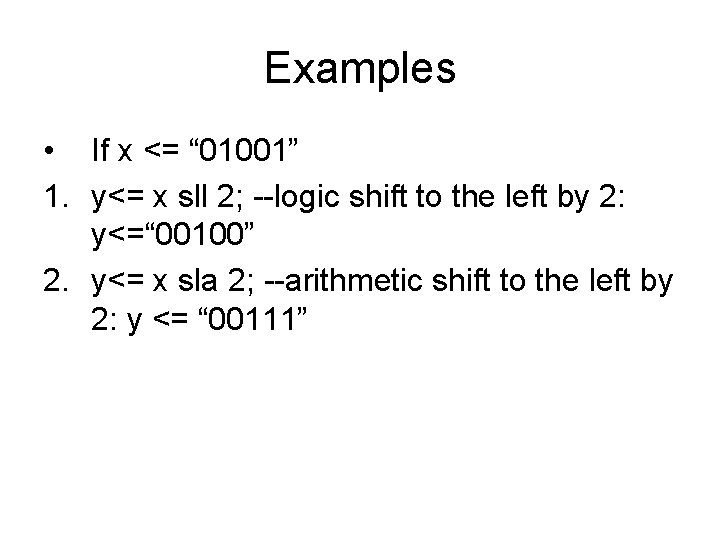

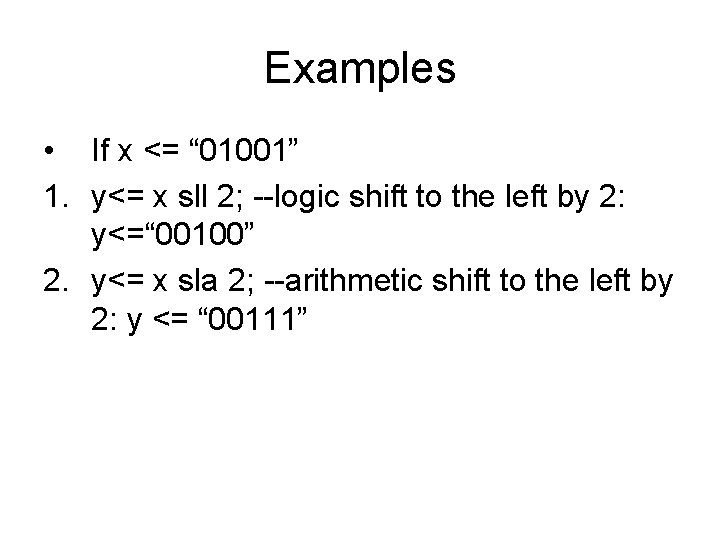

Examples • If x <= “ 01001” 1. y<= x sll 2; --logic shift to the left by 2: y<=“ 00100” 2. y<= x sla 2; --arithmetic shift to the left by 2: y <= “ 00111”

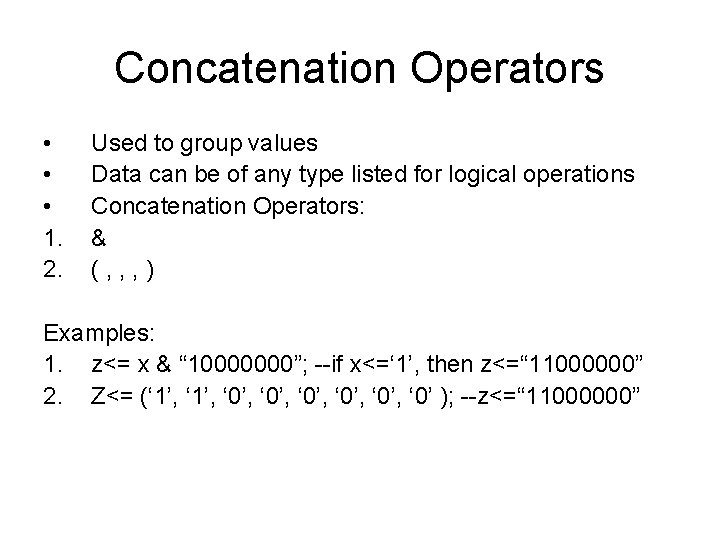

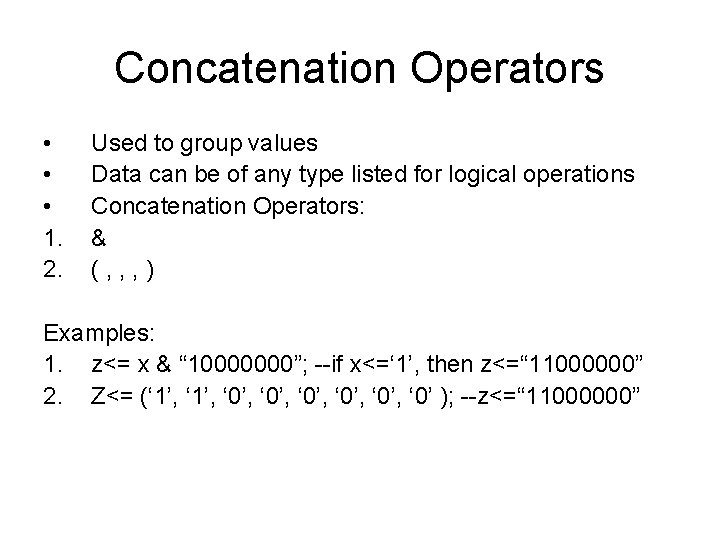

Concatenation Operators • • • 1. 2. Used to group values Data can be of any type listed for logical operations Concatenation Operators: & (, , , ) Examples: 1. z<= x & “ 10000000”; --if x<=‘ 1’, then z<=“ 11000000” 2. Z<= (‘ 1’, ‘ 0’, ‘ 0’, ‘ 0’ ); --z<=“ 11000000”

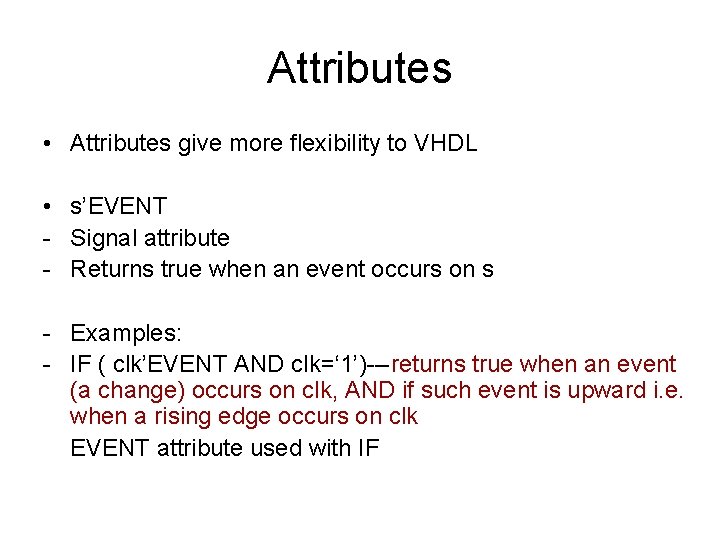

Attributes • Attributes give more flexibility to VHDL • s’EVENT - Signal attribute - Returns true when an event occurs on s - Examples: - IF ( clk’EVENT AND clk=‘ 1’)---returns true when an event (a change) occurs on clk, AND if such event is upward i. e. when a rising edge occurs on clk EVENT attribute used with IF

Modeling Styles • Different modeling styles used in architecture— 1. Structural Style of Modeling-(as a set of interconnected components to represent structure) Dataflow style of modeling-(as a set of concurrent assignment statements to represent dataflow) Behavioral Style of Modeling- (as a set of sequential assignment statements to represent behaviour 0 Mixed Style of Modeling- (any combination of the above three modeling styles) 2. 3. 4.

Structural Style of Modeling • Entity is described as a set of interconnected components • Architecture body consists of two parts: 1. Declarative part 2. Statement part • The structural representation doesn’t say anything about its functionality

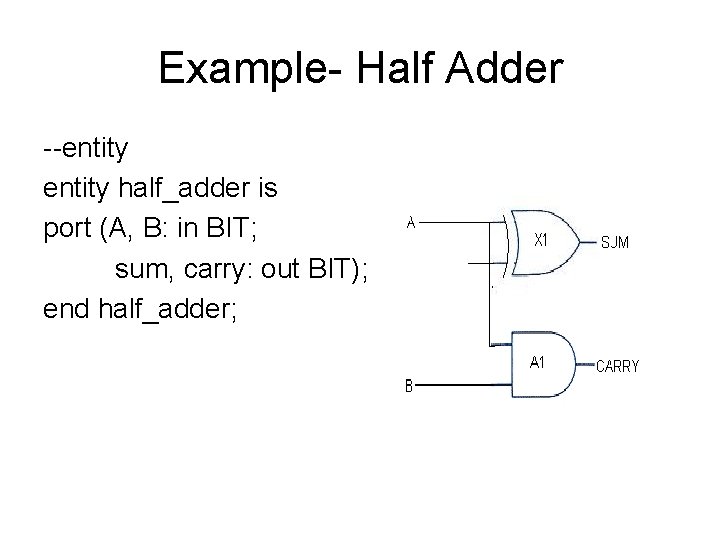

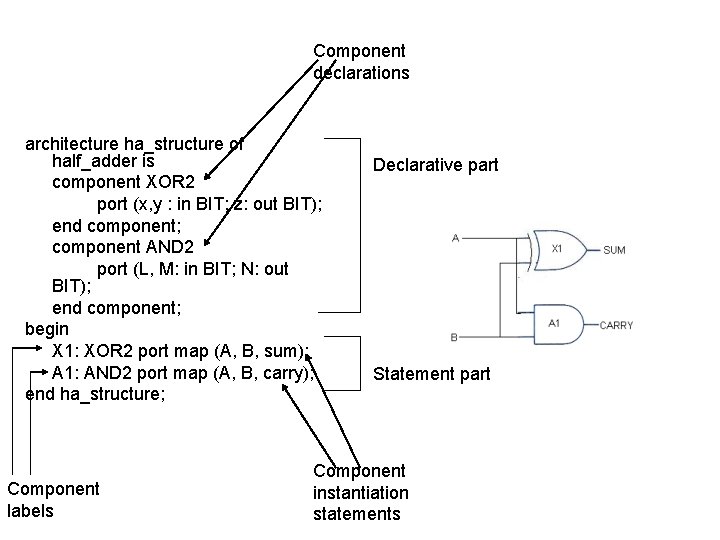

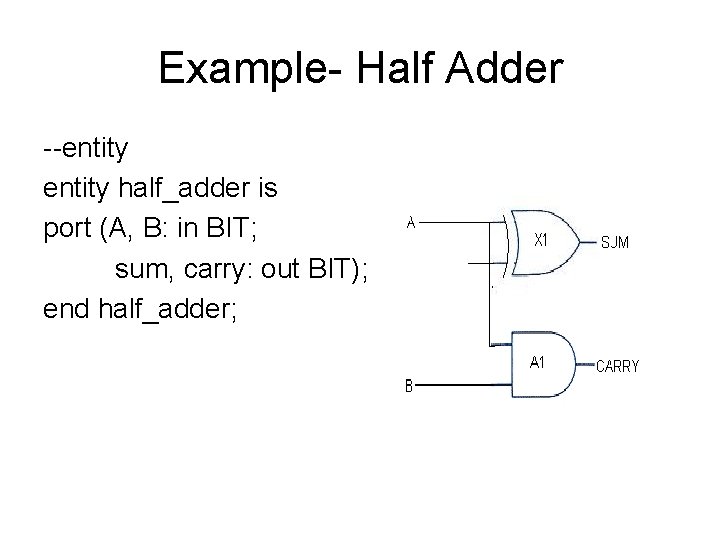

Example- Half Adder --entity half_adder is port (A, B: in BIT; sum, carry: out BIT); end half_adder;

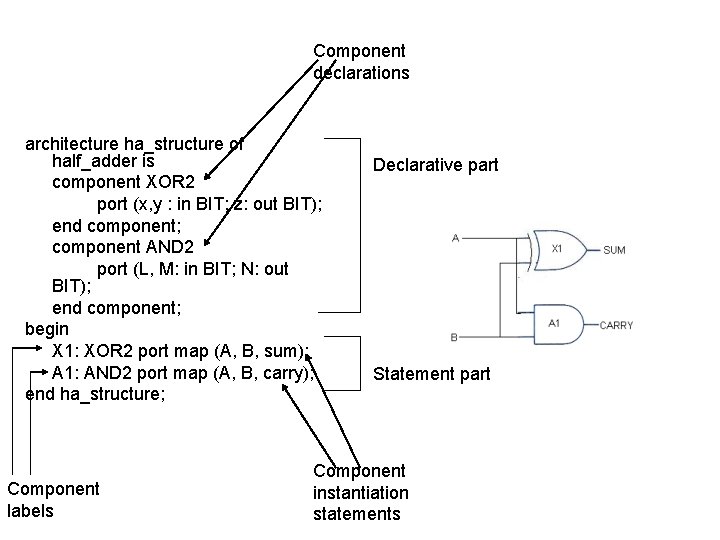

Component declarations architecture ha_structure of half_adder is component XOR 2 port (x, y : in BIT; z: out BIT); end component; component AND 2 port (L, M: in BIT; N: out BIT); end component; begin X 1: XOR 2 port map (A, B, sum); A 1: AND 2 port map (A, B, carry); end ha_structure; Component labels Declarative part Statement part Component instantiation statements

• Component instantiation statement is a concurrent statement. Hence the order of these statements is not important • This modeling style describes only the interconnection of components without implying any behavior of the components themselves nor of the entity that they collectively represent • Positional association is used to map signals in a port map of a component instantiation with the ports of a component specified in its declaration

Dataflow Style of Modeling • • VHDL code is concurrent (parallel) Concurrent code is also called dataflow code In the code, the order of the statements does not matter Purely concurrent code cannot be used to implement synchronous circuits. • In general we can only build combinational logic circuits with concurrent code • To obtain sequential logic circuits sequential code must be used. • Sequential code can be used to implement sequential as well as combinational circuits

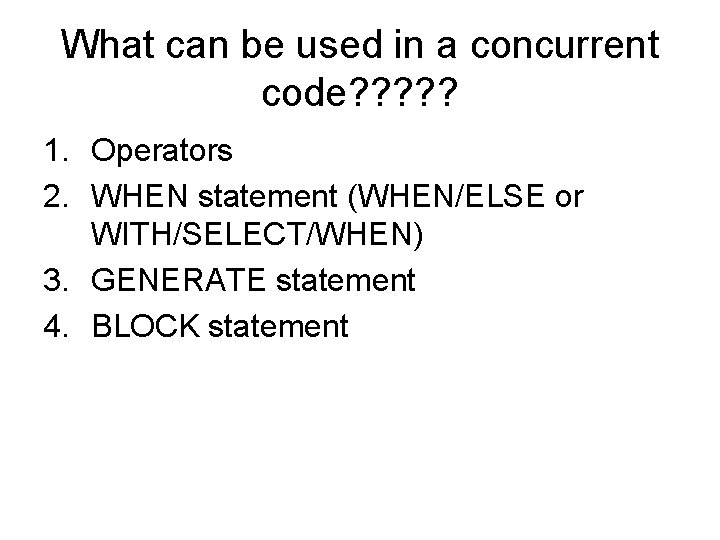

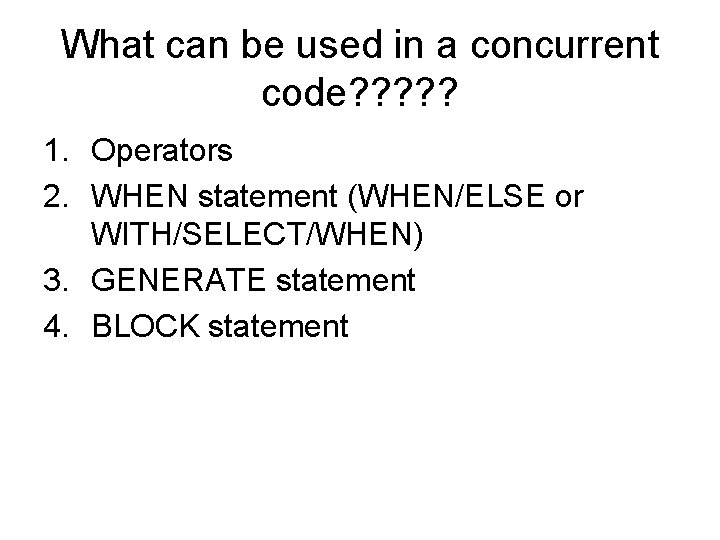

What can be used in a concurrent code? ? ? 1. Operators 2. WHEN statement (WHEN/ELSE or WITH/SELECT/WHEN) 3. GENERATE statement 4. BLOCK statement

Using Operators • Operators can be used to implement any combinational circuit a b MUX c d s 1 0 0 1 1 s 0 0 1 entity mux is port(a, b, c, d, s 0, s 1: in STD_LOGIC; y: out STD_LOGIC); end mux; y y a b c d s 1 s 0 architecture mux of mux is begin y<= ( a AND NOT s 1 AND NOT s 0) OR ( b AND NOT s 1 AND s 0) OR ( c AND s 1 AND NOT s 0) OR ( d AND s 1 AND s 0); end mux;

WHEN 1. WHEN/ELSE syntax assignment WHEN condition ELSE …. ; Example out <= “ 000” WHEN (inp=‘ 0’ OR reset=‘ 1’) ELSE “ 001” WHEN ctl=‘ 1’ ELSE “ 010”;

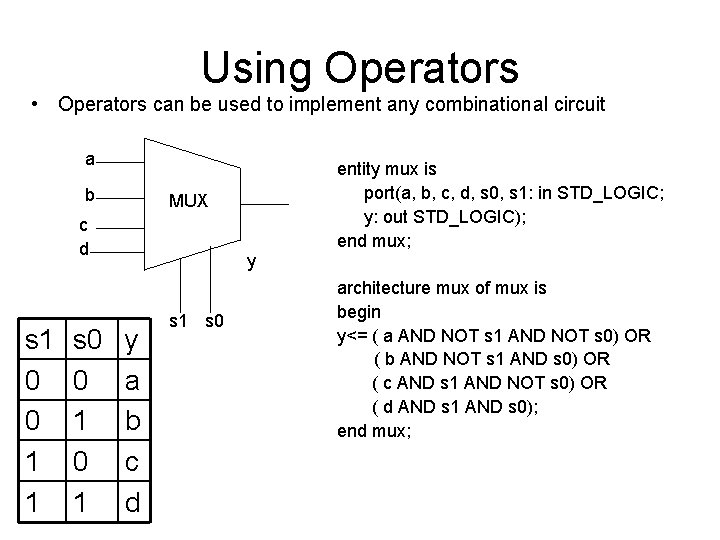

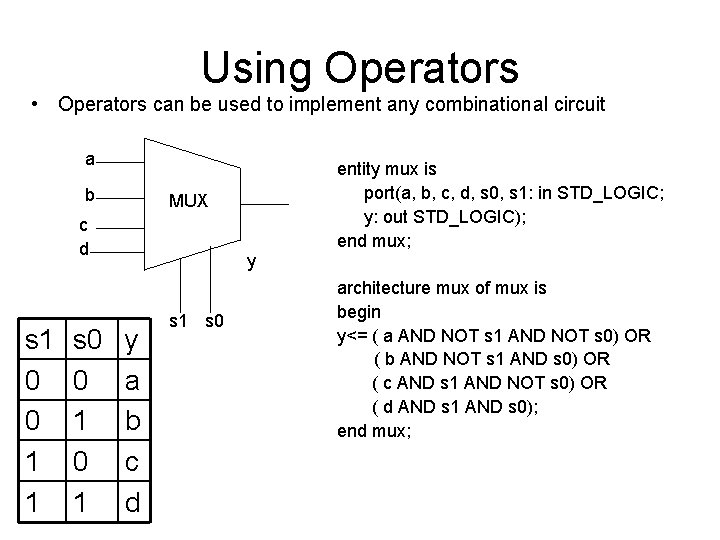

2. WITH/SELECT/ WHEN Syntax WITH identifier SELECT assignment WHEN value, …; Ø When this statement is used, all permutations must be tested, hence we can use the keyword OTHERS. Ø When no action is to take place we can use the keyword UNAFFECTED

• Example WITH control SELECT output <= “ 000” WHEN reset, “ 111” WHEN set, UNAFFETCED when OTHERS;

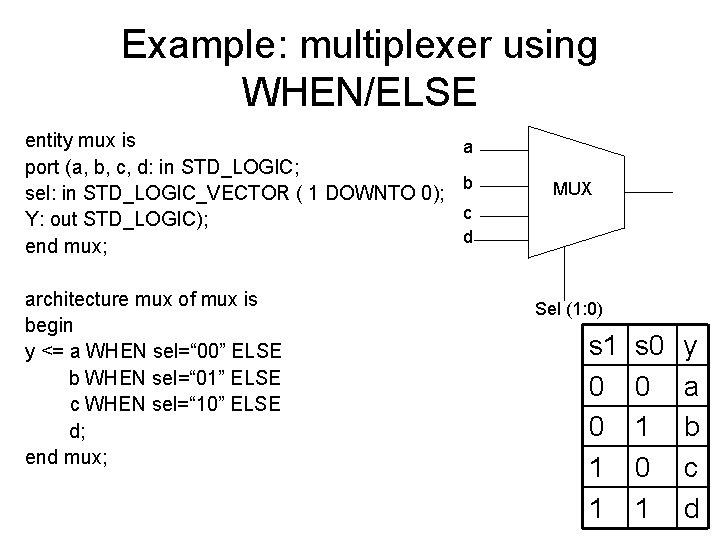

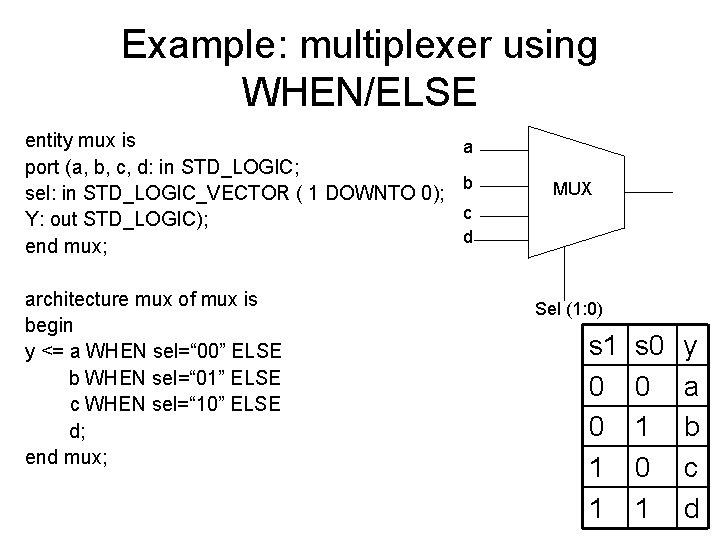

Example: multiplexer using WHEN/ELSE entity mux is port (a, b, c, d: in STD_LOGIC; sel: in STD_LOGIC_VECTOR ( 1 DOWNTO 0); Y: out STD_LOGIC); end mux; architecture mux of mux is begin y <= a WHEN sel=“ 00” ELSE b WHEN sel=“ 01” ELSE c WHEN sel=“ 10” ELSE d; end mux; a b MUX c d Sel (1: 0) s 1 0 0 1 1 s 0 0 1 y a b c d

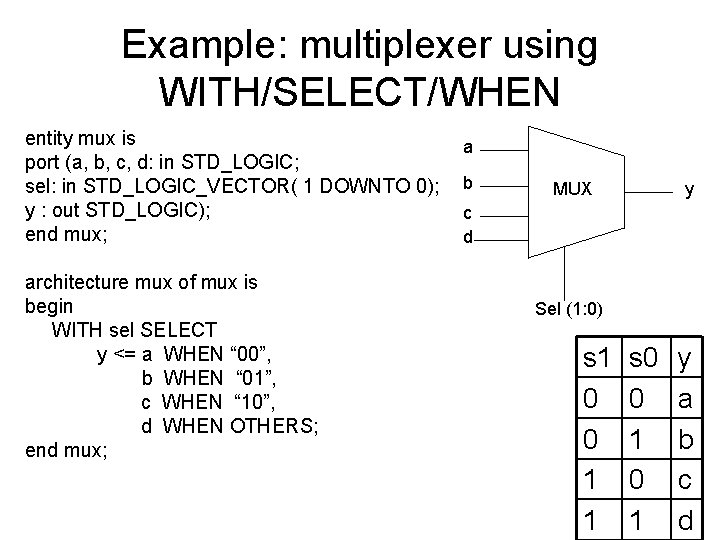

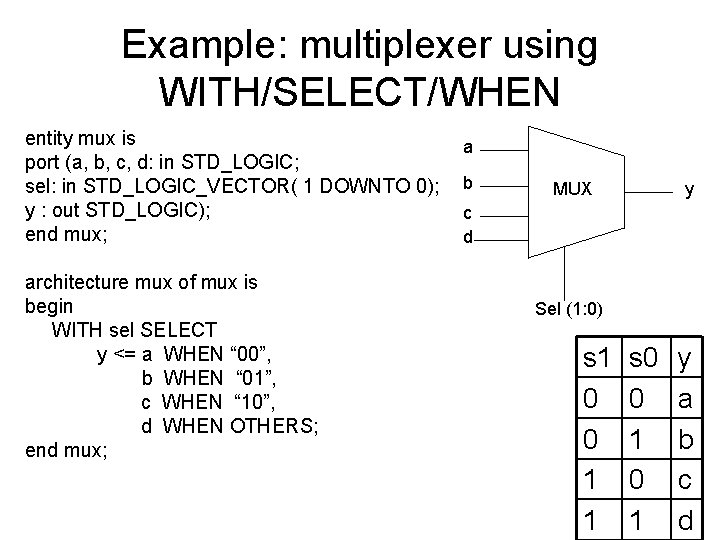

Example: multiplexer using WITH/SELECT/WHEN entity mux is port (a, b, c, d: in STD_LOGIC; sel: in STD_LOGIC_VECTOR( 1 DOWNTO 0); y : out STD_LOGIC); end mux; architecture mux of mux is begin WITH sel SELECT y <= a WHEN “ 00”, b WHEN “ 01”, c WHEN “ 10”, d WHEN OTHERS; end mux; a b MUX y c d Sel (1: 0) s 1 0 0 1 1 s 0 0 1 y a b c d

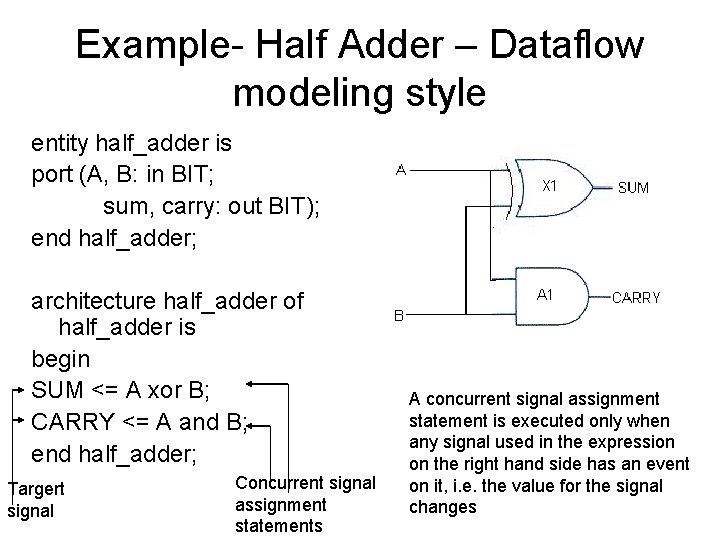

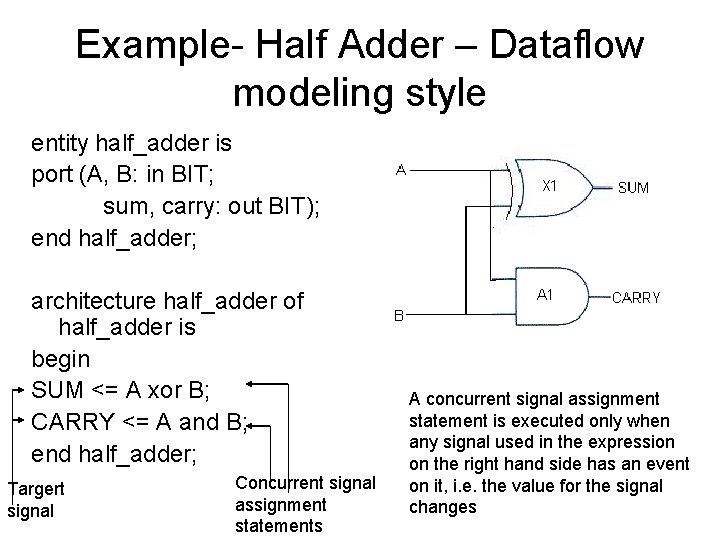

Example- Half Adder – Dataflow modeling style entity half_adder is port (A, B: in BIT; sum, carry: out BIT); end half_adder; architecture half_adder of half_adder is begin SUM <= A xor B; CARRY <= A and B; end half_adder; Targert signal Concurrent signal assignment statements A concurrent signal assignment statement is executed only when any signal used in the expression on the right hand side has an event on it, i. e. the value for the signal changes

Behavioral Style of Modeling • VHDL code is concurrent • PROCESS, FUNCTIONS and PROCEDURES are the only sections of code which are executed sequentially • We can build sequential circuits as well as combinational circuits using sequential code • Sequential code is also called behavioral code • This style of modeling specifies the behaviour of an entity as a set of statements that are executed sequentially in the specified order

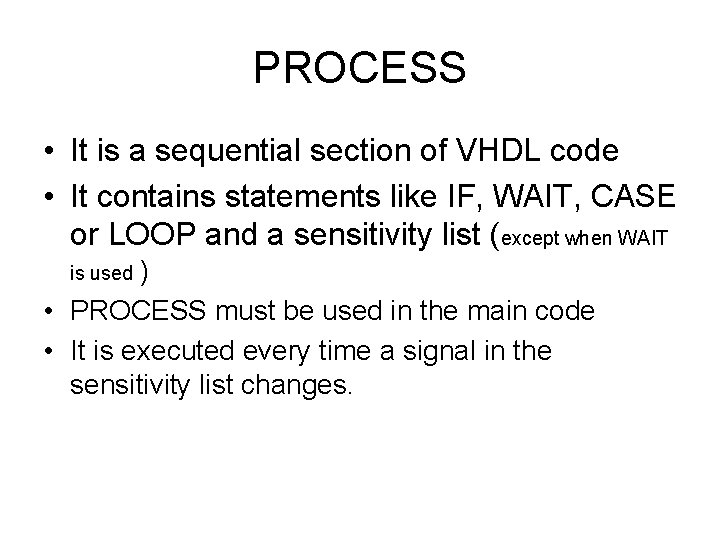

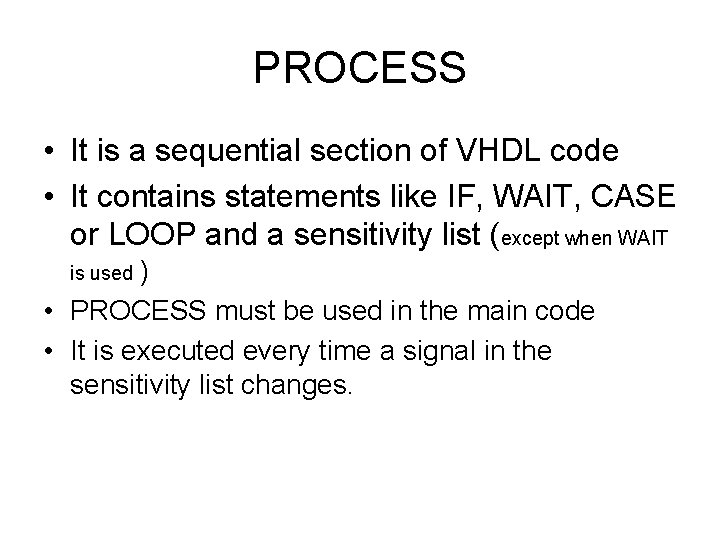

PROCESS • It is a sequential section of VHDL code • It contains statements like IF, WAIT, CASE or LOOP and a sensitivity list (except when WAIT ) • PROCESS must be used in the main code • It is executed every time a signal in the sensitivity list changes. is used

![Syntax of PROCESS label PROCESS sensitivity list VARIABLE name type range • Syntax of PROCESS [label: ] PROCESS (sensitivity list) [VARIABLE name type [range]](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-58.jpg)

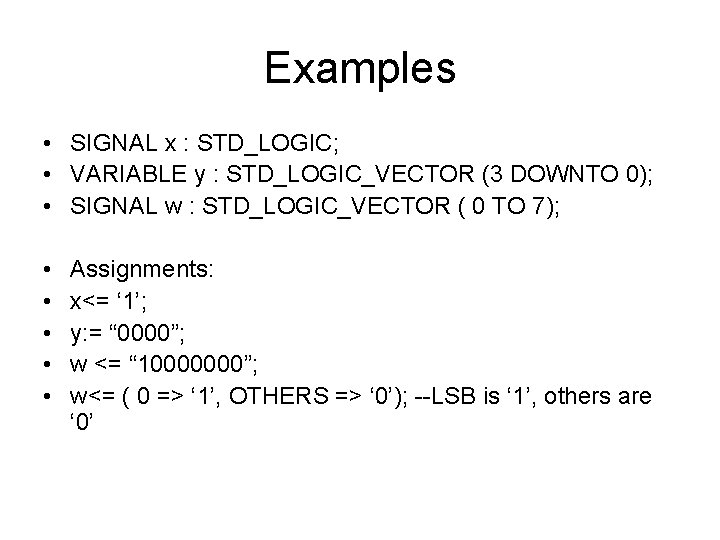

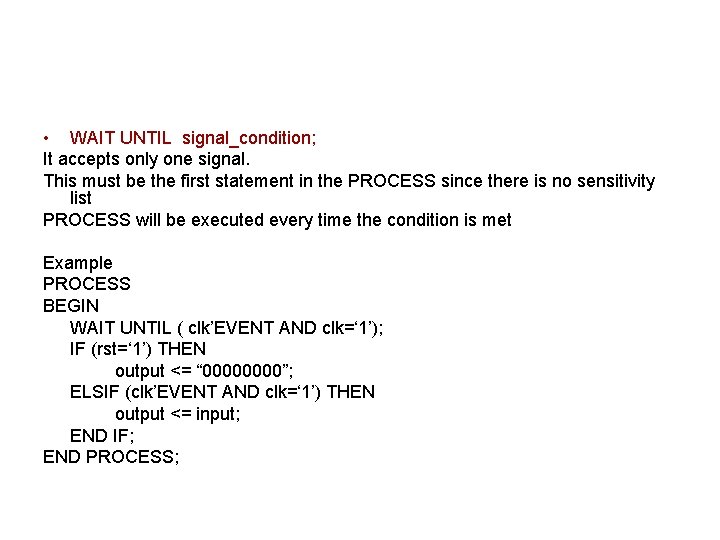

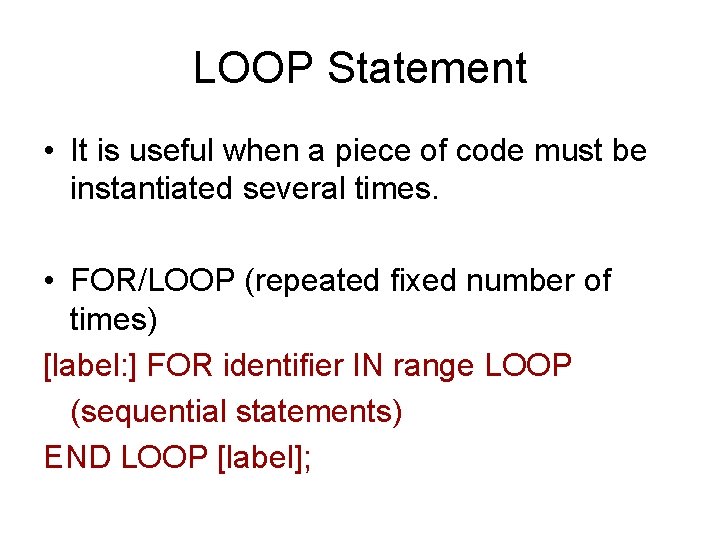

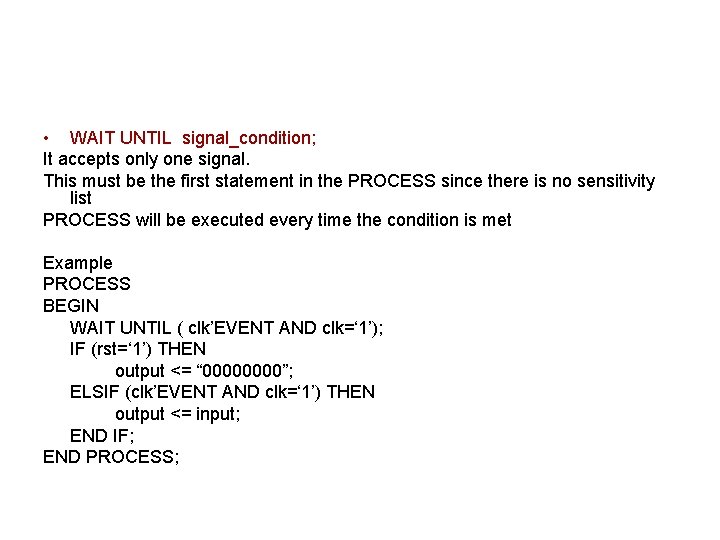

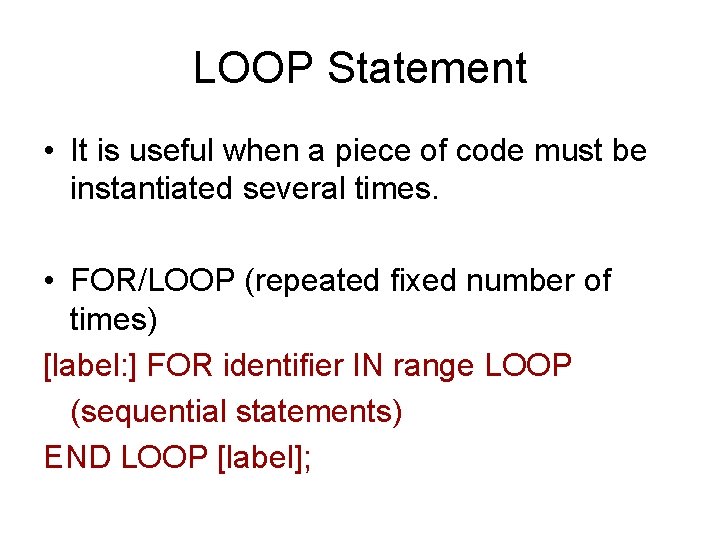

• Syntax of PROCESS [label: ] PROCESS (sensitivity list) [VARIABLE name type [range] [: = initial value; ]] BEGIN (sequential code) Declarative part END PROCESS [label]; Statement part • VARIABLES are optional but if they are to be used, they must be declared in the declarative part of the process • VARIABLES are restricted to be used in sequential code only i. e. inside a PROCESS, FUNCTION or PROCEDURE. • VARIABLE is not global hence its value cannot be passed out directly

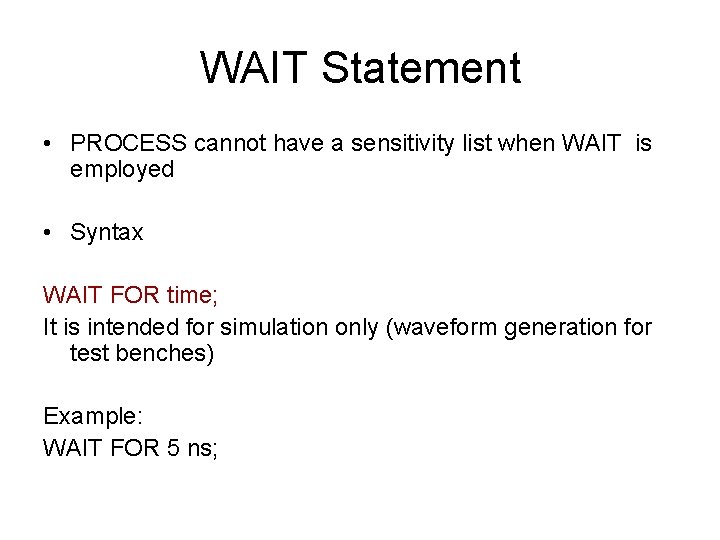

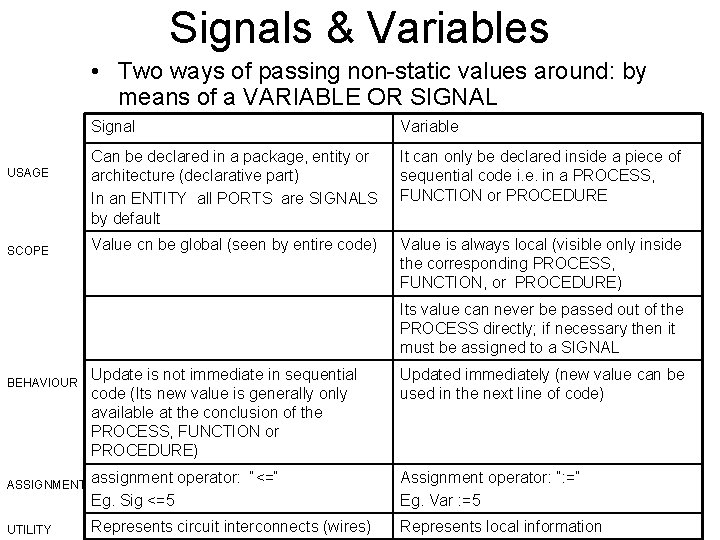

Signals & Variables • Two ways of passing non-static values around: by means of a VARIABLE OR SIGNAL USAGE SCOPE Signal Variable Can be declared in a package, entity or architecture (declarative part) In an ENTITY all PORTS are SIGNALS by default It can only be declared inside a piece of sequential code i. e. in a PROCESS, FUNCTION or PROCEDURE Value cn be global (seen by entire code) Value is always local (visible only inside the corresponding PROCESS, FUNCTION, or PROCEDURE) Its value can never be passed out of the PROCESS directly; if necessary then it must be assigned to a SIGNAL Update is not immediate in sequential code (Its new value is generally only available at the conclusion of the PROCESS, FUNCTION or PROCEDURE) Updated immediately (new value can be used in the next line of code) ASSIGNMENT assignment operator: “<=“ Eg. Sig <=5 Assignment operator: “: =“ Eg. Var : =5 UTILITY Represents circuit interconnects (wires) Represents local information BEHAVIOUR

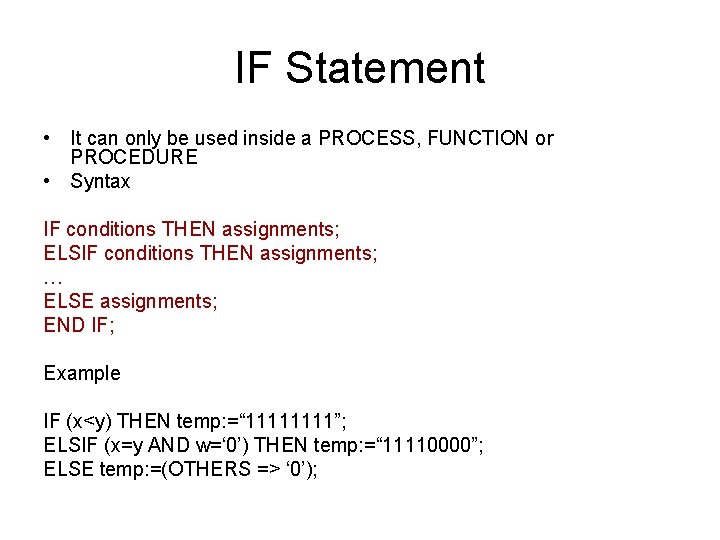

IF Statement • It can only be used inside a PROCESS, FUNCTION or PROCEDURE • Syntax IF conditions THEN assignments; ELSIF conditions THEN assignments; … ELSE assignments; END IF; Example IF (x<y) THEN temp: =“ 1111”; ELSIF (x=y AND w=‘ 0’) THEN temp: =“ 11110000”; ELSE temp: =(OTHERS => ‘ 0’);

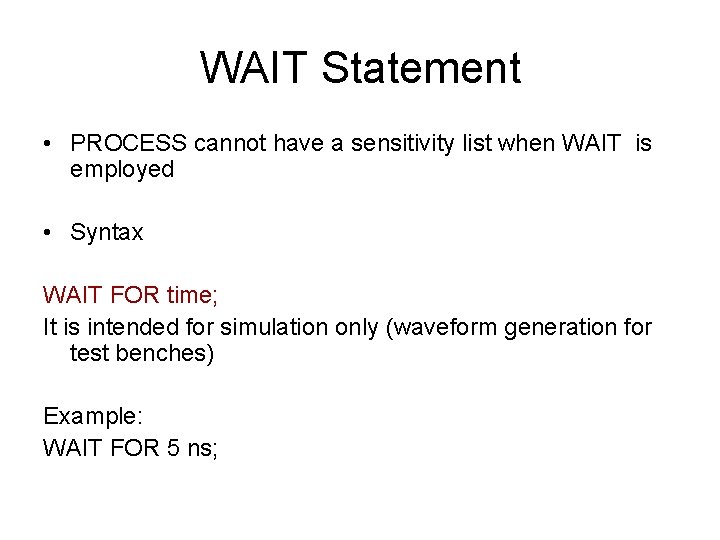

WAIT Statement • PROCESS cannot have a sensitivity list when WAIT is employed • Syntax WAIT FOR time; It is intended for simulation only (waveform generation for test benches) Example: WAIT FOR 5 ns;

• WAIT UNTIL signal_condition; It accepts only one signal. This must be the first statement in the PROCESS since there is no sensitivity list PROCESS will be executed every time the condition is met Example PROCESS BEGIN WAIT UNTIL ( clk’EVENT AND clk=‘ 1’); IF (rst=‘ 1’) THEN output <= “ 0000”; ELSIF (clk’EVENT AND clk=‘ 1’) THEN output <= input; END IF; END PROCESS;

• WAIT ON signal 1, signal 2, …; • It accepts multiple signals • The PROCESS is put on hold until any of the signals listed changes • Example PROCESS BEGIN WAIT ON clk, rst; IF (rst=‘ 1’) THEN output <= “ 0000”; ELSIF (clk’EVENT AND clk=‘ 1’) THEN output <= input; END IF; END PROCESS;

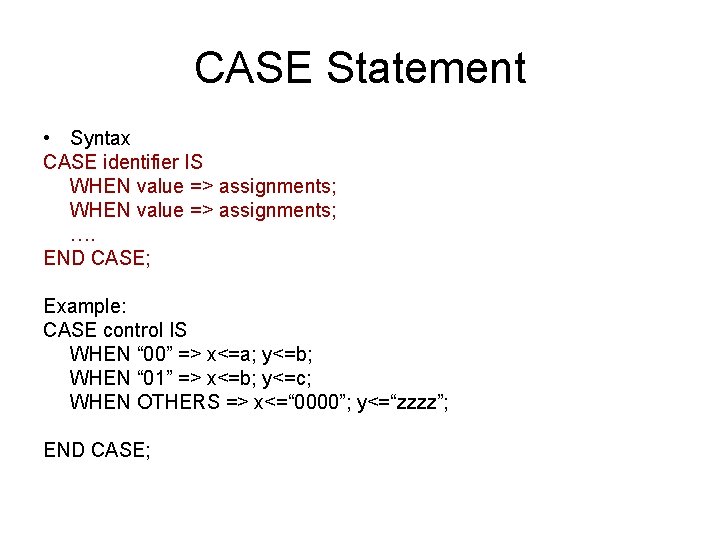

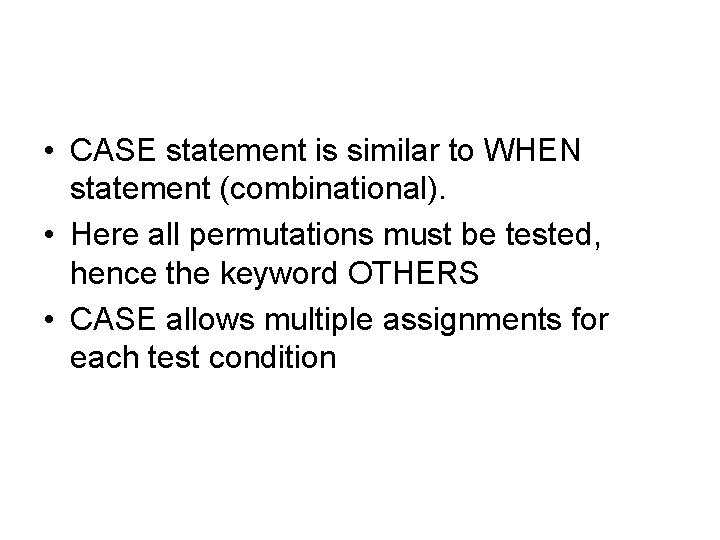

CASE Statement • Syntax CASE identifier IS WHEN value => assignments; …. END CASE; Example: CASE control IS WHEN “ 00” => x<=a; y<=b; WHEN “ 01” => x<=b; y<=c; WHEN OTHERS => x<=“ 0000”; y<=“zzzz”; END CASE;

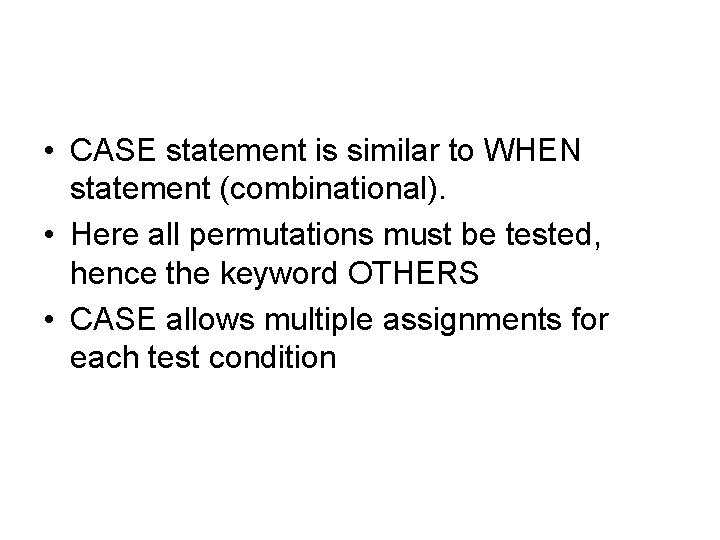

• CASE statement is similar to WHEN statement (combinational). • Here all permutations must be tested, hence the keyword OTHERS • CASE allows multiple assignments for each test condition

LOOP Statement • It is useful when a piece of code must be instantiated several times. • FOR/LOOP (repeated fixed number of times) [label: ] FOR identifier IN range LOOP (sequential statements) END LOOP [label];

![WHILELOOP loop is repeated until a condition no longer holds label • WHILE/LOOP (loop is repeated until a condition no longer holds) [label: ]](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-67.jpg)

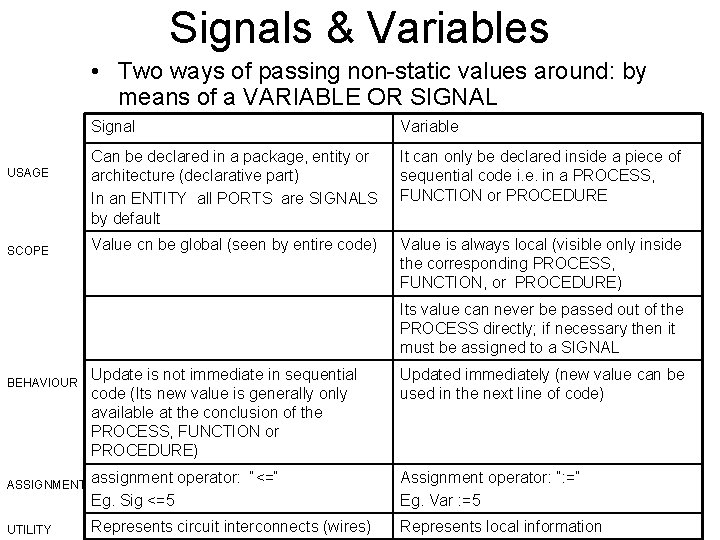

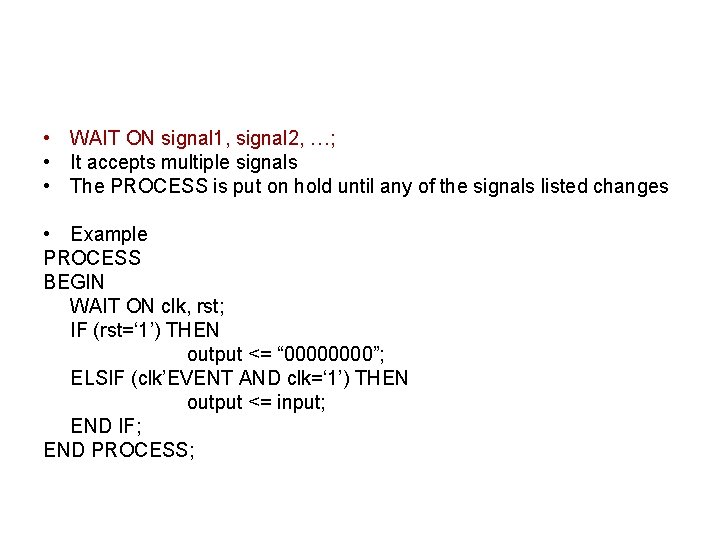

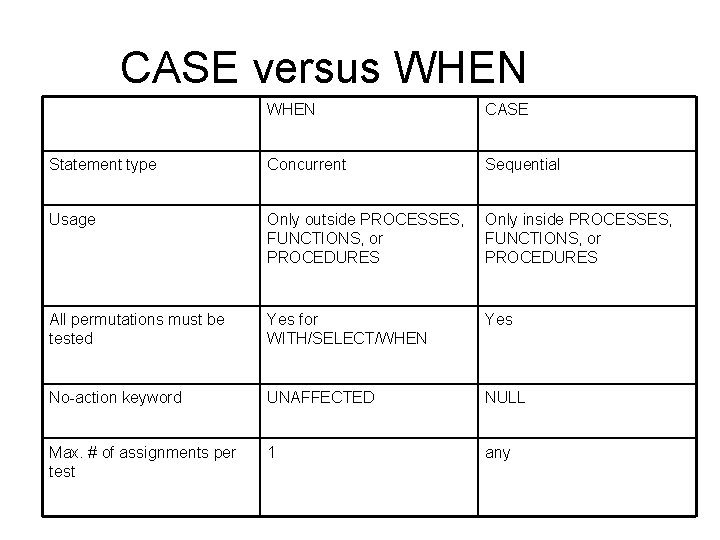

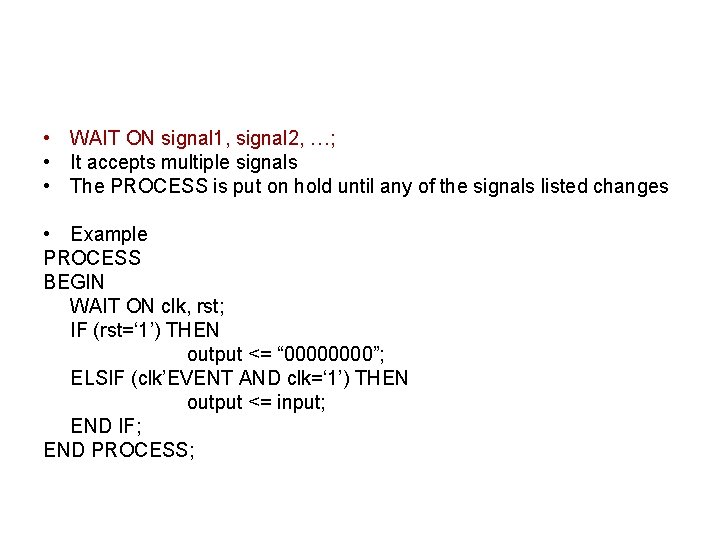

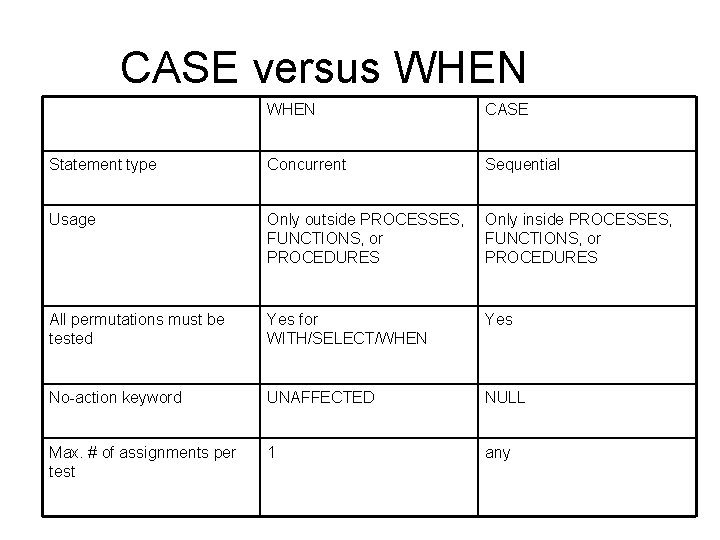

• WHILE/LOOP (loop is repeated until a condition no longer holds) [label: ] WHILE condition LOOP (sequential statements) END LOOP [label]; • EXIT (used for ending the loop) [label: ] EXIT [label] [WHEN condition];

![NEXT used for skipping loop steps label NEXT looplabel WHEN condition • NEXT (used for skipping loop steps) [label: ] NEXT [loop_label] [WHEN condition];](https://slidetodoc.com/presentation_image_h/23d773260c6d0224daaf4bcfe13d8817/image-68.jpg)

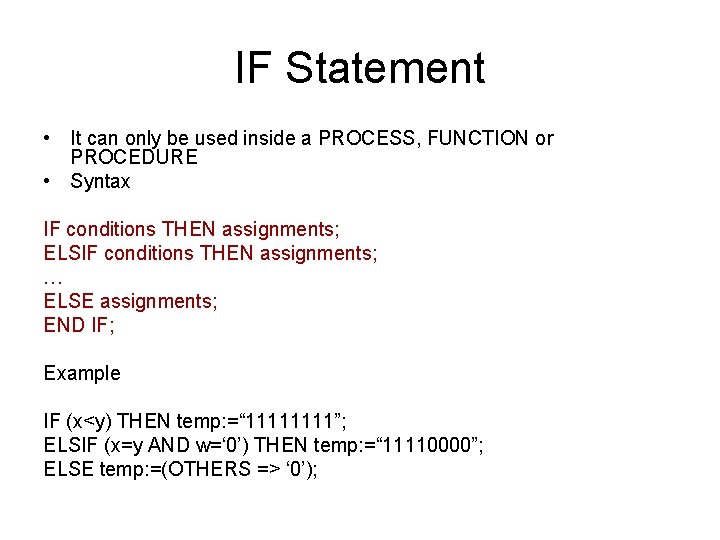

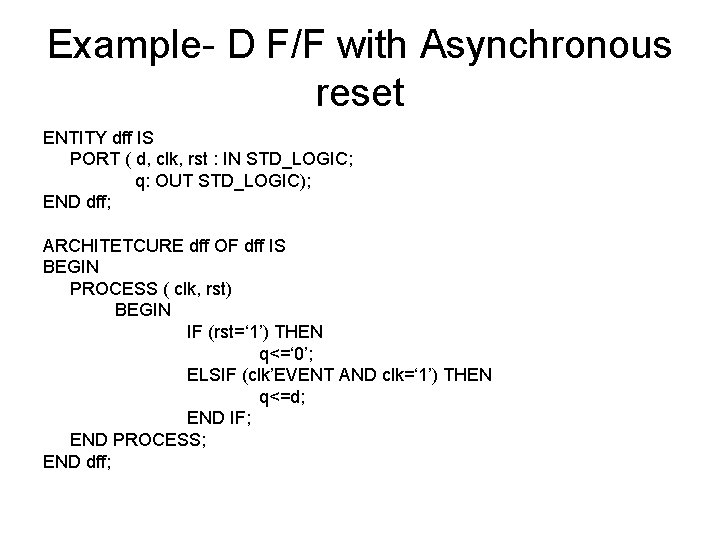

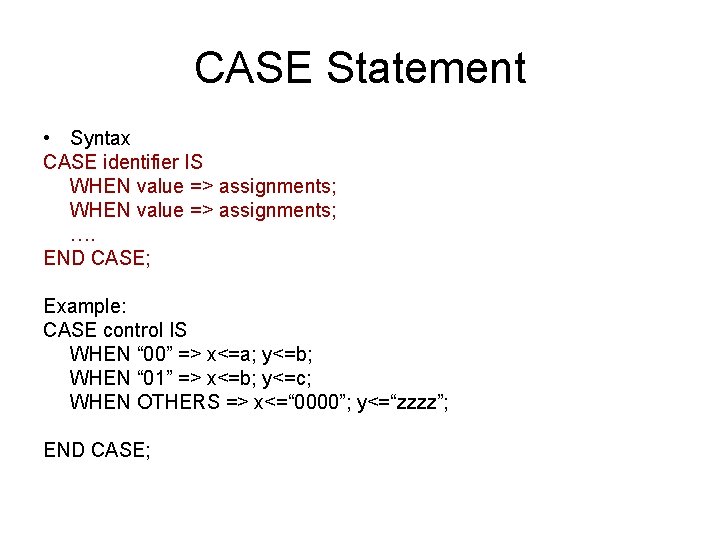

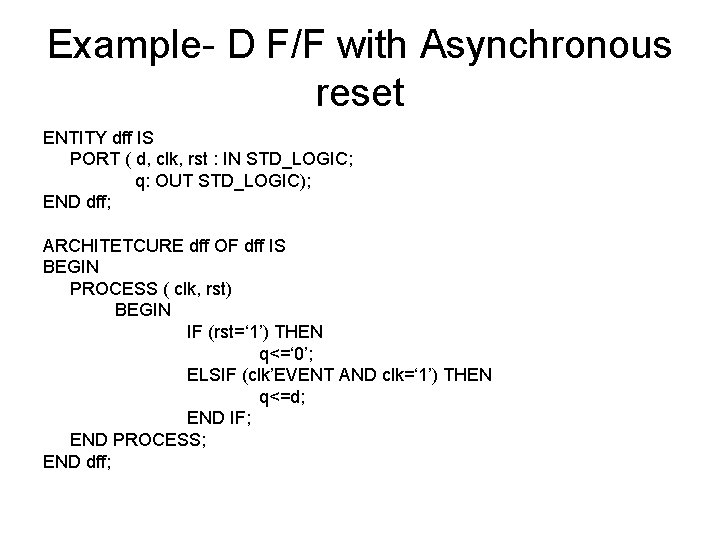

• NEXT (used for skipping loop steps) [label: ] NEXT [loop_label] [WHEN condition];

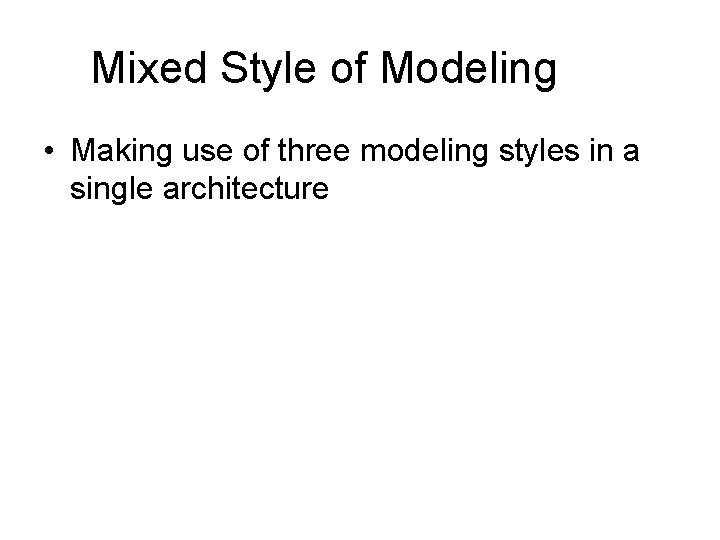

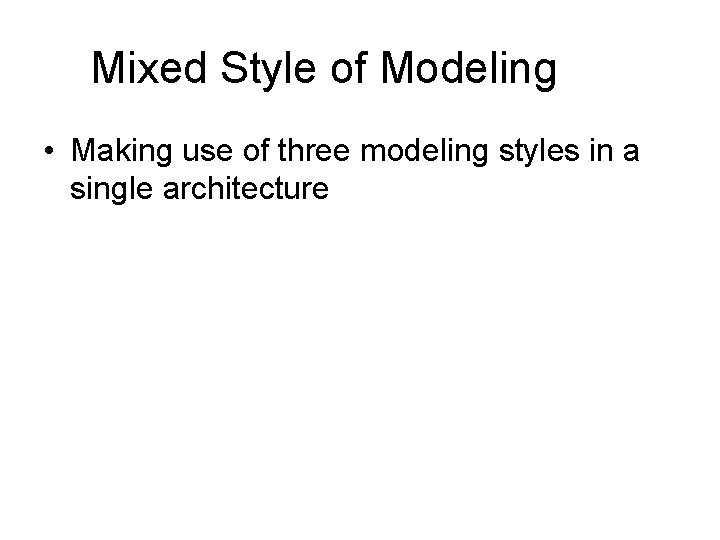

CASE versus WHEN CASE Statement type Concurrent Sequential Usage Only outside PROCESSES, FUNCTIONS, or PROCEDURES Only inside PROCESSES, FUNCTIONS, or PROCEDURES All permutations must be tested Yes for WITH/SELECT/WHEN Yes No-action keyword UNAFFECTED NULL Max. # of assignments per test 1 any

Example- D F/F with Asynchronous reset ENTITY dff IS PORT ( d, clk, rst : IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ARCHITETCURE dff OF dff IS BEGIN PROCESS ( clk, rst) BEGIN IF (rst=‘ 1’) THEN q<=‘ 0’; ELSIF (clk’EVENT AND clk=‘ 1’) THEN q<=d; END IF; END PROCESS; END dff;

Mixed Style of Modeling • Making use of three modeling styles in a single architecture