Uvod v VHDL Laboratorijske vaje Andrej Trost Kaj

Uvod v VHDL Laboratorijske vaje Andrej Trost

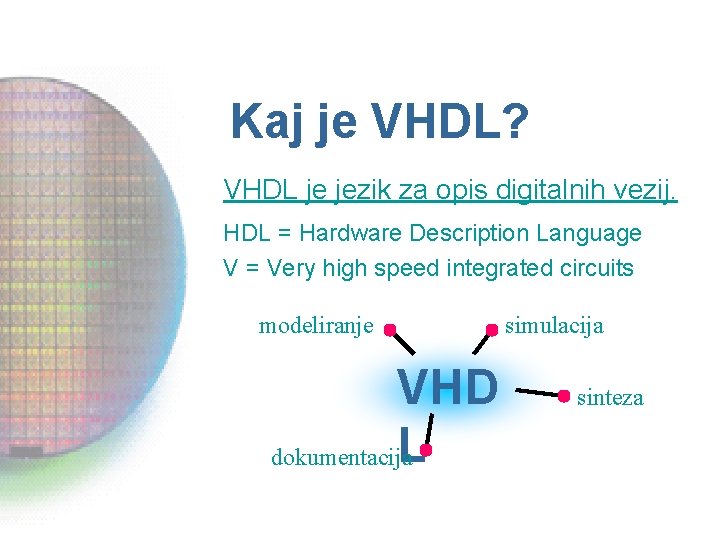

Kaj je VHDL? VHDL je jezik za opis digitalnih vezij. HDL = Hardware Description Language V = Very high speed integrated circuits modeliranje VHD L dokumentacija simulacija sinteza

Kaj je VHDL? VHDL je visokonivojski jezik. n n n Opisujemo obnašanje vezja Ne potrebujemo logičnih funkcij ali Boolovih enačb Drugi visokonivojski jeziki u Abel u Verilog

Kaj je VHDL? VHDL je standardiziran jezik. IEEE standard (1987) vsebuje definicijo jezika n Večina programskih orodij podpira standard IEEE 1076 -93 in dodatne podatkovne tipe iz IEEE 1164 n

Načrtovanje digitalnih vezij Tradicionalni pristop: shematsko n Uporablja se na različnih nivojih u tranzistorji u logična vrata u kompleksni gradniki

Načrtovanje digitalnih vezij Tradicionalni pristop: shematsko 4 Prednosti u shema zelo pregledno prikazuje relacije med posameznimi gradniki 6 Pomanjkljivosti u postane nepregledno pri zelo velikih vezjih

Načrtovanje digitalnih vezij Sodobni pristop: načrtovanje v VHDLu n Opis obnašanja vezja u uporaba visokonivojskih stavkov (npr. if stavek) n Opis strukture vezja u povezava vnaprej pripravljenih komponent

Postopek načrtovanja vezij n Opis vezja n Simulacija n Sinteza logičnega vezja n Tehnološka preslikava

Opis digitalnih vezij • Opis vezja • Simulacija • Sinteza vezja Poimenujemo vse signale v vezju n Enostavni signali u zavzamejo • Tehnološka preslikava n logično vrednost ‘ 0’ ali ‘ 1’ Skupek signalov (vodilo) u predstavimo jih z vektorji npr. “ 0000”

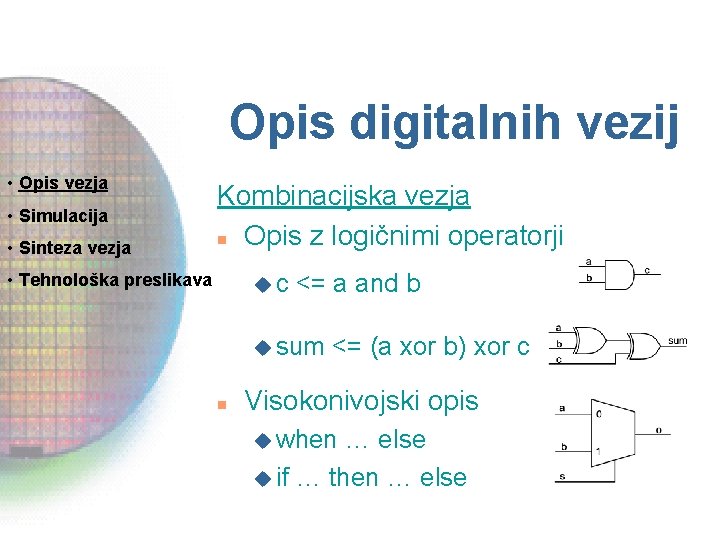

Opis digitalnih vezij • Opis vezja • Simulacija • Sinteza vezja Kombinacijska vezja n Opis z logičnimi operatorji uc • Tehnološka preslikava <= a and b u sum n <= (a xor b) xor c Visokonivojski opis u when … else u if … then … else

Opis digitalnih vezij • Opis vezja • Simulacija • Sinteza vezja Sekvenčna vezja n • Tehnološka preslikava RTL opis (Register Transfer Level) u kombinacijska u registri logika

Simulacija vezja • Opis vezja Funkcionalna simulacija • Simulacija n Opazujemo spreminjanje signalov v • Sinteza vezju, ki mu nastavimo stimulatorje • Tehnološka preslikava n Signali so definirani kot: u bit (‘ 0’, ‘ 1’) u std_logic (‘ 0’, ‘ 1’, ‘U’, ‘Z’, ‘X’ …) F omogoča prikaz nedefiniranega stanja, kratkega stika ipd.

Simulacija vezja • Opis vezja • Simulacija n • Sinteza vezja • Tehnološka preslikava n V visokonivojskem jeziku je izvajanje simulacije veliko hitrejše kot na nivoju logičnih vrat Za generiranje stimulatorjev lahko napišemo poseben VHDL program (Testbench)

Simulacija vezja • Opis vezja Časovna simulacija • Simulacija n V opis vezja dodamo zakasnitve • Sinteza vezja posameznih elementov • Tehnološka preslikava u uporaba knjižnjic z elementi v izbrani tehnologiji u uporaba VHDL datoteke, ki jo generirajo programi za časovno analizo po tehnološki preslikavi

Sinteza vezja • Opis vezja n • Simulacija • Sinteza vezja n • Tehnološka preslikava n Pretvorba visokonivojskega opisa vezja na nivo logičnih vrat Programi za sintezo avtomatsko generirajo vezje na nivoju logičnih vrat in flip-flopov Postopek sinteze je povezan z optimizacijo vezja za izbrano tehnologijo (monolitna vezja, programirljiva …)

Sinteza vezja • Opis vezja n u modeliranje časovnih zakasnitev u funkcije za delo z datotekami • Simulacija • Sinteza vezja • Tehnološka preslikava Vsi ukazi niso primerni za sintezo n n Uporabljamo omejen nabor ukazov Držimo se pravil pisanja VHDL programa (npr. RTL opis sekvenčnih vezij)

Tehnološka preslikava • Opis vezja • Simulacija n Logično vezje pretvorimo v obliko primerno za izdelavo vezja • Sinteza vezja u maske za monolitno integrirano • Tehnološka preslikava vezje u datoteka za programiranje programirljivih vezij

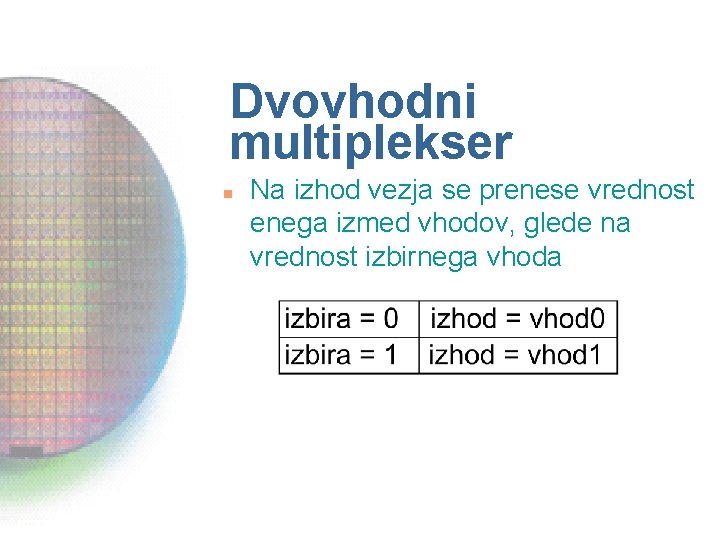

Dvovhodni multiplekser n Na izhod vezja se prenese vrednost enega izmed vhodov, glede na vrednost izbirnega vhoda

Shema multiplekserja n Zapis funkcije: izhod <= (vhod 0 and (not izbira)) or (vhod 1 and izbira);

Zapis logične funkcije n n n Opis vezja v obliki logične funkcije je precej nepregleden Predstavitev vezja z logičnimi vrati prepustimo programom za sintezo Logične operatorje uporabljamo za najosnovnejše gradnike in kadar želimo optimizirati del vezja

Visokonivojski zapis n Pogojni prireditveni stavek: izhod <= vhod 0 when izbira=’ 0’ else vhod 1; n Za opis vezja nam ni potrebno poznati logično funkcijo

Zgradba VHDL programa Opis vezja je sestavljen iz dveh delov n Opis priključkov vezja entity ime_vezja is opis parametrov in signalov end ime_vezja; n Opis delovanja vezja architecture opis of ime_vezja is begin stavki… end opis;

Opis priključkov vezja n Priključki so opisani s stavkom port (vhod 0, vhod 1: in std_logic; izbira: in std_logic; izhod: out std_logic); n Vsak priključek ima definirano smer in tip signala

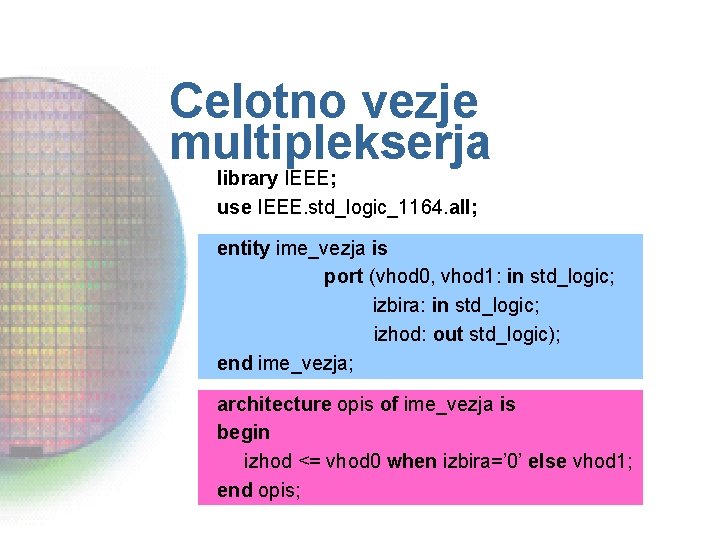

Celotno vezje multiplekserja library IEEE; use IEEE. std_logic_1164. all; entity ime_vezja is port (vhod 0, vhod 1: in std_logic; izbira: in std_logic; izhod: out std_logic); end ime_vezja; architecture opis of ime_vezja is begin izhod <= vhod 0 when izbira=’ 0’ else vhod 1; end opis;

- Slides: 24