HDL V VHDL q VHSIC Very High Speed

![(Signal) ﺳﻴگﻨﺎﻝ signal list_of_signal_names: type [ : = initial value]; signal SUM, CARRY: std_logic; (Signal) ﺳﻴگﻨﺎﻝ signal list_of_signal_names: type [ : = initial value]; signal SUM, CARRY: std_logic;](https://slidetodoc.com/presentation_image_h/7dd9dc0b55c9ccc0c256796944394644/image-42.jpg)

![ﻗﺎﻟﺐ کﻠی ﺩﺳﺘﻮﺭ پﺮﺩﺍﺯﻩ [process_label: ] process [ (sensitivity_list) ] [is] [ process_declarations] ﻗﺎﻟﺐ کﻠی ﺩﺳﺘﻮﺭ پﺮﺩﺍﺯﻩ [process_label: ] process [ (sensitivity_list) ] [is] [ process_declarations]](https://slidetodoc.com/presentation_image_h/7dd9dc0b55c9ccc0c256796944394644/image-86.jpg)

- Slides: 134

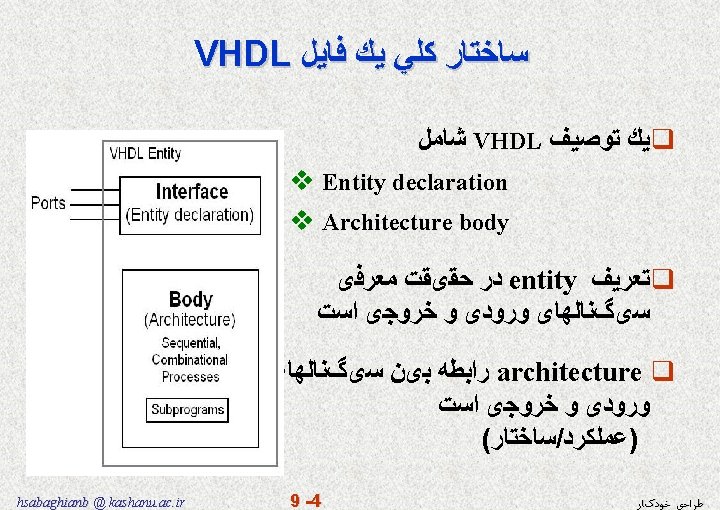

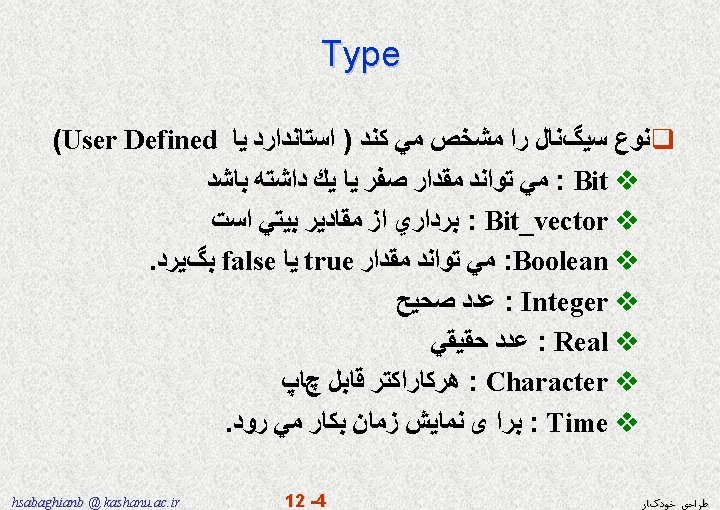

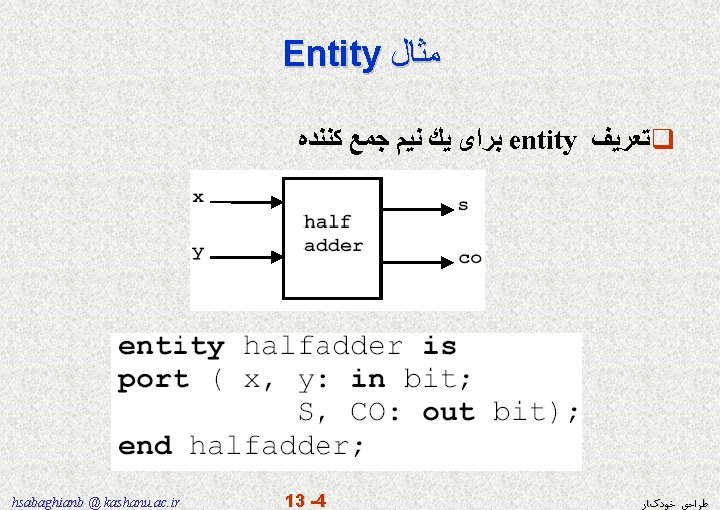

( ﻣﻘﺪﻣﻪ )ﺗﺎﺭﻳﺨچﻪ ﺑﻪ ﻣﻌﻨی HDL ﻭ V ﺷﺎﻣﻞ ﺩﻭ ﺑﺨﺶ VHDL ﻧﺎﻡ q VHSIC : Very High Speed Integrated Circuits HDL : Hardware Description Language IEEE 1076 -1987 ﺍﺳﺘﺎﻧﺪﺍﺭﺩ q IEEE 1076 -1993 ﺍﺳﺘﺎﻧﺪﺍﺭﺩ q (Advanced Boolean Equation Language ) ABEL ﻭ Verilog q hsabaghianb @ kashanu. ac. ir 2 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

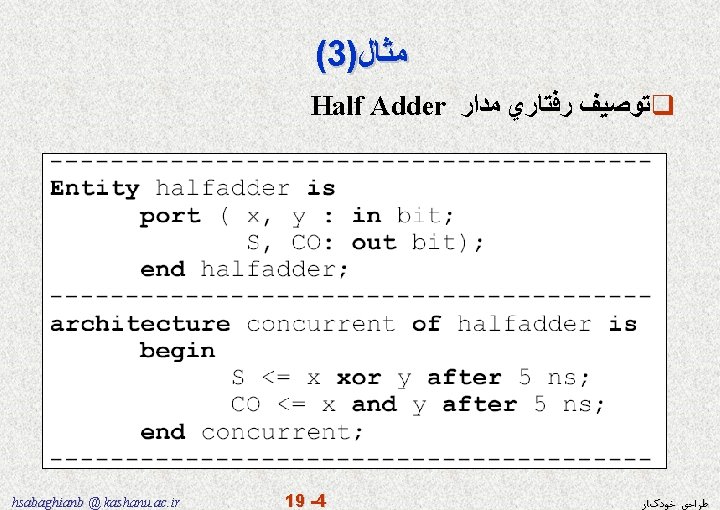

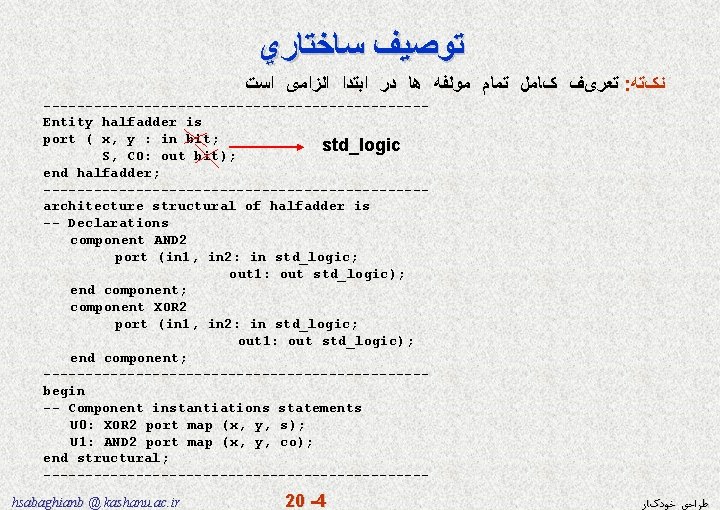

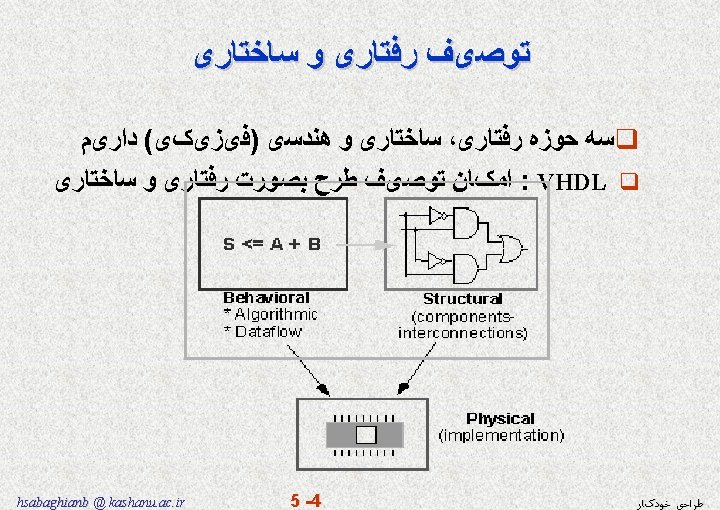

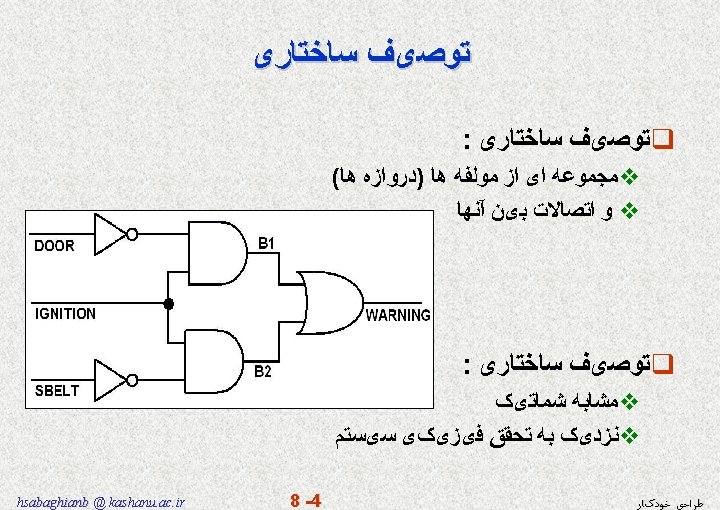

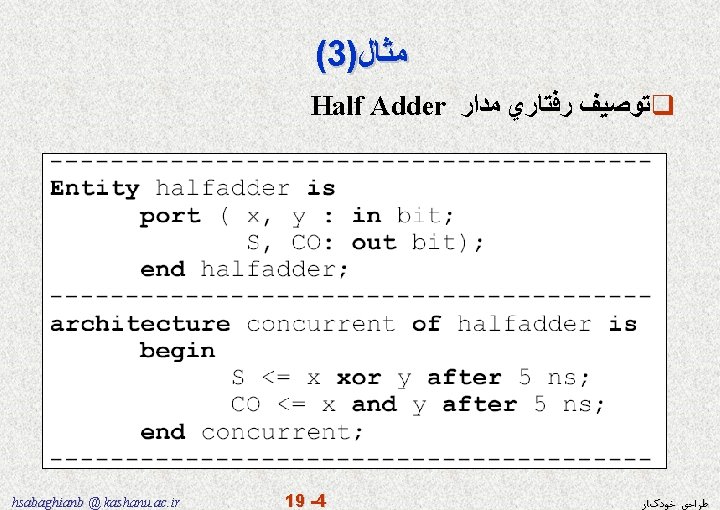

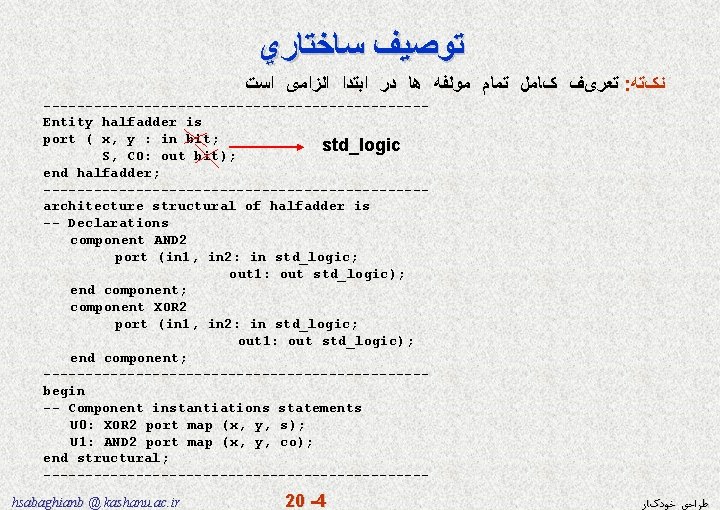

ﺳﺎﺧﺘﺎﺭﻱ ﺗﻮﺻﻴﻒ ﺍﺳﺖ ﺍﻟﺰﺍﻣی ﺍﺑﺘﺪﺍ ﺩﺭ ﻫﺎ ﻣﻮﻟﻔﻪ ﺗﻤﺎﻡ کﺎﻣﻞ ﺗﻌﺮیﻒ : ﻧکﺘﻪ -----------------------Entity halfadder is port ( x, y : in bit; std_logic S, CO: out bit); end halfadder; -----------------------architecture structural of halfadder is -- Declarations component AND 2 port (in 1, in 2: in std_logic; out 1: out std_logic); end component; component XOR 2 port (in 1, in 2: in std_logic; out 1: out std_logic); end component; -----------------------begin -- Component instantiations statements U 0: XOR 2 port map (x, y, s); U 1: AND 2 port map (x, y, co); end structural; -----------------------hsabaghianb @ kashanu. ac. ir 20 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

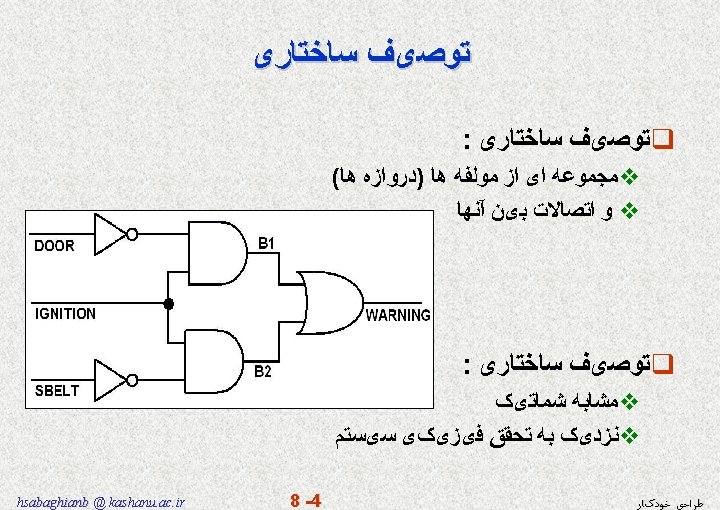

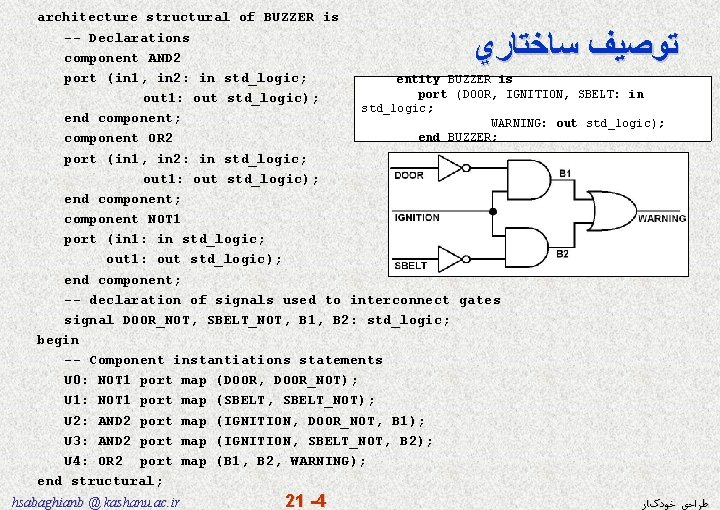

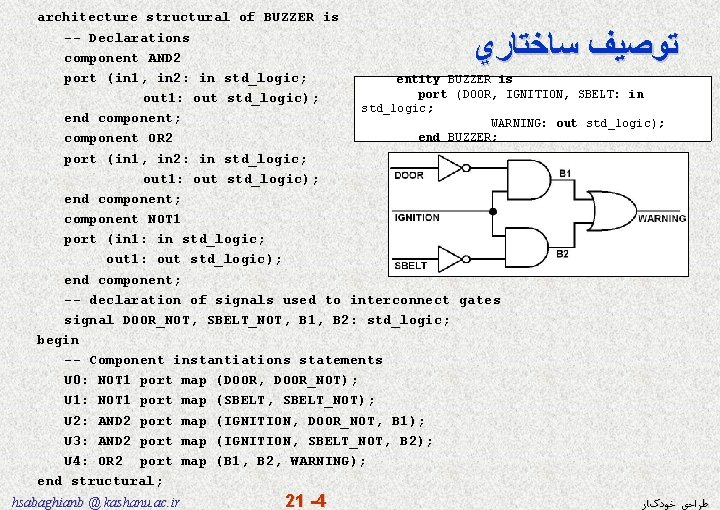

architecture structural of BUZZER is -- Declarations component AND 2 port (in 1, in 2: in std_logic; entity BUZZER is port (DOOR, IGNITION, SBELT: in out 1: out std_logic); std_logic; end component; WARNING: out std_logic); end BUZZER; component OR 2 port (in 1, in 2: in std_logic; out 1: out std_logic); end component; component NOT 1 port (in 1: in std_logic; out 1: out std_logic); end component; -- declaration of signals used to interconnect gates signal DOOR_NOT, SBELT_NOT, B 1, B 2: std_logic; begin -- Component instantiations statements U 0: NOT 1 port map (DOOR, DOOR_NOT); U 1: NOT 1 port map (SBELT, SBELT_NOT); U 2: AND 2 port map (IGNITION, DOOR_NOT, B 1); U 3: AND 2 port map (IGNITION, SBELT_NOT, B 2); U 4: OR 2 port map (B 1, B 2, WARNING); end structural; ﺳﺎﺧﺘﺎﺭﻱ ﺗﻮﺻﻴﻒ hsabaghianb @ kashanu. ac. ir 21 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

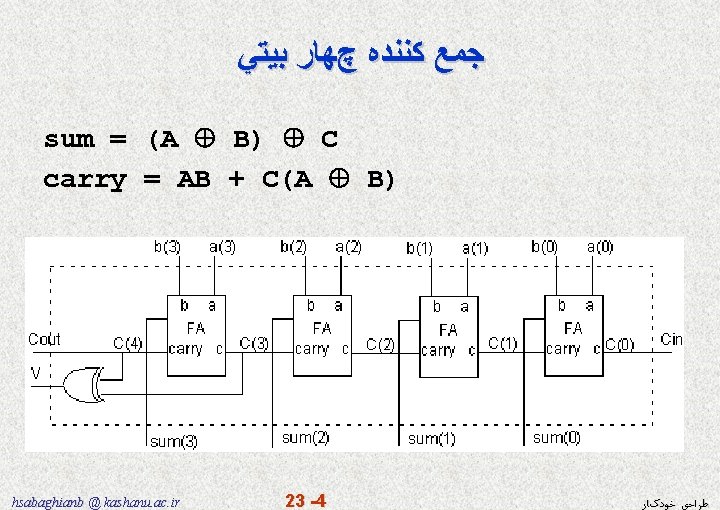

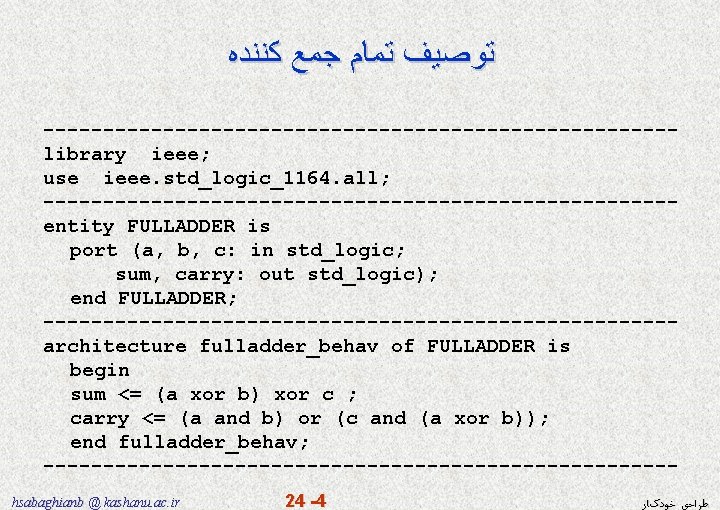

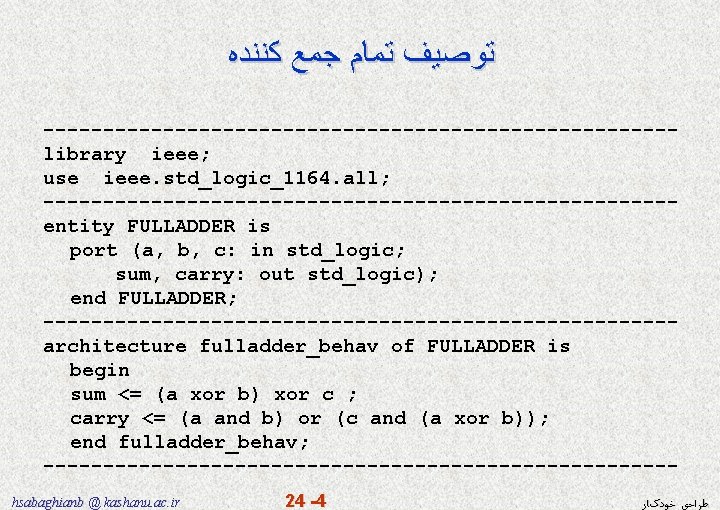

ﺗﻮﺻﻴﻒ ﺗﻤﺎﻡ ﺟﻤﻊ ﻛﻨﻨﺪﻩ --------------------------library ieee; use ieee. std_logic_1164. all; --------------------------entity FULLADDER is port (a, b, c: in std_logic; sum, carry: out std_logic); end FULLADDER; --------------------------architecture fulladder_behav of FULLADDER is begin sum <= (a xor b) xor c ; carry <= (a and b) or (c and (a xor b)); end fulladder_behav; --------------------------hsabaghianb @ kashanu. ac. ir 24 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

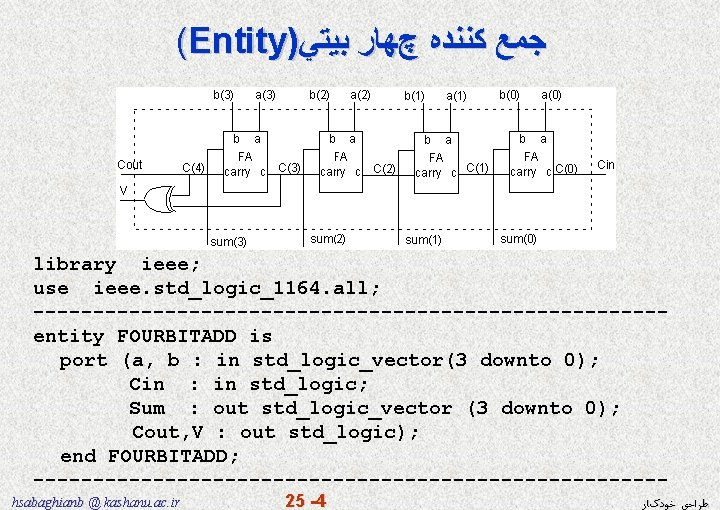

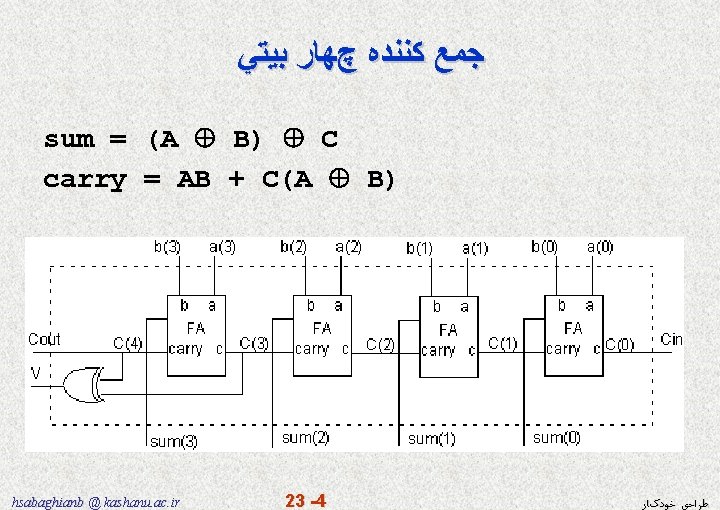

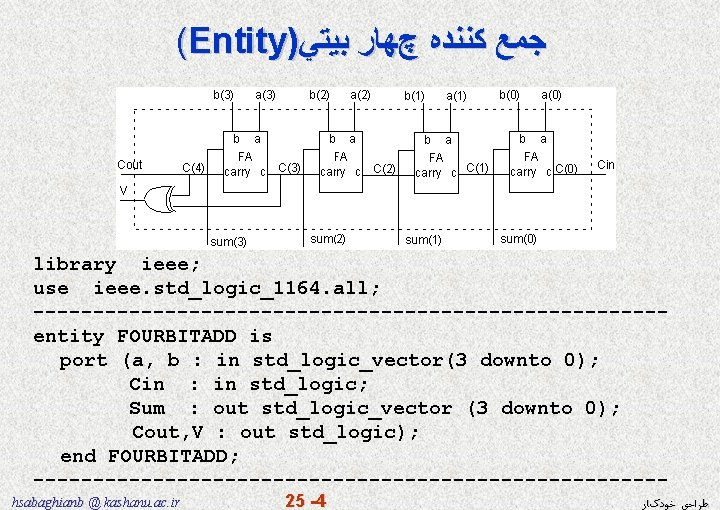

(Entity) ﺑﻴﺘﻲ چﻬﺎﺭ ﻛﻨﻨﺪﻩ ﺟﻤﻊ library ieee; use ieee. std_logic_1164. all; --------------------------entity FOURBITADD is port (a, b : in std_logic_vector(3 downto 0); Cin : in std_logic; Sum : out std_logic_vector (3 downto 0); Cout, V : out std_logic); end FOURBITADD; --------------------------- hsabaghianb @ kashanu. ac. ir 25 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

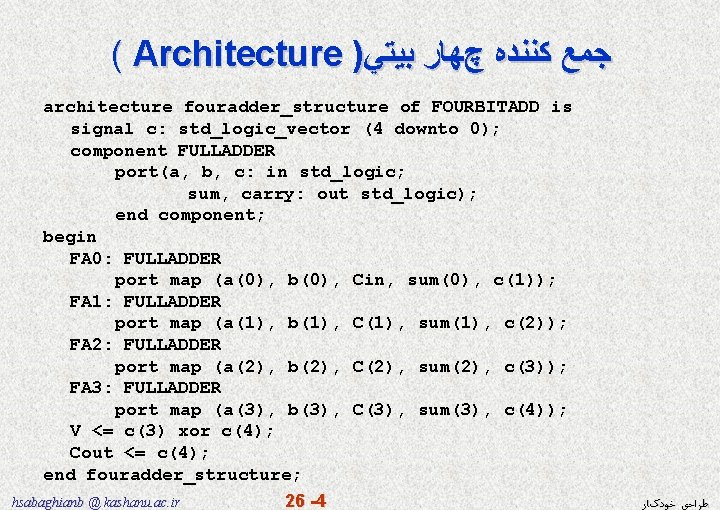

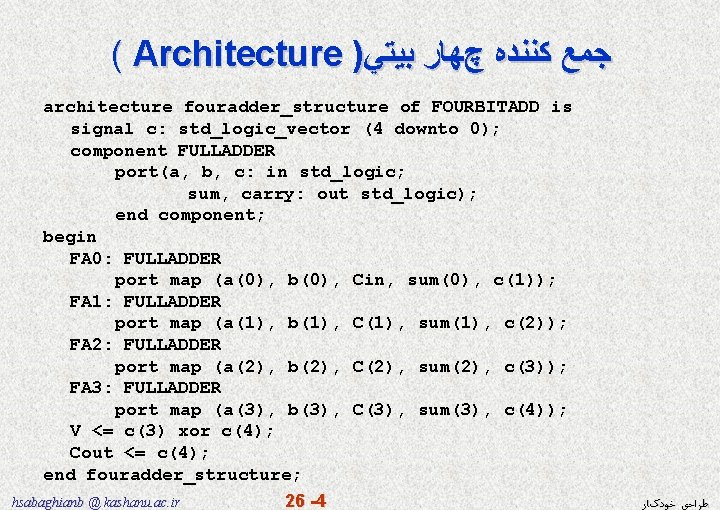

( Architecture ) ﺑﻴﺘﻲ چﻬﺎﺭ ﻛﻨﻨﺪﻩ ﺟﻤﻊ architecture fouradder_structure of FOURBITADD is signal c: std_logic_vector (4 downto 0); component FULLADDER port(a, b, c: in std_logic; sum, carry: out std_logic); end component; begin FA 0: FULLADDER port map (a(0), b(0), Cin, sum(0), c(1)); FA 1: FULLADDER port map (a(1), b(1), C(1), sum(1), c(2)); FA 2: FULLADDER port map (a(2), b(2), C(2), sum(2), c(3)); FA 3: FULLADDER port map (a(3), b(3), C(3), sum(3), c(4)); V <= c(3) xor c(4); Cout <= c(4); end fouradder_structure; hsabaghianb @ kashanu. ac. ir 26 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

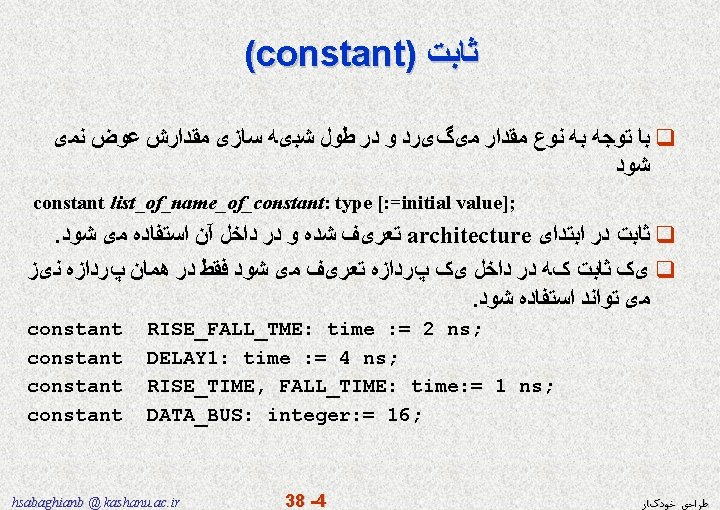

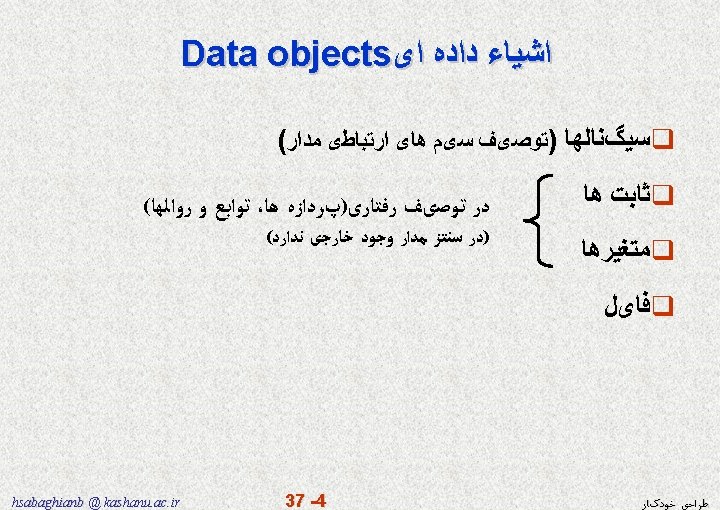

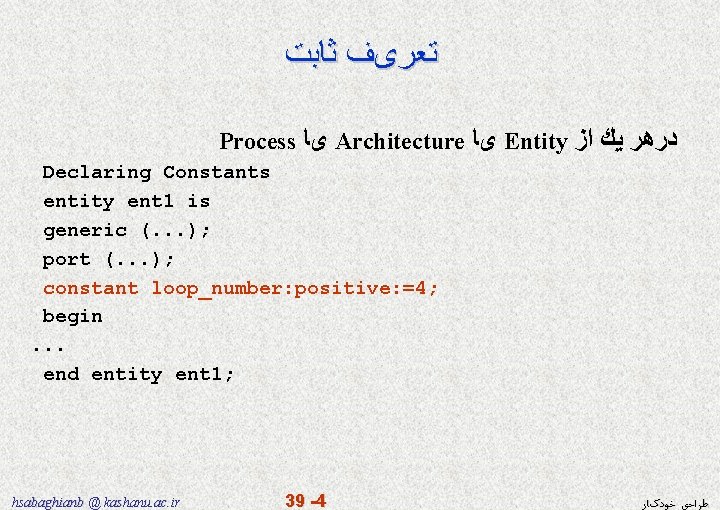

ﺗﻌﺮیﻒ ﺛﺎﺑﺖ Process یﺎ Architecture یﺎ Entity ﺩﺭﻫﺮ ﻳﻚ ﺍﺯ Declaring Constants entity ent 1 is generic (. . . ); port (. . . ); constant loop_number: positive: =4; begin. . . end entity ent 1; hsabaghianb @ kashanu. ac. ir 39 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

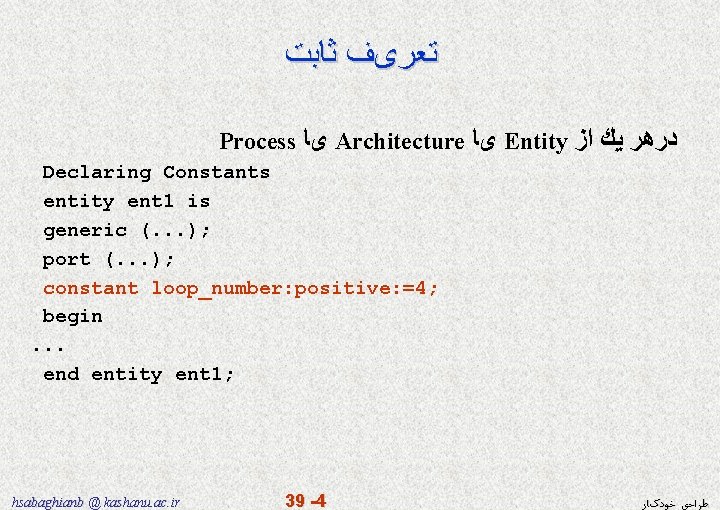

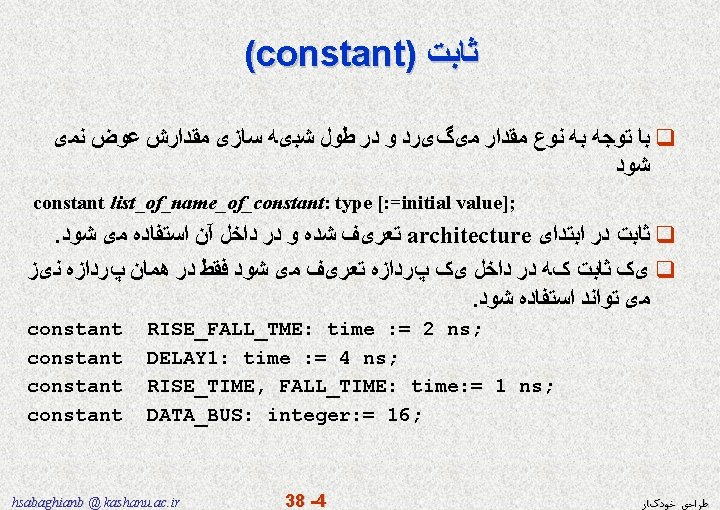

ﺗﻌﺮیﻒ ﺛﺎﺑﺖ Architecture ent 1_arch of Ent 1 is CONSTANT t_propagation: time: =10 ns; Begin. . . End architecture ent 1_arch; ---------------------Declaring Constants p 1: process (A, B) constant t_hold: time: =5 ns; begin. . . end process p 1; hsabaghianb @ kashanu. ac. ir 40 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

![Signal ﺳﻴگﻨﺎﻝ signal listofsignalnames type initial value signal SUM CARRY stdlogic (Signal) ﺳﻴگﻨﺎﻝ signal list_of_signal_names: type [ : = initial value]; signal SUM, CARRY: std_logic;](https://slidetodoc.com/presentation_image_h/7dd9dc0b55c9ccc0c256796944394644/image-42.jpg)

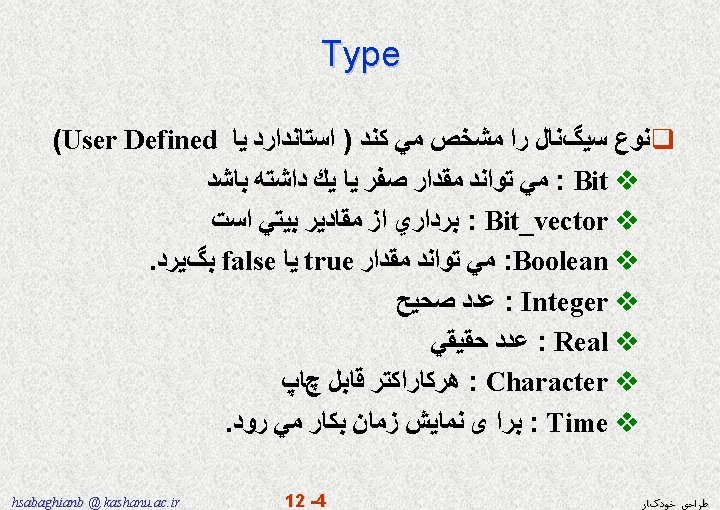

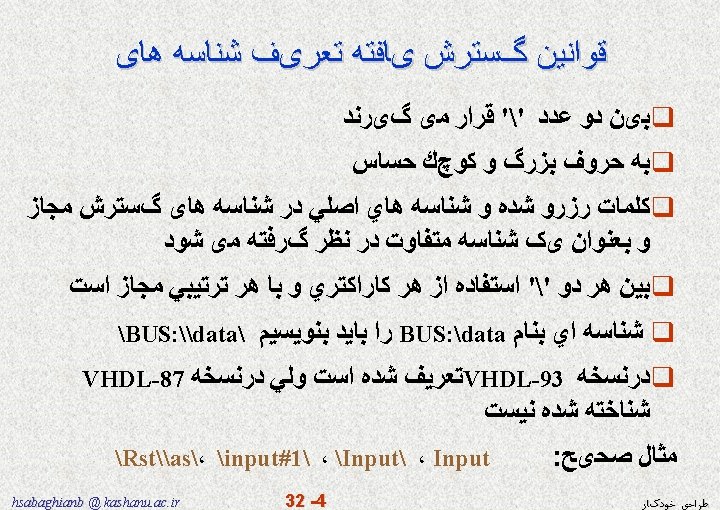

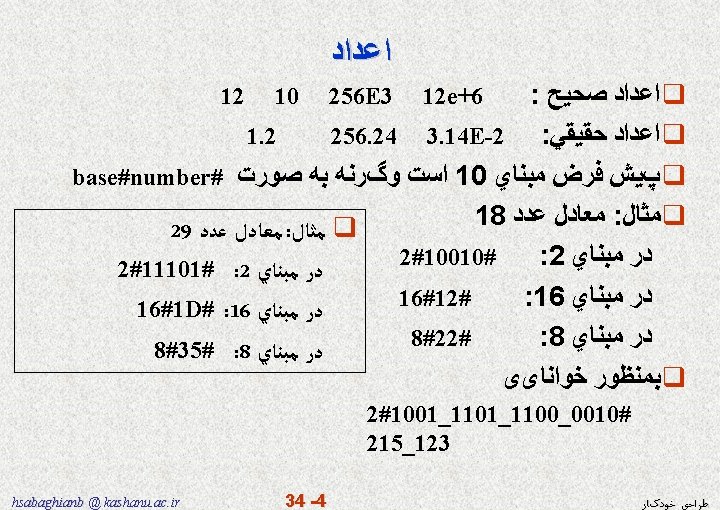

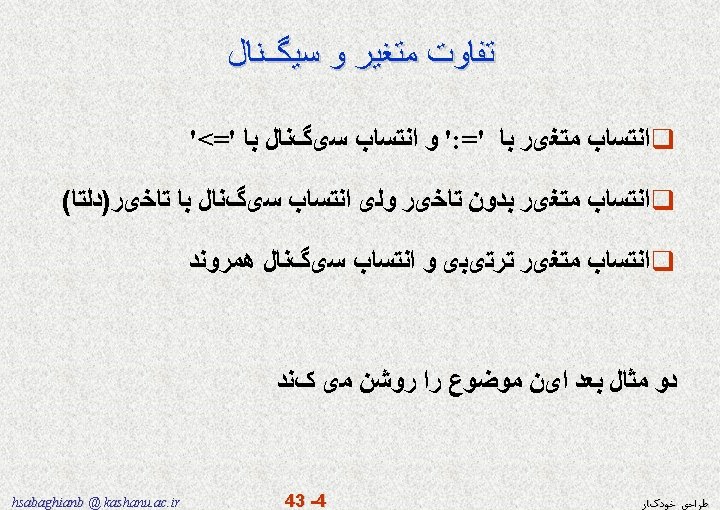

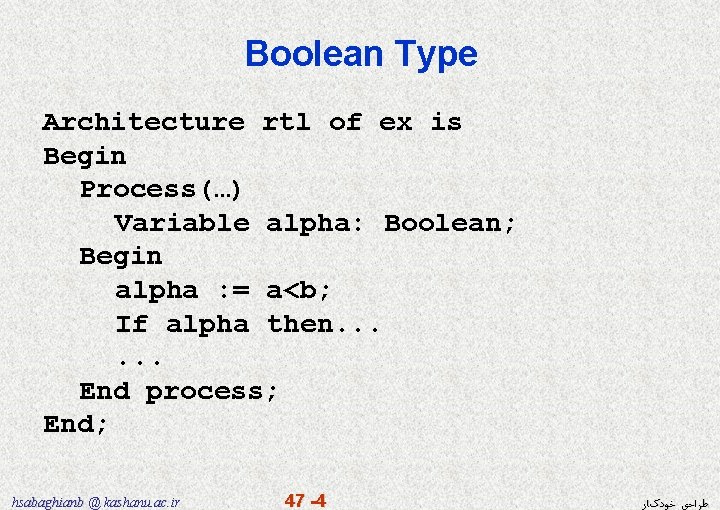

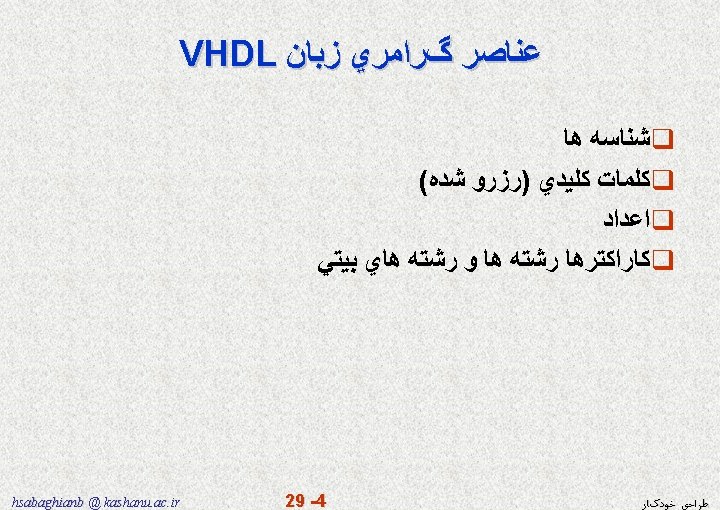

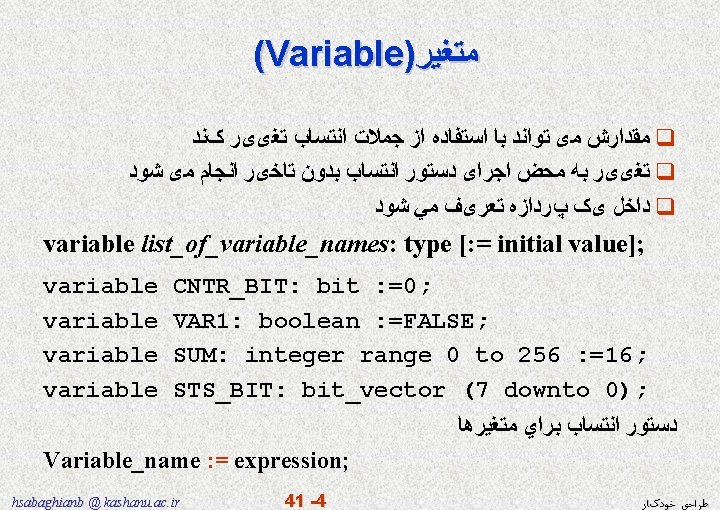

(Signal) ﺳﻴگﻨﺎﻝ signal list_of_signal_names: type [ : = initial value]; signal SUM, CARRY: std_logic; signal CLOCK: bit; signal TRIGGER: integer : =0; signal DATA_BUS: bit_vector (0 to 7); signal VALUE: integer range 0 to 100; ﺑﺎ یک ﺗﺎﺧیﺮ ﻣﺸﺨﺺ پﺲ ﺍﺯ ﺍﺟﺮﺍی ﺩﺳﺘﻮﺭ ﺍﻧﺘﺴﺎﺏ ﺑﻪ ﺭﻭﺯ ﻣی ﺷﻮﻧﺪ SUM <= (A xor B) after 2 ns; یک ﺷکﻞ ﻣﻮﺝ ﺩﻟﺨﻮﺍﻩ ﺍیﺠﺎﺩ کﺮﺩ ، ﻣﻴﺘﻮﺍﻥ ﺑﺎ ﻳﻚ ﺗﻮﺍﻟﻲ ﺍﺯ ﻣﻘﺎﺩیﺮ signal wavefrm : std_logic; wavefrm <=‘ 0’, ‘ 1’ after 5 ns, ‘ 0’ after 10 ns, ‘ 1’ after 20 ns; hsabaghianb @ kashanu. ac. ir 42 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

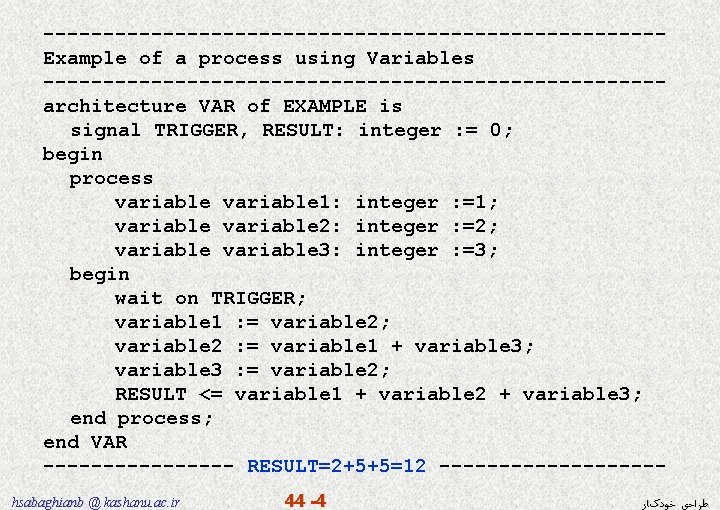

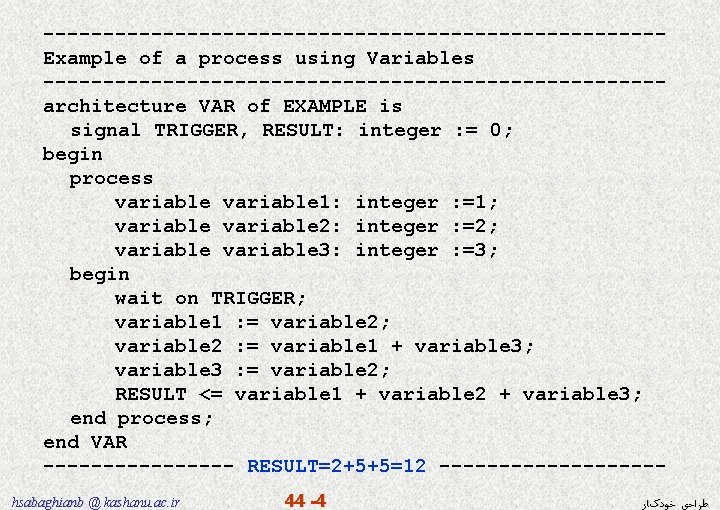

--------------------------Example of a process using Variables --------------------------architecture VAR of EXAMPLE is signal TRIGGER, RESULT: integer : = 0; begin process variable 1: integer : =1; variable 2: integer : =2; variable 3: integer : =3; begin wait on TRIGGER; variable 1 : = variable 2; variable 2 : = variable 1 + variable 3; variable 3 : = variable 2; RESULT <= variable 1 + variable 2 + variable 3; end process; end VAR -------- RESULT=2+5+5=12 ---------hsabaghianb @ kashanu. ac. ir 44 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

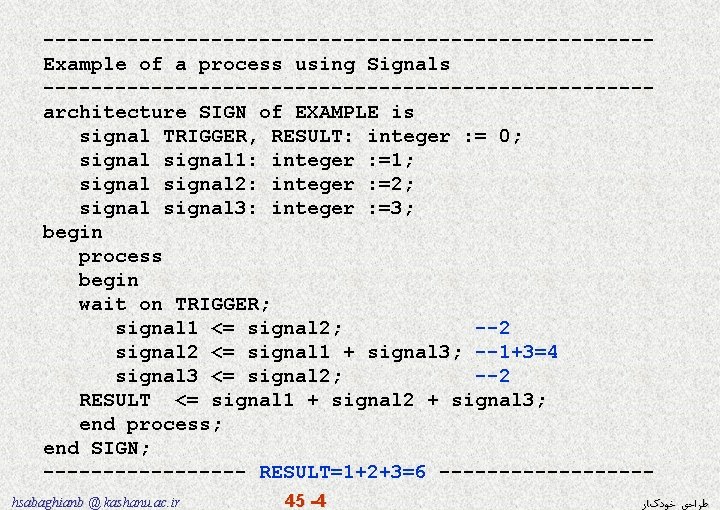

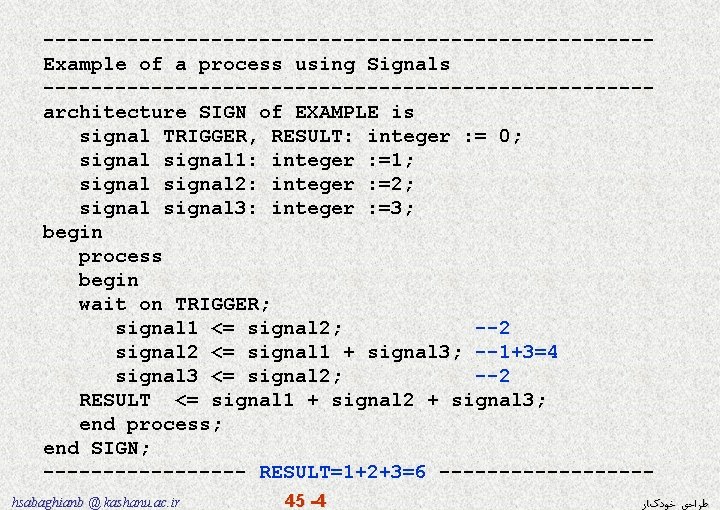

-------------------------Example of a process using Signals -------------------------architecture SIGN of EXAMPLE is signal TRIGGER, RESULT: integer : = 0; signal 1: integer : =1; signal 2: integer : =2; signal 3: integer : =3; begin process begin wait on TRIGGER; signal 1 <= signal 2; --2 signal 2 <= signal 1 + signal 3; --1+3=4 signal 3 <= signal 2; --2 RESULT <= signal 1 + signal 2 + signal 3; end process; end SIGN; --------- RESULT=1+2+3=6 ---------hsabaghianb @ kashanu. ac. ir 45 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

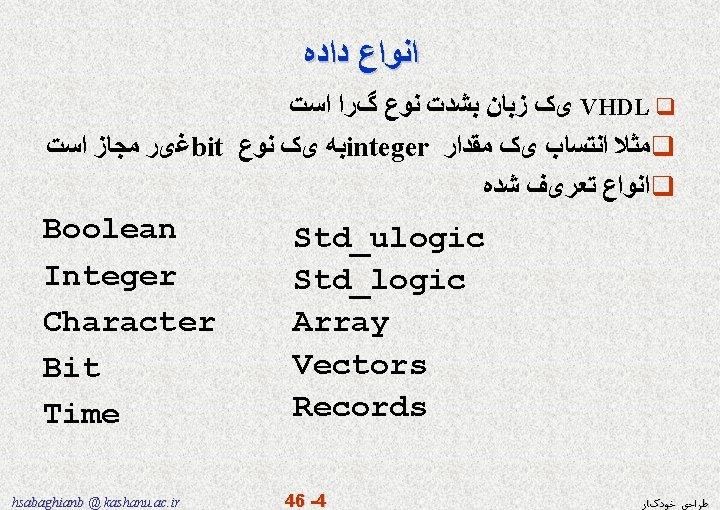

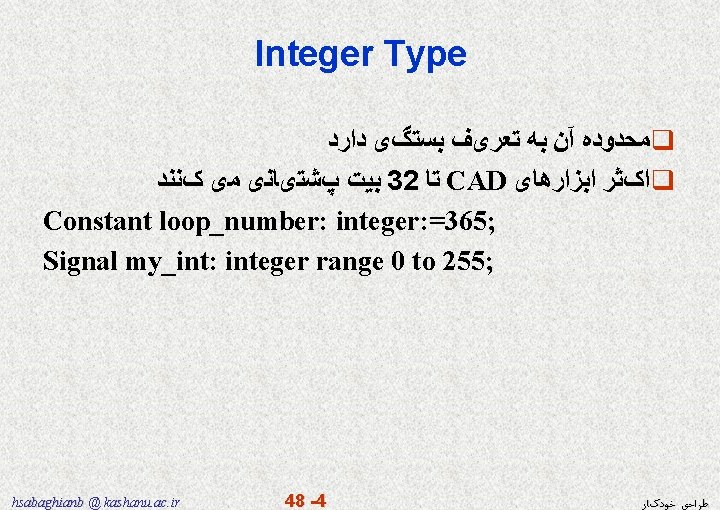

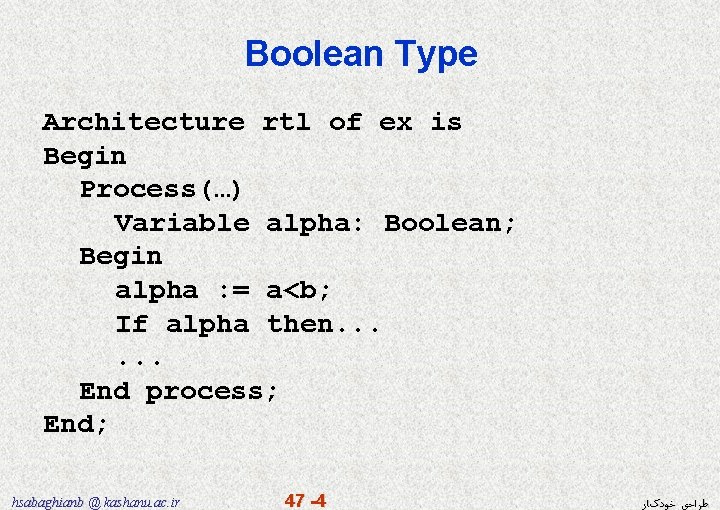

Boolean Type Architecture rtl of ex is Begin Process(…) Variable alpha: Boolean; Begin alpha : = a<b; If alpha then. . . End process; End; hsabaghianb @ kashanu. ac. ir 47 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

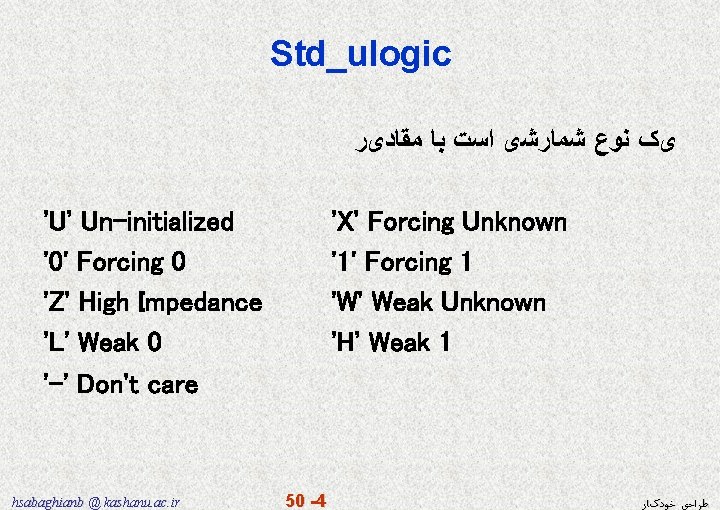

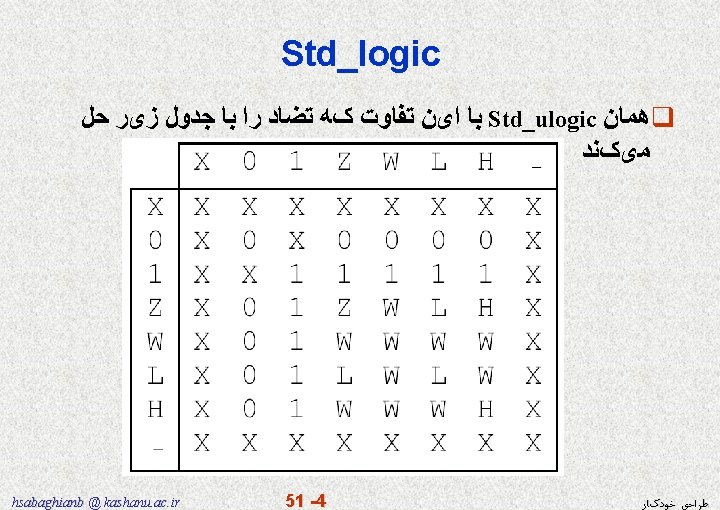

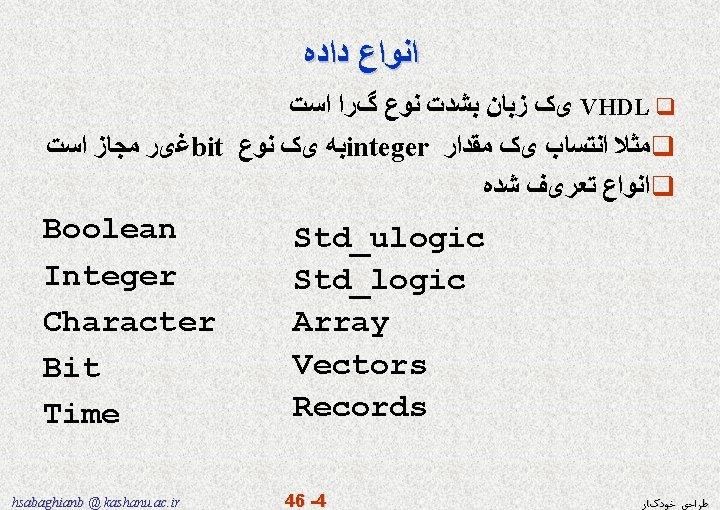

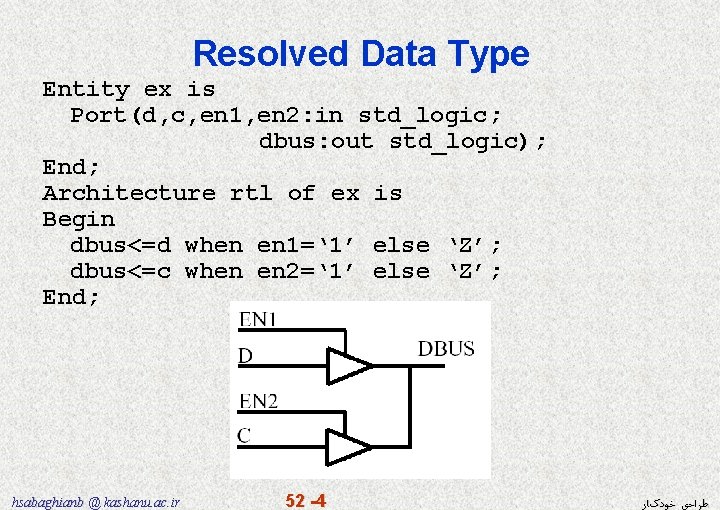

Std_ulogic یک ﻧﻮﻉ ﺷﻤﺎﺭﺷی ﺍﺳﺖ ﺑﺎ ﻣﻘﺎﺩیﺮ 'U' Un-initialized '0' Forcing 0 'Z' High Impedance 'L' Weak 0 '-' Don't care hsabaghianb @ kashanu. ac. ir 'X' Forcing Unknown '1' Forcing 1 'W' Weak Unknown 'H' Weak 1 50 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

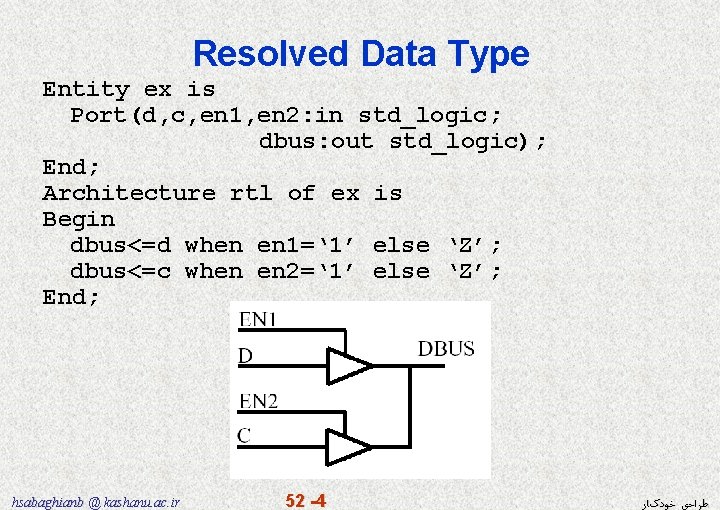

Resolved Data Type Entity ex is Port(d, c, en 1, en 2: in std_logic; dbus: out std_logic); End; Architecture rtl of ex is Begin dbus<=d when en 1=‘ 1’ else ‘Z’; dbus<=c when en 2=‘ 1’ else ‘Z’; End; hsabaghianb @ kashanu. ac. ir 52 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

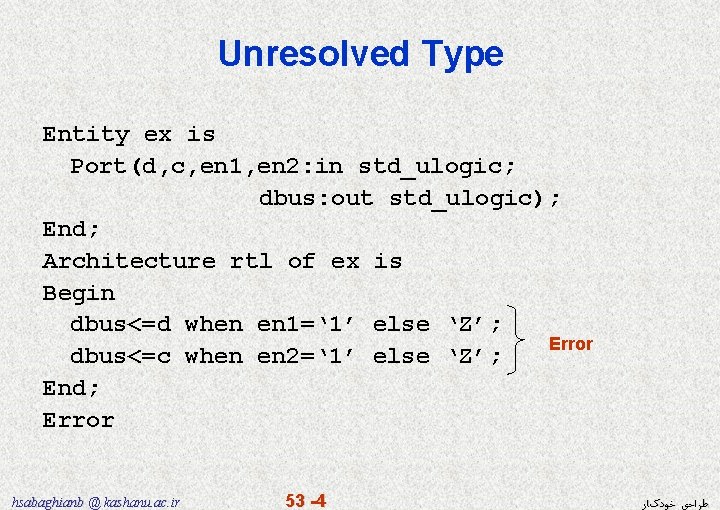

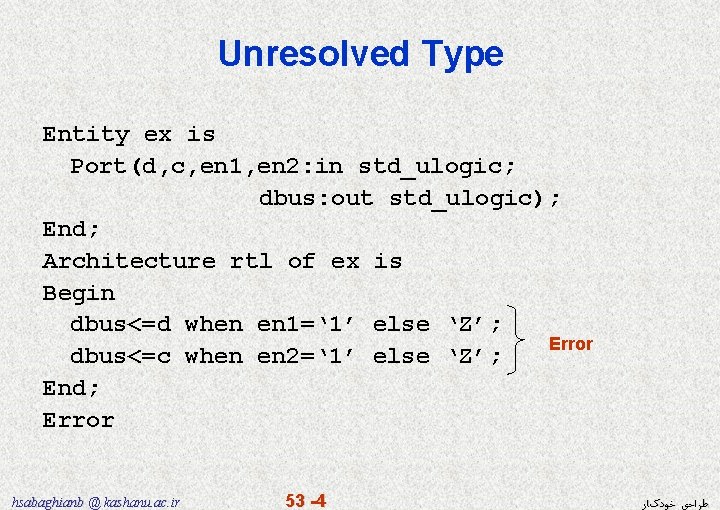

Unresolved Type Entity ex is Port(d, c, en 1, en 2: in std_ulogic; dbus: out std_ulogic); End; Architecture rtl of ex is Begin dbus<=d when en 1=‘ 1’ else ‘Z’; Error dbus<=c when en 2=‘ 1’ else ‘Z’; End; Error hsabaghianb @ kashanu. ac. ir 53 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

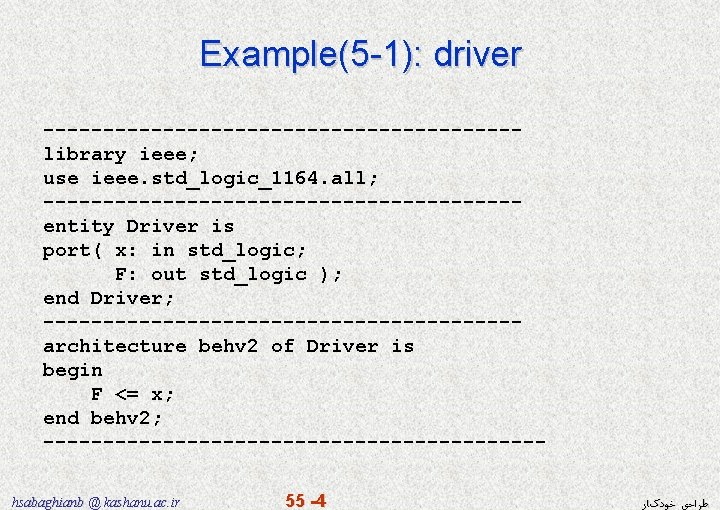

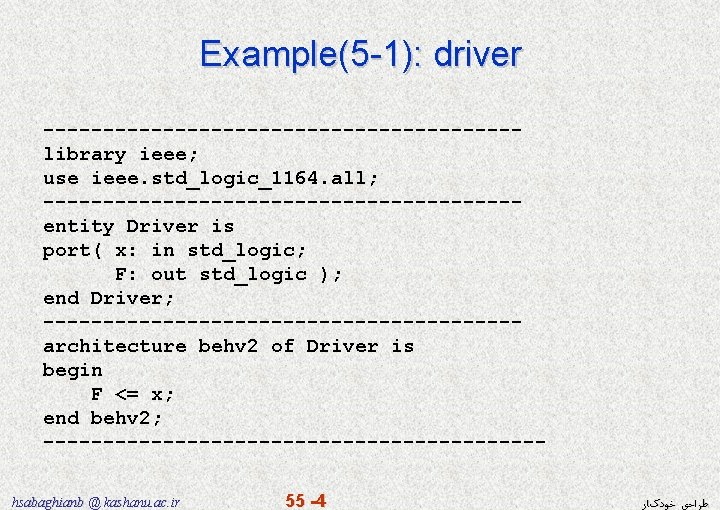

Example(5 -1): driver --------------------library ieee; use ieee. std_logic_1164. all; --------------------entity Driver is port( x: in std_logic; F: out std_logic ); end Driver; --------------------architecture behv 2 of Driver is begin F <= x; end behv 2; ---------------------hsabaghianb @ kashanu. ac. ir 55 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

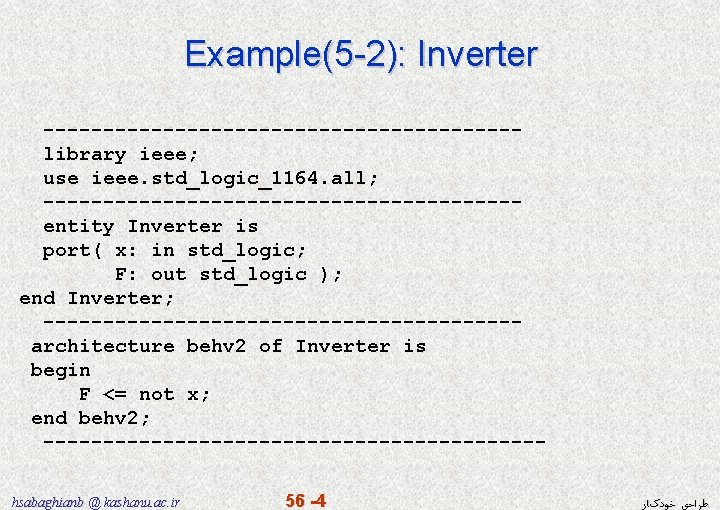

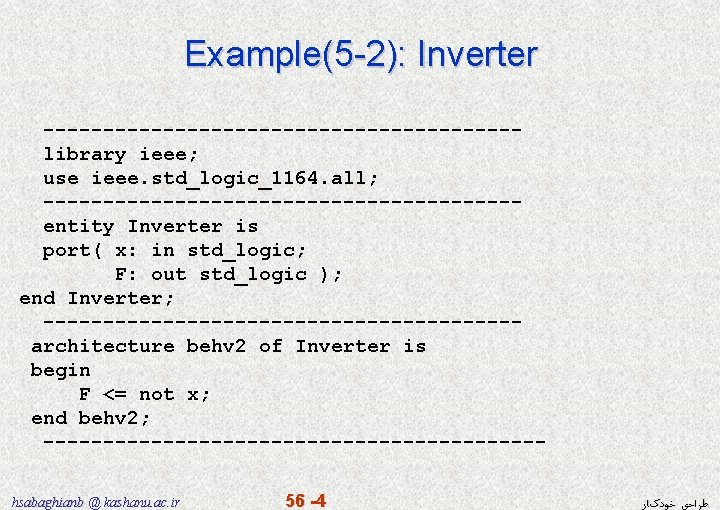

Example(5 -2): Inverter --------------------library ieee; use ieee. std_logic_1164. all; --------------------entity Inverter is port( x: in std_logic; F: out std_logic ); end Inverter; --------------------architecture behv 2 of Inverter is begin F <= not x; end behv 2; ---------------------hsabaghianb @ kashanu. ac. ir 56 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

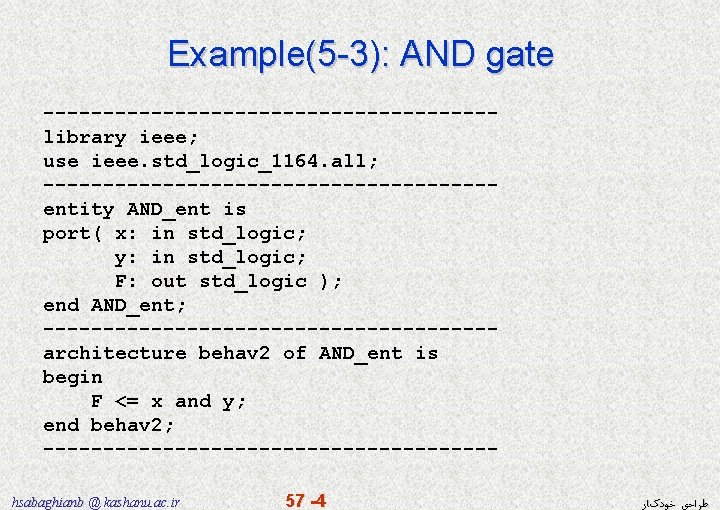

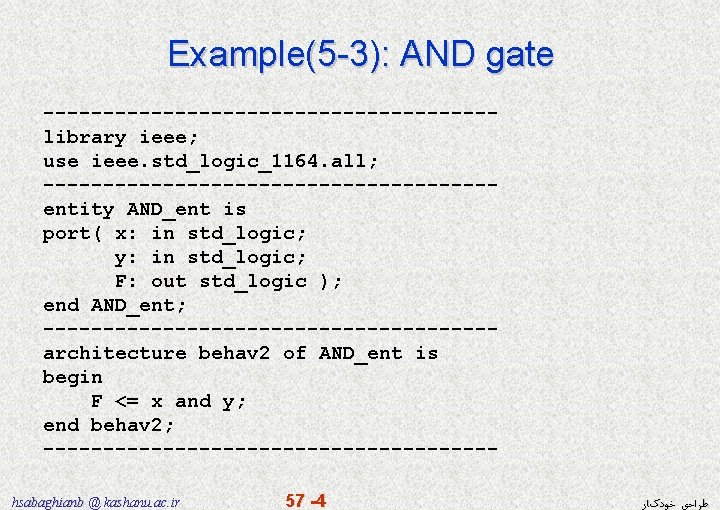

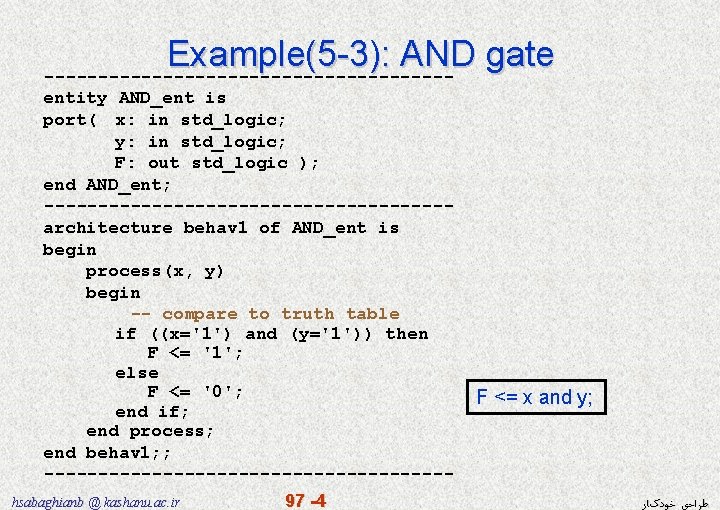

Example(5 -3): AND gate -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity AND_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end AND_ent; -------------------architecture behav 2 of AND_ent is begin F <= x and y; end behav 2; ------------------- hsabaghianb @ kashanu. ac. ir 57 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

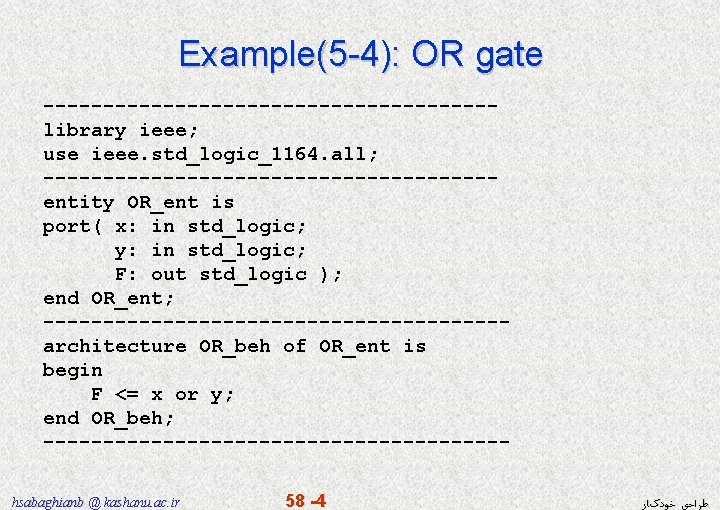

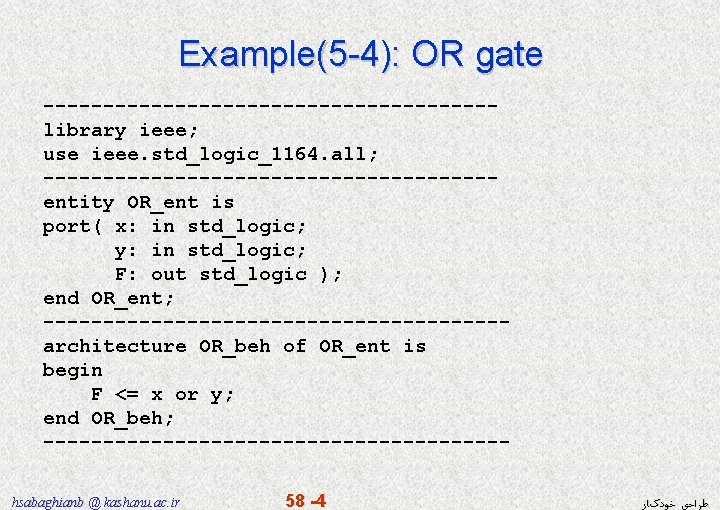

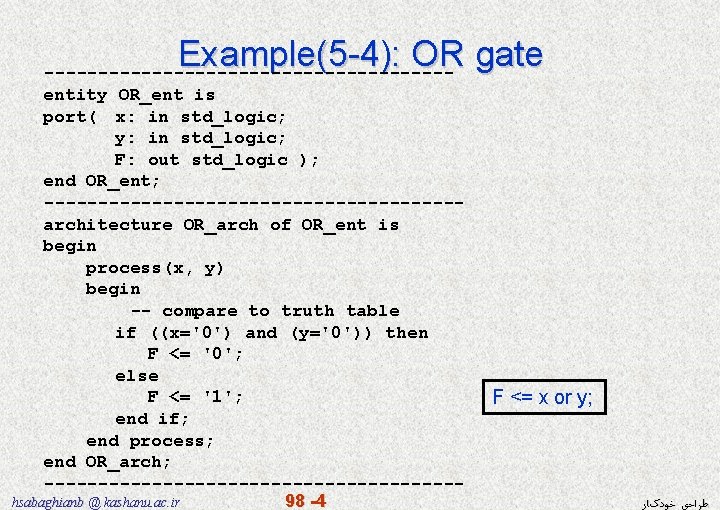

Example(5 -4): OR gate -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity OR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end OR_ent; -------------------architecture OR_beh of OR_ent is begin F <= x or y; end OR_beh; -------------------hsabaghianb @ kashanu. ac. ir 58 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

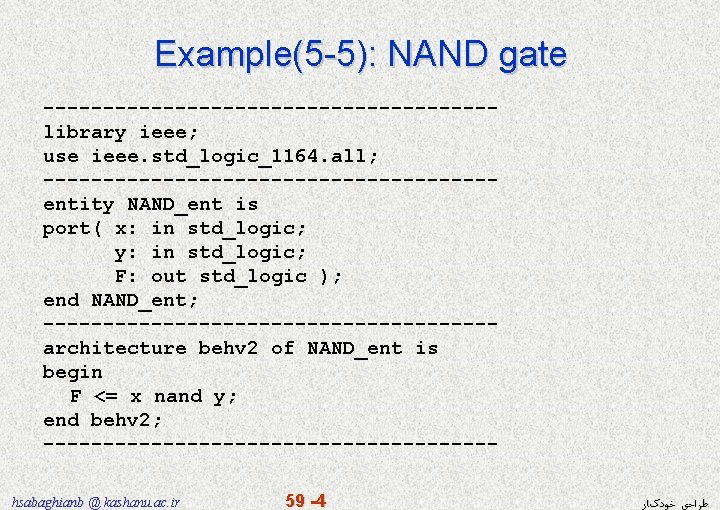

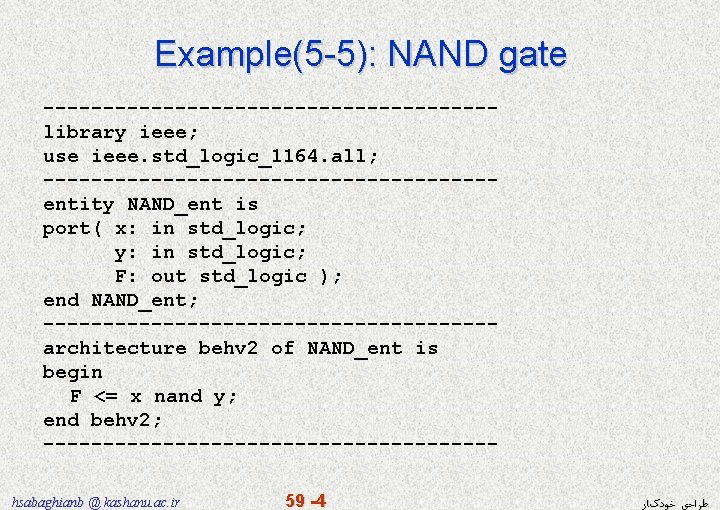

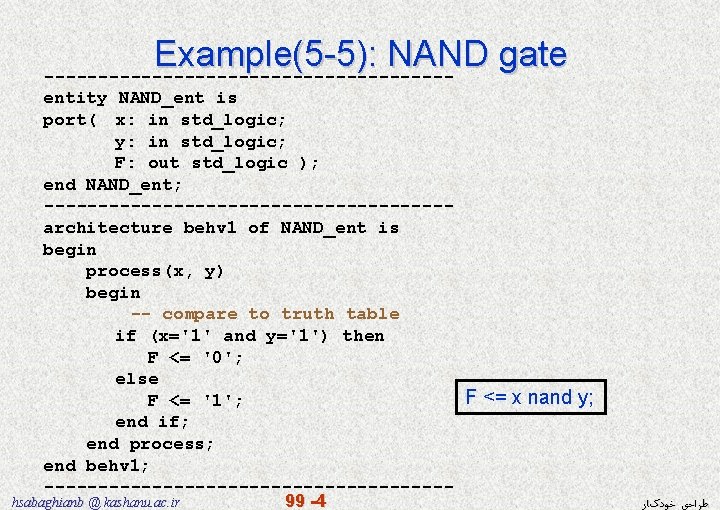

Example(5 -5): NAND gate -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity NAND_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end NAND_ent; -------------------architecture behv 2 of NAND_ent is begin F <= x nand y; end behv 2; -------------------hsabaghianb @ kashanu. ac. ir 59 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

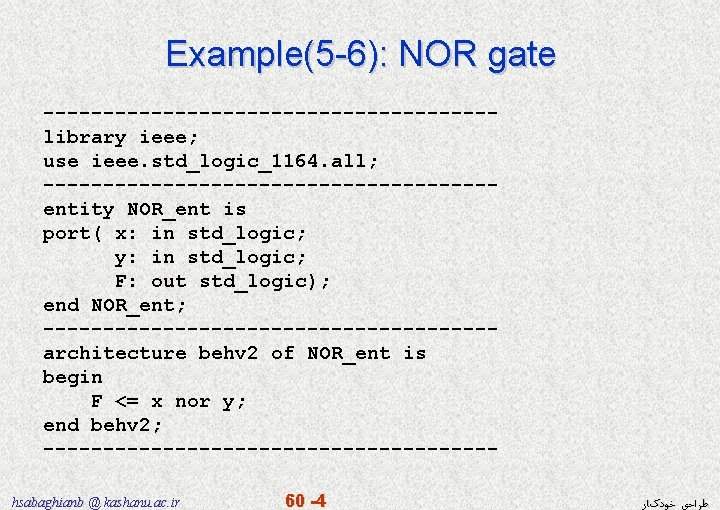

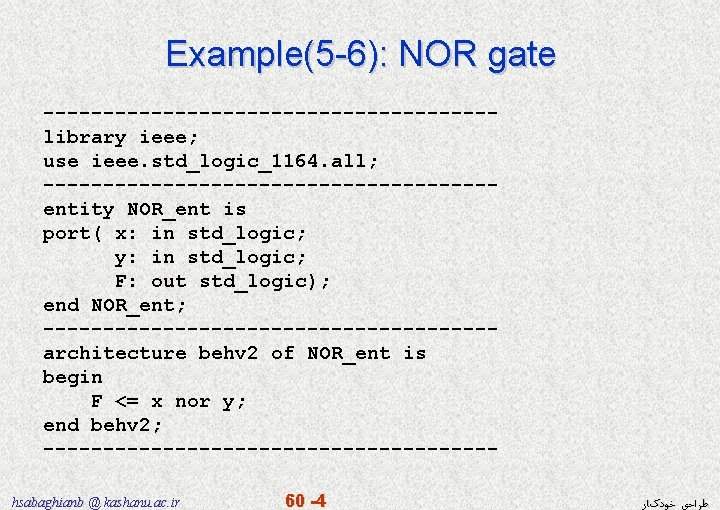

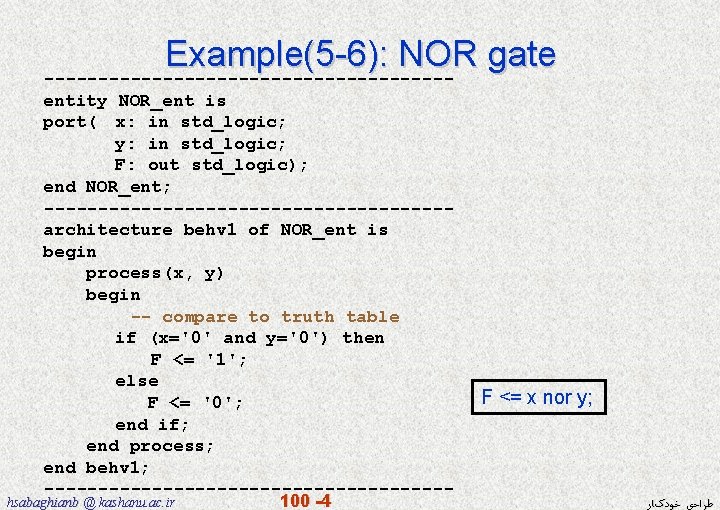

Example(5 -6): NOR gate -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity NOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end NOR_ent; -------------------architecture behv 2 of NOR_ent is begin F <= x nor y; end behv 2; -------------------hsabaghianb @ kashanu. ac. ir 60 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

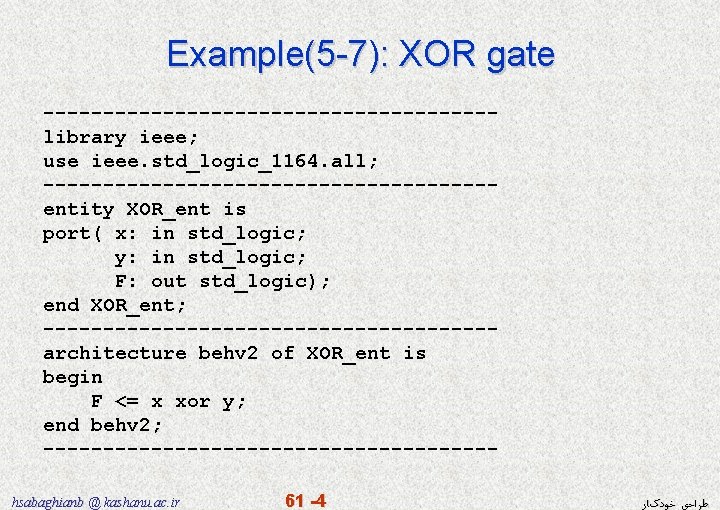

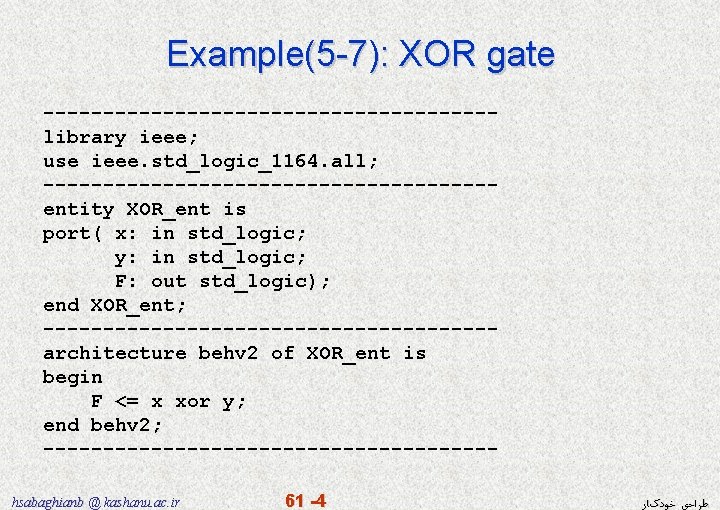

Example(5 -7): XOR gate -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity XOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end XOR_ent; -------------------architecture behv 2 of XOR_ent is begin F <= x xor y; end behv 2; -------------------hsabaghianb @ kashanu. ac. ir 61 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

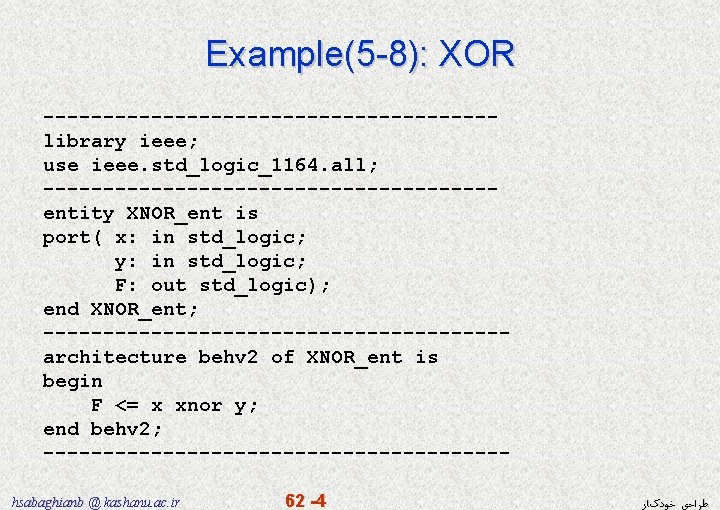

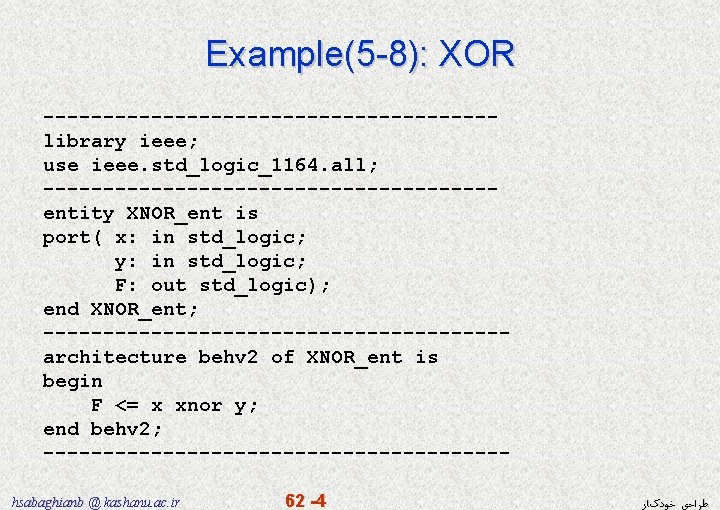

Example(5 -8): XOR -------------------library ieee; use ieee. std_logic_1164. all; -------------------entity XNOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end XNOR_ent; -------------------architecture behv 2 of XNOR_ent is begin F <= x xnor y; end behv 2; -------------------- hsabaghianb @ kashanu. ac. ir 62 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

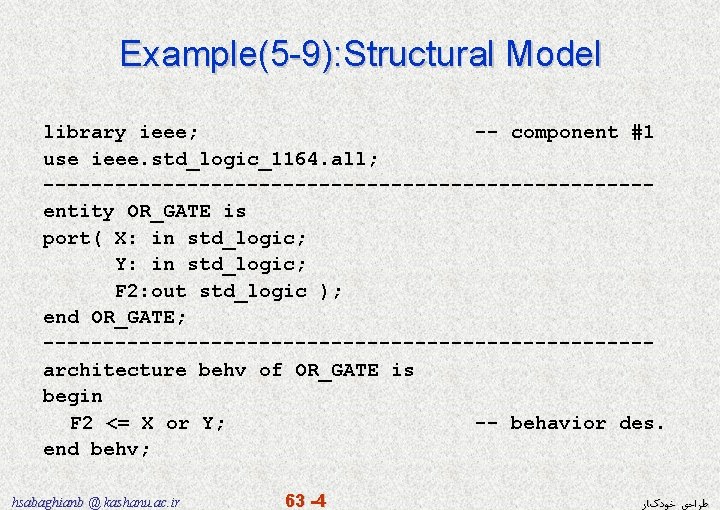

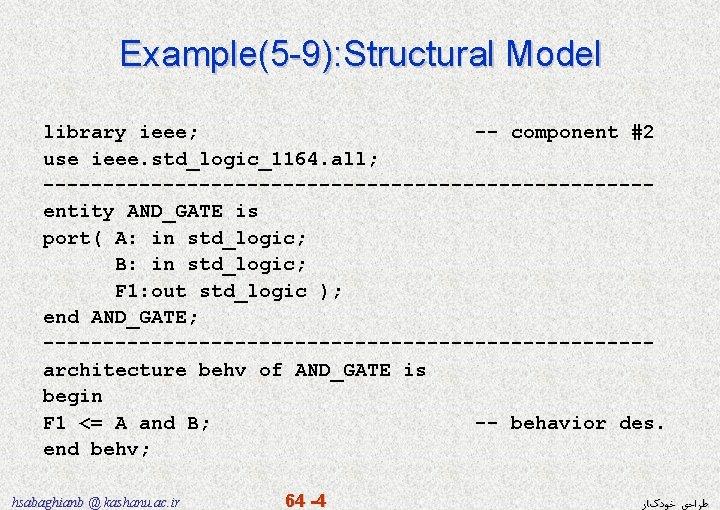

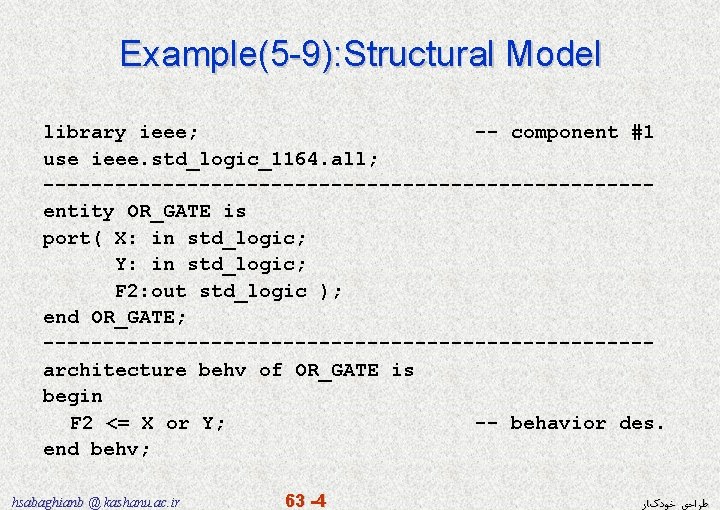

Example(5 -9): Structural Model library ieee; -- component #1 use ieee. std_logic_1164. all; -------------------------entity OR_GATE is port( X: in std_logic; Y: in std_logic; F 2: out std_logic ); end OR_GATE; -------------------------architecture behv of OR_GATE is begin F 2 <= X or Y; -- behavior des. end behv; hsabaghianb @ kashanu. ac. ir 63 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

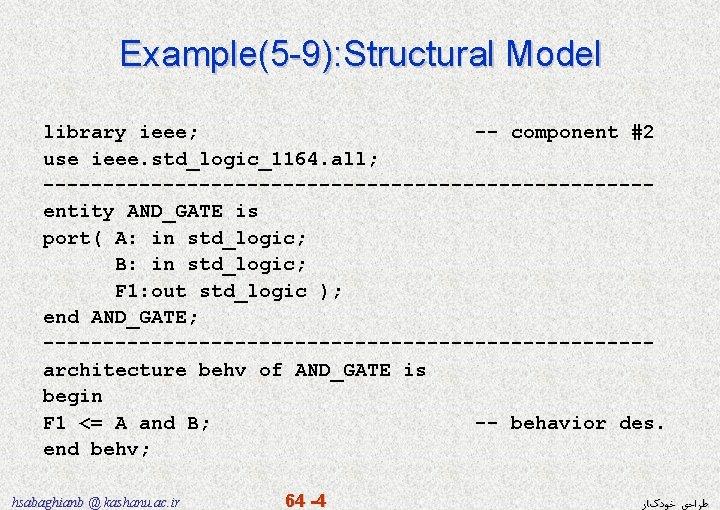

Example(5 -9): Structural Model library ieee; -- component #2 use ieee. std_logic_1164. all; -------------------------entity AND_GATE is port( A: in std_logic; B: in std_logic; F 1: out std_logic ); end AND_GATE; -------------------------architecture behv of AND_GATE is begin F 1 <= A and B; -- behavior des. end behv; hsabaghianb @ kashanu. ac. ir 64 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

library ieee; -- top level circuit use ieee. std_logic_1164. all; use work. all; entity comb_ckt is port( input 1: in std_logic; input 2: in std_logic; input 3: in std_logic; output: out std_logic); end comb_ckt; architecture struct of comb_ckt is component AND_GATE is -- as entity of AND_GATE port(A: in std_logic; B: in std_logic; F 1: out std_logic ); end component; component OR_GATE is -- as entity of OR_GATE port(X: in std_logic; Y: in std_logic; F 2: out std_logic ); end component; hsabaghianb @ kashanu. ac. ir 65 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

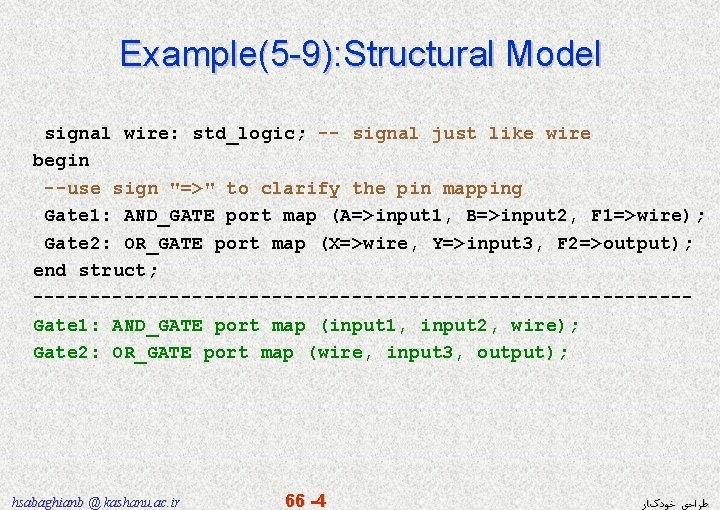

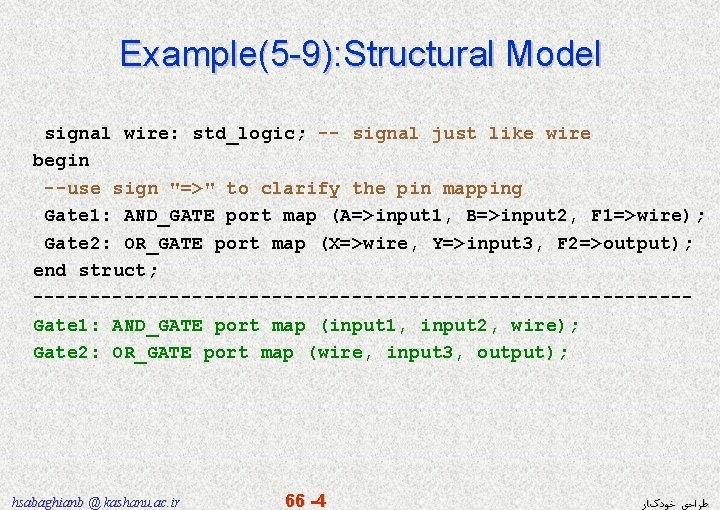

Example(5 -9): Structural Model signal wire: std_logic; -- signal just like wire begin --use sign "=>" to clarify the pin mapping Gate 1: AND_GATE port map (A=>input 1, B=>input 2, F 1=>wire); Gate 2: OR_GATE port map (X=>wire, Y=>input 3, F 2=>output); end struct; -----------------------------Gate 1: AND_GATE port map (input 1, input 2, wire); Gate 2: OR_GATE port map (wire, input 3, output); hsabaghianb @ kashanu. ac. ir 66 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

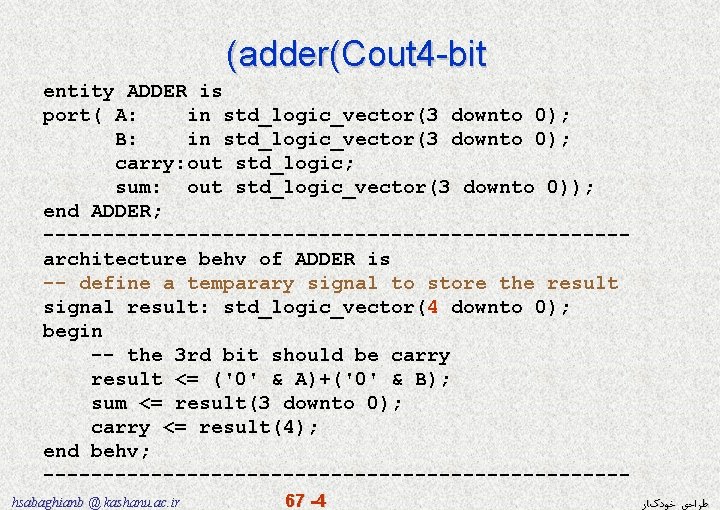

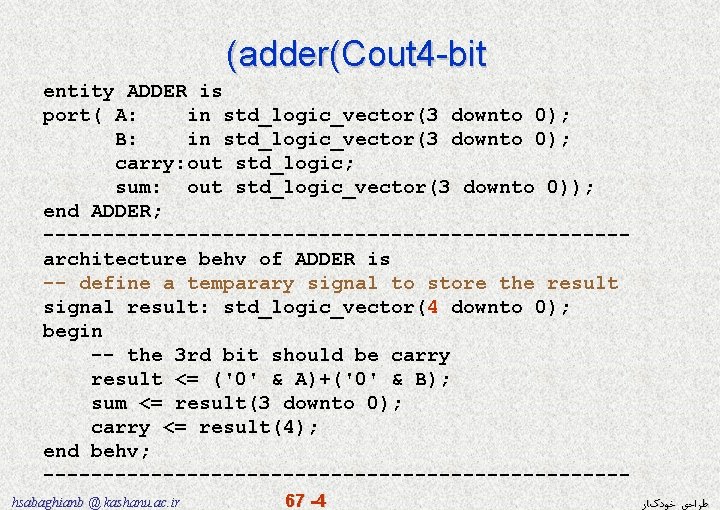

(adder(Cout 4 -bit entity ADDER is port( A: in std_logic_vector(3 downto 0); B: in std_logic_vector(3 downto 0); carry: out std_logic; sum: out std_logic_vector(3 downto 0)); end ADDER; ------------------------architecture behv of ADDER is -- define a temparary signal to store the result signal result: std_logic_vector(4 downto 0); begin -- the 3 rd bit should be carry result <= ('0' & A)+('0' & B); sum <= result(3 downto 0); carry <= result(4); end behv; ------------------------hsabaghianb @ kashanu. ac. ir 67 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

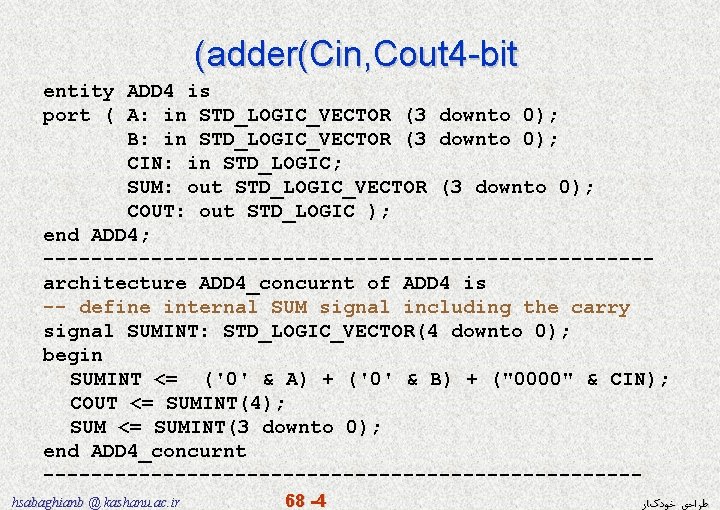

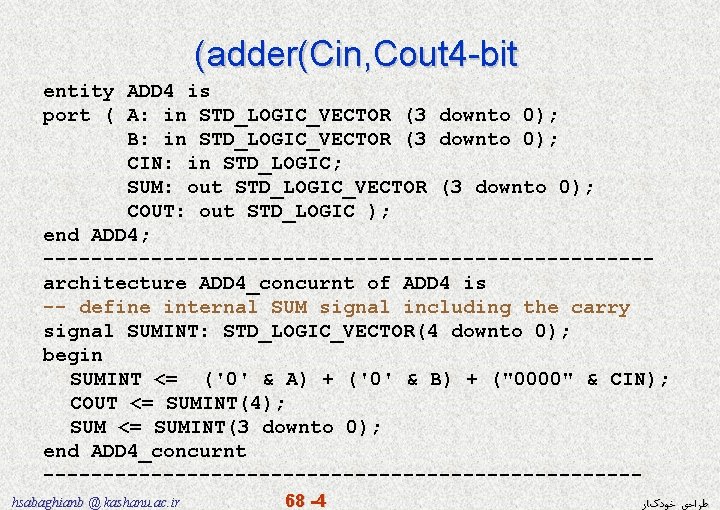

(adder(Cin, Cout 4 -bit entity ADD 4 is port ( A: in STD_LOGIC_VECTOR (3 downto 0); B: in STD_LOGIC_VECTOR (3 downto 0); CIN: in STD_LOGIC; SUM: out STD_LOGIC_VECTOR (3 downto 0); COUT: out STD_LOGIC ); end ADD 4; -------------------------architecture ADD 4_concurnt of ADD 4 is -- define internal SUM signal including the carry signal SUMINT: STD_LOGIC_VECTOR(4 downto 0); begin SUMINT <= ('0' & A) + ('0' & B) + ("0000" & CIN); COUT <= SUMINT(4); SUM <= SUMINT(3 downto 0); end ADD 4_concurnt -------------------------hsabaghianb @ kashanu. ac. ir 68 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

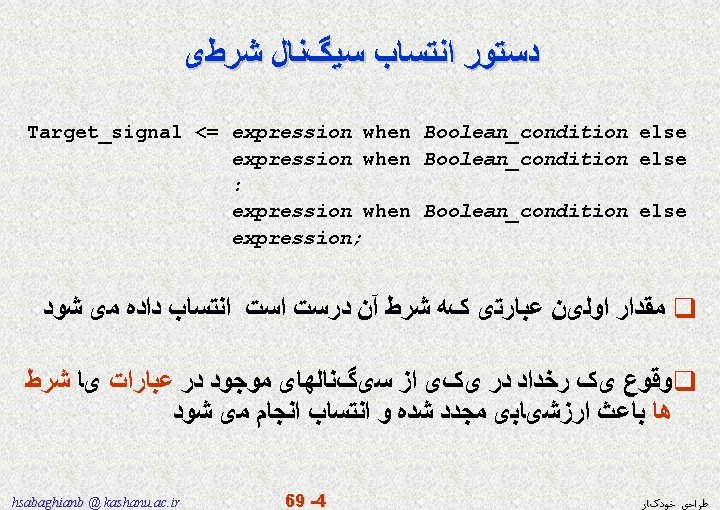

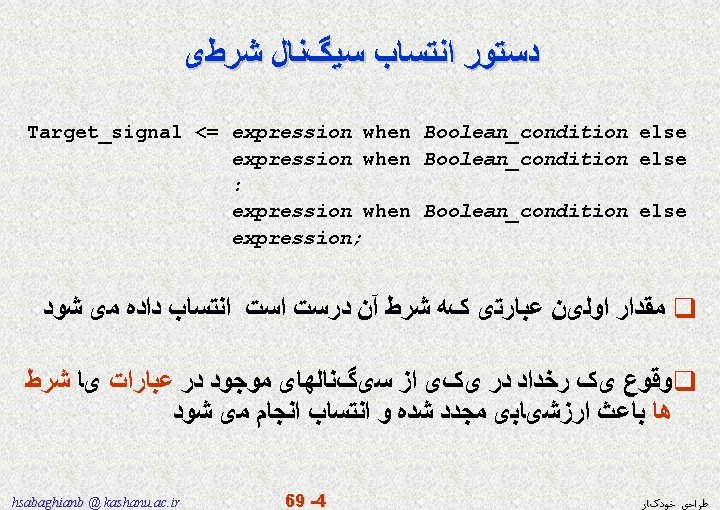

4/1 MUX --------------------------library ieee; use IEEE. std_logic_1164. all; --------------------------entity MUX_4_1_func. Tab is port (A, B, C, D: in std_logic; SEL: in std_logic_vector (1 downto 0); Z: out std_logic); end MUX 4_1_ func. Tab; --------------------------architecture concurr_MUX 41 of MUX_4_1_ func. Tab is begin Z <= A when SEL = ” 00” else B when SEL = ” 01” else C when SEL = “ 10” else D; end concurr_MUX 41; --------------------------- hsabaghianb @ kashanu. ac. ir 70 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

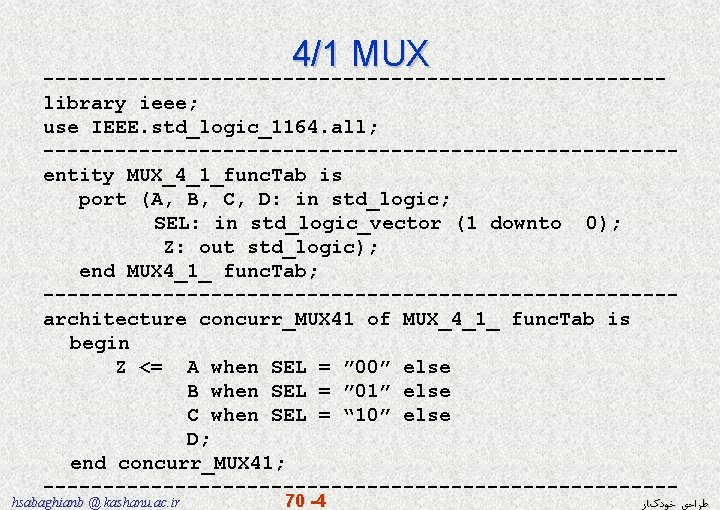

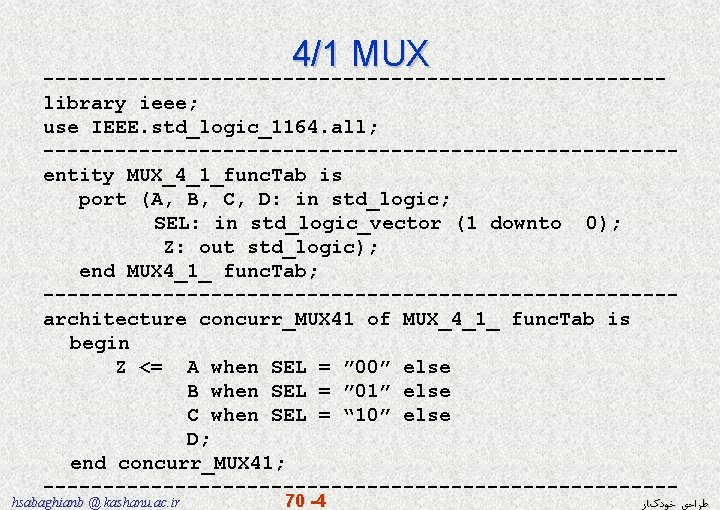

MUX 4/1 --------------------------library ieee; use IEEE. std_logic_1164. all; --------------------------entity MUX_4_1_Conc is port (S 1, S 0, A, B, C, D: in std_logic; Z: out std_logic); end MUX_4_1_Conc; --------------------------architecture concurr_MUX 41 of MUX_4_1_Conc is begin Z <= A when S 1=’ 0’ and S 0=’ 0’ else B when S 1=’ 0’ and S 0=’ 1’ else C when S 1=’ 1’ and S 0=’ 0’ else D; end concurr_MUX 41; --------------------------- hsabaghianb @ kashanu. ac. ir 71 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

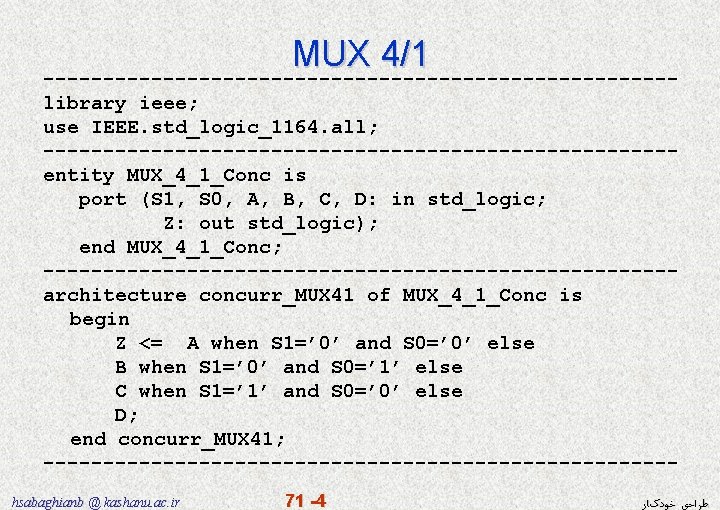

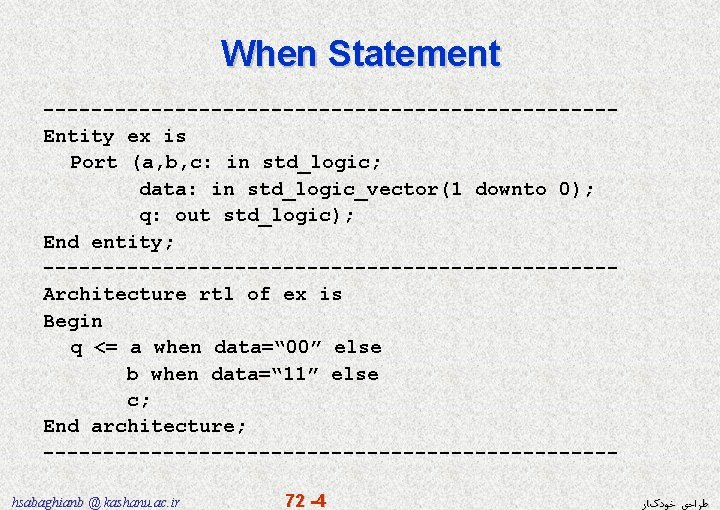

When Statement ------------------------Entity ex is Port (a, b, c: in std_logic; data: in std_logic_vector(1 downto 0); q: out std_logic); End entity; ------------------------Architecture rtl of ex is Begin q <= a when data=“ 00” else b when data=“ 11” else c; End architecture; ------------------------hsabaghianb @ kashanu. ac. ir 72 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

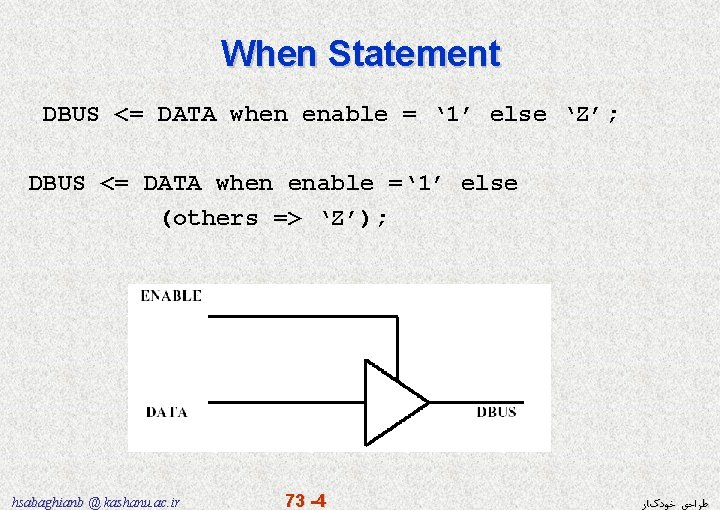

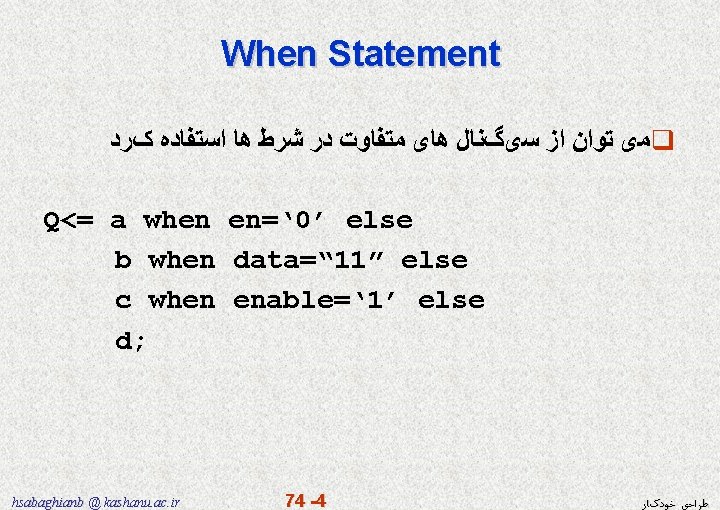

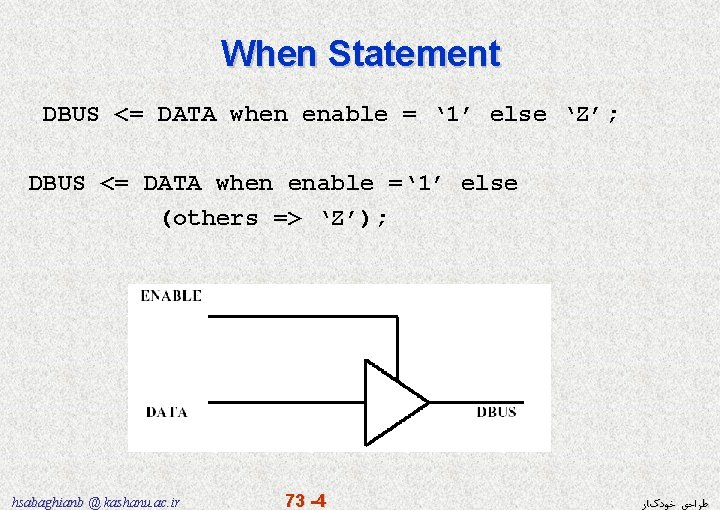

When Statement DBUS <= DATA when enable = ‘ 1’ else ‘Z’; DBUS <= DATA when enable =‘ 1’ else (others => ‘Z’); hsabaghianb @ kashanu. ac. ir 73 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

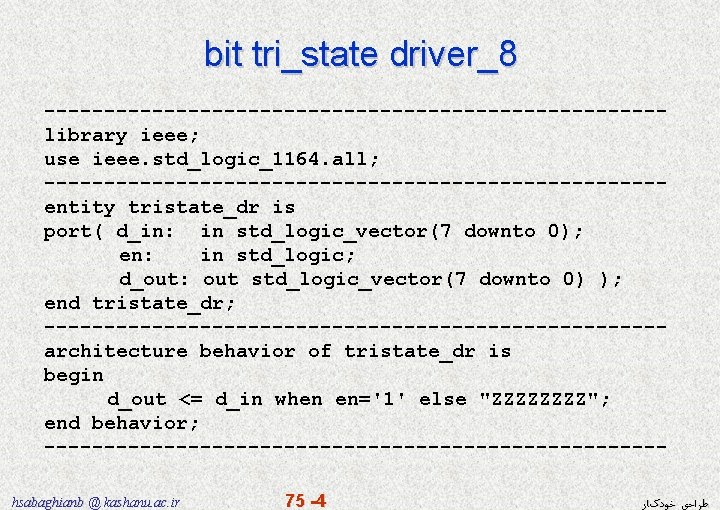

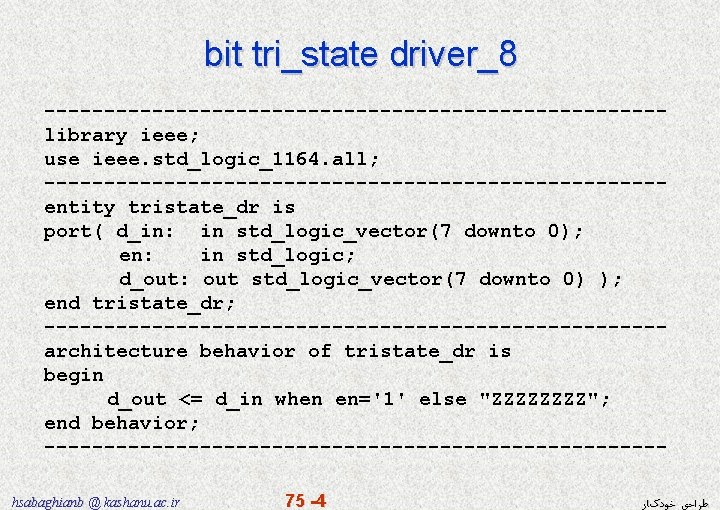

bit tri_state driver_8 --------------------------library ieee; use ieee. std_logic_1164. all; --------------------------entity tristate_dr is port( d_in: in std_logic_vector(7 downto 0); en: in std_logic; d_out: out std_logic_vector(7 downto 0) ); end tristate_dr; --------------------------architecture behavior of tristate_dr is begin d_out <= d_in when en='1' else "ZZZZ"; end behavior; --------------------------hsabaghianb @ kashanu. ac. ir 75 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

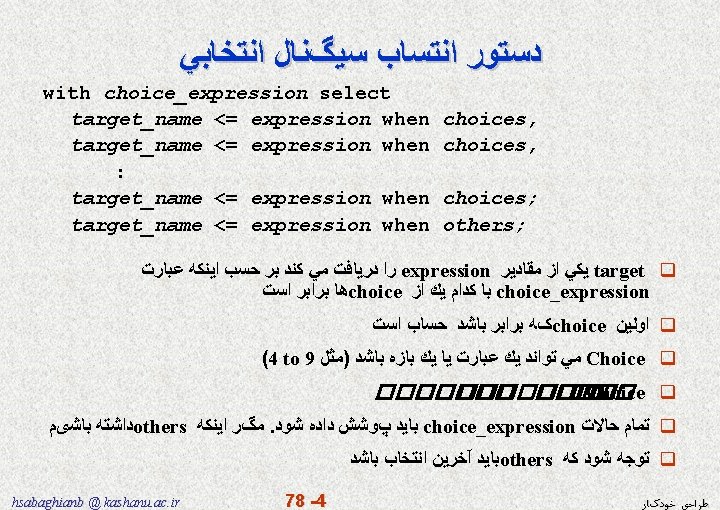

hsabaghianb @ kashanu. ac. ir 76 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

hsabaghianb @ kashanu. ac. ir 77 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

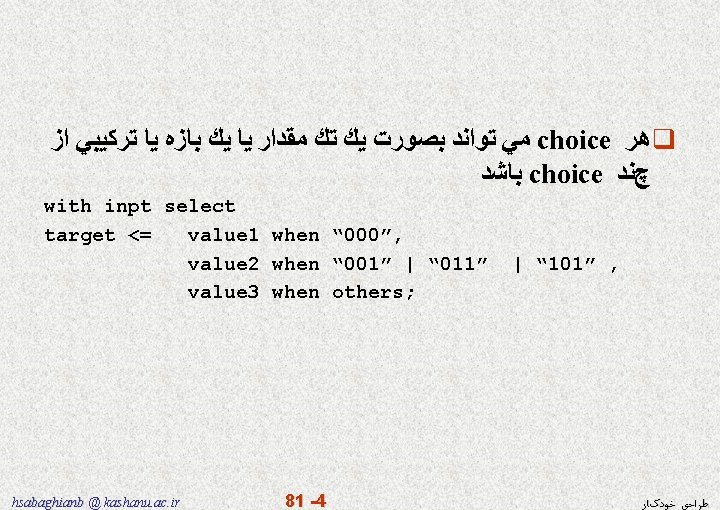

hsabaghianb @ kashanu. ac. ir 79 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

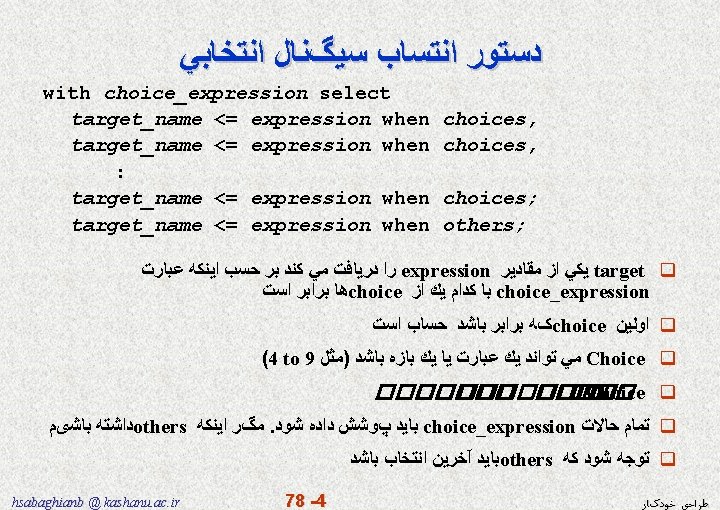

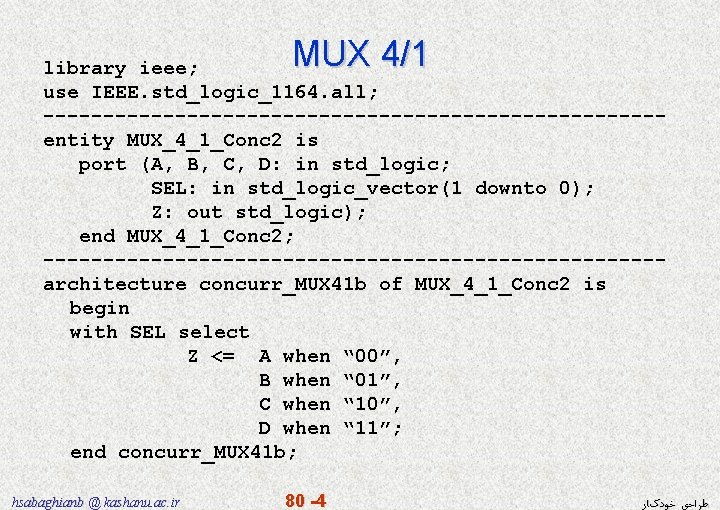

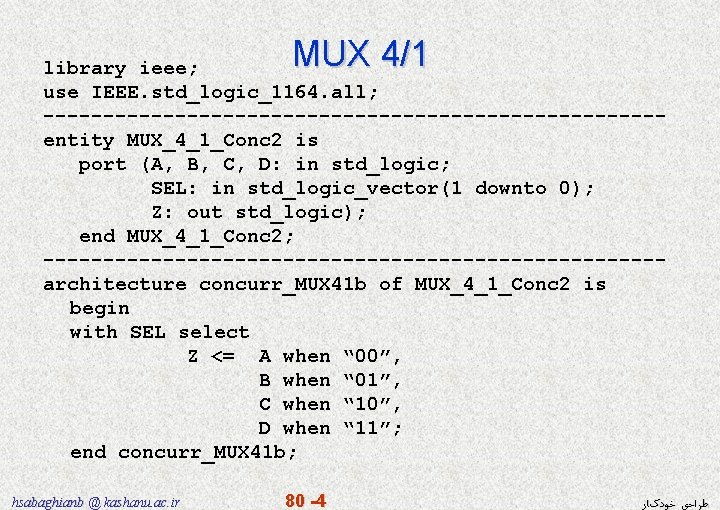

MUX 4/1 library ieee; use IEEE. std_logic_1164. all; --------------------------entity MUX_4_1_Conc 2 is port (A, B, C, D: in std_logic; SEL: in std_logic_vector(1 downto 0); Z: out std_logic); end MUX_4_1_Conc 2; --------------------------architecture concurr_MUX 41 b of MUX_4_1_Conc 2 is begin with SEL select Z <= A when “ 00”, B when “ 01”, C when “ 10”, D when “ 11”; end concurr_MUX 41 b; hsabaghianb @ kashanu. ac. ir 80 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

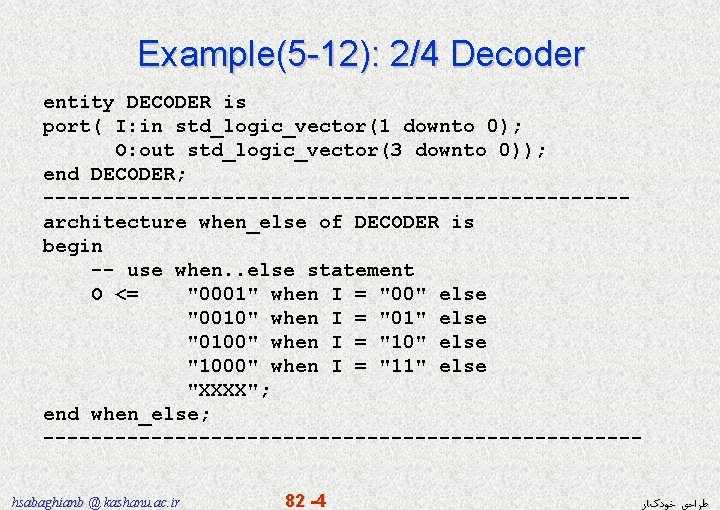

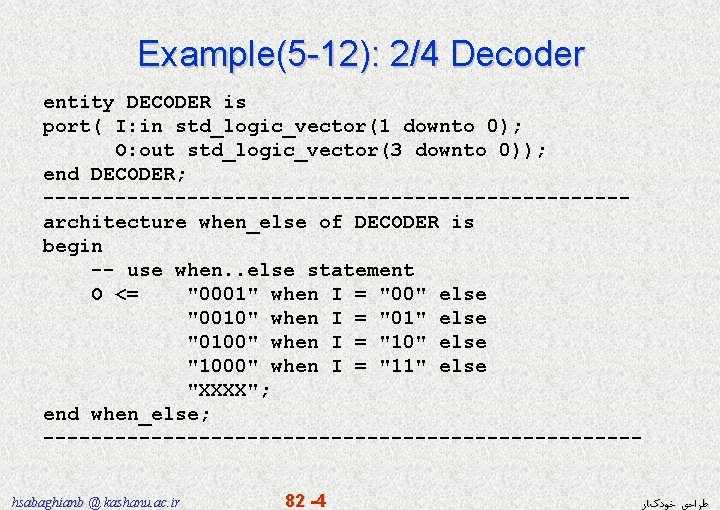

Example(5 -12): 2/4 Decoder entity DECODER is port( I: in std_logic_vector(1 downto 0); O: out std_logic_vector(3 downto 0)); end DECODER; ------------------------architecture when_else of DECODER is begin -- use when. . else statement O <= "0001" when I = "00" else "0010" when I = "01" else "0100" when I = "10" else "1000" when I = "11" else "XXXX"; end when_else; ------------------------- hsabaghianb @ kashanu. ac. ir 82 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

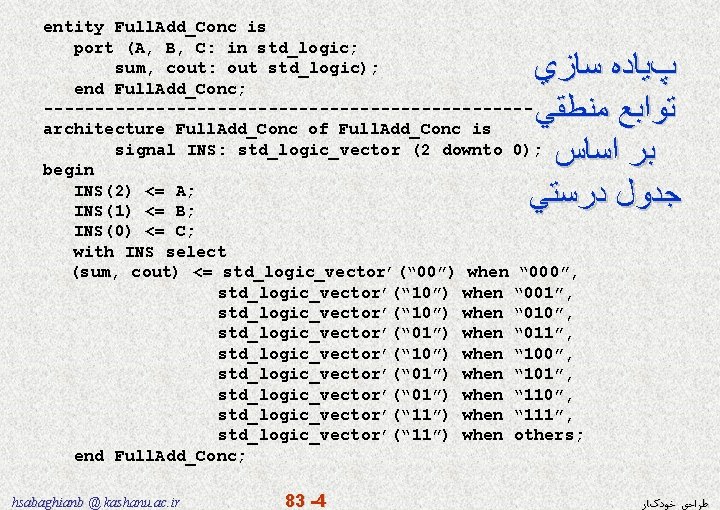

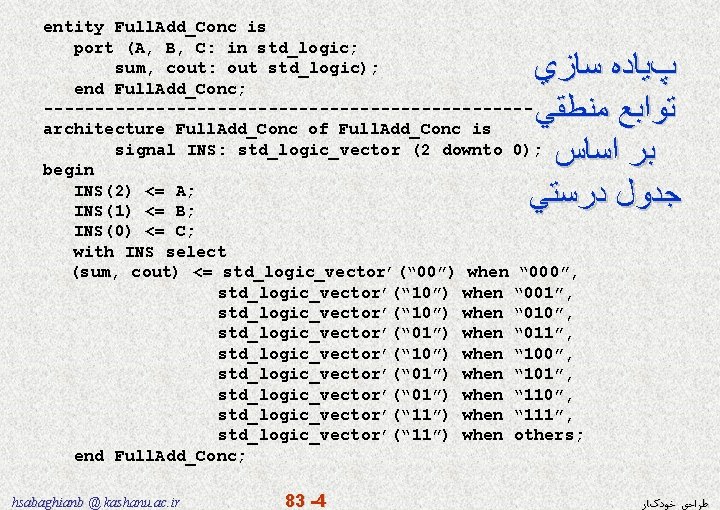

entity Full. Add_Conc is port (A, B, C: in std_logic; sum, cout: out std_logic); end Full. Add_Conc; ------------------------architecture Full. Add_Conc of Full. Add_Conc is signal INS: std_logic_vector (2 downto 0); begin INS(2) <= A; INS(1) <= B; INS(0) <= C; with INS select (sum, cout) <= std_logic_vector’(“ 00”) when “ 000”, std_logic_vector’(“ 10”) when “ 001”, std_logic_vector’(“ 10”) when “ 010”, std_logic_vector’(“ 01”) when “ 011”, std_logic_vector’(“ 10”) when “ 100”, std_logic_vector’(“ 01”) when “ 101”, std_logic_vector’(“ 01”) when “ 110”, std_logic_vector’(“ 11”) when “ 111”, std_logic_vector’(“ 11”) when others; end Full. Add_Conc; پﻴﺎﺩﻩ ﺳﺎﺯﻱ ﺗﻮﺍﺑﻊ ﻣﻨﻄﻘﻲ ﺑﺮ ﺍﺳﺎﺱ ﺟﺪﻭﻝ ﺩﺭﺳﺘﻲ hsabaghianb @ kashanu. ac. ir 83 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

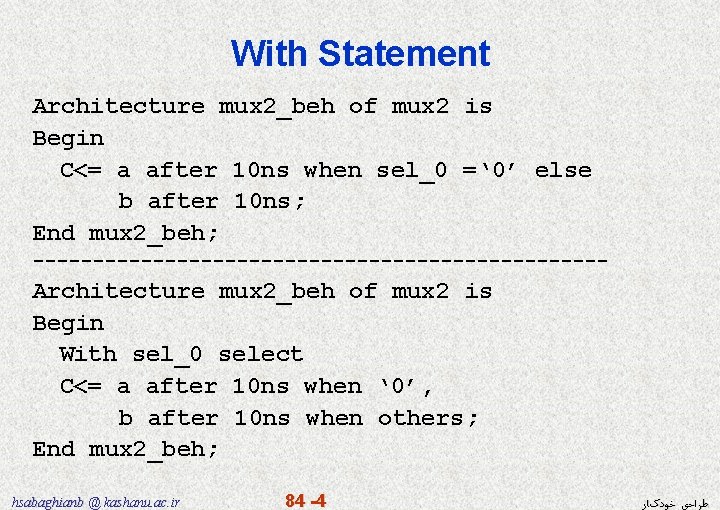

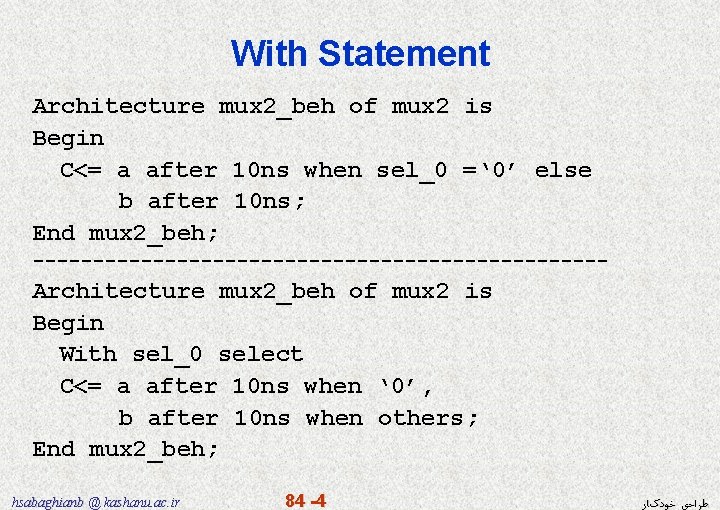

With Statement Architecture mux 2_beh of mux 2 is Begin C<= a after 10 ns when sel_0 =‘ 0’ else b after 10 ns; End mux 2_beh; ------------------------ Architecture mux 2_beh of mux 2 is Begin With sel_0 select C<= a after 10 ns when ‘ 0’, b after 10 ns when others; End mux 2_beh; hsabaghianb @ kashanu. ac. ir 84 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

![ﻗﺎﻟﺐ کﻠی ﺩﺳﺘﻮﺭ پﺮﺩﺍﺯﻩ processlabel process sensitivitylist is processdeclarations ﻗﺎﻟﺐ کﻠی ﺩﺳﺘﻮﺭ پﺮﺩﺍﺯﻩ [process_label: ] process [ (sensitivity_list) ] [is] [ process_declarations]](https://slidetodoc.com/presentation_image_h/7dd9dc0b55c9ccc0c256796944394644/image-86.jpg)

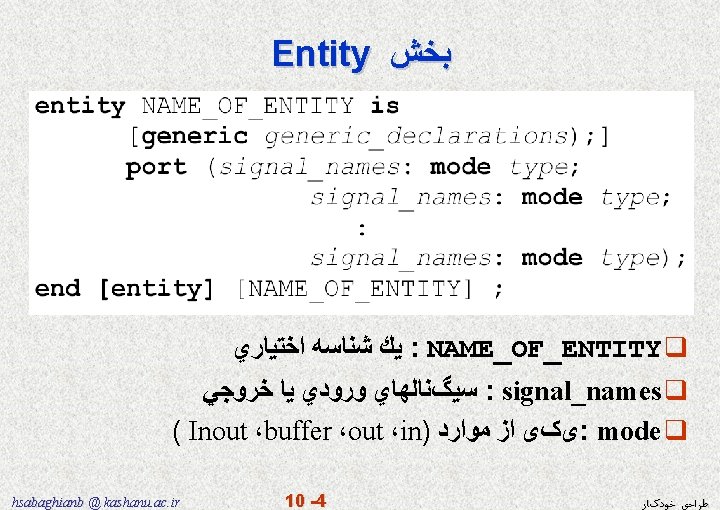

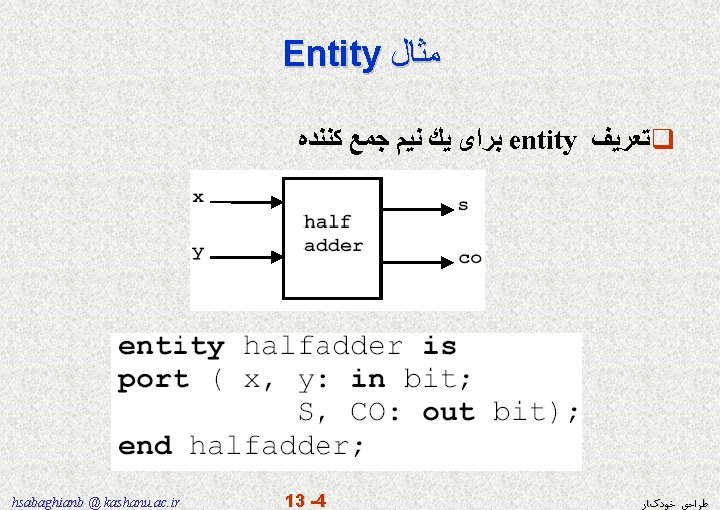

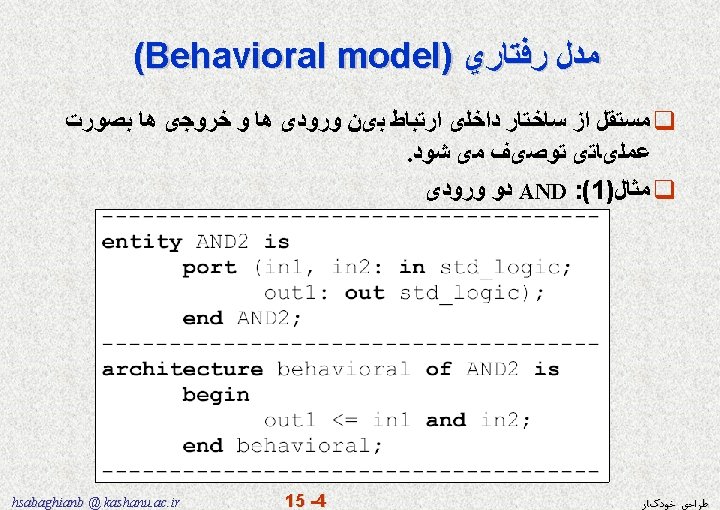

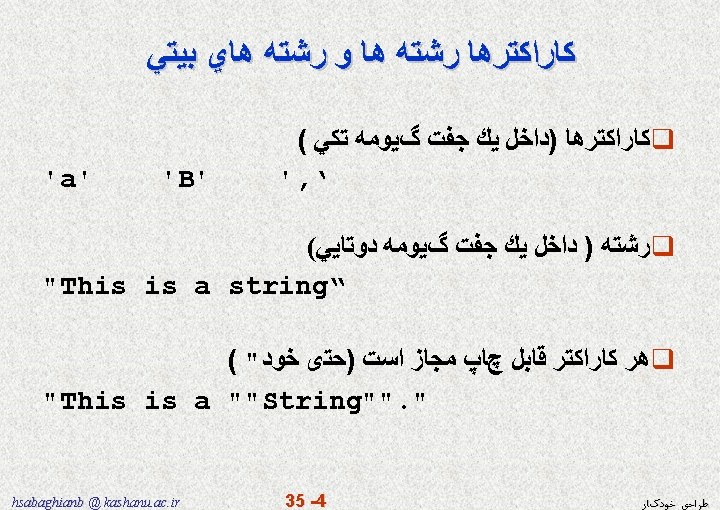

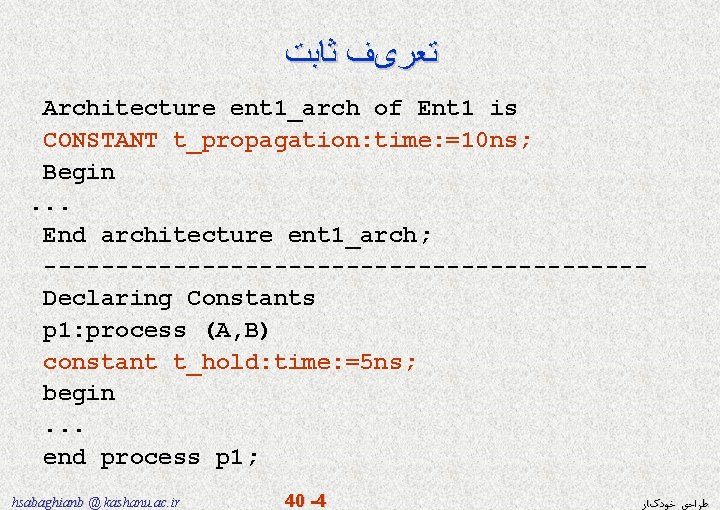

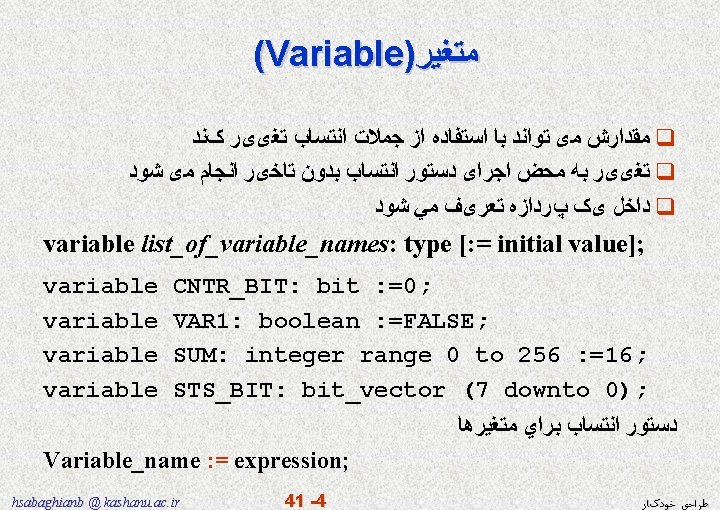

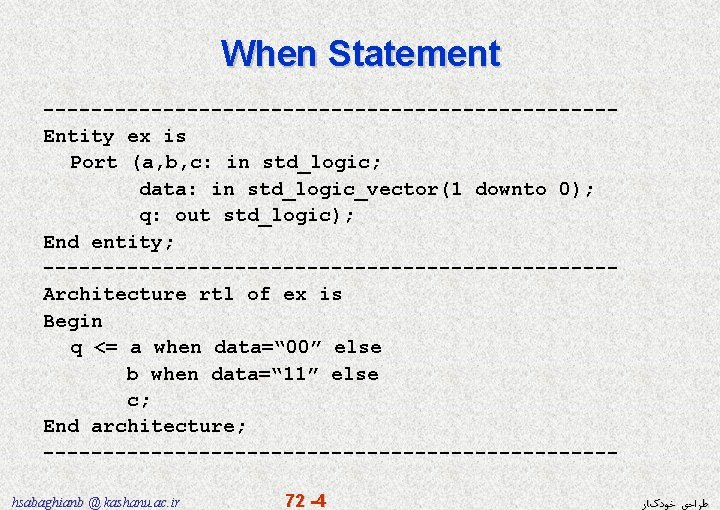

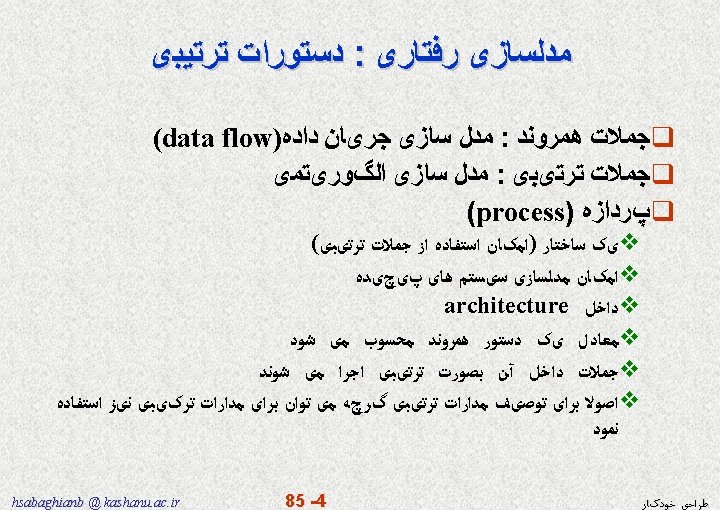

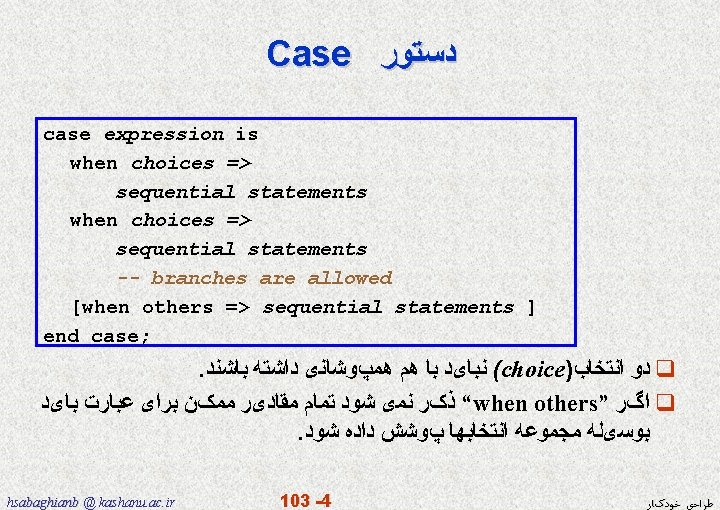

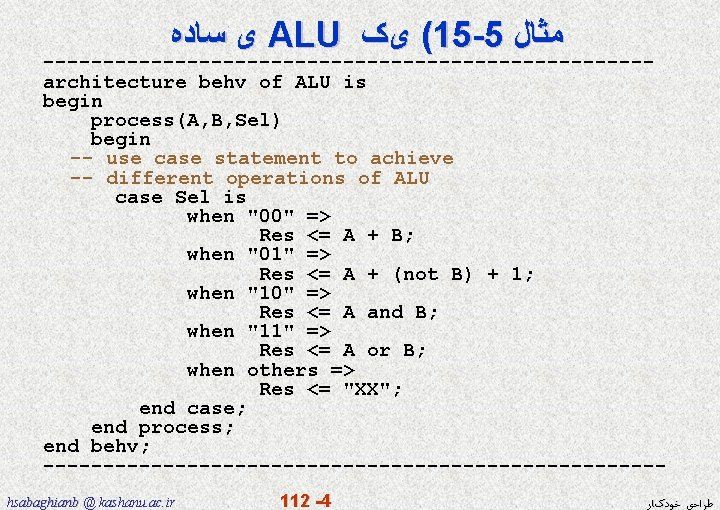

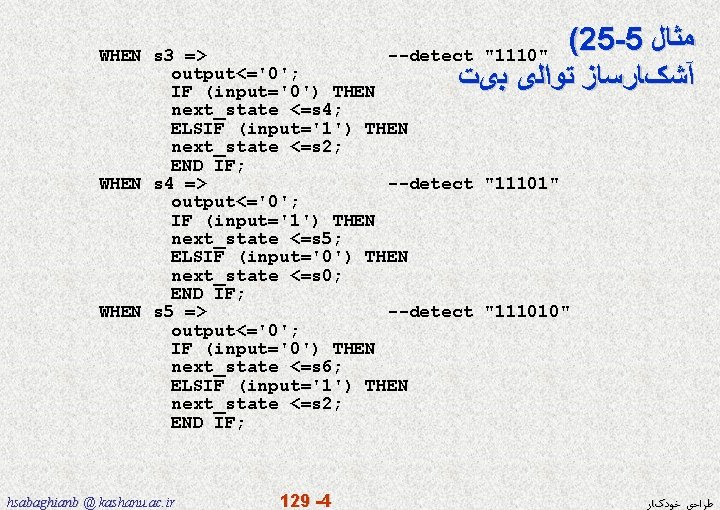

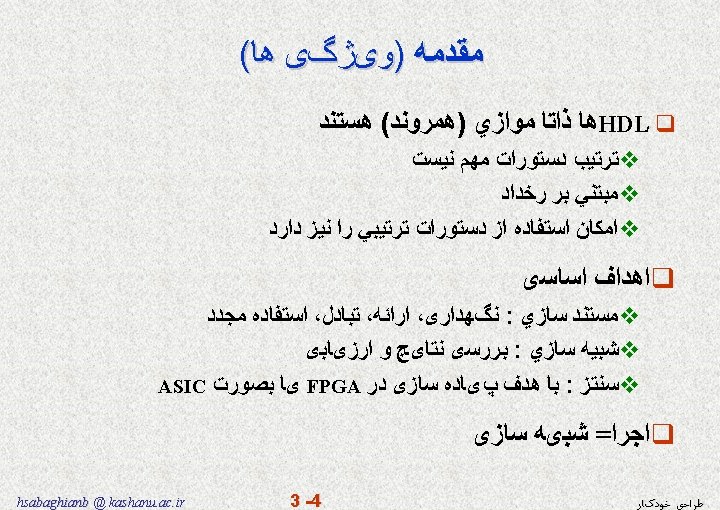

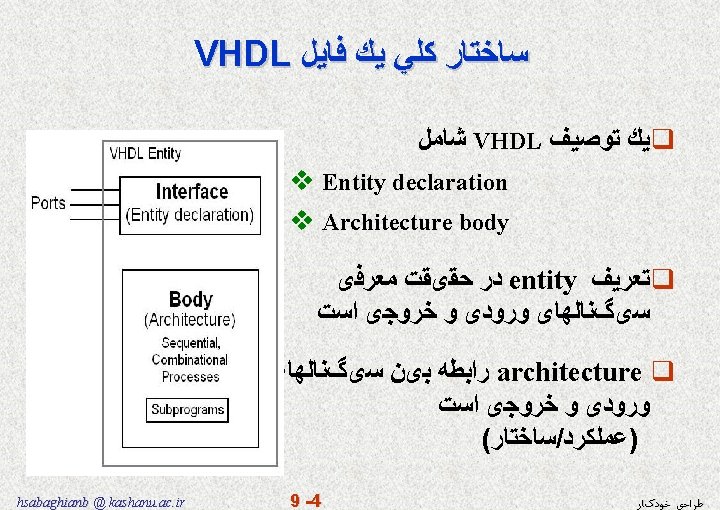

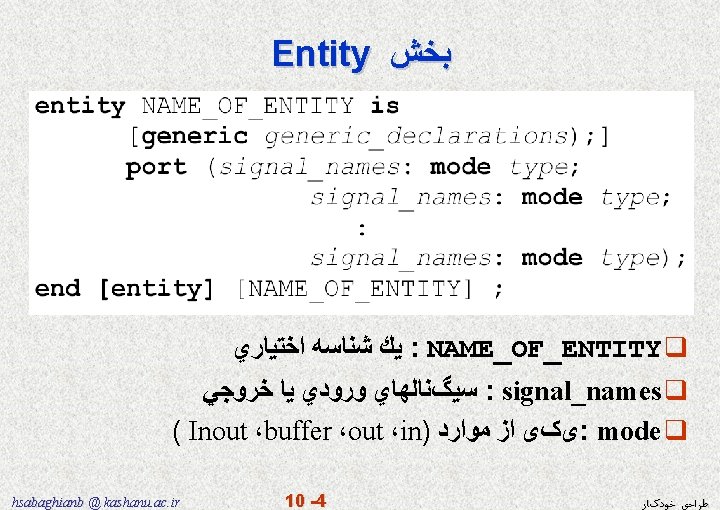

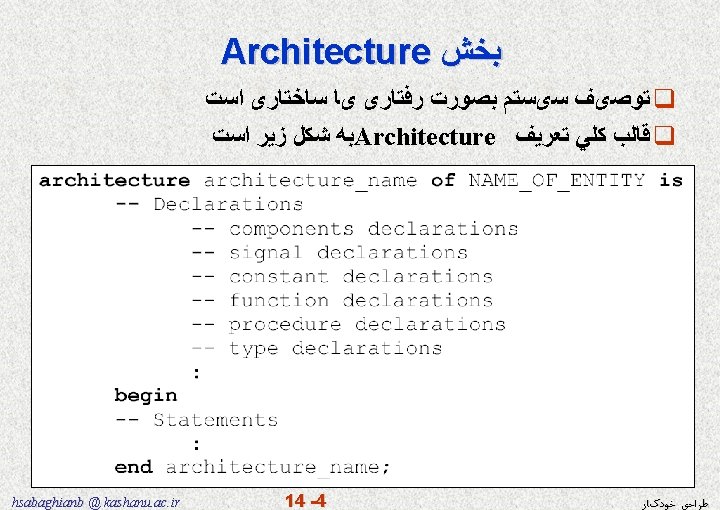

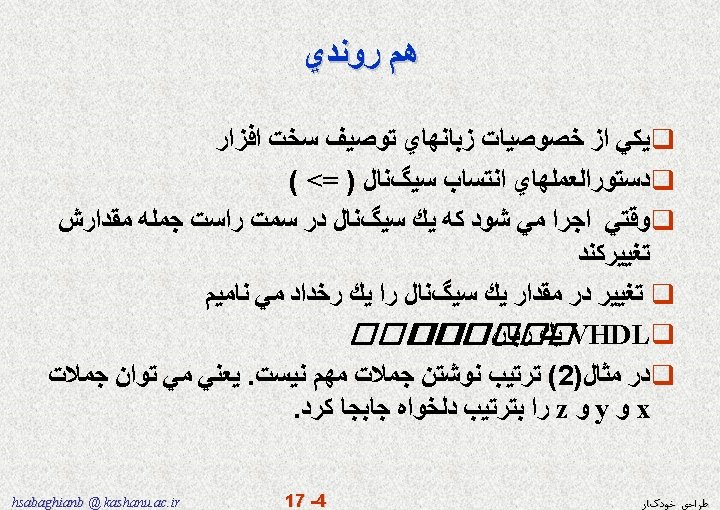

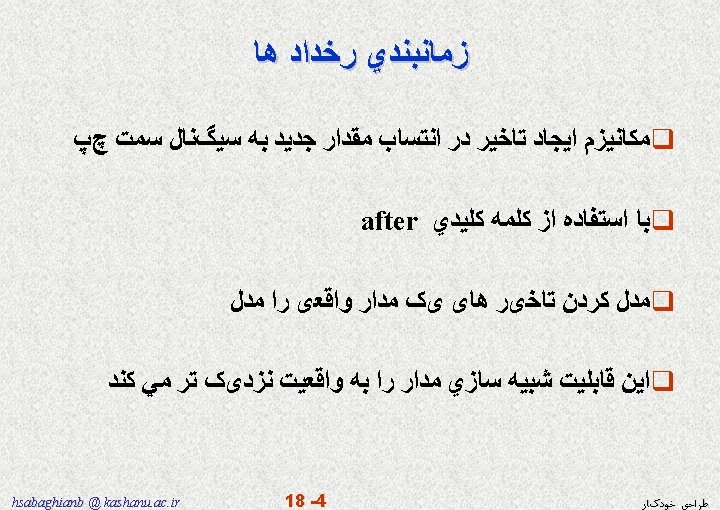

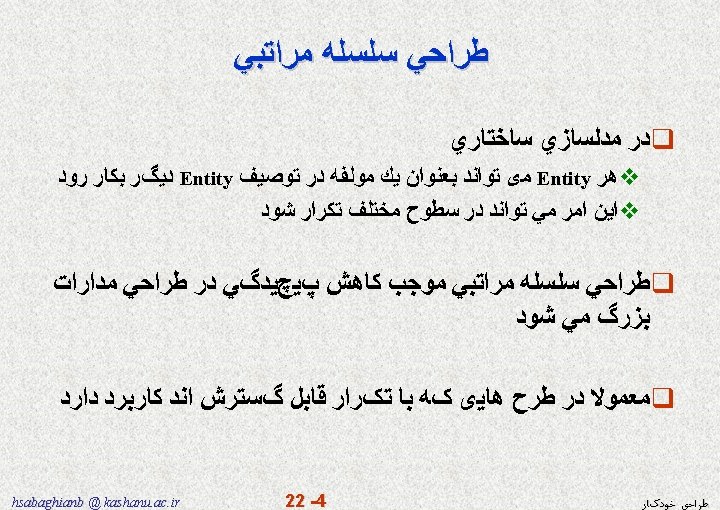

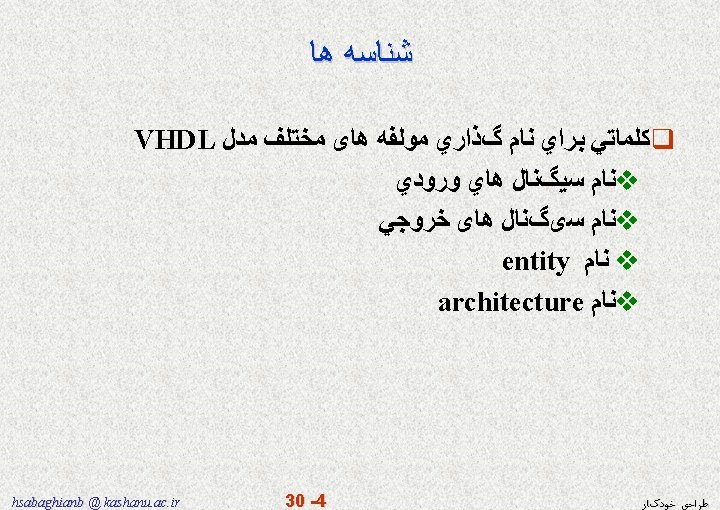

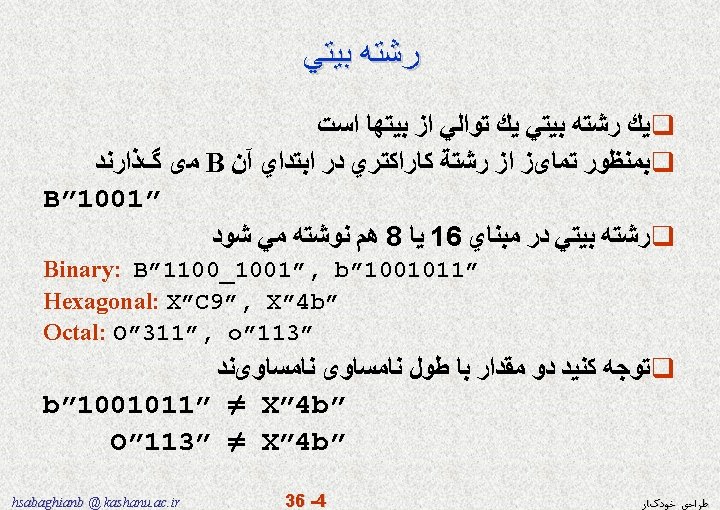

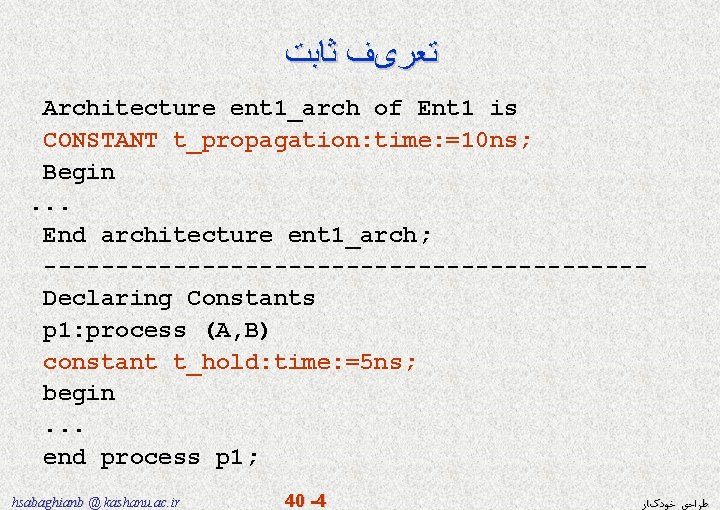

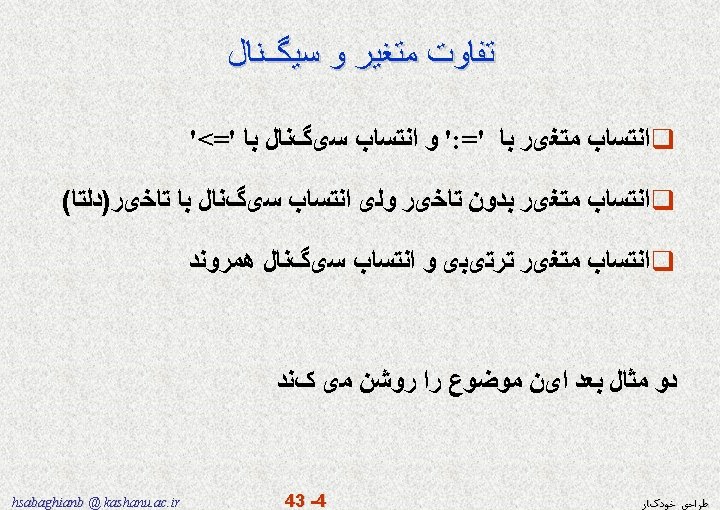

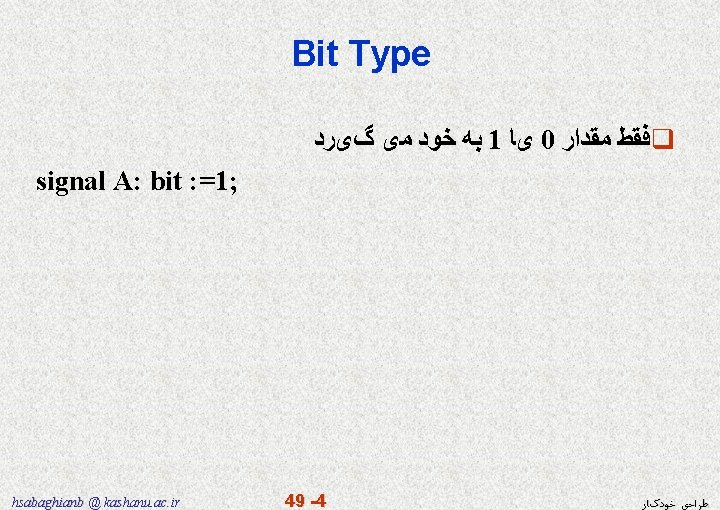

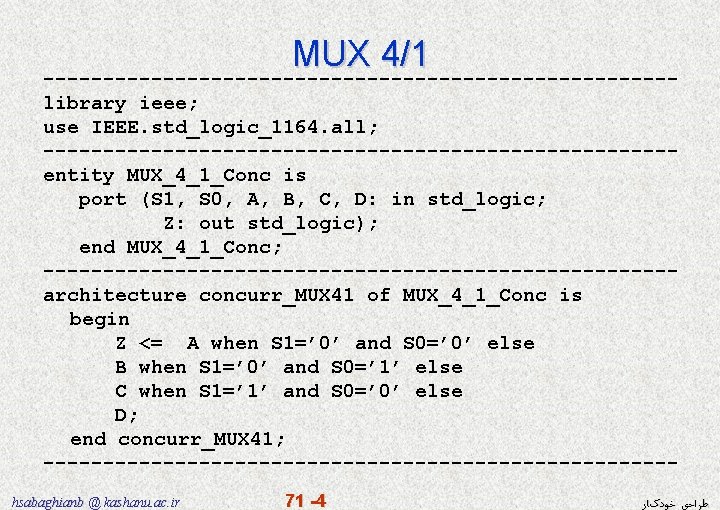

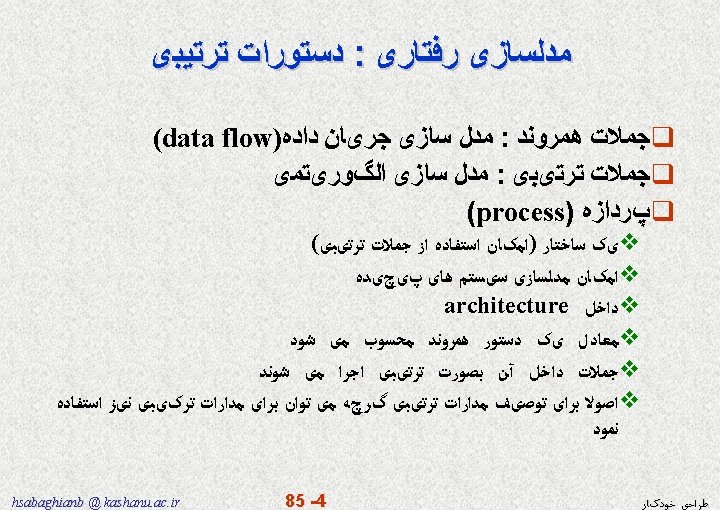

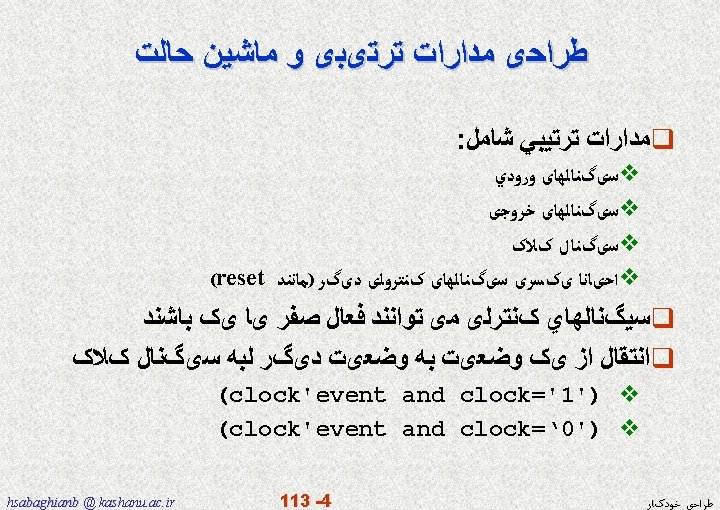

ﻗﺎﻟﺐ کﻠی ﺩﺳﺘﻮﺭ پﺮﺩﺍﺯﻩ [process_label: ] process [ (sensitivity_list) ] [is] [ process_declarations] begin list of sequential statements such as: signal assignments variable assignments case statement exit statement if statement loop statement next statement null statement procedure call wait statement end process [process_label]; hsabaghianb @ kashanu. ac. ir 86 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

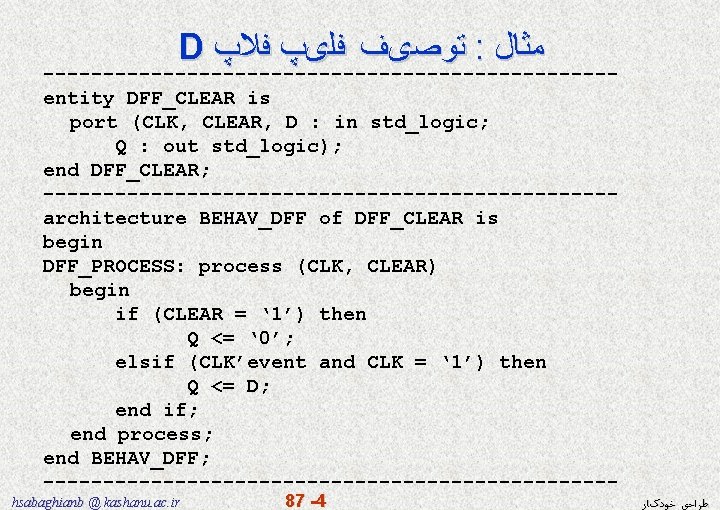

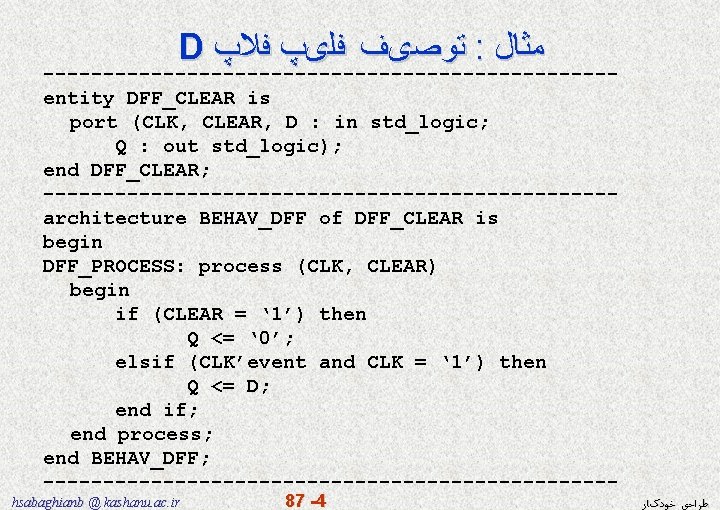

D ﺗﻮﺻیﻒ ﻓﻠیپ ﻓﻼپ : ﻣﺜﺎﻝ ------------------------entity DFF_CLEAR is port (CLK, CLEAR, D : in std_logic; Q : out std_logic); end DFF_CLEAR; ------------------------architecture BEHAV_DFF of DFF_CLEAR is begin DFF_PROCESS: process (CLK, CLEAR) begin if (CLEAR = ‘ 1’) then Q <= ‘ 0’; elsif (CLK’event and CLK = ‘ 1’) then Q <= D; end if; end process; end BEHAV_DFF; ------------------------hsabaghianb @ kashanu. ac. ir 87 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

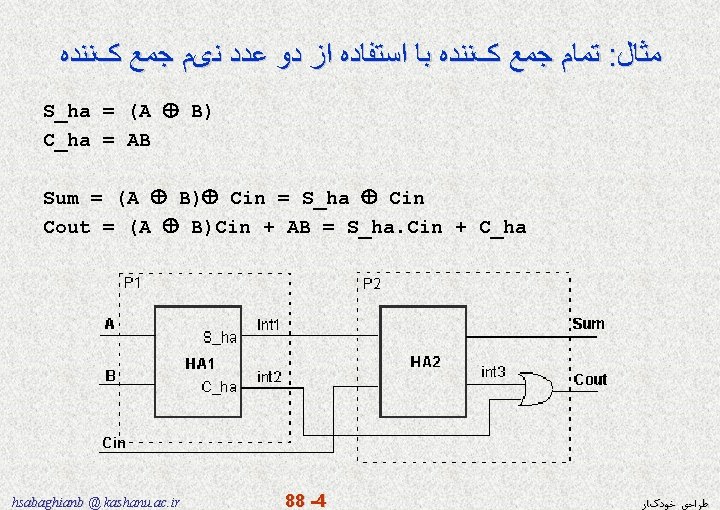

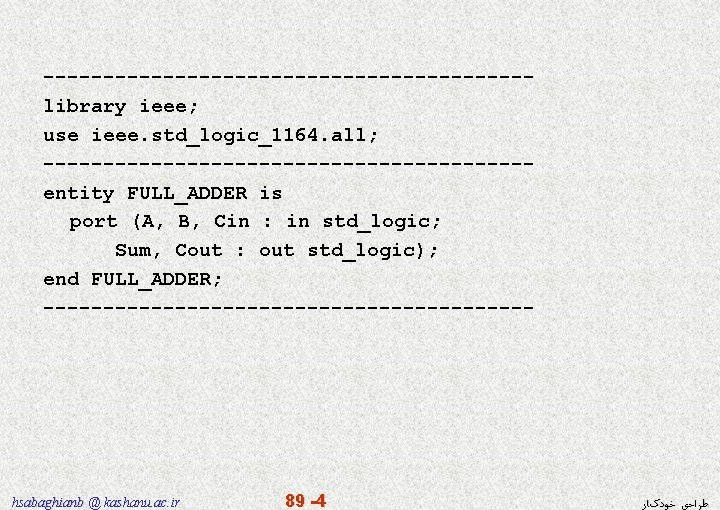

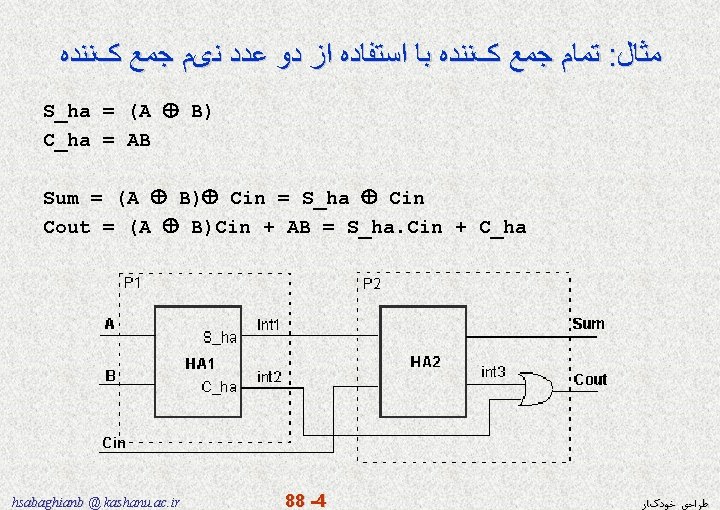

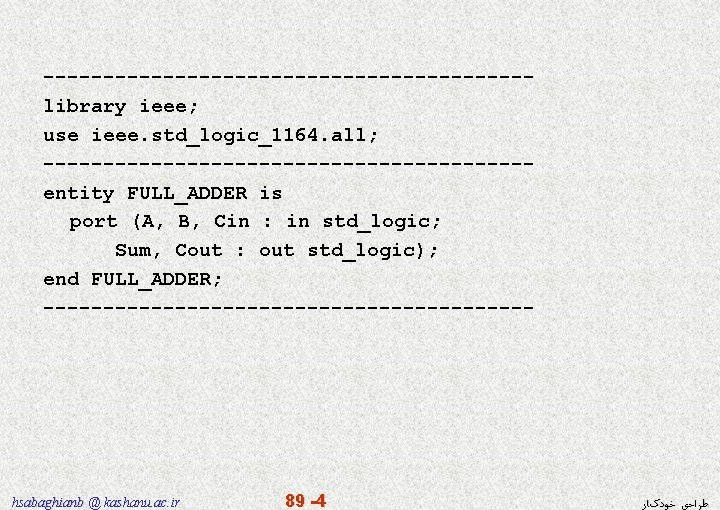

--------------------library ieee; use ieee. std_logic_1164. all; --------------------entity FULL_ADDER is port (A, B, Cin : in std_logic; Sum, Cout : out std_logic); end FULL_ADDER; --------------------- hsabaghianb @ kashanu. ac. ir 89 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

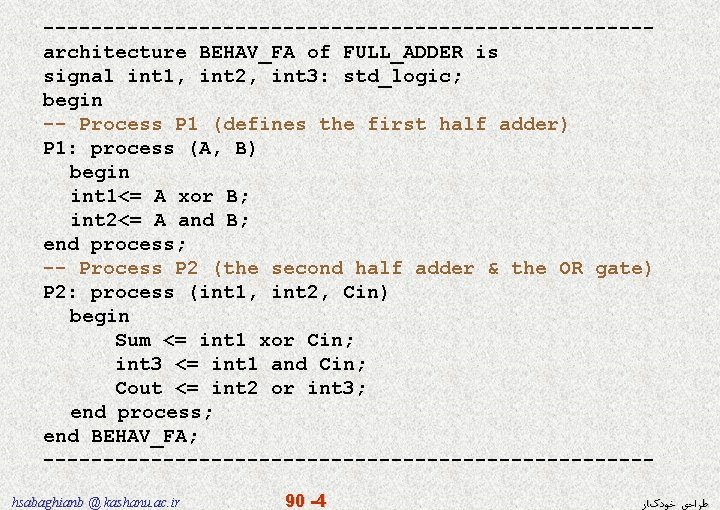

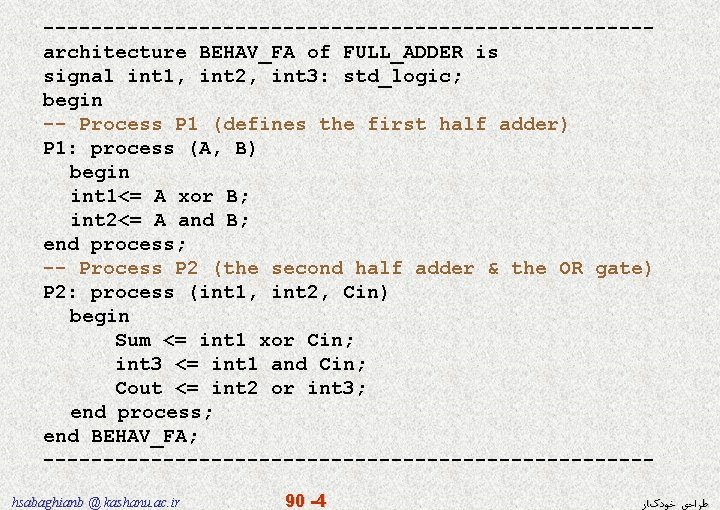

-------------------------architecture BEHAV_FA of FULL_ADDER is signal int 1, int 2, int 3: std_logic; begin -- Process P 1 (defines the first half adder) P 1: process (A, B) begin int 1<= A xor B; int 2<= A and B; end process; -- Process P 2 (the second half adder & the OR gate) P 2: process (int 1, int 2, Cin) begin Sum <= int 1 xor Cin; int 3 <= int 1 and Cin; Cout <= int 2 or int 3; end process; end BEHAV_FA; -------------------------hsabaghianb @ kashanu. ac. ir 90 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

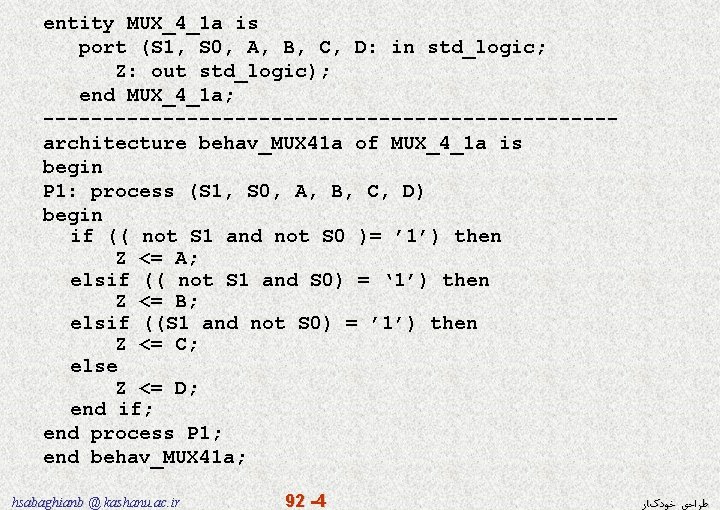

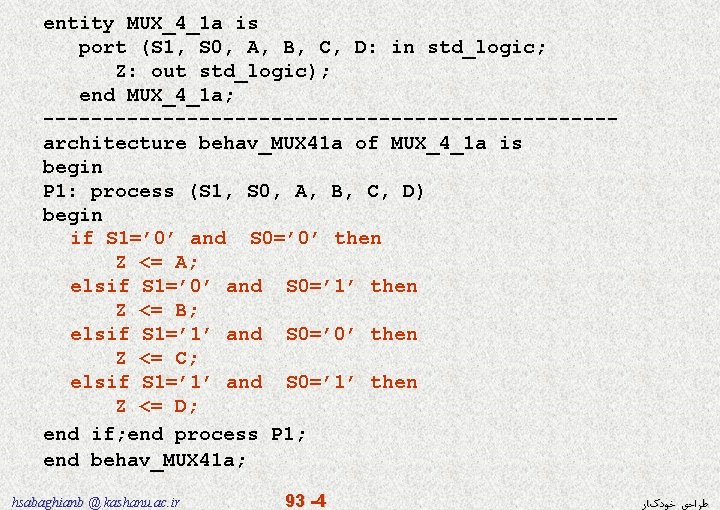

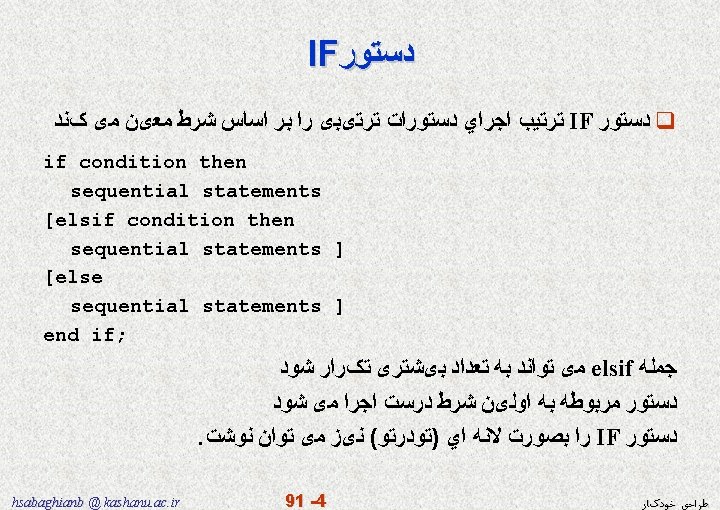

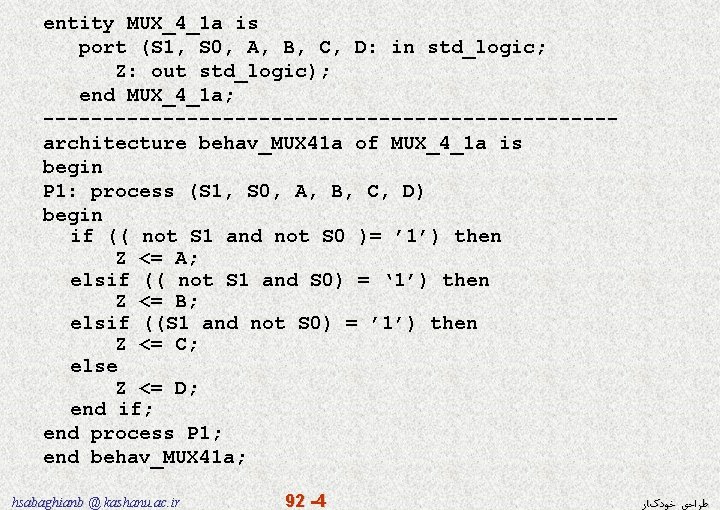

entity MUX_4_1 a is port (S 1, S 0, A, B, C, D: in std_logic; Z: out std_logic); end MUX_4_1 a; ------------------------architecture behav_MUX 41 a of MUX_4_1 a is begin P 1: process (S 1, S 0, A, B, C, D) begin if (( not S 1 and not S 0 )= ’ 1’) then Z <= A; elsif (( not S 1 and S 0) = ‘ 1’) then Z <= B; elsif ((S 1 and not S 0) = ’ 1’) then Z <= C; else Z <= D; end if; end process P 1; end behav_MUX 41 a; hsabaghianb @ kashanu. ac. ir 92 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

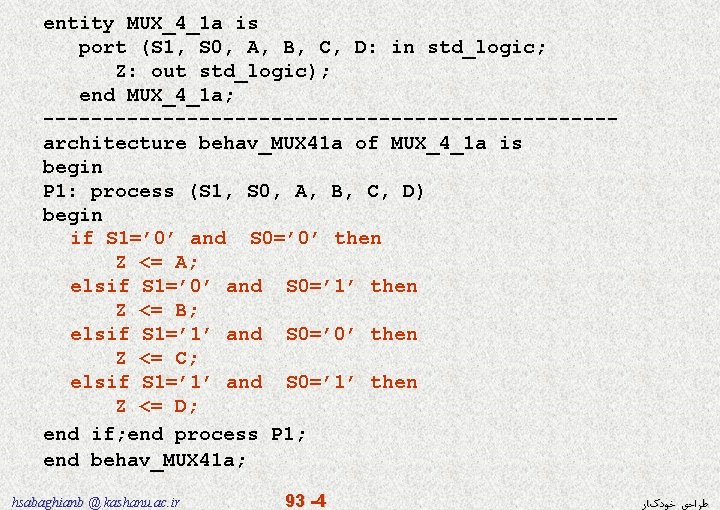

entity MUX_4_1 a is port (S 1, S 0, A, B, C, D: in std_logic; Z: out std_logic); end MUX_4_1 a; ------------------------architecture behav_MUX 41 a of MUX_4_1 a is begin P 1: process (S 1, S 0, A, B, C, D) begin if S 1=’ 0’ and S 0=’ 0’ then Z <= A; elsif S 1=’ 0’ and S 0=’ 1’ then Z <= B; elsif S 1=’ 1’ and S 0=’ 0’ then Z <= C; elsif S 1=’ 1’ and S 0=’ 1’ then Z <= D; end if; end process P 1; end behav_MUX 41 a; hsabaghianb @ kashanu. ac. ir 93 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

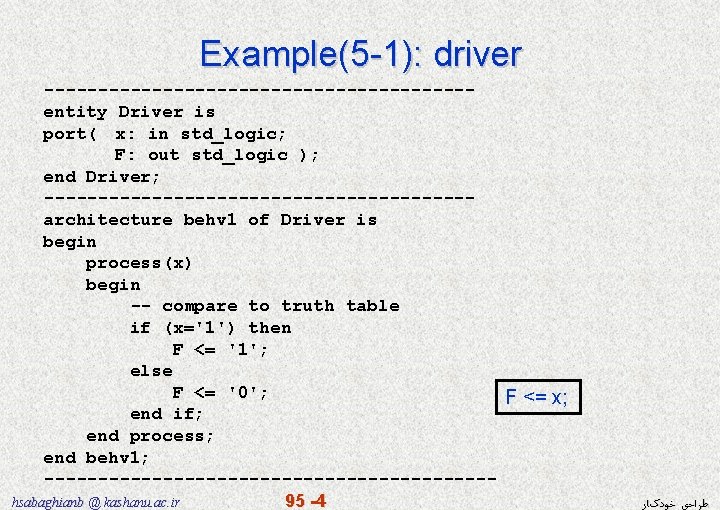

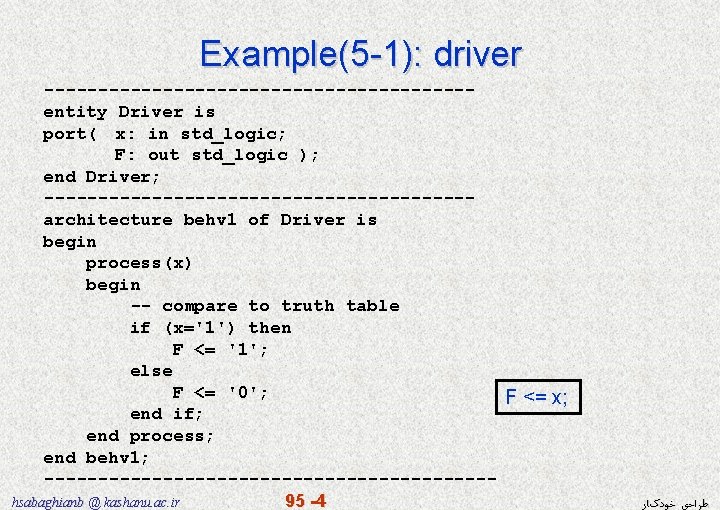

Example(5 -1): driver --------------------entity Driver is port( x: in std_logic; F: out std_logic ); end Driver; --------------------architecture behv 1 of Driver is begin process(x) begin -- compare to truth table if (x='1') then F <= '1'; else F <= '0'; F <= x; end if; end process; end behv 1; ---------------------hsabaghianb @ kashanu. ac. ir 95 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

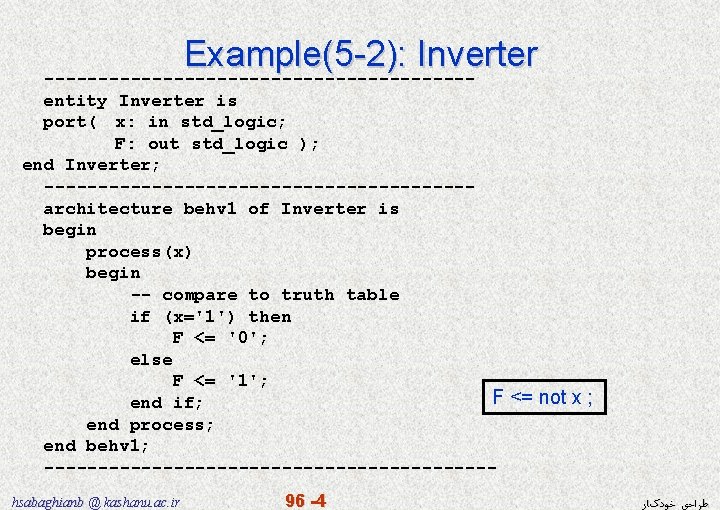

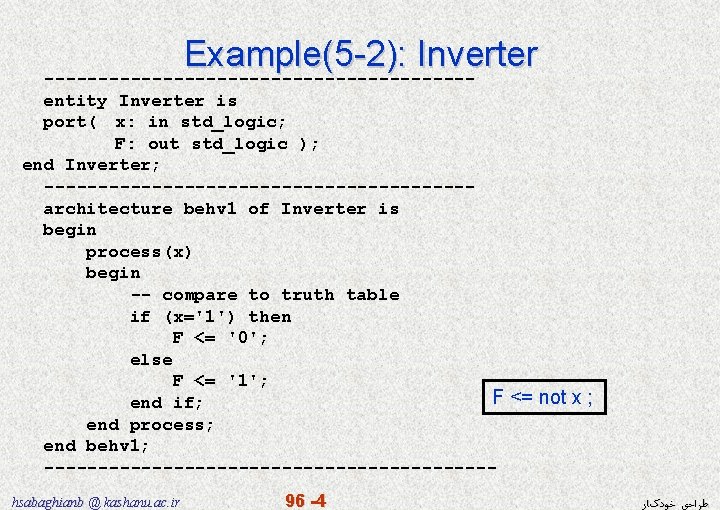

Example(5 -2): Inverter --------------------entity Inverter is port( x: in std_logic; F: out std_logic ); end Inverter; --------------------architecture behv 1 of Inverter is begin process(x) begin -- compare to truth table if (x='1') then F <= '0'; else F <= '1'; F <= not x ; end if; end process; end behv 1; ---------------------hsabaghianb @ kashanu. ac. ir 96 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

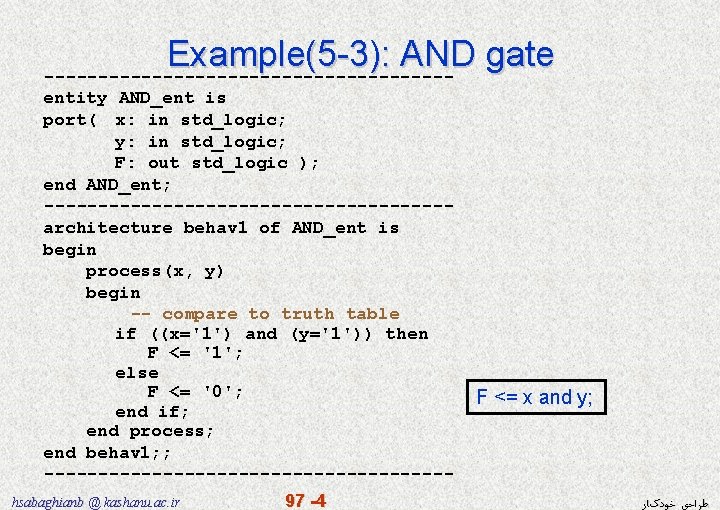

Example(5 -3): AND gate -------------------entity AND_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end AND_ent; -------------------architecture behav 1 of AND_ent is begin process(x, y) begin -- compare to truth table if ((x='1') and (y='1')) then F <= '1'; else F <= '0'; F <= x and y; end if; end process; end behav 1; ; ------------------- hsabaghianb @ kashanu. ac. ir 97 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

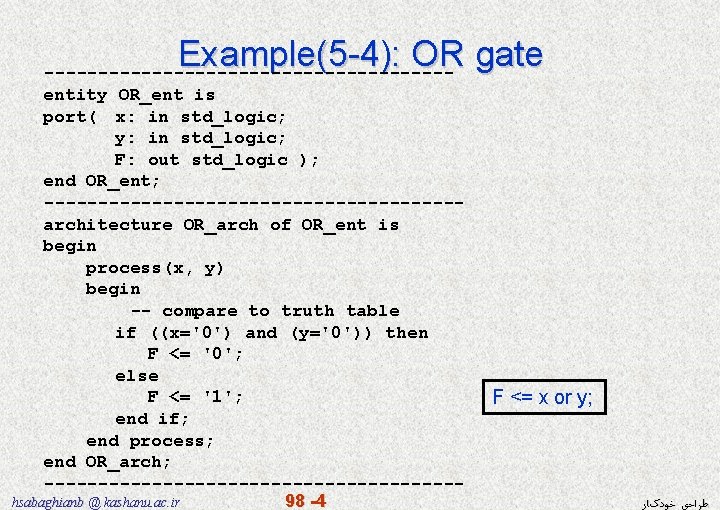

Example(5 -4): OR gate -------------------entity OR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end OR_ent; -------------------architecture OR_arch of OR_ent is begin process(x, y) begin -- compare to truth table if ((x='0') and (y='0')) then F <= '0'; else F <= '1'; end if; end process; end OR_arch; -------------------hsabaghianb @ kashanu. ac. ir 98 -4 F <= x or y; ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

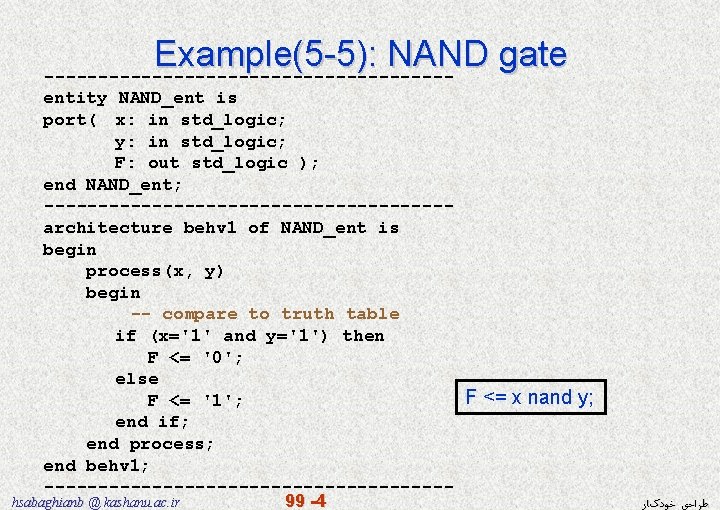

Example(5 -5): NAND gate -------------------entity NAND_ent is port( x: in std_logic; y: in std_logic; F: out std_logic ); end NAND_ent; -------------------architecture behv 1 of NAND_ent is begin process(x, y) begin -- compare to truth table if (x='1' and y='1') then F <= '0'; else F <= x nand y; F <= '1'; end if; end process; end behv 1; -------------------hsabaghianb @ kashanu. ac. ir 99 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

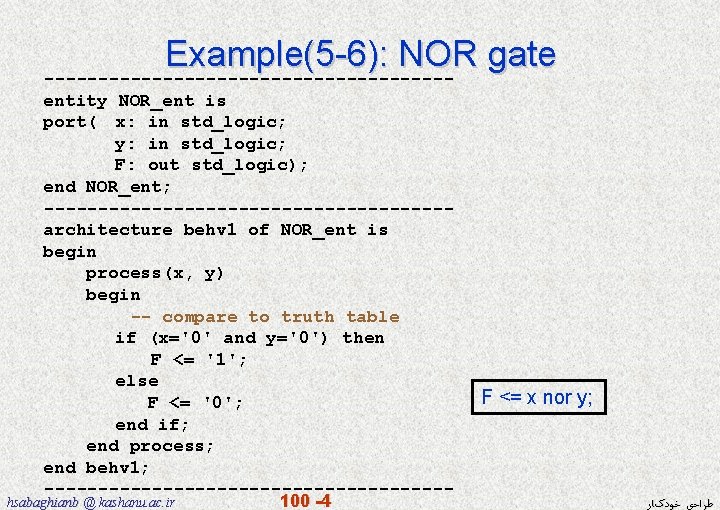

Example(5 -6): NOR gate -------------------entity NOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end NOR_ent; -------------------architecture behv 1 of NOR_ent is begin process(x, y) begin -- compare to truth table if (x='0' and y='0') then F <= '1'; else F <= '0'; end if; end process; end behv 1; -------------------hsabaghianb @ kashanu. ac. ir 100 -4 F <= x nor y; ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

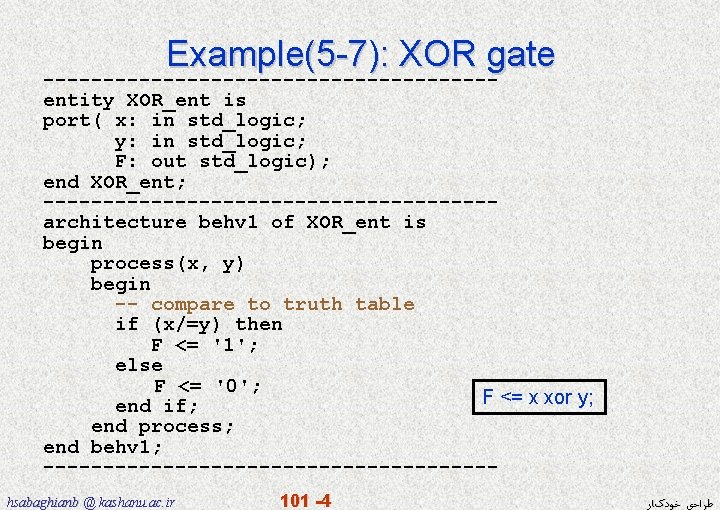

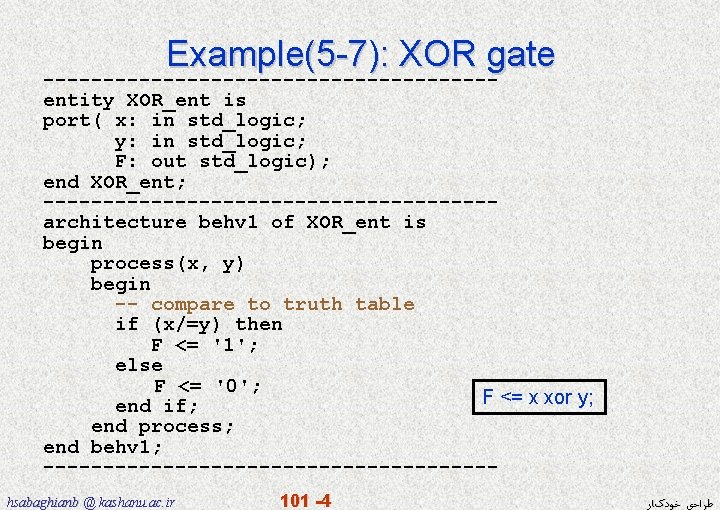

Example(5 -7): XOR gate -------------------entity XOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end XOR_ent; -------------------architecture behv 1 of XOR_ent is begin process(x, y) begin -- compare to truth table if (x/=y) then F <= '1'; else F <= '0'; F <= x xor y; end if; end process; end behv 1; -------------------hsabaghianb @ kashanu. ac. ir 101 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

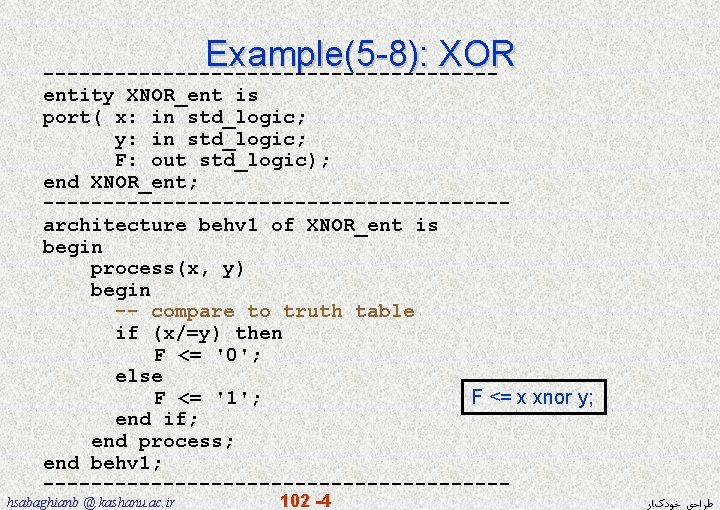

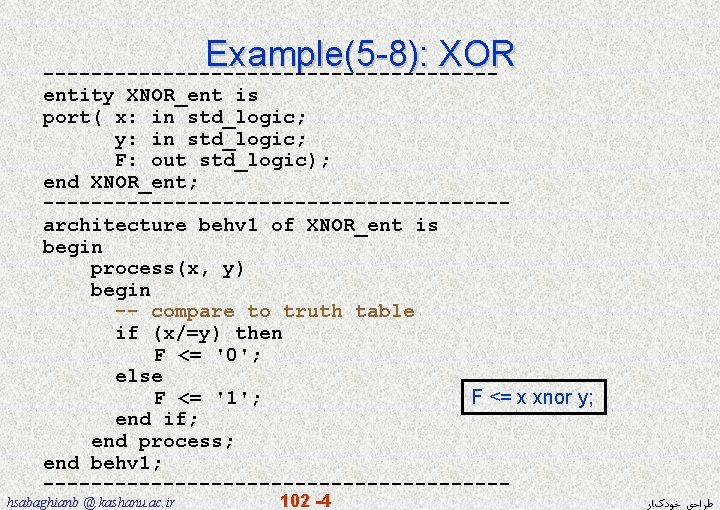

Example(5 -8): XOR ------------------- entity XNOR_ent is port( x: in std_logic; y: in std_logic; F: out std_logic); end XNOR_ent; -------------------architecture behv 1 of XNOR_ent is begin process(x, y) begin -- compare to truth table if (x/=y) then F <= '0'; else F <= '1'; F <= x xnor y; end if; end process; end behv 1; -------------------- hsabaghianb @ kashanu. ac. ir 102 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

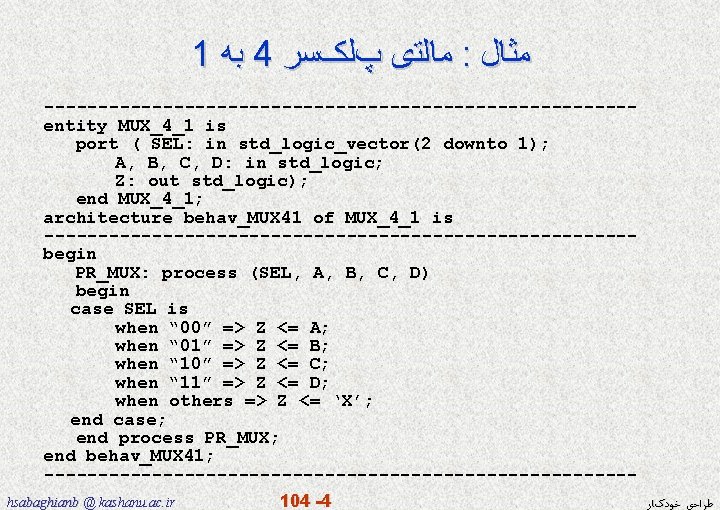

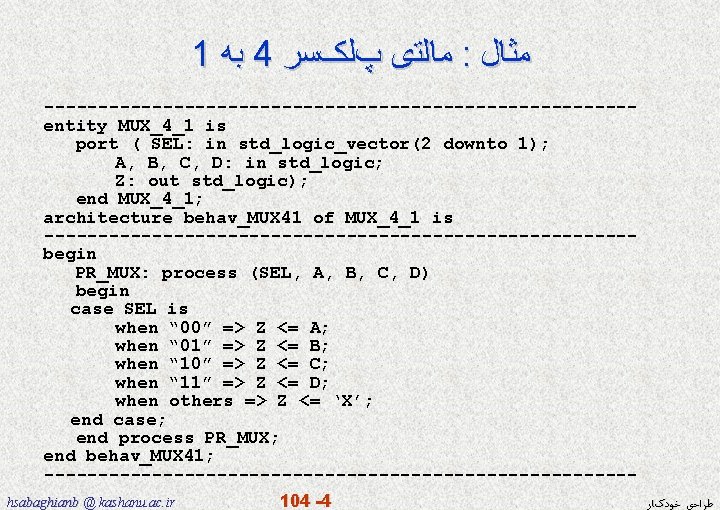

1 ﺑﻪ 4 ﻣﺎﻟﺘی پﻠکﺴﺮ : ﻣﺜﺎﻝ ---------------------------entity MUX_4_1 is port ( SEL: in std_logic_vector(2 downto 1); A, B, C, D: in std_logic; Z: out std_logic); end MUX_4_1; architecture behav_MUX 41 of MUX_4_1 is ---------------------------begin PR_MUX: process (SEL, A, B, C, D) begin case SEL is when “ 00” => Z <= A; when “ 01” => Z <= B; when “ 10” => Z <= C; when “ 11” => Z <= D; when others => Z <= ‘X’; end case; end process PR_MUX; end behav_MUX 41; ---------------------------hsabaghianb @ kashanu. ac. ir 104 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

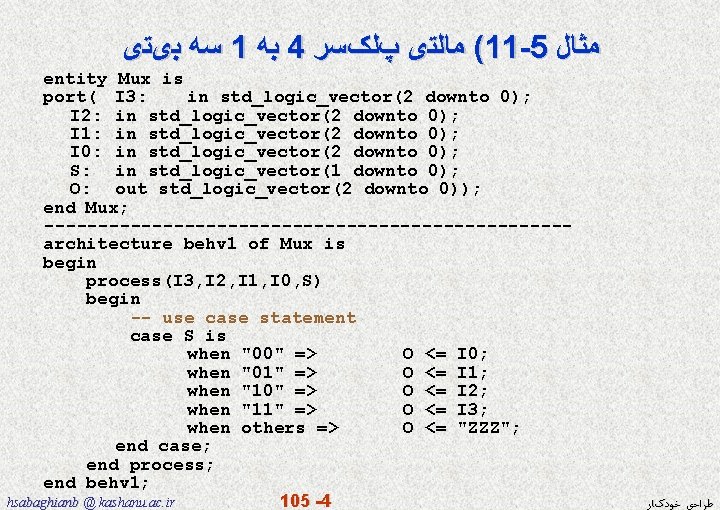

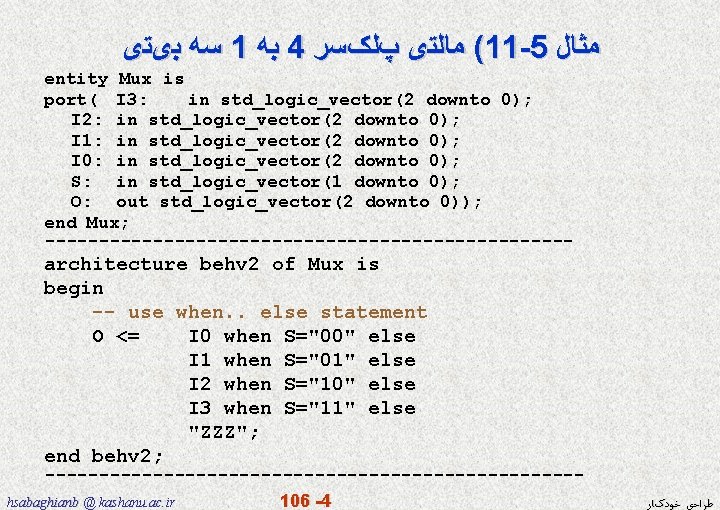

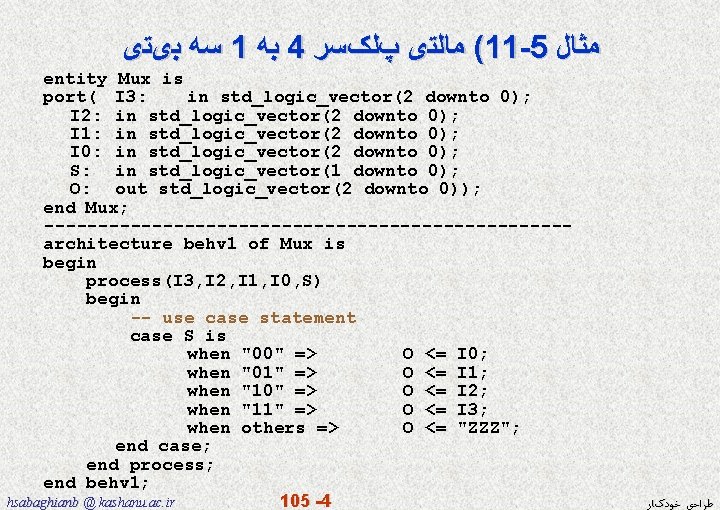

ﺑیﺘی ﺳﻪ 1 ﺑﻪ 4 پﻠکﺴﺮ ﻣﺎﻟﺘی (11 -5 ﻣﺜﺎﻝ entity Mux is port( I 3: in std_logic_vector(2 downto 0); I 2: in std_logic_vector(2 downto 0); I 1: in std_logic_vector(2 downto 0); I 0: in std_logic_vector(2 downto 0); S: in std_logic_vector(1 downto 0); O: out std_logic_vector(2 downto 0)); end Mux; ------------------------architecture behv 1 of Mux is begin process(I 3, I 2, I 1, I 0, S) begin -- use case statement case S is when "00" => O <= I 0; when "01" => O <= I 1; when "10" => O <= I 2; when "11" => O <= I 3; when others => O <= "ZZZ"; end case; end process; end behv 1; hsabaghianb @ kashanu. ac. ir 105 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

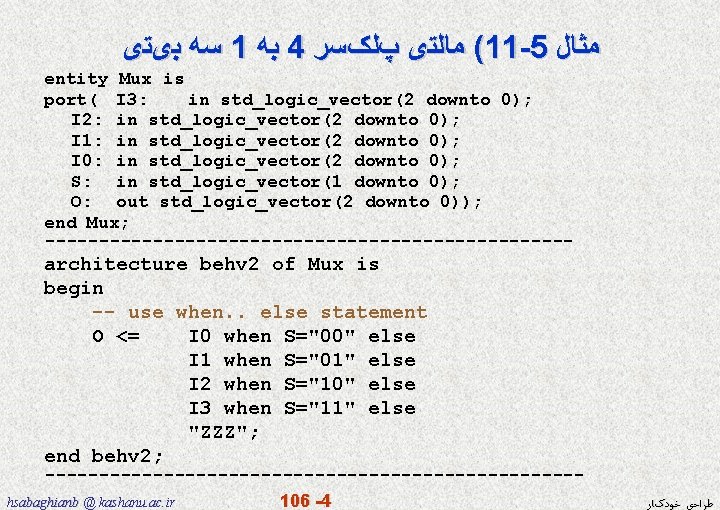

ﺑیﺘی ﺳﻪ 1 ﺑﻪ 4 پﻠکﺴﺮ ﻣﺎﻟﺘی (11 -5 ﻣﺜﺎﻝ entity Mux is port( I 3: in std_logic_vector(2 downto 0); I 2: in std_logic_vector(2 downto 0); I 1: in std_logic_vector(2 downto 0); I 0: in std_logic_vector(2 downto 0); S: in std_logic_vector(1 downto 0); O: out std_logic_vector(2 downto 0)); end Mux; ------------------------- architecture behv 2 of Mux is begin -- use when. . else statement O <= I 0 when S="00" else I 1 when S="01" else I 2 when S="10" else I 3 when S="11" else "ZZZ"; end behv 2; -------------------------hsabaghianb @ kashanu. ac. ir 106 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

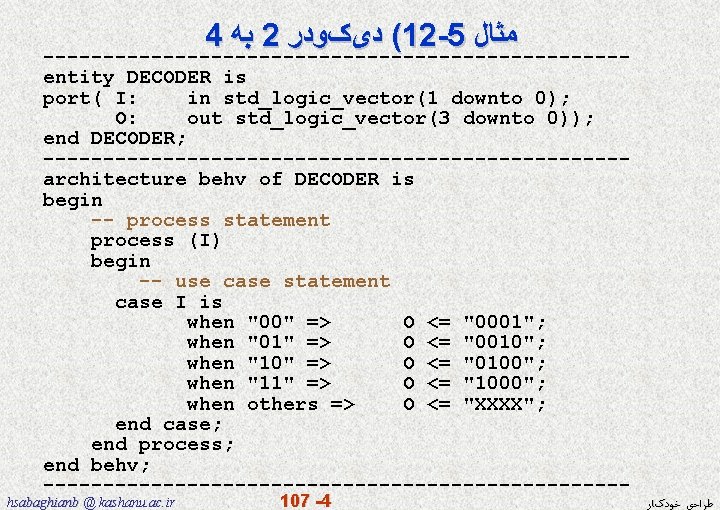

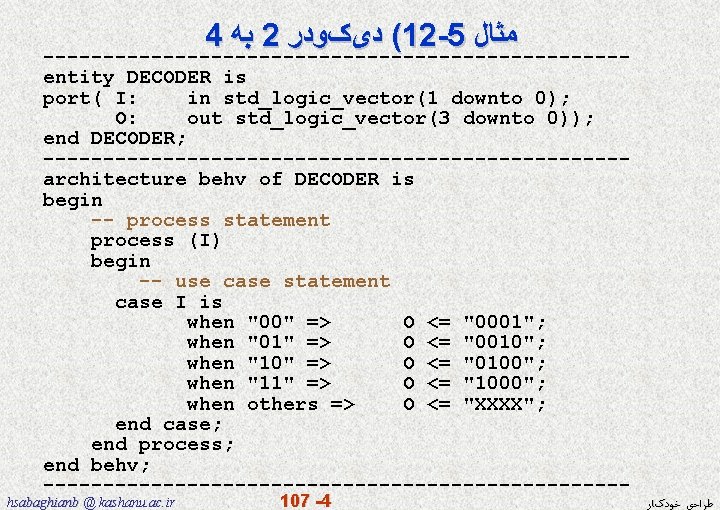

4 ﺑﻪ 2 ﺩیکﻮﺩﺭ (12 -5 ﻣﺜﺎﻝ ------------------------entity DECODER is port( I: in std_logic_vector(1 downto 0); O: out std_logic_vector(3 downto 0)); end DECODER; ------------------------architecture behv of DECODER is begin -- process statement process (I) begin -- use case statement case I is when "00" => O <= "0001"; when "01" => O <= "0010"; when "10" => O <= "0100"; when "11" => O <= "1000"; when others => O <= "XXXX"; end case; end process; end behv; ------------------------- hsabaghianb @ kashanu. ac. ir 107 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

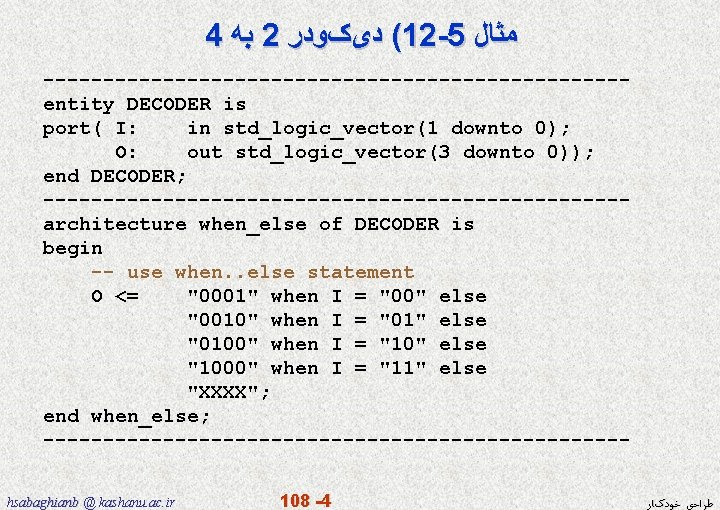

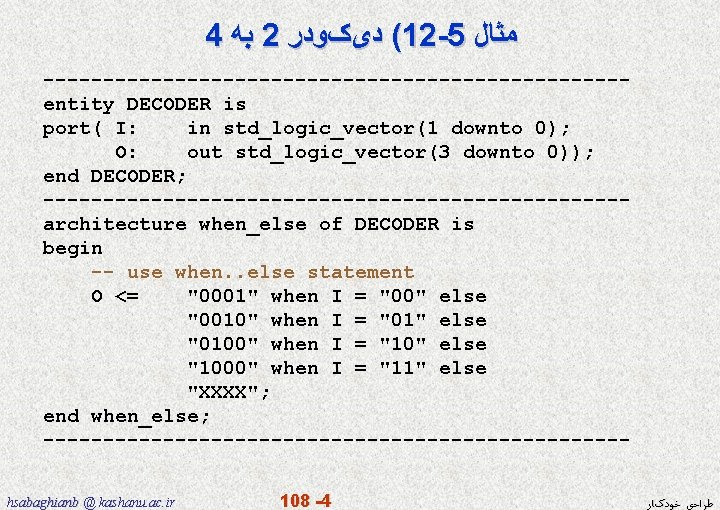

4 ﺑﻪ 2 ﺩیکﻮﺩﺭ (12 -5 ﻣﺜﺎﻝ ------------------------entity DECODER is port( I: in std_logic_vector(1 downto 0); O: out std_logic_vector(3 downto 0)); end DECODER; ------------------------architecture when_else of DECODER is begin -- use when. . else statement O <= "0001" when I = "00" else "0010" when I = "01" else "0100" when I = "10" else "1000" when I = "11" else "XXXX"; end when_else; ------------------------hsabaghianb @ kashanu. ac. ir 108 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

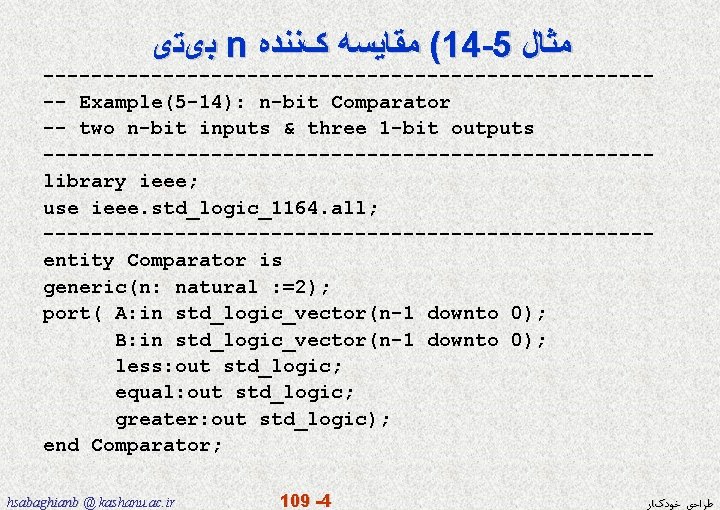

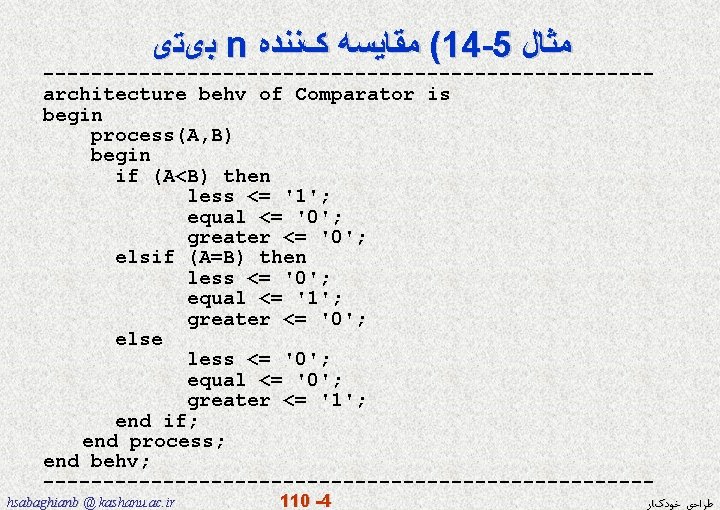

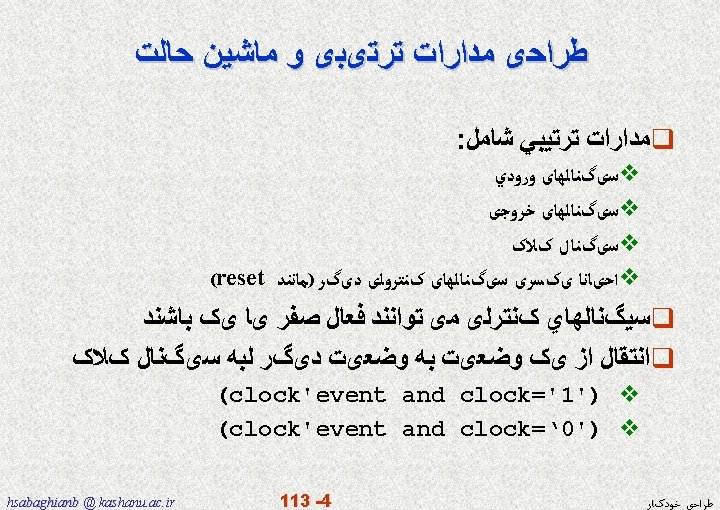

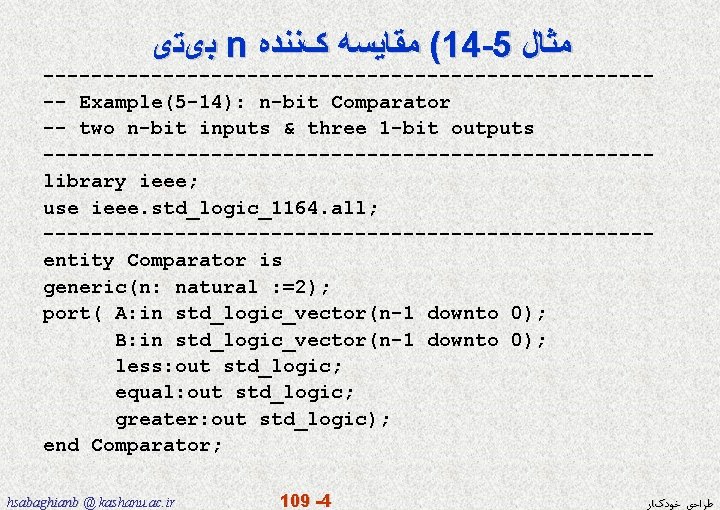

ﺑیﺘی n کﻨﻨﺪﻩ ﻣﻘﺎﻳﺴﻪ (14 -5 ﻣﺜﺎﻝ -------------------------- Example(5 -14): n-bit Comparator -- two n-bit inputs & three 1 -bit outputs -------------------------library ieee; use ieee. std_logic_1164. all; -------------------------entity Comparator is generic(n: natural : =2); port( A: in std_logic_vector(n-1 downto 0); B: in std_logic_vector(n-1 downto 0); less: out std_logic; equal: out std_logic; greater: out std_logic); end Comparator; hsabaghianb @ kashanu. ac. ir 109 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

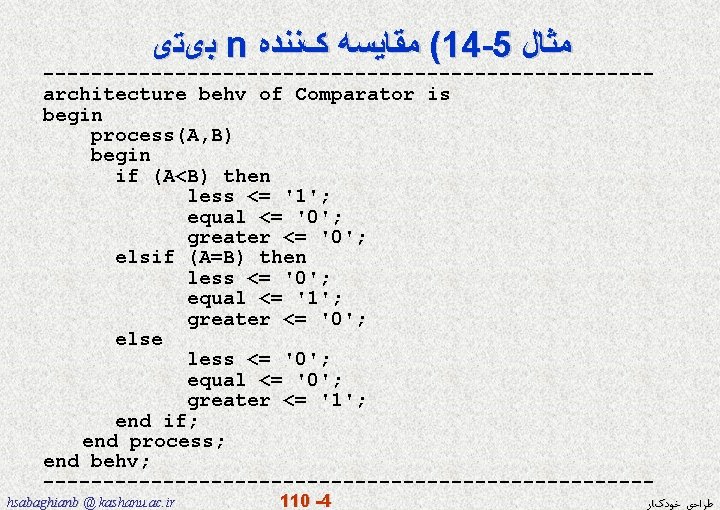

ﺑیﺘی n کﻨﻨﺪﻩ ﻣﻘﺎﻳﺴﻪ (14 -5 ﻣﺜﺎﻝ -------------------------architecture behv of Comparator is begin process(A, B) begin if (A<B) then less <= '1'; equal <= '0'; greater <= '0'; elsif (A=B) then less <= '0'; equal <= '1'; greater <= '0'; else less <= '0'; equal <= '0'; greater <= '1'; end if; end process; end behv; -------------------------hsabaghianb @ kashanu. ac. ir 110 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

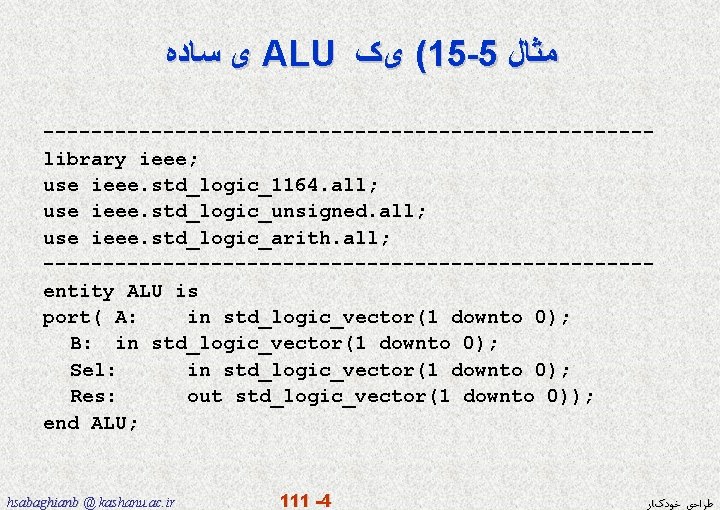

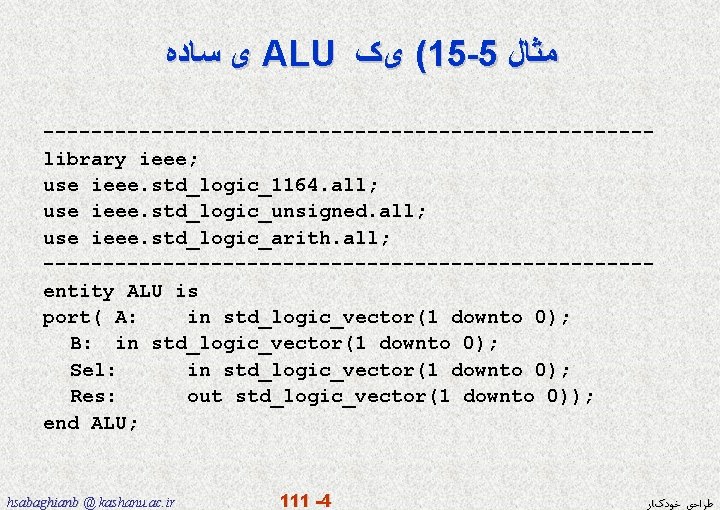

ﺳﺎﺩﻩ ی ALU یک (15 -5 ﻣﺜﺎﻝ -------------------------library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. std_logic_arith. all; -------------------------entity ALU is port( A: in std_logic_vector(1 downto 0); B: in std_logic_vector(1 downto 0); Sel: in std_logic_vector(1 downto 0); Res: out std_logic_vector(1 downto 0)); end ALU; hsabaghianb @ kashanu. ac. ir 111 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

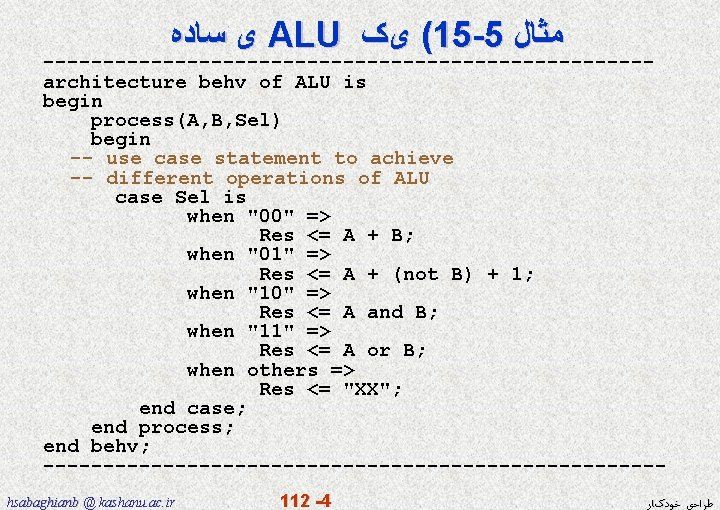

ﺳﺎﺩﻩ ی ALU یک (15 -5 ﻣﺜﺎﻝ -------------------------architecture behv of ALU is begin process(A, B, Sel) begin -- use case statement to achieve -- different operations of ALU case Sel is when "00" => Res <= A + B; when "01" => Res <= A + (not B) + 1; when "10" => Res <= A and B; when "11" => Res <= A or B; when others => Res <= "XX"; end case; end process; end behv; --------------------------hsabaghianb @ kashanu. ac. ir 112 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

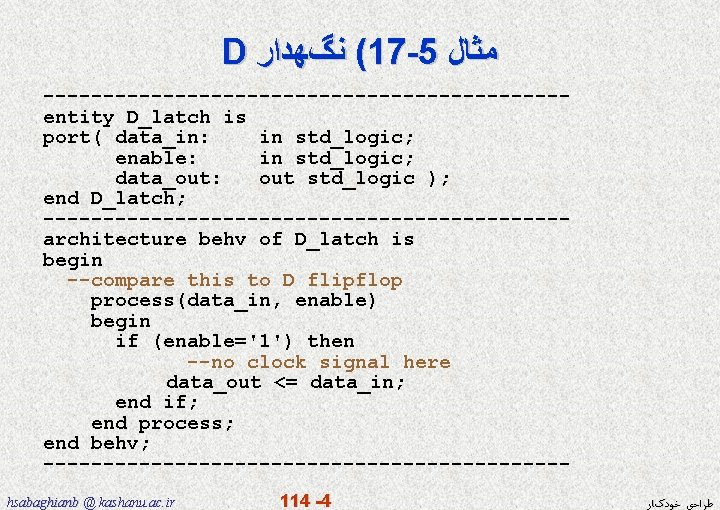

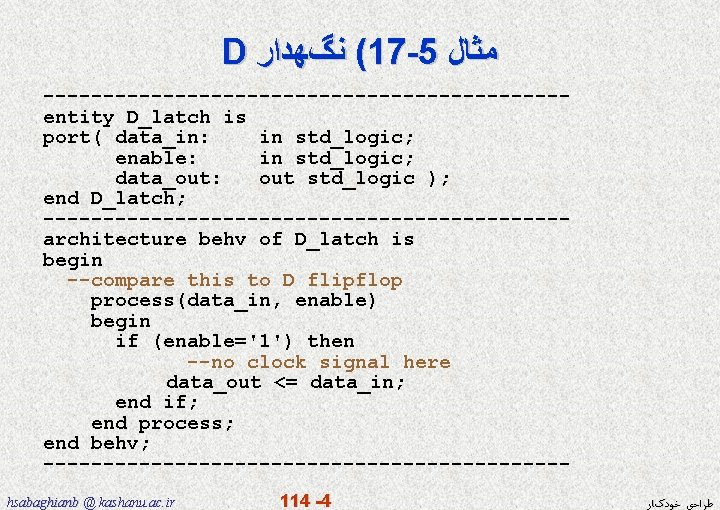

D ﻧگﻬﺪﺍﺭ (17 -5 ﻣﺜﺎﻝ ----------------------entity D_latch is port( data_in: in std_logic; enable: in std_logic; data_out: out std_logic ); end D_latch; ----------------------architecture behv of D_latch is begin --compare this to D flipflop process(data_in, enable) begin if (enable='1') then --no clock signal here data_out <= data_in; end if; end process; end behv; ----------------------hsabaghianb @ kashanu. ac. ir 114 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

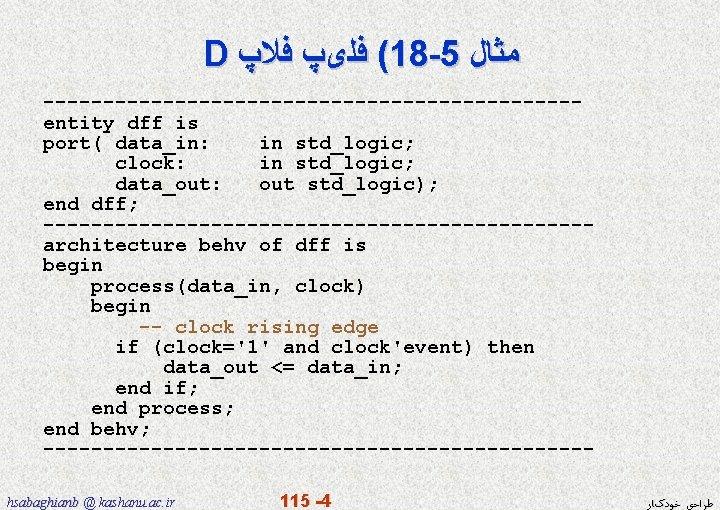

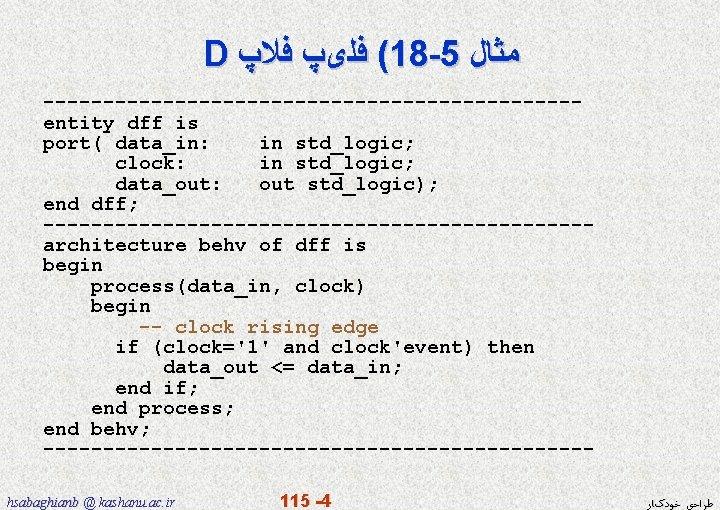

D ﻓﻼپ ﻓﻠیپ (18 -5 ﻣﺜﺎﻝ ----------------------entity dff is port( data_in: in std_logic; clock: in std_logic; data_out: out std_logic); end dff; -----------------------architecture behv of dff is begin process(data_in, clock) begin -- clock rising edge if (clock='1' and clock'event) then data_out <= data_in; end if; end process; end behv; -----------------------hsabaghianb @ kashanu. ac. ir 115 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

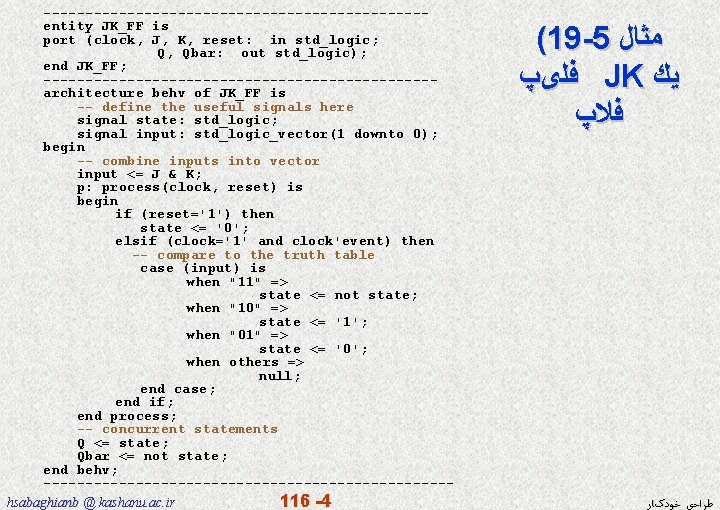

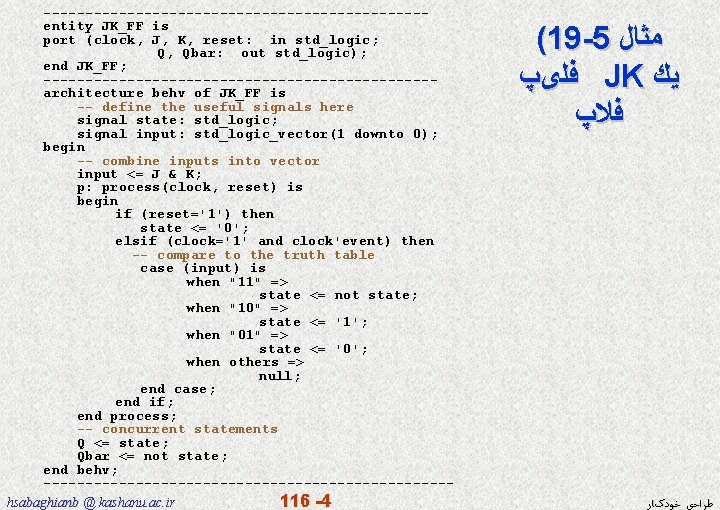

-----------------------entity JK_FF is port (clock, J, K, reset: in std_logic; Q, Qbar: out std_logic); end JK_FF; -----------------------architecture behv of JK_FF is -- define the useful signals here signal state: std_logic; signal input: std_logic_vector(1 downto 0); begin -- combine inputs into vector input <= J & K; p: process(clock, reset) is begin if (reset='1') then state <= '0'; elsif (clock='1' and clock'event) then -- compare to the truth table case (input) is when "11" => state <= not state; when "10" => state <= '1'; when "01" => state <= '0'; when others => null; end case; end if; end process; -- concurrent statements Q <= state; Qbar <= not state; end behv; ------------------------hsabaghianb @ kashanu. ac. ir 116 -4 (19 -5 ﻣﺜﺎﻝ ﻓﻠیپ JK ﻳﻚ ﻓﻼپ ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

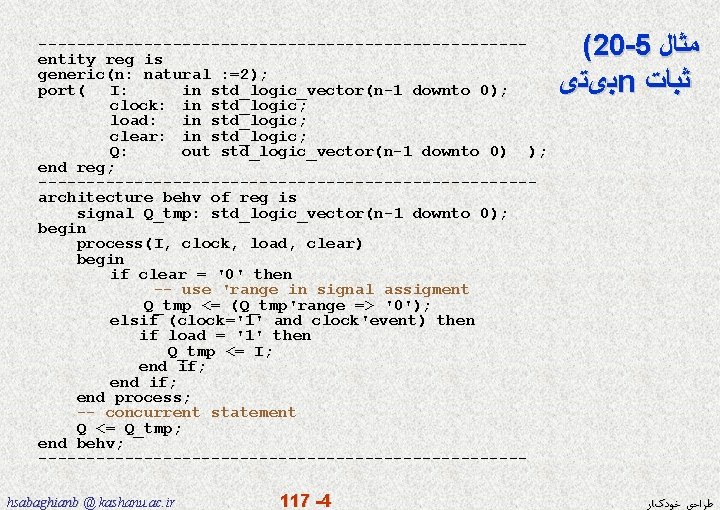

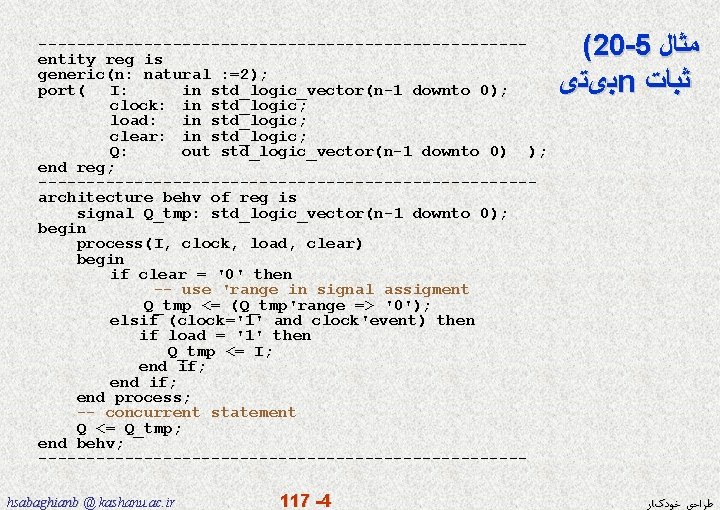

-------------------------entity reg is generic(n: natural : =2); port( I: in std_logic_vector(n-1 downto 0); clock: in std_logic; load: in std_logic; clear: in std_logic; Q: out std_logic_vector(n-1 downto 0) ); end reg; --------------------------architecture behv of reg is signal Q_tmp: std_logic_vector(n-1 downto 0); begin process(I, clock, load, clear) begin if clear = '0' then -- use 'range in signal assigment Q_tmp <= (Q_tmp'range => '0'); elsif (clock='1' and clock'event) then if load = '1' then Q_tmp <= I; end if; end process; -- concurrent statement Q <= Q_tmp; end behv; -------------------------hsabaghianb @ kashanu. ac. ir 117 -4 (20 -5 ﻣﺜﺎﻝ ﺑیﺘی n ﺛﺒﺎﺕ ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

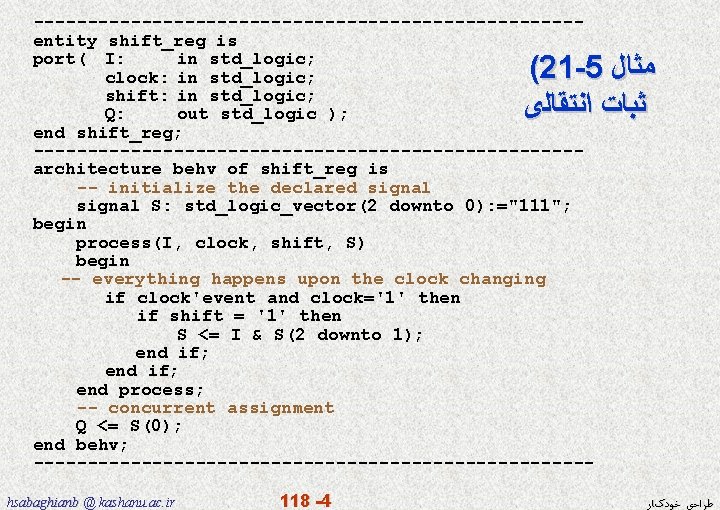

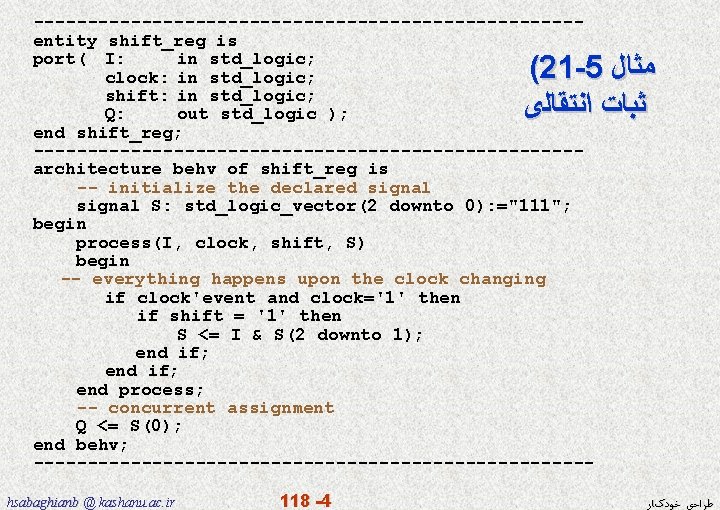

-------------------------entity shift_reg is port( I: in std_logic; clock: in std_logic; shift: in std_logic; Q: out std_logic ); end shift_reg; -------------------------architecture behv of shift_reg is -- initialize the declared signal S: std_logic_vector(2 downto 0): ="111"; begin process(I, clock, shift, S) begin -- everything happens upon the clock changing if clock'event and clock='1' then if shift = '1' then S <= I & S(2 downto 1); end if; end process; -- concurrent assignment Q <= S(0); end behv; -------------------------- (21 -5 ﻣﺜﺎﻝ ﺍﻧﺘﻘﺎﻟی ﺛﺒﺎﺕ hsabaghianb @ kashanu. ac. ir 118 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

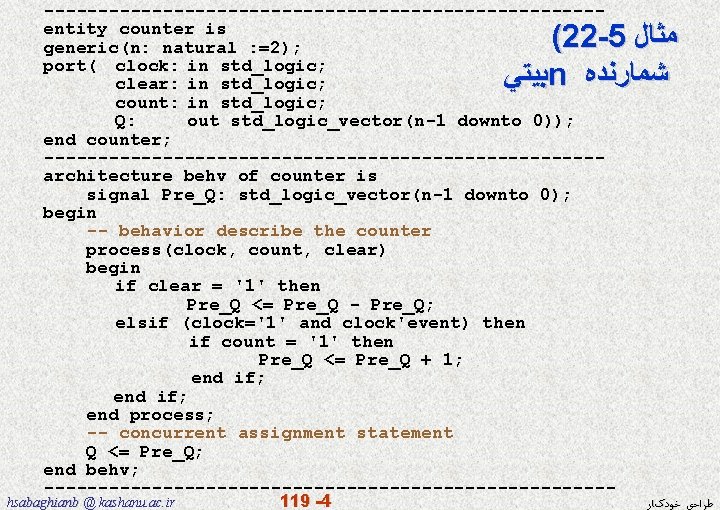

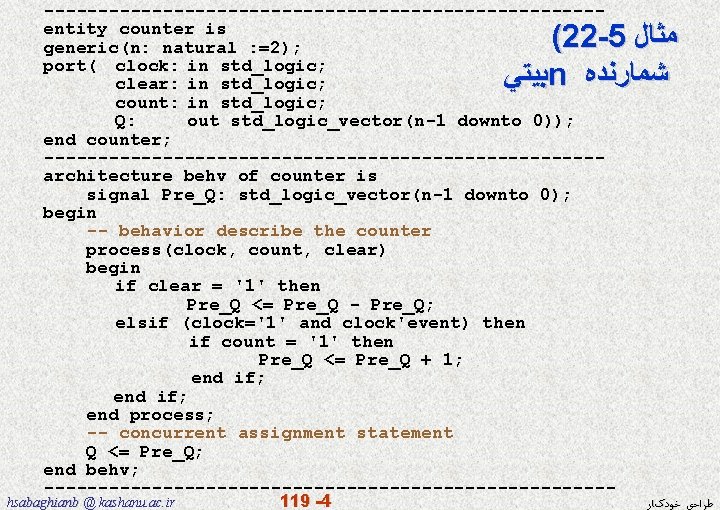

--------------------------entity counter is generic(n: natural : =2); port( clock: in std_logic; clear: in std_logic; count: in std_logic; Q: out std_logic_vector(n-1 downto 0)); end counter; --------------------------architecture behv of counter is signal Pre_Q: std_logic_vector(n-1 downto 0); begin -- behavior describe the counter process(clock, count, clear) begin if clear = '1' then Pre_Q <= Pre_Q - Pre_Q; elsif (clock='1' and clock'event) then if count = '1' then Pre_Q <= Pre_Q + 1; end if; end process; -- concurrent assignment statement Q <= Pre_Q; end behv; --------------------------hsabaghianb @ kashanu. ac. ir 119 -4 (22 -5 ﻣﺜﺎﻝ ﺑﻴﺘﻲ n ﺷﻤﺎﺭﻧﺪﻩ ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

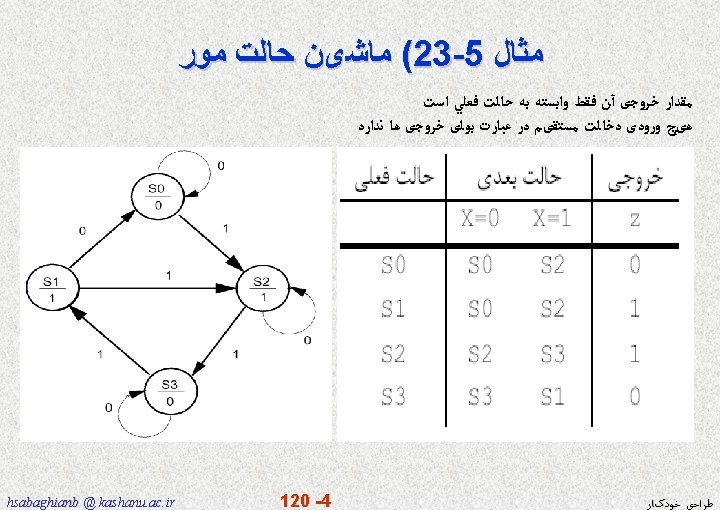

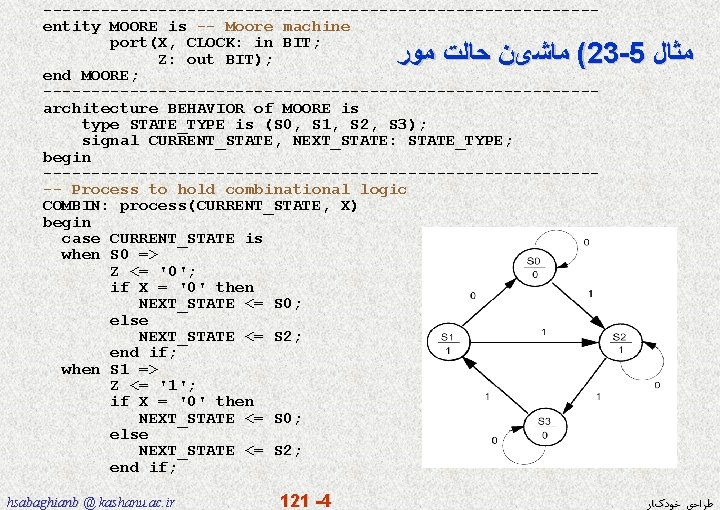

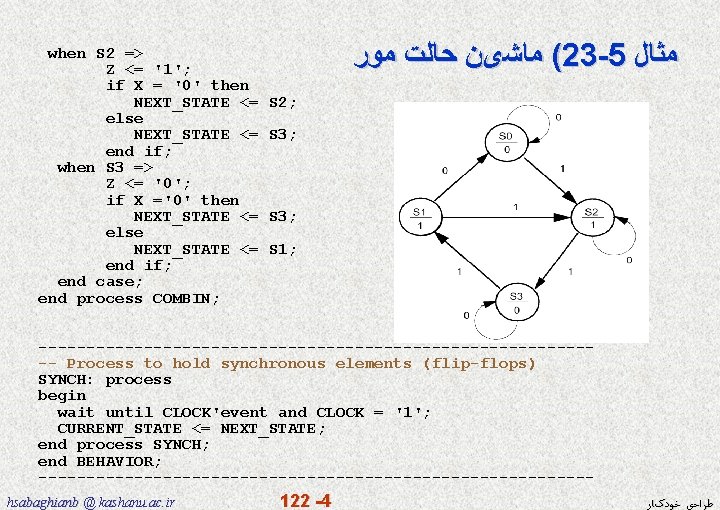

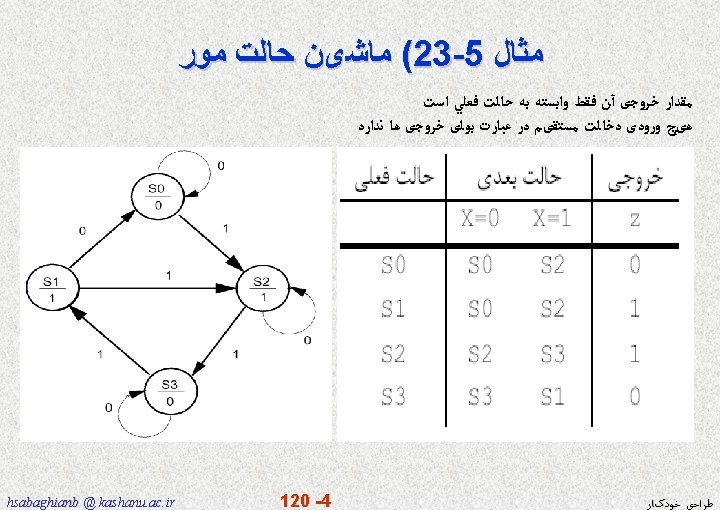

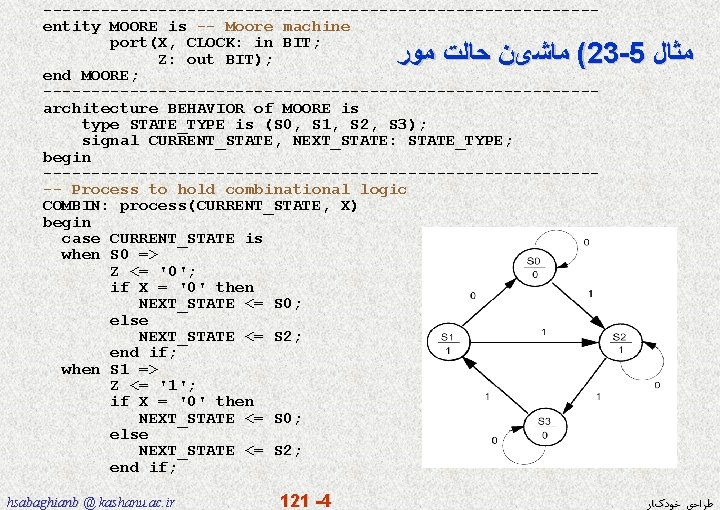

-----------------------------entity MOORE is -- Moore machine port(X, CLOCK: in BIT; Z: out BIT); end MOORE; -----------------------------architecture BEHAVIOR of MOORE is type STATE_TYPE is (S 0, S 1, S 2, S 3); signal CURRENT_STATE, NEXT_STATE: STATE_TYPE; begin ------------------------------ Process to hold combinational logic COMBIN: process(CURRENT_STATE, X) begin case CURRENT_STATE is when S 0 => Z <= '0'; if X = '0' then NEXT_STATE <= S 0; else NEXT_STATE <= S 2; end if; when S 1 => Z <= '1'; if X = '0' then NEXT_STATE <= S 0; else NEXT_STATE <= S 2; end if; ﻣﻮﺭ ﺣﺎﻟﺖ ﻣﺎﺷیﻦ (23 -5 ﻣﺜﺎﻝ hsabaghianb @ kashanu. ac. ir 121 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

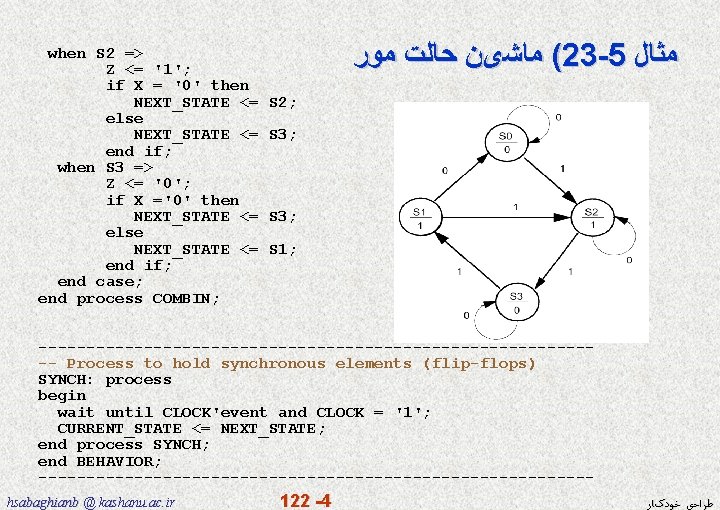

when S 2 => Z <= '1'; if X = '0' then NEXT_STATE <= S 2; else NEXT_STATE <= S 3; end if; when S 3 => Z <= '0'; if X ='0' then NEXT_STATE <= S 3; else NEXT_STATE <= S 1; end if; end case; end process COMBIN; ﻣﻮﺭ ﺣﺎﻟﺖ ﻣﺎﺷیﻦ (23 -5 ﻣﺜﺎﻝ ------------------------------ Process to hold synchronous elements (flip-flops) SYNCH: process begin wait until CLOCK'event and CLOCK = '1'; CURRENT_STATE <= NEXT_STATE; end process SYNCH; end BEHAVIOR; -----------------------------hsabaghianb @ kashanu. ac. ir 122 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

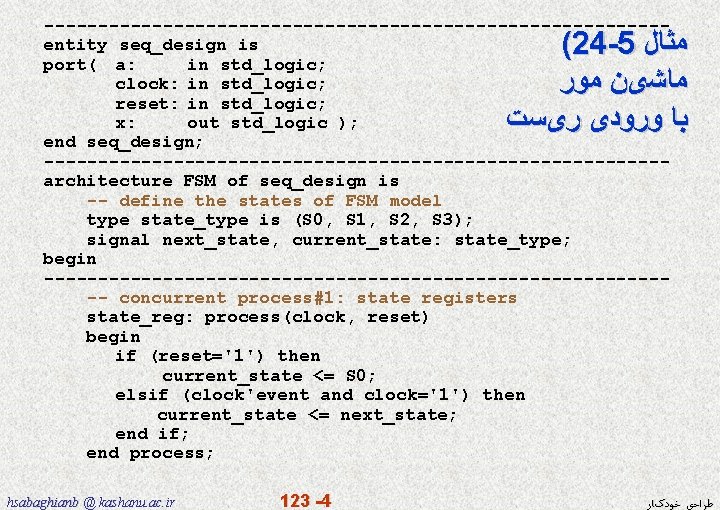

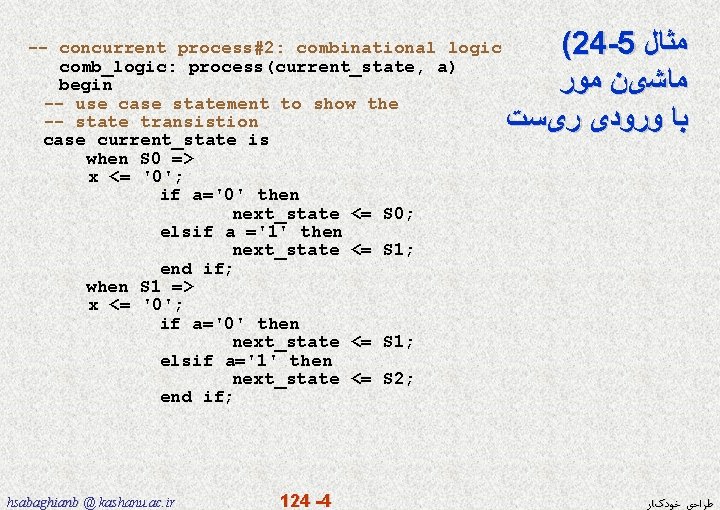

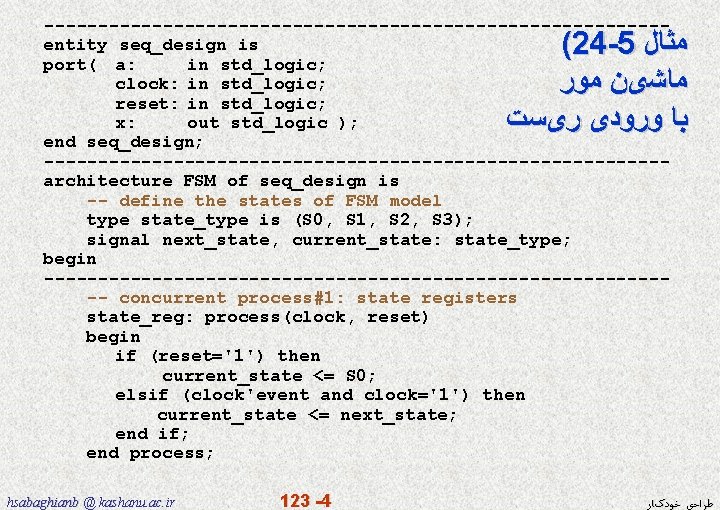

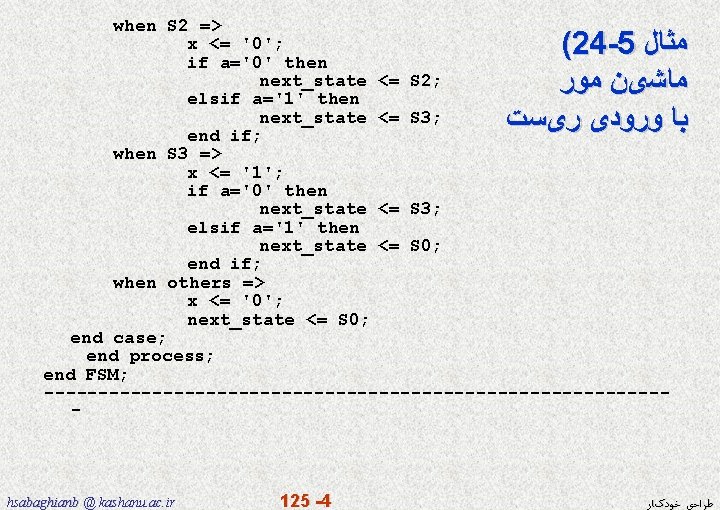

-----------------------------entity seq_design is port( a: in std_logic; clock: in std_logic; reset: in std_logic; x: out std_logic ); end seq_design; -----------------------------architecture FSM of seq_design is -- define the states of FSM model type state_type is (S 0, S 1, S 2, S 3); signal next_state, current_state: state_type; begin ----------------------------- -- concurrent process#1: state registers state_reg: process(clock, reset) begin if (reset='1') then current_state <= S 0; elsif (clock'event and clock='1') then current_state <= next_state; end if; end process; (24 -5 ﻣﺜﺎﻝ ﻣﻮﺭ ﻣﺎﺷیﻦ ﺭیﺴﺖ ﻭﺭﻭﺩی ﺑﺎ hsabaghianb @ kashanu. ac. ir 123 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

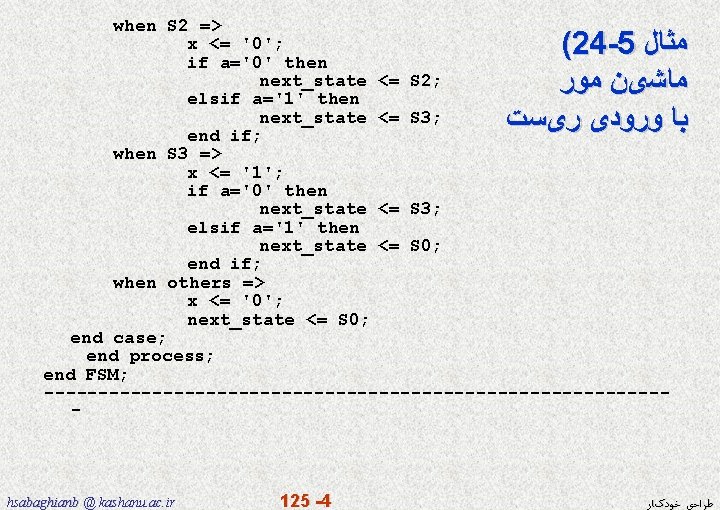

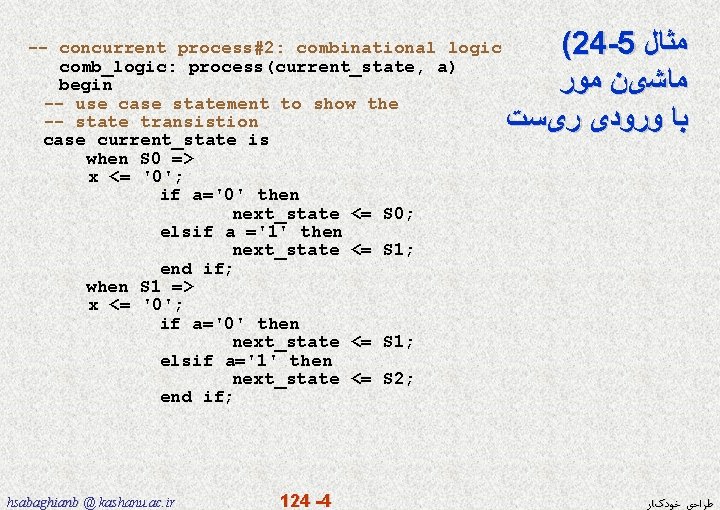

-- concurrent process#2: combinational logic comb_logic: process(current_state, a) begin -- use case statement to show the -- state transistion case current_state is when S 0 => x <= '0'; if a='0' then next_state <= S 0; elsif a ='1' then next_state <= S 1; end if; when S 1 => x <= '0'; if a='0' then next_state <= S 1; elsif a='1' then next_state <= S 2; end if; hsabaghianb @ kashanu. ac. ir 124 -4 (24 -5 ﻣﺜﺎﻝ ﻣﻮﺭ ﻣﺎﺷیﻦ ﺭیﺴﺖ ﻭﺭﻭﺩی ﺑﺎ ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

when S 2 => x <= '0'; if a='0' then next_state <= S 2; elsif a='1' then next_state <= S 3; end if; when S 3 => x <= '1'; if a='0' then next_state <= S 3; elsif a='1' then next_state <= S 0; end if; when others => x <= '0'; next_state <= S 0; end case; end process; end FSM; ----------------------------- (24 -5 ﻣﺜﺎﻝ ﻣﻮﺭ ﻣﺎﺷیﻦ ﺭیﺴﺖ ﻭﺭﻭﺩی ﺑﺎ hsabaghianb @ kashanu. ac. ir 125 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

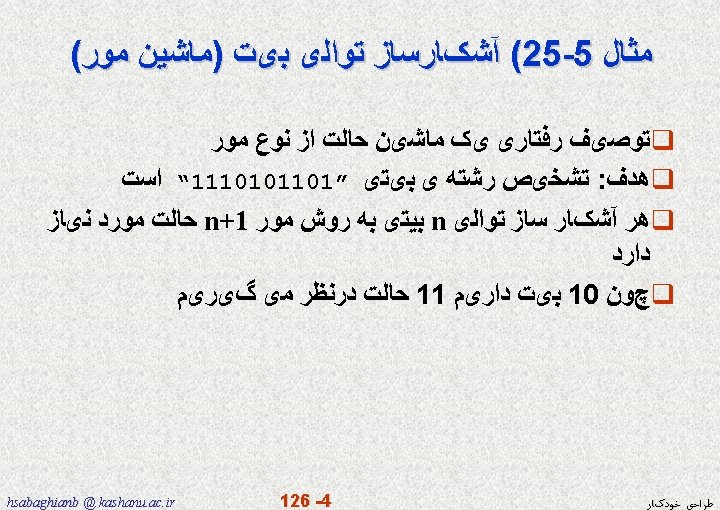

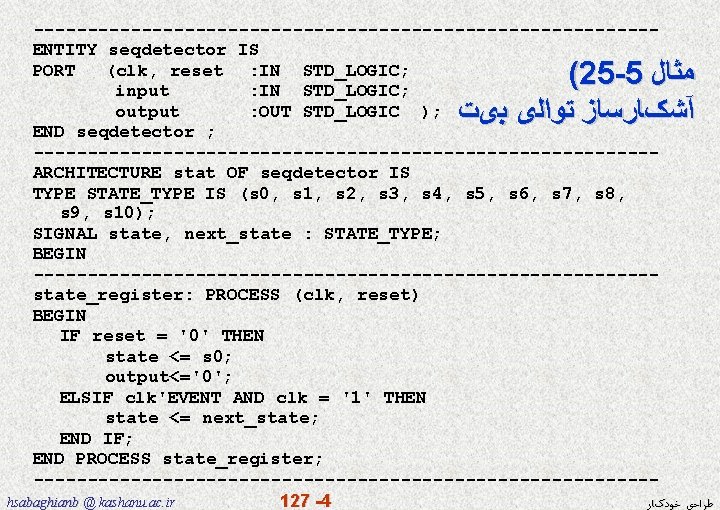

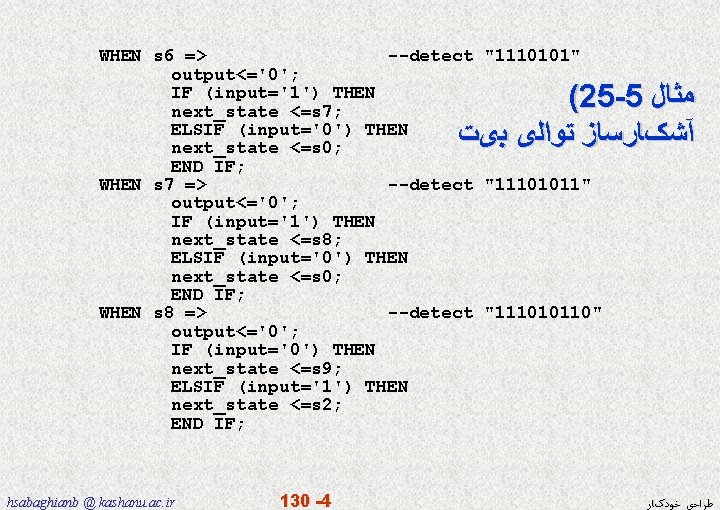

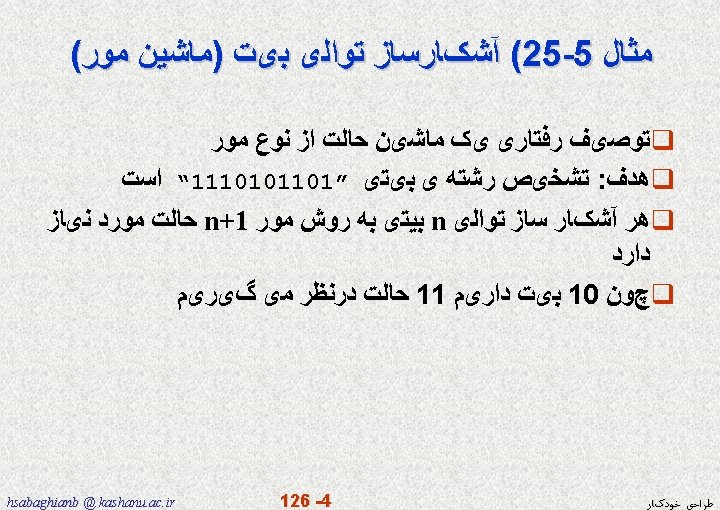

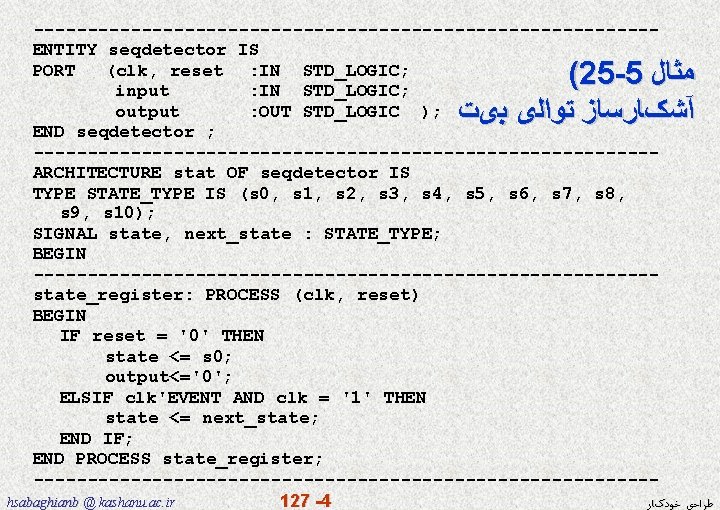

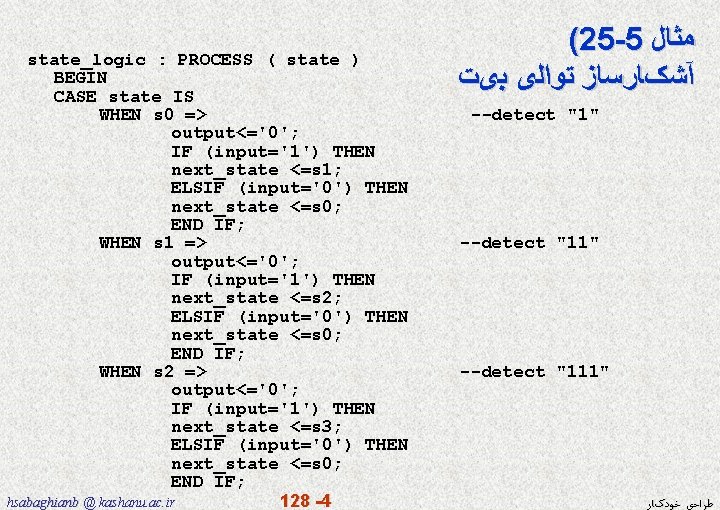

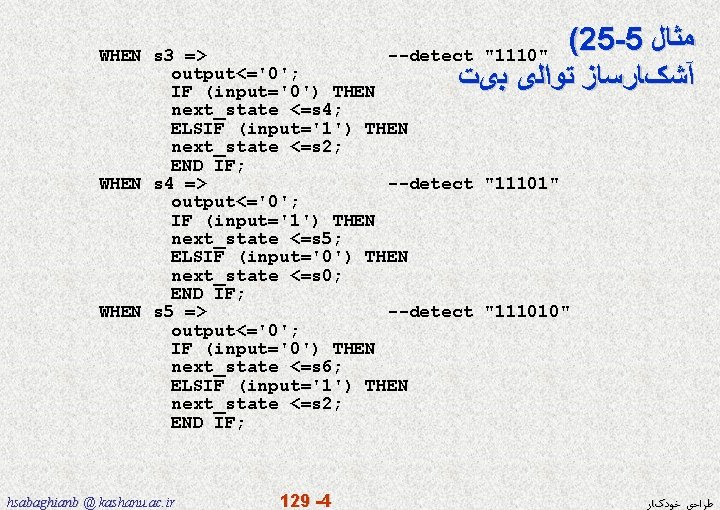

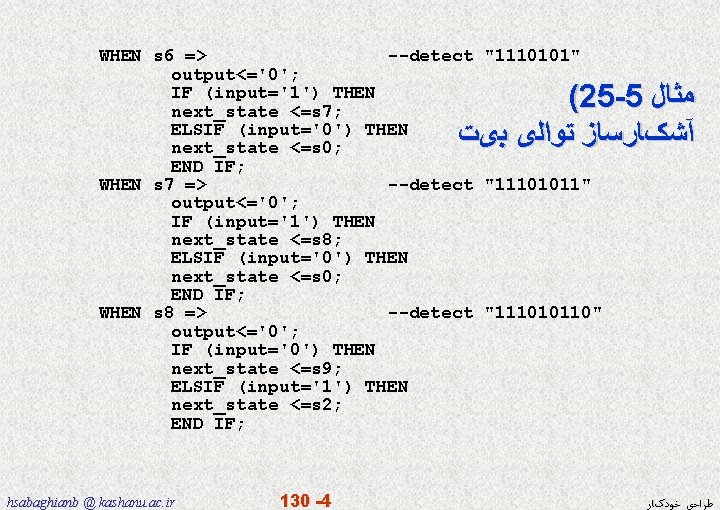

-----------------------------ENTITY seqdetector IS PORT (clk, reset : IN STD_LOGIC; input : IN STD_LOGIC; output : OUT STD_LOGIC ); END seqdetector ; -----------------------------ARCHITECTURE stat OF seqdetector IS TYPE STATE_TYPE IS (s 0, s 1, s 2, s 3, s 4, s 5, s 6, s 7, s 8, s 9, s 10); SIGNAL state, next_state : STATE_TYPE; BEGIN -----------------------------state_register: PROCESS (clk, reset) BEGIN IF reset = '0' THEN state <= s 0; output<='0'; ELSIF clk'EVENT AND clk = '1' THEN state <= next_state; END IF; END PROCESS state_register; -----------------------------hsabaghianb @ kashanu. ac. ir 127 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ (25 -5 ﻣﺜﺎﻝ ﺑیﺖ ﺗﻮﺍﻟی آﺸکﺎﺭﺳﺎﺯ

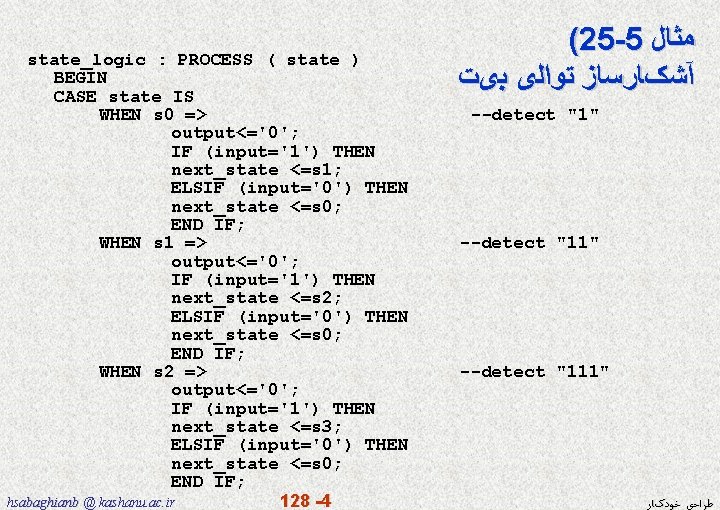

state_logic : PROCESS ( state ) BEGIN CASE state IS WHEN s 0 => output<='0'; IF (input='1') THEN next_state <=s 1; ELSIF (input='0') THEN next_state <=s 0; END IF; WHEN s 1 => output<='0'; IF (input='1') THEN next_state <=s 2; ELSIF (input='0') THEN next_state <=s 0; END IF; WHEN s 2 => output<='0'; IF (input='1') THEN next_state <=s 3; ELSIF (input='0') THEN next_state <=s 0; END IF; hsabaghianb @ kashanu. ac. ir 128 -4 (25 -5 ﻣﺜﺎﻝ ﺑیﺖ ﺗﻮﺍﻟی آﺸکﺎﺭﺳﺎﺯ --detect "1" --detect "111" ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

(25 -5 ﻣﺜﺎﻝ ﺑیﺖ ﺗﻮﺍﻟی آﺸکﺎﺭﺳﺎﺯ WHEN s 3 => --detect "1110" output<='0'; IF (input='0') THEN next_state <=s 4; ELSIF (input='1') THEN next_state <=s 2; END IF; WHEN s 4 => --detect "11101" output<='0'; IF (input='1') THEN next_state <=s 5; ELSIF (input='0') THEN next_state <=s 0; END IF; WHEN s 5 => --detect "111010" output<='0'; IF (input='0') THEN next_state <=s 6; ELSIF (input='1') THEN next_state <=s 2; END IF; hsabaghianb @ kashanu. ac. ir 129 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

WHEN s 6 => --detect "1110101" output<='0'; IF (input='1') THEN next_state <=s 7; ELSIF (input='0') THEN next_state <=s 0; END IF; WHEN s 7 => --detect "11101011" output<='0'; IF (input='1') THEN next_state <=s 8; ELSIF (input='0') THEN next_state <=s 0; END IF; WHEN s 8 => --detect "111010110" output<='0'; IF (input='0') THEN next_state <=s 9; ELSIF (input='1') THEN next_state <=s 2; END IF; (25 -5 ﻣﺜﺎﻝ ﺑیﺖ ﺗﻮﺍﻟی آﺸکﺎﺭﺳﺎﺯ hsabaghianb @ kashanu. ac. ir 130 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

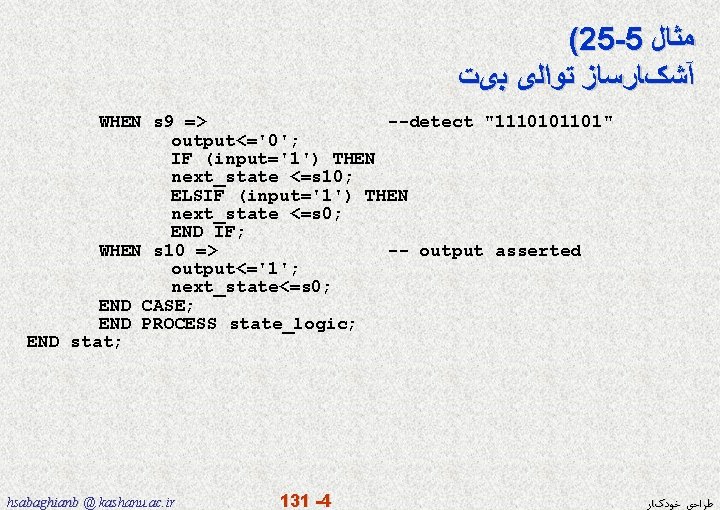

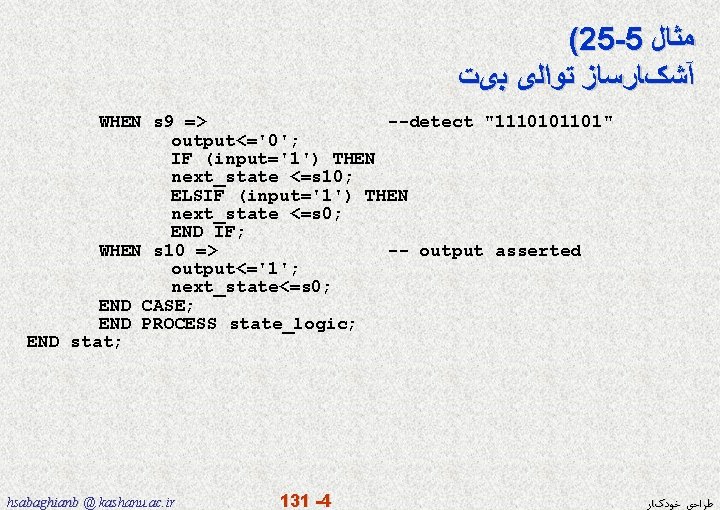

(25 -5 ﻣﺜﺎﻝ ﺑیﺖ ﺗﻮﺍﻟی آﺸکﺎﺭﺳﺎﺯ WHEN s 9 => --detect "1110101101" output<='0'; IF (input='1') THEN next_state <=s 10; ELSIF (input='1') THEN next_state <=s 0; END IF; WHEN s 10 => -- output asserted output<='1'; next_state<=s 0; END CASE; END PROCESS state_logic; END stat; hsabaghianb @ kashanu. ac. ir 131 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

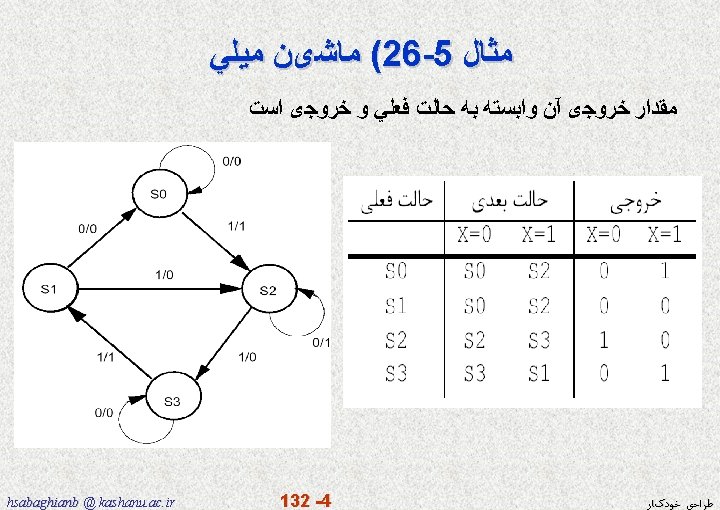

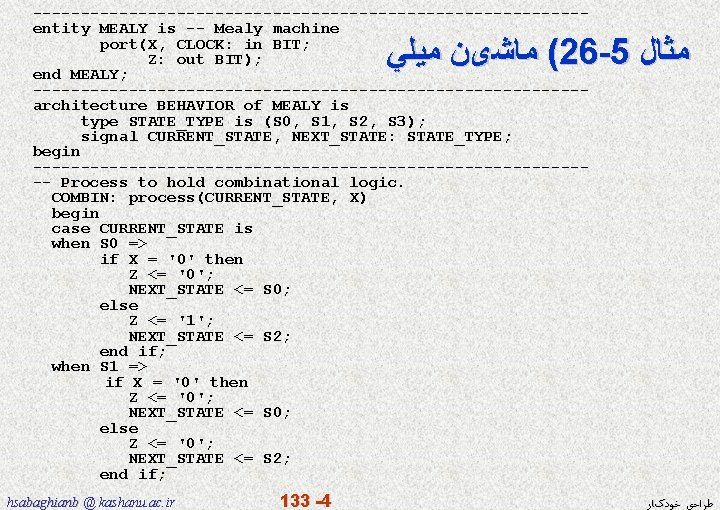

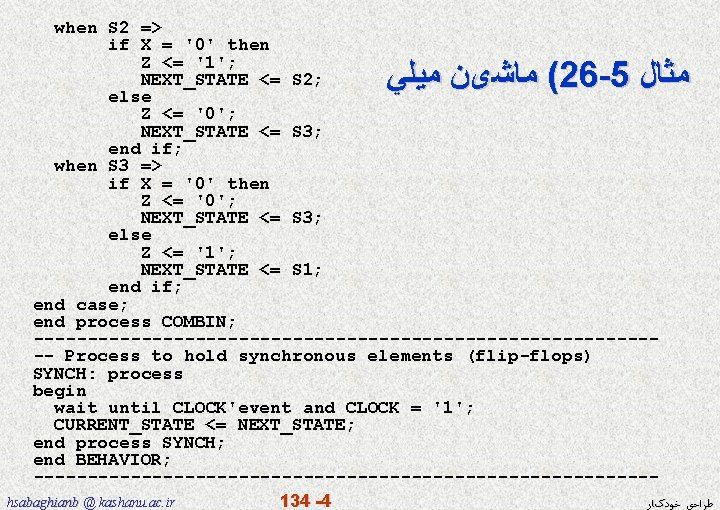

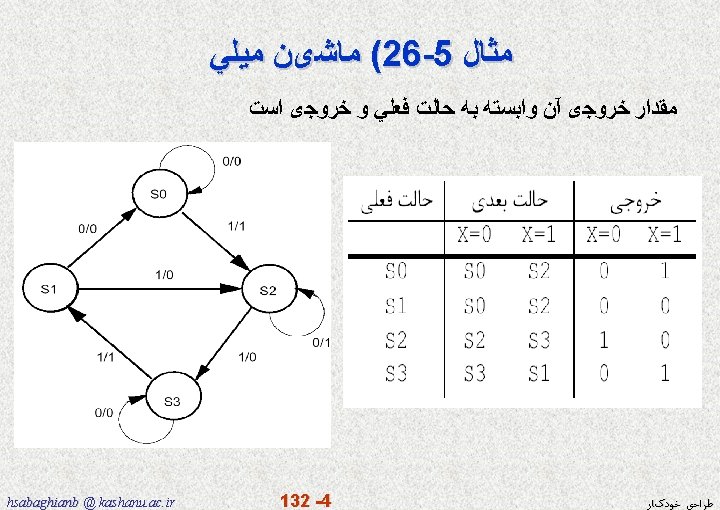

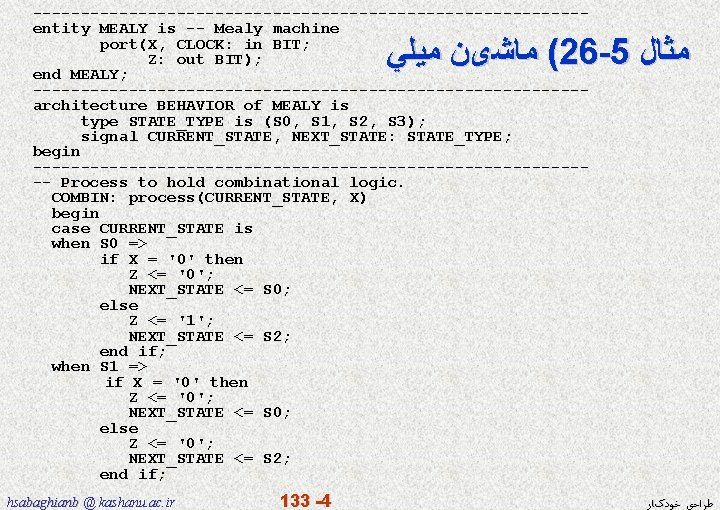

-----------------------------entity MEALY is -- Mealy machine port(X, CLOCK: in BIT; Z: out BIT); end MEALY; -----------------------------architecture BEHAVIOR of MEALY is type STATE_TYPE is (S 0, S 1, S 2, S 3); signal CURRENT_STATE, NEXT_STATE: STATE_TYPE; begin ------------------------------ Process to hold combinational logic. COMBIN: process(CURRENT_STATE, X) begin case CURRENT_STATE is when S 0 => if X = '0' then Z <= '0'; NEXT_STATE <= S 0; else Z <= '1'; NEXT_STATE <= S 2; end if; when S 1 => if X = '0' then Z <= '0'; NEXT_STATE <= S 0; else Z <= '0'; NEXT_STATE <= S 2; end if; ﻣﻴﻠﻲ ﻣﺎﺷیﻦ (26 -5 ﻣﺜﺎﻝ hsabaghianb @ kashanu. ac. ir 133 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

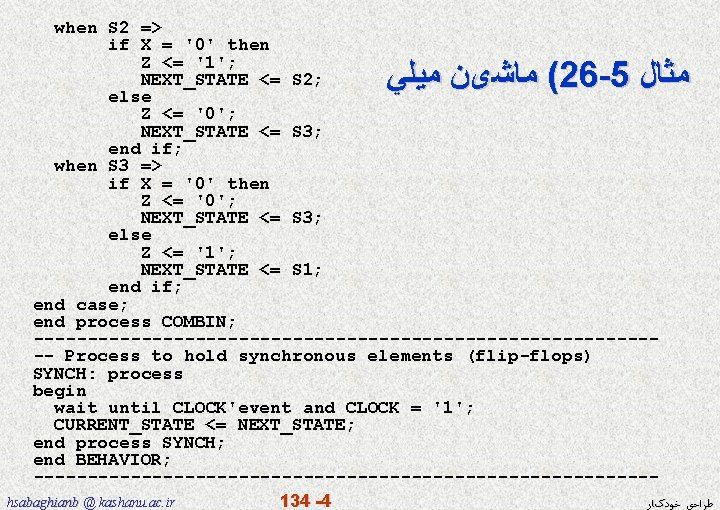

when S 2 => if X = '0' then Z <= '1'; NEXT_STATE <= S 2; else Z <= '0'; NEXT_STATE <= S 3; end if; when S 3 => if X = '0' then Z <= '0'; NEXT_STATE <= S 3; else Z <= '1'; NEXT_STATE <= S 1; end if; end case; end process COMBIN; ------------------------------ Process to hold synchronous elements (flip-flops) SYNCH: process begin wait until CLOCK'event and CLOCK = '1'; CURRENT_STATE <= NEXT_STATE; end process SYNCH; end BEHAVIOR; -----------------------------hsabaghianb @ kashanu. ac. ir 134 -4 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ ﻣﻴﻠﻲ ﻣﺎﺷیﻦ (26 -5 ﻣﺜﺎﻝ