Ch 3 Verilog and Test Benches Verilog HDL

Ch. 3: Verilog and Test Benches • Verilog HDL (Hardware Description Language) – Started as proprietary language (owned by Cadence) – Opened to outside, became IEEE Standard 1364 – Widely used in industry (simpler than VHDL) • Uses of Verilog (and other HDLs) – Hardware specification – Input to a synthesis tool • Synthesis: “automatic” generation of “netlist” (used in IC design and gate-level design) from high-level design description – Design documentation – Logic simulation "Computer Design" by Sunggu Lee

Hardware Description Language • Similar to a Programming Language – Customized for description of digital hardware – Important difference: hardware is inherently parallel • Hardware Description Methods – Behavioral description • Procedural description of how device should operate – Structural description • Specifies how device is connected internally – Mixed behavioral/structural description "Computer Design" by Sunggu Lee

Basic Verilog Description • Starts with module, ends with endmodule – Similar to a “C language” function definition – Signal parameters are defined as input, output, or inout – C language based definition • • Uses many C constructs and operators Sub-module instantiation instead of sub-function call Most behavioral descriptions enclosed in always blocks Inherently parallel execution behavior "Computer Design" by Sunggu Lee

Test Bench • Objectives – Test the functionality of the circuit – Test for manufacturing defects • Test bench written in Verilog – Just like any other device (module) description – Advantages of language-based test bench • Portable • Reproducible "Computer Design" by Sunggu Lee

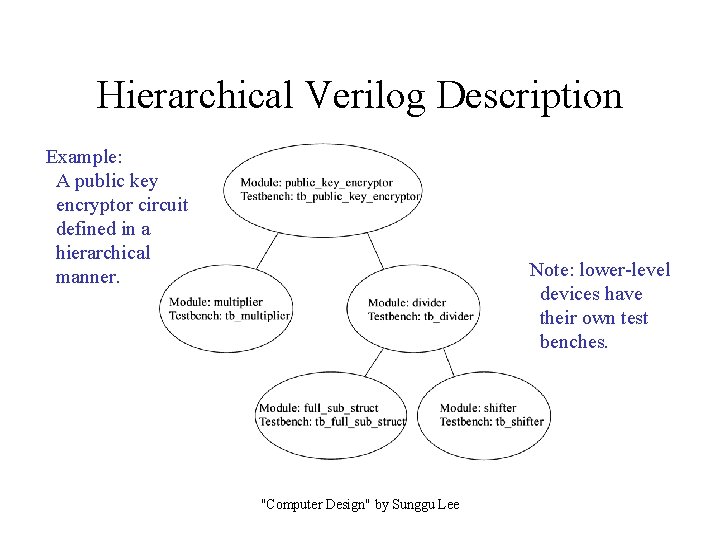

Hierarchical Verilog Description Example: A public key encryptor circuit defined in a hierarchical manner. Note: lower-level devices have their own test benches. "Computer Design" by Sunggu Lee

Four-Valued Logic System • Signal and variable values represented using a 4 valued logic system – 1’b 0: 1 -bit binary logic 0 value – 1’b 1: 1 -bit binary logic 1 value – 1’bx: 1 -bit binary ‘x’ or ‘X’ value • Unknown value, produced for uninitialized values or values driven to conflicting values by more than one signal source – 1’bz: 1 -bit binary ‘z’ or ‘Z’ value • High impedance value, produced when a wire is disconnected from all signal sources driving that wire "Computer Design" by Sunggu Lee

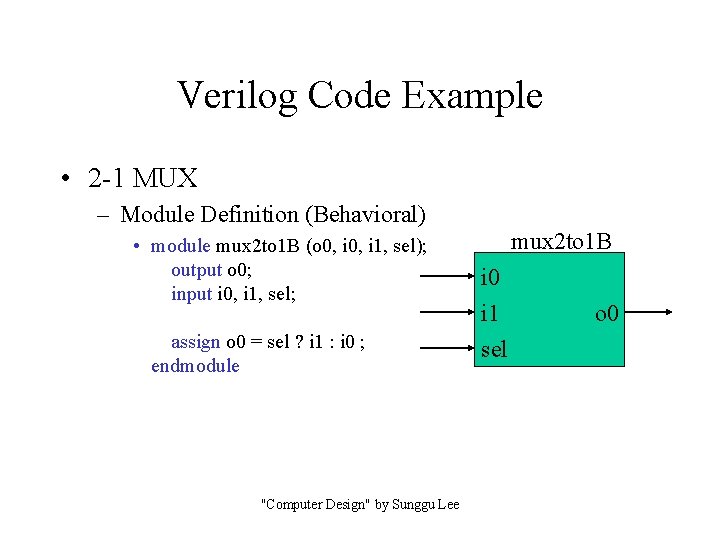

Verilog Code Example • 2 -1 MUX – Module Definition (Behavioral) • module mux 2 to 1 B (o 0, i 1, sel); output o 0; input i 0, i 1, sel; assign o 0 = sel ? i 1 : i 0 ; endmodule "Computer Design" by Sunggu Lee mux 2 to 1 B i 0 i 1 sel o 0

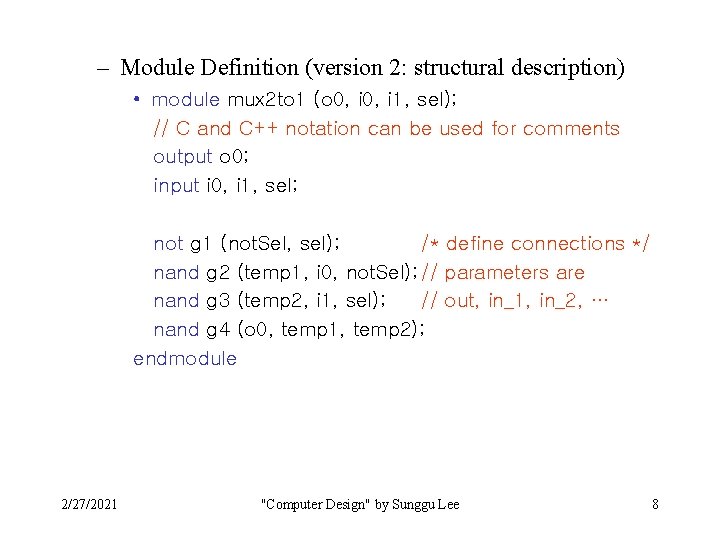

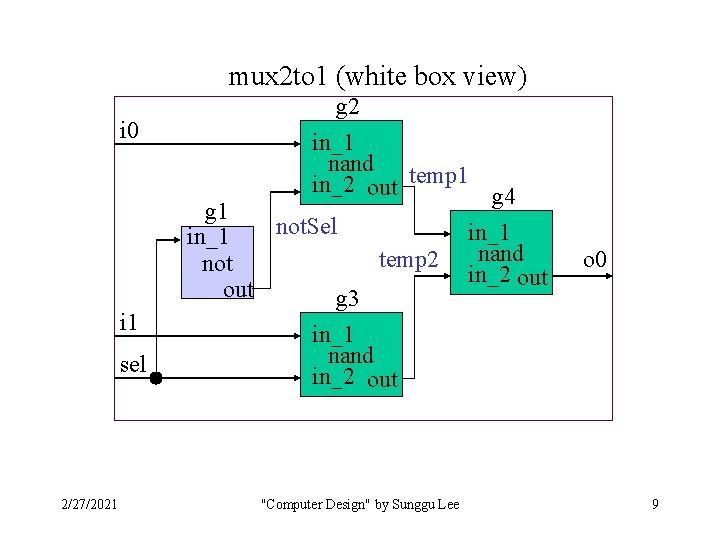

– Module Definition (version 2: structural description) • module mux 2 to 1 (o 0, i 1, sel); // C and C++ notation can be used for comments output o 0; input i 0, i 1, sel; not g 1 (not. Sel, sel); /* define connections */ nand g 2 (temp 1, i 0, not. Sel); // parameters are nand g 3 (temp 2, i 1, sel); // out, in_1, in_2, … nand g 4 (o 0, temp 1, temp 2); endmodule 2/27/2021 "Computer Design" by Sunggu Lee 8

mux 2 to 1 (white box view) i 0 i 1 sel 2/27/2021 g 2 in_1 nand in_2 out temp 1 g 4 g 1 not. Sel in_1 nand temp 2 not in_2 out g 3 in_1 nand in_2 out "Computer Design" by Sunggu Lee o 0 9

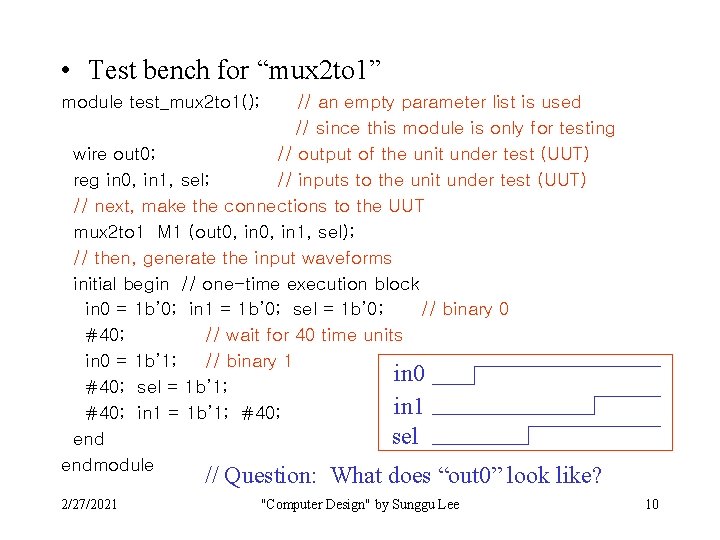

• Test bench for “mux 2 to 1” module test_mux 2 to 1(); // an empty parameter list is used // since this module is only for testing wire out 0; // output of the unit under test (UUT) reg in 0, in 1, sel; // inputs to the unit under test (UUT) // next, make the connections to the UUT mux 2 to 1 M 1 (out 0, in 1, sel); // then, generate the input waveforms initial begin // one-time execution block in 0 = 1 b’ 0; in 1 = 1 b’ 0; sel = 1 b’ 0; // binary 0 #40; // wait for 40 time units in 0 = 1 b’ 1; // binary 1 in 0 #40; sel = 1 b’ 1; in 1 #40; in 1 = 1 b’ 1; #40; sel endmodule // Question: What does “out 0” look like? 2/27/2021 "Computer Design" by Sunggu Lee 10

Concurrent and Sequential Verilog • Hardware is concurrent by nature – All hardware components are active all of the time – Statements in Verilog are concurrent by default • Sequences of Verilog statements execute concurrently • Some hardware circuits are modeled as executing in a sequential manner – For example, sequential logic devices, clock signals, … – Sequences of Verilog statements enclosed within an always or initial block execute one after the other "Computer Design" by Sunggu Lee

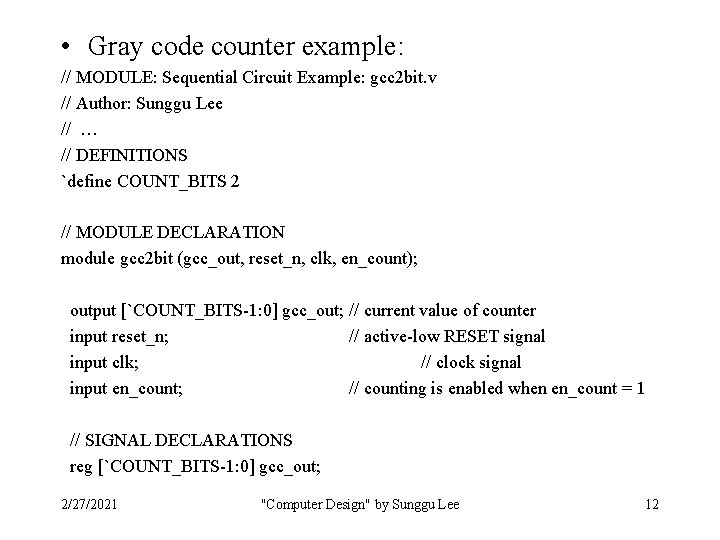

• Gray code counter example: // MODULE: Sequential Circuit Example: gcc 2 bit. v // Author: Sunggu Lee // … // DEFINITIONS `define COUNT_BITS 2 // MODULE DECLARATION module gcc 2 bit (gcc_out, reset_n, clk, en_count); output [`COUNT_BITS-1: 0] gcc_out; // current value of counter input reset_n; // active-low RESET signal input clk; // clock signal input en_count; // counting is enabled when en_count = 1 // SIGNAL DECLARATIONS reg [`COUNT_BITS-1: 0] gcc_out; 2/27/2021 "Computer Design" by Sunggu Lee 12

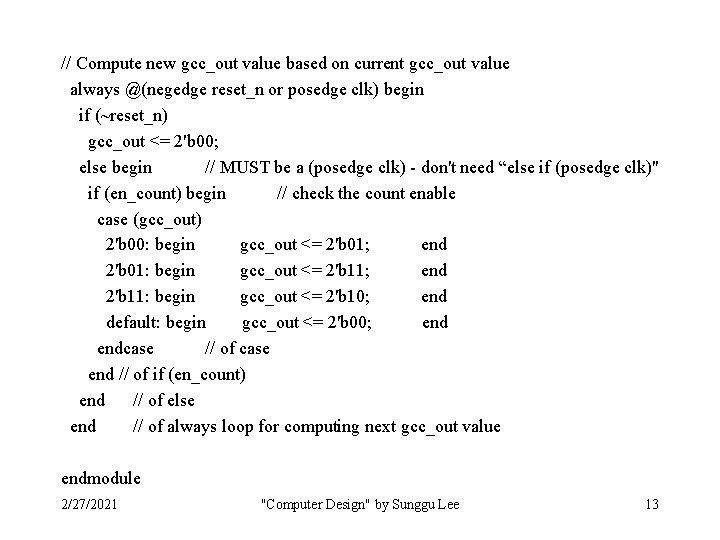

// Compute new gcc_out value based on current gcc_out value always @(negedge reset_n or posedge clk) begin if (~reset_n) gcc_out <= 2'b 00; else begin // MUST be a (posedge clk) - don't need “else if (posedge clk)" if (en_count) begin // check the count enable case (gcc_out) 2'b 00: begin gcc_out <= 2'b 01; end 2'b 01: begin gcc_out <= 2'b 11; end 2'b 11: begin gcc_out <= 2'b 10; end default: begin gcc_out <= 2'b 00; endcase // of case end // of if (en_count) end // of else end // of always loop for computing next gcc_out value endmodule 2/27/2021 "Computer Design" by Sunggu Lee 13

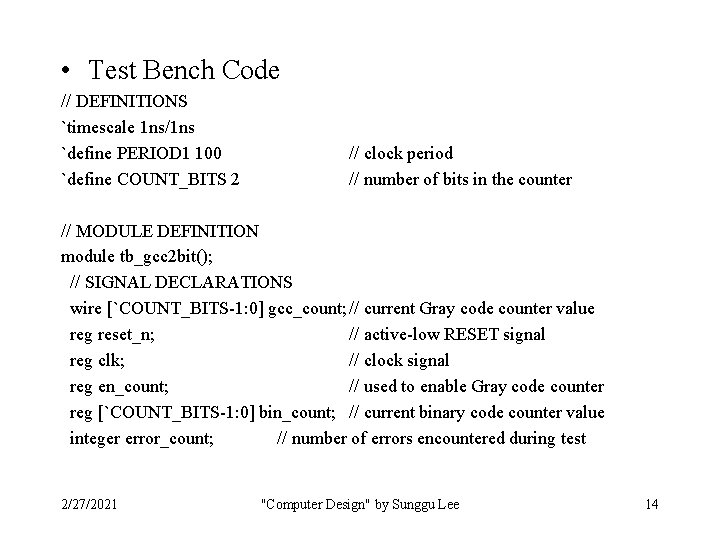

• Test Bench Code // DEFINITIONS `timescale 1 ns/1 ns `define PERIOD 1 100 `define COUNT_BITS 2 // clock period // number of bits in the counter // MODULE DEFINITION module tb_gcc 2 bit(); // SIGNAL DECLARATIONS wire [`COUNT_BITS-1: 0] gcc_count; // current Gray code counter value reg reset_n; // active-low RESET signal reg clk; // clock signal reg en_count; // used to enable Gray code counter reg [`COUNT_BITS-1: 0] bin_count; // current binary code counter value integer error_count; // number of errors encountered during test 2/27/2021 "Computer Design" by Sunggu Lee 14

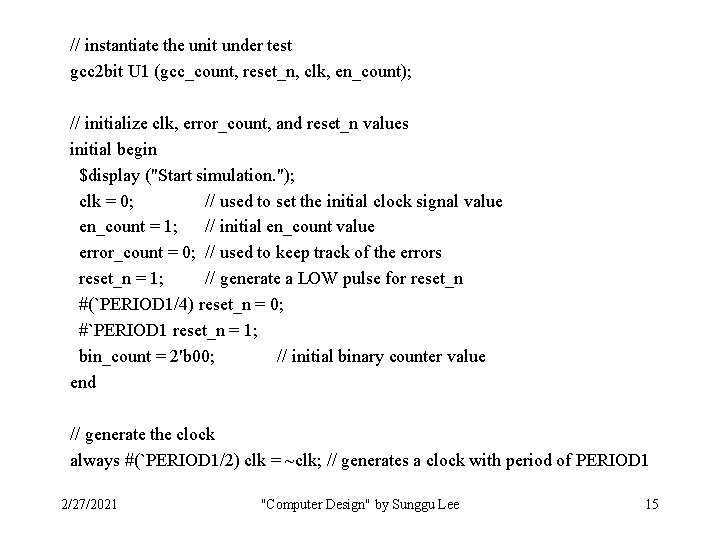

// instantiate the unit under test gcc 2 bit U 1 (gcc_count, reset_n, clk, en_count); // initialize clk, error_count, and reset_n values initial begin $display ("Start simulation. "); clk = 0; // used to set the initial clock signal value en_count = 1; // initial en_count value error_count = 0; // used to keep track of the errors reset_n = 1; // generate a LOW pulse for reset_n #(`PERIOD 1/4) reset_n = 0; #`PERIOD 1 reset_n = 1; bin_count = 2'b 00; // initial binary counter value end // generate the clock always #(`PERIOD 1/2) clk = ~clk; // generates a clock with period of PERIOD 1 2/27/2021 "Computer Design" by Sunggu Lee 15

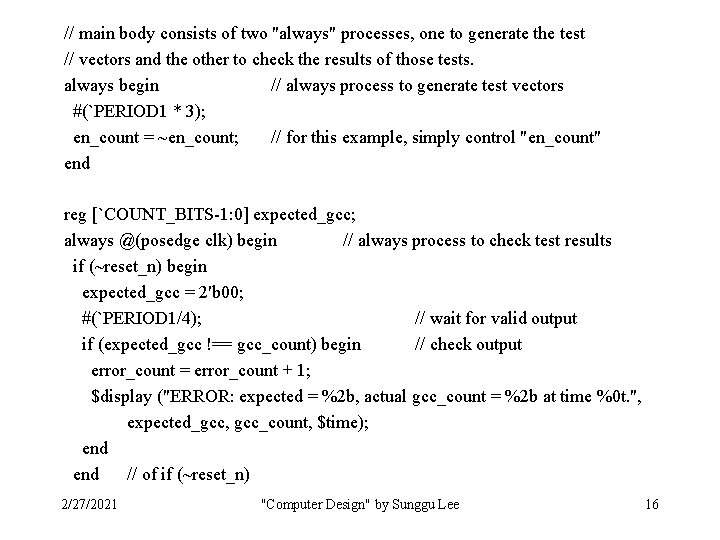

// main body consists of two "always" processes, one to generate the test // vectors and the other to check the results of those tests. always begin // always process to generate test vectors #(`PERIOD 1 * 3); en_count = ~en_count; // for this example, simply control "en_count" end reg [`COUNT_BITS-1: 0] expected_gcc; always @(posedge clk) begin // always process to check test results if (~reset_n) begin expected_gcc = 2'b 00; #(`PERIOD 1/4); // wait for valid output if (expected_gcc !== gcc_count) begin // check output error_count = error_count + 1; $display ("ERROR: expected = %2 b, actual gcc_count = %2 b at time %0 t. ", expected_gcc, gcc_count, $time); end // of if (~reset_n) 2/27/2021 "Computer Design" by Sunggu Lee 16

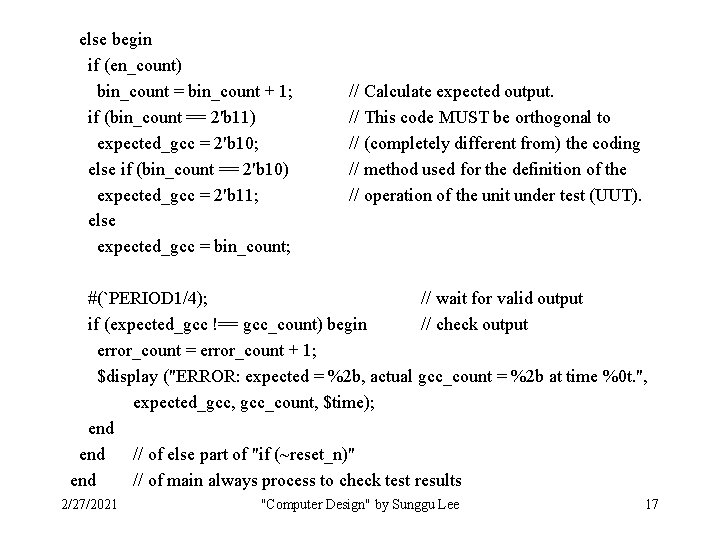

else begin if (en_count) bin_count = bin_count + 1; if (bin_count == 2'b 11) expected_gcc = 2'b 10; else if (bin_count == 2'b 10) expected_gcc = 2'b 11; else expected_gcc = bin_count; // Calculate expected output. // This code MUST be orthogonal to // (completely different from) the coding // method used for the definition of the // operation of the unit under test (UUT). #(`PERIOD 1/4); // wait for valid output if (expected_gcc !== gcc_count) begin // check output error_count = error_count + 1; $display ("ERROR: expected = %2 b, actual gcc_count = %2 b at time %0 t. ", expected_gcc, gcc_count, $time); end // of else part of "if (~reset_n)" end // of main always process to check test results 2/27/2021 "Computer Design" by Sunggu Lee 17

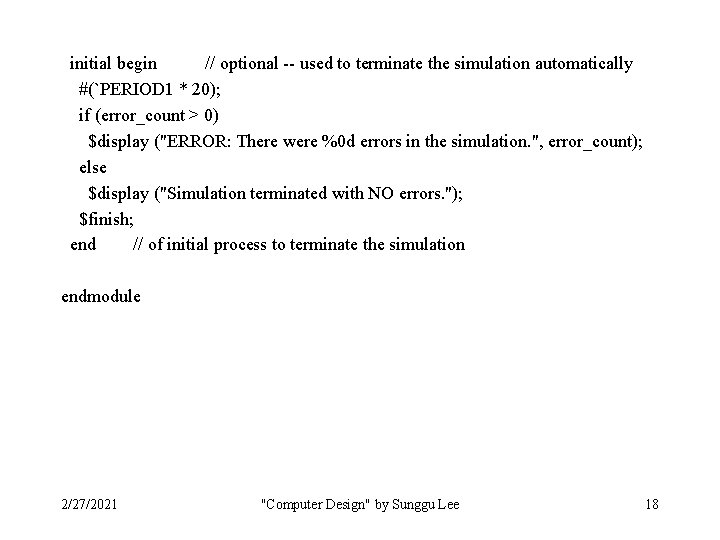

initial begin // optional -- used to terminate the simulation automatically #(`PERIOD 1 * 20); if (error_count > 0) $display ("ERROR: There were %0 d errors in the simulation. ", error_count); else $display ("Simulation terminated with NO errors. "); $finish; end // of initial process to terminate the simulation endmodule 2/27/2021 "Computer Design" by Sunggu Lee 18

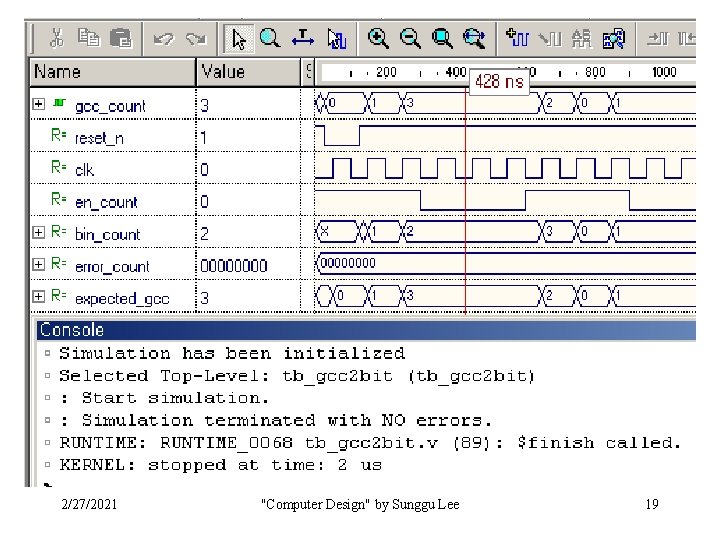

2/27/2021 "Computer Design" by Sunggu Lee 19

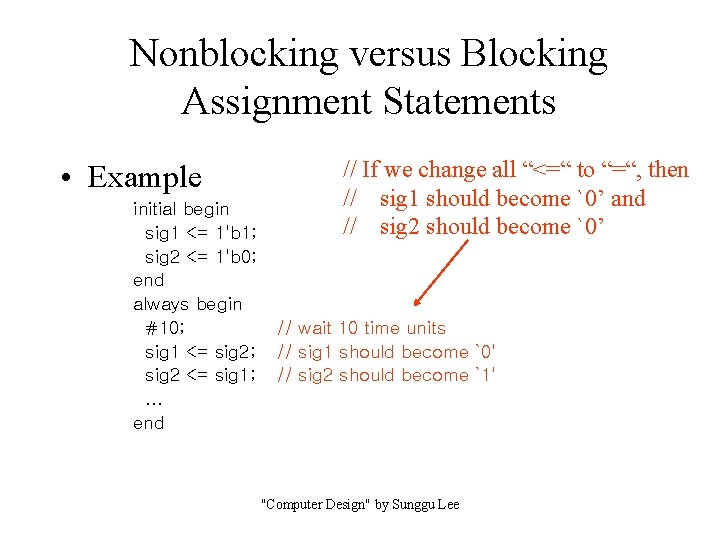

Nonblocking versus Blocking Assignment Statements • Example initial begin sig 1 <= 1'b 1; sig 2 <= 1'b 0; end always begin #10; sig 1 <= sig 2; sig 2 <= sig 1; . . . end // If we change all “<=“ to “=“, then // sig 1 should become `0’ and // sig 2 should become `0’ // wait 10 time units // sig 1 should become `0' // sig 2 should become `1' "Computer Design" by Sunggu Lee

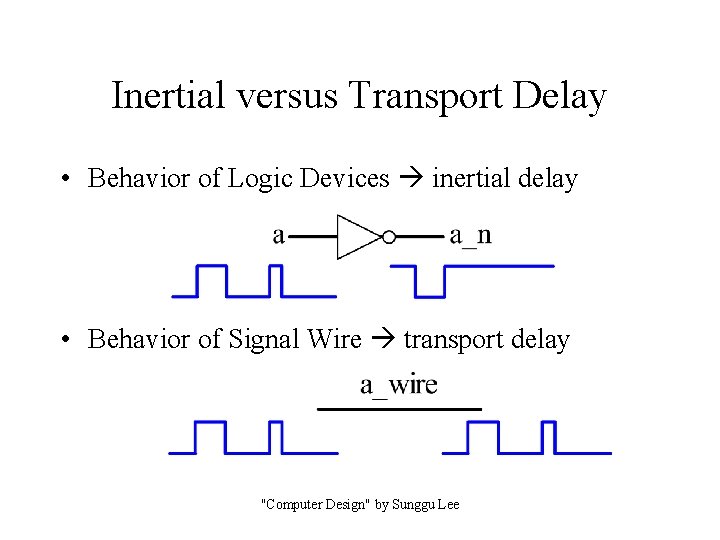

Inertial versus Transport Delay • Behavior of Logic Devices inertial delay • Behavior of Signal Wire transport delay "Computer Design" by Sunggu Lee

Concluding Remarks • Refer to other examples in textbook – Combinational Logic: Full Subtracter, Test Bench – Sequential Logic: State machines seq 1, power • Best way to learn Verilog is by “practicing” – Obtain Active-HDL or another Verilog simulation tool – Refer to example Verilog code provided with tool – Test out simple device descriptions • Be sure to write a test bench description • Check the resulting simulation waveforms • Check the synthesis results "Computer Design" by Sunggu Lee

- Slides: 22