Digital System Design Verilog HDL 2005 Verilog HDL

![Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 TFF Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 TFF](https://slidetodoc.com/presentation_image_h/9c5dccfca7ea10dbd7688d9b9f2da260/image-29.jpg)

![Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the](https://slidetodoc.com/presentation_image_h/9c5dccfca7ea10dbd7688d9b9f2da260/image-34.jpg)

- Slides: 36

Digital System Design Verilog® HDL 2005 Verilog HDL Maziar Goudarzi

Today program l History of Verilog® HDL l Overview of Digital Design with Verilog® HDL l Hello World! l Hierarchical Modeling Concepts 2005 Verilog HDL 2

History of Verilog® HDL l Beginning: 1983 ¡ “Gateway Design Automation” company ¡ Simulation environment l Comprising various levels of abstraction • Switch (transistors), gate, register-transfer, and higher levels 2005 Verilog HDL 3

History of Verilog® HDL (cont’d) l Three factors to success of Verilog ¡ Programming l Extend and customize simulation environment ¡ Close l Language Interface (PLI) attention to the needs of ASIC foundries “Gateway Design Automation” partnership with Motorola, National, and UTMC in 1987 -89 ¡ Verilog-based synthesis technology “Gateway Design Automation” licensed Verilog to Synopsys l Synopsys introduced synthesis from Verilog in 1987 l 2005 Verilog HDL 4

History of Verilog® HDL (cont’d) l VHDL ¡ VHSIC (Very High Speed Integrated Circuit) Hardware Description Language ¡ Developed under contract from DARPA ¡ IEEE standard ¡ Public domain ¡ Other EDA vendors adapted VHDL ¡ “Gateway” put Verilog in public domain 2005 Verilog HDL 5

History of Verilog® HDL (cont’d) l Today ¡ Market divided between Verilog & VHDL mostly in Europe l Verilog dominant in US l ¡ VHDL More general language l Not all constructs are synthesizable l ¡ Verilog: Not as general as VHDL l Most constructs are synthesizable l 2005 Verilog HDL 6

Verilog® HDL Overview of Digital Design Using Verilog 2005 Verilog HDL

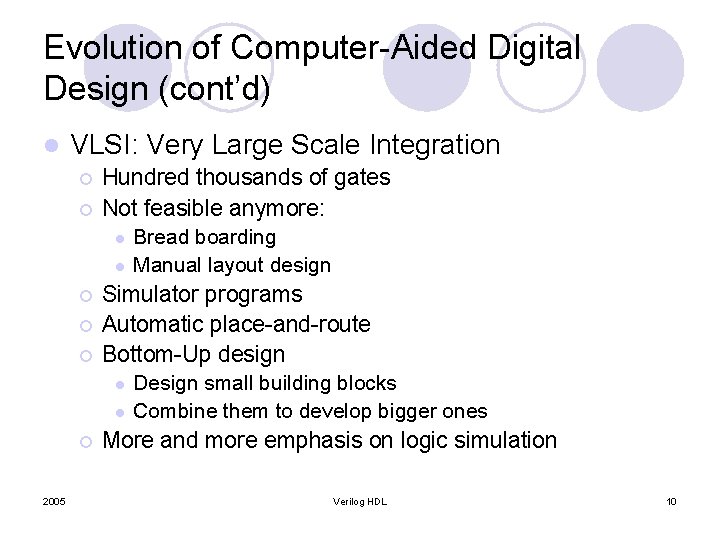

Overview of Digital Design Using Verilog l Evolution of Computer-Aided Digital Design l Emergence of HDLs l Typical Design Flow l Importance of HDLs l Popularity of Verilog HDL l Trends in HDLs 2005 Verilog HDL 8

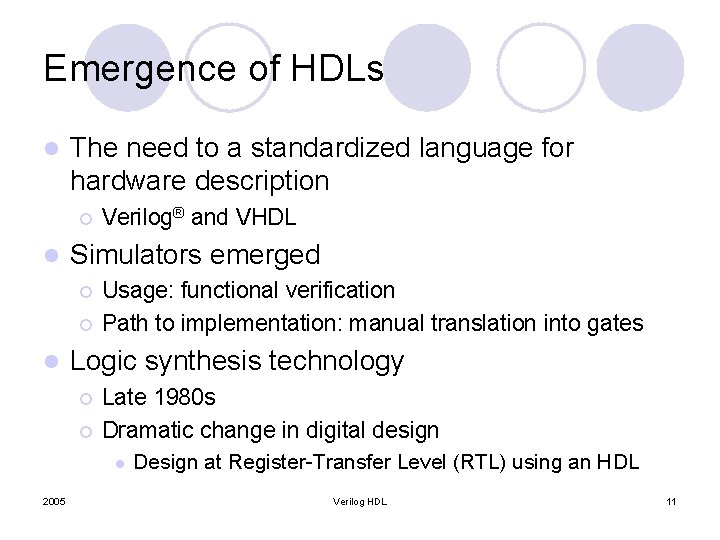

Evolution of Computer-Aided Digital Design l SSI: Small scale integration ¡ l MSI: Medium scale integration ¡ l A few gates on a chip Hundreds of gates on a chip LSI: Large scale integration ¡ ¡ Thousands of gates on a chip CAD: Computer-Aided Design l ¡ ¡ ¡ 2005 CAD vs. CAE Logic and circuit simulators Prototyping on bread board Layout by hand (on paper or a computer terminal) Verilog HDL 9

Evolution of Computer-Aided Digital Design (cont’d) l VLSI: Very Large Scale Integration ¡ ¡ Hundred thousands of gates Not feasible anymore: l l ¡ ¡ ¡ Simulator programs Automatic place-and-route Bottom-Up design l l ¡ 2005 Bread boarding Manual layout design Design small building blocks Combine them to develop bigger ones More and more emphasis on logic simulation Verilog HDL 10

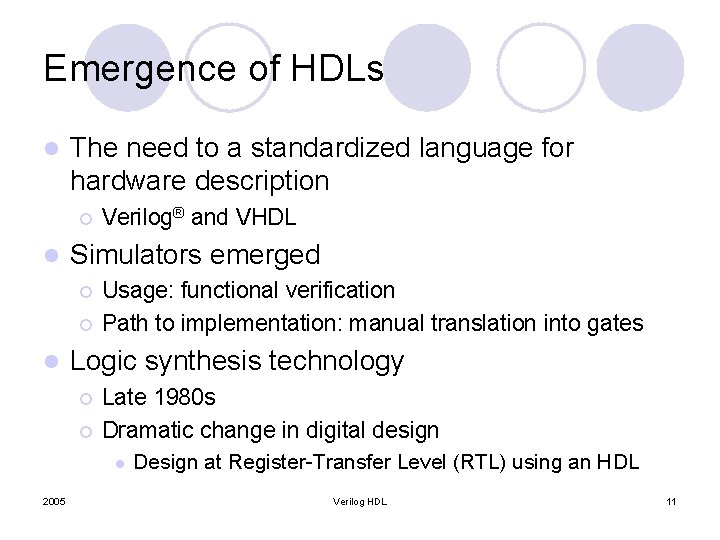

Emergence of HDLs l The need to a standardized language for hardware description ¡ l Simulators emerged ¡ ¡ l Verilog® and VHDL Usage: functional verification Path to implementation: manual translation into gates Logic synthesis technology ¡ ¡ Late 1980 s Dramatic change in digital design l 2005 Design at Register-Transfer Level (RTL) using an HDL Verilog HDL 11

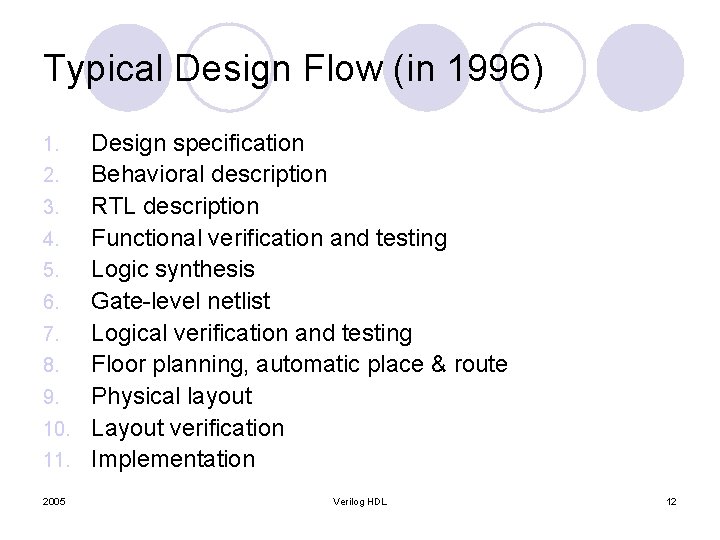

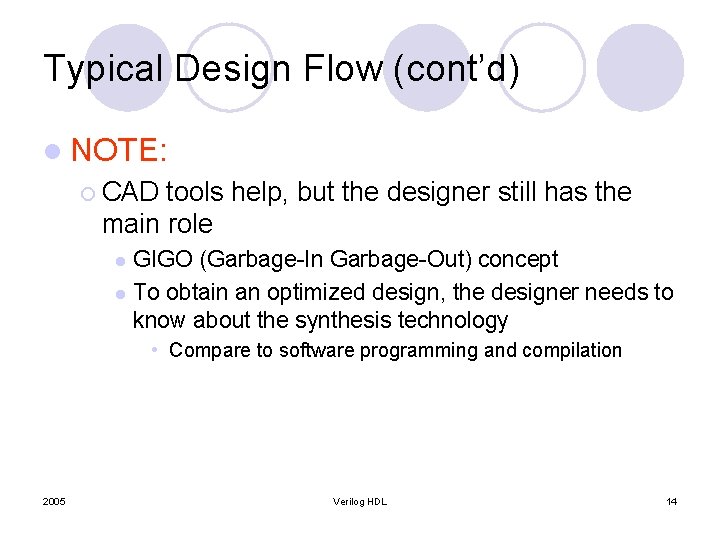

Typical Design Flow (in 1996) Design specification 2. Behavioral description 3. RTL description 4. Functional verification and testing 5. Logic synthesis 6. Gate-level netlist 7. Logical verification and testing 8. Floor planning, automatic place & route 9. Physical layout 10. Layout verification 11. Implementation 1. 2005 Verilog HDL 12

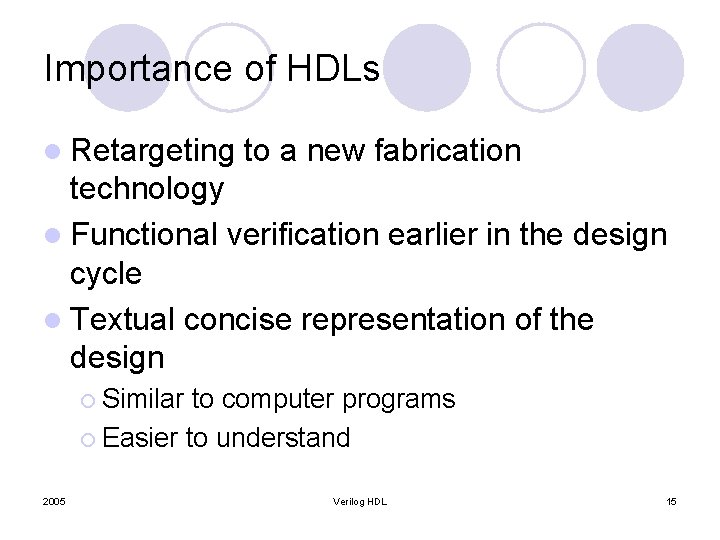

Typical Design Flow (cont’d) l Most ¡ In design activity 1996: Manually optimizing the RTL design l CAD tools take care of generating lower-level details l Reducing design time to months from years l ¡ Today Still RTL is used in many cases l But, synthesis from behavioral-level also possible l Digital design now resembles high-level computer programming l 2005 Verilog HDL 13

Typical Design Flow (cont’d) l NOTE: ¡ CAD tools help, but the designer still has the main role GIGO (Garbage-In Garbage-Out) concept l To obtain an optimized design, the designer needs to know about the synthesis technology l • Compare to software programming and compilation 2005 Verilog HDL 14

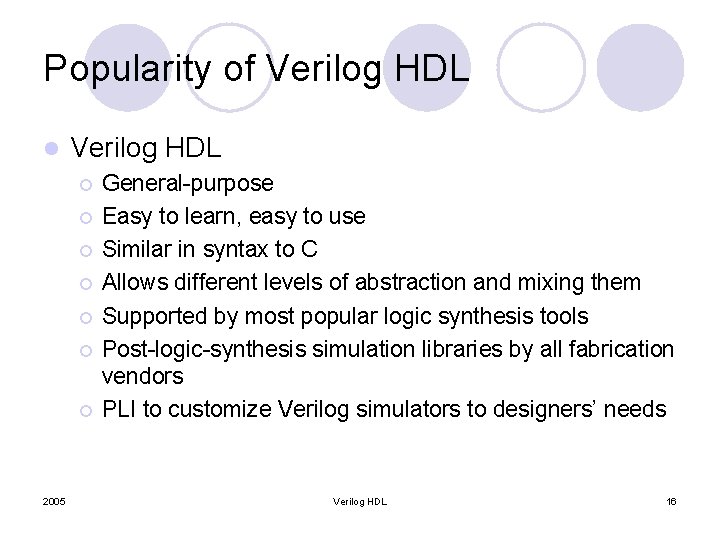

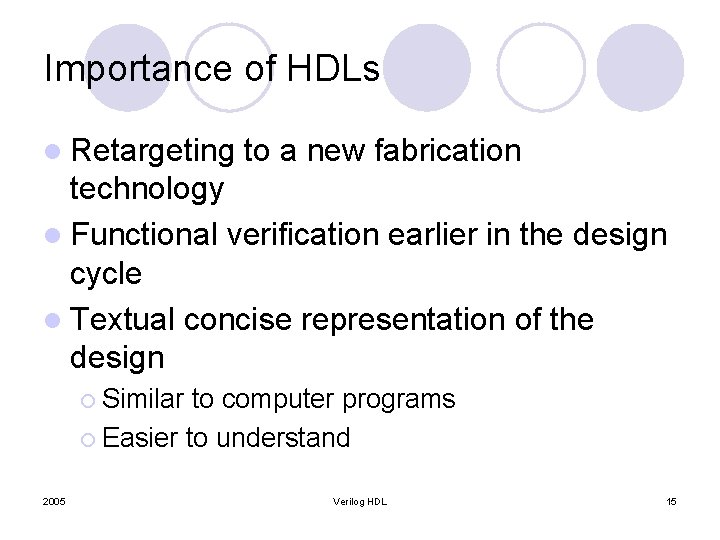

Importance of HDLs l Retargeting to a new fabrication technology l Functional verification earlier in the design cycle l Textual concise representation of the design ¡ Similar to computer programs ¡ Easier to understand 2005 Verilog HDL 15

Popularity of Verilog HDL l Verilog HDL ¡ ¡ ¡ ¡ 2005 General-purpose Easy to learn, easy to use Similar in syntax to C Allows different levels of abstraction and mixing them Supported by most popular logic synthesis tools Post-logic-synthesis simulation libraries by all fabrication vendors PLI to customize Verilog simulators to designers’ needs Verilog HDL 16

Trends in HDLs l Design at behavioral level l Formal verification techniques l Very high speed and time critical circuits ¡ e. g. microprocessors ¡ Mixed gate-level and RTL designs l Hardware-Software ¡ System-level 2005 Co-design languages: System. C, Spec. C, … Verilog HDL 17

Verilog® HDL Hello World! 2005 Verilog HDL

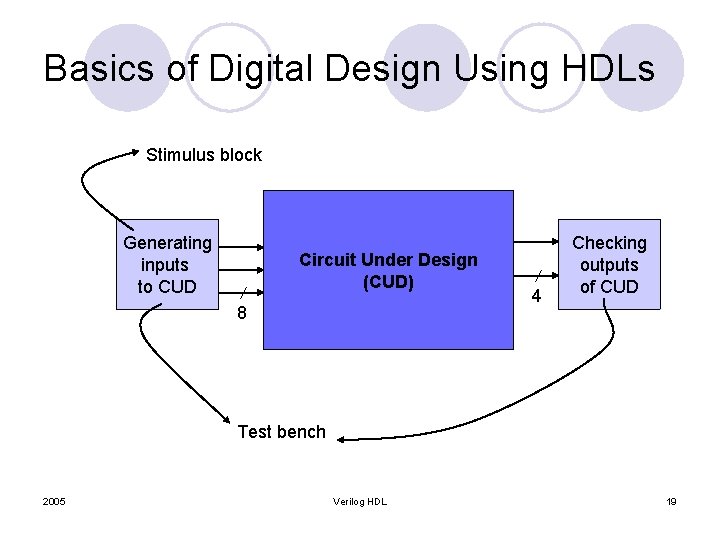

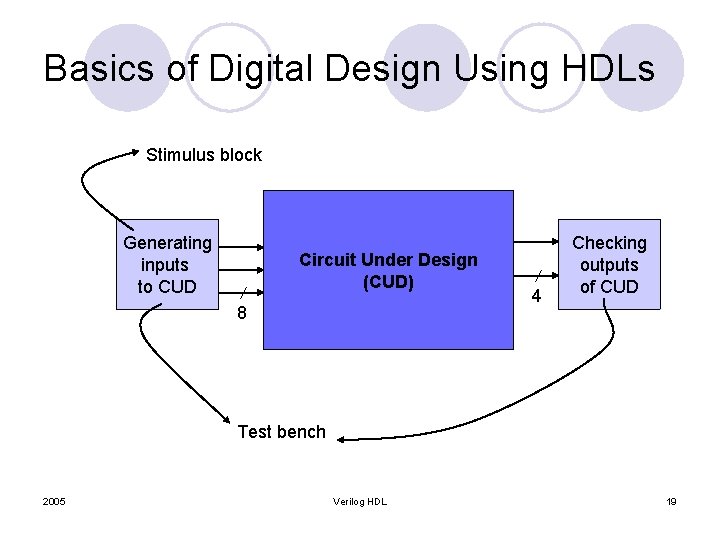

Basics of Digital Design Using HDLs Stimulus block Generating inputs to CUD Circuit Under Design (CUD) 8 4 Checking outputs of CUD Test bench 2005 Verilog HDL 19

Model. Sim® Simulation Environment l You’ll 2005 see in the laboratory Verilog HDL 20

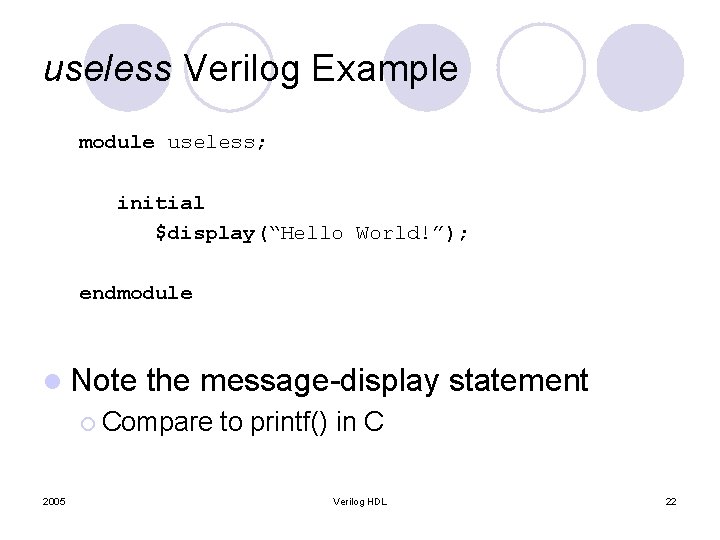

Verilog Basic Building Block l Module module not_gate(in, out); // module name+ports // comments: declaring port type input in; output out; // Defining circuit functionality assign out = ~in; endmodule 2005 Verilog HDL 21

useless Verilog Example module useless; initial $display(“Hello World!”); endmodule l Note the message-display statement ¡ Compare 2005 to printf() in C Verilog HDL 22

Verilog® HDL Hierarchical Modeling Concepts 2005 Verilog HDL

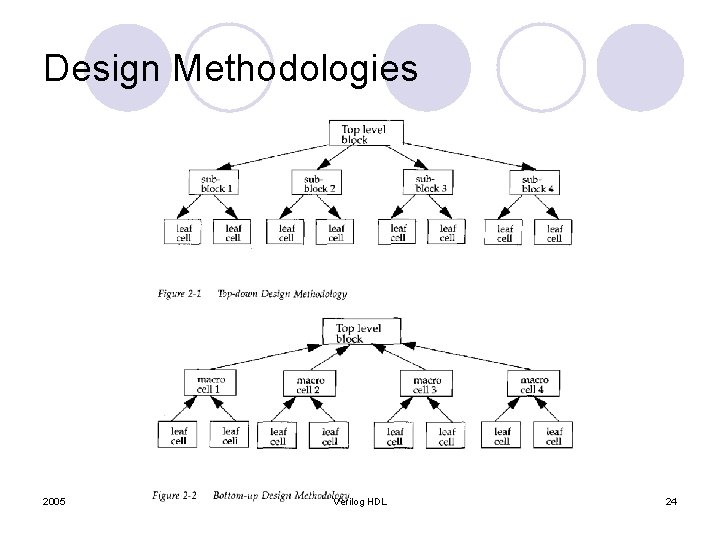

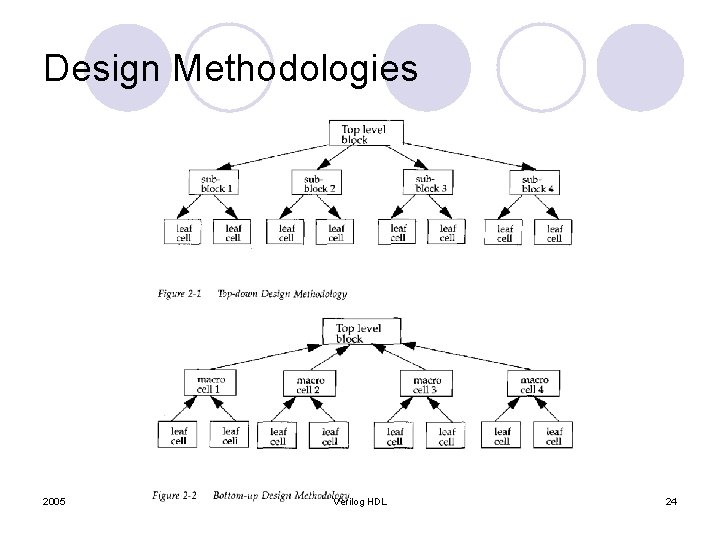

Design Methodologies 2005 Verilog HDL 24

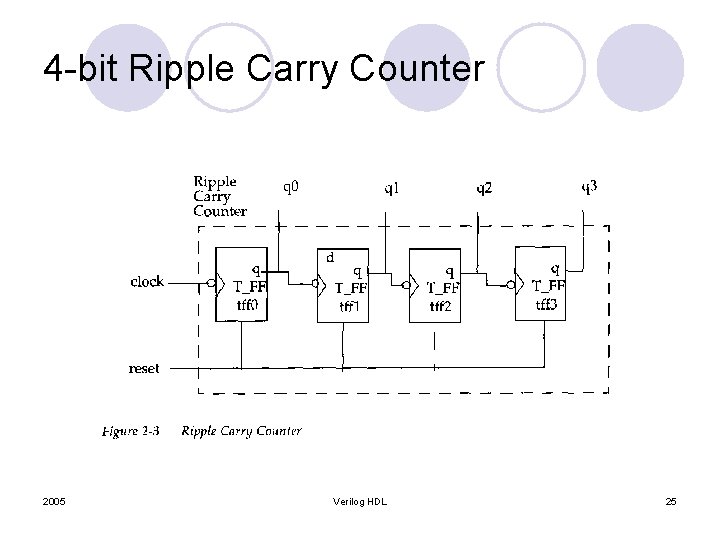

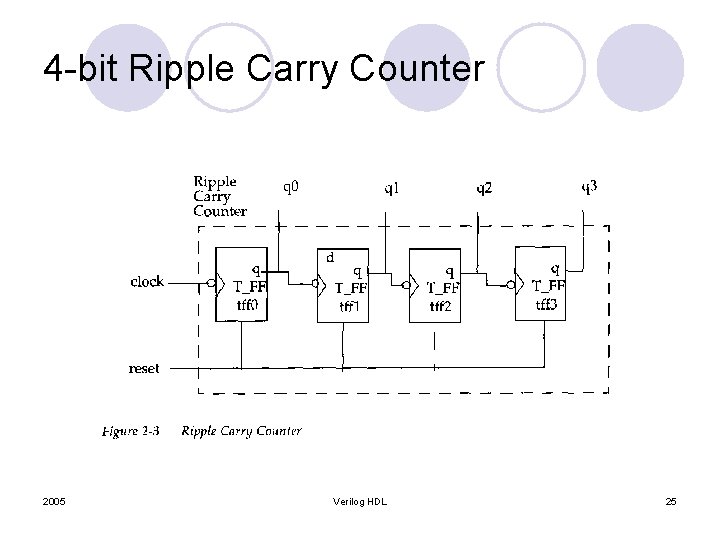

4 -bit Ripple Carry Counter 2005 Verilog HDL 25

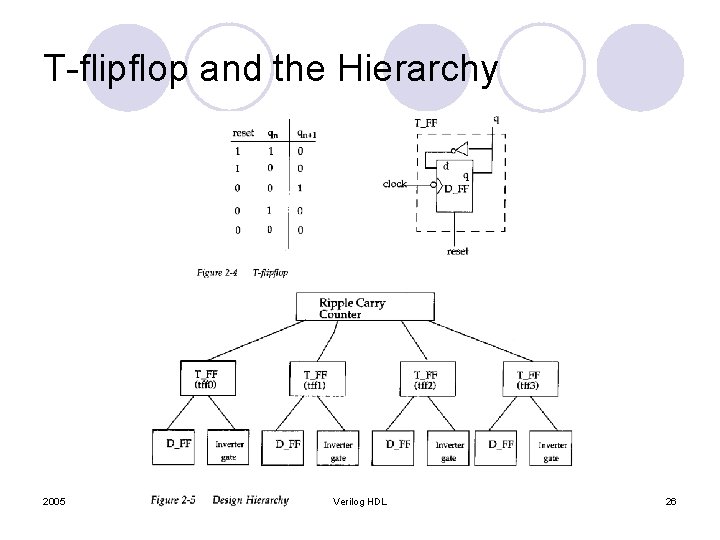

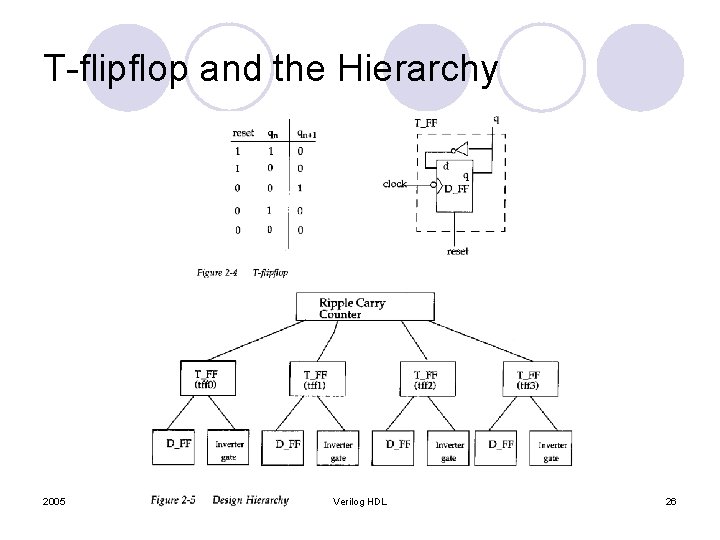

T-flipflop and the Hierarchy 2005 Verilog HDL 26

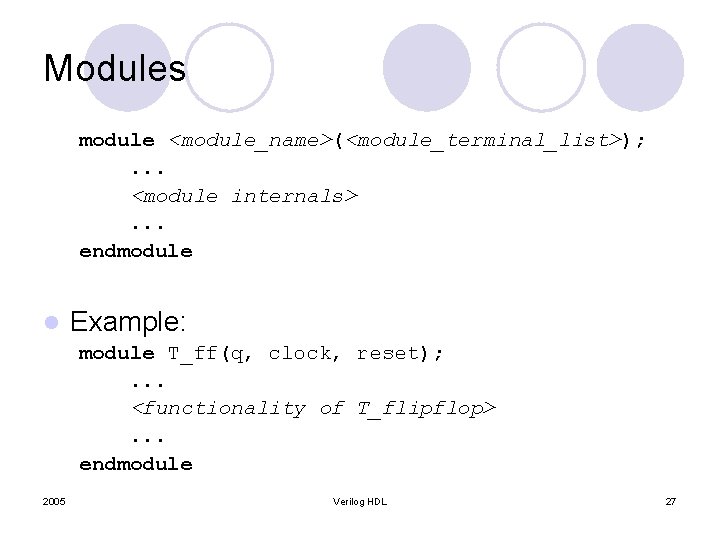

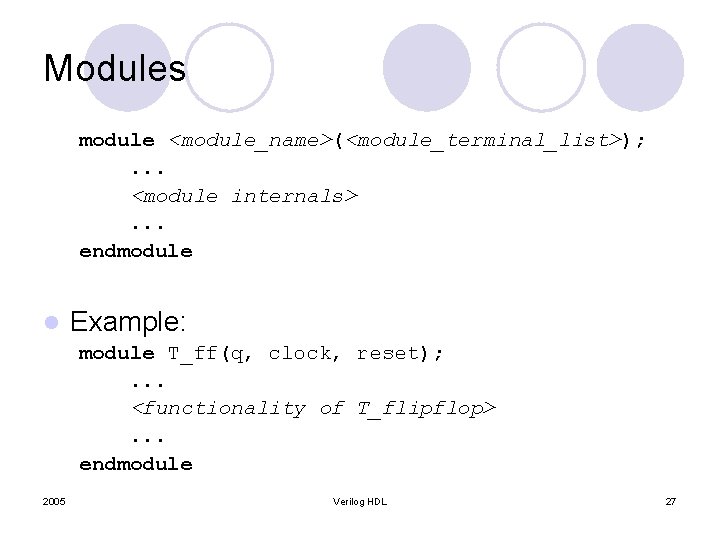

Modules module <module_name>(<module_terminal_list>); . . . <module internals>. . . endmodule l Example: module T_ff(q, clock, reset); . . . <functionality of T_flipflop>. . . endmodule 2005 Verilog HDL 27

Modules (cont’d) l Verilog supported levels of abstraction ¡ Behavioral (algorithmic) level l l ¡ Dataflow level l ¡ Interconnect transistors (MOS transistors) Register-Transfer Level (RTL) ¡ 2005 Interconnect logic gates Switch level l l Describe how data flows between registers and is processed Gate level l ¡ Describe the algorithm used Very similar to C programming Generally known as a combination of behavioral+dataflow that is synthesizable by EDA tools Verilog HDL 28

![Instances module ripplecarrycounterq clk reset output 3 0 q input clk reset 4 TFF Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 TFF](https://slidetodoc.com/presentation_image_h/9c5dccfca7ea10dbd7688d9b9f2da260/image-29.jpg)

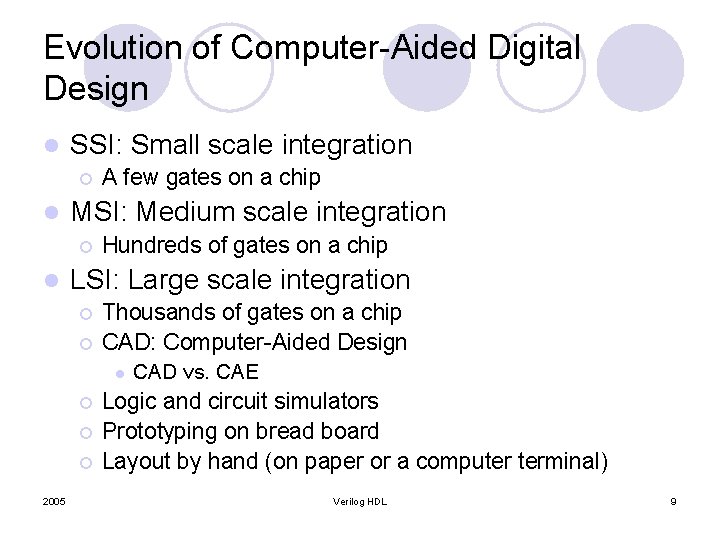

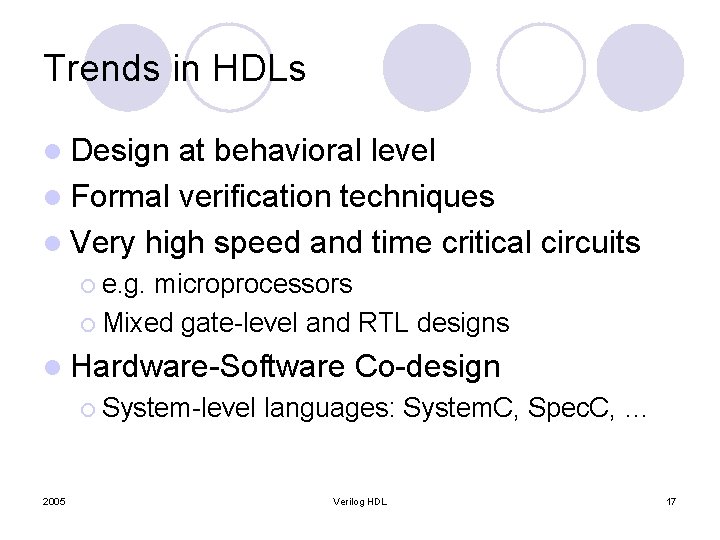

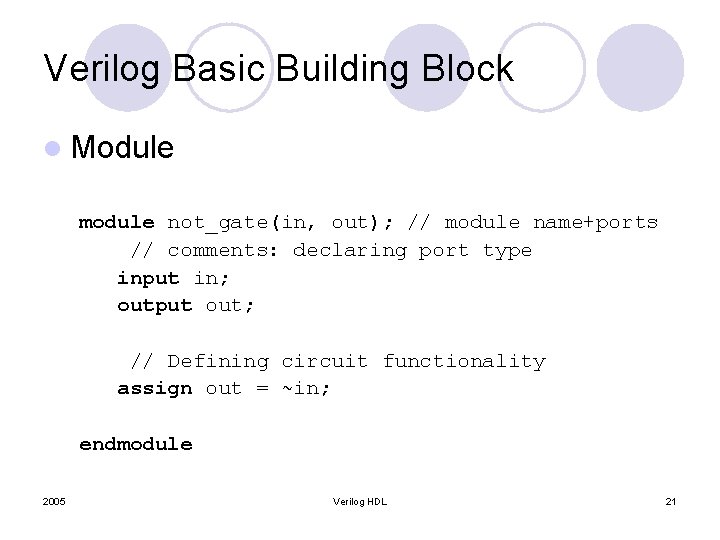

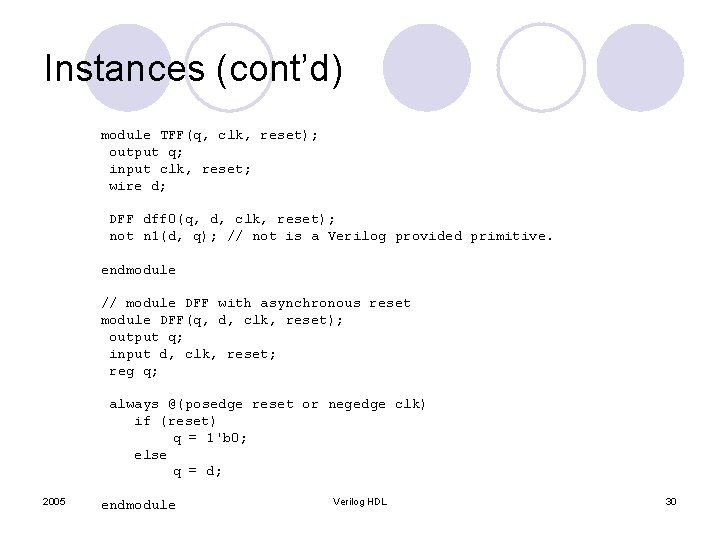

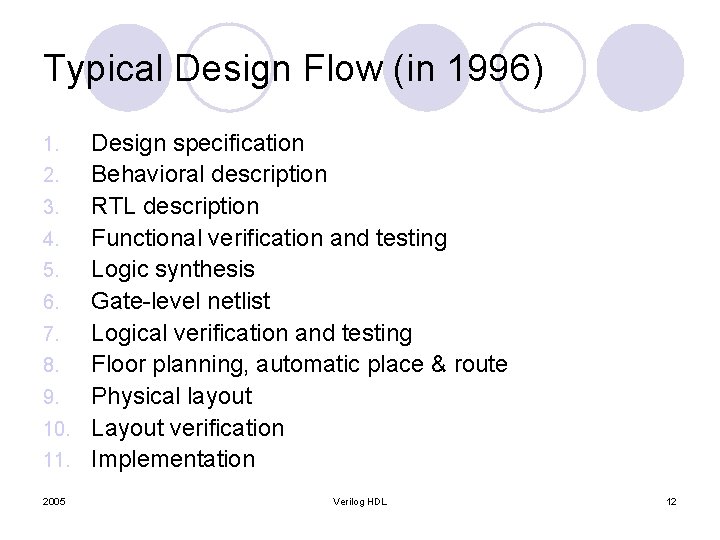

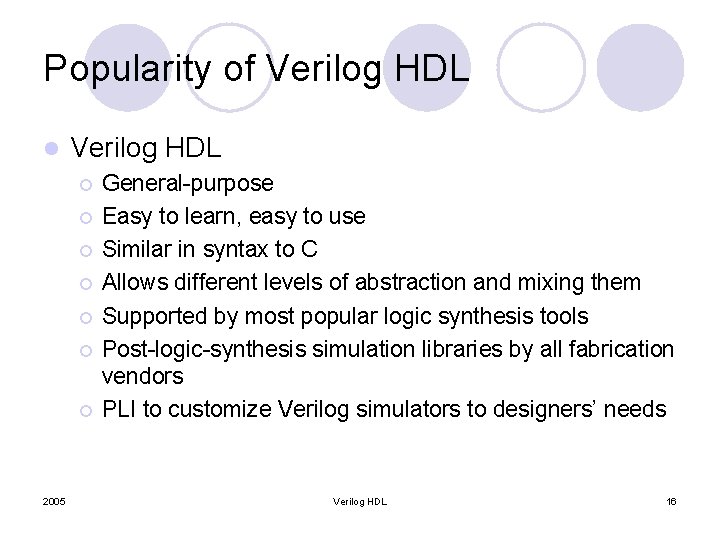

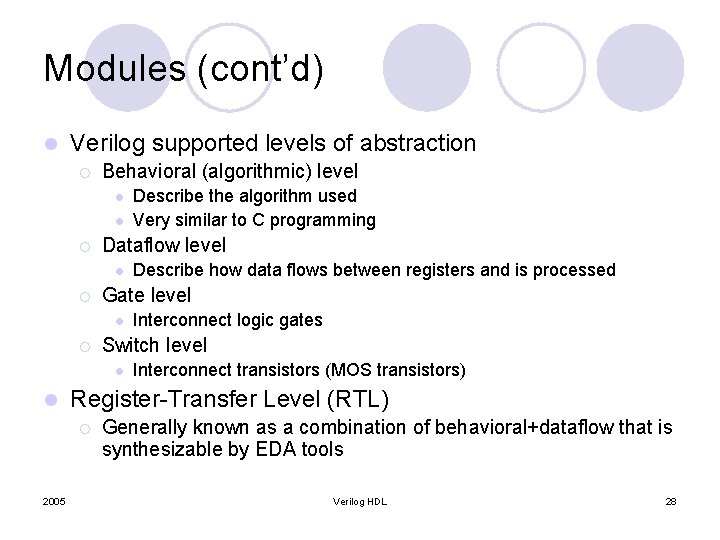

Instances module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 TFF TFF instances of the module TFF are created. tff 0(q[0], clk, reset); tff 1(q[1], q[0], reset); tff 2(q[2], q[1], reset); tff 3(q[3], q[2], reset); endmodule 2005 Verilog HDL 29

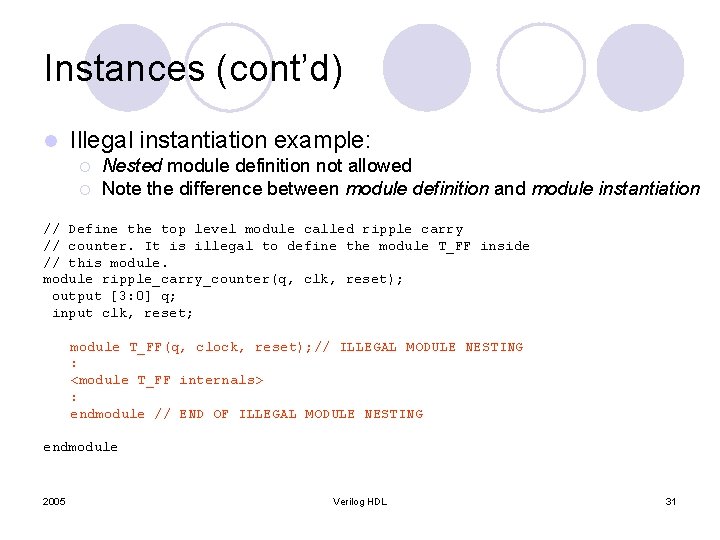

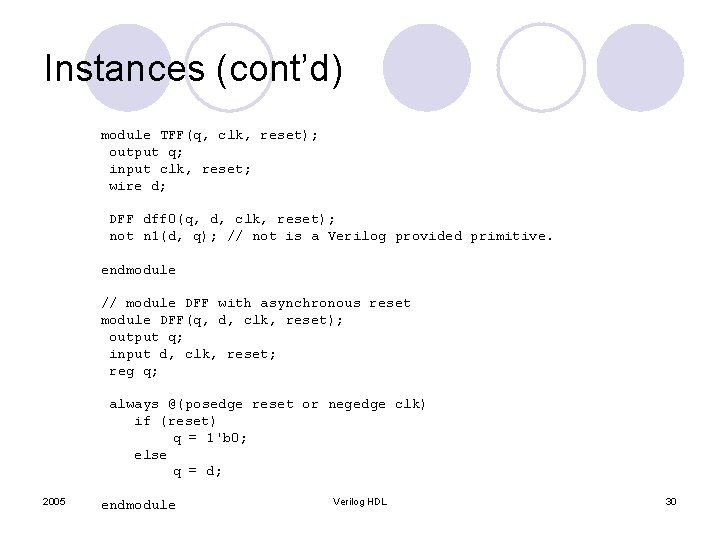

Instances (cont’d) module TFF(q, clk, reset); output q; input clk, reset; wire d; DFF dff 0(q, d, clk, reset); not n 1(d, q); // not is a Verilog provided primitive. endmodule // module DFF with asynchronous reset module DFF(q, d, clk, reset); output q; input d, clk, reset; reg q; always @(posedge reset or negedge clk) if (reset) q = 1'b 0; else q = d; 2005 endmodule Verilog HDL 30

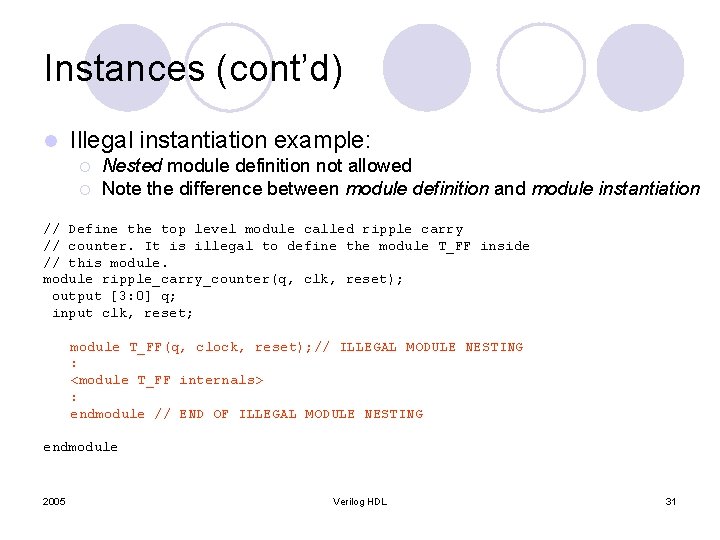

Instances (cont’d) l Illegal instantiation example: ¡ ¡ Nested module definition not allowed Note the difference between module definition and module instantiation // Define the top level module called ripple carry // counter. It is illegal to define the module T_FF inside // this module ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; module T_FF(q, clock, reset); // ILLEGAL MODULE NESTING : <module T_FF internals> : endmodule // END OF ILLEGAL MODULE NESTING endmodule 2005 Verilog HDL 31

Simulation- Test Bench Styles 2005 Verilog HDL 32

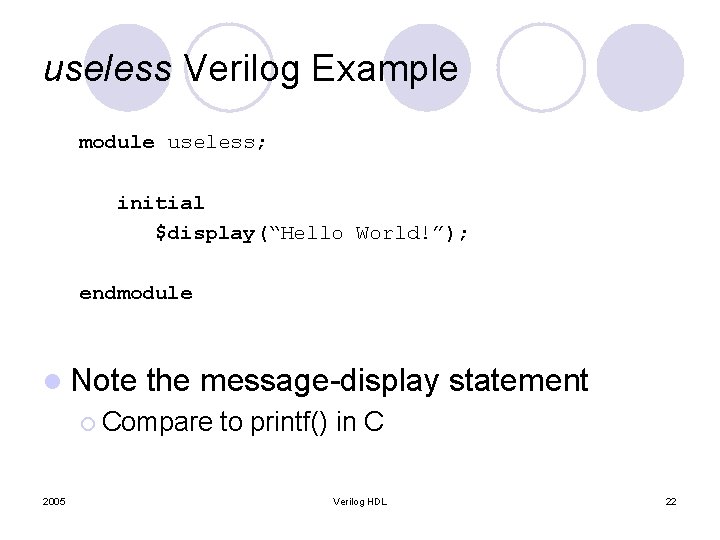

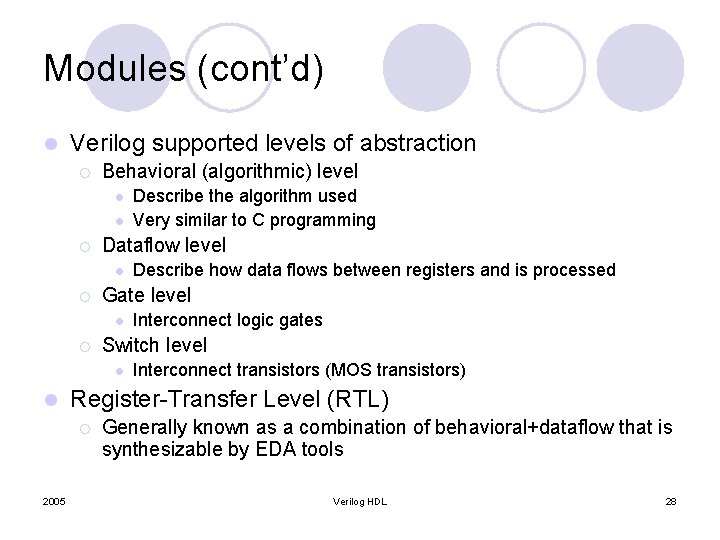

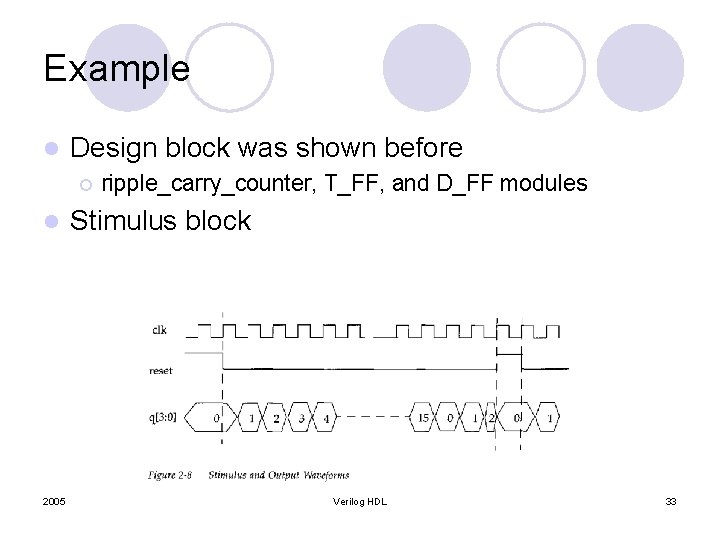

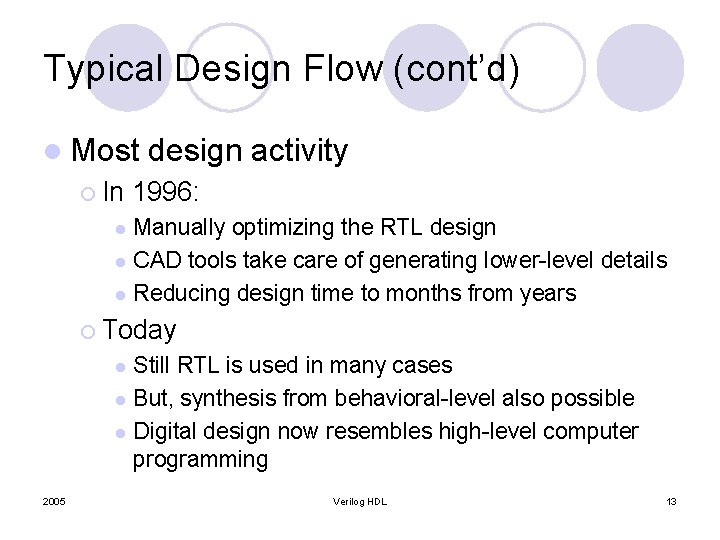

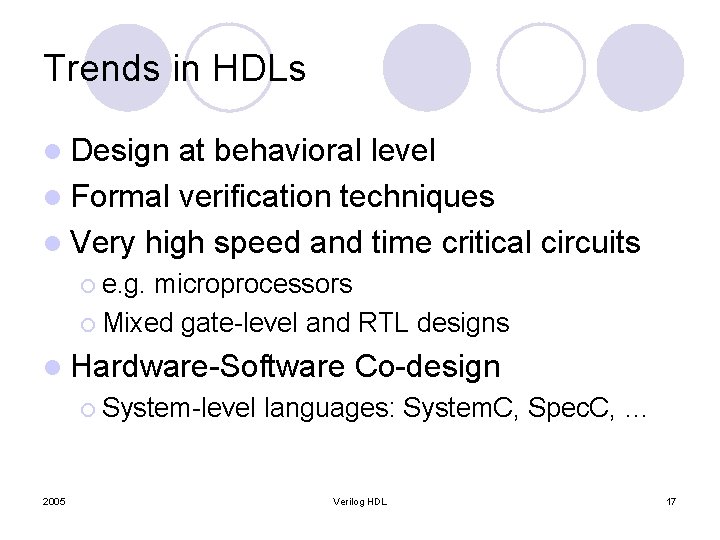

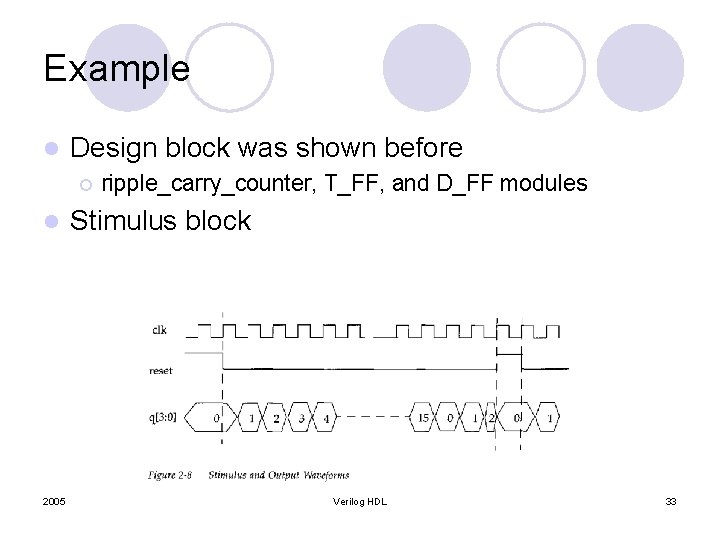

Example l Design block was shown before ¡ l 2005 ripple_carry_counter, T_FF, and D_FF modules Stimulus block Verilog HDL 33

![Example contd module stimulus reg clk reg reset wire3 0 q instantiate the Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the](https://slidetodoc.com/presentation_image_h/9c5dccfca7ea10dbd7688d9b9f2da260/image-34.jpg)

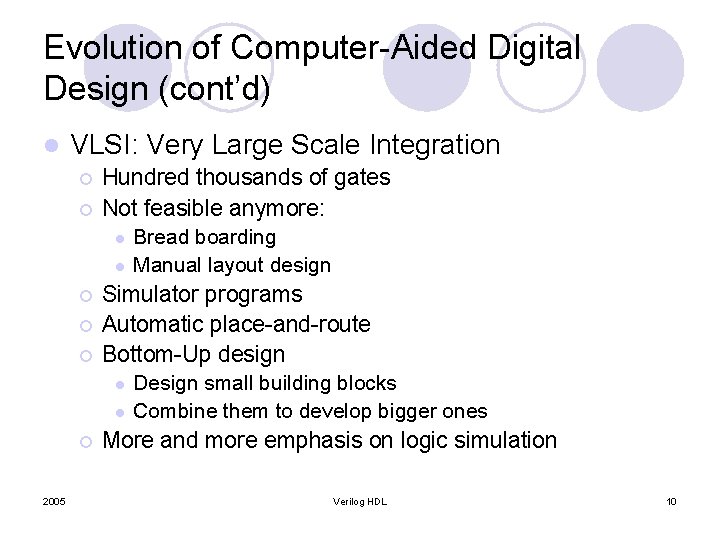

Example (cont’d) module stimulus; reg clk; reg reset; wire[3: 0] q; // instantiate the design block ripple_carry_counter r 1(q, clk, reset); // Control the clk signal that drives the design block. initial clk = 1'b 0; always #5 clk = ~clk; // Control the reset signal that drives the design block initial begin reset = 1'b 1; #15 reset = 1'b 0; #180 reset = 1'b 1; #10 reset = 1'b 0; #20 $stop; end initial // Monitor the outputs $monitor($time, " Output q = %d", q); 2005 Verilog HDL endmodule 34

What we learned today l History of Verilog HDL l Principles of digital design using HDLs l Our first Verilog design example 2005 Verilog HDL 35

Other Notes l Course web-page ¡ http: //ce. sharif. edu/courses l Exercise 1 ¡ Install and use Model. Sim in the lab. to simulate ripple_carry_counter example ¡ Chapter 2005 2 exercises Verilog HDL 36