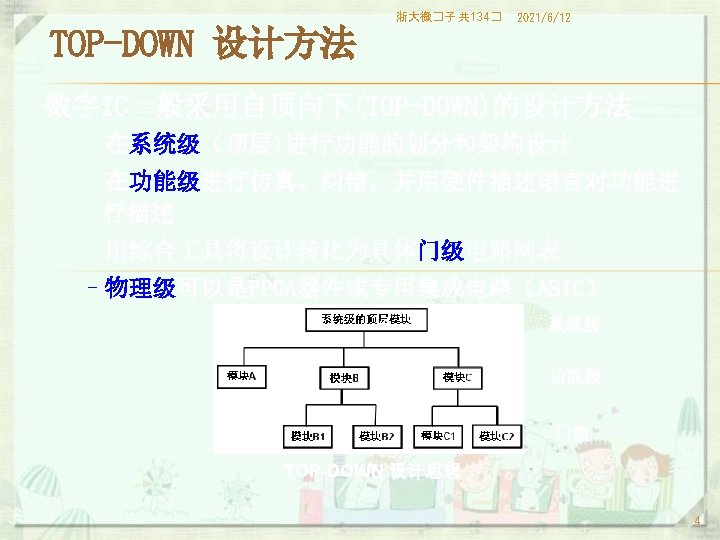

134 VERILOG HDL 2021612 Verilog HDL Verilog HDL

- Slides: 86

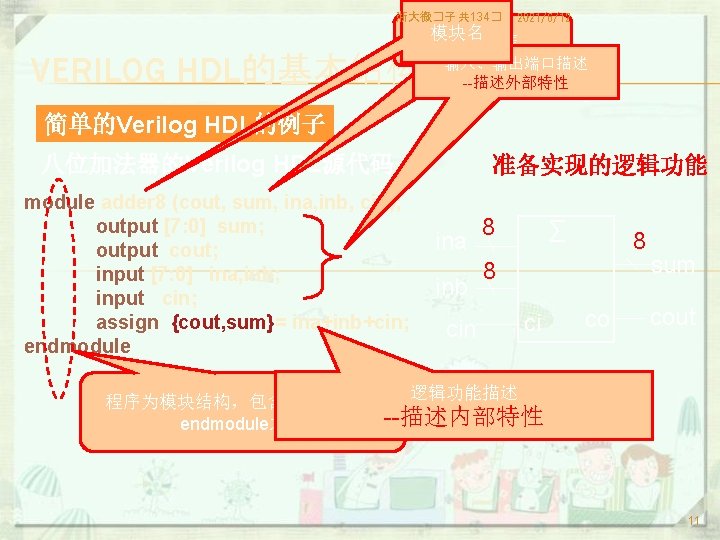

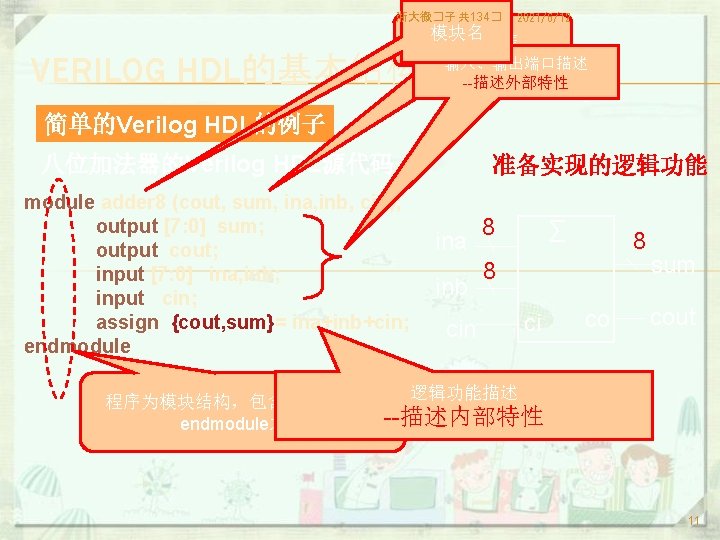

浙大微�子 共 134� VERILOG HDL的基本结构 2021/6/12 模块名 端口列表 输入、输出端口描述 --描述外部特性 简单的Verilog HDL的例子 八位加法器的Verilog HDL源代码 module adder 8 (cout, sum, ina, inb, cin); output [7: 0] sum; output cout; input [7: 0] ina, inb; input cin; assign {cout, sum}= ina+inb+cin; endmodule 准备实现的逻辑功能 ina inb cin 8 ∑ 8 8 ci co sum cout 逻辑功能描述 程序为模块结构,包含在module与 --描述内部特性 endmodule之间 11

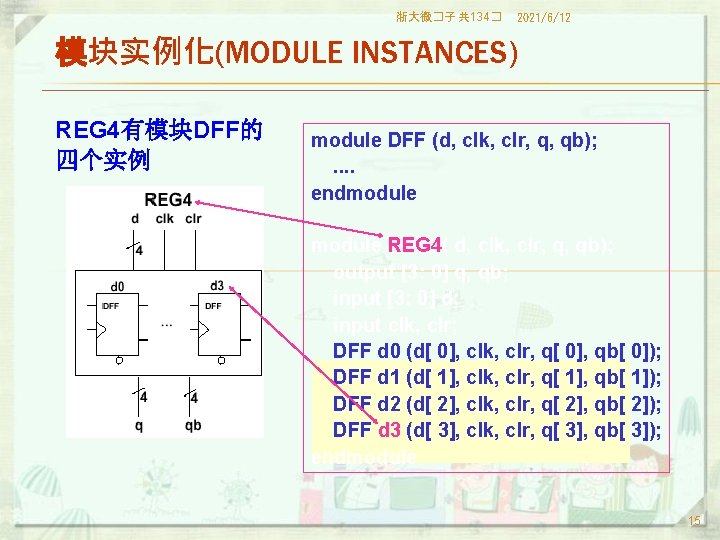

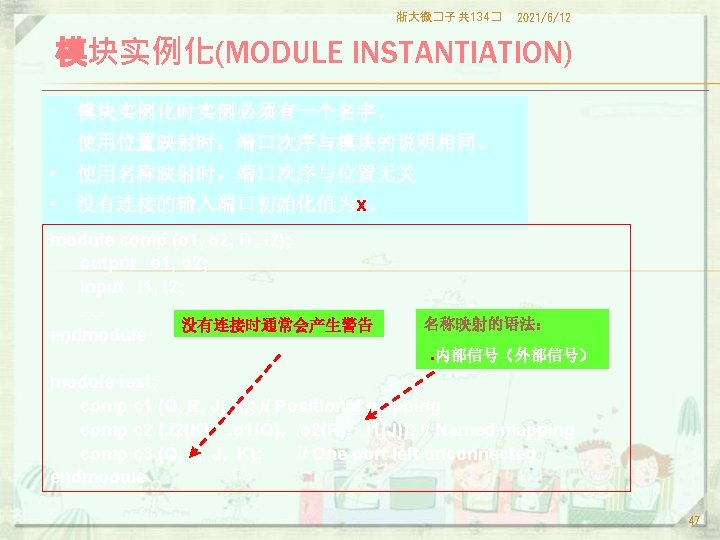

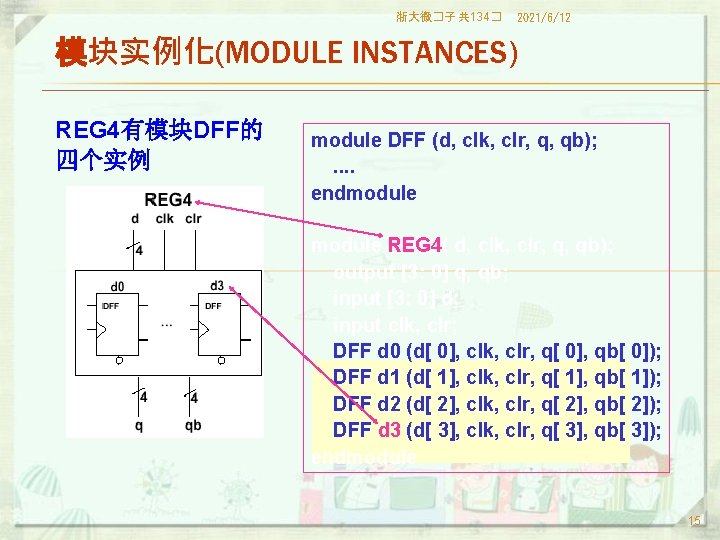

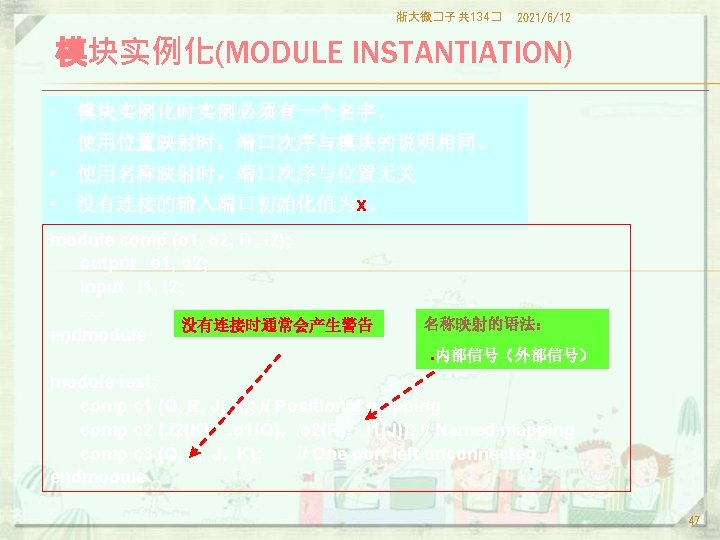

浙大微�子 共 134� 2021/6/12 模块实例化(MODULE INSTANCES) REG 4有模块DFF的 四个实例 module DFF (d, clk, clr, q, qb); . . endmodule REG 4( d, clk, clr, q, qb); output [3: 0] q, qb; input [3: 0] d; input clk, clr; DFF d 0 (d[ 0], clk, clr, q[ 0], qb[ 0]); DFF d 1 (d[ 1], clk, clr, q[ 1], qb[ 1]); DFF d 2 (d[ 2], clk, clr, q[ 2], qb[ 2]); DFF d 3 (d[ 3], clk, clr, q[ 3], qb[ 3]); endmodule 15

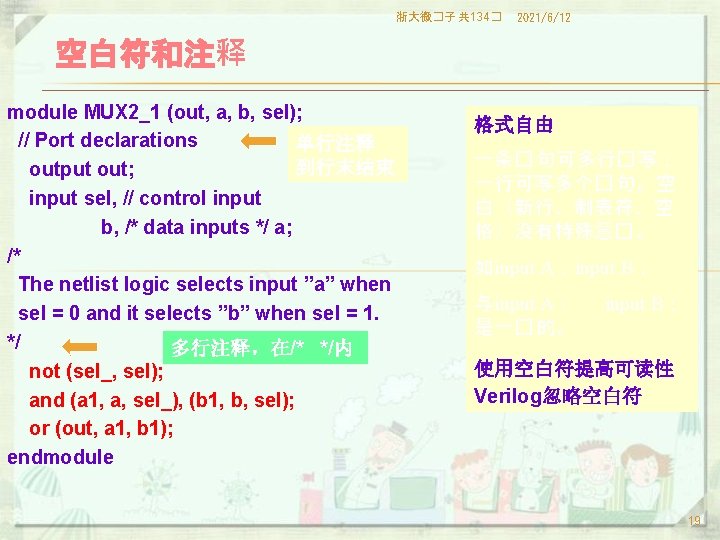

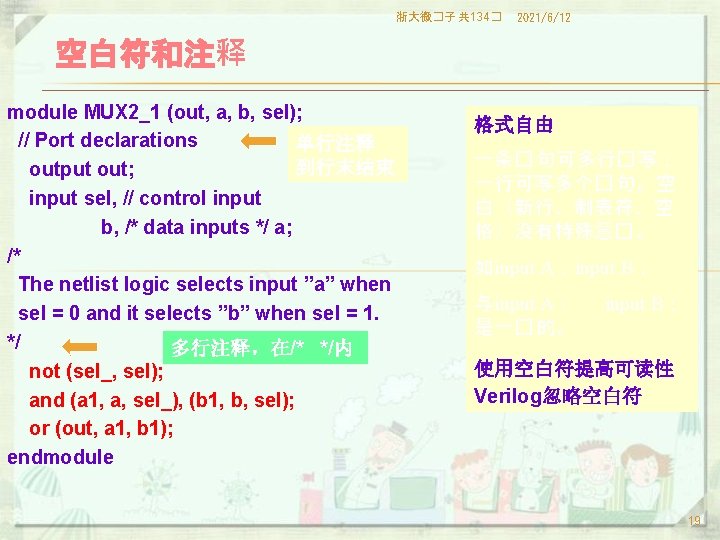

浙大微�子 共 134� 2021/6/12 空白符和注释 module MUX 2_1 (out, a, b, sel); // Port declarations 单行注释 到行末结束 output out; input sel, // control input b, /* data inputs */ a; /* The netlist logic selects input ”a” when sel = 0 and it selects ”b” when sel = 1. */ 多行注释,在/* */内 not (sel_, sel); and (a 1, a, sel_), (b 1, b, sel); or (out, a 1, b 1); endmodule 格式自由 一条� 句可多行� 写; 一行可写多个� 句。空 白(新行、制表符、空 格)没有特殊意� 。 如input A;input B; 与input A; 是一� 的。 input B; 使用空白符提高可读性 Verilog忽略空白符 19

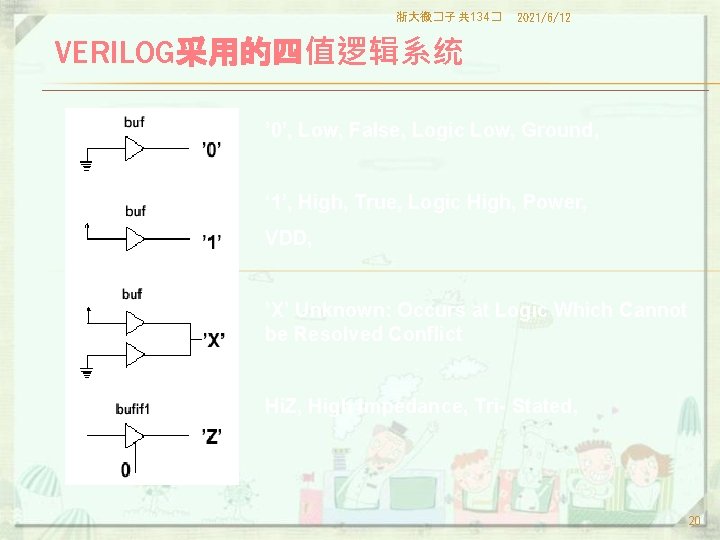

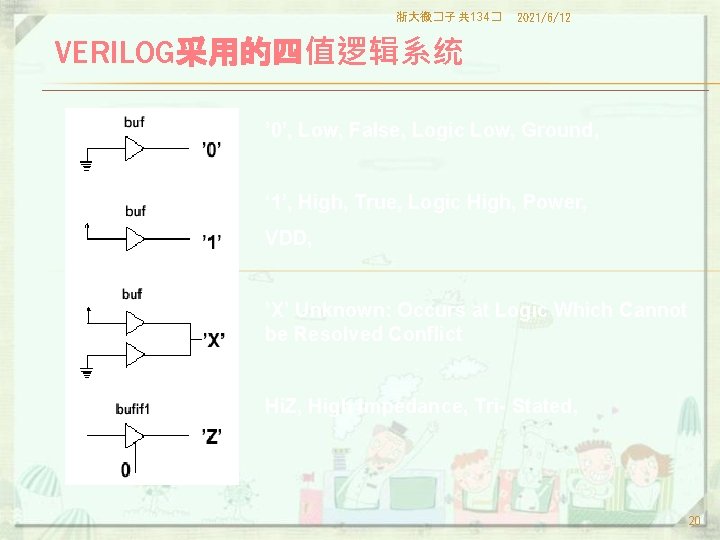

浙大微�子 共 134� 2021/6/12 VERILOG采用的四值逻辑系统 ’ 0’, Low, False, Logic Low, Ground, ‘ 1’, High, True, Logic High, Power, VDD, ’X’ Unknown: Occurs at Logic Which Cannot be Resolved Conflict Hi. Z, High Impedance, Tri- Stated, 20

浙大微�子 共 134� 2021/6/12 字符串(STRING) 格式符 %h %o %d %b %c %s %m %t hex oct dec bin ACSII string module time 转义符 t n \ ” <1 -3 digit octal number> tab 换行 反斜杠 双引号 ASCII representation of above 22

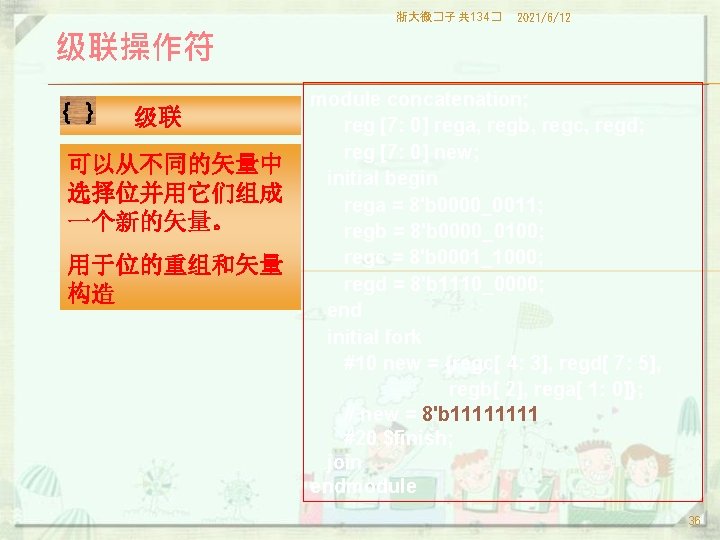

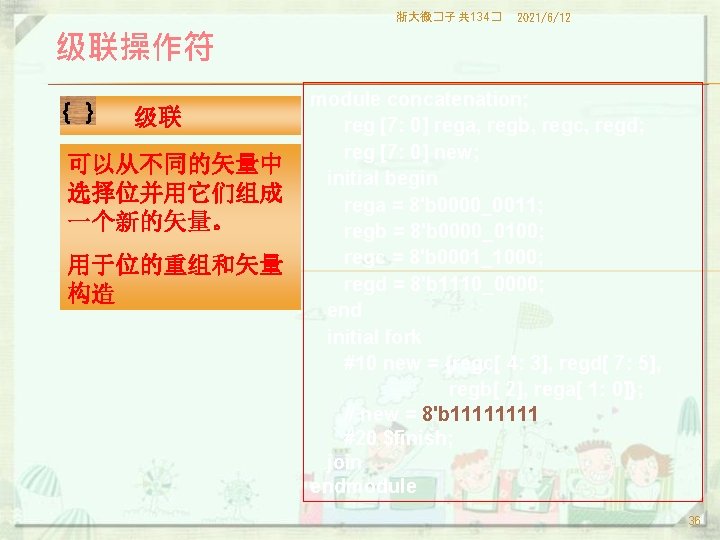

浙大微�子 共 134� 2021/6/12 级联操作符 { } 级联 可以从不同的矢量中 选择位并用它们组成 一个新的矢量。 用于位的重组和矢量 构造 module concatenation; reg [7: 0] rega, regb, regc, regd; reg [7: 0] new; initial begin rega = 8'b 0000_0011; regb = 8'b 0000_0100; regc = 8'b 0001_1000; regd = 8'b 1110_0000; end initial fork #10 new = {regc[ 4: 3], regd[ 7: 5], regb[ 2], rega[ 1: 0]}; // new = 8'b 1111 #20 $finish; join endmodule 36

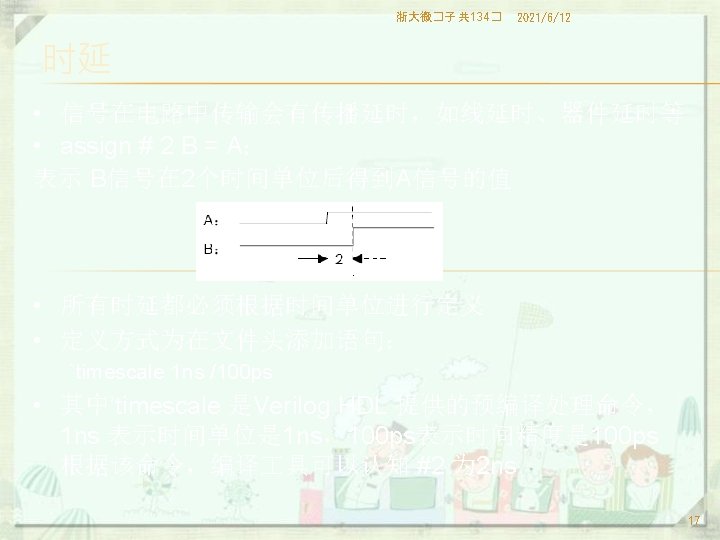

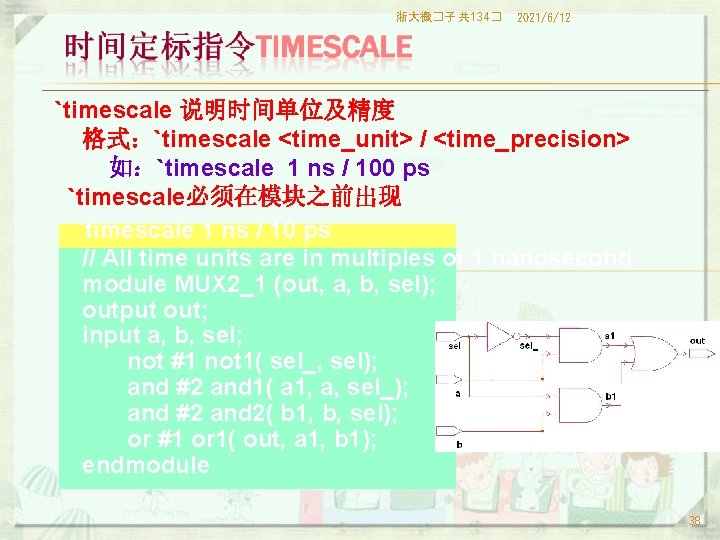

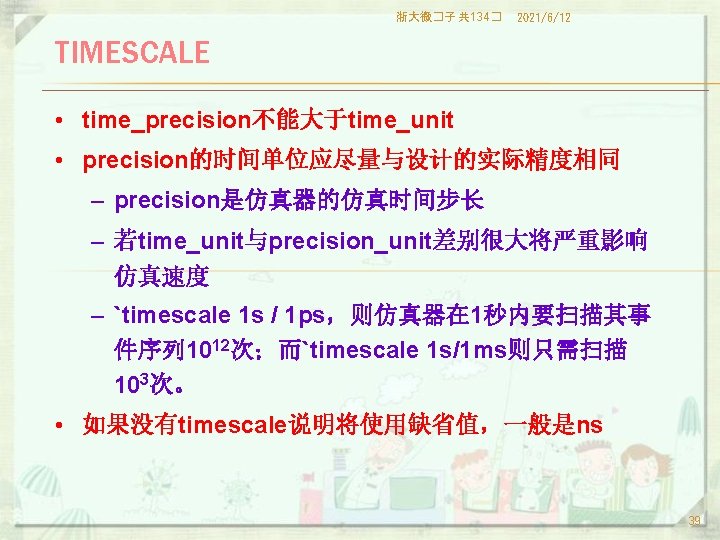

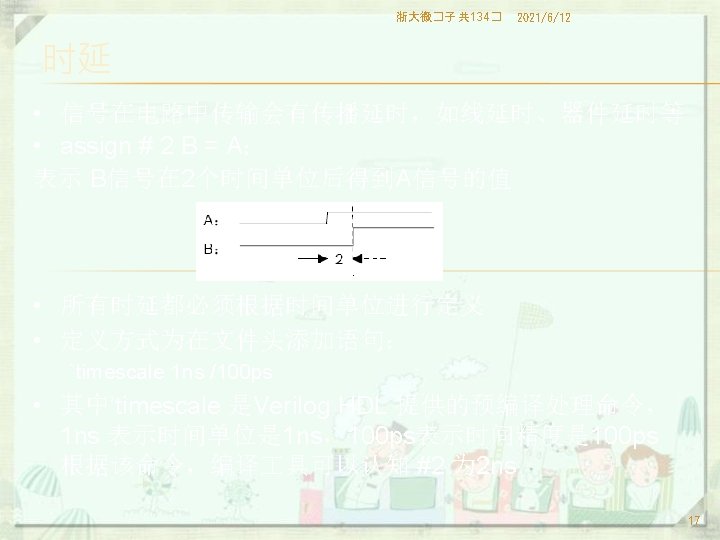

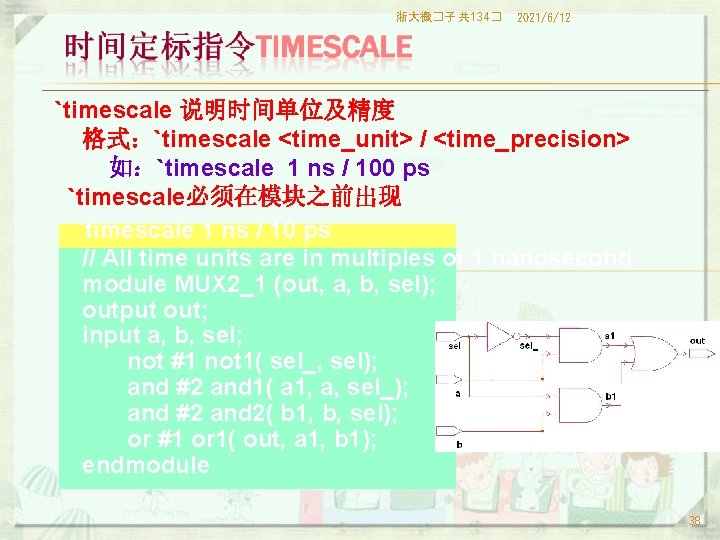

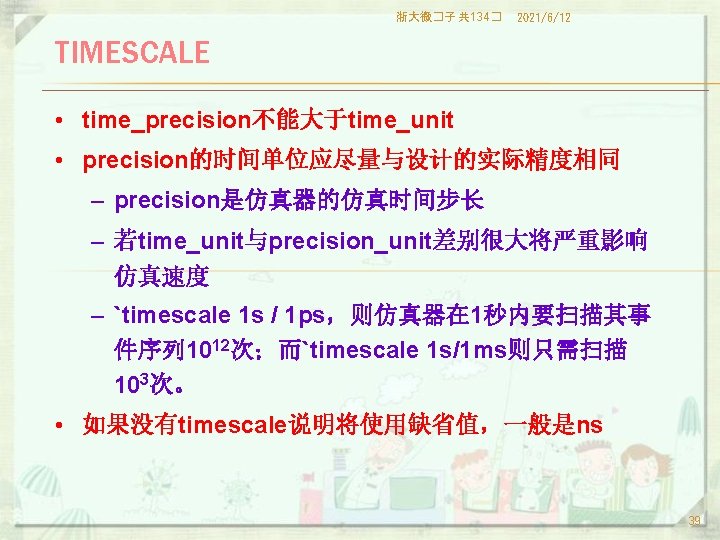

浙大微�子 共 134� 2021/6/12 `timescale 说明时间单位及精度 格式:`timescale <time_unit> / <time_precision> 如:`timescale 1 ns / 100 ps `timescale必须在模块之前出现 `timescale 1 ns / 10 ps // All time units are in multiples of 1 nanosecond module MUX 2_1 (out, a, b, sel); output out; input a, b, sel; not #1 not 1( sel_, sel); and #2 and 1( a 1, a, sel_); and #2 and 2( b 1, b, sel); or #1 or 1( out, a 1, b 1); endmodule 38

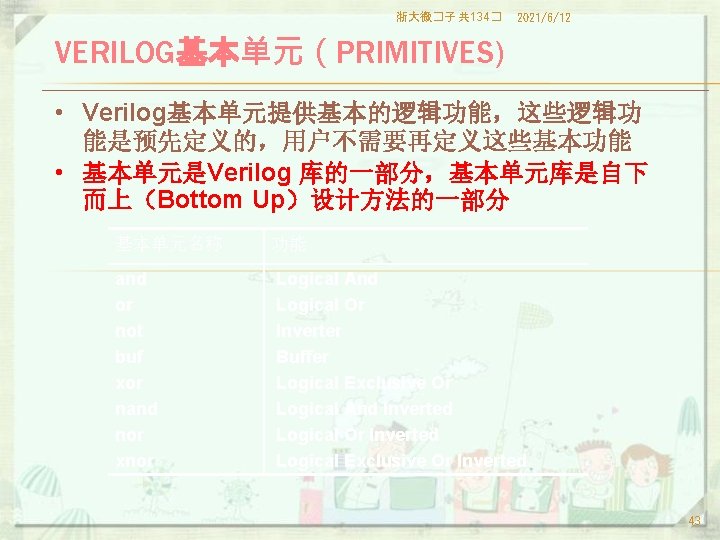

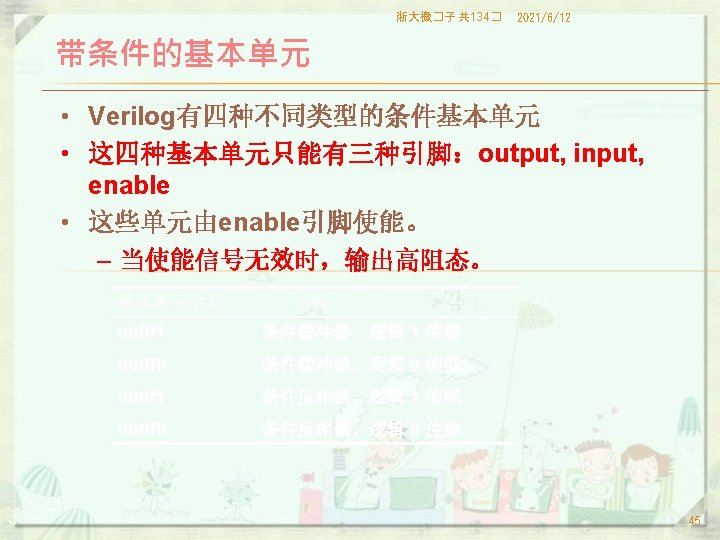

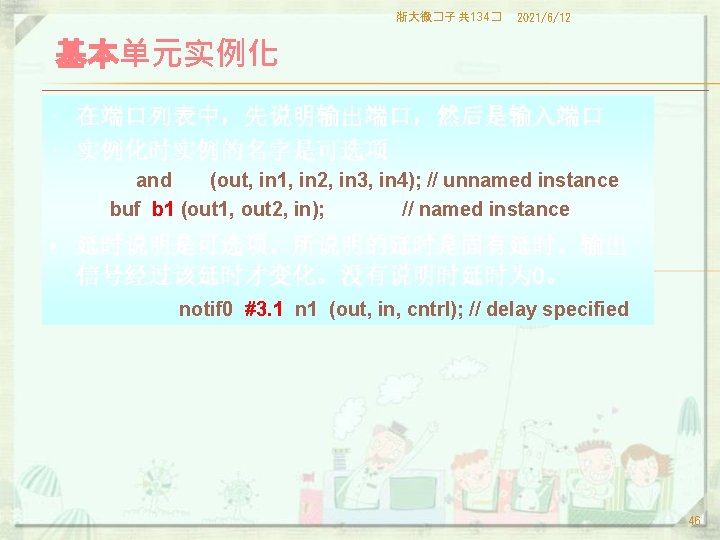

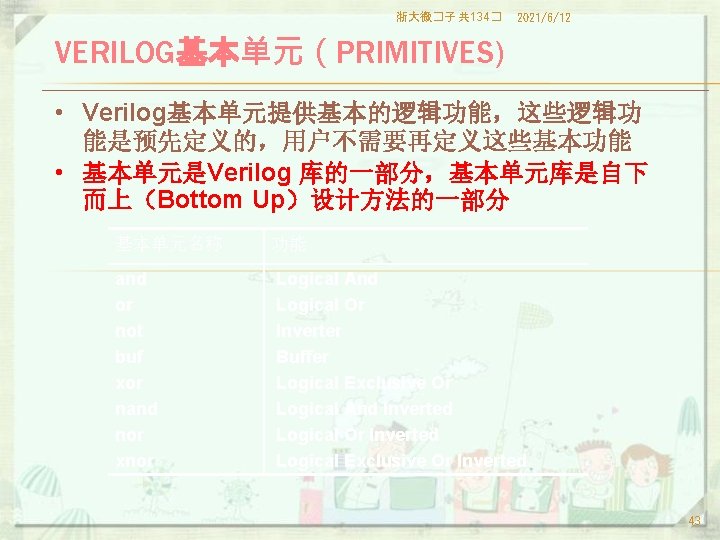

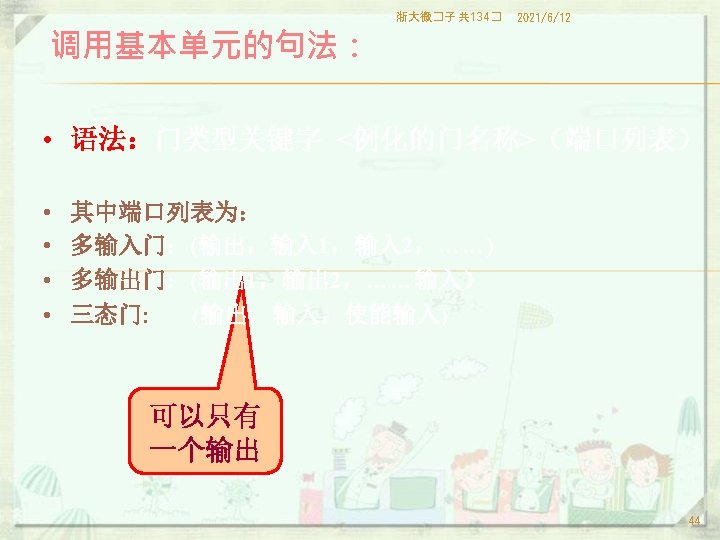

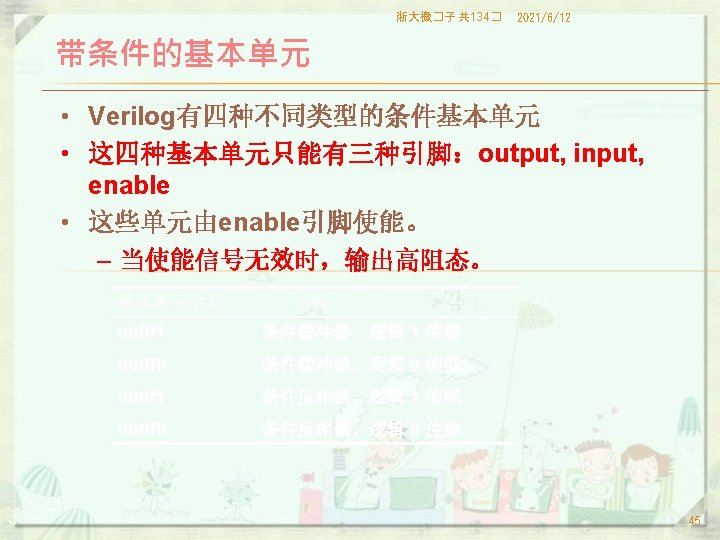

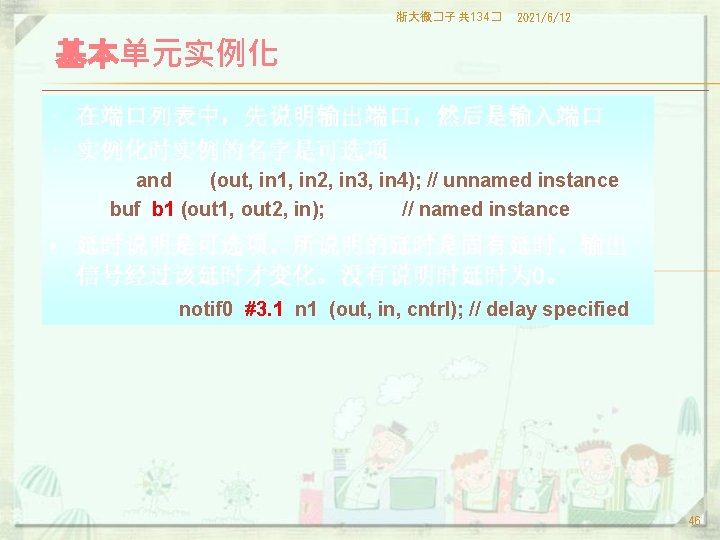

浙大微�子 共 134� 2021/6/12 VERILOG基本单元(PRIMITIVES) • Verilog基本单元提供基本的逻辑功能,这些逻辑功 能是预先定义的,用户不需要再定义这些基本功能 • 基本单元是Verilog 库的一部分,基本单元库是自下 而上(Bottom Up)设计方法的一部分 基本单元名称 功能 and or not buf xor nand nor xnor Logical And Logical Or Inverter Buffer Logical Exclusive Or Logical And Inverted Logical Or Inverted Logical Exclusive Or Inverted 43

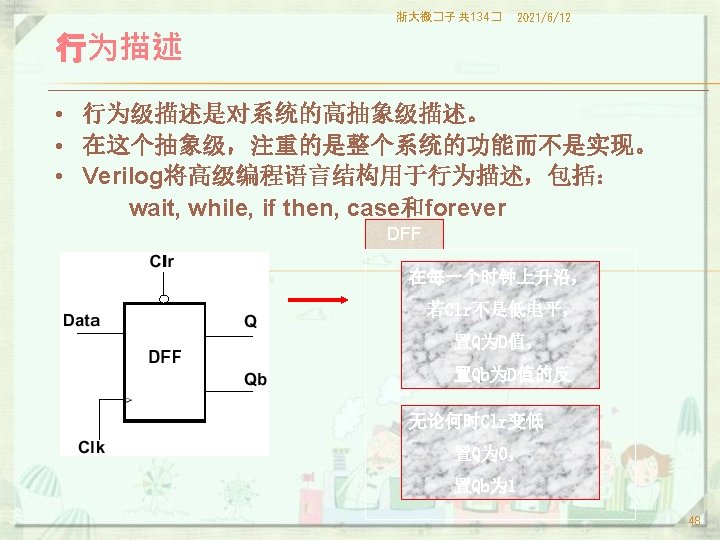

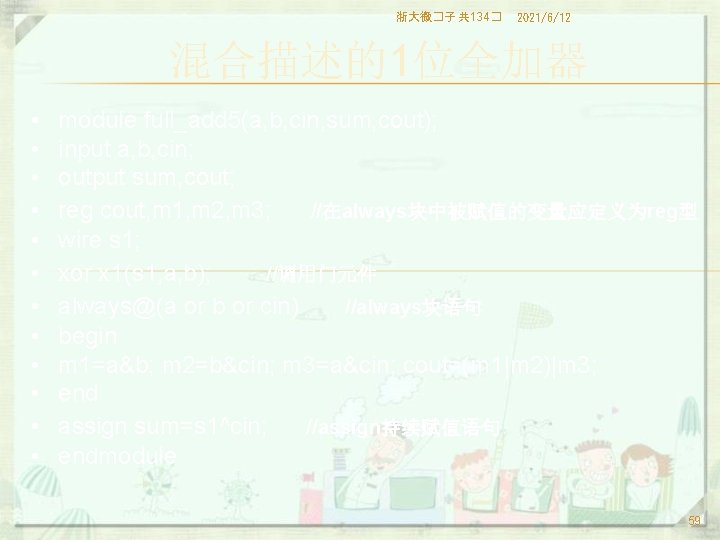

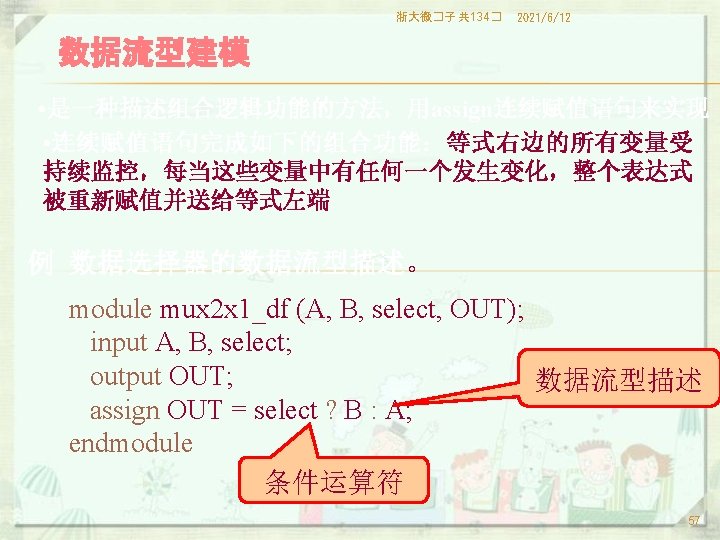

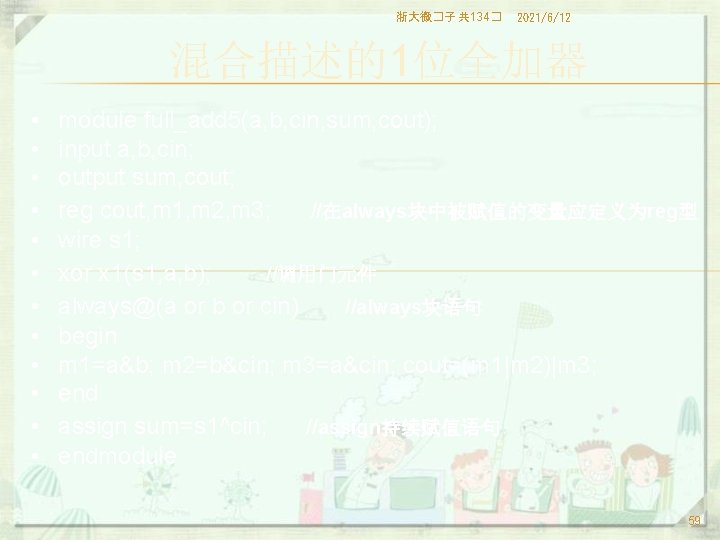

浙大微�子 共 134� 2021/6/12 混合描述的1位全加器 • • • module full_add 5(a, b, cin, sum, cout); input a, b, cin; output sum, cout; reg cout, m 1, m 2, m 3; //在always块中被赋值的变量应定义为reg型 wire s 1; xor x 1(s 1, a, b); //调用门元件 always@(a or b or cin) //always块语句 begin m 1=a&b; m 2=b&cin; m 3=a&cin; cout=(m 1|m 2)|m 3; end assign sum=s 1^cin; //assign持续赋值语句 endmodule 59

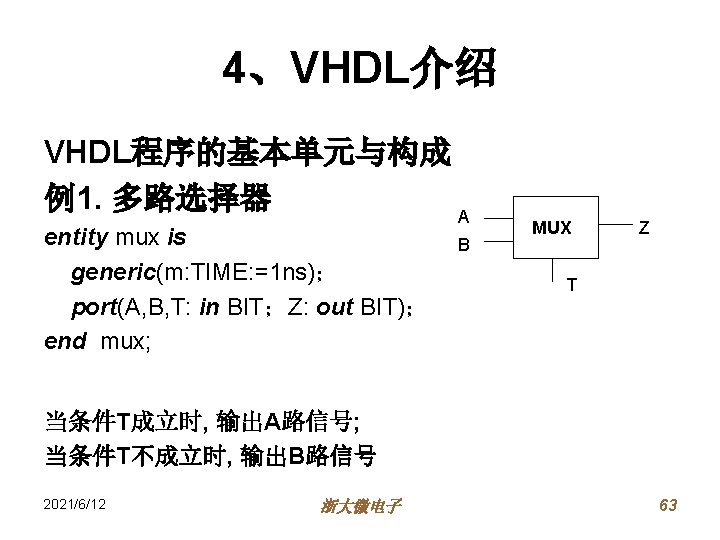

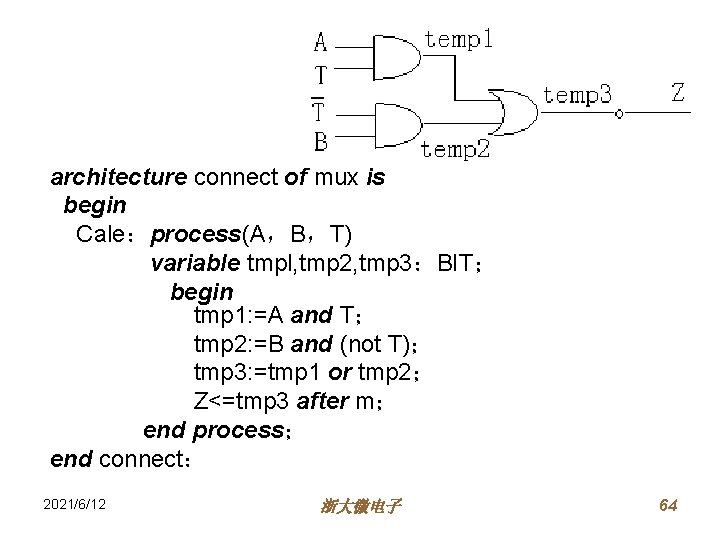

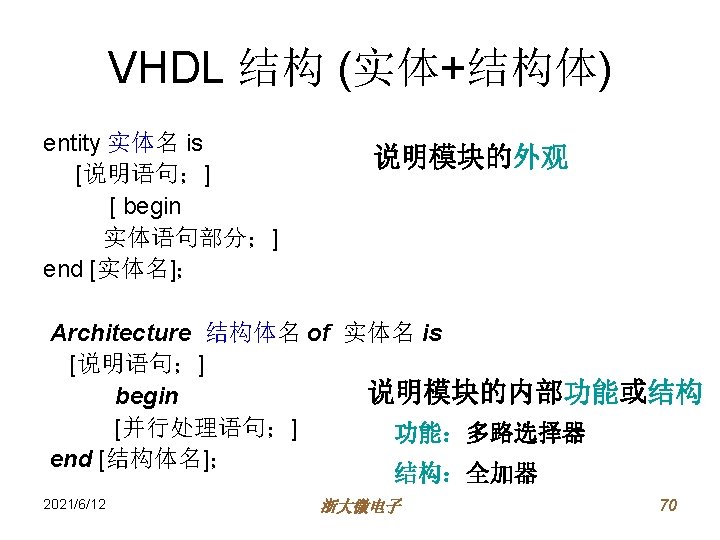

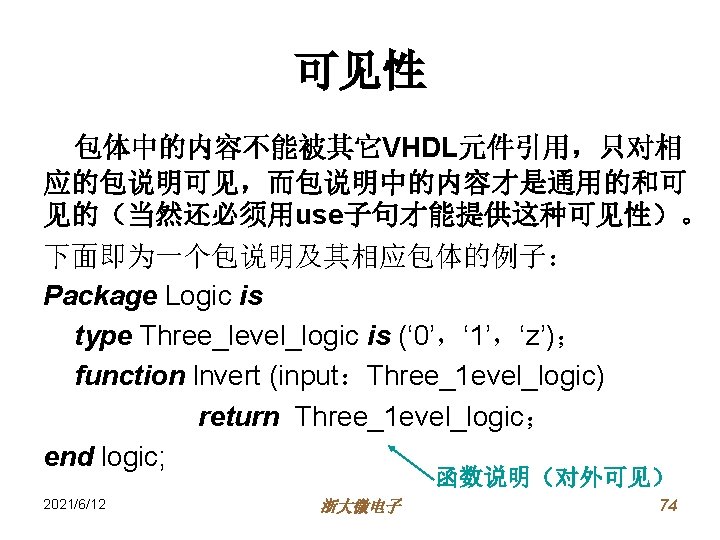

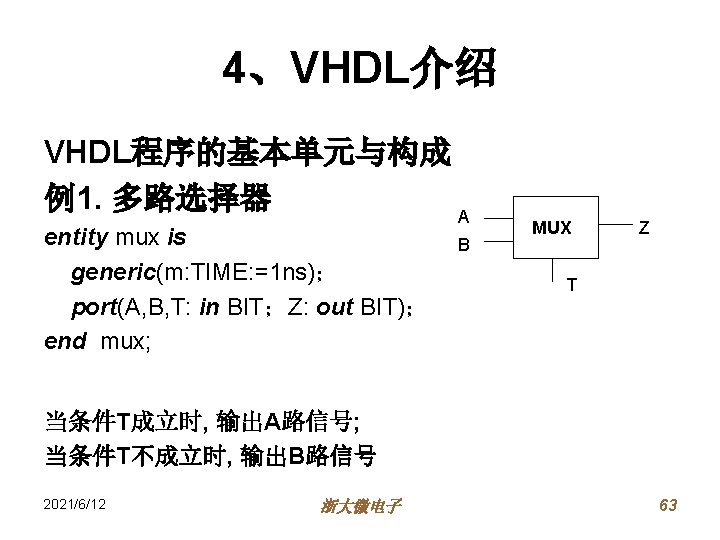

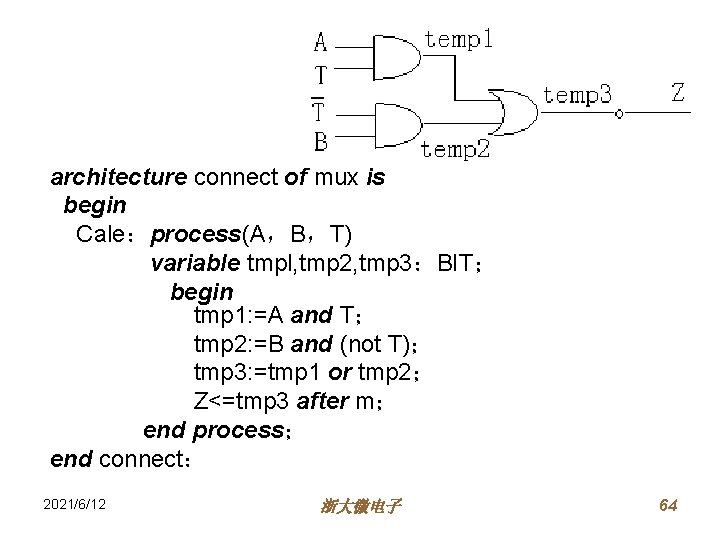

architecture connect of mux is begin Cale:process(A,B,T) variable tmpl, tmp 2, tmp 3:BIT; begin tmp 1: =A and T; tmp 2: =B and (not T); tmp 3: =tmp 1 or tmp 2; Z<=tmp 3 after m; end process; end connect: 2021/6/12 浙大微电子 64

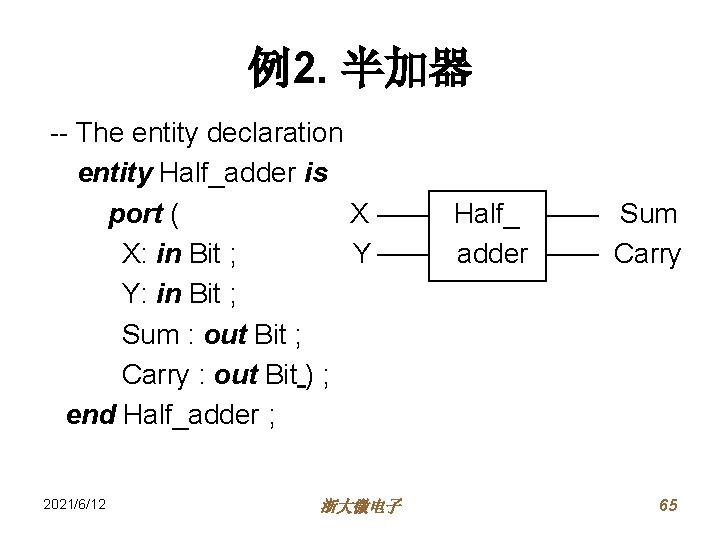

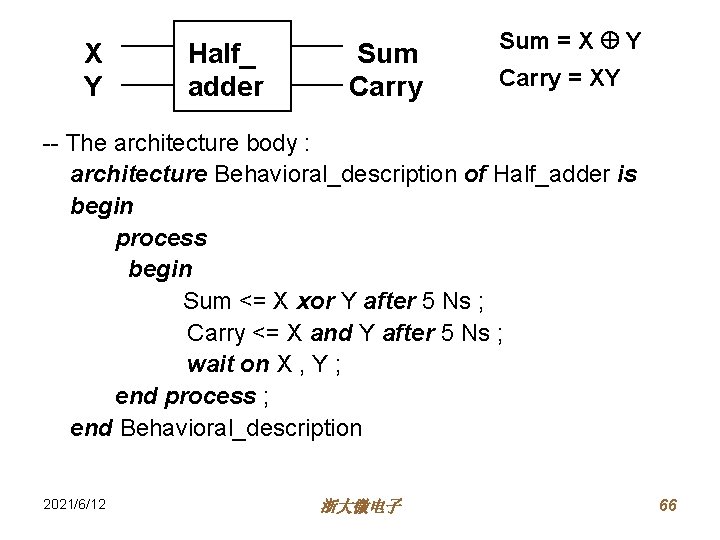

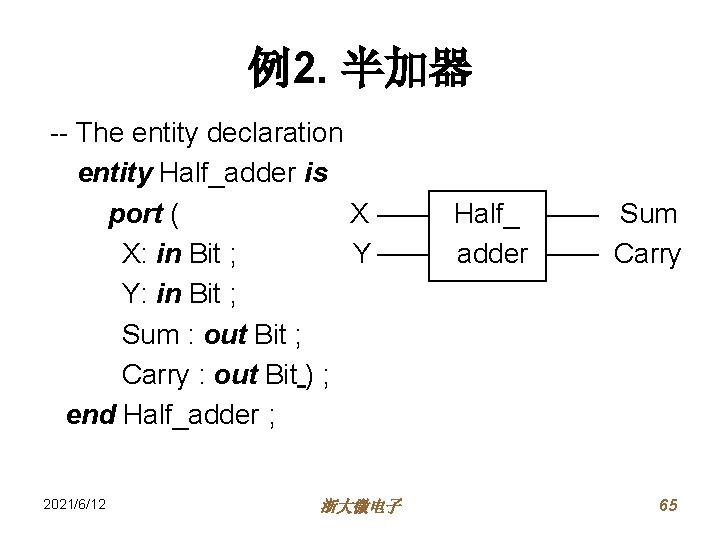

例2. 半加器 -- The entity declaration entity Half_adder is port ( X X: in Bit ; Y Y: in Bit ; Sum : out Bit ; Carry : out Bit ) ; end Half_adder ; 2021/6/12 浙大微电子 Half_ adder Sum Carry 65

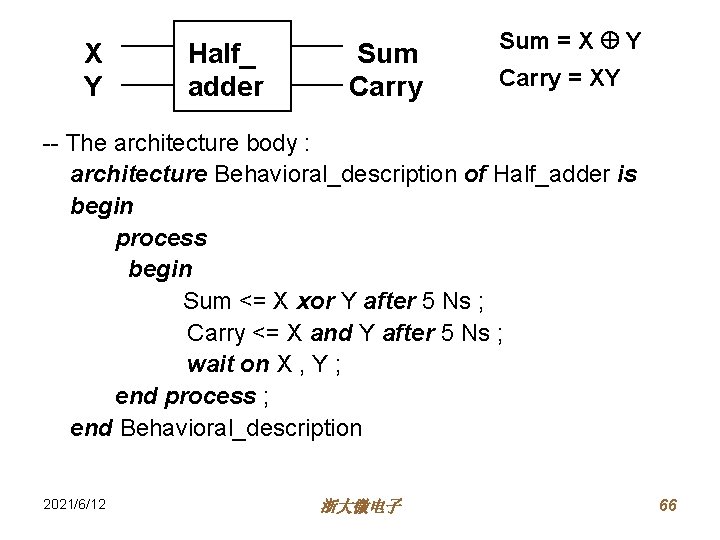

X Y Half_ adder Sum Carry Sum = X Y Carry = XY -- The architecture body : architecture Behavioral_description of Half_adder is begin process begin Sum <= X xor Y after 5 Ns ; Carry <= X and Y after 5 Ns ; wait on X , Y ; end process ; end Behavioral_description 2021/6/12 浙大微电子 66

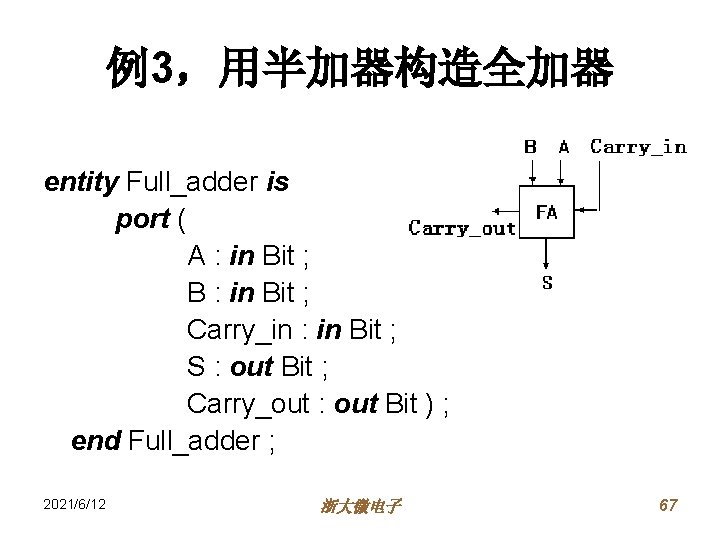

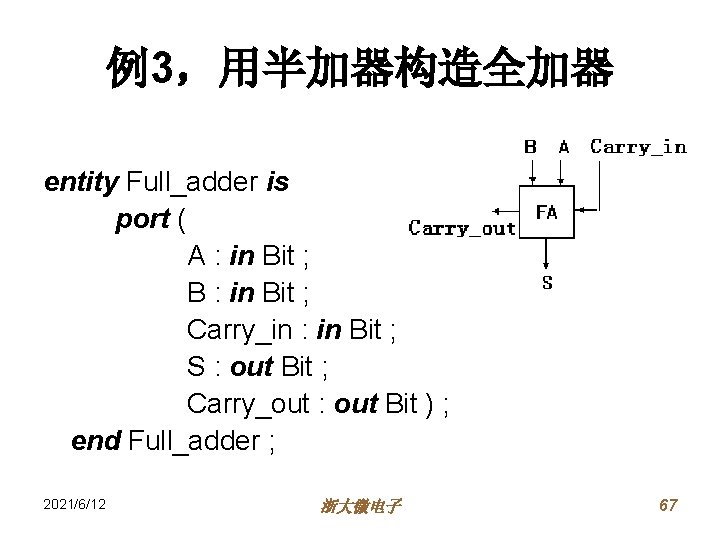

例3,用半加器构造全加器 entity Full_adder is port ( A : in Bit ; B : in Bit ; Carry_in : in Bit ; S : out Bit ; Carry_out : out Bit ) ; end Full_adder ; 2021/6/12 浙大微电子 67

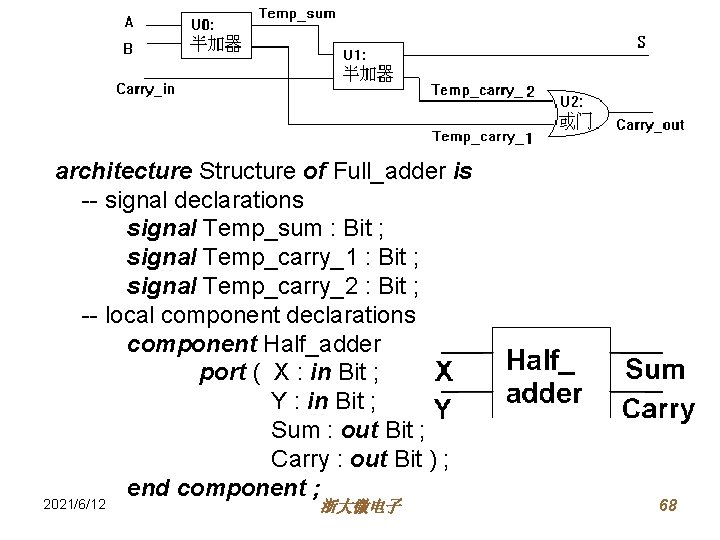

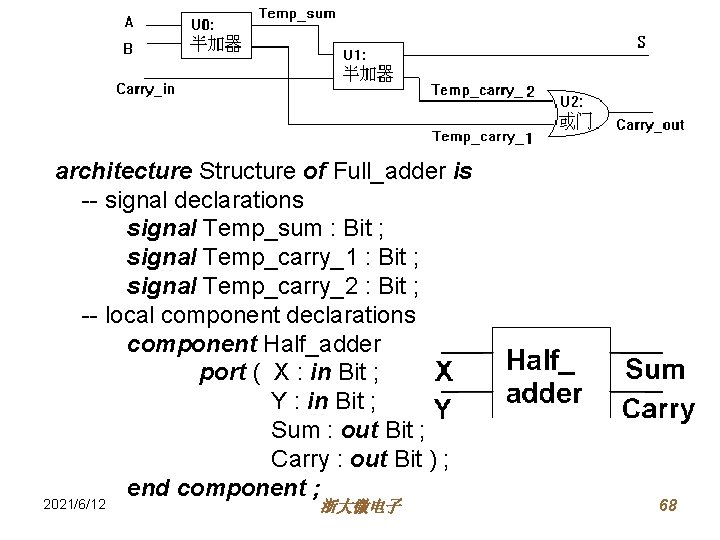

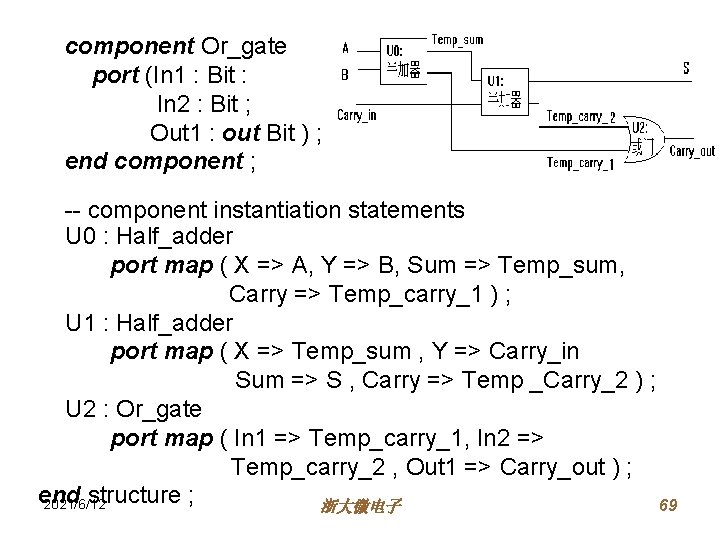

architecture Structure of Full_adder is -- signal declarations signal Temp_sum : Bit ; signal Temp_carry_1 : Bit ; signal Temp_carry_2 : Bit ; -- local component declarations component Half_adder port ( X : in Bit ; Y : in Bit ; Sum : out Bit ; Carry : out Bit ) ; end component ; 2021/6/12 浙大微电子 68

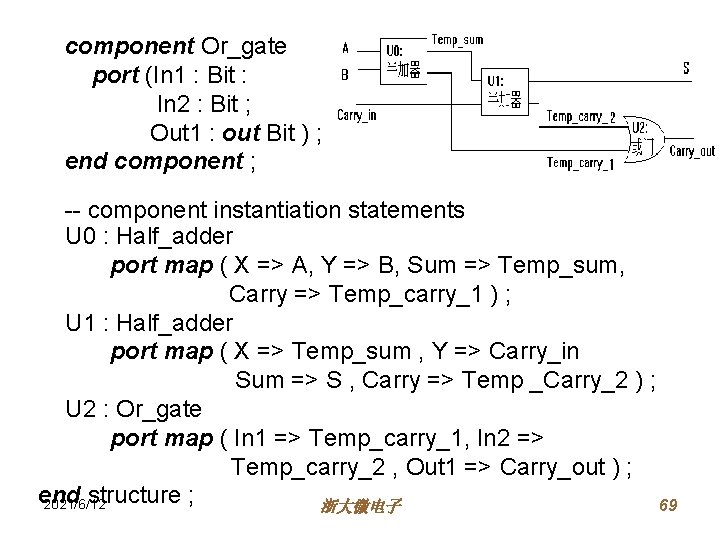

component Or_gate port (In 1 : Bit : In 2 : Bit ; Out 1 : out Bit ) ; end component ; -- component instantiation statements U 0 : Half_adder port map ( X => A, Y => B, Sum => Temp_sum, Carry => Temp_carry_1 ) ; U 1 : Half_adder port map ( X => Temp_sum , Y => Carry_in Sum => S , Carry => Temp _Carry_2 ) ; U 2 : Or_gate port map ( In 1 => Temp_carry_1, In 2 => Temp_carry_2 , Out 1 => Carry_out ) ; end structure ; 2021/6/12 69 浙大微电子

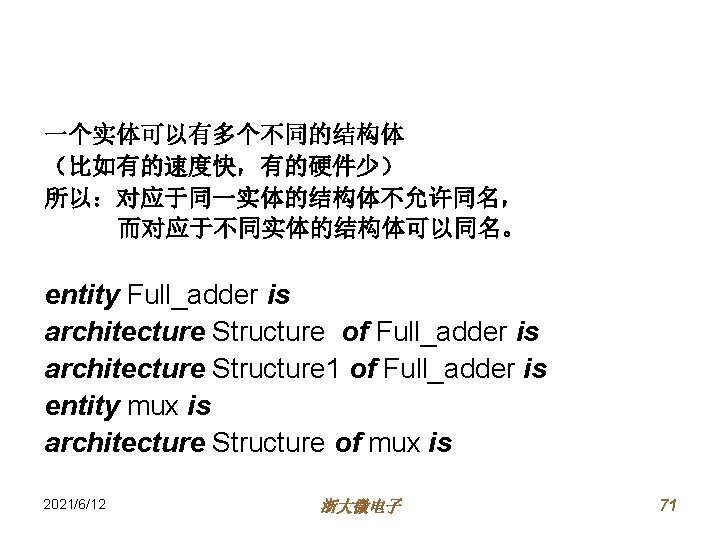

一个实体可以有多个不同的结构体 (比如有的速度快,有的硬件少) 所以:对应于同一实体的结构体不允许同名, 而对应于不同实体的结构体可以同名。 entity Full_adder is architecture Structure of Full_adder is architecture Structure 1 of Full_adder is entity mux is architecture Structure of mux is 2021/6/12 浙大微电子 71

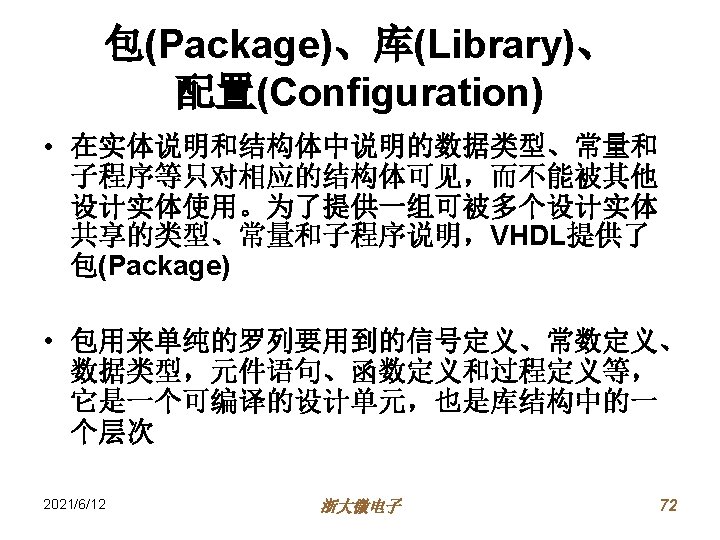

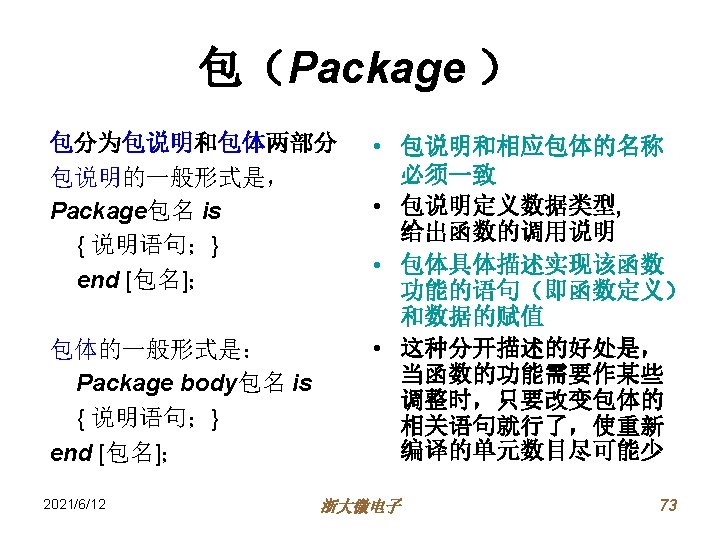

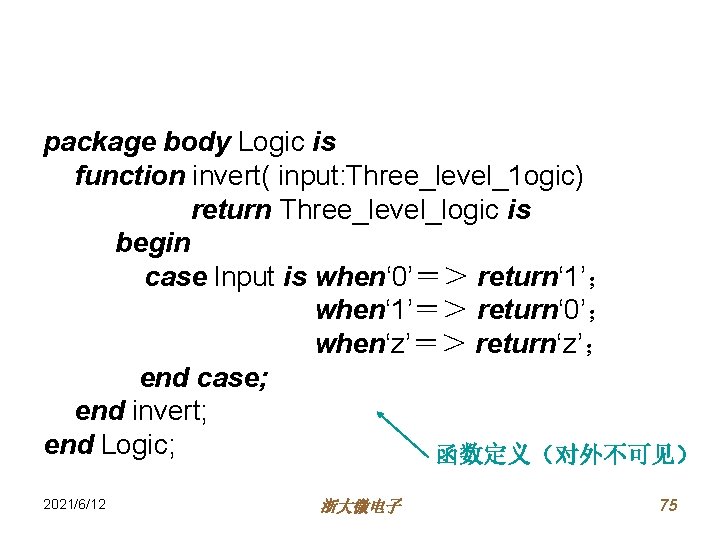

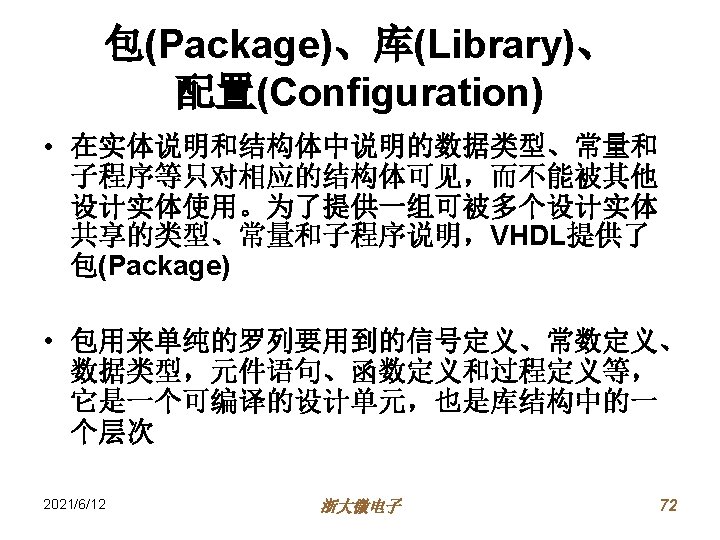

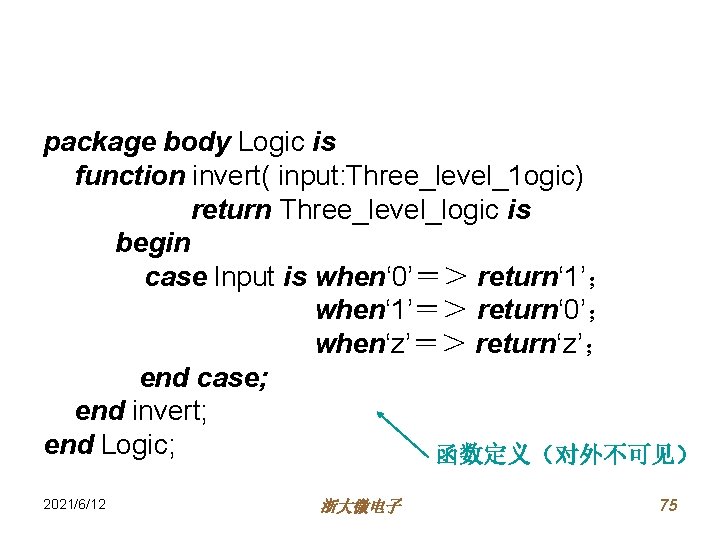

package body Logic is function invert( input: Three_level_1 ogic) return Three_level_logic is begin case lnput is when‘ 0’=> return‘ 1’; when‘ 1’=> return‘ 0’; when‘z’=> return‘z’; end case; end invert; end Logic; 函数定义(对外不可见) 2021/6/12 浙大微电子 75

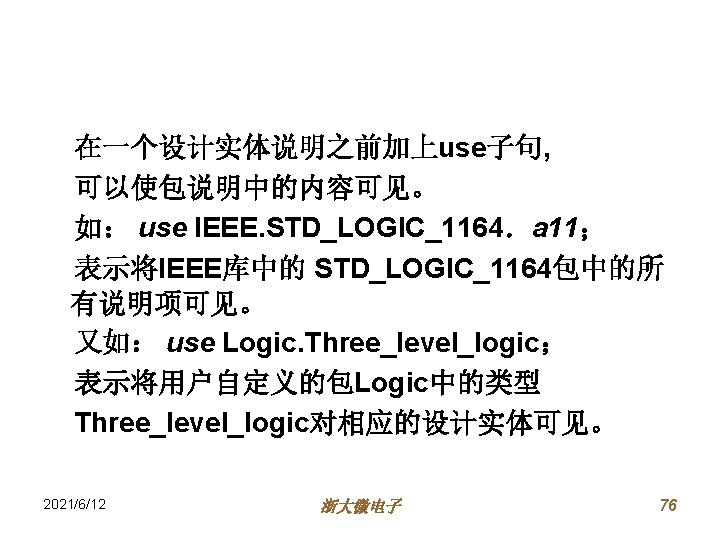

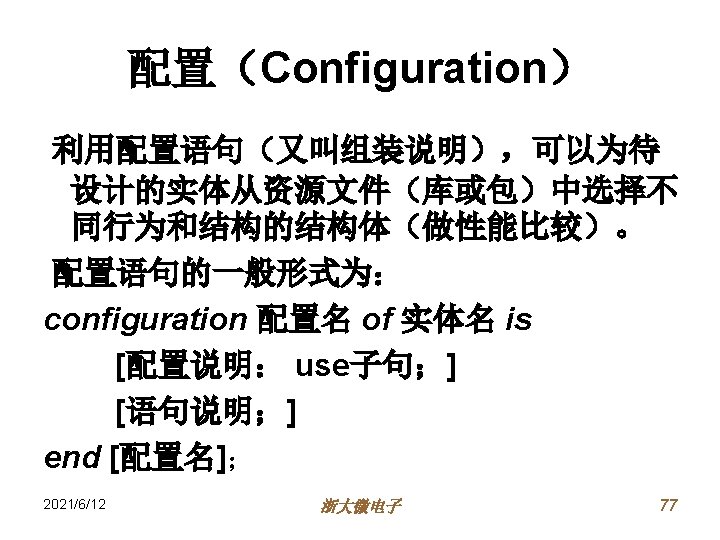

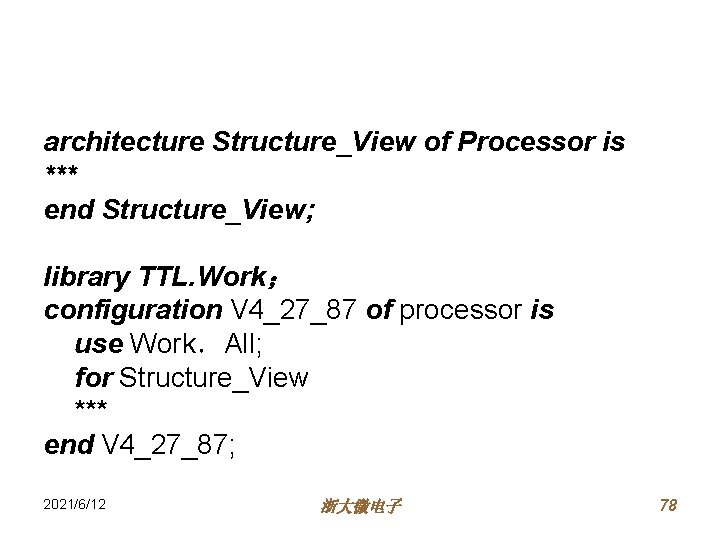

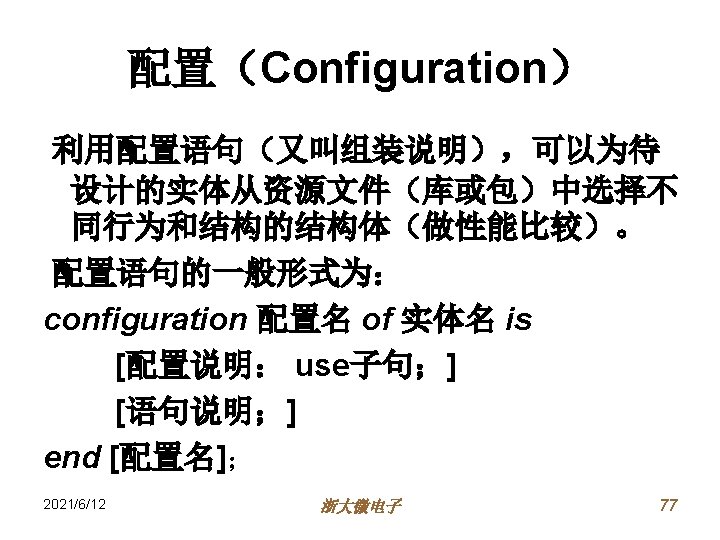

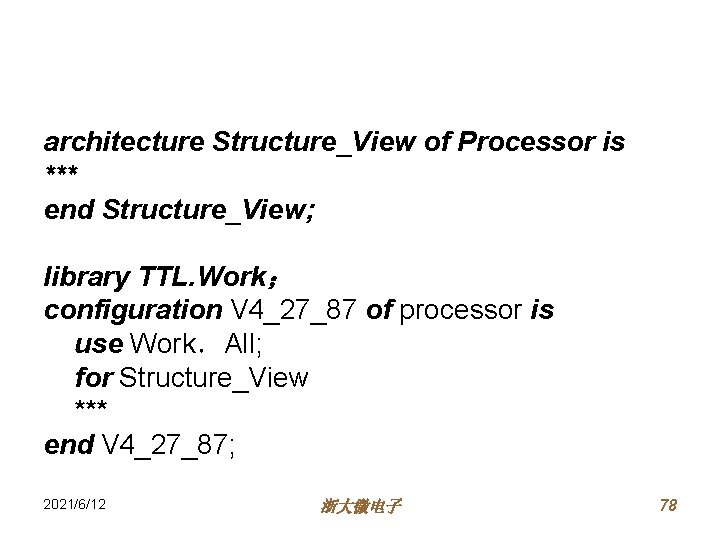

architecture Structure_View of Processor is *** end Structure_View; library TTL. Work; configuration V 4_27_87 of processor is use Work.All; for Structure_View *** end V 4_27_87; 2021/6/12 浙大微电子 78

浙大微�子 共 134� 2021/6/12 THE END 86