VHDL and HDL Designer Primer Instructor Jason D

![Constructs in Structural VHDL • Concurrent assignment statement [output] <= [function of inputs] after Constructs in Structural VHDL • Concurrent assignment statement [output] <= [function of inputs] after](https://slidetodoc.com/presentation_image_h2/4d1a36e3789c143777c2fbdf6de7c17c/image-8.jpg)

- Slides: 46

VHDL and HDL Designer Primer Instructor: Jason D. Bakos

VHDL (Appendix B in Textbook) • • • HDL => VHDL / Verilog VHDL more verbose, better for team projects Not case-sensitive • • • VHDL => “VHSIC Hardware Description Language” VHSIC => “US Do. D Very-High-Speed Integrated Circuit” Do. D project – – • Used to describe behavior of digital logic – • Document behavior of ASICs from suppliers Alternative to manuals Extensions for analog High-level programming language, subset of Ada – Also looks like Pascal • IEEE standards: 1987, 1993, 2000, 2002 • • • First came the language… …next came simulators… …then came synthesizers (FPGA and ASIC) 2

VHDL • By its nature, VHDL is – Self-documenting – Allows for easy testbench design (simulators, instruments) • Any VHDL code may be simulated • Only some VHDL codes may be synthesized – Depends on packages, data types, and constructs • VHDL descriptions (programs) have structure similar to C++ • Each design (component) is made up of – Entity section • Component interface (I/O) • Analogous to C++ header (public methods only) – Architecture section • Contains behavior (implementation) • Can have multiple architectures for any entity • Example: different types of adders with consistent interfaces 3

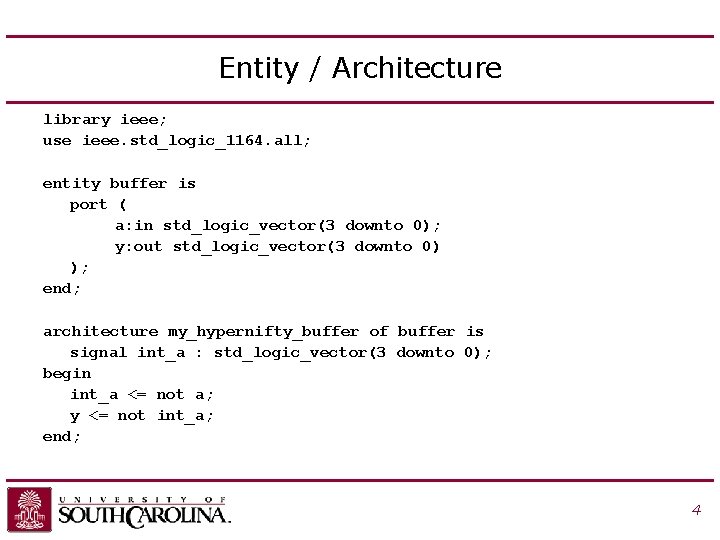

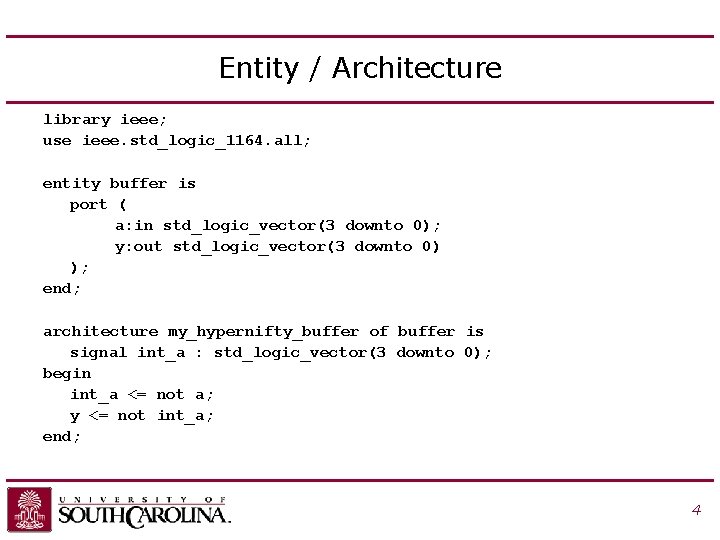

Entity / Architecture library ieee; use ieee. std_logic_1164. all; entity buffer is port ( a: in std_logic_vector(3 downto 0); y: out std_logic_vector(3 downto 0) ); end; architecture my_hypernifty_buffer of buffer is signal int_a : std_logic_vector(3 downto 0); begin int_a <= not a; y <= not int_a; end; 4

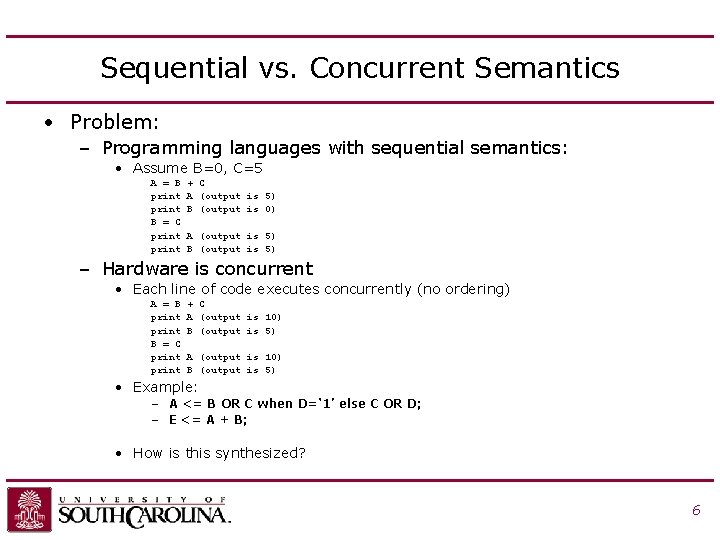

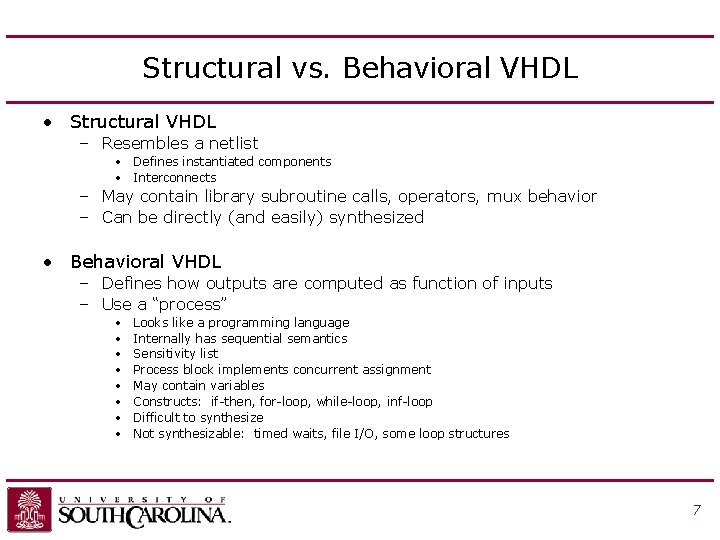

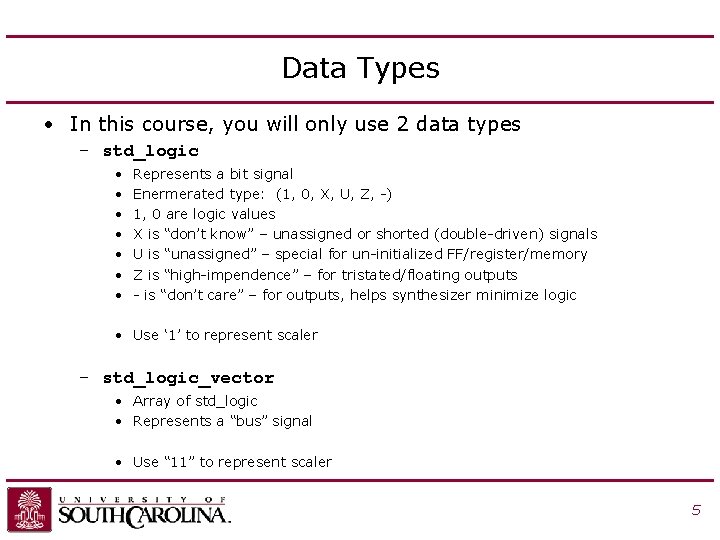

Data Types • In this course, you will only use 2 data types – std_logic • • Represents a bit signal Enermerated type: (1, 0, X, U, Z, -) 1, 0 are logic values X is “don’t know” – unassigned or shorted (double-driven) signals U is “unassigned” – special for un-initialized FF/register/memory Z is “high-impendence” – for tristated/floating outputs - is “don’t care” – for outputs, helps synthesizer minimize logic • Use ‘ 1’ to represent scaler – std_logic_vector • Array of std_logic • Represents a “bus” signal • Use “ 11” to represent scaler 5

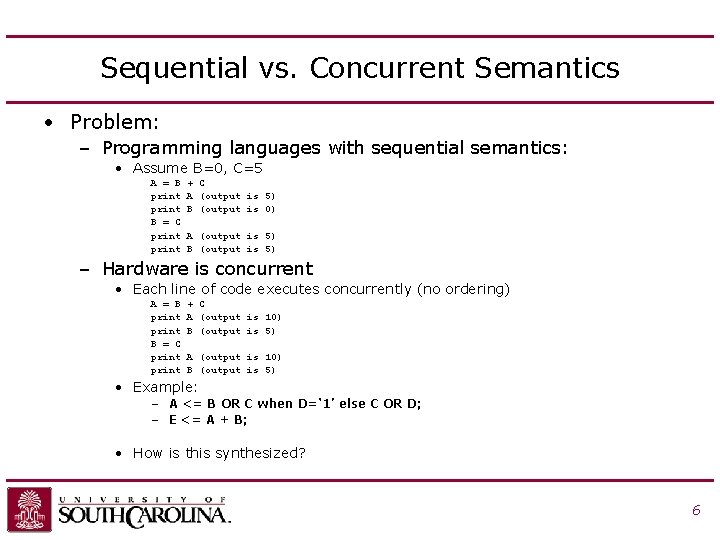

Sequential vs. Concurrent Semantics • Problem: – Programming languages with sequential semantics: • Assume B=0, C=5 A = B print B = C print + C A (output is 5) B (output is 0) A (output is 5) B (output is 5) – Hardware is concurrent • Each line of code executes concurrently (no ordering) A = B print B = C print + C A (output is 10) B (output is 5) • Example: – A <= B OR C when D=‘ 1’ else C OR D; – E <= A + B; • How is this synthesized? 6

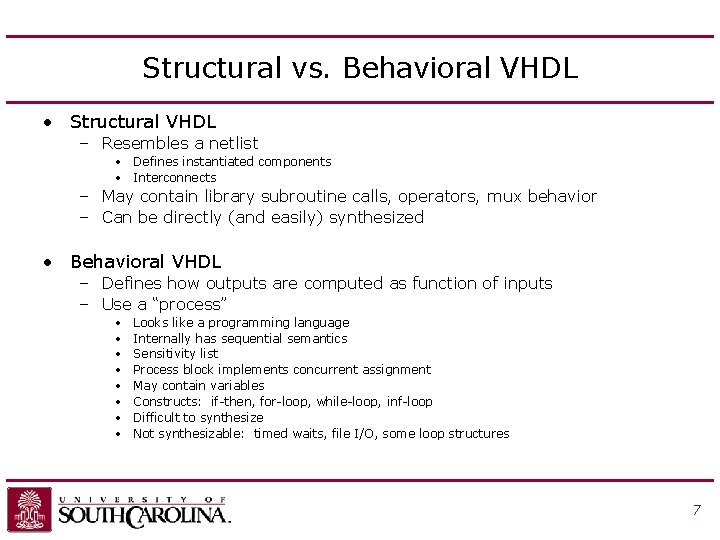

Structural vs. Behavioral VHDL • Structural VHDL – Resembles a netlist • Defines instantiated components • Interconnects – May contain library subroutine calls, operators, mux behavior – Can be directly (and easily) synthesized • Behavioral VHDL – Defines how outputs are computed as function of inputs – Use a “process” • • Looks like a programming language Internally has sequential semantics Sensitivity list Process block implements concurrent assignment May contain variables Constructs: if-then, for-loop, while-loop, inf-loop Difficult to synthesize Not synthesizable: timed waits, file I/O, some loop structures 7

![Constructs in Structural VHDL Concurrent assignment statement output function of inputs after Constructs in Structural VHDL • Concurrent assignment statement [output] <= [function of inputs] after](https://slidetodoc.com/presentation_image_h2/4d1a36e3789c143777c2fbdf6de7c17c/image-8.jpg)

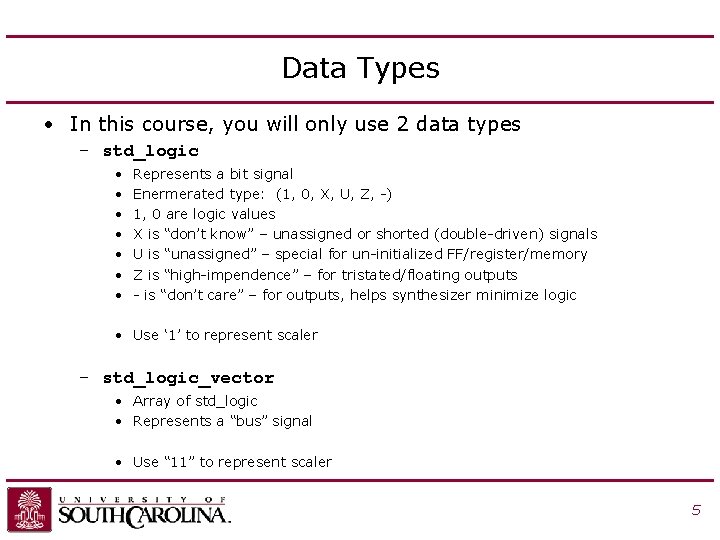

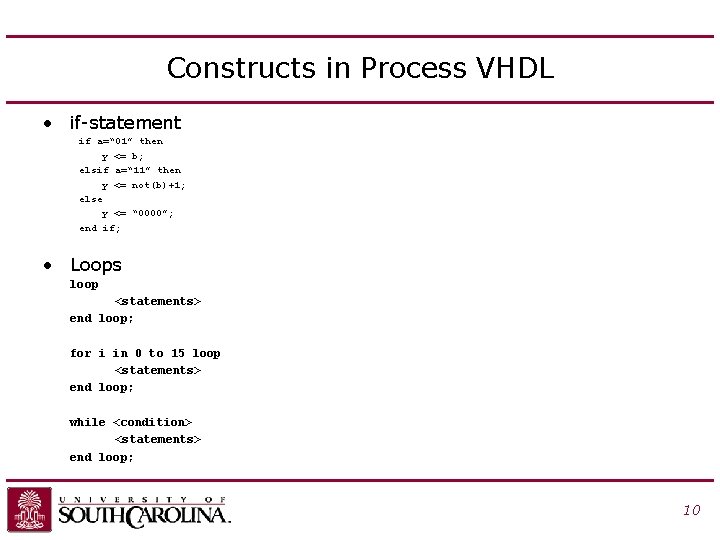

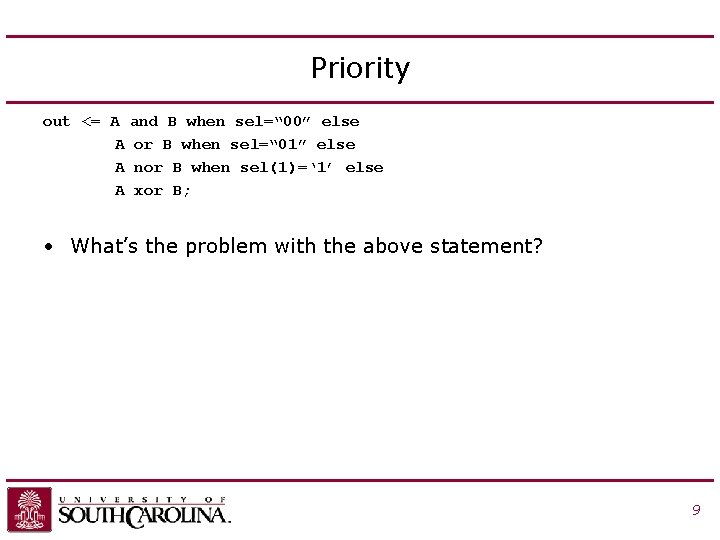

Constructs in Structural VHDL • Concurrent assignment statement [output] <= [function of inputs] after [delay] when [condition] else … [function of inputs]; • Example: out <= A and B when sel=“ 00” else A or B when sel=“ 01” else A nor B when sel=“ 10” else A xor B; sel <= “ 00” when (C or D)=“ 0101” else “ 10”; 8

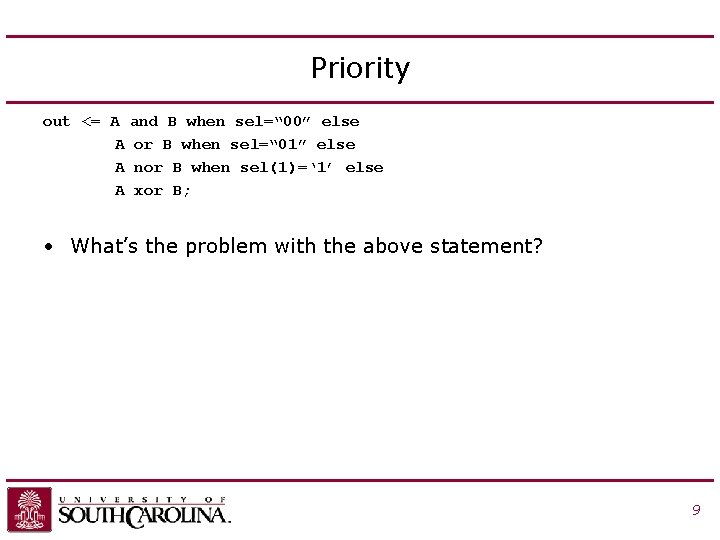

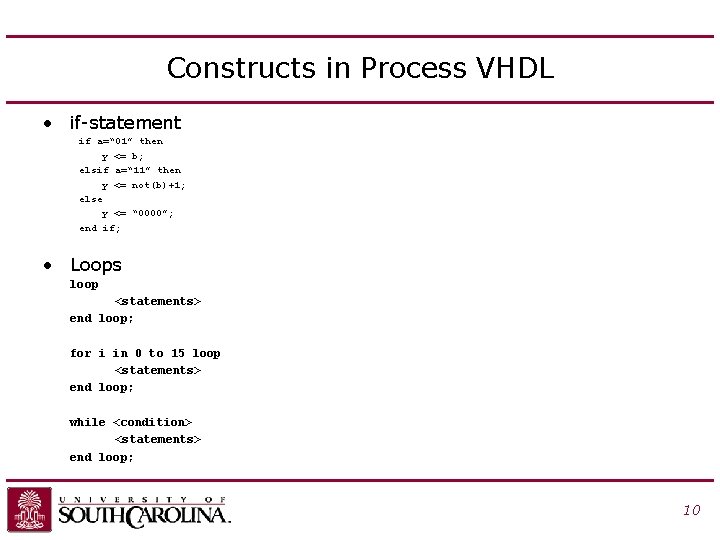

Priority out <= A and B when sel=“ 00” else A or B when sel=“ 01” else A nor B when sel(1)=‘ 1’ else A xor B; • What’s the problem with the above statement? 9

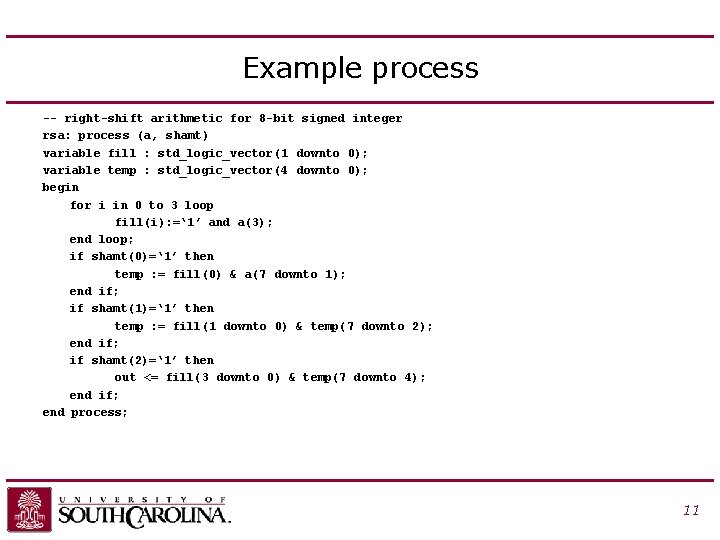

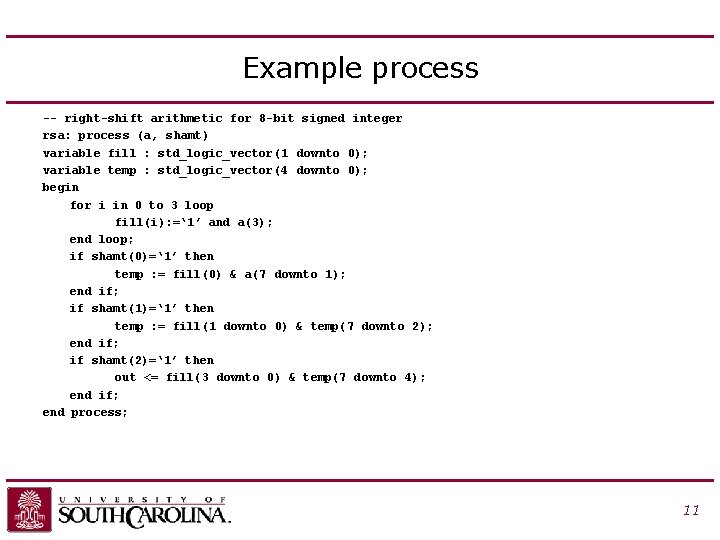

Constructs in Process VHDL • if-statement if a=“ 01” then y <= b; elsif a=“ 11” then y <= not(b)+1; else y <= “ 0000”; end if; • Loops loop <statements> end loop; for i in 0 to 15 loop <statements> end loop; while <condition> <statements> end loop; 10

Example process -- right-shift arithmetic for 8 -bit signed integer rsa: process (a, shamt) variable fill : std_logic_vector(1 downto 0); variable temp : std_logic_vector(4 downto 0); begin for i in 0 to 3 loop fill(i): =‘ 1’ and a(3); end loop; if shamt(0)=‘ 1’ then temp : = fill(0) & a(7 downto 1); end if; if shamt(1)=‘ 1’ then temp : = fill(1 downto 0) & temp(7 downto 2); end if; if shamt(2)=‘ 1’ then out <= fill(3 downto 0) & temp(7 downto 4); end if; end process; 11

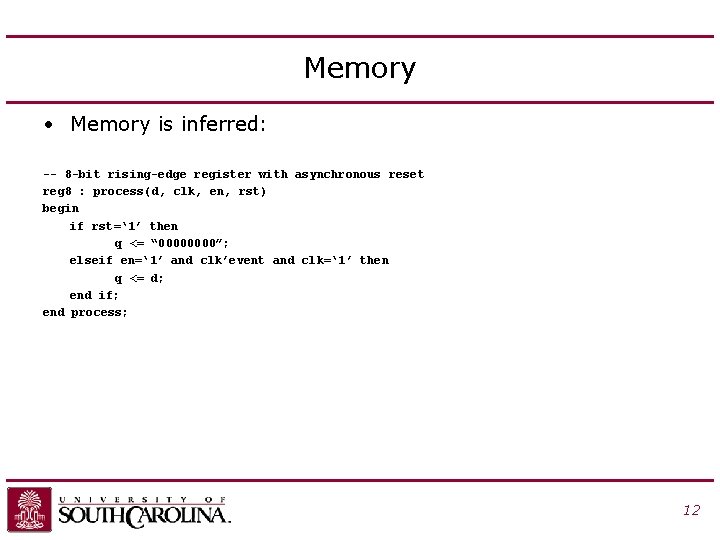

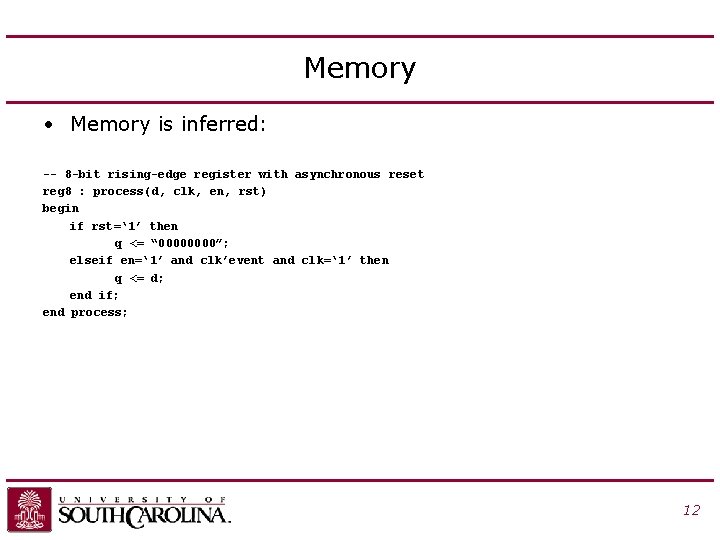

Memory • Memory is inferred: -- 8 -bit rising-edge register with asynchronous reset reg 8 : process(d, clk, en, rst) begin if rst=‘ 1’ then q <= “ 0000”; elseif en=‘ 1’ and clk’event and clk=‘ 1’ then q <= d; end if; end process; 12

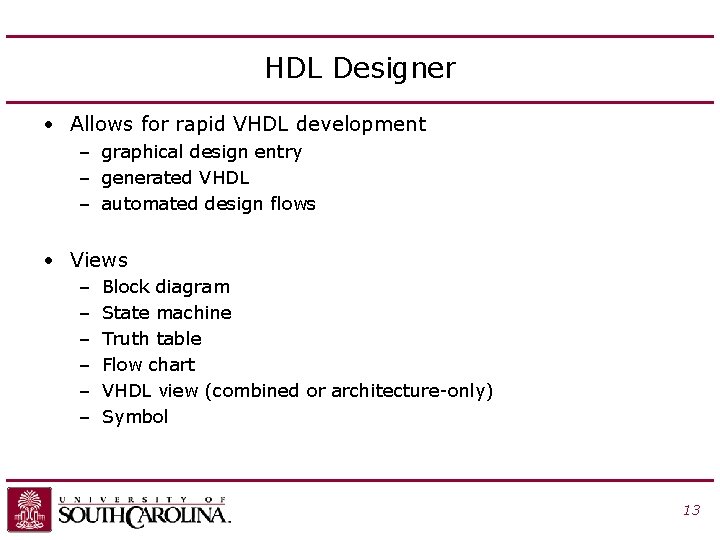

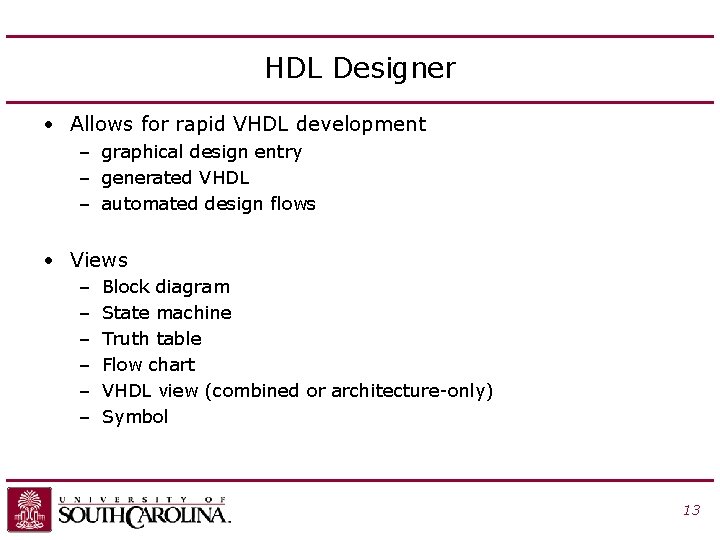

HDL Designer • Allows for rapid VHDL development – graphical design entry – generated VHDL – automated design flows • Views – – – Block diagram State machine Truth table Flow chart VHDL view (combined or architecture-only) Symbol 13

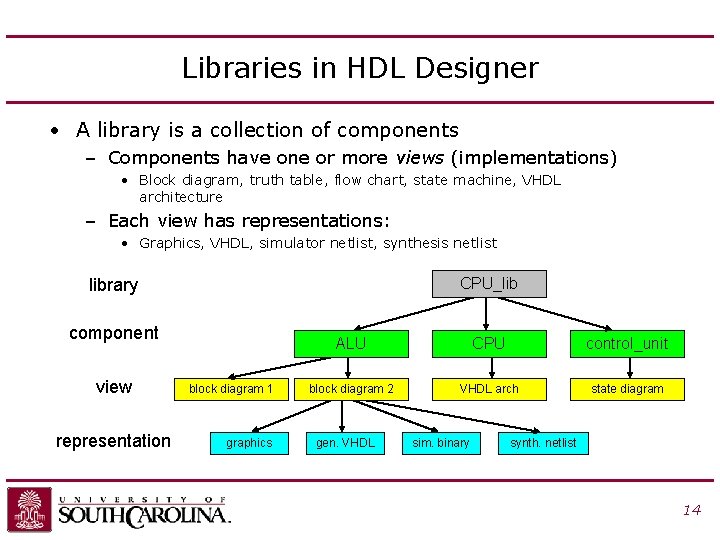

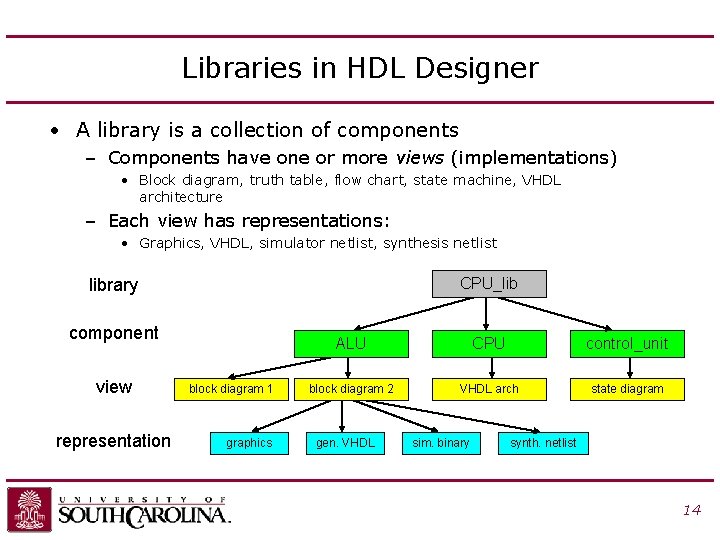

Libraries in HDL Designer • A library is a collection of components – Components have one or more views (implementations) • Block diagram, truth table, flow chart, state machine, VHDL architecture – Each view has representations: • Graphics, VHDL, simulator netlist, synthesis netlist CPU_lib library component view representation block diagram 1 graphics ALU CPU control_unit block diagram 2 VHDL arch state diagram gen. VHDL sim. binary synth. netlist 14

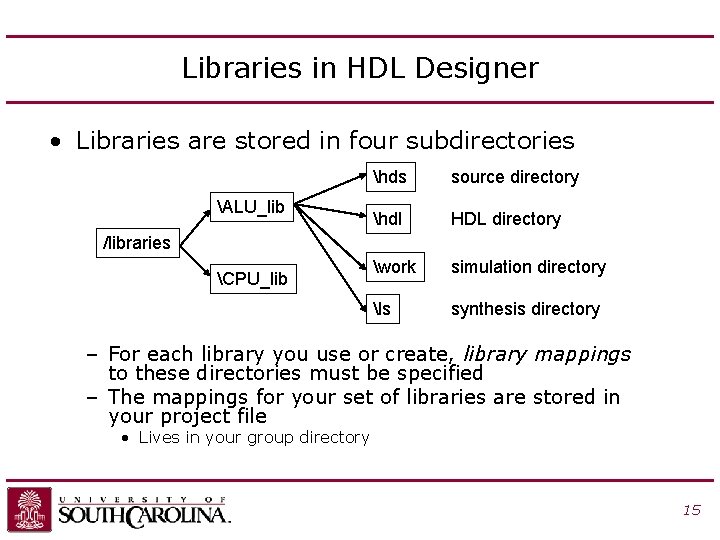

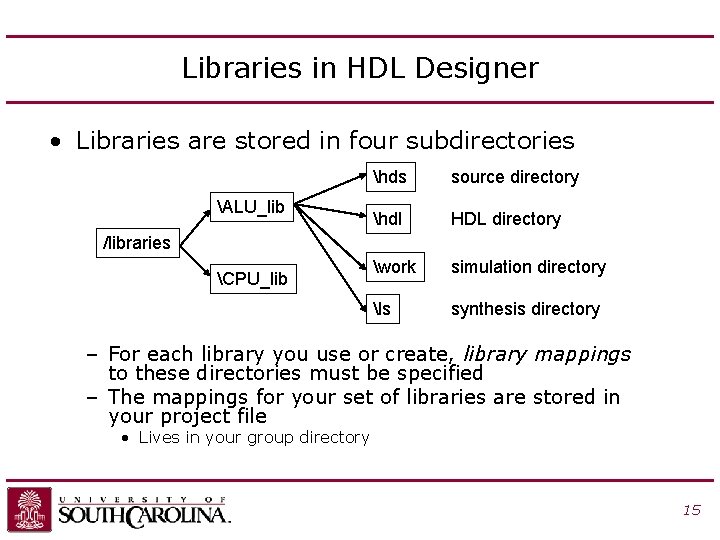

Libraries in HDL Designer • Libraries are stored in four subdirectories ALU_lib hds source directory hdl HDL directory work simulation directory ls synthesis directory /libraries CPU_lib – For each library you use or create, library mappings to these directories must be specified – The mappings for your set of libraries are stored in your project file • Lives in your group directory 15

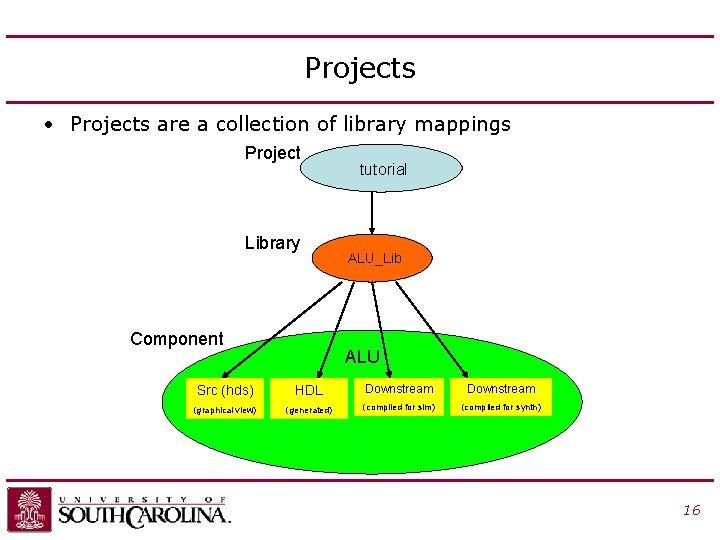

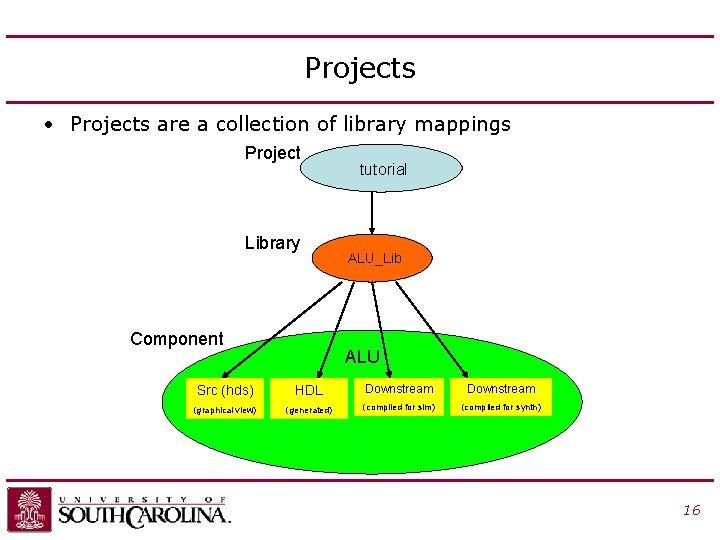

Projects • Projects are a collection of library mappings Project Library Component tutorial ALU_Lib ALU Src (hds) HDL Downstream (graphical view) (generated) (compiled for sim) (compiled for synth) 16

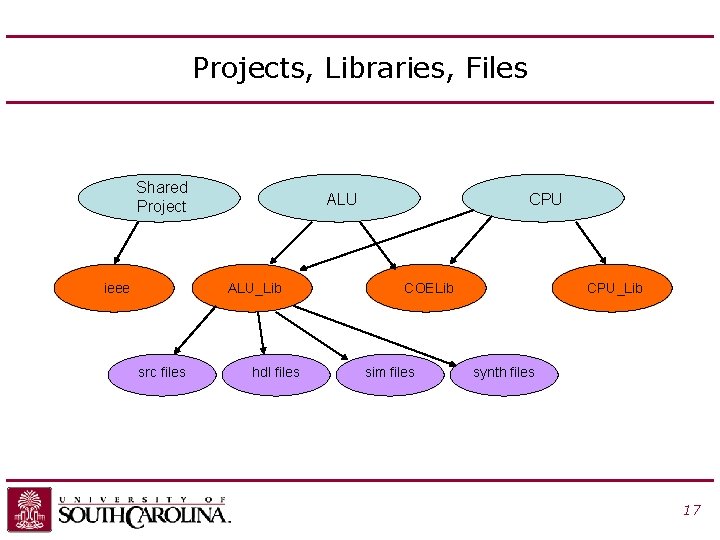

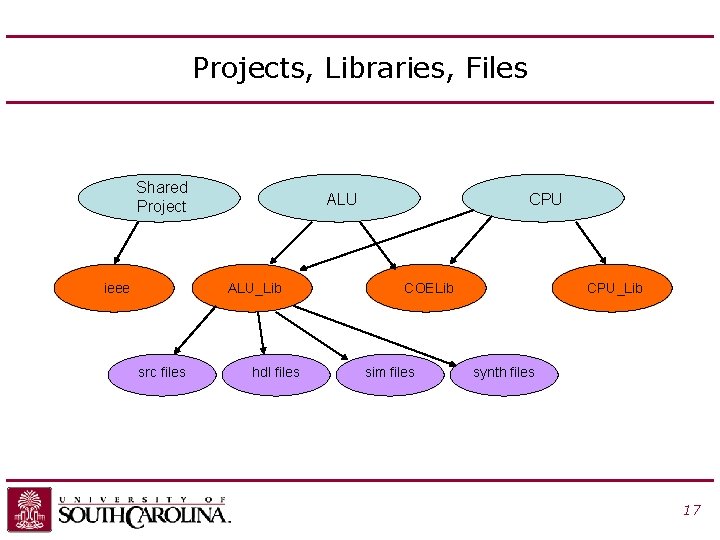

Projects, Libraries, Files Shared Project ieee ALU_Lib src files hdl files CPU COELib sim files CPU_Lib synth files 17

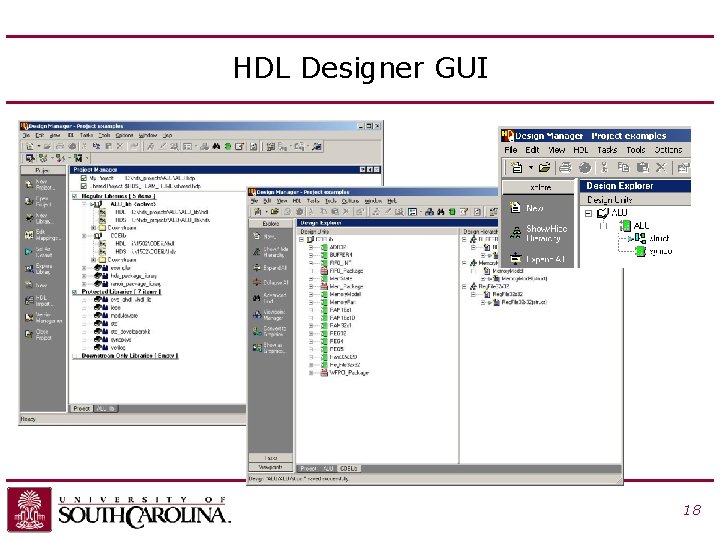

HDL Designer GUI 18

Block Diagram Editor 19

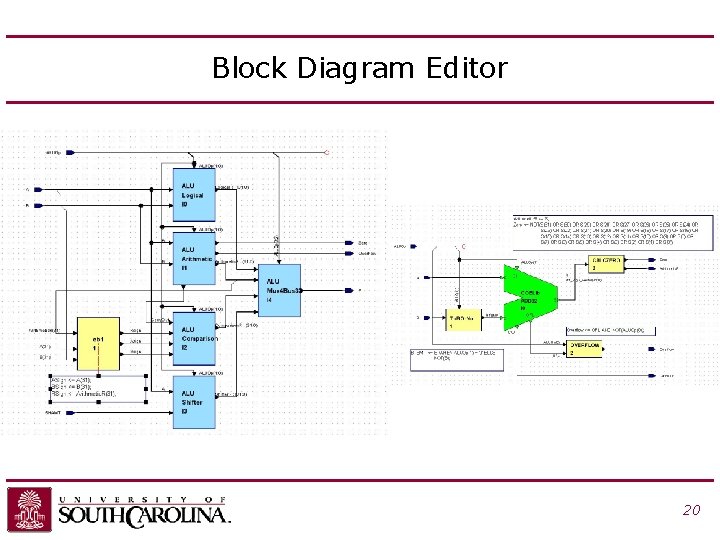

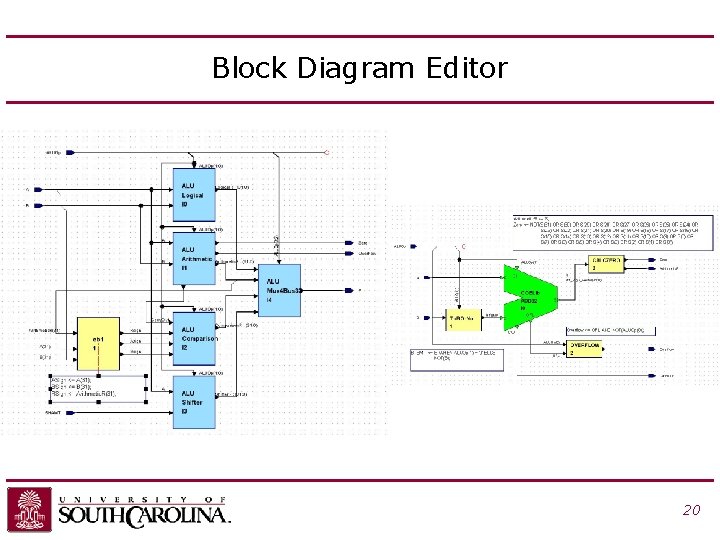

Block Diagram Editor 20

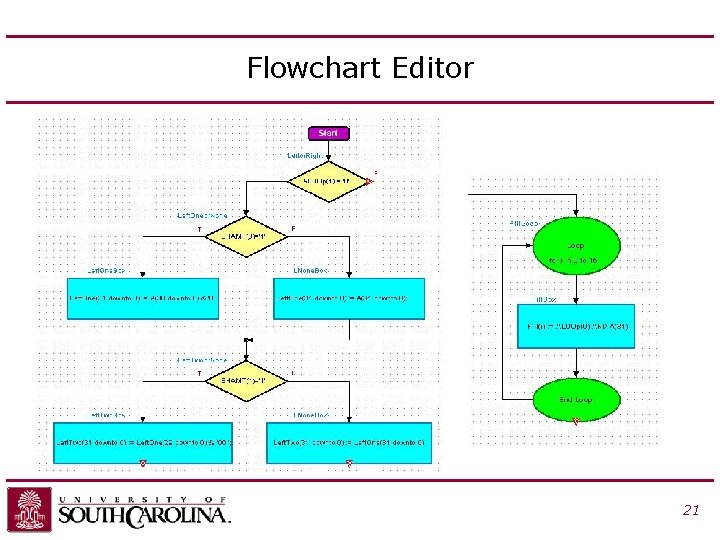

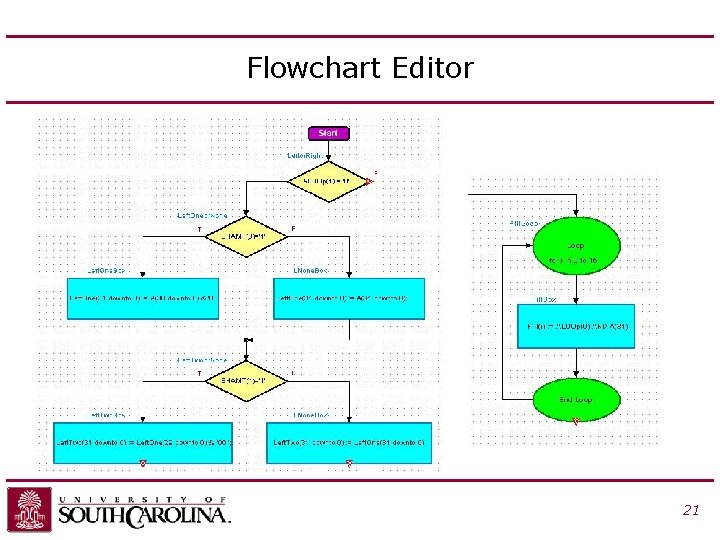

Flowchart Editor 21

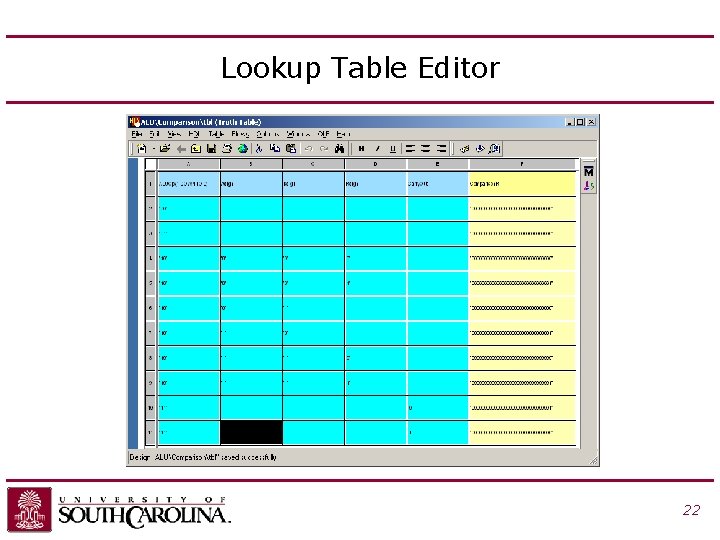

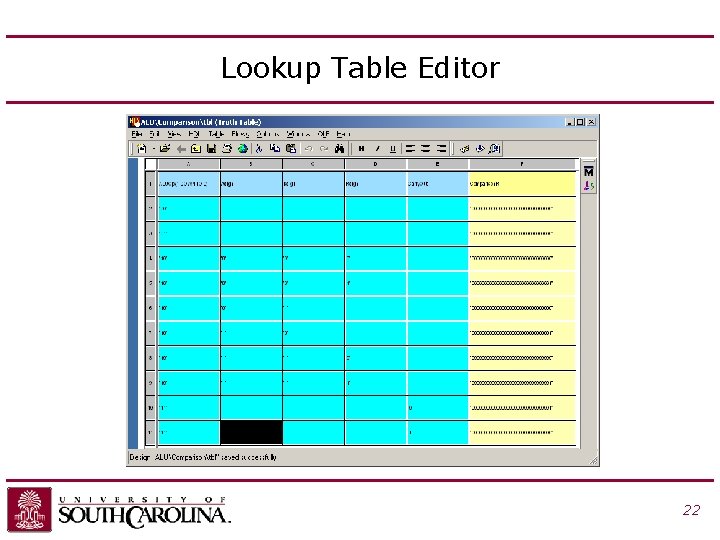

Lookup Table Editor 22

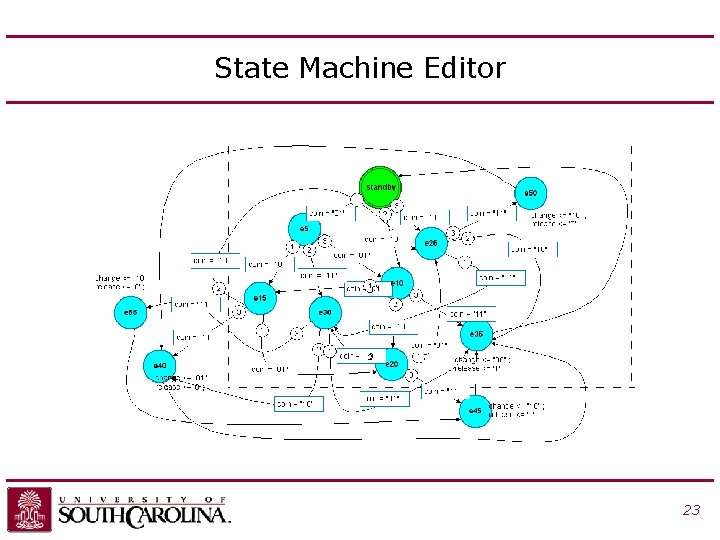

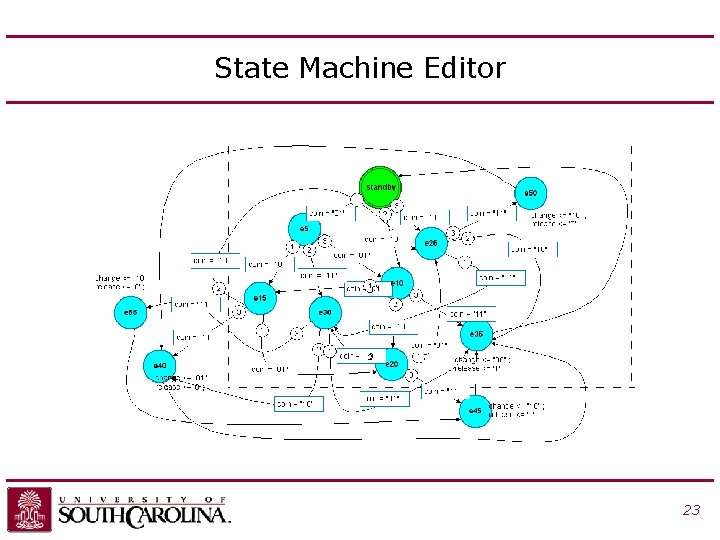

State Machine Editor 23

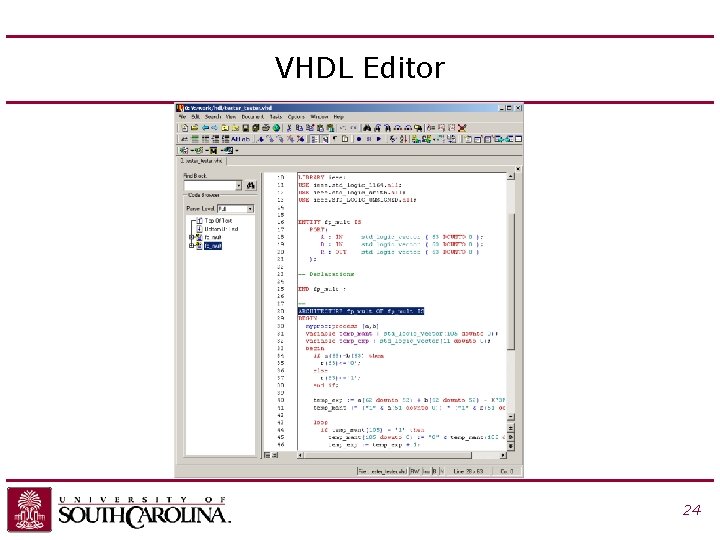

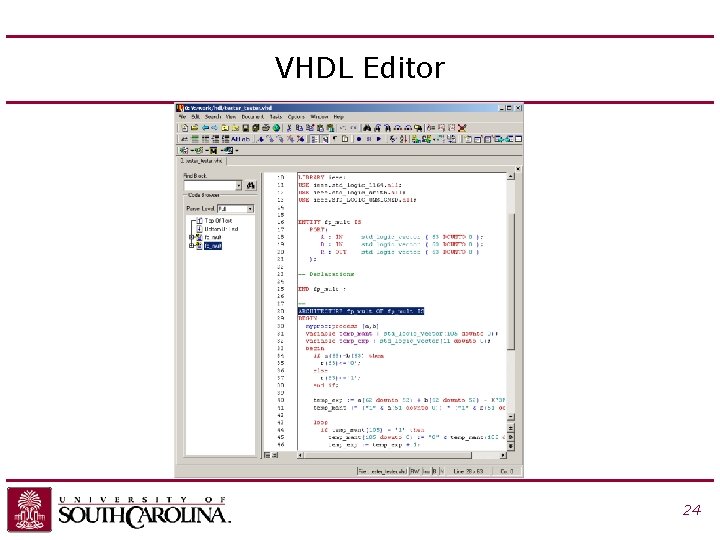

VHDL Editor 24

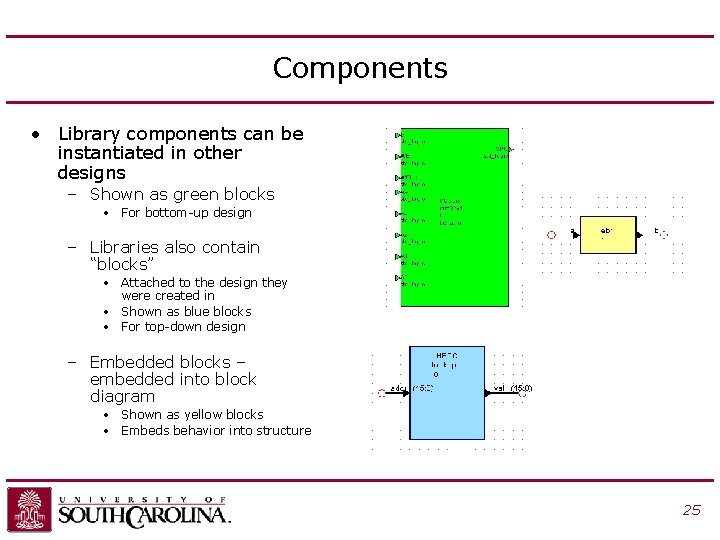

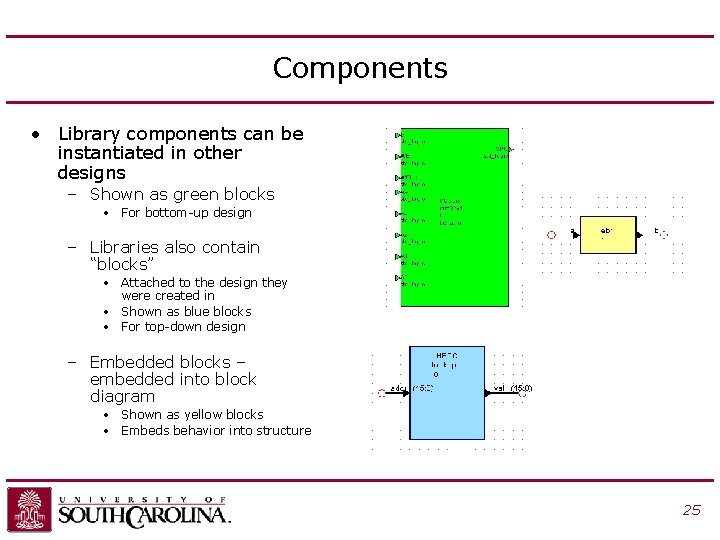

Components • Library components can be instantiated in other designs – Shown as green blocks • For bottom-up design – Libraries also contain “blocks” • Attached to the design they were created in • Shown as blue blocks • For top-down design – Embedded blocks – embedded into block diagram • Shown as yellow blocks • Embeds behavior into structure 25

Sequential Logic • Combinational logic – Output = f (input) • Sequential logic – Output = f (input, input history) – Involves use of memory elements • Registers 26

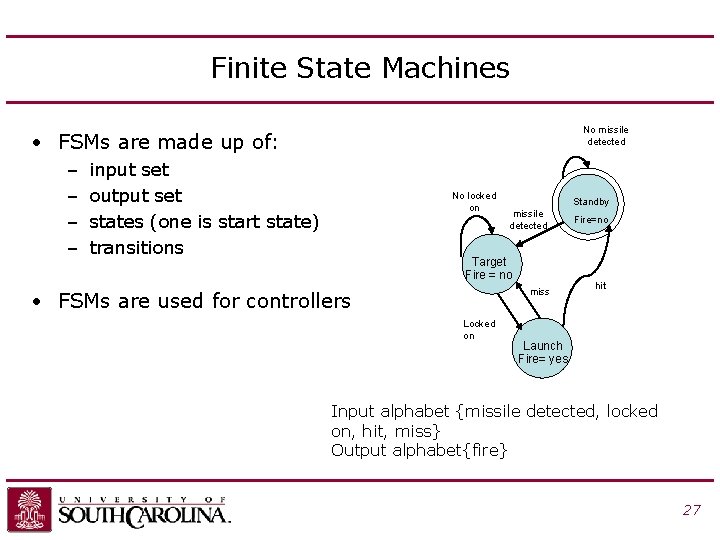

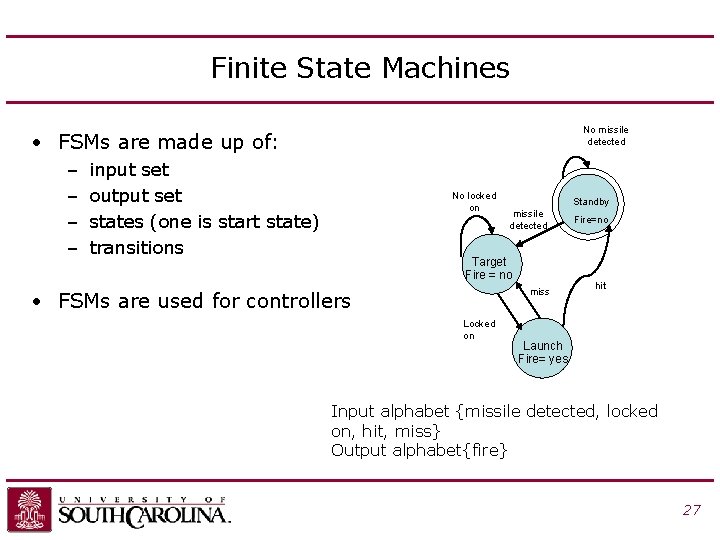

Finite State Machines No missile detected • FSMs are made up of: – – input set output set states (one is start state) transitions No locked on Standby missile detected Target Fire = no miss • FSMs are used for controllers Locked on Fire=no hit Launch Fire= yes Input alphabet {missile detected, locked on, hit, miss} Output alphabet{fire} 27

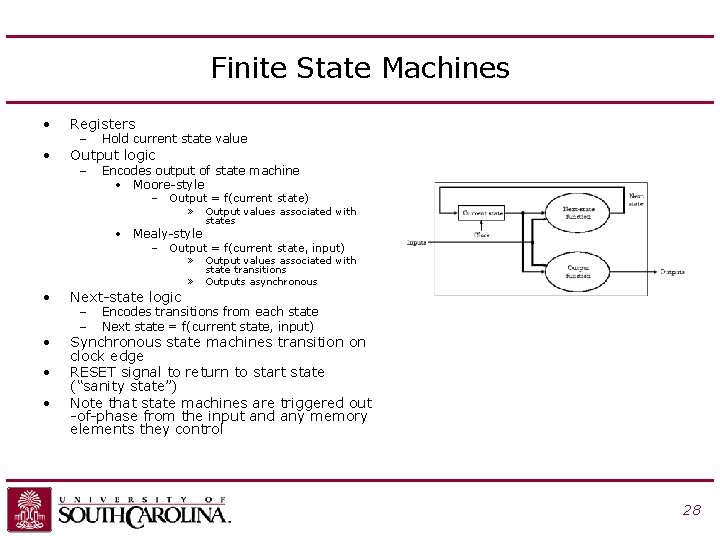

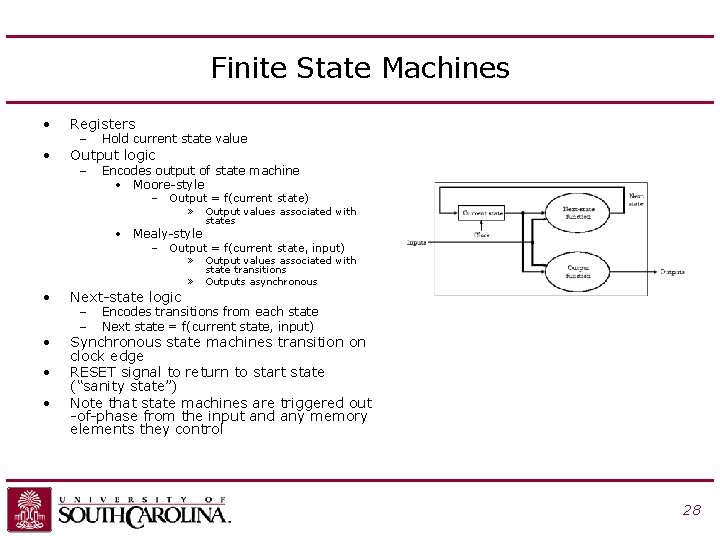

Finite State Machines • Registers • Output logic – Hold current state value – Encodes output of state machine • Moore-style – Output = f(current state) » • Mealy-style Output values associated with states – Output = f(current state, input) » » Output values associated with state transitions Outputs asynchronous • Next-state logic • Synchronous state machines transition on clock edge RESET signal to return to start state (“sanity state”) Note that state machines are triggered out -of-phase from the input and any memory elements they control • • – – Encodes transitions from each state Next state = f(current state, input) 28

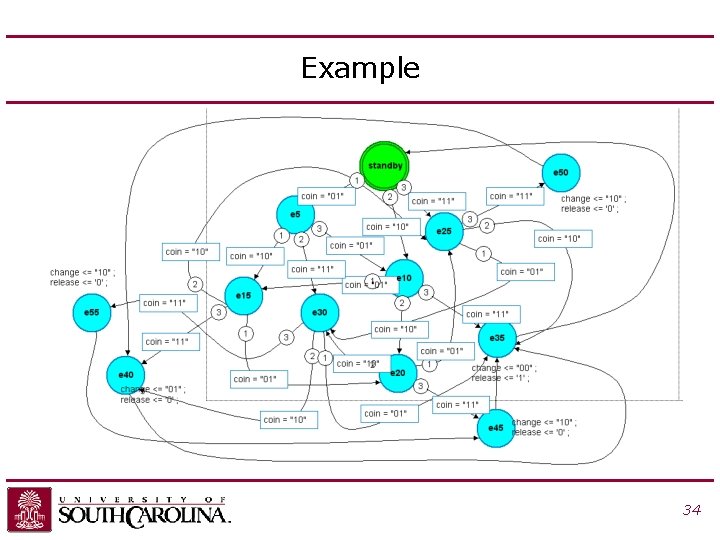

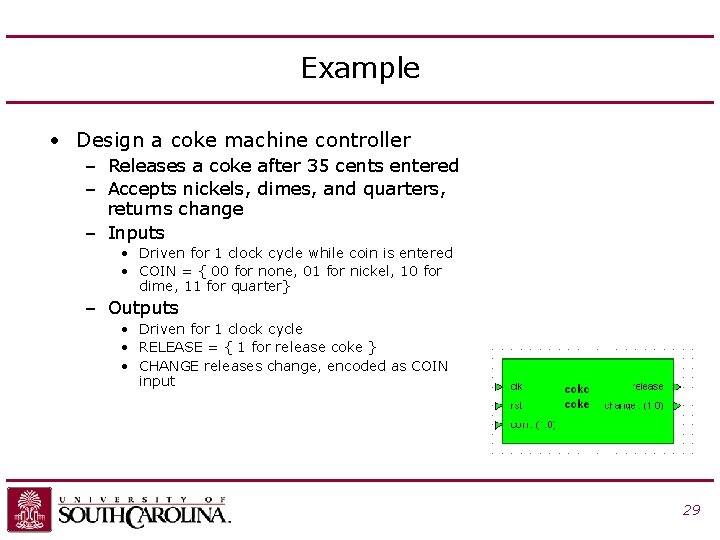

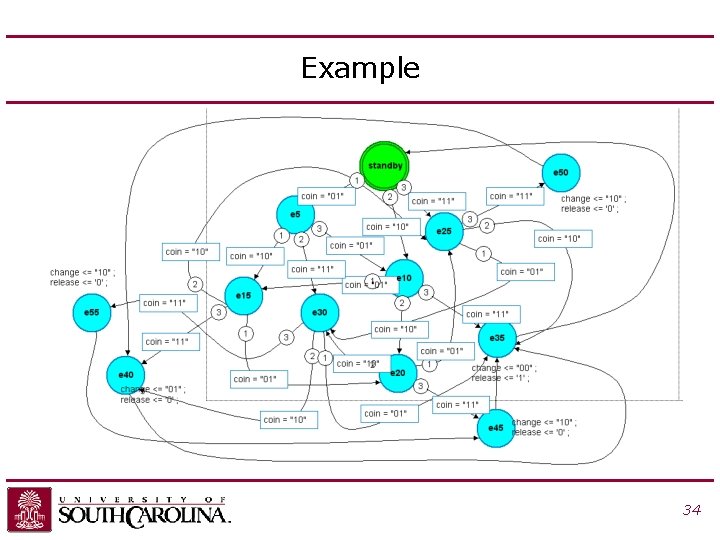

Example • Design a coke machine controller – Releases a coke after 35 cents entered – Accepts nickels, dimes, and quarters, returns change – Inputs • Driven for 1 clock cycle while coin is entered • COIN = { 00 for none, 01 for nickel, 10 for dime, 11 for quarter} – Outputs • Driven for 1 clock cycle • RELEASE = { 1 for release coke } • CHANGE releases change, encoded as COIN input 29

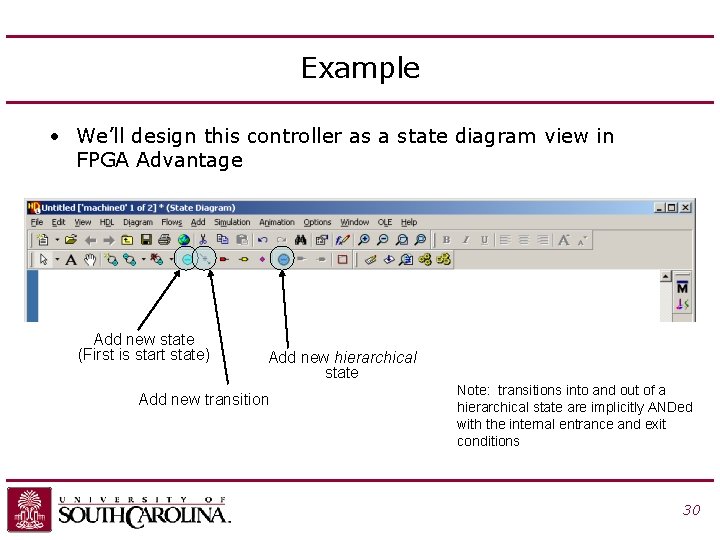

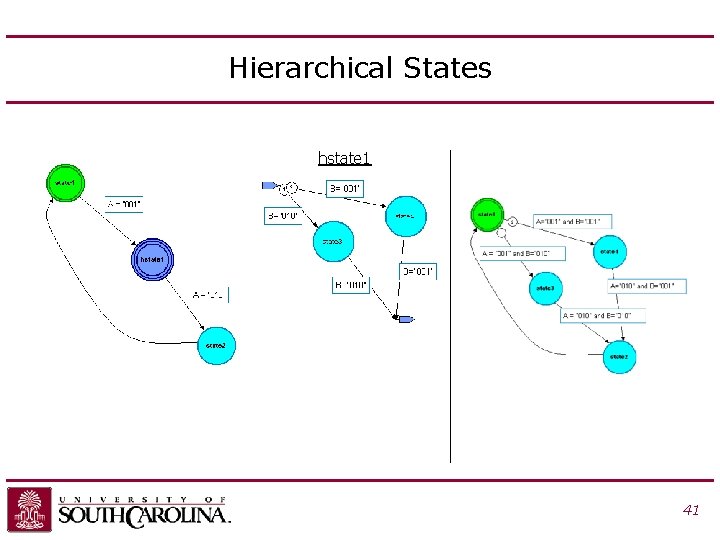

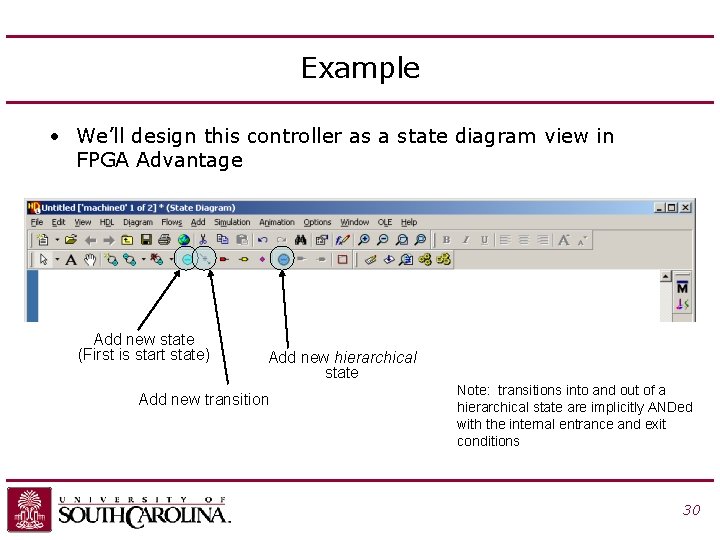

Example • We’ll design this controller as a state diagram view in FPGA Advantage Add new state (First is start state) Add new hierarchical state Add new transition Note: transitions into and out of a hierarchical state are implicitly ANDed with the internal entrance and exit conditions 30

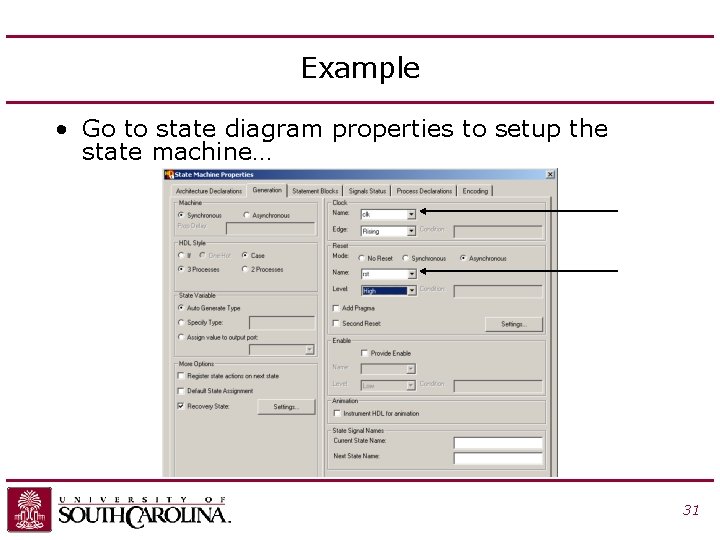

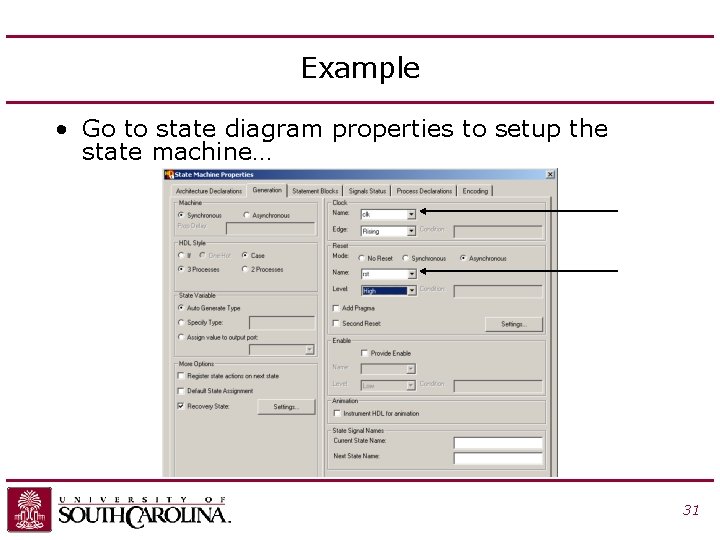

Example • Go to state diagram properties to setup the state machine… 31

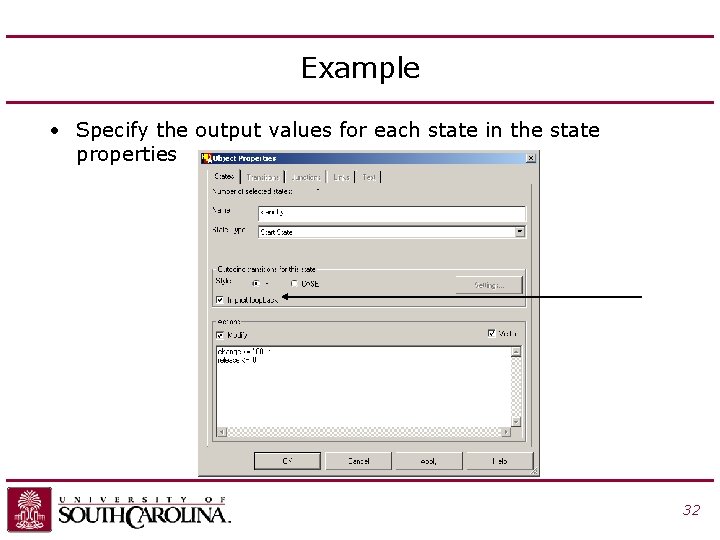

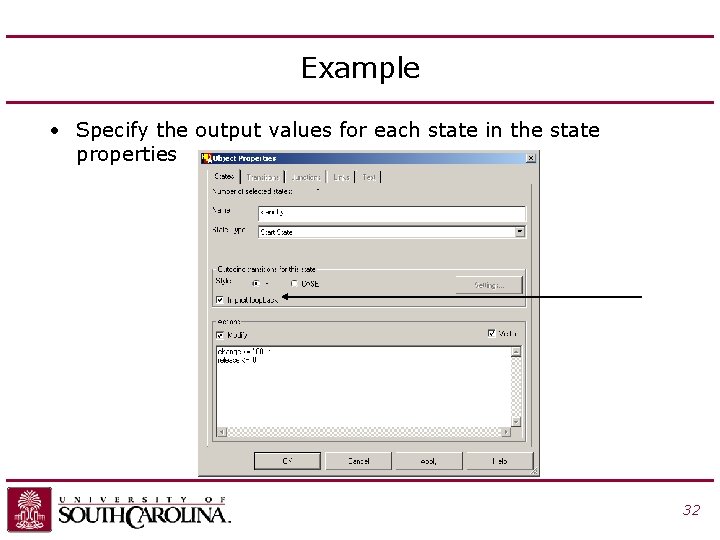

Example • Specify the output values for each state in the state properties 32

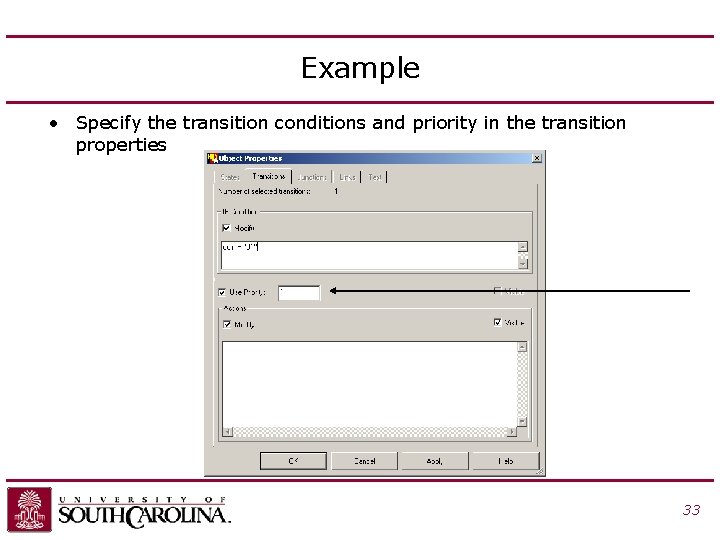

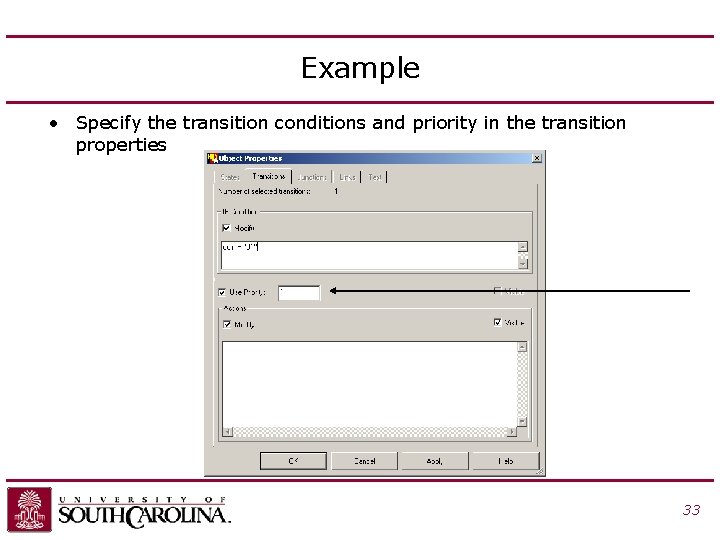

Example • Specify the transition conditions and priority in the transition properties 33

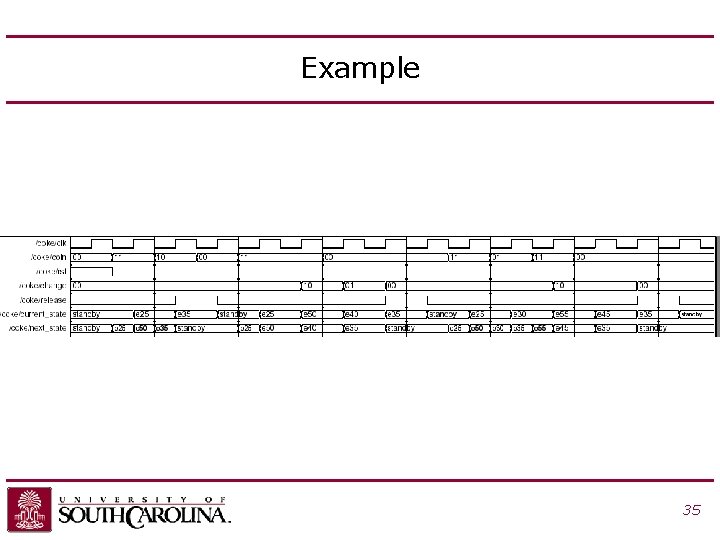

Example 34

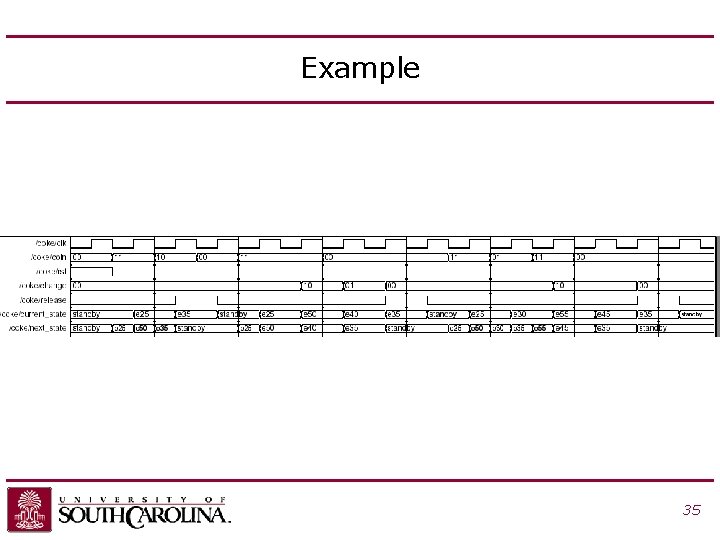

Example 35

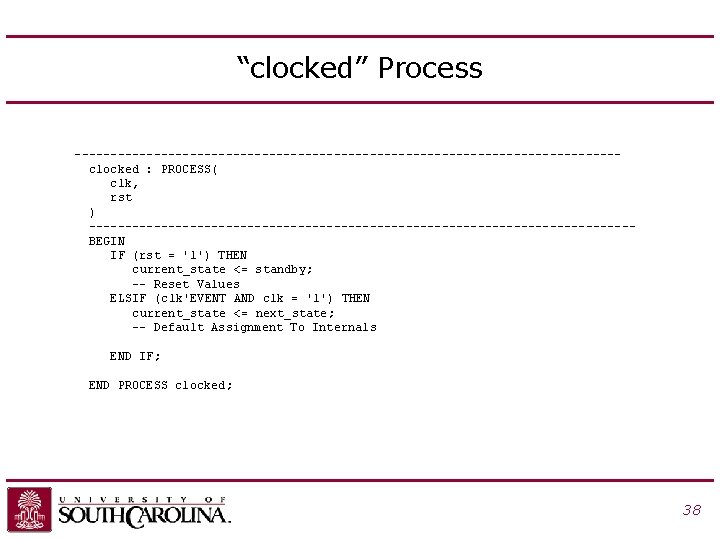

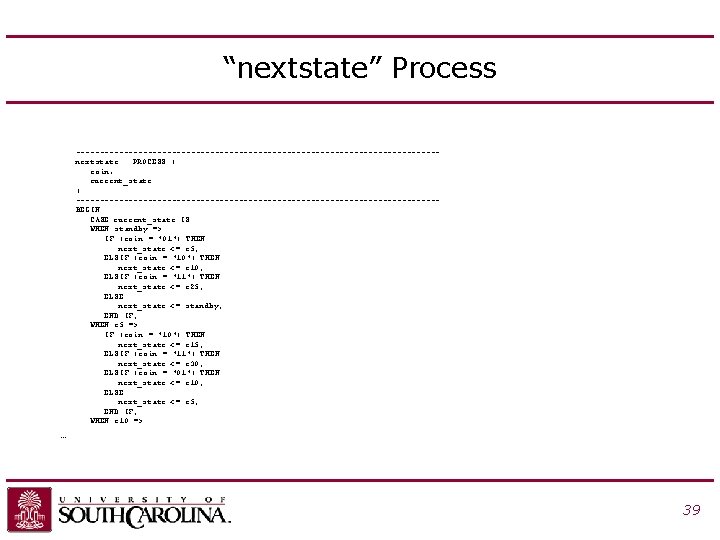

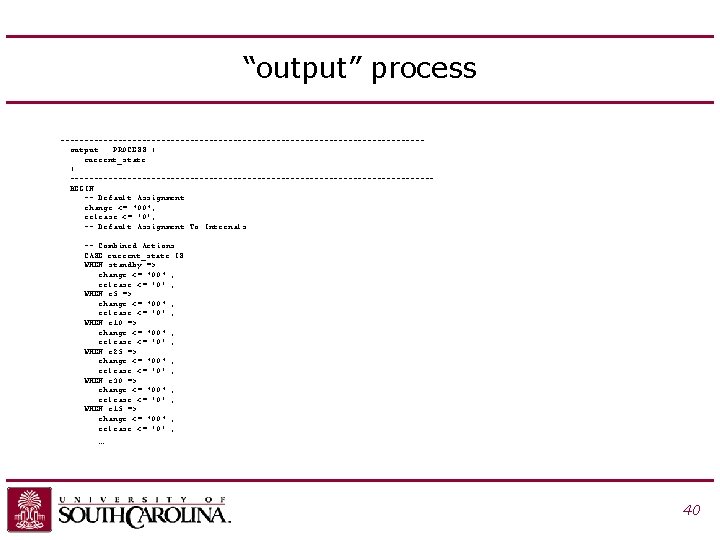

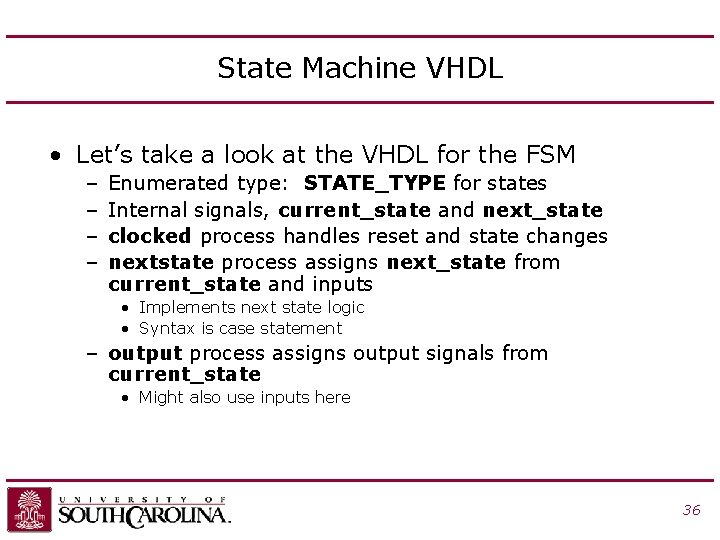

State Machine VHDL • Let’s take a look at the VHDL for the FSM – – Enumerated type: STATE_TYPE for states Internal signals, current_state and next_state clocked process handles reset and state changes nextstate process assigns next_state from current_state and inputs • Implements next state logic • Syntax is case statement – output process assigns output signals from current_state • Might also use inputs here 36

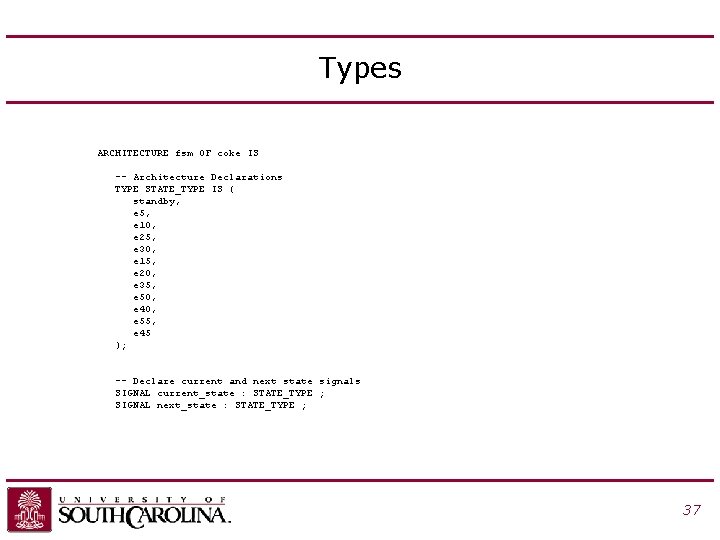

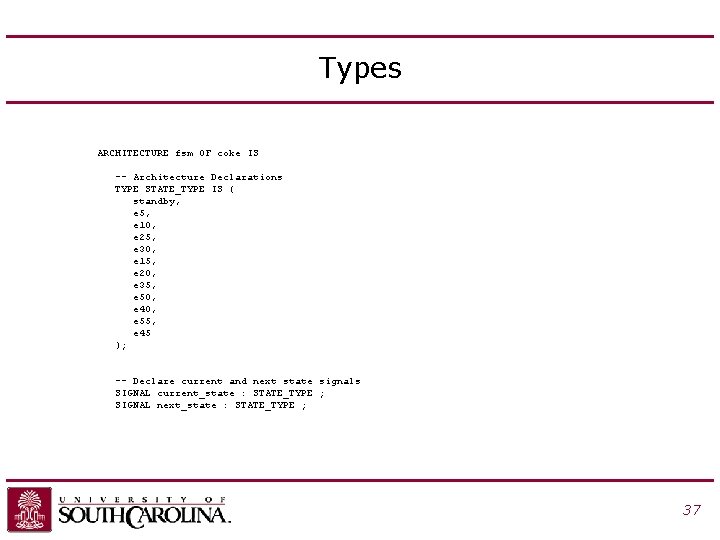

Types ARCHITECTURE fsm OF coke IS -- Architecture Declarations TYPE STATE_TYPE IS ( standby, e 5, e 10, e 25, e 30, e 15, e 20, e 35, e 50, e 40, e 55, e 45 ); -- Declare current and next state signals SIGNAL current_state : STATE_TYPE ; SIGNAL next_state : STATE_TYPE ; 37

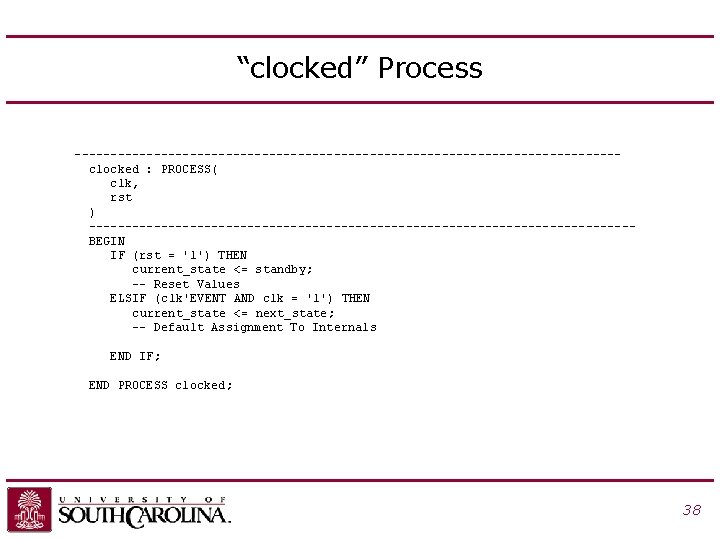

“clocked” Process --------------------------------------clocked : PROCESS( clk, rst ) --------------------------------------BEGIN IF (rst = '1') THEN current_state <= standby; -- Reset Values ELSIF (clk'EVENT AND clk = '1') THEN current_state <= next_state; -- Default Assignment To Internals END IF; END PROCESS clocked; 38

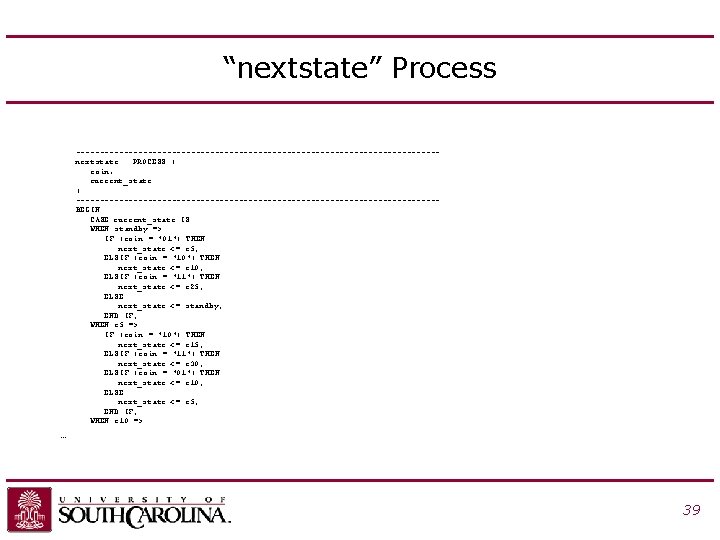

“nextstate” Process --------------------------------------nextstate : PROCESS ( coin, current_state ) --------------------------------------BEGIN CASE current_state IS WHEN standby => IF (coin = "01") THEN next_state <= e 5; ELSIF (coin = "10") THEN next_state <= e 10; ELSIF (coin = "11") THEN next_state <= e 25; ELSE next_state <= standby; END IF; WHEN e 5 => IF (coin = "10") THEN next_state <= e 15; ELSIF (coin = "11") THEN next_state <= e 30; ELSIF (coin = "01") THEN next_state <= e 10; ELSE next_state <= e 5; END IF; WHEN e 10 => … 39

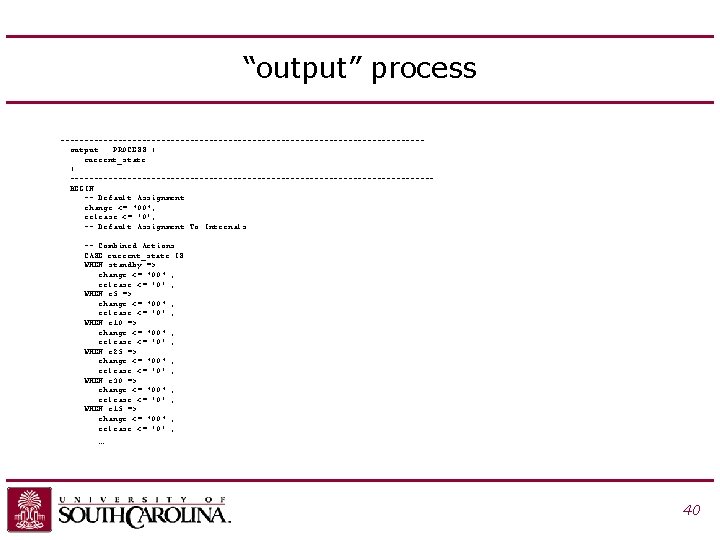

“output” process --------------------------------------output : PROCESS ( current_state ) --------------------------------------BEGIN -- Default Assignment change <= "00"; release <= '0'; -- Default Assignment To Internals -- Combined Actions CASE current_state IS WHEN standby => change <= "00" ; release <= '0' ; WHEN e 5 => change <= "00" ; release <= '0' ; WHEN e 10 => change <= "00" ; release <= '0' ; WHEN e 25 => change <= "00" ; release <= '0' ; WHEN e 30 => change <= "00" ; release <= '0' ; WHEN e 15 => change <= "00" ; release <= '0' ; … 40

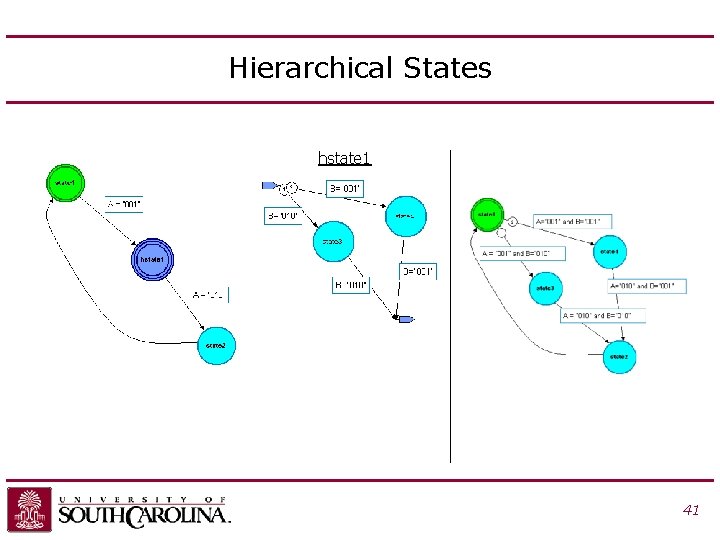

Hierarchical States hstate 1 41

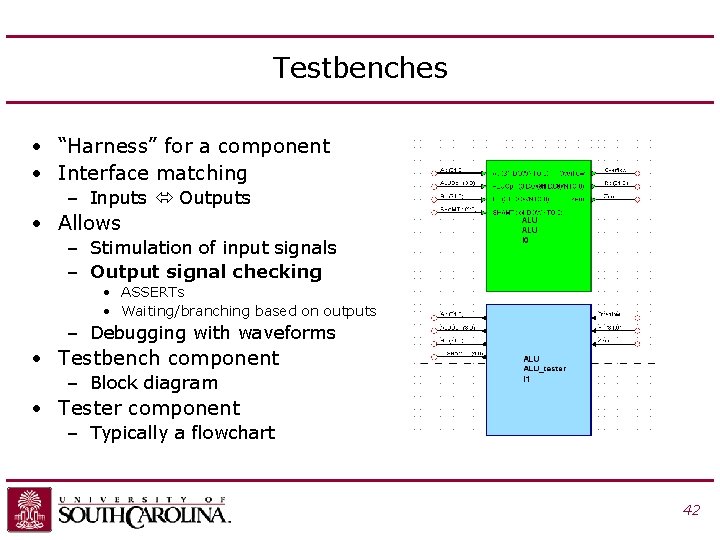

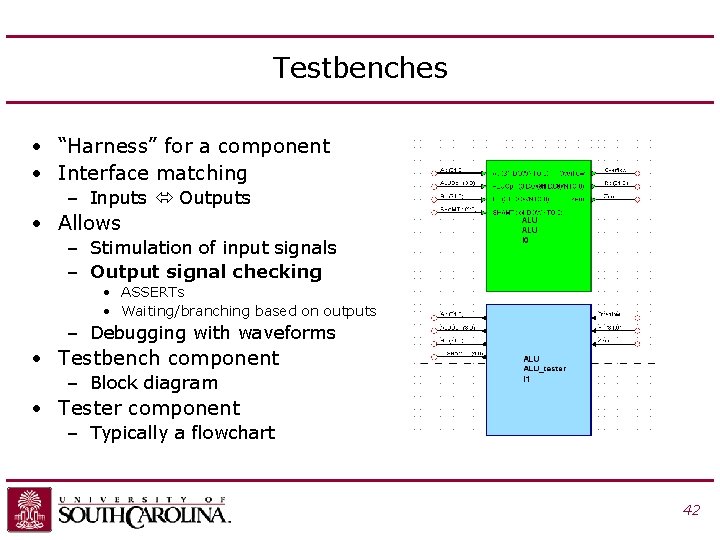

Testbenches • “Harness” for a component • Interface matching – Inputs Outputs • Allows – Stimulation of input signals – Output signal checking • ASSERTs • Waiting/branching based on outputs – Debugging with waveforms • Testbench component – Block diagram • Tester component – Typically a flowchart 42

Testbenches • Advantage over ad hoc methods – Ex. do-files • Allows simulation of inputs, but no output checking • Testbench code reveals interface specification and functionality (“self documenting”) • Reproducible – Can use same testbench for multiple implementations/generations of a component – Can generate or utilize data file to share tests between simulation and hardware testing 43

Testbenches • A test procedure is a methodology for testing a design – Sequence of steps – Testing aspects of a design’s functionality • Example: ALU – Test each type of operation with different inputs – Along with asserting inputs/operations, can also verify correctness of output values – Also, use if-then-else semantics 44

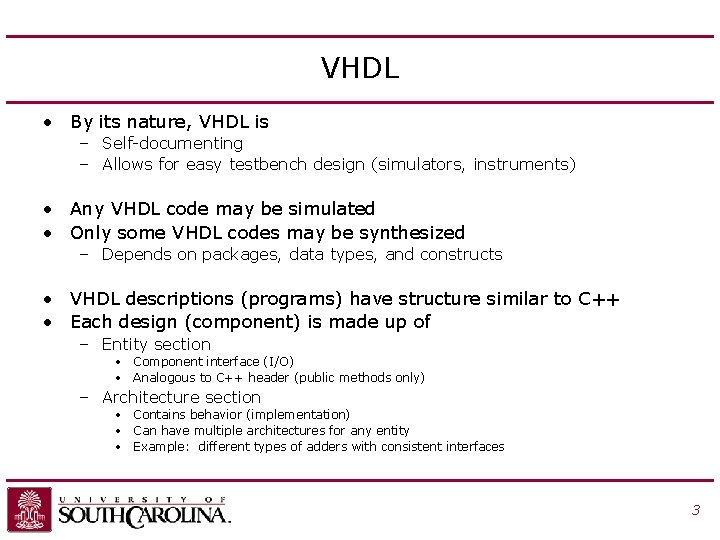

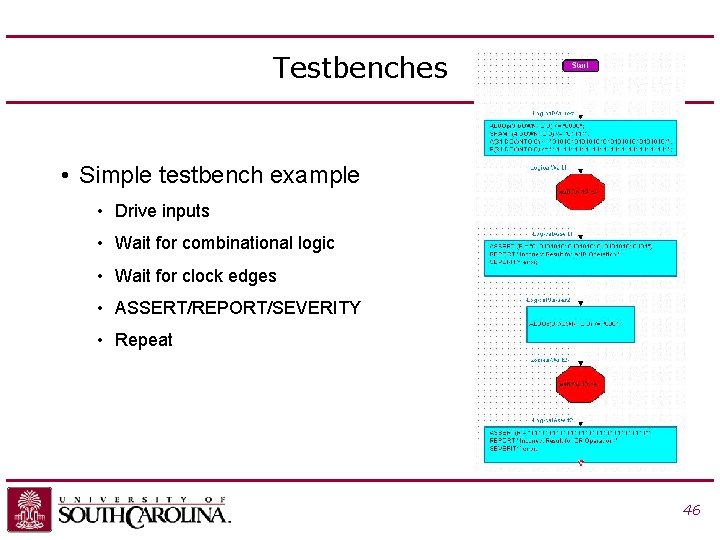

Testbenches • Facilities in HDL Designer – Easy creation of tester/testbench – Flowchart view is natural choice for implementing a test bench • Mirrors test procedure in a graphical representation – VHDL support for testbenches • ASSERT/REPORT/SEVERITY clause – Can use boolean operators here • Testbench operates in simulation 45

Testbenches • Simple testbench example • Drive inputs • Wait for combinational logic • Wait for clock edges • ASSERT/REPORT/SEVERITY • Repeat 46