The Physical Structure NMOS Gate oxide Polysilicon Gate

![Modelling: Resistance 1. Resistance: Rint= Rsh [l/w] Rsh values for 0. 35 u CMOS Modelling: Resistance 1. Resistance: Rint= Rsh [l/w] Rsh values for 0. 35 u CMOS](https://slidetodoc.com/presentation_image_h/0b4889420586bc2559569495e4ba6136/image-15.jpg)

- Slides: 46

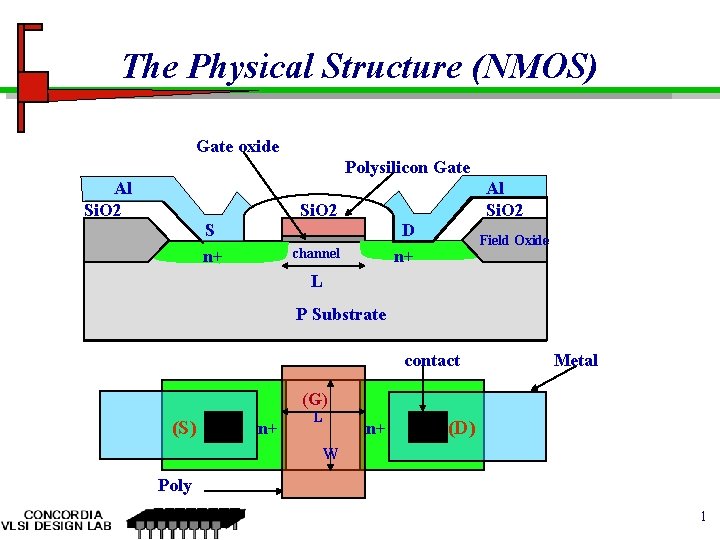

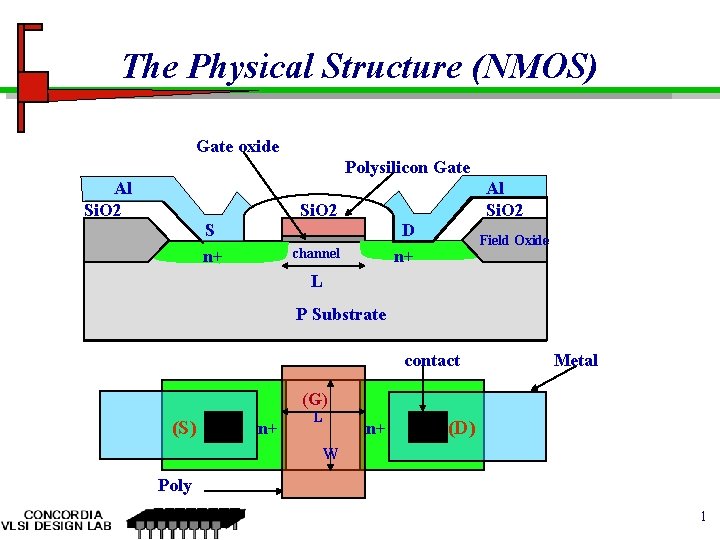

The Physical Structure (NMOS) Gate oxide Polysilicon Gate Al Si. O 2 S n+ Field Oxide D n+ channel Field Oxide L P Substrate contact Metal (G) (S) n+ L n+ (D) W Poly 1

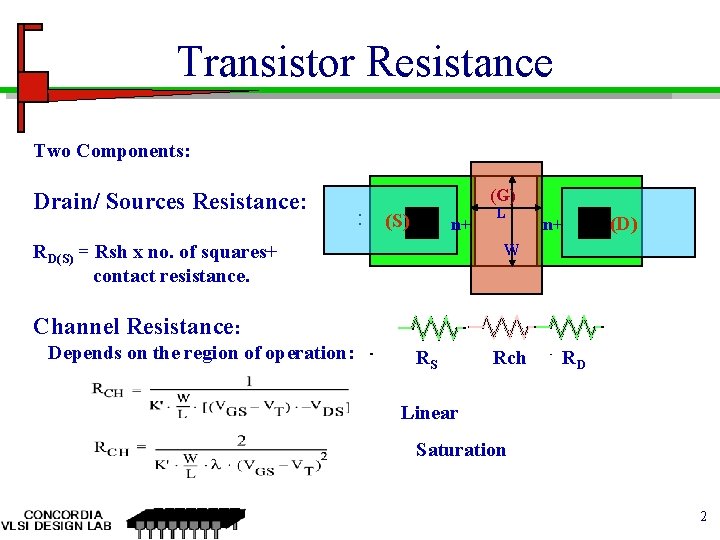

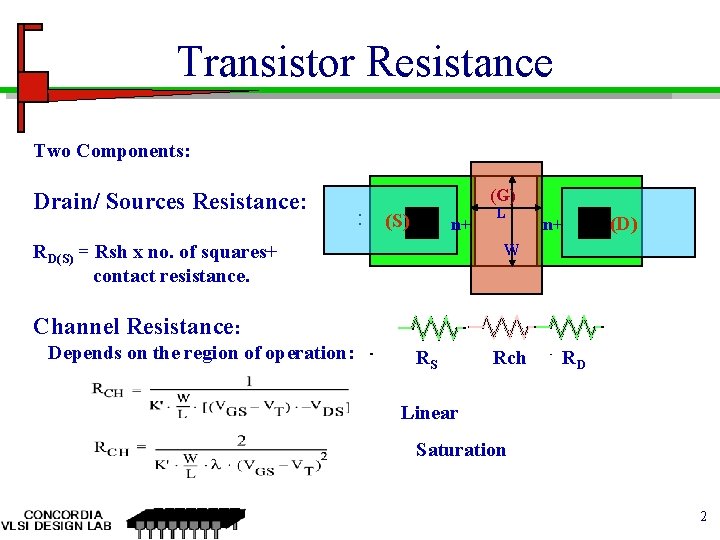

Transistor Resistance Two Components: Drain/ Sources Resistance: (G) : (S) n+ RD(S) = Rsh x no. of squares+ contact resistance. L n+ (D) W Channel Resistance: Depends on the region of operation: RS Rch RD Linear Saturation 2

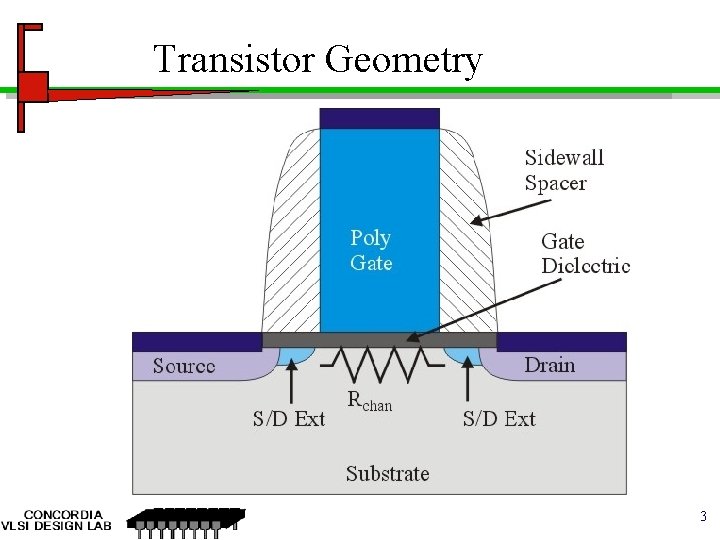

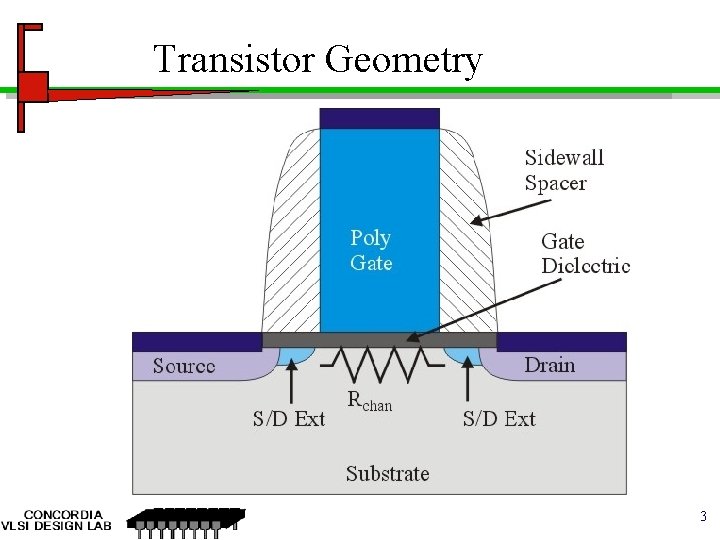

Transistor Geometry 3

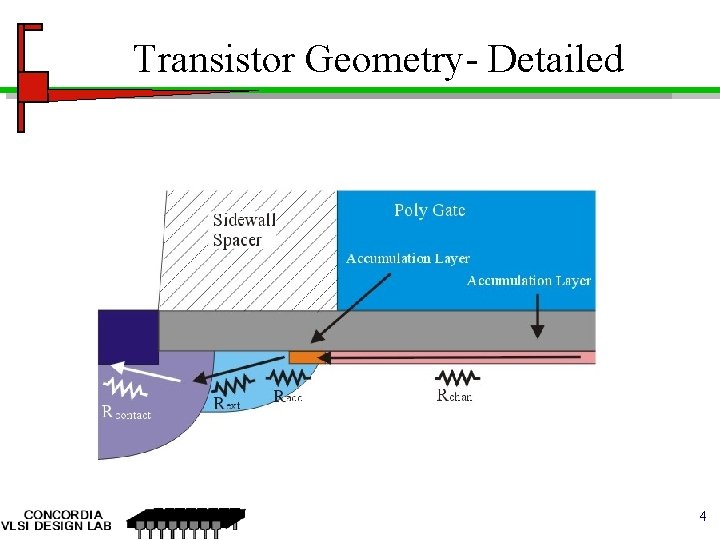

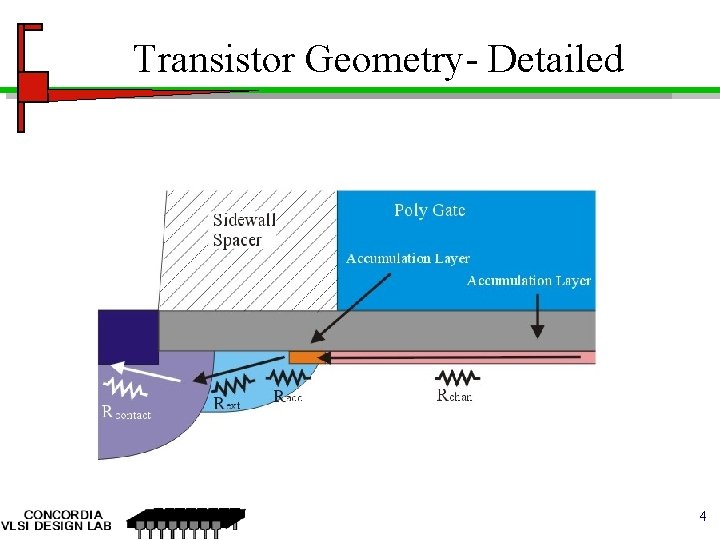

Transistor Geometry- Detailed 4

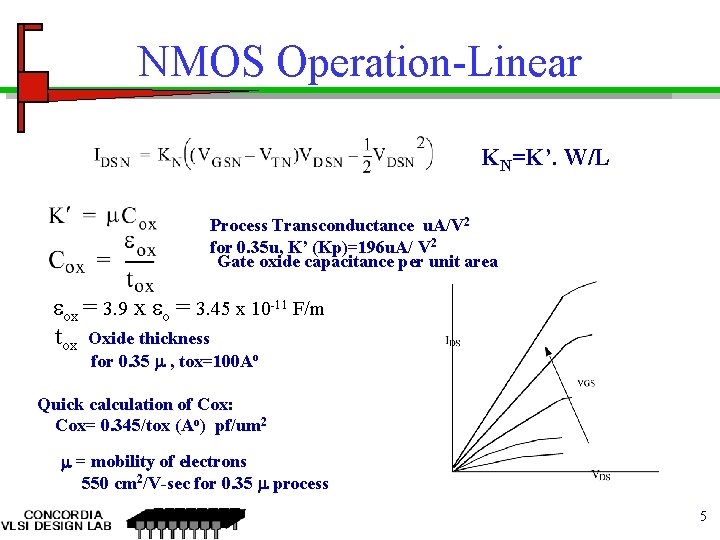

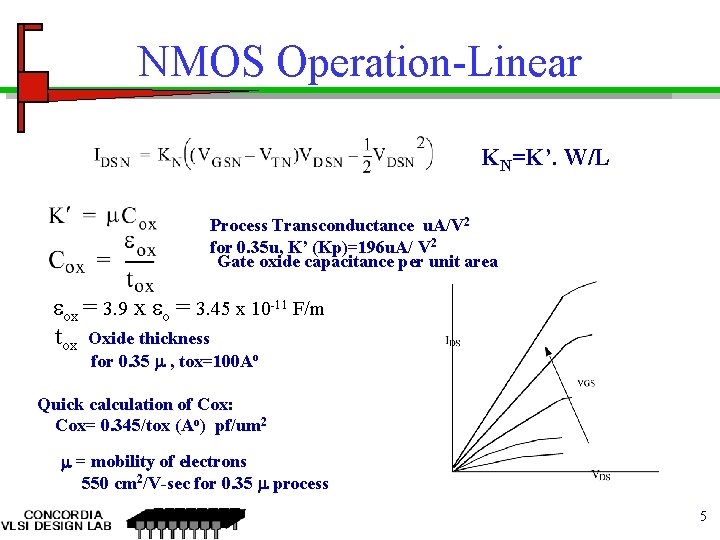

NMOS Operation-Linear KN=K’. W/L Process Transconductance u. A/V 2 for 0. 35 u, K’ (Kp)=196 u. A/ V 2 Gate oxide capacitance per unit area eox = 3. 9 x eo = 3. 45 x 10 -11 F/m tox Oxide thickness for 0. 35 m , tox=100 Ao Quick calculation of Cox: Cox= 0. 345/tox (Ao) pf/um 2 m = mobility of electrons 550 cm 2/V-sec for 0. 35 m process 5

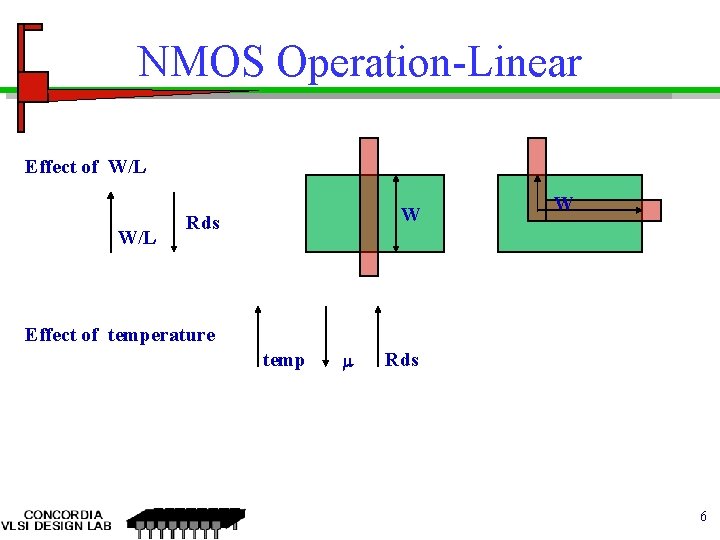

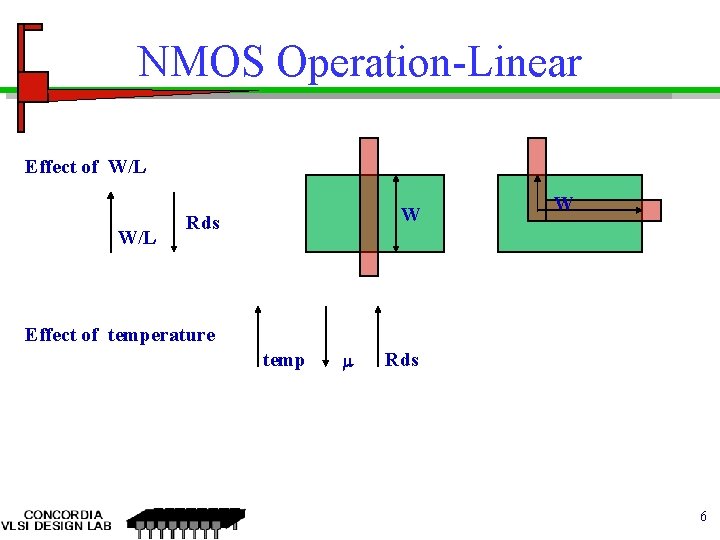

NMOS Operation-Linear Effect of W/L W Rds W Effect of temperature temp m Rds 6

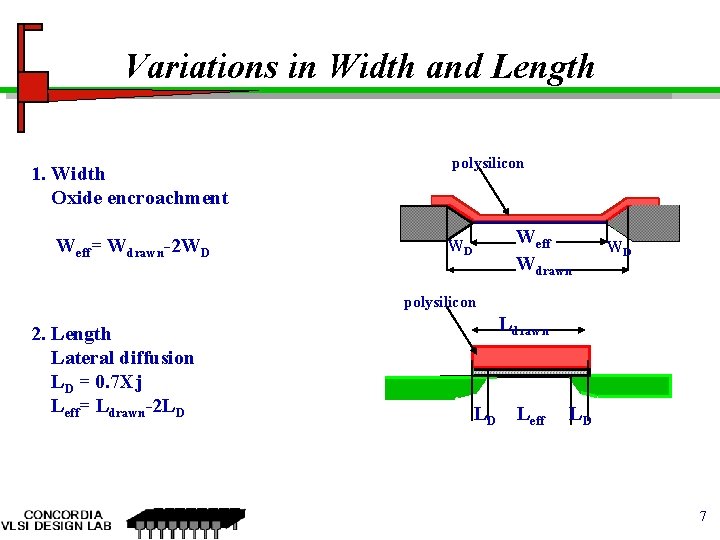

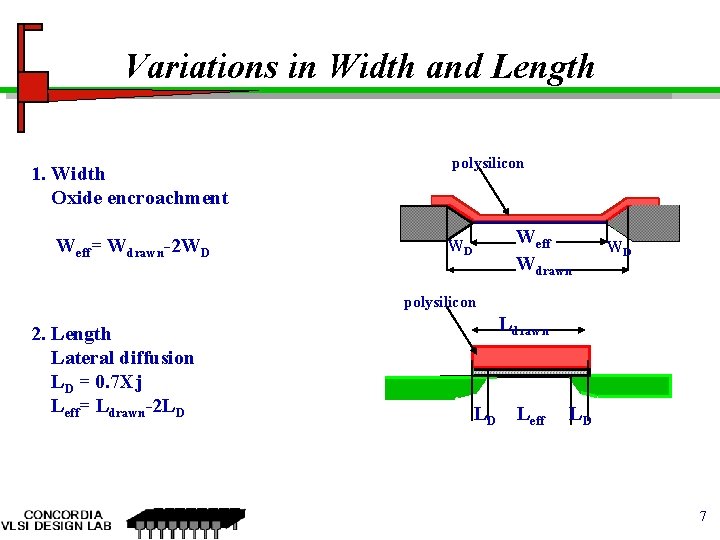

Variations in Width and Length 1. Width Oxide encroachment Weff= Wdrawn-2 WD polysilicon Weff Wdrawn WD WD polysilicon 2. Length Lateral diffusion LD = 0. 7 Xj Leff= Ldrawn-2 LD Ldrawn LD Leff LD 7

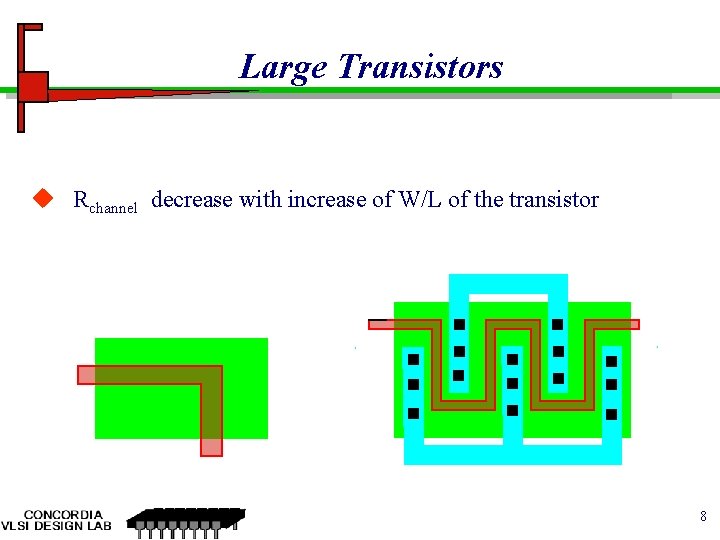

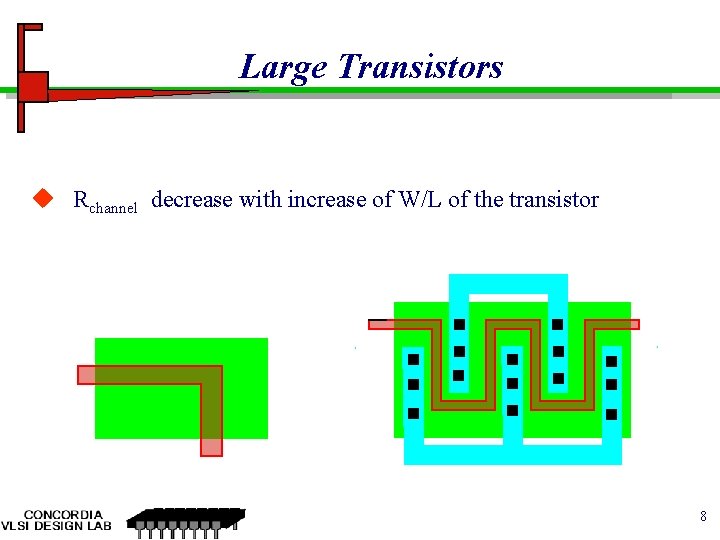

Large Transistors u Rchannel decrease with increase of W/L of the transistor 8

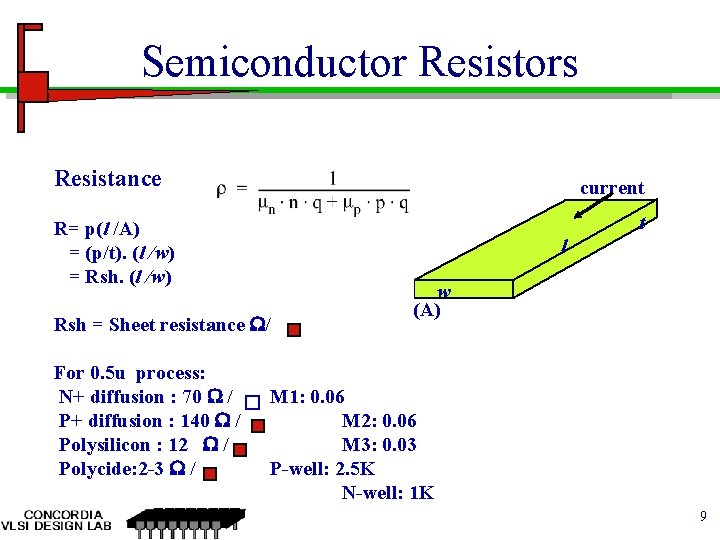

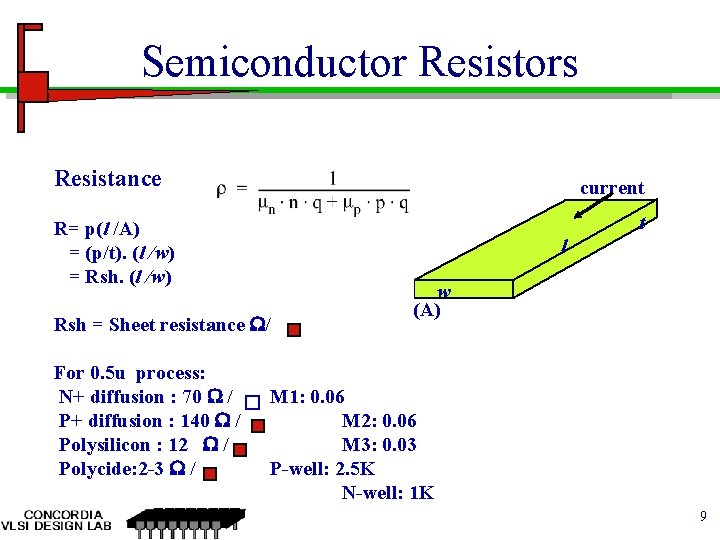

Semiconductor Resistors Resistance current t R= p(l /A) = (p/t). (l /w) = Rsh. (l /w) l Rsh = Sheet resistance / For 0. 5 u process: N+ diffusion : 70 / P+ diffusion : 140 / Polysilicon : 12 / Polycide: 2 -3 / w (A) M 1: 0. 06 M 2: 0. 06 M 3: 0. 03 P-well: 2. 5 K N-well: 1 K 9

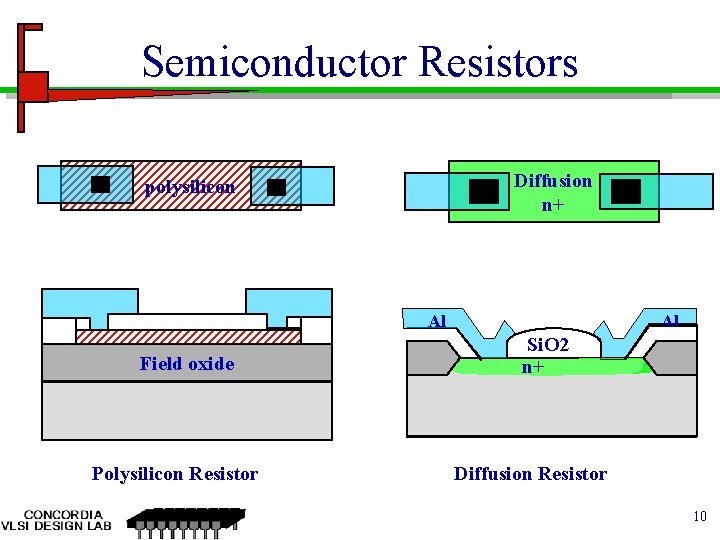

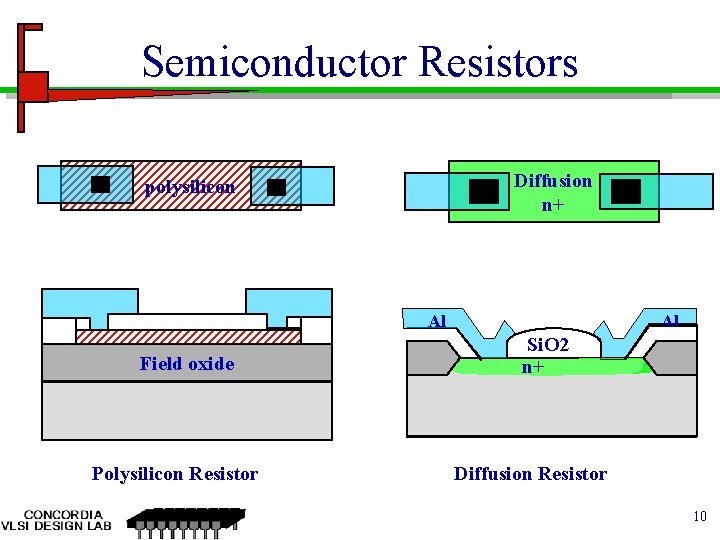

Semiconductor Resistors Diffusion n+ polysilicon Al Field oxide Polysilicon Resistor Al Si. O 2 n+ Diffusion Resistor 10

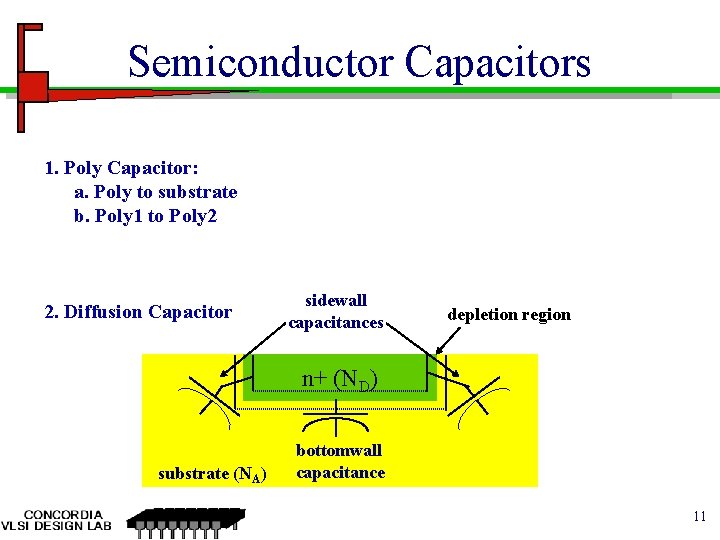

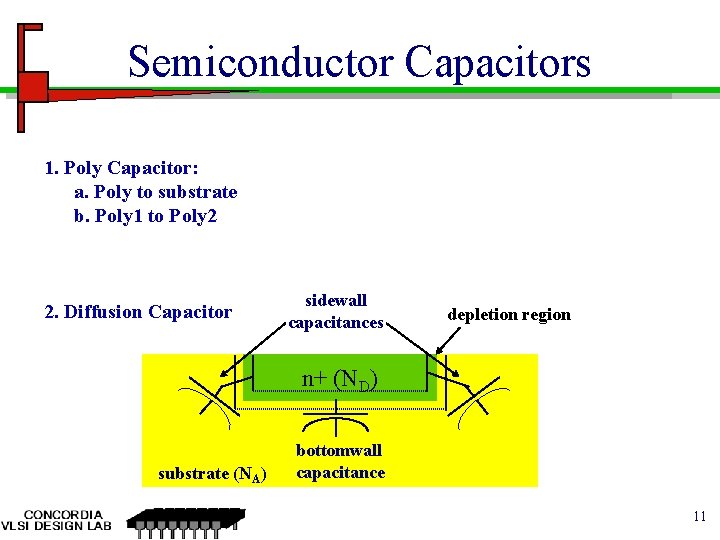

Semiconductor Capacitors 1. Poly Capacitor: a. Poly to substrate b. Poly 1 to Poly 2 2. Diffusion Capacitor sidewall capacitances depletion region n+ (ND) substrate (NA) bottomwall capacitance 11

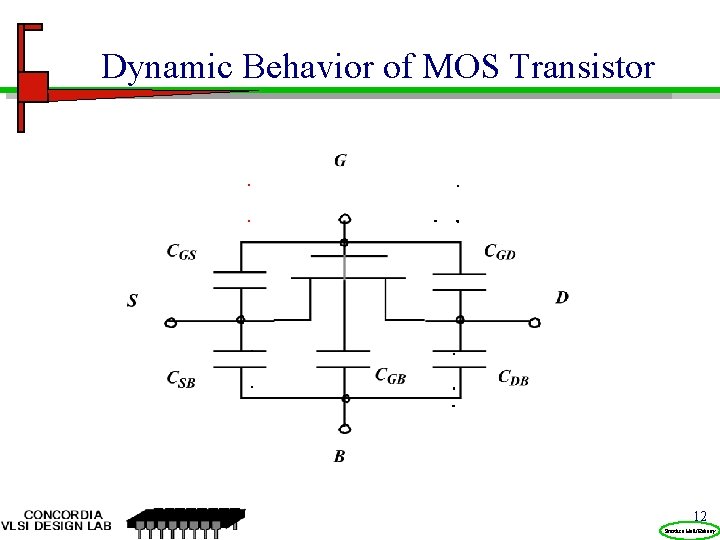

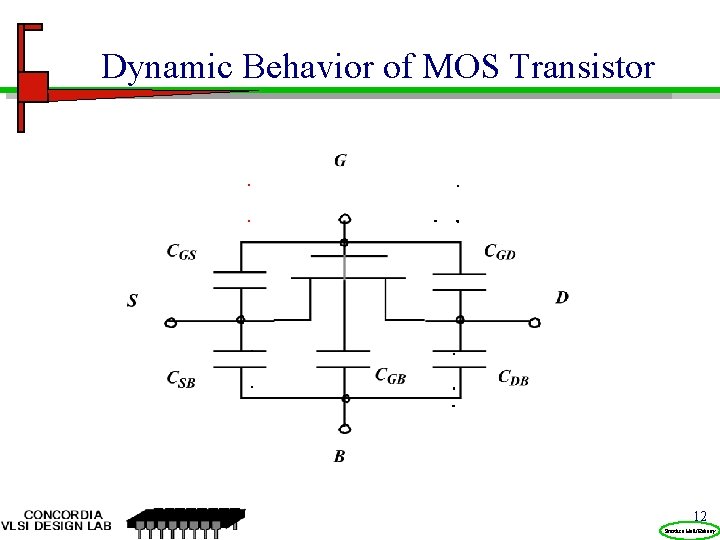

Dynamic Behavior of MOS Transistor 12 Prentice Hall/Rabaey

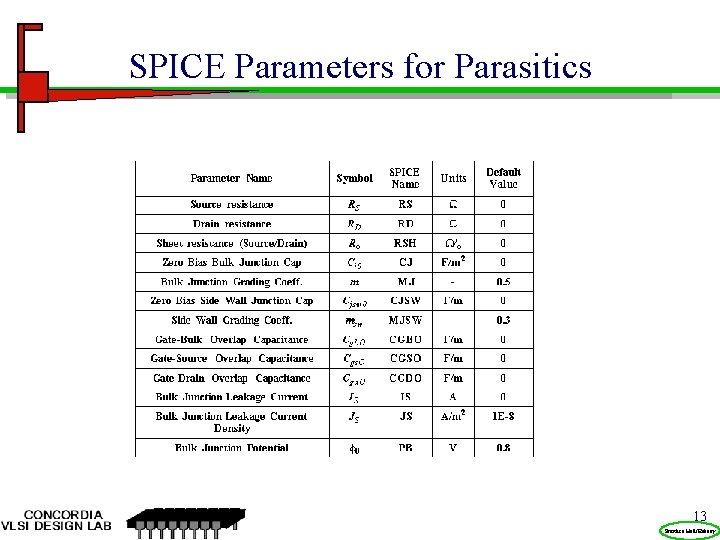

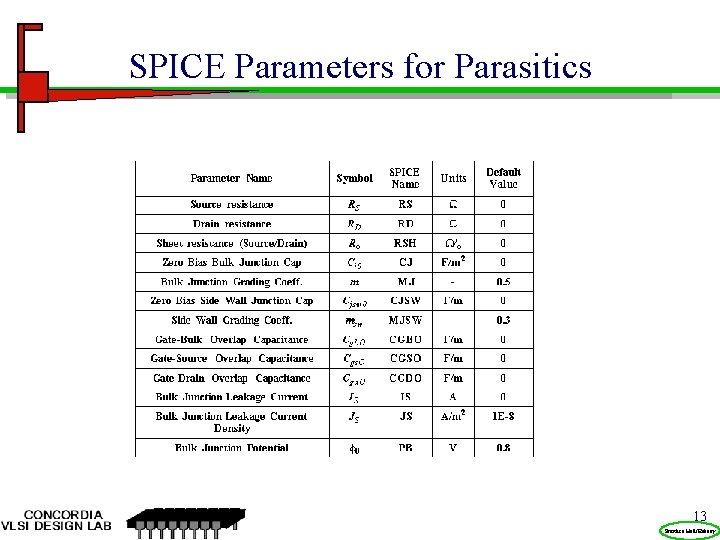

SPICE Parameters for Parasitics 13 Prentice Hall/Rabaey

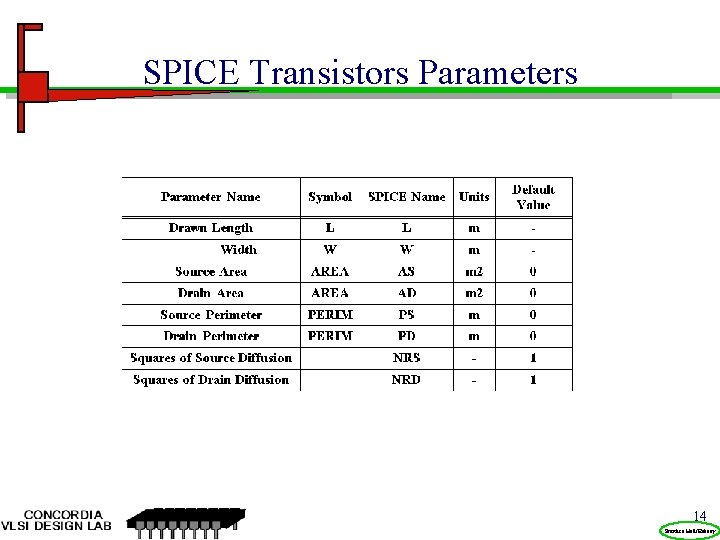

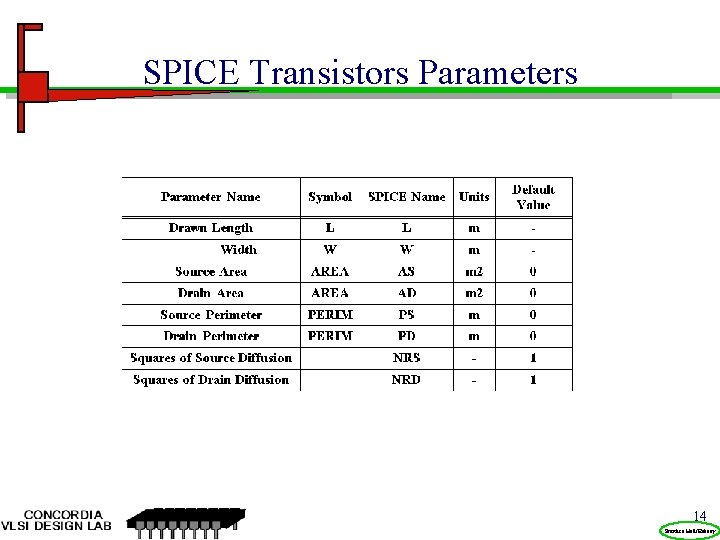

SPICE Transistors Parameters 14 Prentice Hall/Rabaey

![Modelling Resistance 1 Resistance Rint Rsh lw Rsh values for 0 35 u CMOS Modelling: Resistance 1. Resistance: Rint= Rsh [l/w] Rsh values for 0. 35 u CMOS](https://slidetodoc.com/presentation_image_h/0b4889420586bc2559569495e4ba6136/image-15.jpg)

Modelling: Resistance 1. Resistance: Rint= Rsh [l/w] Rsh values for 0. 35 u CMOS Process: Polysilicon 10 / Polycide 2 / Metal 1 0. 07 / Metal III 0. 05 / Contact resistance: Poly. I to Metal. I 50 Via resistance: Metal I to Metal II 1. 5 Via resistance: Metal II to metal III 1. 15

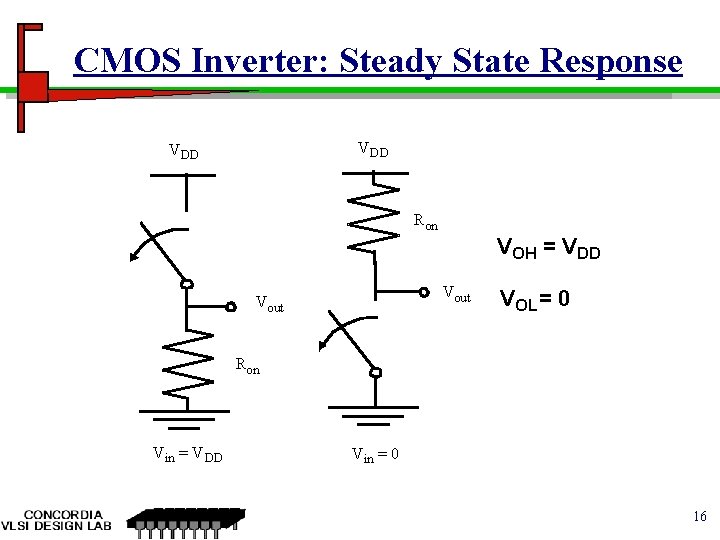

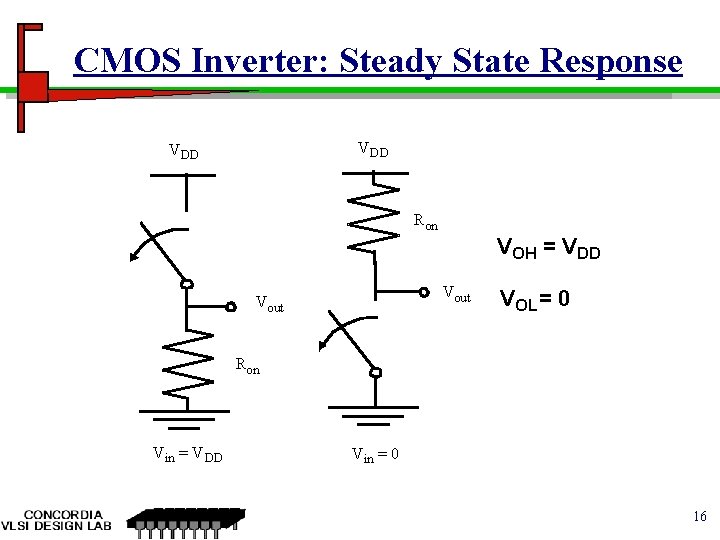

CMOS Inverter: Steady State Response VDD Ron VOH = VDD Vout VOL = 0 Ron Vin = V DD Vin = 0 16

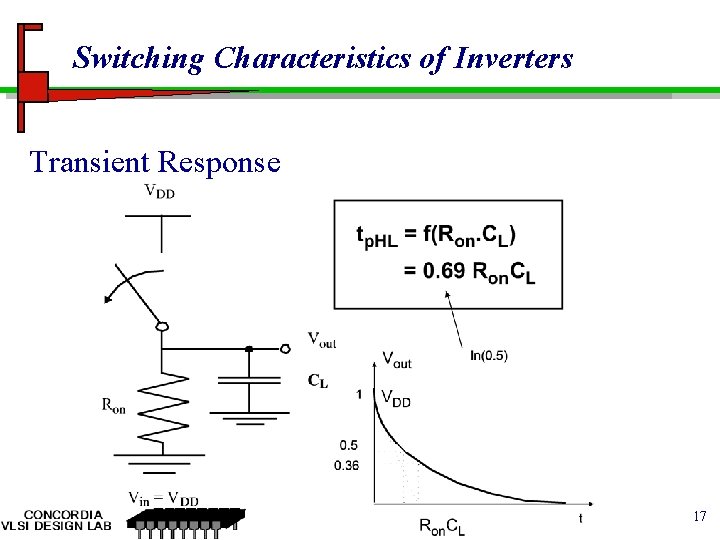

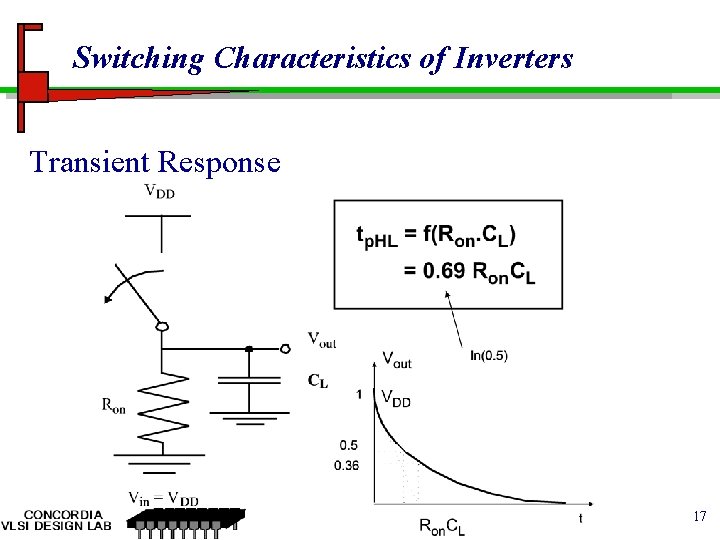

Switching Characteristics of Inverters Transient Response 17

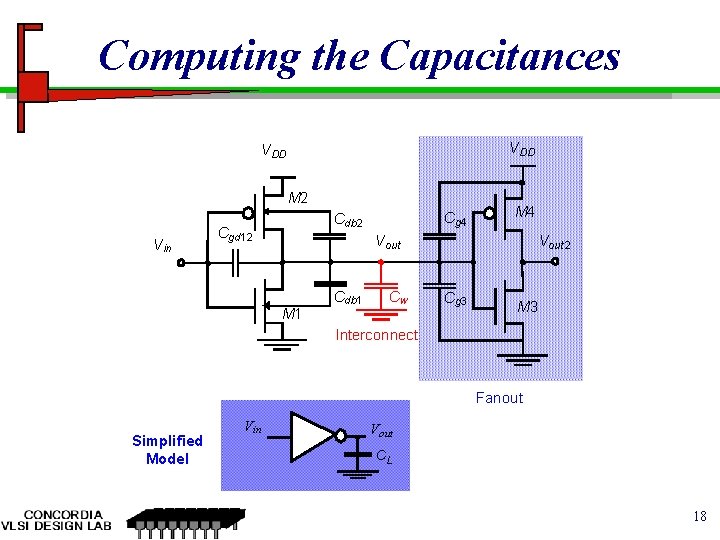

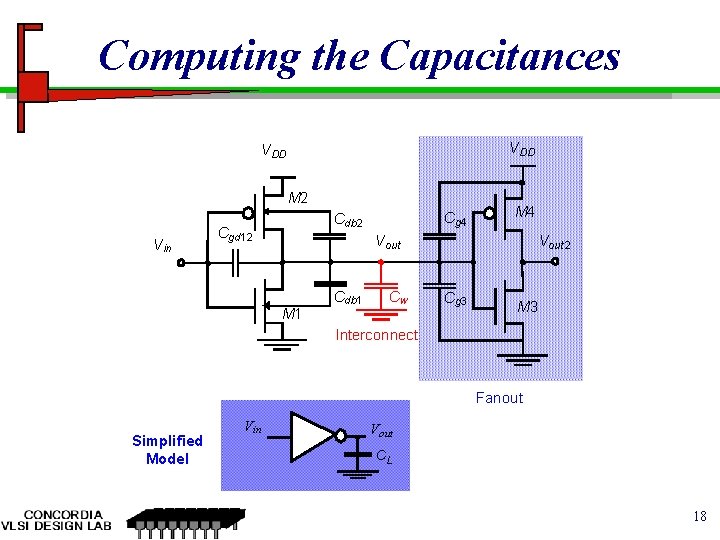

Computing the Capacitances VDD M 2 Vin Cg 4 Cdb 2 Cgd 12 M 4 Vout M 1 Cdb 1 Cw Vout 2 Cg 3 M 3 Interconnect Fanout Simplified Model Vin Vout CL 18

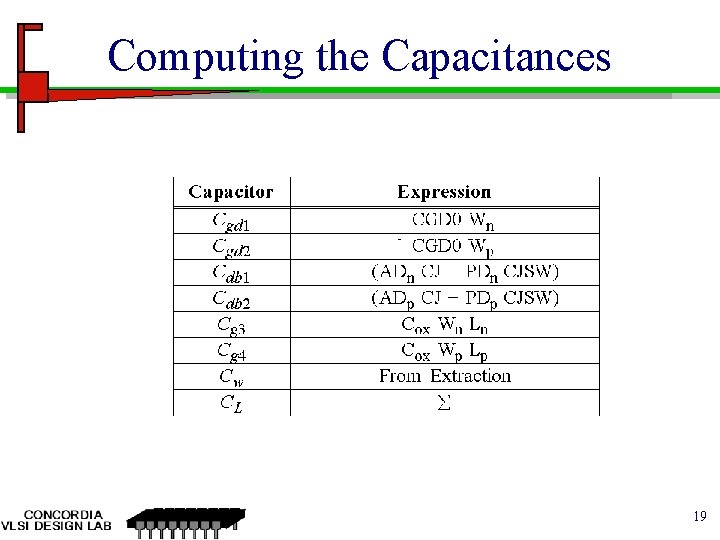

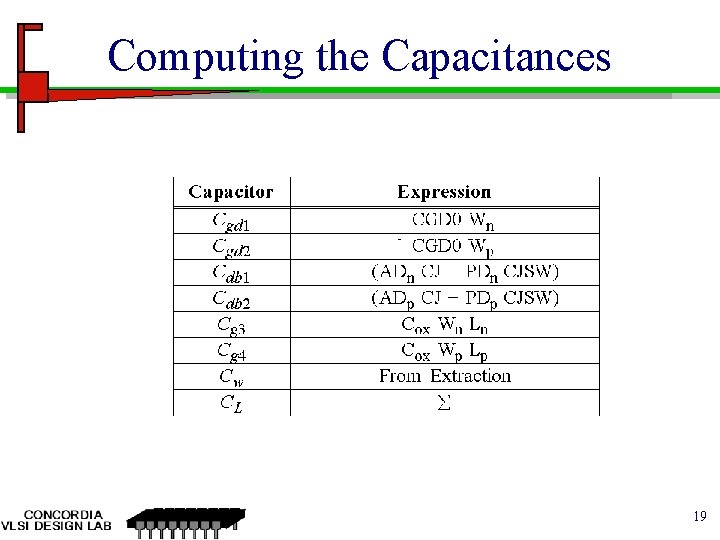

Computing the Capacitances 19

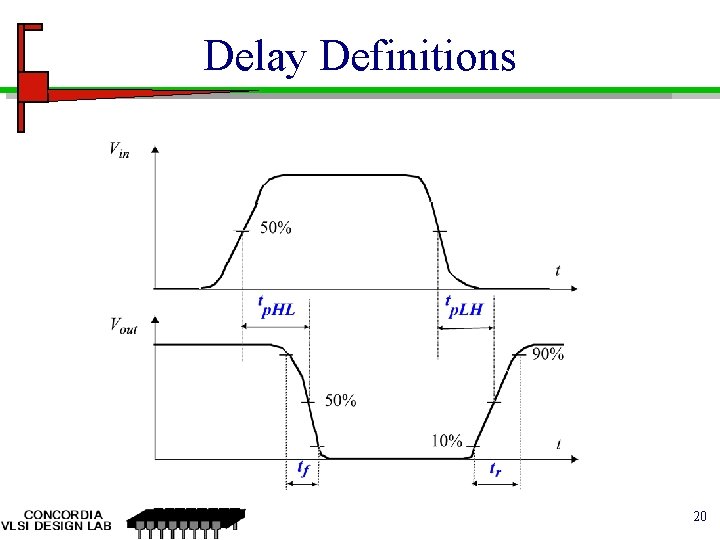

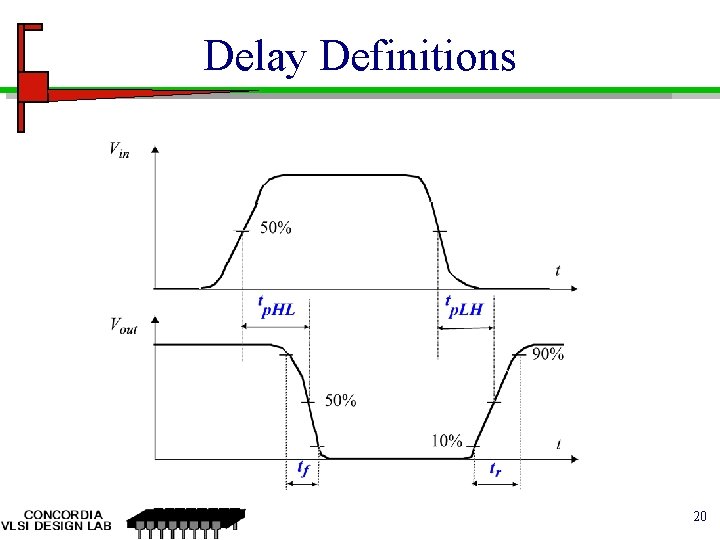

Delay Definitions 20

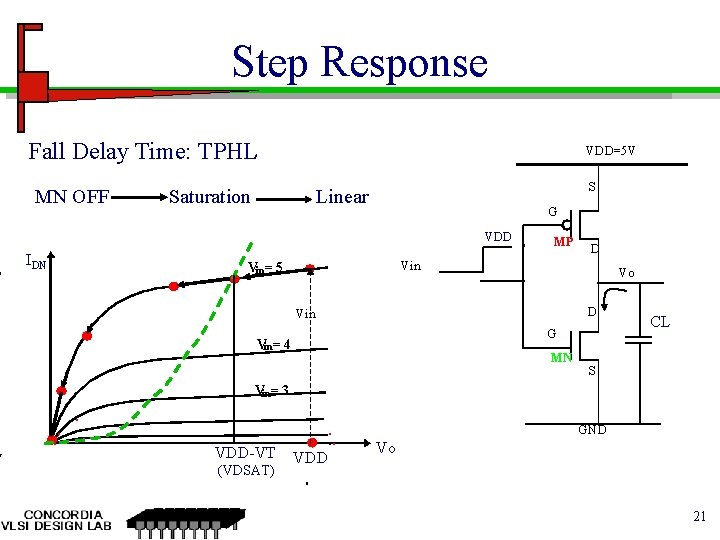

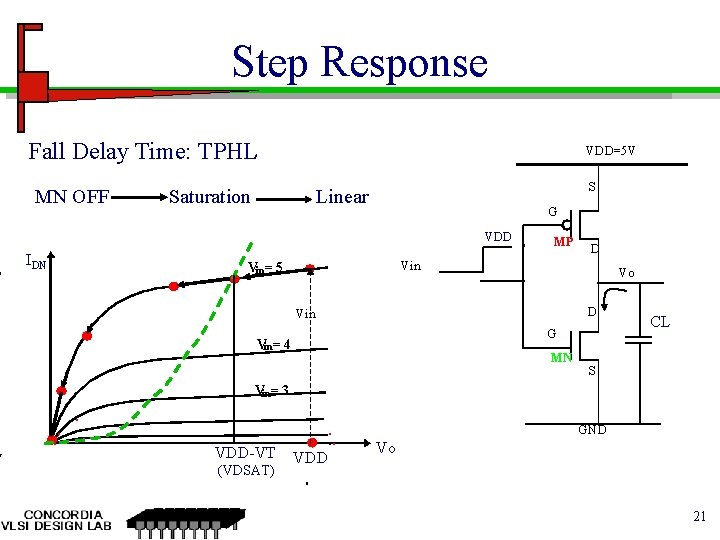

Step Response Fall Delay Time: TPHL MN OFF VDD=5 V Saturation S Linear G VDD IDN MP D Vin = 5 Vo D Vin G Vin= 4 MN CL S Vin= 3 GND VDD-VT (VDSAT) VDD Vo 21

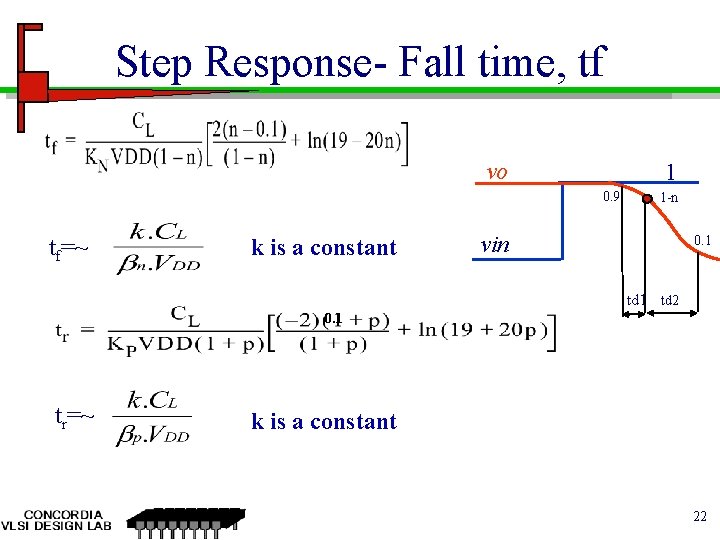

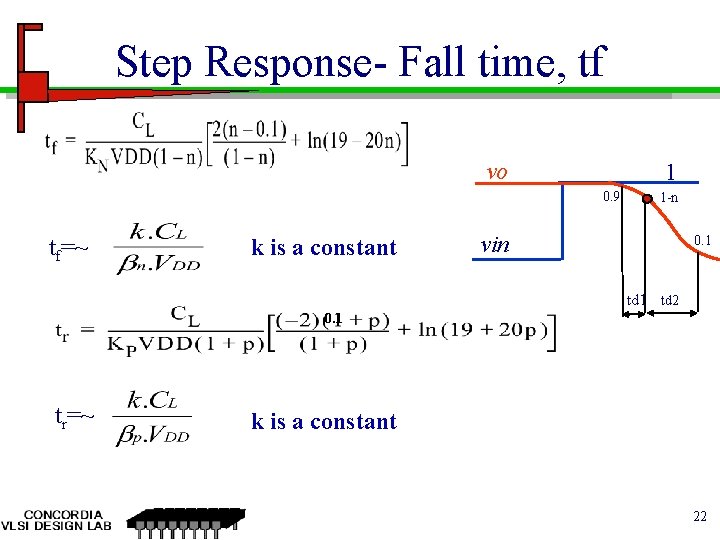

Step Response- Fall time, tf vo 1 0. 9 tf=~ k is a constant 1 -n vin 0. 1 td 2 0. 1 tr=~ k is a constant 22

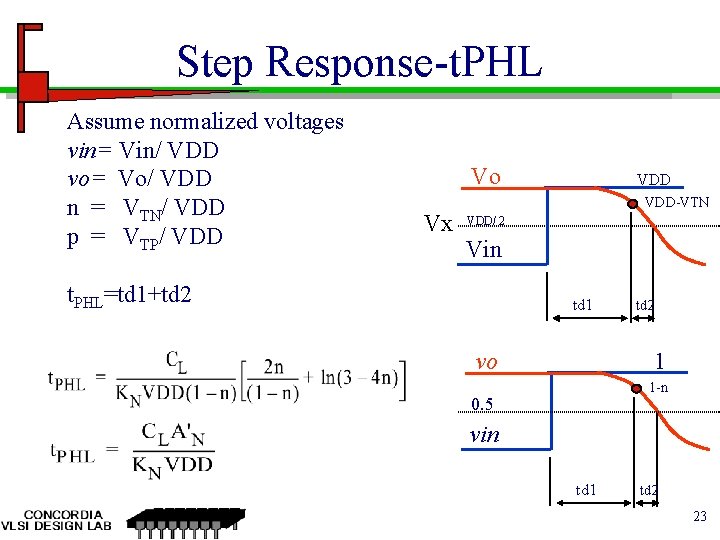

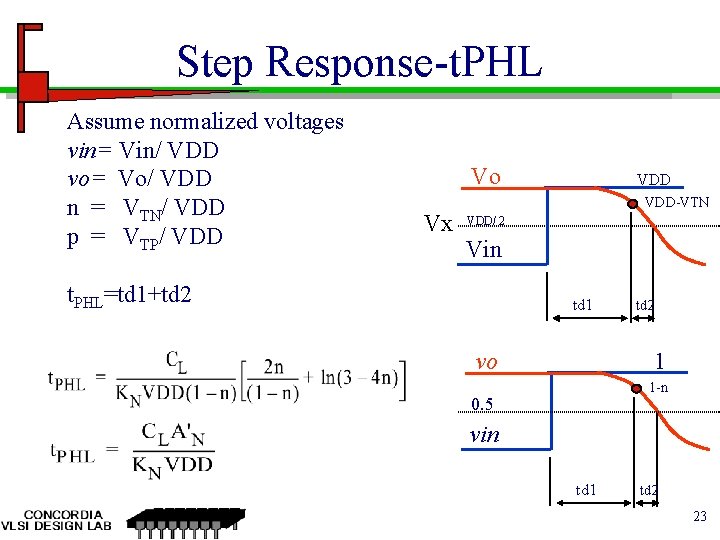

Step Response-t. PHL Assume normalized voltages vin= Vin/ VDD vo= Vo/ VDD n = VTN/ VDD p = VTP/ VDD Vo Vx VDD-VTN VDD/ 2 Vin t. PHL=td 1+td 2 td 1 vo td 2 1 1 -n 0. 5 vin td 1 td 2 23

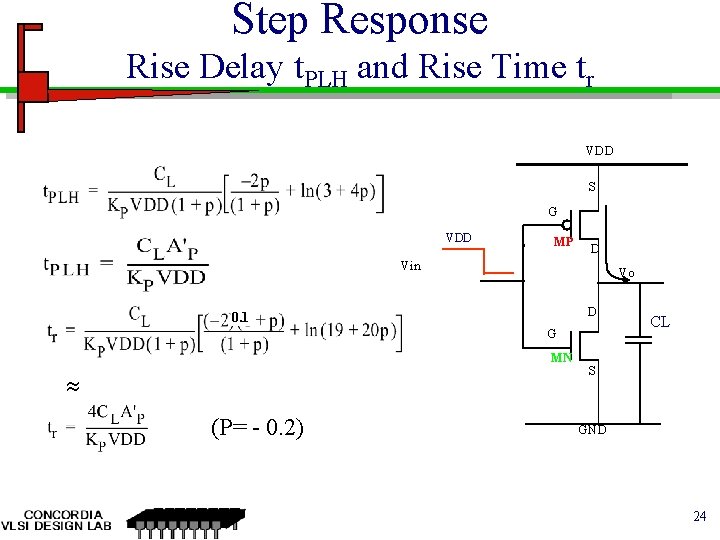

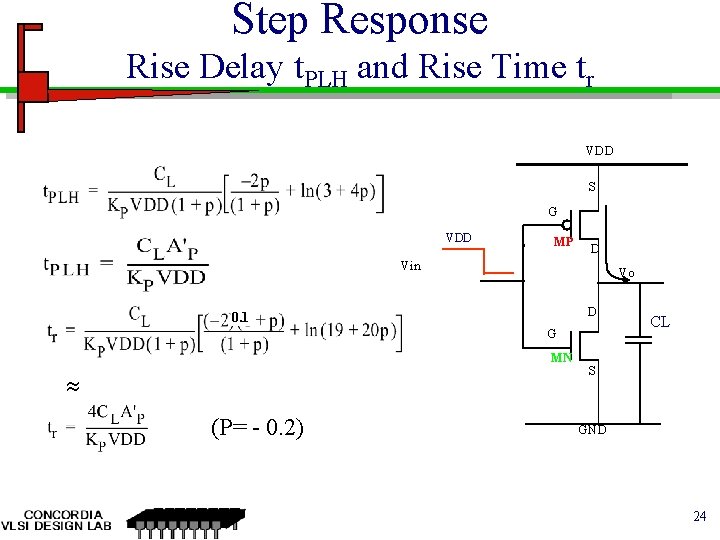

Step Response Rise Delay t. PLH and Rise Time tr VDD S G VDD MP D Vin Vo D 0. 1 G MN (P= - 0. 2) CL S GND 24

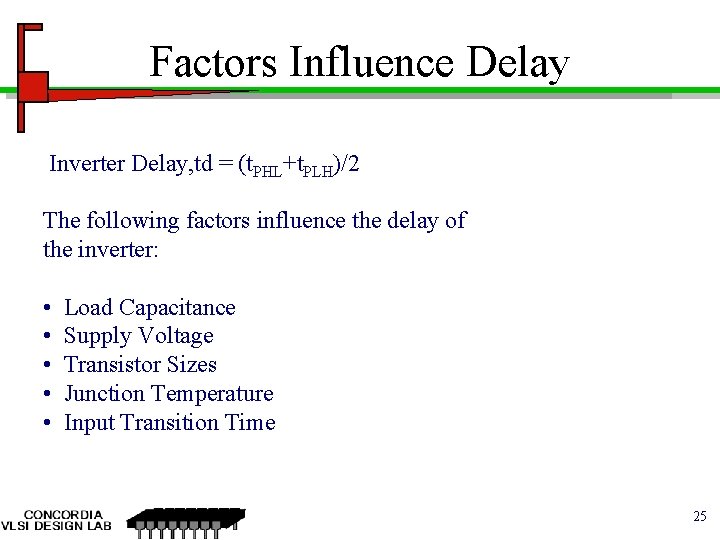

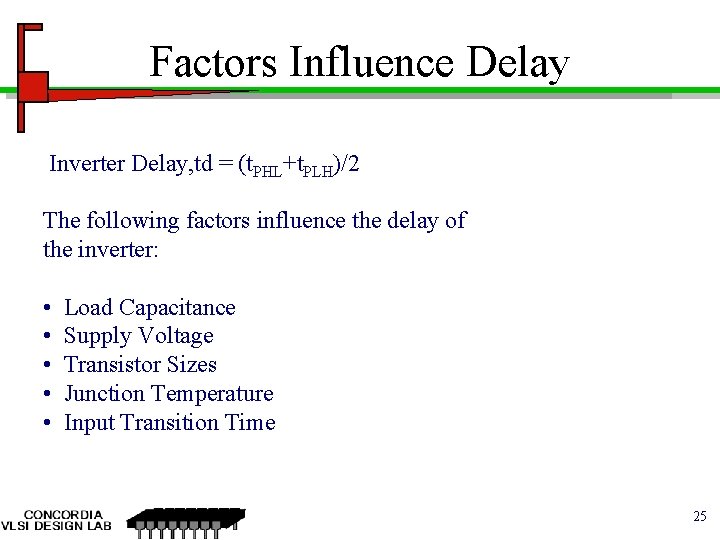

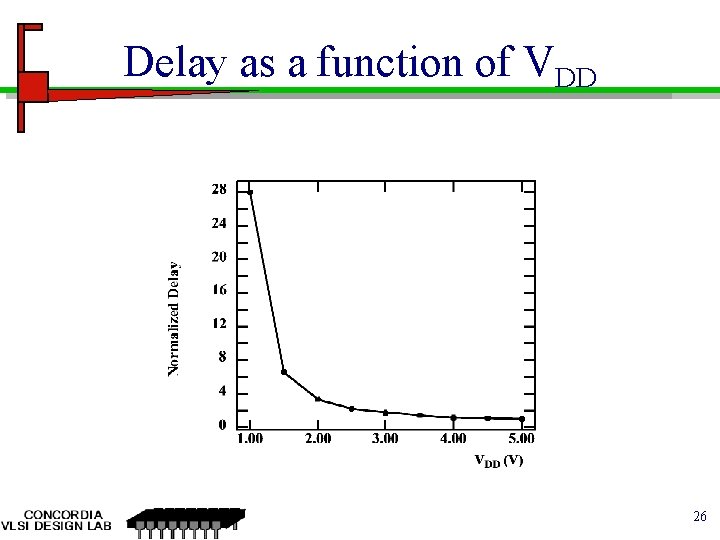

Factors Influence Delay Inverter Delay, td = (t. PHL+t. PLH)/2 The following factors influence the delay of the inverter: • • • Load Capacitance Supply Voltage Transistor Sizes Junction Temperature Input Transition Time 25

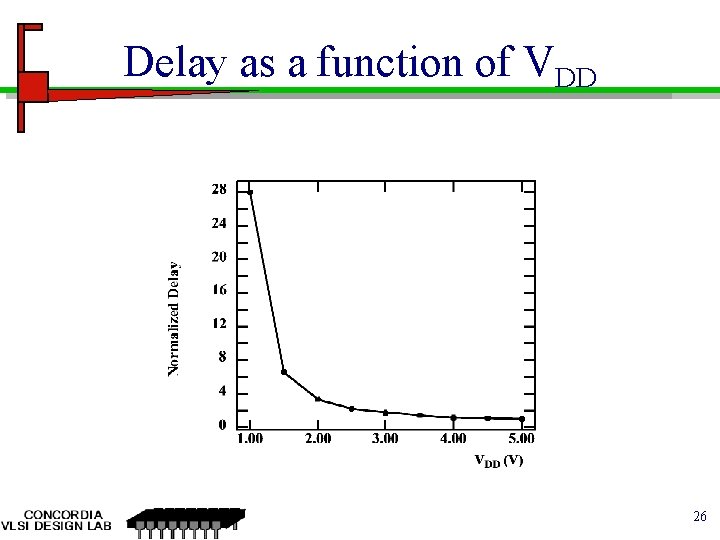

Delay as a function of VDD 26

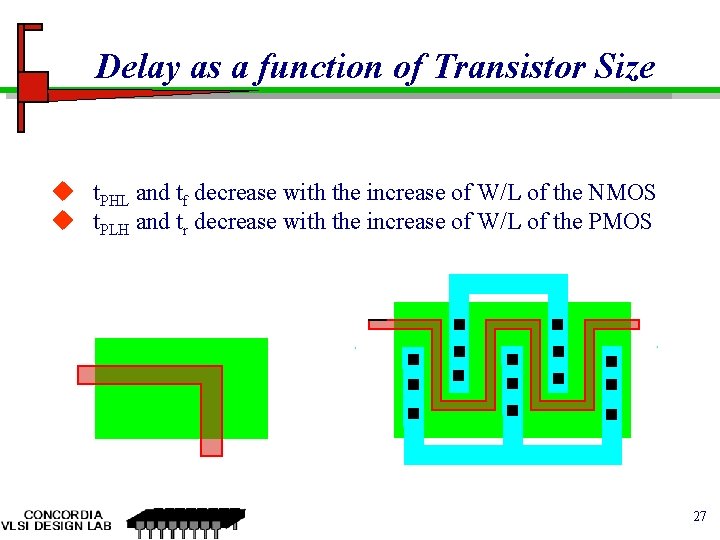

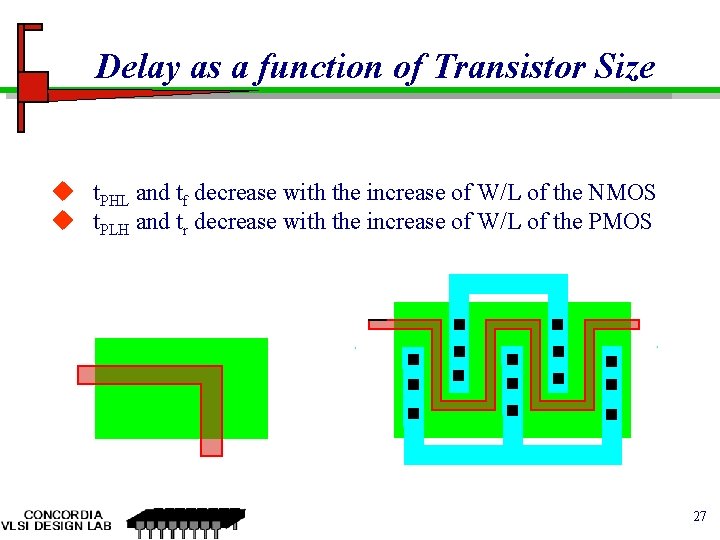

Delay as a function of Transistor Size u t. PHL and tf decrease with the increase of W/L of the NMOS u t. PLH and tr decrease with the increase of W/L of the PMOS 27

Temperature Effect u u Temperature ranges: commercial : 0 to 700 C industrial: -40 to 850 C military: -55 to 1250 C Calculation of the junction temperature tj= ta + ja X Pd Effect of temperature on mobility Delay and speed implications 28

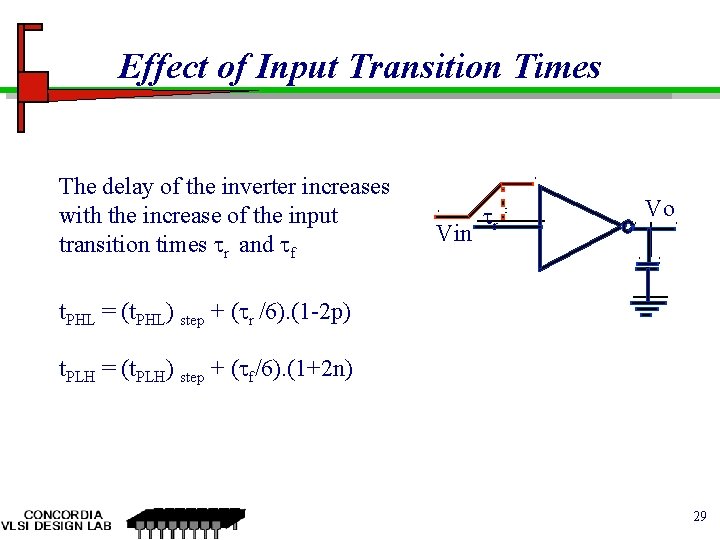

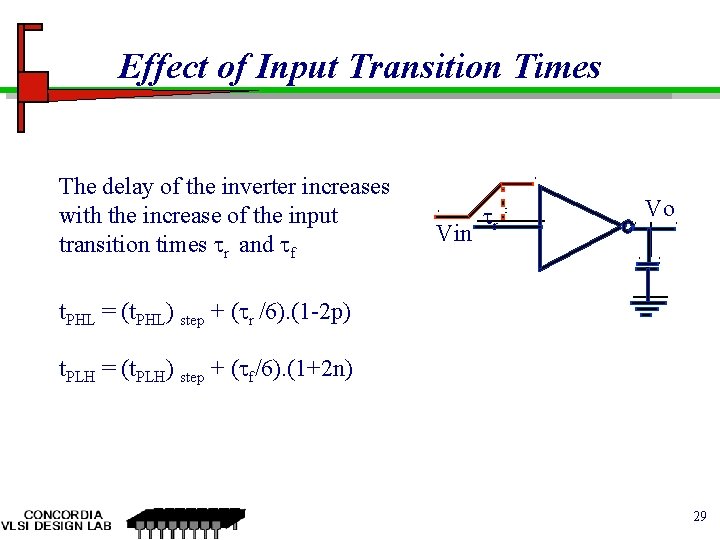

Effect of Input Transition Times The delay of the inverter increases with the increase of the input transition times r and f Vin r Vo t. PHL = (t. PHL) step + ( r /6). (1 -2 p) t. PLH = (t. PLH) step + ( f/6). (1+2 n) 29

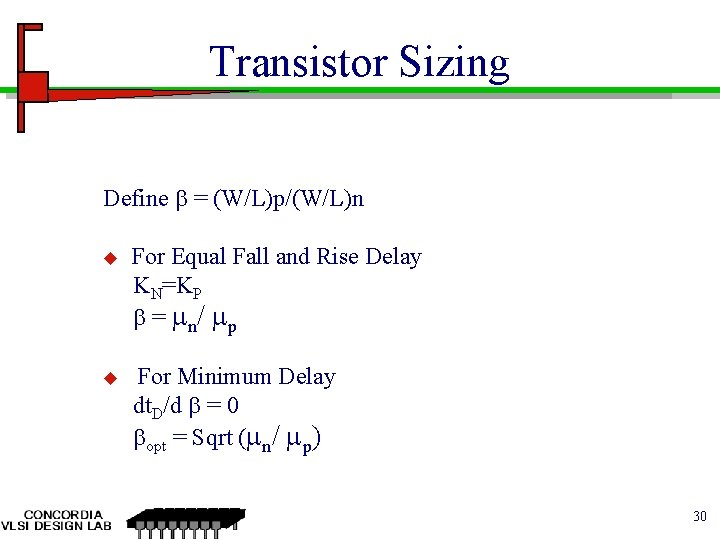

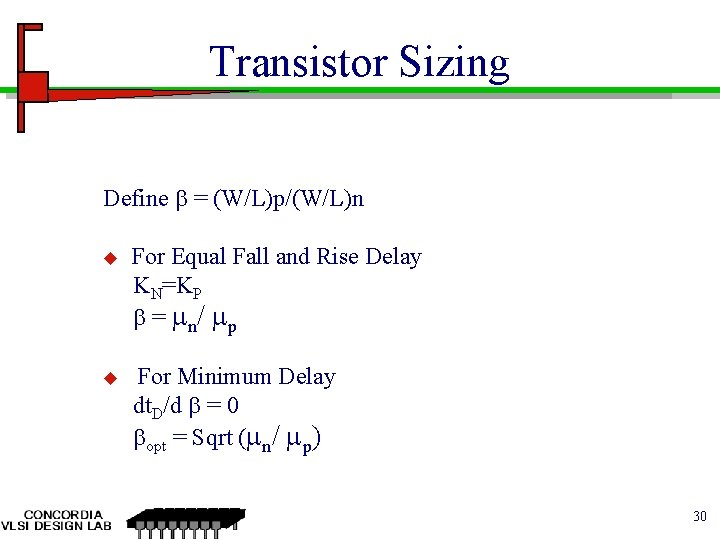

Transistor Sizing Define = (W/L)p/(W/L)n u For Equal Fall and Rise Delay KN=KP = n/ p u For Minimum Delay dt. D/d = 0 opt = Sqrt ( n/ p) 30

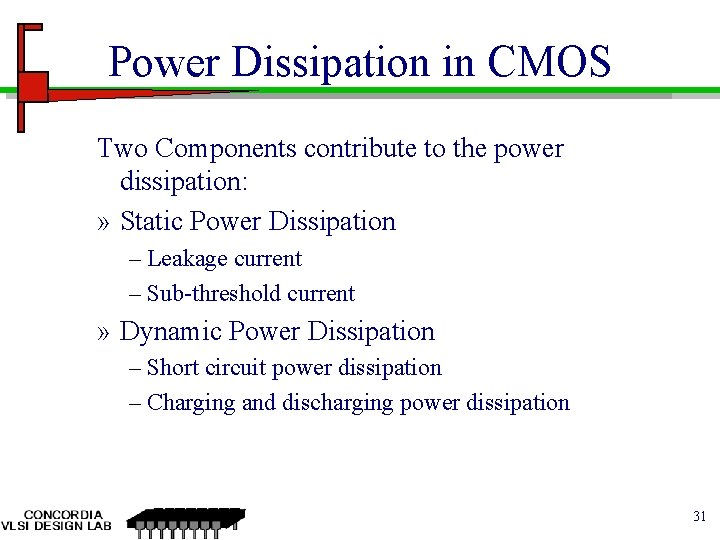

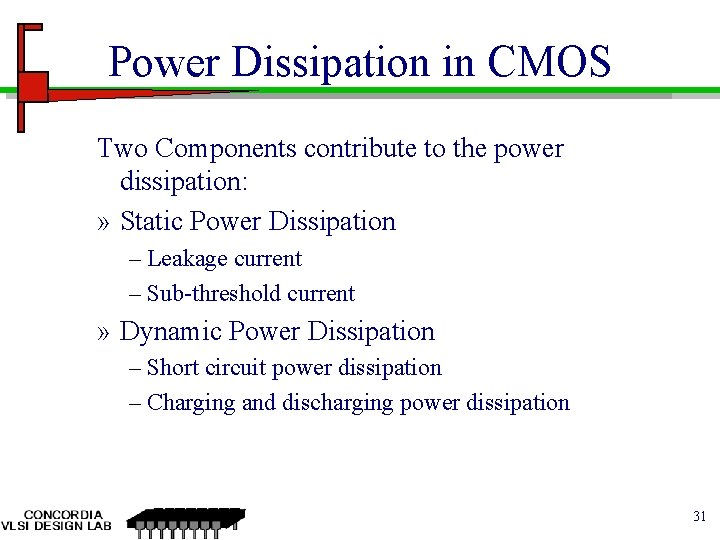

Power Dissipation in CMOS Two Components contribute to the power dissipation: » Static Power Dissipation – Leakage current – Sub-threshold current » Dynamic Power Dissipation – Short circuit power dissipation – Charging and discharging power dissipation 31

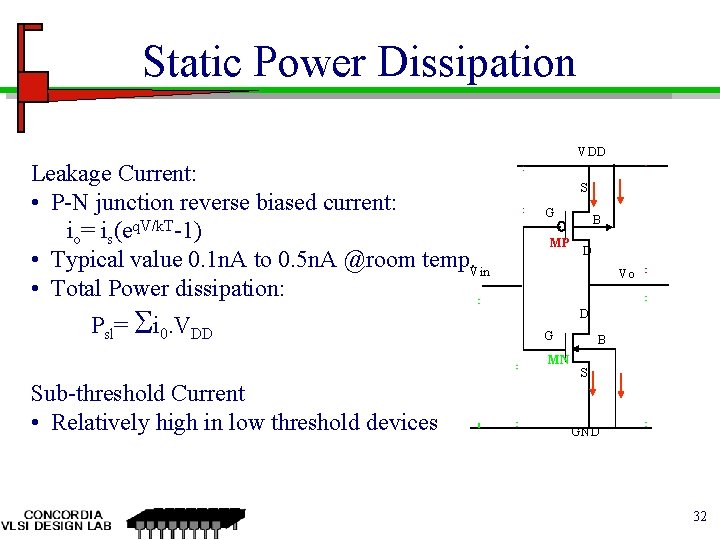

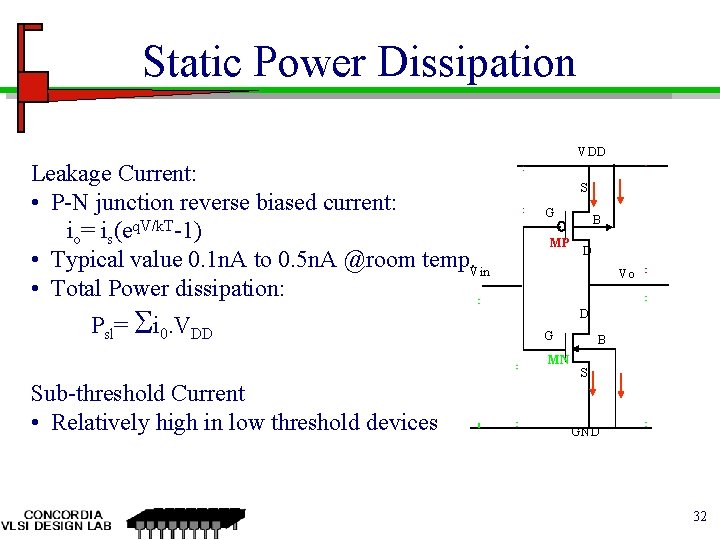

Static Power Dissipation VDD Leakage Current: • P-N junction reverse biased current: io= is(eq. V/k. T-1) • Typical value 0. 1 n. A to 0. 5 n. A @room temp. Vin • Total Power dissipation: Psl= i 0. VDD S G MP D Vo D G MN Sub-threshold Current • Relatively high in low threshold devices B B S GND 32

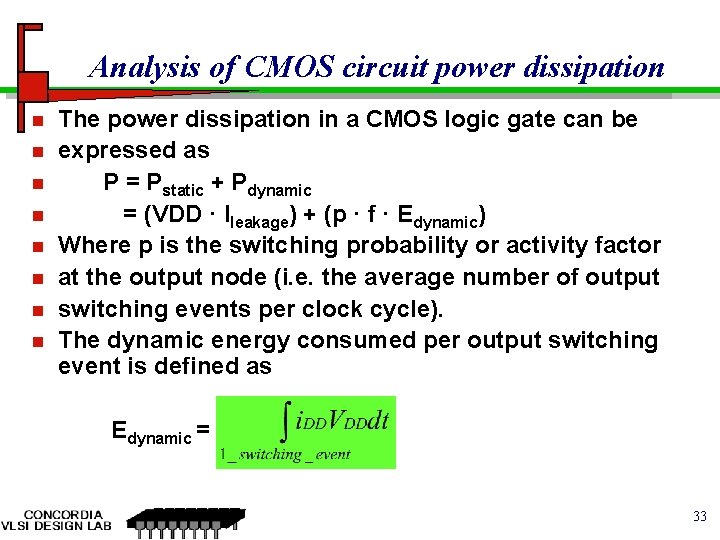

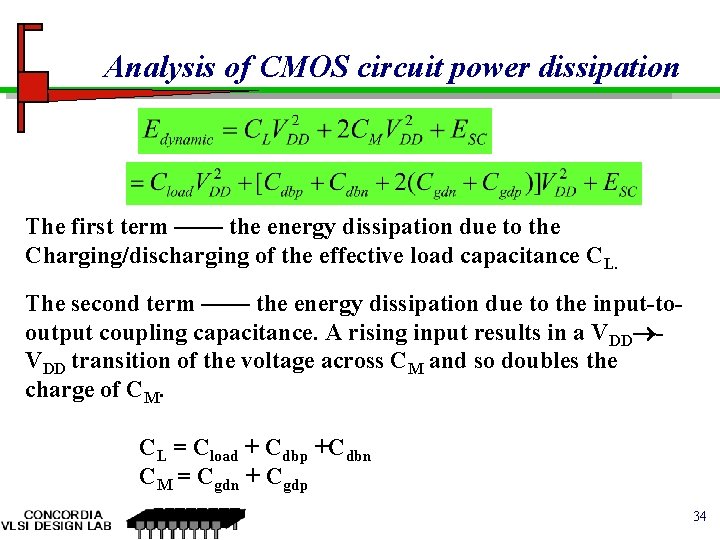

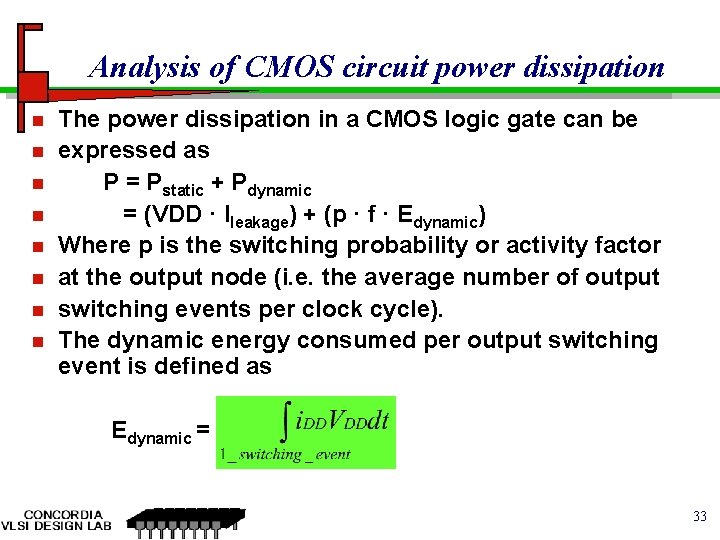

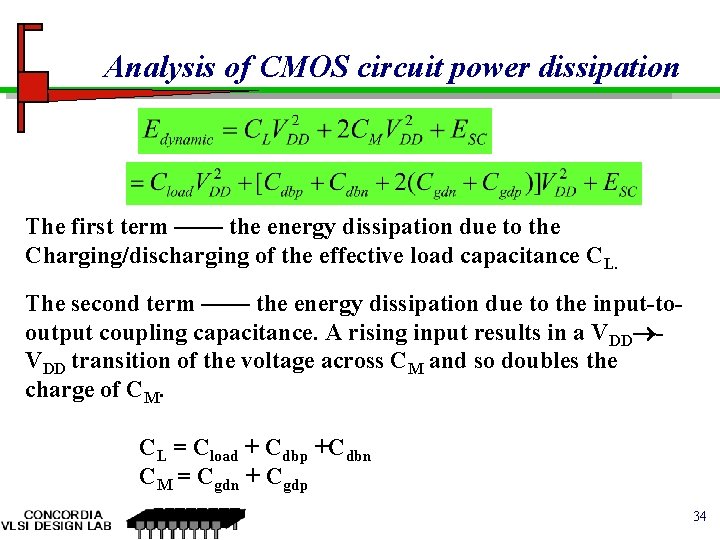

Analysis of CMOS circuit power dissipation n n n n The power dissipation in a CMOS logic gate can be expressed as P = Pstatic + Pdynamic = (VDD · Ileakage) + (p · f · Edynamic) Where p is the switching probability or activity factor at the output node (i. e. the average number of output switching events per clock cycle). The dynamic energy consumed per output switching event is defined as Edynamic = 33

Analysis of CMOS circuit power dissipation The first term —— the energy dissipation due to the Charging/discharging of the effective load capacitance CL. The second term —— the energy dissipation due to the input-tooutput coupling capacitance. A rising input results in a VDD transition of the voltage across CM and so doubles the charge of CM. CL = Cload + Cdbp +Cdbn CM = Cgdn + Cgdp 34

The MOSFET parasitic capacitances • distributed, n • voltage-dependent, and n • nonlinear. n So their exact modeling is quite complex. Even ESC can be modeled, it is also difficult to calculate the Edynamic. n On the other hand, if the short-circuit current i. SC can be Modeled, the power-supply current i. DD may be modeled with the same method. So there is a possibility to directly model i. DD instead of i. SC. 35

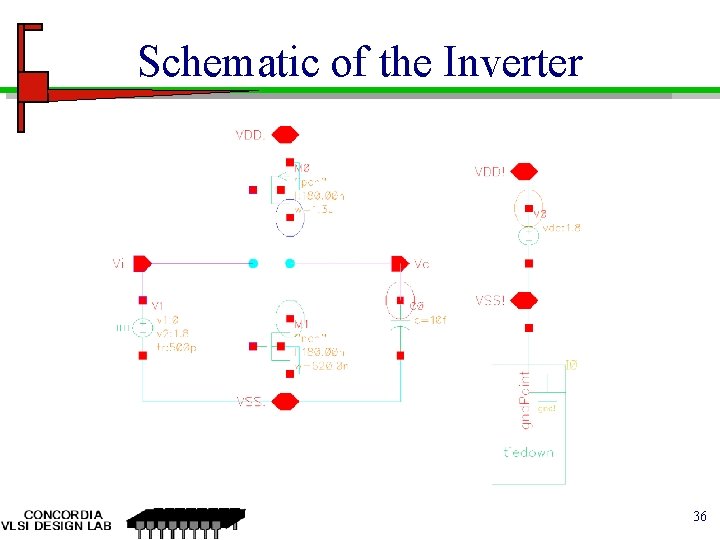

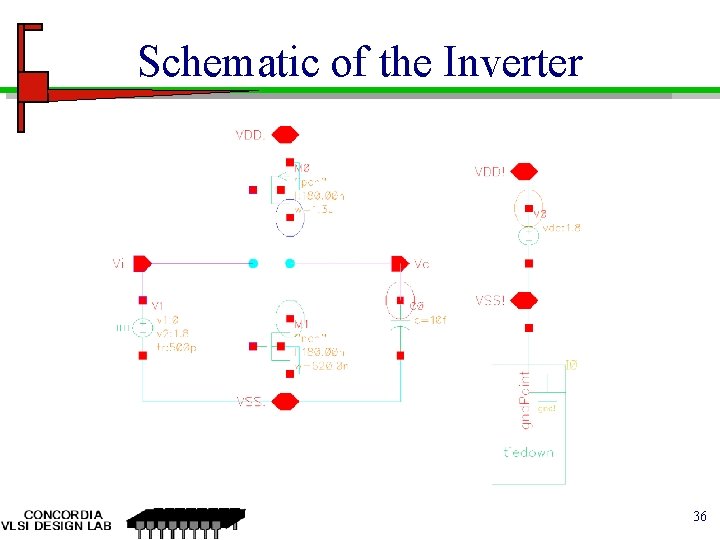

Schematic of the Inverter 36

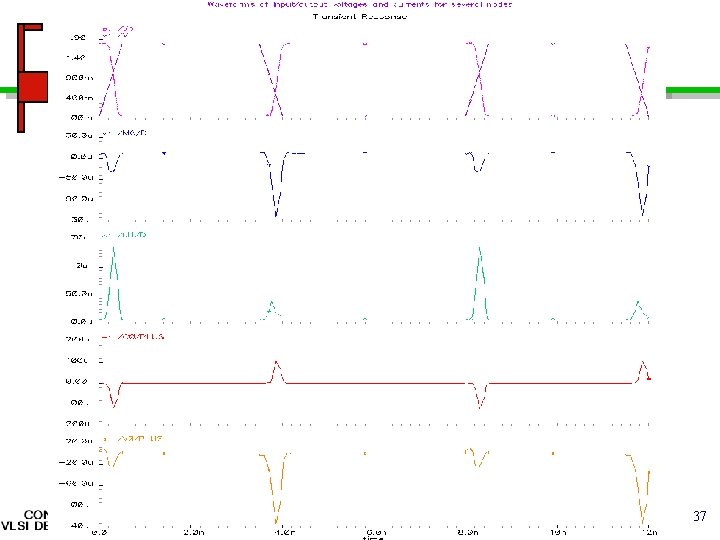

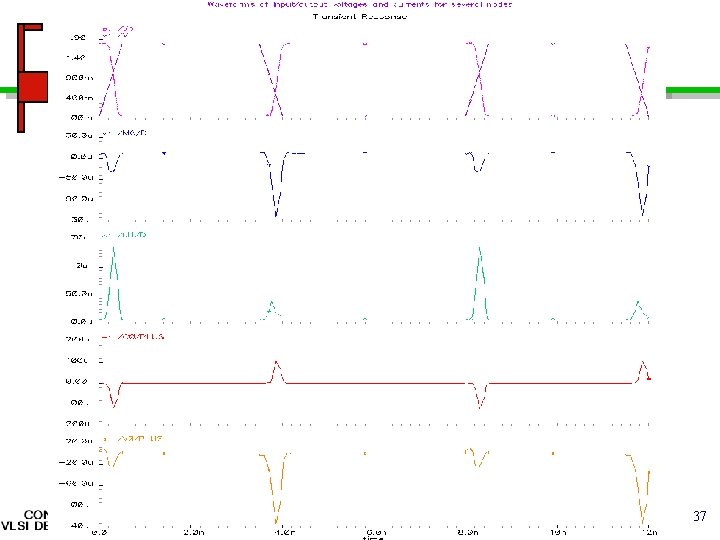

37

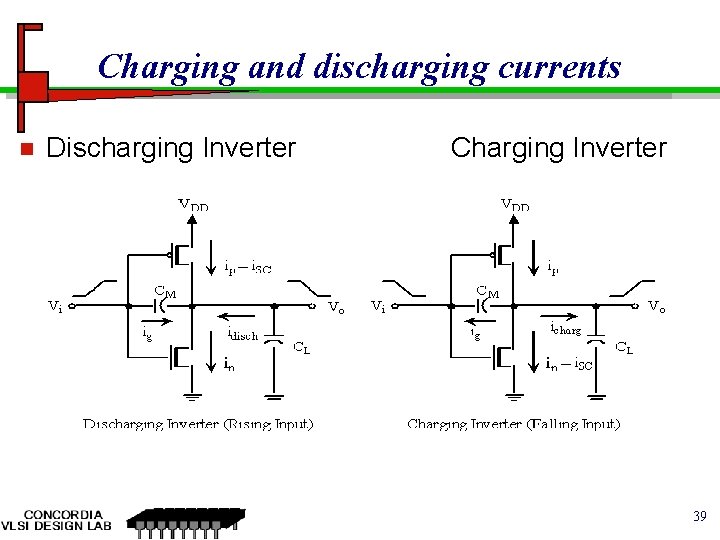

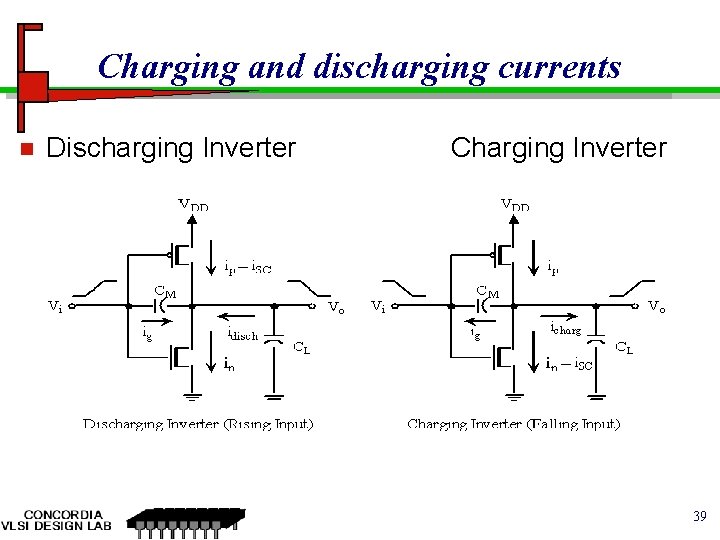

Analysis of short-circuit current The short-circuit energy dissipation ESC is due to the railto-rail current when both the PMOS and NMOS devices are simultaneously on. ESC = ESC_C + ESC_n Where and 38

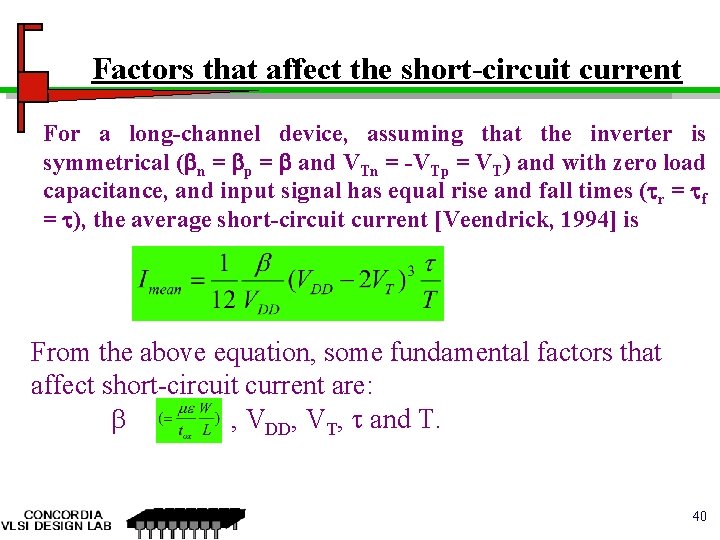

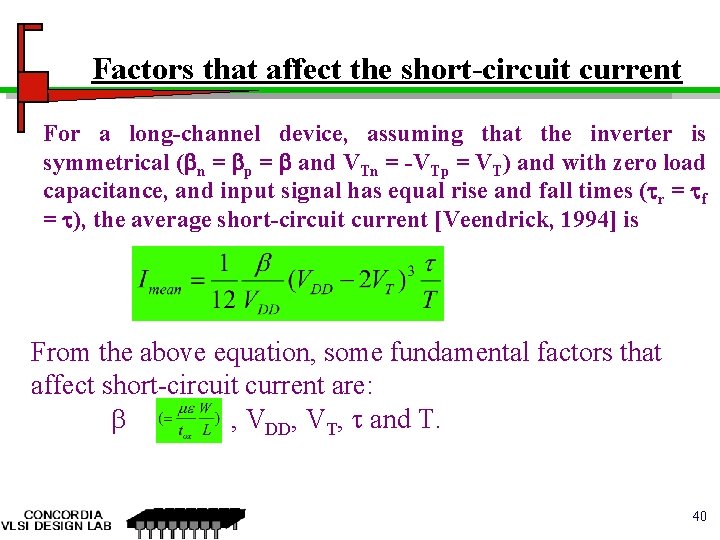

Charging and discharging currents n Discharging Inverter Charging Inverter 39

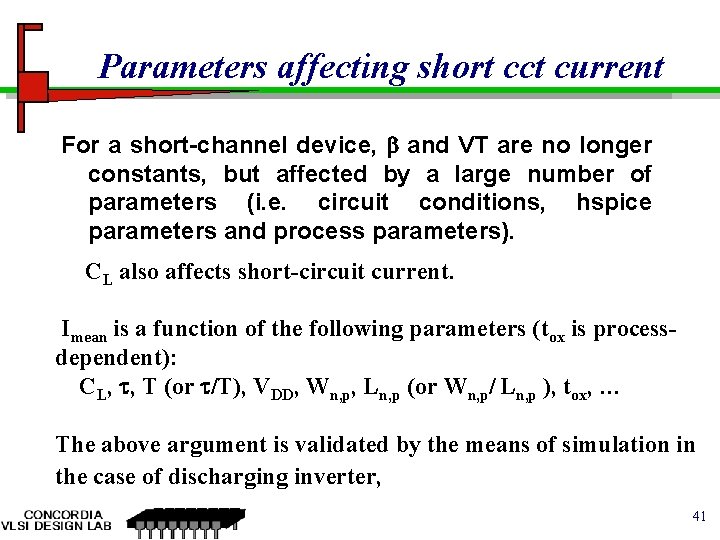

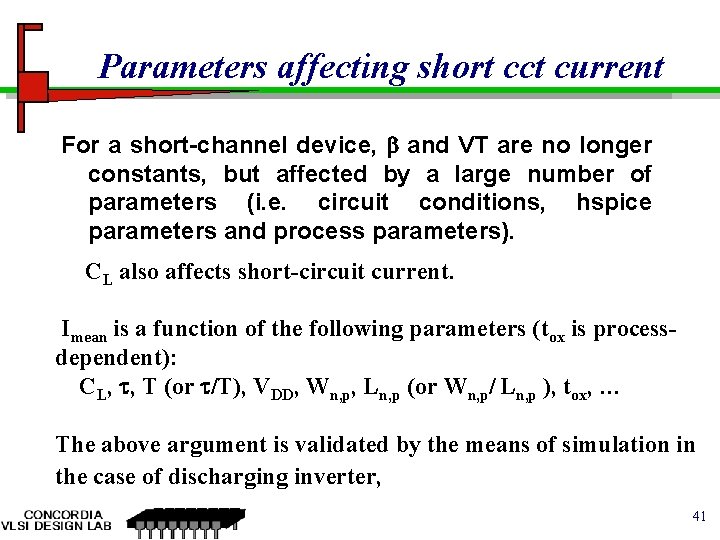

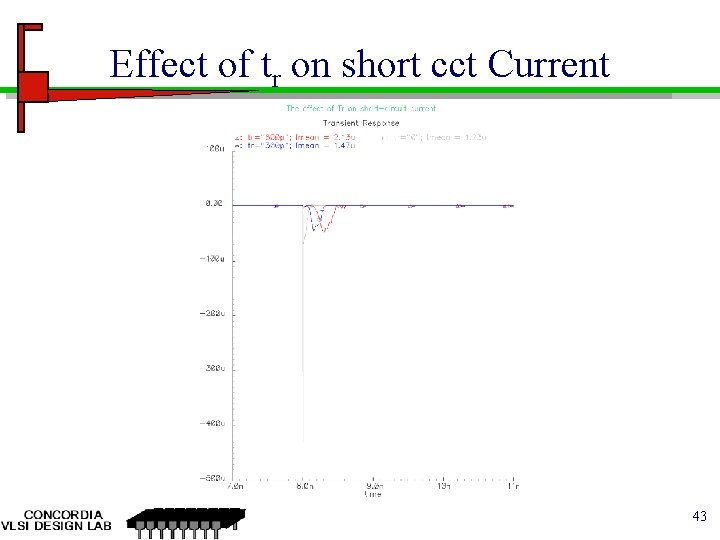

Factors that affect the short-circuit current For a long-channel device, assuming that the inverter is symmetrical ( n = p = and VTn = -VTp = VT) and with zero load capacitance, and input signal has equal rise and fall times ( r = f = ), the average short-circuit current [Veendrick, 1994] is From the above equation, some fundamental factors that affect short-circuit current are: , VDD, VT, and T. 40

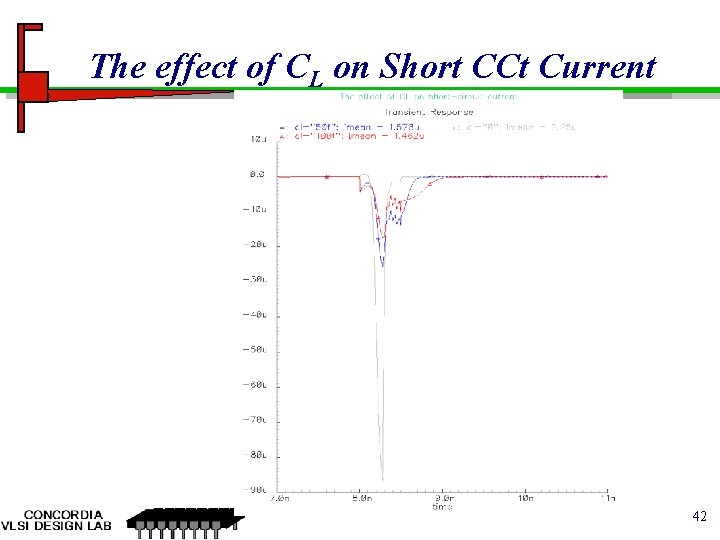

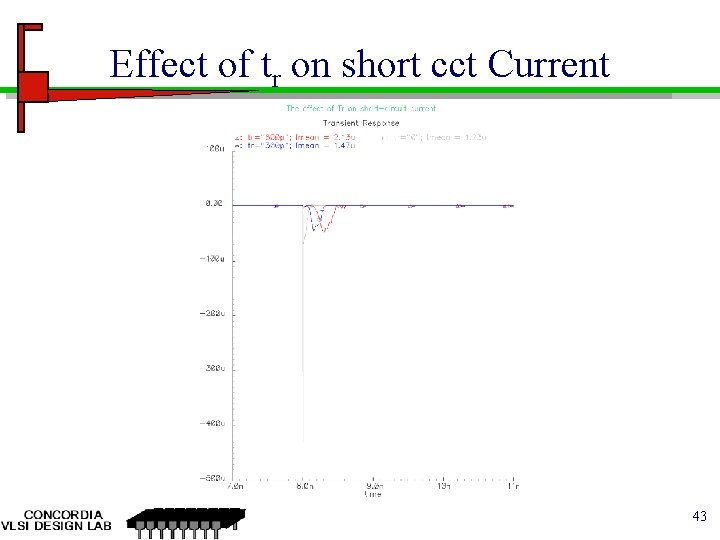

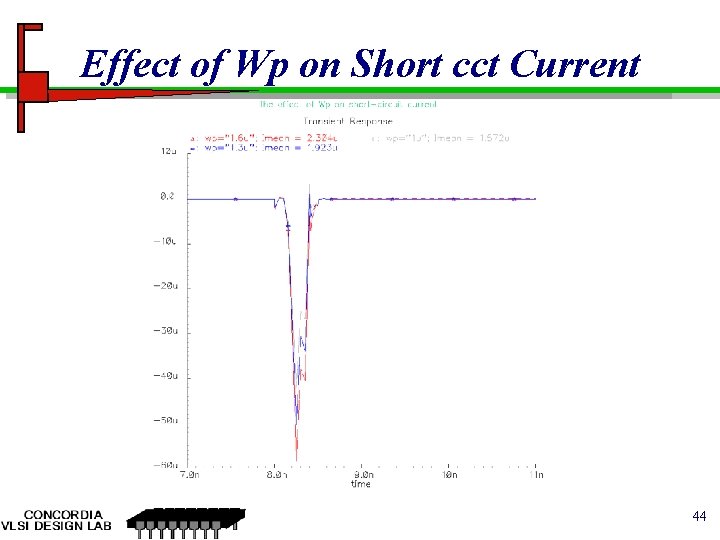

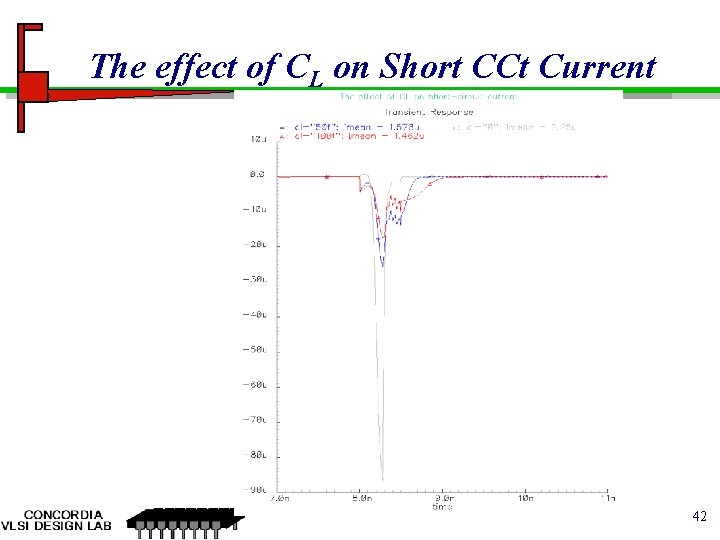

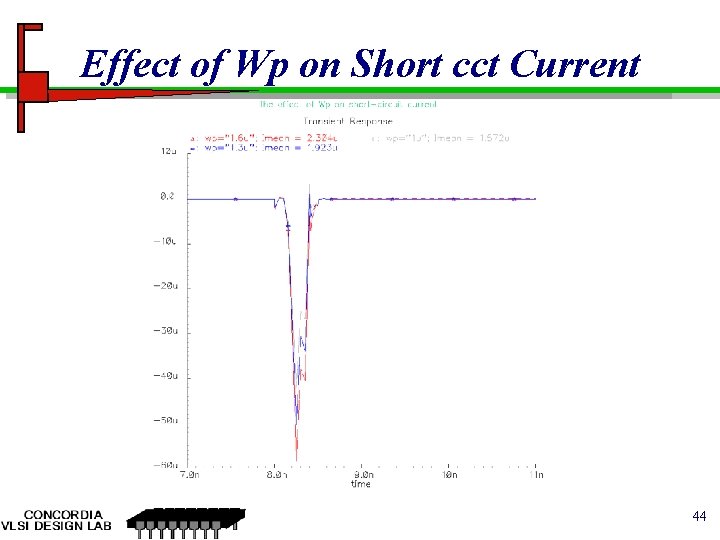

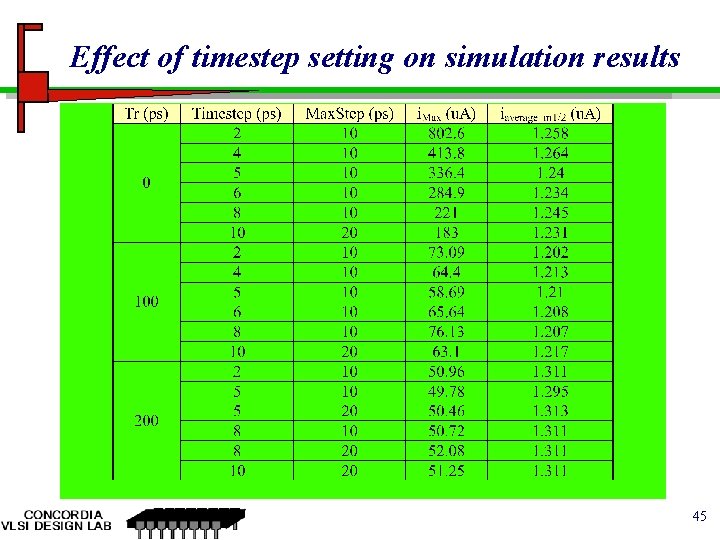

Parameters affecting short cct current For a short-channel device, and VT are no longer constants, but affected by a large number of parameters (i. e. circuit conditions, hspice parameters and process parameters). CL also affects short-circuit current. Imean is a function of the following parameters (tox is processdependent): CL, , T (or /T), VDD, Wn, p, Ln, p (or Wn, p/ Ln, p ), tox, … The above argument is validated by the means of simulation in the case of discharging inverter, 41

The effect of CL on Short CCt Current 42

Effect of tr on short cct Current 43

Effect of Wp on Short cct Current 44

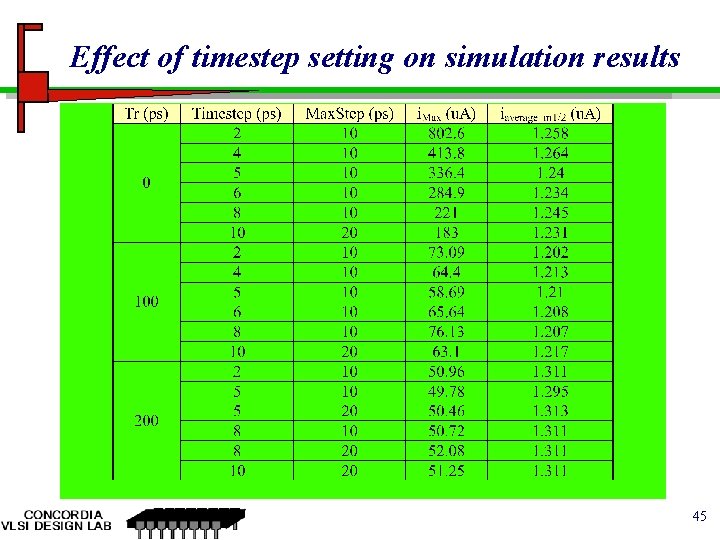

Effect of timestep setting on simulation results 45

Thank you ! 46