MICROPROCESSOR AND ASSEMBLY LANGUAGE LECTURE3 THE 80 X

MICROPROCESSOR AND ASSEMBLY LANGUAGE LECTURE-3 -THE 80 X 86 MICROPROCESSOR MUHAMMAD HAFEEZ DEPARTMENT OF COMPUTER SCIENCE GC UNIVERSITY LAHORE

TODAY’S AGENDA l History of Computer l Intel Microprocessors

HISTORY OF COMPUTERS l Zeroth Generation (1642 -1945) - Mechanical l Blaise Pascal – Four Function Calculator Charles Babbage – Difference Engine and Analytical Engine First Generation (1945 -1955) – Vacuum Tubes l l l ENIAC (Electronic Numerical Integrator and Computer) – 30 Tons, 1800 vacuum tubes, 1400 KW power EDVAC (Electronic Discrete Variable Automatic Computer IBM 701 – IBM first industrial machine

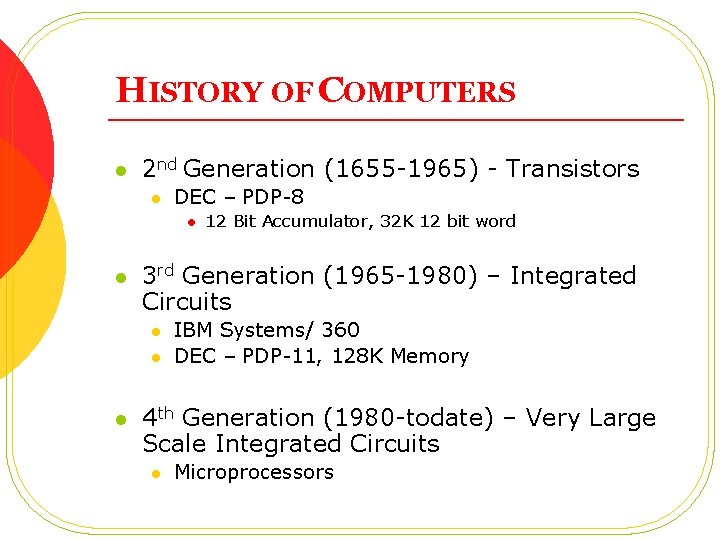

HISTORY OF COMPUTERS l 2 nd Generation (1655 -1965) - Transistors l DEC – PDP-8 l l 3 rd Generation (1965 -1980) – Integrated Circuits l l l 12 Bit Accumulator, 32 K 12 bit word IBM Systems/ 360 DEC – PDP-11, 128 K Memory 4 th Generation (1980 -todate) – Very Large Scale Integrated Circuits l Microprocessors

HISTORY OF COMPUTERS l 2 nd Generation (1655 -1965) - Transistors l DEC – PDP-8 l l 3 rd Generation (1965 -1980) – Integrated Circuits l l l 12 Bit Accumulator, 32 K 12 bit word IBM Systems/ 360 DEC – PDP-11, 128 K Memory 4 th Generation (1980 -todate) – Very Large Scale Integrated Circuits l Microprocessors

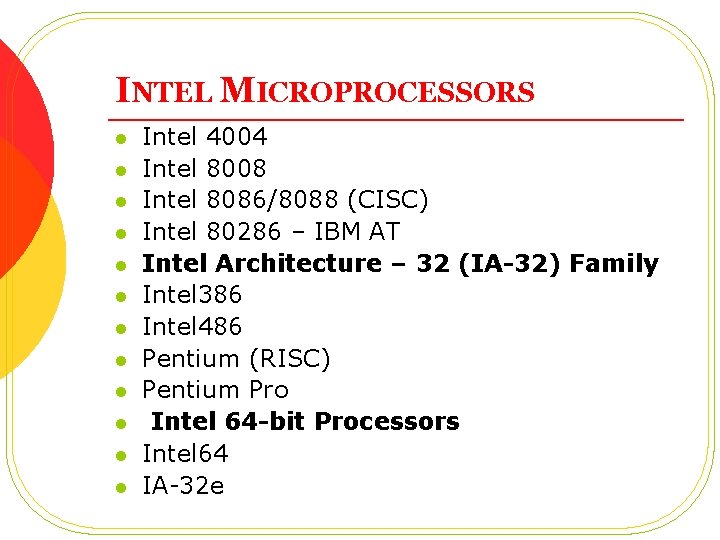

INTEL MICROPROCESSORS l l l Intel 4004 Intel 8008 Intel 8086/8088 (CISC) Intel 80286 – IBM AT Intel Architecture – 32 (IA-32) Family Intel 386 Intel 486 Pentium (RISC) Pentium Pro Intel 64 -bit Processors Intel 64 IA-32 e

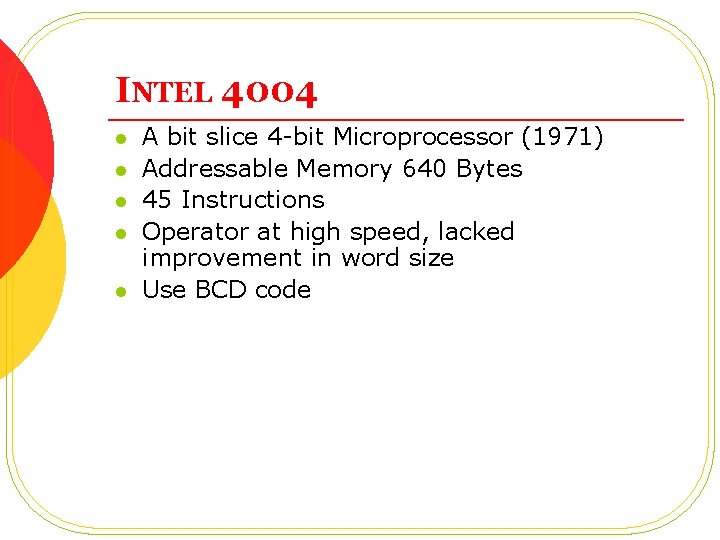

INTEL 4004 l l l A bit slice 4 -bit Microprocessor (1971) Addressable Memory 640 Bytes 45 Instructions Operator at high speed, lacked improvement in word size Use BCD code

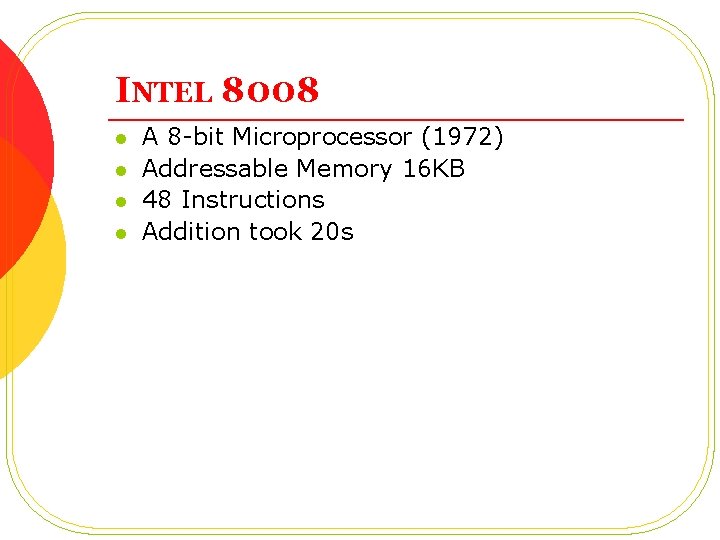

INTEL 8008 l l A 8 -bit Microprocessor (1972) Addressable Memory 16 KB 48 Instructions Addition took 20 s

INTEL 8080 l l l A 8 -bit Microprocessor (1974) 8 -bit data bus, 16 -bit address bus Addressable Memory 64 K CP/M Operating System Addition took 2. 0 s

INTEL 8086/8088 l l l l l IBM-PC Used 8088 (1978) 8088 open system (h/w, s/w documents open) 2. 5 millions of instructions per second 1 MB addressable RAM 16 -bit registers 4 - or 6 -byte instruction cache 16 -bit data bus (8 -bit for 8088) contained 246 instructions (20, 000 variations) separate floating-point unit (8087) Our Target Processor

INTEL 80286 l l l IBM-AT 16 Bit Data Bus 24 Bit Address bus Protected Memory Feature 8. 0 MHz, 4. 0 MIPS, several time faster than 8086

INTEL ARCHITECTURE-32 -IA-32 FAMILY l l l l Intel 386 4 GB addressable RAM, 32 -bit registers, memory management unit paging (virtual memory) Intel 486 50 MHz, 50 MIPS instruction pipelining 8 -16 KB cache Pentium (RISC) 60 MHz, 110 MIPS contains two independent internal integer processors called superscaler technology executes two instructions not dependent on each other, simultaneously per clocking period 32 -bit address bus, 64 -bit internal data path

INTEL PENTIUM PRO l l l l l A recent entry, formerly named the P 6. 21 million transistors, integer units, floating-point unit, Clock frequency 150 and 166 MHz Internal 16 K level-one (L 1) cache. 8 K data, 8 K for instructions 256 K level-two (L 2) cache Three execution engines, to execute up to three instructions at a time. Address 4 G-byte or a 64 G-byte memory system. 36 -bit address bus if configured for a 64 G memory system

INTEL 64 BIT PROCESSORS l l l Intel 64 64 -bit linear address space Intel: Pentium Extreme, Xeon, Celeron D, Pentium D, Core 2 and Core i 7 IA-32 e Mode Compatibility mode for legacy 16 - and 32 bit applications 64 -bit Mode uses 64 -bit addresses and operands

CISC AND RISC l l l CISC complex instruction set large instruction set high-level operations requires microcode interpreter examples: Intel 80 x 86 family RISC reduced instruction set simple, atomic instructions small instruction set directly executed by hardware examples: ARM (Advanced RISC Machines) DEC Alpha (now Compaq)

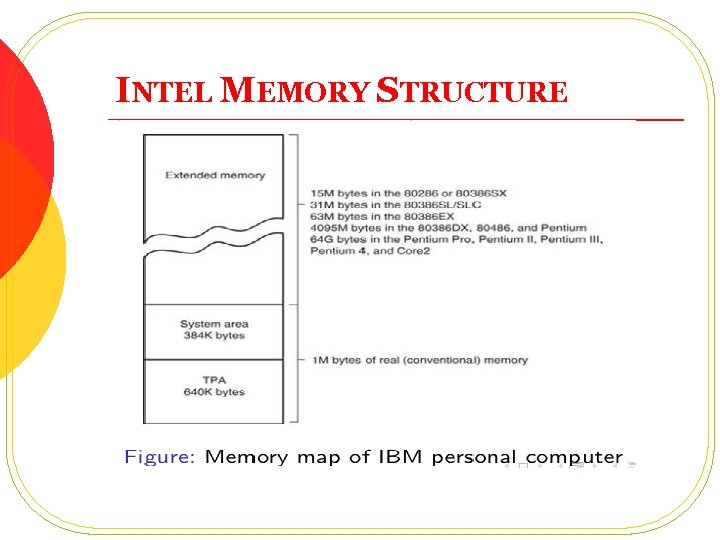

INTEL MEMORY STRUCTURE l l l TPA (Transient Program Area) System Area XMS (Extended Memory System)

INTEL MEMORY STRUCTURE

INTEL MEMORY STRUCTURE l l l First 1 M byte of memory often called the real or conventional memory system. Intel microprocessors designed to function in this area using real mode operation 80286 through the Core 2 contain the TPA (640 K bytes) and system area (384 K bytes). Extended memory up to 15 M bytes in the 80286 80386 I 4095 M bytes in 80486 80386 DX, Pentium microprocessors. The Pentium Pro through Core 2 computer systems have up to 1 M less than 4 G or 1 M less than 64 G of extended memory.

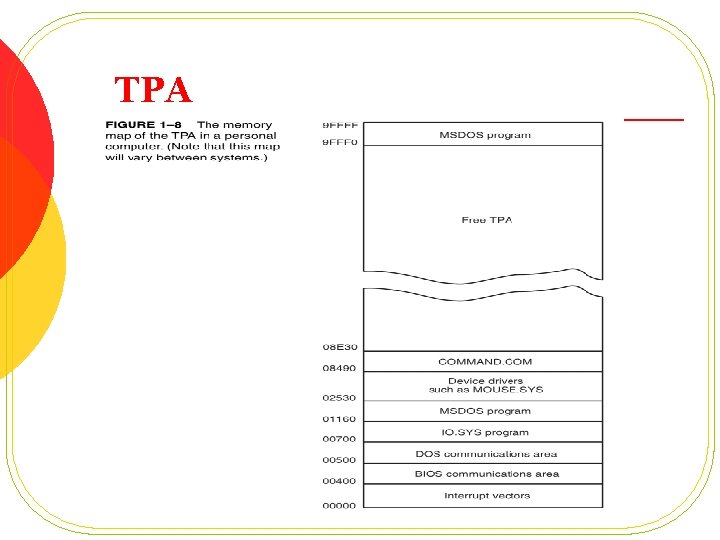

TPA

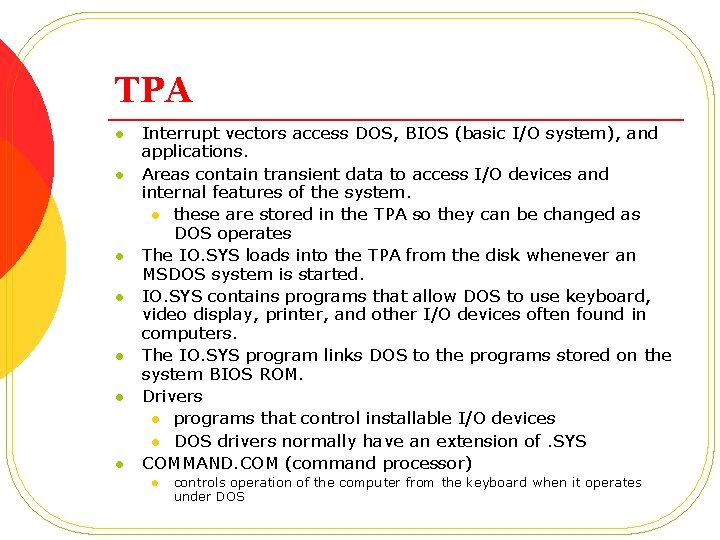

TPA l l Holds DOS and other programs that control the system TPA is a DOS concept and not applicable to windows Also stored currently active/inactive DOS application programs Size = 640 K

TPA l l l l Interrupt vectors access DOS, BIOS (basic I/O system), and applications. Areas contain transient data to access I/O devices and internal features of the system. l these are stored in the TPA so they can be changed as DOS operates The IO. SYS loads into the TPA from the disk whenever an MSDOS system is started. IO. SYS contains programs that allow DOS to use keyboard, video display, printer, and other I/O devices often found in computers. The IO. SYS program links DOS to the programs stored on the system BIOS ROM. Drivers l programs that control installable I/O devices l DOS drivers normally have an extension of. SYS COMMAND. COM (command processor) l controls operation of the computer from the keyboard when it operates under DOS

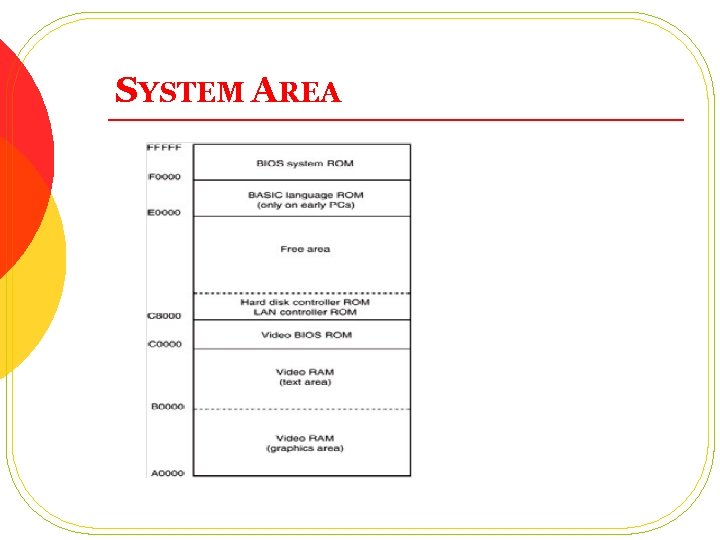

SYSTEM AREA

SYSTEM AREA l l l Smaller than the TPA; just as important. The system area contains programs on read -only (ROM) or flash memory, and areas of read/write (RAM) memory for data storage. First area of system space contains video display RAM and video control programs on ROM or flash memory. l l l area starts at location A 0000 H and extends to C 7 FFFH size/amount of memory depends on type of video display adapter attached

WINDOWS MEMORY l Difference between DOS l l l Size/ Location TPA First 2 GB System Area is Last 2 GB

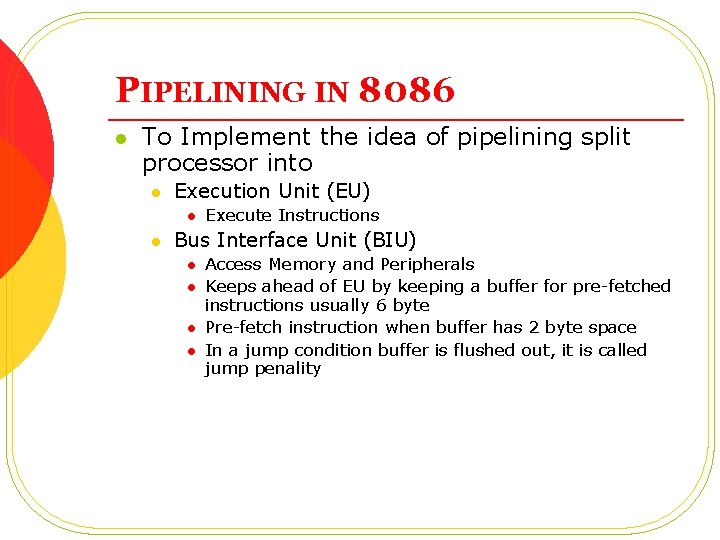

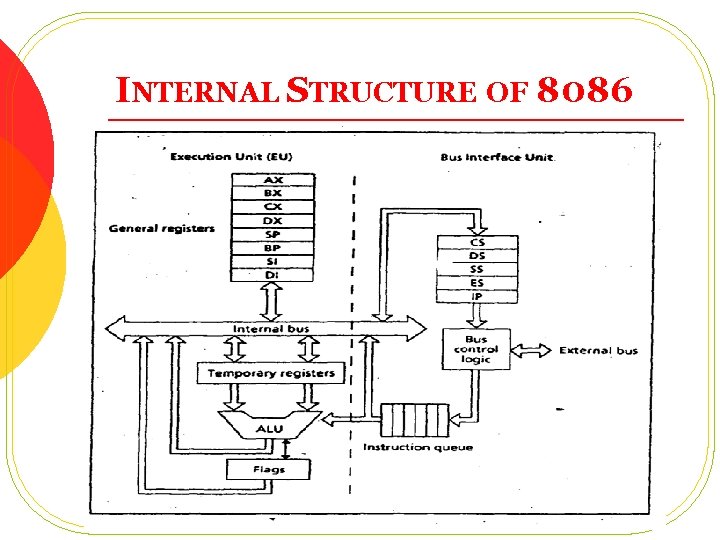

INTERNAL STRUCTURE OF 8086 l l Two ways to make processor fast Increase working frequency l l Demands Technology, No. of IC’s in a Package with Respect to Cost and Technology Change Internal Working l Pipelining l Fetch and Execute at the same time

PIPELINING IN 8086 l To Implement the idea of pipelining split processor into l Execution Unit (EU) l l Execute Instructions Bus Interface Unit (BIU) l l Access Memory and Peripherals Keeps ahead of EU by keeping a buffer for pre-fetched instructions usually 6 byte Pre-fetch instruction when buffer has 2 byte space In a jump condition buffer is flushed out, it is called jump penality

INTERNAL STRUCTURE OF 8086

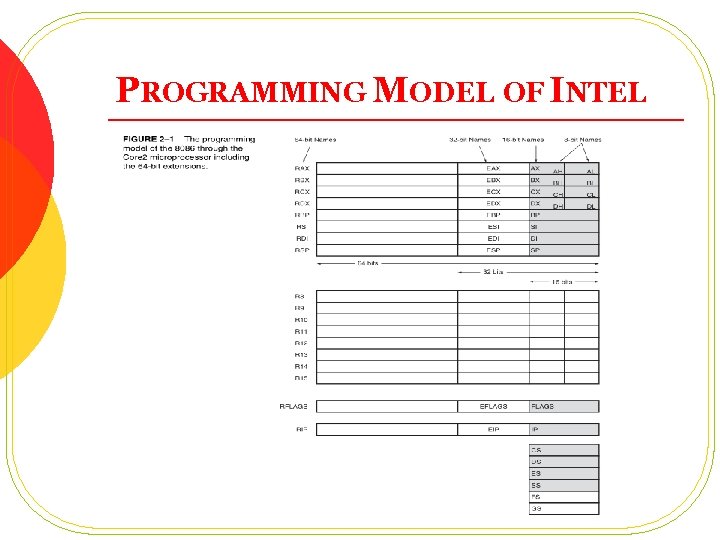

PROGRAMMING MODEL OF INTEL l Registers:

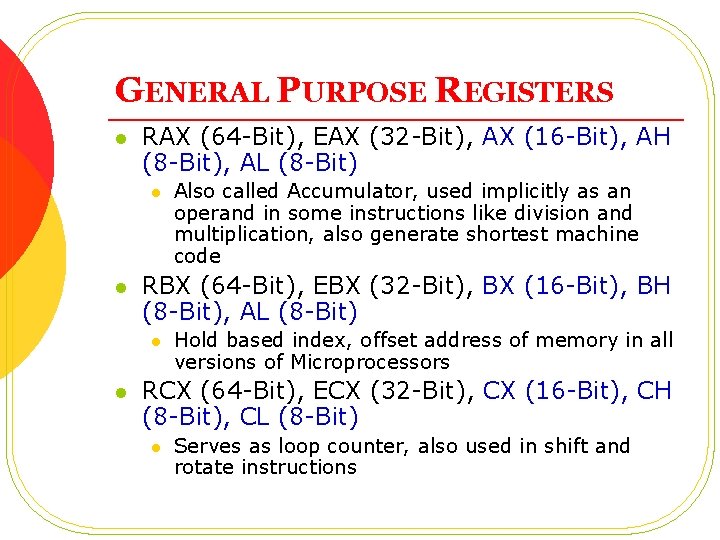

GENERAL PURPOSE REGISTERS l RAX (64 -Bit), EAX (32 -Bit), AX (16 -Bit), AH (8 -Bit), AL (8 -Bit) l l RBX (64 -Bit), EBX (32 -Bit), BX (16 -Bit), BH (8 -Bit), AL (8 -Bit) l l Also called Accumulator, used implicitly as an operand in some instructions like division and multiplication, also generate shortest machine code Hold based index, offset address of memory in all versions of Microprocessors RCX (64 -Bit), ECX (32 -Bit), CX (16 -Bit), CH (8 -Bit), CL (8 -Bit) l Serves as loop counter, also used in shift and rotate instructions

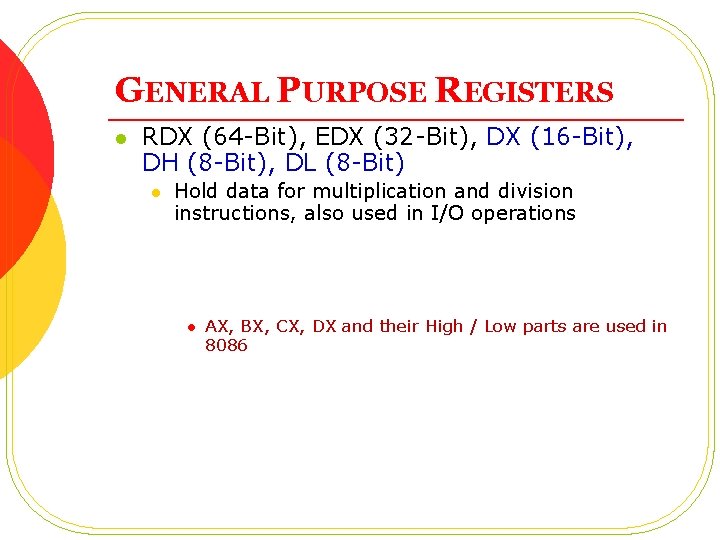

GENERAL PURPOSE REGISTERS l RDX (64 -Bit), EDX (32 -Bit), DX (16 -Bit), DH (8 -Bit), DL (8 -Bit) l Hold data for multiplication and division instructions, also used in I/O operations l AX, BX, CX, DX and their High / Low parts are used in 8086

SEGMENT REGISTERS TO ADDRESS SEGMENTED MEMORY l A Typical assembly language program has four segments in memory l l Code Segment Data Segment Stack Segment Extra Segment

SEGMENTED MEMORY l l 8085 predecessor of 8086 had 64 K addressable memory, 216 memory locations, 16 address lines 8086 has 1 MB addressable memory, 220 memory locations, 20 address lines l l l For compatibility reason memory in 8086 is segmented in 64 K segments, each assigned to Code Segment, Data Segment, Stack Segment and Extra Segment Therefore, a program in 8086 can handle at maximum of 64 K Stack Segment, 64 K Data Segment, 64 K Code Segment and 64 K Extra Segment starts at every 10 H=16 bytes, called paragraph, an address divisible by 16 called a paragraph boundary

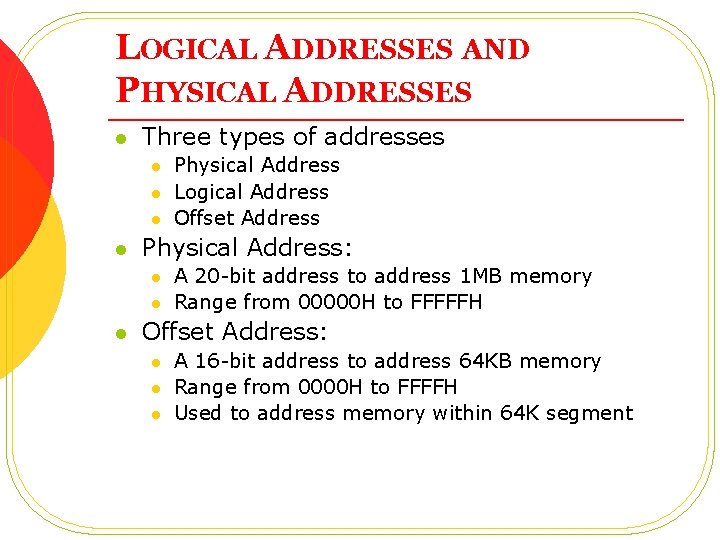

LOGICAL ADDRESSES AND PHYSICAL ADDRESSES l Three types of addresses l l Physical Address: l l l Physical Address Logical Address Offset Address A 20 -bit address to address 1 MB memory Range from 00000 H to FFFFFH Offset Address: l l l A 16 -bit address to address 64 KB memory Range from 0000 H to FFFFH Used to address memory within 64 K segment

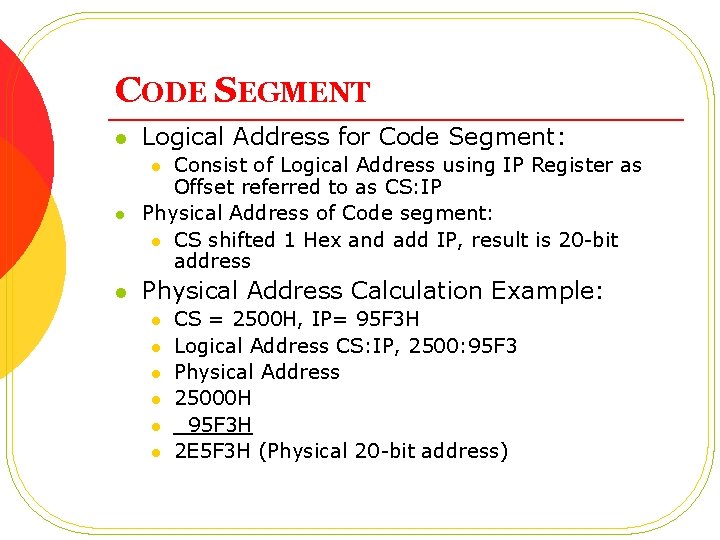

CODE SEGMENT l Logical Address for Code Segment: l Consist of Logical Address using IP Register as Offset referred to as CS: IP Physical Address of Code segment: l CS shifted 1 Hex and add IP, result is 20 -bit address l Physical Address Calculation Example: l l l l CS = 2500 H, IP= 95 F 3 H Logical Address CS: IP, 2500: 95 F 3 Physical Address 25000 H 95 F 3 H 2 E 5 F 3 H (Physical 20 -bit address)

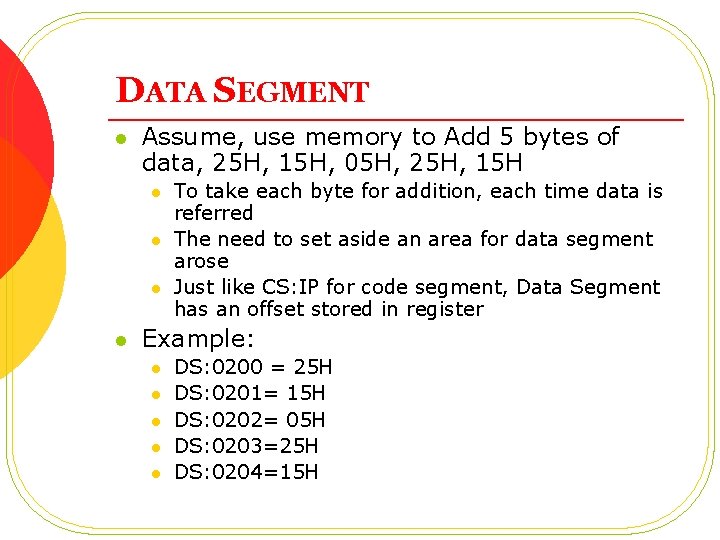

DATA SEGMENT l Assume, use memory to Add 5 bytes of data, 25 H, 15 H, 05 H, 25 H, 15 H l l To take each byte for addition, each time data is referred The need to set aside an area for data segment arose Just like CS: IP for code segment, Data Segment has an offset stored in register Example: l l l DS: 0200 = 25 H DS: 0201= 15 H DS: 0202= 05 H DS: 0203=25 H DS: 0204=15 H

DATA SEGMENT l It is more convenient to store offset address of data segment in register l In 8086 BX, SI and DI are used as offset register for data segment

STACK SEGMENT l Used to hold the values stored in Stack during program execution

EXTRA SEGMENT l This segment is used if the program spans beyond 64 K for Code or Data Segment, i. e. we have to use two segments for a program

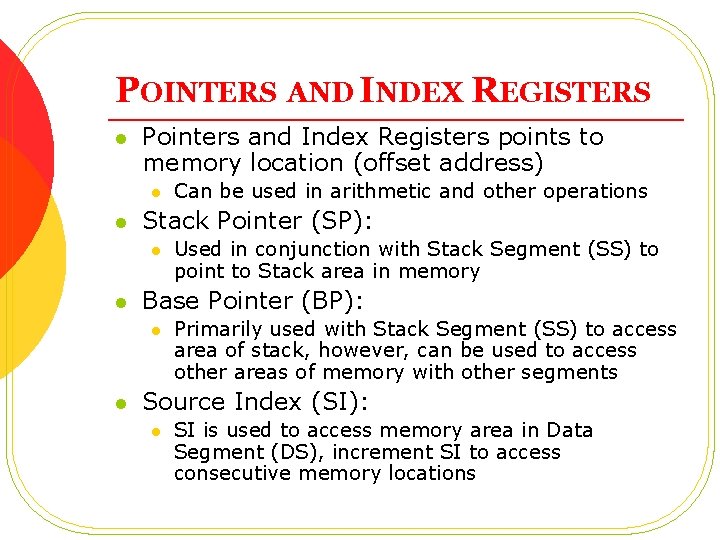

POINTERS AND INDEX REGISTERS l Pointers and Index Registers points to memory location (offset address) l l Stack Pointer (SP): l l Used in conjunction with Stack Segment (SS) to point to Stack area in memory Base Pointer (BP): l l Can be used in arithmetic and other operations Primarily used with Stack Segment (SS) to access area of stack, however, can be used to access other areas of memory with other segments Source Index (SI): l SI is used to access memory area in Data Segment (DS), increment SI to access consecutive memory locations

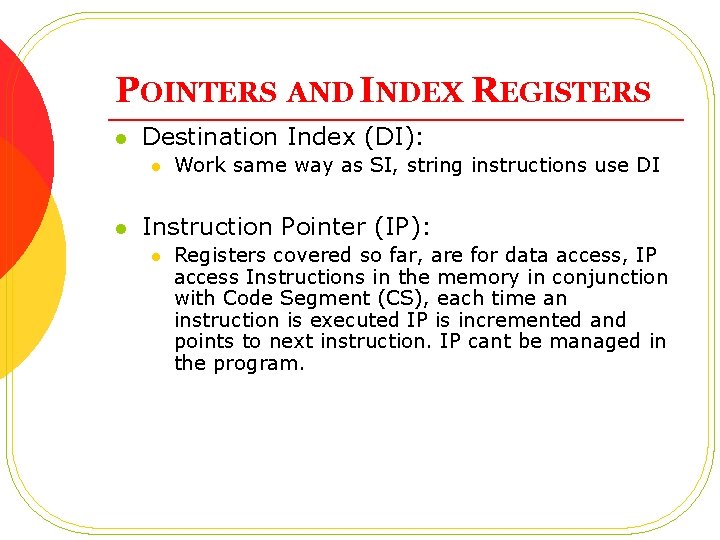

POINTERS AND INDEX REGISTERS l Destination Index (DI): l l Work same way as SI, string instructions use DI Instruction Pointer (IP): l Registers covered so far, are for data access, IP access Instructions in the memory in conjunction with Code Segment (CS), each time an instruction is executed IP is incremented and points to next instruction. IP cant be managed in the program.

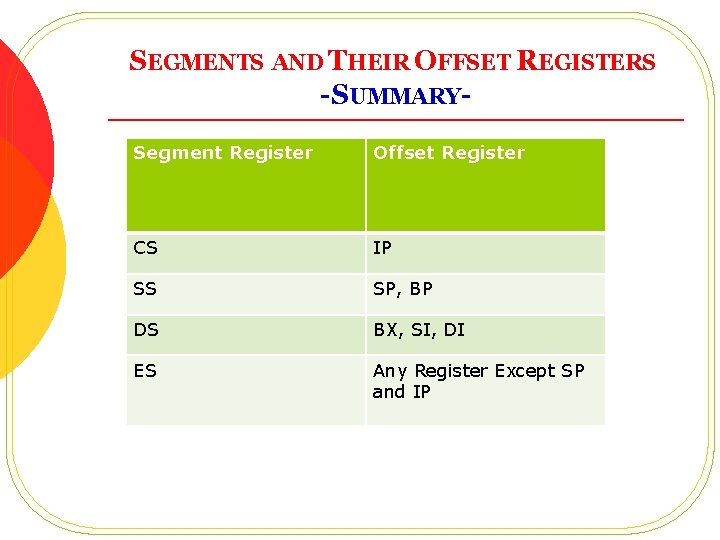

SEGMENTS AND THEIR OFFSET REGISTERS -SUMMARYSegment Register Offset Register CS IP SS SP, BP DS BX, SI, DI ES Any Register Except SP and IP

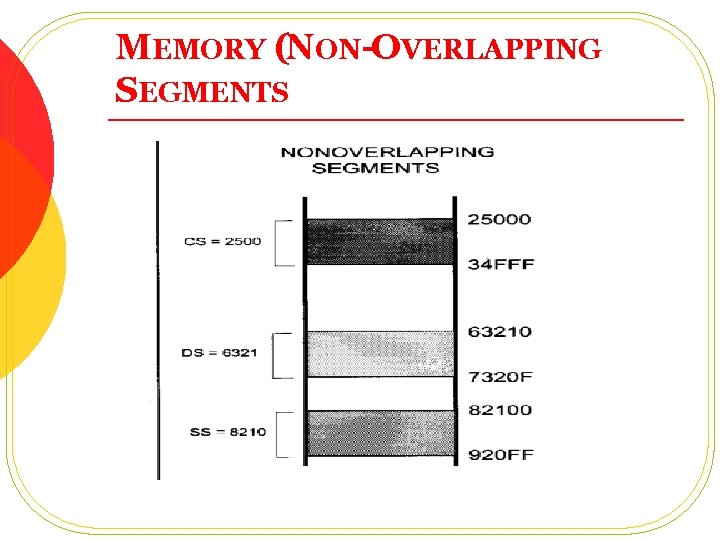

MEMORY (NON-OVERLAPPING SEGMENTS

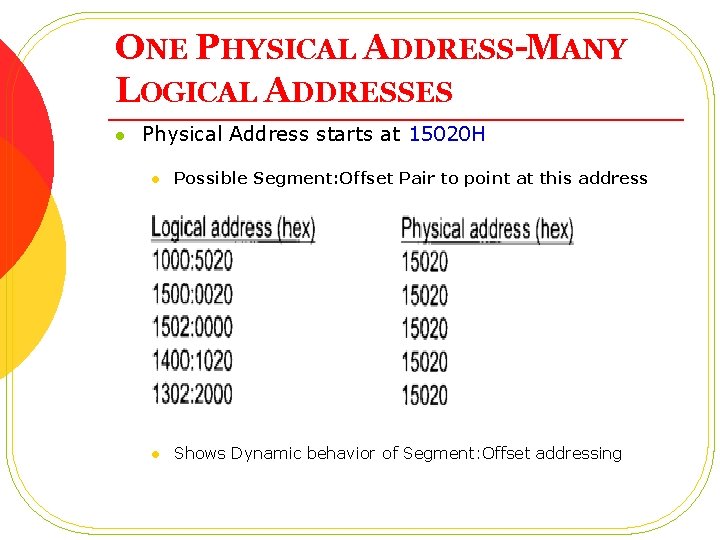

ONE PHYSICAL ADDRESS-MANY LOGICAL ADDRESSES l Physical Address starts at 15020 H l Possible Segment: Offset Pair to point at this address l Shows Dynamic behavior of Segment: Offset addressing

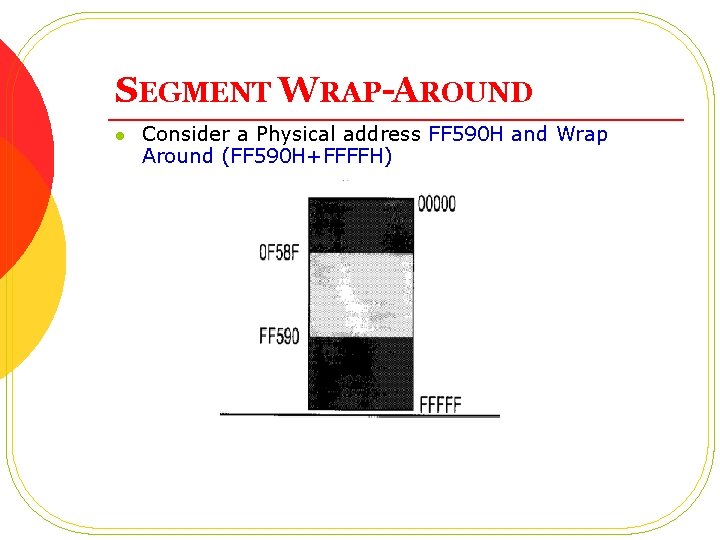

SEGMENT WRAP-AROUND l Consider a Physical address FF 590 H and Wrap Around (FF 590 H+FFFFH)

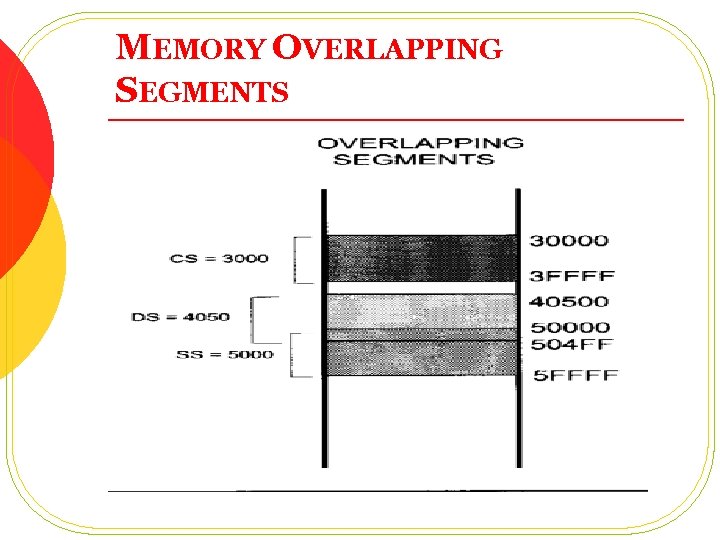

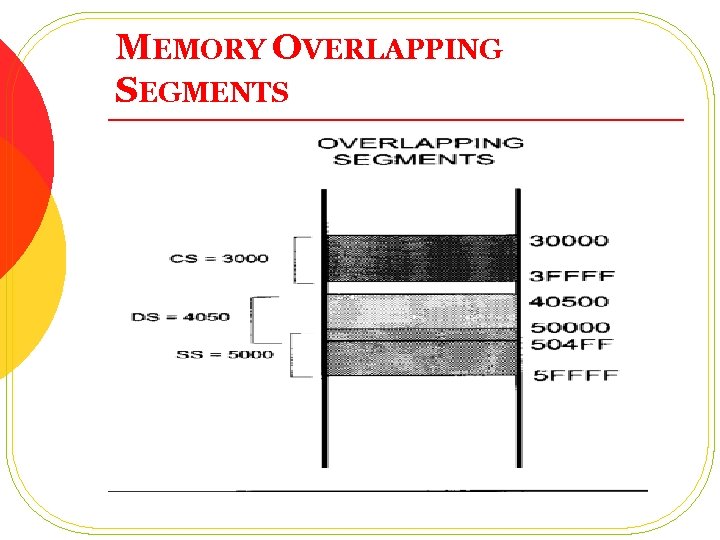

MEMORY OVERLAPPING SEGMENTS

MEMORY OVERLAPPING SEGMENTS

QUESTIONS l ? ? ? ? ? ? ?

- Slides: 47