Microprocessor Assembly Language Logical shift rotate and bit

Microprocessor & Assembly Language Logical, shift, rotate, and bit Instructions

Basic Logic Instructions • Include AND, OR, Exclusive-OR, and NOT. – also TEST, a special form of the AND instruction – NEG, similar to the NOT instruction • Logic operations provide binary bit control in low-level software. –Can manipulate bits, do logical operations, allow bits to be set, cleared, or complemented and do arithmetic operations • Low-level software appears in machine language or assembly language form and often controls the I/O devices in a system. • Logic operations always clear the carry and overflow flags, while the other flags change to reflect the condition of the result – Except not instruction it does not affect any flags

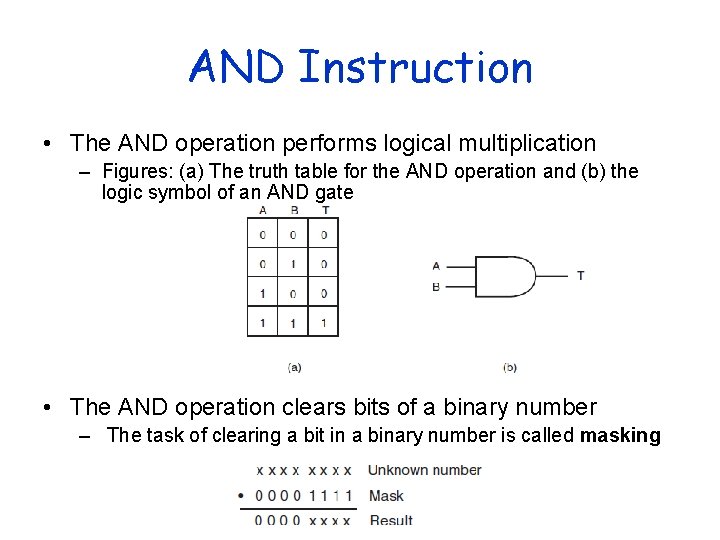

AND Instruction • The AND operation performs logical multiplication – Figures: (a) The truth table for the AND operation and (b) the logic symbol of an AND gate • The AND operation clears bits of a binary number – The task of clearing a bit in a binary number is called masking

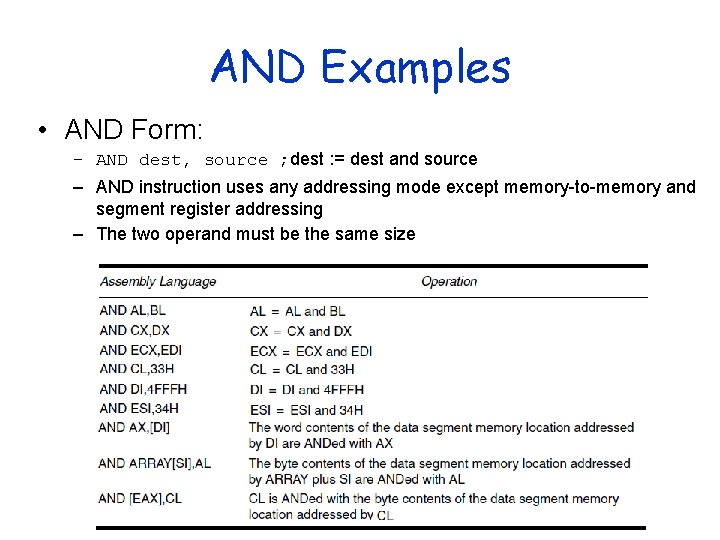

AND Examples • AND Form: – AND dest, source ; dest : = dest and source – AND instruction uses any addressing mode except memory-to-memory and segment register addressing – The two operand must be the same size

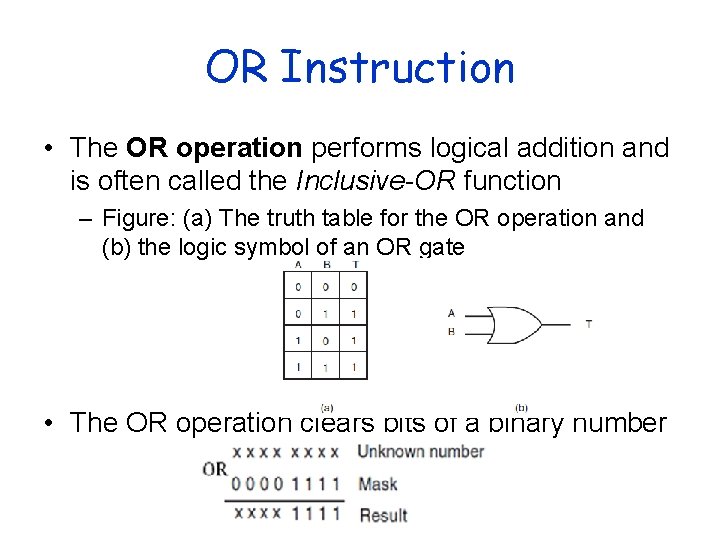

OR Instruction • The OR operation performs logical addition and is often called the Inclusive-OR function – Figure: (a) The truth table for the OR operation and (b) the logic symbol of an OR gate • The OR operation clears bits of a binary number

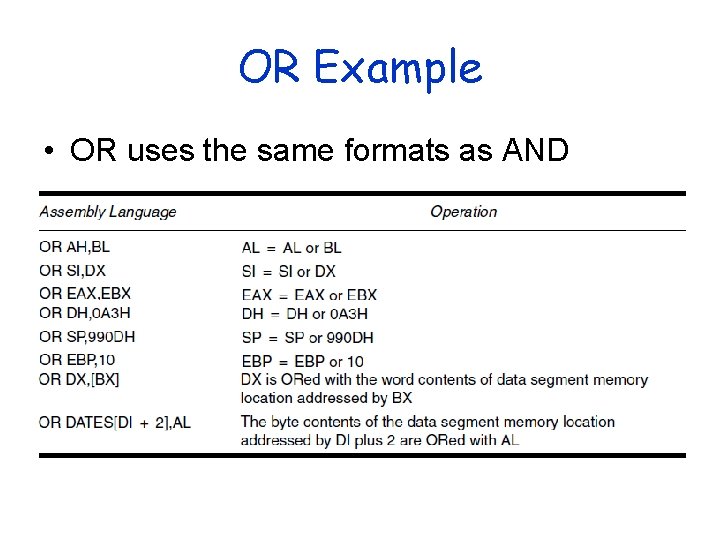

OR Example • OR uses the same formats as AND

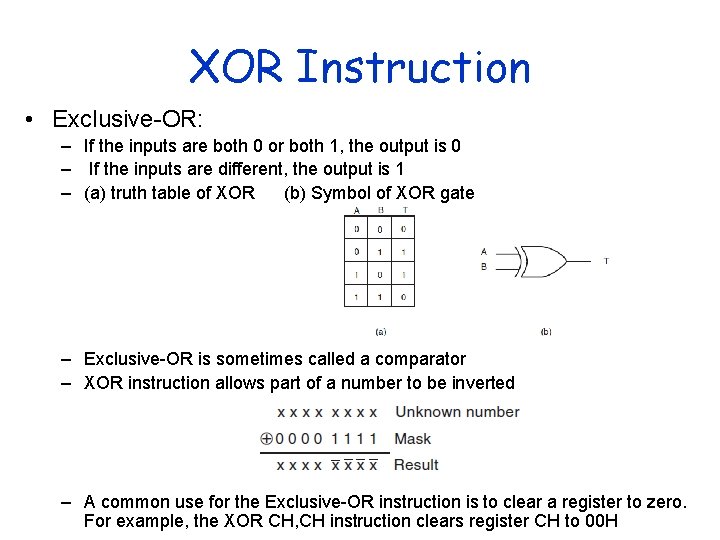

XOR Instruction • Exclusive-OR: – If the inputs are both 0 or both 1, the output is 0 – If the inputs are different, the output is 1 – (a) truth table of XOR (b) Symbol of XOR gate – Exclusive-OR is sometimes called a comparator – XOR instruction allows part of a number to be inverted – A common use for the Exclusive-OR instruction is to clear a register to zero. For example, the XOR CH, CH instruction clears register CH to 00 H

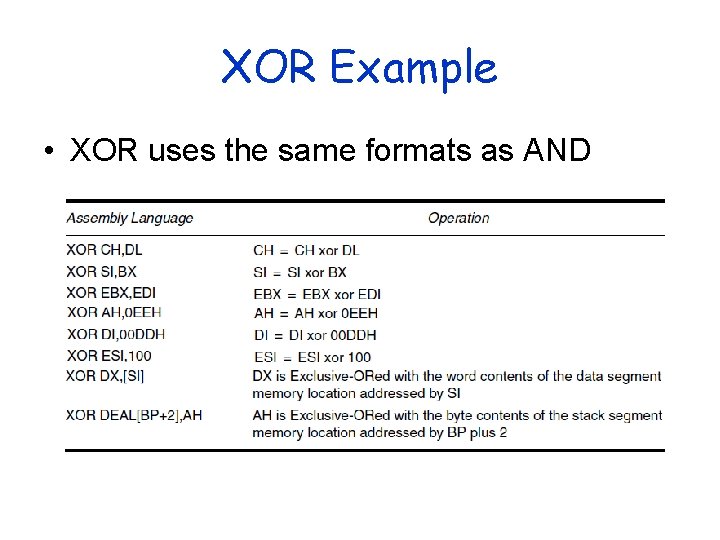

XOR Example • XOR uses the same formats as AND

TEST Instruction • The TEST instruction performs the AND operation BUT – AND instruction changes the destination operand – TEST instruction does not changes the destination operand • TEST only affects the condition of the flag register, which indicates the result of the test • The zero flag (Z) is a logic 1 if the bit under test is a zero, and (indicating a nonzero result) if the bit under test is not zero. • The TEST instruction functions in the same manner as a CMP instruction, The difference is – TEST instruction normally tests a single bit (or occasionally multiple bits) – CMP instruction tests the entire byte, word, or doubleword. • The TEST instruction uses the same addressing modes as the AND instruction • The destination operand is normally tested against immediate data – The value of immediate data is 1 to test the rightmost bit position, 2 to test the next bit, 4 for the next, and so on. – Usually the TEST instruction is followed by either the JZ (jump if zero) or JNZ (jump if not zero) instruction

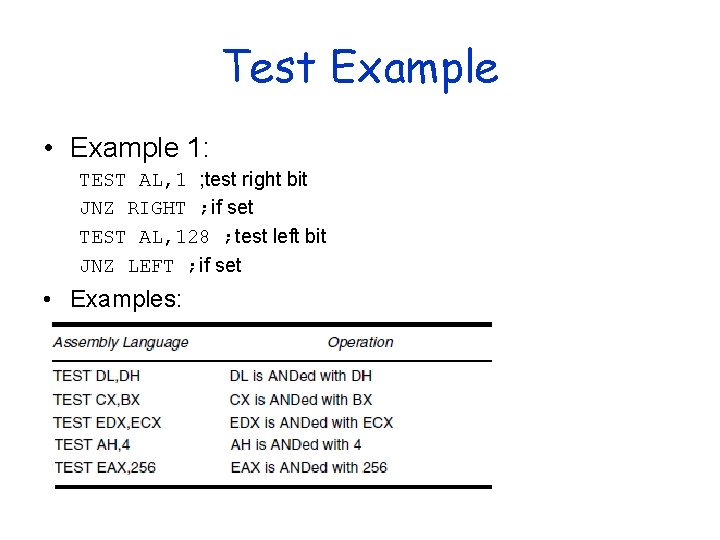

Test Example • Example 1: TEST AL, 1 ; test right bit JNZ RIGHT ; if set TEST AL, 128 ; test left bit JNZ LEFT ; if set • Examples:

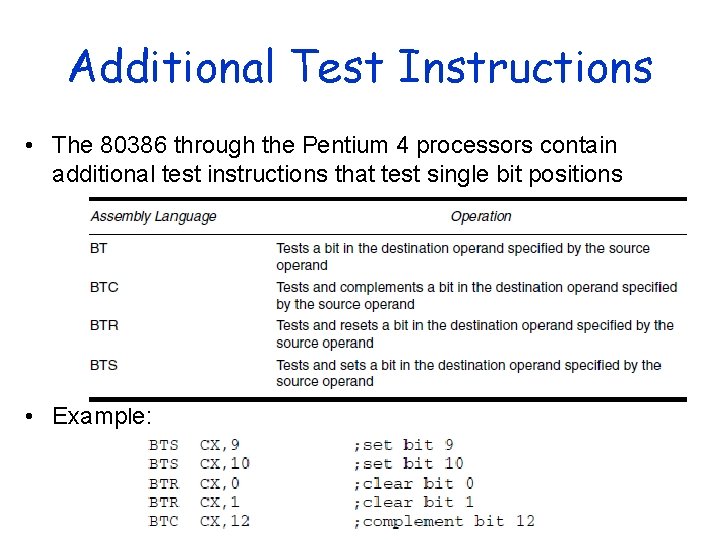

Additional Test Instructions • The 80386 through the Pentium 4 processors contain additional test instructions that test single bit positions • Example:

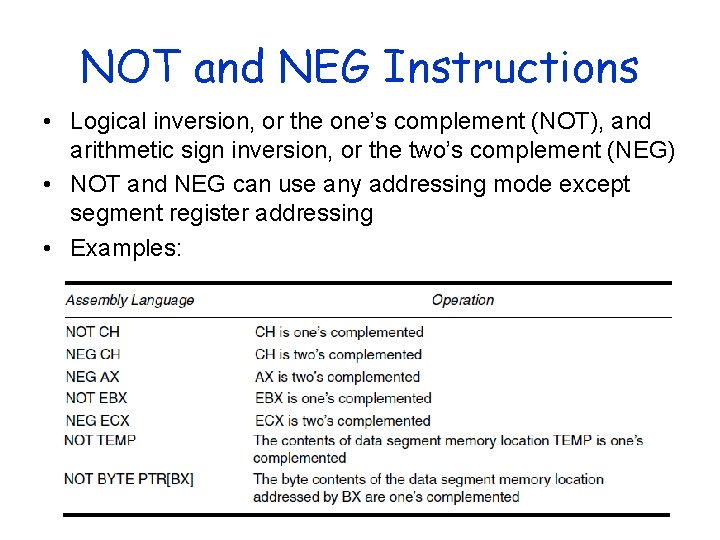

NOT and NEG Instructions • Logical inversion, or the one’s complement (NOT), and arithmetic sign inversion, or the two’s complement (NEG) • NOT and NEG can use any addressing mode except segment register addressing • Examples:

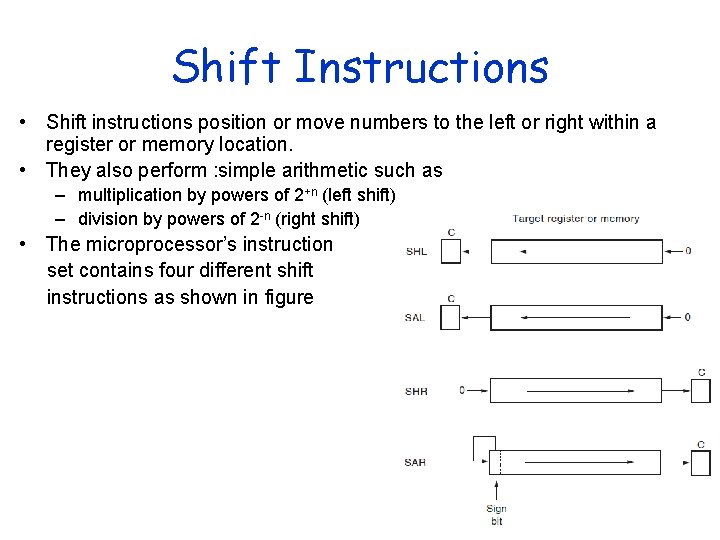

Shift Instructions • Shift instructions position or move numbers to the left or right within a register or memory location. • They also perform : simple arithmetic such as – multiplication by powers of 2+n (left shift) – division by powers of 2 -n (right shift) • The microprocessor’s instruction set contains four different shift instructions as shown in figure

Shift Instructions • Logical shift function with unsigned numbers • Arithmetic shift function with signed numbers • Logical shifts multiply or divide unsigned data; • arithmetic shifts multiply or divide signed data. – a shift left always multiplies by 2 for each bit position shifted – a shift right always divides by 2 for each position – shifting a two places, multiplies or divides by 4 • Shift form: – shl dest, count – shl dest, CL ; cl aontain count number • Destination can be memory location or register; Segment shift not allowed.

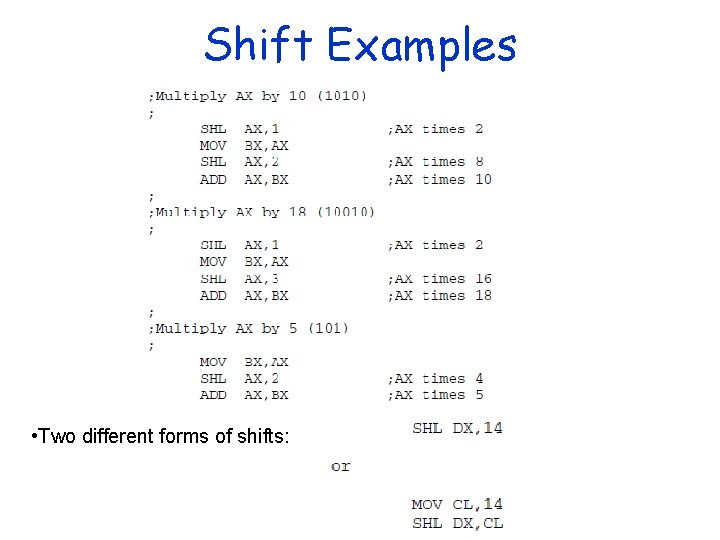

Shift Examples • Two different forms of shifts:

Shift Instructions and Flags Register • If the shift count is zero, the Shift instruction doesn’t affect any flags. • The carry flag contains the last bit shifted out of the operand. • The overflow flag will contain one if the two sign bits were different prior to a single bit shift. The overflow flag is undefined if the shift count is not one. • The zero flag will be one if the shift produces a zero result. • The sign flag will contain the H. O. bit of the result. • The parity flag will contain one if there an even number of one bits in the L. O. byte of the result. • The A flag is always undefined after the Shift instruction

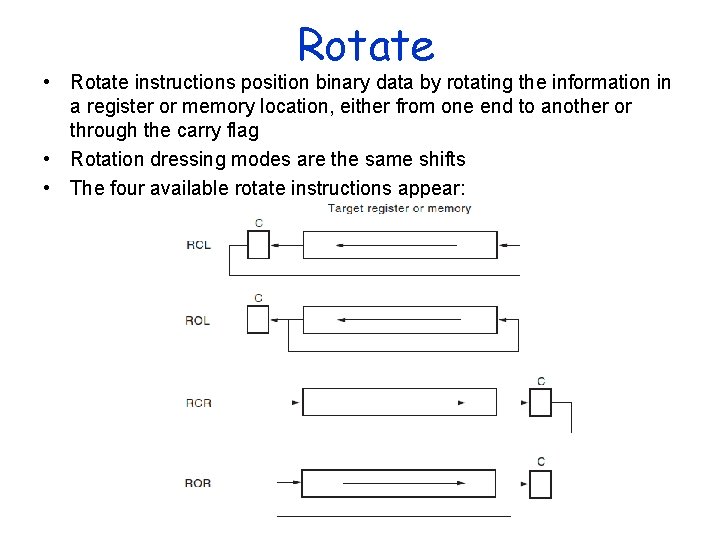

Rotate • Rotate instructions position binary data by rotating the information in a register or memory location, either from one end to another or through the carry flag • Rotation dressing modes are the same shifts • The four available rotate instructions appear:

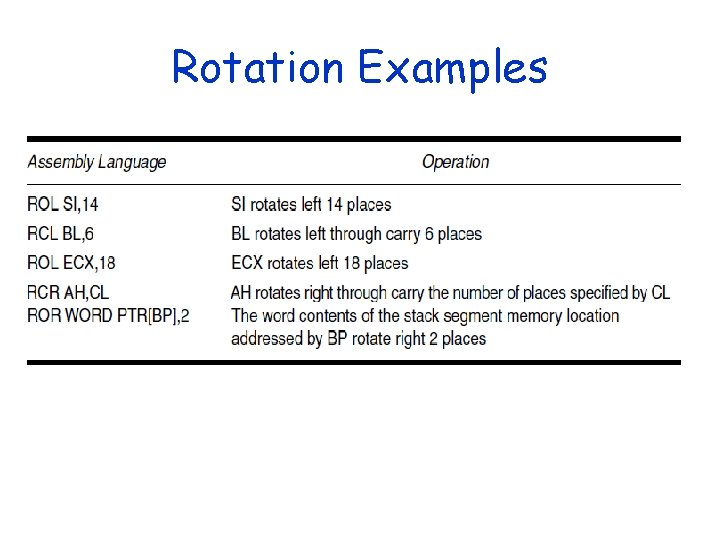

Rotation Examples

Rotate Instructions and Flags Register • The carry flag contains the last bit shifted out of the operand. • If the rotate count is one, then sets the overflow flag if the sign changes. if the count is not one, the value of the overflow flag is undefined. • The rotate instruction does not affect the zero, sign, parity, or auxiliary carry flags.

- Slides: 19