MICROPROCESSOR AND ASSEMBLY LANGUAGE LECTURE5 ADDRESSING MODES MUHAMMAD

MICROPROCESSOR AND ASSEMBLY LANGUAGE LECTURE-5 -ADDRESSING MODES MUHAMMAD HAFEEZ DEPARTMENT OF COMPUTER SCIENCE GC UNIVERSITY LAHORE

TODAY’S AGENDA l l Arrays Addressing Modes

DECLARE AN ARRAY l DUP Operator l l Possible to define data, who elements share a common initial value DATA 1 DB 100 DUP(0) DATA 2 DB 50 DUP(? ) DATA 3 DB 5, 4, 3 DUP(2, 2 DUP(1), 1)

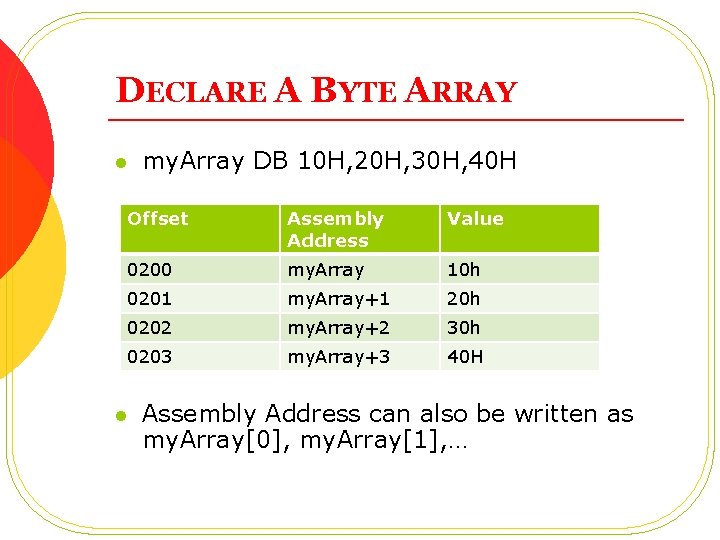

DECLARE A BYTE ARRAY l my. Array DB 10 H, 20 H, 30 H, 40 H Offset Assembly Address Value 0200 my. Array 10 h 0201 my. Array+1 20 h 0202 my. Array+2 30 h 0203 my. Array+3 40 H l Assembly Address can also be written as my. Array[0], my. Array[1], …

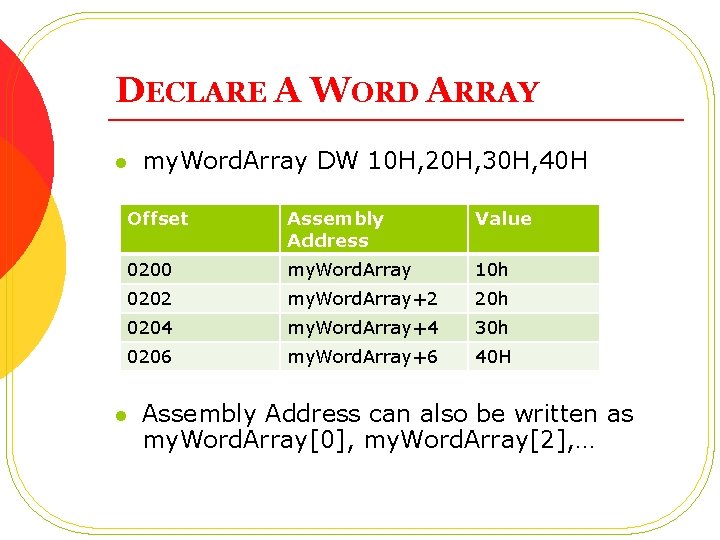

DECLARE A WORD ARRAY l my. Word. Array DW 10 H, 20 H, 30 H, 40 H Offset Assembly Address Value 0200 my. Word. Array 10 h 0202 my. Word. Array+2 20 h 0204 my. Word. Array+4 30 h 0206 my. Word. Array+6 40 H l Assembly Address can also be written as my. Word. Array[0], my. Word. Array[2], …

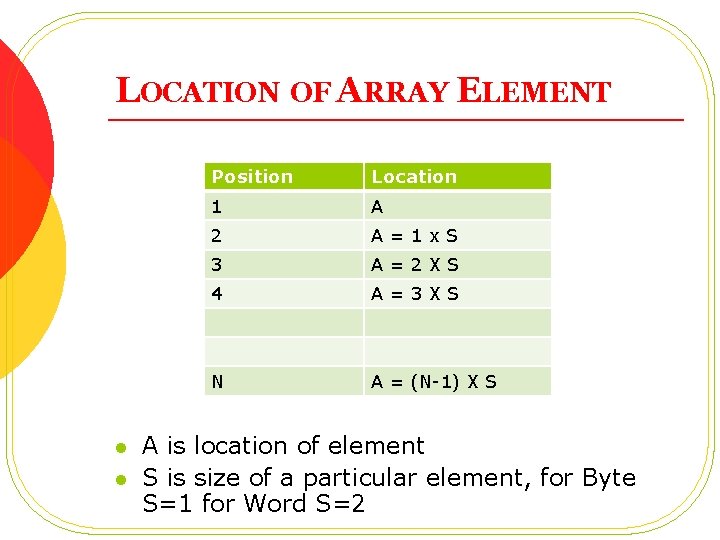

LOCATION OF ARRAY ELEMENT l l Position Location 1 A 2 A = 1 x S 3 A = 2 X S 4 A = 3 X S N A = (N-1) X S A is location of element S is size of a particular element, for Byte S=1 for Word S=2

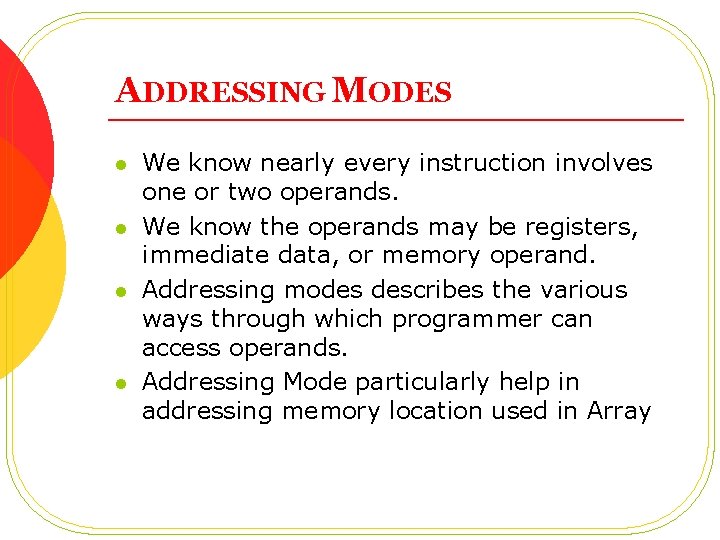

ADDRESSING MODES l l We know nearly every instruction involves one or two operands. We know the operands may be registers, immediate data, or memory operand. Addressing modes describes the various ways through which programmer can access operands. Addressing Mode particularly help in addressing memory location used in Array

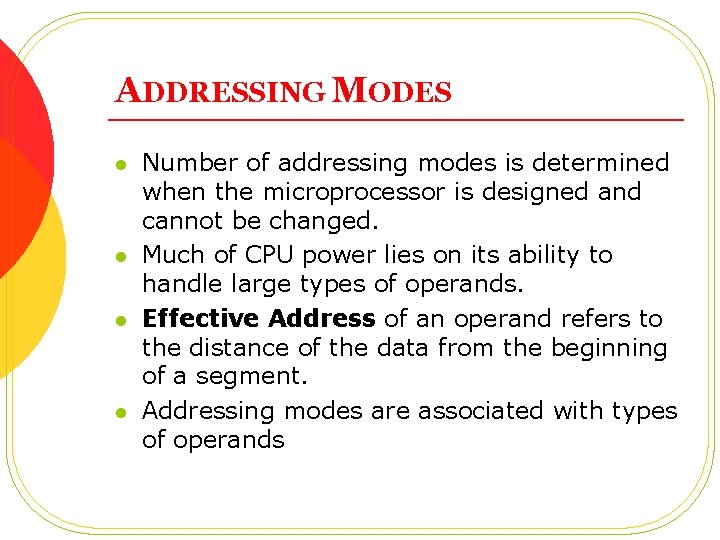

ADDRESSING MODES l l Number of addressing modes is determined when the microprocessor is designed and cannot be changed. Much of CPU power lies on its ability to handle large types of operands. Effective Address of an operand refers to the distance of the data from the beginning of a segment. Addressing modes are associated with types of operands

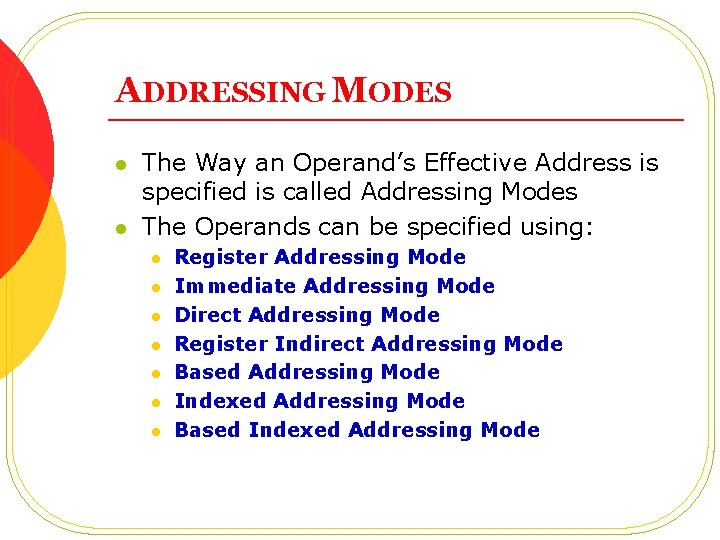

ADDRESSING MODES l l The Way an Operand’s Effective Address is specified is called Addressing Modes The Operands can be specified using: l l l l Register Addressing Mode Immediate Addressing Mode Direct Addressing Mode Register Indirect Addressing Mode Based Addressing Mode Indexed Addressing Mode Based Indexed Addressing Mode

REGISTER ADDRESSING MODE l Transfers a copy of a byte or word from the Source Register to the Destination Register. l Example: MOV AX, BX

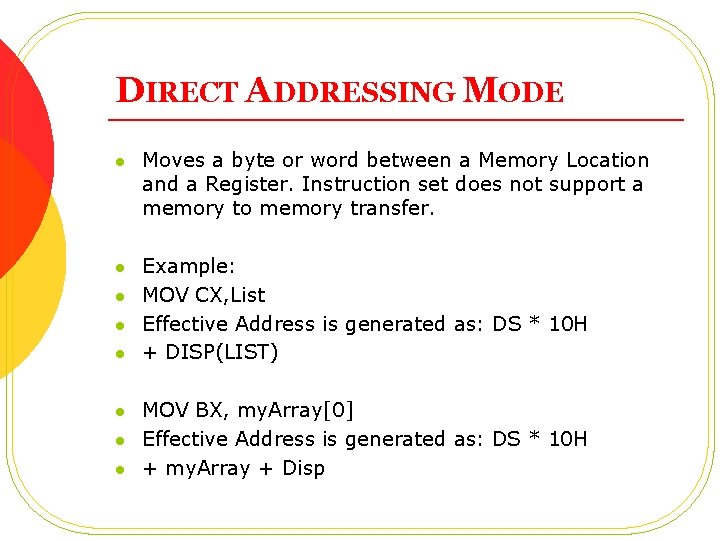

DIRECT ADDRESSING MODE l Moves a byte or word between a Memory Location and a Register. Instruction set does not support a memory to memory transfer. l Example: MOV CX, List Effective Address is generated as: DS * 10 H + DISP(LIST) l l l MOV BX, my. Array[0] Effective Address is generated as: DS * 10 H + my. Array + Disp

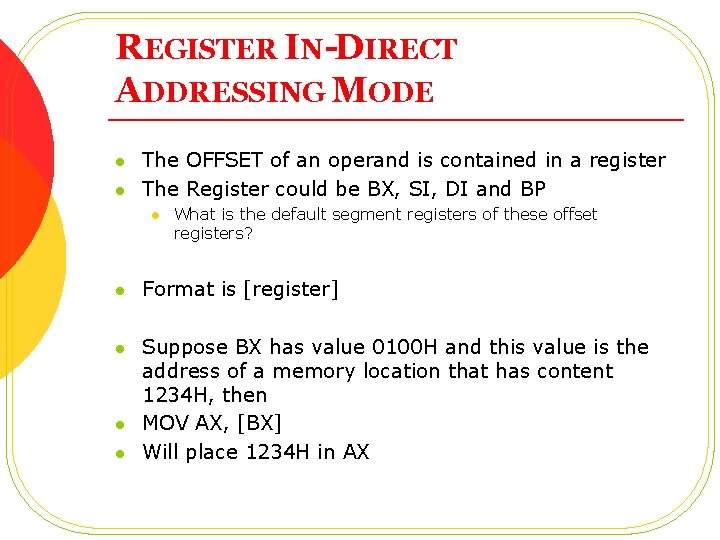

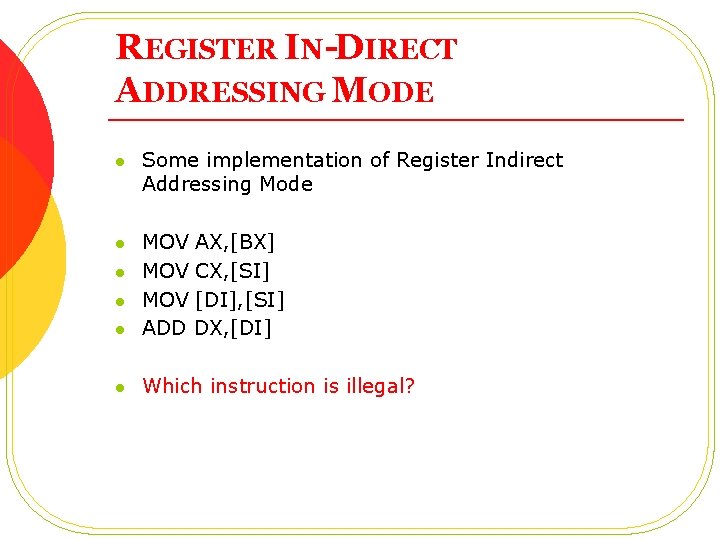

REGISTER IN-DIRECT ADDRESSING MODE l l The OFFSET of an operand is contained in a register The Register could be BX, SI, DI and BP l What is the default segment registers of these offset registers? l Format is [register] l Suppose BX has value 0100 H and this value is the address of a memory location that has content 1234 H, then MOV AX, [BX] Will place 1234 H in AX l l

REGISTER IN-DIRECT ADDRESSING MODE l Some implementation of Register Indirect Addressing Mode l l MOV AX, [BX] MOV CX, [SI] MOV [DI], [SI] ADD DX, [DI] l Which instruction is illegal? l l

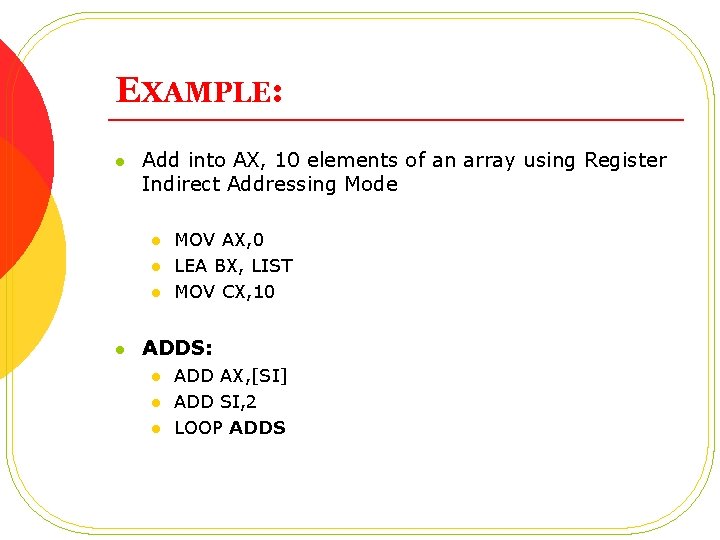

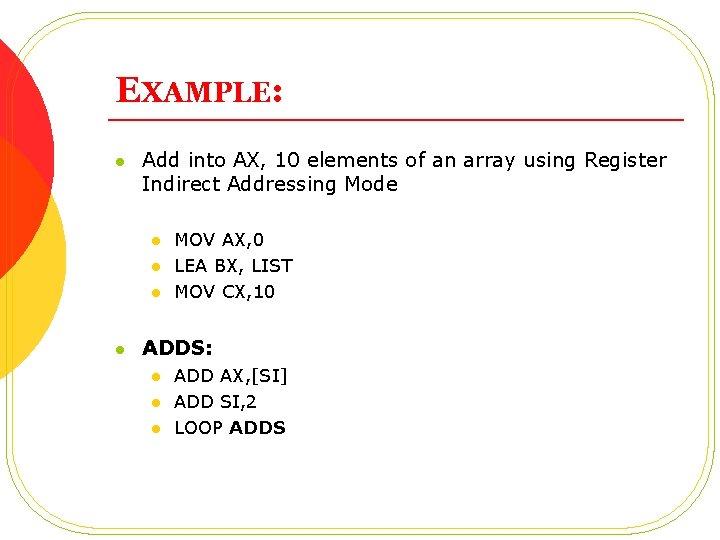

EXAMPLE: l Add into AX, 10 elements of an array using Register Indirect Addressing Mode l l MOV AX, 0 LEA BX, LIST MOV CX, 10 ADDS: l l l ADD AX, [SI] ADD SI, 2 LOOP ADDS

EXAMPLE: l Add into AX, 10 elements of an array using Register Indirect Addressing Mode l l MOV AX, 0 LEA BX, LIST MOV CX, 10 ADDS: l l l ADD AX, [SI] ADD SI, 2 LOOP ADDS

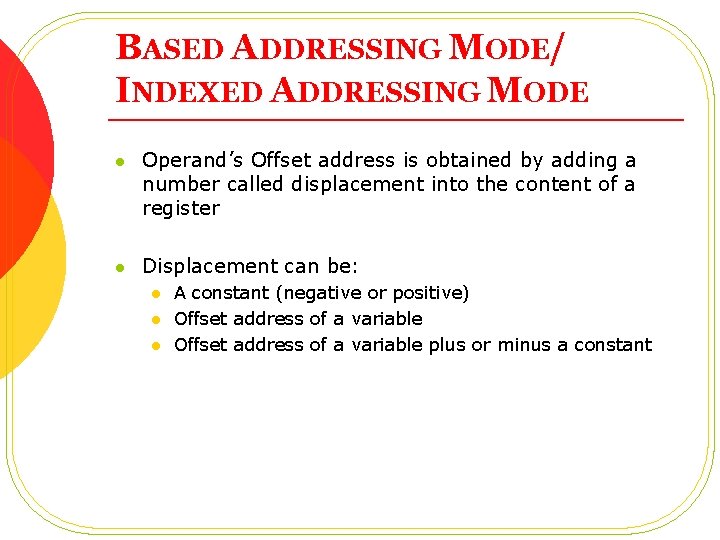

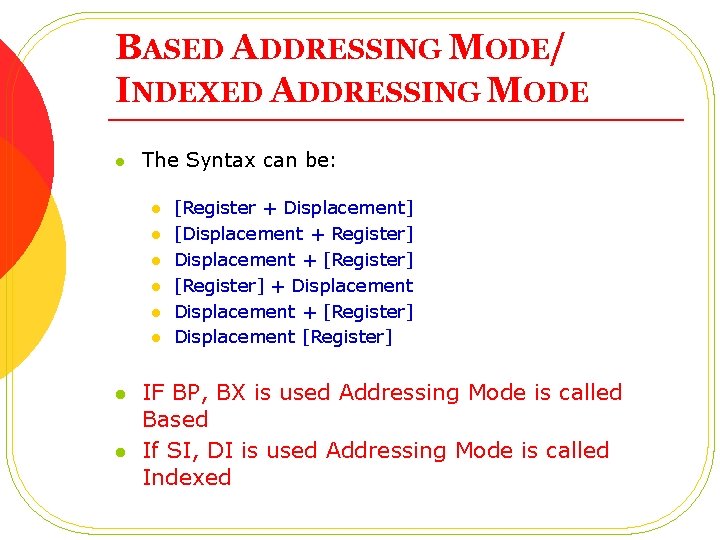

BASED ADDRESSING MODE/ INDEXED ADDRESSING MODE l Operand’s Offset address is obtained by adding a number called displacement into the content of a register l Displacement can be: l l l A constant (negative or positive) Offset address of a variable plus or minus a constant

BASED ADDRESSING MODE/ INDEXED ADDRESSING MODE l The Syntax can be: l l l l [Register + Displacement] [Displacement + Register] Displacement + [Register] + Displacement + [Register] Displacement [Register] IF BP, BX is used Addressing Mode is called Based If SI, DI is used Addressing Mode is called Indexed

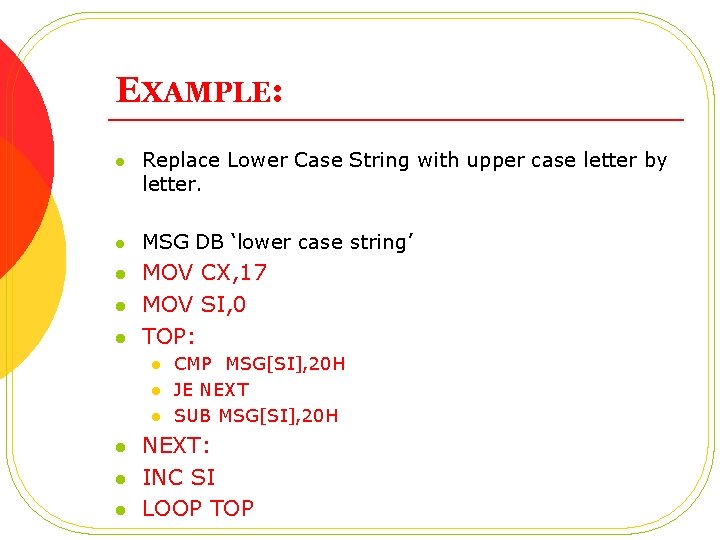

EXAMPLE: l Replace Lower Case String with upper case letter by letter. l MSG DB ‘lower case string’ l l l MOV CX, 17 MOV SI, 0 TOP: l l l CMP MSG[SI], 20 H JE NEXT SUB MSG[SI], 20 H NEXT: INC SI LOOP TOP

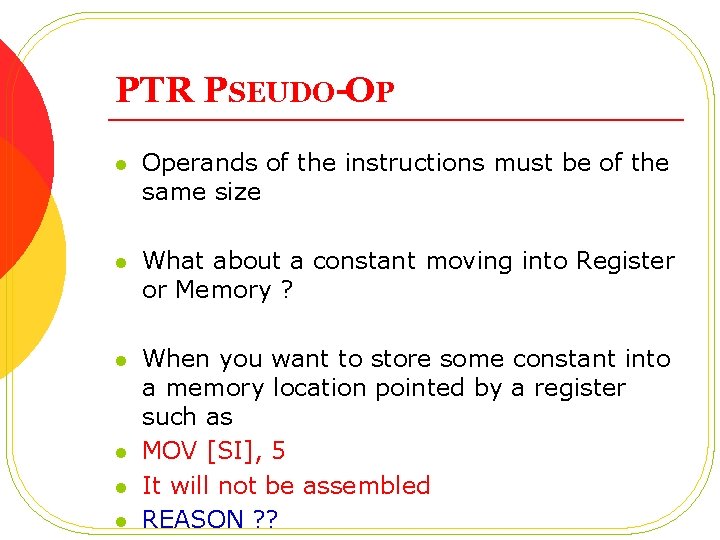

PTR PSEUDO-OP l Operands of the instructions must be of the same size l What about a constant moving into Register or Memory ? l When you want to store some constant into a memory location pointed by a register such as MOV [SI], 5 It will not be assembled REASON ? ? l l l

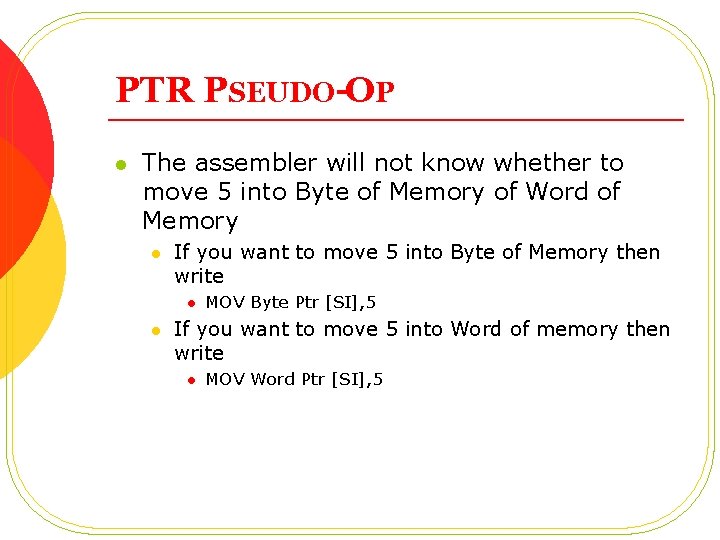

PTR PSEUDO-OP l The assembler will not know whether to move 5 into Byte of Memory of Word of Memory l If you want to move 5 into Byte of Memory then write l l MOV Byte Ptr [SI], 5 If you want to move 5 into Word of memory then write l MOV Word Ptr [SI], 5

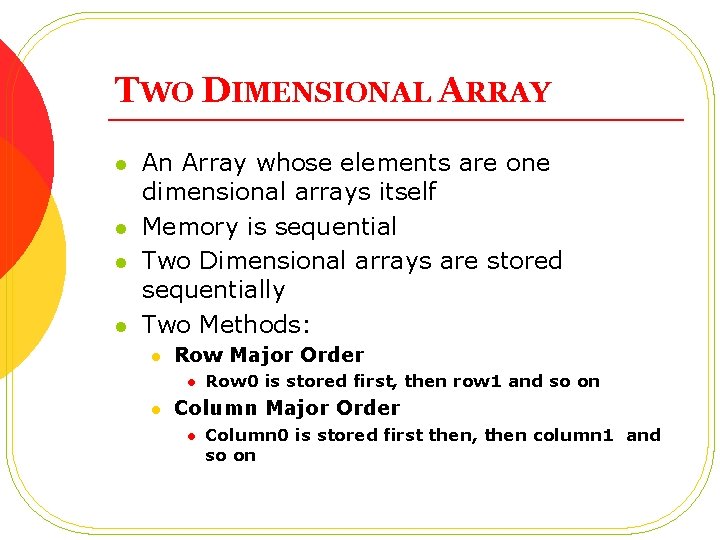

TWO DIMENSIONAL ARRAY l l An Array whose elements are one dimensional arrays itself Memory is sequential Two Dimensional arrays are stored sequentially Two Methods: l Row Major Order l l Row 0 is stored first, then row 1 and so on Column Major Order l Column 0 is stored first then, then column 1 and so on

![ROW MAJOR ORDER /COLUMN MAJOR ORDER l l l Row Major Order: B[0, 0], ROW MAJOR ORDER /COLUMN MAJOR ORDER l l l Row Major Order: B[0, 0],](http://slidetodoc.com/presentation_image/e584503cc3a2afe47da0fc75cfd4ff67/image-22.jpg)

ROW MAJOR ORDER /COLUMN MAJOR ORDER l l l Row Major Order: B[0, 0], B[0, 1], B[0, 2], B[1, 0], B[1, 1], B[1, 2], …. Column Major Order: B[0, 0], B[1, 0], B[2, 0], B[0, 1], B[1, 1], B[2, 1], …. Most High Level Languages store data in Row Major Order

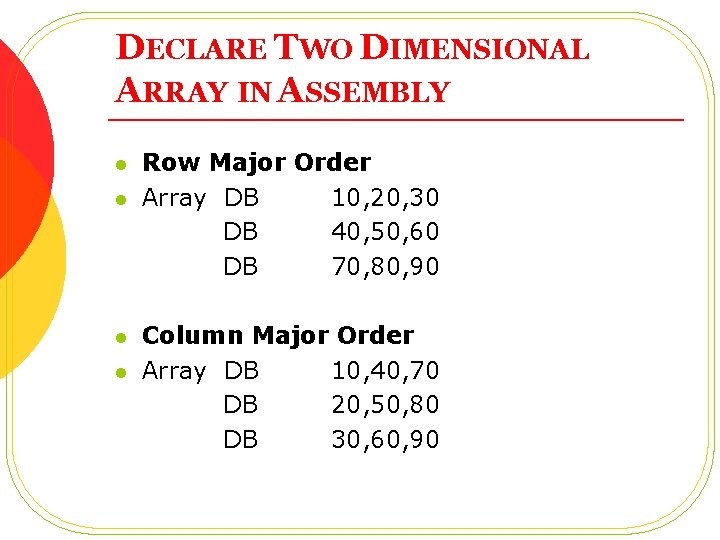

DECLARE TWO DIMENSIONAL ARRAY IN ASSEMBLY l l Row Major Order Array DB 10, 20, 30 DB 40, 50, 60 DB 70, 80, 90 Column Major Order Array DB 10, 40, 70 DB 20, 50, 80 DB 30, 60, 90

![LOCATE AN ELEMENT IN TWO DIMENSIONAL ARRAY l l l A [i, j] is LOCATE AN ELEMENT IN TWO DIMENSIONAL ARRAY l l l A [i, j] is](http://slidetodoc.com/presentation_image/e584503cc3a2afe47da0fc75cfd4ff67/image-24.jpg)

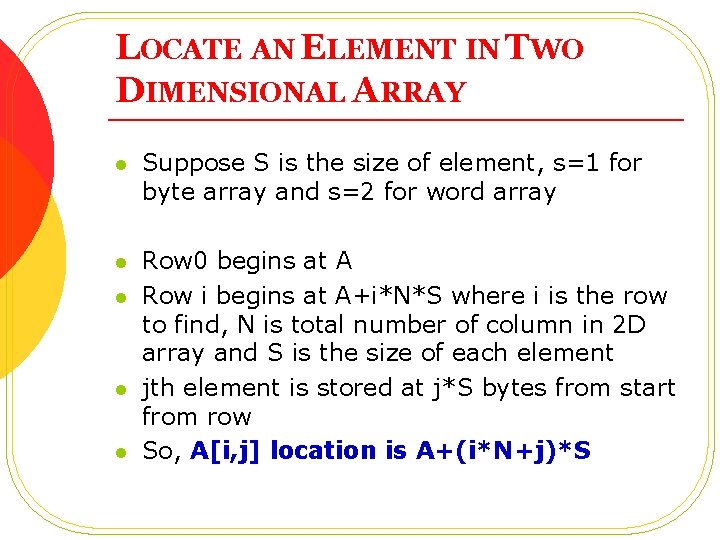

LOCATE AN ELEMENT IN TWO DIMENSIONAL ARRAY l l l A [i, j] is Mx. N a 2 D array, stored in Row Major Order M is Total Number of rows N is Total Number of columns Where i is row number and j is column Locate, where i begins Find jth Column in that ith row

LOCATE AN ELEMENT IN TWO DIMENSIONAL ARRAY l Suppose S is the size of element, s=1 for byte array and s=2 for word array l Row 0 begins at A Row i begins at A+i*N*S where i is the row to find, N is total number of column in 2 D array and S is the size of each element jth element is stored at j*S bytes from start from row So, A[i, j] location is A+(i*N+j)*S l l l

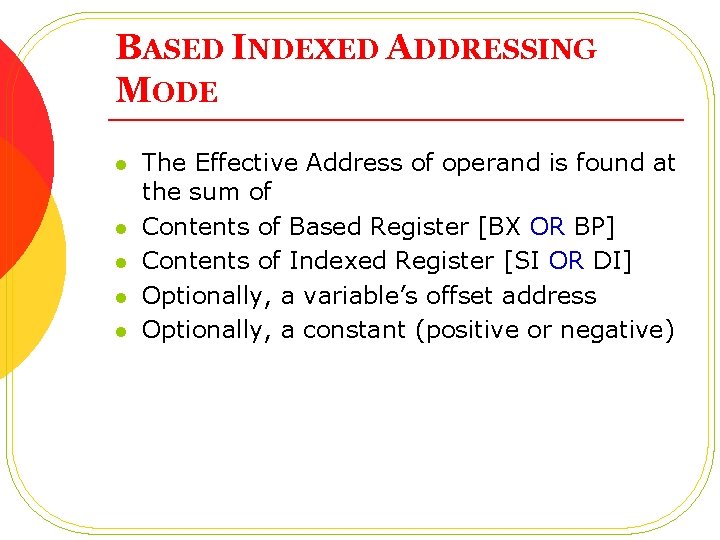

BASED INDEXED ADDRESSING MODE l l l The Effective Address of operand is found at the sum of Contents of Based Register [BX OR BP] Contents of Indexed Register [SI OR DI] Optionally, a variable’s offset address Optionally, a constant (positive or negative)

BASED INDEXED ADDRESSING MODE l There are many valid ways to write Based Indexed Addressing Mode, some of them are l l l [base + index + variable + constant]<-- preferred variable[base + index + constant] constant[base + index + variable]

EXAMPLE: BASED INDEXED ADDRESSING MODE l l Suppose A is a 5 x 7 word array stored in row-major order. Write code to clear row 2. MOV BX, 28 ; BX indexes row 2 MOV SI, 0 ; SI will index columns MOV CX, 7 ; # elements in a row clear: MOV [BX + SI + A], 0 ; clear A[2, j] ADD SI, 2 ; go to next column LOOP clear ; loop until done

EXAMPLE: BASED INDEXED ADDRESSING MODE Another Example: Write code to clear column 3 -- Since A is a 7 column word array we need to add 2*7 = 14 to get to the next row mov si, 6 ; si indexes column 3 xor bx, bx ; bx will index rows mov cx, 5 ; #elements in a column clear: mov [bx + si + A], 0 ; clear A[i, 3] add bx, 14 ; go to next row loop clear ; loop until done l

QUESTIONS l ? ? ? ? ? ? ?

- Slides: 30