Improving Op Amp performance Improving gain cascoding cascading

- Slides: 81

Improving Op Amp performance • Improving gain – cascoding – cascading – feedback – feed forward – push pull – complementary input – decreasing current – using “analog friendly” CMOS processes – using bipolar

• Improving speed – Increasing UGF, increase transient speed • Settling may not improve, which depends on PM and secondary poles • Cannot simply increase W/L ratio optimal sizing for a given CL • Two stage optimal design: can potentially achieve higher UGF than single stage – Increasing PM at UGF, reduce ringing • Once PM large enough, no effect – Taking care of secondary poles and zeros, reduce settling time to 1/A 0 level • Pole zero cancellation be accurate and at sufficiently high frequency • Cascode or mirror poles sufficiently high frequency • Reduce parasitic capacitances – Increasing current – Using better processes

• Other specifications to improve – reduced power consumption – low voltage operation – low output impedance (to drive resistive load, or deliver sufficient real power) – large output swing (large signal to noise ratio) – large input common mode range – large CMRR – large PSRR – small offset voltage – improved linearity – low noise operation – common mode stability

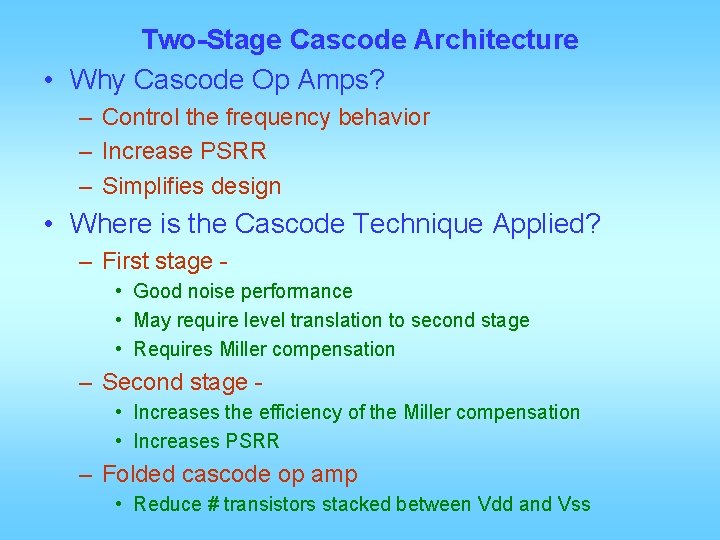

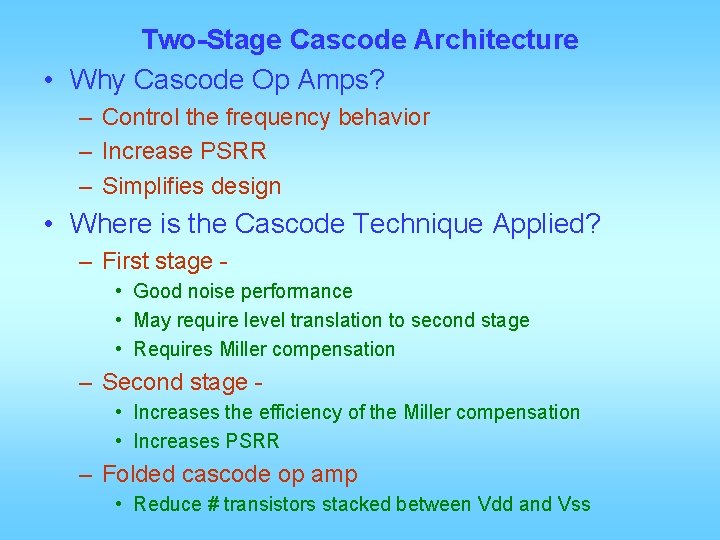

Two-Stage Cascode Architecture • Why Cascode Op Amps? – Control the frequency behavior – Increase PSRR – Simplifies design • Where is the Cascode Technique Applied? – First stage • Good noise performance • May require level translation to second stage • Requires Miller compensation – Second stage • Increases the efficiency of the Miller compensation • Increases PSRR – Folded cascode op amp • Reduce # transistors stacked between Vdd and Vss

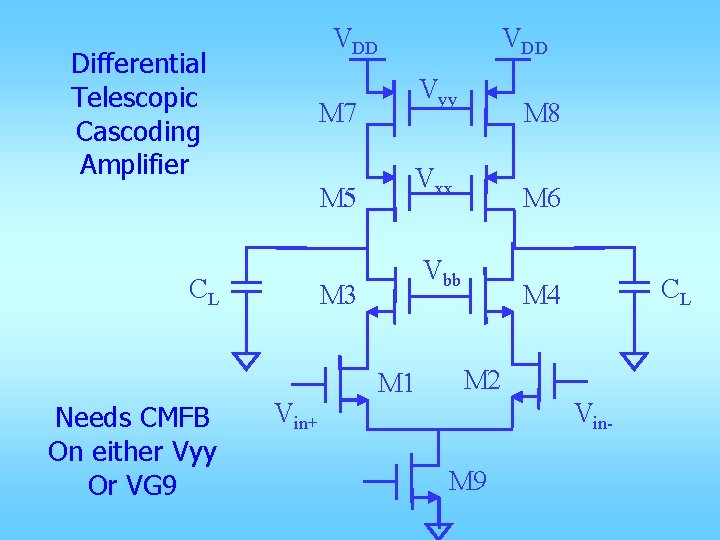

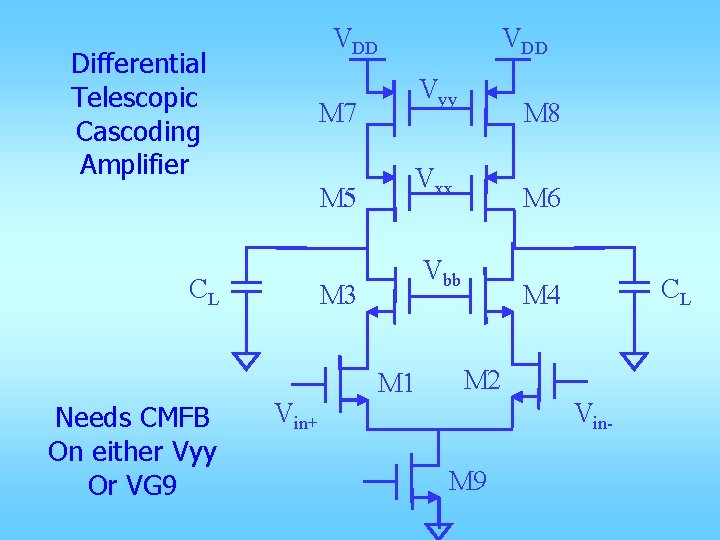

Differential Telescopic Cascoding Amplifier VDD Vyy M 7 M 5 CL Needs CMFB On either Vyy Or VG 9 VDD Vxx M 6 Vbb M 3 Vin+ M 8 M 1 CL M 4 M 2 Vin- M 9

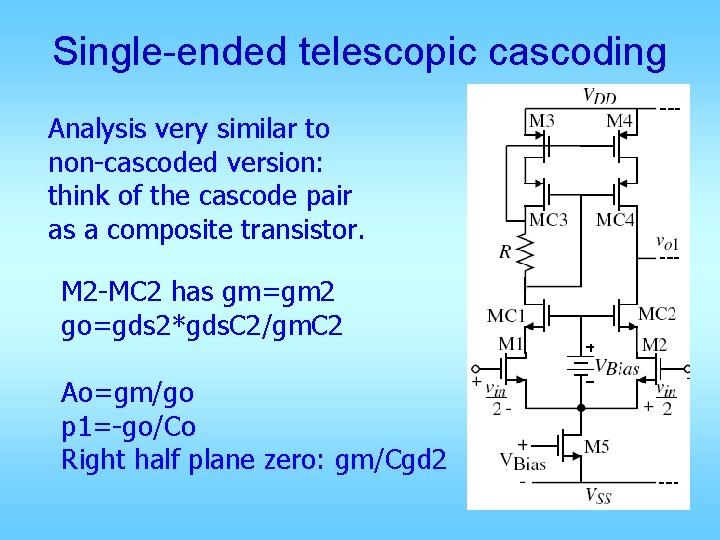

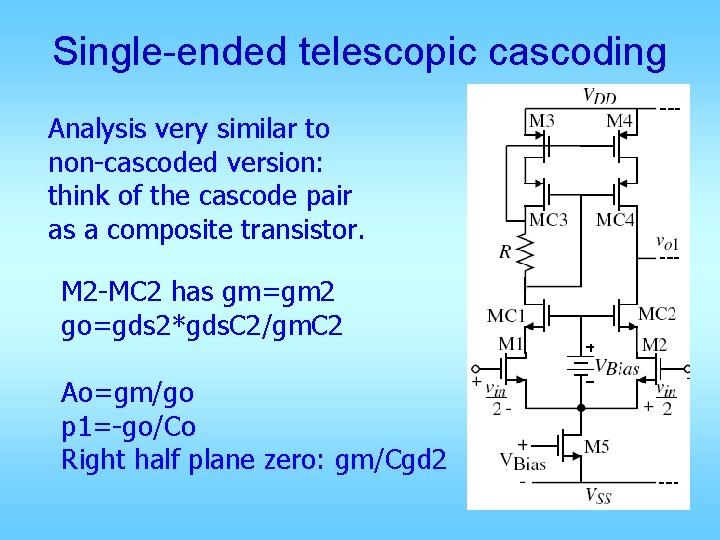

Single-ended telescopic cascoding Analysis very similar to non-cascoded version: think of the cascode pair as a composite transistor. M 2 -MC 2 has gm=gm 2 go=gds 2*gds. C 2/gm. C 2 Ao=gm/go p 1=-go/Co Right half plane zero: gm/Cgd 2

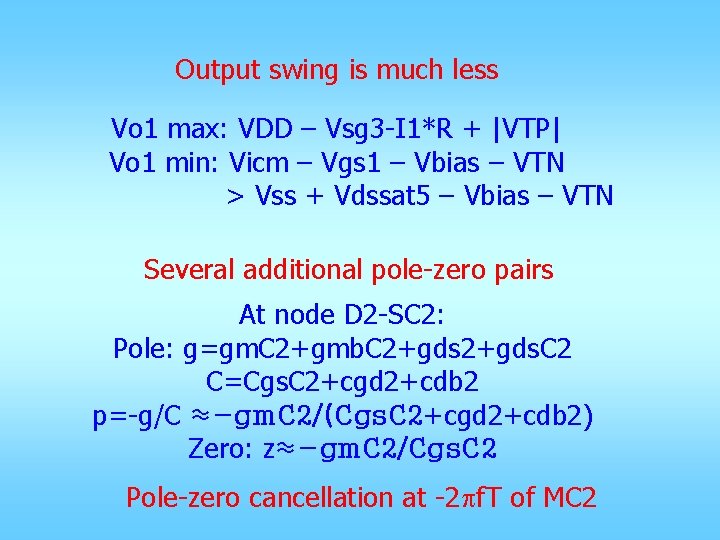

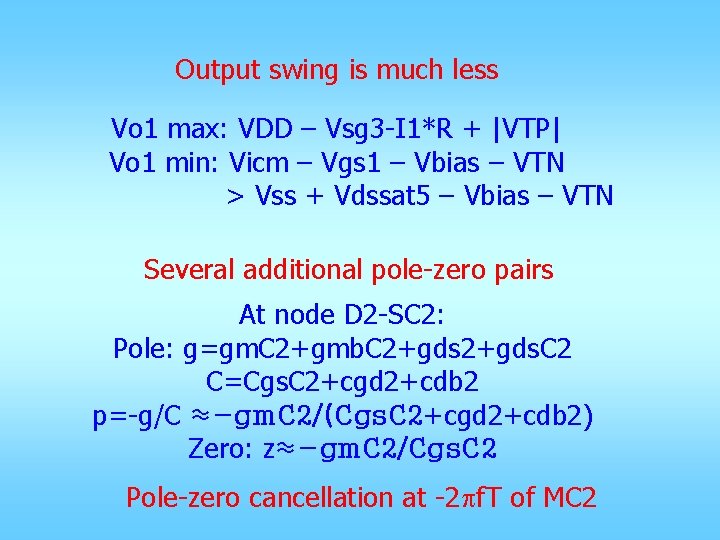

Output swing is much less Vo 1 max: VDD – Vsg 3 -I 1*R + |VTP| Vo 1 min: Vicm – Vgs 1 – Vbias – VTN > Vss + Vdssat 5 – Vbias – VTN Several additional pole-zero pairs At node D 2 -SC 2: Pole: g=gm. C 2+gmb. C 2+gds. C 2 C=Cgs. C 2+cgd 2+cdb 2 p=-g/C ≈-gm. C 2/(Cgs. C 2+cgd 2+cdb 2) Zero: z≈-gm. C 2/Cgs. C 2 Pole-zero cancellation at -2 pf. T of MC 2

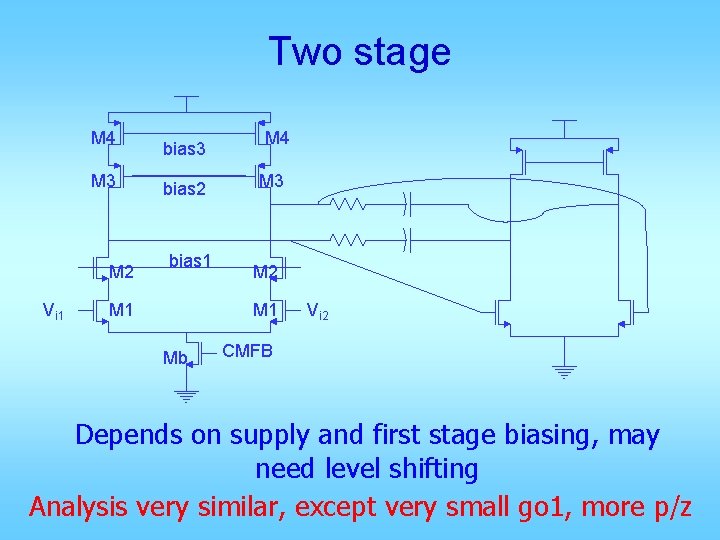

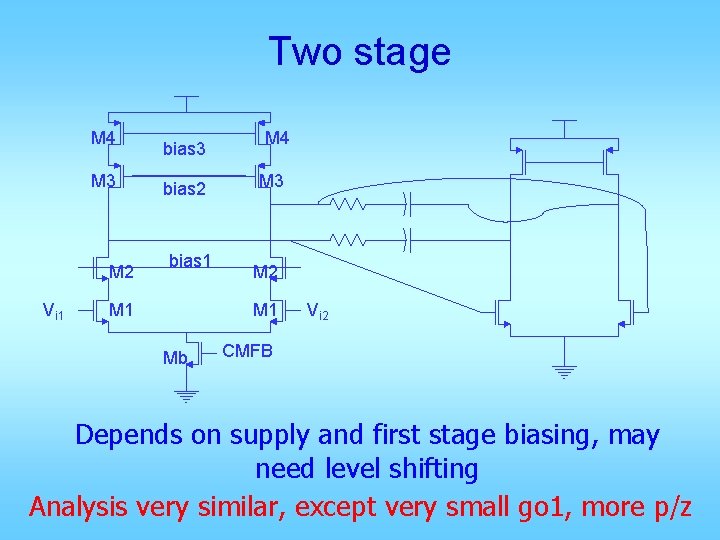

Two stage M 4 M 3 M 2 Vi 1 bias 3 bias 2 bias 1 M 4 M 3 M 2 M 1 Mb Vi 2 CMFB Depends on supply and first stage biasing, may need level shifting Analysis very similar, except very small go 1, more p/z

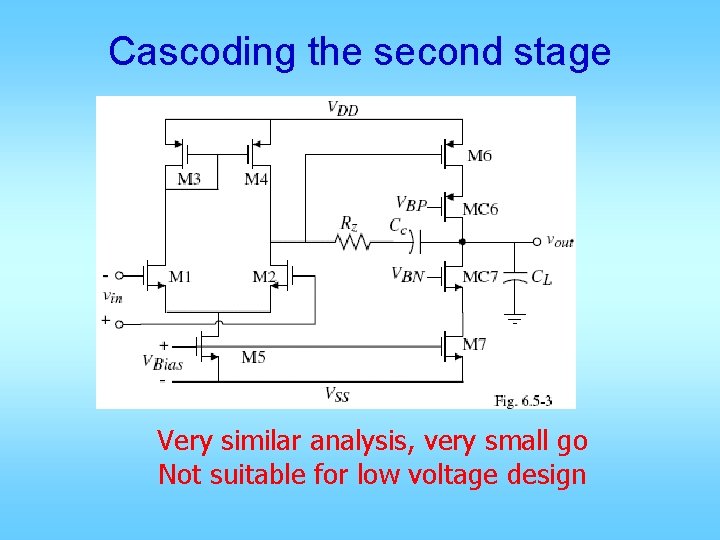

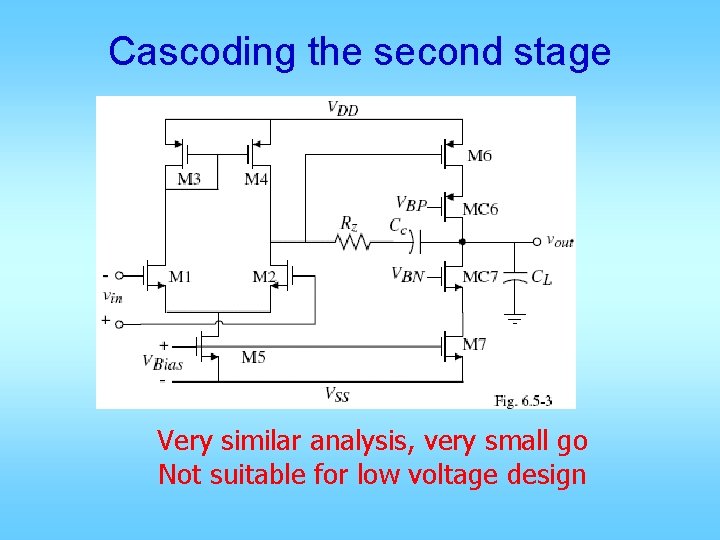

Cascoding the second stage Very similar analysis, very small go Not suitable for low voltage design

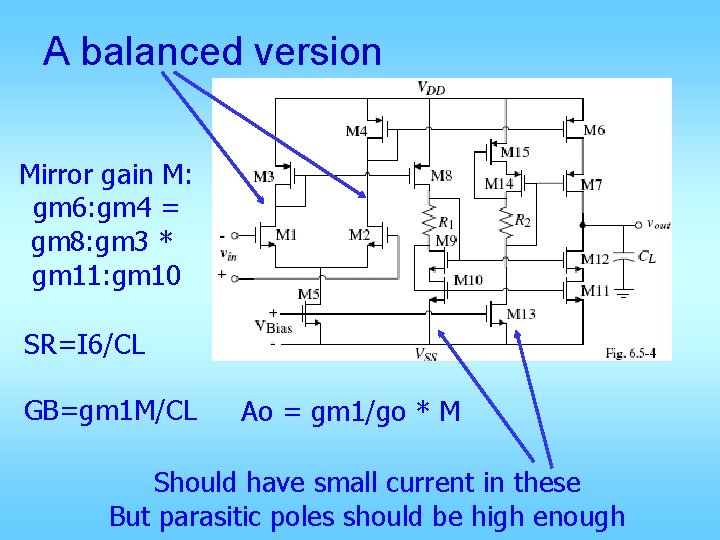

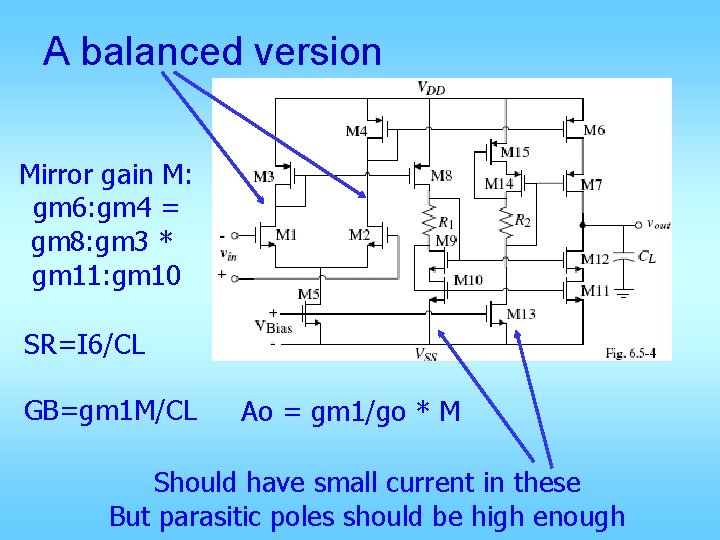

A balanced version Mirror gain M: gm 6: gm 4 = gm 8: gm 3 * gm 11: gm 10 SR=I 6/CL GB=gm 1 M/CL Ao = gm 1/go * M Should have small current in these But parasitic poles should be high enough

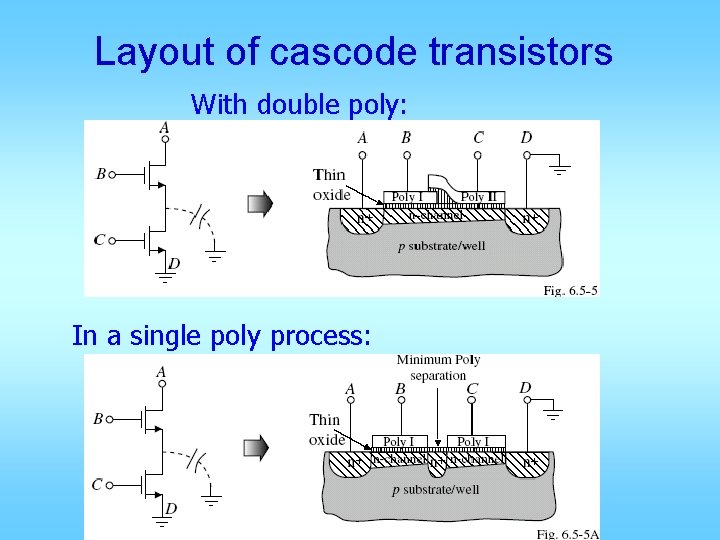

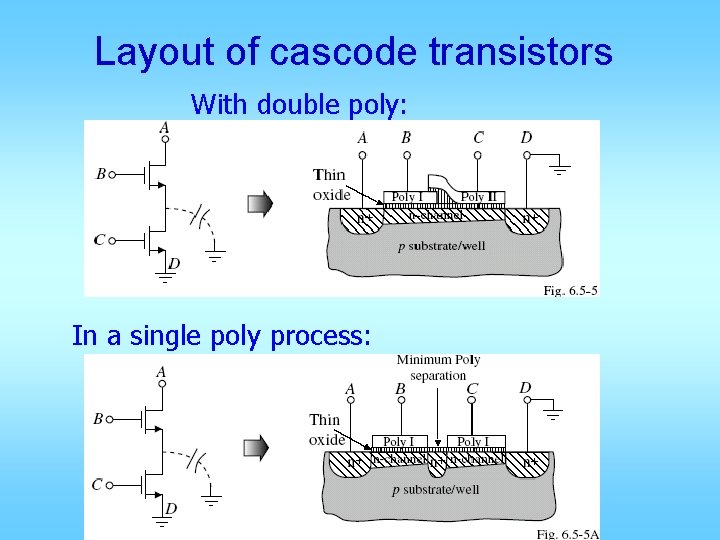

Layout of cascode transistors With double poly: In a single poly process:

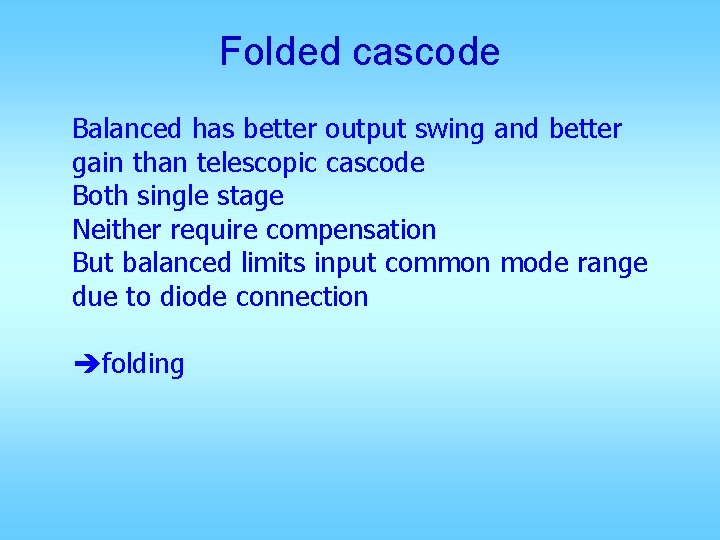

Folded cascode Balanced has better output swing and better gain than telescopic cascode Both single stage Neither require compensation But balanced limits input common mode range due to diode connection folding

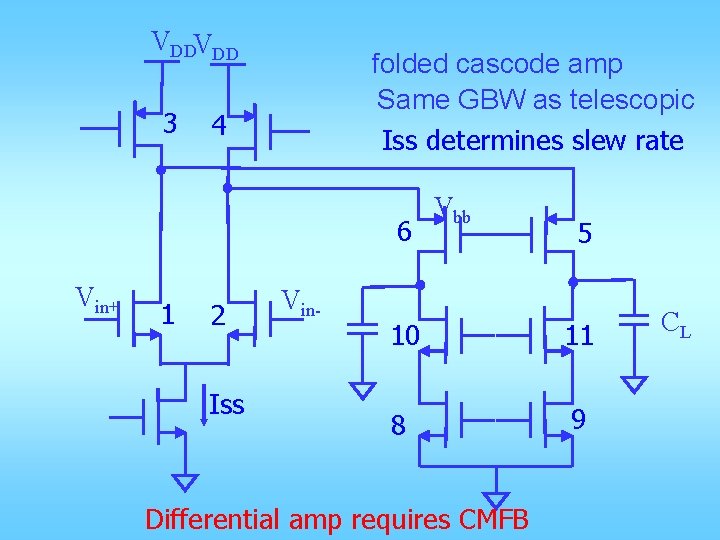

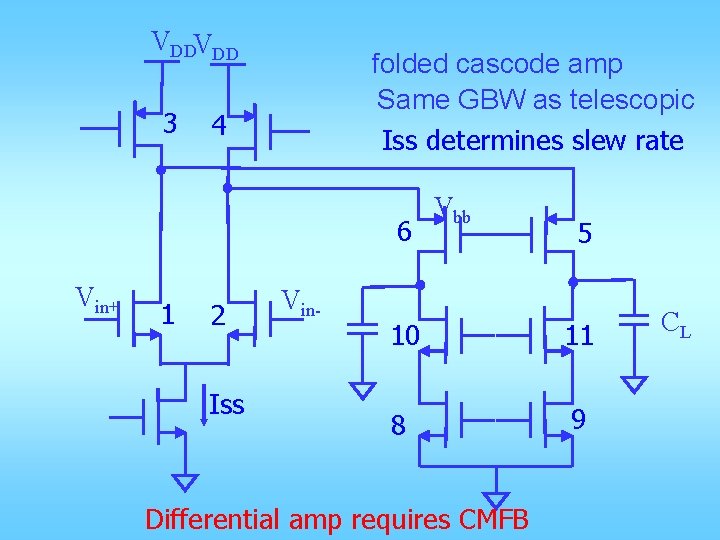

VDDVDD 3 folded cascode amp Same GBW as telescopic Iss determines slew rate 4 6 Vin+ 1 2 Iss Vin- Vbb 5 10 11 8 9 Differential amp requires CMFB CL

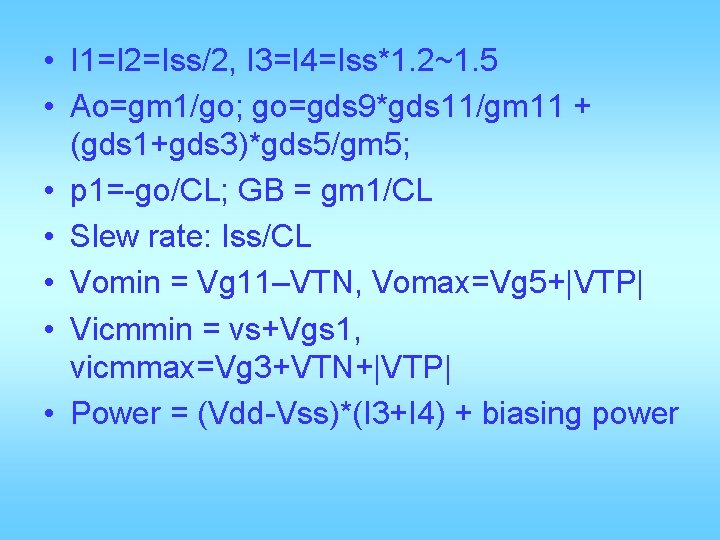

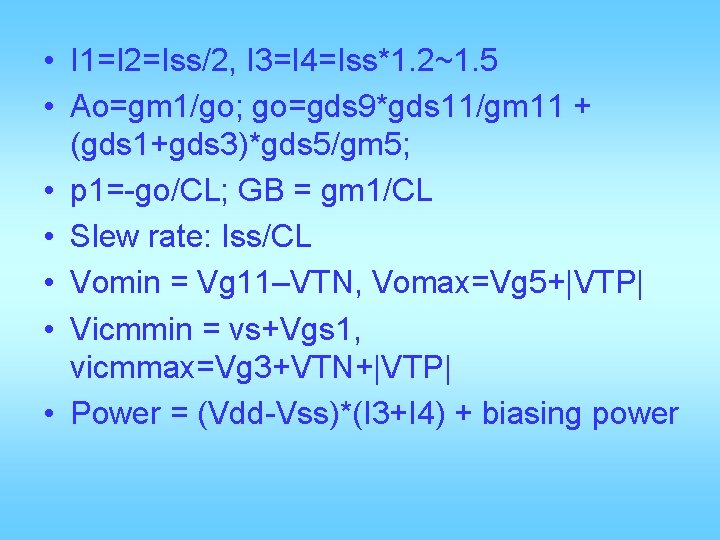

• I 1=I 2=Iss/2, I 3=I 4=Iss*1. 2~1. 5 • Ao=gm 1/go; go=gds 9*gds 11/gm 11 + (gds 1+gds 3)*gds 5/gm 5; • p 1=-go/CL; GB = gm 1/CL • Slew rate: Iss/CL • Vomin = Vg 11–VTN, Vomax=Vg 5+|VTP| • Vicmmin = vs+Vgs 1, vicmmax=Vg 3+VTN+|VTP| • Power = (Vdd-Vss)*(I 3+I 4) + biasing power

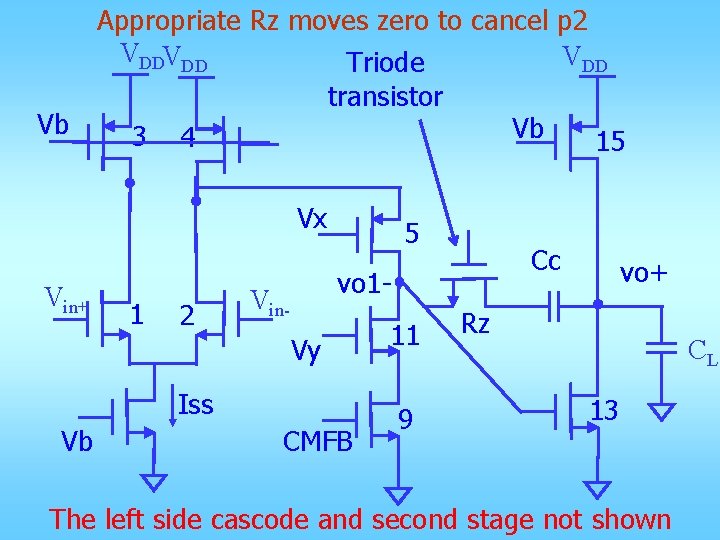

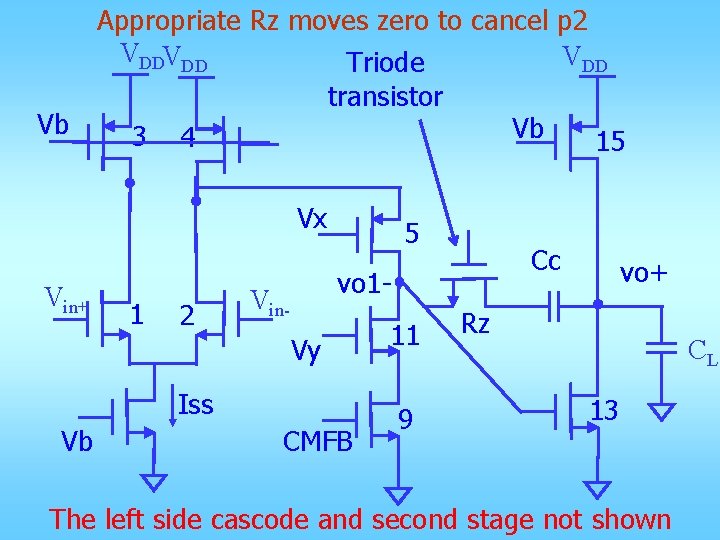

Appropriate Rz moves zero to cancel p 2 VDDVDD Triode transistor Vb Vb 3 4 15 Vx Vin+ 1 2 5 vo 1 - Vin. Vy Iss Vb Cc CMFB 11 9 vo+ Rz CL 13 The left side cascode and second stage not shown

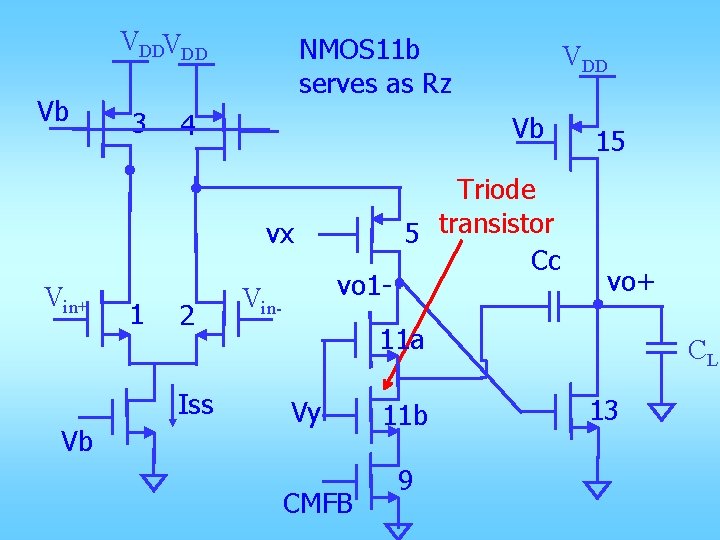

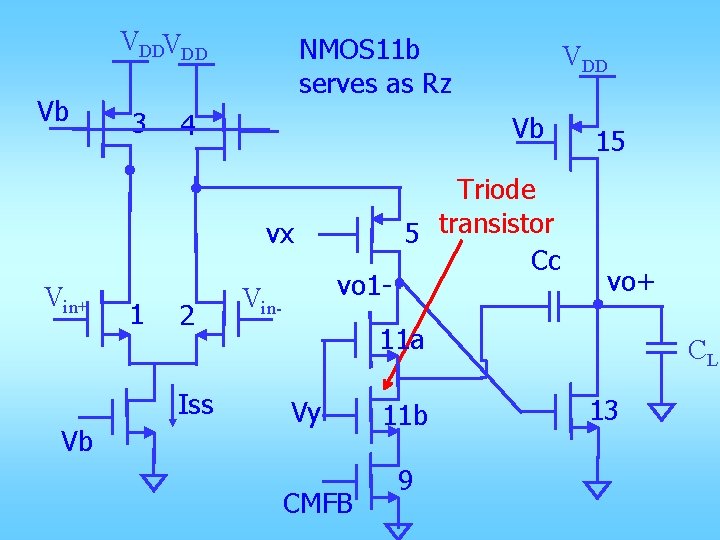

VDDVDD Vb 3 NMOS 11 b serves as Rz 4 Vb vx Vin+ 1 2 Iss Vb VDD vo 1 - Vin- Triode 5 transistor Cc 15 vo+ 11 a Vy CMFB 11 b 9 CL 13

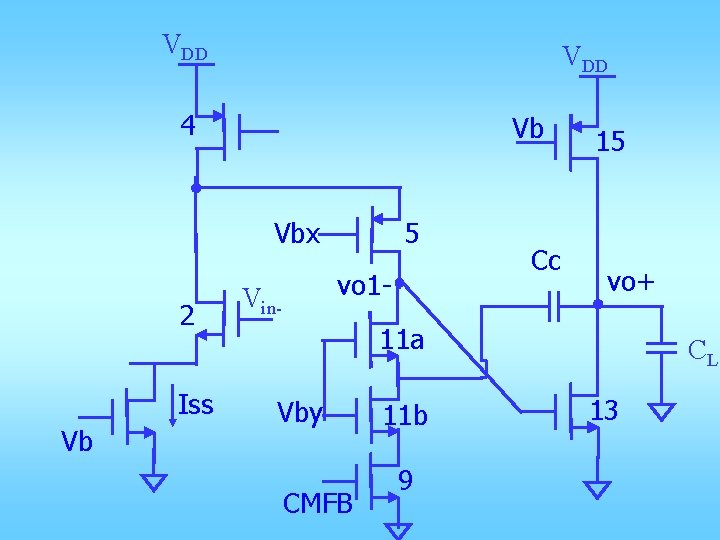

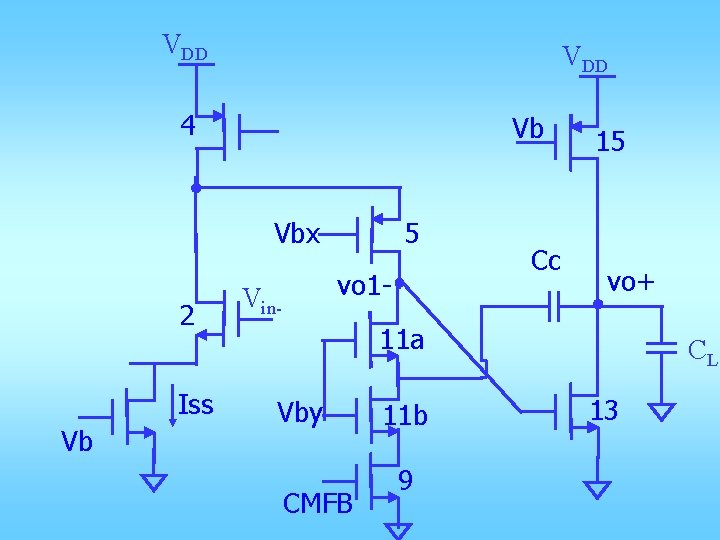

VDD 4 Vb Vbx 2 Iss Vb 5 vo 1 - Vin- Cc 15 vo+ 11 a Vby CMFB 11 b 9 CL 13

High speed low voltage design • Assume VDD-VSS<VTN-VTP, assume a given Itot • Use minimum length for high speed operation • Use appropriate Von 13, 15 to achieve balance between high f. T and high swing • Select Von 4, 5, 9, 11 so that vo 1 has + – 10% (VDD-VSS) swing • Set desired vocm at (VDD+VSS+Vdssat 13 Vsdsat 15)/2 • Size transistors so that Vgs 13 = mid range of vo 1 swing

• Show that the compensation scheme has very similar pole splitting effect as in 7 transistor op amp before • Show that appropriate sizing of M 11 b can cause the zero to move over p 2 • If CMFB is applied at G 3, 4, compensation can be connected to channel of M 9 • Show that with an appropriate attenuator, the go at vo 1 can be made zero by positive feedback from opposite side vo 1+ to G 5 • Show that with an appropriate gm 5, the go at vo 1 can be made zero by positive feedback from opposite side v. D 12 to G 5

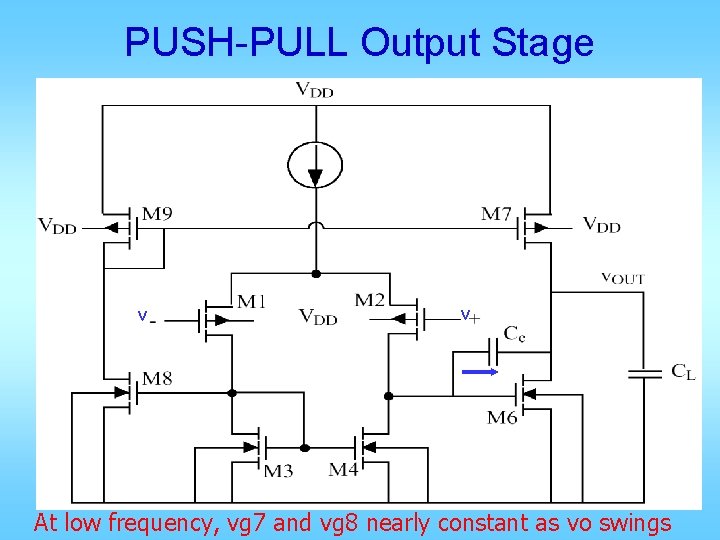

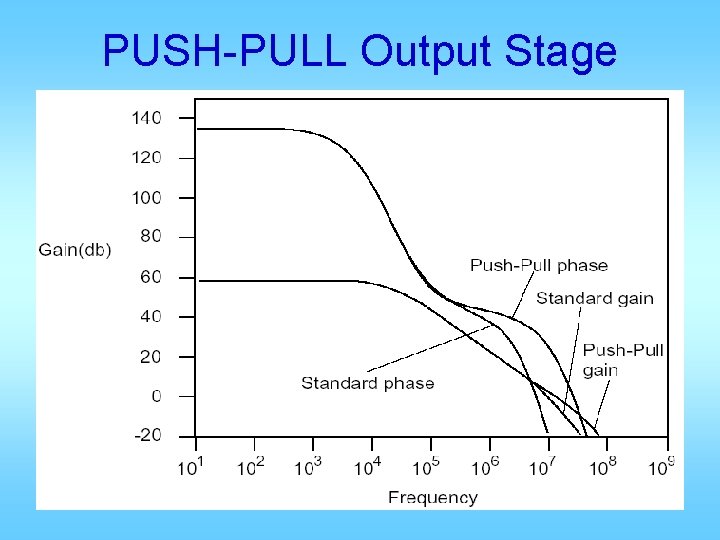

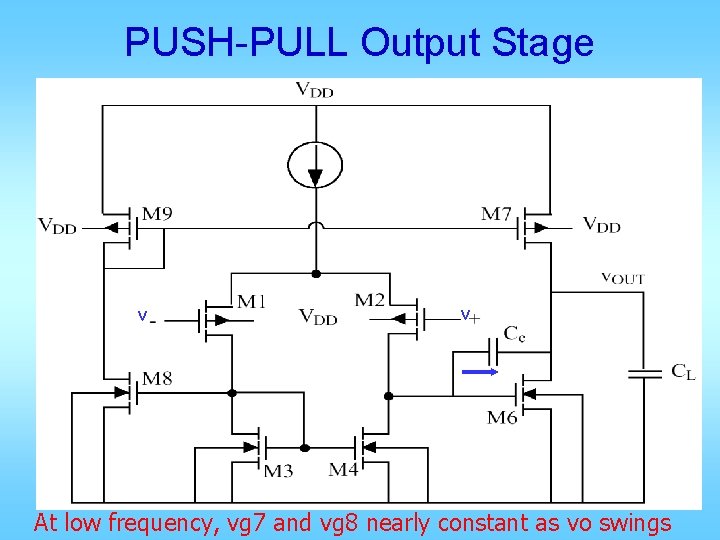

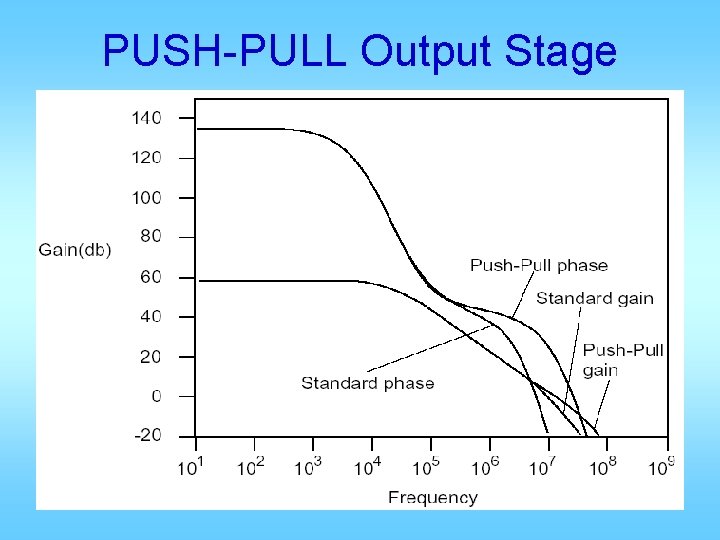

PUSH-PULL Output Stage v v At low frequency, vg 7 and vg 8 nearly constant as vo swings

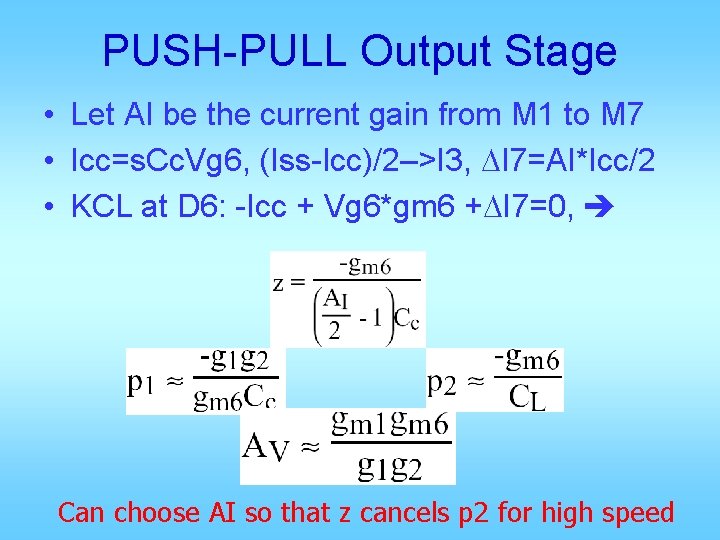

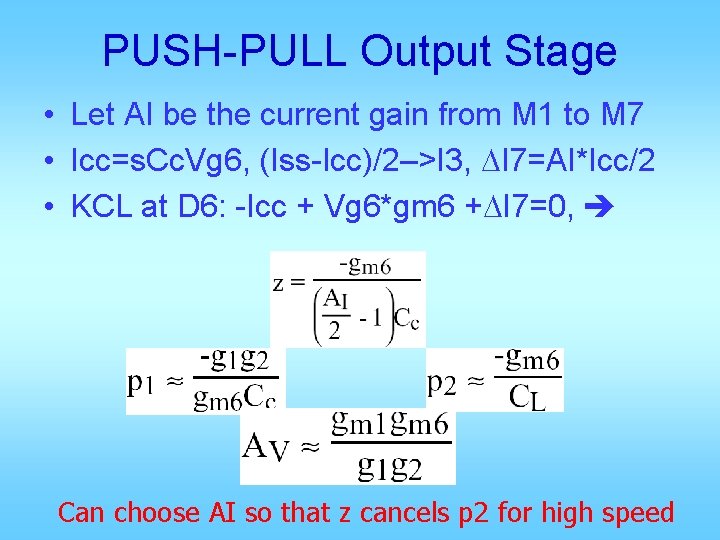

PUSH-PULL Output Stage • Let AI be the current gain from M 1 to M 7 • Icc=s. Cc. Vg 6, (Iss-Icc)/2–>I 3, DI 7=AI*Icc/2 • KCL at D 6: -Icc + Vg 6*gm 6 +DI 7=0, Can choose AI so that z cancels p 2 for high speed

PUSH-PULL Output Stage

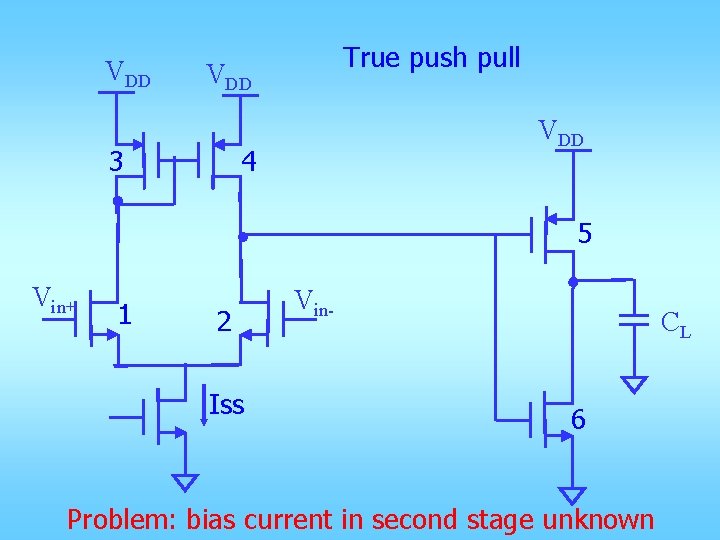

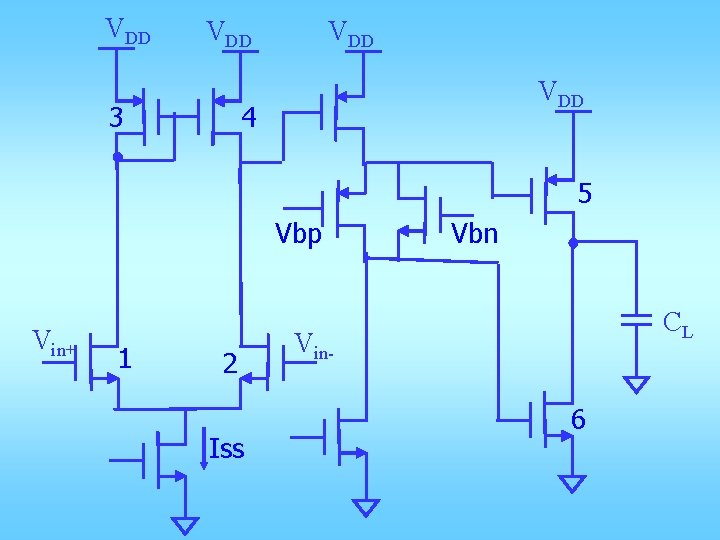

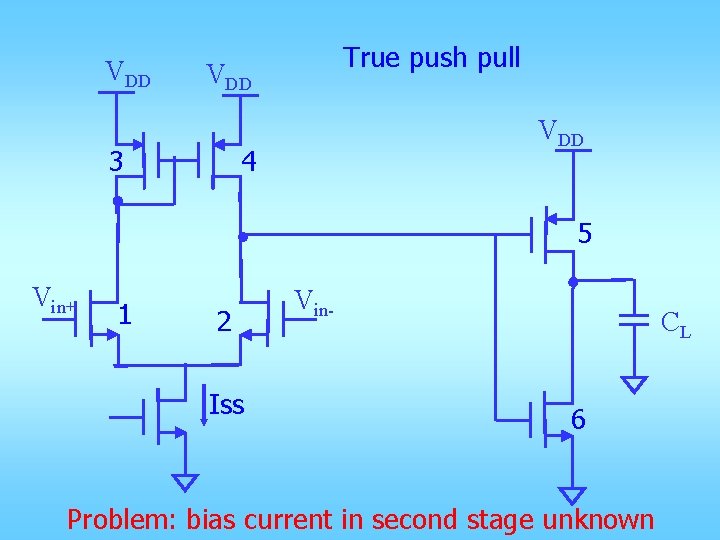

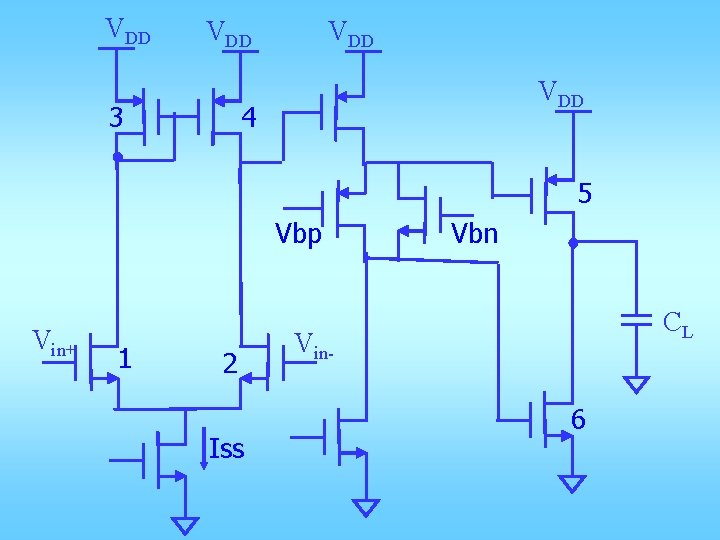

VDD True push pull VDD 3 VDD 4 5 Vin+ 1 2 Iss Vin- CL 6 Problem: bias current in second stage unknown

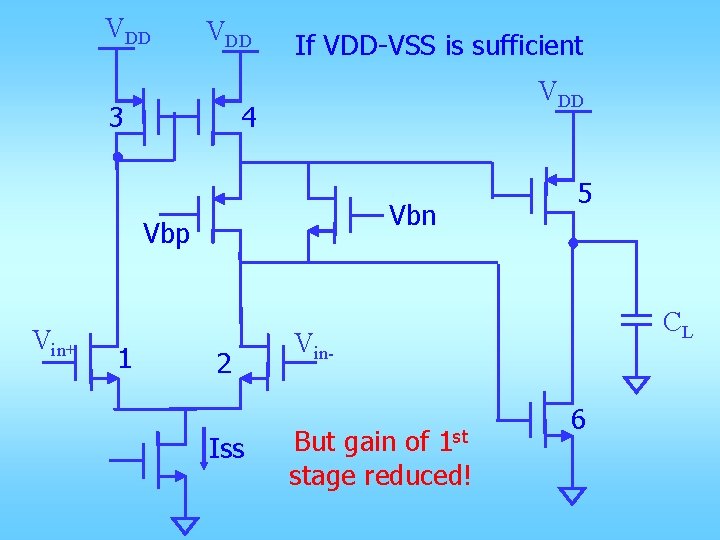

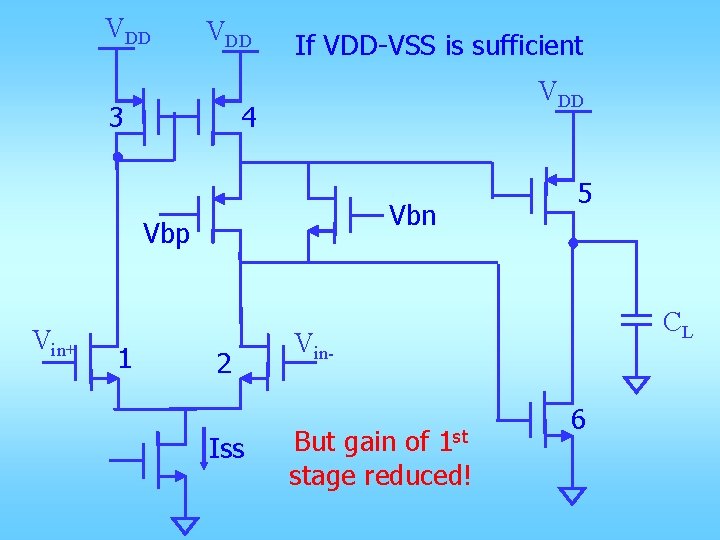

VDD 3 If VDD-VSS is sufficient VDD 4 Vbn Vbp Vin+ 1 5 2 Iss CL Vin 1 st But gain of stage reduced! 6

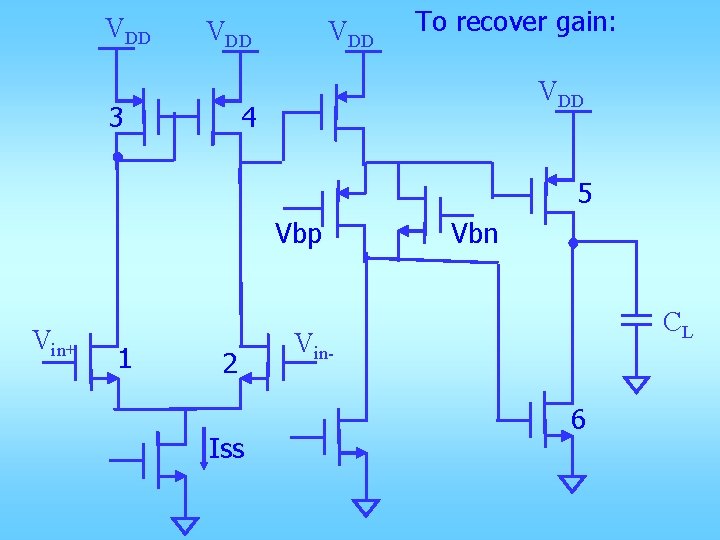

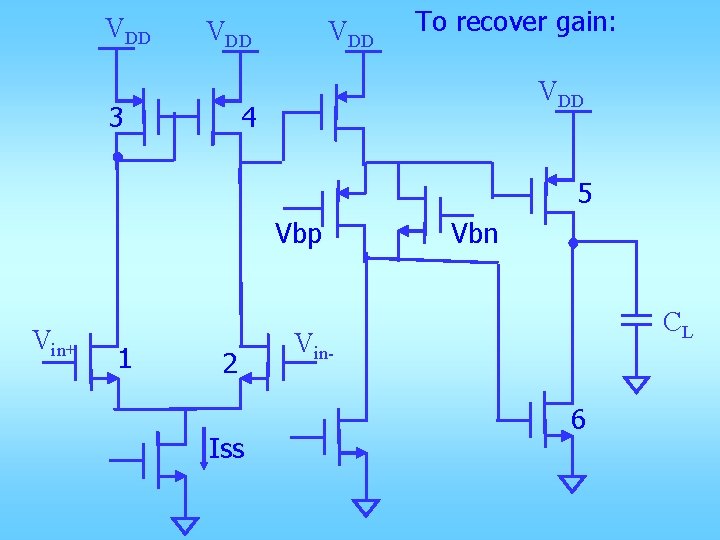

VDD 3 VDD To recover gain: VDD 4 5 Vbp Vin+ 1 2 Iss Vbn CL Vin 6

VDD 3 VDD 4 5 Vbp Vin+ 1 2 Iss Vbn CL Vin 6

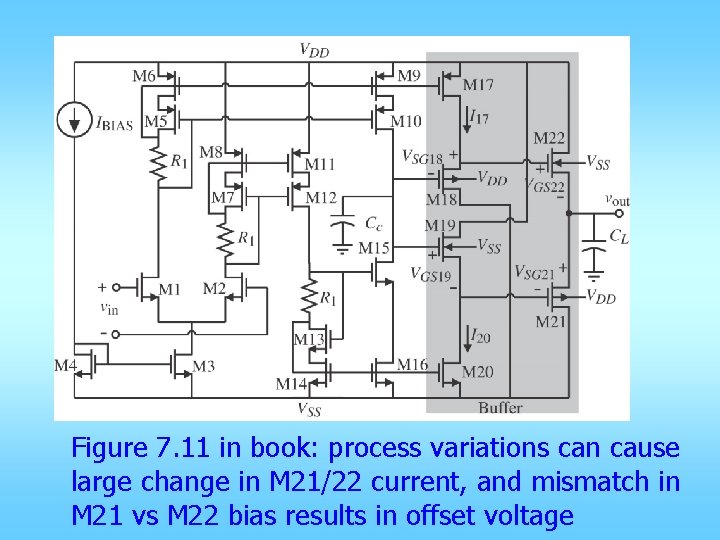

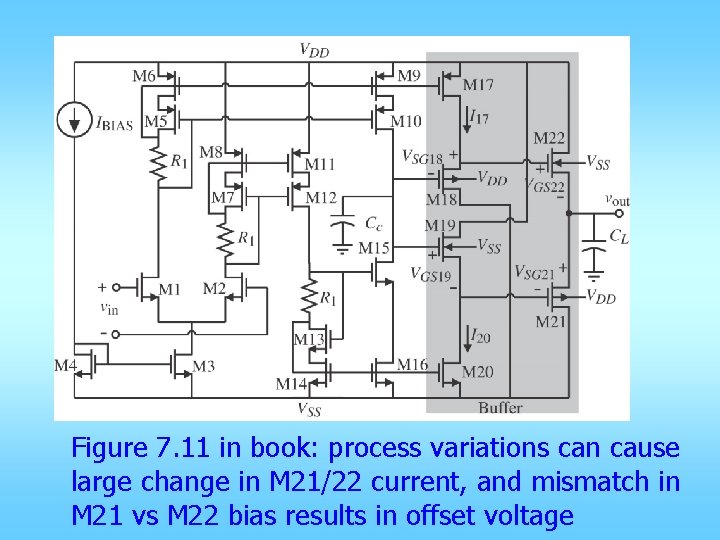

Figure 7. 11 in book: process variations can cause large change in M 21/22 current, and mismatch in M 21 vs M 22 bias results in offset voltage

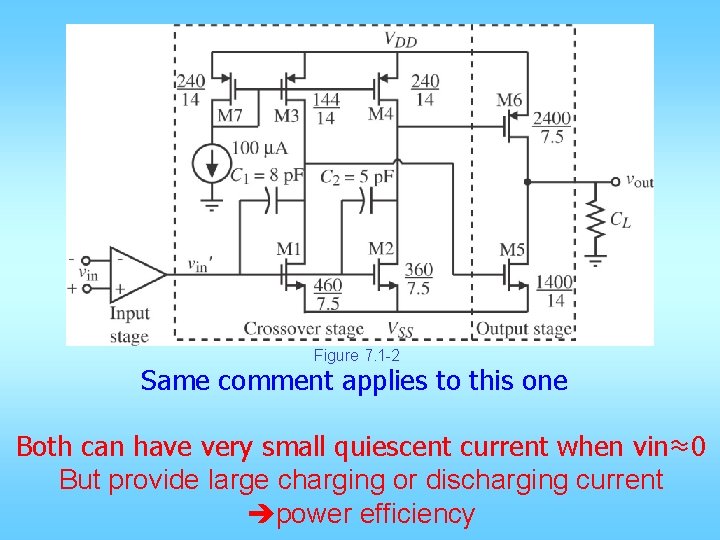

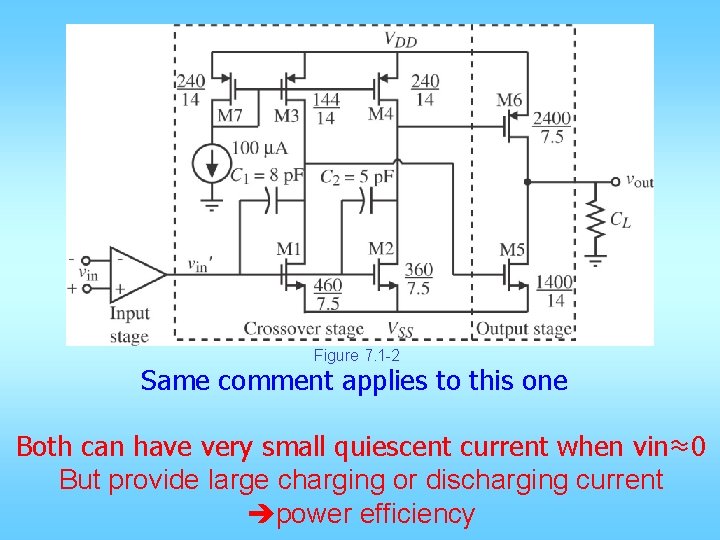

Figure 7. 1 -2 Same comment applies to this one Both can have very small quiescent current when vin≈0 But provide large charging or discharging current power efficiency

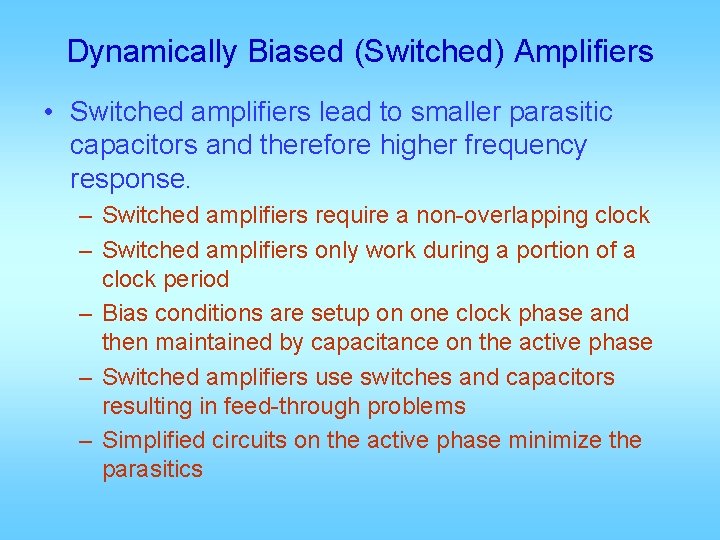

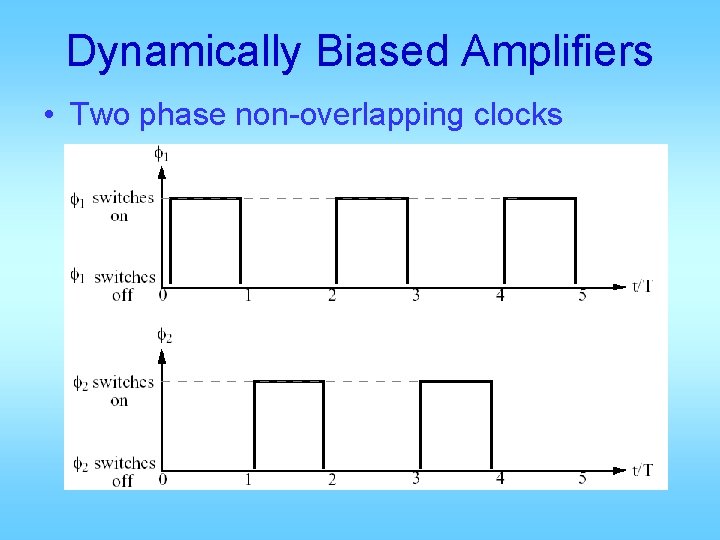

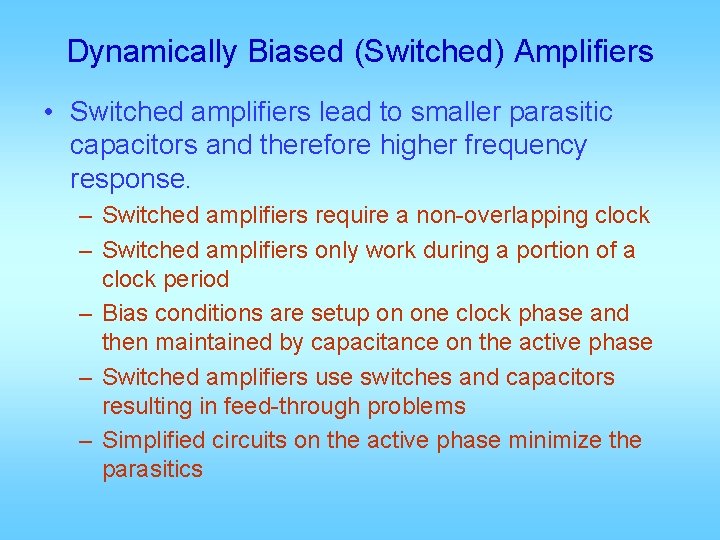

Dynamically Biased (Switched) Amplifiers • Switched amplifiers lead to smaller parasitic capacitors and therefore higher frequency response. – Switched amplifiers require a non-overlapping clock – Switched amplifiers only work during a portion of a clock period – Bias conditions are setup on one clock phase and then maintained by capacitance on the active phase – Switched amplifiers use switches and capacitors resulting in feed-through problems – Simplified circuits on the active phase minimize the parasitics

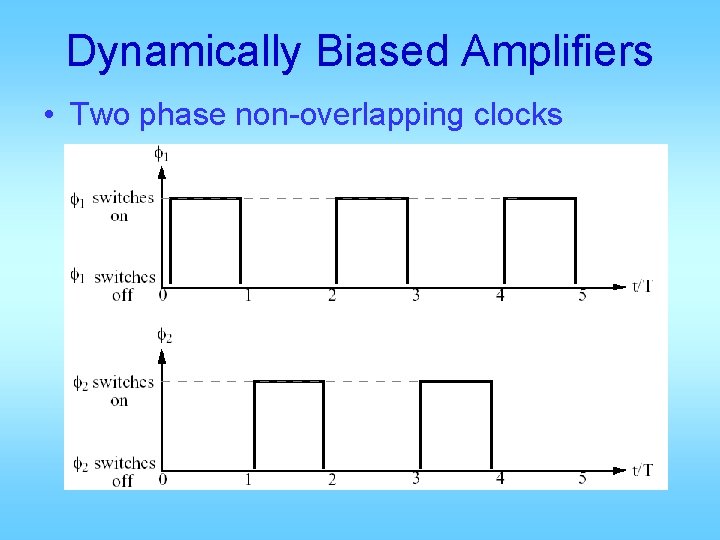

Dynamically Biased Amplifiers • Two phase non-overlapping clocks

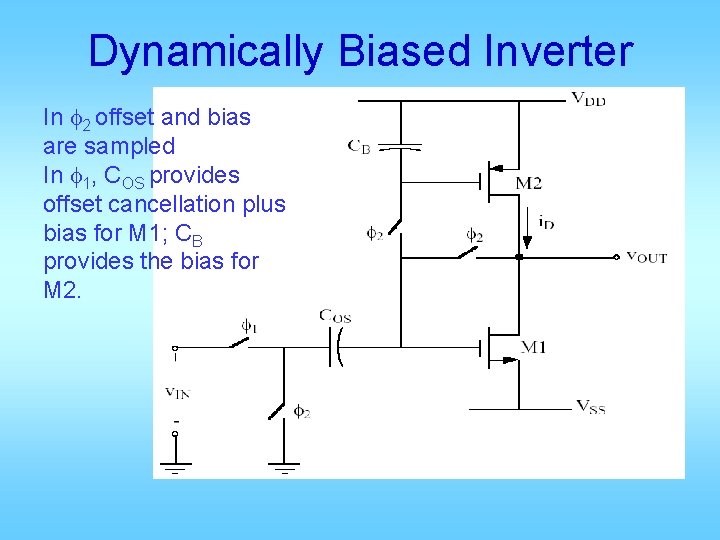

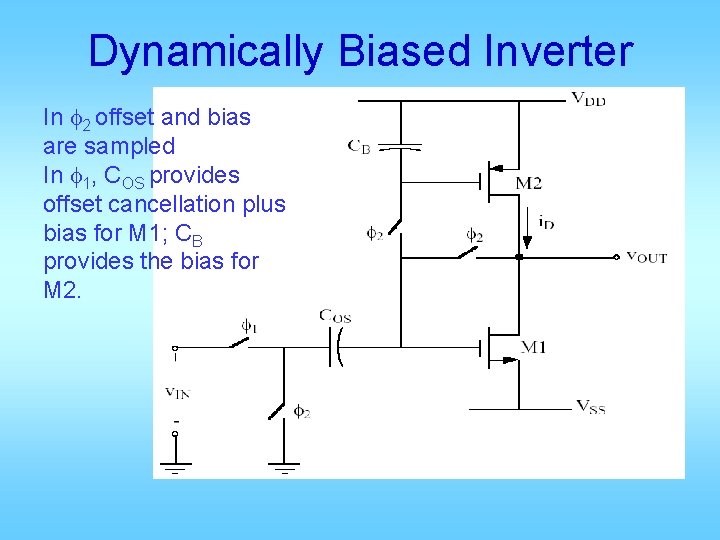

Dynamically Biased Inverter In f 2 offset and bias are sampled In f 1, COS provides offset cancellation plus bias for M 1; CB provides the bias for M 2.

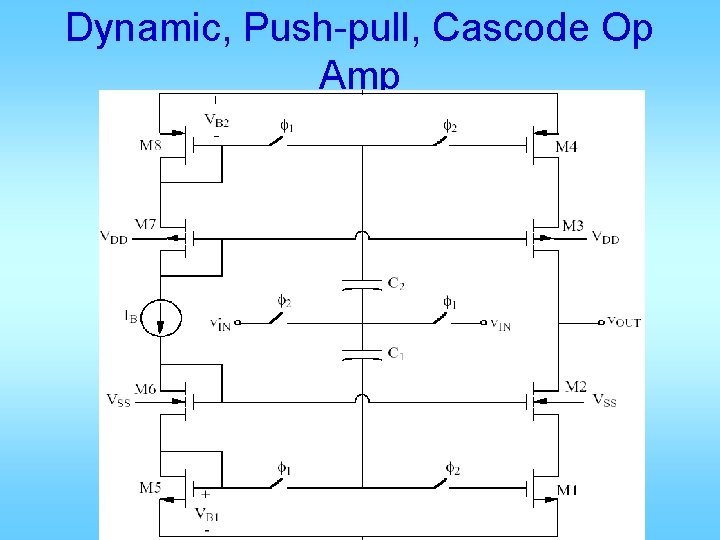

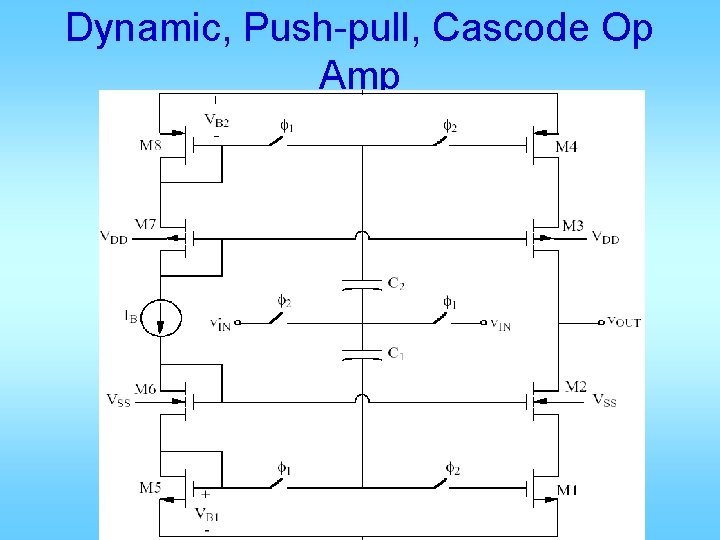

Dynamic, Push-pull, Cascode Op Amp

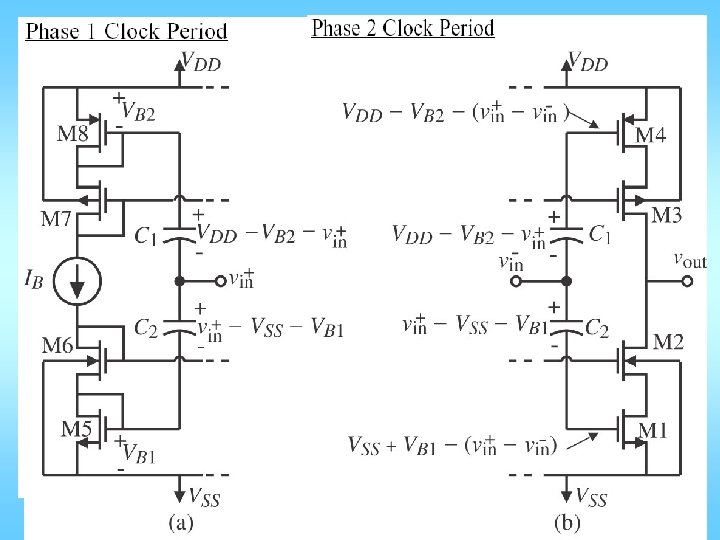

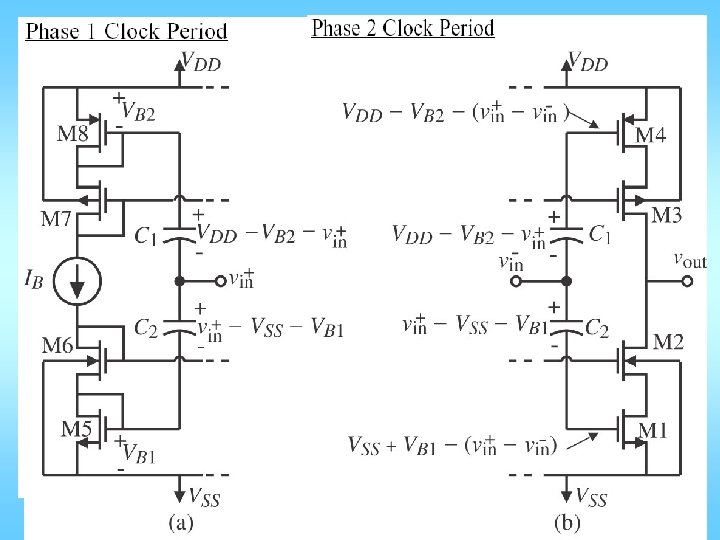

VDD - VB 2 - v. IN - VSS - VB 1

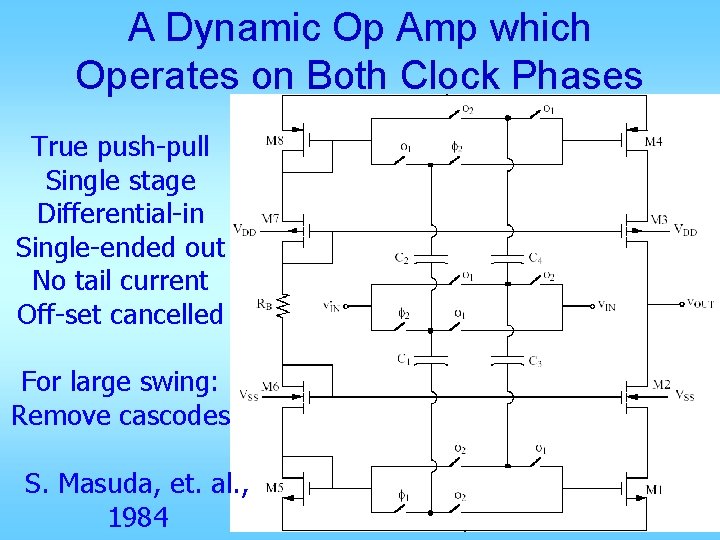

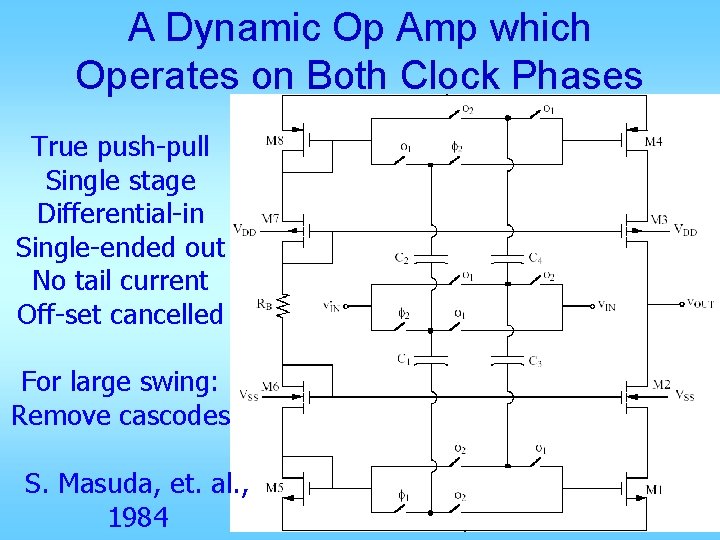

A Dynamic Op Amp which Operates on Both Clock Phases True push-pull Single stage Differential-in Single-ended out No tail current Off-set cancelled For large swing: Remove cascodes S. Masuda, et. al. , 1984

LOW VOLTAGE OP AMPS • We will cover: – Low voltage input stages – Low voltage bias circuits – Low voltage op amps – Examples • Methodology: – Modify standard circuit blocks for reduced power supply voltage – Explore new circuits suitable for low voltage design

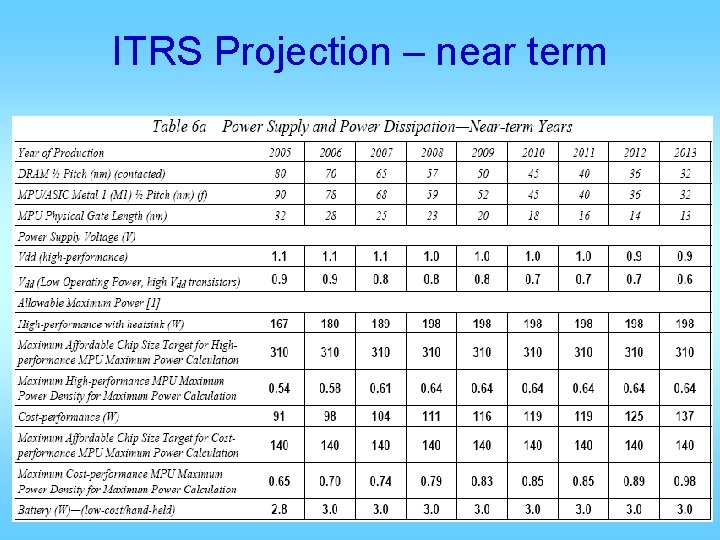

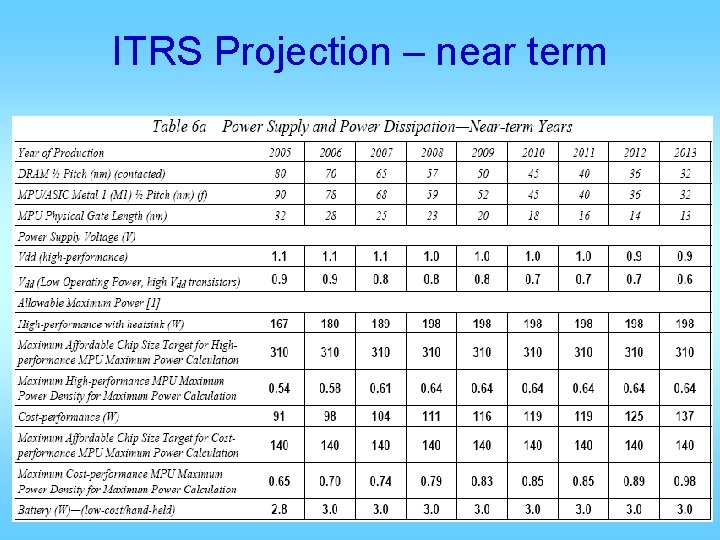

ITRS Projection – near term

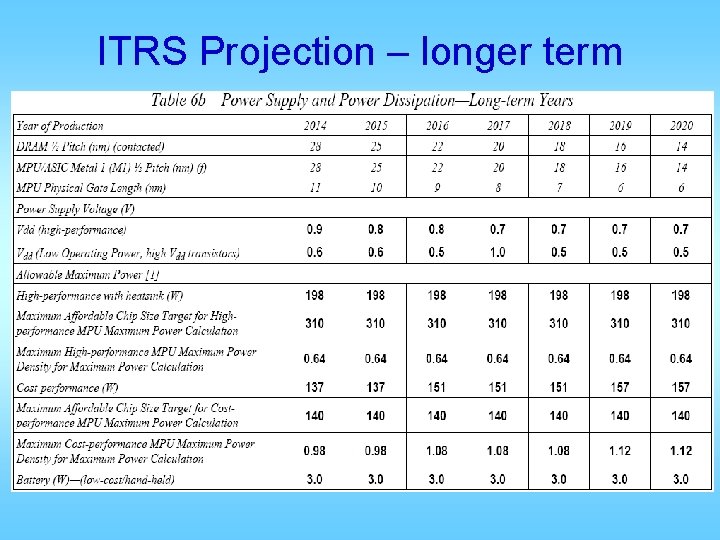

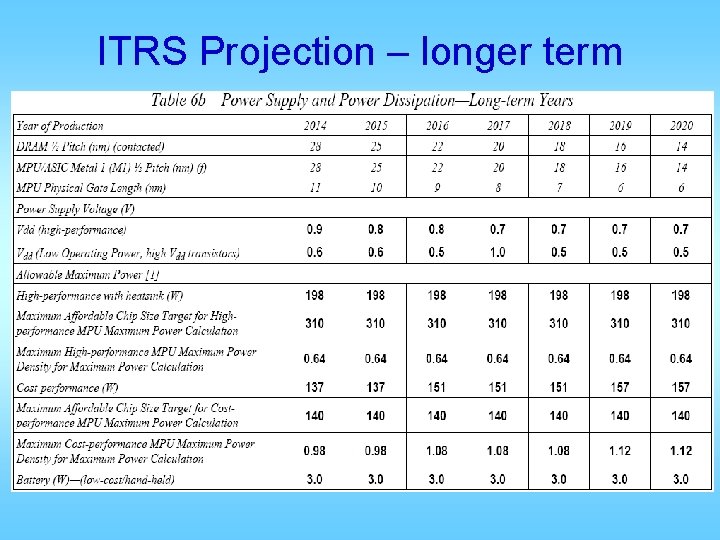

ITRS Projection – longer term

Low-Voltage, Strong-Inversion Operation • Reduced power supply means decreased dynamic range • Nonlinearity will increase because the transistor is working close to VDS(sat) • Large values of λ because the transistor is working close to VDS(sat) • Increased drain-bulk and source-bulk capacitances because they are less reverse biased. • Large values of currents and W/L ratios to get high transconductance • Small values of currents and large values of W/L will give small. VDS(sat) • Severely reduced input common mode range • Switches will require charge pumps

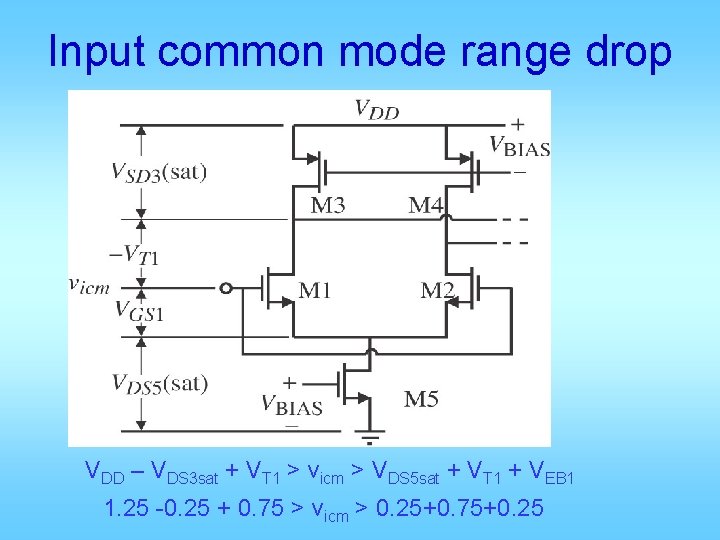

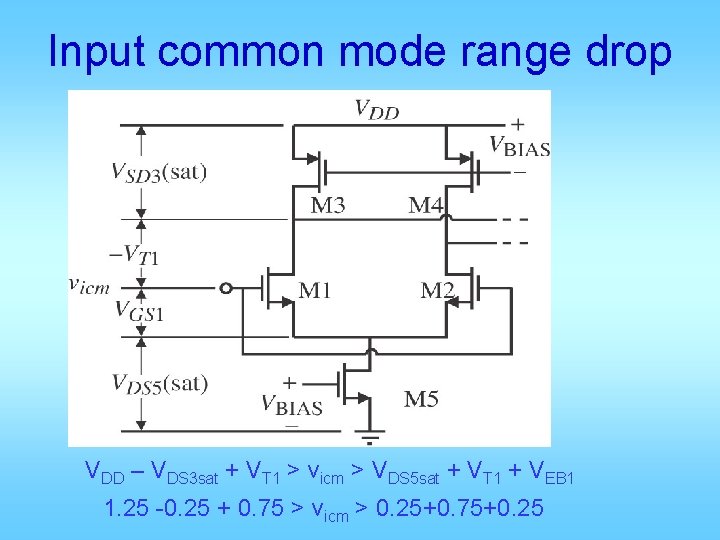

Input common mode range drop VDD – VDS 3 sat + VT 1 > vicm > VDS 5 sat + VT 1 + VEB 1 1. 25 -0. 25 + 0. 75 > vicm > 0. 25+0. 75+0. 25

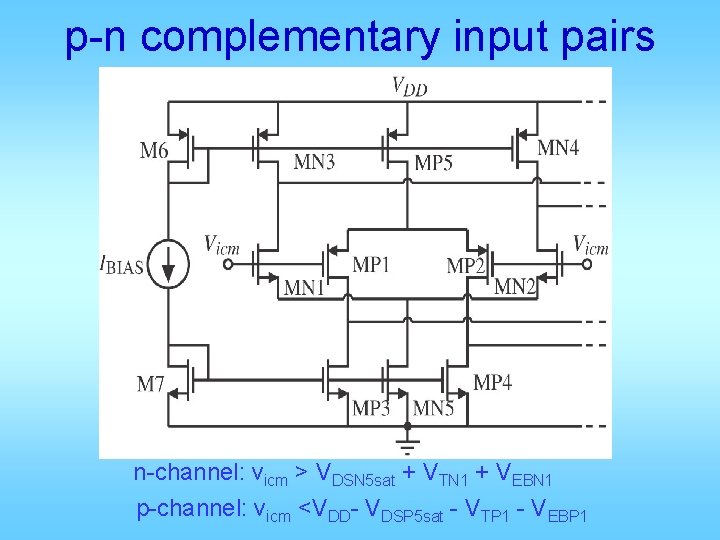

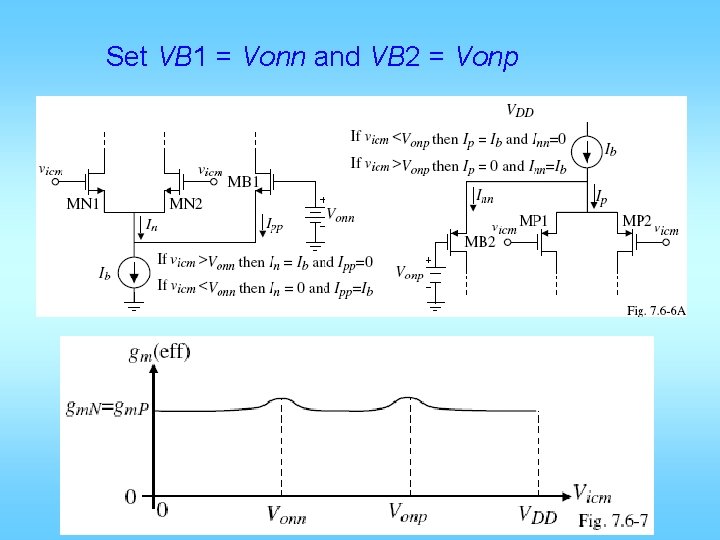

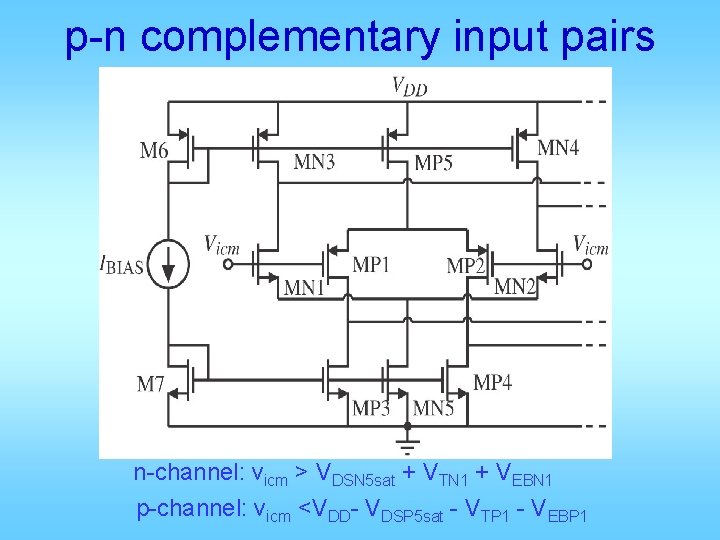

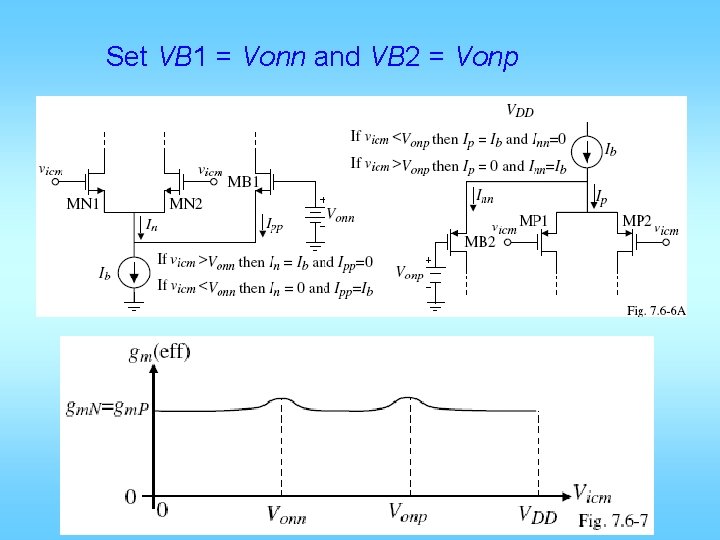

p-n complementary input pairs n-channel: vicm > VDSN 5 sat + VTN 1 + VEBN 1 p-channel: vicm <VDD- VDSP 5 sat - VTP 1 - VEBP 1

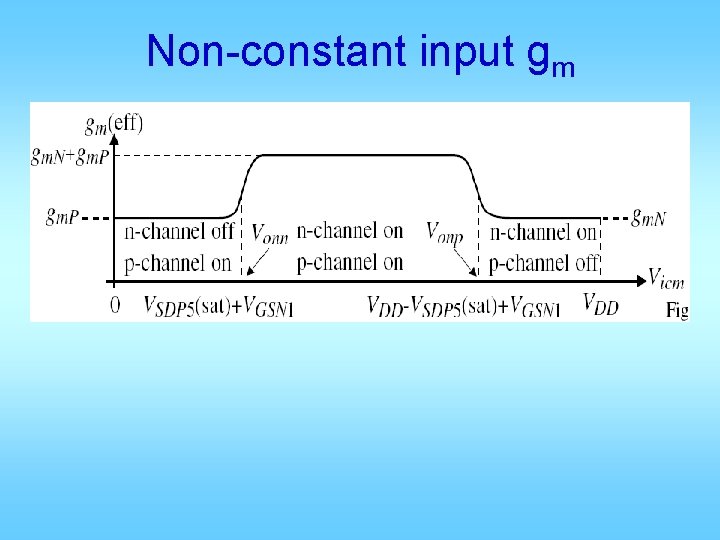

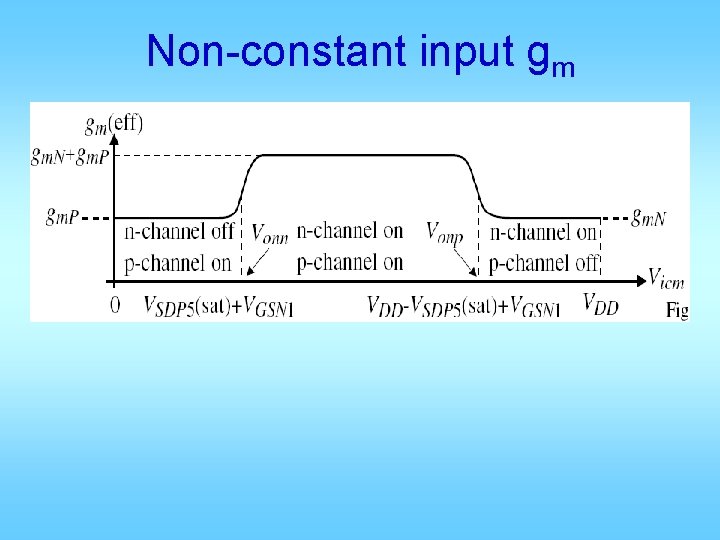

Non-constant input gm

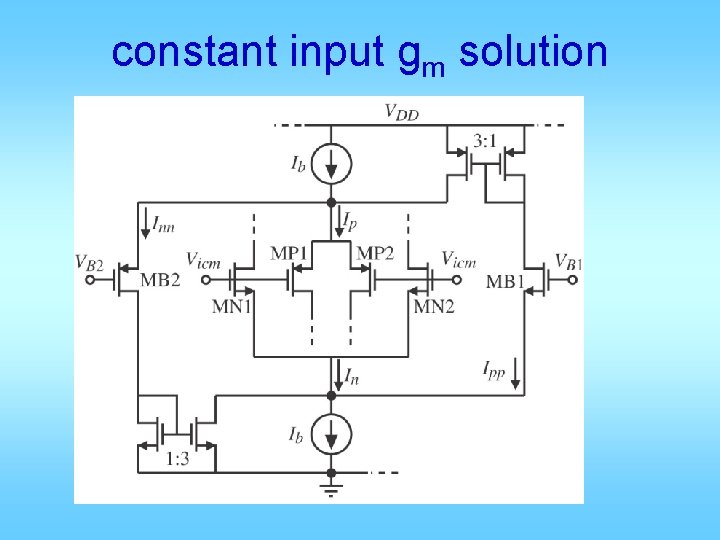

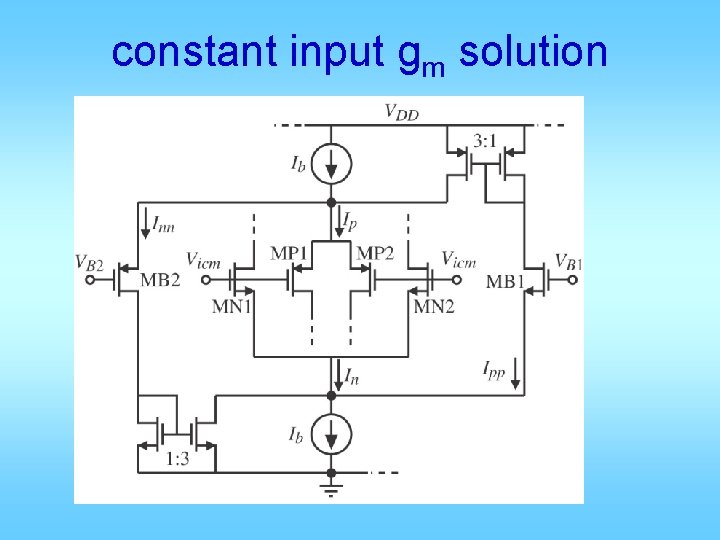

constant input gm solution

Set VB 1 = Vonn and VB 2 = Vonp

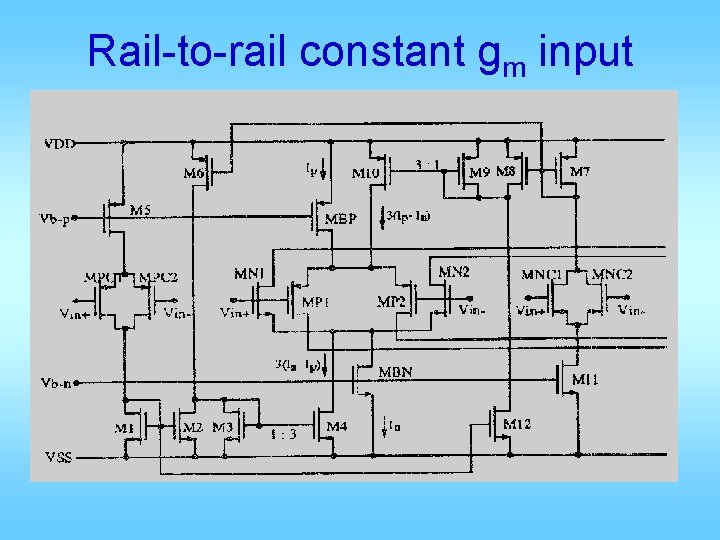

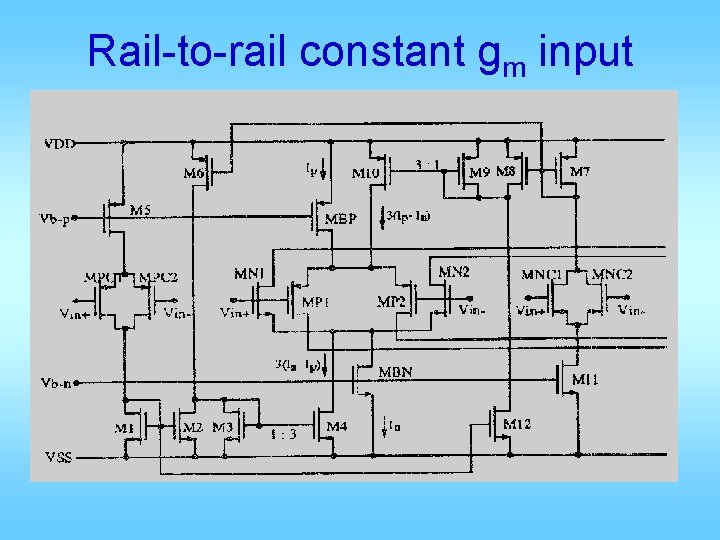

Rail-to-rail constant gm input

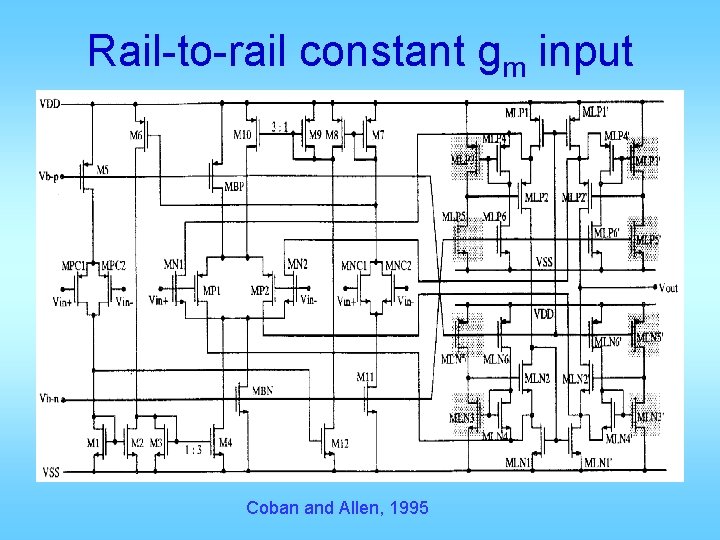

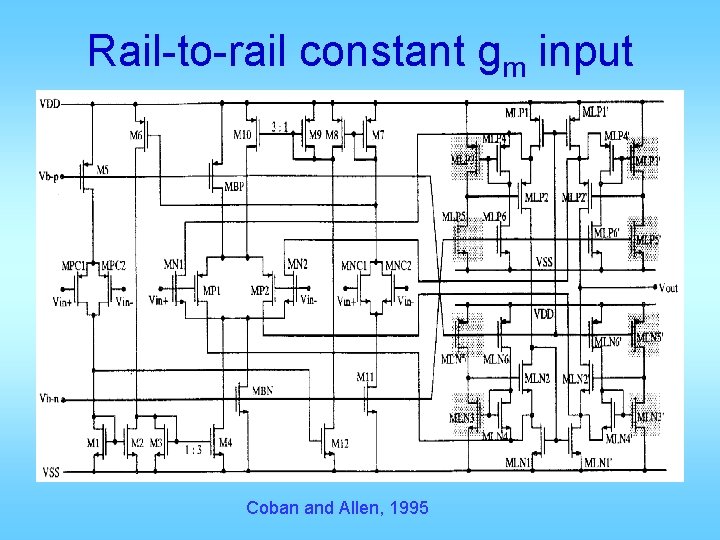

Rail-to-rail constant gm input Coban and Allen, 1995

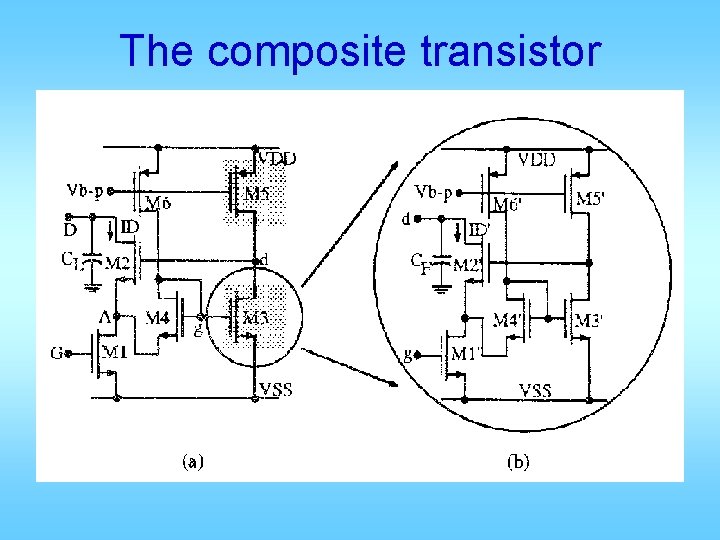

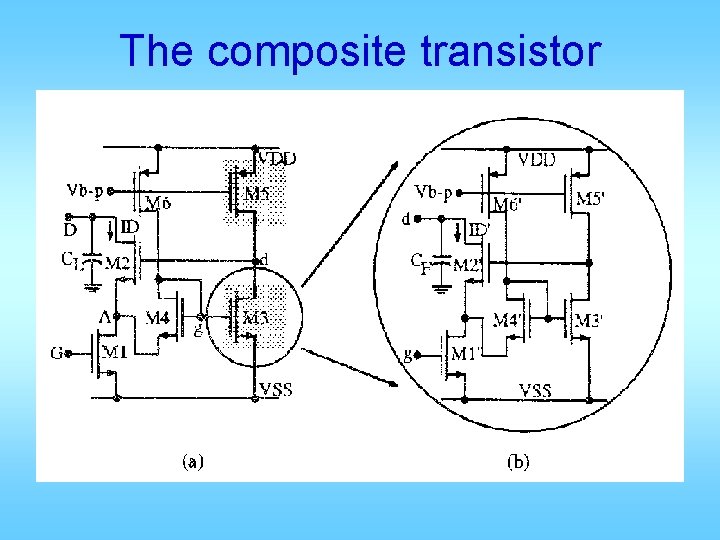

The composite transistor

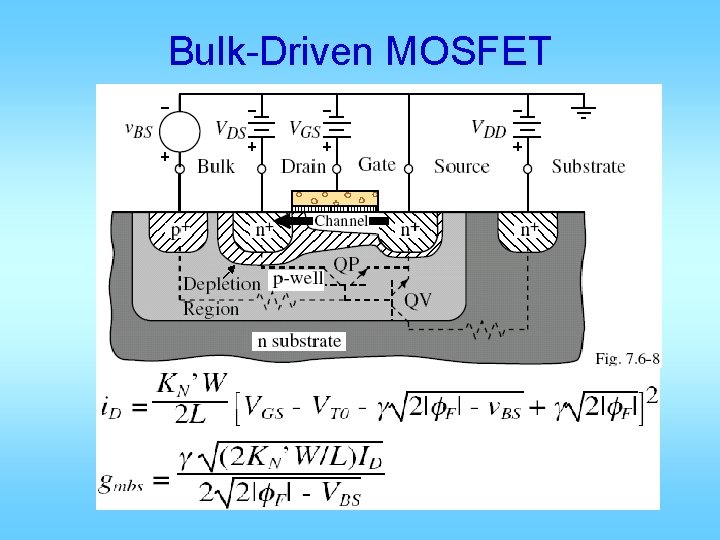

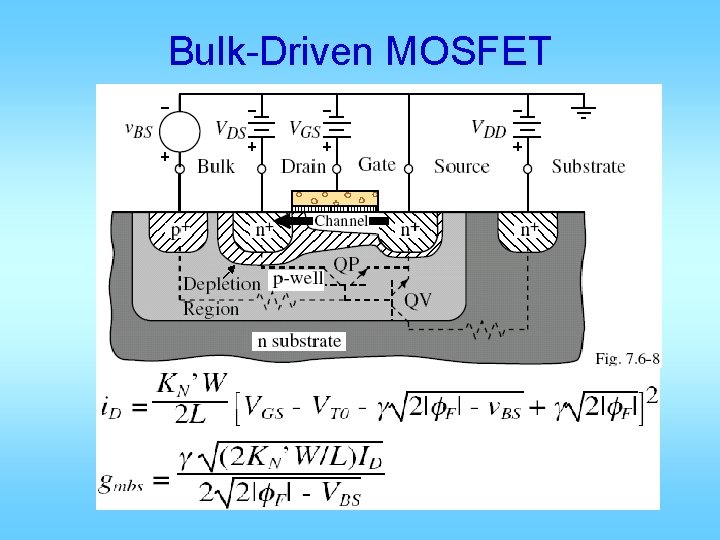

Bulk-Driven MOSFET

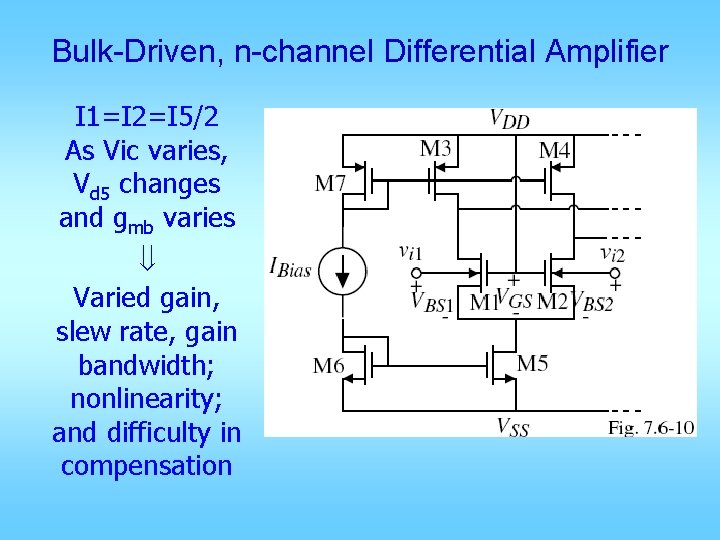

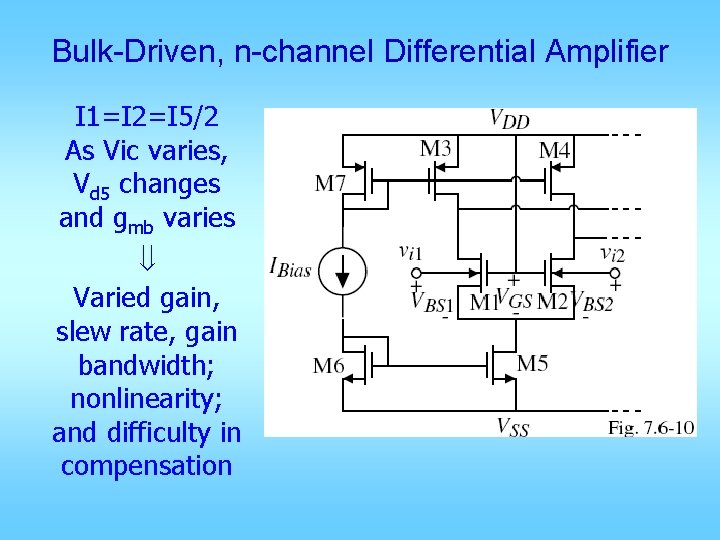

Bulk-Driven, n-channel Differential Amplifier I 1=I 2=I 5/2 As Vic varies, Vd 5 changes and gmb varies Varied gain, slew rate, gain bandwidth; nonlinearity; and difficulty in compensation

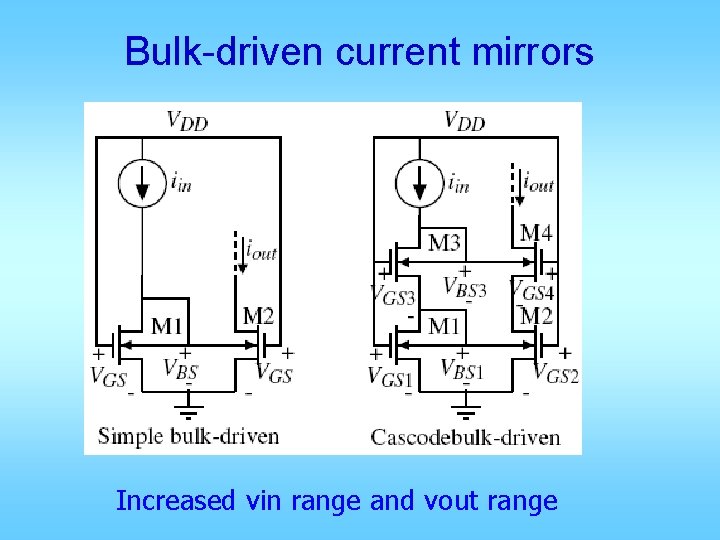

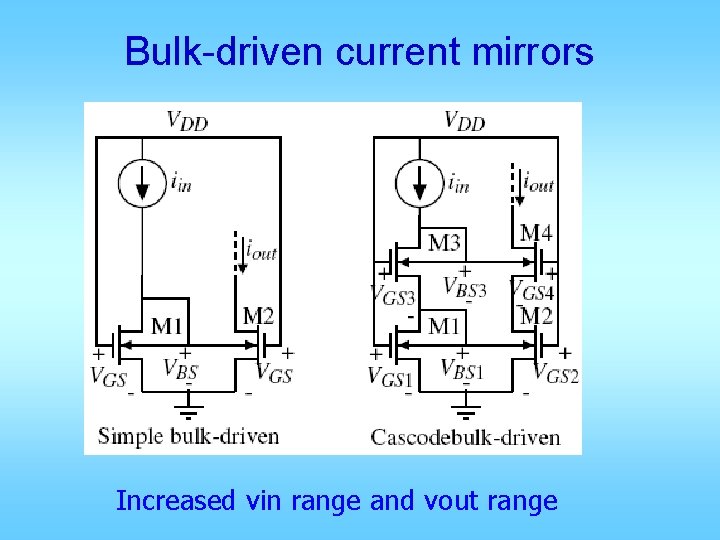

Bulk-driven current mirrors Increased vin range and vout range

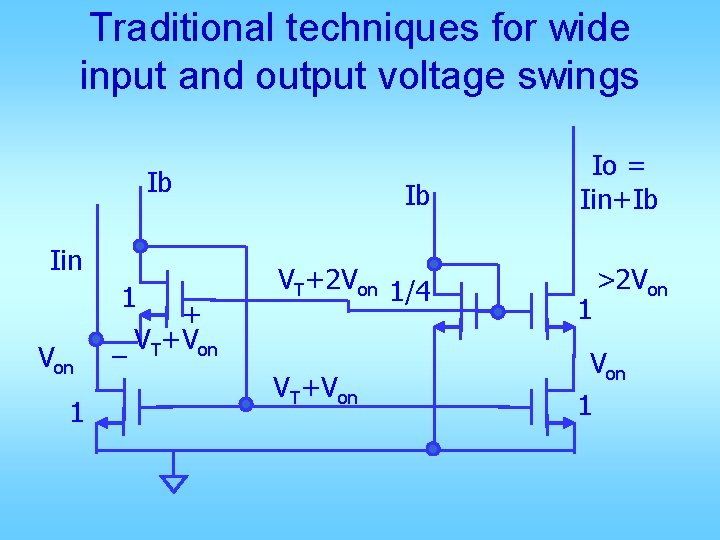

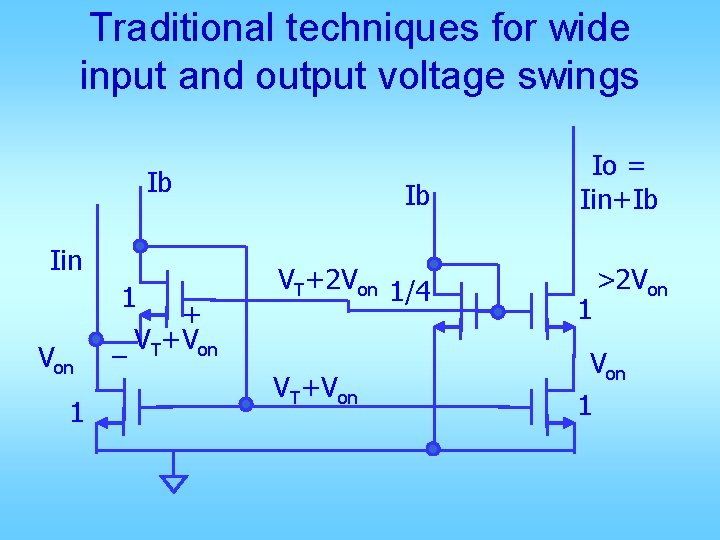

Traditional techniques for wide input and output voltage swings Ib Iin Von 1 1 + VT+Von – Ib VT+2 Von 1/4 VT+Von Io = Iin+Ib 1 >2 Von 1

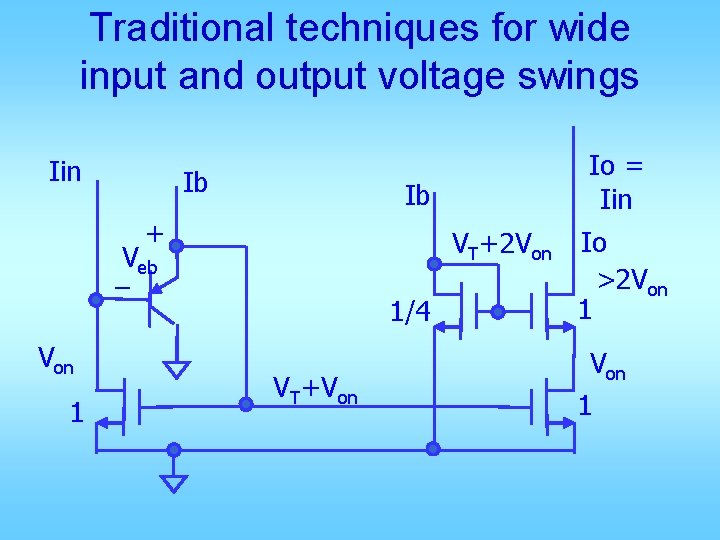

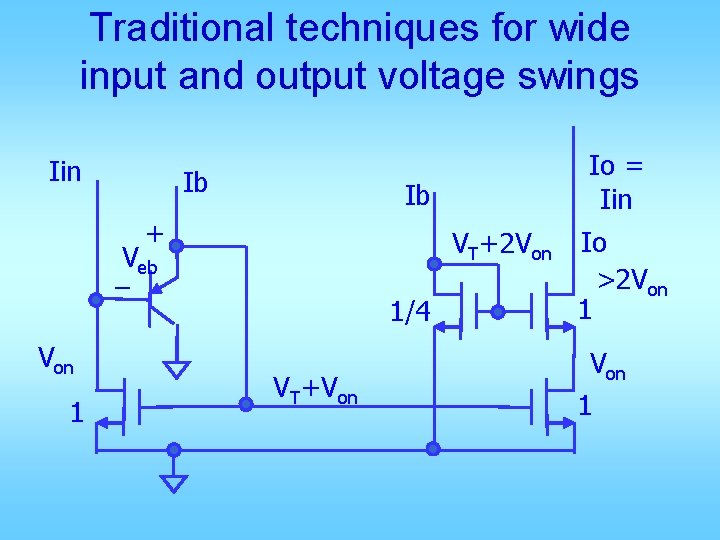

Traditional techniques for wide input and output voltage swings Iin Ib Ib + VT+2 Von Veb – Von 1 Io = Iin 1/4 VT+Von Io >2 Von 1

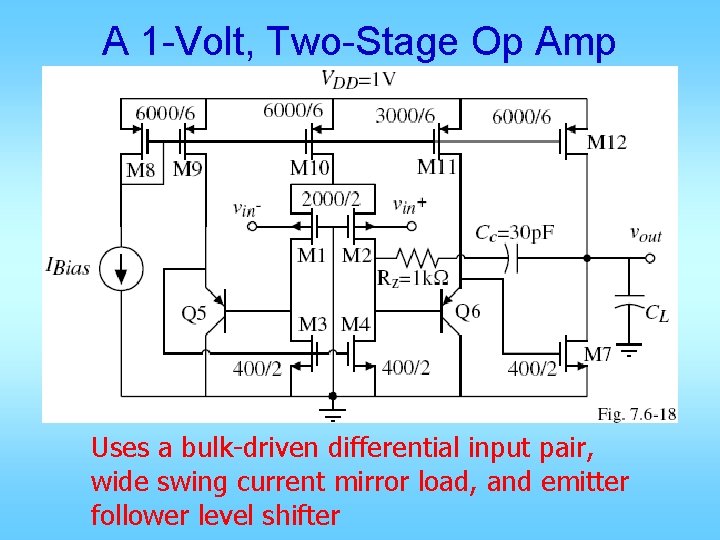

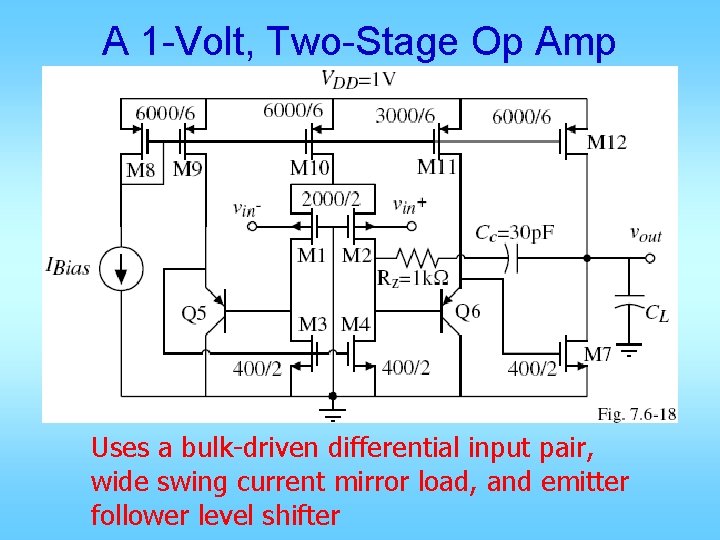

A 1 -Volt, Two-Stage Op Amp Uses a bulk-driven differential input pair, wide swing current mirror load, and emitter follower level shifter

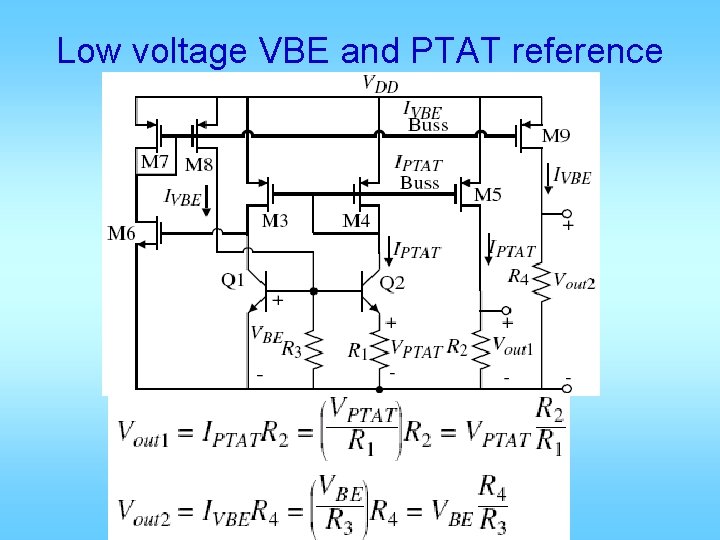

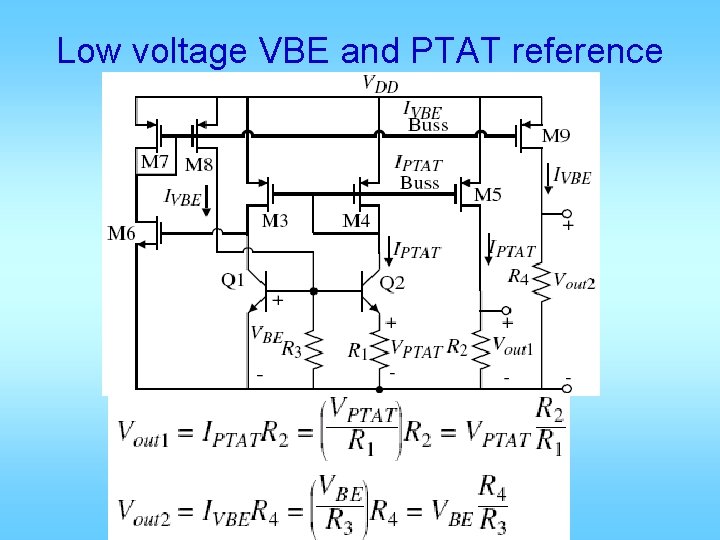

Low voltage VBE and PTAT reference

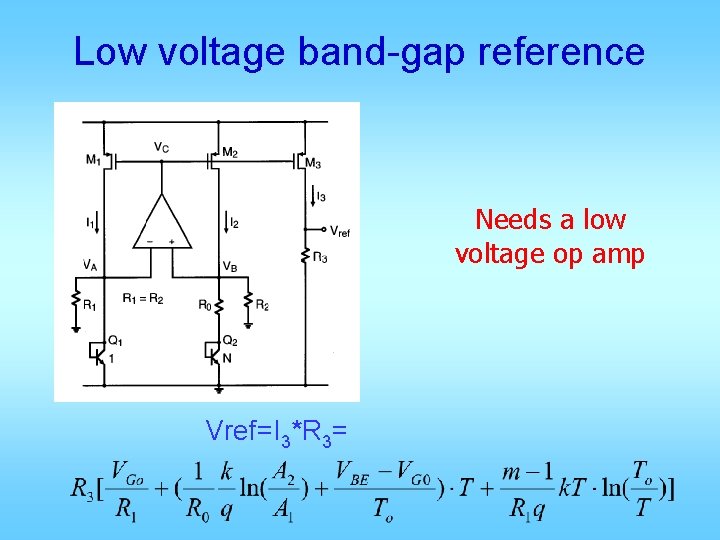

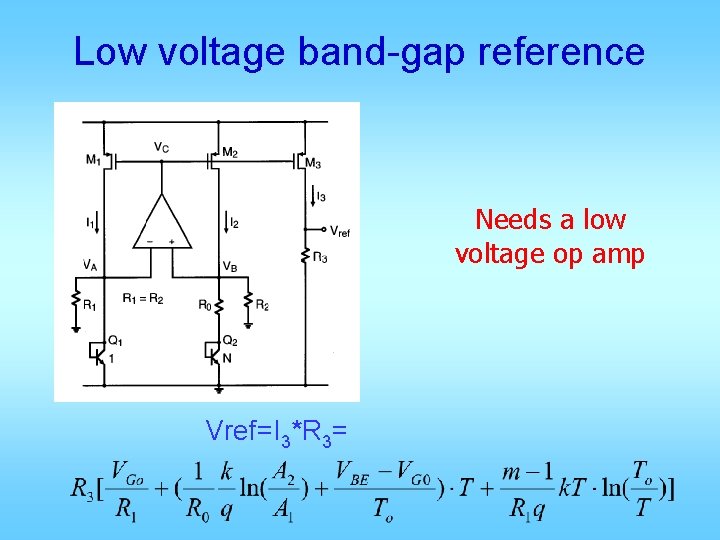

Low voltage band-gap reference Needs a low voltage op amp Vref=I 3*R 3=

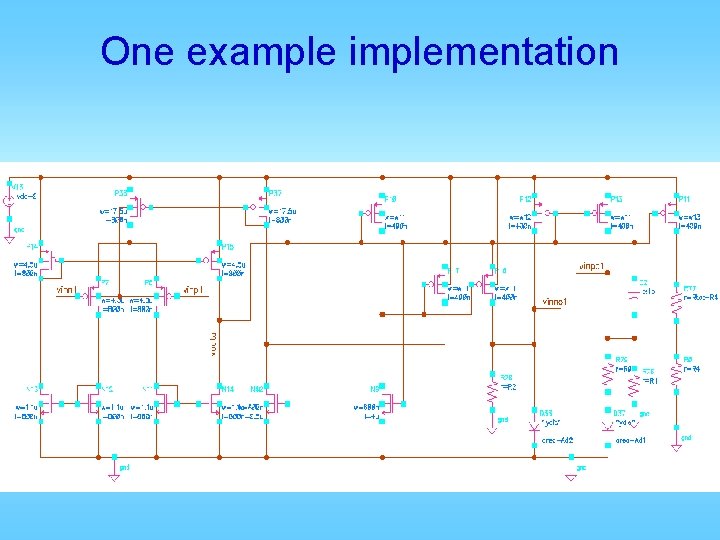

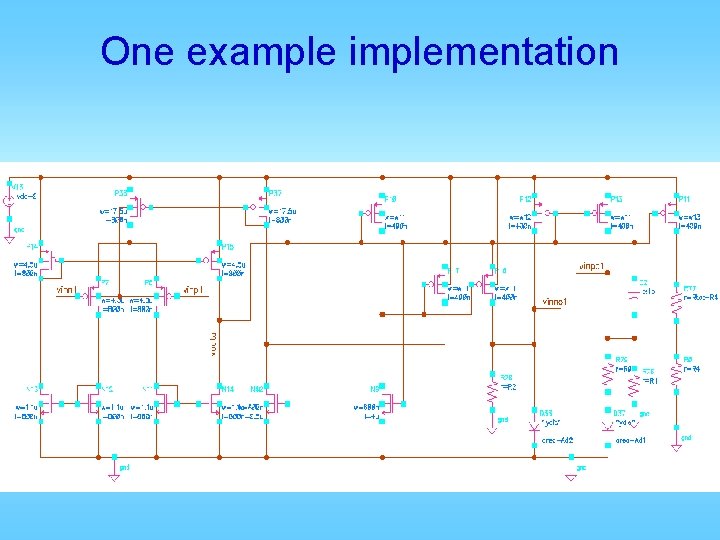

One example implementation

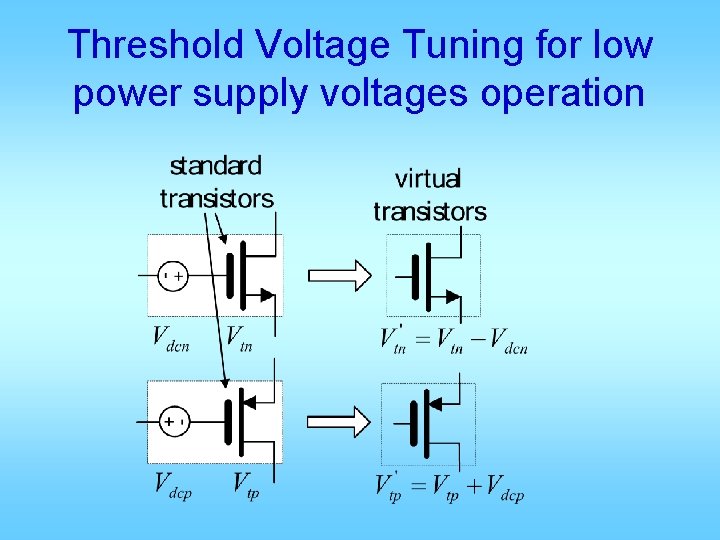

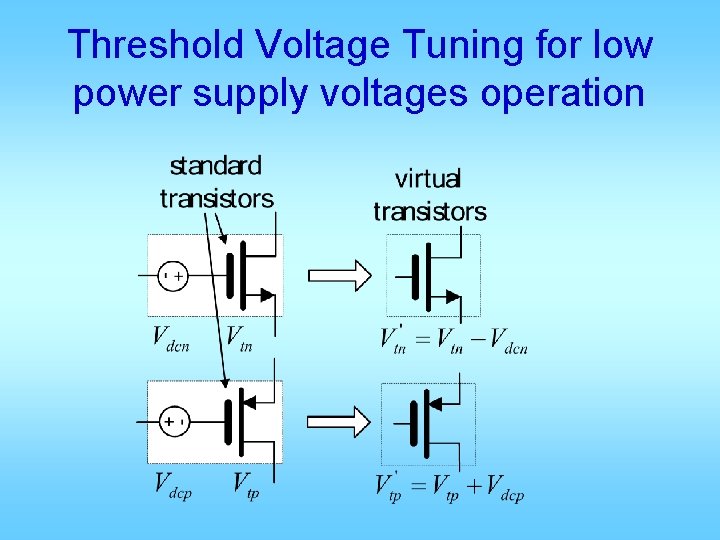

Threshold Voltage Tuning for low power supply voltages operation

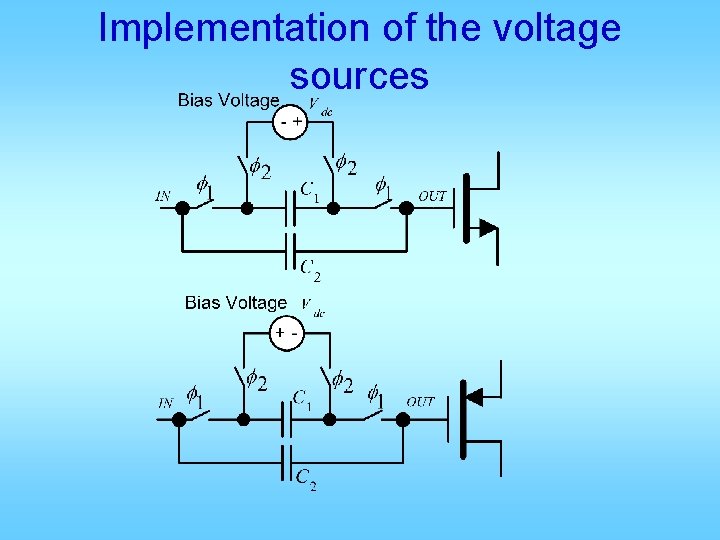

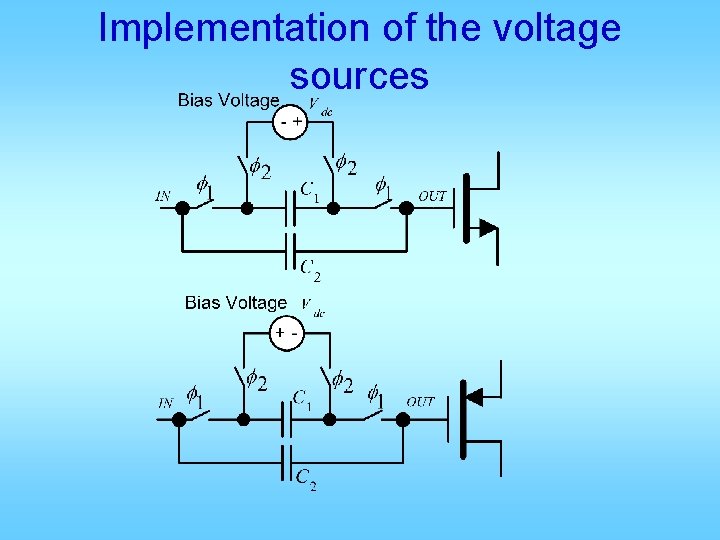

Implementation of the voltage sources

A low voltage Op Amp core

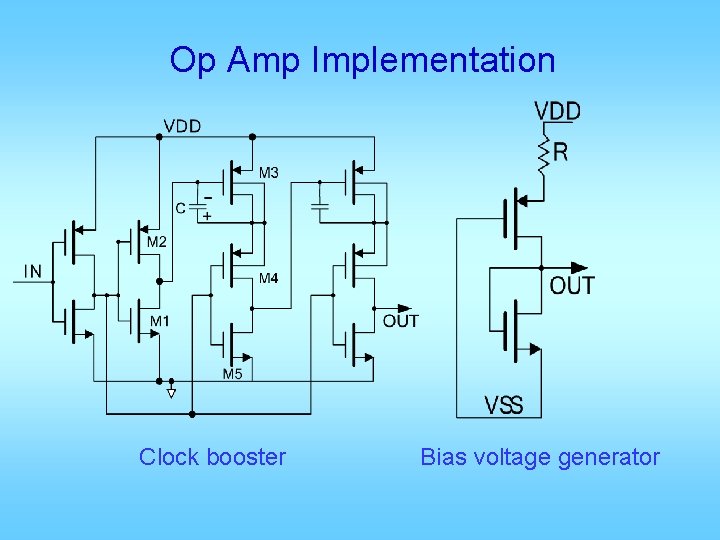

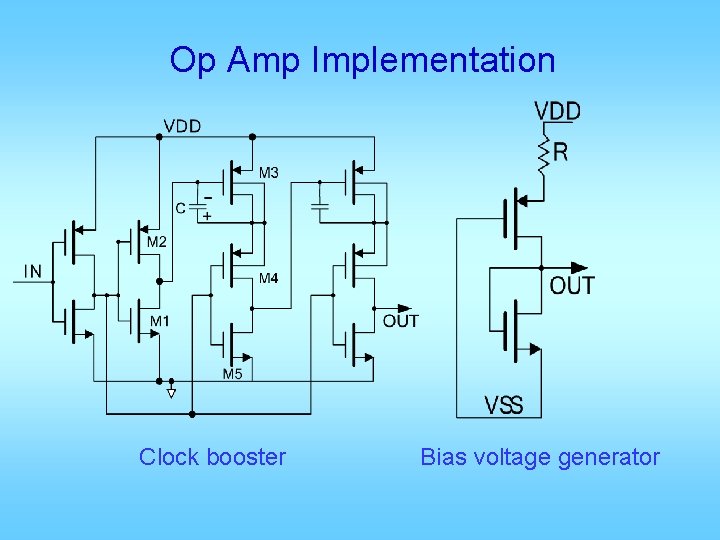

Op Amp Implementation Clock booster Bias voltage generator

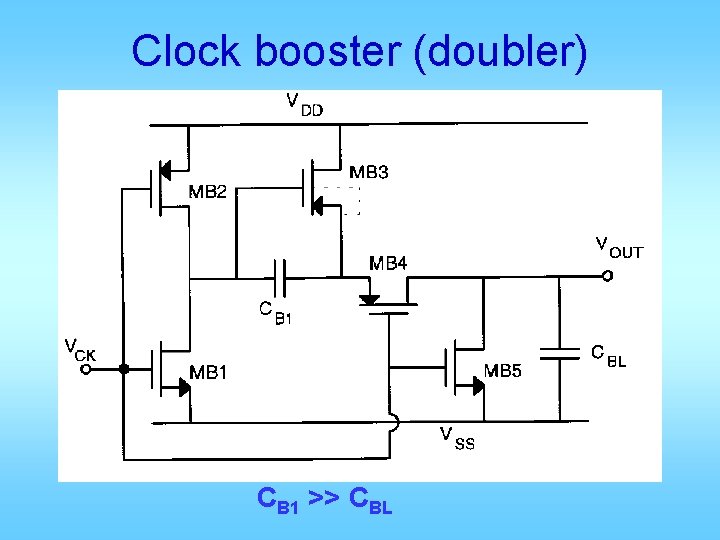

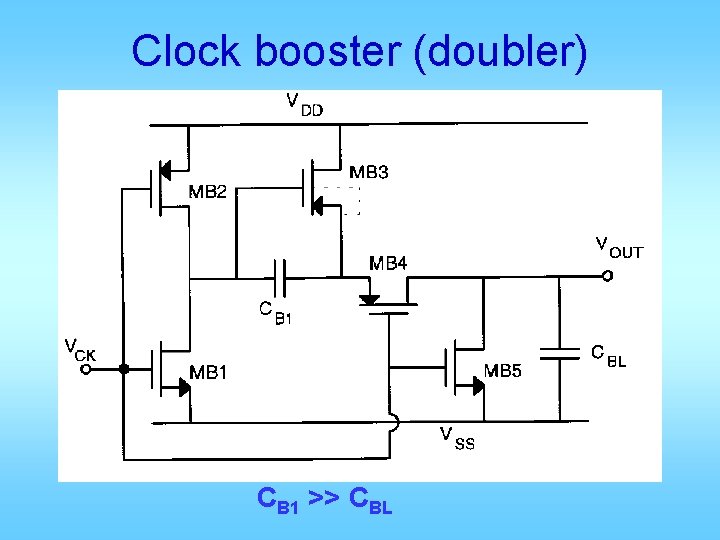

Clock booster (doubler) CB 1 >> CBL

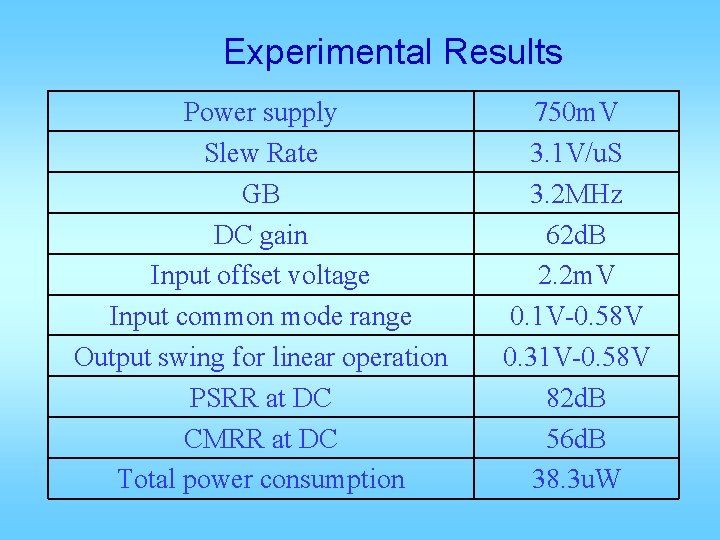

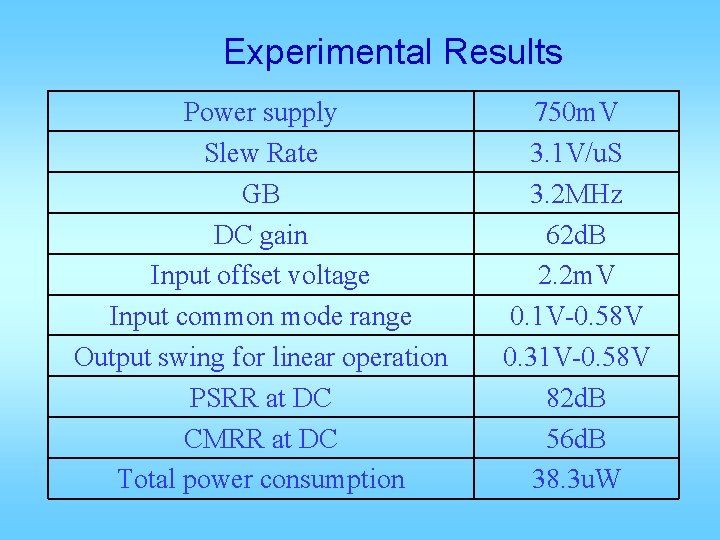

Experimental Results Power supply Slew Rate GB DC gain Input offset voltage Input common mode range Output swing for linear operation PSRR at DC CMRR at DC Total power consumption 750 m. V 3. 1 V/u. S 3. 2 MHz 62 d. B 2. 2 m. V 0. 1 V-0. 58 V 0. 31 V-0. 58 V 82 d. B 56 d. B 38. 3 u. W

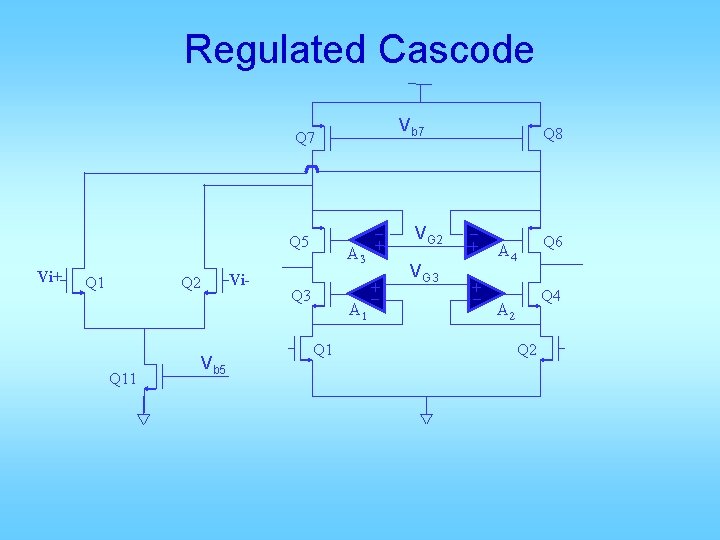

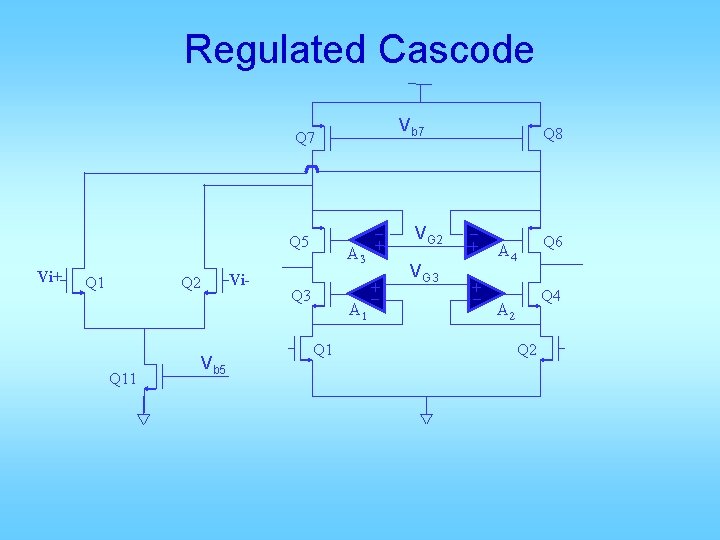

Regulated Cascode Vb 7 Vi+ Q 1 Q 2 Q 11 Vb 5 Vi- A 3 Q 3 A 1 Q 1 + - Q 5 + - VG 2 VG 3 Q 8 + - Q 7 + - Q 6 A 4 Q 4 A 2 Q 2

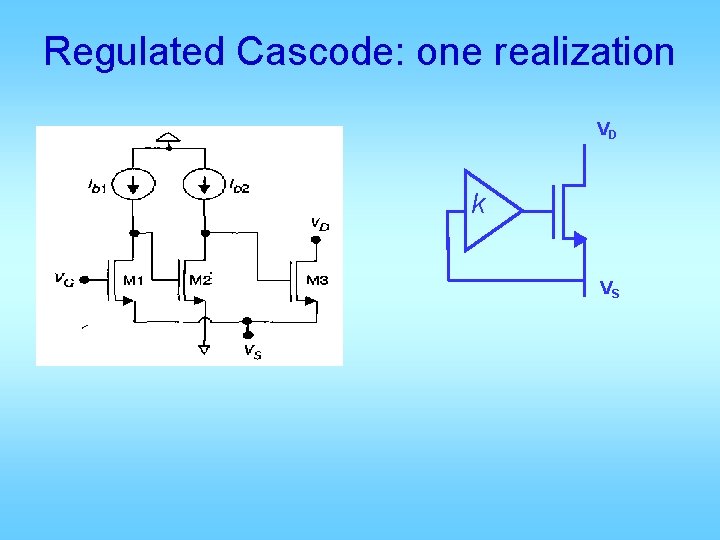

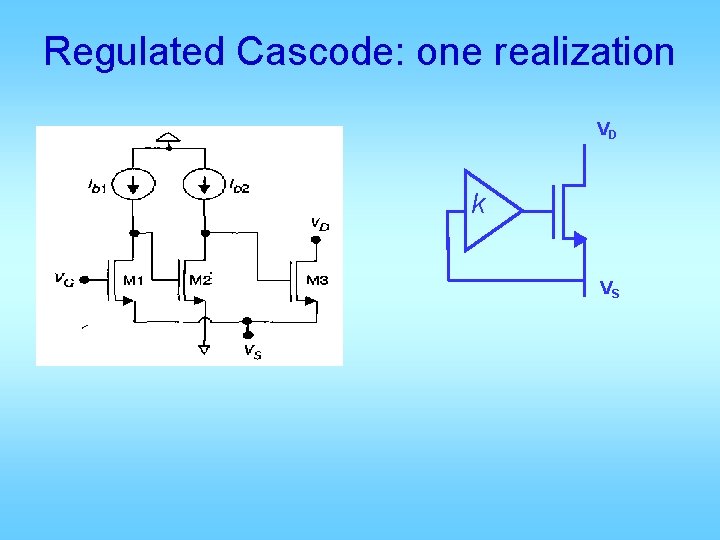

Regulated Cascode: one realization VD k VS

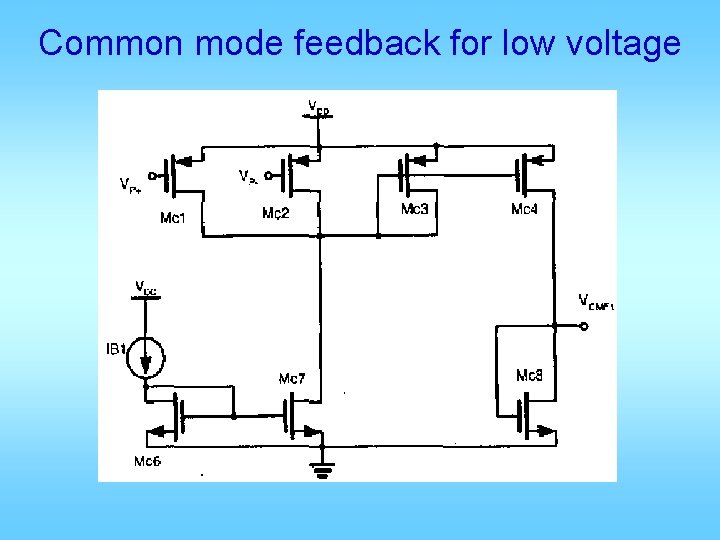

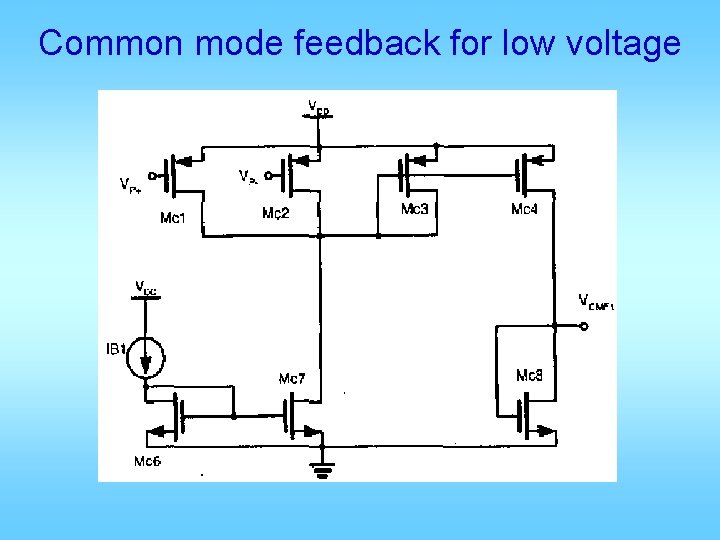

Common mode feedback for low voltage

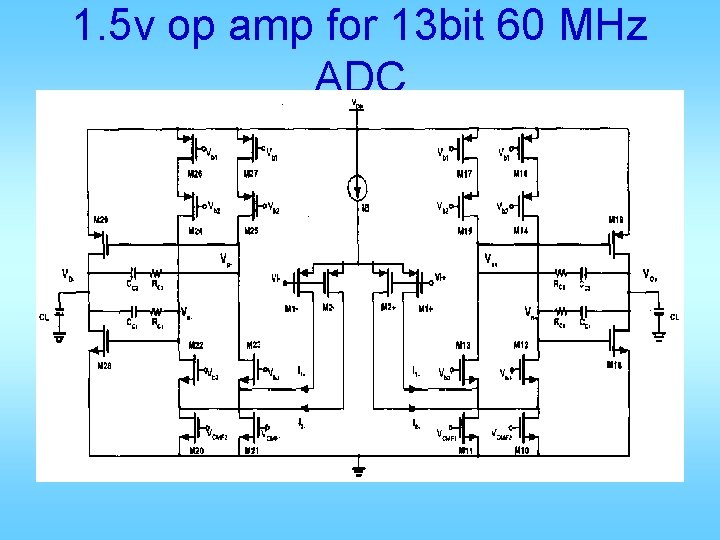

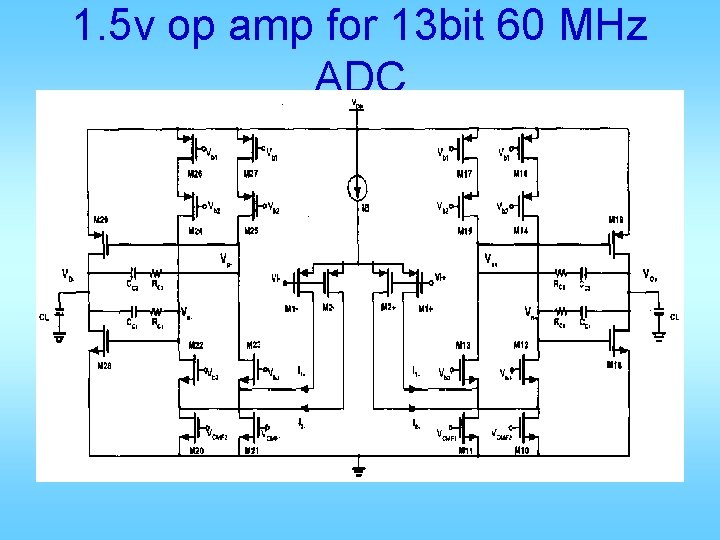

1. 5 v op amp for 13 bit 60 MHz ADC

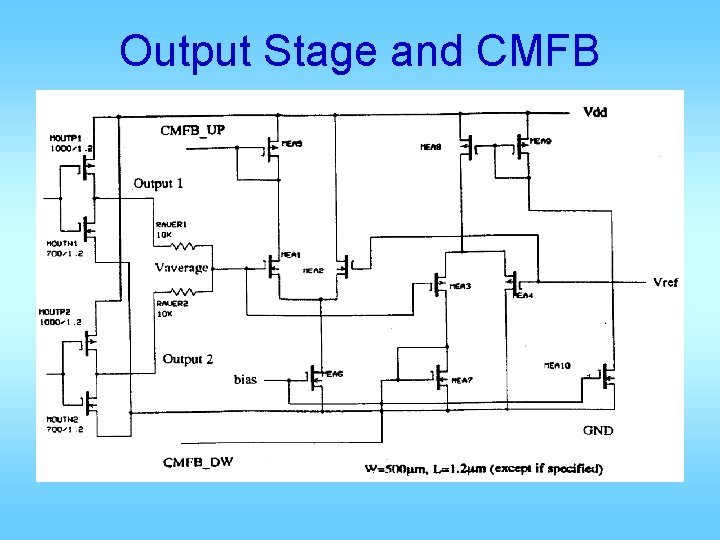

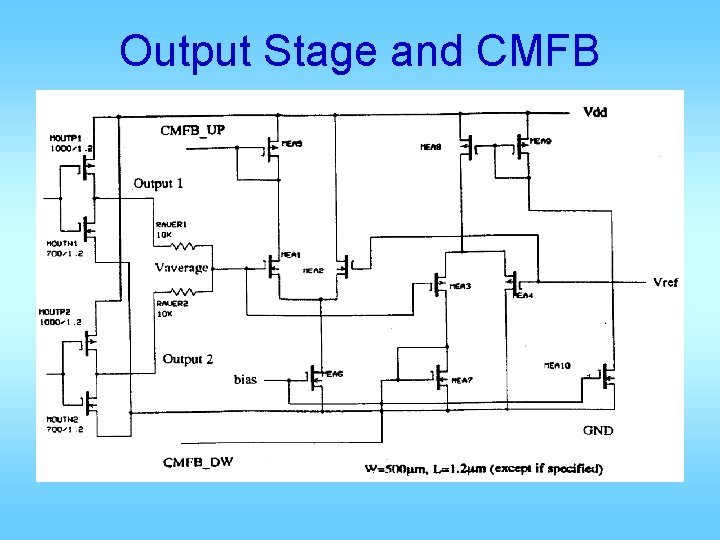

Output Stage and CMFB

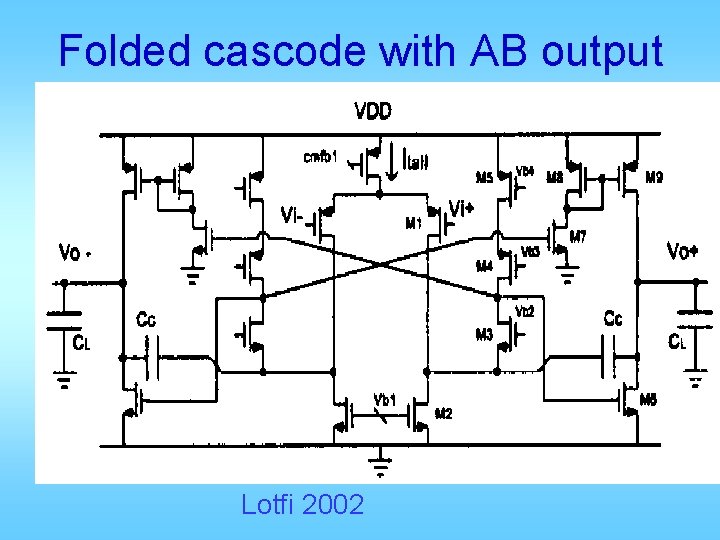

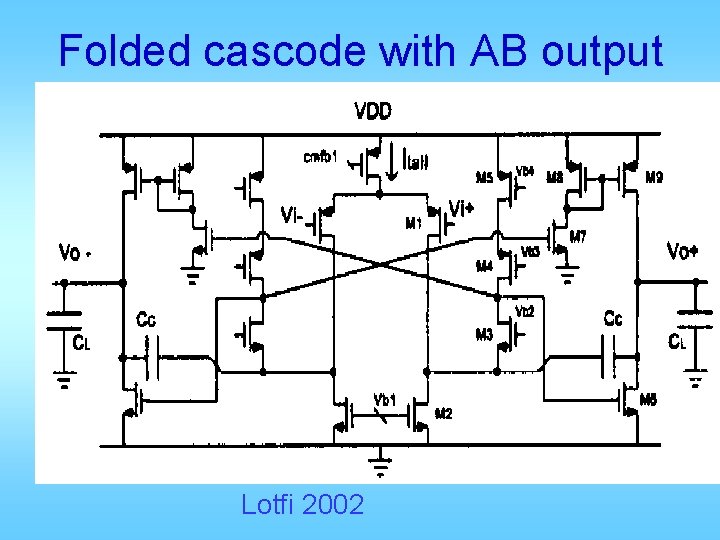

Folded cascode with AB output Lotfi 2002

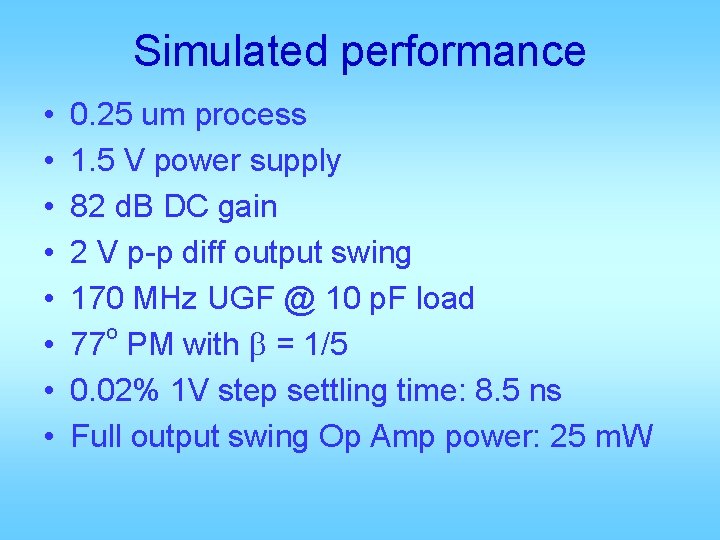

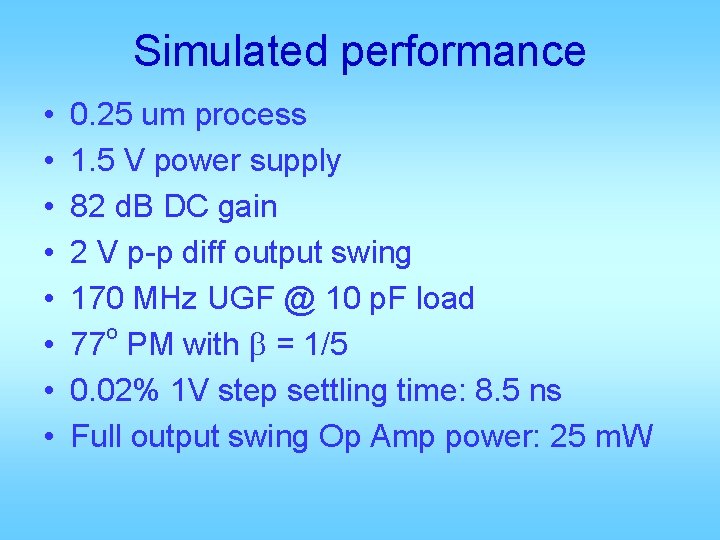

Simulated performance • • 0. 25 um process 1. 5 V power supply 82 d. B DC gain 2 V p-p diff output swing 170 MHz UGF @ 10 p. F load o 77 PM with b = 1/5 0. 02% 1 V step settling time: 8. 5 ns Full output swing Op Amp power: 25 m. W

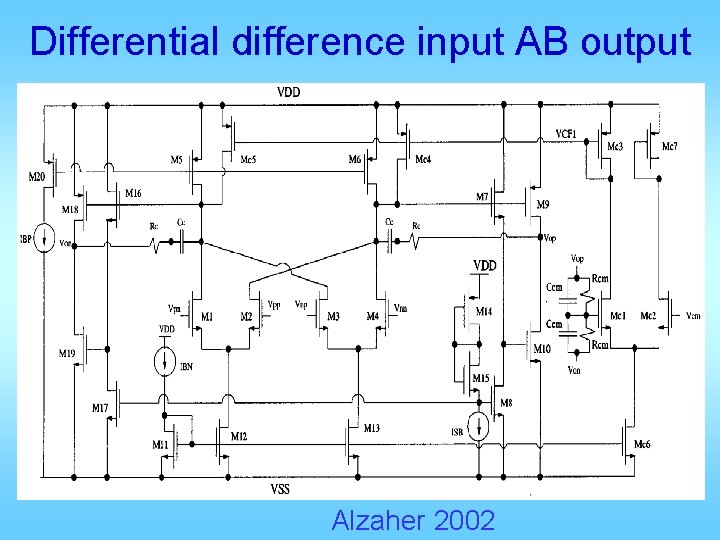

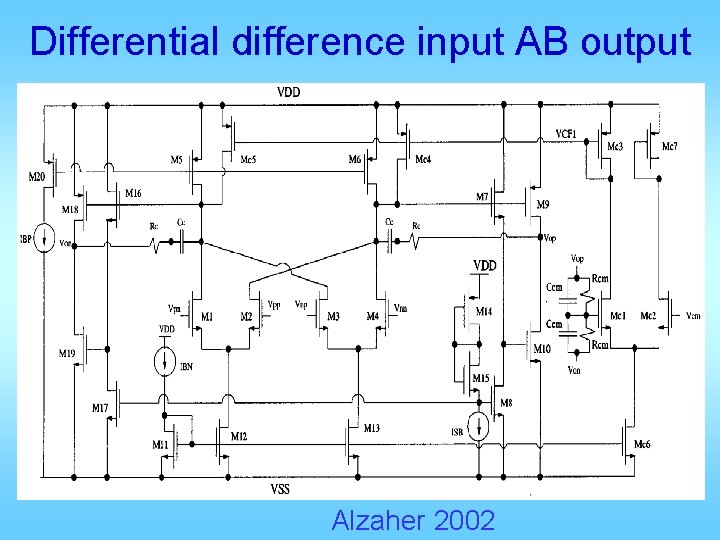

Differential difference input AB output Alzaher 2002

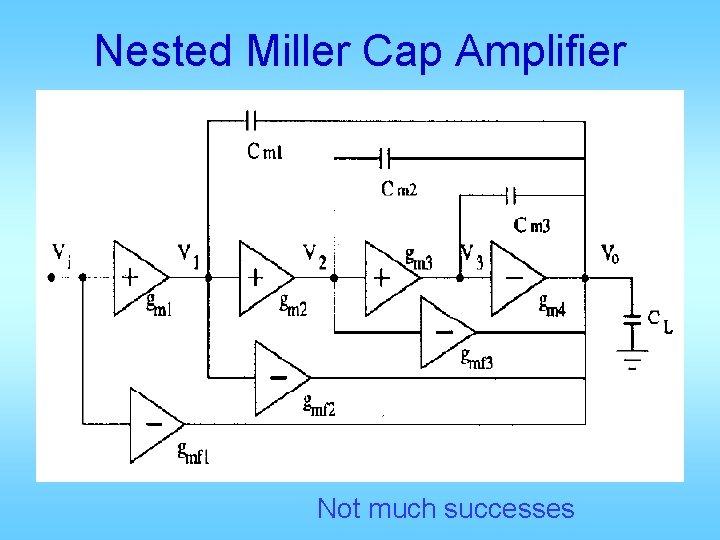

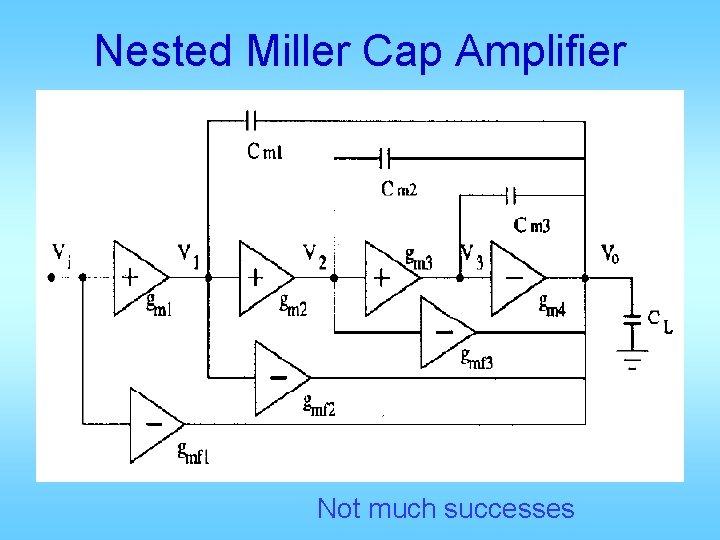

Nested Miller Cap Amplifier Not much successes

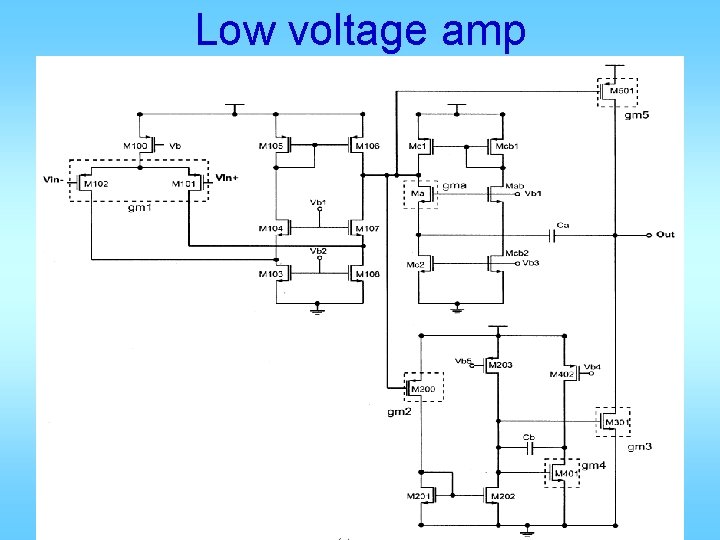

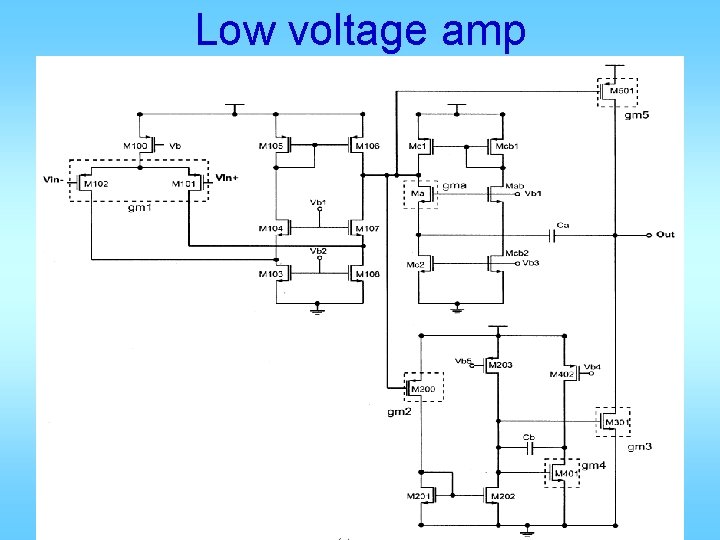

Low voltage amp

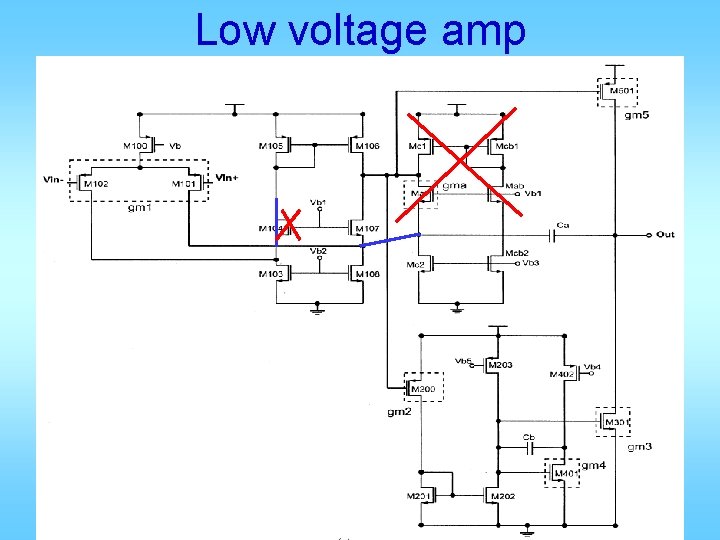

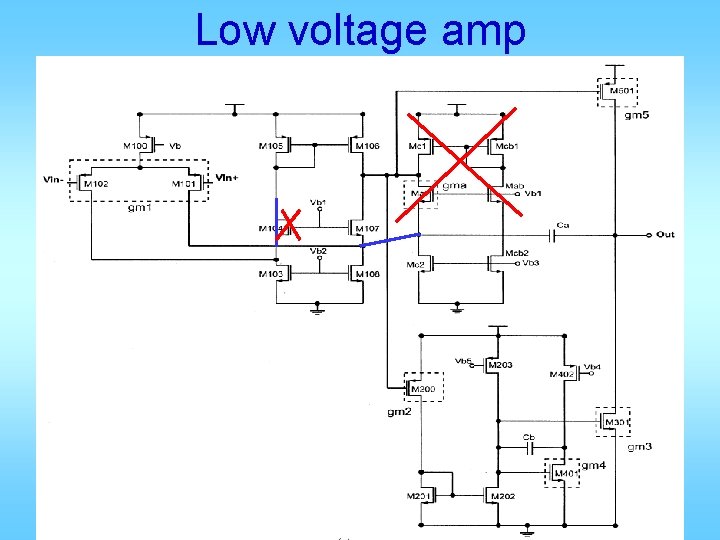

Low voltage amp

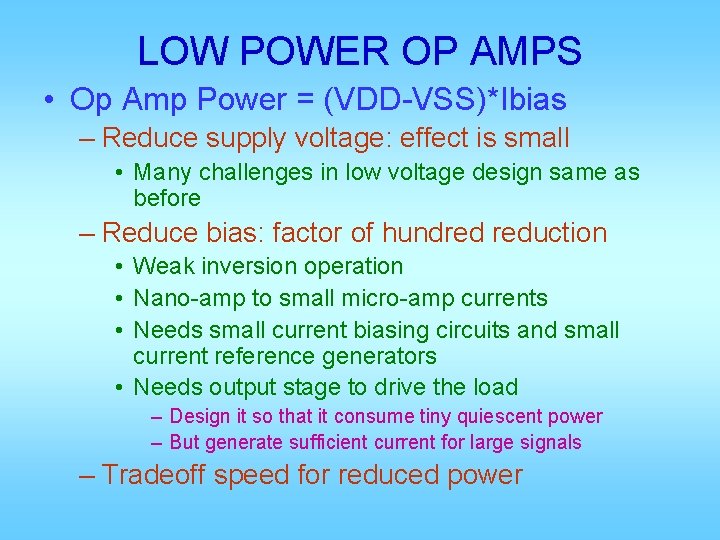

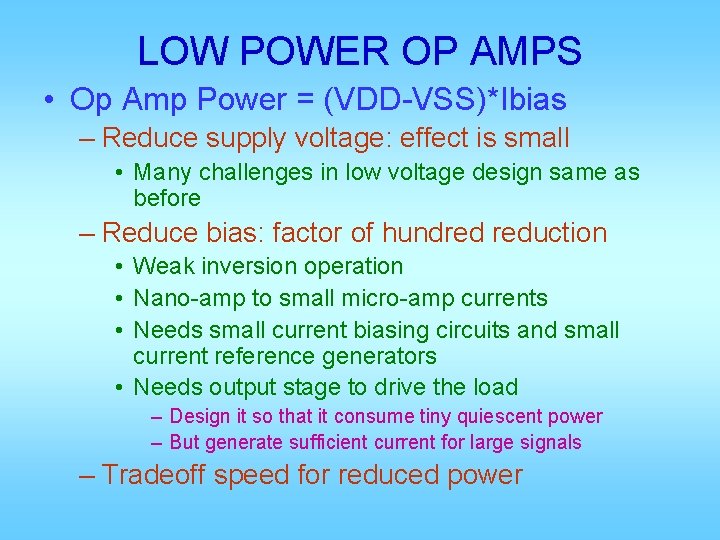

LOW POWER OP AMPS • Op Amp Power = (VDD-VSS)*Ibias – Reduce supply voltage: effect is small • Many challenges in low voltage design same as before – Reduce bias: factor of hundred reduction • Weak inversion operation • Nano-amp to small micro-amp currents • Needs small current biasing circuits and small current reference generators • Needs output stage to drive the load – Design it so that it consume tiny quiescent power – But generate sufficient current for large signals – Tradeoff speed for reduced power

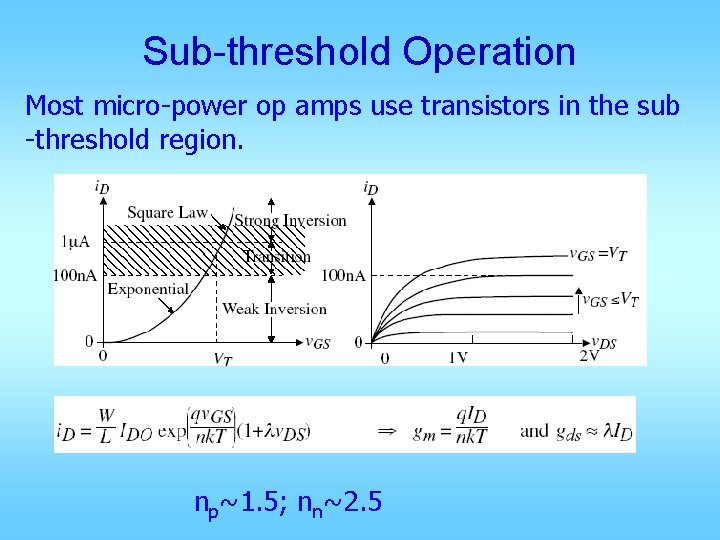

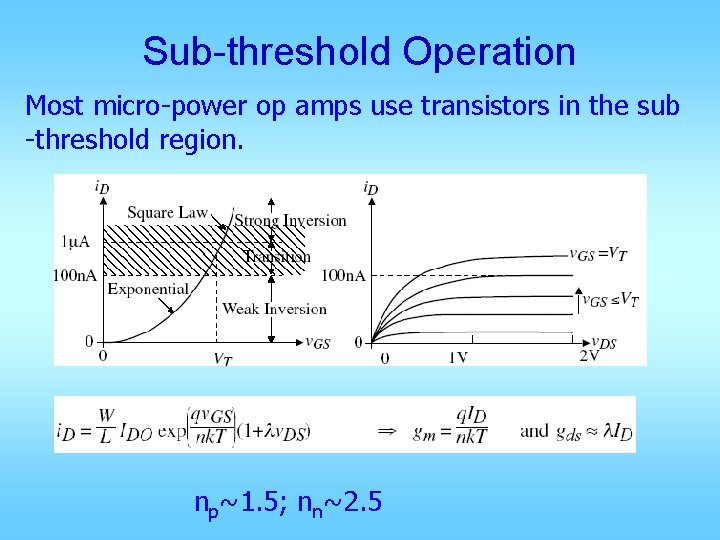

Sub-threshold Operation Most micro-power op amps use transistors in the sub -threshold region. np~1. 5; nn~2. 5

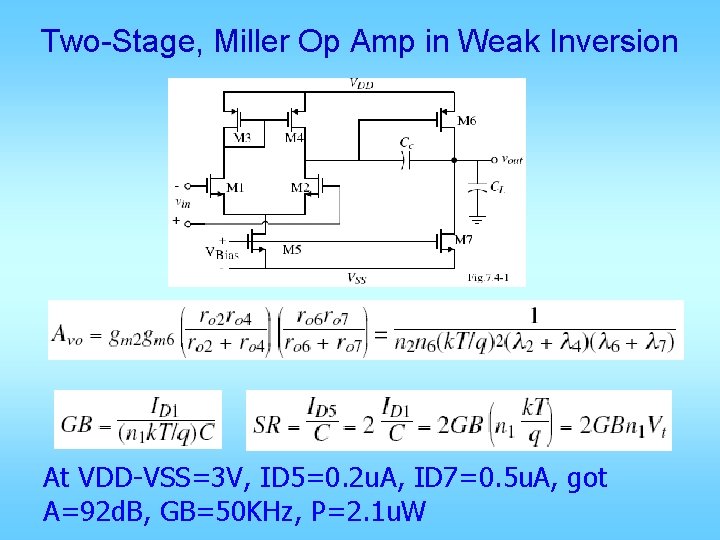

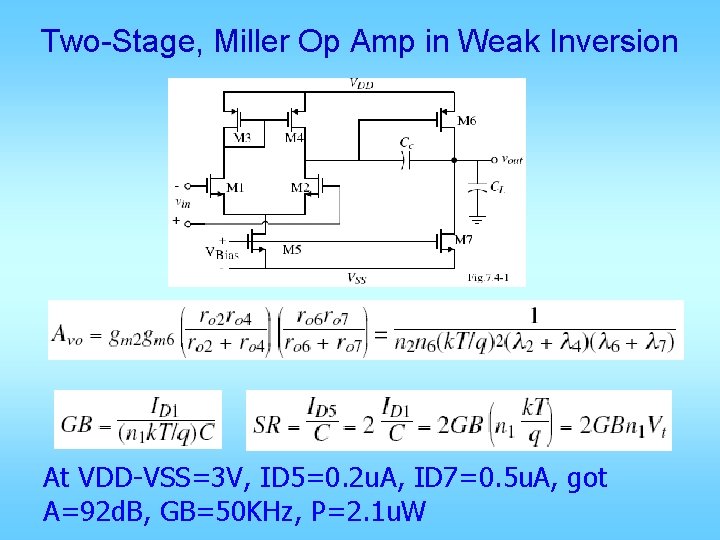

Two-Stage, Miller Op Amp in Weak Inversion At VDD-VSS=3 V, ID 5=0. 2 u. A, ID 7=0. 5 u. A, got A=92 d. B, GB=50 KHz, P=2. 1 u. W

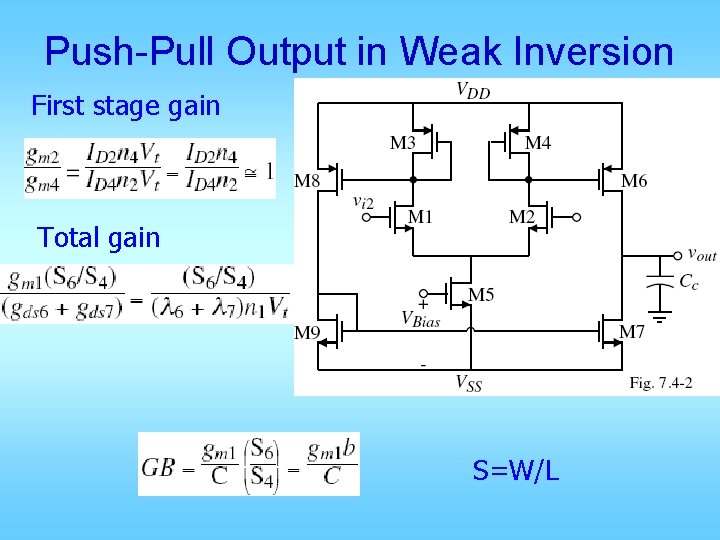

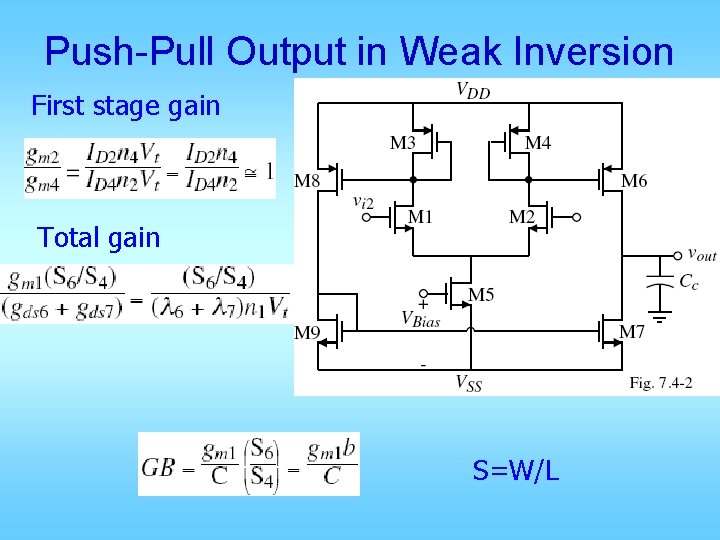

Push-Pull Output in Weak Inversion First stage gain Total gain S=W/L

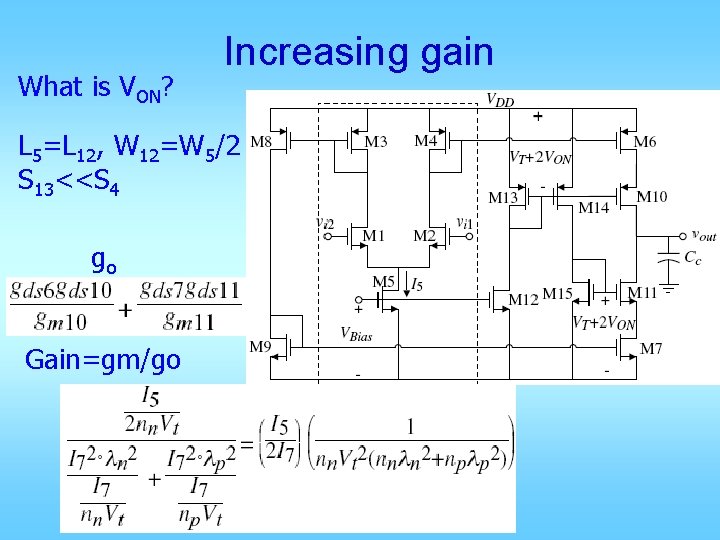

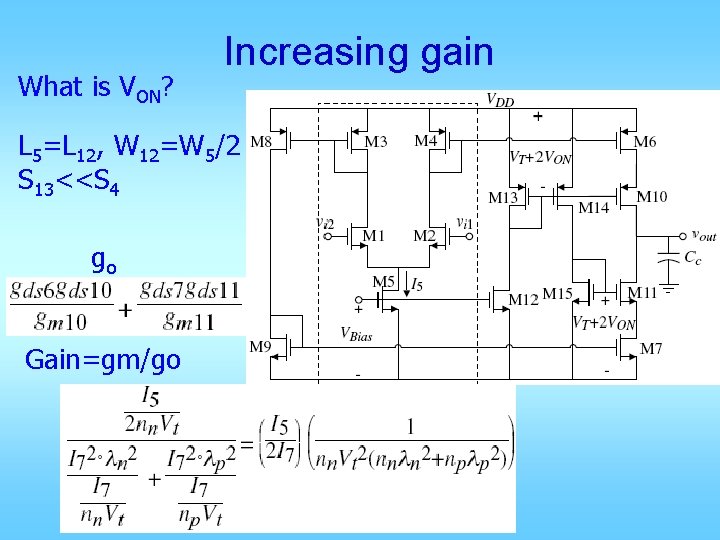

What is VON? Increasing gain L 5=L 12, W 12=W 5/2 S 13<<S 4 go Gain=gm/go

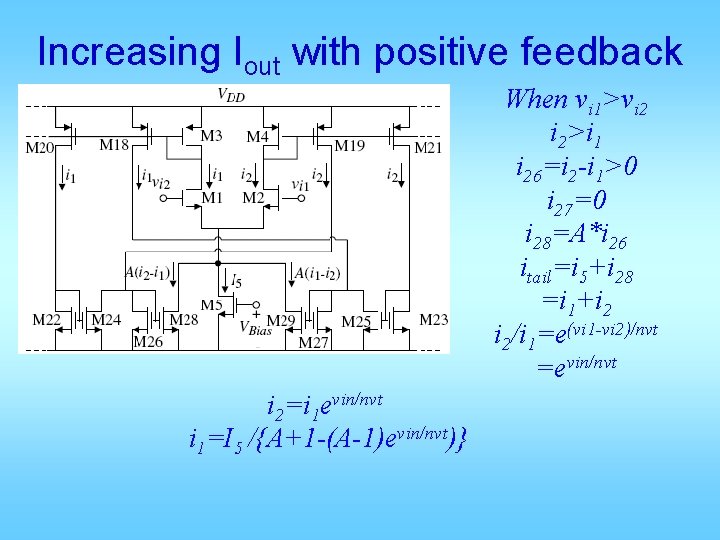

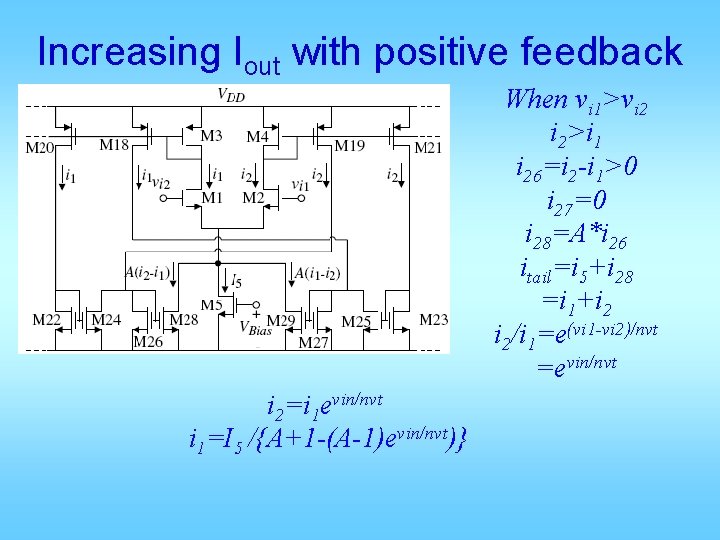

Increasing Iout with positive feedback When vi 1>vi 2 i 2>i 1 i 26=i 2 -i 1>0 i 27=0 i 28=A*i 26 itail=i 5+i 28 =i 1+i 2 i 2/i 1=e(vi 1 -vi 2)/nvt =evin/nvt i 2=i 1 evin/nvt i 1=I 5 /{A+1 -(A-1)evin/nvt)}

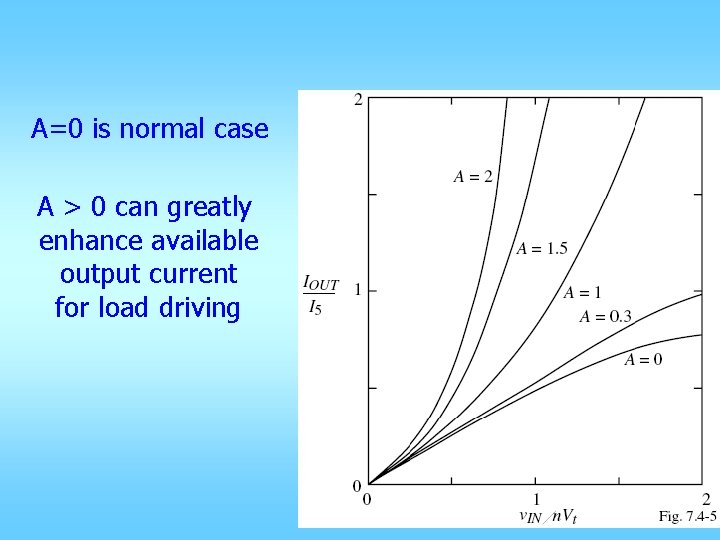

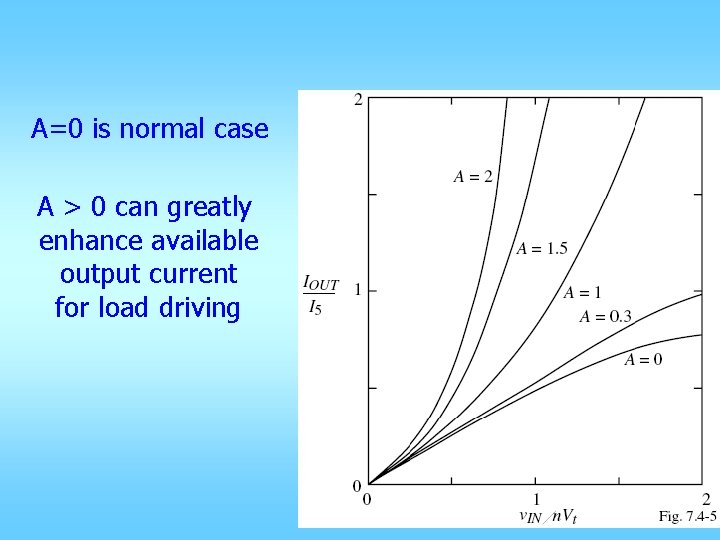

A=0 is normal case A > 0 can greatly enhance available output current for load driving

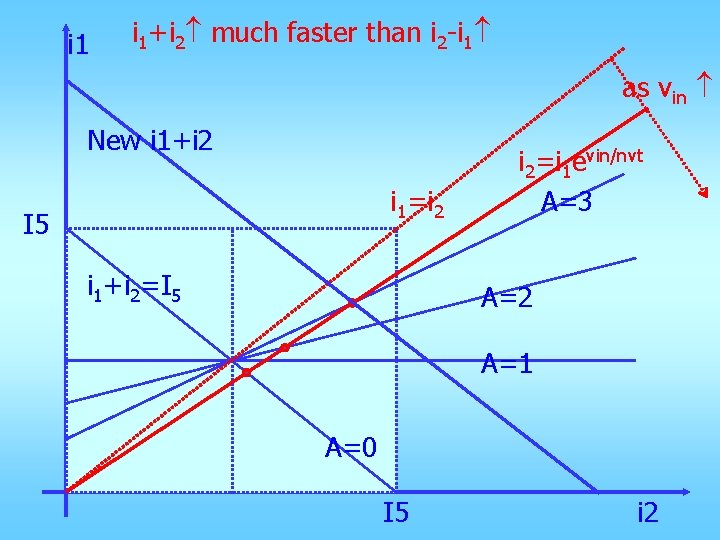

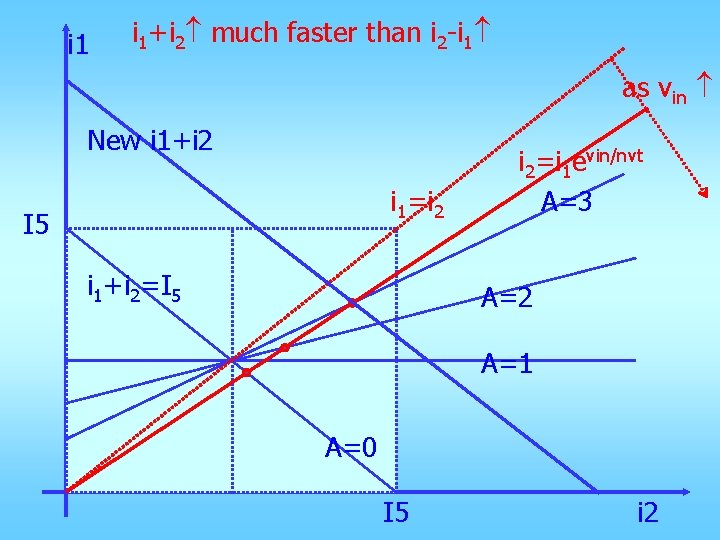

i 1 i 1+i 2 much faster than i 2 -i 1 as vin New i 1+i 2 i 1=i 2 I 5 i 1+i 2=I 5 i 2=i 1 evin/nvt A=3 A=2 A=1 A=0 I 5 i 2