Elektronski fakultet u Niu Katedra za Elektroniku MENTOR

- Slides: 88

Elektronski fakultet u Nišu Katedra za Elektroniku

MENTOR prof. dr Mile K. Stojčev STUDENTI: Bojan Antonijević 3212, Dragan Županjac 3028 PREDMET: MIKROPROCESORSKA TEHNIKA TEMA: INDUSTRIJSKA TOKEN RING RAČUNARSKA MREŽA

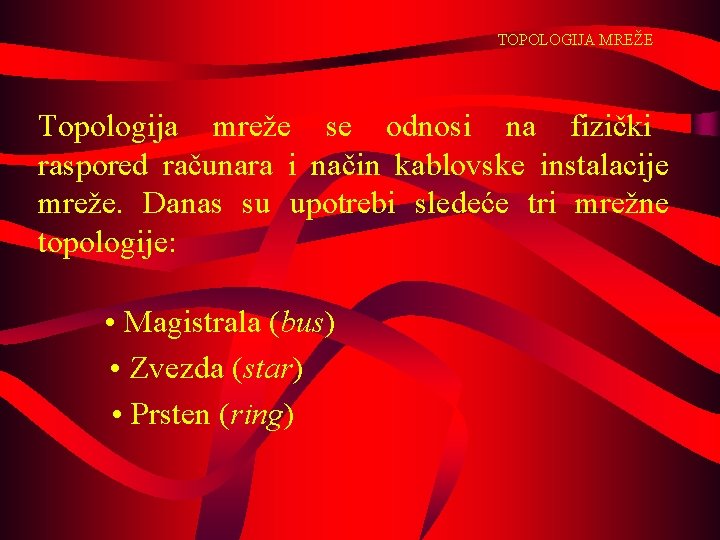

TOPOLOGIJA MREŽE

TOPOLOGIJA MREŽE Topologija mreže se odnosi na fizički raspored računara i način kablovske instalacije mreže. Danas su upotrebi sledeće tri mrežne topologije: • Magistrala (bus) • Zvezda (star) • Prsten (ring)

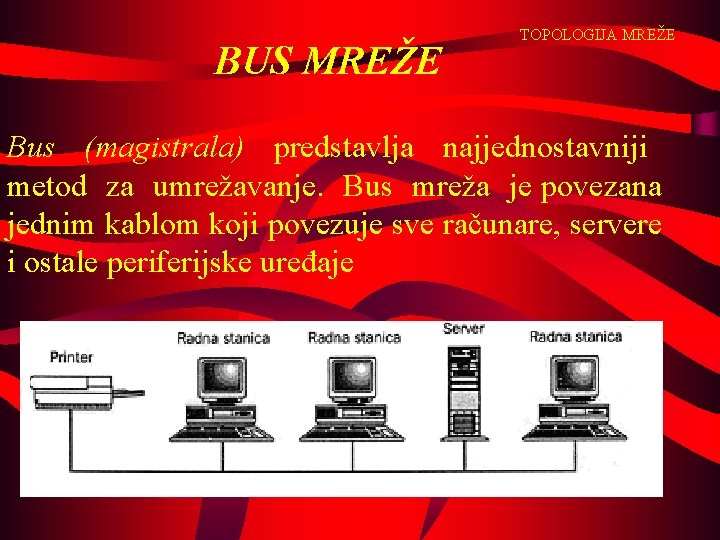

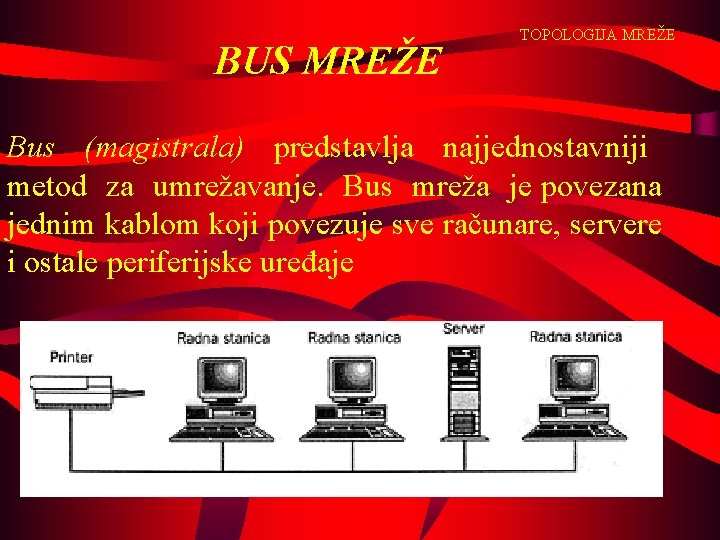

BUS MREŽE TOPOLOGIJA MREŽE Bus (magistrala) predstavlja najjednostavniji metod za umrežavanje. Bus mreža je povezana jednim kablom koji povezuje sve računare, servere i ostale periferijske uređaje

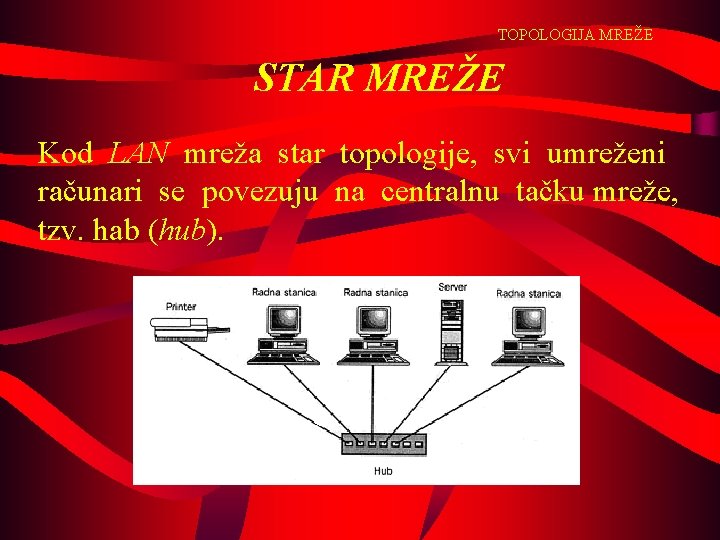

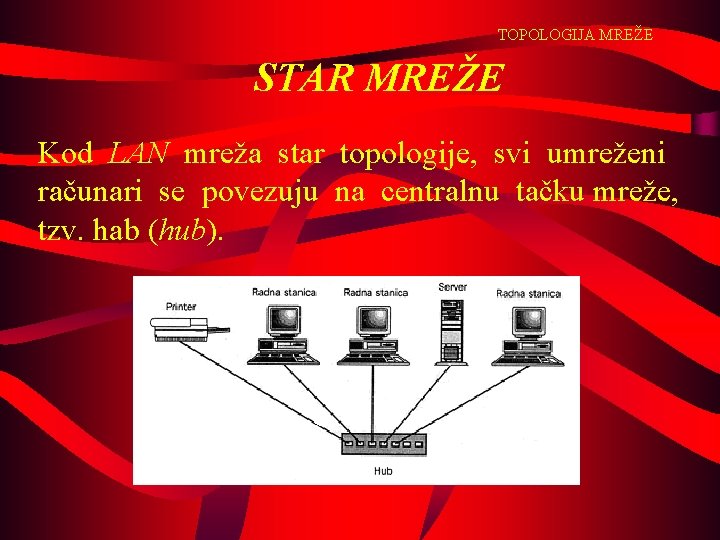

TOPOLOGIJA MREŽE STAR MREŽE Kod LAN mreža star topologije, svi umreženi računari se povezuju na centralnu tačku mreže, tzv. hab (hub).

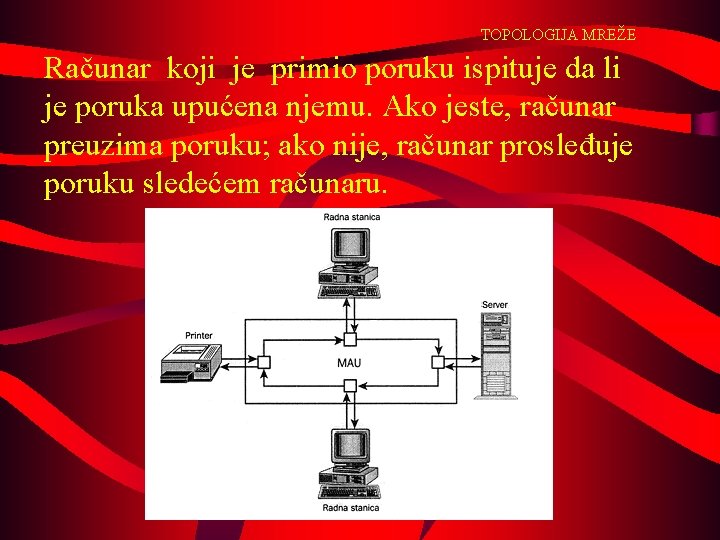

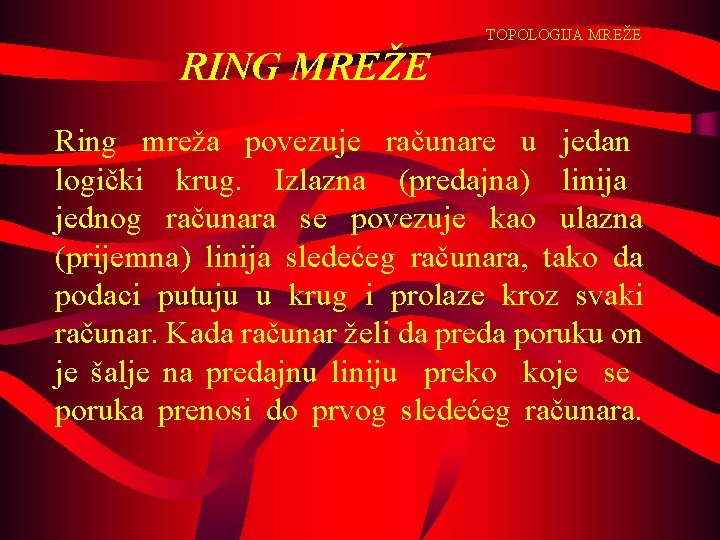

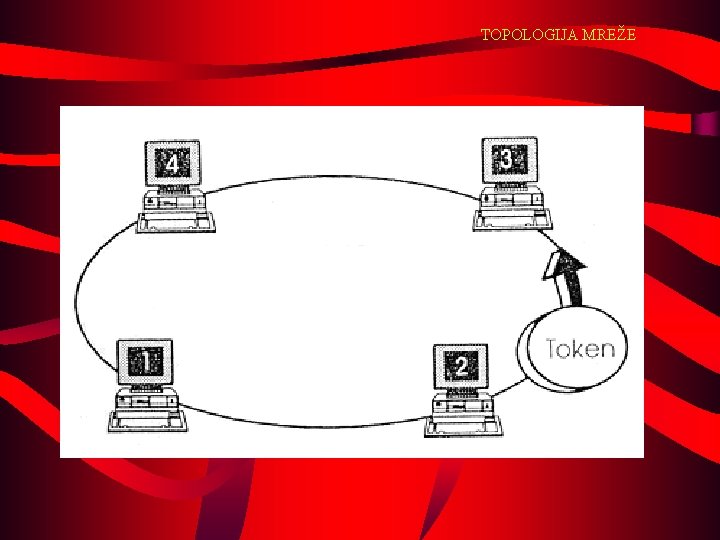

TOPOLOGIJA MREŽE RING MREŽE Ring mreža povezuje računare u jedan logički krug. Izlazna (predajna) linija jednog računara se povezuje kao ulazna (prijemna) linija sledećeg računara, tako da podaci putuju u krug i prolaze kroz svaki računar. Kada računar želi da preda poruku on je šalje na predajnu liniju preko koje se poruka prenosi do prvog sledećeg računara.

TOPOLOGIJA MREŽE Računar koji je primio poruku ispituje da li je poruka upućena njemu. Ako jeste, računar preuzima poruku; ako nije, računar prosleđuje poruku sledećem računaru.

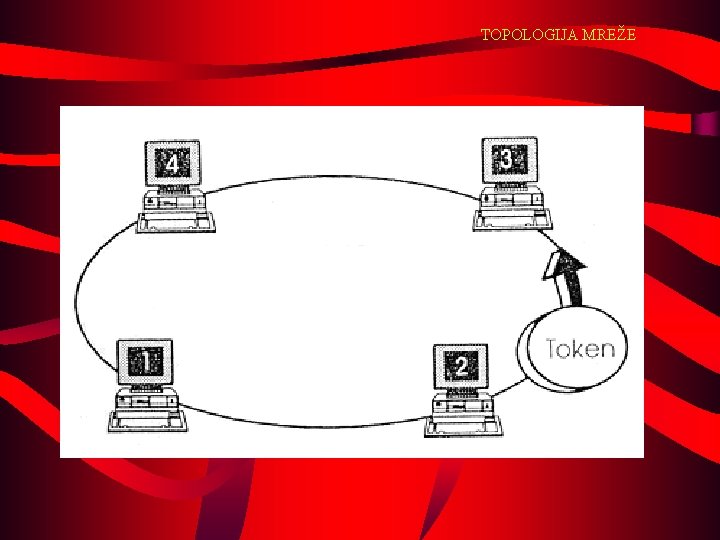

TOPOLOGIJA MREŽE Za prenos podataka kroz ring mrežu koristi se metod pristupa token passing. Token je oblik kontrolne poruke koja se neprekidno, sukcesivno prenosi od jednog do drugog računara sve dok ne stigne do računara koji želi da koristi mrežu. Na mreži uvek postoji samo jedan token. Ukoliko neki računar želi da preda poruku, a token je već u upotrebi, on mora sačekati da dobije token. Samo računar koji je primio token može da šalje podatke na mrežu

TOPOLOGIJA MREŽE

TOPOLOGIJA MREŽE ALGORITAM TOKEN RING

ARHITEKTURA MIKROKONTROLERA PIC 16 F 84

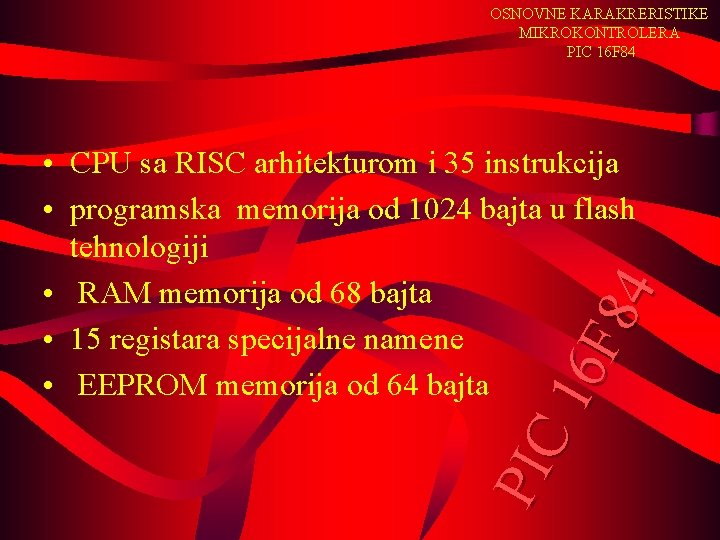

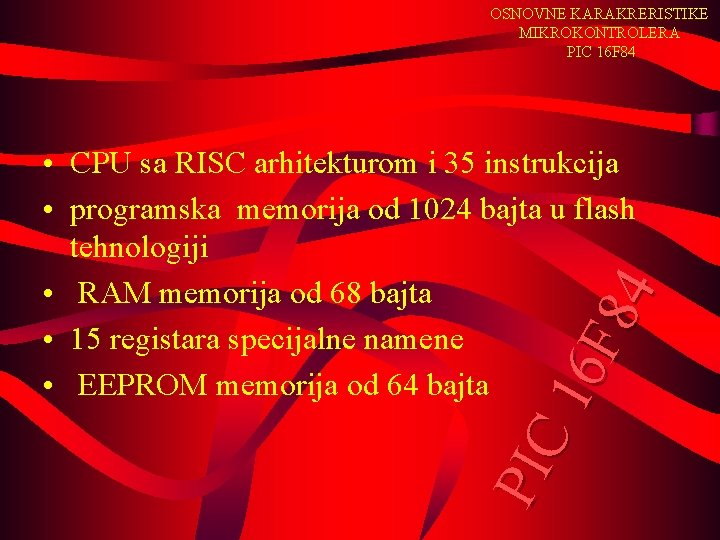

OSNOVNE KARAKRERISTIKE MIKROKONTROLERA PIC 16 F 84 PIC 16 F 8 4 • CPU sa RISC arhitekturom i 35 instrukcija • programska memorija od 1024 bajta u flash tehnologiji • RAM memorija od 68 bajta • 15 registara specijalne namene • EEPROM memorija od 64 bajta

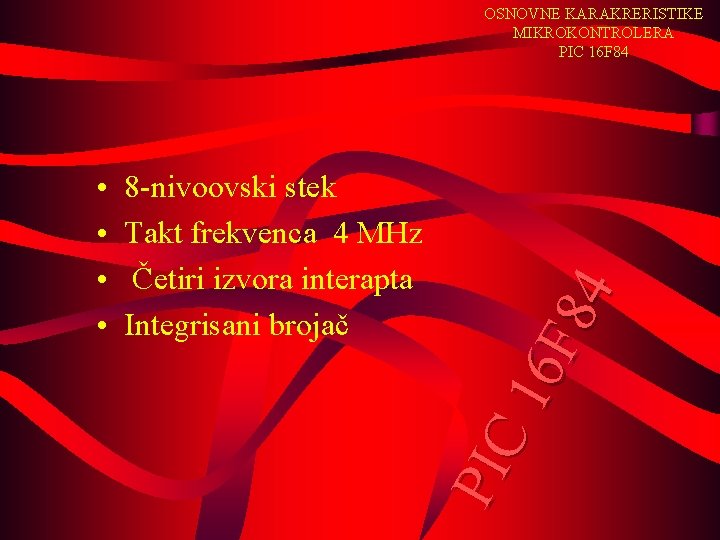

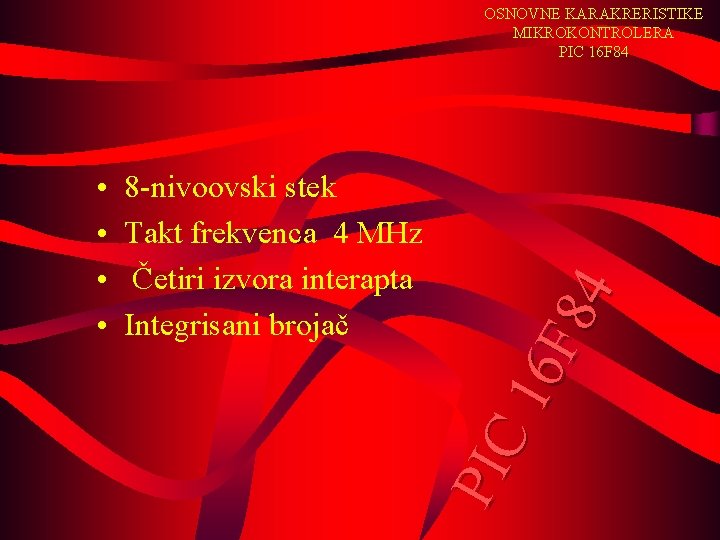

• • 8 -nivoovski stek Takt frekvenca 4 MHz Četiri izvora interapta Integrisani brojač P IC 16 F 8 4 OSNOVNE KARAKRERISTIKE MIKROKONTROLERA PIC 16 F 84

U/I KARAKTERISTIKE

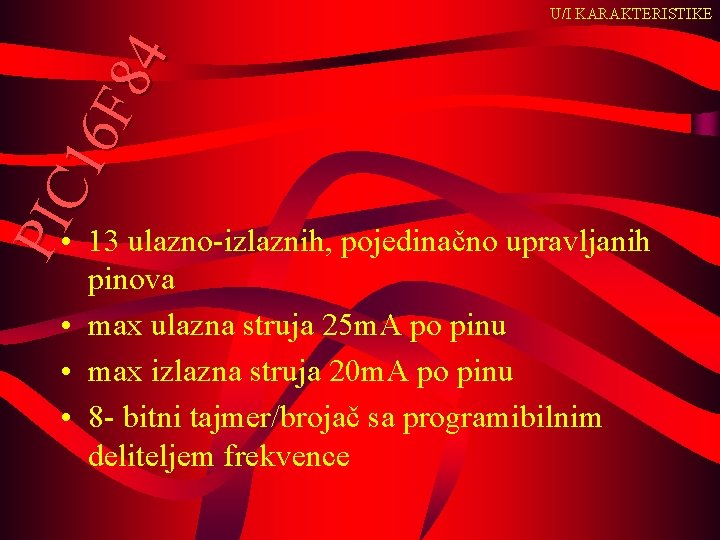

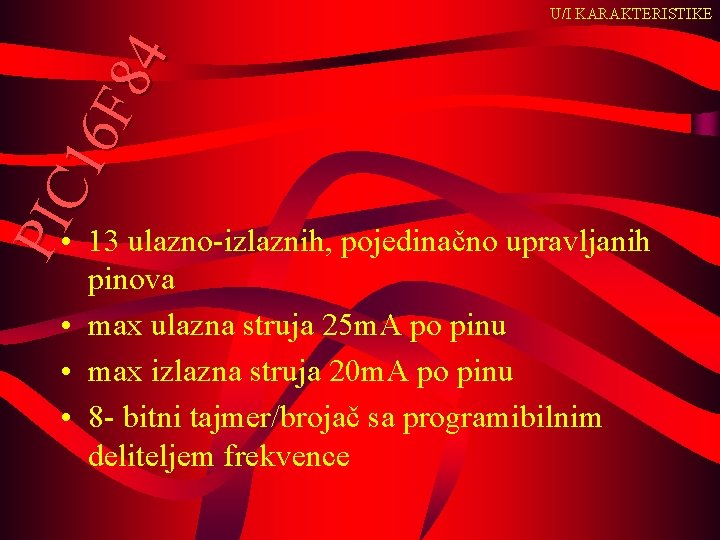

PIC 16 F 8 4 U/I KARAKTERISTIKE • 13 ulazno-izlaznih, pojedinačno upravljanih pinova • max ulazna struja 25 m. A po pinu • max izlazna struja 20 m. A po pinu • 8 - bitni tajmer/brojač sa programibilnim deliteljem frekvence

POSEBNE KARAKTERISTIKE

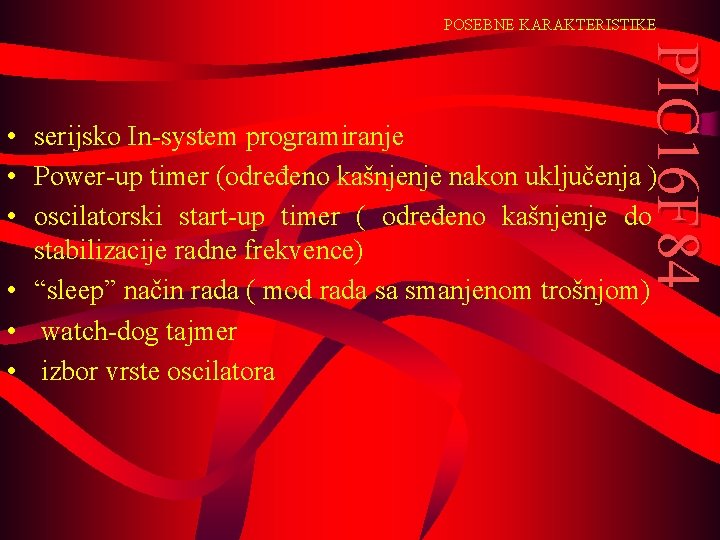

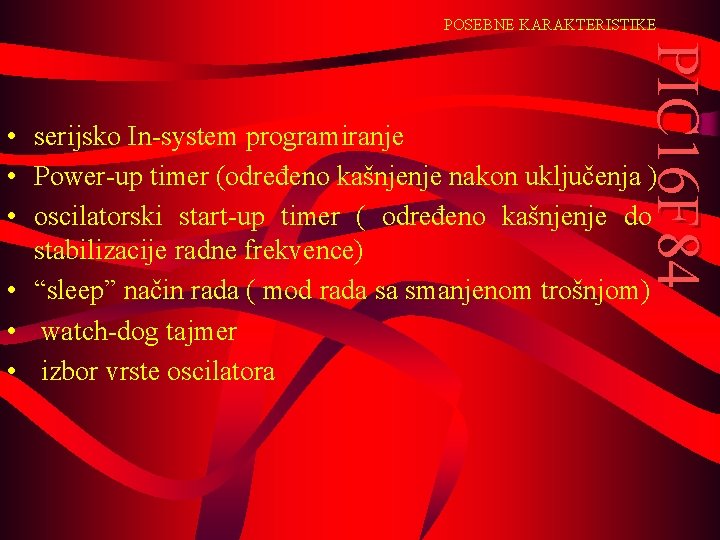

POSEBNE KARAKTERISTIKE PIC 16 F 84 • serijsko In-system programiranje • Power-up timer (određeno kašnjenje nakon uključenja ) • oscilatorski start-up timer ( određeno kašnjenje do stabilizacije radne frekvence) • “sleep” način rada ( mod rada sa smanjenom trošnjom) • watch-dog tajmer • izbor vrste oscilatora

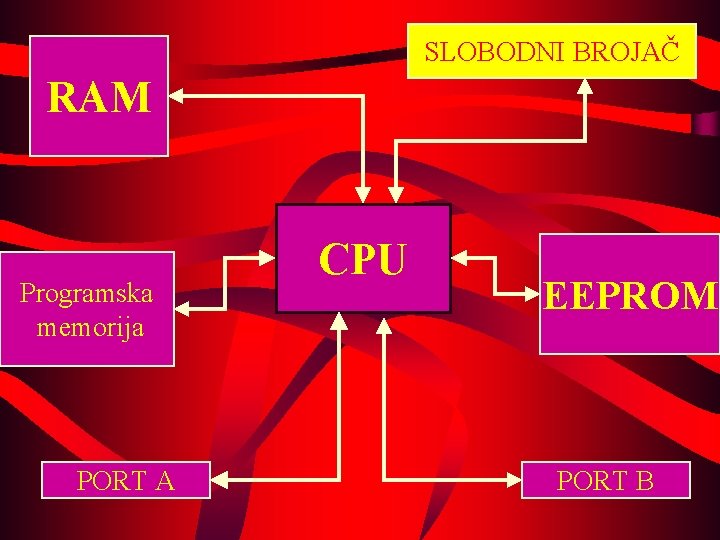

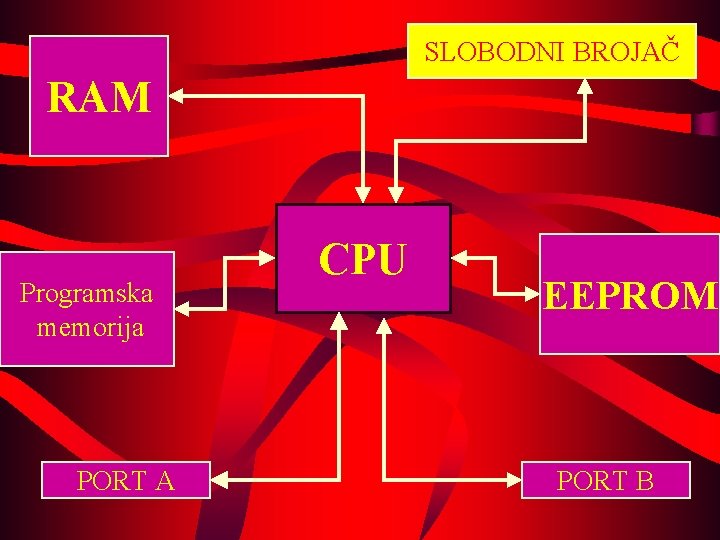

SLOBODNI BROJAČ RAM Programska memorija PORT A CPU EEPROM PORT B

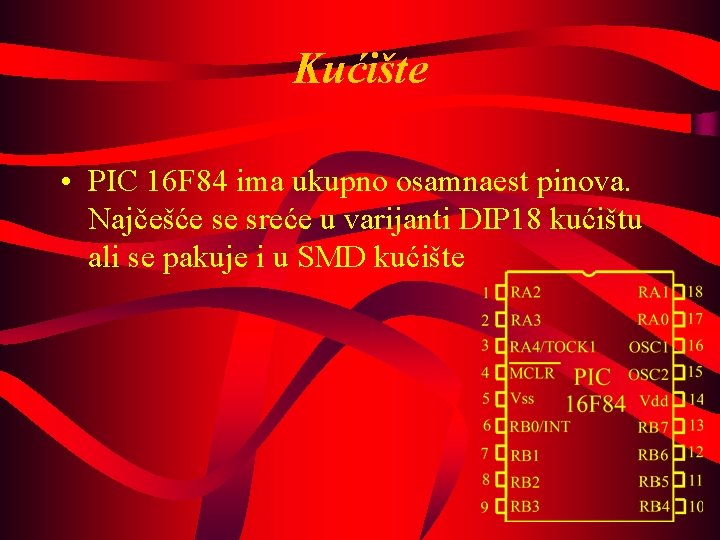

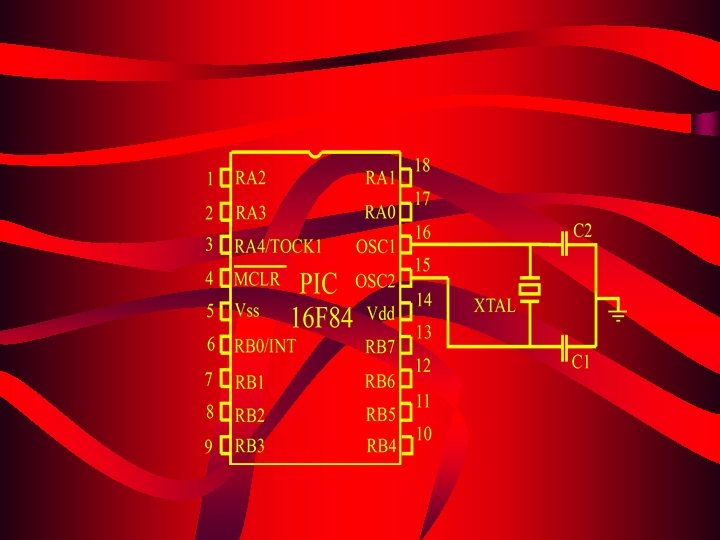

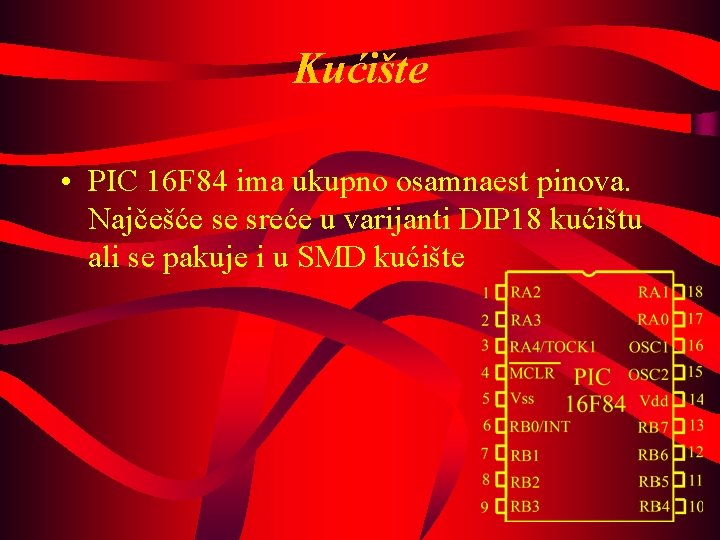

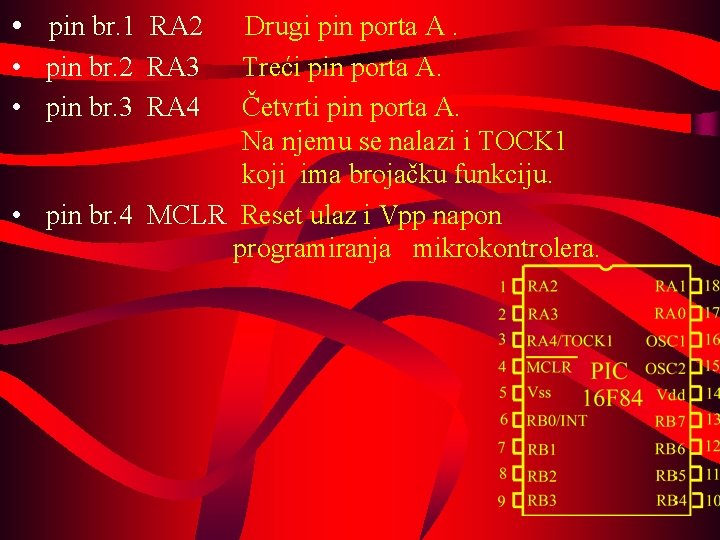

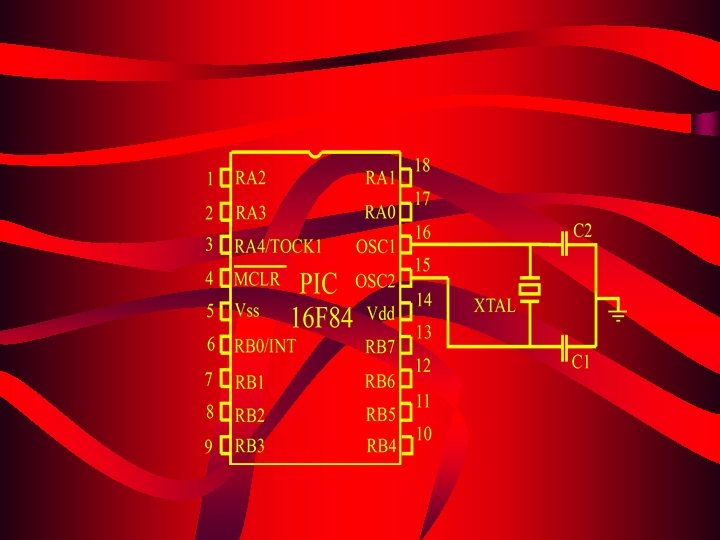

Kućište • PIC 16 F 84 ima ukupno osamnaest pinova. Najčešće se sreće u varijanti DIP 18 kućištu ali se pakuje i u SMD kućište

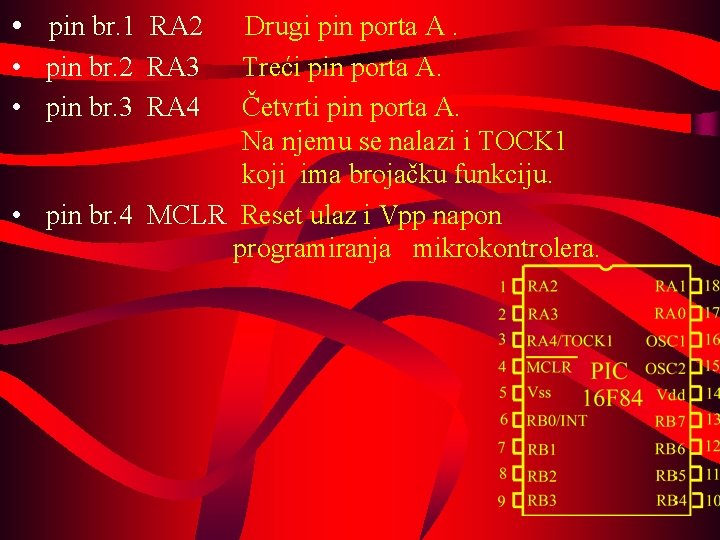

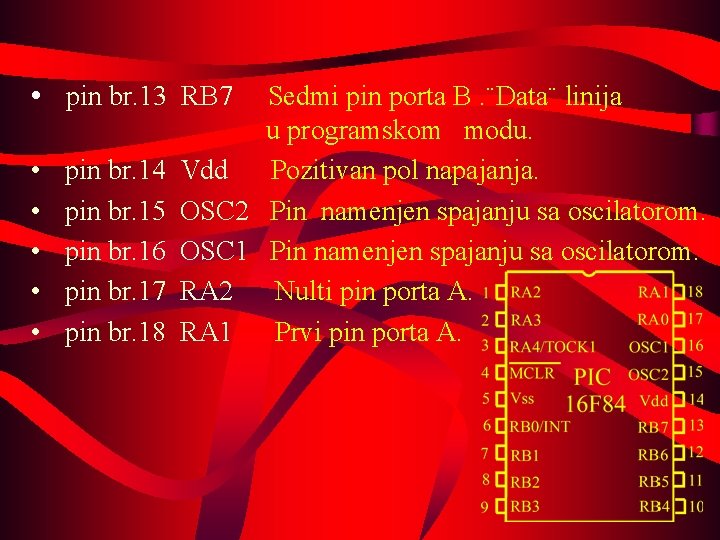

• pin br. 1 RA 2 Drugi pin porta A. • pin br. 2 RA 3 Treći pin porta A. • pin br. 3 RA 4 Četvrti pin porta A. Na njemu se nalazi i TOCK 1 koji ima brojačku funkciju. • pin br. 4 MCLR Reset ulaz i Vpp napon programiranja mikrokontrolera.

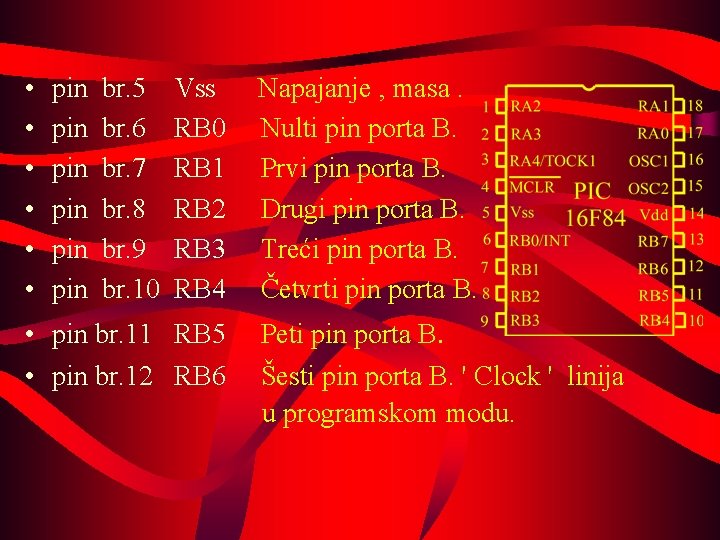

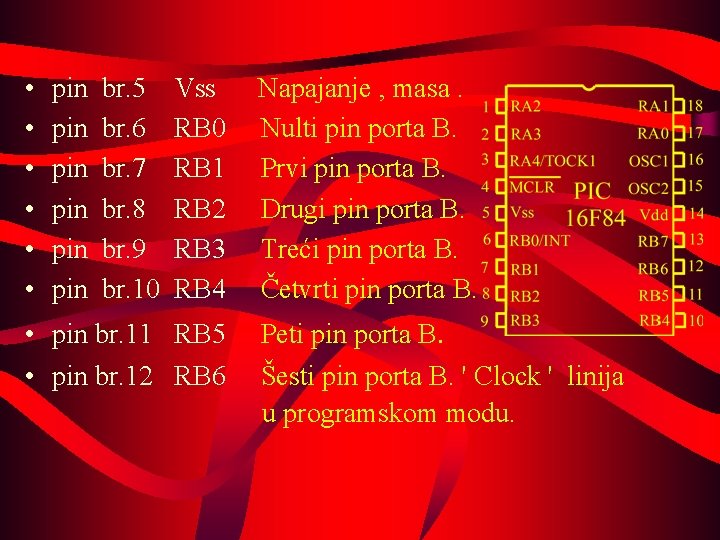

• • • pin br. 5 Vss Napajanje , masa. pin br. 6 RB 0 Nulti pin porta B. pin br. 7 RB 1 Prvi pin porta B. pin br. 8 RB 2 Drugi pin porta B. pin br. 9 RB 3 Treći pin porta B. pin br. 10 RB 4 Četvrti pin porta B. • pin br. 11 RB 5 Peti pin porta B. • pin br. 12 RB 6 Šesti pin porta B. ' Clock ' linija u programskom modu.

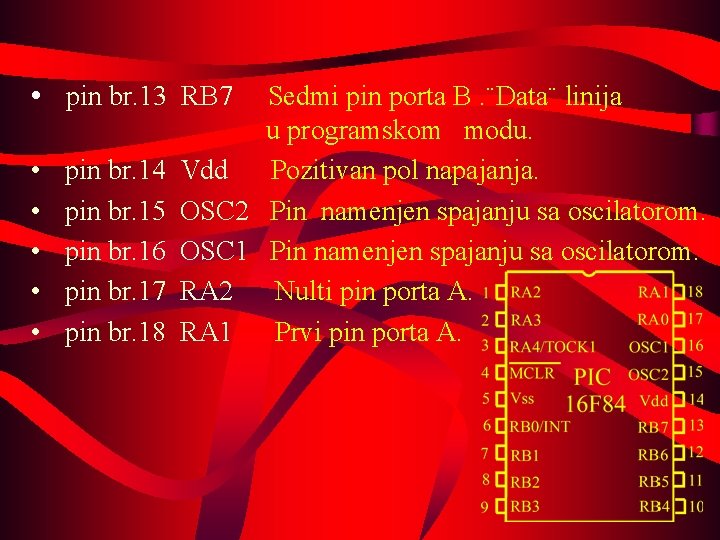

• pin br. 13 RB 7 Sedmi pin porta B. ¨Data¨ linija • • • u programskom modu. pin br. 14 Vdd Pozitivan pol napajanja. pin br. 15 OSC 2 Pin namenjen spajanju sa oscilatorom. pin br. 16 OSC 1 Pin namenjen spajanju sa oscilatorom. pin br. 17 RA 2 Nulti pin porta A. pin br. 18 RA 1 Prvi pin porta A.

ORGANIZACIJA MEMORIJE

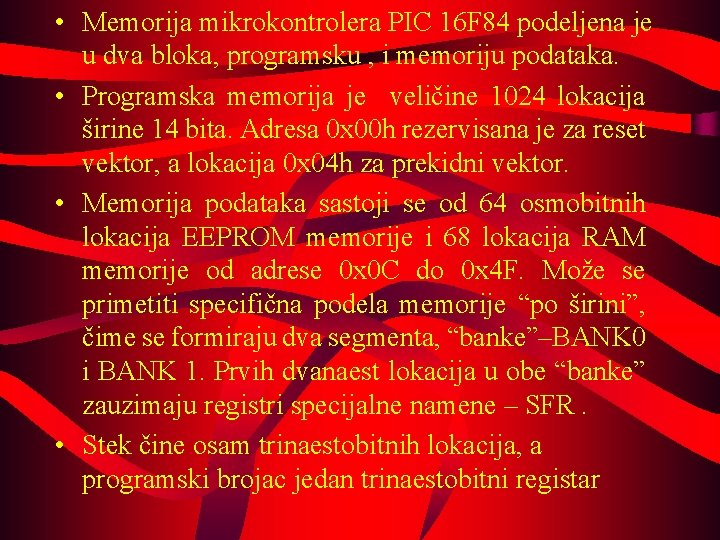

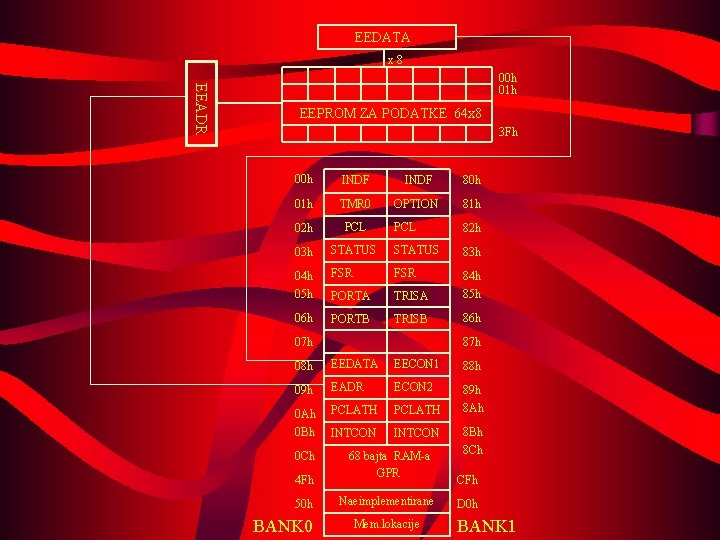

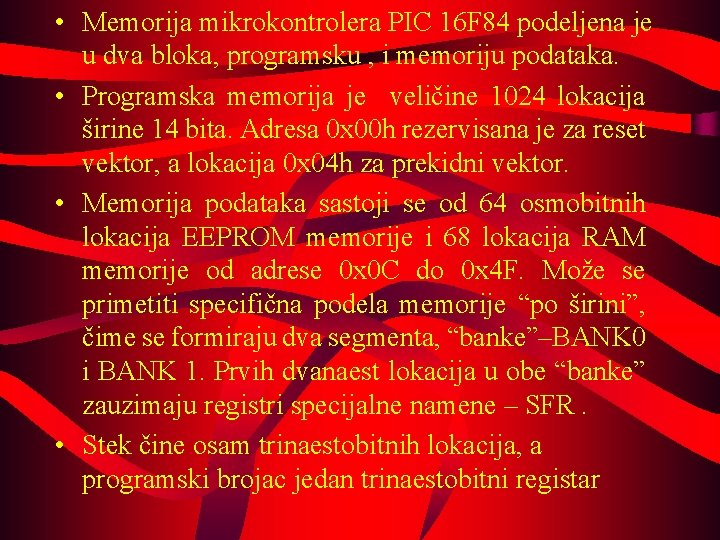

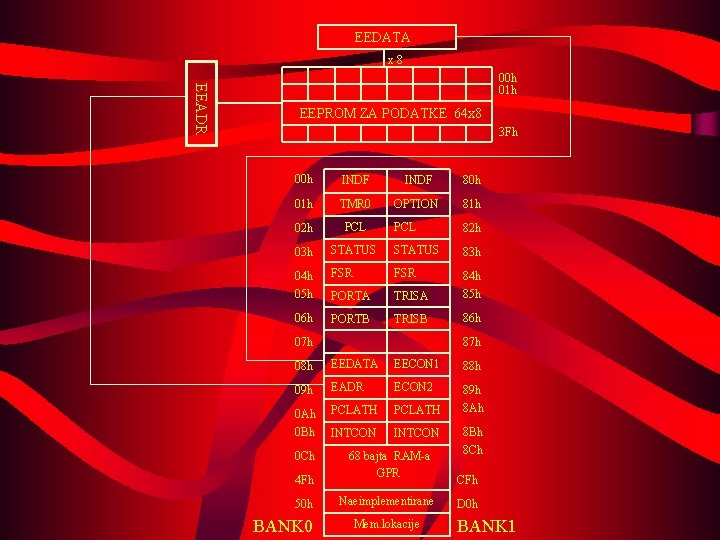

• Memorija mikrokontrolera PIC 16 F 84 podeljena je u dva bloka, programsku , i memoriju podataka. • Programska memorija je veličine 1024 lokacija širine 14 bita. Adresa 0 x 00 h rezervisana je za reset vektor, a lokacija 0 x 04 h za prekidni vektor. • Memorija podataka sastoji se od 64 osmobitnih lokacija EEPROM memorije i 68 lokacija RAM memorije od adrese 0 x 0 C do 0 x 4 F. Može se primetiti specifična podela memorije “po širini”, čime se formiraju dva segmenta, “banke”–BANK 0 i BANK 1. Prvih dvanaest lokacija u obe “banke” zauzimaju registri specijalne namene – SFR. • Stek čine osam trinaestobitnih lokacija, a programski brojac jedan trinaestobitni registar

EEDATA STEK NIVO 1 x 8 EEADR STEK NIVO 3 00 h 01 h EEPROM ZA PODATKE 64 x 8 3 Fh STEK NIVO 8 ADRESNA MAGISTRALA PCL <12: 0> ADRESNA MAGISTRALA 0000 h Adresa reseta MAGISTRALA PODATAKA 00 h INDF 80 h 01 h TMR 0 OPTION 81 h 02 h PCL 82 h 03 h STATUS 83 h 04 h FSR 84 h 05 h PORTA TRISA 85 h 06 h PORTB TRISB 86 h 07 h 0004 h Adresa prekidnog vektora Programska memorija 1024 x 14 bajta 1 FFFh 87 h 08 h EEDATA EECON 1 88 h 09 h EADR ECON 2 0 Ah 0 Bh PCLATH 89 h 8 Ah INTCON 0 Ch 68 bajta RAM-a GPR 4 Fh 50 h BANK 0 Naeimplementirane Mem. lokacije 8 Bh 8 Ch CFh D 0 h BANK 1

ULAZNO/IZLAZNI PORTOVI

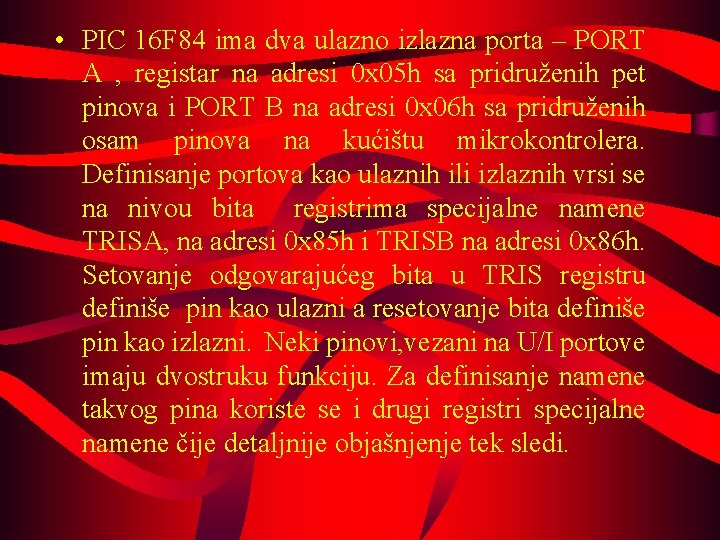

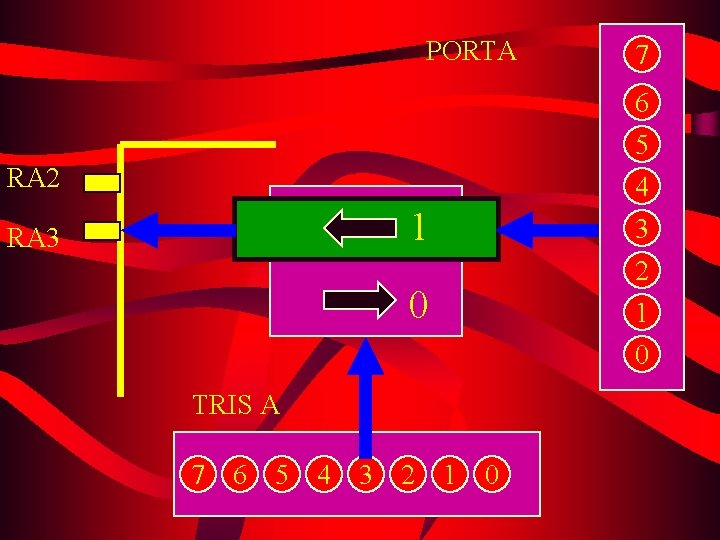

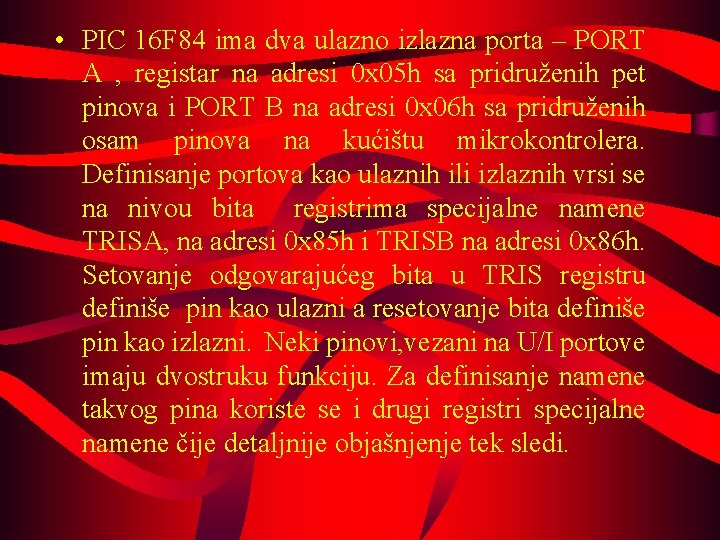

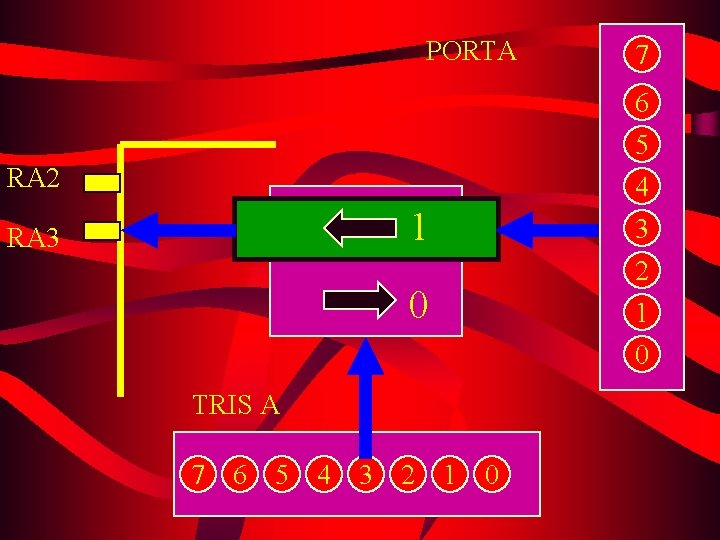

• PIC 16 F 84 ima dva ulazno izlazna porta – PORT A , registar na adresi 0 x 05 h sa pridruženih pet pinova i PORT B na adresi 0 x 06 h sa pridruženih osam pinova na kućištu mikrokontrolera. Definisanje portova kao ulaznih ili izlaznih vrsi se na nivou bita registrima specijalne namene TRISA, na adresi 0 x 85 h i TRISB na adresi 0 x 86 h. Setovanje odgovarajućeg bita u TRIS registru definiše pin kao ulazni a resetovanje bita definiše pin kao izlazni. Neki pinovi, vezani na U/I portove imaju dvostruku funkciju. Za definisanje namene takvog pina koriste se i drugi registri specijalne namene čije detaljnije objašnjenje tek sledi.

PORTA 7 6 5 4 3 RA 2 1 RA 3 2 1 0 0 TRIS A 7 6 5 4 3 2 1 0

OSCILATOR

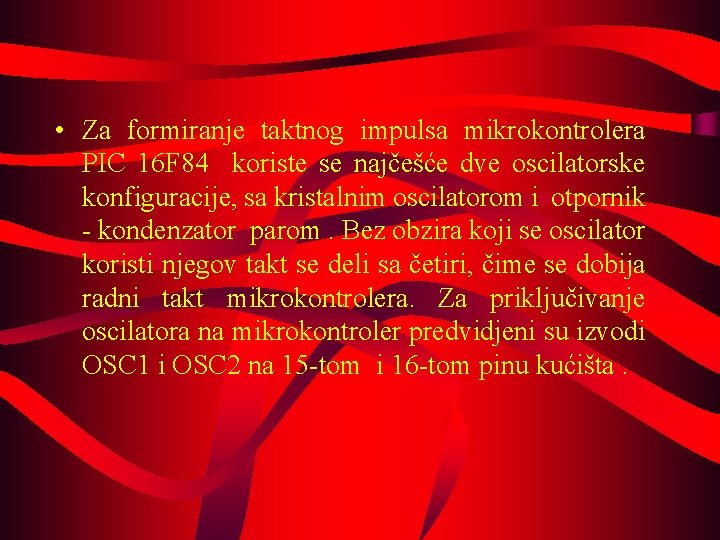

• Za formiranje taktnog impulsa mikrokontrolera PIC 16 F 84 koriste se najčešće dve oscilatorske konfiguracije, sa kristalnim oscilatorom i otpornik - kondenzator parom. Bez obzira koji se oscilator koristi njegov takt se deli sa četiri, čime se dobija radni takt mikrokontrolera. Za priključivanje oscilatora na mikrokontroler predvidjeni su izvodi OSC 1 i OSC 2 na 15 -tom i 16 -tom pinu kućišta.

RESET

Mikrokontroler PIC 16 F 84 poznaje nekoliko izvora reseta : • Resetovanje pri dovođenju napajanja , power on reset – POR • Resetovanje tokom rada, dovođenjem logičke nule na pin MCLR • Resetovanje za vreme sleep režima mikrokontrolera • Resetovanje pri prekotačenju sigurnosnog brojača (WDT) tokom regularnog rada • Resetovanje na prekoračenje sigurnosnog brojača tokom sleep režima

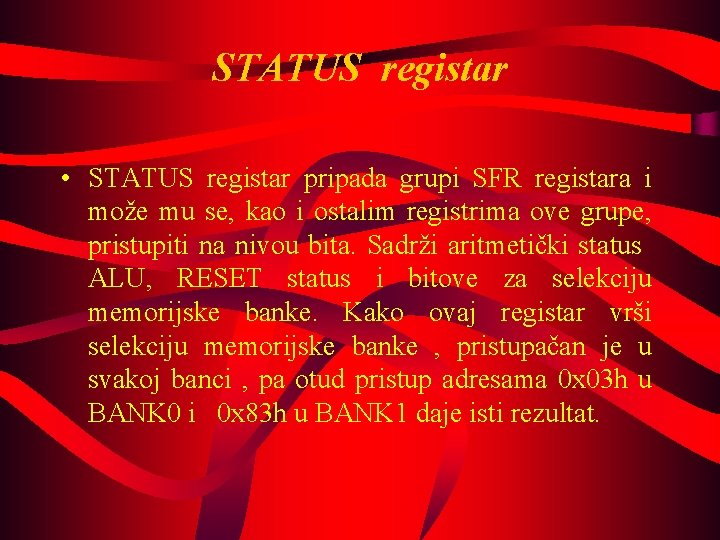

STATUS registar • STATUS registar pripada grupi SFR registara i može mu se, kao i ostalim registrima ove grupe, pristupiti na nivou bita. Sadrži aritmetički status ALU, RESET status i bitove za selekciju memorijske banke. Kako ovaj registar vrši selekciju memorijske banke , pristupačan je u svakoj banci , pa otud pristup adresama 0 x 03 h u BANK 0 i 0 x 83 h u BANK 1 daje isti rezultat.

STATUS REGISTAR R/W- 0 R - 1 R/W- x R/W-x IRP RP 1 RP 0 T 0 PD Z DC C 7 6 5 4 3 2 1 Bit 0 R=bit koji se može pročitati W= bit koji se može pisati - n = vrednost posle reseta

bit 0 C – (Carry) prenos 1 = pojavio se prenos sa najvišeg bita rezultata 0 = prenos se nije pojavio bit 1 DC - ( Digit Carry) DC prenos 1 = pojavio se prenos na četvrtom bitu po redu rezultata 0 = prenos se nije pojavio bit 2 Z – ( Zero bit) indikacija nultog rezultata 1 = rezultat je jednak nuli 0 = rezultat je različit od nule bit 3 PD – ( Power – Down bit ) Bit koji se setuje dovođenjem napajanja , posle svakog regularnog reseta, resetovanjem se mikrokontroler prevodi u SLEEP režim.

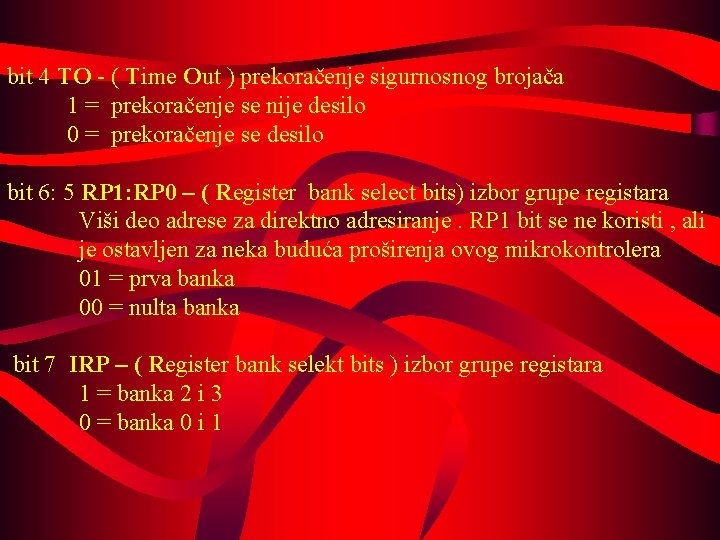

bit 4 TO - ( Time Out ) prekoračenje sigurnosnog brojača 1 = prekoračenje se nije desilo 0 = prekoračenje se desilo bit 6: 5 RP 1: RP 0 – ( Register bank select bits) izbor grupe registara Viši deo adrese za direktno adresiranje. RP 1 bit se ne koristi , ali je ostavljen za neka buduća proširenja ovog mikrokontrolera 01 = prva banka 00 = nulta banka bit 7 IRP – ( Register bank selekt bits ) izbor grupe registara 1 = banka 2 i 3 0 = banka 0 i 1

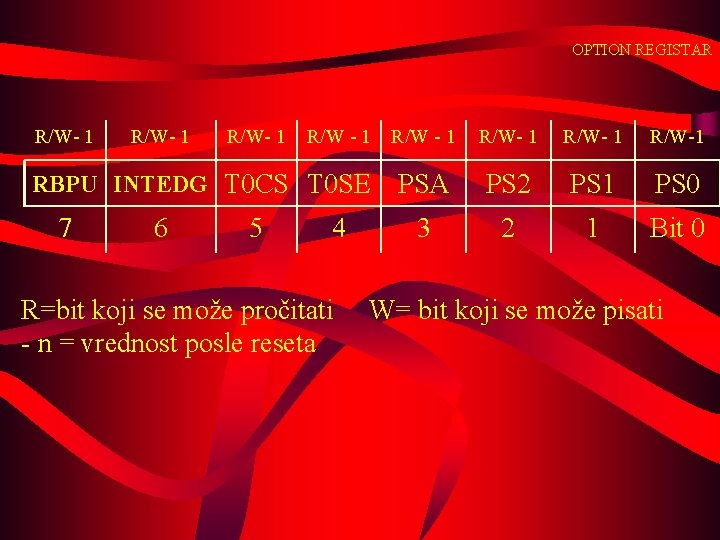

OPTION REGISTAR

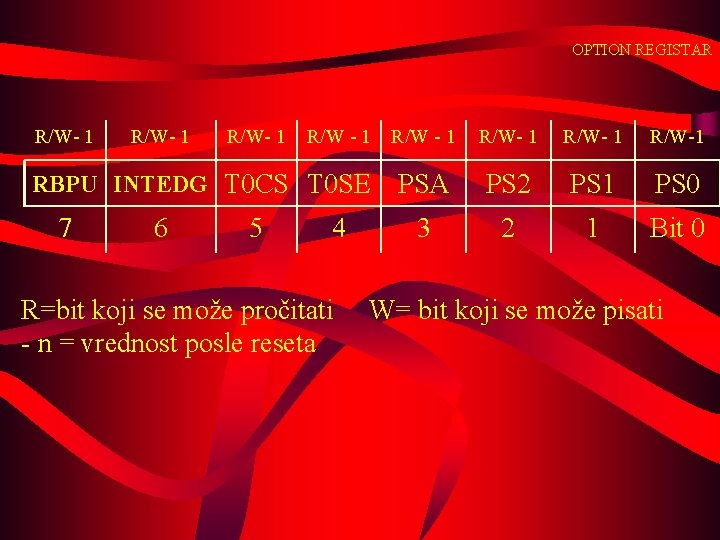

OPTION REGISTAR R/W- 1 R/W - 1 RBPU INTEDG T 0 CS T 0 SE 7 6 5 4 R/W - 1 R/W-1 PSA PS 2 PS 1 PS 0 3 2 1 Bit 0 R=bit koji se može pročitati W= bit koji se može pisati - n = vrednost posle reseta

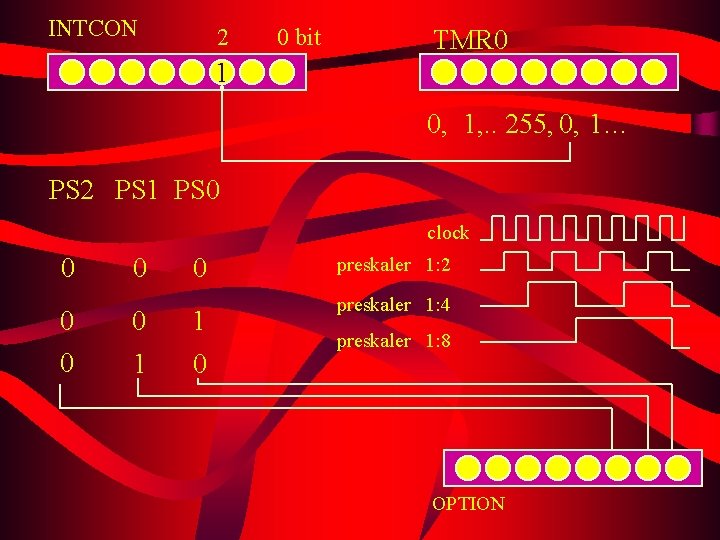

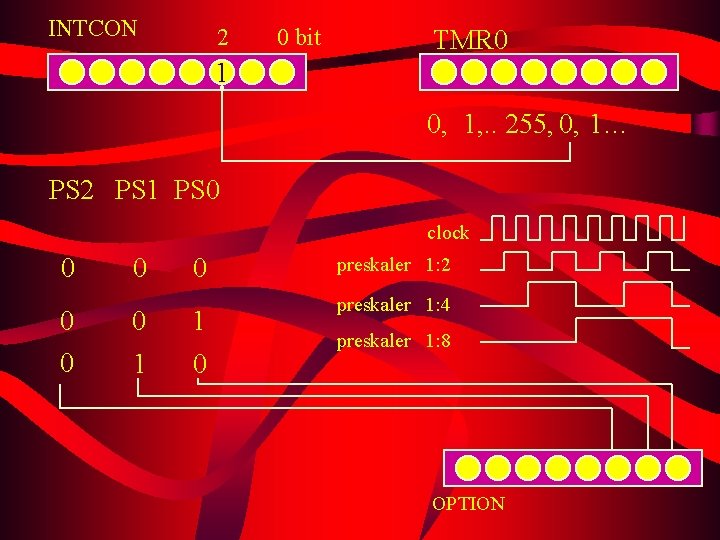

PS 2 PS 1 PS 0 clock 0 0 0 1 1 0 preskaler 1: 2 preskaler 1: 4 preskaler 1: 8 OPTION

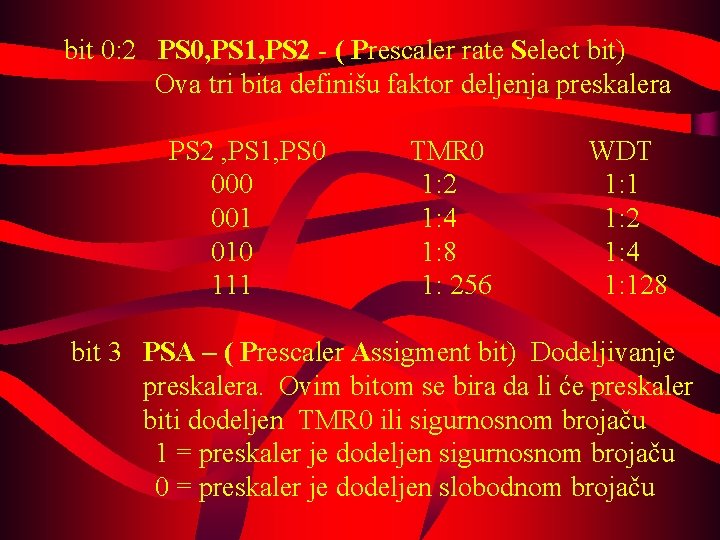

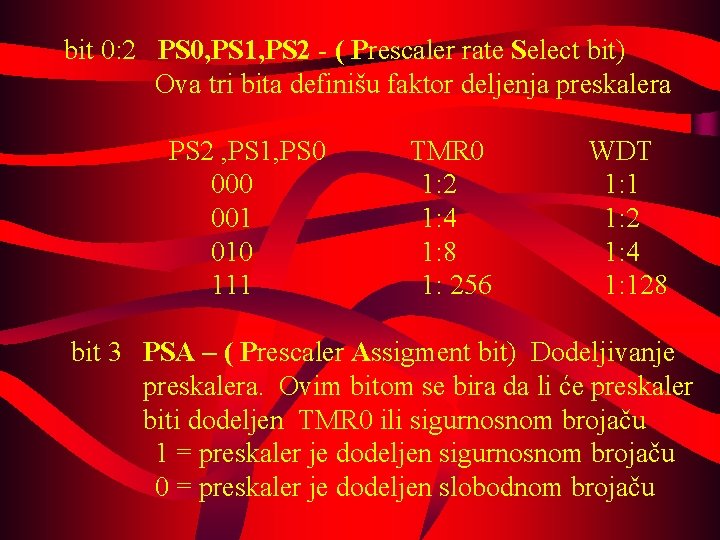

bit 0: 2 PS 0, PS 1, PS 2 - ( Prescaler rate Select bit) Ova tri bita definišu faktor deljenja preskalera PS 2 , PS 1, PS 0 TMR 0 WDT 000 1: 2 1: 1 001 1: 4 1: 2 010 1: 8 1: 4 111 1: 256 1: 128 bit 3 PSA – ( Prescaler Assigment bit) Dodeljivanje preskalera. Ovim bitom se bira da li će preskaler biti dodeljen TMR 0 ili sigurnosnom brojaču 1 = preskaler je dodeljen sigurnosnom brojaču 0 = preskaler je dodeljen slobodnom brojaču

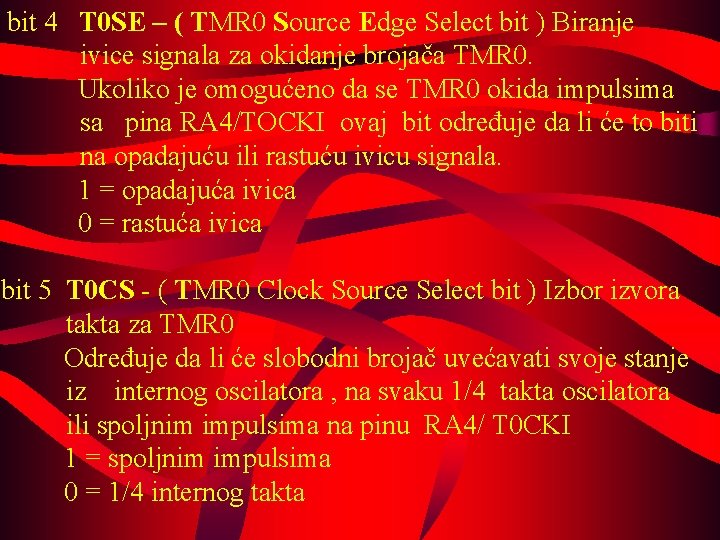

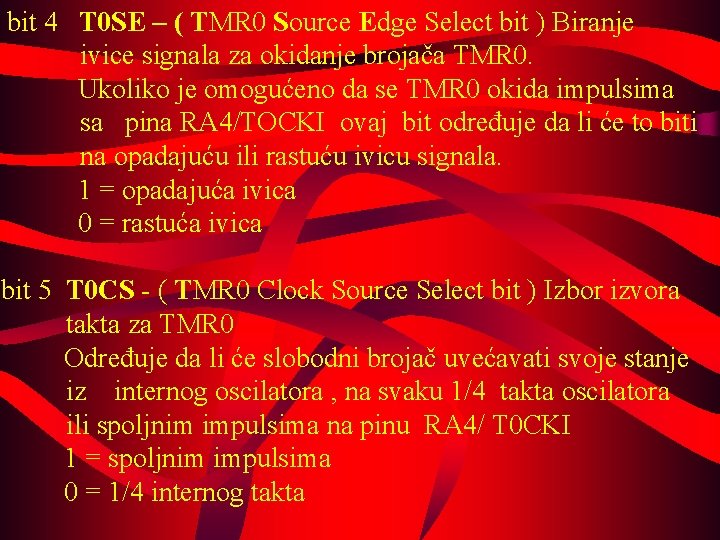

bit 4 T 0 SE – ( TMR 0 Source Edge Select bit ) Biranje ivice signala za okidanje brojača TMR 0. Ukoliko je omogućeno da se TMR 0 okida impulsima sa pina RA 4/TOCKI ovaj bit određuje da li će to biti na opadajuću ili rastuću ivicu signala. 1 = opadajuća ivica 0 = rastuća ivica bit 5 T 0 CS - ( TMR 0 Clock Source Select bit ) Izbor izvora takta za TMR 0 Određuje da li će slobodni brojač uvećavati svoje stanje iz internog oscilatora , na svaku 1/4 takta oscilatora ili spoljnim impulsima na pinu RA 4/ T 0 CKI 1 = spoljnim impulsima 0 = 1/4 internog takta

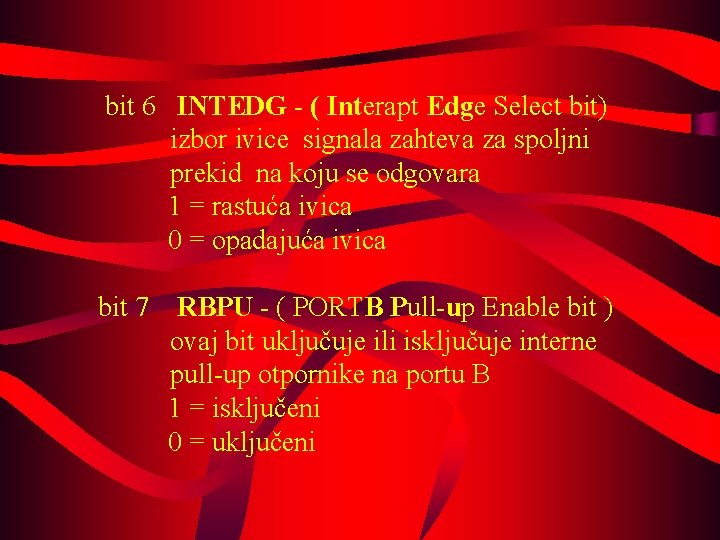

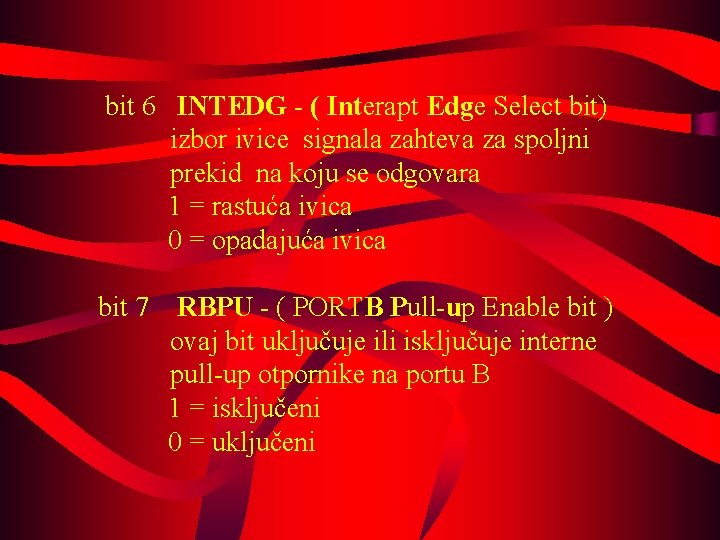

bit 6 INTEDG - ( Interapt Edge Select bit) izbor ivice signala zahteva za spoljni prekid na koju se odgovara 1 = rastuća ivica 0 = opadajuća ivica bit 7 RBPU - ( PORTB Pull-up Enable bit ) ovaj bit uključuje ili isključuje interne pull-up otpornike na portu B 1 = isključeni 0 = uključeni

EEPROM MEMORIJA

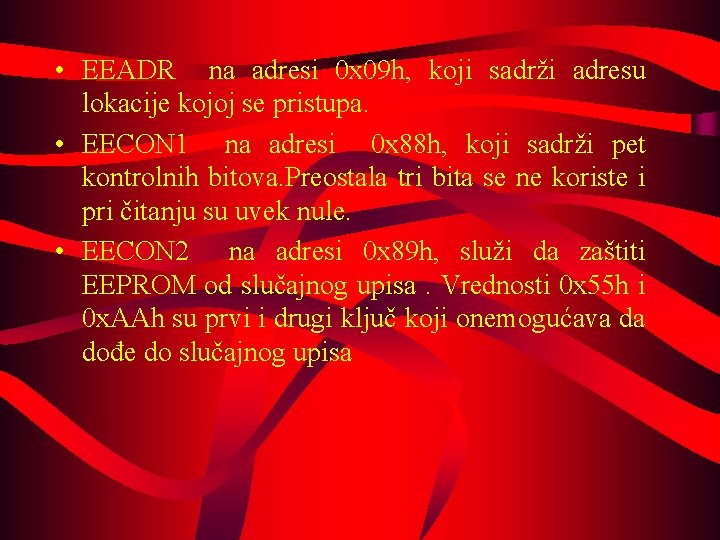

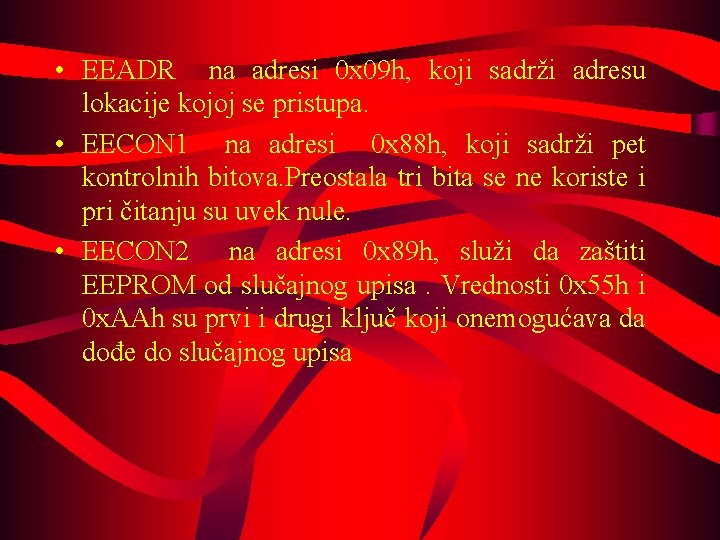

• Već je rečeno da PIC 16 F 84 ima 64 bajta EEPROM memorijskih lokacija na adresama 0 x 00 h do 0 x 3 Fh. EEPROM memorija se nalazi u posebnom memorijskom prostoru i pristupa joj se preko specijalnih registara : • EEDATA na adresi 0 x 08 h, koja sadrži podatak koji je ili pročitan ili ga treba upisati.

• EEADR na adresi 0 x 09 h, koji sadrži adresu lokacije kojoj se pristupa. • EECON 1 na adresi 0 x 88 h, koji sadrži pet kontrolnih bitova. Preostala tri bita se ne koriste i pri čitanju su uvek nule. • EECON 2 na adresi 0 x 89 h, služi da zaštiti EEPROM od slučajnog upisa. Vrednosti 0 x 55 h i 0 x. AAh su prvi i drugi ključ koji onemogućava da dođe do slučajnog upisa

EECON 1 U-0 U-0 - - - 7 6 5 R/W-1 R/W - 1 R/W- x EEIF WRERR WREN 4 3 2 R/W- 0 R/W-x WR RD 1 Bit 0 R=bit koji se može pročitati W= bit koji se može pisati - n = vrednost posle reseta

EEDATA x 8 EEADR 00 h 01 h EEPROM ZA PODATKE 64 x 8 3 Fh 00 h INDF 80 h 01 h TMR 0 OPTION 81 h 02 h PCL 82 h 03 h STATUS 83 h 04 h 05 h FSR PORTA TRISA 84 h 85 h 06 h PORTB TRISB 86 h 07 h 87 h 08 h EEDATA EECON 1 88 h 09 h EADR ECON 2 0 Ah 0 Bh PCLATH 89 h 8 Ah INTCON 0 Ch 68 bajta RAM-a GPR 4 Fh 50 h BANK 0 Naeimplementirane Mem. lokacije 8 Bh 8 Ch CFh D 0 h BANK 1

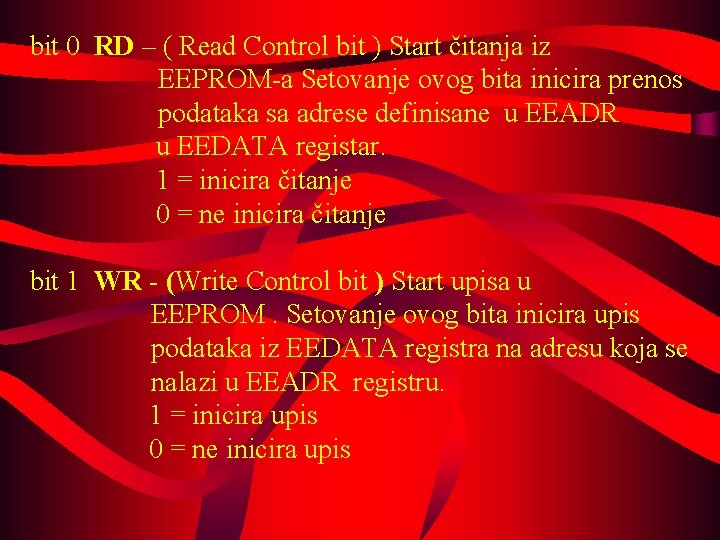

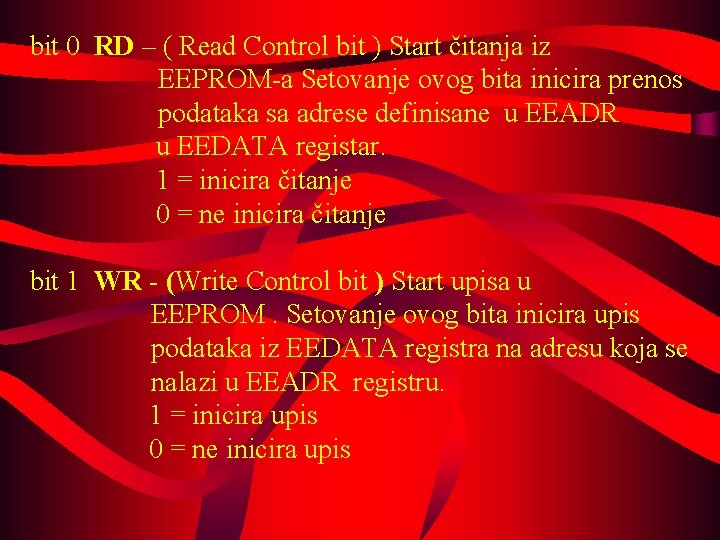

bit 0 RD – ( Read Control bit ) Start čitanja iz EEPROM-a Setovanje ovog bita inicira prenos podataka sa adrese definisane u EEADR u EEDATA registar. 1 = inicira čitanje 0 = ne inicira čitanje bit 1 WR - (Write Control bit ) Start upisa u EEPROM. Setovanje ovog bita inicira upis podataka iz EEDATA registra na adresu koja se nalazi u EEADR registru. 1 = inicira upis 0 = ne inicira upis

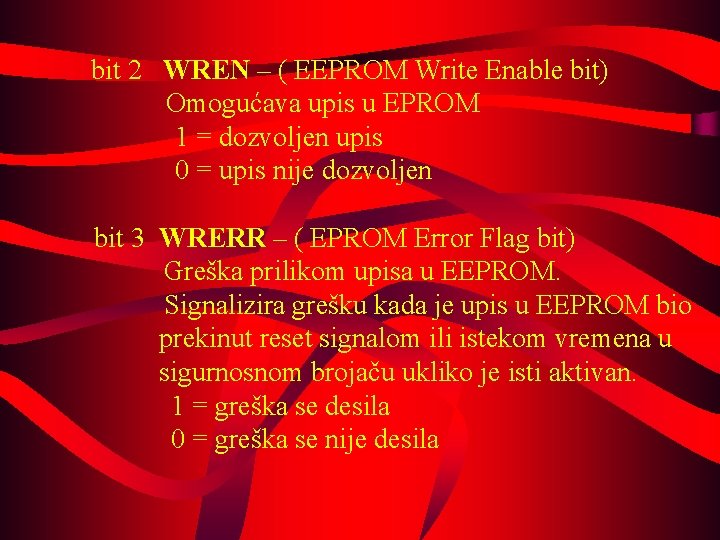

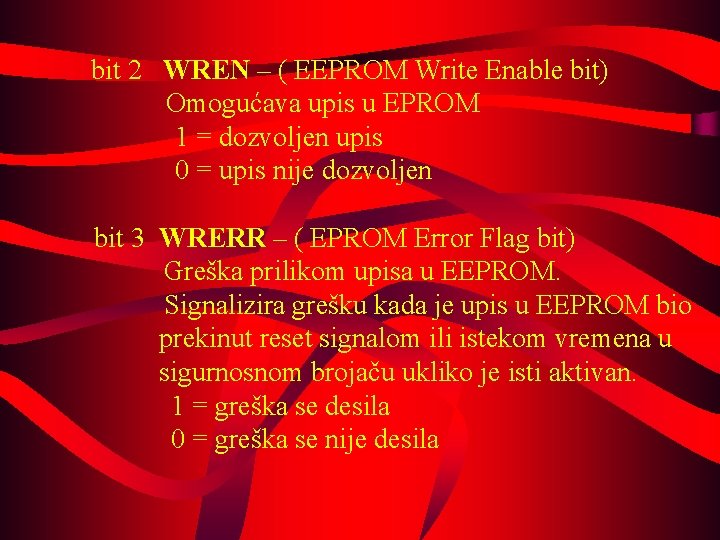

bit 2 WREN – ( EEPROM Write Enable bit) Omogućava upis u EPROM 1 = dozvoljen upis 0 = upis nije dozvoljen bit 3 WRERR – ( EPROM Error Flag bit) Greška prilikom upisa u EEPROM. Signalizira grešku kada je upis u EEPROM bio prekinut reset signalom ili istekom vremena u sigurnosnom brojaču ukliko je isti aktivan. 1 = greška se desila 0 = greška se nije desila

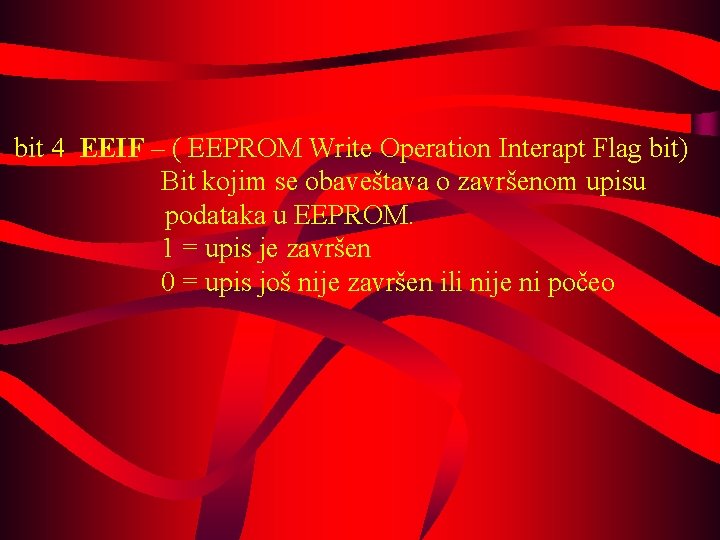

bit 4 EEIF – ( EEPROM Write Operation Interapt Flag bit) Bit kojim se obaveštava o završenom upisu podataka u EEPROM. 1 = upis je završen 0 = upis još nije završen ili nije ni počeo

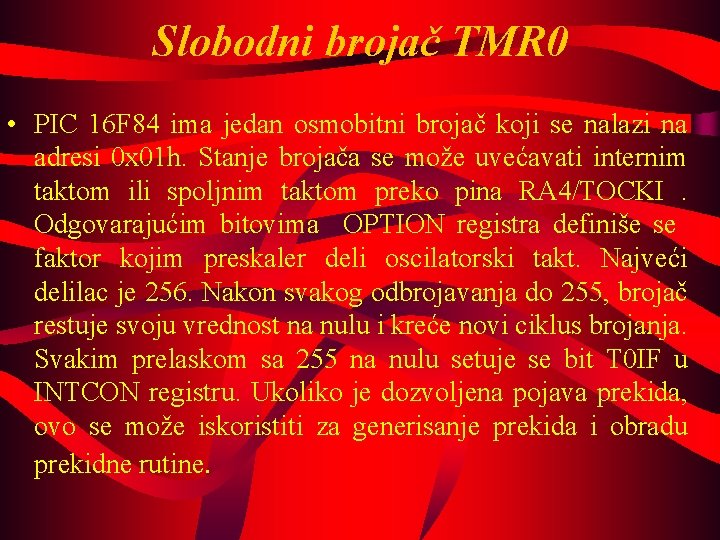

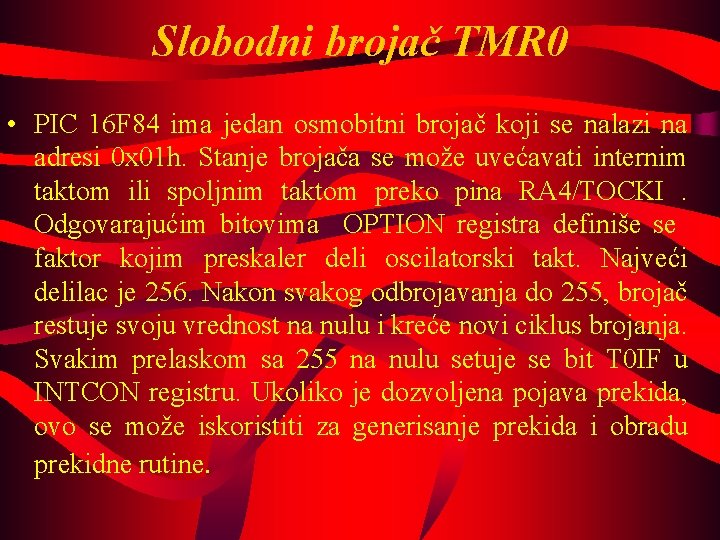

Slobodni brojač TMR 0 • PIC 16 F 84 ima jedan osmobitni brojač koji se nalazi na adresi 0 x 01 h. Stanje brojača se može uvećavati internim taktom ili spoljnim taktom preko pina RA 4/TOCKI . Odgovarajućim bitovima OPTION registra definiše se faktor kojim preskaler deli oscilatorski takt. Najveći delilac je 256. Nakon svakog odbrojavanja do 255, brojač restuje svoju vrednost na nulu i kreće novi ciklus brojanja. Svakim prelaskom sa 255 na nulu setuje se bit T 0 IF u INTCON registru. Ukoliko je dozvoljena pojava prekida, ovo se može iskoristiti za generisanje prekida i obradu prekidne rutine.

INTCON 2 0 bit TMR 0 1 0, 1, . . 255, 0, 1… PS 2 PS 1 PS 0 clock 0 0 0 1 1 0 preskaler 1: 2 preskaler 1: 4 preskaler 1: 8 OPTION

Programiranje unutar sistema - In System Programing Da bi se programirala programska memorija, mirokontroler mora biti postavljen u specijalni režim rada postavljanjem napona od 13. 5 v na MCLR, sa stabilnim naponom napajanja između 4. 5 v i 5. 5 v. Programiranje se vrši serijski preko dve data/clock nožice.

PROGRAMSKI BROJAČ Programski brojač (PC) je trinaesto bitni registar koji sadrži adresu instrukcije koja se izvršava. Njegovim uvećavanjem ili promenom (npr. u slučaju skoka) mikrokontroler izvršava jednu po jednu instrukciju programa.

MAGACIN PIC 16 F 84 ima trinaestobitni magacin sa osam nivoa. Njegova osnovna uloga je da sačuva vrednost programskog brojača nakon što se iz glavnog programa pređe na adresu podprograma koji se izvršava. Da bi program znao da se vrati na mesto odakle je pošao mora sa magacina je da vrati vrednost programskog brojača. Pri prelasku iz programa u podprogram vrednost gramskog brojača se smešta u magacin, a na kraju podprograma vraća iz magacina u programski brojač, da bi program mogao da nastavi tamo gde je prekinut.

PREKIDI KOD PIC 16 F 84

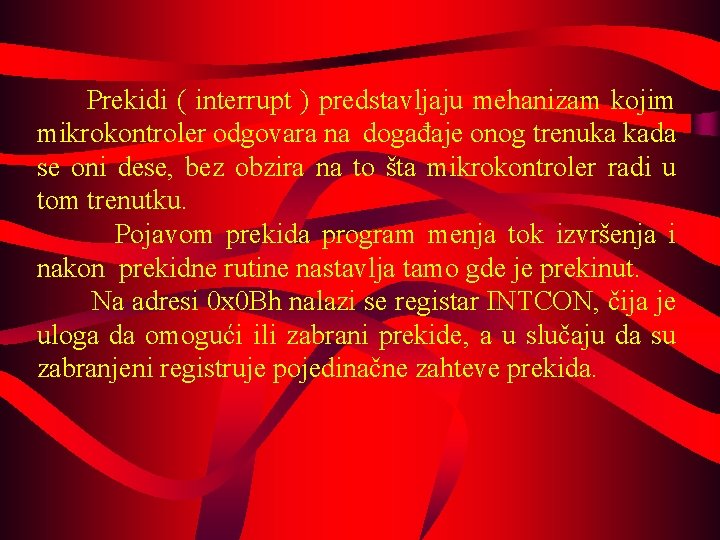

Prekidi ( interrupt ) predstavljaju mehanizam kojim mikrokontroler odgovara na događaje onog trenuka kada se oni dese, bez obzira na to šta mikrokontroler radi u tom trenutku. Pojavom prekida program menja tok izvršenja i nakon prekidne rutine nastavlja tamo gde je prekinut. Na adresi 0 x 0 Bh nalazi se registar INTCON, čija je uloga da omogući ili zabrani prekide, a u slučaju da su zabranjeni registruje pojedinačne zahteve prekida.

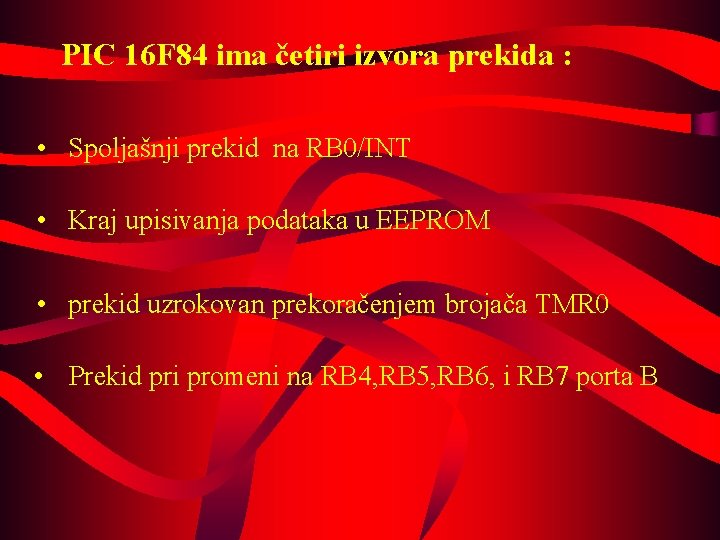

PIC 16 F 84 ima četiri izvora prekida : • Spoljašnji prekid na RB 0/INT • Kraj upisivanja podataka u EEPROM • prekid uzrokovan prekoračenjem brojača TMR 0 • Prekid pri promeni na RB 4, RB 5, RB 6, i RB 7 porta B

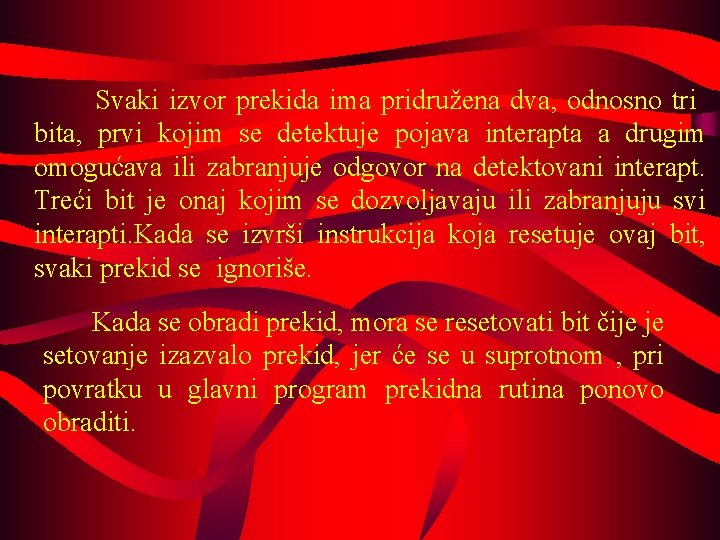

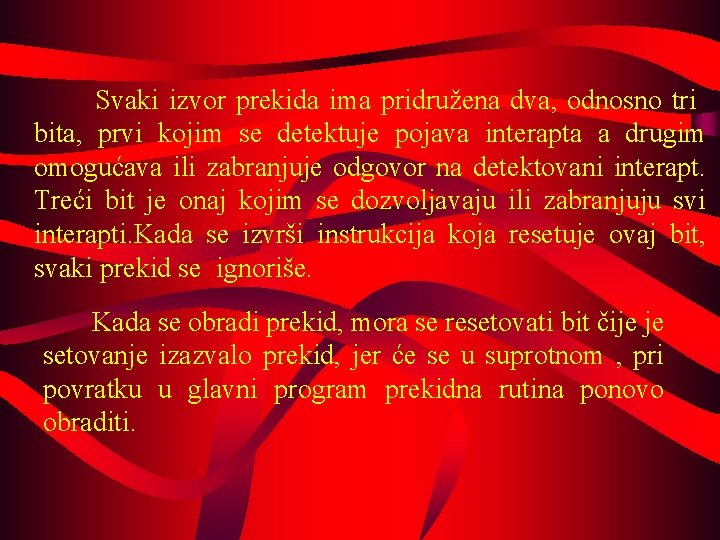

Svaki izvor prekida ima pridružena dva, odnosno tri bita, prvi kojim se detektuje pojava interapta a drugim omogućava ili zabranjuje odgovor na detektovani interapt. Treći bit je onaj kojim se dozvoljavaju ili zabranjuju svi interapti. Kada se izvrši instrukcija koja resetuje ovaj bit, svaki prekid se ignoriše. Kada se obradi prekid, mora se resetovati bit čije je setovanje izazvalo prekid, jer će se u suprotnom , pri povratku u glavni program prekidna rutina ponovo obraditi.

INTCON REGISTAR R/W- 0 GIE EEIE T 0 IE INTE RBIE TOIF INTF RBIF 7 6 5 R/W - 0 4 R/W - 0 3 R/W- 0 2 R/W- 0 1 R/W-0 Bit 0 R=bit koji se može pročitati W= bit koji se može pisati - n = vrednost posle reseta

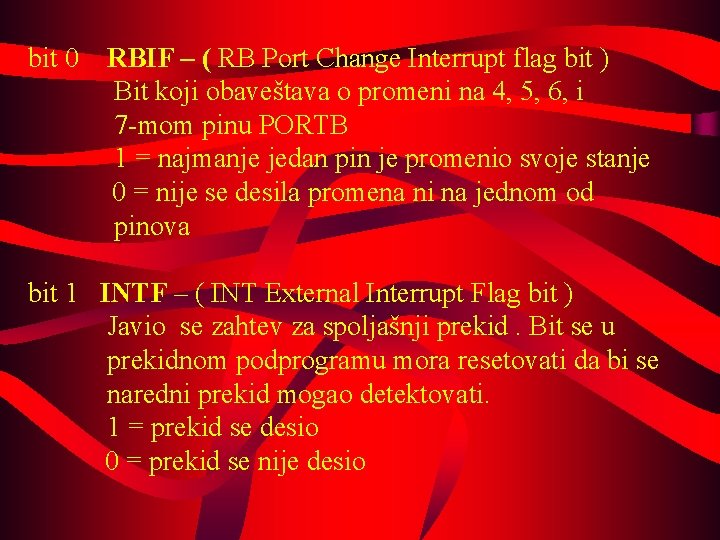

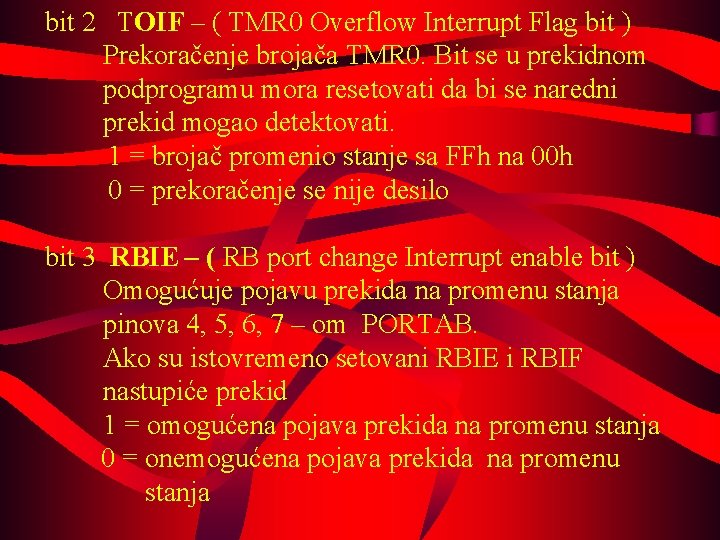

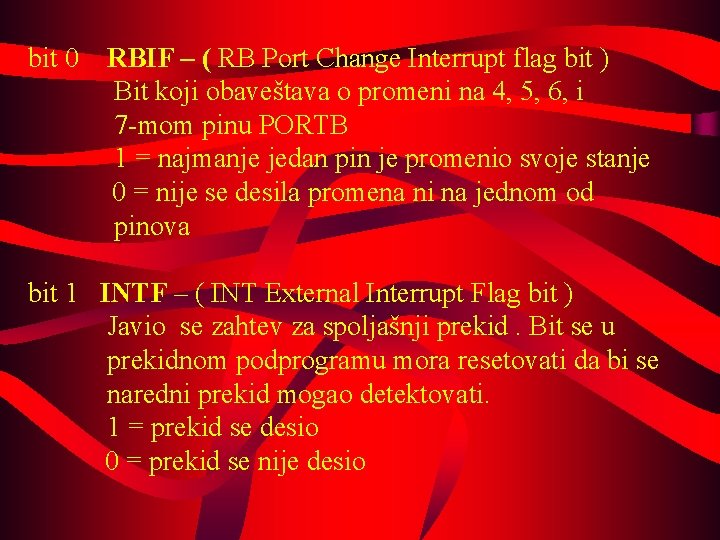

bit 0 RBIF – ( RB Port Change Interrupt flag bit ) Bit koji obaveštava o promeni na 4, 5, 6, i 7 -mom pinu PORTB 1 = najmanje jedan pin je promenio svoje stanje 0 = nije se desila promena ni na jednom od pinova bit 1 INTF – ( INT External Interrupt Flag bit ) Javio se zahtev za spoljašnji prekid. Bit se u prekidnom podprogramu mora resetovati da bi se naredni prekid mogao detektovati. 1 = prekid se desio 0 = prekid se nije desio

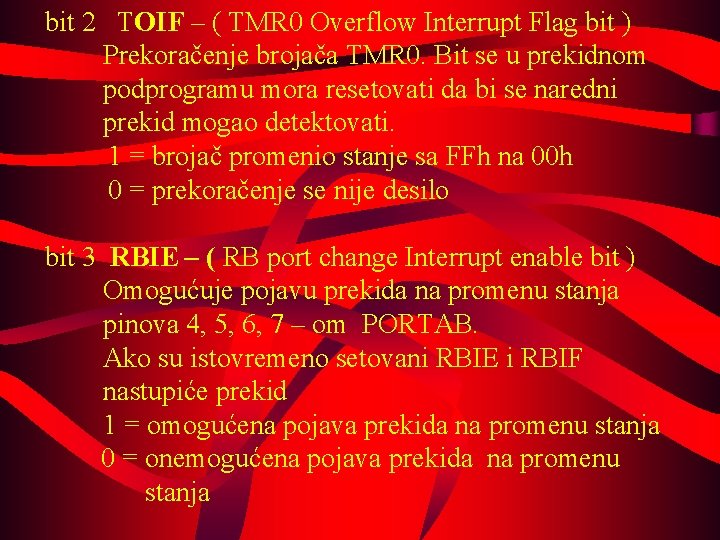

bit 2 TOIF – ( TMR 0 Overflow Interrupt Flag bit ) Prekoračenje brojača TMR 0. Bit se u prekidnom podprogramu mora resetovati da bi se naredni prekid mogao detektovati. 1 = brojač promenio stanje sa FFh na 00 h 0 = prekoračenje se nije desilo bit 3 RBIE – ( RB port change Interrupt enable bit ) Omogućuje pojavu prekida na promenu stanja pinova 4, 5, 6, 7 – om PORTAB. Ako su istovremeno setovani RBIE i RBIF nastupiće prekid 1 = omogućena pojava prekida na promenu stanja 0 = onemogućena pojava prekida na promenu stanja

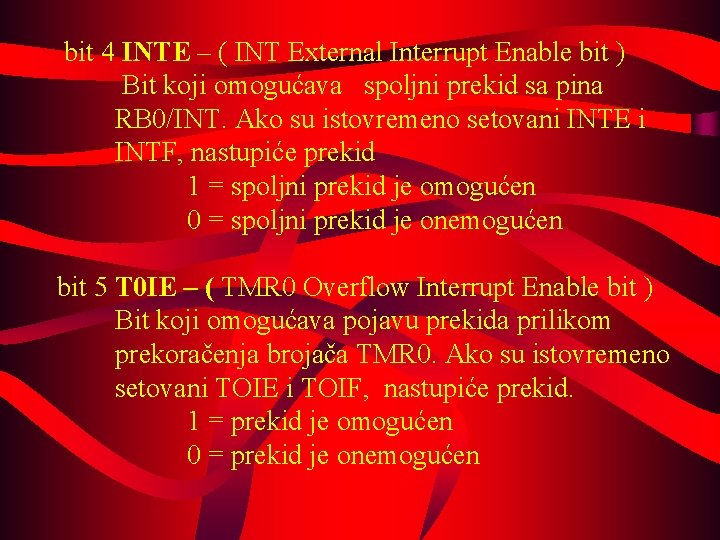

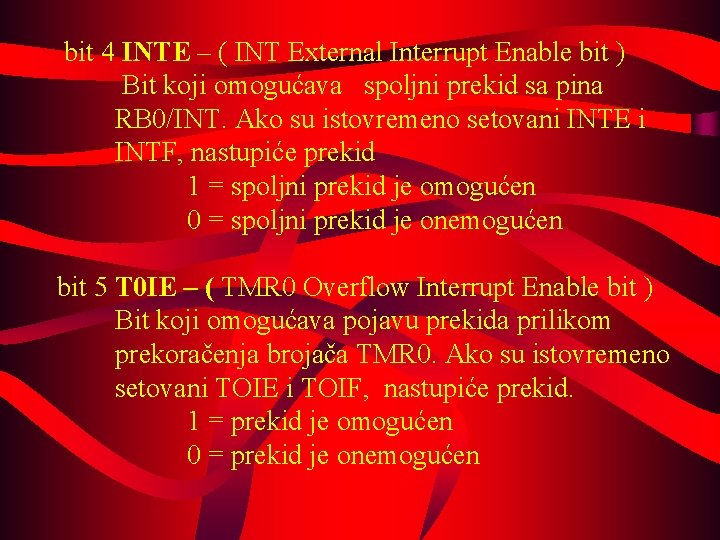

bit 4 INTE – ( INT External Interrupt Enable bit ) Bit koji omogućava spoljni prekid sa pina RB 0/INT. Ako su istovremeno setovani INTE i INTF, nastupiće prekid 1 = spoljni prekid je omogućen 0 = spoljni prekid je onemogućen bit 5 T 0 IE – ( TMR 0 Overflow Interrupt Enable bit ) Bit koji omogućava pojavu prekida prilikom prekoračenja brojača TMR 0. Ako su istovremeno setovani TOIE i TOIF, nastupiće prekid. 1 = prekid je omogućen 0 = prekid je onemogućen

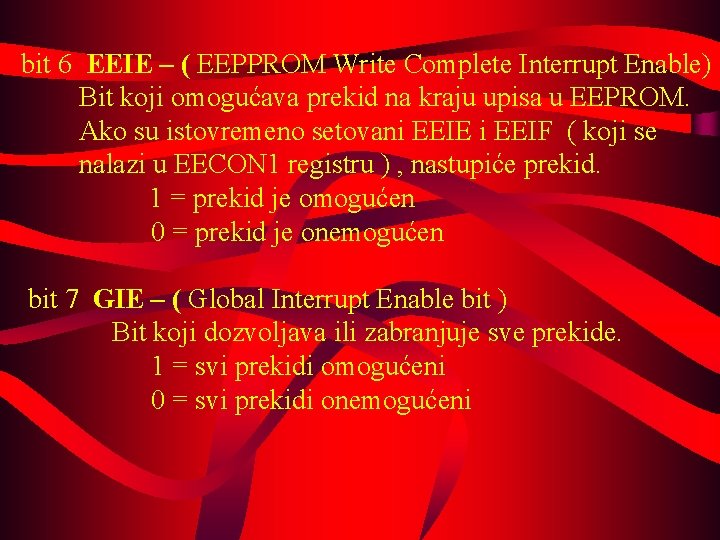

bit 6 EEIE – ( EEPPROM Write Complete Interrupt Enable) Bit koji omogućava prekid na kraju upisa u EEPROM. Ako su istovremeno setovani EEIE i EEIF ( koji se nalazi u EECON 1 registru ) , nastupiće prekid. 1 = prekid je omogućen 0 = prekid je onemogućen bit 7 GIE – ( Global Interrupt Enable bit ) Bit koji dozvoljava ili zabranjuje sve prekide. 1 = svi prekidi omogućeni 0 = svi prekidi onemogućeni

ALL PIC PROGRAMATOR

ALLPIC programator

Programator korišćen u ovom projektu namenjen je programiranju većine serijskih PIC mikrokontrolera. ( PIC 16 F 8 x, 16 F 62 x, 16 F 87 x, 12 C 50 x, 12 F 6 xx ). Odlikuju ga jednostavnost i kompaktnost. Povezuje se na računar preko serijskog porta. Za rad programatora potreban je i slabiji izvor napajanja ( 15 v ). Poseduje zaštitu od suprotno priključenog polariteta iz ispravljača. Izvor napajanja može da bude i naizmenični napon, a stabilisani napon od 5 v, potreban za napajanje mikrokontrolera obezbeđuje 78 L 05.

Indikator LED 1 (crvena) informiše o prisustvu napona napajanja programatora , i on treba da bude u granicama 14 v – 20 v, pri čemu treba računati da pri naponu od 20 v grejanje stabilizatora može biti primetno. Indikator LED 2 (zelena), indicira prisutan napon napajanja Vdd ( +5 v) na čipu koji se programira. Ukoliko je kratkospajač JP 1 spojen, Vdd ( +5 v ) napon će biti stalno prisutan, što će se videti upaljenom LED 2. Ovaj mod rada je namenjen Microchip PIC mikrokontrolerima koji nemaju interni oscilator ( 16 F 84, 16 F 87 x ), kao i EEPROM-ima.

Za mikrokontrolere ( 16 F 627, 16 F 628, 12 F 629, 12 F 657) potrebno je skinuti JP 1 i u tom modu Vdd se pojavljuje tek po uspostavljanju programskog napona Vpp ( 13 v ), na početku programiranja. Kratkospajač JP 2 služi za izbor write protect moda za EEPROME 24 Cxx. Poseban konektor, koji je na šemi označen kao CON 1, koristi se za eksterni priključak za in – circuit programiranje ( ICSP).

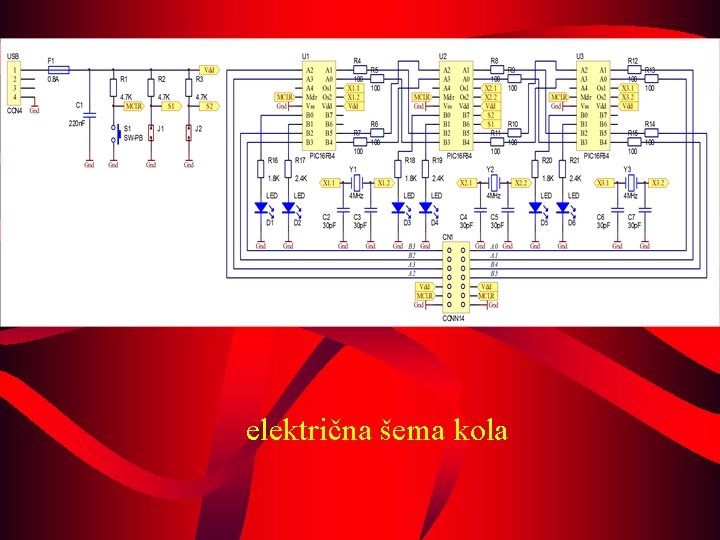

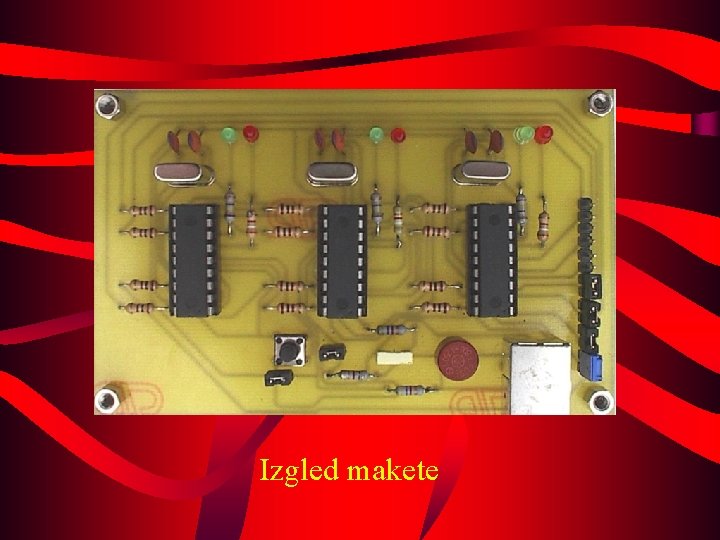

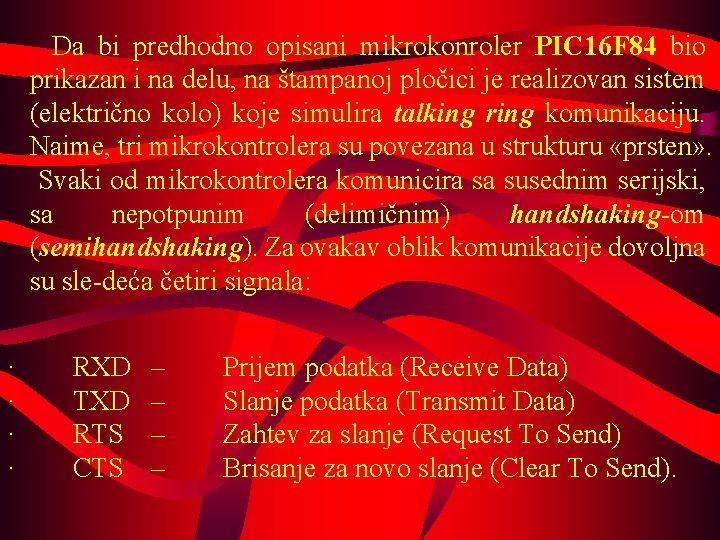

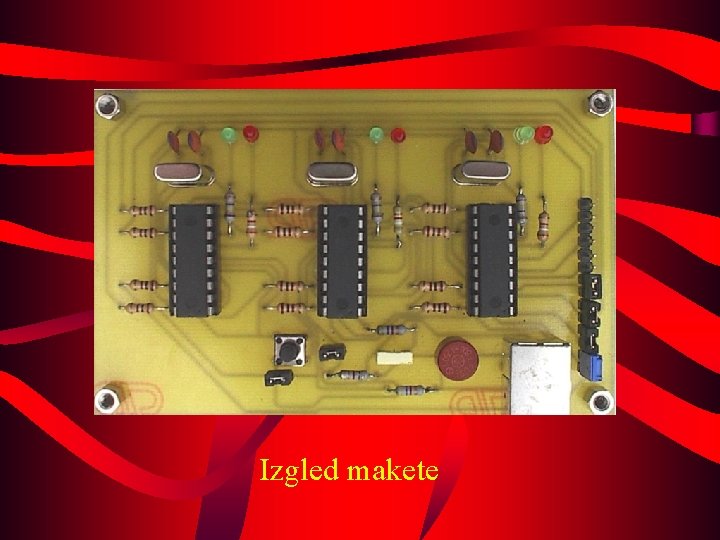

Da bi predhodno opisani mikrokonroler PIC 16 F 84 bio prikazan i na delu, na štampanoj pločici je realizovan sistem (električno kolo) koje simulira talking ring komunikaciju. Naime, tri mikrokontrolera su povezana u strukturu «prsten» . Svaki od mikrokontrolera komunicira sa susednim serijski, sa nepotpunim (delimičnim) handshaking-om (semihandshaking). Za ovakav oblik komunikacije dovoljna su sle-deća četiri signala: · RXD · TXD · RTS · CTS – – Prijem podatka (Receive Data) Slanje podatka (Transmit Data) Zahtev za slanje (Request To Send) Brisanje za novo slanje (Clear To Send).

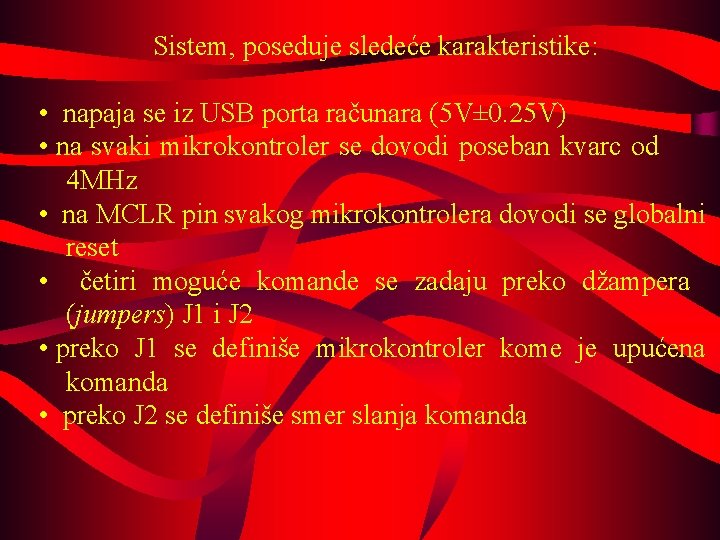

Sistem, poseduje sledeće karakteristike: • napaja se iz USB porta računara (5 V± 0. 25 V) • na svaki mikrokontroler se dovodi poseban kvarc od 4 MHz • na MCLR pin svakog mikrokontrolera dovodi se globalni reset • četiri moguće komande se zadaju preko džampera (jumpers) J 1 i J 2 • preko J 1 se definiše mikrokontroler kome je upućena komanda • preko J 2 se definiše smer slanja komanda

• token može da poseduje samo jedan mikrokontroler u jednom trenutku • za signalizaciju posedovanja token-a služe crvene LED • za signalizaciju izršavanja komande služe zelene LED • postoji mogućnost proširenja sistema preko 14 pinskog konektora.

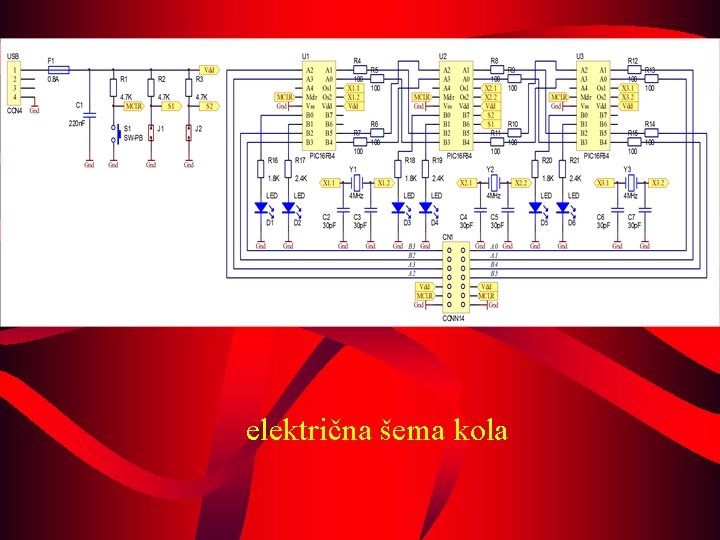

električna šema kola

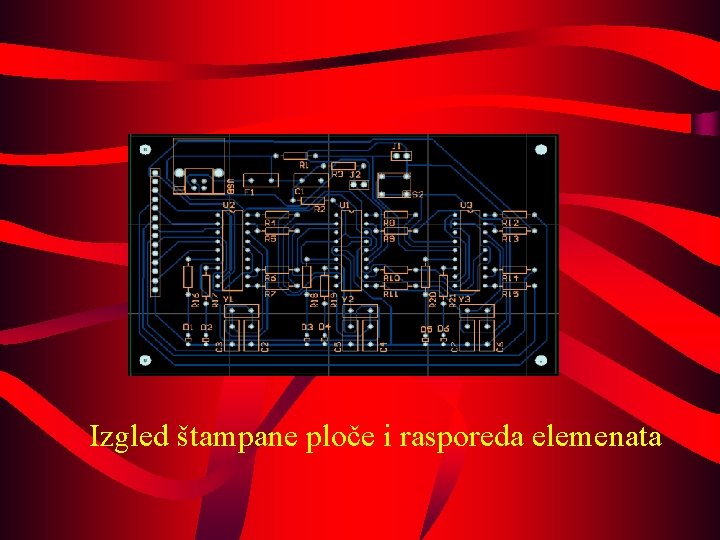

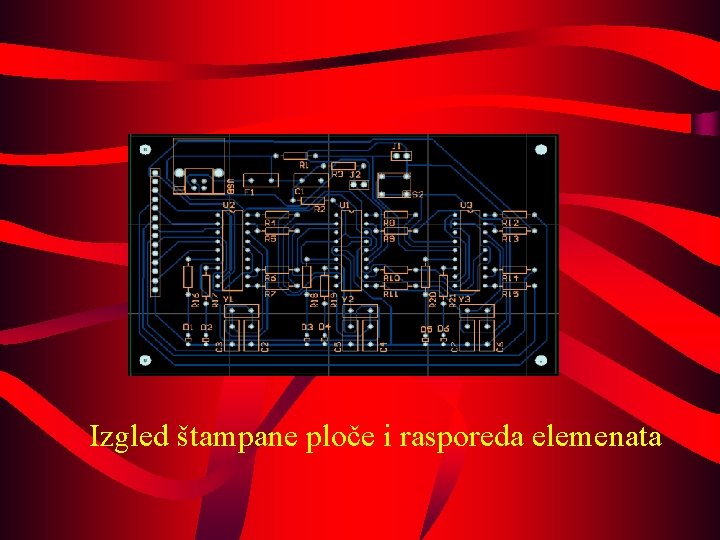

Izgled štampane ploče i rasporeda elemenata

Uređaj započinje svoj rad dovođenjem napajanja. U početnom trenutku mikrokontroler br. 1 (U 1) ima ulogu mastera. Njegova LED signalizacija predstavlja ovo stanje konstantno upaljenom crvenom diodom – koja signalizira posedovanje token-a, i konstantno upaljenom zelenom LED koja signalizira obavlja-nje zadatka, tj. obradu komande koja je zadata preko J 1 i J 2.

Postoje četiri moguće kombinacije. Mikrokontroler (U 2 ili U 3) koji je dobio informaciju preuzima token i ulogu master-a u sistemu, a zatim «čita» sadržaj primljene informacije (komande). Kao indikacija da je token u njegovom posedu, odgovarajuća crvena LED će konstantno da svetli (gori). Ukoliko pročitani sadržaj informacije ukazuje da je komanda namenjena njemu, ona se izvršava – generiše se povorka impulsa na pinu na kome je povezana odgovarajuća zelena LED, a zatim se vraća token mikrokontroleru br. 1 (U 1). Ako, međutim, komanda nije namenjena njemu, prosleđuje je sledećem mikrokontroleru u prstenu. Po izvršenoj komandi, mikrokontroler br. 1 (U 1) ponovo poseduje token i može da izvrši (eventualnu) sledeću komandu. U slučaju gubljenja token-a, posle određenog vremena, mikrokontroler br. 1 (U 1) generiše novi token i proces počinje iznova.

MOD 1 Režim prvog moda podrazumeva da su J 1 i J 2 otvoreni. Ovakvom kombinacijom J 1 i J 2, mikrolontroler U 1 se obraća mikrokontroleru U 2. Mikrokontroler U 2 po prijemu informacije signalizira svojom crvenom LED da je token u njegovom posedu i preuzima ulogu mastera. Kako pročitani sadržaj informacije ukazuje da je komanda namenjena njemu, on izvršava komandu, generiše povorku impulsa, a zelena LED indicira generisanu povorku impulsa. Po završenoj komandi, mikrokontroler U 2 vraća token mikrokontroleru U 1.

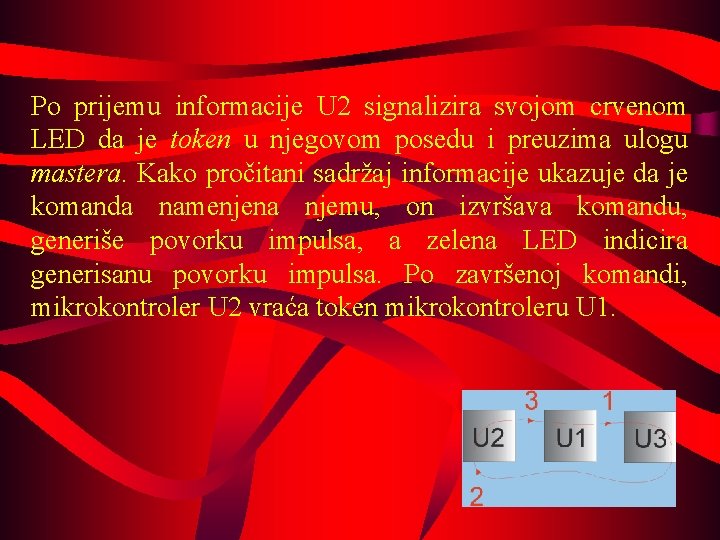

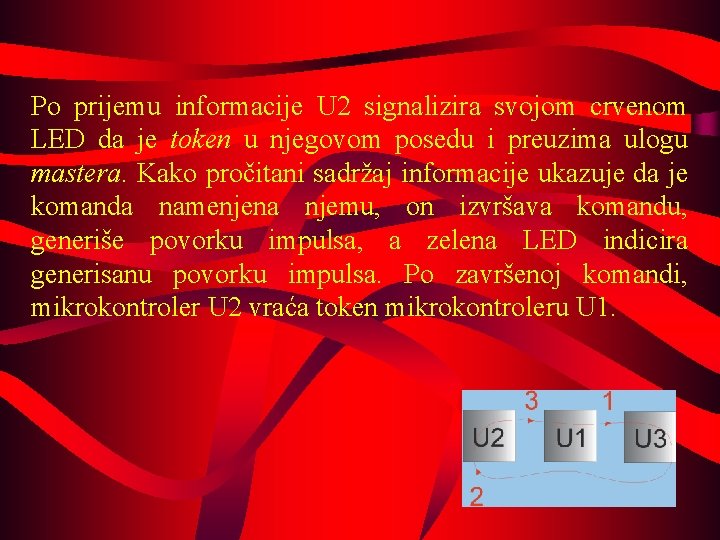

MOD 2 Režim drugog moda podrazumeva da je J 1 otvoren a J 2 zatvoren. Ovakvom konbinacijom J 1 i J 2, mikrokontroler U 1 se obraća mikrokontroleru U 2. Zatvaranjem J 2 promenjen je smer kretanja token-a prema mikrokontroleru U 2. Mikrokontroler U 1 šalje informaciju mikrokontroleru U 3, koji po prijemu informacije svojom crvenom LED signalizira da je token u njegovom posedu i preuzima ulogu mastera. Kako pročitani sadržaj informacije ukazuje da informacija nije namenjena njemu, on informaciju prosleđije sledećem mikrokontroleru – U 2.

Po prijemu informacije U 2 signalizira svojom crvenom LED da je token u njegovom posedu i preuzima ulogu mastera. Kako pročitani sadržaj informacije ukazuje da je komanda namenjena njemu, on izvršava komandu, generiše povorku impulsa, a zelena LED indicira generisanu povorku impulsa. Po završenoj komandi, mikrokontroler U 2 vraća token mikrokontroleru U 1.

MOD 3 Režim trećeg moda podrazumeva da je J 1 zatvoren a J 2 otvoren. Ovakvom konbinacijom J 1 i J 2, mikrokontroler U 1 se obraća mikrokontroleru U 3. Mikrokontroler U 1 šalje informaciju mikrokontroleru U 2, koji po prijemu informacije svojom crvenom LED signalizira da je token u njegovom posedu i preuzima ulogu mastera. Kako pročitani sadržaj informacije ukazuje da informacija nije namenjena njemu, on informaciju prosleđije sledećem mikrokontroleru – U 3. Po prijemu informacije U 3 signalizira svojom crvenom LED da je token u njegovom posedu i preuzima ulogu mastera.

Kako pročitani sadržaj informacije ukazuje da je komanda namenjena njemu, on izvršava komandu, generiše povorku impulsa, a zelena LED indicira generisanu povorku impulsa. Po završenoj komandi, mikrokontroler U 2 vraća token mikrokontroleru U 1.

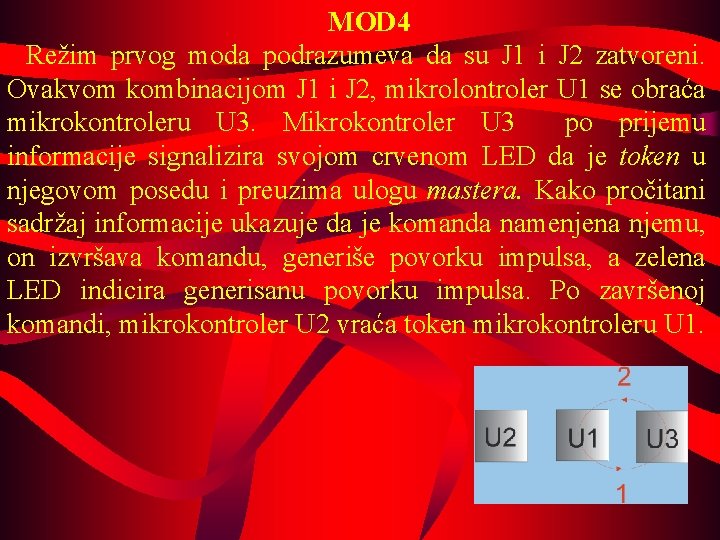

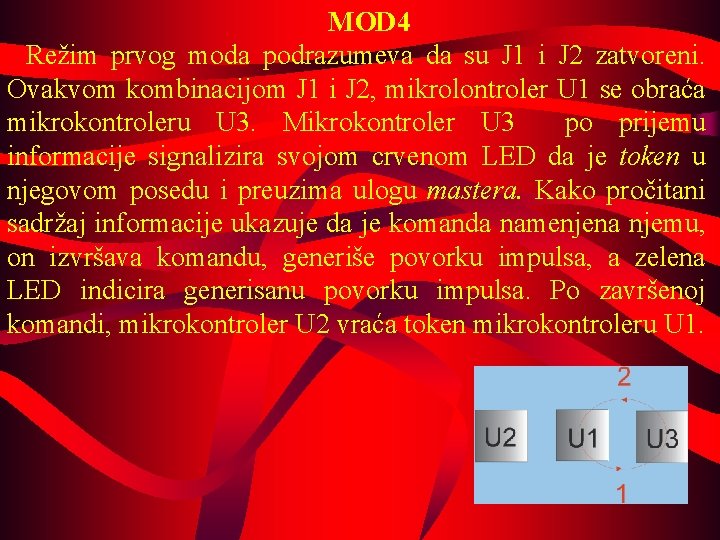

MOD 4 Režim prvog moda podrazumeva da su J 1 i J 2 zatvoreni. Ovakvom kombinacijom J 1 i J 2, mikrolontroler U 1 se obraća mikrokontroleru U 3. Mikrokontroler U 3 po prijemu informacije signalizira svojom crvenom LED da je token u njegovom posedu i preuzima ulogu mastera. Kako pročitani sadržaj informacije ukazuje da je komanda namenjena njemu, on izvršava komandu, generiše povorku impulsa, a zelena LED indicira generisanu povorku impulsa. Po završenoj komandi, mikrokontroler U 2 vraća token mikrokontroleru U 1.

Izgled makete

“TEORIJA FORMIRA PRAKSU. . . PRAKSA KORIGUJE TEORIJU”

Prezime: Antonijević Ime: Bojan Datum rođenja: 12. 09. 1973. Nacionalnost: Srbin Bračno stanje: Neoženjen Obrazovanje : Saradnik u prirodnim naukama IV stepen Gimnazija Svilajnac Apsolvent Elektronskog fakulteta u Nišu Student fakulteta civilne odbrane u Beogradu Pirotehničar Živi i radi u selu Roćevcu kod Svilajnca, vlasnik privarne firme „ANTES“ – Svilajnac. Bavi se izradom i održavanjem uređaja za saobraćajnu signalizaciju i projektovanjem mikrokontrolerskih uređaja.

Prezime: Ime: Datum rođenja: Nacionalnost: Bračno stanje: Županjac Dragan 02. 01. 1971. Srbin Oženjen Marijanom, otac Nemanje i Obrazovanje : Stefana Elektrotehničar za Radio TV tehniku Elektrotehnička škola u Kraljevu Apsolvent Elektronskog fakulteta u Nišu Licencirani serviser Fiskalnih uređaja, prateće opreme i softvera Galeb GROUP –Šabac. Živi i radi u Nišu, zaposlen u „MIKOPS-u“, nalazi se na radnom mestu Servisera Fiskalnih registar kasa i GPRS uređaja. Bavi se grafičkom obradom, softverskim projektovanjem za komunikaciju računara i Fiskalnih uređaja, kao i projektovanjem PCB- štampanih kola.