ELEKTRONSKI FAKULTET U NIU KATEDRA ZA ELEKTRONIKU SEMINARSKI

- Slides: 57

ELEKTRONSKI FAKULTET U NIŠU KATEDRA ZA ELEKTRONIKU SEMINARSKI RAD VHDL OPIS SAYEH PROCESORA Predmet: Mikroprocesorski sistemi Profesor: Prof. dr. Mile Stojčev Studenti: Nikola Sekulović (10963) Lazar Velimirović (11017) Niš, jul 2007.

SAYEH U delu koji sledi prikazaćemo dizajn i opis procesora. CPU je SAYEH ( Simple Architecture, Yet Enough Hardware jednostavna arhitektura, ali sa dovoljno hardvera) koji je dizajniran za svrhe učenja i testiranja.

Detalji funkcionalnosti procesora n Jednostavan CPU primer koji je ovde razmatran ima registarsko polje koje se koristi za instrukcije za obradu podataka. n CPU ima 16 -bitnu magistralu podataka i 16 bitnu adresnu magistralu.

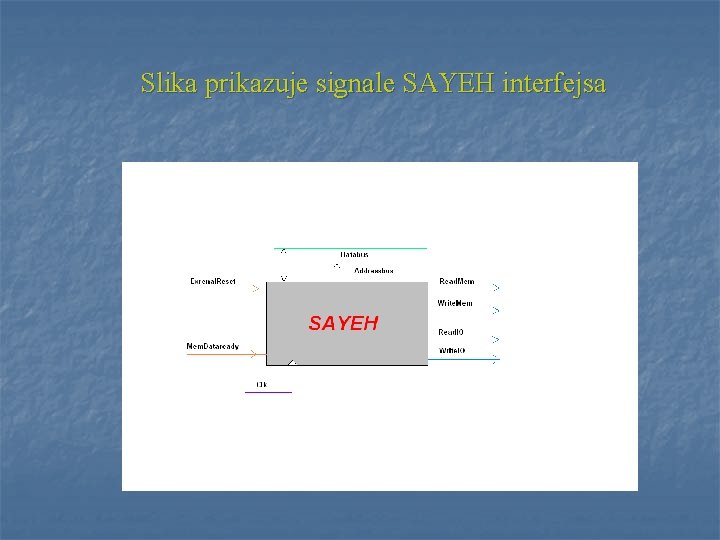

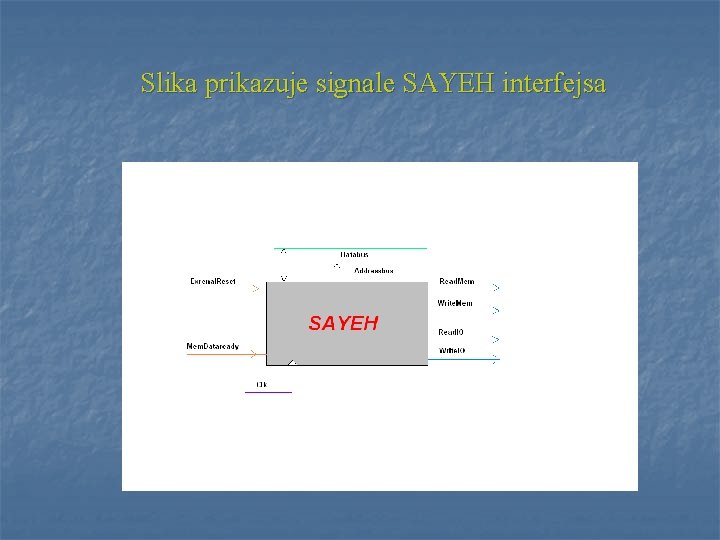

Slika prikazuje signale SAYEH interfejsa

Komponente CPU-a n SAYEH komponente koje se koriste za instrukcije uključuju standardne registre kao što su: 1. programski brojač 2. instrukcioni registar 3. aritmetičko-logička jedinica i 4. statusni registar.

Komponenete CPU-a Ovaj procesor ima registre koji čine polje registara R 0, R 1, R 2, R 3, kao i pokazivač prozora (Window Pointer) koji definiše R 0, R 1, R 2, R 3 unutar polja registara

Komponenete CPU-a n CPU komponente i kratak opis svake: - PC: Programski brojač, 16 bitova - R 0, R 1, R 2, R 3 registri opšte namene koji su deo polja registara, 16 bita -Reg. File: Registri opšte namene koji čine prozor od 4 registra u registarskom polju od 8 registara

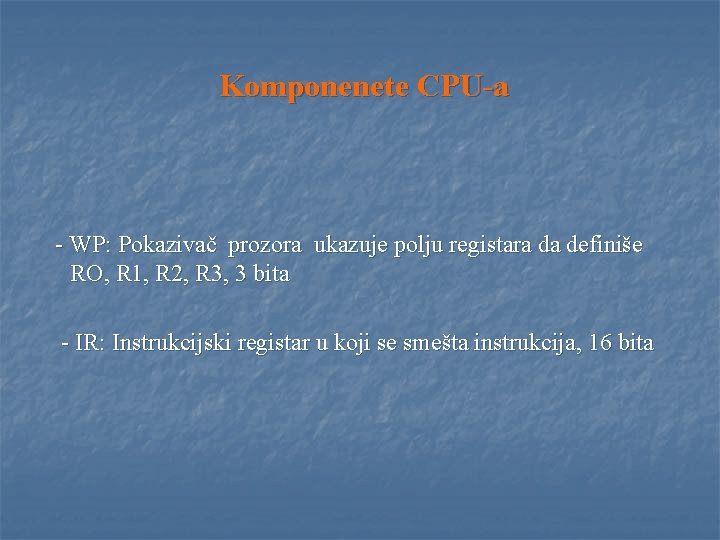

Komponenete CPU-a - WP: Pokazivač prozora ukazuje polju registara da definiše RO, R 1, R 2, R 3, 3 bita - IR: Instrukcijski registar u koji se smešta instrukcija, 16 bita

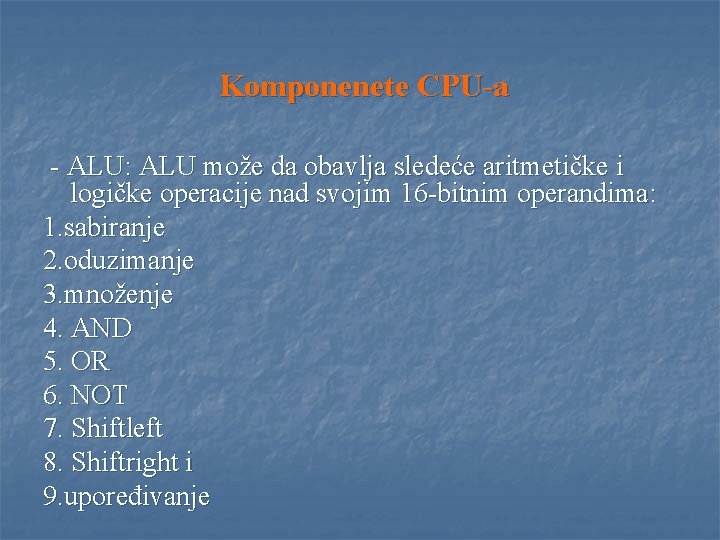

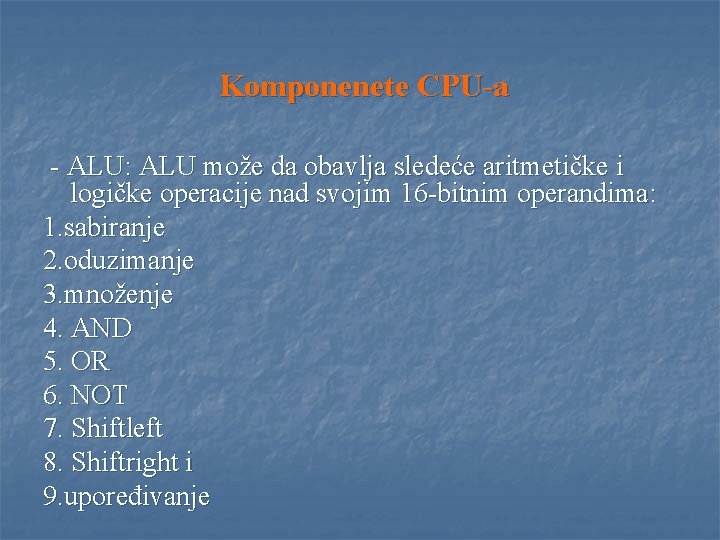

Komponenete CPU-a - ALU: ALU može da obavlja sledeće aritmetičke i logičke operacije nad svojim 16 -bitnim operandima: 1. sabiranje 2. oduzimanje 3. množenje 4. AND 5. OR 6. NOT 7. Shiftleft 8. Shiftright i 9. upoređivanje

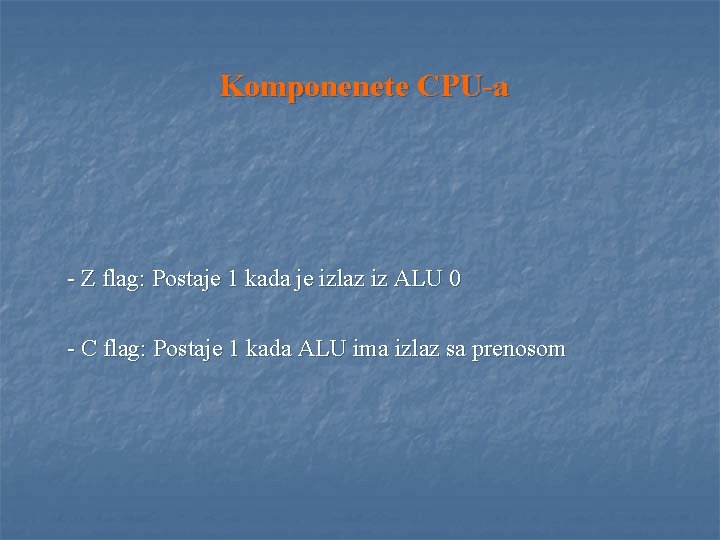

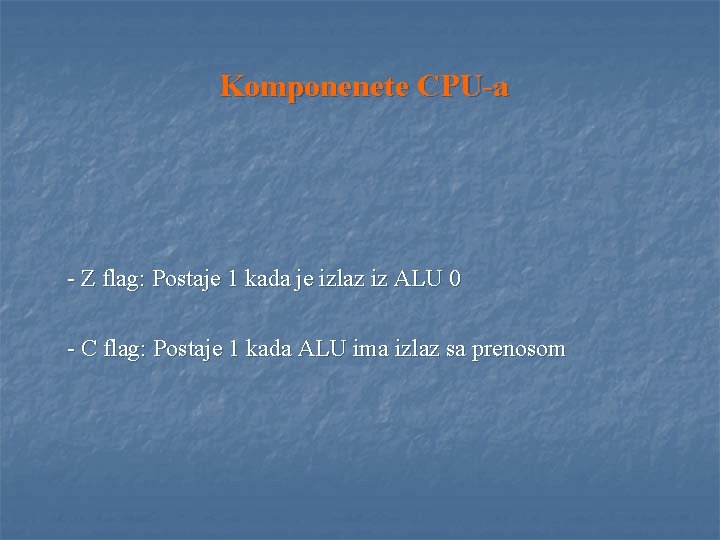

Komponenete CPU-a - Z flag: Postaje 1 kada je izlaz iz ALU 0 - C flag: Postaje 1 kada ALU ima izlaz sa prenosom

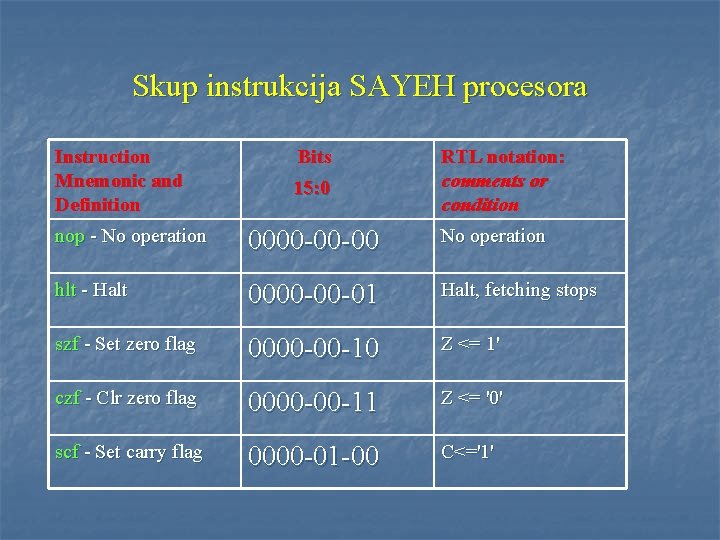

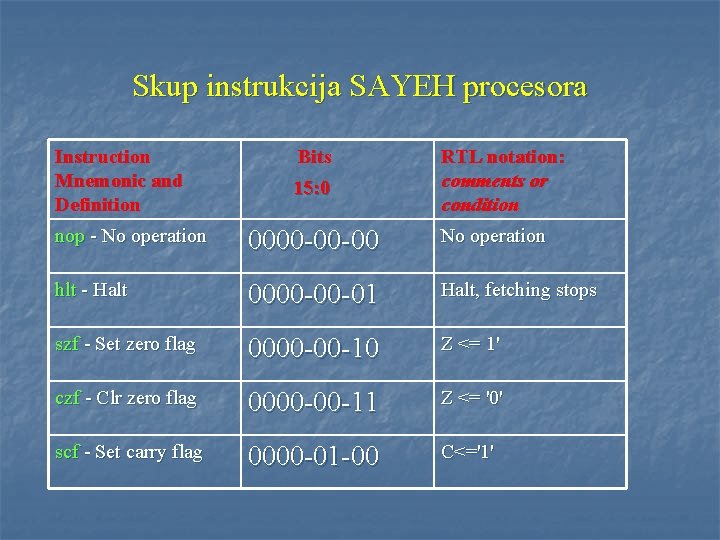

Skup instrukcija SAYEH procesora Instruction Mnemonic and Definition Bits 15: 0 RTL notation: comments or condition nop - No operation 0000 -00 -00 No operation hlt - Halt 0000 -00 -01 Halt, fetching stops szf - Set zero flag 0000 -00 -10 Z <= 1' czf - Clr zero flag 0000 -00 -11 Z <= '0' scf - Set carry flag 0000 -01 -00 C<='1'

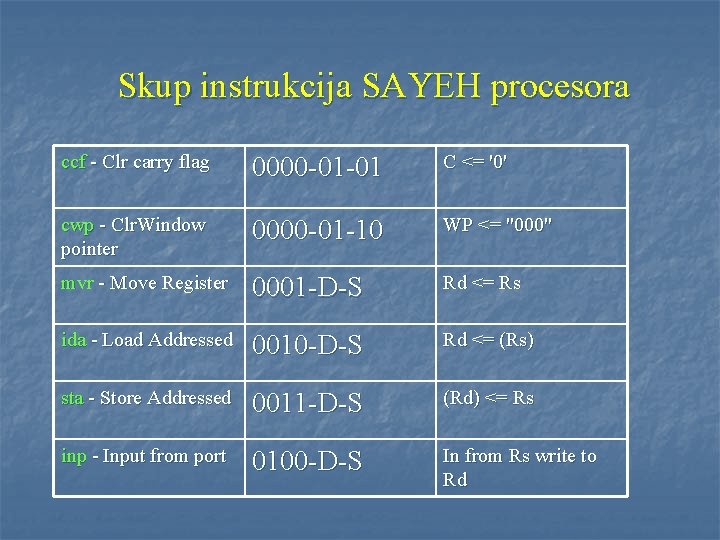

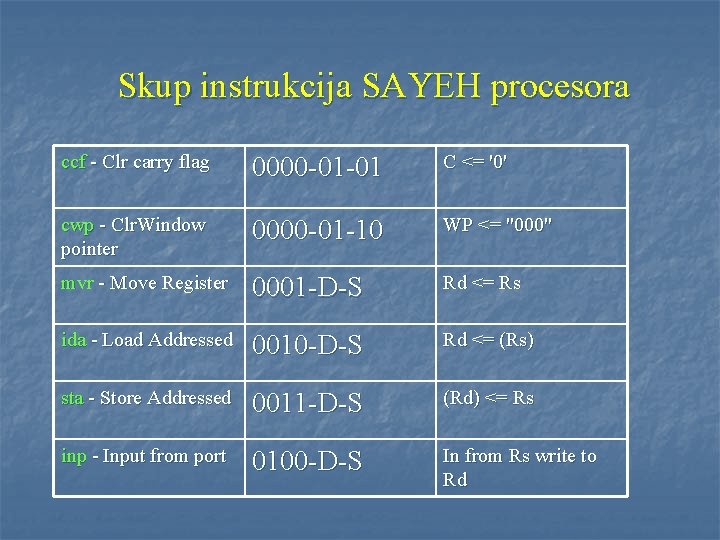

Skup instrukcija SAYEH procesora ccf - Clr carry flag 0000 -01 -01 C <= '0' cwp - Clr. Window pointer 0000 -01 -10 WP <= "000" mvr - Move Register 0001 -D-S Rd <= Rs ida - Load Addressed 0010 -D-S Rd <= (Rs) sta - Store Addressed 0011 -D-S (Rd) <= Rs inp - Input from port 0100 -D-S In from Rs write to Rd

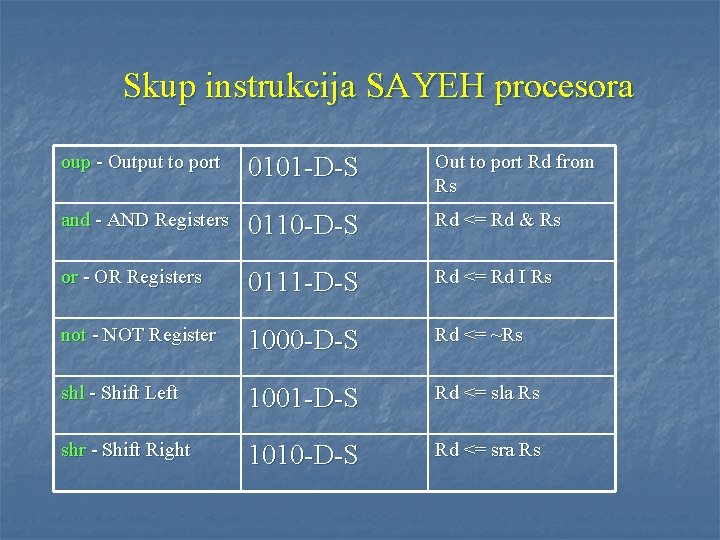

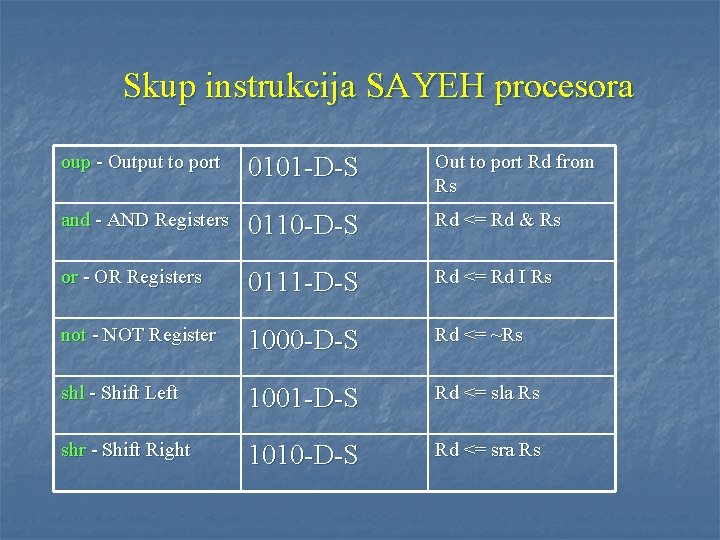

Skup instrukcija SAYEH procesora oup - Output to port 0101 -D-S Out to port Rd from Rs and - AND Registers 0110 -D-S Rd <= Rd & Rs or - OR Registers 0111 -D-S Rd <= Rd I Rs not - NOT Register 1000 -D-S Rd <= ~Rs shl - Shift Left 1001 -D-S Rd <= sla Rs shr - Shift Right 1010 -D-S Rd <= sra Rs

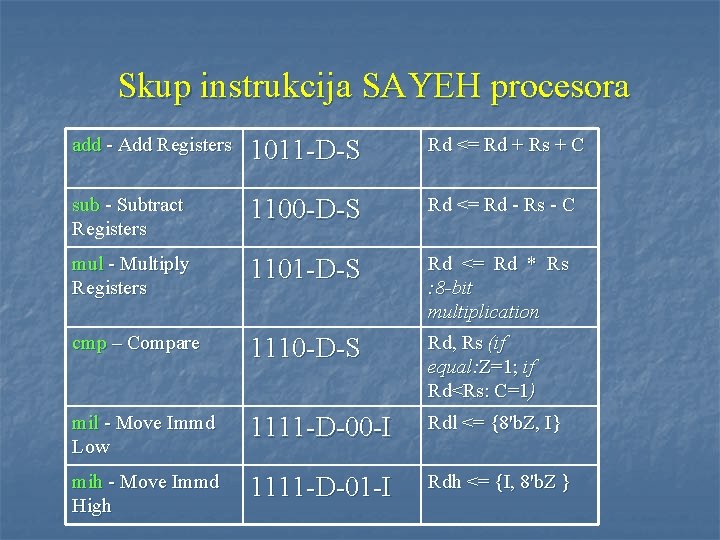

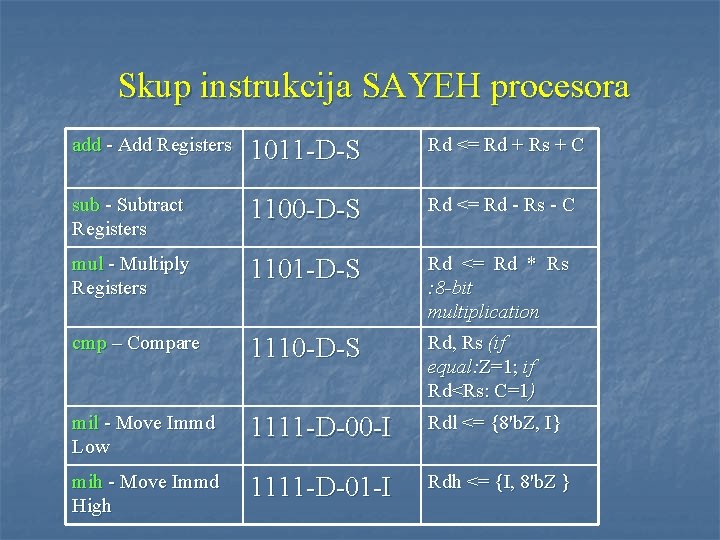

Skup instrukcija SAYEH procesora add - Add Registers 1011 -D-S Rd <= Rd + Rs + C sub - Subtract Registers 1100 -D-S Rd <= Rd - Rs - C mul - Multiply Registers 1101 -D-S Rd <= Rd * Rs : 8 -bit multiplication cmp – Compare 1110 -D-S Rd, Rs (if equal: Z=1; if Rd<Rs: C=1) mil - Move Immd Low 1111 -D-00 -I Rdl <= {8'b. Z, I} mih - Move Immd High 1111 -D-01 -I Rdh <= {I, 8'b. Z }

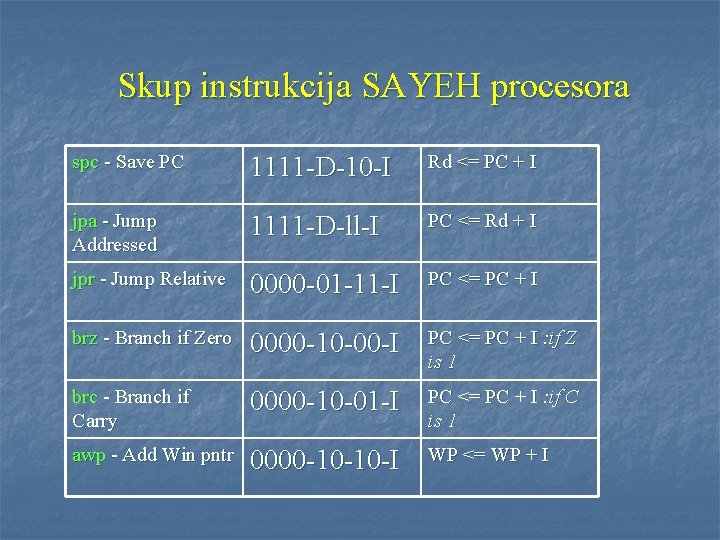

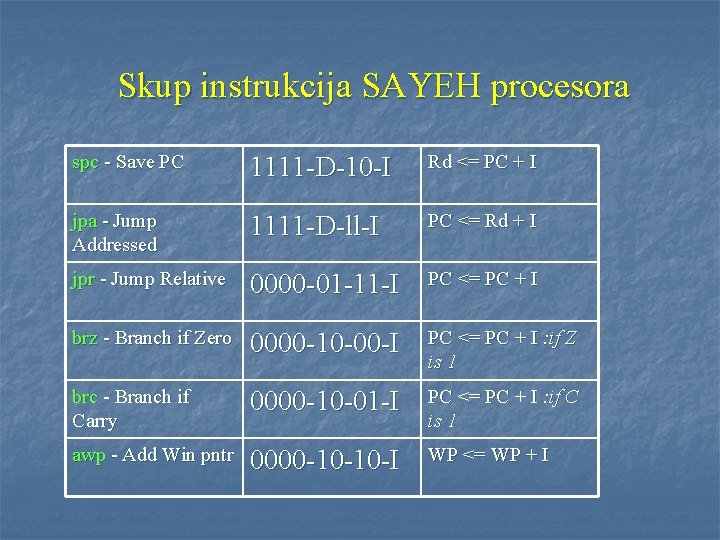

Skup instrukcija SAYEH procesora spc - Save PC 1111 -D-10 -I Rd <= PC + I jpa - Jump Addressed 1111 -D-ll-I PC <= Rd + I jpr - Jump Relative 0000 -01 -11 -I PC <= PC + I brz - Branch if Zero 0000 -10 -00 -I PC <= PC + I : if Z is 1 brc - Branch if Carry 0000 -10 -01 -I PC <= PC + I : if C is 1 awp - Add Win pntr 0000 -10 -10 -I WP <= WP + I

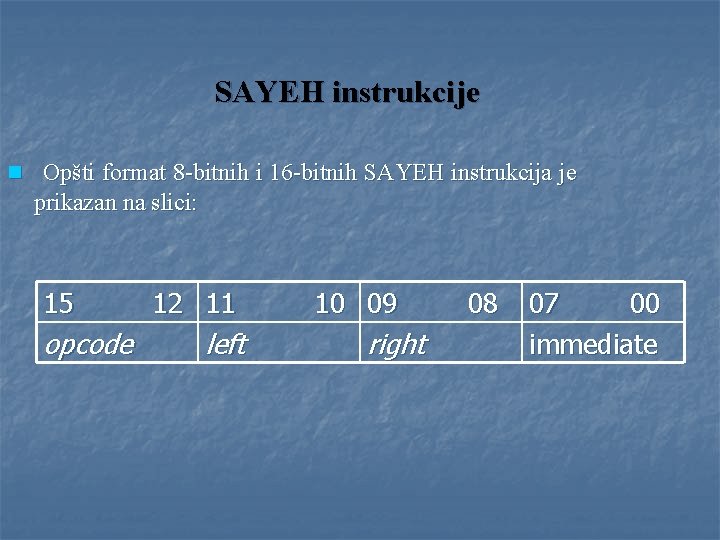

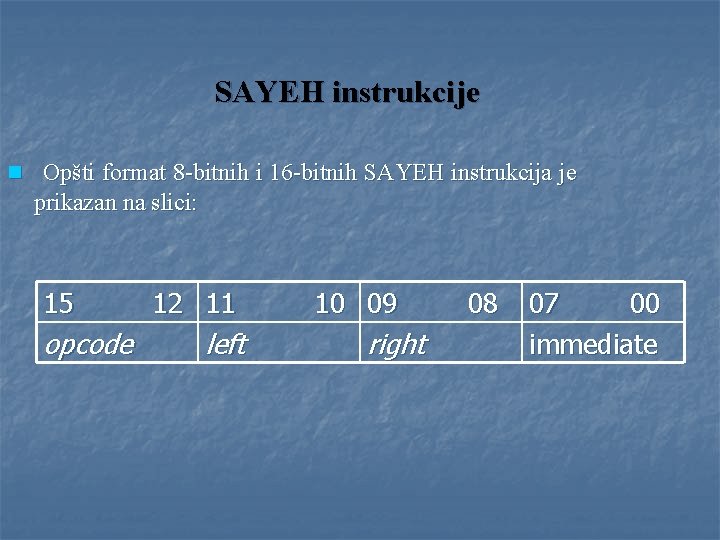

SAYEH instrukcije n Opšti format 8 -bitnih i 16 -bitnih SAYEH instrukcija je prikazan na slici: 15 opcode 12 11 left 10 09 right 08 07 00 immediate

SAYEH instrukcije - OPCODE polje je 4 -bitni kod koji odredjuje tip instrukcije. - Polja Left (levo) i Right (desno) su 2 -bitni kodovi koji biraju registre R 0 do R 3 za izvor i/ili odredište instrukcije. Obično, Left se koristi za odredište, a Right za izvor. - Immediate polje se koristi za trenutne podatke, ili ako su dve 8 -bitne instrukcije zapakovane koristi se za drugu instrukciju.

SAYEH instrukcije - Naš procesor ima ukupno 29 instrukcija - Instrukcije sa I trenutnim poljem su 16 -bitne instrukcije a ostale su 8 -bitne instrukcije - Instrukcije koriste polja Destination (odredište) i Source (izvor) (označeni sa D i S u tabeli seta instrukcija) imaju OPCODE koji je ograničen na 4 bita - Instrukcije koje ne zahtevaju specifikaciju izvornih i odredišnih registara korise ova polja kao OPCODE ekstenzije

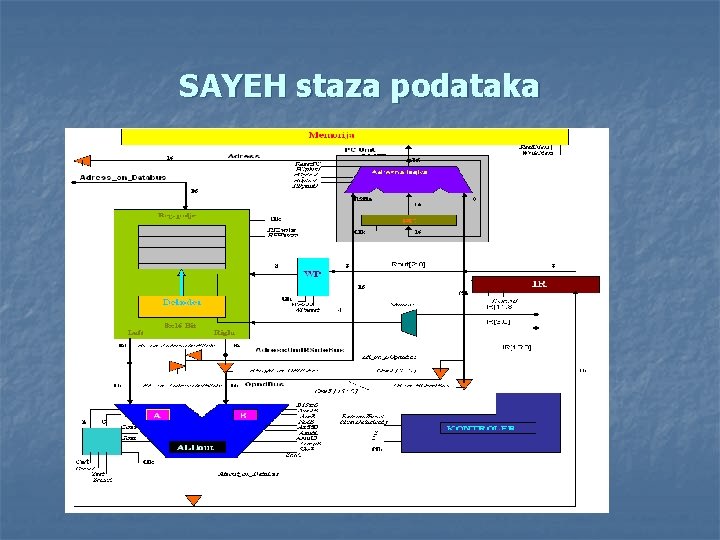

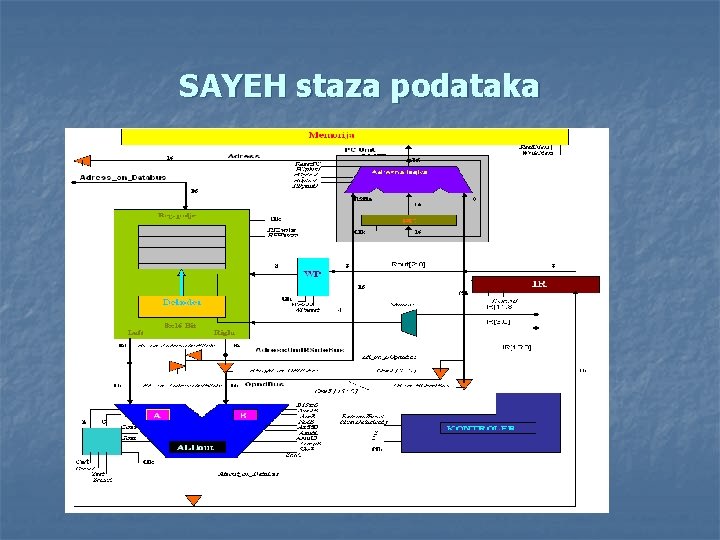

SAYEH staza podataka Glavne komponente SAYEH procesora su Addressing Unit(adresna jedinica) koja se sastoji od PC (Program Counter-programski brojač) i Address Logic (adresna logika), IR (instrukcioni registar), WP (Window Pointer), Register File koji se sastoji od Left Decoder 1 i Right Decoder 2, ALU (aritmetičko-logička jedinica) i Flags (zastavice).

SAYEH staza podataka

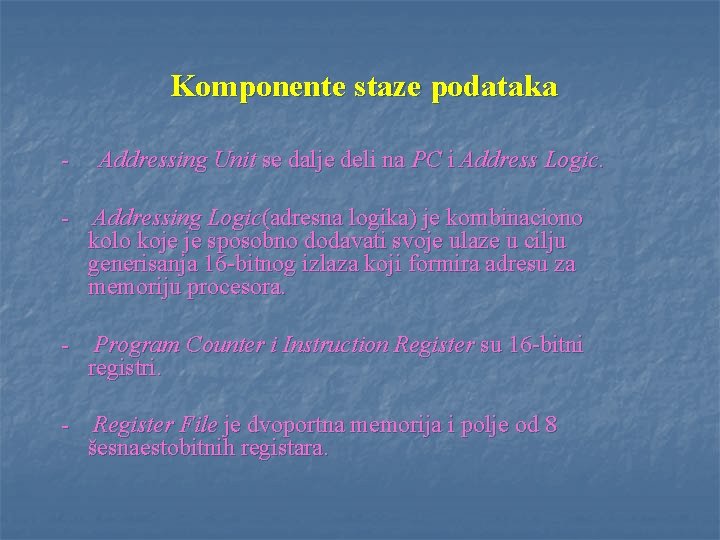

Komponente staze podataka Slika pokazuje hijerarhijsku strukturu SAYEH komponenti.

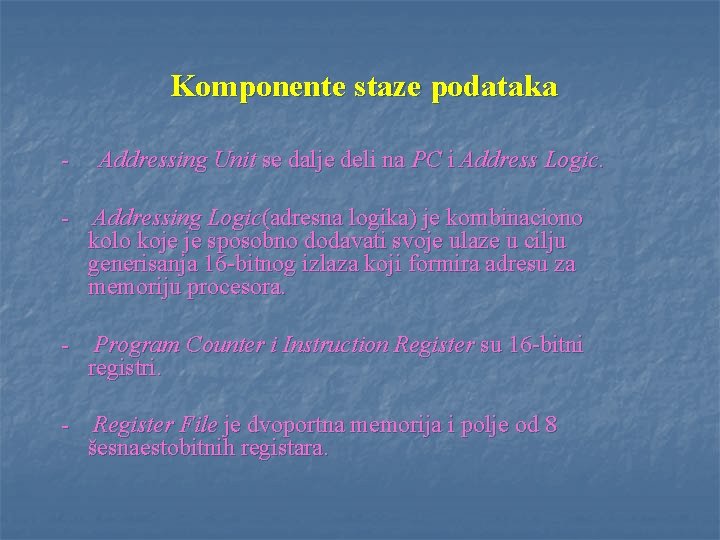

Komponente staze podataka - Addressing Unit se dalje deli na PC i Address Logic. - Addressing Logic(adresna logika) je kombinaciono kolo koje je sposobno dodavati svoje ulaze u cilju generisanja 16 -bitnog izlaza koji formira adresu za memoriju procesora. - Program Counter i Instruction Register su 16 -bitni registri. - Register File je dvoportna memorija i polje od 8 šesnaestobitnih registara.

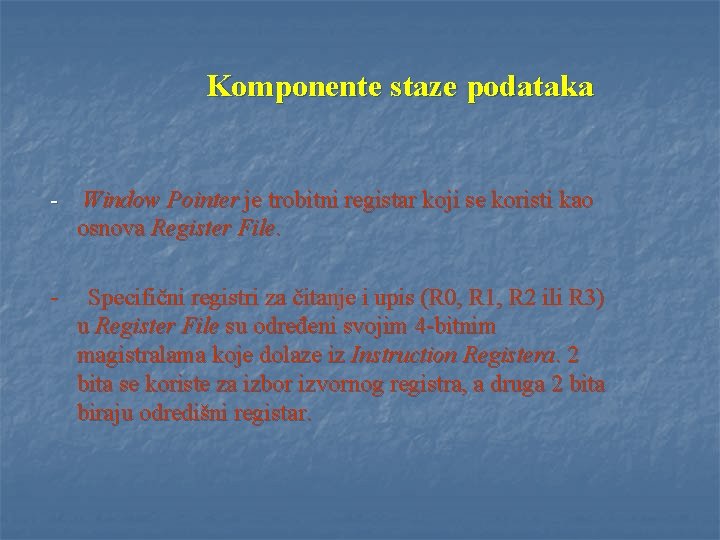

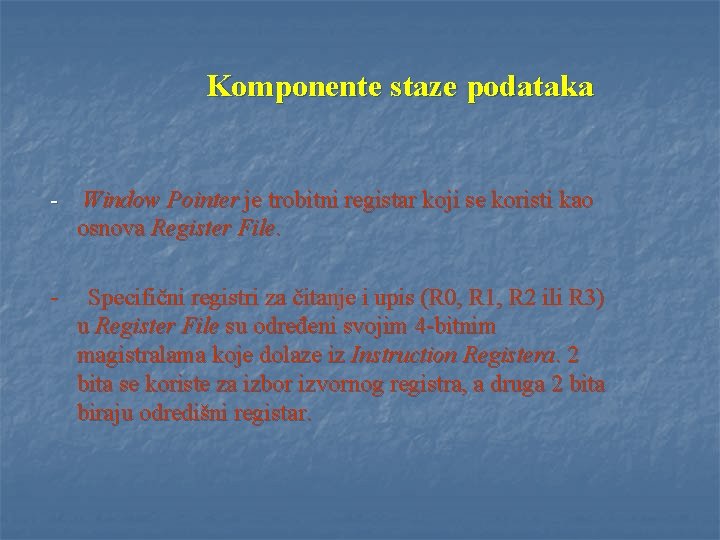

Komponente staze podataka - Window Pointer je trobitni registar koji se koristi kao osnova Register File. - Specifični registri za čitanje i upis (R 0, R 1, R 2 ili R 3) u Register File su određeni svojim 4 -bitnim magistralama koje dolaze iz Instruction Registera. 2 bita se koriste za izbor izvornog registra, a druga 2 bita biraju odredišni registar.

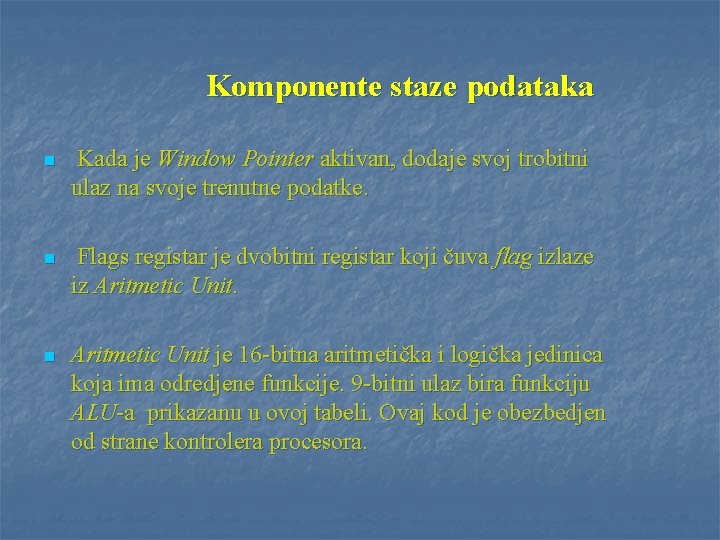

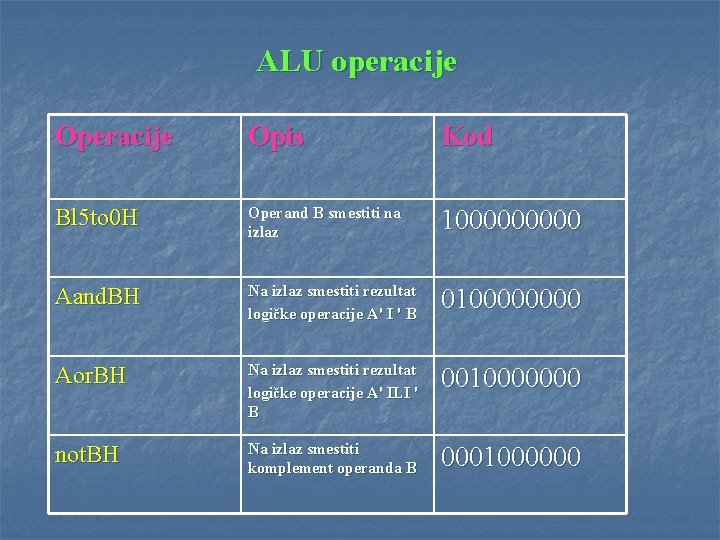

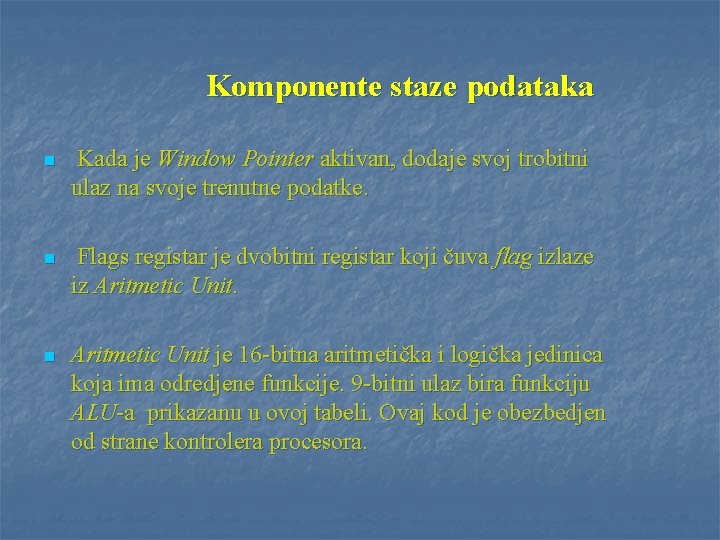

Komponente staze podataka n Kada je Window Pointer aktivan, dodaje svoj trobitni ulaz na svoje trenutne podatke. n Flags registar je dvobitni registar koji čuva flag izlaze iz Aritmetic Unit. n Aritmetic Unit je 16 -bitna aritmetička i logička jedinica koja ima odredjene funkcije. 9 -bitni ulaz bira funkciju ALU-a prikazanu u ovoj tabeli. Ovaj kod je obezbedjen od strane kontrolera procesora.

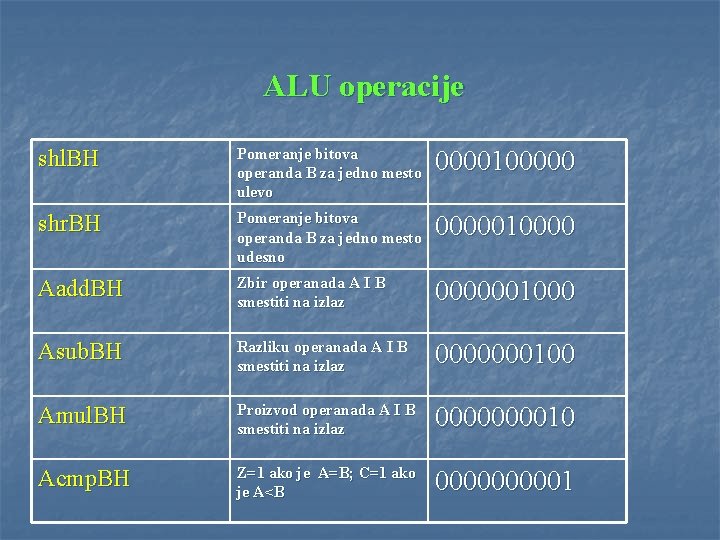

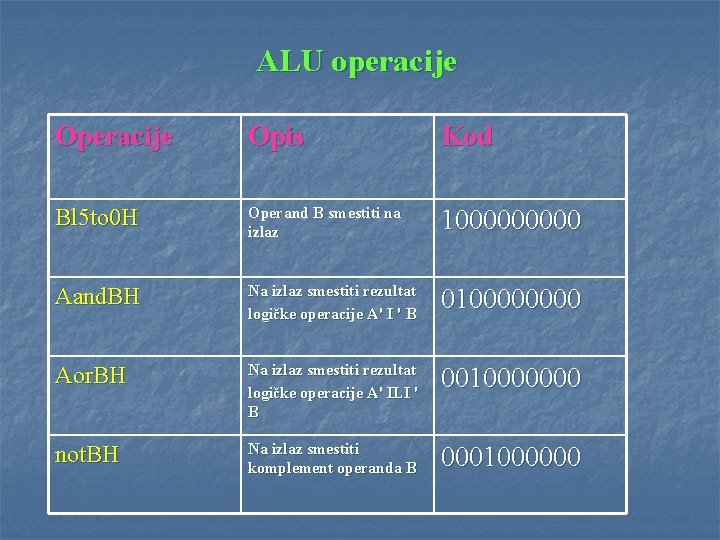

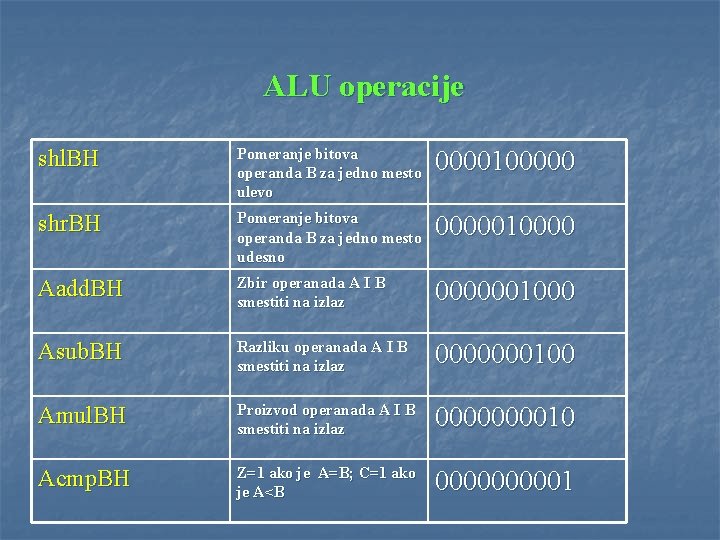

ALU operacije Opis Kod Bl 5 to 0 H Operand B smestiti na izlaz 100000 Aand. BH Na izlaz smestiti rezultat logičke operacije A' I ' B 010000 Aor. BH Na izlaz smestiti rezultat logičke operacije A' ILI ' B 0010000000 not. BH Na izlaz smestiti komplement operanda B 0001000000

ALU operacije shl. BH Pomeranje bitova operanda B za jedno mesto ulevo 0000100000 shr. BH Pomeranje bitova operanda B za jedno mesto udesno 0000010000 Aadd. BH Zbir operanada A I B smestiti na izlaz 0000001000 Asub. BH Razliku operanada A I B smestiti na izlaz 0000000100 Amul. BH Proizvod operanada A I B smestiti na izlaz 000010 Acmp. BH Z=1 ako je A=B; C=1 ako je A<B 000001

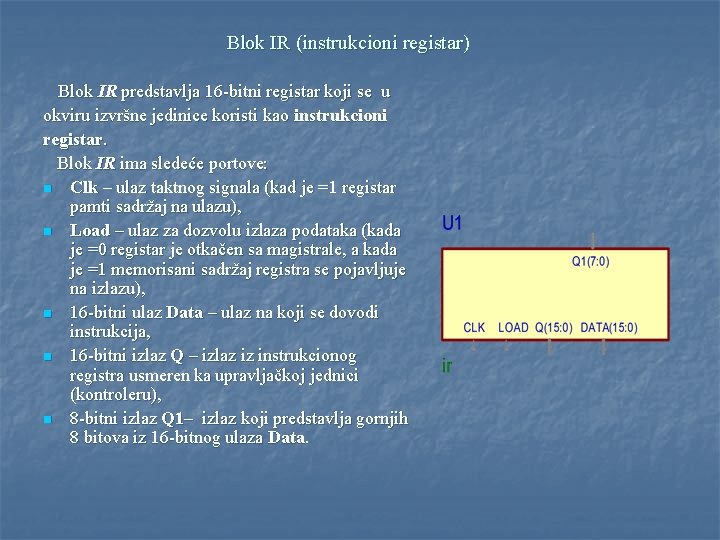

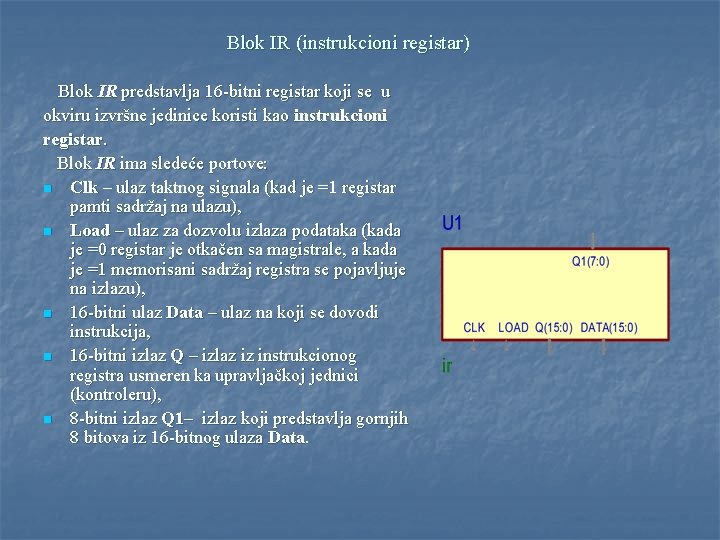

Blok IR (instrukcioni registar) Blok IR predstavlja 16 -bitni registar koji se u okviru izvršne jedinice koristi kao instrukcioni registar. Blok IR ima sledeće portove: n Clk – ulaz taktnog signala (kad je =1 registar pamti sadržaj na ulazu), n Load – ulaz za dozvolu izlaza podataka (kada je =0 registar je otkačen sa magistrale, a kada je =1 memorisani sadržaj registra se pojavljuje na izlazu), n 16 -bitni ulaz Data – ulaz na koji se dovodi instrukcija, n 16 -bitni izlaz Q – izlaz iz instrukcionog registra usmeren ka upravljačkoj jednici (kontroleru), n 8 -bitni izlaz Q 1– izlaz koji predstavlja gornjih 8 bitova iz 16 -bitnog ulaza Data.

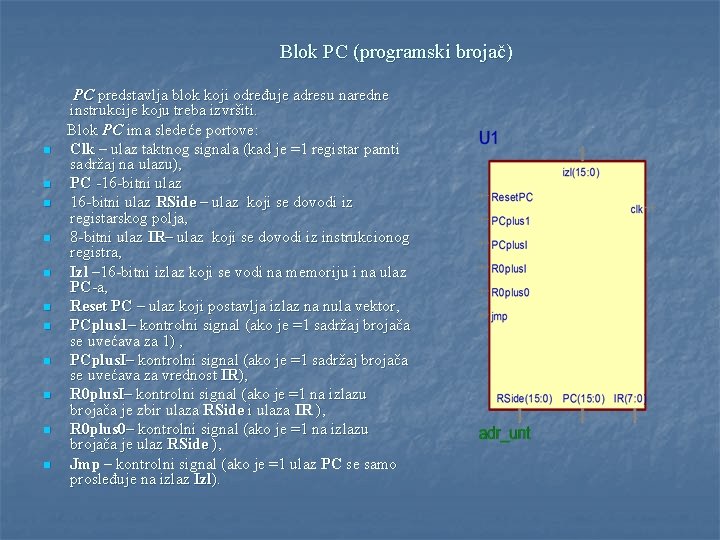

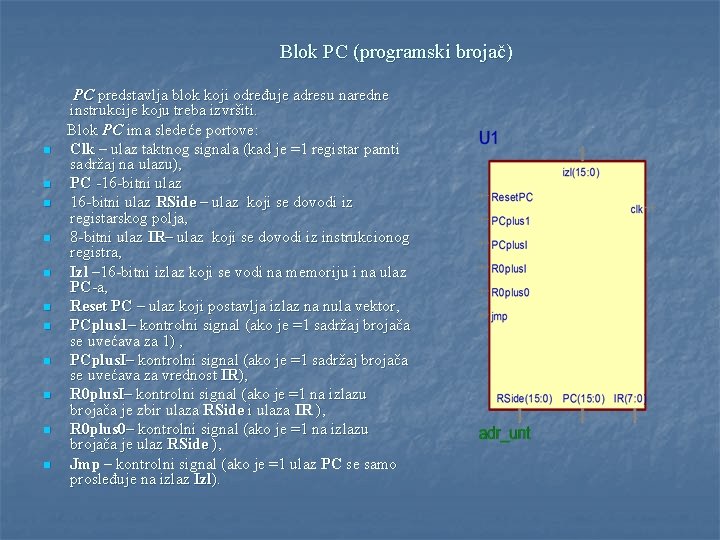

Blok PC (programski brojač) n n n PC predstavlja blok koji određuje adresu naredne instrukcije koju treba izvršiti. Blok PC ima sledeće portove: Clk – ulaz taktnog signala (kad je =1 registar pamti sadržaj na ulazu), PC -16 -bitni ulaz RSide – ulaz koji se dovodi iz registarskog polja, 8 -bitni ulaz IR– ulaz koji se dovodi iz instrukcionog registra, Izl – 16 -bitni izlaz koji se vodi na memoriju i na ulaz PC-a, Reset PC – ulaz koji postavlja izlaz na nula vektor, PCplus 1– kontrolni signal (ako je =1 sadržaj brojača se uvećava za 1) , PCplus. I– kontrolni signal (ako je =1 sadržaj brojača se uvećava za vrednost IR), R 0 plus. I– kontrolni signal (ako je =1 na izlazu brojača je zbir ulaza RSide i ulaza IR ), R 0 plus 0– kontrolni signal (ako je =1 na izlazu brojača je ulaz RSide ), Jmp – kontrolni signal (ako je =1 ulaz PC se samo prosleđuje na izlaz Izl).

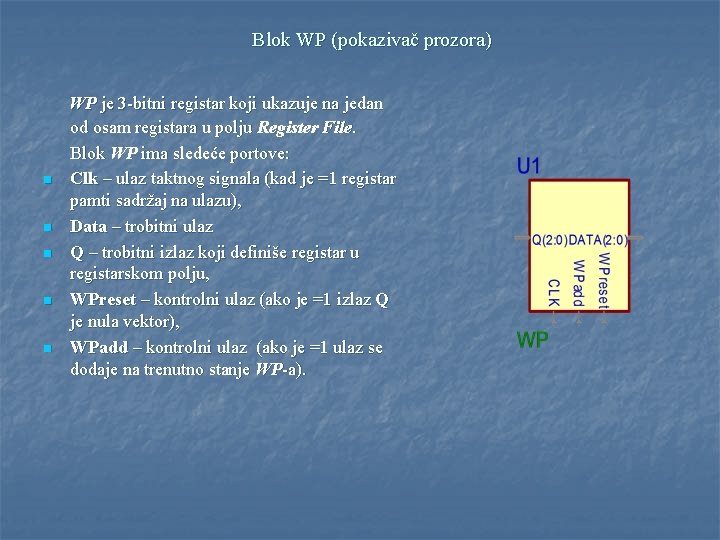

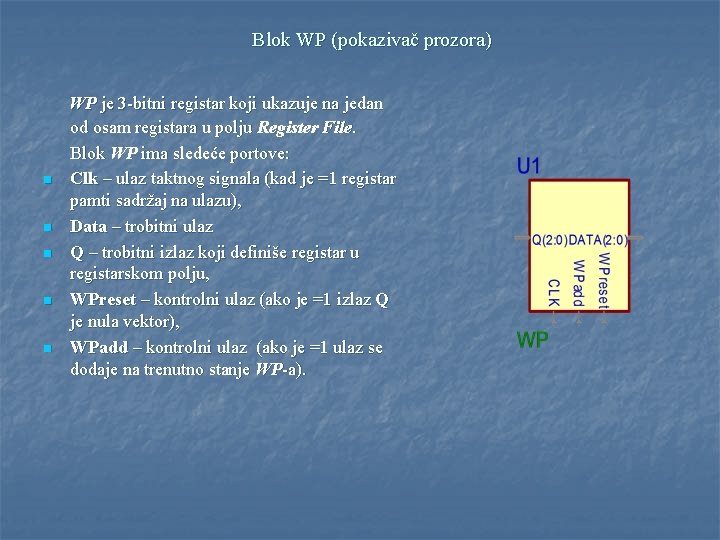

Blok WP (pokazivač prozora) n n n WP je 3 -bitni registar koji ukazuje na jedan od osam registara u polju Register File. Blok WP ima sledeće portove: Clk – ulaz taktnog signala (kad je =1 registar pamti sadržaj na ulazu), Data – trobitni ulaz Q – trobitni izlaz koji definiše registar u registarskom polju, WPreset – kontrolni ulaz (ako je =1 izlaz Q je nula vektor), WPadd – kontrolni ulaz (ako je =1 ulaz se dodaje na trenutno stanje WP-a).

Blok FR n n n n FR je 2 -bitni registar koji opisuje stanje aritmetičko-logičke jedinice. Blok FR ima sledeće portove: Clk – ulaz taktnog signala (kad je =1 registar pamti sadržaj na ulazu), Cout, Zout – 1 -bitni ulazi, C, Z – 1 -bitni izlazi, Cset – kontrolni ulaz (ako je =1 izlaz C se postavlja na 1), Creset – kontrolni ulaz (ako je =1 izlaz C se postavlja na 0), Zset – kontrolni ulaz (ako je =1 izlaz Z se postavlja na 1), Zreset – kontrolni ulaz (ako je =1 izlaz Z se postavlja na 0).

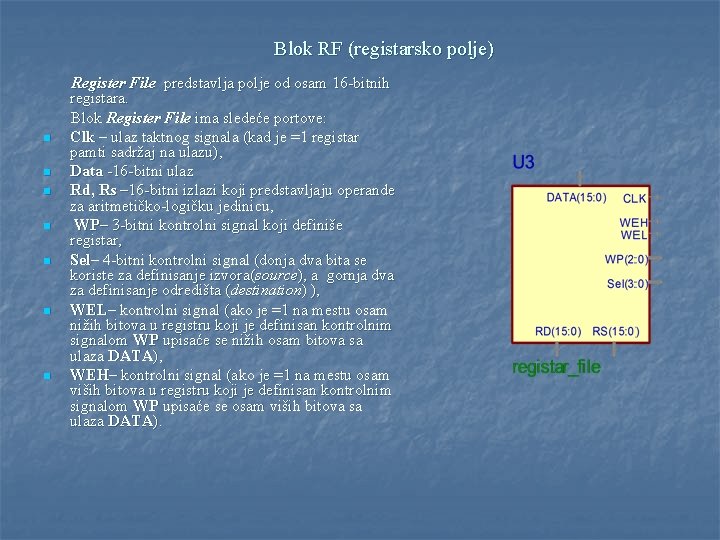

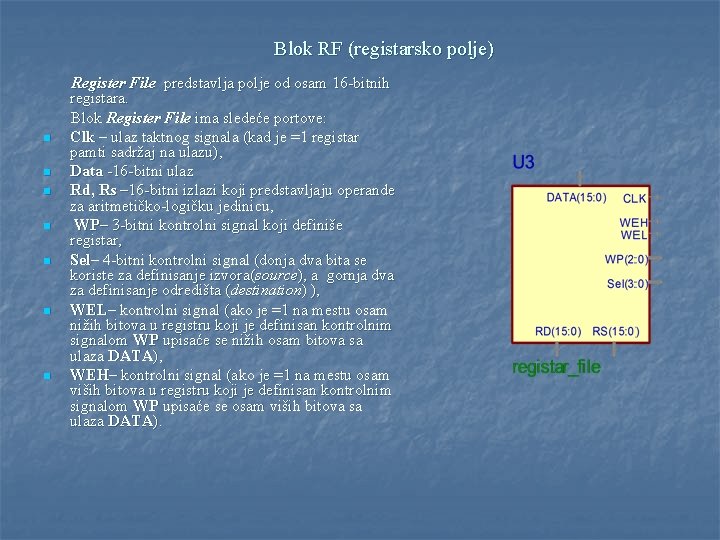

Blok RF (registarsko polje) n n n n Register File predstavlja polje od osam 16 -bitnih registara. Blok Register File ima sledeće portove: Clk – ulaz taktnog signala (kad je =1 registar pamti sadržaj na ulazu), Data -16 -bitni ulaz Rd, Rs – 16 -bitni izlazi koji predstavljaju operande za aritmetičko-logičku jedinicu, WP– 3 -bitni kontrolni signal koji definiše registar, Sel– 4 -bitni kontrolni signal (donja dva bita se koriste za definisanje izvora(source), a gornja dva za definisanje odredišta (destination) ), WEL– kontrolni signal (ako je =1 na mestu osam nižih bitova u registru koji je definisan kontrolnim signalom WP upisaće se nižih osam bitova sa ulaza DATA), WEH– kontrolni signal (ako je =1 na mestu osam viših bitova u registru koji je definisan kontrolnim signalom WP upisaće se osam viših bitova sa ulaza DATA).

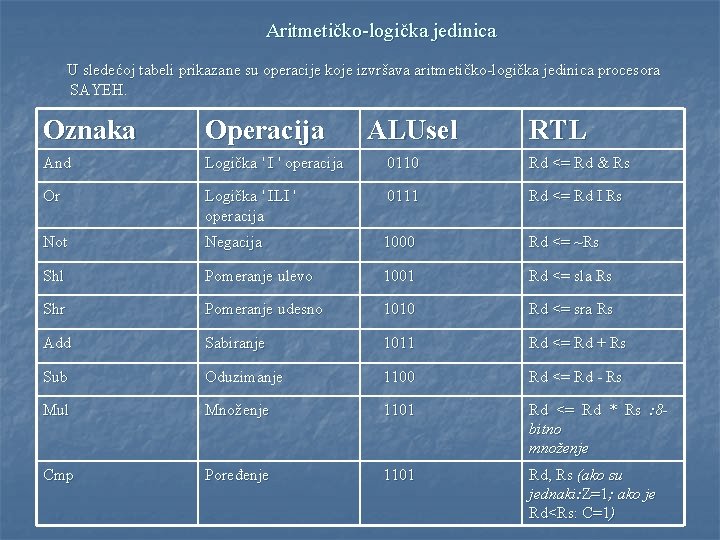

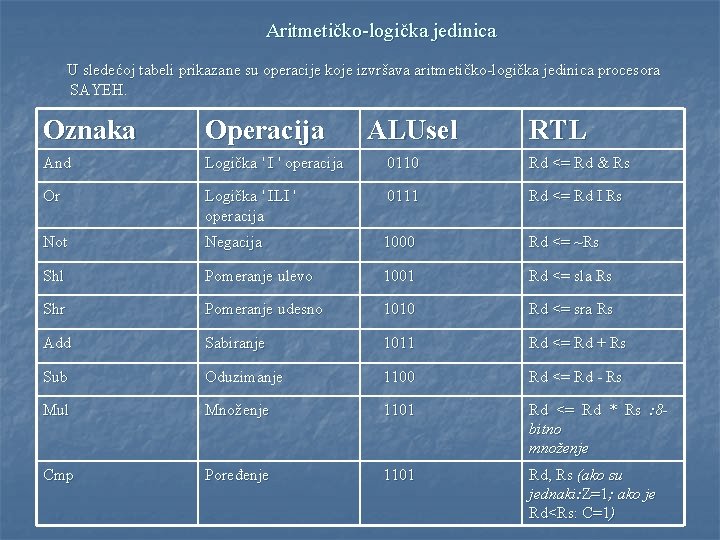

Aritmetičko-logička jedinica U sledećoj tabeli prikazane su operacije koje izvršava aritmetičko-logička jedinica procesora SAYEH. Oznaka Operacija ALUsel RTL And Logička ' I ' operacija 0110 Rd <= Rd & Rs Or Logička ' ILI ' operacija 0111 Rd <= Rd I Rs Not Negacija 1000 Rd <= ~Rs Shl Pomeranje ulevo 1001 Rd <= sla Rs Shr Pomeranje udesno 1010 Rd <= sra Rs Add Sabiranje 1011 Rd <= Rd + Rs Sub Oduzimanje 1100 Rd <= Rd - Rs Mul Množenje 1101 Rd <= Rd * Rs : 8 bitno množenje Cmp Poređenje 1101 Rd, Rs (ako su jednaki: Z=1; ako je Rd<Rs: C=1)

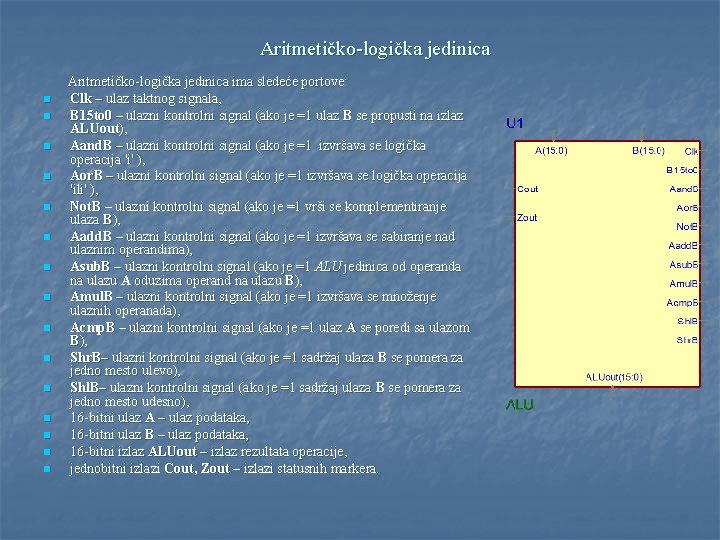

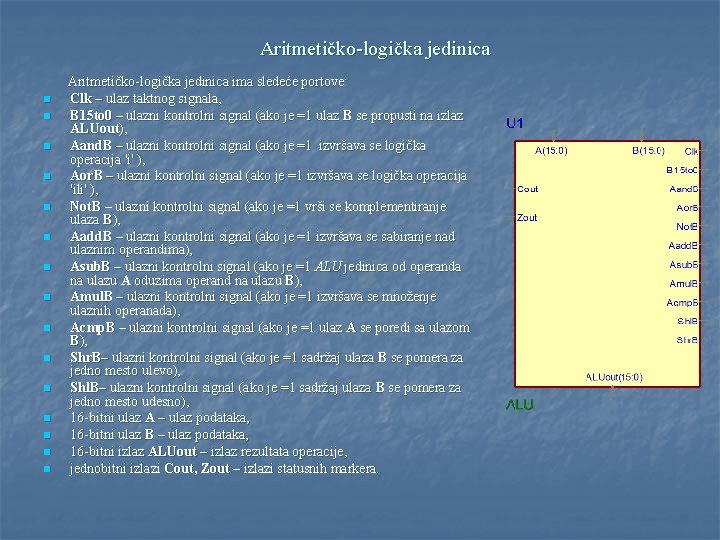

Aritmetičko-logička jedinica n n n n Aritmetičko-logička jedinica ima sledeće portove: Clk – ulaz taktnog signala, B 15 to 0 – ulazni kontrolni signal (ako je =1 ulaz B se propusti na izlaz ALUout), Aand. B – ulazni kontrolni signal (ako je =1 izvršava se logička operacija 'i' ), Aor. B – ulazni kontrolni signal (ako je =1 izvršava se logička operacija 'ili' ), Not. B – ulazni kontrolni signal (ako je =1 vrši se komplementiranje ulaza B), Aadd. B – ulazni kontrolni signal (ako je =1 izvršava se sabiranje nad ulaznim operandima), Asub. B – ulazni kontrolni signal (ako je =1 ALU jedinica od operanda na ulazu A oduzima operand na ulazu B), Amul. B – ulazni kontrolni signal (ako je =1 izvršava se množenje ulaznih operanada), Acmp. B – ulazni kontrolni signal (ako je =1 ulaz A se poredi sa ulazom B), Shr. B– ulazni kontrolni signal (ako je =1 sadržaj ulaza B se pomera za jedno mesto ulevo), Shl. B– ulazni kontrolni signal (ako je =1 sadržaj ulaza B se pomera za jedno mesto udesno), 16 -bitni ulaz A – ulaz podataka, 16 -bitni ulaz B – ulaz podataka, 16 -bitni izlaz ALUout – izlaz rezultata operacije, jednobitni izlazi Cout, Zout – izlazi statusnih markera.

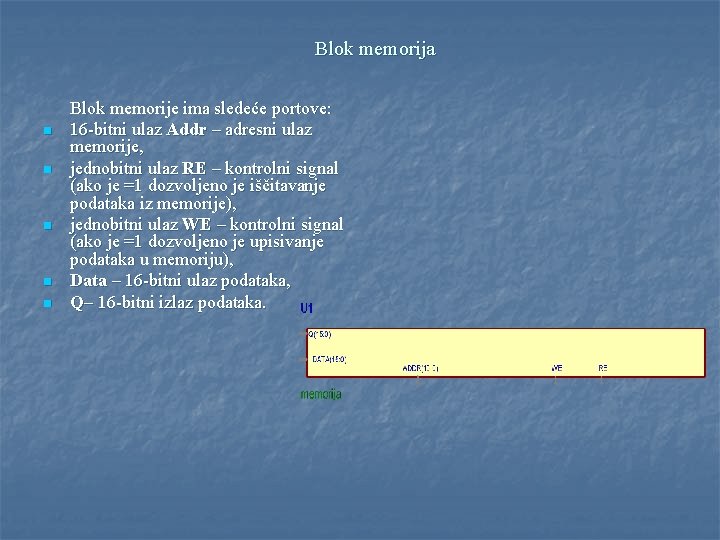

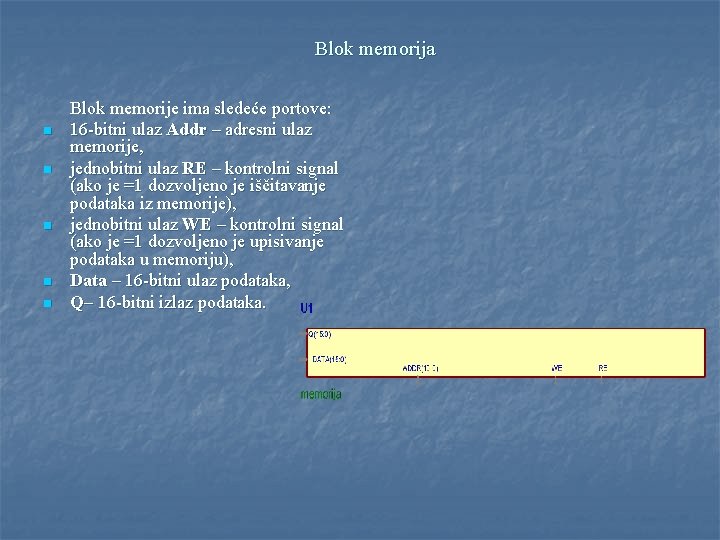

Blok memorija n n n Blok memorije ima sledeće portove: 16 -bitni ulaz Addr – adresni ulaz memorije, jednobitni ulaz RE – kontrolni signal (ako je =1 dozvoljeno je iščitavanje podataka iz memorije), jednobitni ulaz WE – kontrolni signal (ako je =1 dozvoljeno je upisivanje podataka u memoriju), Data – 16 -bitni ulaz podataka, Q– 16 -bitni izlaz podataka.

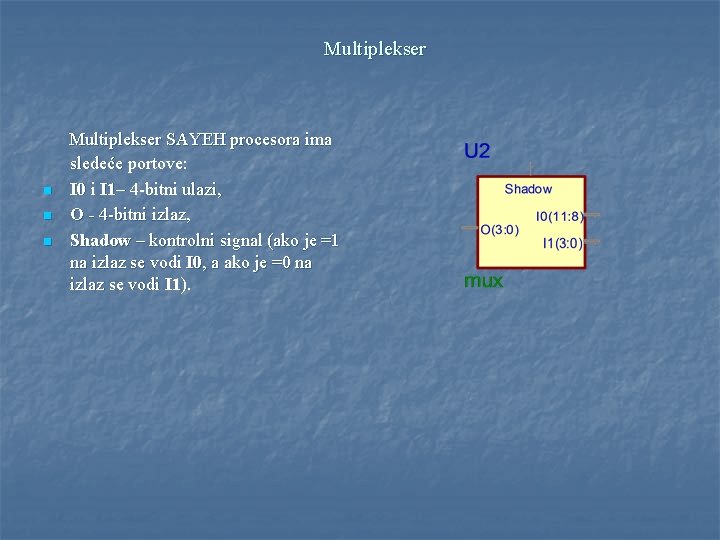

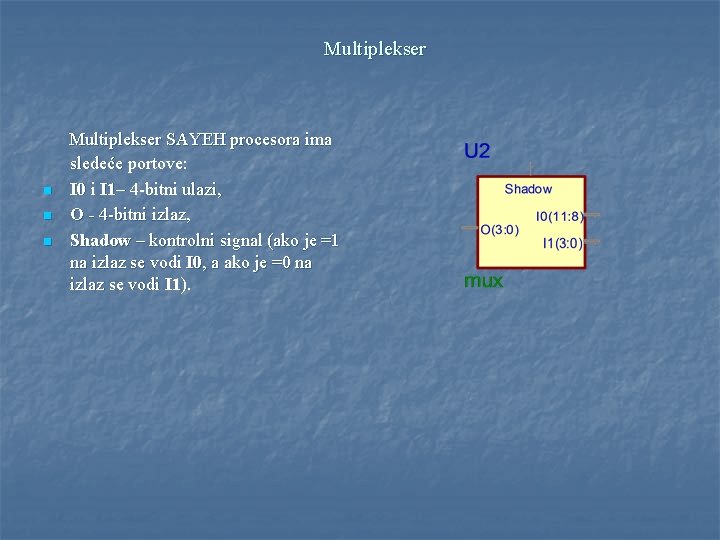

Multiplekser n n n Multiplekser SAYEH procesora ima sledeće portove: I 0 i I 1– 4 -bitni ulazi, O - 4 -bitni izlaz, Shadow – kontrolni signal (ako je =1 na izlaz se vodi I 0, a ako je =0 na izlaz se vodi I 1).

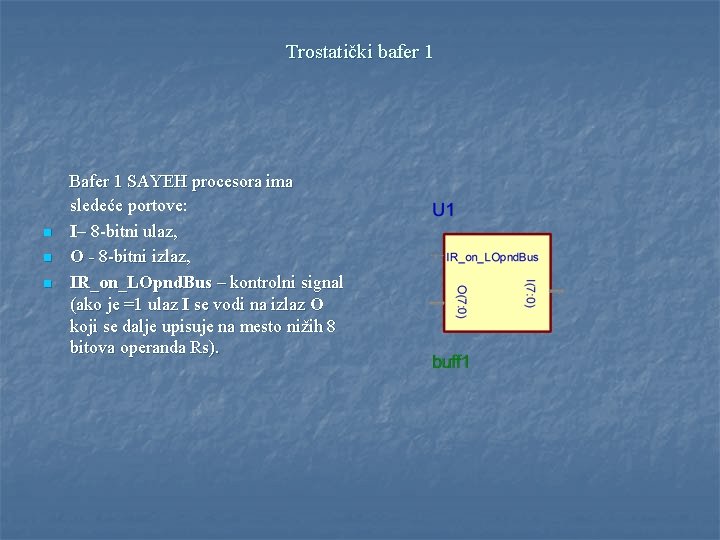

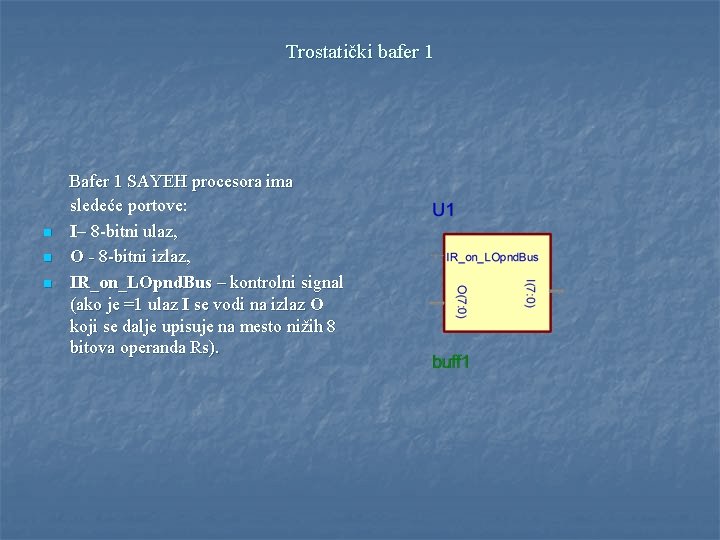

Trostatički bafer 1 n n n Bafer 1 SAYEH procesora ima sledeće portove: I– 8 -bitni ulaz, O - 8 -bitni izlaz, IR_on_LOpnd. Bus – kontrolni signal (ako je =1 ulaz I se vodi na izlaz O koji se dalje upisuje na mesto nižih 8 bitova operanda Rs).

Trostatički bafer 2 n n n Bafer 2 SAYEH procesora ima sledeće portove: I– 8 -bitni ulaz, O - 8 -bitni izlaz, IR_on_HOpnd. Bus – kontrolni signal (ako je =1 ulaz I se vodi na izlaz O koji se dalje upisuje na mesto viših 8 bitova operanda Rs).

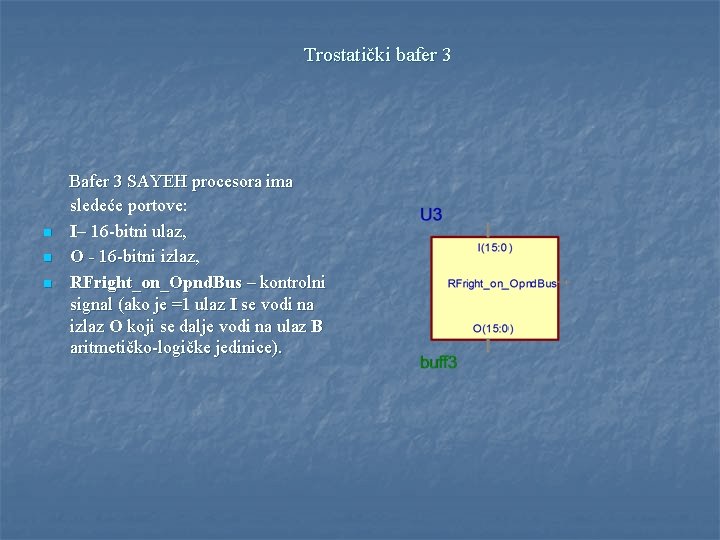

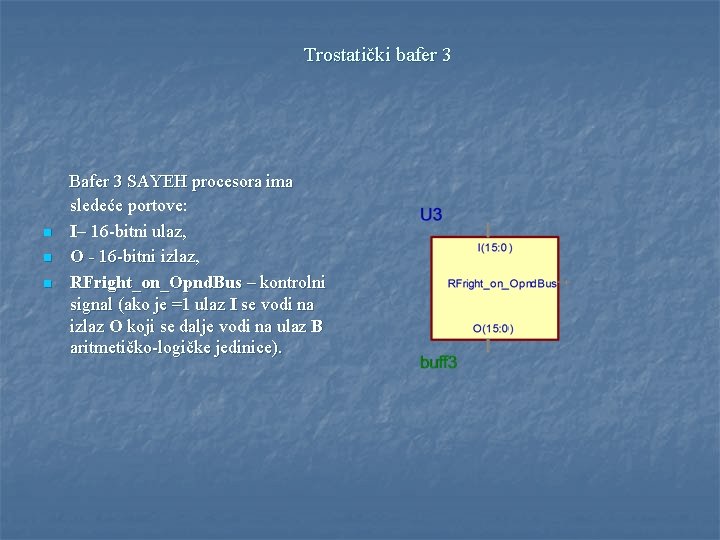

Trostatički bafer 3 n n n Bafer 3 SAYEH procesora ima sledeće portove: I– 16 -bitni ulaz, O - 16 -bitni izlaz, RFright_on_Opnd. Bus – kontrolni signal (ako je =1 ulaz I se vodi na izlaz O koji se dalje vodi na ulaz B aritmetičko-logičke jedinice).

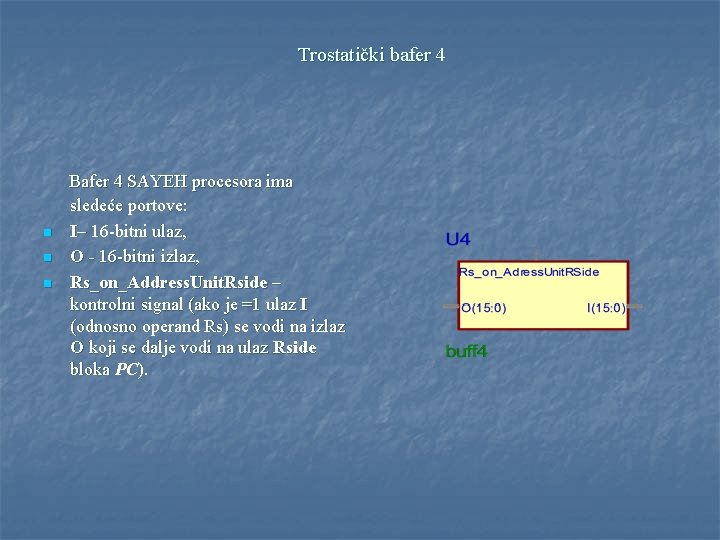

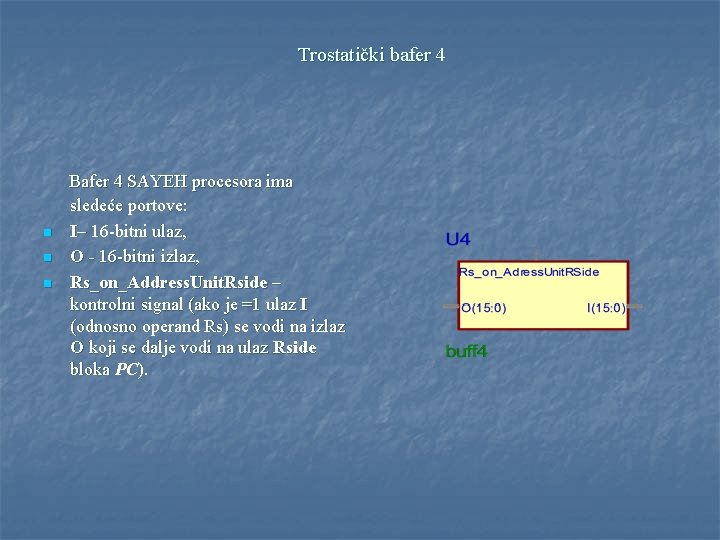

Trostatički bafer 4 n n n Bafer 4 SAYEH procesora ima sledeće portove: I– 16 -bitni ulaz, O - 16 -bitni izlaz, Rs_on_Address. Unit. Rside – kontrolni signal (ako je =1 ulaz I (odnosno operand Rs) se vodi na izlaz O koji se dalje vodi na ulaz Rside bloka PC).

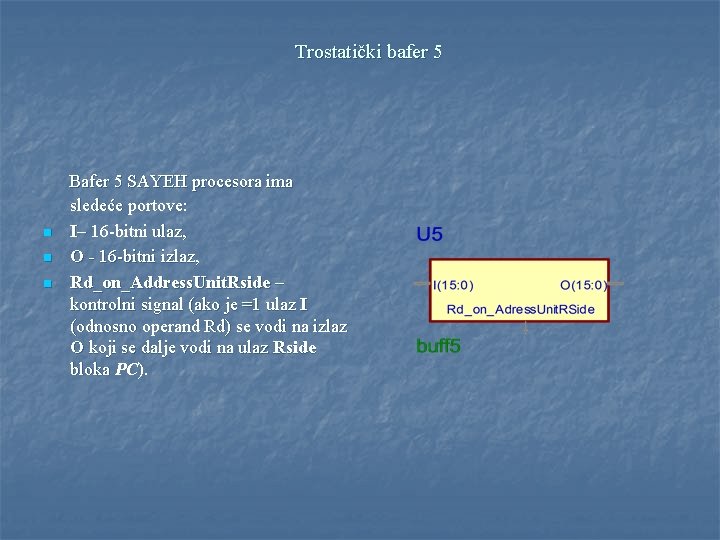

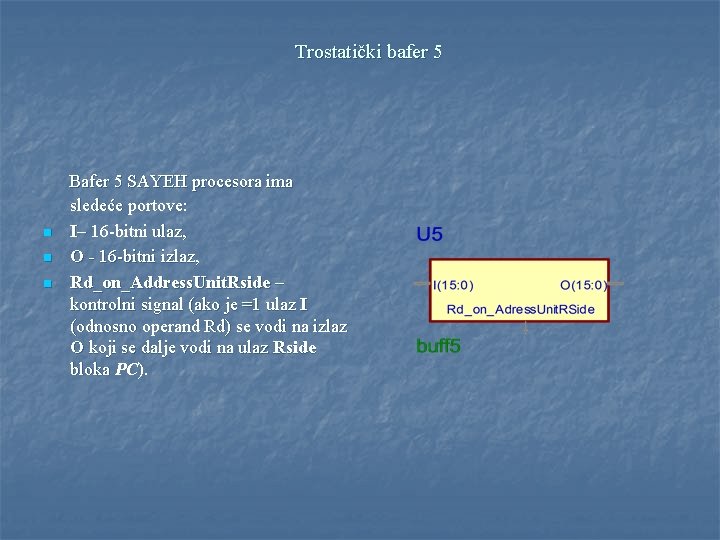

Trostatički bafer 5 n n n Bafer 5 SAYEH procesora ima sledeće portove: I– 16 -bitni ulaz, O - 16 -bitni izlaz, Rd_on_Address. Unit. Rside – kontrolni signal (ako je =1 ulaz I (odnosno operand Rd) se vodi na izlaz O koji se dalje vodi na ulaz Rside bloka PC).

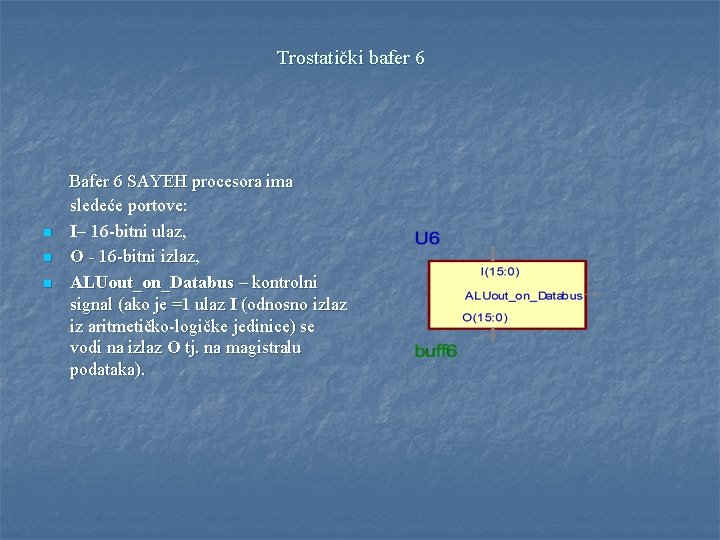

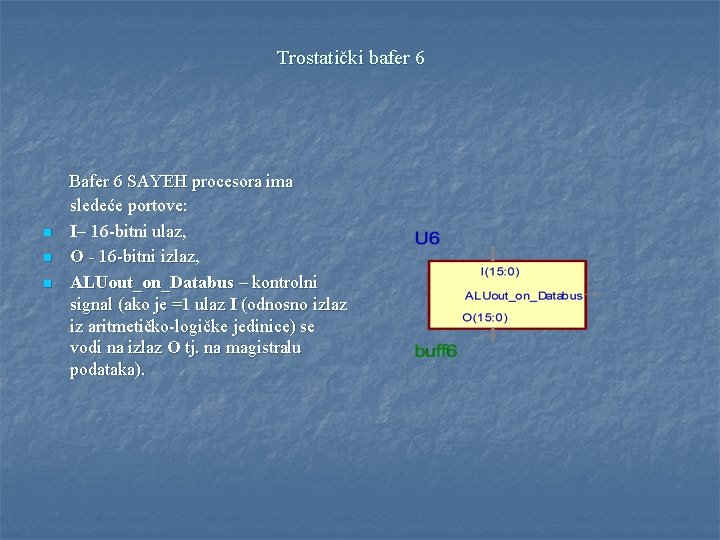

Trostatički bafer 6 n n n Bafer 6 SAYEH procesora ima sledeće portove: I– 16 -bitni ulaz, O - 16 -bitni izlaz, ALUout_on_Databus – kontrolni signal (ako je =1 ulaz I (odnosno izlaz iz aritmetičko-logičke jedinice) se vodi na izlaz O tj. na magistralu podataka).

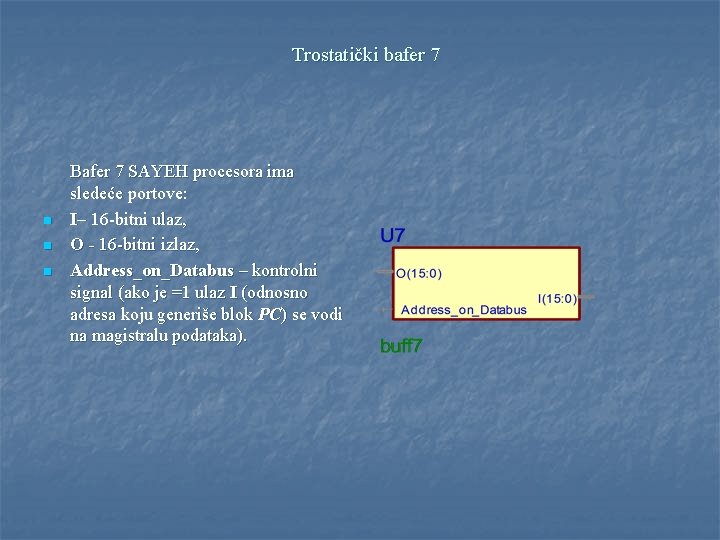

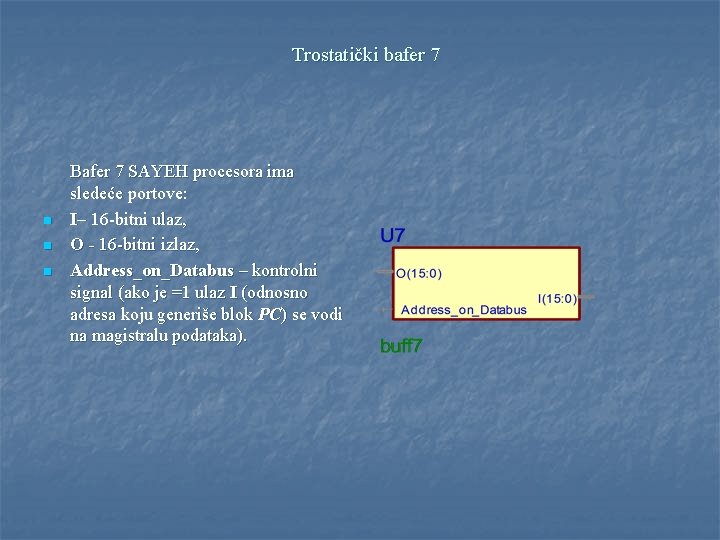

Trostatički bafer 7 n n n Bafer 7 SAYEH procesora ima sledeće portove: I– 16 -bitni ulaz, O - 16 -bitni izlaz, Address_on_Databus – kontrolni signal (ako je =1 ulaz I (odnosno adresa koju generiše blok PC) se vodi na magistralu podataka).

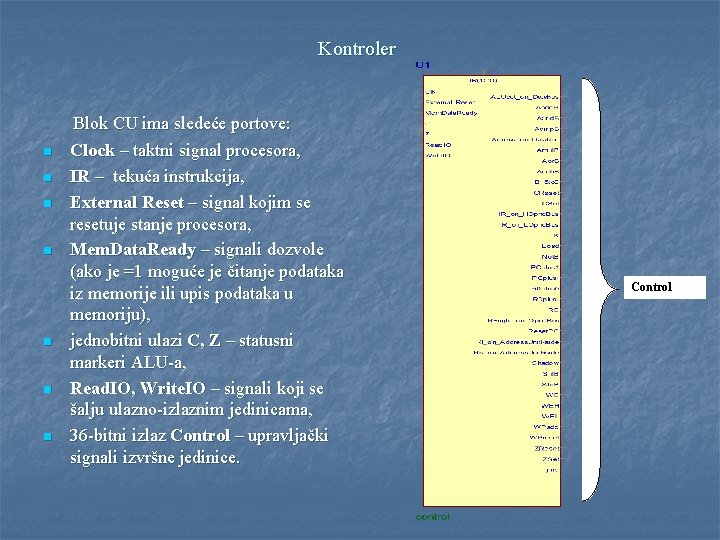

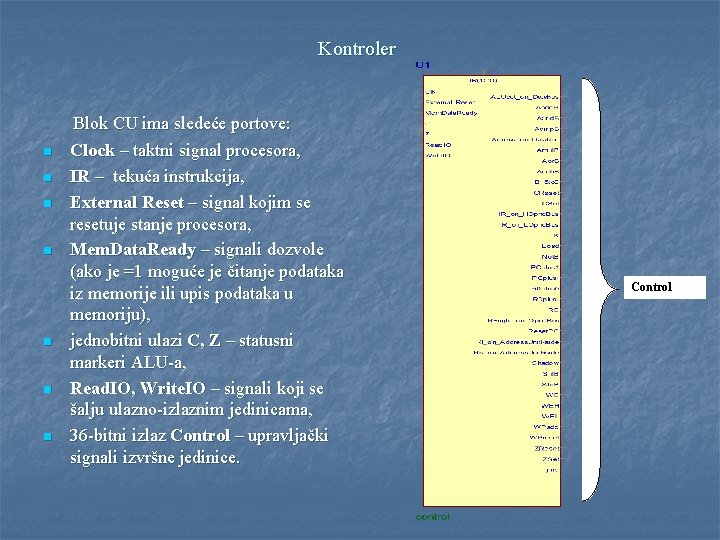

Kontroler Upravljačka jedinica služi da na osnovu trenutne instrukcije izvrši generisanje upravljačkih signala. Upravljačka jednica procesora SAYEH je realizovana kao upravljačka jedinica sa direktnim upravljanjem (eng. hardwired control).

Kontroler n n n n Blok CU ima sledeće portove: Clock – taktni signal procesora, IR – tekuća instrukcija, External Reset – signal kojim se resetuje stanje procesora, Mem. Data. Ready – signali dozvole (ako je =1 moguće je čitanje podataka iz memorije ili upis podataka u memoriju), jednobitni ulazi C, Z – statusni markeri ALU-a, Read. IO, Write. IO – signali koji se šalju ulazno-izlaznim jedinicama, 36 -bitni izlaz Control – upravljački signali izvršne jedinice. Control

Procesor SAYEH n Blokovi koji su do sada opisani povezani su na sledeći način:

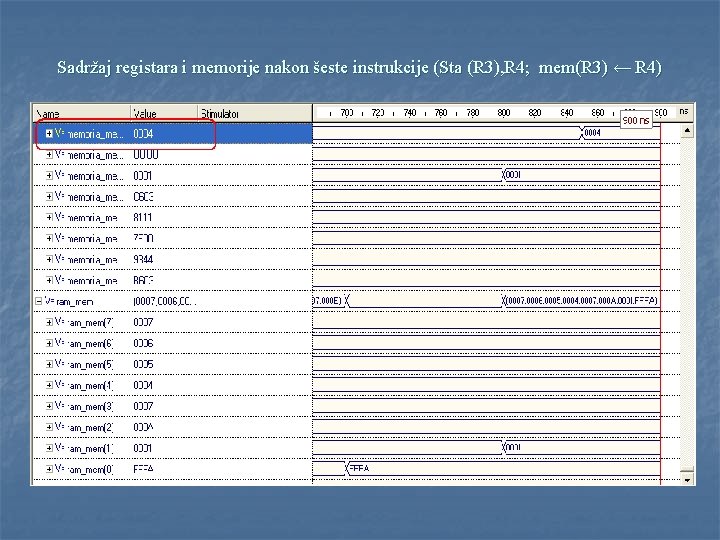

Testiranje sintetizovanog procesora n n n Programskom sekvencom od šest naredbi testiraćemo korektnost rada sintetizovanog procesora SAYEH. Add R 1, R 6; R 1 ← R 1 + R 6 Shl R 7; R 0 ← Shl R 7 Or R 3, R 7; R 3 ← R 3 Or R 7 Not R 5; R 0 ← Not R 5 Sub R 1, R 6; R 1 ← R 1 – R 6 Sta (R 3), R 4; mem(R 3) ← R 4

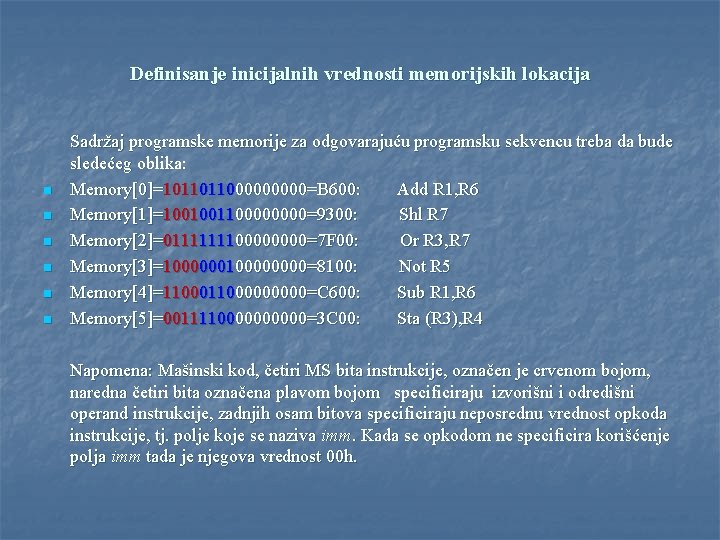

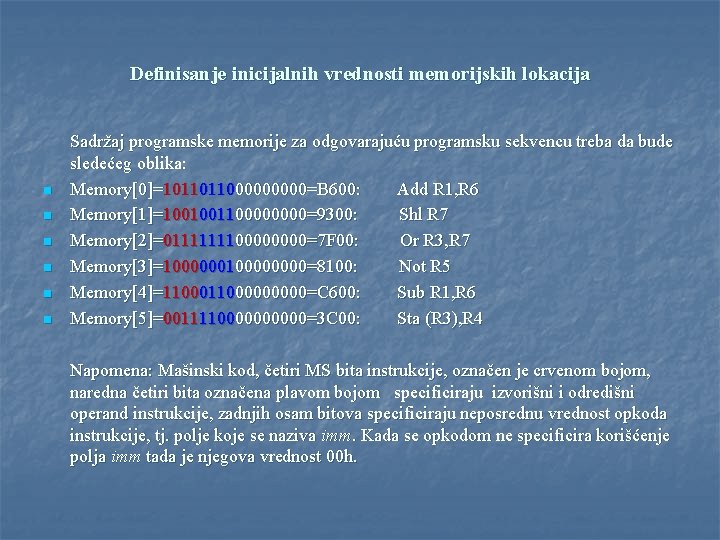

Definisanje inicijalnih vrednosti memorijskih lokacija n n n Sadržaj programske memorije za odgovarajuću programsku sekvencu treba da bude sledećeg oblika: Memory[0]=101101100000=B 600: Add R 1, R 6 Memory[1]=100100110000=9300: Shl R 7 Memory[2]=011111110000=7 F 00: Or R 3, R 7 Memory[3]=100000000=8100: Not R 5 Memory[4]=11000000000=C 600: Sub R 1, R 6 Memory[5]=00111100000=3 C 00: Sta (R 3), R 4 Napomena: Mašinski kod, četiri MS bita instrukcije, označen je crvenom bojom, naredna četiri bita označena plavom bojom specificiraju izvorišni i odredišni operand instrukcije, zadnjih osam bitova specificiraju neposrednu vrednost opkoda instrukcije, tj. polje koje se naziva imm. Kada se opkodom ne specificira korišćenje polja imm tada je njegova vrednost 00 h.

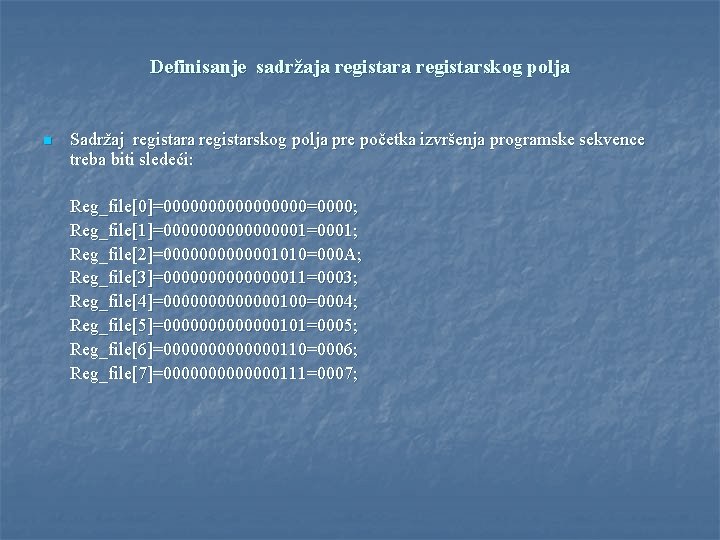

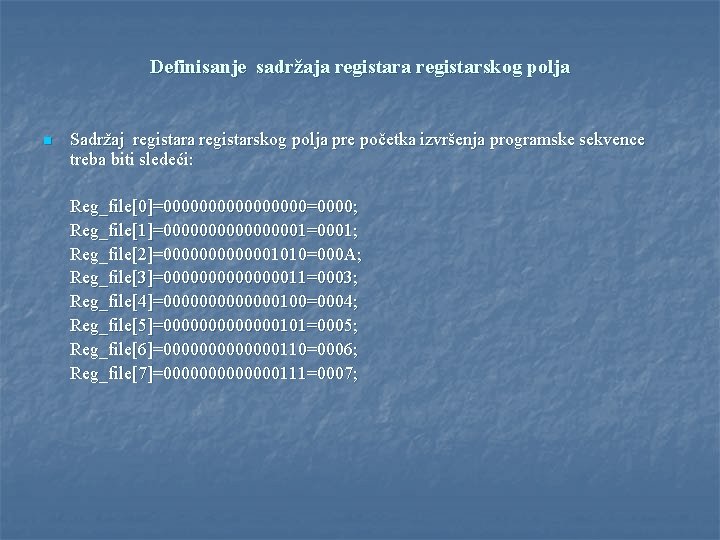

Definisanje sadržaja registarskog polja n Sadržaj registara registarskog polja pre početka izvršenja programske sekvence treba biti sledeći: Reg_file[0]=00000000=0000; Reg_file[1]=000000001=0001; Reg_file[2]=0000001010=000 A; Reg_file[3]=000000011=0003; Reg_file[4]=0000000100=0004; Reg_file[5]=0000000101=0005; Reg_file[6]=0000000110=0006; Reg_file[7]=0000000111=0007;

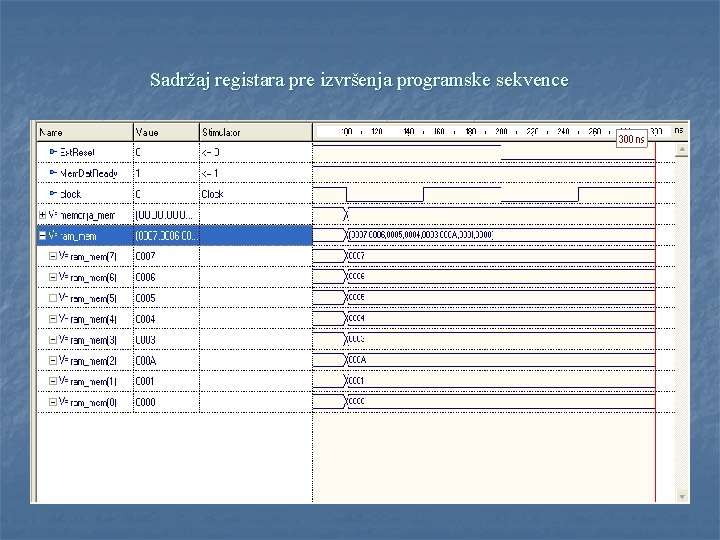

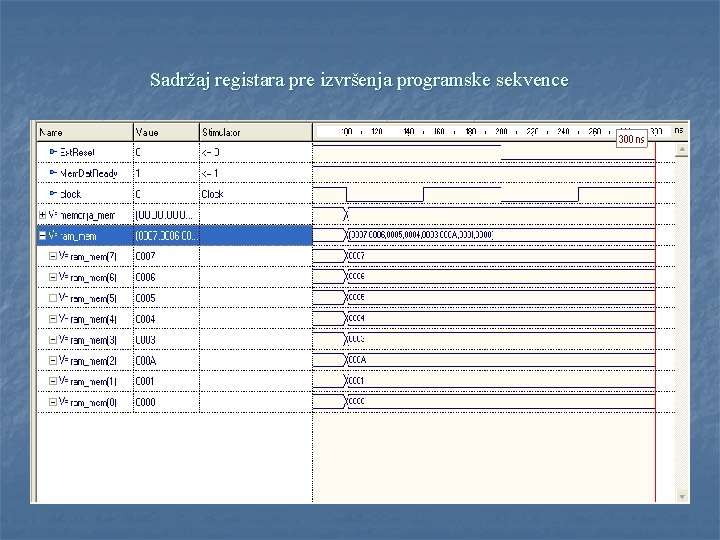

Sadržaj registara pre izvršenja programske sekvence

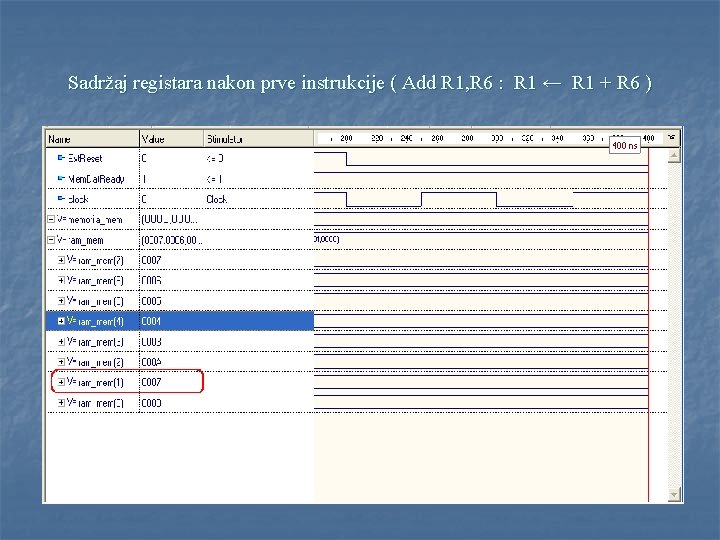

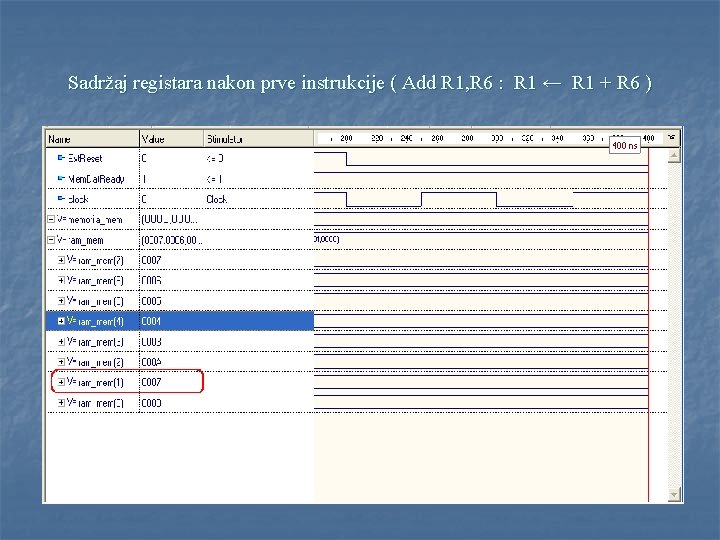

Sadržaj registara nakon prve instrukcije ( Add R 1, R 6 : R 1 ← R 1 + R 6 )

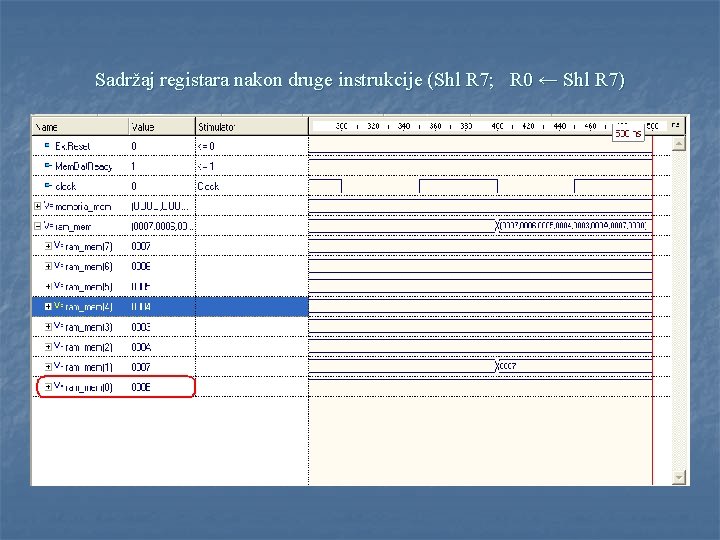

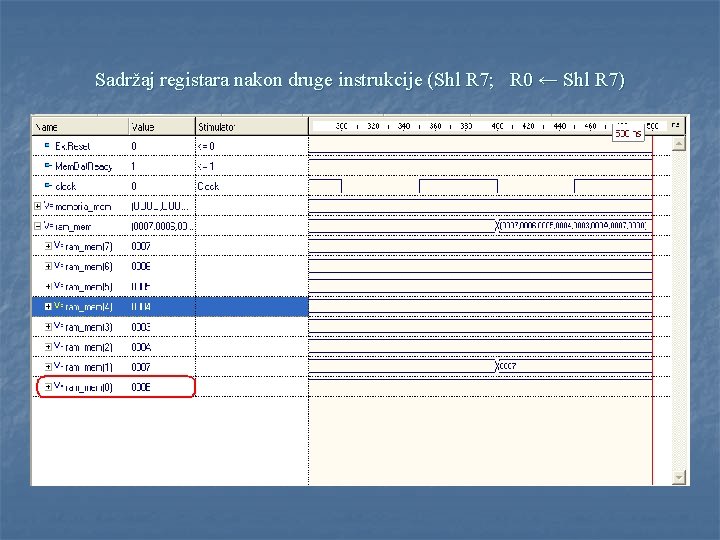

Sadržaj registara nakon druge instrukcije (Shl R 7; R 0 ← Shl R 7)

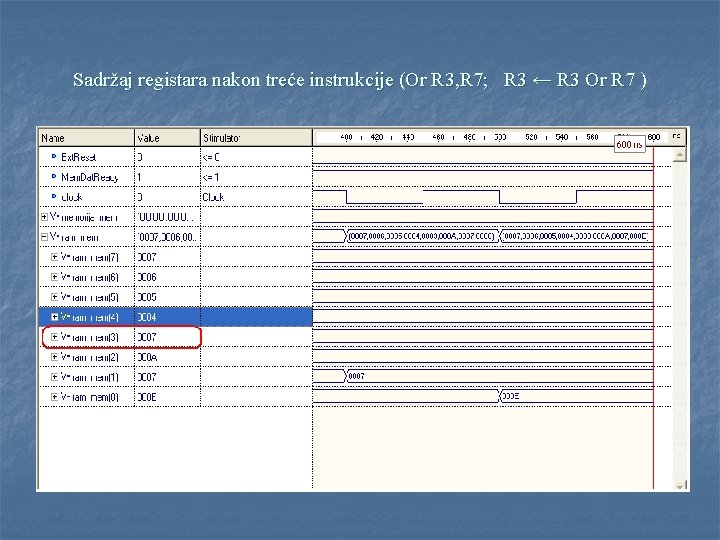

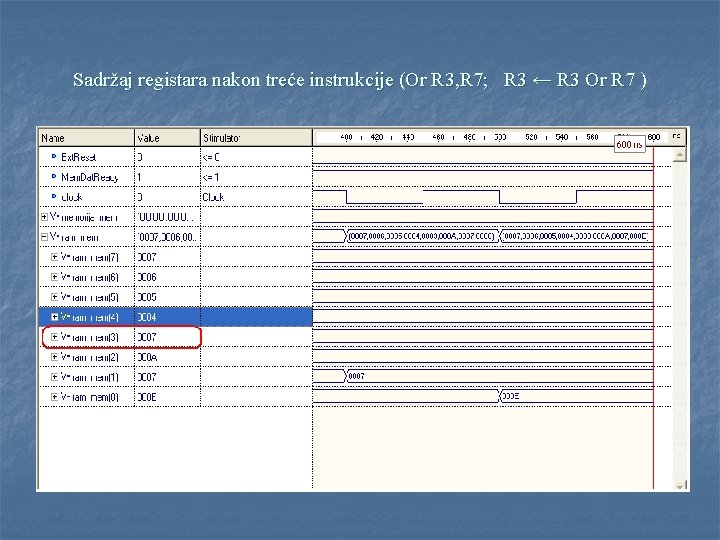

Sadržaj registara nakon treće instrukcije (Or R 3, R 7; R 3 ← R 3 Or R 7 )

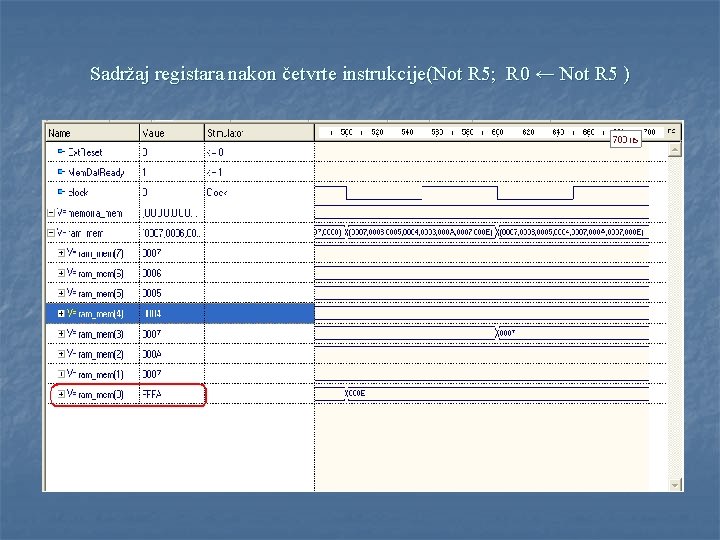

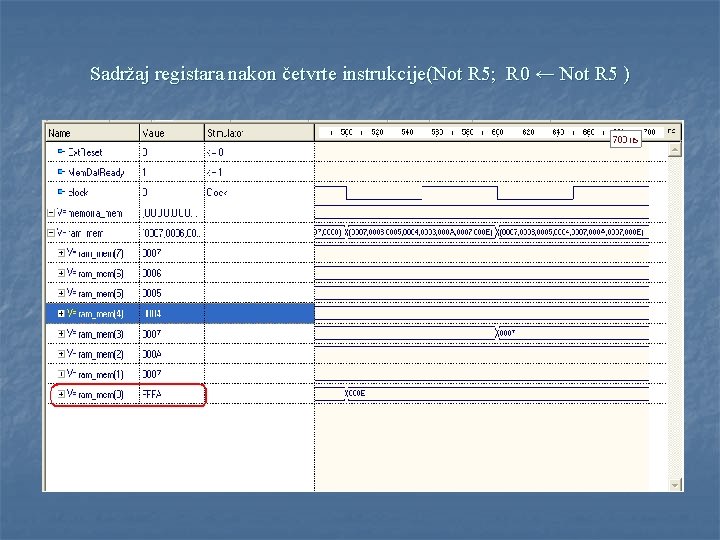

Sadržaj registara nakon četvrte instrukcije(Not R 5; R 0 ← Not R 5 )

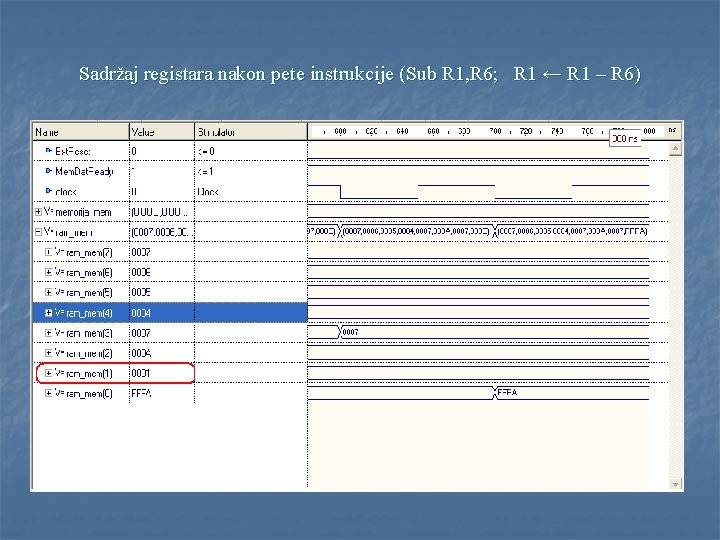

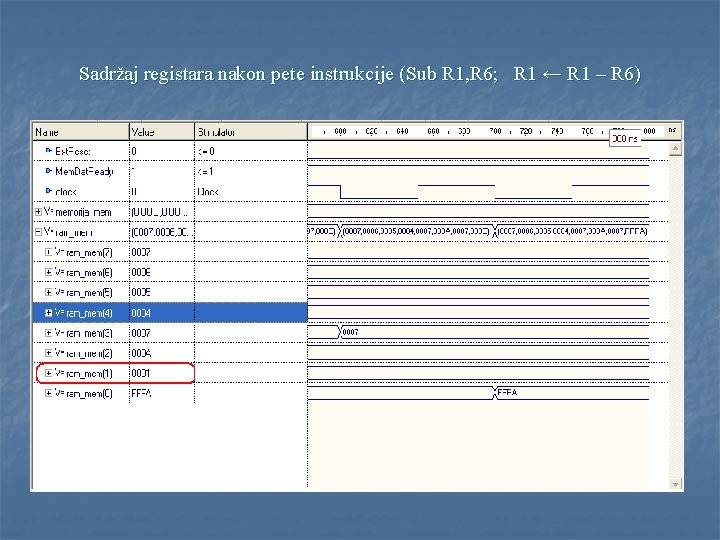

Sadržaj registara nakon pete instrukcije (Sub R 1, R 6; R 1 ← R 1 – R 6)

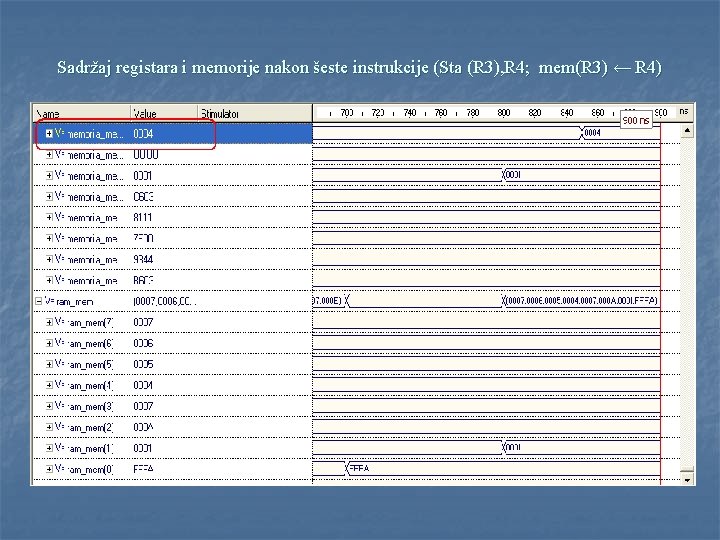

Sadržaj registara i memorije nakon šeste instrukcije (Sta (R 3), R 4; mem(R 3) ← R 4)

Zaključak n n n VHDL je jedan od najčešće korišćenih jezika za opis hardware-a Prednosti upotrebe VHDL-a : n jednostavna i efikasna implementacija n skraćeno vreme dizajniranja n lakša detekcija grešaka n jednostavno testiranje n visok nivo apstrakcije n maksimalno tačan i pouzdan dizajn uz najmanju cenu u najkraćem roku razvijanja Zbog navedenih prednosti VHDL se često koristi u procesima dizajniranja komponenti i razvoja složenih sistema

Autori Ime i prezime : Rodjen : Mesto : Škola : Smer : Broj indeksa : Kontakt : Nikola Sekulović 27. 04. 1983. Niš Elektronski fakultet , Niš telekomunikacije 10963 sekulani@bankerinter. net Ime i prezime : Lazar Velimirović Rodjen : 17. 05. 1983. Mesto : Prokuplje Škola : Elektronski fakultet , Niš Smer : telekomunikacije Broj indeksa : 11017 Kontakt : lami@bankerinter. net