Univerzitet u Niu Elektronski fakultet Katedra za elektroniku

- Slides: 18

Univerzitet u Nišu Elektronski fakultet Katedra za elektroniku FPGA kola Student: Nenad Stojanović Broj indeksa: 9806

FPGA kola (Field Programmable Gate Arrey) n n In Field Programmable – funkcija FPGA kola definisna je od strane korisnika a ne proizvođača uređaja Sastoje se iz logičkih ćelija Povezivanje ćelija se vrši preko matrice međuveza i selektivnih prekidača Logika se implementira preko Look-up tabela ili multipleksera i gejtova

OSNOVNI PRINCIPI FPGA KOLA Osnovne karakteristike FPGA kola: n Reprogramiranje hardverske strukture se izvodi lako i jednostavno n Brzina rada je velika n Potrošnja mala n Cena relativno niska u odnosu na ASIC

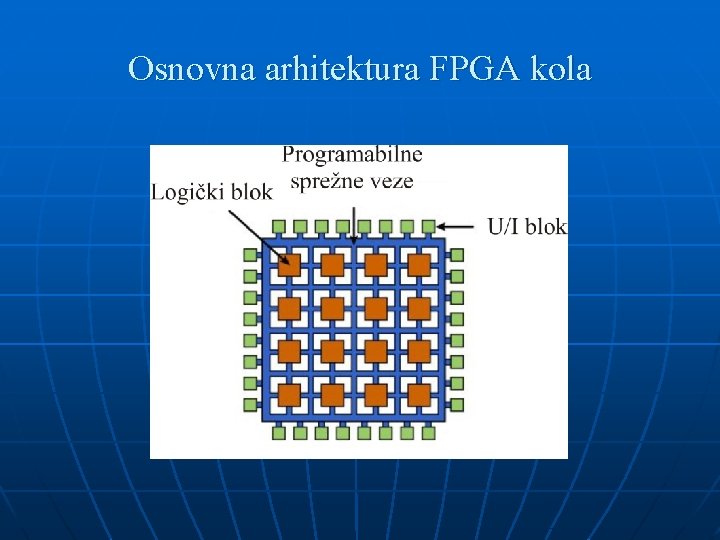

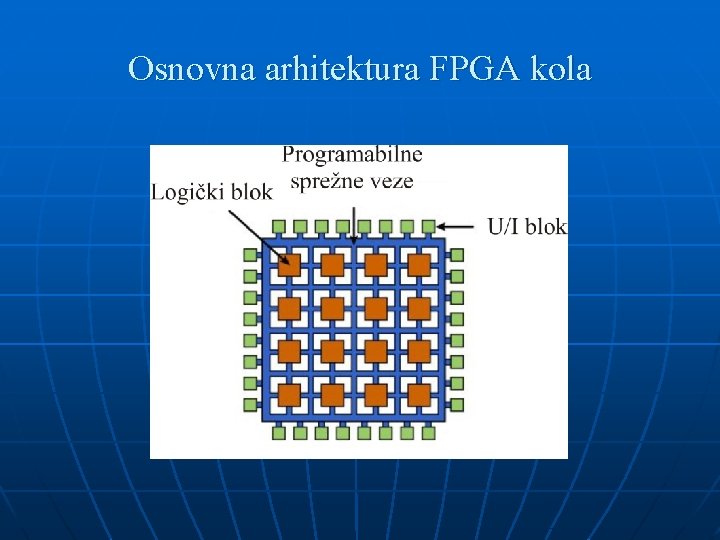

Osnovna arhitektura FPGA kola

Arhitektura FPGA kola Moze biti: n Sitno-zrnasta struktura n Krupno-zrnasta struktura n n Kod sitno-zrnastih struktura logički blokovi se koriste za realizaciju relativno jednostavnih logičkih funkcija (OR, AND, NAND ili D-leč, D-flipflop) Kod krupno-zrnastih struktura, logički blokovi sadrže relativno veći iznos logike, pa je moguce realizovati odjednom više memorijskih elemenata, sabirača itd.

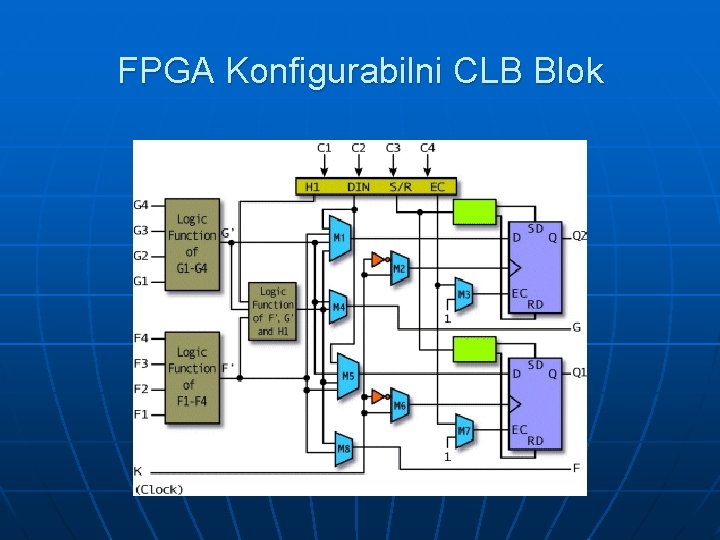

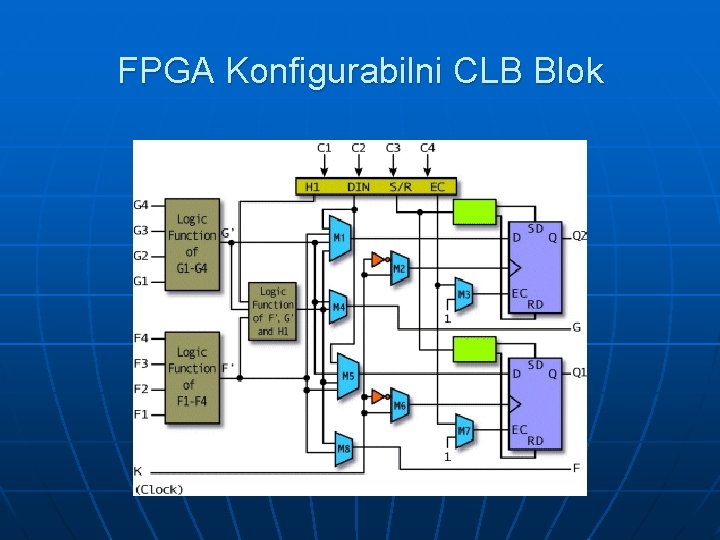

Konfigurabilni Logički Blokovi (CLB blokovi) (kod krupnozrnaste strukture) n n n U ovim blokovima se nalazi dovoljan iznos logike za formiranje dovoljnog broja konačnih automata sa malim brojem stanja CLB sadrži RAM koji se koristi za generisanje proizvoljnih kombinacionih logičkih funkcija, naziva se još i LUT - tabela pretraživanja sadrži flip – flopove koji se koriste kao taktovani memorijski elementi, kojima se pridružuju multiplekseri čija je uloga da usmeravaju puteve logičkih signala, kako u okviru internog razvođenja tako i signala koji se prihvataju od spoljnih resursa

FPGA Konfigurabilni CLB Blok

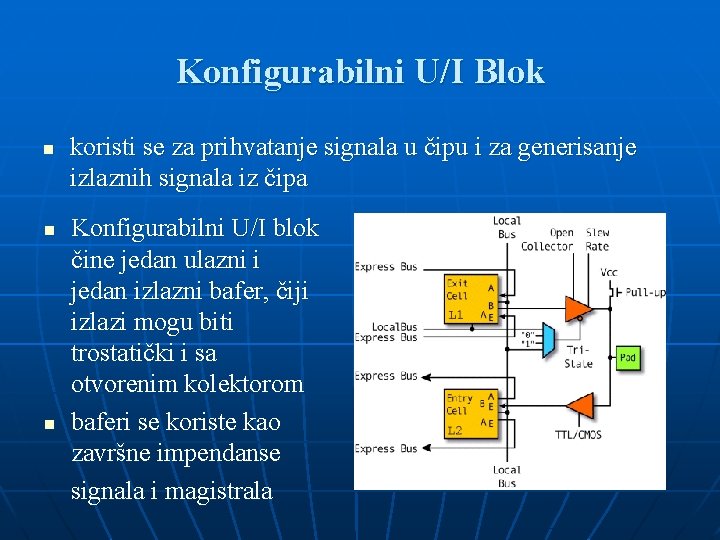

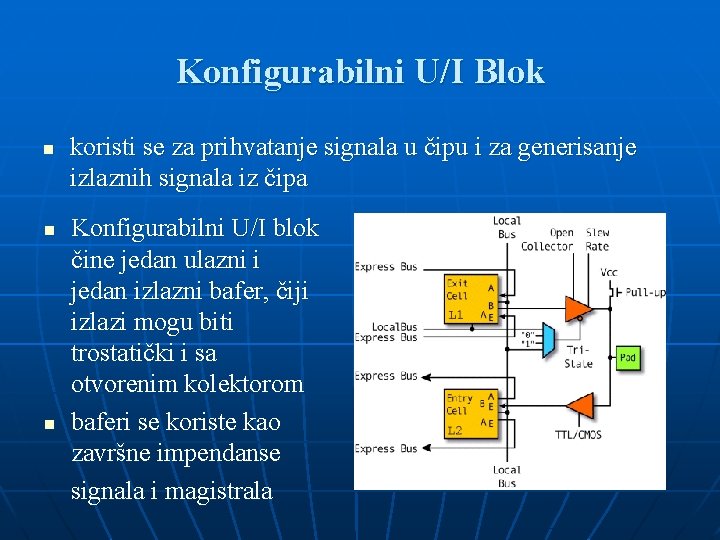

Konfigurabilni U/I Blok n n n koristi se za prihvatanje signala u čipu i za generisanje izlaznih signala iz čipa Konfigurabilni U/I blok čine jedan ulazni i jedan izlazni bafer, čiji izlazi mogu biti trostatički i sa otvorenim kolektorom baferi se koriste kao završne impendanse signala i magistrala

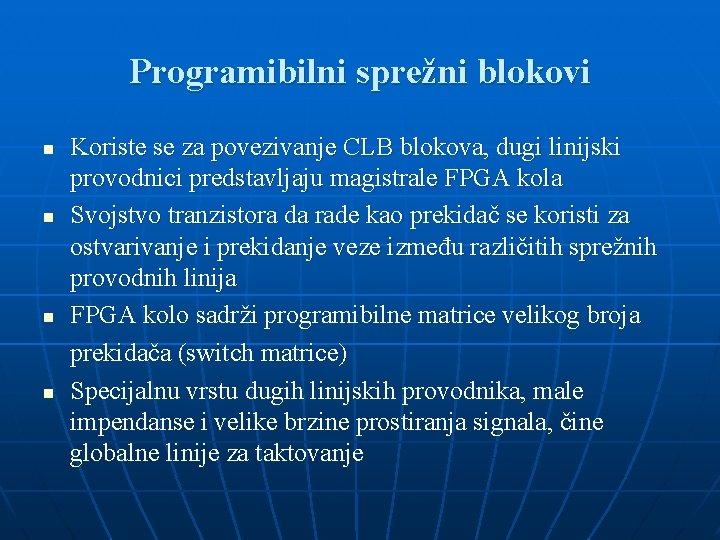

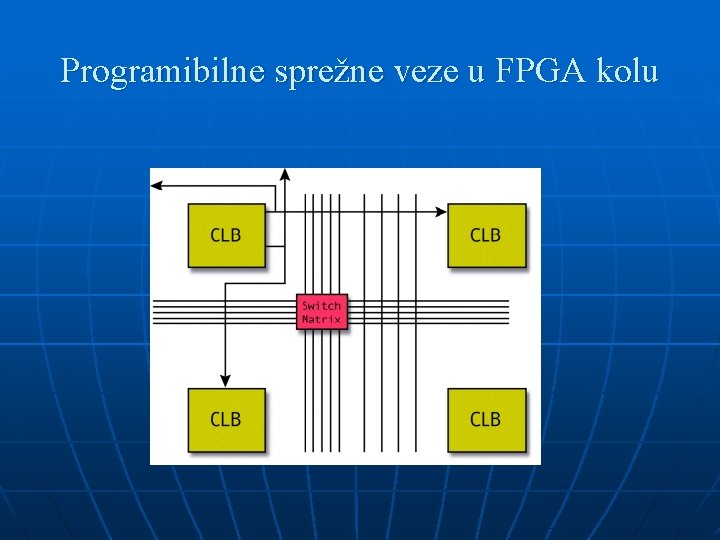

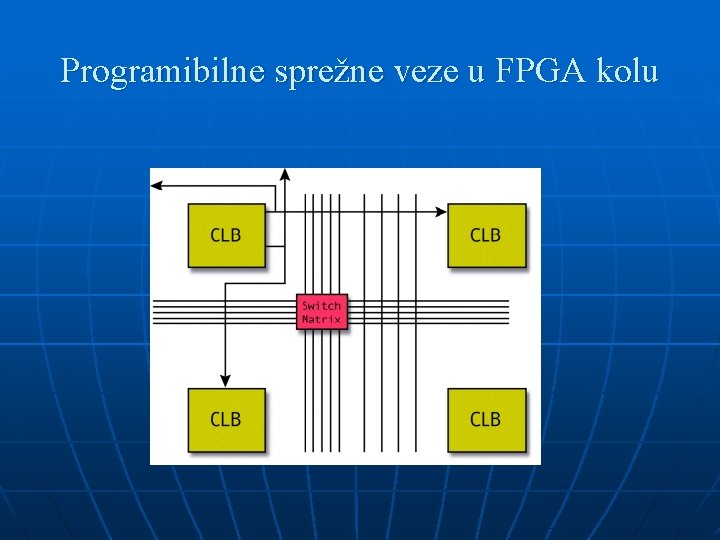

Programibilni sprežni blokovi n n Koriste se za povezivanje CLB blokova, dugi linijski provodnici predstavljaju magistrale FPGA kola Svojstvo tranzistora da rade kao prekidač se koristi za ostvarivanje i prekidanje veze između različitih sprežnih provodnih linija FPGA kolo sadrži programibilne matrice velikog broja prekidača (switch matrice) Specijalnu vrstu dugih linijskih provodnika, male impendanse i velike brzine prostiranja signala, čine globalne linije za taktovanje

Programibilne sprežne veze u FPGA kolu

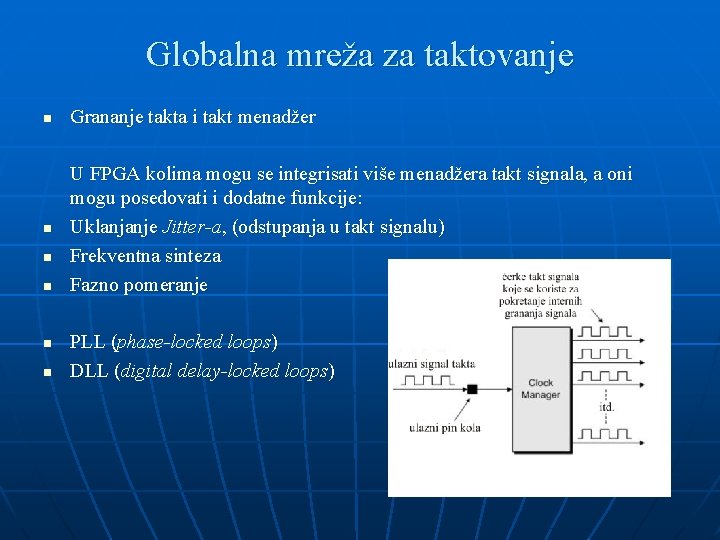

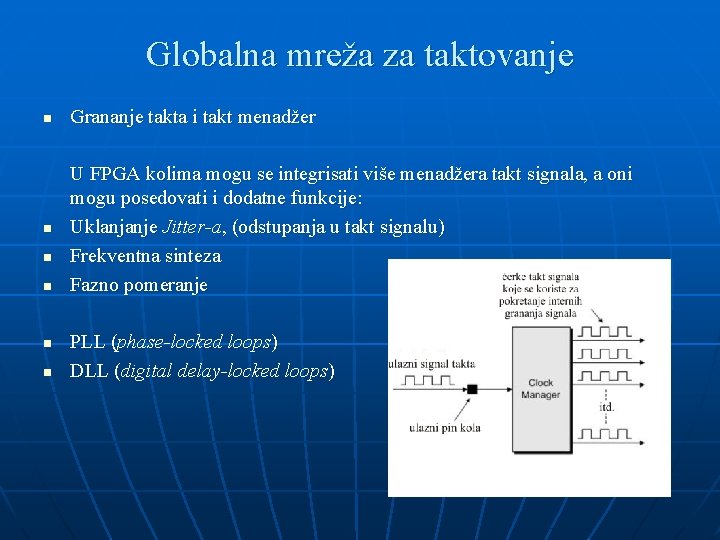

Globalna mreža za taktovanje n Grananje takta i takt menadžer n U FPGA kolima mogu se integrisati više menadžera takt signala, a oni mogu posedovati i dodatne funkcije: Uklanjanje Jitter-a, (odstupanja u takt signalu) Frekventna sinteza Fazno pomeranje n n PLL (phase-locked loops) DLL (digital delay-locked loops)

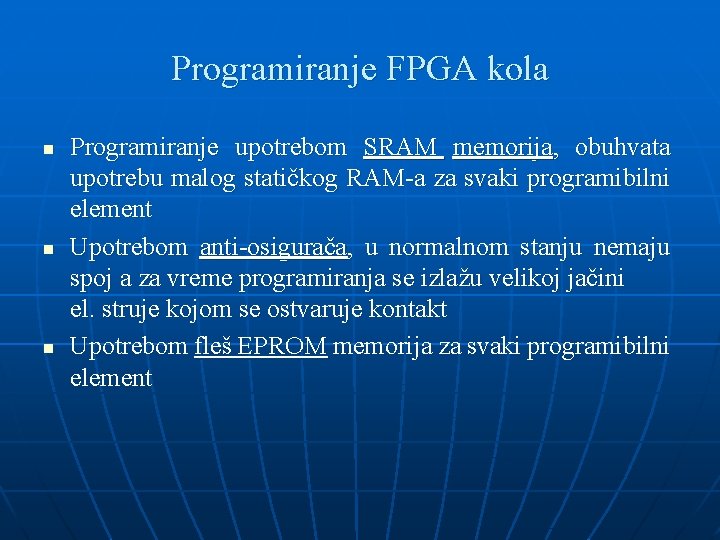

Programiranje FPGA kola n n n Programiranje upotrebom SRAM memorija, obuhvata upotrebu malog statičkog RAM-a za svaki programibilni element Upotrebom anti-osigurača, u normalnom stanju nemaju spoj a za vreme programiranja se izlažu velikoj jačini el. struje kojom se ostvaruje kontakt Upotrebom fleš EPROM memorija za svaki programibilni element

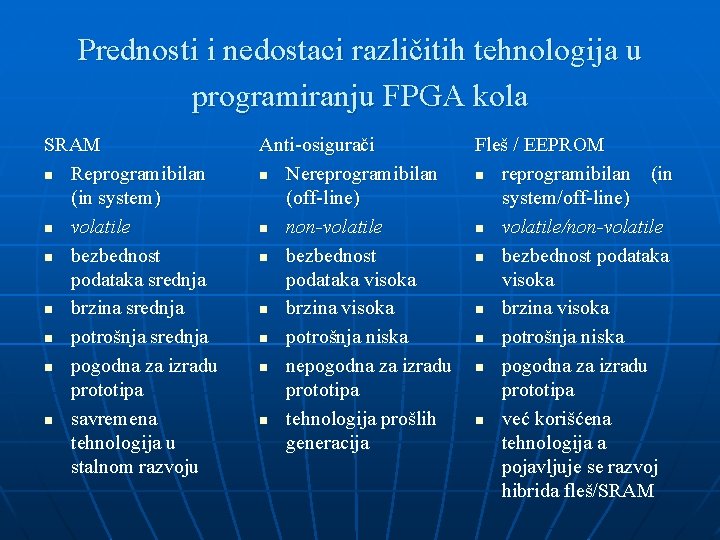

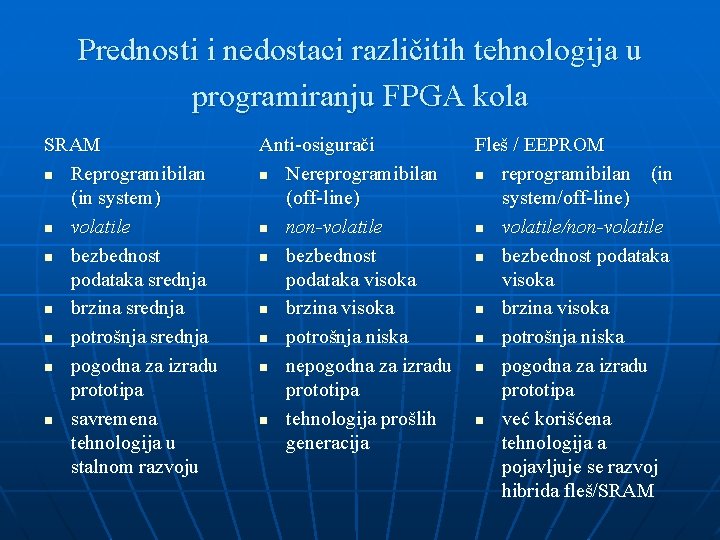

Prednosti i nedostaci različitih tehnologija u programiranju FPGA kola SRAM n Reprogramibilan (in system) n volatile n bezbednost podataka srednja n brzina srednja n potrošnja srednja n pogodna za izradu prototipa n savremena tehnologija u stalnom razvoju Anti-osigurači n Nereprogramibilan (off-line) n non-volatile n bezbednost podataka visoka n brzina visoka n potrošnja niska n nepogodna za izradu prototipa n tehnologija prošlih generacija Fleš / EEPROM n reprogramibilan (in system/off-line) n volatile/non-volatile n bezbednost podataka visoka n brzina visoka n potrošnja niska n pogodna za izradu prototipa n već korišćena tehnologija a pojavljuje se razvoj hibrida fleš/SRAM

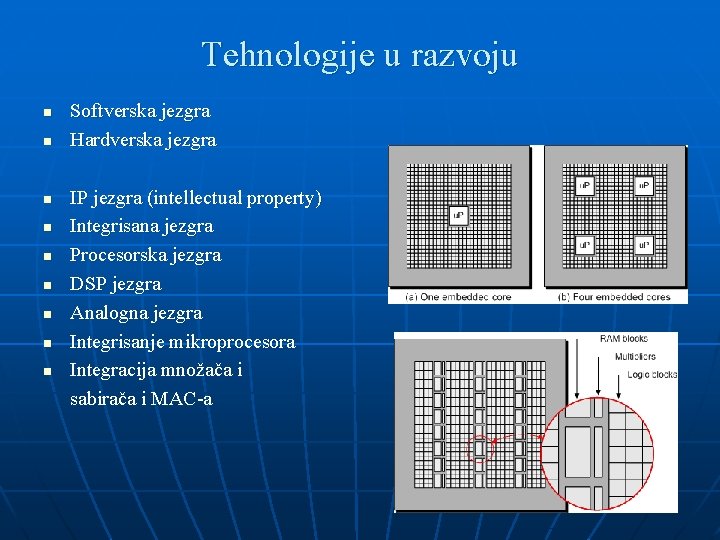

Tehnologije u razvoju n n n n n Softverska jezgra Hardverska jezgra IP jezgra (intellectual property) Integrisana jezgra Procesorska jezgra DSP jezgra Analogna jezgra Integrisanje mikroprocesora Integracija množača i sabirača i MAC-a

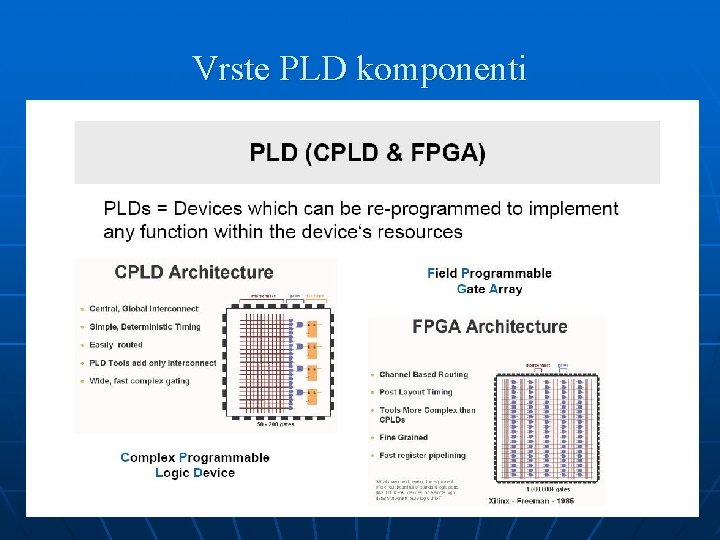

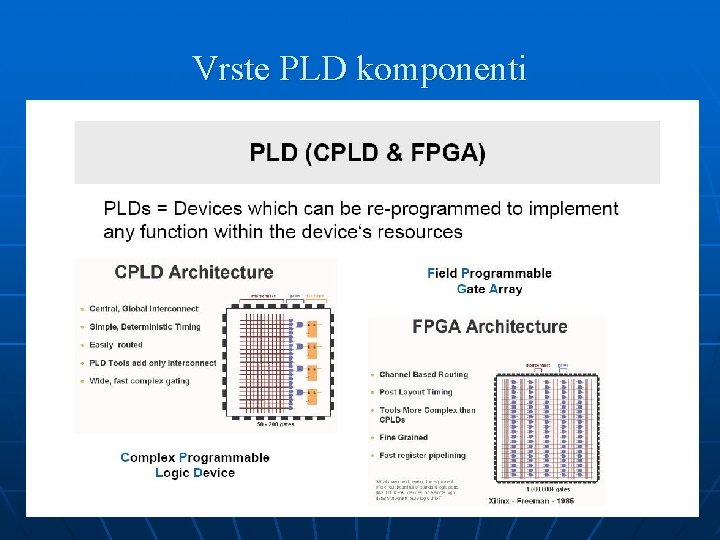

Vrste PLD komponenti

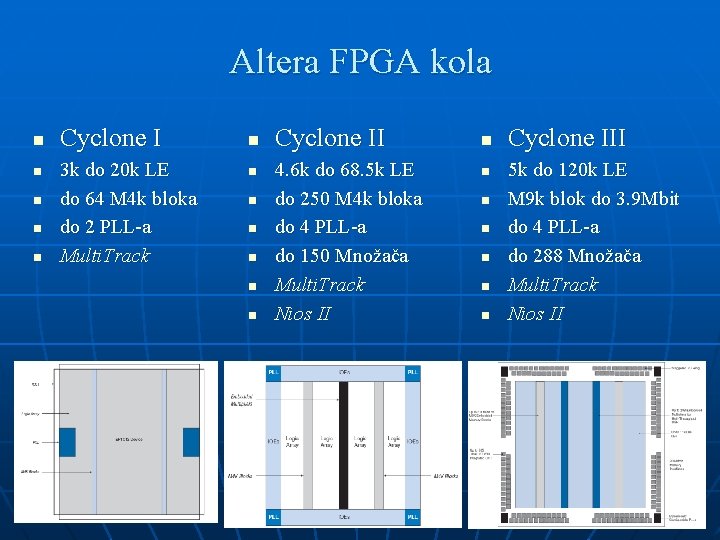

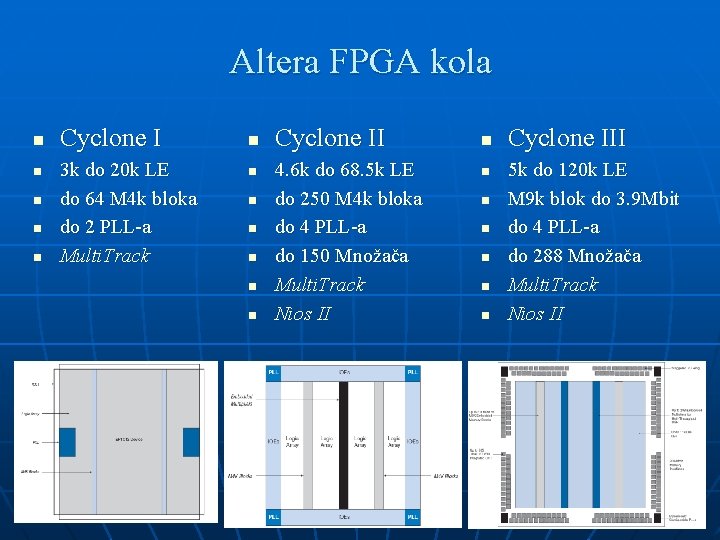

Altera FPGA kola n n n Cyclone I 3 k do 20 k LE do 64 M 4 k bloka do 2 PLL-a Multi. Track n n n n Cyclone II 4. 6 k do 68. 5 k LE do 250 M 4 k bloka do 4 PLL-a do 150 Množača Multi. Track Nios II n n n n Cyclone III 5 k do 120 k LE M 9 k blok do 3. 9 Mbit do 4 PLL-a do 288 Množača Multi. Track Nios II

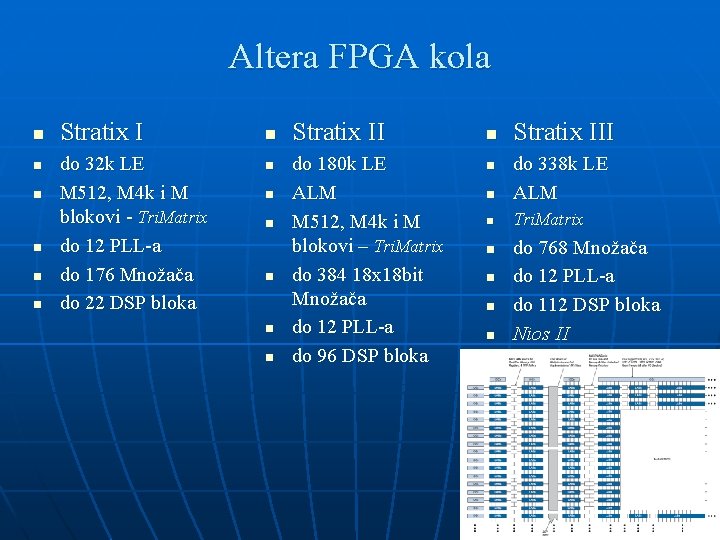

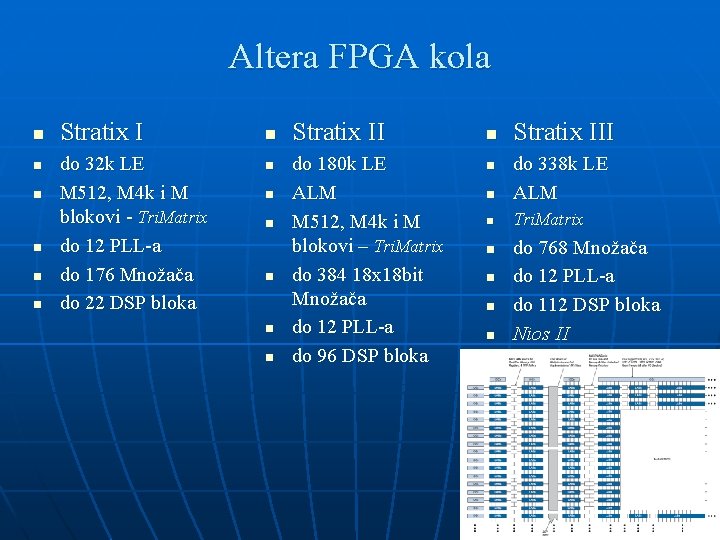

Altera FPGA kola n n n Stratix I do 32 k LE M 512, M 4 k i M blokovi - Tri. Matrix do 12 PLL-a do 176 Množača do 22 DSP bloka n n n n Stratix II do 180 k LE ALM M 512, M 4 k i M blokovi – Tri. Matrix do 384 18 x 18 bit Množača do 12 PLL-a do 96 DSP bloka n Stratix III n do 338 k LE ALM n Tri. Matrix n n n do 768 Množača do 12 PLL-a do 112 DSP bloka Nios II

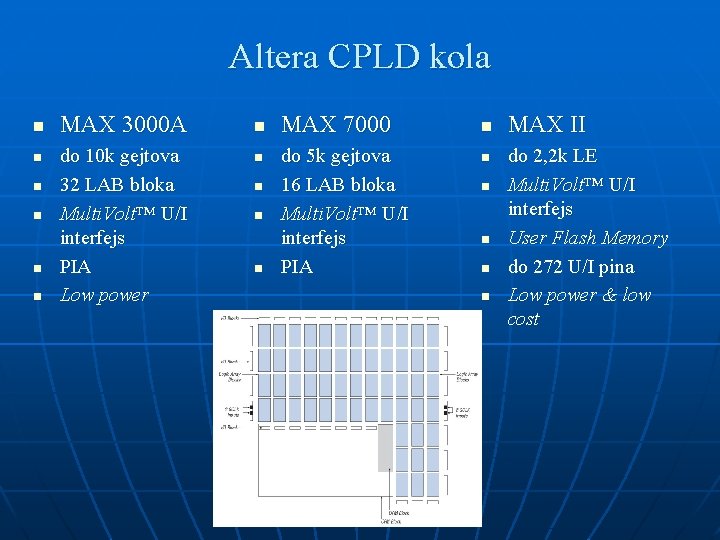

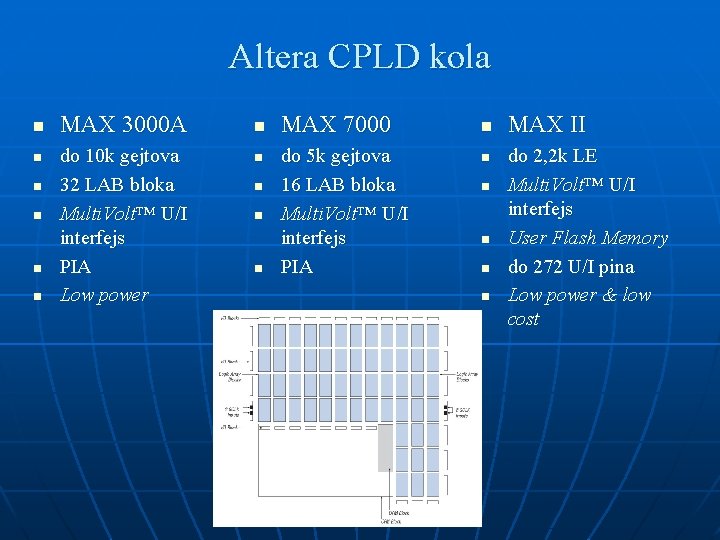

Altera CPLD kola n n n MAX 3000 A do 10 k gejtova 32 LAB bloka Multi. Volt™ U/I interfejs PIA Low power n n n MAX 7000 do 5 k gejtova 16 LAB bloka Multi. Volt™ U/I interfejs PIA n n n MAX II do 2, 2 k LE Multi. Volt™ U/I interfejs User Flash Memory do 272 U/I pina Low power & low cost

Katedra za elektroniku

Katedra za elektroniku Katedra za elektroniku

Katedra za elektroniku Katedra za elektroniku

Katedra za elektroniku Pravni fakultet podgorica smjerovi

Pravni fakultet podgorica smjerovi Uvod u digitalnu i mikroracunarsku elektroniku

Uvod u digitalnu i mikroracunarsku elektroniku Niu blackboard

Niu blackboard Niu irb

Niu irb Qian niu

Qian niu Webcourses niu

Webcourses niu Niu

Niu Qian niu

Qian niu Seasite tagalog

Seasite tagalog Cooperative business definition

Cooperative business definition Artemus ward niu

Artemus ward niu Actor affix

Actor affix Niu

Niu Unvi edu ba

Unvi edu ba Kallos tuzla akreditacija

Kallos tuzla akreditacija Univerzitet u novom sadu

Univerzitet u novom sadu