Digital Integrated Circuits A Design Perspective Jan M

- Slides: 60

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic Memórias Semicondutoras December 20, 2002 © Digital Integrated Circuits 2 nd Memories

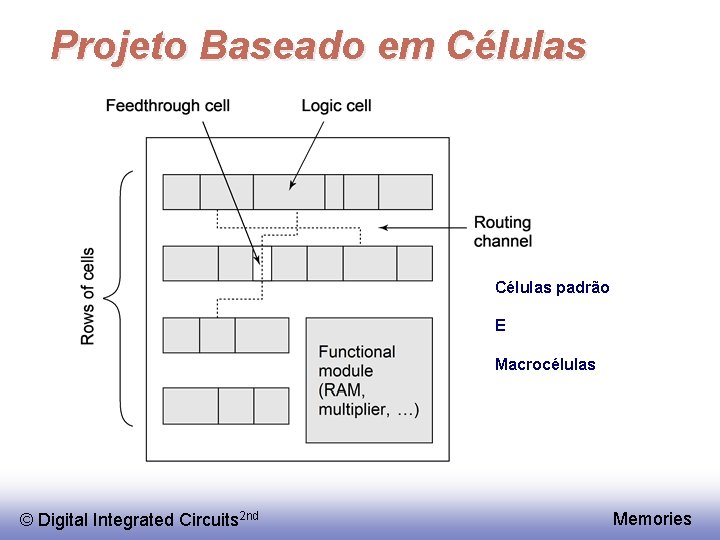

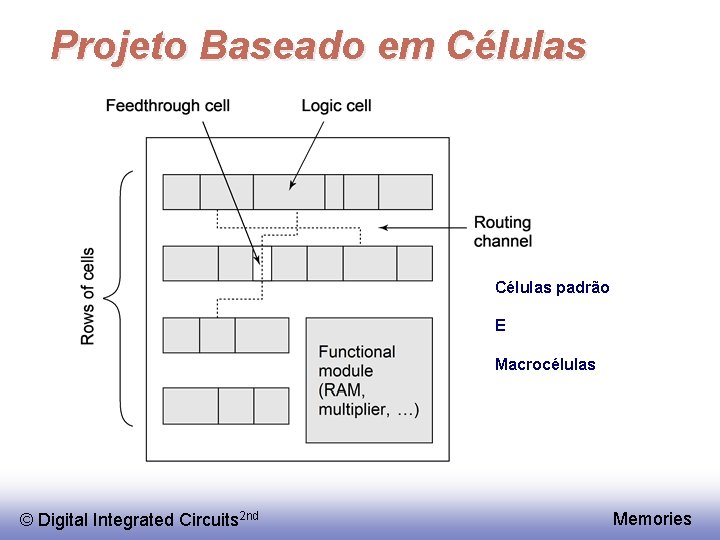

Projeto Baseado em Células padrão E Macrocélulas © Digital Integrated Circuits 2 nd Memories

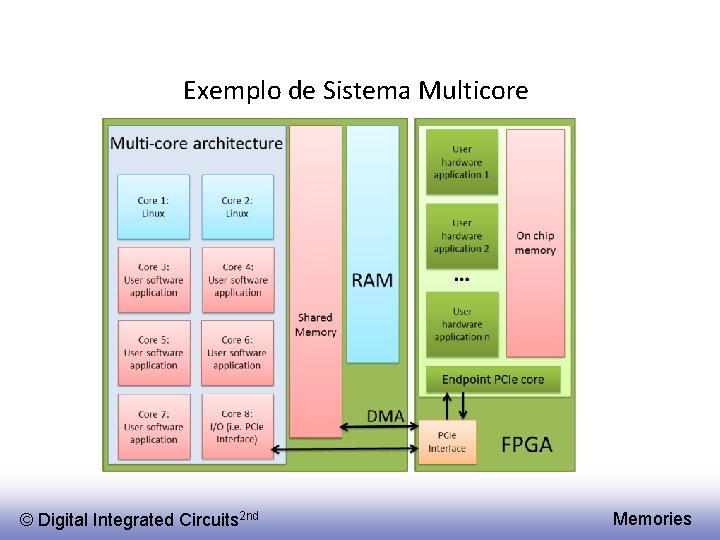

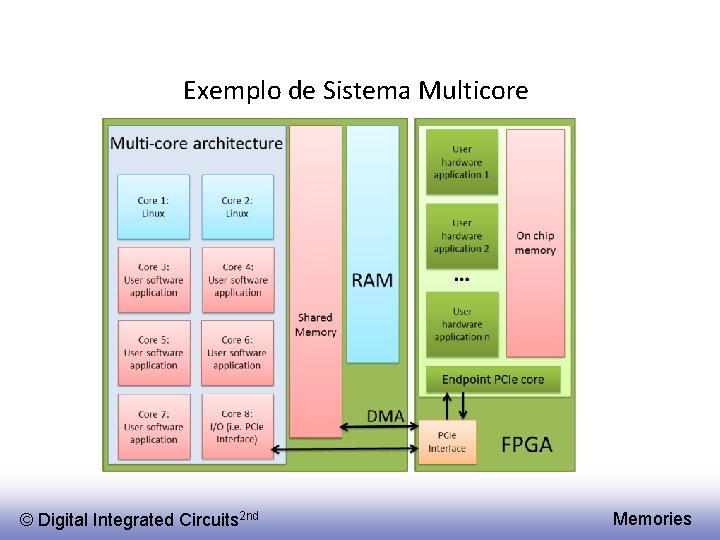

Exemplo de Sistema Multicore © Digital Integrated Circuits 2 nd Memories

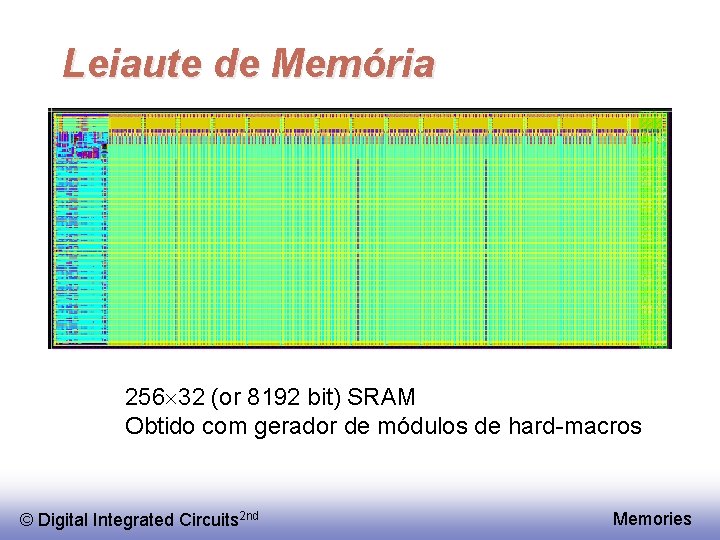

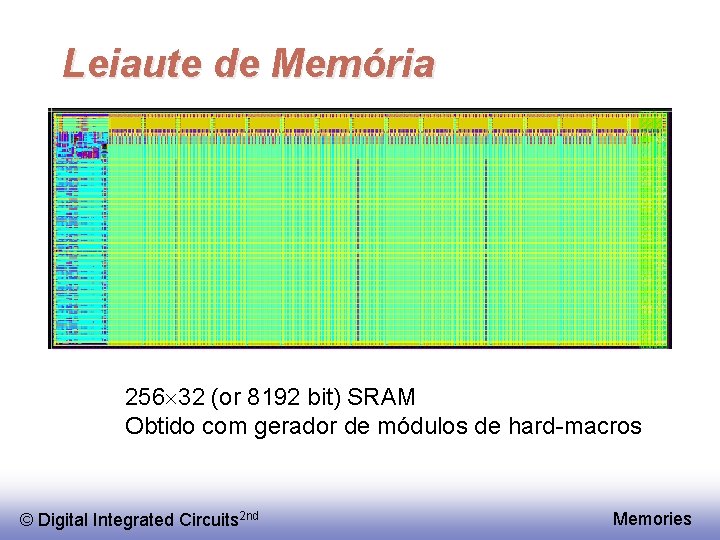

Leiaute de Memória 256 32 (or 8192 bit) SRAM Obtido com gerador de módulos de hard-macros © Digital Integrated Circuits 2 nd Memories

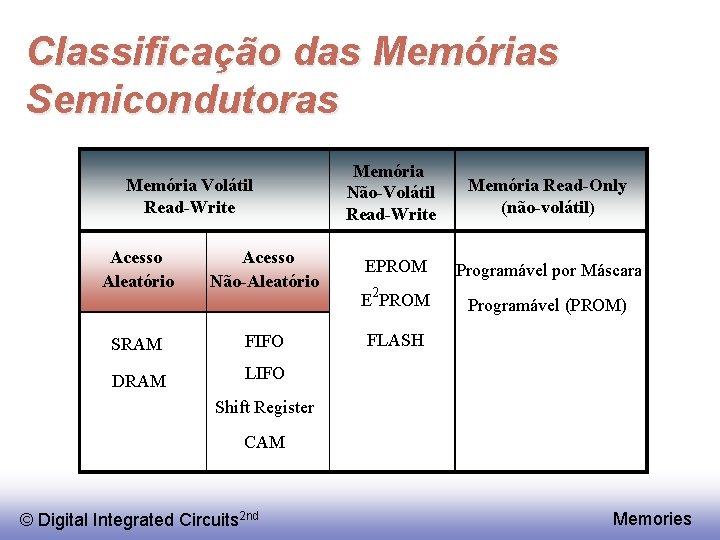

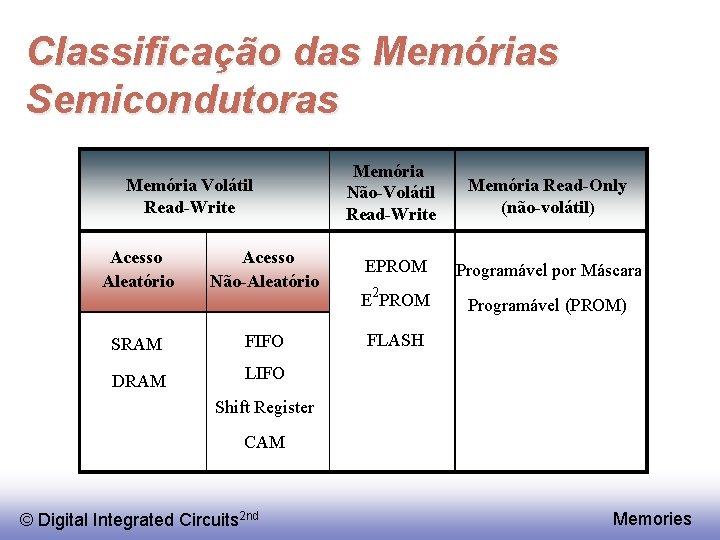

Classificação das Memórias Semicondutoras Memória Volátil Read-Write Acesso Aleatório Acesso Não-Aleatório SRAM FIFO DRAM LIFO Memória Não-Volátil Read-Write Memória Read-Only (não-volátil) EPROM Programável por Máscara E 2 PROM Programável (PROM) FLASH Shift Register CAM © Digital Integrated Circuits 2 nd Memories

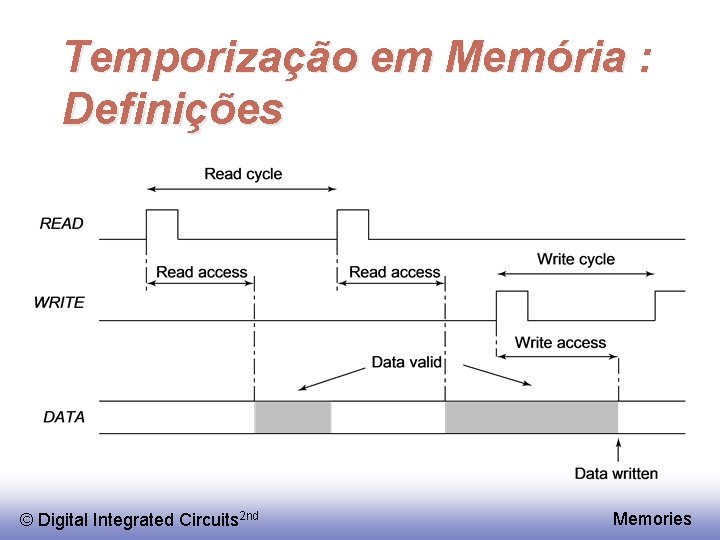

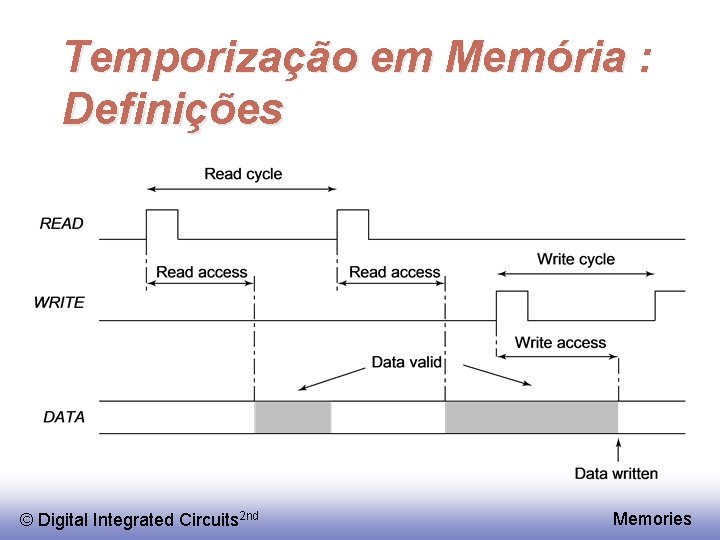

Temporização em Memória : Definições © Digital Integrated Circuits 2 nd Memories

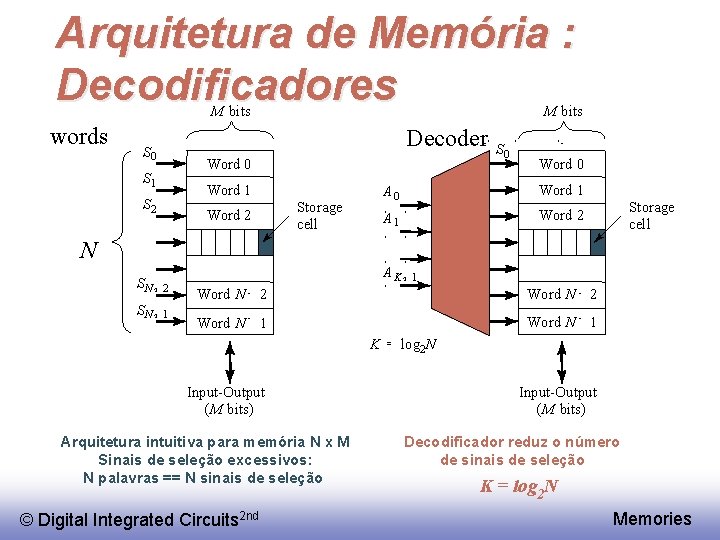

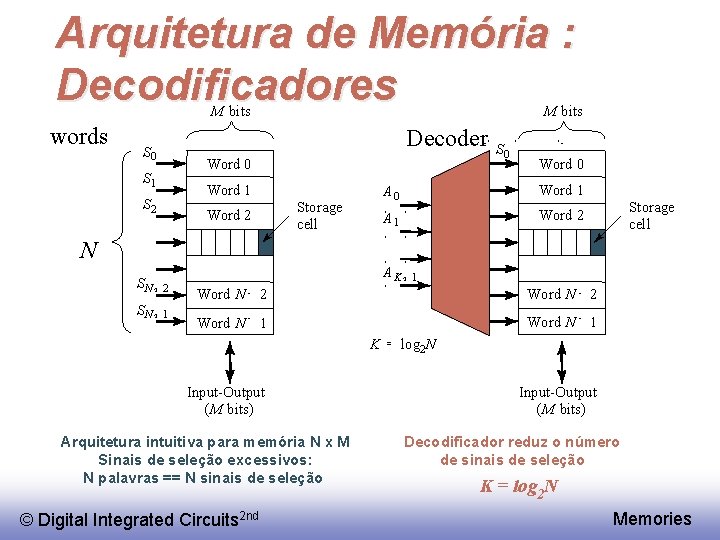

Arquitetura de Memória : Decodificadores M bits words M bits Decoder S 0 Word 0 S 1 Word 1 S 2 Word 2 Storage cell S 0 Word 0 A 0 Word 1 A 1 Word 2 Storage cell N SN 2 2 SN 2 1 Word N _ 2 _ Word N 1 A K 2 1 Word N _ 2 _ Word N 1 K = log 2 N Input-Output (M bits) Arquitetura intuitiva para memória N x M Sinais de seleção excessivos: N palavras == N sinais de seleção © Digital Integrated Circuits 2 nd Input-Output (M bits) Decodificador reduz o número de sinais de seleção K = log 2 N Memories

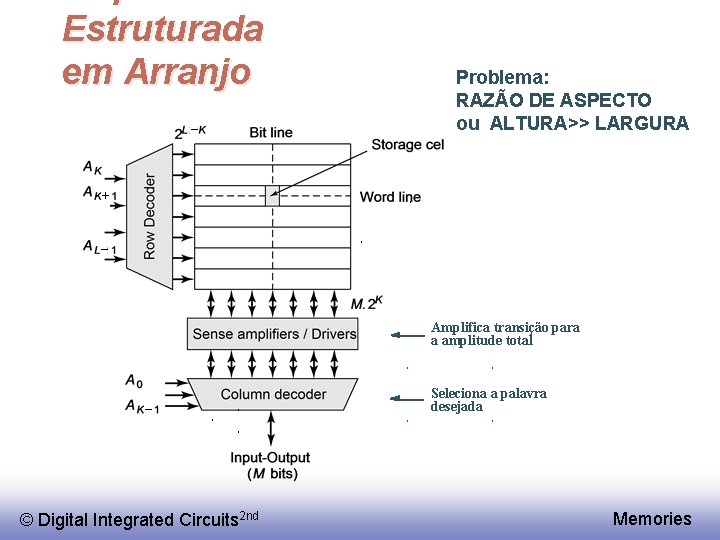

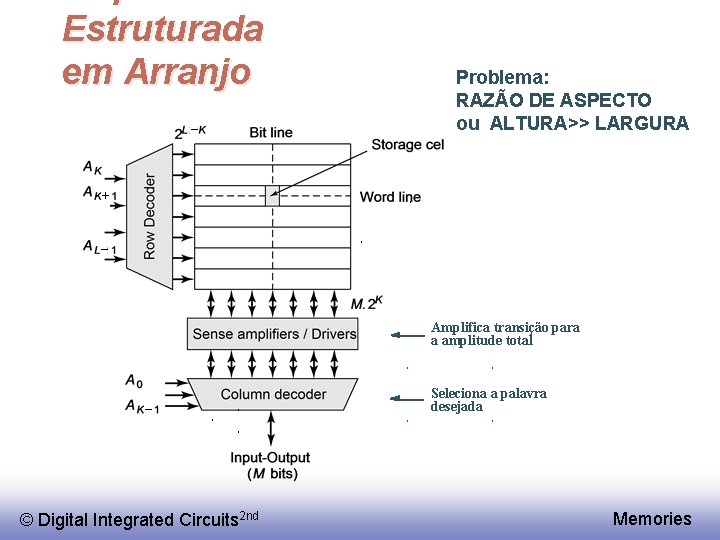

Estruturada em Arranjo _ Problema: RAZÃO DE ASPECTO ou ALTURA>> LARGURA + _ Amplifica transição para a amplitude total _ © Digital Integrated Circuits 2 nd Seleciona a palavra desejada Memories

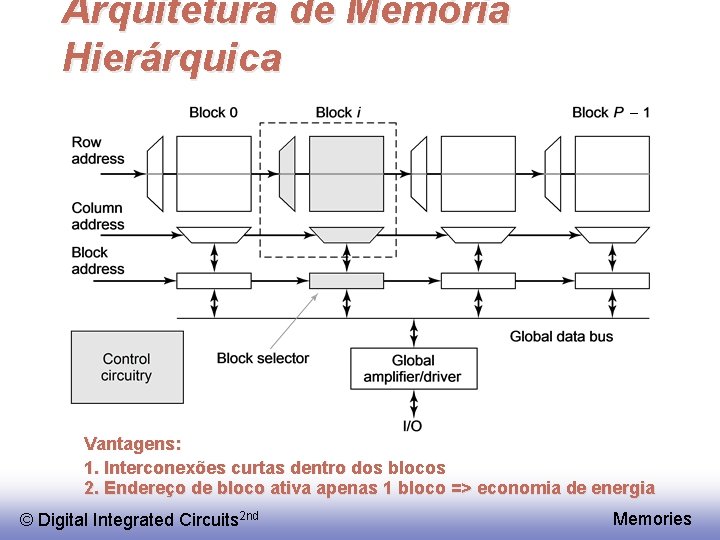

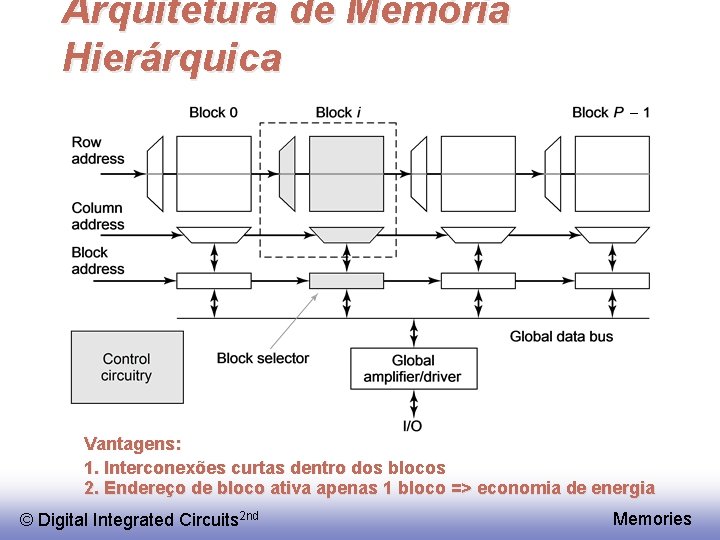

Arquitetura de Memória Hierárquica _ Vantagens: 1. Interconexões curtas dentro dos blocos 2. Endereço de bloco ativa apenas 1 bloco => economia de energia © Digital Integrated Circuits 2 nd Memories

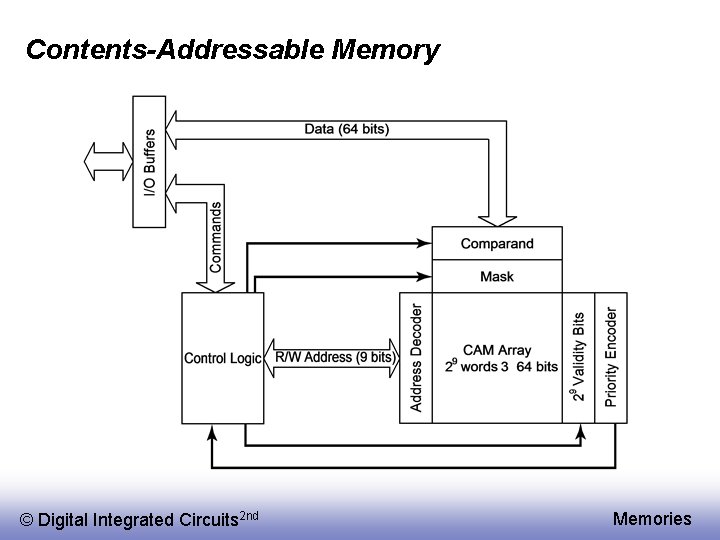

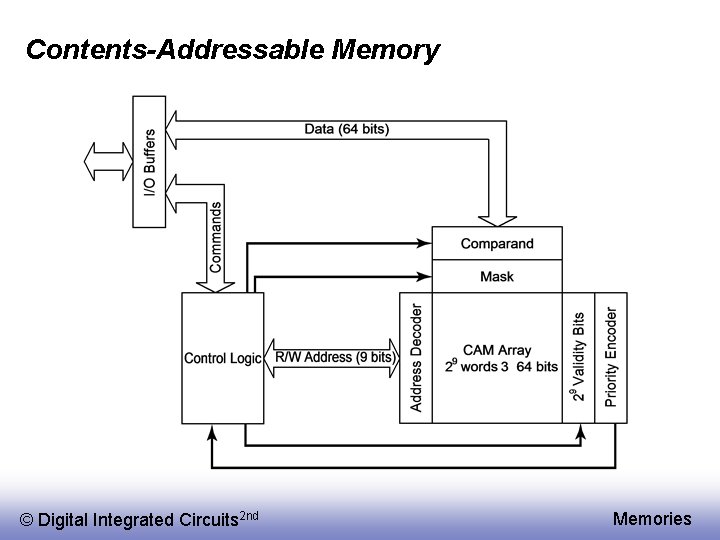

Contents-Addressable Memory © Digital Integrated Circuits 2 nd Memories

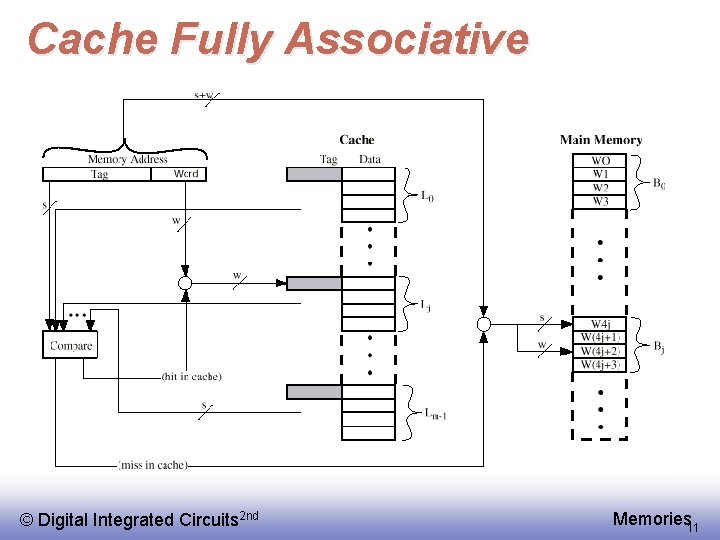

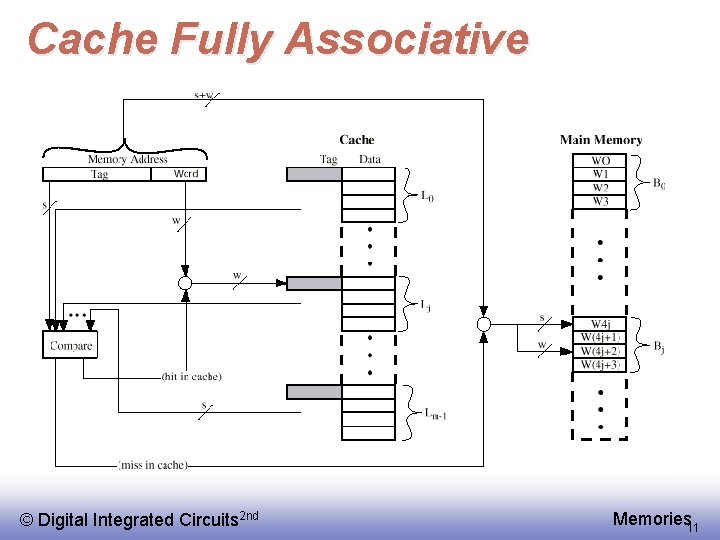

Cache Fully Associative © Digital Integrated Circuits 2 nd Memories 11

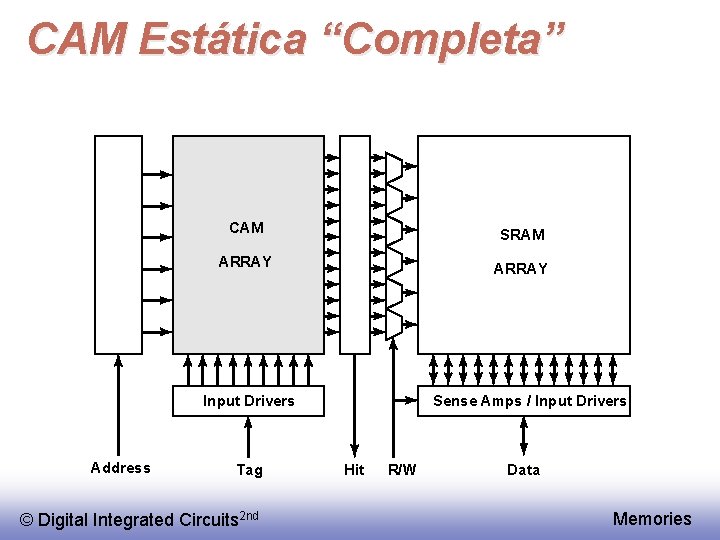

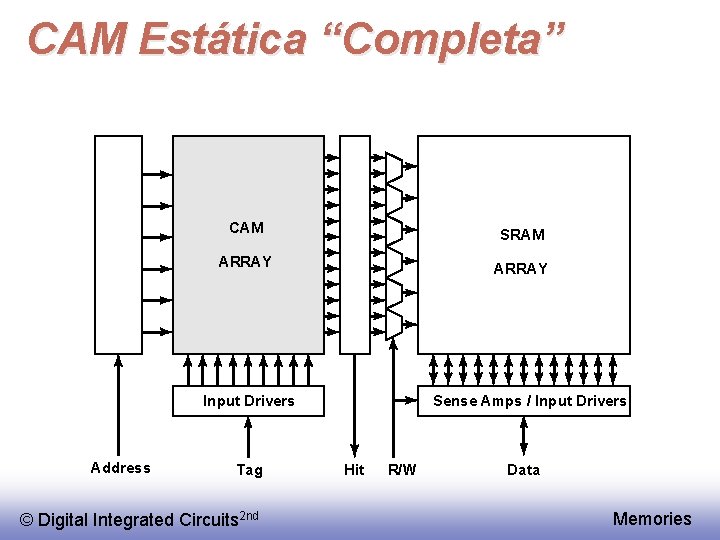

CAM Estática “Completa” CAM SRAM ARRAY Input Drivers Address Tag © Digital Integrated Circuits 2 nd Sense Amps / Input Drivers Hit R/W Data Memories

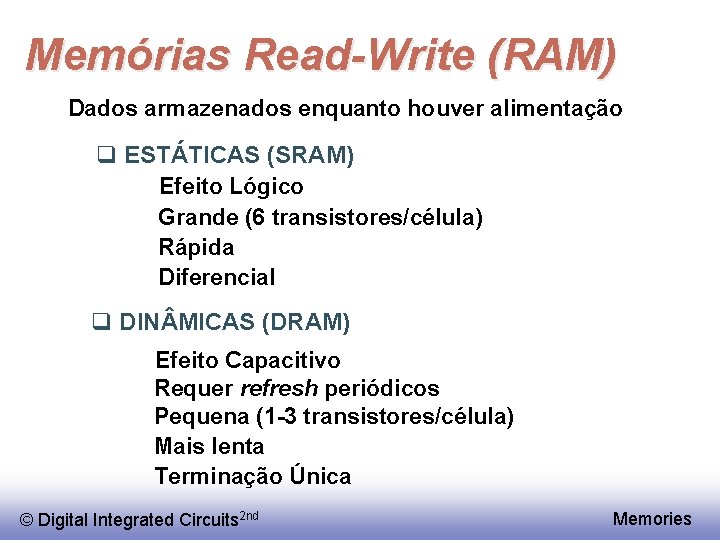

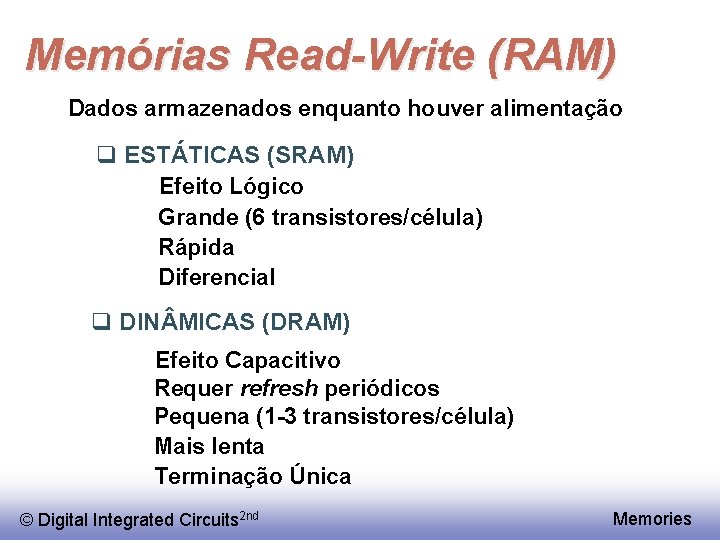

Memórias Read-Write (RAM) Dados armazenados enquanto houver alimentação q ESTÁTICAS (SRAM) Efeito Lógico Grande (6 transistores/célula) Rápida Diferencial q DIN MICAS (DRAM) Efeito Capacitivo Requer refresh periódicos Pequena (1 -3 transistores/célula) Mais lenta Terminação Única © Digital Integrated Circuits 2 nd Memories

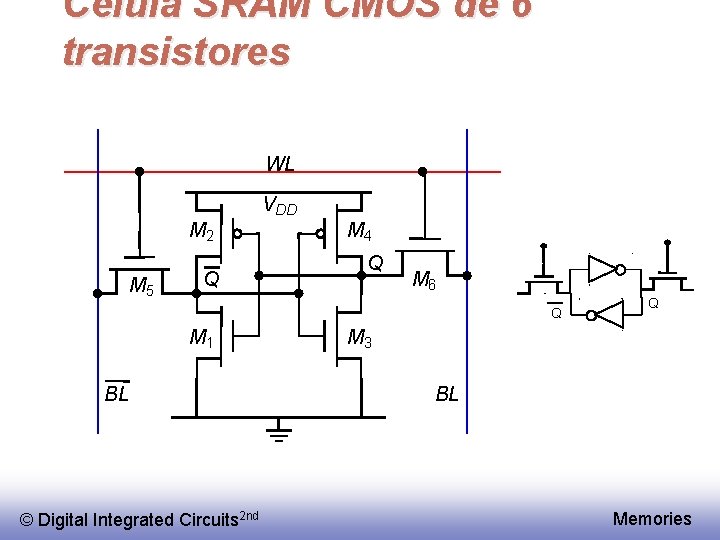

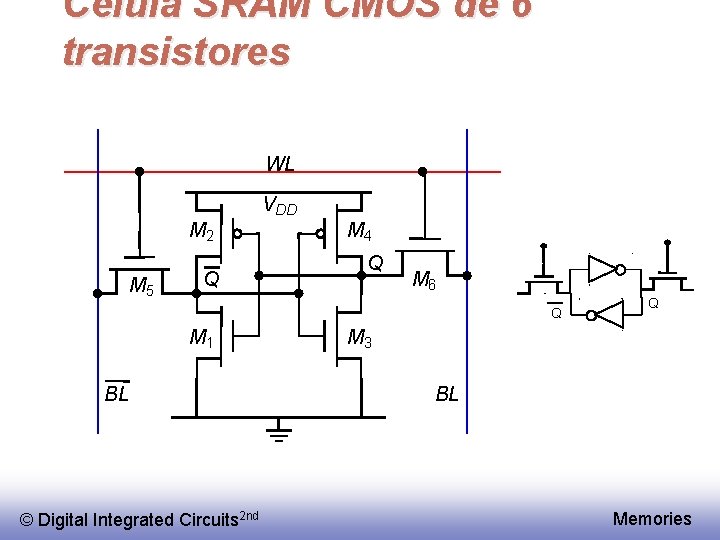

Célula SRAM CMOS de 6 transistores WL VDD M 2 M 5 Q M 4 Q M 6 Q M 1 BL © Digital Integrated Circuits 2 nd Q M 3 BL Memories

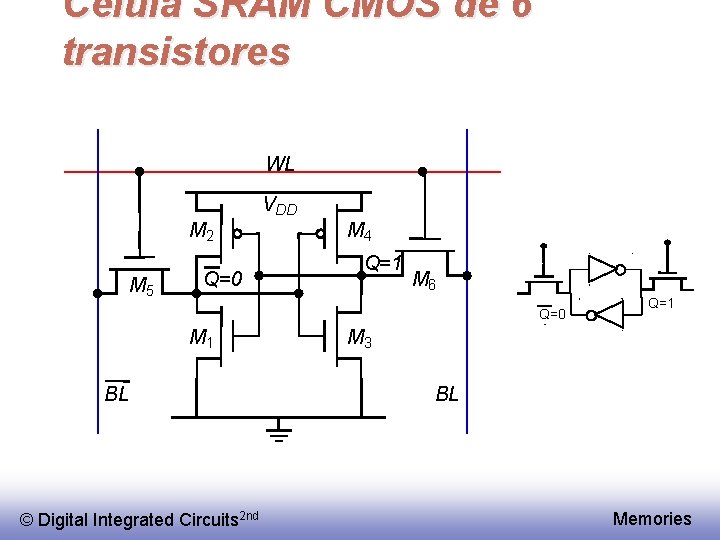

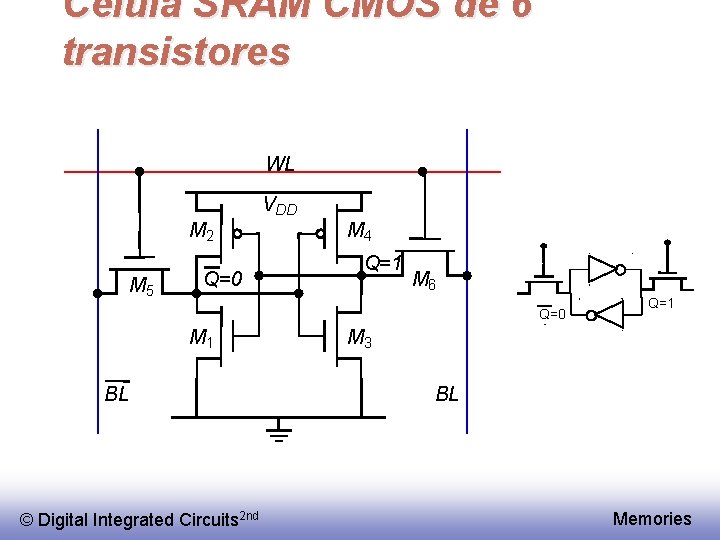

Célula SRAM CMOS de 6 transistores WL VDD M 2 M 5 Q=0 M 4 Q=1 M 6 Q=0 M 1 BL © Digital Integrated Circuits 2 nd Q=1 M 3 BL Memories

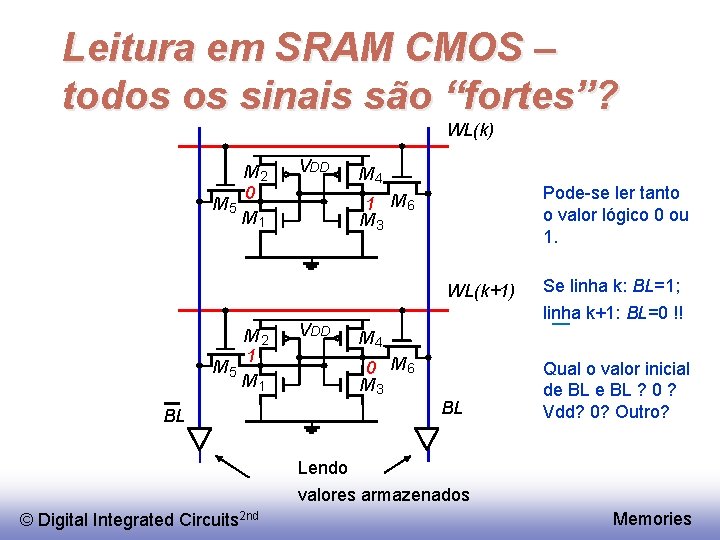

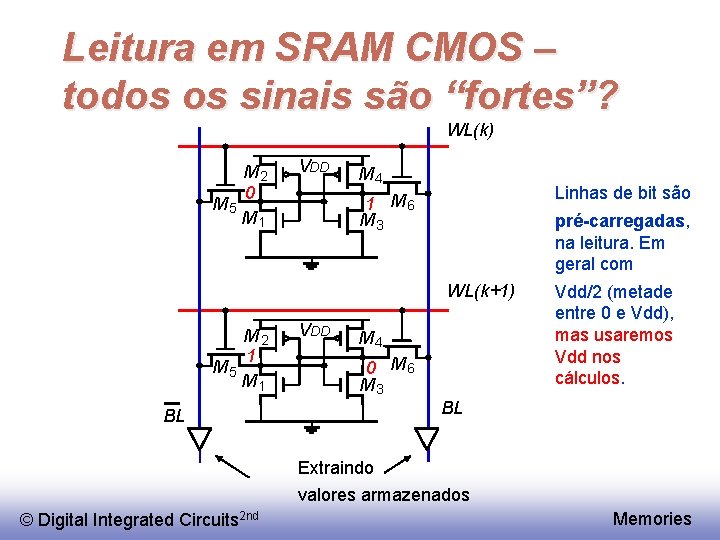

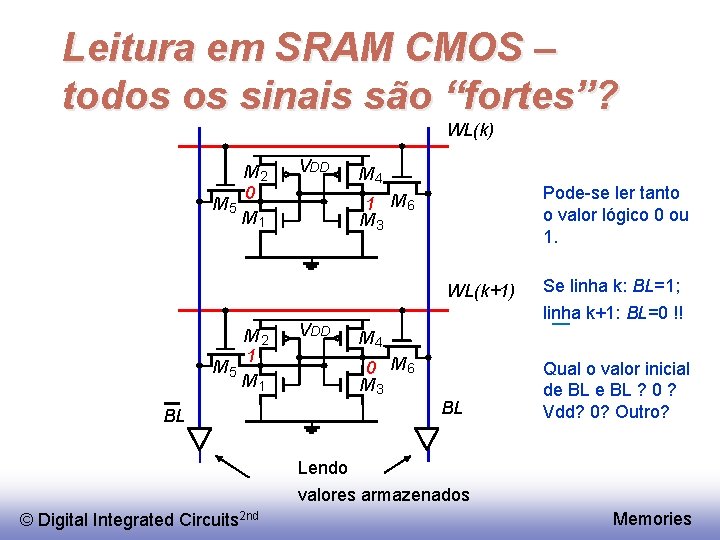

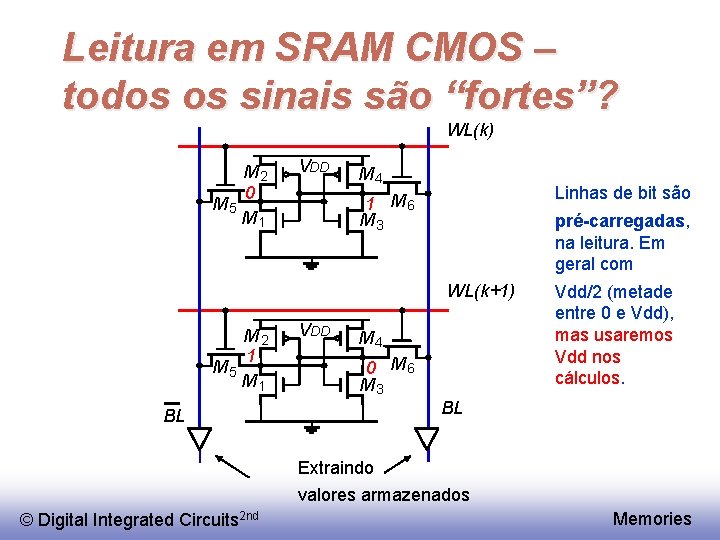

Leitura em SRAM CMOS – todos os sinais são “fortes”? WL(k) M 2 0 M 5 M 1 VDD M 4 Pode-se ler tanto o valor lógico 0 ou 1. 1 M 6 M 3 WL(k+1) M 2 1 M 5 M 1 VDD linha k+1: BL=0 !! M 4 0 M 6 M 3 BL BL Se linha k: BL=1; Qual o valor inicial de BL ? 0 ? Vdd? 0? Outro? Lendo valores armazenados © Digital Integrated Circuits 2 nd Memories

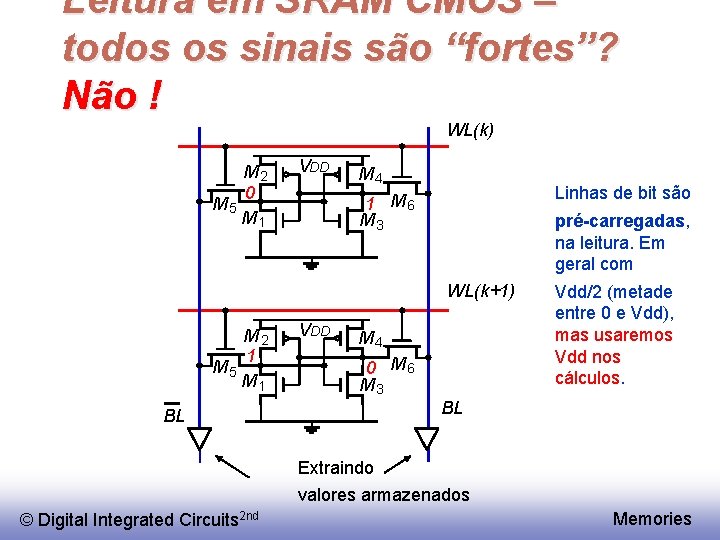

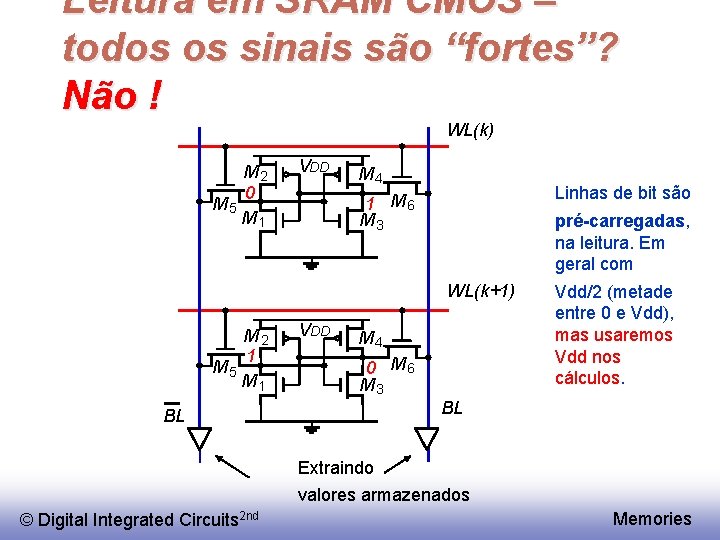

Leitura em SRAM CMOS – todos os sinais são “fortes”? WL(k) M 2 0 M 5 M 1 VDD M 4 Linhas de bit são 1 M 6 M 3 pré-carregadas, na leitura. Em geral com WL(k+1) M 2 1 M 5 M 1 VDD M 4 0 M 6 M 3 Vdd/2 (metade entre 0 e Vdd), mas usaremos Vdd nos cálculos. BL BL Extraindo valores armazenados © Digital Integrated Circuits 2 nd Memories

Leitura em SRAM CMOS – todos os sinais são “fortes”? Não ! WL(k) M 2 0 M 5 M 1 VDD M 4 Linhas de bit são 1 M 6 M 3 pré-carregadas, na leitura. Em geral com WL(k+1) M 2 1 M 5 M 1 VDD M 4 0 M 6 M 3 Vdd/2 (metade entre 0 e Vdd), mas usaremos Vdd nos cálculos. BL BL Extraindo valores armazenados © Digital Integrated Circuits 2 nd Memories

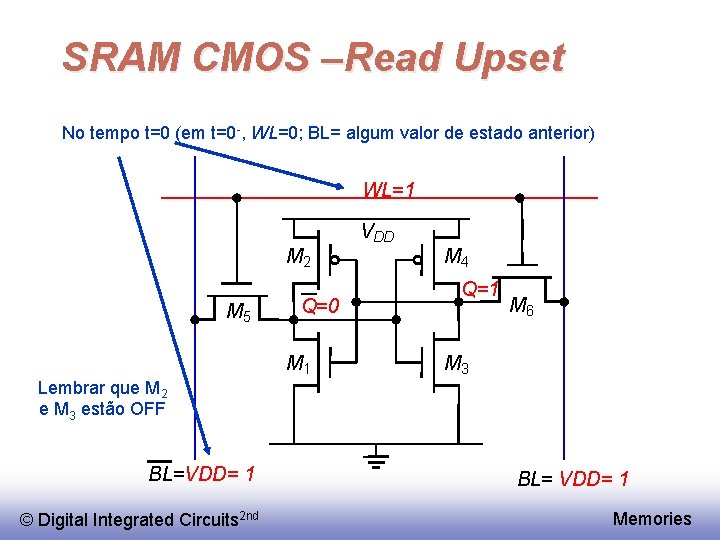

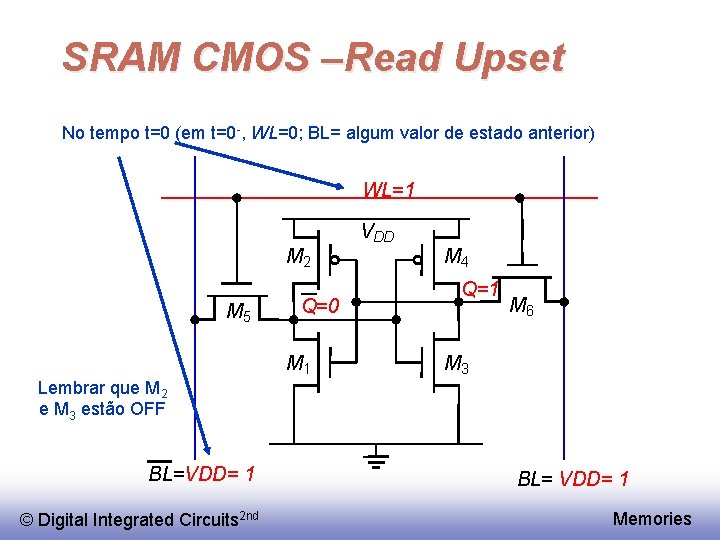

SRAM CMOS –Read Upset No tempo t=0 (em t=0 -, WL=0; BL= algum valor de estado anterior) WL=1 VDD M 2 M 5 Lembrar que M 2 e M 3 estão OFF BL=VDD= 1 © Digital Integrated Circuits 2 nd Q=0 M 1 M 4 Q=1 M 6 M 3 BL= VDD= 1 Memories

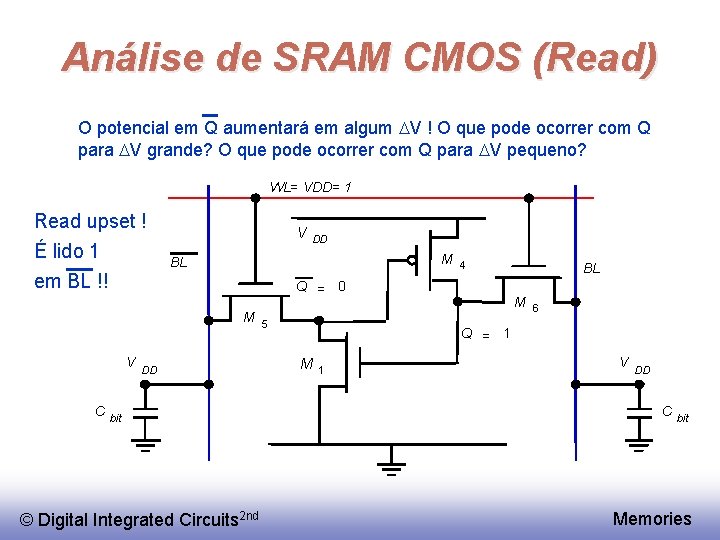

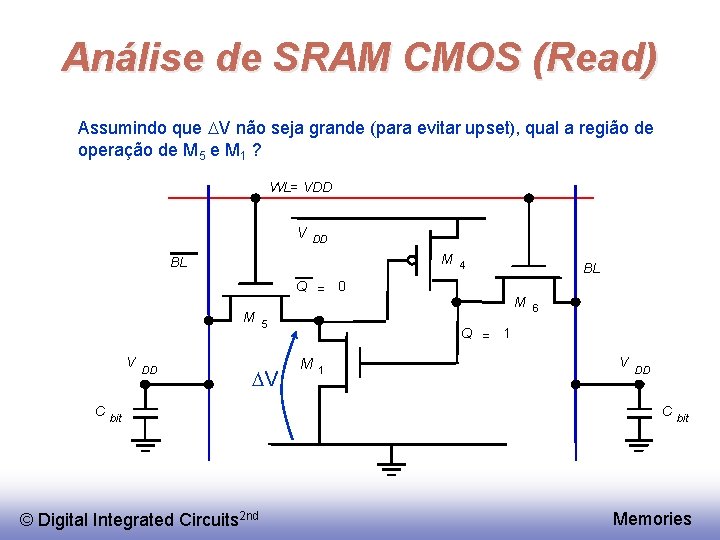

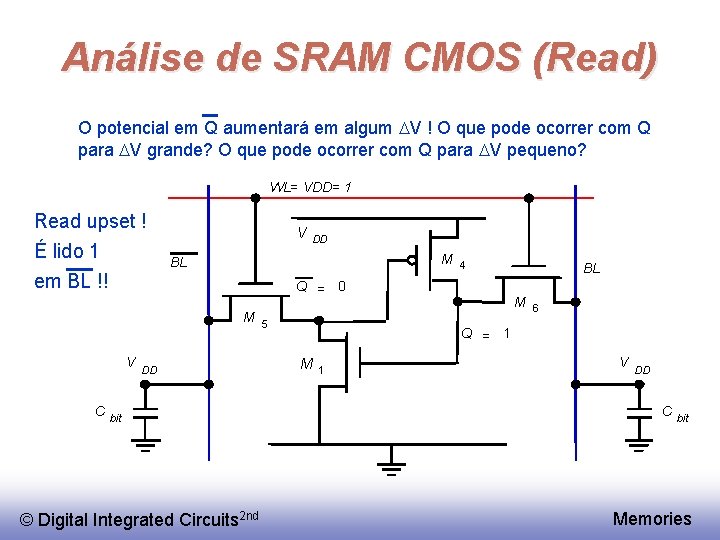

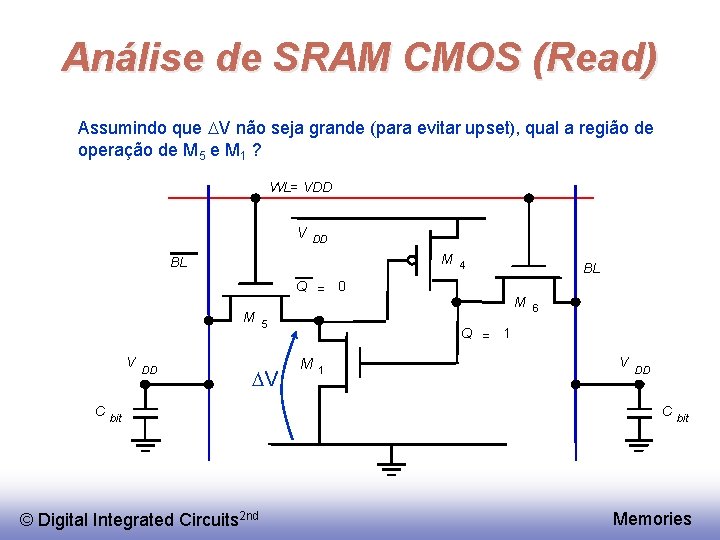

Análise de SRAM CMOS (Read) O potencial em Q aumentará em algum DV ! O que pode ocorrer com Q para DV grande? O que pode ocorrer com Q para DV pequeno? WL= VDD= 1 Read upset ! É lido 1 em BL !! V M BL 4 Q = 0 M V C DD DD bit © Digital Integrated Circuits 2 nd 5 BL M 6 Q = 1 M 1 V DD C bit Memories

Análise de SRAM CMOS (Read) Assumindo que DV não seja grande (para evitar upset), qual a região de operação de M 5 e M 1 ? WL= VDD V DD M BL 4 Q = 0 M V C DD 5 DV bit © Digital Integrated Circuits 2 nd BL M 6 Q = 1 M 1 V DD C bit Memories

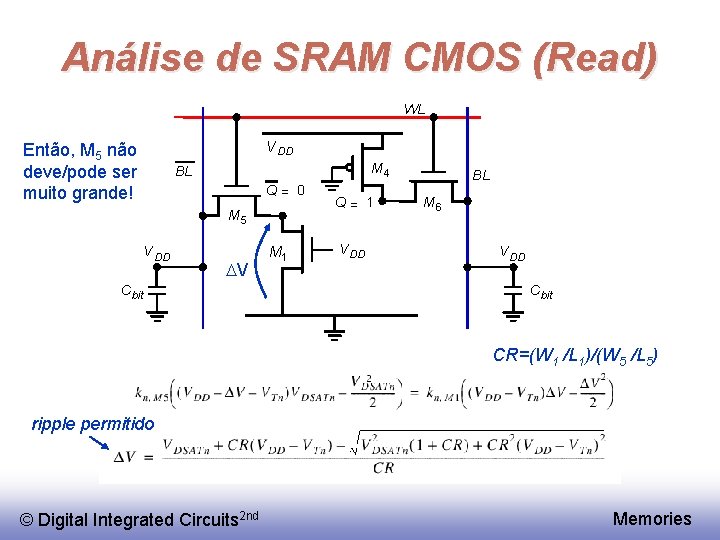

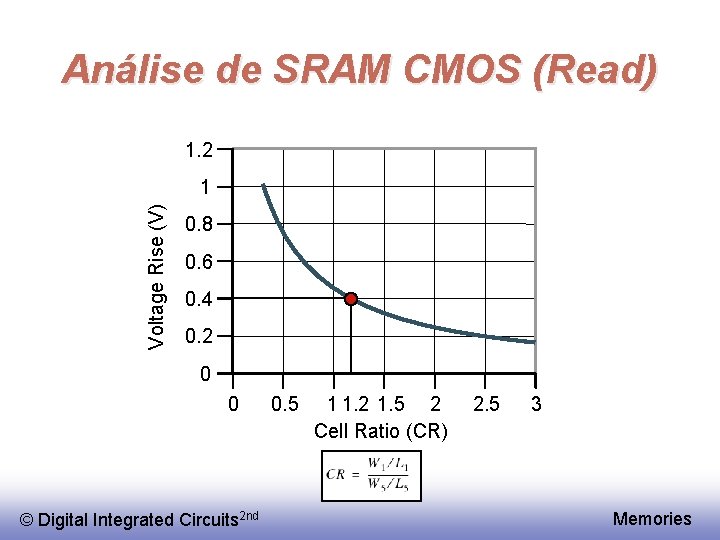

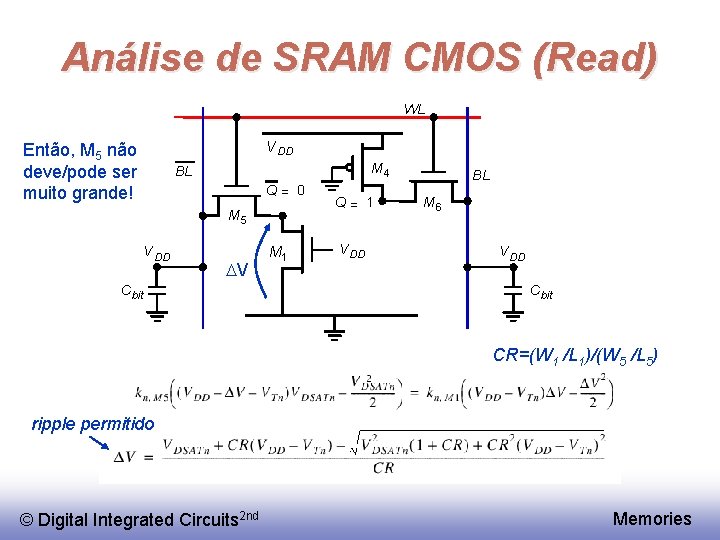

Análise de SRAM CMOS (Read) WL V DD Então, M 5 não deve/pode ser muito grande! M 4 BL Q= 0 M 5 V DD DV Cbit M 1 Q= 1 V DD BL M 6 V DD Cbit CR=(W 1 /L 1)/(W 5 /L 5) ripple permitido © Digital Integrated Circuits 2 nd Memories

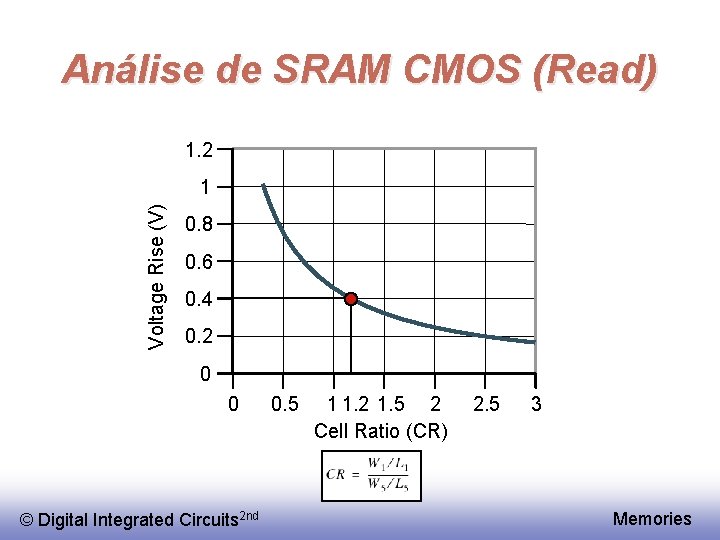

Análise de SRAM CMOS (Read) 1. 2 Voltage Rise (V) 1 0. 8 0. 6 0. 4 0. 2 0 0 © Digital Integrated Circuits 2 nd 0. 5 1 1. 2 1. 5 2 Cell Ratio (CR) 2. 5 3 Memories

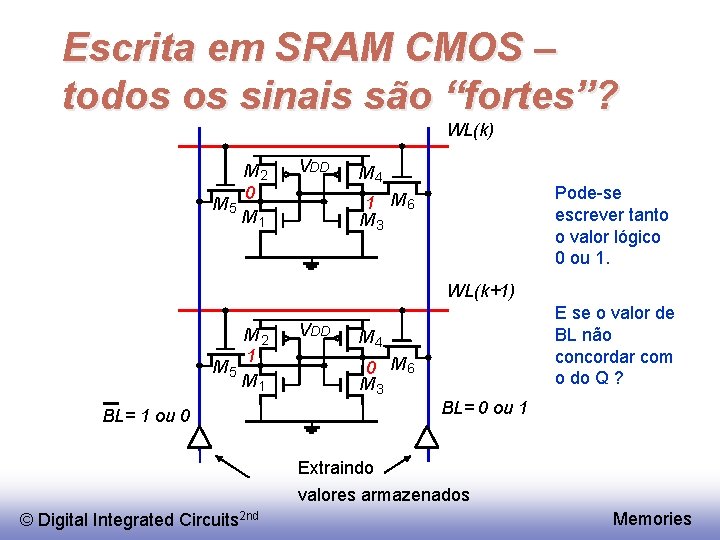

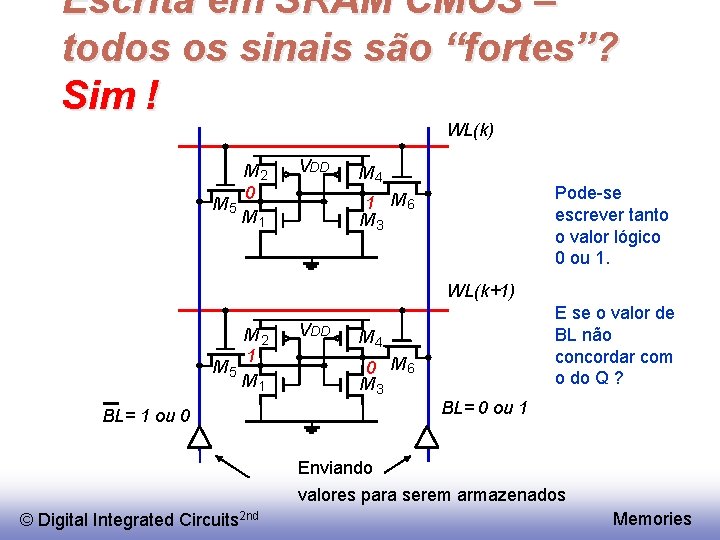

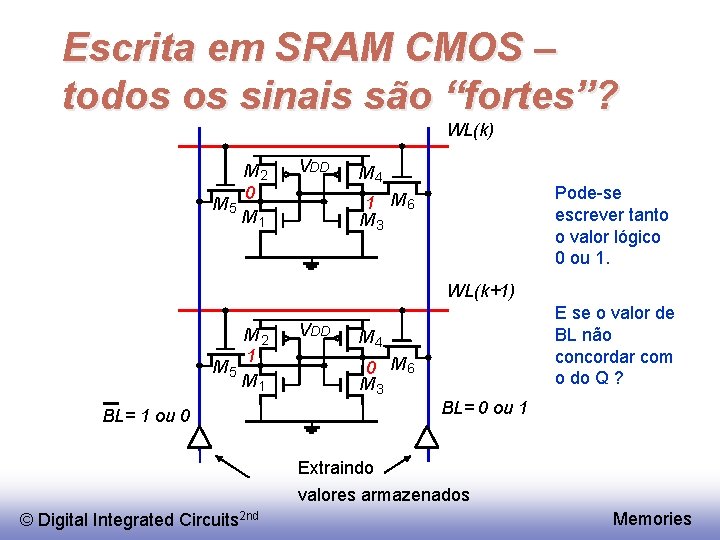

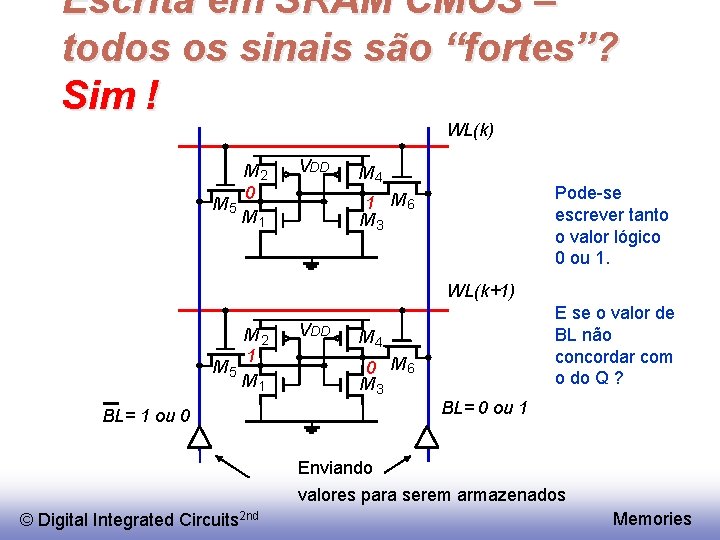

Escrita em SRAM CMOS – todos os sinais são “fortes”? WL(k) M 2 0 M 5 M 1 VDD M 4 Pode-se escrever tanto o valor lógico 0 ou 1. 1 M 6 M 3 WL(k+1) M 2 1 M 5 M 1 VDD E se o valor de BL não concordar com o do Q ? M 4 0 M 6 M 3 BL= 0 ou 1 BL= 1 ou 0 Extraindo valores armazenados © Digital Integrated Circuits 2 nd Memories

Escrita em SRAM CMOS – todos os sinais são “fortes”? Sim ! WL(k) M 2 0 M 5 M 1 VDD M 4 Pode-se escrever tanto o valor lógico 0 ou 1. 1 M 6 M 3 WL(k+1) M 2 1 M 5 M 1 VDD E se o valor de BL não concordar com o do Q ? M 4 0 M 6 M 3 BL= 0 ou 1 BL= 1 ou 0 Enviando valores para serem armazenados © Digital Integrated Circuits 2 nd Memories

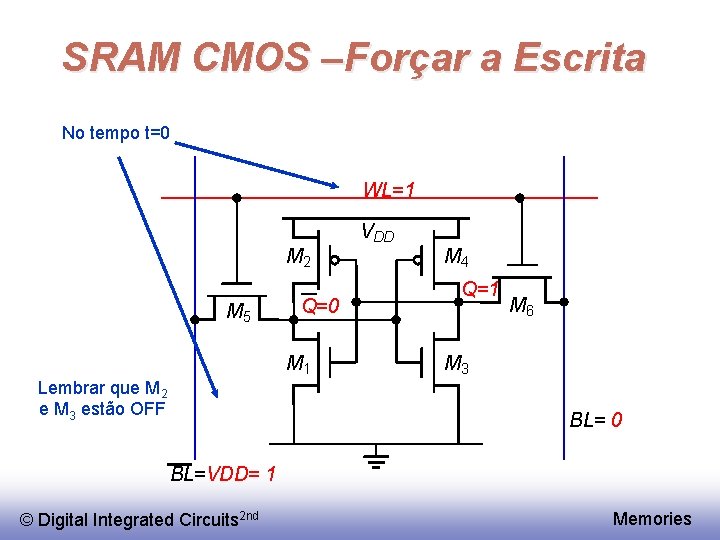

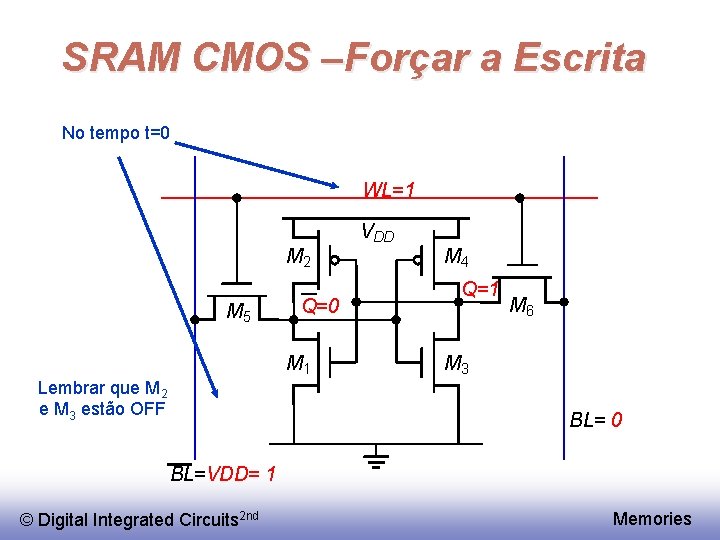

SRAM CMOS –Forçar a Escrita No tempo t=0 WL=1 VDD M 2 M 5 Q=0 M 1 Lembrar que M 2 e M 3 estão OFF M 4 Q=1 M 6 M 3 BL= 0 BL=VDD= 1 © Digital Integrated Circuits 2 nd Memories

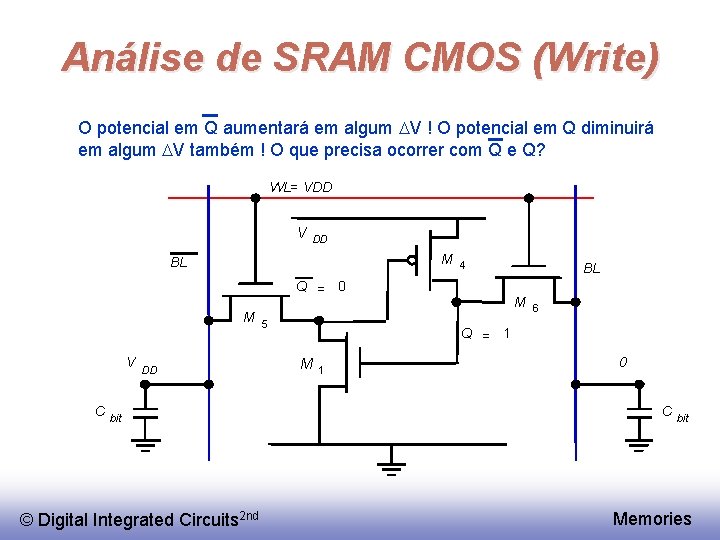

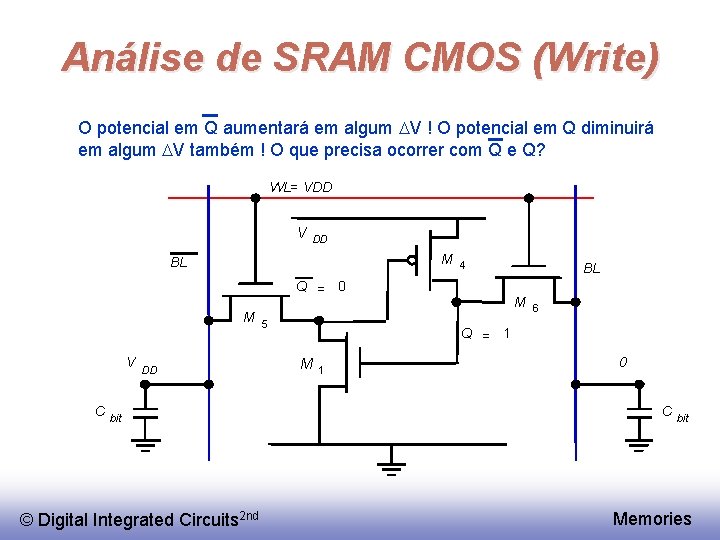

Análise de SRAM CMOS (Write) O potencial em Q aumentará em algum DV ! O potencial em Q diminuirá em algum DV também ! O que precisa ocorrer com Q e Q? WL= VDD V DD M BL 4 Q = 0 M V C DD bit © Digital Integrated Circuits 2 nd 5 BL M 6 Q = 1 M 1 0 C bit Memories

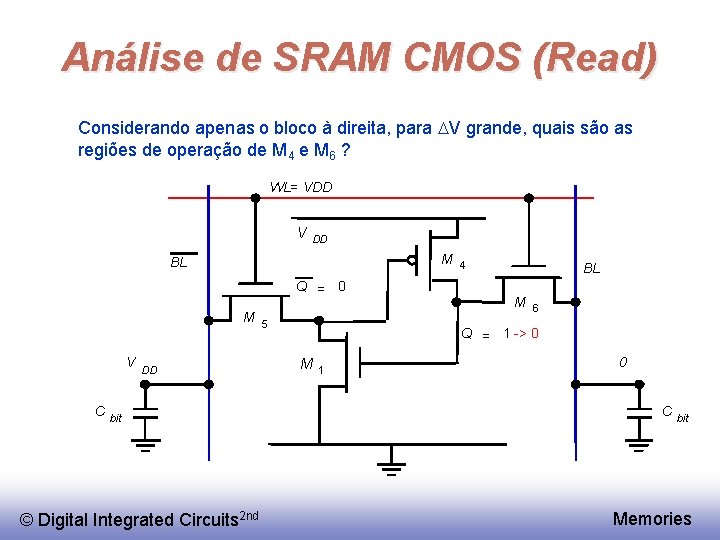

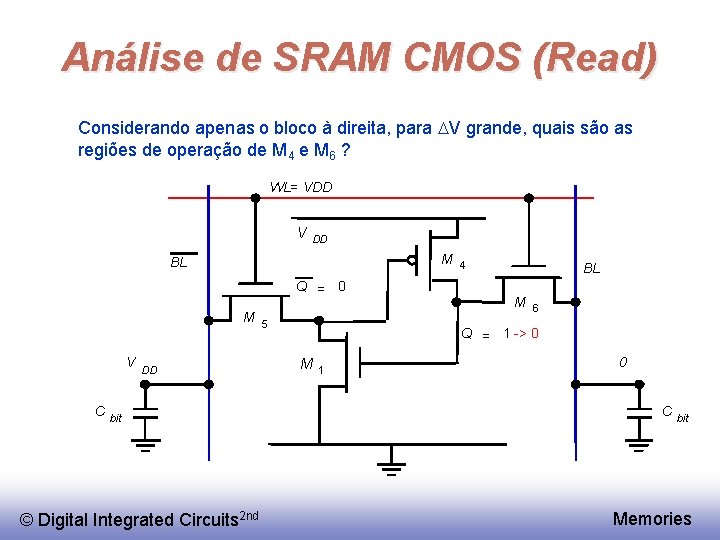

Análise de SRAM CMOS (Read) Considerando apenas o bloco à direita, para DV grande, quais são as regiões de operação de M 4 e M 6 ? WL= VDD V DD M BL Q = 0 M V C DD bit © Digital Integrated Circuits 2 nd 5 4 BL M 6 Q = 1 -> 0 M 1 0 C bit Memories

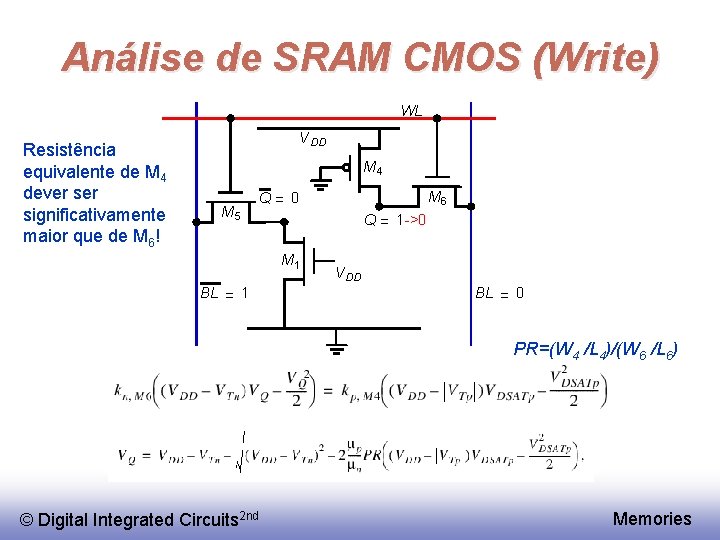

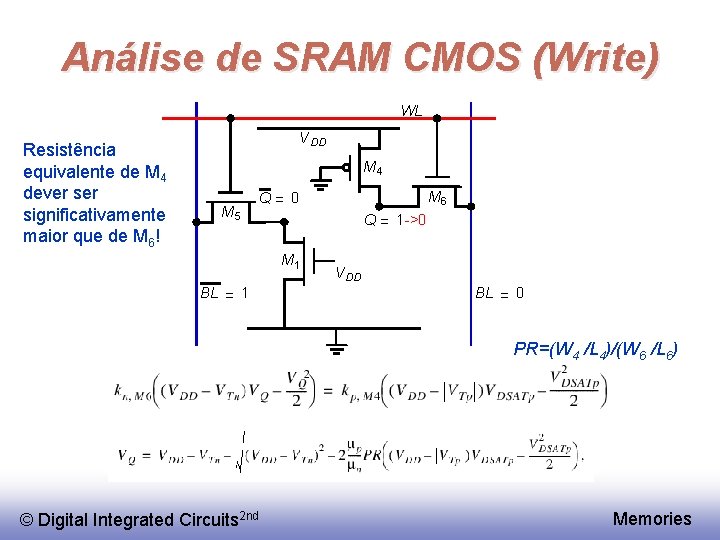

Análise de SRAM CMOS (Write) WL Resistência equivalente de M 4 dever significativamente maior que de M 6! V DD M 4 M 5 Q = 1 ->0 M 1 BL = 1 M 6 Q= 0 V DD BL = 0 PR=(W 4 /L 4)/(W 6 /L 6) © Digital Integrated Circuits 2 nd Memories

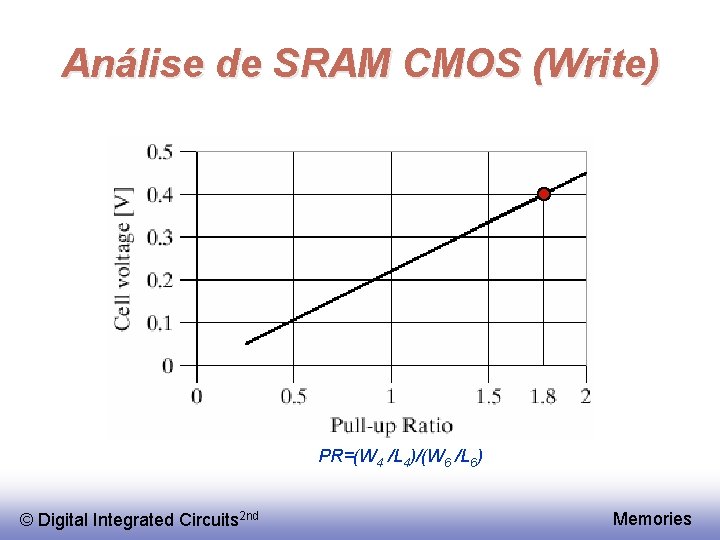

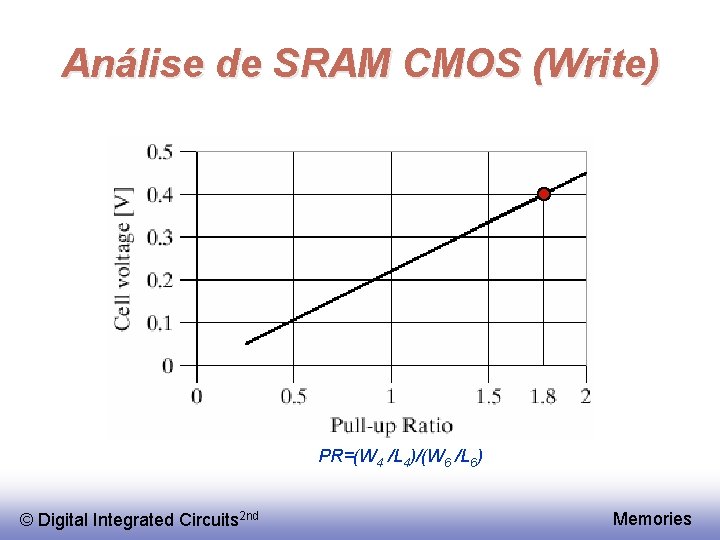

Análise de SRAM CMOS (Write) PR=(W 4 /L 4)/(W 6 /L 6) © Digital Integrated Circuits 2 nd Memories

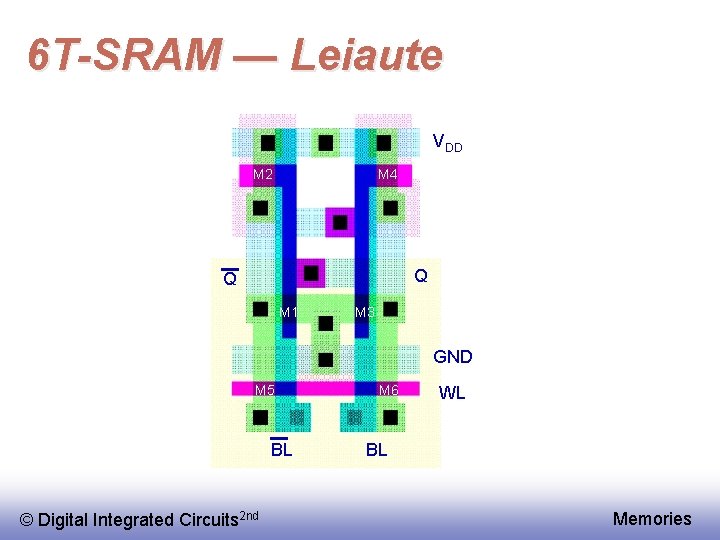

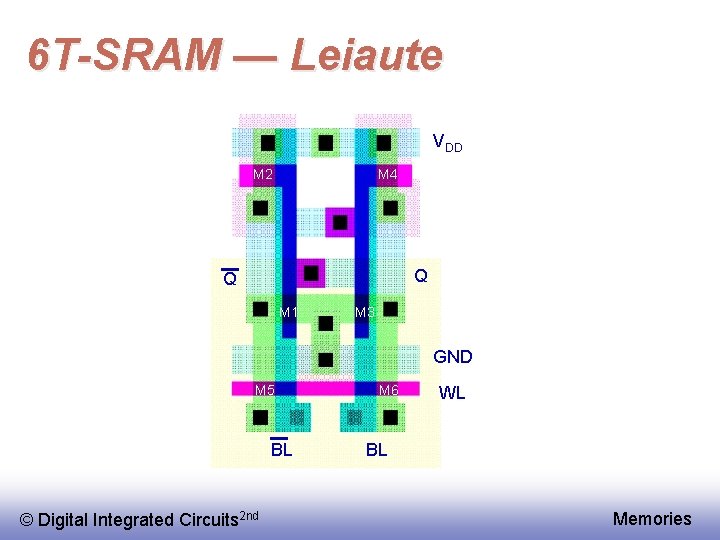

6 T-SRAM — Leiaute VDD M 2 M 4 Q Q M 1 M 3 GND M 5 BL © Digital Integrated Circuits 2 nd M 6 WL BL Memories

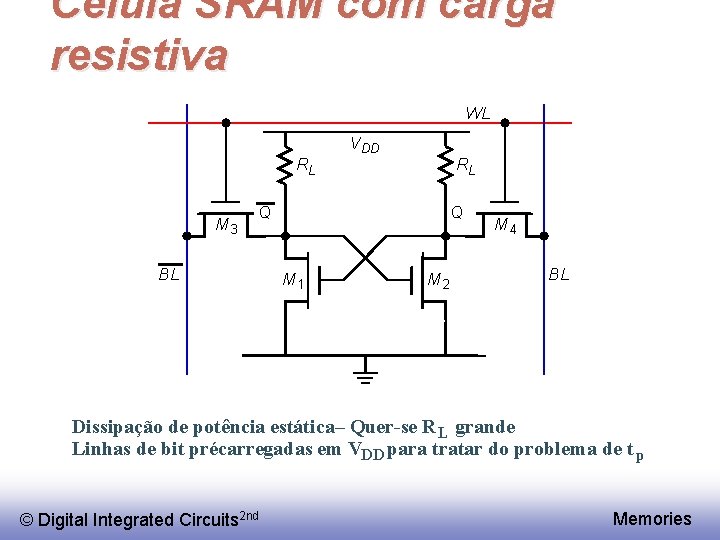

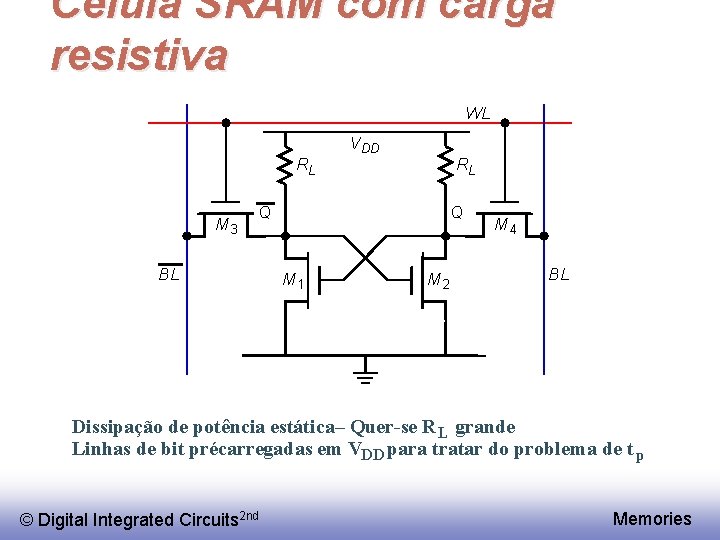

Célula SRAM com carga resistiva WL RL M 3 V DD RL Q BL Q M 1 M 2 M 4 BL Dissipação de potência estática– Quer-se R L grande Linhas de bit précarregadas em VDD para tratar do problema de t p © Digital Integrated Circuits 2 nd Memories

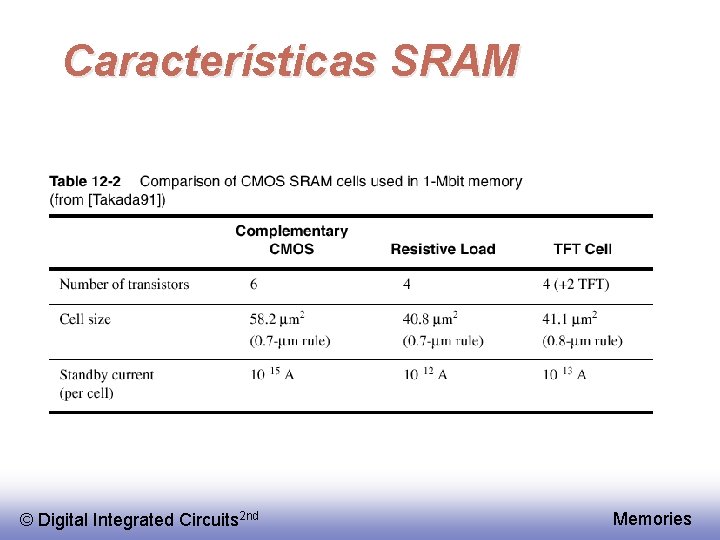

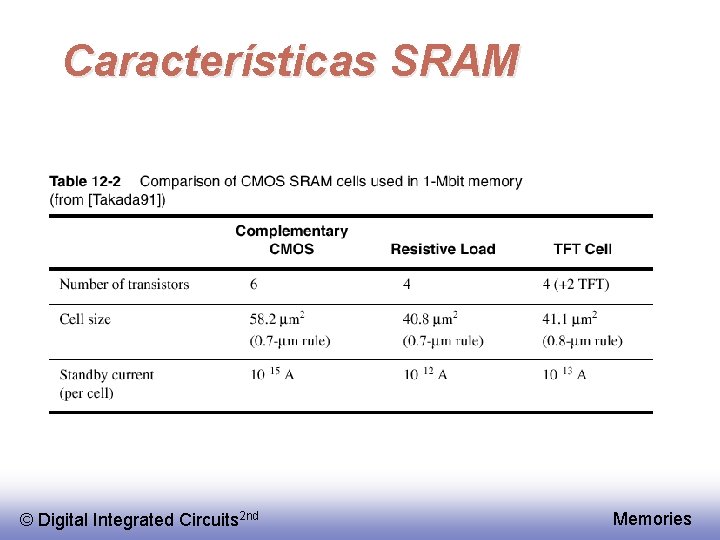

Características SRAM © Digital Integrated Circuits 2 nd Memories

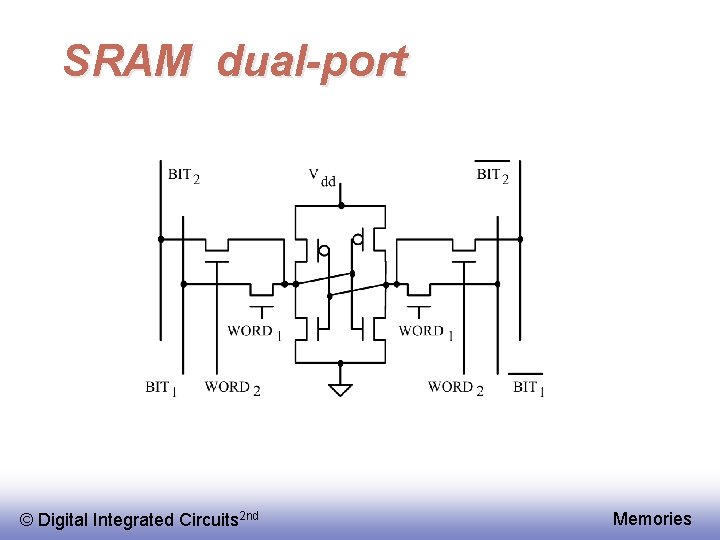

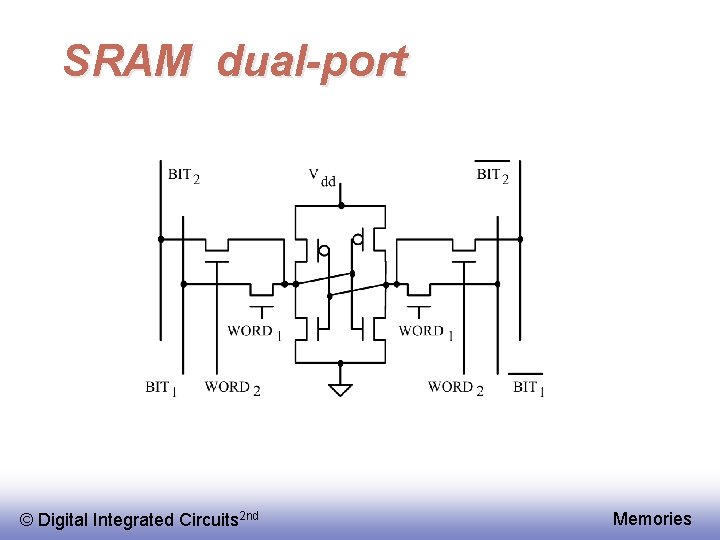

SRAM dual-port © Digital Integrated Circuits 2 nd Memories

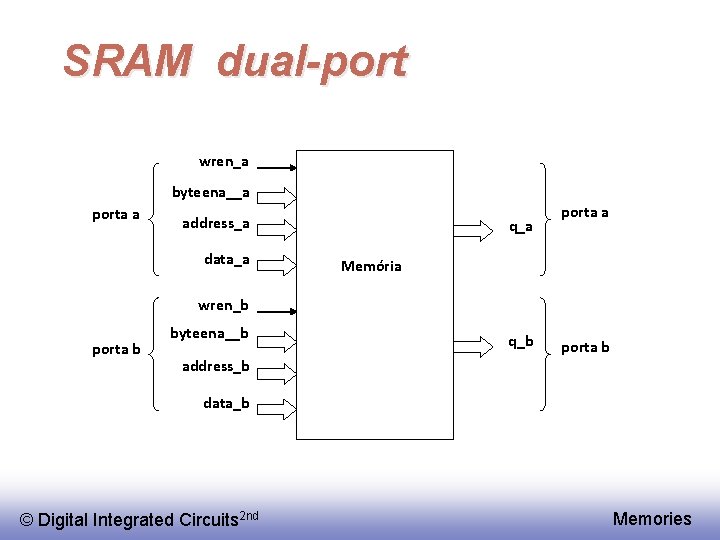

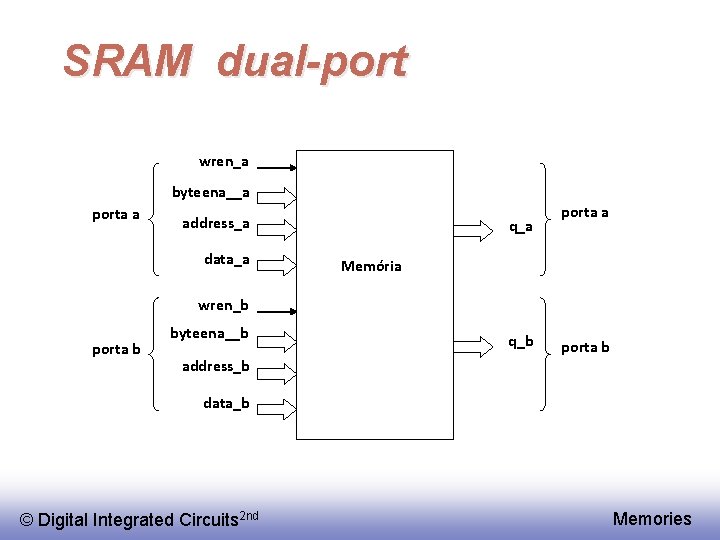

SRAM dual-port wren_a byteena__a porta a address_a data_a q_a porta a Memória wren_b porta b byteena__b address_b q_b porta b data_b © Digital Integrated Circuits 2 nd Memories

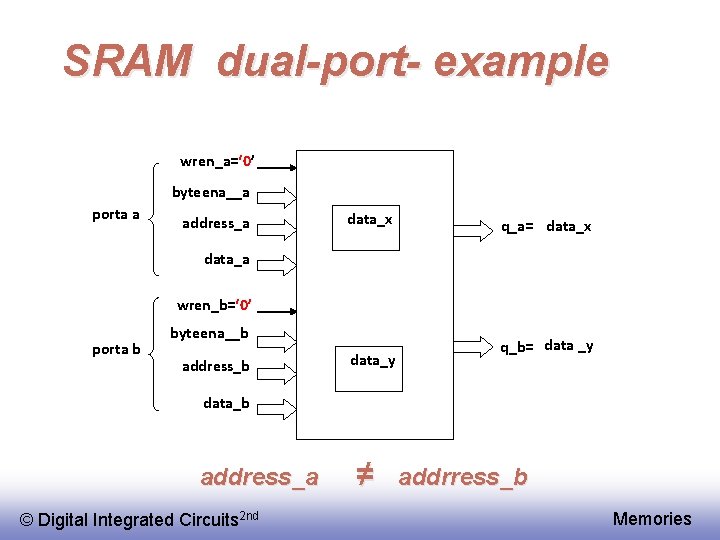

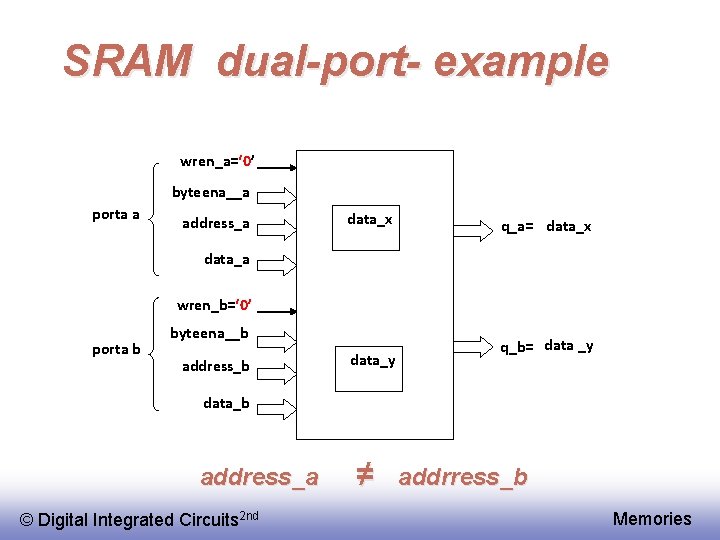

SRAM dual-port- example wren_a=‘ 0’ byteena__a porta a address_a data_x q_a= data_x data_a wren_b=‘ 0’ porta b byteena__b address_b data_y q_b= data _y data_b address_a © Digital Integrated Circuits 2 nd ≠ addrress_b Memories

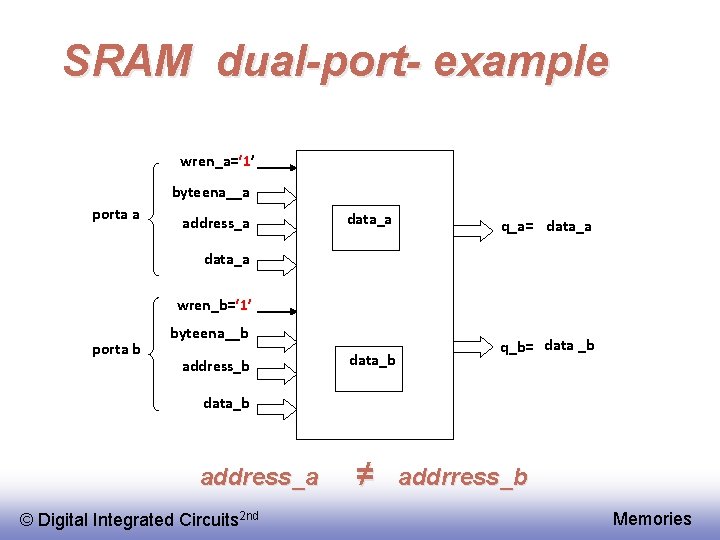

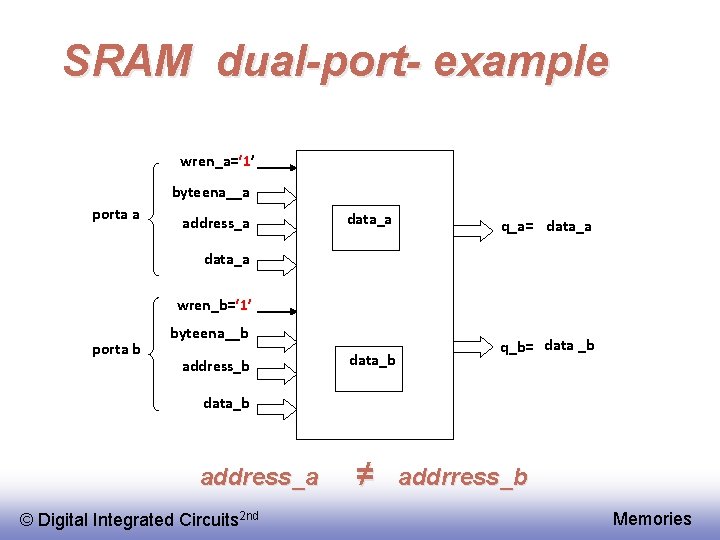

SRAM dual-port- example wren_a=‘ 1’ byteena__a porta a address_a data_a q_a= data_a wren_b=‘ 1’ porta b byteena__b address_b data_b q_b= data _b data_b address_a © Digital Integrated Circuits 2 nd ≠ addrress_b Memories

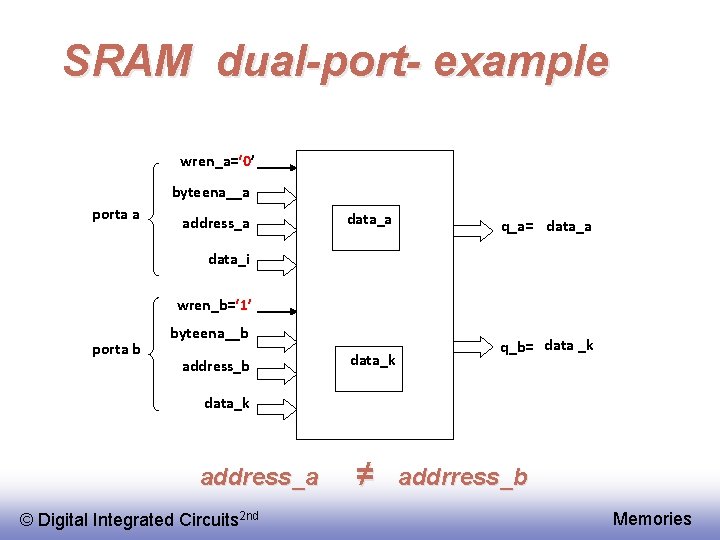

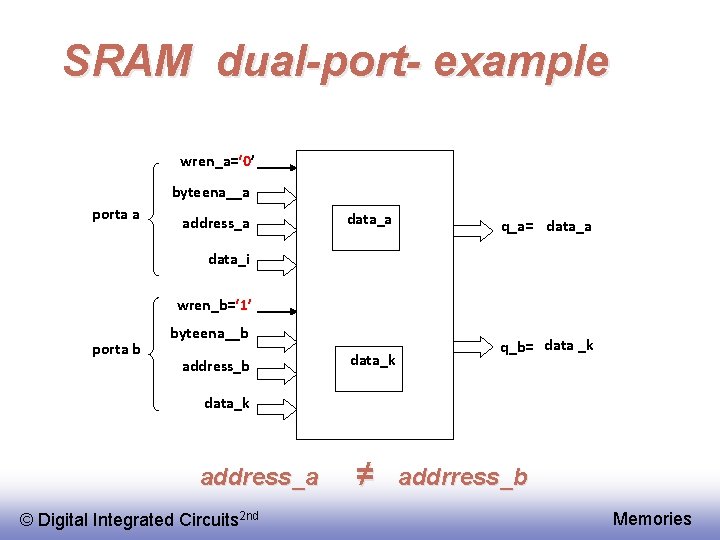

SRAM dual-port- example wren_a=‘ 0’ byteena__a porta a address_a data_a q_a= data_a data_i wren_b=‘ 1’ porta b byteena__b address_b data_k q_b= data _k data_k address_a © Digital Integrated Circuits 2 nd ≠ addrress_b Memories

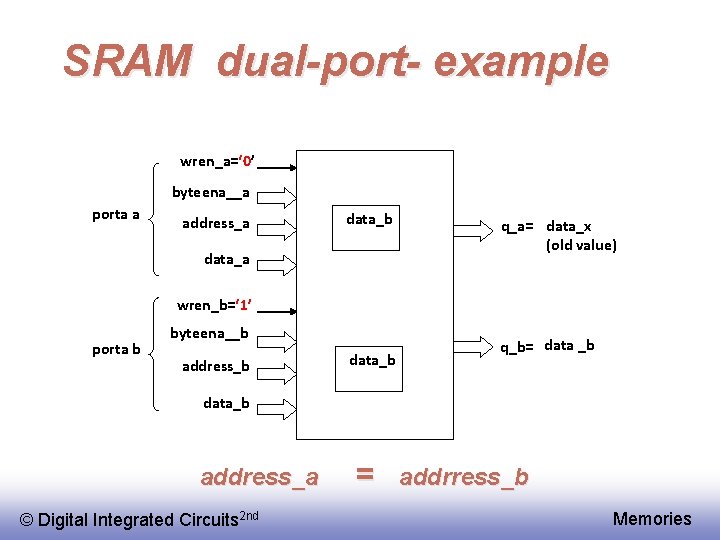

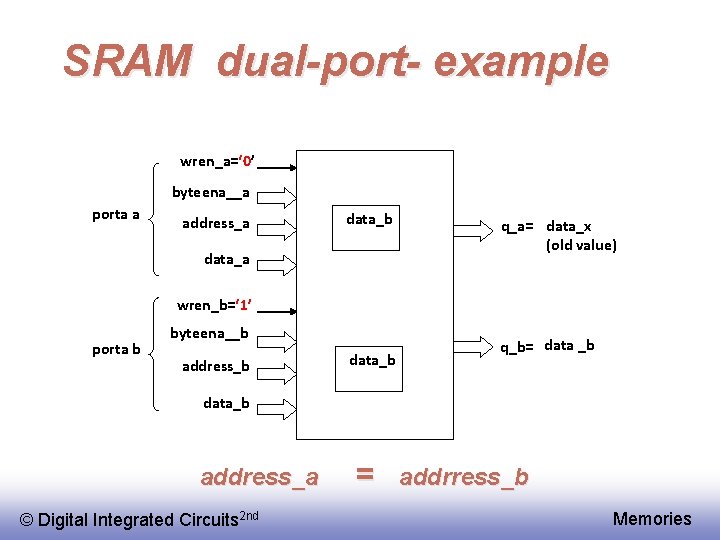

SRAM dual-port- example wren_a=‘ 0’ byteena__a porta a address_a data_b data_a q_a= data_x (old value) wren_b=‘ 1’ porta b byteena__b address_b data_b q_b= data _b data_b address_a © Digital Integrated Circuits 2 nd = addrress_b Memories

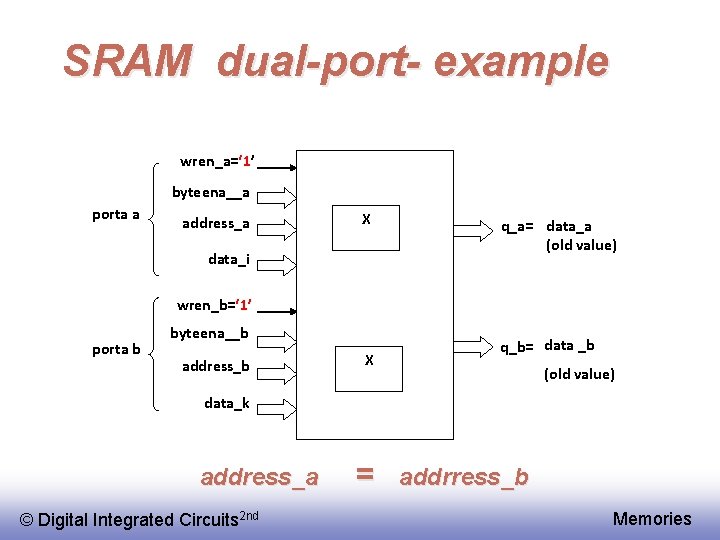

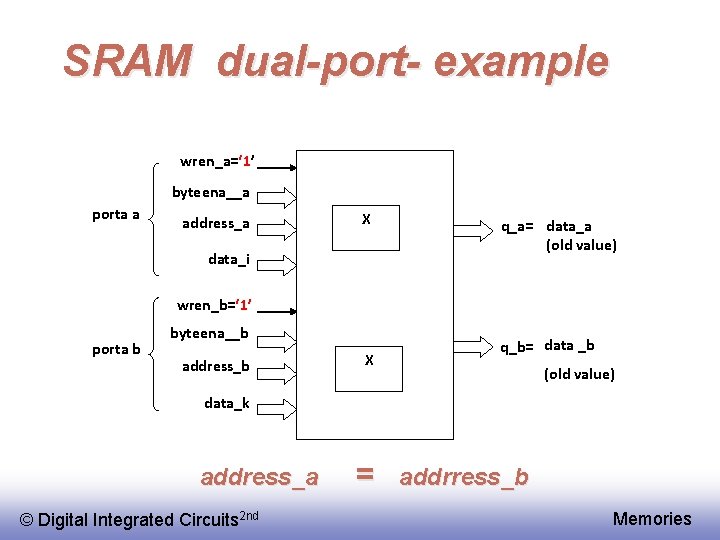

SRAM dual-port- example wren_a=‘ 1’ byteena__a porta a address_a X data_i q_a= data_a (old value) wren_b=‘ 1’ porta b byteena__b address_b X q_b= data _b (old value) data_k address_a © Digital Integrated Circuits 2 nd = addrress_b Memories

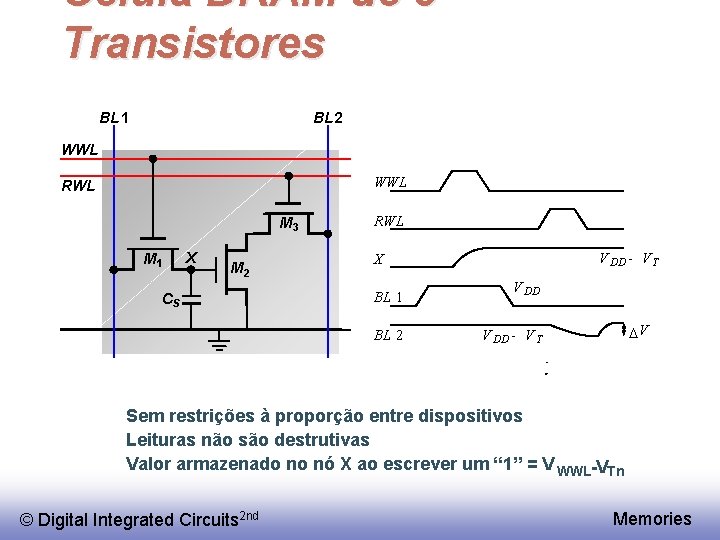

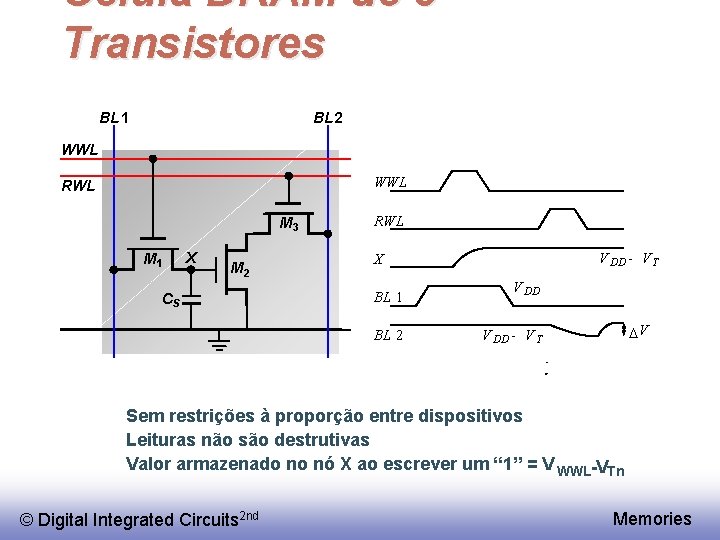

Célula DRAM de 3 Transistores BL 1 BL 2 WWL RWL M 3 M 1 X M 2 CS RWL V DD - V T X BL 1 BL 2 V DD DV V DD - V T Sem restrições à proporção entre dispositivos Leituras não são destrutivas Valor armazenado no nó X ao escrever um “ 1” = V WWL-VTn © Digital Integrated Circuits 2 nd Memories

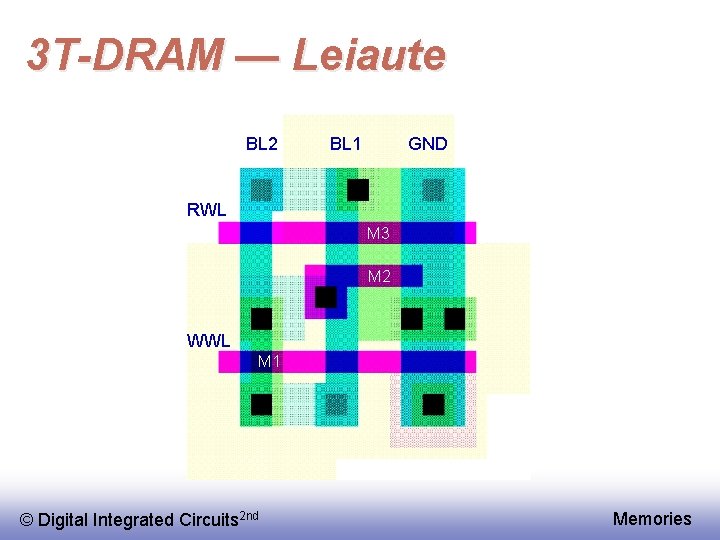

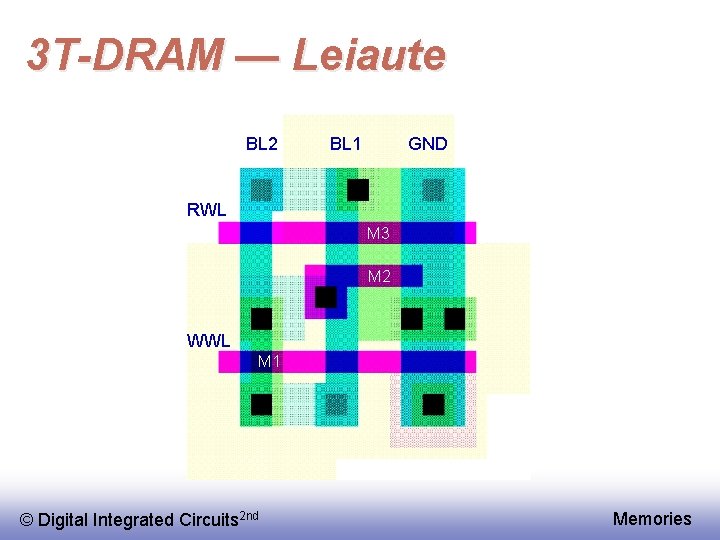

3 T-DRAM — Leiaute BL 2 BL 1 GND RWL M 3 M 2 WWL M 1 © Digital Integrated Circuits 2 nd Memories

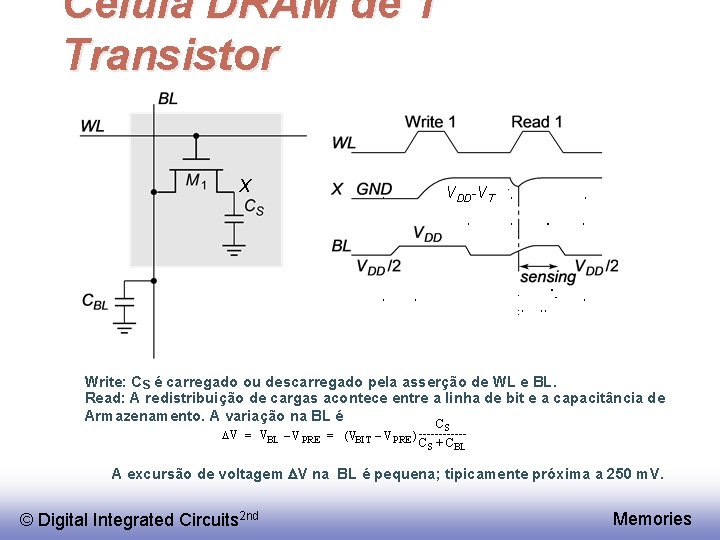

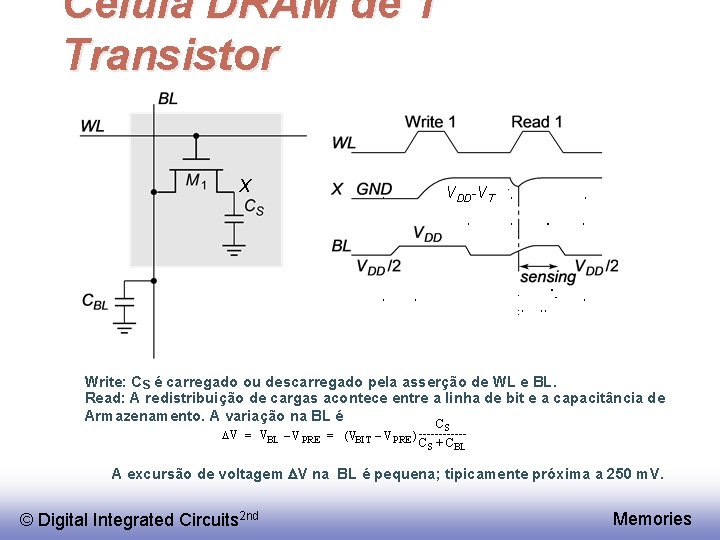

Célula DRAM de 1 Transistor X VDD-VT Write: C S é carregado ou descarregado pela asserção de WL e BL. Read: A redistribuição de cargas acontece entre a linha de bit e a capacitância de Armazenamento. A variação na BL é C S DV = VBL – V PRE = (VBIT – V PRE ) ------C S + CBL A excursão de voltagem DV na BL é pequena; tipicamente próxima a 250 m. V. © Digital Integrated Circuits 2 nd Memories

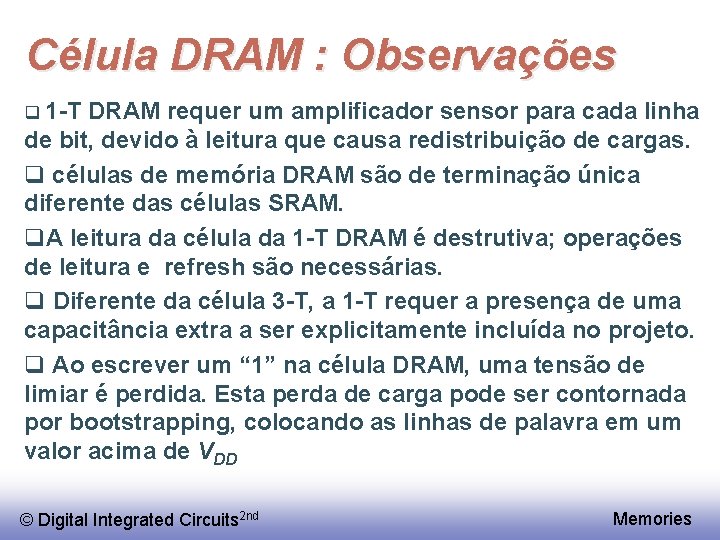

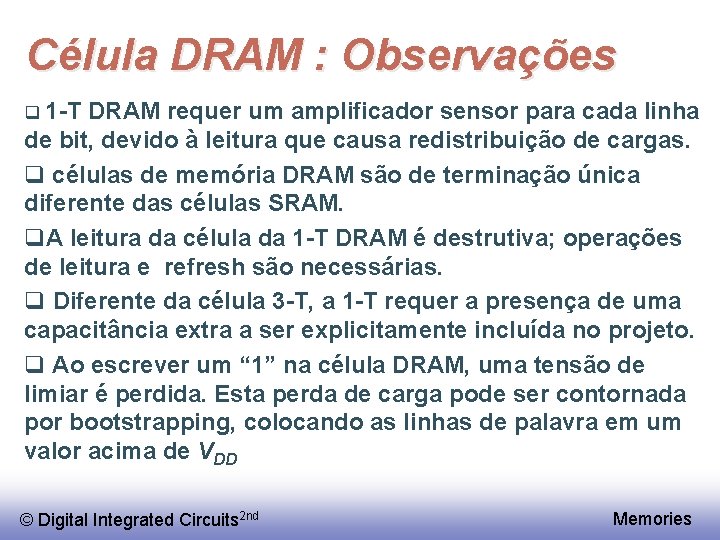

Célula DRAM : Observações q 1 -T DRAM requer um amplificador sensor para cada linha de bit, devido à leitura que causa redistribuição de cargas. q células de memória DRAM são de terminação única diferente das células SRAM. q. A leitura da célula da 1 -T DRAM é destrutiva; operações de leitura e refresh são necessárias. q Diferente da célula 3 -T, a 1 -T requer a presença de uma capacitância extra a ser explicitamente incluída no projeto. q Ao escrever um “ 1” na célula DRAM, uma tensão de limiar é perdida. Esta perda de carga pode ser contornada por bootstrapping, colocando as linhas de palavra em um valor acima de VDD © Digital Integrated Circuits 2 nd Memories

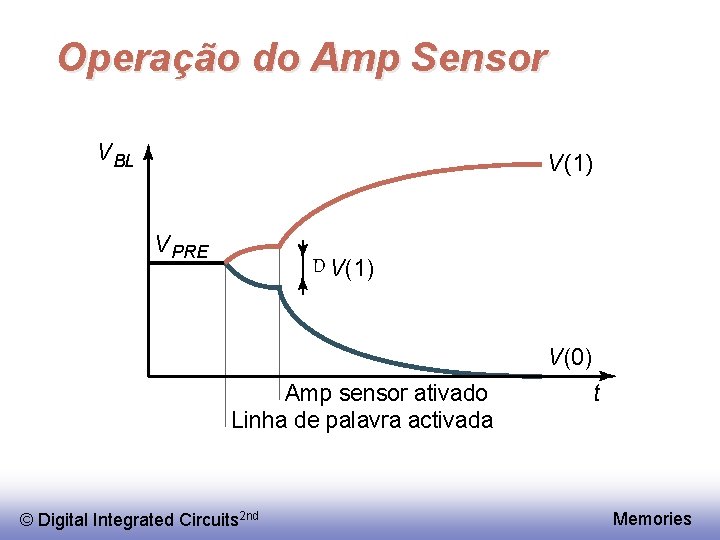

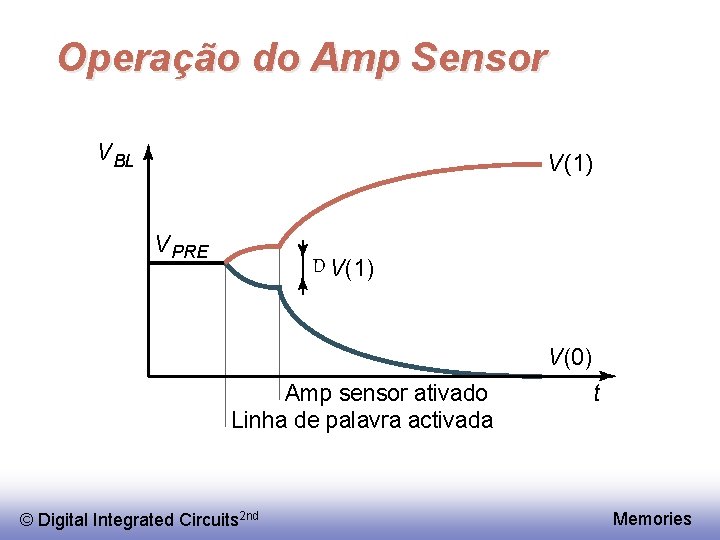

Operação do Amp Sensor V BL V(1) V PRE D V(1) V(0) Amp sensor ativado Linha de palavra activada © Digital Integrated Circuits 2 nd t Memories

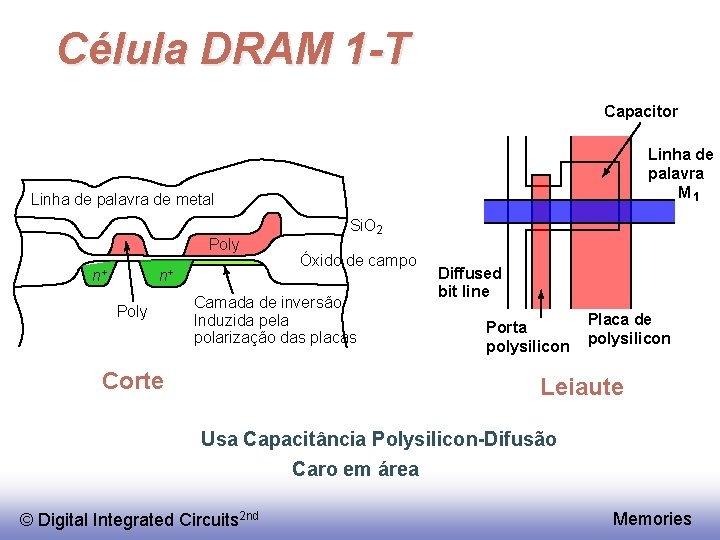

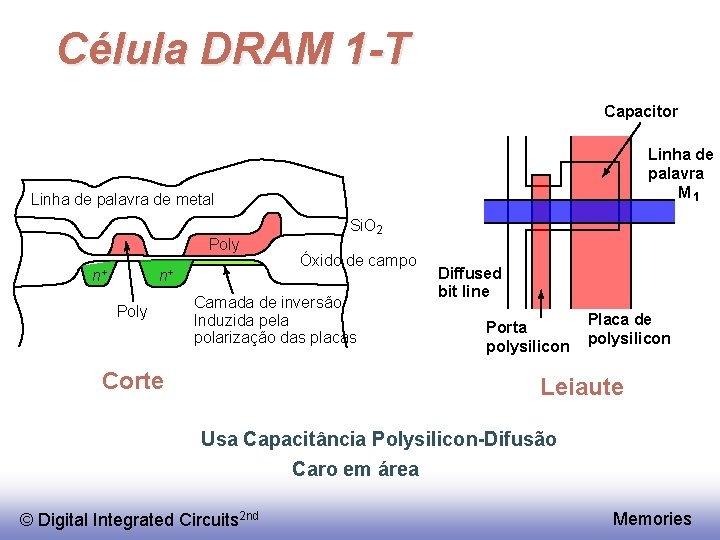

Célula DRAM 1 -T Capacitor Linha de palavra M 1 Linha de palavra de metal Poly n+ n+ Poly Si. O 2 Óxido de campo Camada de inversão Induzida pela polarização das placas Corte Diffused bit line Porta polysilicon Placa de polysilicon Leiaute Usa Capacitância Polysilicon-Difusão Caro em área © Digital Integrated Circuits 2 nd Memories

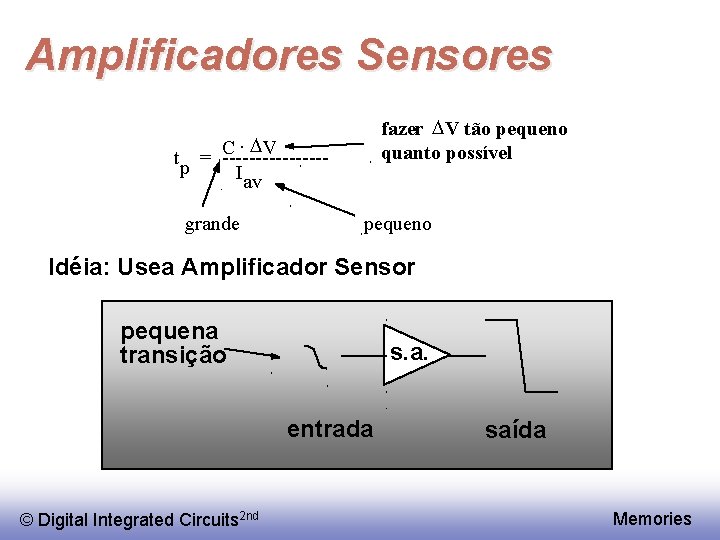

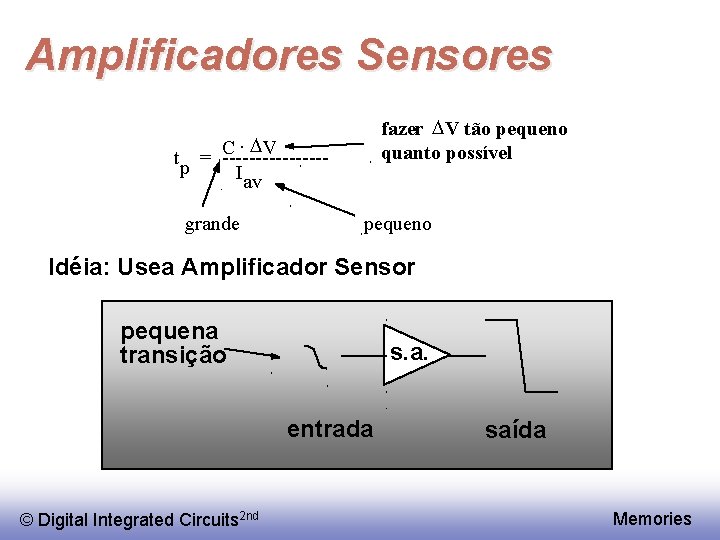

Amplificadores Sensores fazer D V tão pequeno quanto possível × DV C tp = --------Iav grande pequeno Idéia: Usea Amplificador Sensor pequena transição s. a. entrada © Digital Integrated Circuits 2 nd saída Memories

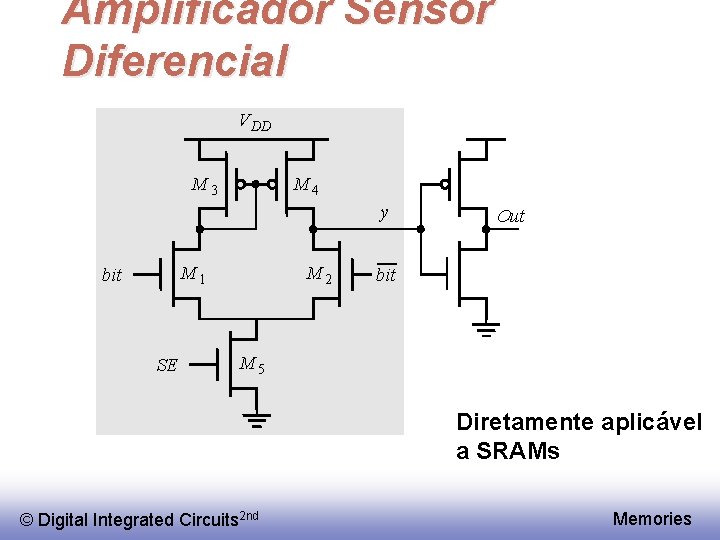

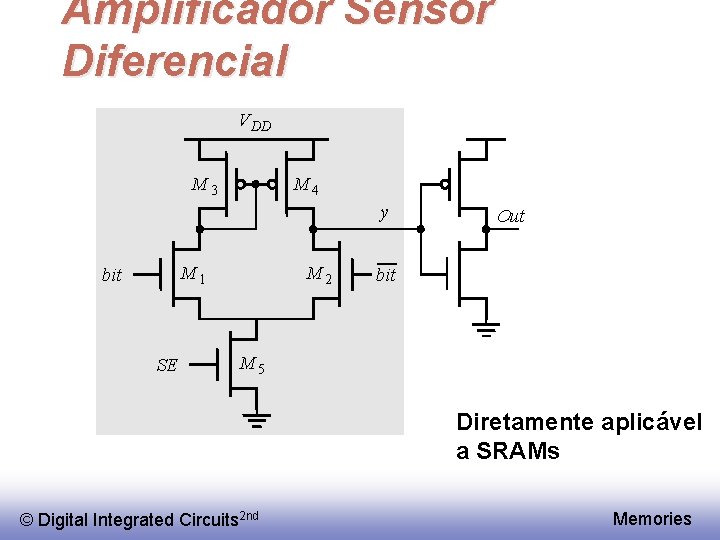

Amplificador Sensor Diferencial V DD M 3 M 4 y M 1 bit SE M 2 Out bit M 5 Diretamente aplicável a SRAMs © Digital Integrated Circuits 2 nd Memories

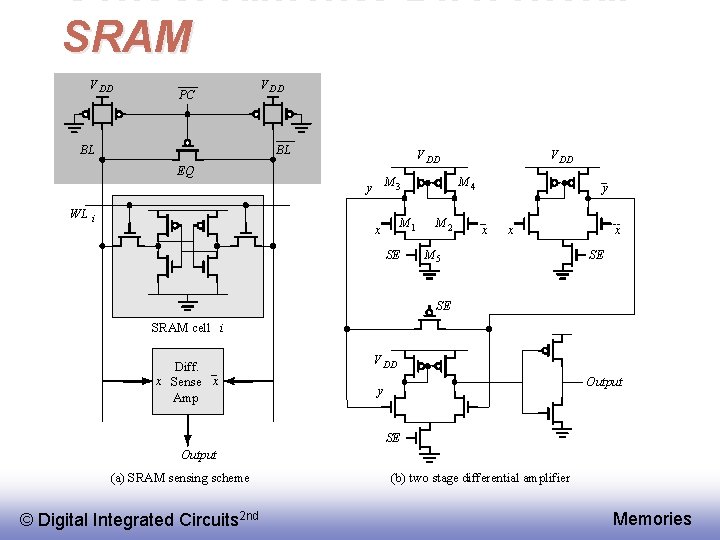

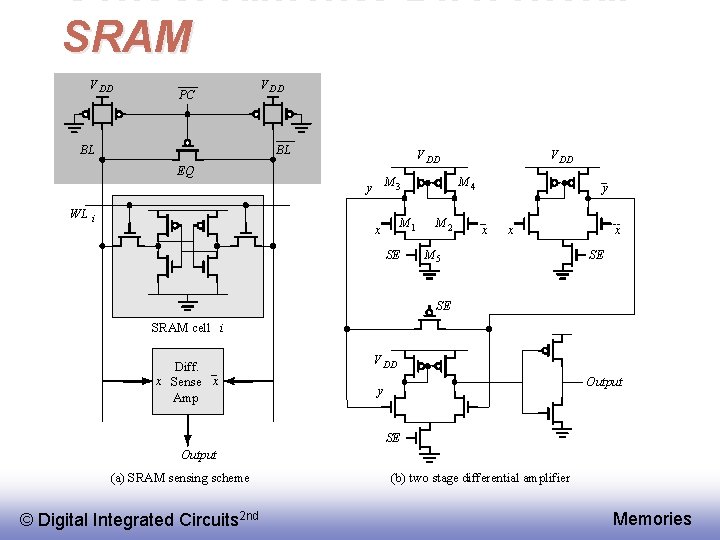

Sensoreamento Diferencial ― SRAM V DD PC BL BL EQ WL V DD i V DD y M 3 M 1 x SE V DD M 4 M 2 -y -x -x x M 5 SE SE SRAM cell i Diff. -x Sense x Amp V DD Output y SE Output (a) SRAM sensing scheme © Digital Integrated Circuits 2 nd (b) two stage differential amplifier Memories

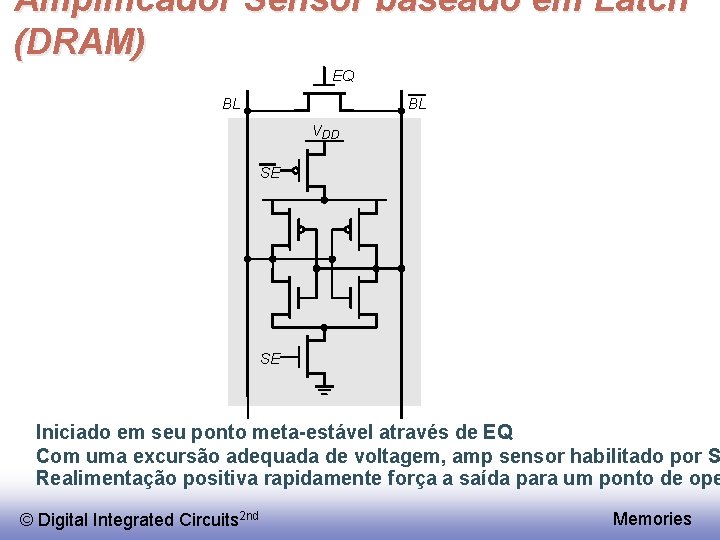

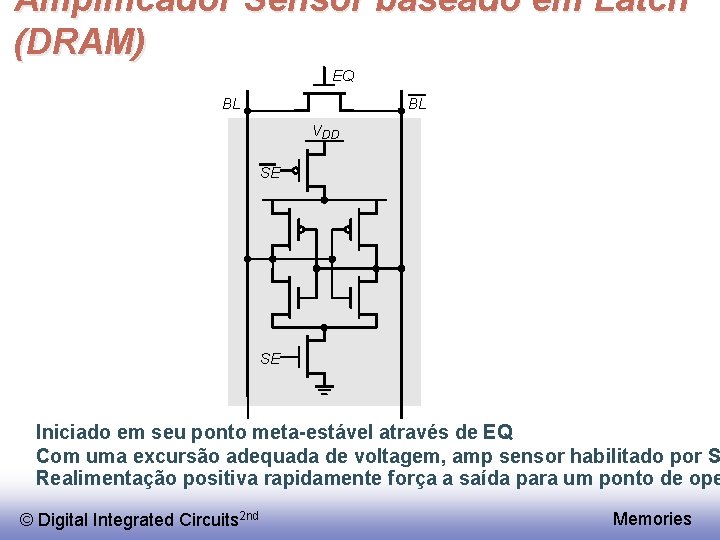

Amplificador Sensor baseado em Latch (DRAM) EQ BL BL VDD SE SE Iniciado em seu ponto meta-estável através de EQ Com uma excursão adequada de voltagem, amp sensor habilitado por S Realimentação positiva rapidamente força a saída para um ponto de ope © Digital Integrated Circuits 2 nd Memories

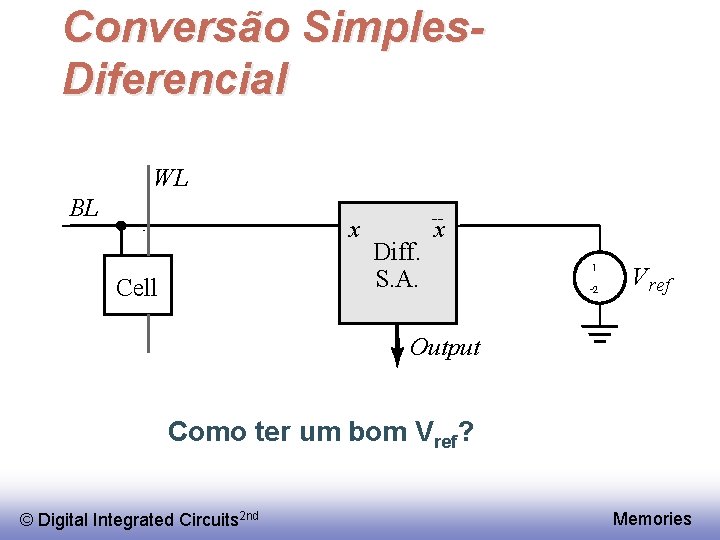

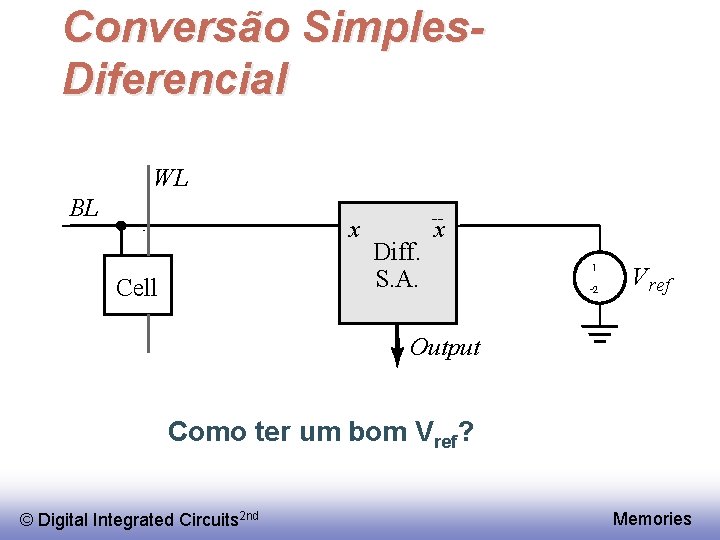

Conversão Simples. Diferencial WL BL x Cell Diff. S. A. -x 1 2 V ref Output Como ter um bom Vref? © Digital Integrated Circuits 2 nd Memories

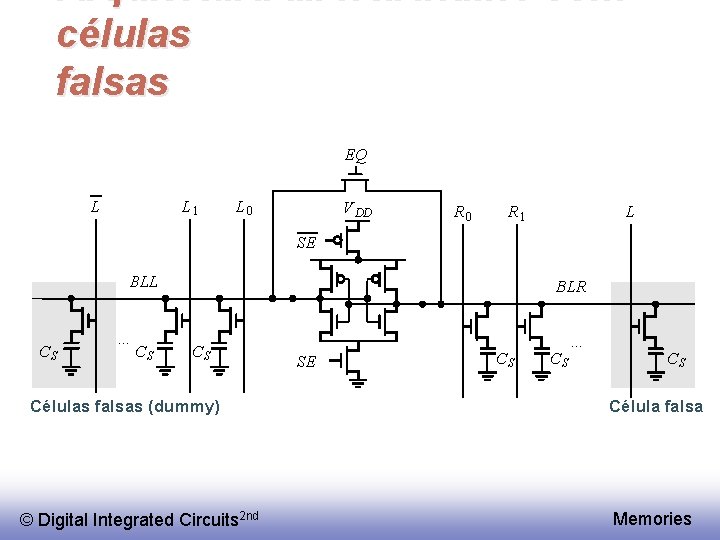

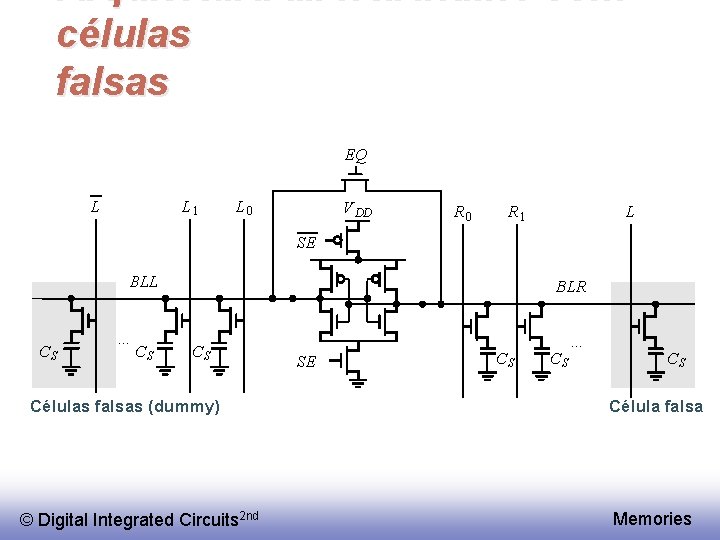

Arquitetura aberta bitline com células falsas EQ L L 1 L 0 V DD R 0 R 1 L SE BLL CS … CS BLR CS Células falsas (dummy) © Digital Integrated Circuits 2 nd SE CS CS … CS Célula falsa Memories

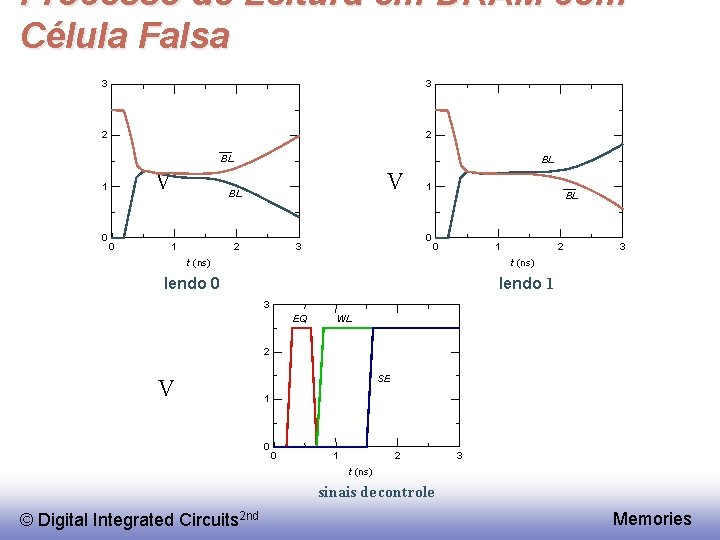

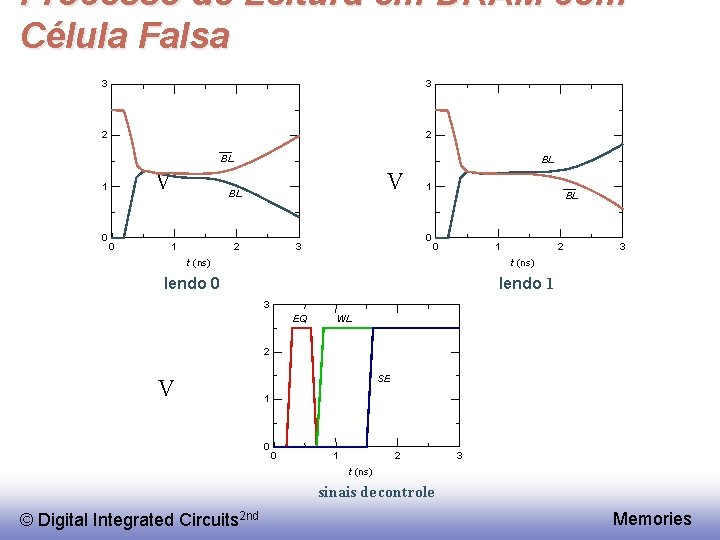

Processo de Leitura em DRAM com Célula Falsa 3 3 2 2 BL V 1 0 0 BL V BL 1 2 1 0 3 BL 0 1 t (ns) 2 3 t (ns) lendo 1 lendo 0 3 EQ WL 2 V SE 1 0 0 1 2 3 t (ns) sinais de controle © Digital Integrated Circuits 2 nd Memories

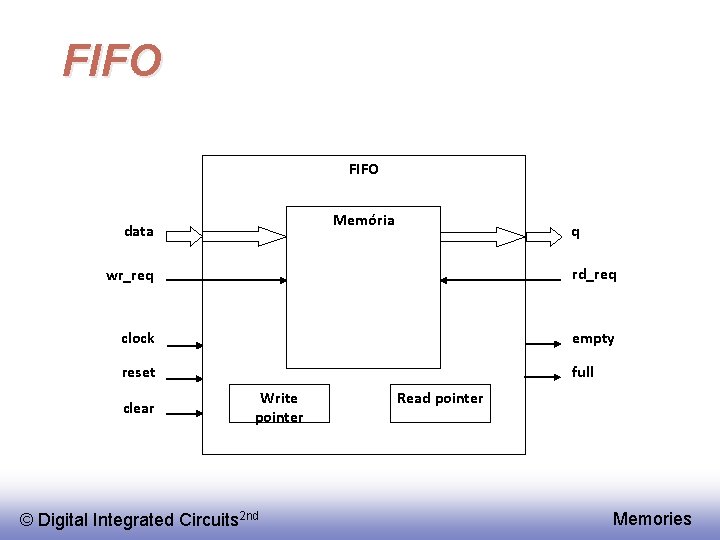

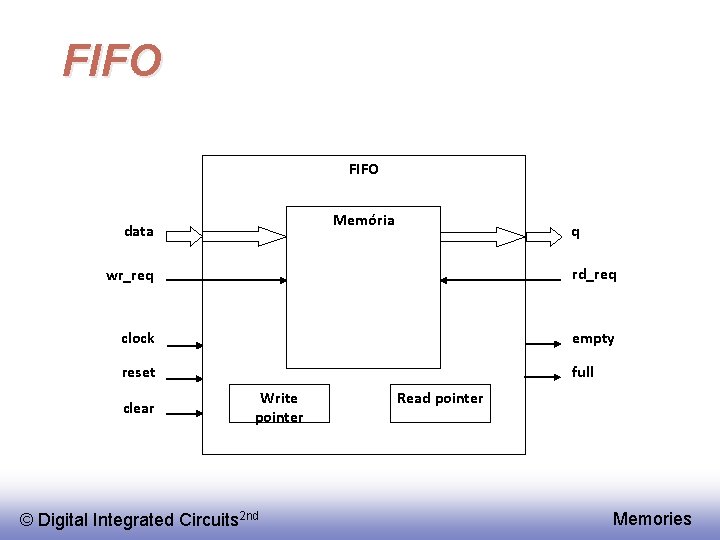

FIFO Memória data q wr_req rd_req clock empty reset full clear Write pointer © Digital Integrated Circuits 2 nd Read pointer Memories

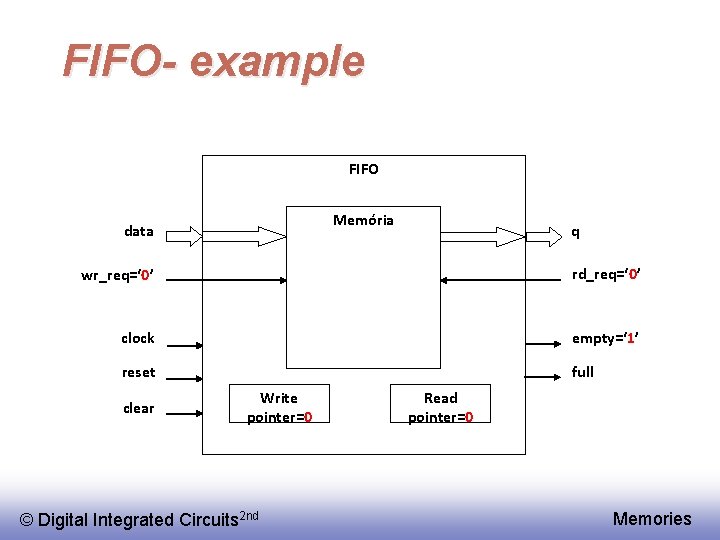

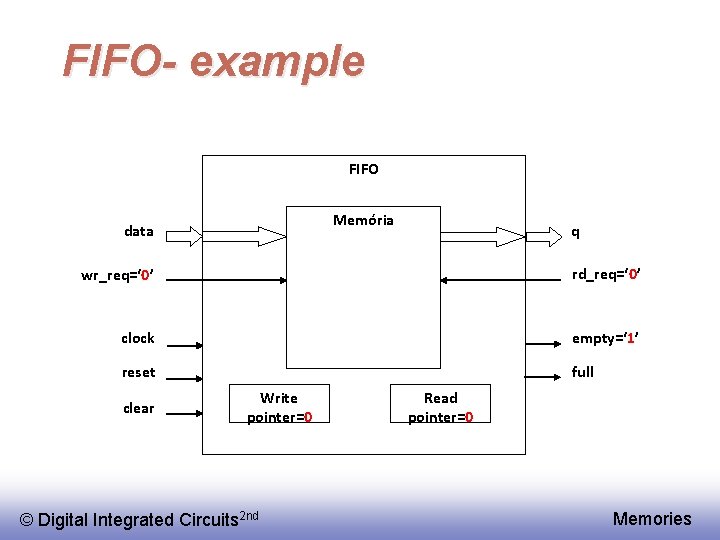

FIFO- example FIFO Memória data q wr_req=‘ 0’ rd_req=‘ 0’ clock empty=‘ 1’ reset full clear Write pointer=0 © Digital Integrated Circuits 2 nd Read pointer=0 Memories

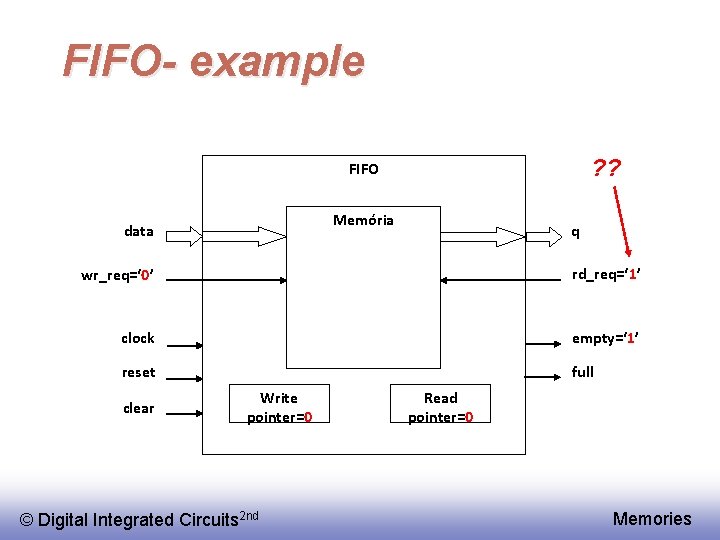

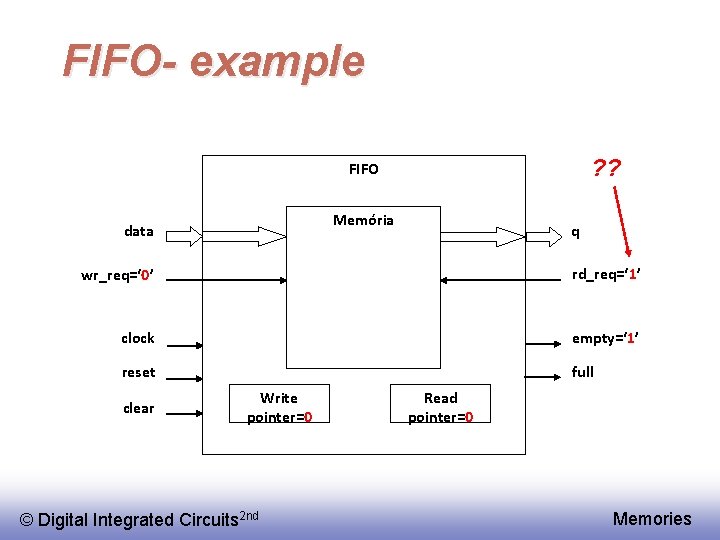

FIFO- example ? ? FIFO Memória data q wr_req=‘ 0’ rd_req=‘ 1’ clock empty=‘ 1’ reset full clear Write pointer=0 © Digital Integrated Circuits 2 nd Read pointer=0 Memories

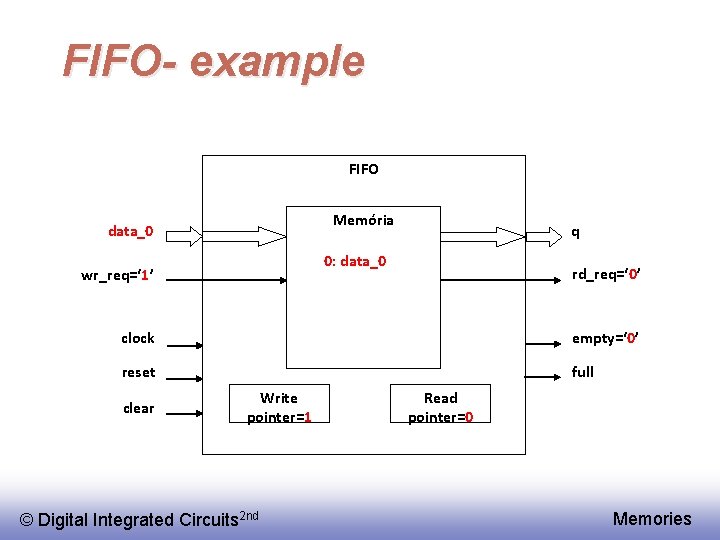

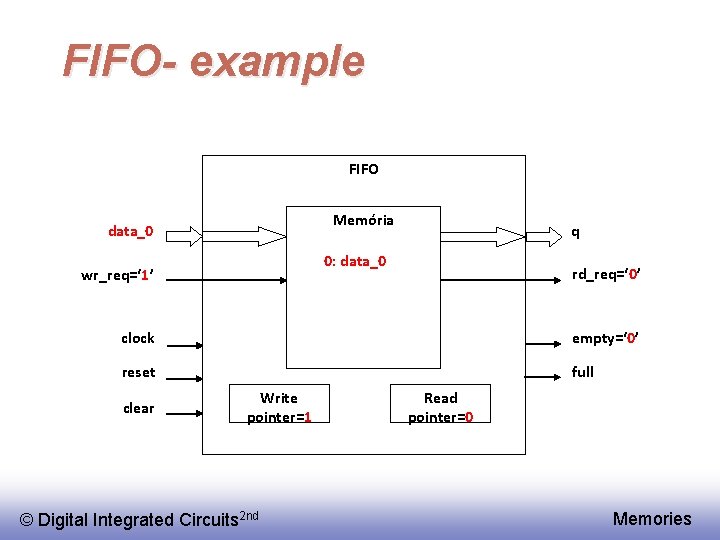

FIFO- example FIFO Memória data_0 q 0: data_0 wr_req=‘ 1’ rd_req=‘ 0’ clock empty=‘ 0’ reset full clear Write pointer=1 © Digital Integrated Circuits 2 nd Read pointer=0 Memories

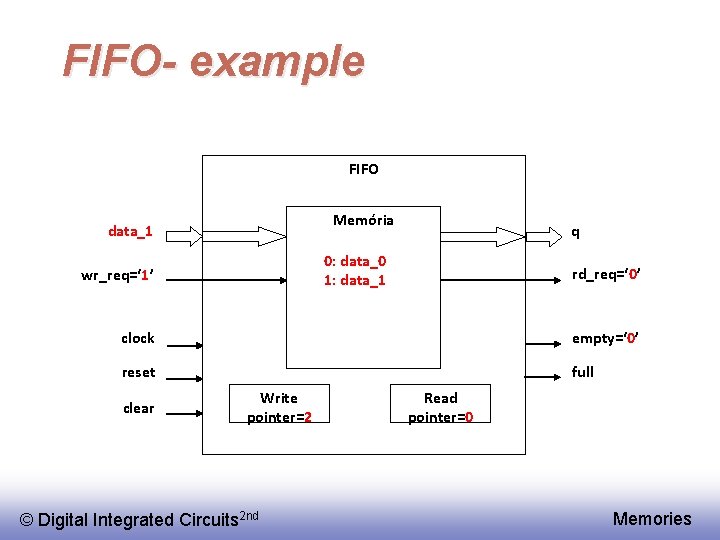

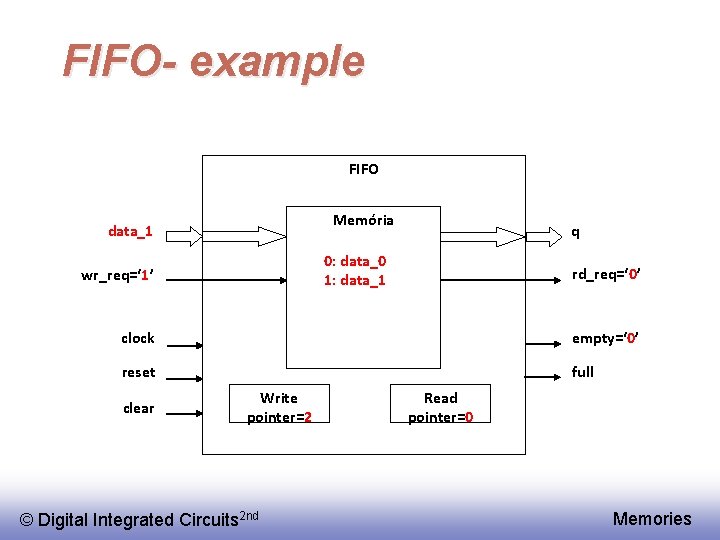

FIFO- example FIFO Memória data_1 q 0: data_0 1: data_1 wr_req=‘ 1’ rd_req=‘ 0’ clock empty=‘ 0’ reset full clear Write pointer=2 © Digital Integrated Circuits 2 nd Read pointer=0 Memories

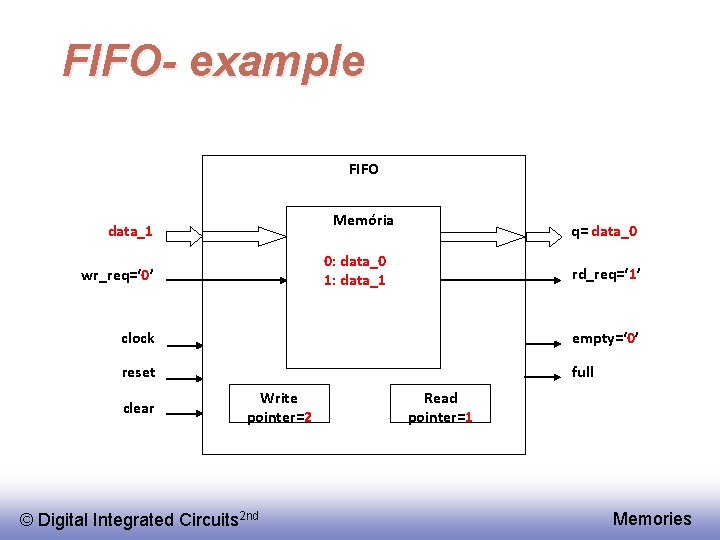

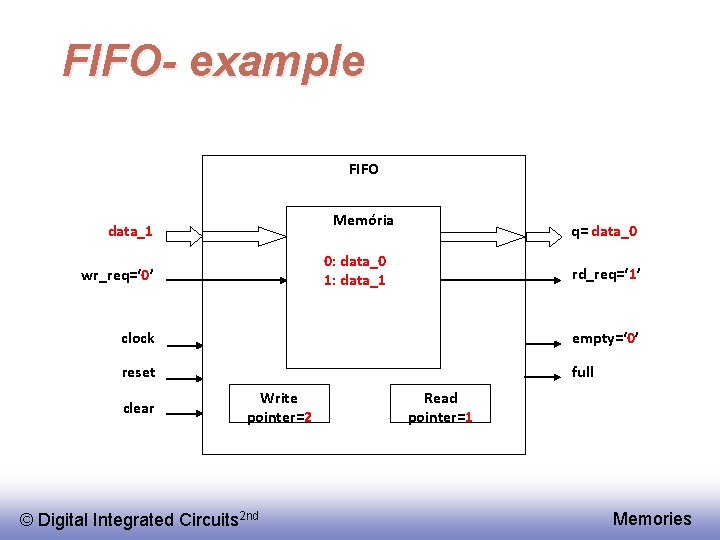

FIFO- example FIFO Memória data_1 q= data_0 0: data_0 1: data_1 wr_req=‘ 0’ rd_req=‘ 1’ clock empty=‘ 0’ reset full clear Write pointer=2 © Digital Integrated Circuits 2 nd Read pointer=1 Memories

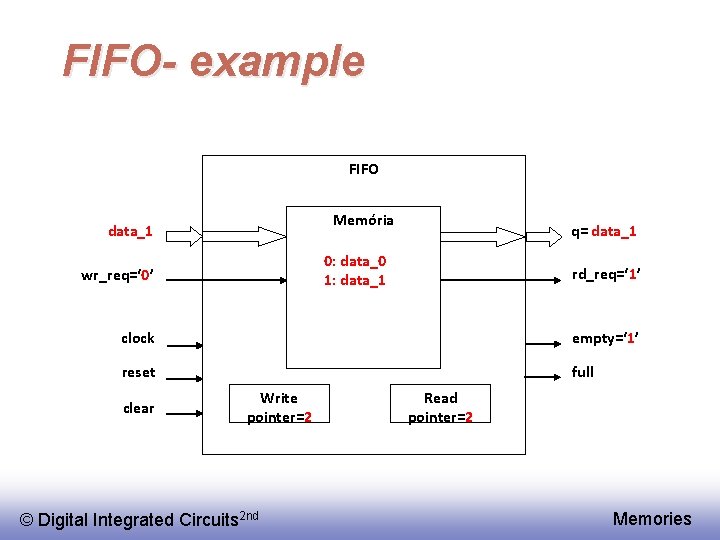

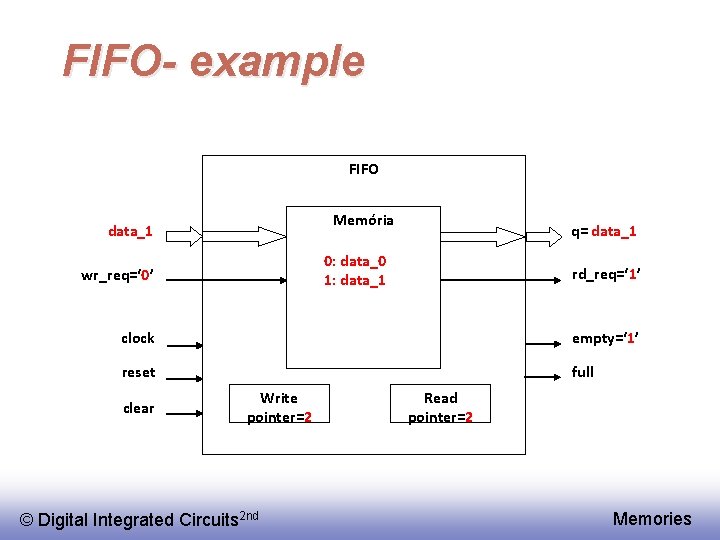

FIFO- example FIFO Memória data_1 q= data_1 0: data_0 1: data_1 wr_req=‘ 0’ rd_req=‘ 1’ clock empty=‘ 1’ reset full clear Write pointer=2 © Digital Integrated Circuits 2 nd Read pointer=2 Memories