Digital Integrated Circuits A Design Perspective Jan M

- Slides: 25

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolić Designing Combinational Logic Circuits November 2002. © EE 141 Digital Integrated Circuits 2 nd 1 Combinational Circu

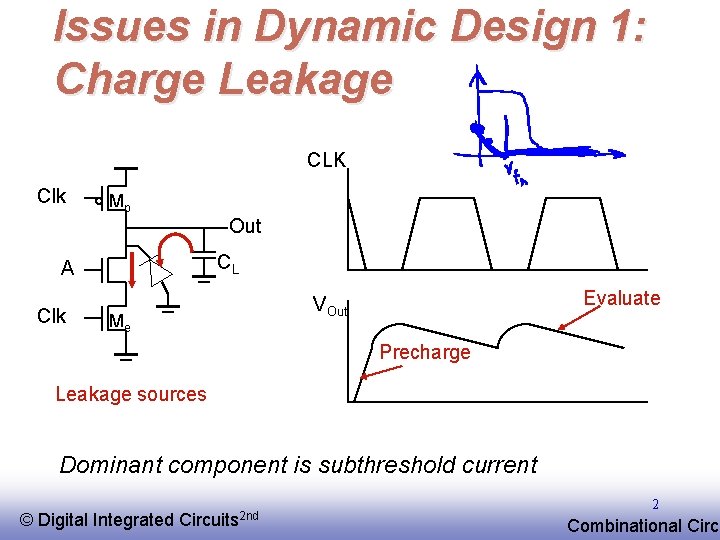

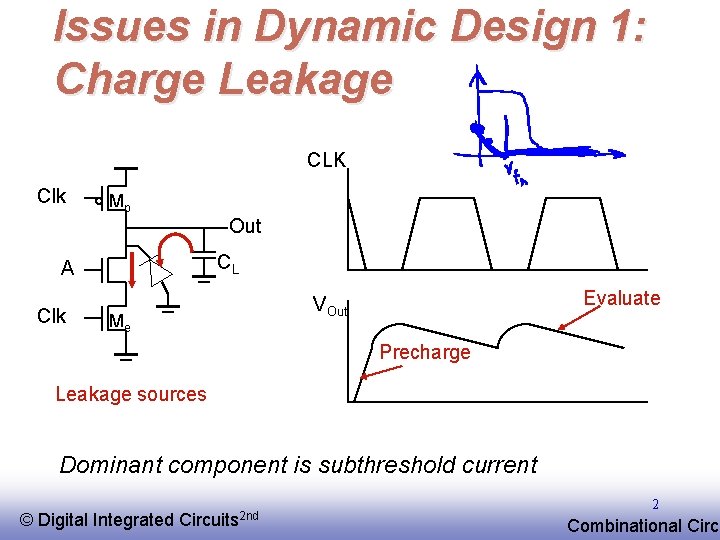

Issues in Dynamic Design 1: Charge Leakage CLK Clk Mp Out CL A Clk Evaluate VOut Me Precharge Leakage sources Dominant component is subthreshold current © EE 141 Digital Integrated Circuits 2 nd 2 Combinational Circu

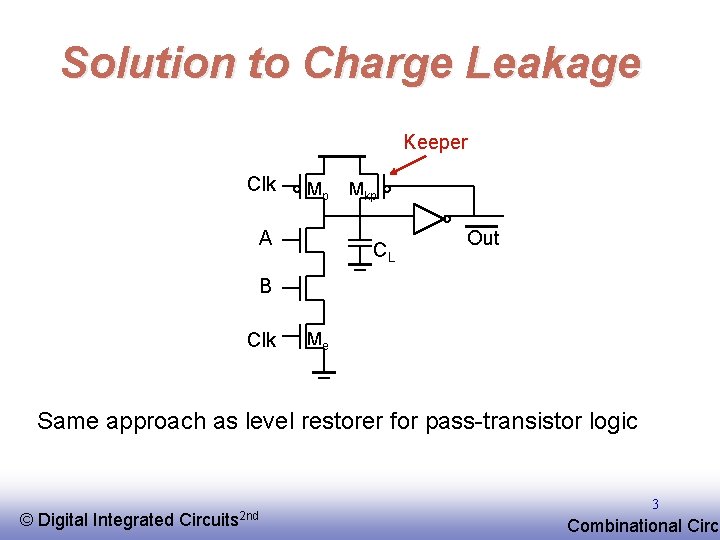

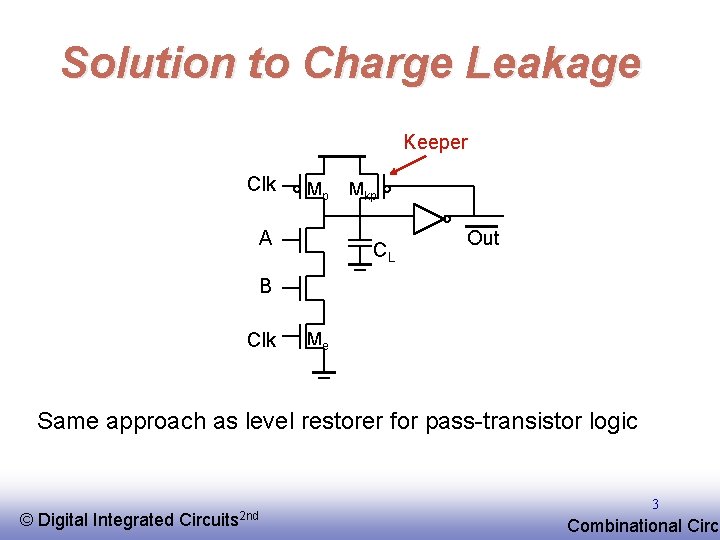

Solution to Charge Leakage Keeper Clk Mp A Mkp CL Out B Clk Me Same approach as level restorer for pass-transistor logic © EE 141 Digital Integrated Circuits 2 nd 3 Combinational Circu

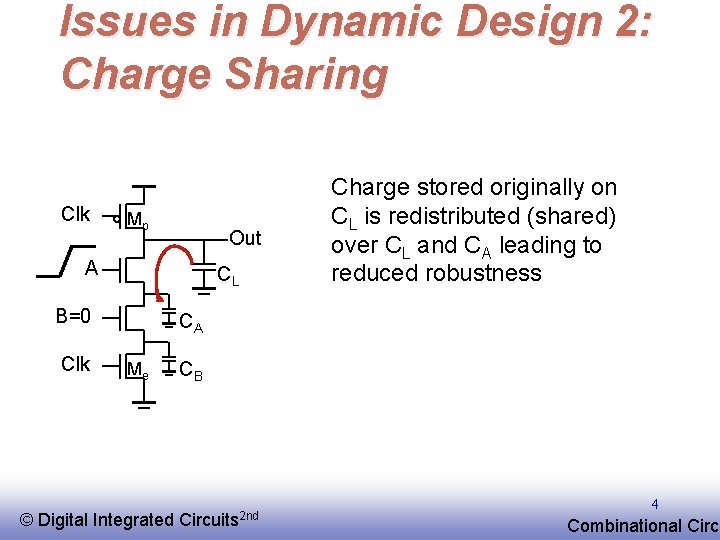

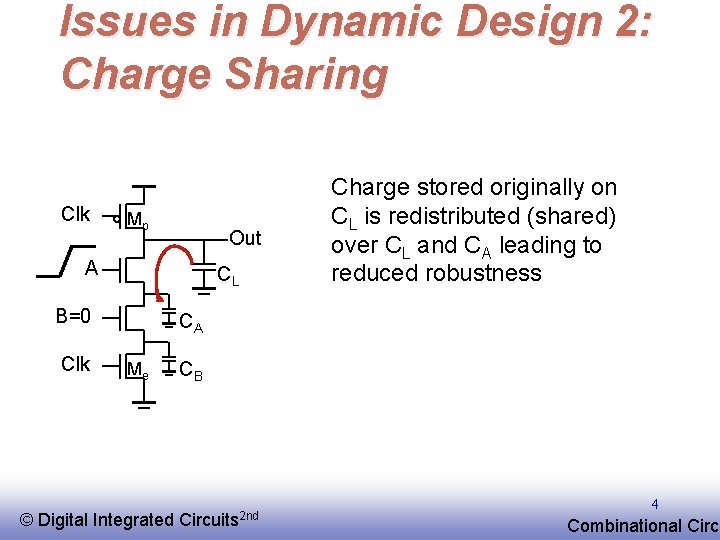

Issues in Dynamic Design 2: Charge Sharing Clk Mp Out A CL B=0 Clk Charge stored originally on CL is redistributed (shared) over CL and CA leading to reduced robustness CA Me © EE 141 Digital Integrated CB Circuits 2 nd 4 Combinational Circu

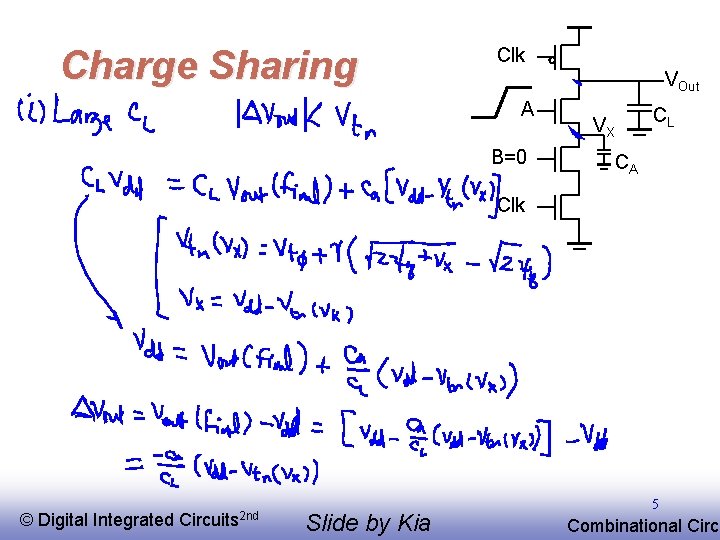

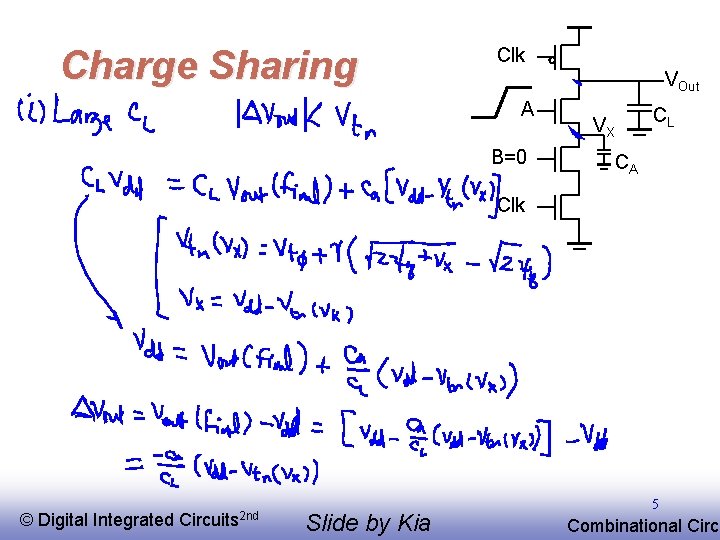

Charge Sharing Clk VOut A B=0 VX CL CA Clk © EE 141 Digital Integrated Circuits 2 nd Slide by Kia 5 Combinational Circu

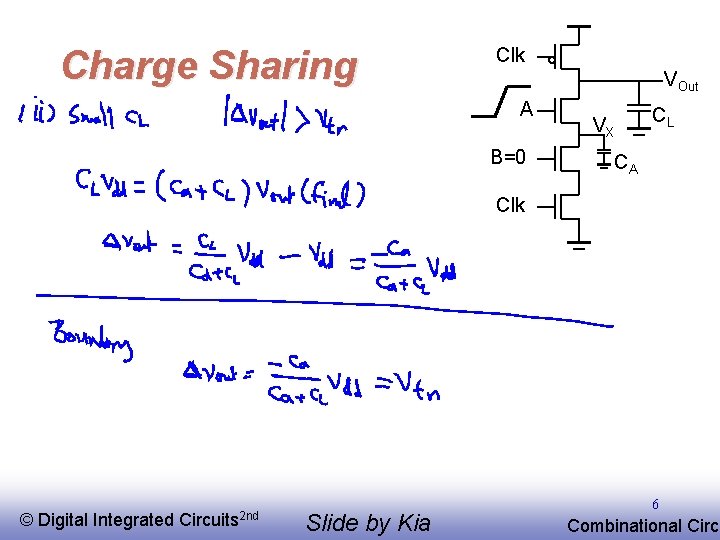

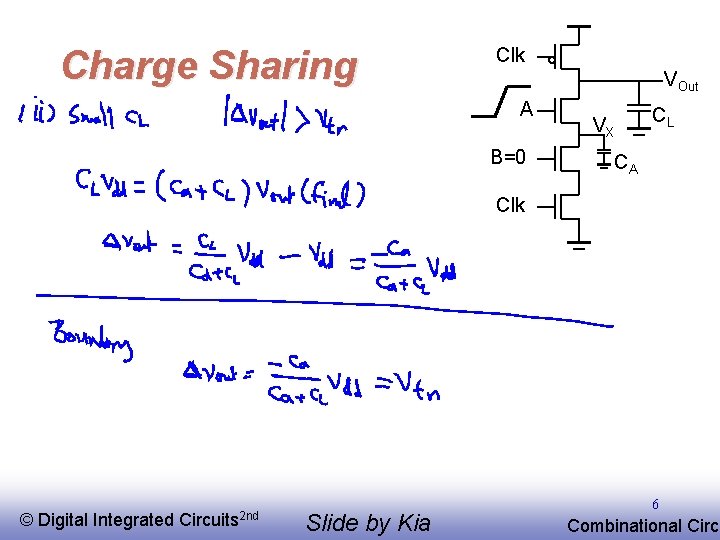

Charge Sharing Clk VOut A B=0 VX CL CA Clk © EE 141 Digital Integrated Circuits 2 nd Slide by Kia 6 Combinational Circu

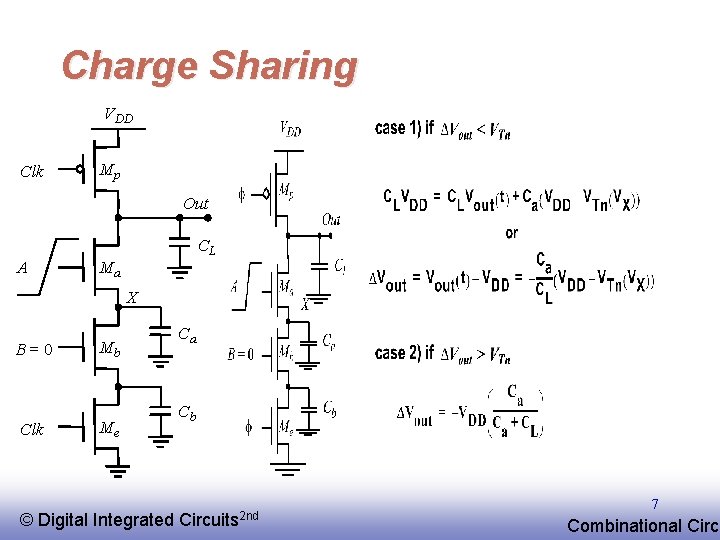

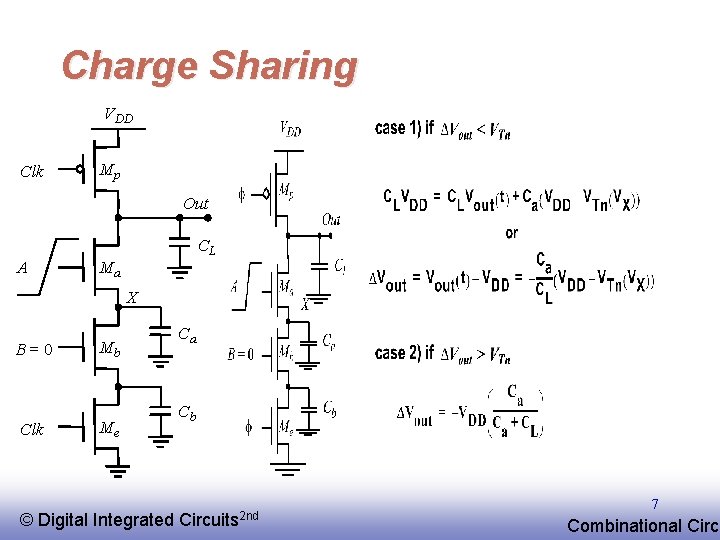

Charge Sharing VDD Clk Mp Out CL A Ma X B=0 Clk Mb Me © EE 141 Digital Integrated Ca Cb Circuits 2 nd 7 Combinational Circu

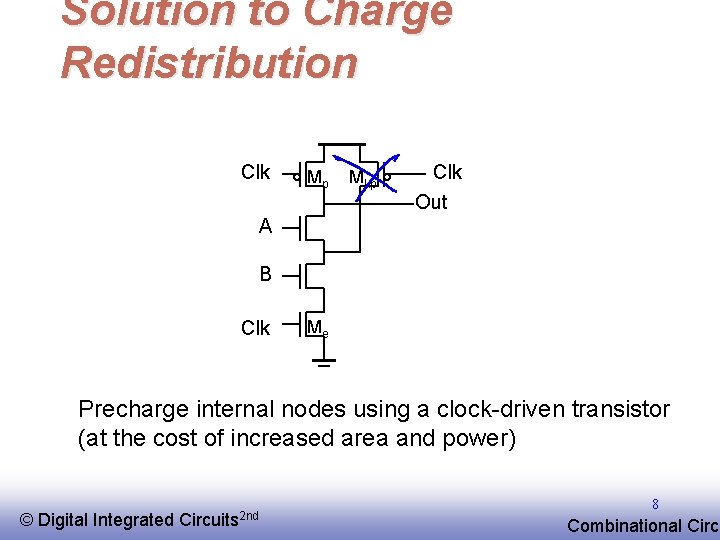

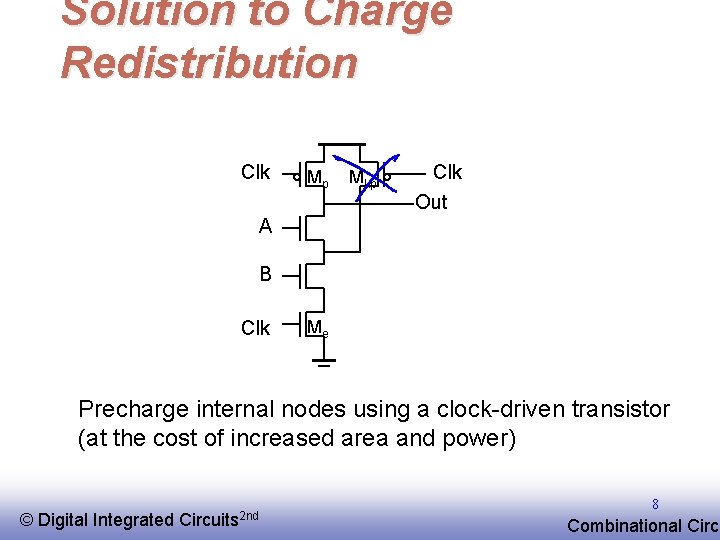

Solution to Charge Redistribution Clk Mp Mkp Clk Out A B Clk Me Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power) © EE 141 Digital Integrated Circuits 2 nd 8 Combinational Circu

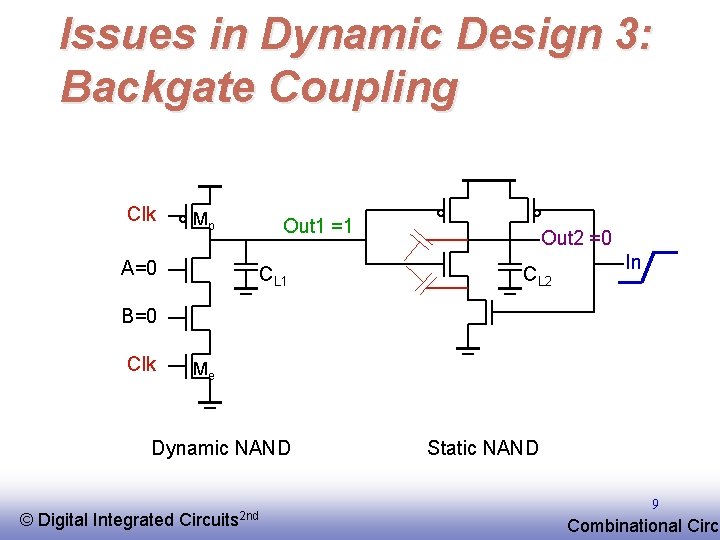

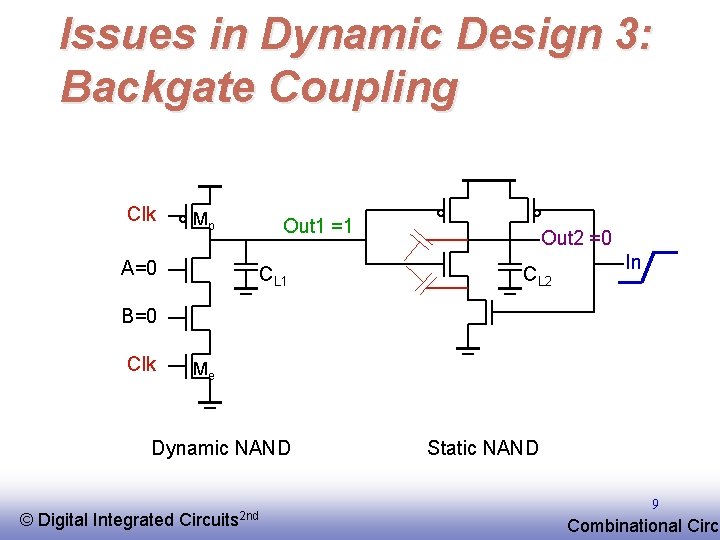

Issues in Dynamic Design 3: Backgate Coupling Clk Mp A=0 Out 1 =1 CL 1 Out 2 =0 CL 2 In B=0 Clk Me Dynamic NAND © EE 141 Digital Integrated Circuits 2 nd Static NAND 9 Combinational Circu

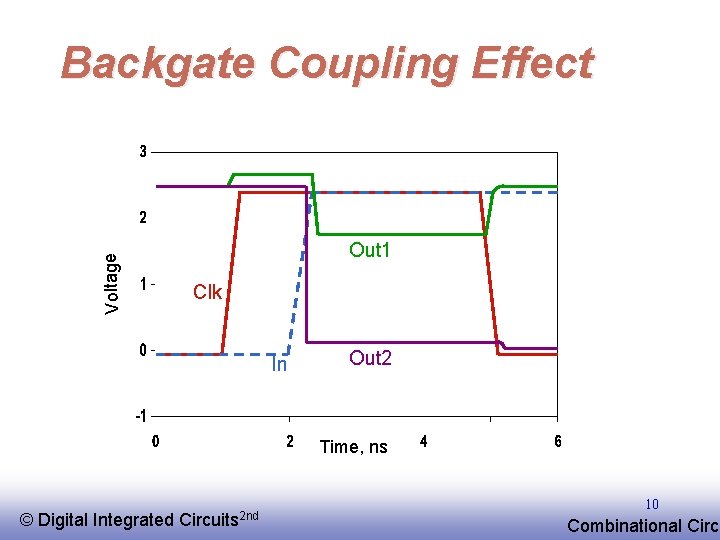

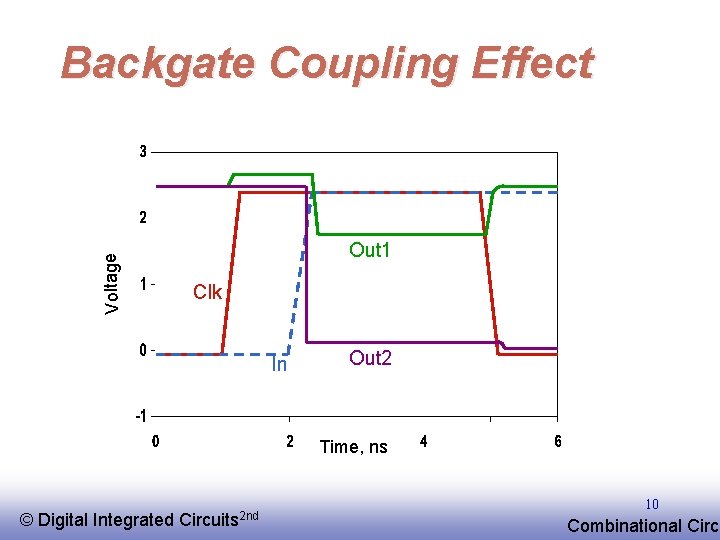

Voltage Backgate Coupling Effect Out 1 Clk In Out 2 Time, ns © EE 141 Digital Integrated Circuits 2 nd 10 Combinational Circu

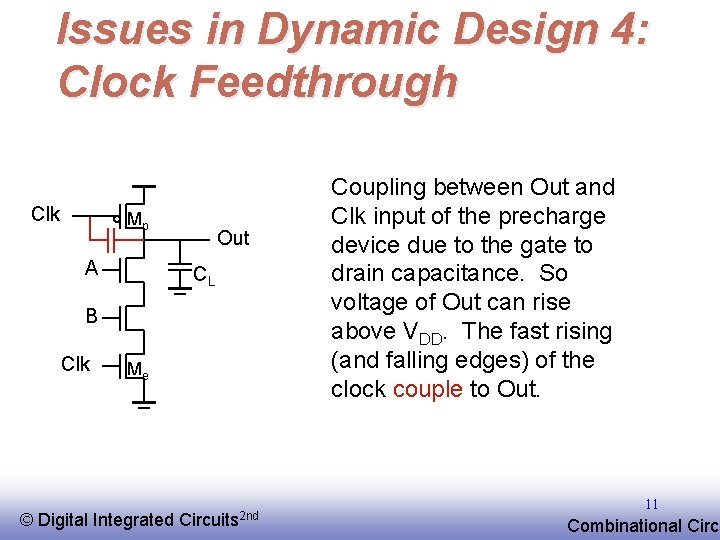

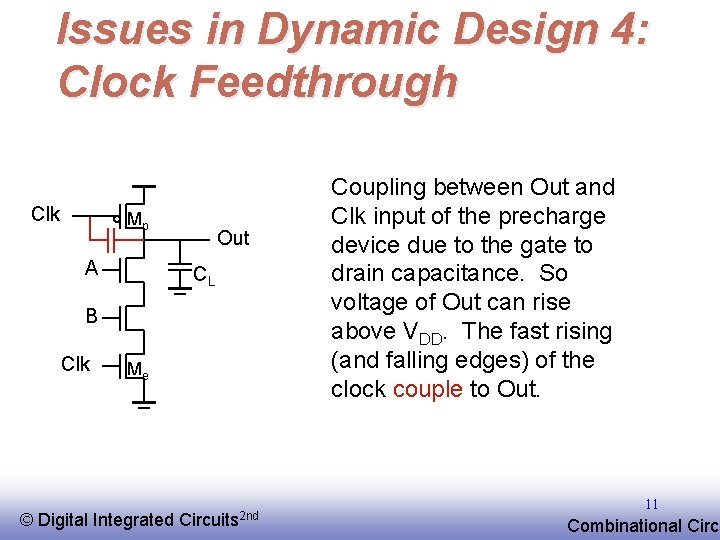

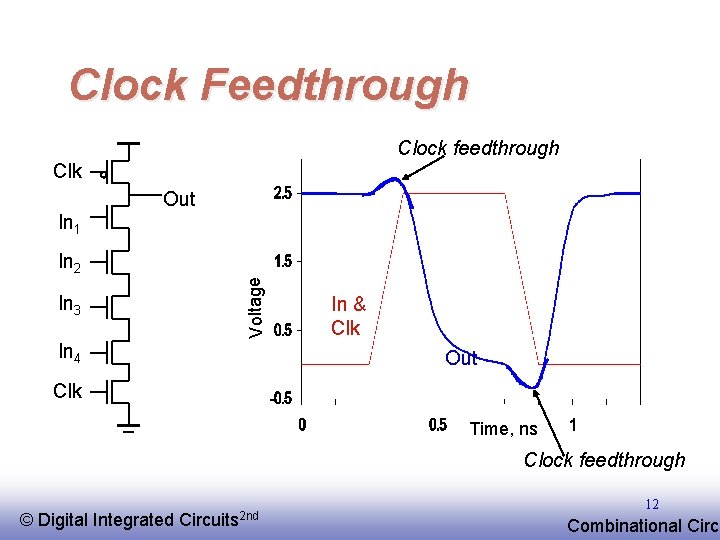

Issues in Dynamic Design 4: Clock Feedthrough Clk Mp A Out CL B Clk Me © EE 141 Digital Integrated Circuits 2 nd Coupling between Out and Clk input of the precharge device due to the gate to drain capacitance. So voltage of Out can rise above VDD. The fast rising (and falling edges) of the clock couple to Out. 11 Combinational Circu

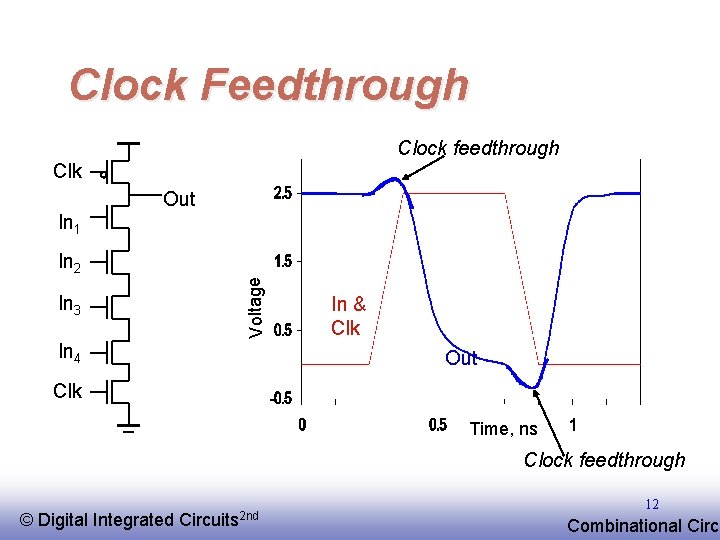

Clock Feedthrough Clock feedthrough Clk Out In 1 In 3 Voltage In 2 In 4 In & Clk Out Clk Time, ns Clock feedthrough © EE 141 Digital Integrated Circuits 2 nd 12 Combinational Circu

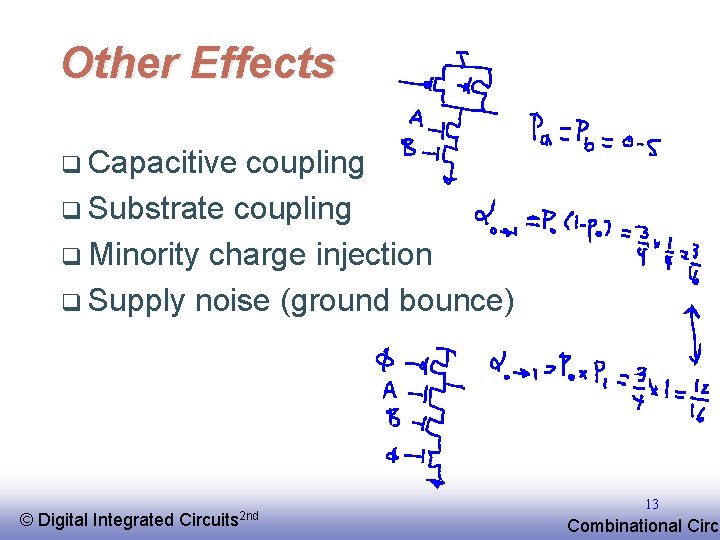

Other Effects q Capacitive coupling q Substrate coupling q Minority charge injection q Supply noise (ground bounce) © EE 141 Digital Integrated Circuits 2 nd 13 Combinational Circu

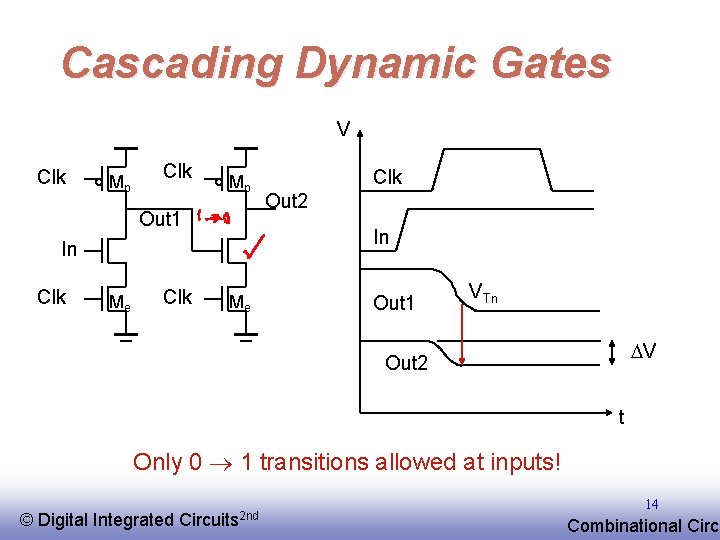

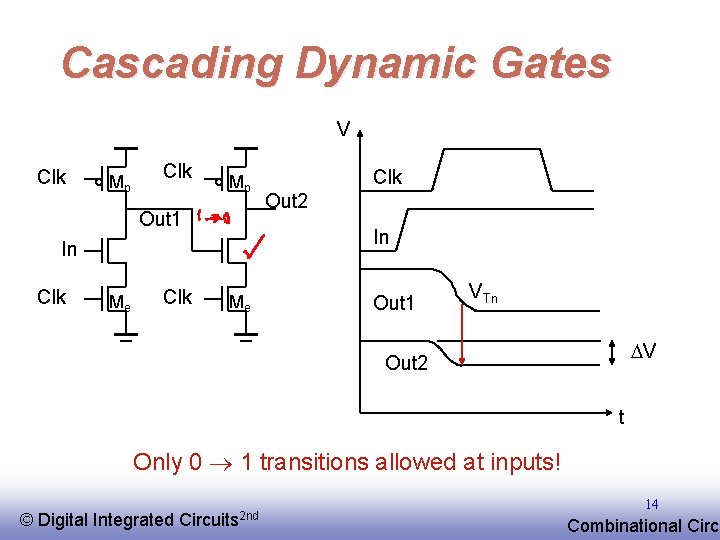

Cascading Dynamic Gates V Clk Mp Out 1 Me Clk Out 2 In In Clk Me Out 1 VTn V Out 2 t Only 0 1 transitions allowed at inputs! © EE 141 Digital Integrated Circuits 2 nd 14 Combinational Circu

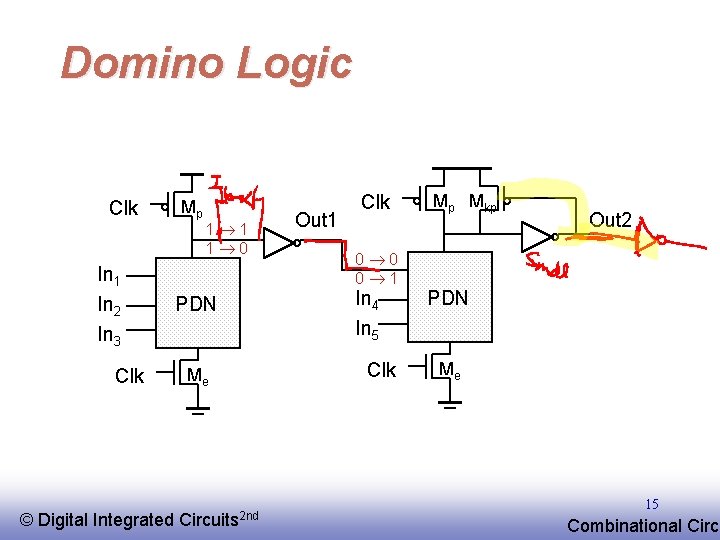

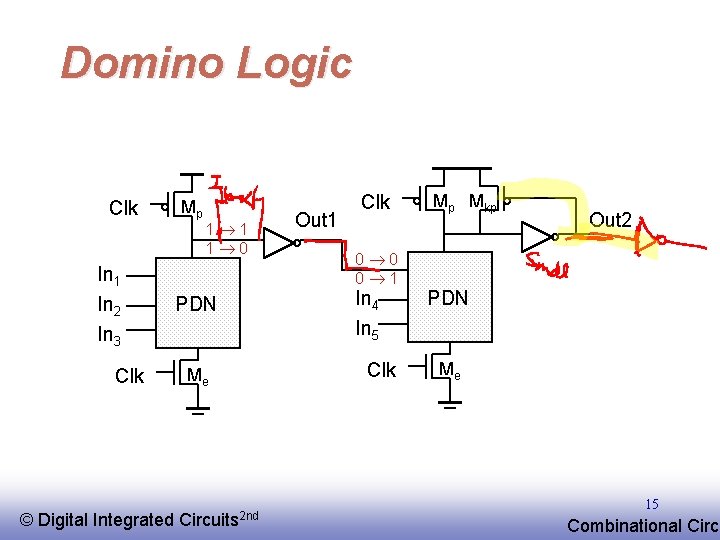

Domino Logic Clk In 1 In 2 In 3 Clk © EE 141 Digital Integrated Mp 1 1 1 0 PDN Me Circuits 2 nd Out 1 Clk 0 0 0 1 In 4 In 5 Clk Mp Mkp Out 2 PDN Me 15 Combinational Circu

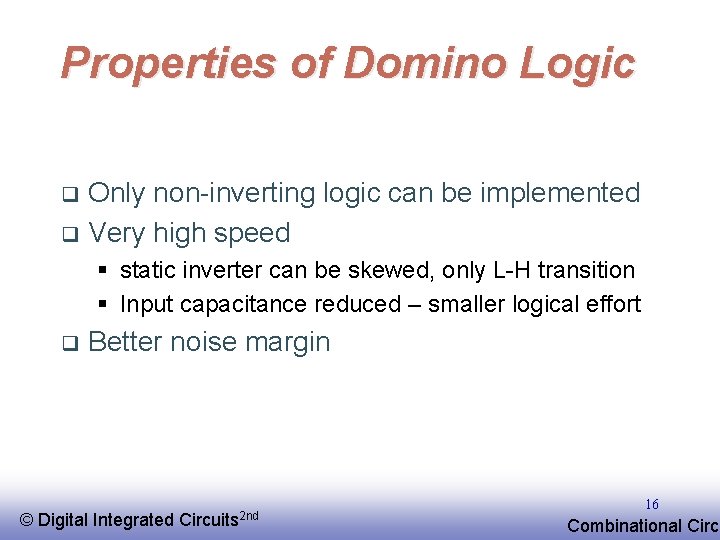

Properties of Domino Logic Only non-inverting logic can be implemented q Very high speed q § static inverter can be skewed, only L-H transition § Input capacitance reduced – smaller logical effort q Better noise margin © EE 141 Digital Integrated Circuits 2 nd 16 Combinational Circu

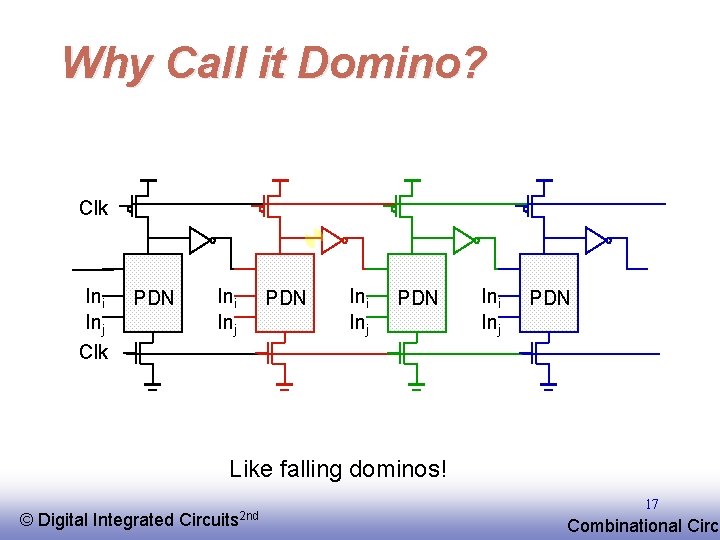

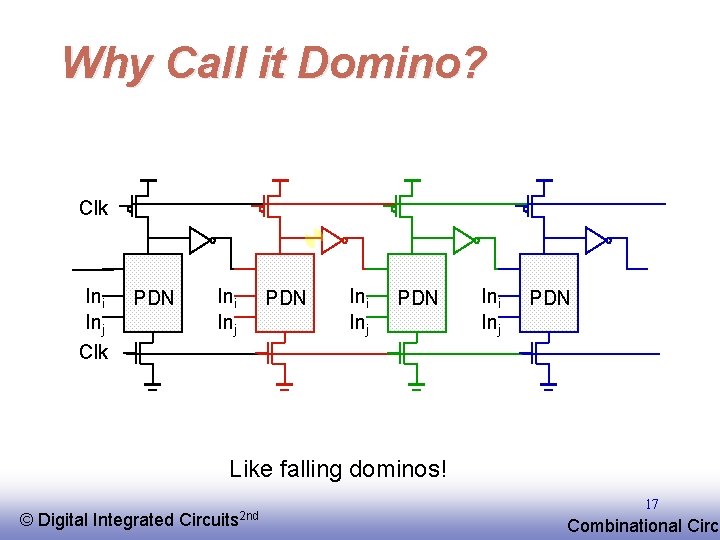

Why Call it Domino? Clk Ini Inj Clk PDN Ini Inj PDN Like falling dominos! © EE 141 Digital Integrated Circuits 2 nd 17 Combinational Circu

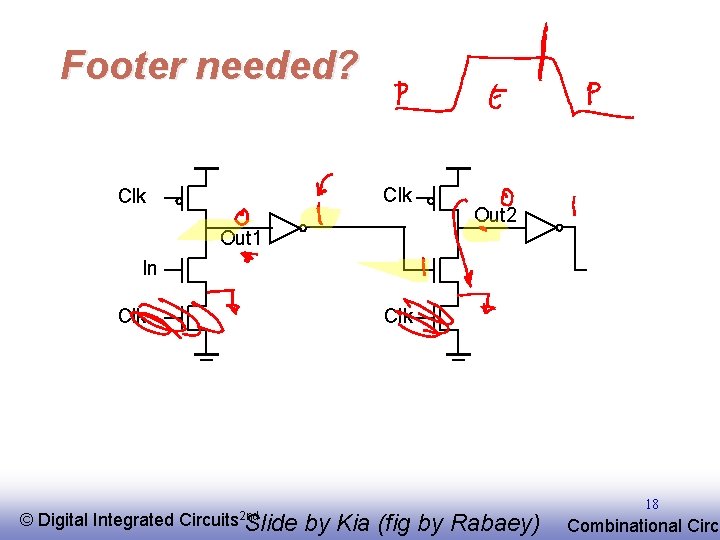

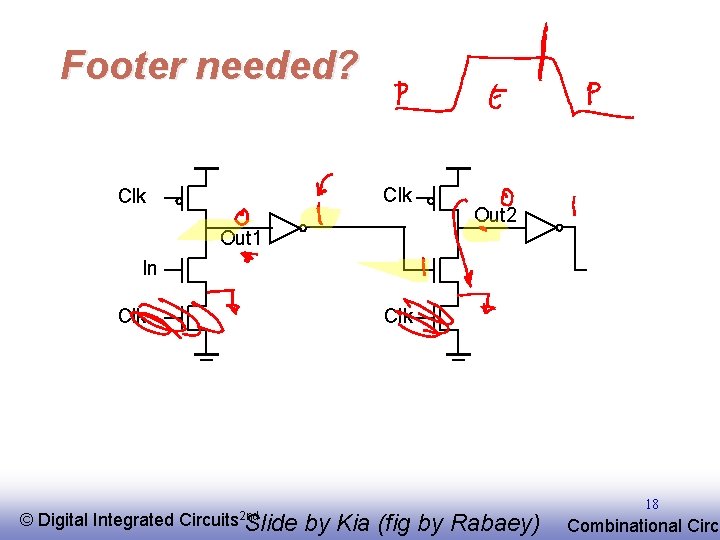

Footer needed? Clk Out 2 Out 1 In Clk © EE 141 Digital Integrated Clk Slide by Kia (fig by Rabaey) Circuits 2 nd 18 Combinational Circu

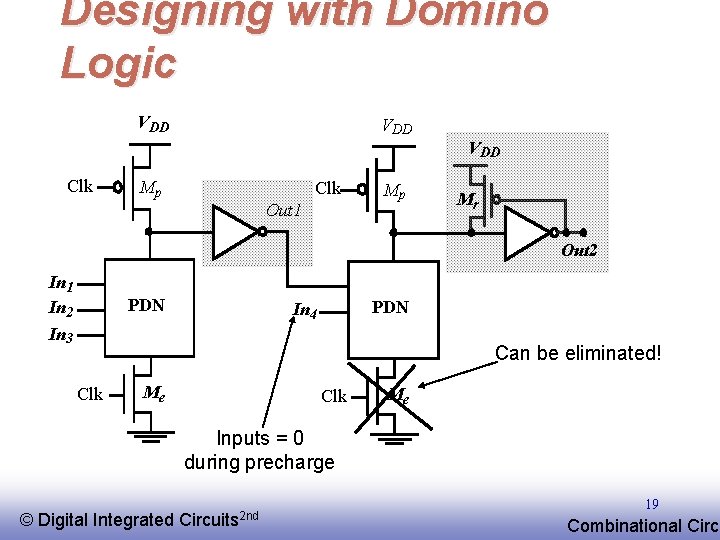

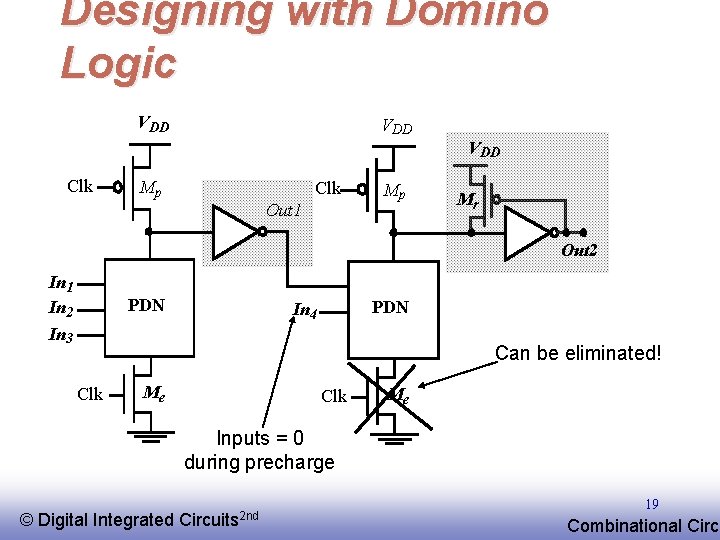

Designing with Domino Logic VDD VDD Clk Mp Clk Out 1 Mp Mr Out 2 In 1 In 2 In 3 PDN In 4 Can be eliminated! Clk Me Inputs = 0 during precharge © EE 141 Digital Integrated Circuits 2 nd 19 Combinational Circu

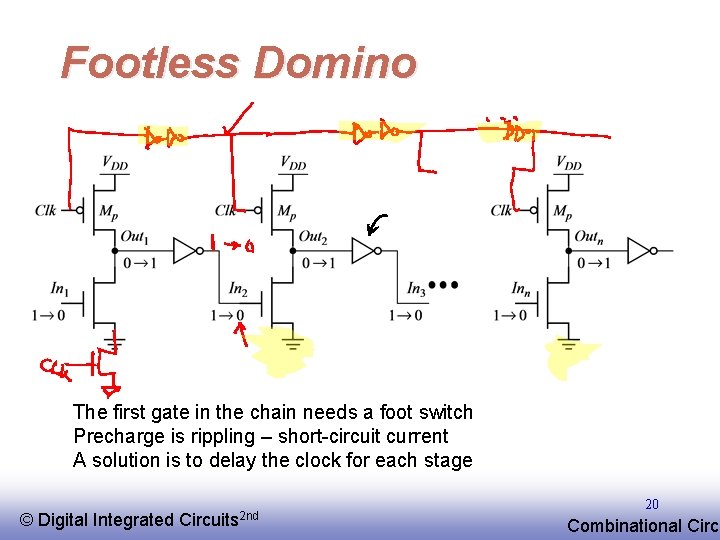

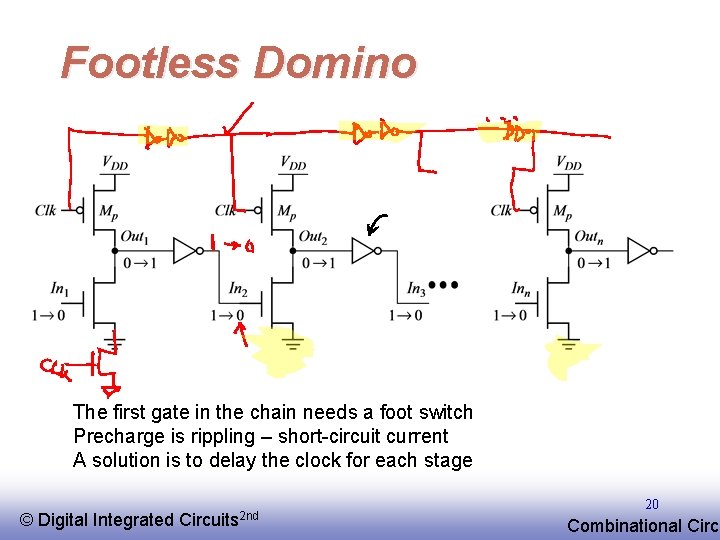

Footless Domino The first gate in the chain needs a foot switch Precharge is rippling – short-circuit current A solution is to delay the clock for each stage © EE 141 Digital Integrated Circuits 2 nd 20 Combinational Circu

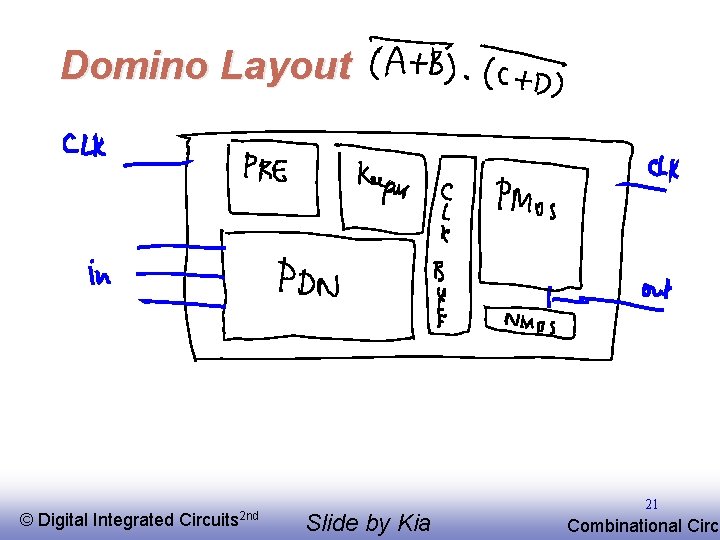

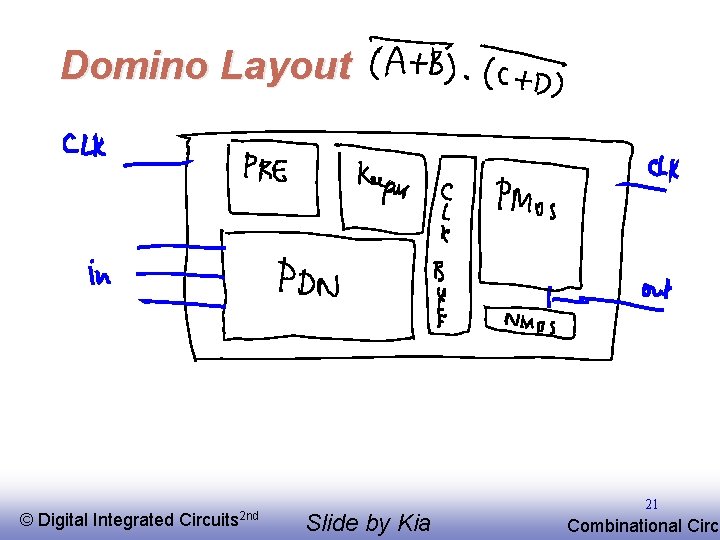

Domino Layout © EE 141 Digital Integrated Circuits 2 nd Slide by Kia 21 Combinational Circu

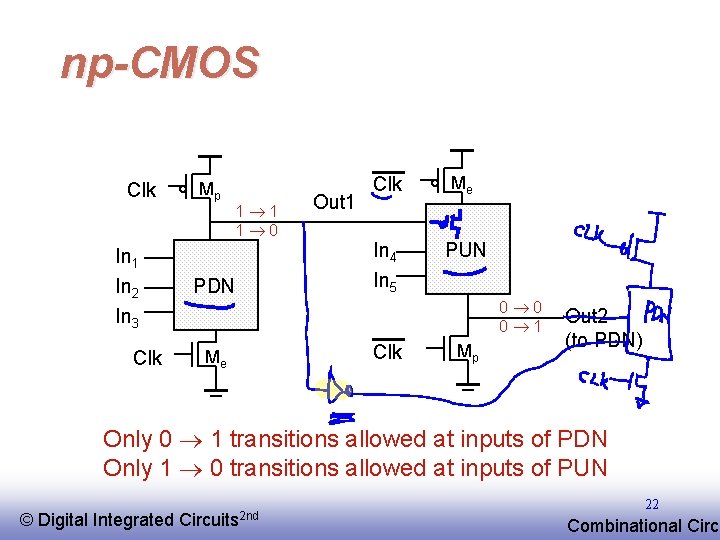

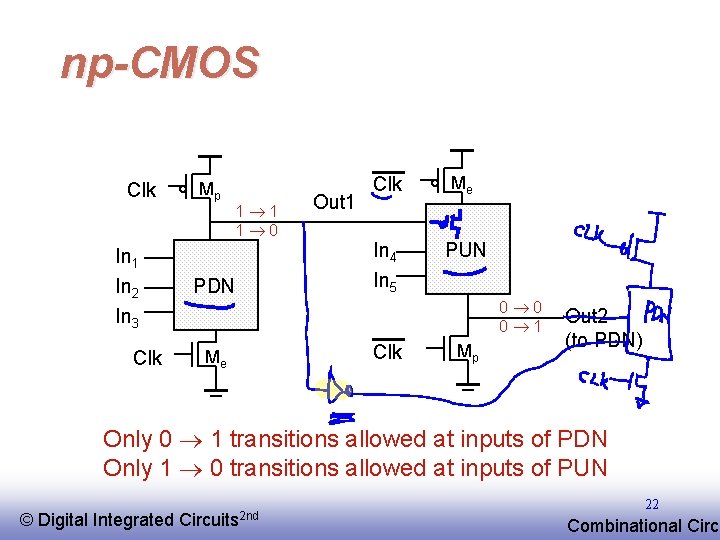

np-CMOS Clk In 1 In 2 In 3 Clk Mp 1 1 1 0 PDN Me Out 1 Clk Me In 4 In 5 PUN 0 0 0 1 Clk Mp Out 2 (to PDN) Only 0 1 transitions allowed at inputs of PDN Only 1 0 transitions allowed at inputs of PUN © EE 141 Digital Integrated Circuits 2 nd 22 Combinational Circu

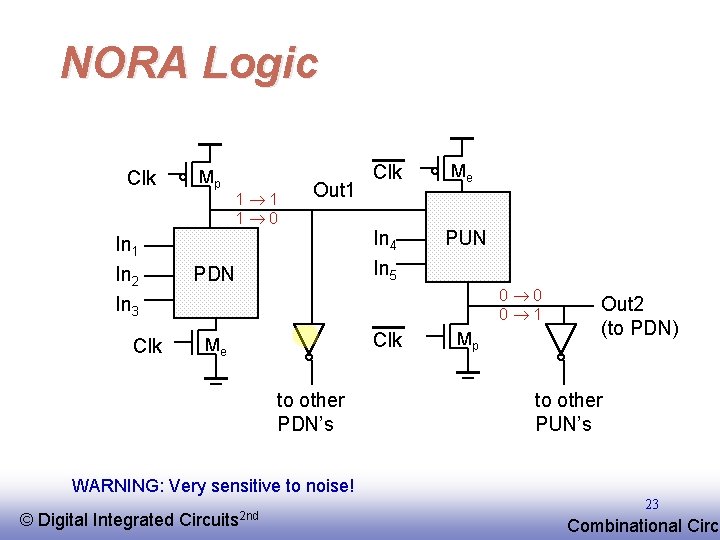

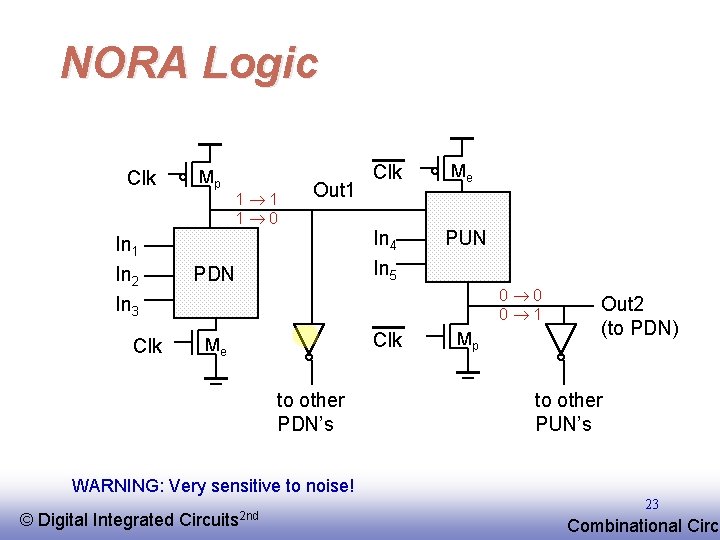

NORA Logic Clk In 1 In 2 In 3 Clk Mp 1 1 1 0 Out 1 PDN Clk Me In 4 In 5 PUN 0 0 0 1 Clk Me to other PDN’s Mp Out 2 (to PDN) to other PUN’s WARNING: Very sensitive to noise! © EE 141 Digital Integrated Circuits 2 nd 23 Combinational Circu

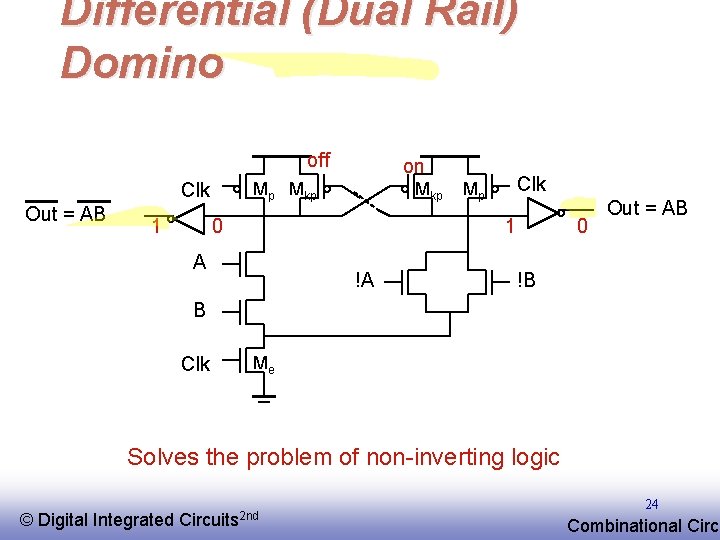

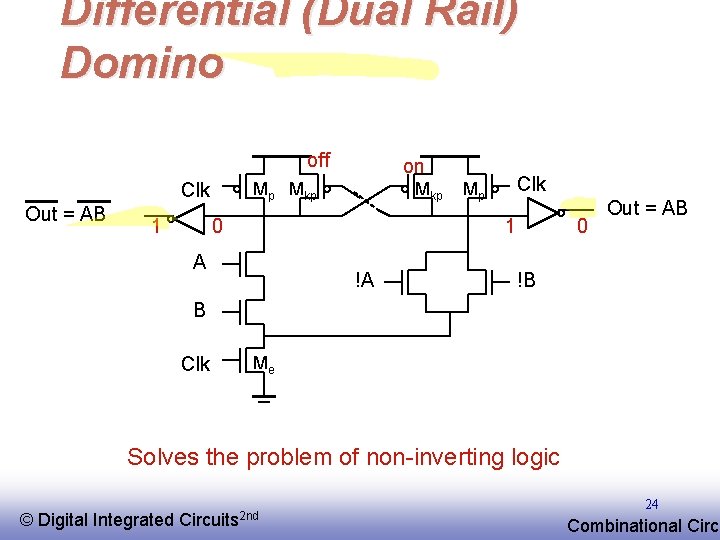

Differential (Dual Rail) Domino off Mp Mkp Clk Out = AB 1 on Mkp 0 Clk Mp 1 A !A 0 Out = AB !B B Clk Me Solves the problem of non-inverting logic © EE 141 Digital Integrated Circuits 2 nd 24 Combinational Circu

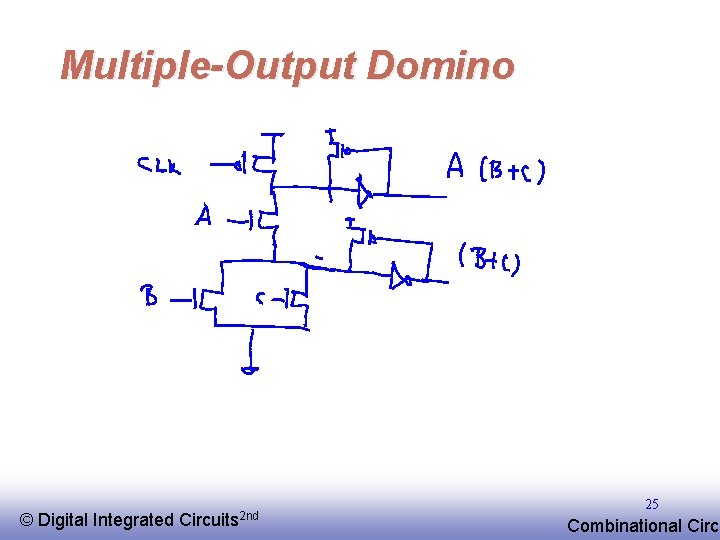

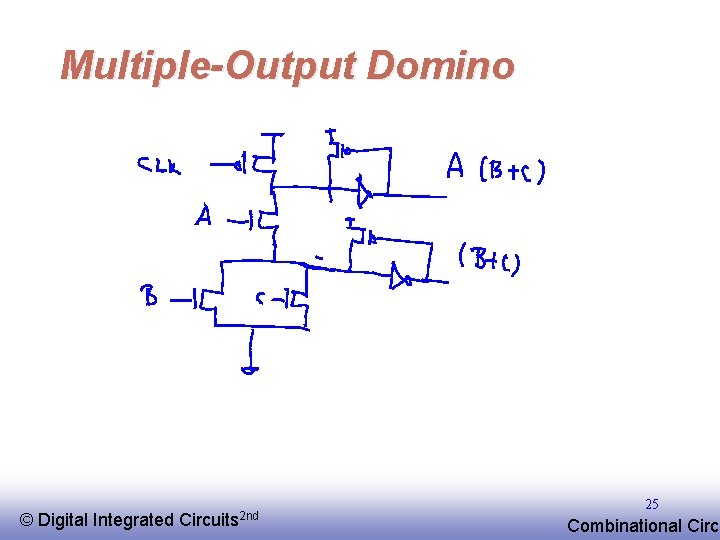

Multiple-Output Domino © EE 141 Digital Integrated Circuits 2 nd 25 Combinational Circu