COE 405 Synthesis of Combinational Sequential Logic Dr

COE 405 Synthesis of Combinational & Sequential Logic Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

Outline n Circuit Synthesis n Multilevel Logic Synthesis n Timing Issues in Multiple-Level Logic Optimization n Behavioral or High-Level Synthesis n Synthesis of Combinational Logic n Synthesis of Priority Structures n Exploiting Logical Don’t Care Conditions n Resource Sharing 1 -2

Outline n Synthesis of Sequential Logic with Latches n Synthesis of Three-State Devices and Bus Interfaces n Synthesis of Sequential Logic with Flip-Flops n Synthesis of Explicit State Machine n Synthesis of Gated Clocks and Clock Enable n Synthesis of Loops 1 -3

Circuit Synthesis n Architectural-level synthesis • Determine the macroscopic structure • Interconnection of major building blocks. n Logic-level synthesis • Determine the microscopic structure • Interconnection of logic gates. n Geometrical-level synthesis (Physical design) • Placement and routing. • Determine positions and connections. 1 -4

Logic Synthesis Flow 1 -5

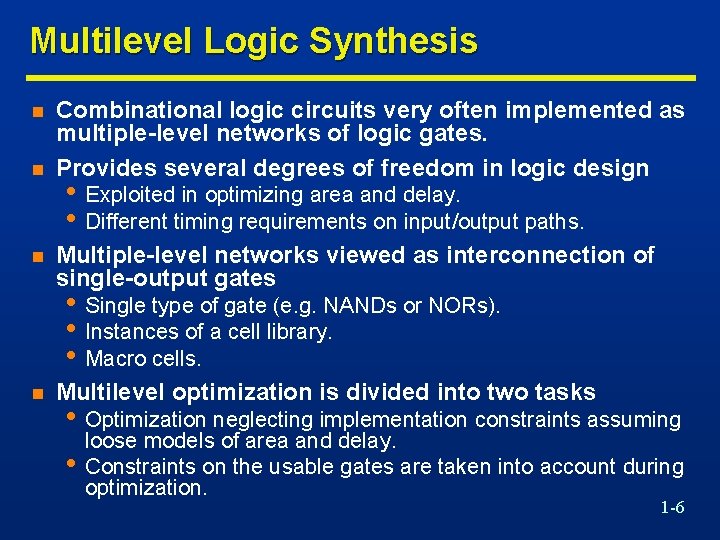

Multilevel Logic Synthesis n n n Combinational logic circuits very often implemented as multiple-level networks of logic gates. Provides several degrees of freedom in logic design • Exploited in optimizing area and delay. • Different timing requirements on input/output paths. Multiple-level networks viewed as interconnection of single-output gates • Single type of gate (e. g. NANDs or NORs). • Instances of a cell library. • Macro cells. n Multilevel optimization is divided into two tasks • Optimization neglecting implementation constraints assuming loose models of area and delay. • Constraints on the usable gates are taken into account during optimization. 1 -6

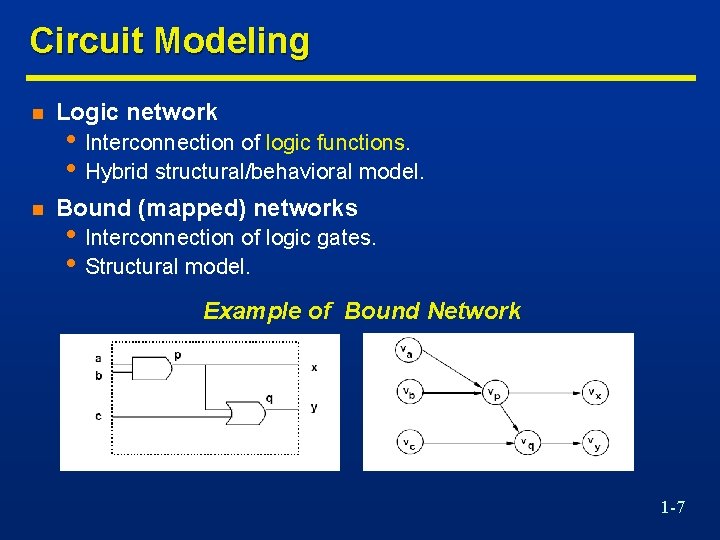

Circuit Modeling n Logic network n Bound (mapped) networks • Interconnection of logic functions. • Hybrid structural/behavioral model. • Interconnection of logic gates. • Structural model. Example of Bound Network 1 -7

Example of a Logic Network 1 -8

Network Optimization n Two-level logic • Area and delay proportional to cover size. • Achieving minimum (or irredundant) covers corresponds to optimizing area and speed. • Achieving irredundant cover corresponds to maximizing testability. n Multiple-level logic • Minimal-area implementations do not correspond in general to minimum-delay implementations and vice versa. • Minimize area (power) estimate • subject to delay constraints. • Minimize maximum delay • subject to area (power) constraints. • Minimize power consumption. • subject to delay constraints. • Maximize testability. 1 -9

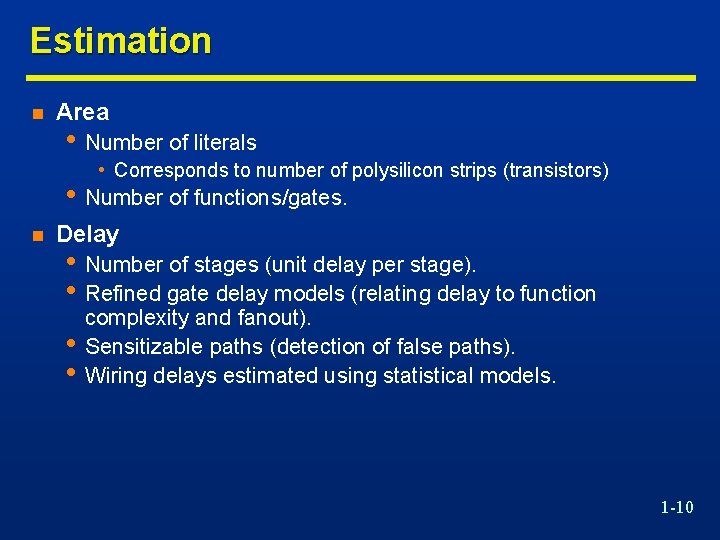

Estimation n Area • Number of literals • Corresponds to number of polysilicon strips (transistors) • Number of functions/gates. n Delay • Number of stages (unit delay per stage). • Refined gate delay models (relating delay to function • • complexity and fanout). Sensitizable paths (detection of false paths). Wiring delays estimated using statistical models. 1 -10

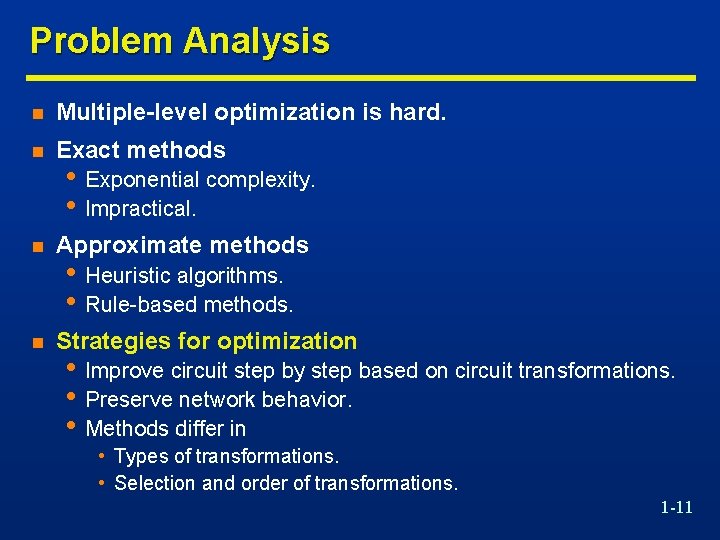

Problem Analysis n Multiple-level optimization is hard. n Exact methods n Approximate methods n Strategies for optimization • Exponential complexity. • Impractical. • Heuristic algorithms. • Rule-based methods. • Improve circuit step by step based on circuit transformations. • Preserve network behavior. • Methods differ in • Types of transformations. • Selection and order of transformations. 1 -11

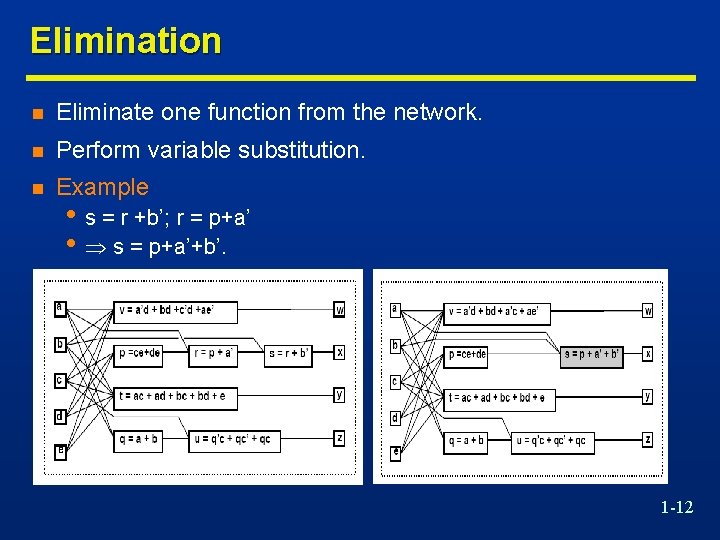

Elimination n Eliminate one function from the network. n Perform variable substitution. n Example • s = r +b’; r = p+a’ • s = p+a’+b’. 1 -12

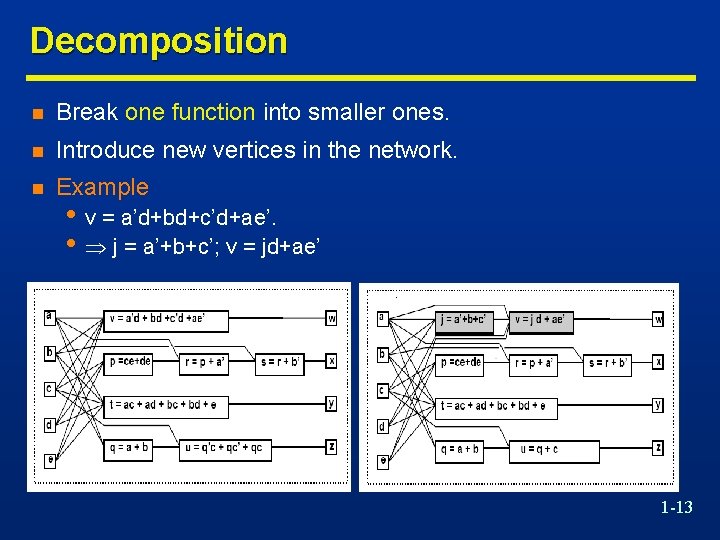

Decomposition n Break one function into smaller ones. n Introduce new vertices in the network. n Example • v = a’d+bd+c’d+ae’. • j = a’+b+c’; v = jd+ae’ 1 -13

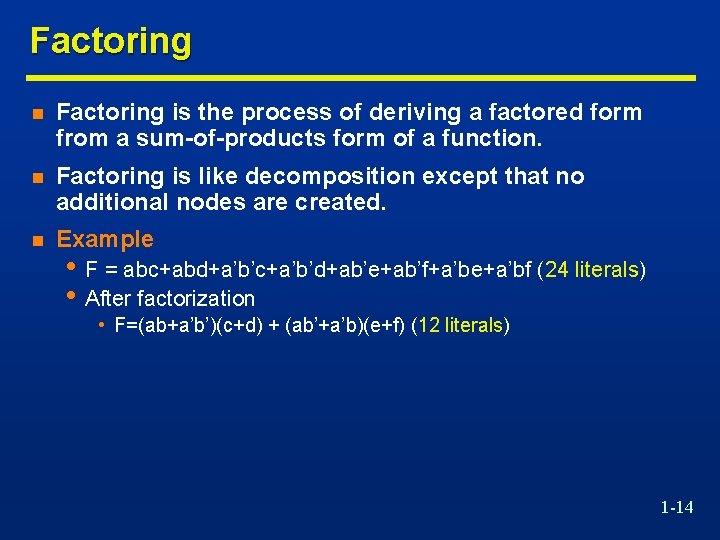

Factoring n Factoring is the process of deriving a factored form from a sum-of-products form of a function. n Factoring is like decomposition except that no additional nodes are created. n Example • F = abc+abd+a’b’c+a’b’d+ab’e+ab’f+a’be+a’bf (24 literals) • After factorization • F=(ab+a’b’)(c+d) + (ab’+a’b)(e+f) (12 literals) 1 -14

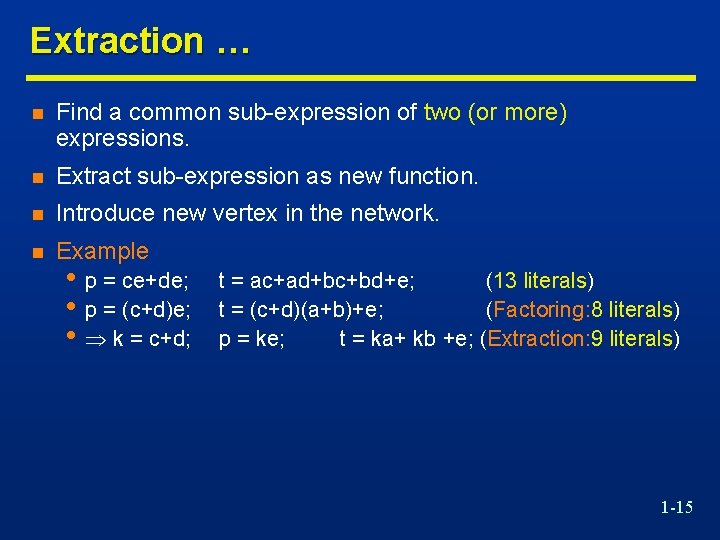

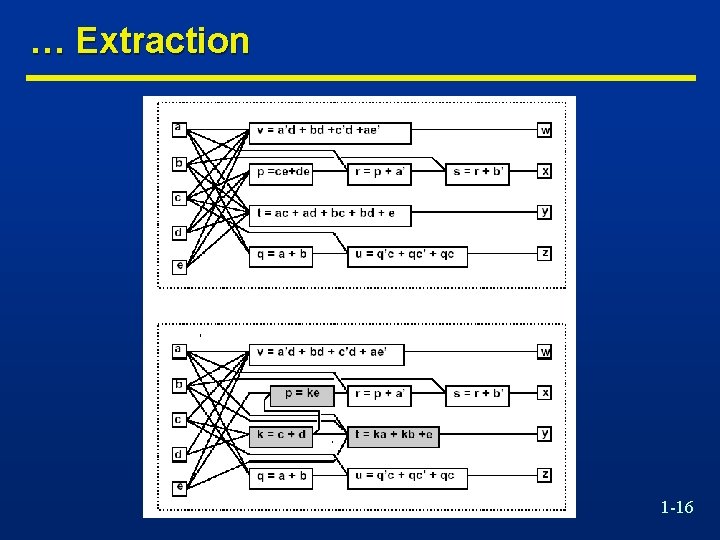

Extraction … n Find a common sub-expression of two (or more) expressions. n Extract sub-expression as new function. n Introduce new vertex in the network. n Example • p = ce+de; • p = (c+d)e; • k = c+d; t = ac+ad+bc+bd+e; (13 literals) t = (c+d)(a+b)+e; (Factoring: 8 literals) p = ke; t = ka+ kb +e; (Extraction: 9 literals) 1 -15

… Extraction 1 -16

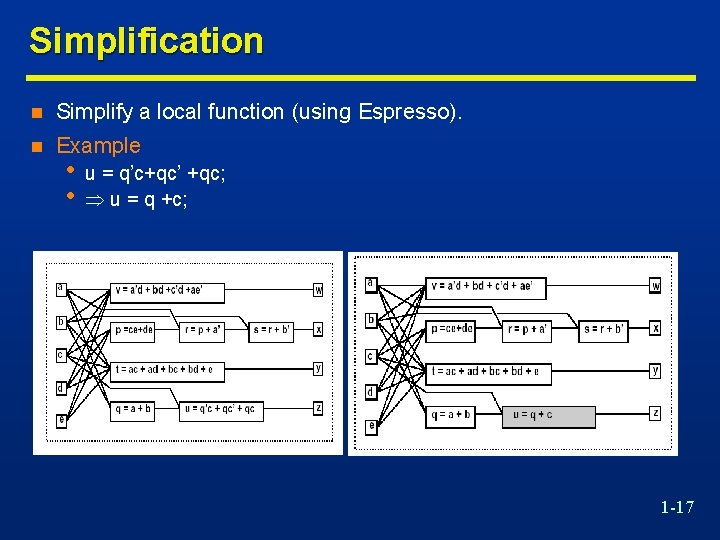

Simplification n Simplify a local function (using Espresso). n Example • • u = q’c+qc’ +qc; u = q +c; 1 -17

Substitution n Simplify a local function by using an additional input that was not previously in its support set. n Example • • t = ka+kb+e. t = kq +e; because q = a+b. 1 -18

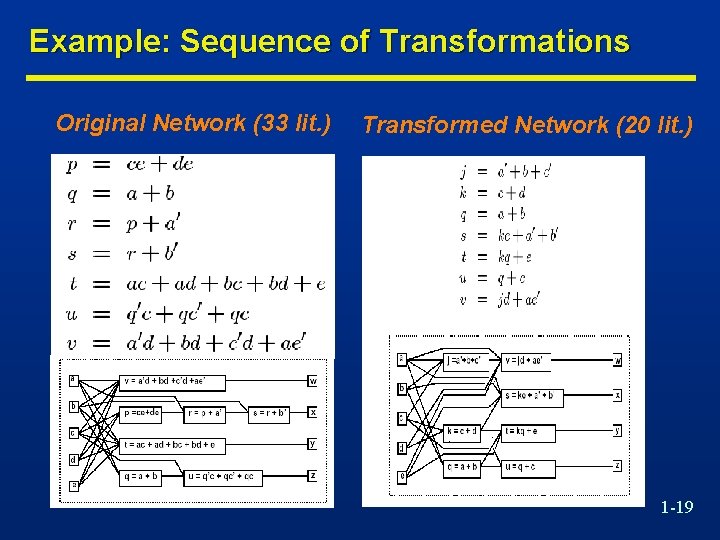

Example: Sequence of Transformations Original Network (33 lit. ) Transformed Network (20 lit. ) 1 -19

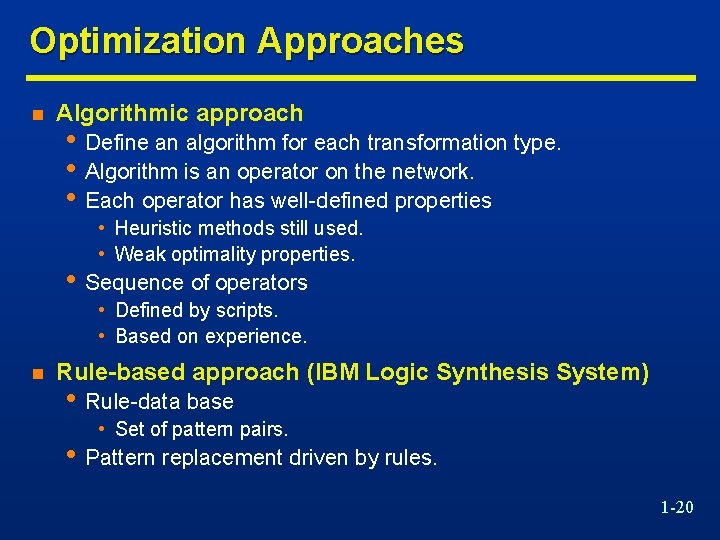

Optimization Approaches n Algorithmic approach • Define an algorithm for each transformation type. • Algorithm is an operator on the network. • Each operator has well-defined properties • Heuristic methods still used. • Weak optimality properties. • Sequence of operators • Defined by scripts. • Based on experience. n Rule-based approach (IBM Logic Synthesis System) • Rule-data base • Set of pattern pairs. • Pattern replacement driven by rules. 1 -20

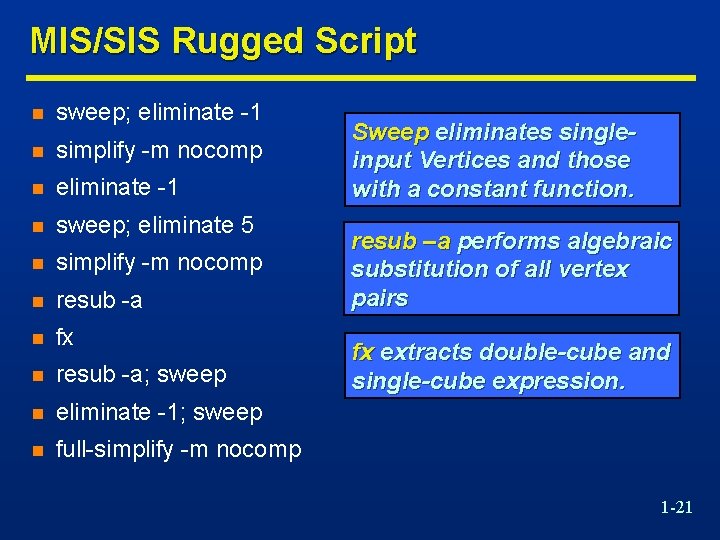

MIS/SIS Rugged Script n sweep; eliminate -1 n simplify -m nocomp n eliminate -1 n sweep; eliminate 5 n simplify -m nocomp n resub -a n fx n resub -a; sweep n eliminate -1; sweep n full-simplify -m nocomp Sweep eliminates singleinput Vertices and those with a constant function. resub –a performs algebraic substitution of all vertex pairs fx extracts double-cube and single-cube expression. 1 -21

Synthesis and Testability n Assumptions n Full testability n Synergy between synthesis and testing. n Testable networks correlate to small-area networks. n Don't care conditions play a major role. • Ease of testing a circuit. • Combinational circuit. • Single or multiple stuck-at faults. • Possible to generate test set for all faults. 1 -22

Test for Stuck-at-Faults n Net y stuck-at 0 • Input pattern that sets y to true. • Observe output. • Output of faulty circuit differs. • {t | y(t). ODC’y(t) = 1}. n Net y stuck-at 1 n Need controllability and observability. • Same, but set y to false. • {t | y’(t). ODC’y(t) = 1}. 1 -23

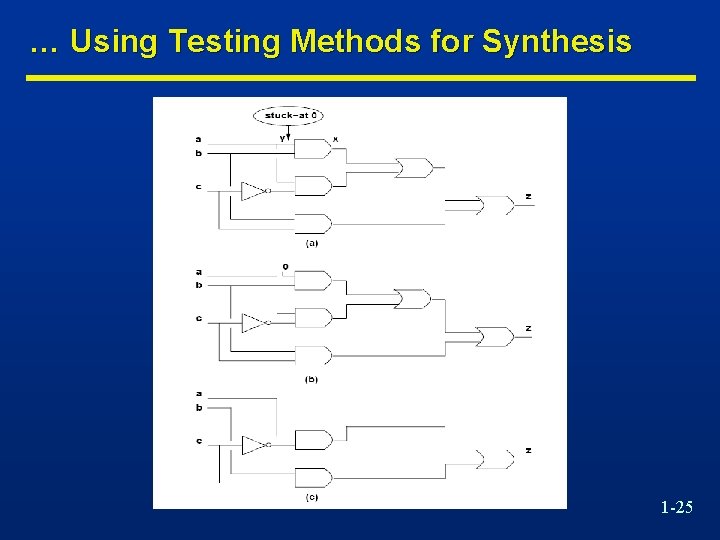

Using Testing Methods for Synthesis … n Redundancy removal. • Use ATPG to search for untestable faults. n If stuck-at 0 on net y is untestable n If stuck-at 1 on y is untestable • Set y = 0. • Propagate constant. • Set y = 1. • Propagate constant. 1 -24

… Using Testing Methods for Synthesis 1 -25

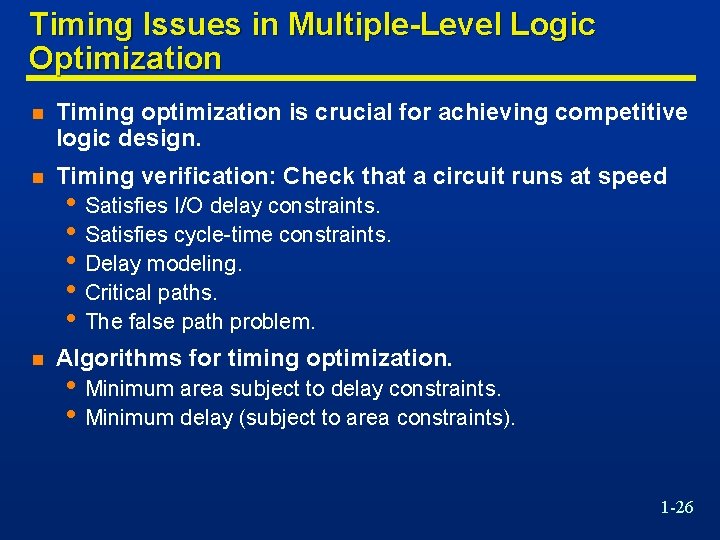

Timing Issues in Multiple-Level Logic Optimization n Timing optimization is crucial for achieving competitive logic design. n Timing verification: Check that a circuit runs at speed n Algorithms for timing optimization. • Satisfies I/O delay constraints. • Satisfies cycle-time constraints. • Delay modeling. • Critical paths. • The false path problem. • Minimum area subject to delay constraints. • Minimum delay (subject to area constraints). 1 -26

Delay Modeling n Gate delay modeling n Network delay modeling • Straightforward for bound networks. • Approximations for unbound networks. • Compute signal propagation • Topological methods. • Logic/topological methods. n Gate delay modeling for unbound networks • Virtual gates: Logic expressions. • Stage delay model: Unit delay per vertex. • Refined models: Depending on size and fanout. 1 -27

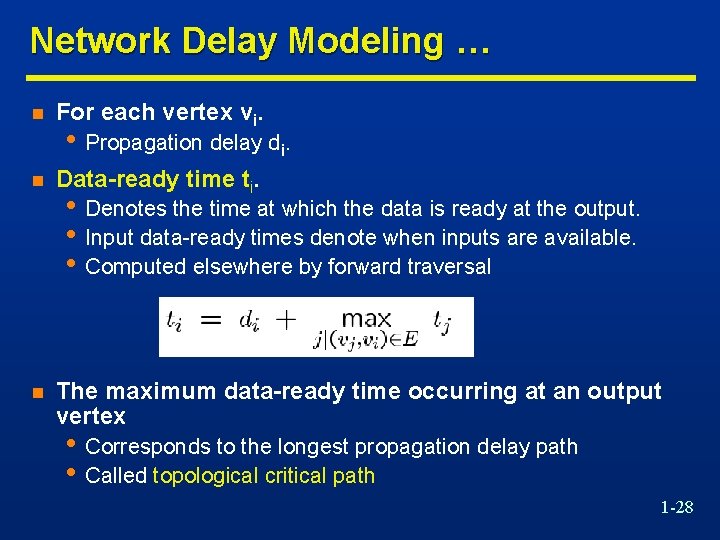

Network Delay Modeling … n For each vertex vi. n Data-ready time ti. n The maximum data-ready time occurring at an output vertex • Propagation delay di. • Denotes the time at which the data is ready at the output. • Input data-ready times denote when inputs are available. • Computed elsewhere by forward traversal • Corresponds to the longest propagation delay path • Called topological critical path 1 -28

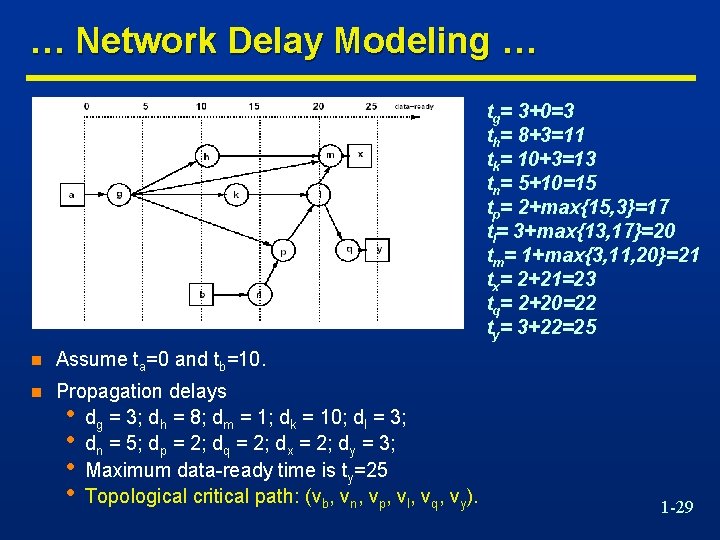

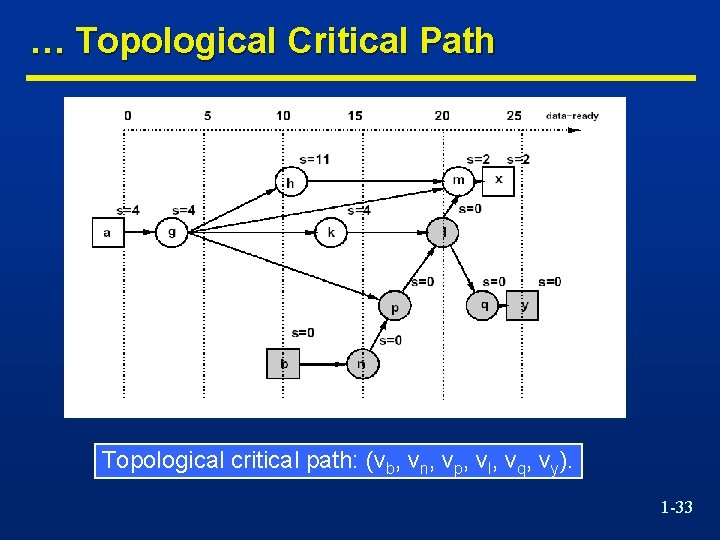

… Network Delay Modeling … tg= 3+0=3 th= 8+3=11 tk= 10+3=13 tn= 5+10=15 tp= 2+max{15, 3}=17 tl= 3+max{13, 17}=20 tm= 1+max{3, 11, 20}=21 tx= 2+21=23 tq= 2+20=22 ty= 3+22=25 n Assume ta=0 and tb=10. n Propagation delays • dg = 3; dh = 8; dm = 1; dk = 10; dl = 3; • dn = 5; dp = 2; dq = 2; dx = 2; dy = 3; • Maximum data-ready time is ty=25 • Topological critical path: (vb, vn, vp, vl, vq, vy). 1 -29

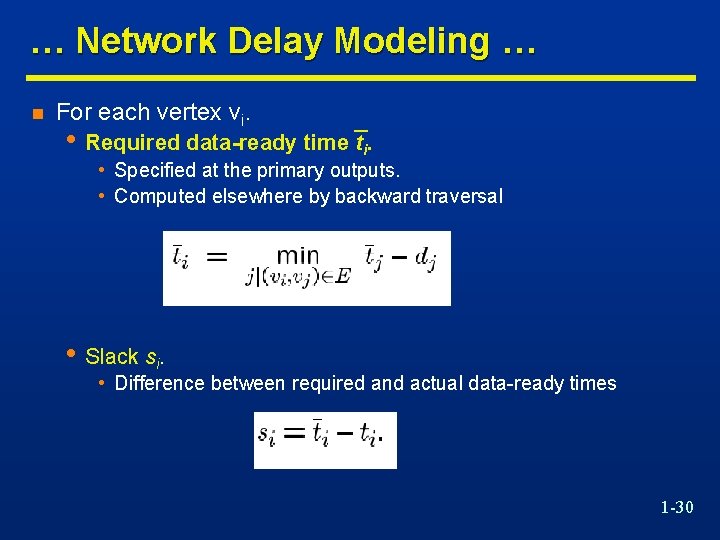

… Network Delay Modeling … n For each vertex vi. • Required data-ready time ti. • Specified at the primary outputs. • Computed elsewhere by backward traversal • Slack si. • Difference between required and actual data-ready times 1 -30

… Network Delay Modeling n Required data-ready times • tx = 25 and ty = 25. Required Times & Slack: sx= 2; sy=0 tm= 25 -2=23; sm=23 -21=2 tq= 25 -3=22; sq=22 -22=0 tl= min{23 -1, 22 -2}=20; sl=0 th= 23 -1=22; sh=22 -11=11 tk= 20 -3=17; sk=17 -13=4 tp= 20 -3=17; sp=17 -17=0 tn= 17 -2=15; sn=15 -15=0 tb= 15 -5=10; sb=10 -10=0 tg= min{22 -8; 17 -10; 17 -2}=7; sg=4 ta=7 -3=4; sa=4 -0=4 Propagation Delays : dg = 3; dh = 8; dm = 1; dk = 10; dl = 3; dn = 5; dp = 2; dq = 2; dx = 2; dy = 3 Data-Ready Times: tg= 3+0=3 th= 8+3=11 tk= 10+3=13 tn= 5+10=15 tp= 2+max{15, 3}=17 tl= 3+max{13, 17}=20 tm= 1+max{3, 11, 20}=21 tx= 2+21=23 tq= 2+20=22 ty= 3+22=25 1 -31

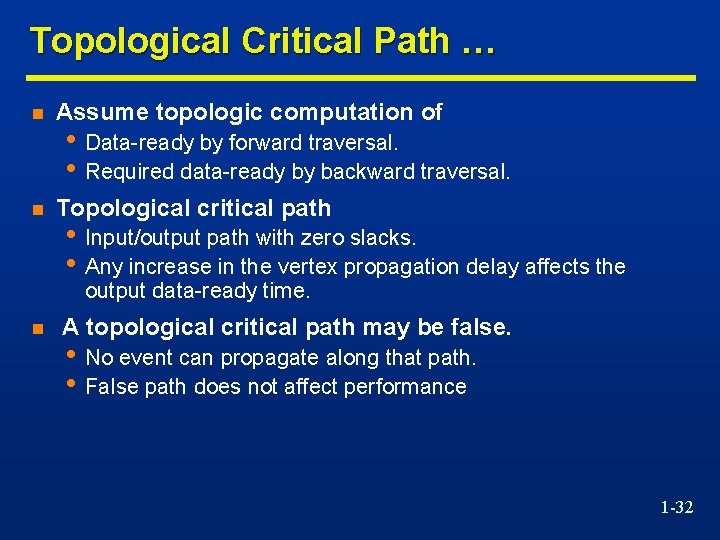

Topological Critical Path … n Assume topologic computation of n Topological critical path • Data-ready by forward traversal. • Required data-ready by backward traversal. • Input/output path with zero slacks. • Any increase in the vertex propagation delay affects the output data-ready time. n A topological critical path may be false. • No event can propagate along that path. • False path does not affect performance 1 -32

… Topological Critical Path Topological critical path: (vb, vn, vp, vl, vq, vy). 1 -33

False Path Example n All gates have unit delay. n All inputs ready at time 0. n Longest topological path: (va, vc, vd, vy, vz). n • • Path delay: 4 units. False path: event cannot propagate through it Critical true path: (va, vc, vd, vy). • Path delay: 3 units. 1 -34

Algorithms for Delay Minimization … n n n Alternate • • Critical path computation. Logic transformation on critical vertices. Consider quasi critical paths • • Paths with near-critical delay. Small slacks. Small difference between critical paths and largest delay of a non-critical path leads to smaller gain in speeding up critical paths only. 1 -35

Behavioral or High-Level Synthesis n The automatic generation of data path and control unit is known as high-level synthesis. n Tasks involved in HLS are scheduling and allocation. n Scheduling distributes the execution of operations throughout time steps. n Allocation assigns hardware to operations and values. • Allocation of hardware cells includes functional unit allocation, register allocation and bus allocation. • Allocation determines the interconnections required. 1 -36

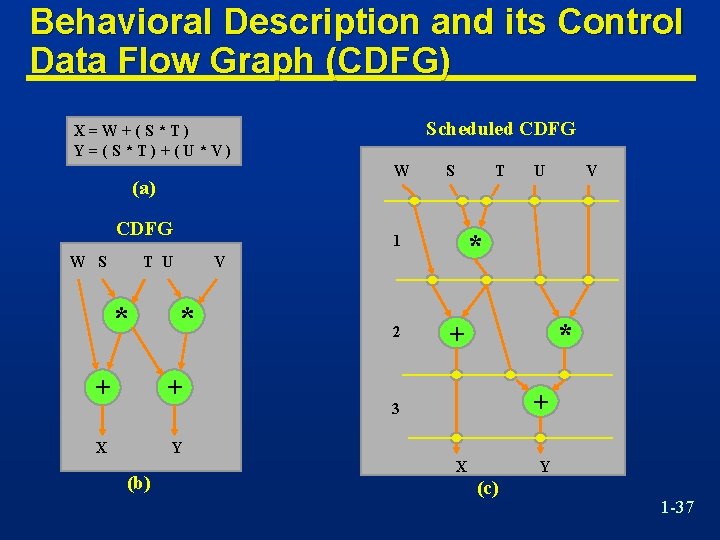

Behavioral Description and its Control Data Flow Graph (CDFG) Scheduled CDFG X=W+(S*T) Y=(S*T)+(U*V) W (a) CDFG W S * + X Y 2 U V * V + (b) T 1 T U * S * + + 3 X Y (c) 1 -37

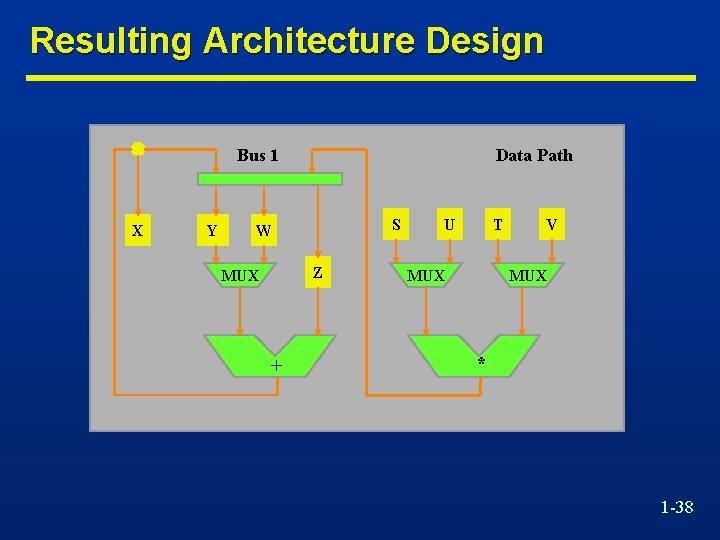

Resulting Architecture Design Bus 1 X Y Data Path S W Z MUX + U T MUX V MUX * 1 -38

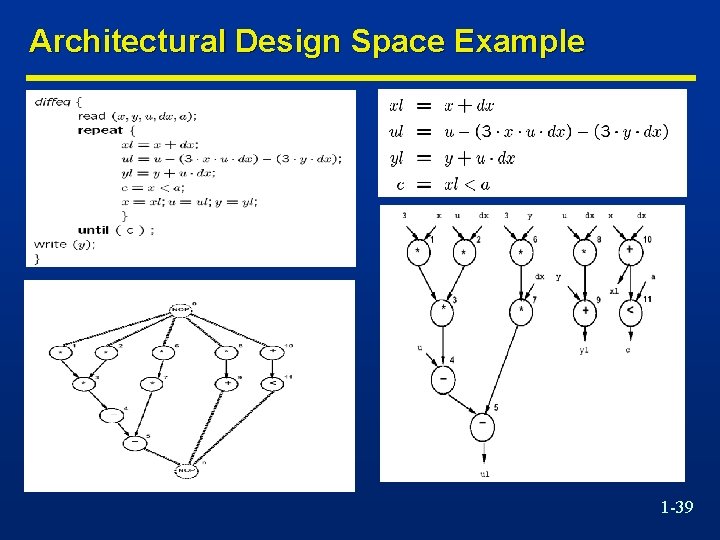

Architectural Design Space Example 1 -39

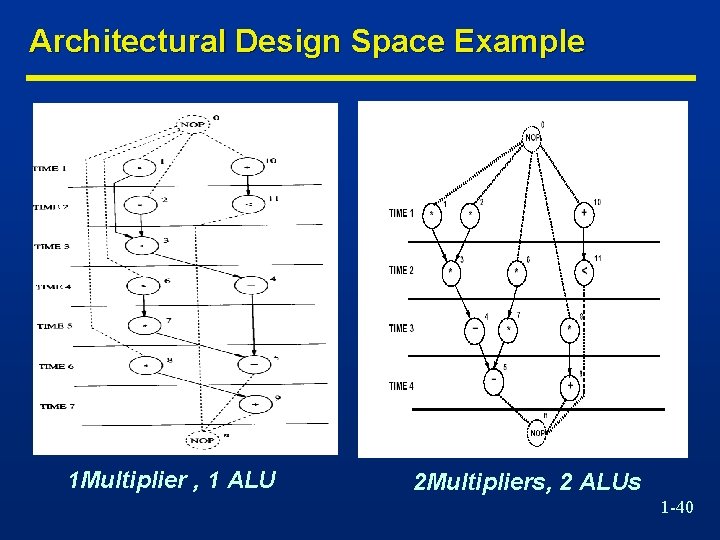

Architectural Design Space Example 1 Multiplier , 1 ALU 2 Multipliers, 2 ALUs 1 -40

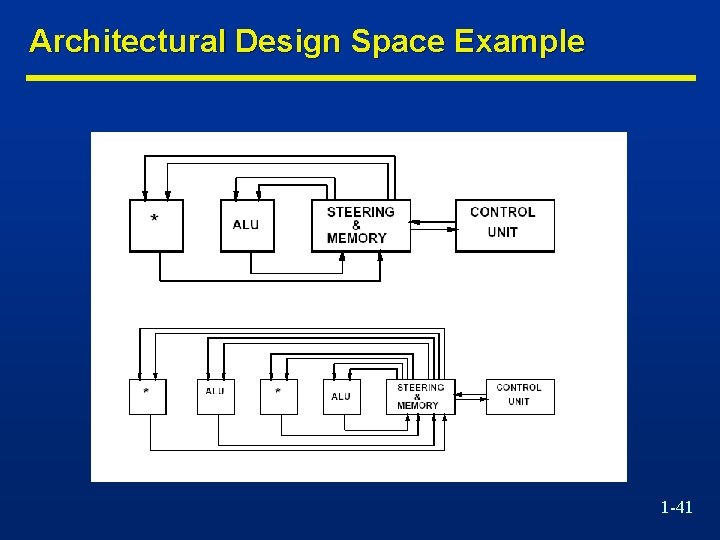

Architectural Design Space Example 1 -41

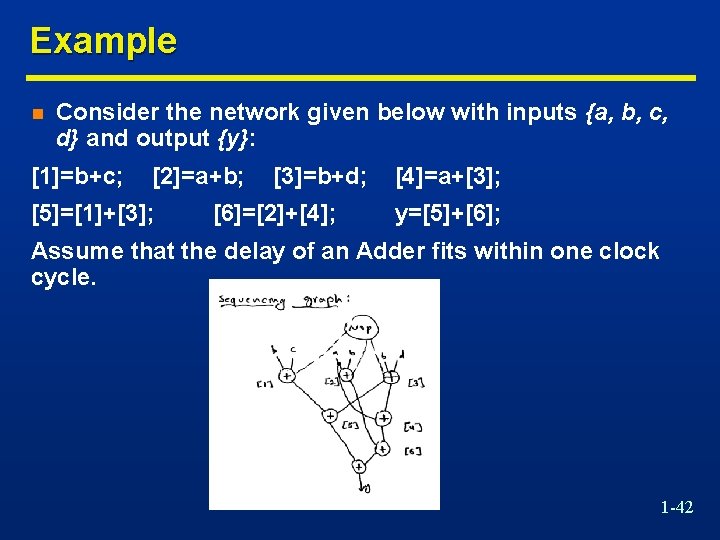

Example n Consider the network given below with inputs {a, b, c, d} and output {y}: [1]=b+c; [2]=a+b; [5]=[1]+[3]; [3]=b+d; [6]=[2]+[4]; [4]=a+[3]; y=[5]+[6]; Assume that the delay of an Adder fits within one clock cycle. 1 -42

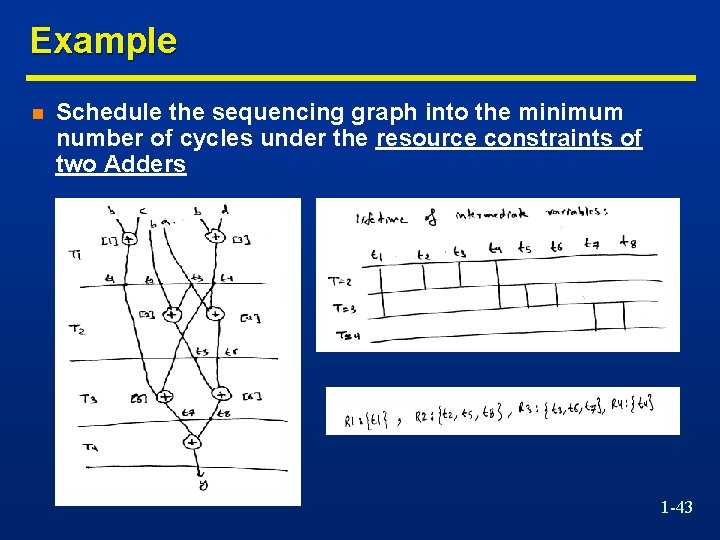

Example n Schedule the sequencing graph into the minimum number of cycles under the resource constraints of two Adders 1 -43

Example n Datapath 1 -44

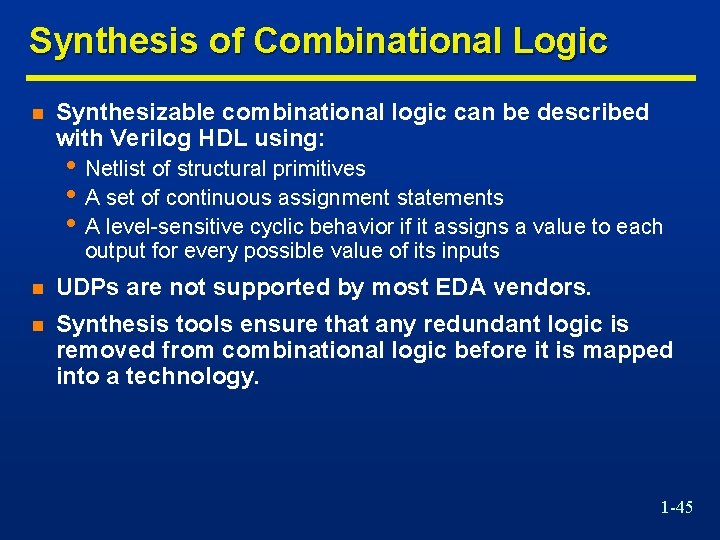

Synthesis of Combinational Logic n Synthesizable combinational logic can be described with Verilog HDL using: • Netlist of structural primitives • A set of continuous assignment statements • A level-sensitive cyclic behavior if it assigns a value to each output for every possible value of its inputs n UDPs are not supported by most EDA vendors. n Synthesis tools ensure that any redundant logic is removed from combinational logic before it is mapped into a technology. 1 -45

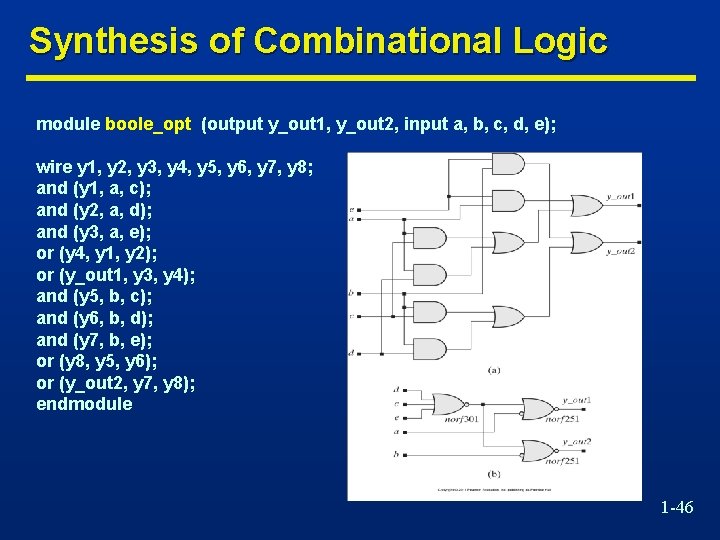

Synthesis of Combinational Logic module boole_opt (output y_out 1, y_out 2, input a, b, c, d, e); wire y 1, y 2, y 3, y 4, y 5, y 6, y 7, y 8; and (y 1, a, c); and (y 2, a, d); and (y 3, a, e); or (y 4, y 1, y 2); or (y_out 1, y 3, y 4); and (y 5, b, c); and (y 6, b, d); and (y 7, b, e); or (y 8, y 5, y 6); or (y_out 2, y 7, y 8); endmodule 1 -46

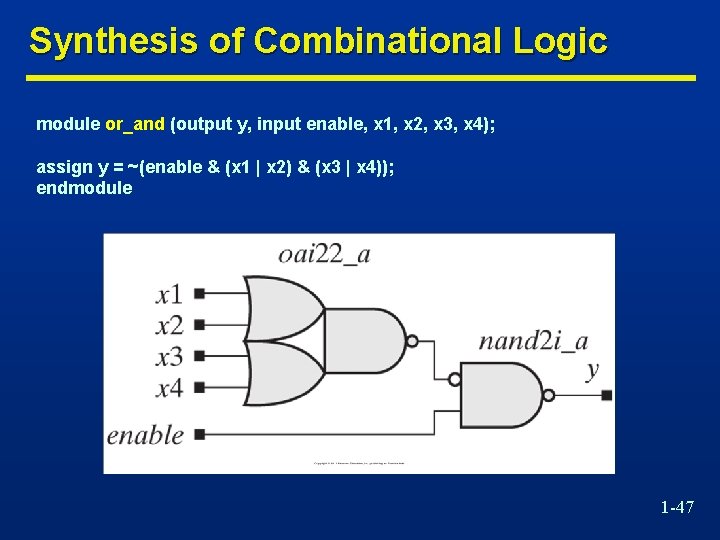

Synthesis of Combinational Logic module or_and (output y, input enable, x 1, x 2, x 3, x 4); assign y = ~(enable & (x 1 | x 2) & (x 3 | x 4)); endmodule 1 -47

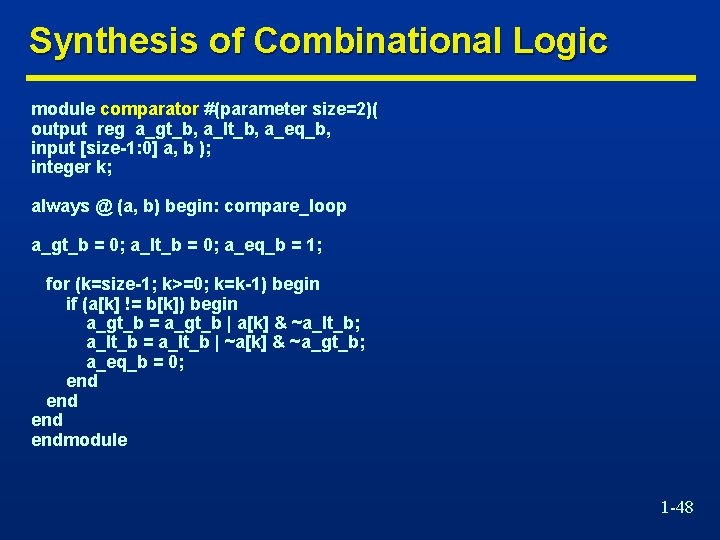

Synthesis of Combinational Logic module comparator #(parameter size=2)( output reg a_gt_b, a_lt_b, a_eq_b, input [size-1: 0] a, b ); integer k; always @ (a, b) begin: compare_loop a_gt_b = 0; a_lt_b = 0; a_eq_b = 1; for (k=size-1; k>=0; k=k-1) begin if (a[k] != b[k]) begin a_gt_b = a_gt_b | a[k] & ~a_lt_b; a_lt_b = a_lt_b | ~a[k] & ~a_gt_b; a_eq_b = 0; end endmodule 1 -48

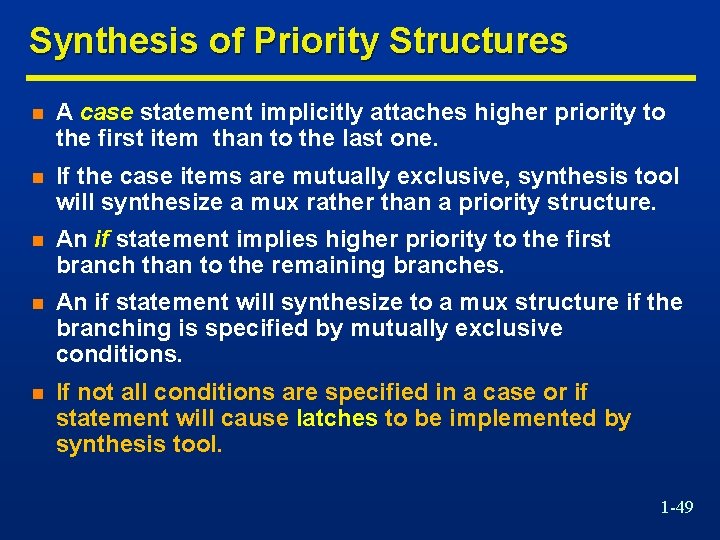

Synthesis of Priority Structures n A case statement implicitly attaches higher priority to the first item than to the last one. n If the case items are mutually exclusive, synthesis tool will synthesize a mux rather than a priority structure. n An if statement implies higher priority to the first branch than to the remaining branches. n An if statement will synthesize to a mux structure if the branching is specified by mutually exclusive conditions. n If not all conditions are specified in a case or if statement will cause latches to be implemented by synthesis tool. 1 -49

Synthesis of Priority Structures module mux_4 pri (output reg y, input a, b, c, d, sel_a, sel_b, sel_c); always @ (*) // wildcard for complete sensitivity list if (sel_a == 1) y=a; else if (sel_b==1) y=b; else if (sel_c==1) y=c; else y=d; endmodule 1 -50

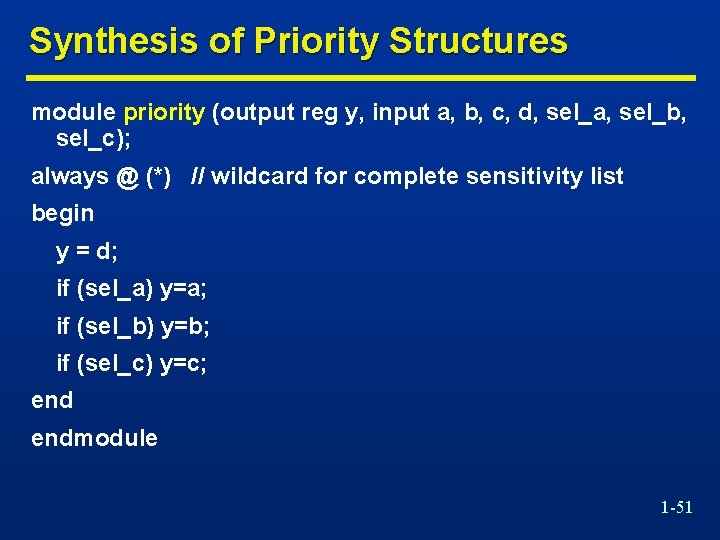

Synthesis of Priority Structures module priority (output reg y, input a, b, c, d, sel_a, sel_b, sel_c); always @ (*) // wildcard for complete sensitivity list begin y = d; if (sel_a) y=a; if (sel_b) y=b; if (sel_c) y=c; endmodule 1 -51

Exploiting Logical Don’t Care Conditions n An assignment to x in a case or if statement will be treated as a don’t care condition in synthesis. module alu_with_x (output [3: 0] alu_out, input [3: 0] data_a, data_b, input [2: 0] opcode, input enable); reg [3: 0] alu_reg; assign alu_out=(enable==1)? alu_reg: 4’bz; always @ (opcode, data_a, data_b) case (opcode) 3’b 001: alu_reg= data_a | data_b; 3’b 010: alu_reg= data_a ^ data_b; 3’b 110: alu_reg= ~data_b; default: alu_reg= 4’b 0; endcase endmodule 1 -52

![Exploiting Logical Don’t Care Conditions module alu_with_x (output [3: 0] alu_out, input [3: 0] Exploiting Logical Don’t Care Conditions module alu_with_x (output [3: 0] alu_out, input [3: 0]](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-53.jpg)

Exploiting Logical Don’t Care Conditions module alu_with_x (output [3: 0] alu_out, input [3: 0] data_a, data_b, input [2: 0] opcode, input enable); reg [3: 0] alu_reg; assign alu_out=(enable==1)? alu_reg: 4’bz; always @ (opcode, data_a, data_b) case (opcode) 3’b 001: alu_reg= data_a | data_b; 3’b 010: alu_reg= data_a ^ data_b; 3’b 110: alu_reg= ~data_b; default: alu_reg= 4’bx; endcase endmodule 1 -53

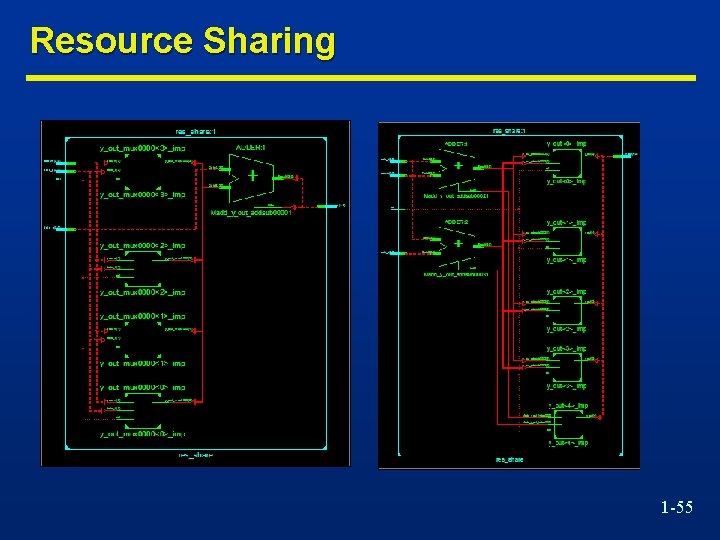

Resource Sharing n A synthesis tool must recognize whether physical resources required to implement behaviors can be shared. n Example: module res_share (output [4: 0] y_out, input [3: 0] data_a, data_b, accum, input sel); assign y_out = data_a + (sel ? accum : data_b); // assign y_out = sel ? data_a+accum : data_a+data_b; endmodule 1 -54

Resource Sharing 1 -55

![Synthesis of Sequential Logic with Latches module latch 1 (output [3: 0] data_out, input Synthesis of Sequential Logic with Latches module latch 1 (output [3: 0] data_out, input](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-56.jpg)

Synthesis of Sequential Logic with Latches module latch 1 (output [3: 0] data_out, input [3: 0] data_in, input latch_enable); assign data_out = data_enable? data_in: data_out; endmodule latch 2 (output reg [3: 0] data_out, input [3: 0] data_in, input latch_enable); always @ (latch_enable, data_in) if (latch_enable) data_out = data_in; endmodule 1 -56

Synthesis of Sequential Logic with Latches module latch_case (output reg latch_out, input latch_in, set, clear, enable); always @(enable or set or clear or latch_in) // latch_in in activity list. case ({enable, set, clear}) 3’b 000: latch_out = latch_in; 3’b 110: latch_out = 1’b 1; 3’b 010: latch_out = 1’b 1; 3’b 101: latch_out = 1’b 0; 3’b 001: latch_out = 1’b 0; endcase endmodule 1 -57

![Synthesis of Sequential Logic with Latches module Latched_Seven_Seg_Display (output reg [6: 0] Display_L, Display_R, Synthesis of Sequential Logic with Latches module Latched_Seven_Seg_Display (output reg [6: 0] Display_L, Display_R,](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-58.jpg)

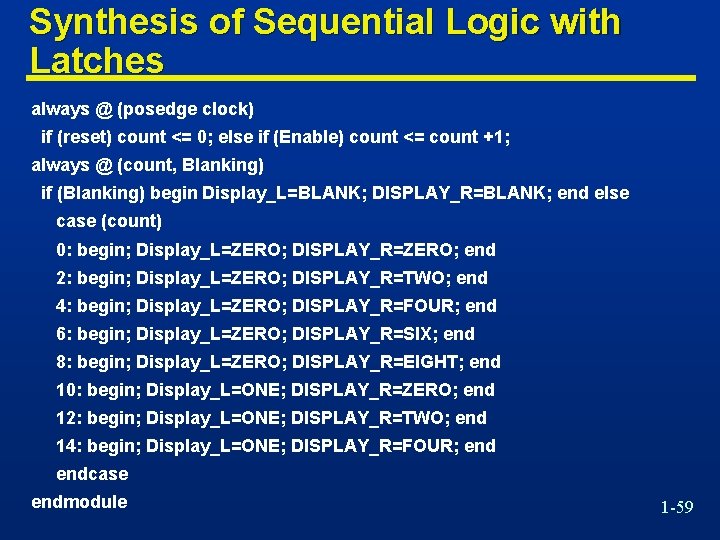

Synthesis of Sequential Logic with Latches module Latched_Seven_Seg_Display (output reg [6: 0] Display_L, Display_R, input Blcnking, Enable, clock, reset); reg [3: 0] count; // abc_defg parameter BLANK = 7’b 111_1111; parameter Zero= 7’b 000_0001; // h 01 parameter ONE= 7’b 100_1111; // h 4 f parameter TWO= 7’b 001_0010; // h 12 parameter THREE= 7’b 000_0110; // h 06 parameter FOUR= 7’b 100_1100; // h 4 c parameter FIVE= 7’b 010_0100; // h 24 parameter SIX= 7’b 010_0000; // h 20 parameter SEVEN= 7’b 000_1111; // h 0 f parameter EIGHT= 7’b 000_0000; // h 00 parameter NINE= 7’b 000_0100; // h 04 1 -58

Synthesis of Sequential Logic with Latches always @ (posedge clock) if (reset) count <= 0; else if (Enable) count <= count +1; always @ (count, Blanking) if (Blanking) begin Display_L=BLANK; DISPLAY_R=BLANK; end else case (count) 0: begin; Display_L=ZERO; DISPLAY_R=ZERO; end 2: begin; Display_L=ZERO; DISPLAY_R=TWO; end 4: begin; Display_L=ZERO; DISPLAY_R=FOUR; end 6: begin; Display_L=ZERO; DISPLAY_R=SIX; end 8: begin; Display_L=ZERO; DISPLAY_R=EIGHT; end 10: begin; Display_L=ONE; DISPLAY_R=ZERO; end 12: begin; Display_L=ONE; DISPLAY_R=TWO; end 14: begin; Display_L=ONE; DISPLAY_R=FOUR; endcase endmodule 1 -59

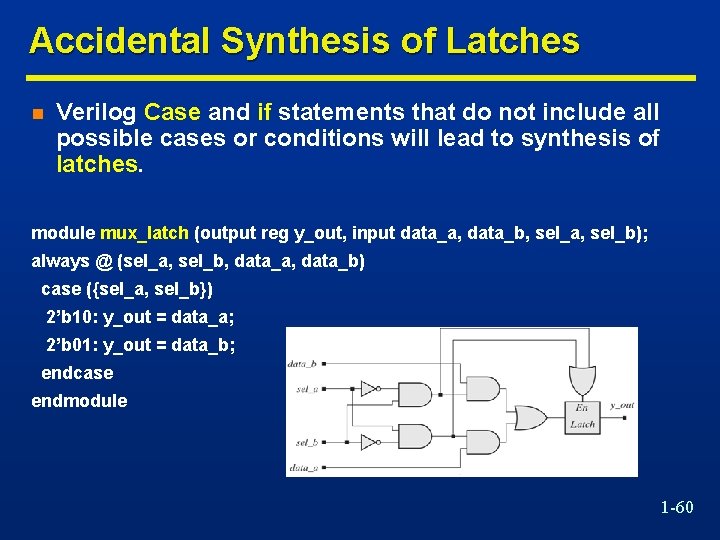

Accidental Synthesis of Latches n Verilog Case and if statements that do not include all possible cases or conditions will lead to synthesis of latches. module mux_latch (output reg y_out, input data_a, data_b, sel_a, sel_b); always @ (sel_a, sel_b, data_a, data_b) case ({sel_a, sel_b}) 2’b 10: y_out = data_a; 2’b 01: y_out = data_b; endcase endmodule 1 -60

Synthesis of Three-State Devices and Bus Interfaces n Three-state devices allow buses to be shared among multiple devices. n Preferred style for inferring a three-state bus driver uses a continuous assignment that has one branch set to z. module Uni_dir_bus (output [31: 0] data_to_bus, input bus_enable); reg [31: 0] ckt_to_bus; assign data_to_bus = (bus_enable) ? ckt_to_bus ? 32’bz; // description of core circuit goes here to drive ckt_to_bus endmodule 1 -61

![Synthesis of Three-State Devices and Bus Interfaces module Bi_dir_bus (inout [31: 0] data_to_from_bus, input Synthesis of Three-State Devices and Bus Interfaces module Bi_dir_bus (inout [31: 0] data_to_from_bus, input](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-62.jpg)

Synthesis of Three-State Devices and Bus Interfaces module Bi_dir_bus (inout [31: 0] data_to_from_bus, input send_data, rcv_data); wire [31: 0] ckt_to_bus; wire [31: 0] data_from_bus; assign data_from_bus = (rcv_data)? data_to_from_bus: 32’bz; assign data_to_from_bus = (send_data)? ckt_to_bus: 32’bz; // Behavior using data_from_bus and generating ckt_to_bus goes here endmodule 1 -62

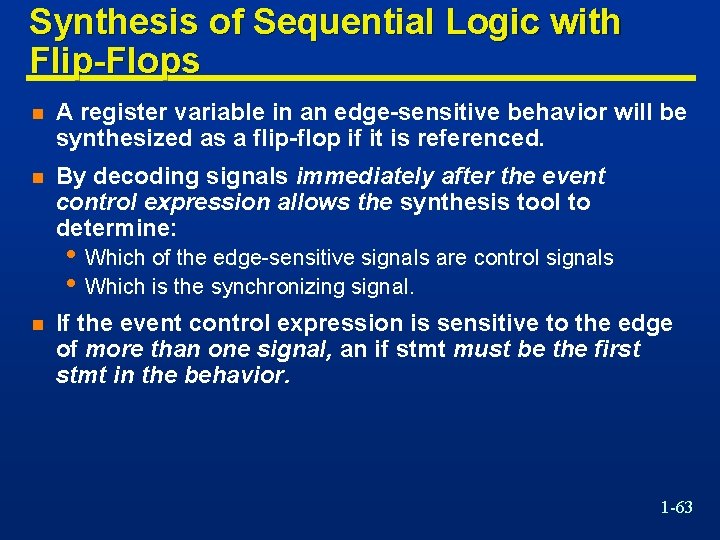

Synthesis of Sequential Logic with Flip-Flops n A register variable in an edge-sensitive behavior will be synthesized as a flip-flop if it is referenced. n By decoding signals immediately after the event control expression allows the synthesis tool to determine: • Which of the edge-sensitive signals are control signals • Which is the synchronizing signal. n If the event control expression is sensitive to the edge of more than one signal, an if stmt must be the first stmt in the behavior. 1 -63

Synthesis of Sequential Logic with Flip-Flops n The control signals must be decoded explicitly in the branches of the if stmt. n Decode the reset condition first. module swap_synth (output reg data_a, data_b, input set 1, set 2, clk); always @ (posedge clk) begin if (set 1) begin data_a<=1; data_b<=0; end else if (set 2) begin data_a<=0; data_b<=1; end else begin data_b <= data_a; data_a <= data_b; end endmodule 1 -64

![Synthesis of Sequential Logic with Flip-Flops module D_reg 4 (output reg [3: 0] Data_out, Synthesis of Sequential Logic with Flip-Flops module D_reg 4 (output reg [3: 0] Data_out,](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-65.jpg)

Synthesis of Sequential Logic with Flip-Flops module D_reg 4 (output reg [3: 0] Data_out, input [3: 0] Data_in, input clock, reset); always @ (posedge clock, posedge reset) begin if (reset == 1’b 1) Data_out <= 4’b 0; else Data_out <= Data_in; endmodule 1 -65

Synthesis of Sequential Logic with Flip-Flops n The behavior in empty_circuit assigns value to register variable D_out, but D_out is not referenced outside the scope of behavior. n Synthesis tool will eliminate D_out. module empty_circuit (input D_in, clk); reg D_out; always @ (posedge clk) begin D_out<= D_in; endmodule 1 -66

Synthesis of Explicit State Machine n Use two cyclic behaviors to describe an explicit state machine: • A level-sensitive behavior to describe the combinational logic • for the next state and outputs An edge-sensitive behavior to synchronize the state transitions n Use the blocking procedural assignment operator (=) in the level-sensitive cyclic behaviors describing the combinational logic of a FSM. n Use the nonblocking assignment operator (<=) in the edge-sensitive cyclic behavior describing the state transitions of a FSM and the register transfers of the datapath of the sequential machine. 1 -67

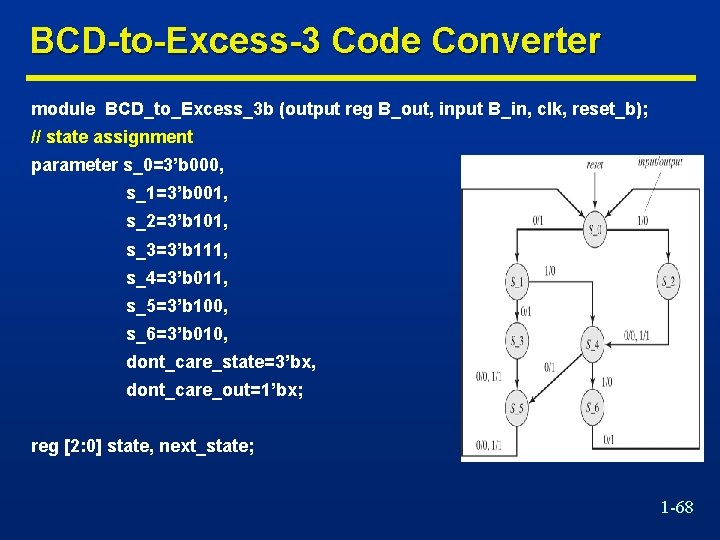

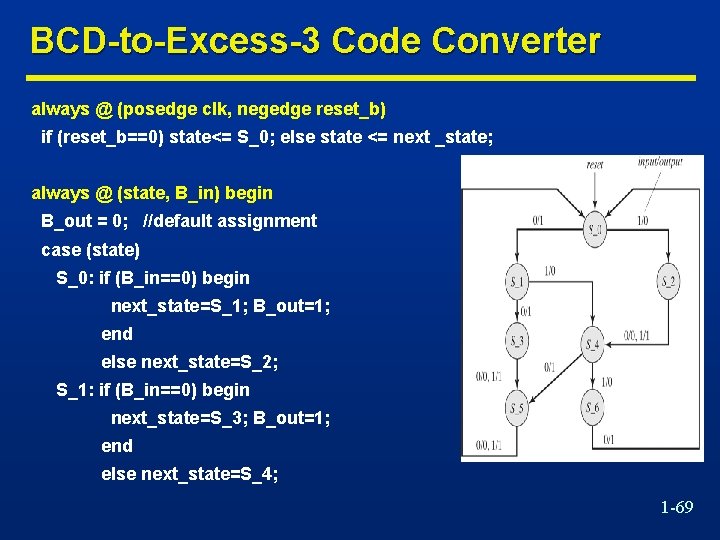

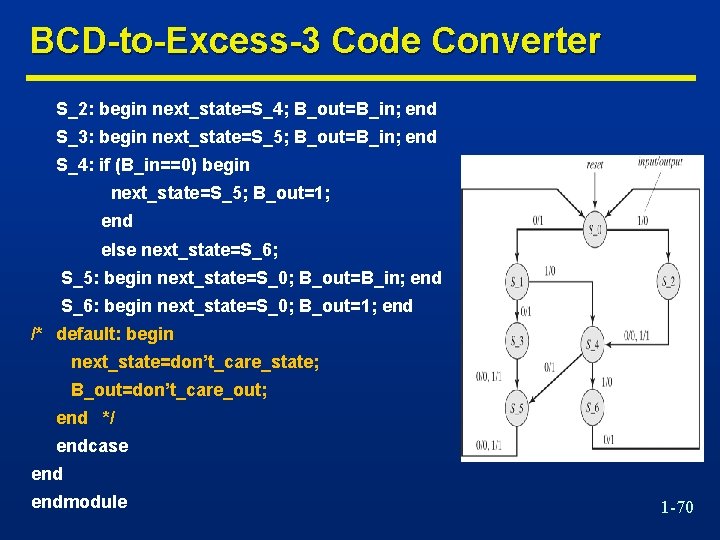

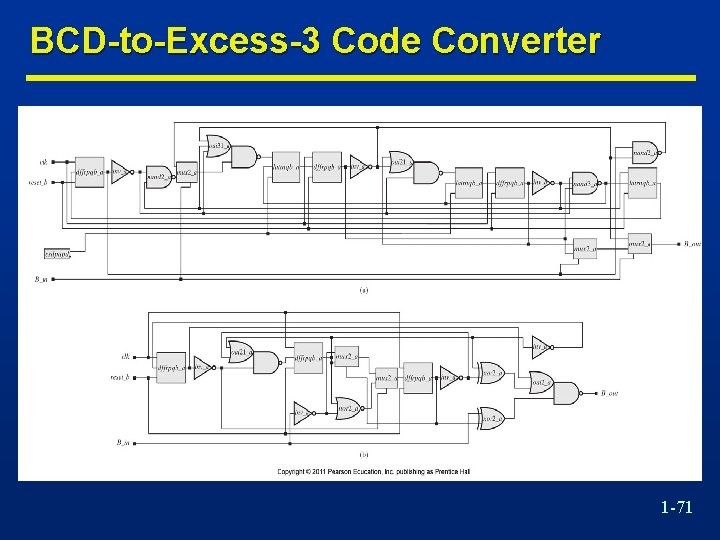

BCD-to-Excess-3 Code Converter module BCD_to_Excess_3 b (output reg B_out, input B_in, clk, reset_b); // state assignment parameter s_0=3’b 000, s_1=3’b 001, s_2=3’b 101, s_3=3’b 111, s_4=3’b 011, s_5=3’b 100, s_6=3’b 010, dont_care_state=3’bx, dont_care_out=1’bx; reg [2: 0] state, next_state; 1 -68

BCD-to-Excess-3 Code Converter always @ (posedge clk, negedge reset_b) if (reset_b==0) state<= S_0; else state <= next _state; always @ (state, B_in) begin B_out = 0; //default assignment case (state) S_0: if (B_in==0) begin next_state=S_1; B_out=1; end else next_state=S_2; S_1: if (B_in==0) begin next_state=S_3; B_out=1; end else next_state=S_4; 1 -69

BCD-to-Excess-3 Code Converter S_2: begin next_state=S_4; B_out=B_in; end S_3: begin next_state=S_5; B_out=B_in; end S_4: if (B_in==0) begin next_state=S_5; B_out=1; end else next_state=S_6; S_5: begin next_state=S_0; B_out=B_in; end S_6: begin next_state=S_0; B_out=1; end /* default: begin next_state=don’t_care_state; B_out=don’t_care_out; end */ endcase endmodule 1 -70

BCD-to-Excess-3 Code Converter 1 -71

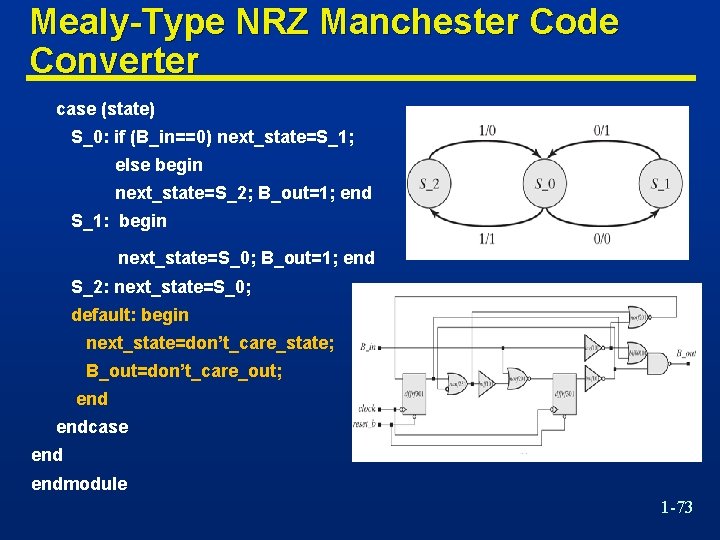

Mealy-Type NRZ Manchester Code Converter module NRZ_2_Manchester_Mealy (output reg B_out, input B_in, clock, reset_b); reg [1: 0] state, next_state; parameter s_0=2’d 0, s_1=2’d 1, s_2=2’d 2, dont_care_state=3’bx, dont_care_out=1’bx; always @ (posedge clk, negedge reset_b) if (reset_b==0) state<= S_0; else state <= next _state; always @ (state, B_in) begin B_out = 0; //default assignment 1 -72

Mealy-Type NRZ Manchester Code Converter case (state) S_0: if (B_in==0) next_state=S_1; else begin next_state=S_2; B_out=1; end S_1: begin next_state=S_0; B_out=1; end S_2: next_state=S_0; default: begin next_state=don’t_care_state; B_out=don’t_care_out; endcase endmodule 1 -73

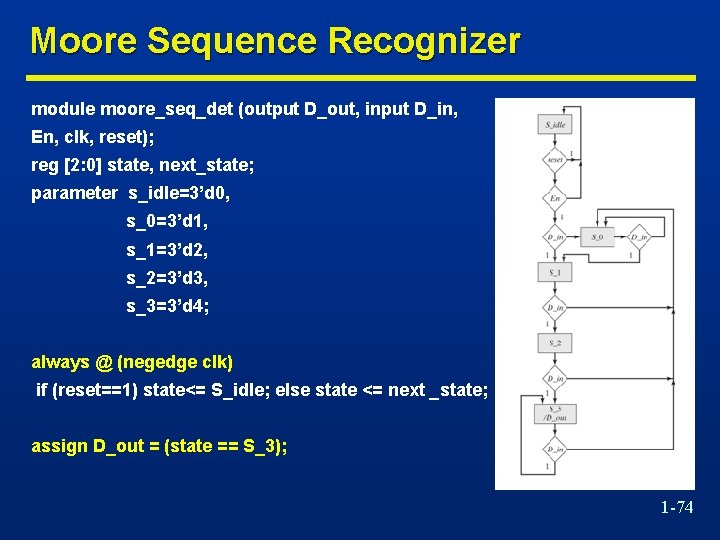

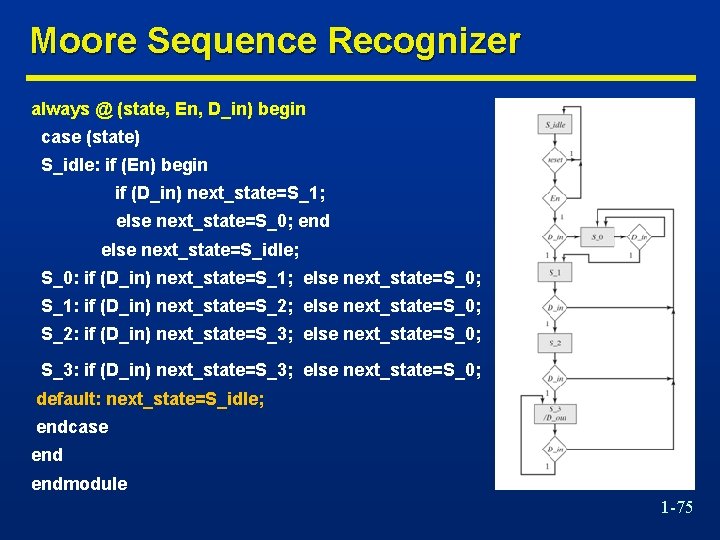

Moore Sequence Recognizer module moore_seq_det (output D_out, input D_in, En, clk, reset); reg [2: 0] state, next_state; parameter s_idle=3’d 0, s_0=3’d 1, s_1=3’d 2, s_2=3’d 3, s_3=3’d 4; always @ (negedge clk) if (reset==1) state<= S_idle; else state <= next _state; assign D_out = (state == S_3); 1 -74

Moore Sequence Recognizer always @ (state, En, D_in) begin case (state) S_idle: if (En) begin if (D_in) next_state=S_1; else next_state=S_0; end else next_state=S_idle; S_0: if (D_in) next_state=S_1; else next_state=S_0; S_1: if (D_in) next_state=S_2; else next_state=S_0; S_2: if (D_in) next_state=S_3; else next_state=S_0; S_3: if (D_in) next_state=S_3; else next_state=S_0; default: next_state=S_idle; endcase endmodule 1 -75

![Synthesis of Accumulator module Add_Accum_1 ( output reg [3: 0] accum, output reg overflow, Synthesis of Accumulator module Add_Accum_1 ( output reg [3: 0] accum, output reg overflow,](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-76.jpg)

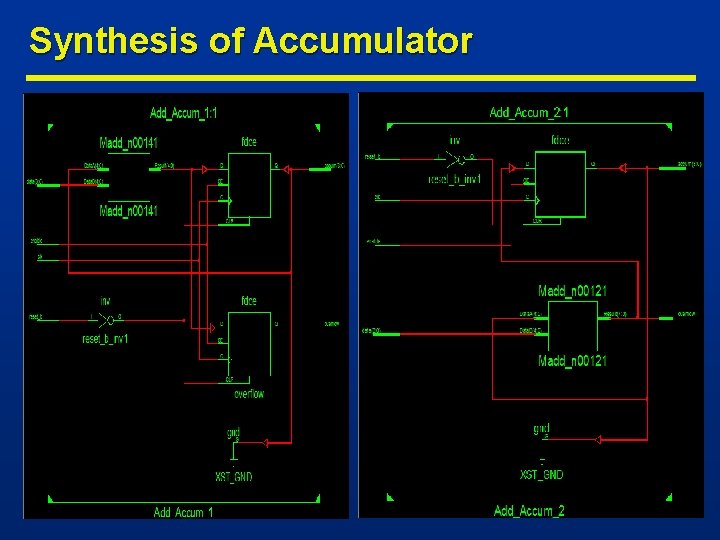

Synthesis of Accumulator module Add_Accum_1 ( output reg [3: 0] accum, output reg overflow, input [3: 0] data, input enable, clk, reset_b); always @ (posedge clk, negedge reset_b) if (reset_b==0) begin accum<=0; overflow<=0; end else if (enable) {overflow, accum} <= accum + data; endmodule Add_Accum_2 ( output reg [3: 0] accum, output overflow, input [3: 0] data, input enable, clk, reset_b); wire [3: 0] sum; assign {overflow, sum} = accum + data; always @ (posedge clk, negedge reset_b) if (reset_b==0) accum<=0; else if (enable) accum <= sum; endmodule 1 -76

Synthesis of Accumulator 1 -77

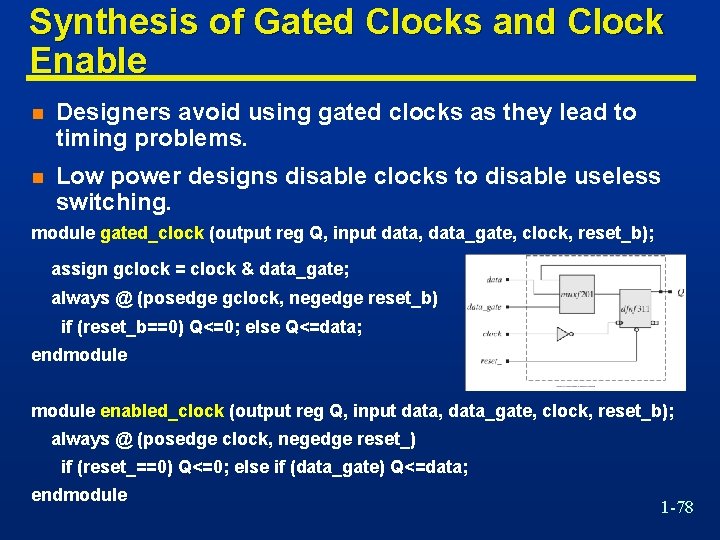

Synthesis of Gated Clocks and Clock Enable n Designers avoid using gated clocks as they lead to timing problems. n Low power designs disable clocks to disable useless switching. module gated_clock (output reg Q, input data, data_gate, clock, reset_b); assign gclock = clock & data_gate; always @ (posedge gclock, negedge reset_b) if (reset_b==0) Q<=0; else Q<=data; endmodule enabled_clock (output reg Q, input data, data_gate, clock, reset_b); always @ (posedge clock, negedge reset_) if (reset_==0) Q<=0; else if (data_gate) Q<=data; endmodule 1 -78

Operator Grouping n Use parenthesis to form sub-expressions to influence outcome of synthesis. module operator_group (output [4: 0] sum 1, sum 2, input [4: 0] a, b, c, d); assign sum 1 = a + b + c + d; assign sum 2 = (a + b) + (c + d); endmodule 1 -79

![Expression Substitution module multiple_reg_assign ( output reg [4: 0] data_out 1, data_out 2, input Expression Substitution module multiple_reg_assign ( output reg [4: 0] data_out 1, data_out 2, input](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-80.jpg)

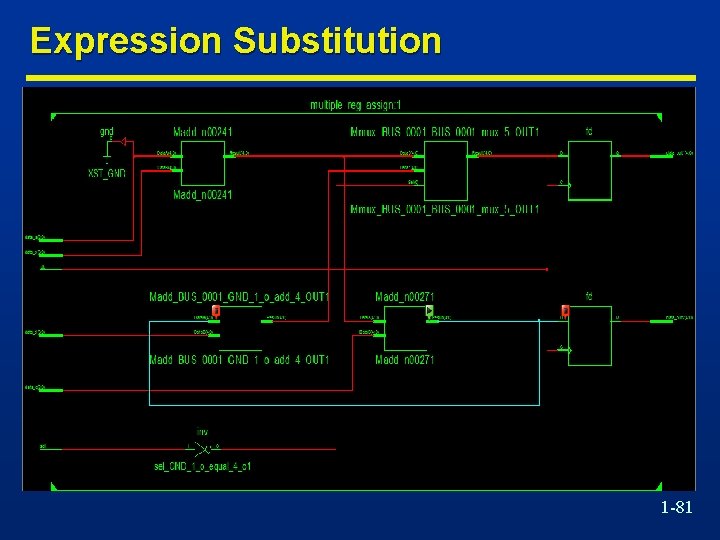

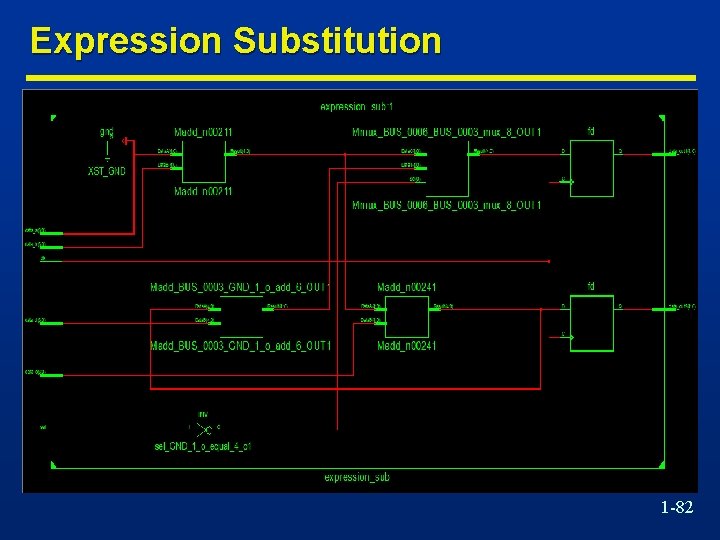

Expression Substitution module multiple_reg_assign ( output reg [4: 0] data_out 1, data_out 2, input [3: 0] data_a, data_b, data_c, data_d, input sel, clk); always @ (posedge clk) begin data_out 1 = data_a + data_b; data_out 2 = data_out 1+ data_c; if (sel==1’b 0) data_out 1 = data_out 2 + data_d; endmodule expression_sub ( output reg [4: 0] data_out 1, data_out 2, input [3: 0] data_a, data_b, data_c, data_d, input sel, clk); always @ (posedge clk) begin data_out 2 = data_a + data_b + data_c; if (sel==1’b 0) data_out 1 = data_a + data_b + data_c+ data_d; else data_out 1 = data_a + data_b; endmodule 1 -80

Expression Substitution 1 -81

Expression Substitution 1 -82

![Expression Substitution module expression_sub_nb ( output reg [4: 0] data_out 1, data_out 2, input Expression Substitution module expression_sub_nb ( output reg [4: 0] data_out 1, data_out 2, input](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-83.jpg)

Expression Substitution module expression_sub_nb ( output reg [4: 0] data_out 1, data_out 2, input [3: 0] data_a, data_b, data_c, data_d, input sel, clk); always @ (posedge clk) begin data_out 2 <= data_a + data_b + data_c; if (sel==1’b 0) data_out 1 <= data_a + data_b + data_c+ data_d; else data_out 1 <= data_a + data_b; endmodule multiple_reg_assign_nb ( output reg [4: 0] data_out 1, data_out 2, input [3: 0] data_a, data_b, data_c, data_d, input sel, clk); always @ (posedge clk) begin data_out 1 <= data_a + data_b; data_out 2 <= data_out 1+ data_c; if (sel==1’b 0) data_out 1 <= data_out 2 + data_d; endmodule 1 -83

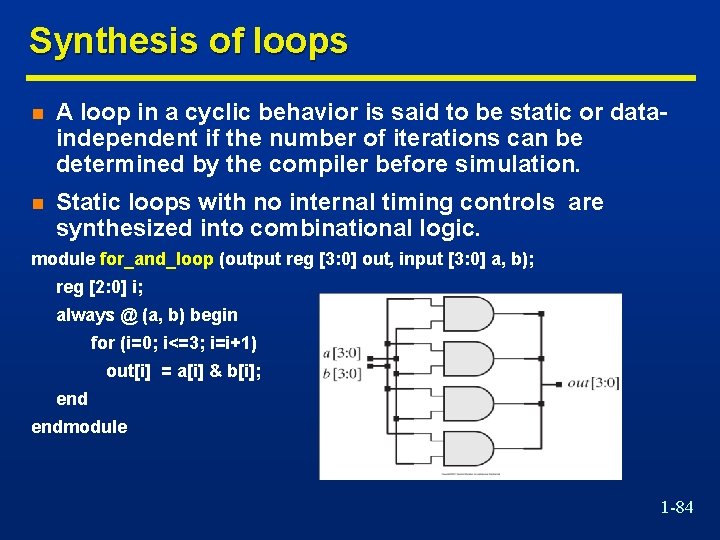

Synthesis of loops n A loop in a cyclic behavior is said to be static or dataindependent if the number of iterations can be determined by the compiler before simulation. n Static loops with no internal timing controls are synthesized into combinational logic. module for_and_loop (output reg [3: 0] out, input [3: 0] a, b); reg [2: 0] i; always @ (a, b) begin for (i=0; i<=3; i=i+1) out[i] = a[i] & b[i]; endmodule 1 -84

![Synthesis of loops module count_ones # (parameter data_width=4, count_width=3)(output reg [count_width-1: 0] bit_count, input Synthesis of loops module count_ones # (parameter data_width=4, count_width=3)(output reg [count_width-1: 0] bit_count, input](http://slidetodoc.com/presentation_image_h/999ab0b7b129a4662d3c1e4bcb1e4d92/image-85.jpg)

Synthesis of loops module count_ones # (parameter data_width=4, count_width=3)(output reg [count_width-1: 0] bit_count, input [data_width-1: 0] data, input clk, reset); reg [count_width-1: 0] index; reg [data_width-1: 0] temp; always @ (posedge clk) if (reset) bit_count=0; else begin bit_count = 0; temp = data; for (index=0; index<data_width; index=index+1) begin bit_count = bit_count + temp[0]; temp = temp >> 1; end endmodule 1 -85

- Slides: 85