Sequential logic circuits CS 3402 Digital Logic Sequential

- Slides: 34

Sequential logic circuits CS 3402 --Digital Logic Sequential logic circuits

Outline • Sequential Circuit Models – Asynchronous – Synchronous • Latches • Flip-Flops CS 3402 --Digital Logic Sequential logic circuits 2

Sequential logic circuits • The main characteristic of combinational logic circuits is that their output values depend on their present input values. • Sequential logic circuits differ from combinational logic circuits because they contain memory elements so that their output values depend on both present and past input values CS 3402 --Digital Logic Sequential logic circuits 3

Sequential logic circuits Sequential circuits can be Asynchronous or synchronous. Asynchronous sequential circuits change their states and output values whenever a change in input values occurs. Synchronous sequential circuits change their states and output values at fixed points of time, i. e. clock signals. CS 3402 --Digital Logic Sequential logic circuits 4

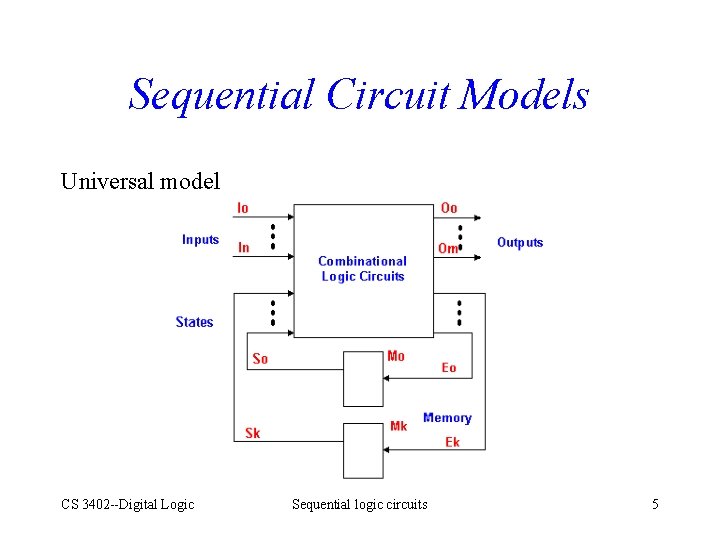

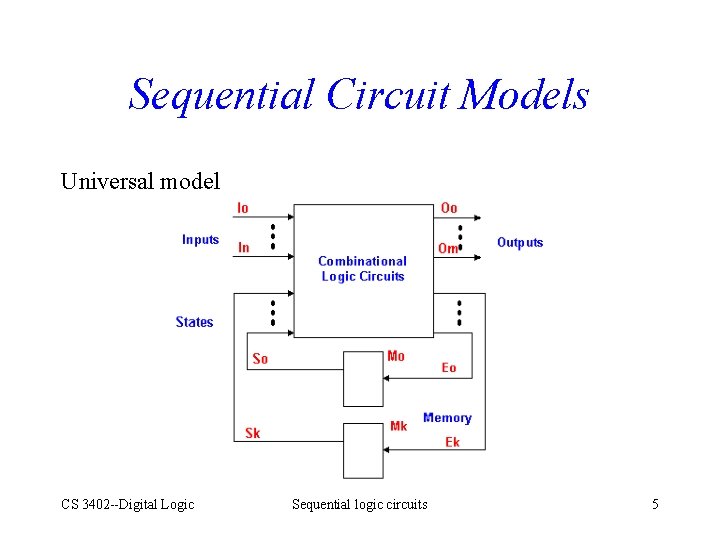

Sequential Circuit Models Universal model CS 3402 --Digital Logic Sequential logic circuits 5

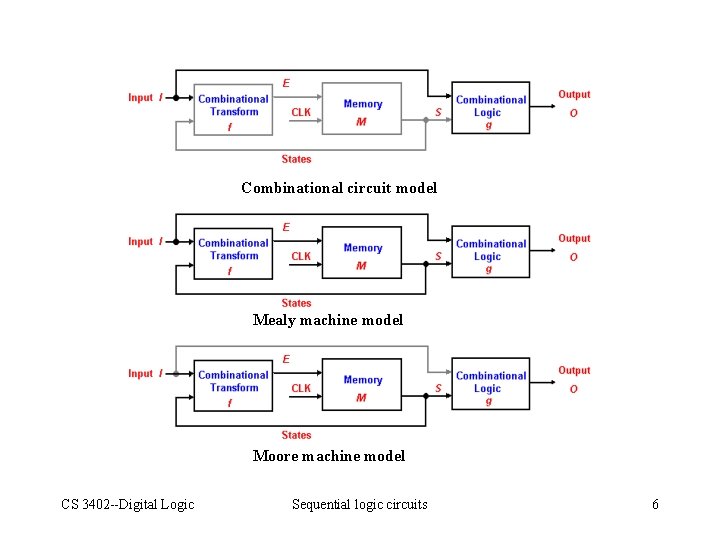

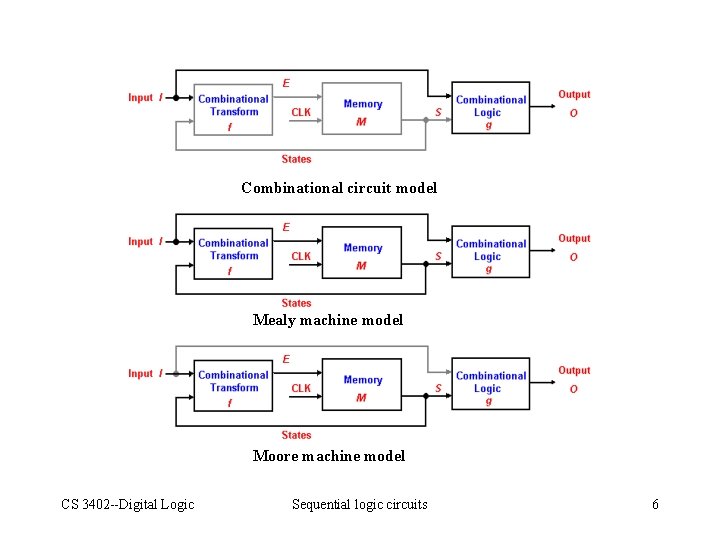

Combinational circuit model Mealy machine model Moore machine model CS 3402 --Digital Logic Sequential logic circuits 6

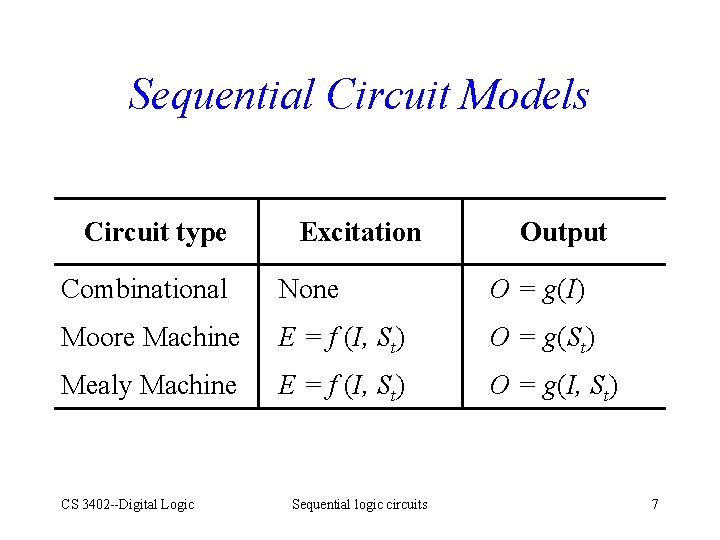

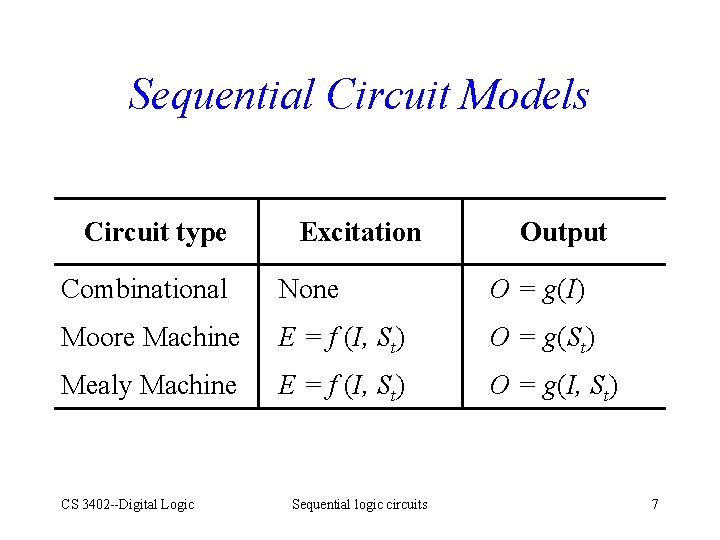

Sequential Circuit Models Circuit type Excitation Output Combinational None O = g(I) Moore Machine E = f (I, St) O = g(St) Mealy Machine E = f (I, St) O = g(I, St) CS 3402 --Digital Logic Sequential logic circuits 7

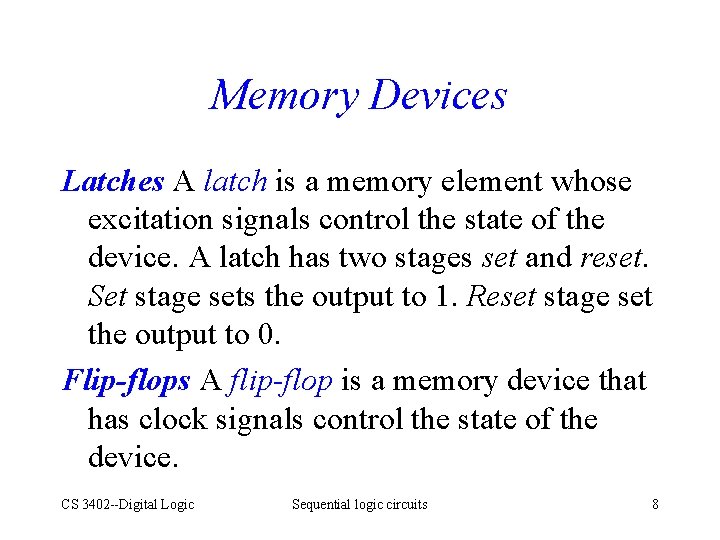

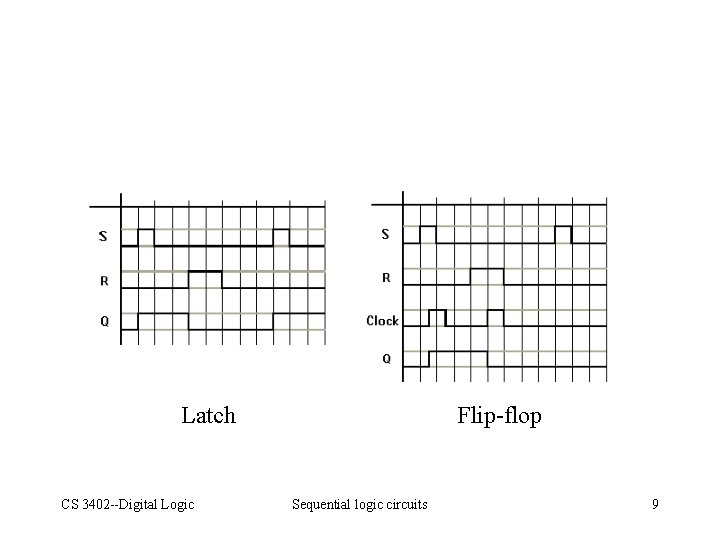

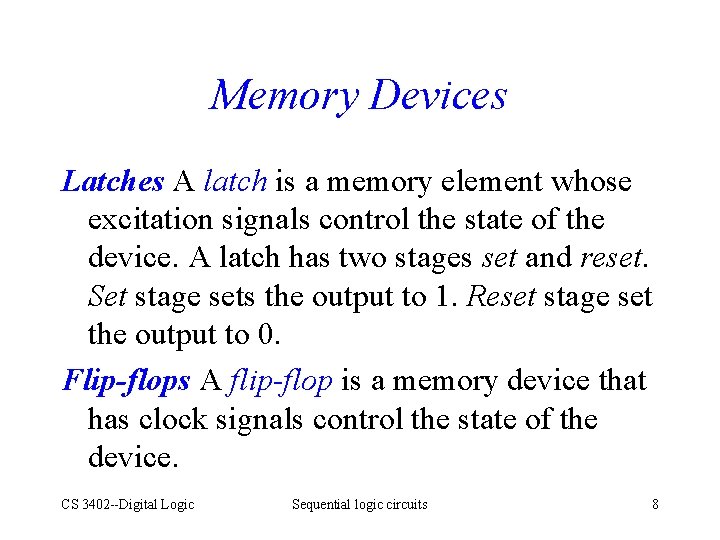

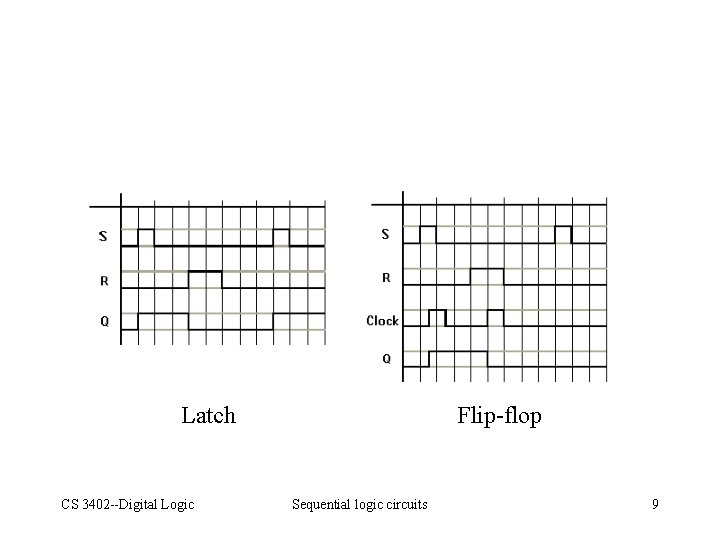

Memory Devices Latches A latch is a memory element whose excitation signals control the state of the device. A latch has two stages set and reset. Set stage sets the output to 1. Reset stage set the output to 0. Flip-flops A flip-flop is a memory device that has clock signals control the state of the device. CS 3402 --Digital Logic Sequential logic circuits 8

Latch CS 3402 --Digital Logic Flip-flop Sequential logic circuits 9

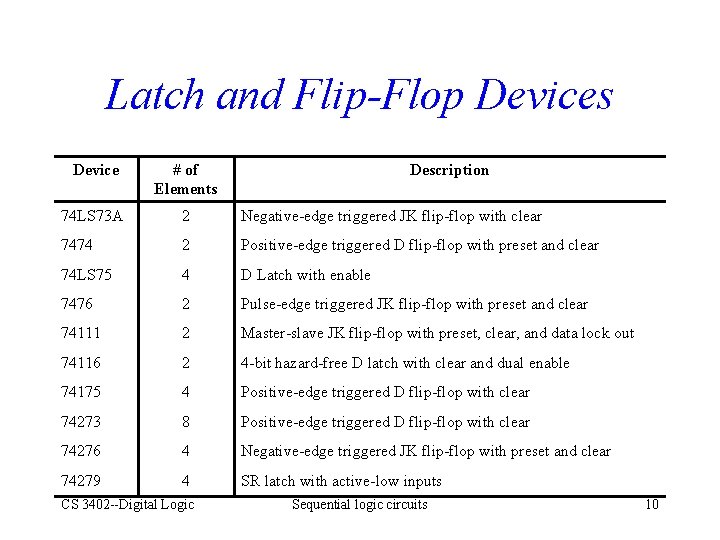

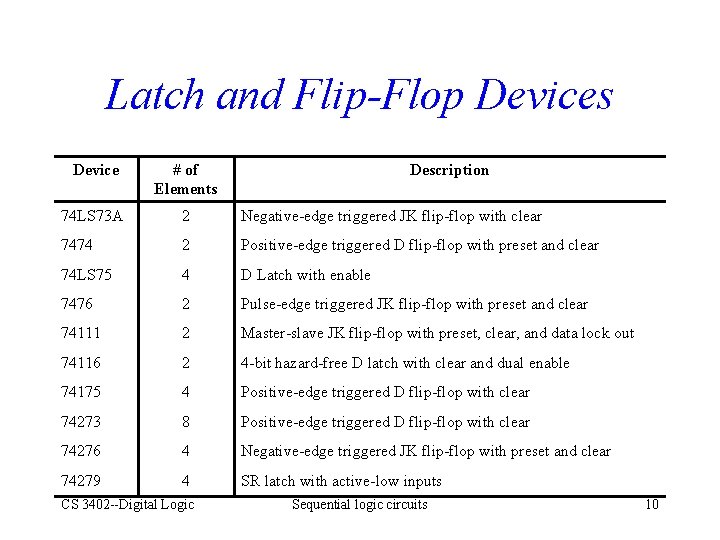

Latch and Flip-Flop Devices Device # of Elements 74 LS 73 A 2 Negative-edge triggered JK flip-flop with clear 7474 2 Positive-edge triggered D flip-flop with preset and clear 74 LS 75 4 D Latch with enable 7476 2 Pulse-edge triggered JK flip-flop with preset and clear 74111 2 Master-slave JK flip-flop with preset, clear, and data lock out 74116 2 4 -bit hazard-free D latch with clear and dual enable 74175 4 Positive-edge triggered D flip-flop with clear 74273 8 Positive-edge triggered D flip-flop with clear 74276 4 Negative-edge triggered JK flip-flop with preset and clear 74279 4 SR latch with active-low inputs CS 3402 --Digital Logic Description Sequential logic circuits 10

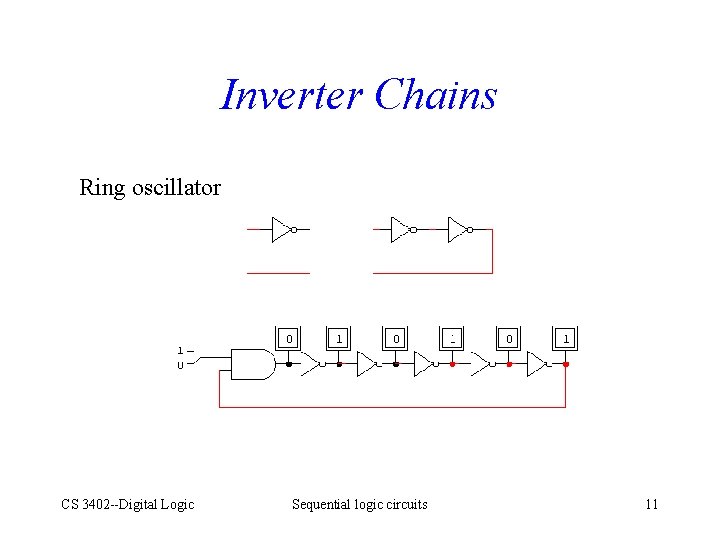

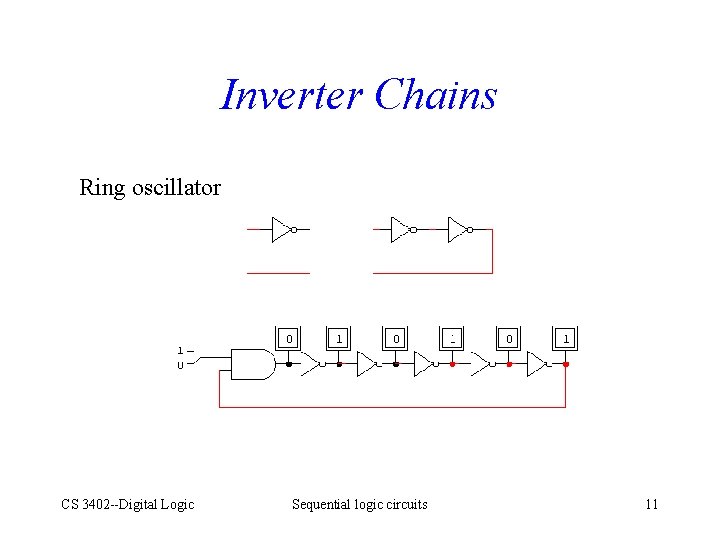

Inverter Chains Ring oscillator CS 3402 --Digital Logic Sequential logic circuits 11

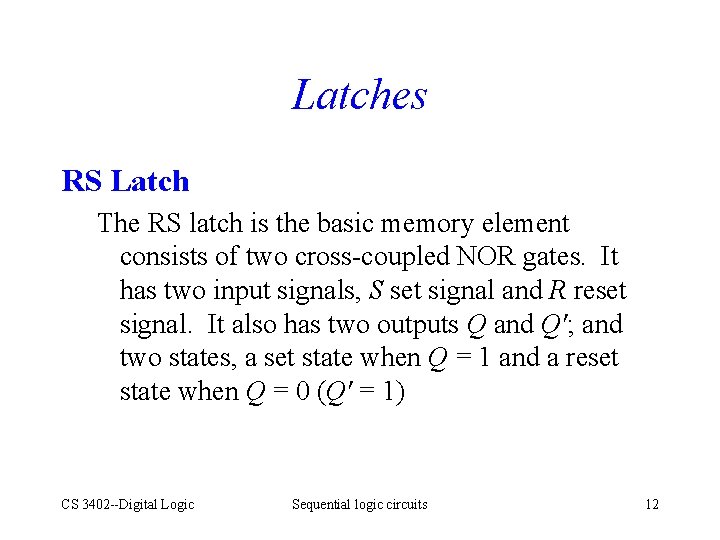

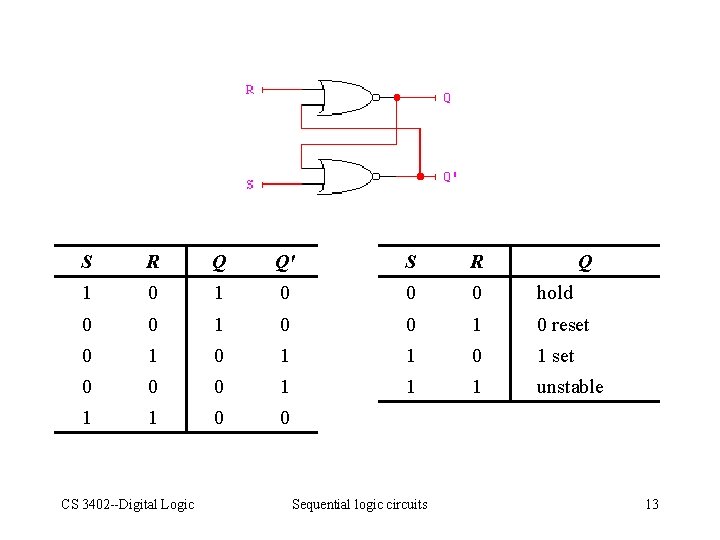

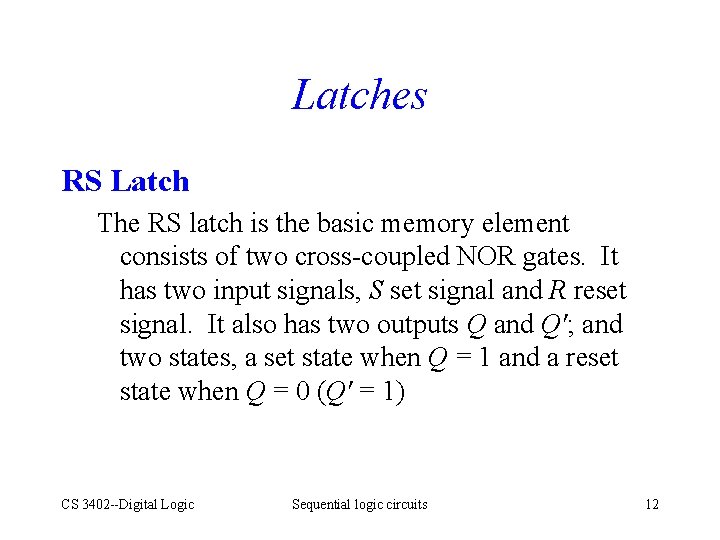

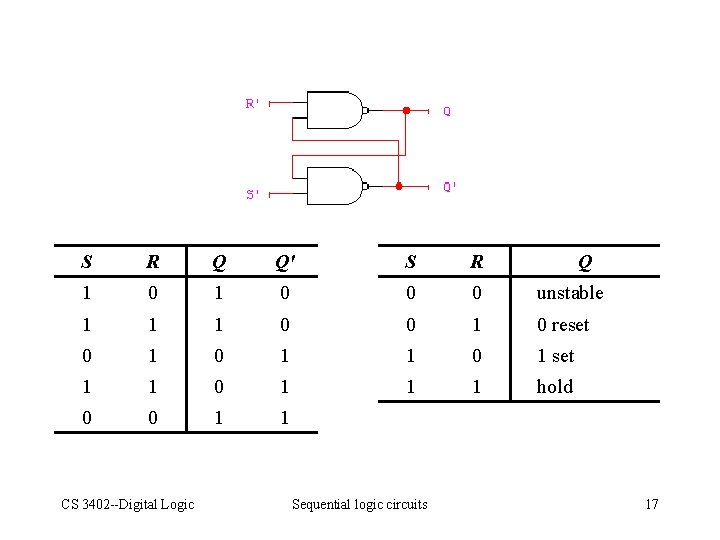

Latches RS Latch The RS latch is the basic memory element consists of two cross-coupled NOR gates. It has two input signals, S set signal and R reset signal. It also has two outputs Q and Q'; and two states, a set state when Q = 1 and a reset state when Q = 0 (Q' = 1) CS 3402 --Digital Logic Sequential logic circuits 12

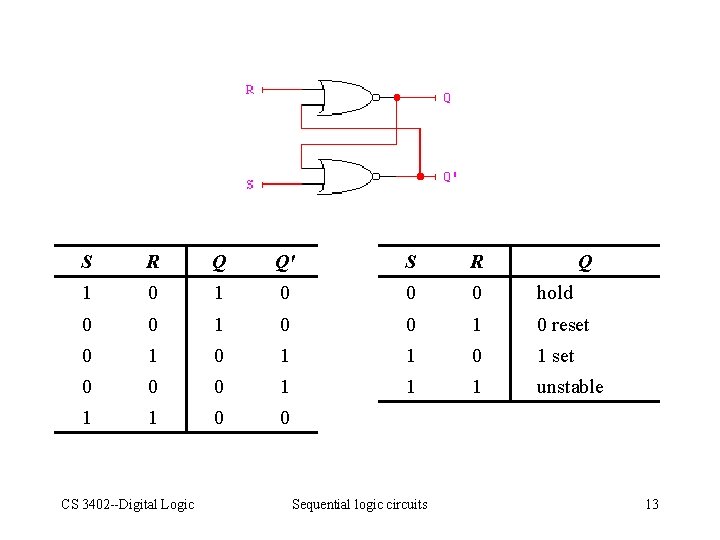

S R Q Q' S R 1 0 0 0 hold 0 0 1 0 reset 0 1 1 0 1 set 0 0 0 1 1 1 unstable 1 1 0 0 CS 3402 --Digital Logic Sequential logic circuits Q 13

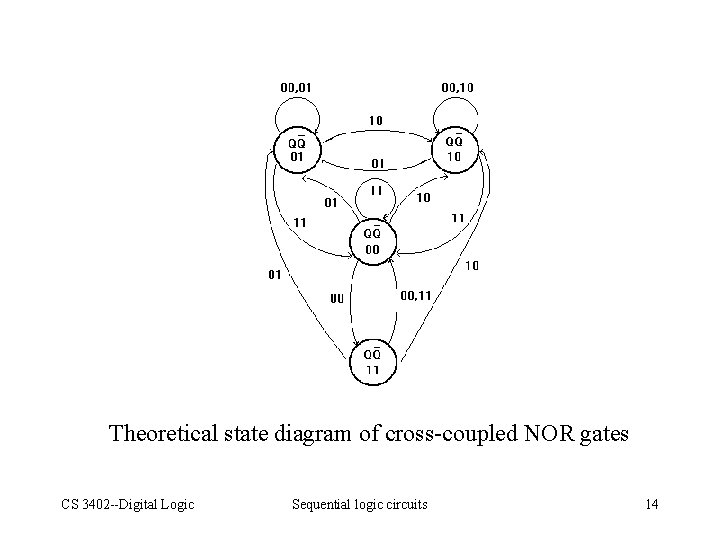

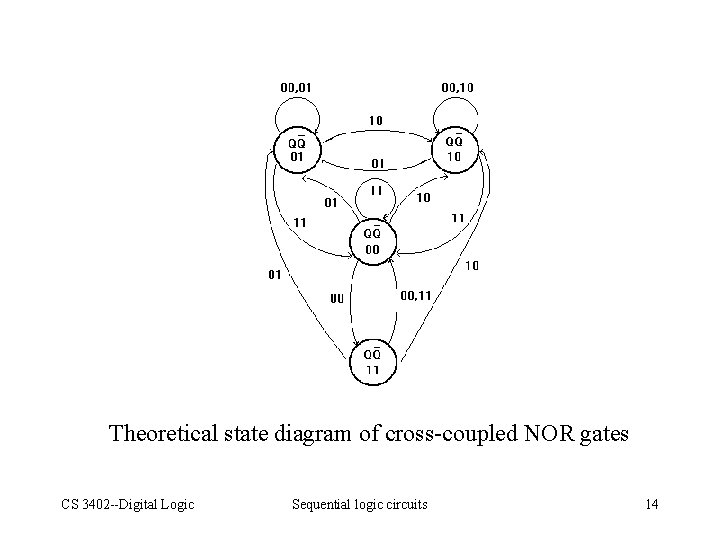

Theoretical state diagram of cross-coupled NOR gates CS 3402 --Digital Logic Sequential logic circuits 14

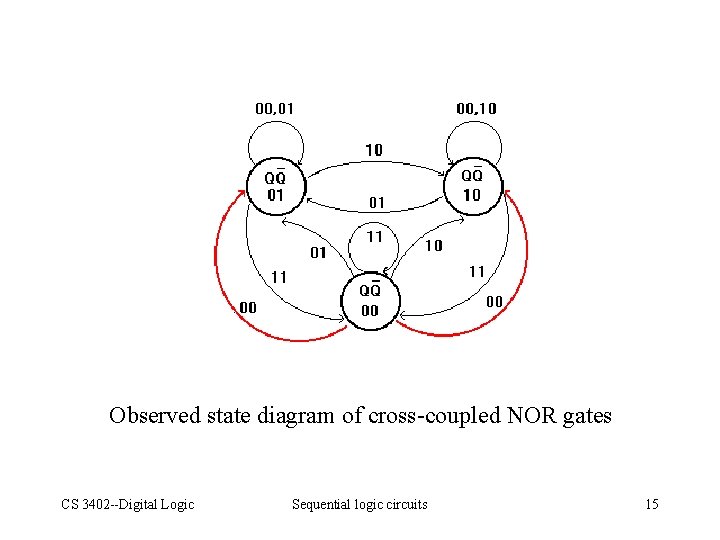

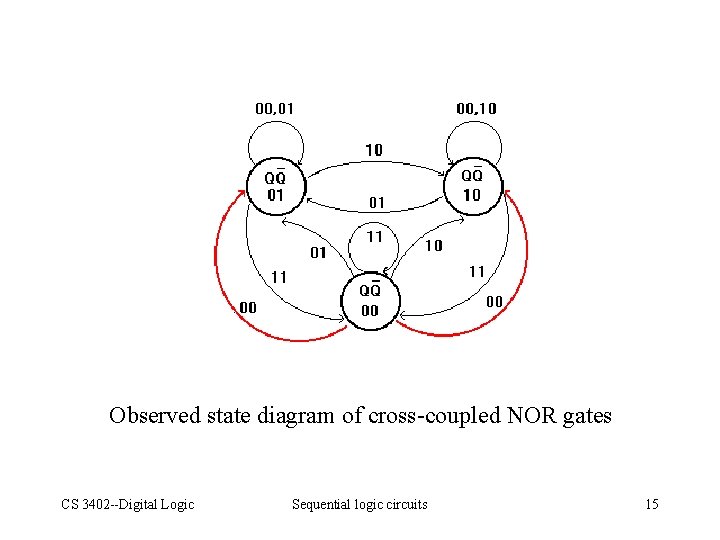

Observed state diagram of cross-coupled NOR gates CS 3402 --Digital Logic Sequential logic circuits 15

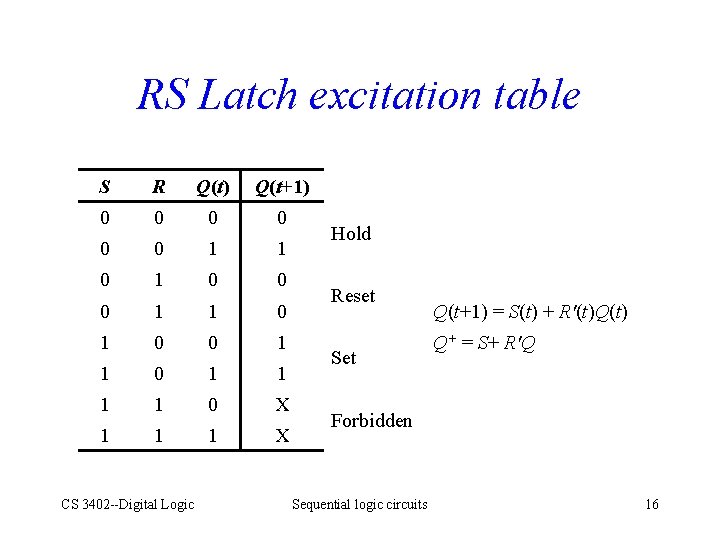

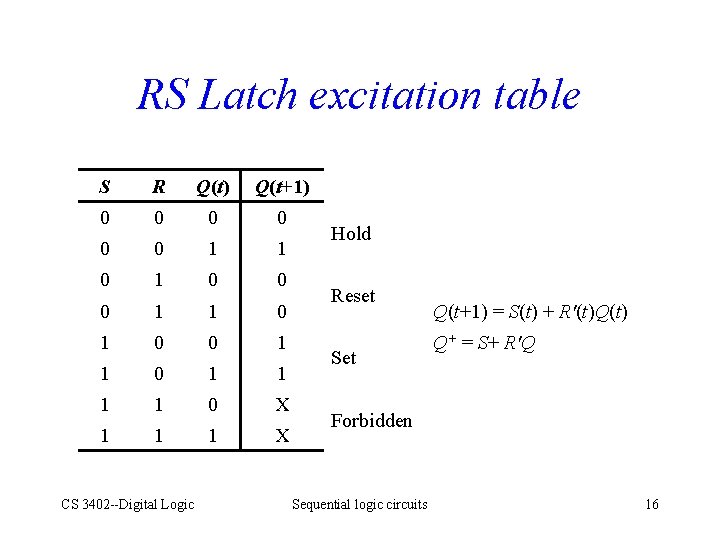

RS Latch excitation table S R Q(t) Q(t+1) 0 0 0 1 1 0 1 1 1 1 0 X 1 1 1 X CS 3402 --Digital Logic Hold Reset Set Q(t+1) = S(t) + R'(t)Q(t) Q+ = S+ R'Q Forbidden Sequential logic circuits 16

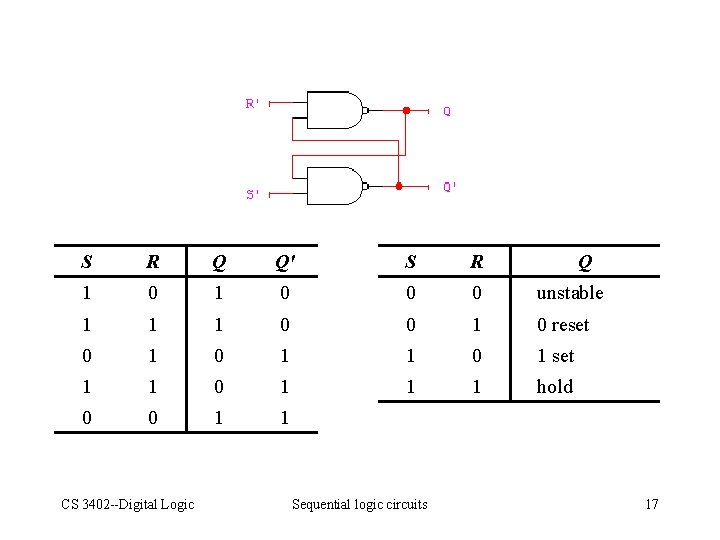

S R Q Q' S R 1 0 0 0 unstable 1 1 1 0 0 1 0 reset 0 1 1 0 1 set 1 1 0 1 1 1 hold 0 0 1 1 CS 3402 --Digital Logic Sequential logic circuits Q 17

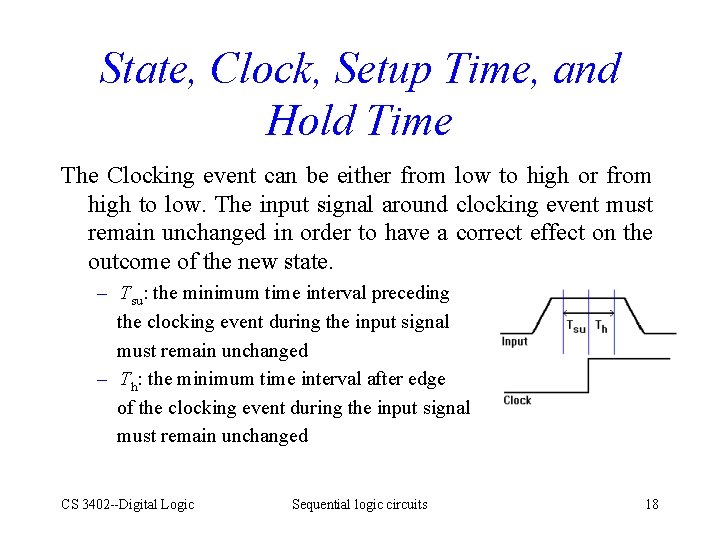

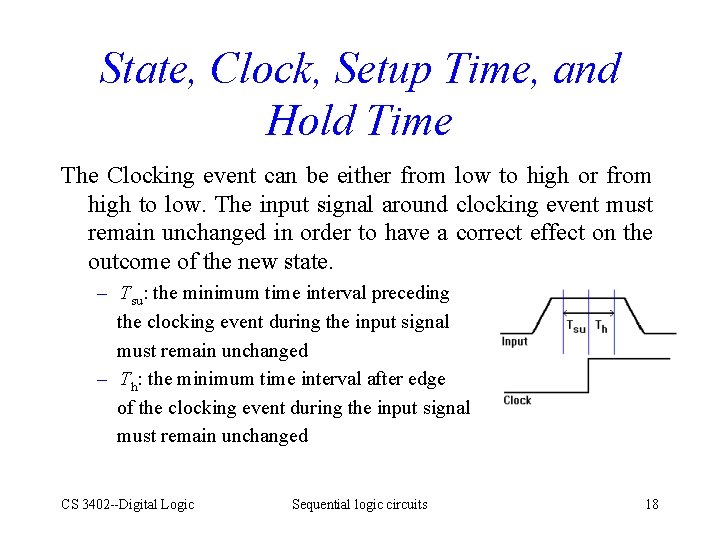

State, Clock, Setup Time, and Hold Time The Clocking event can be either from low to high or from high to low. The input signal around clocking event must remain unchanged in order to have a correct effect on the outcome of the new state. – Tsu: the minimum time interval preceding the clocking event during the input signal must remain unchanged – Th: the minimum time interval after edge of the clocking event during the input signal must remain unchanged CS 3402 --Digital Logic Sequential logic circuits 18

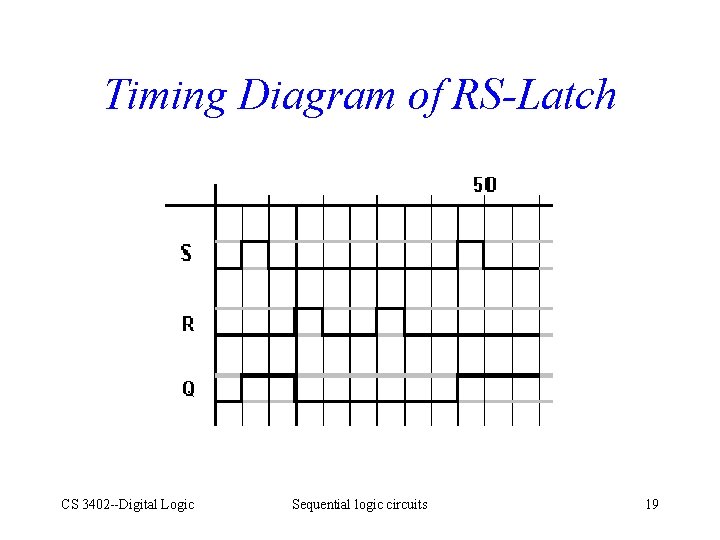

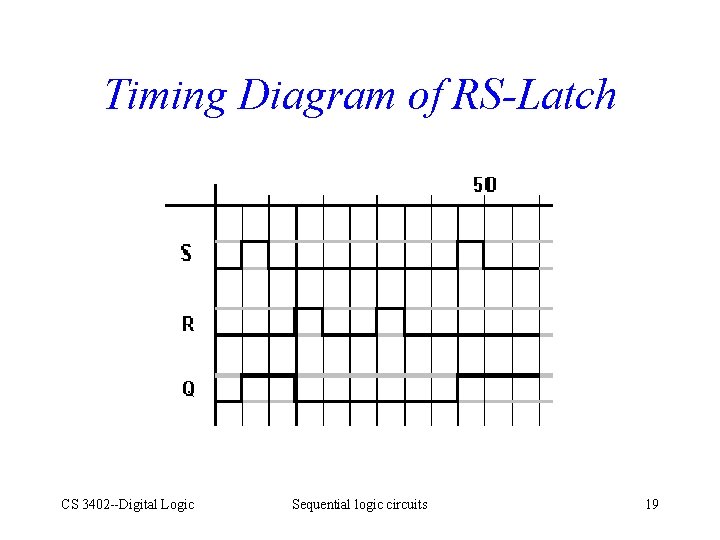

Timing Diagram of RS-Latch CS 3402 --Digital Logic Sequential logic circuits 19

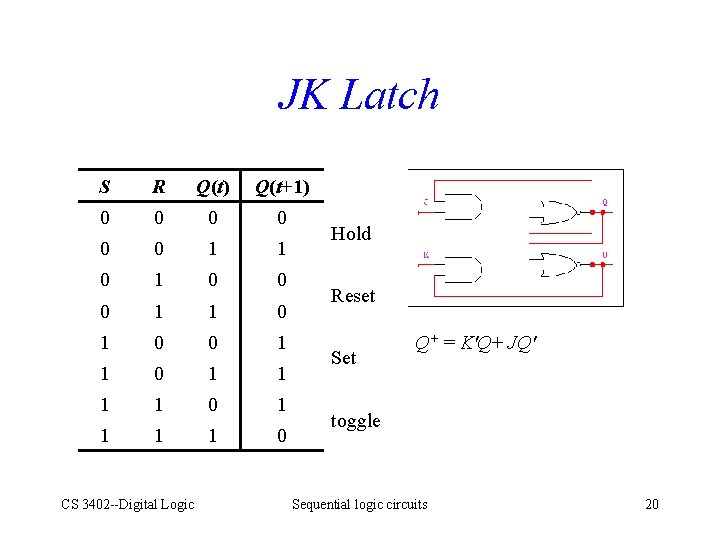

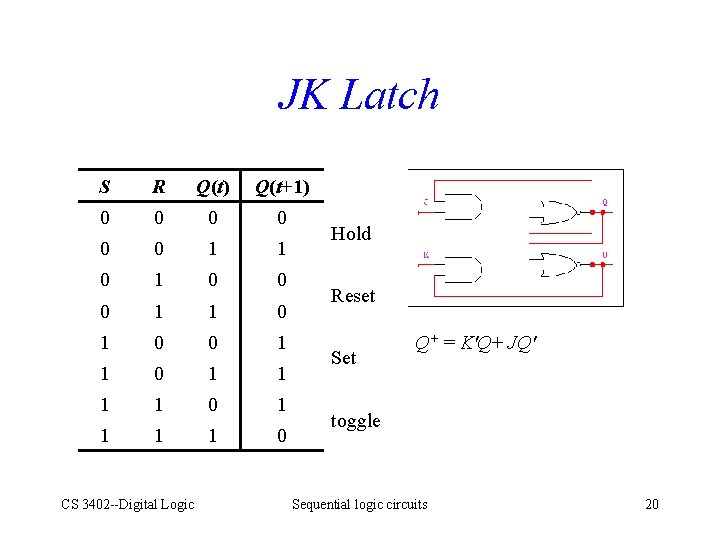

JK Latch S R Q(t) Q(t+1) 0 0 0 1 1 0 1 1 1 1 0 CS 3402 --Digital Logic Hold Reset Set Q+ = K'Q+ JQ' toggle Sequential logic circuits 20

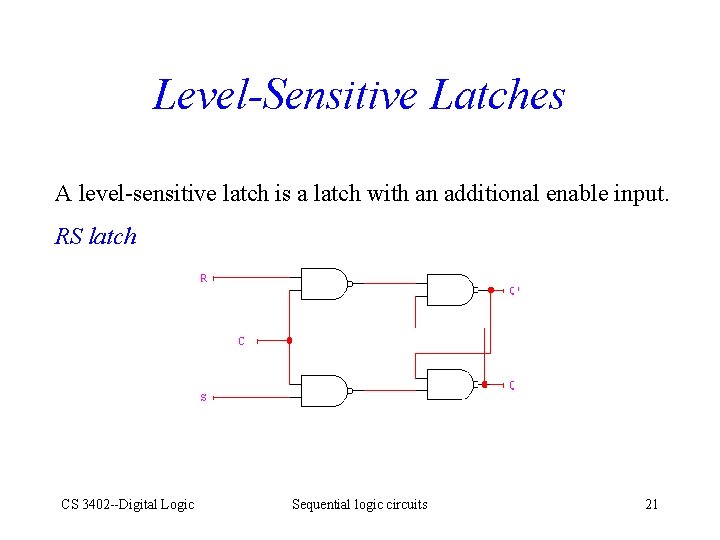

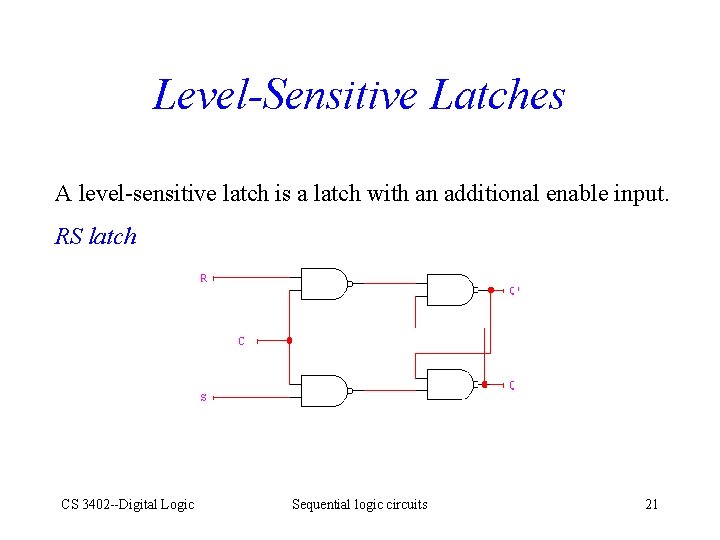

Level-Sensitive Latches A level-sensitive latch is a latch with an additional enable input. RS latch CS 3402 --Digital Logic Sequential logic circuits 21

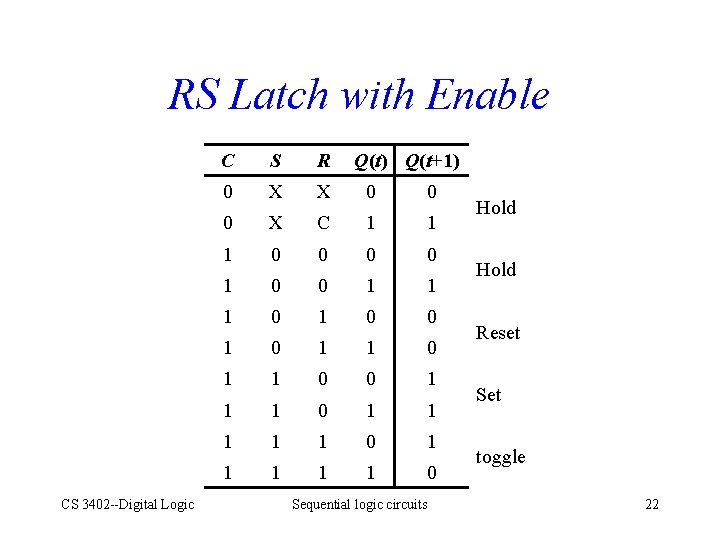

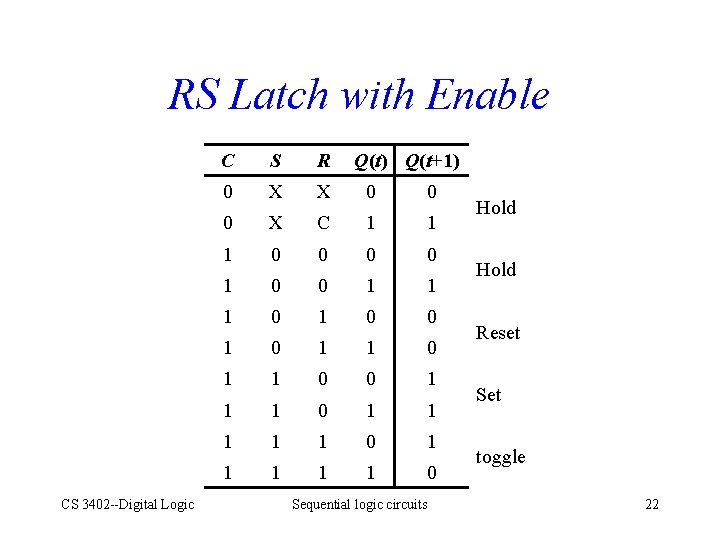

RS Latch with Enable CS 3402 --Digital Logic C S R Q(t) Q(t+1) 0 X X 0 0 0 X C 1 1 1 0 0 1 1 1 0 0 1 1 0 0 1 1 1 1 1 0 Sequential logic circuits Hold Reset Set toggle 22

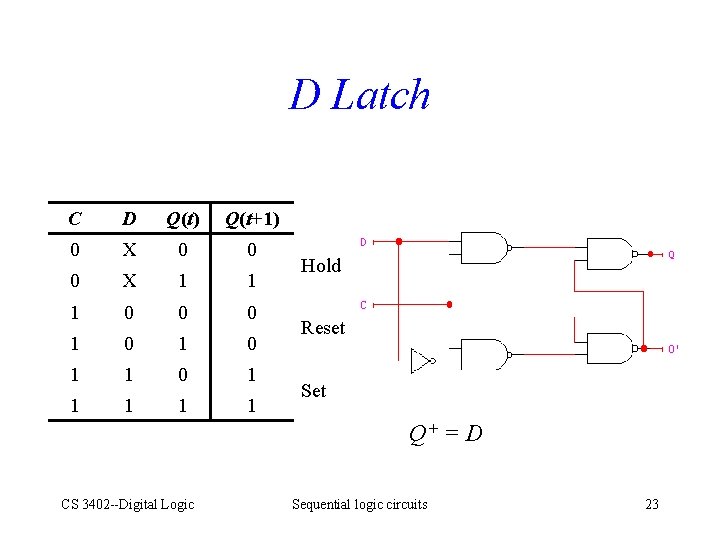

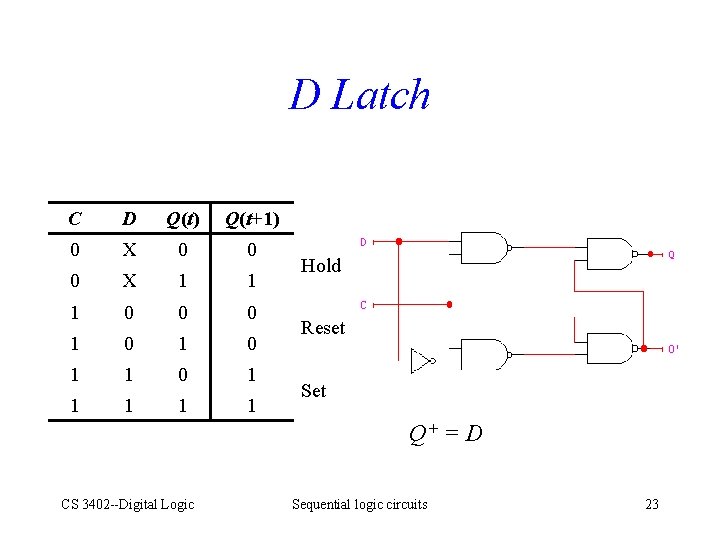

D Latch C D Q(t) Q(t+1) 0 X 0 0 0 X 1 1 1 0 0 0 1 0 1 1 1 1 1 Hold Reset Set Q+ = D CS 3402 --Digital Logic Sequential logic circuits 23

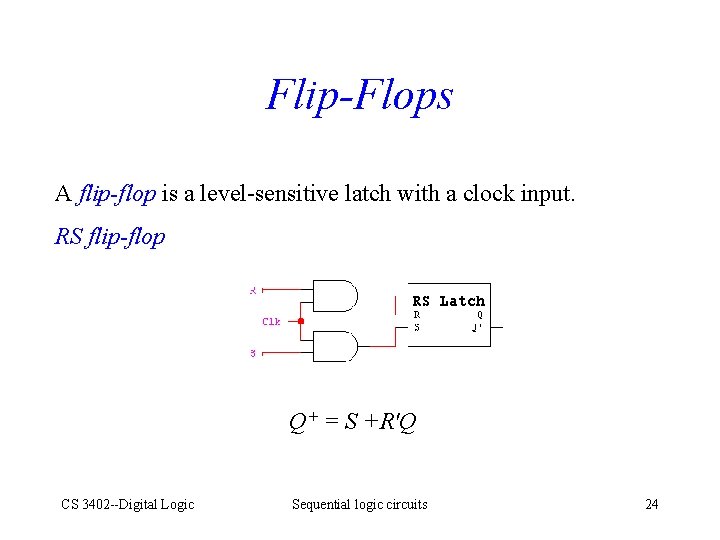

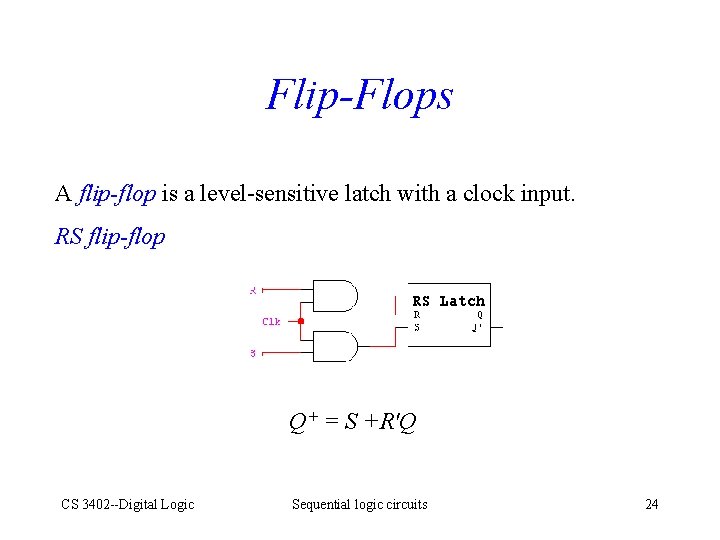

Flip-Flops A flip-flop is a level-sensitive latch with a clock input. RS flip-flop Q+ = S +R'Q CS 3402 --Digital Logic Sequential logic circuits 24

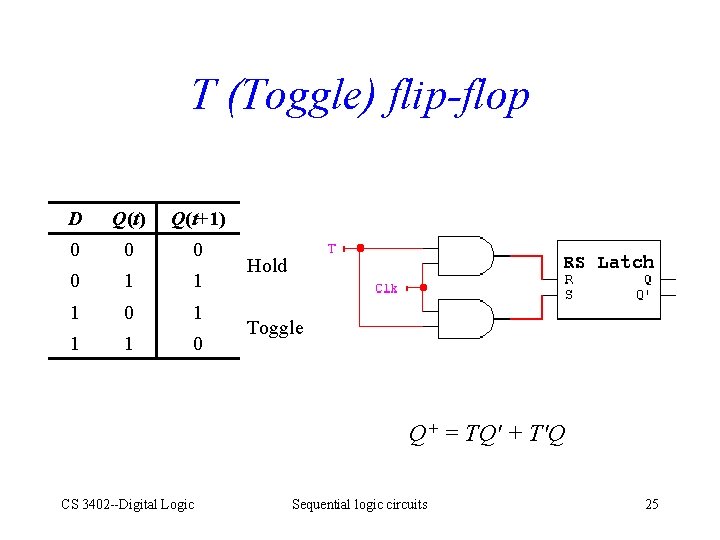

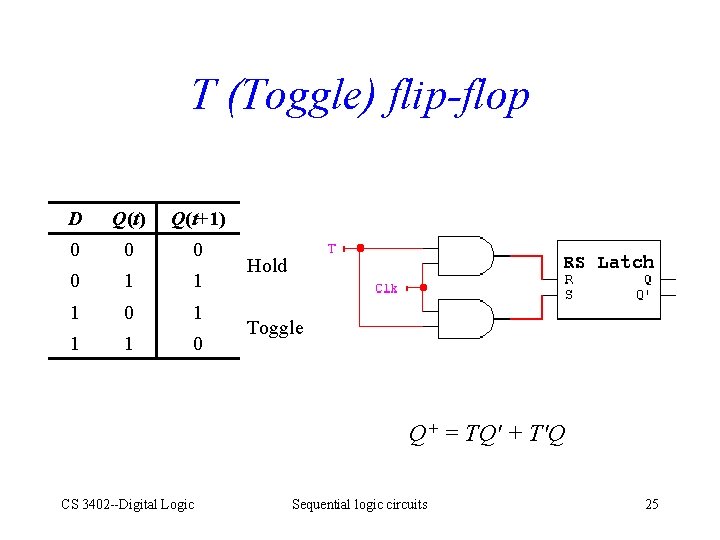

T (Toggle) flip-flop D Q(t) Q(t+1) 0 0 1 1 1 0 Hold Toggle Q+ = TQ' + T'Q CS 3402 --Digital Logic Sequential logic circuits 25

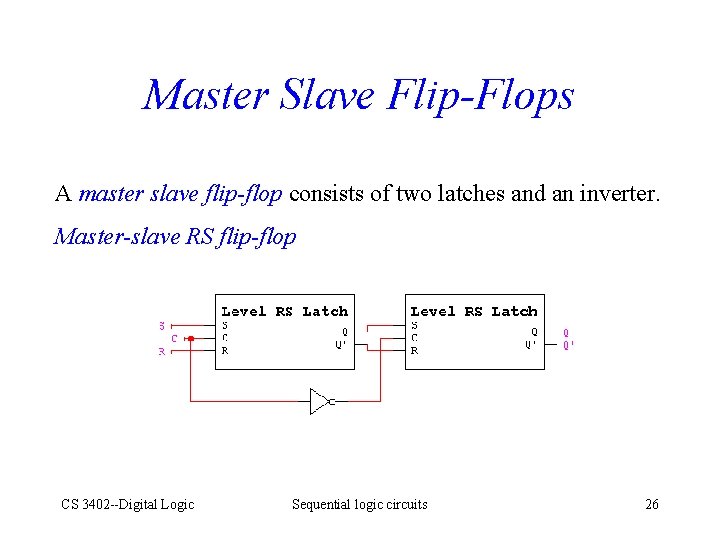

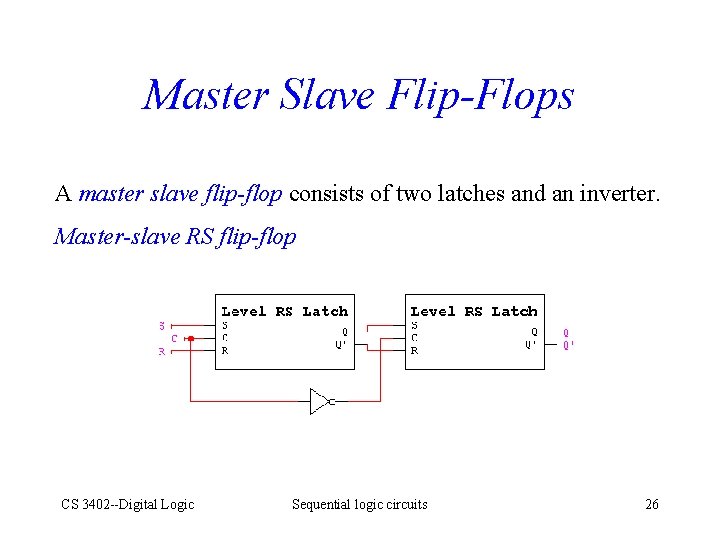

Master Slave Flip-Flops A master slave flip-flop consists of two latches and an inverter. Master-slave RS flip-flop CS 3402 --Digital Logic Sequential logic circuits 26

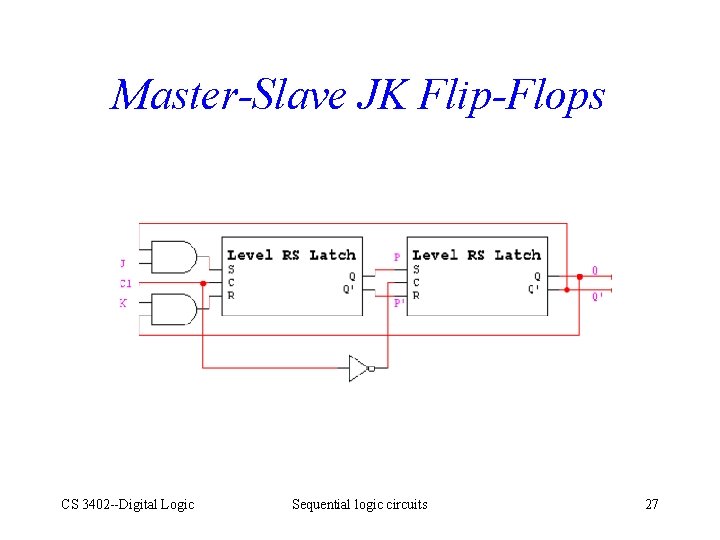

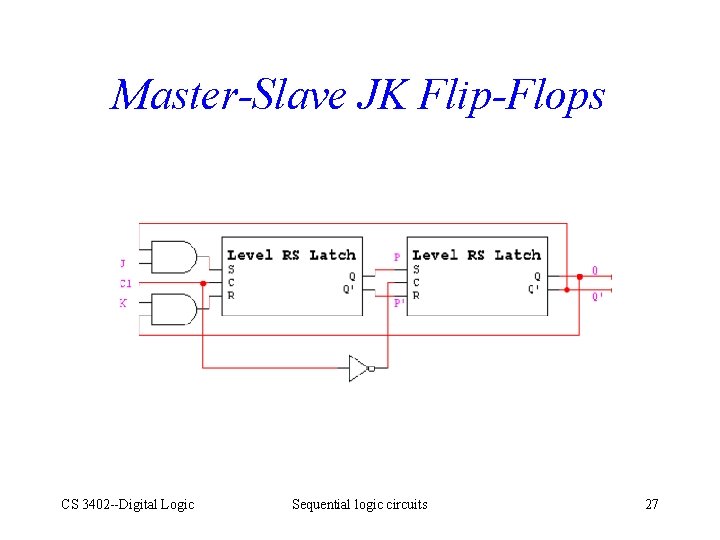

Master-Slave JK Flip-Flops CS 3402 --Digital Logic Sequential logic circuits 27

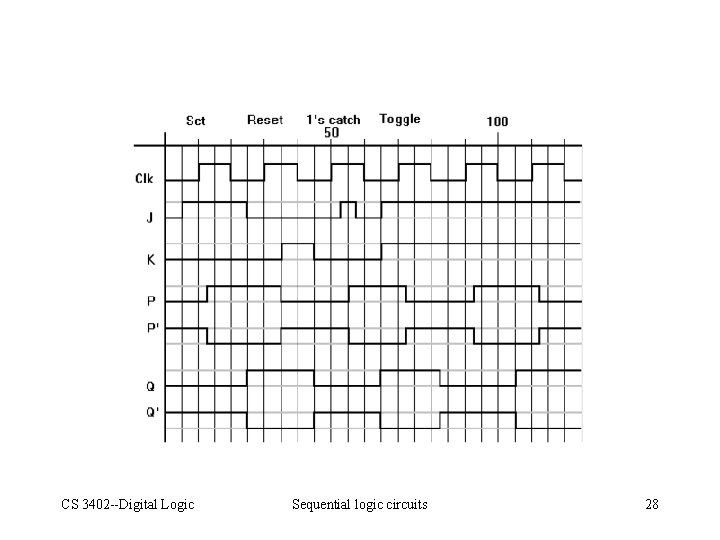

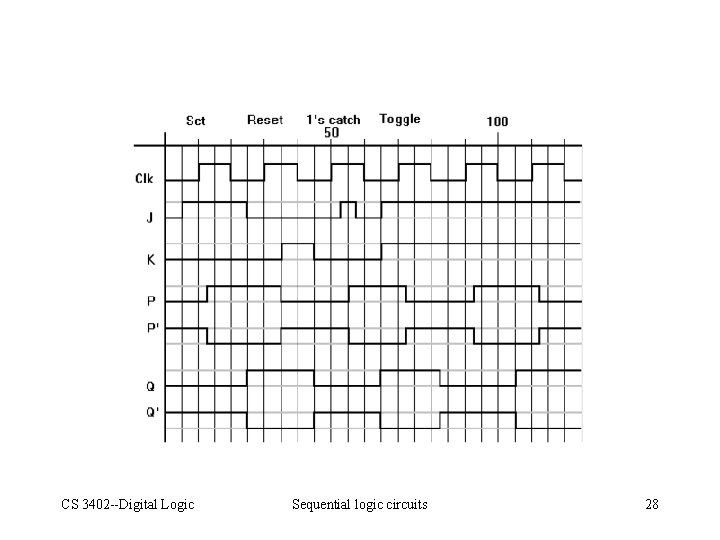

CS 3402 --Digital Logic Sequential logic circuits 28

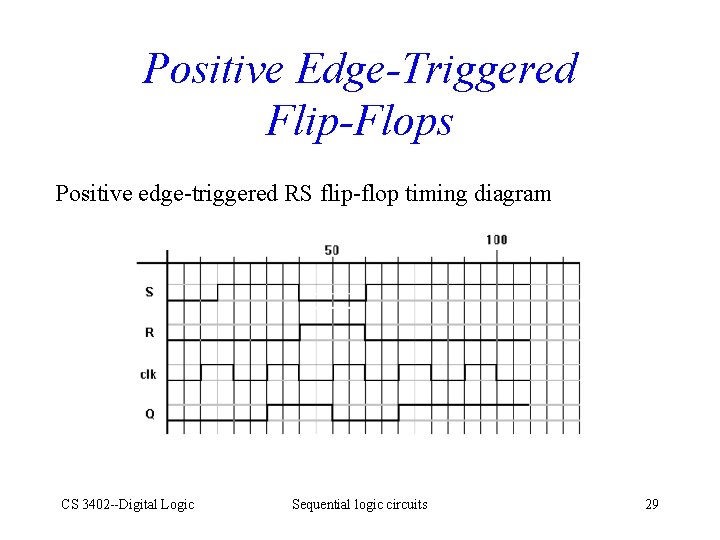

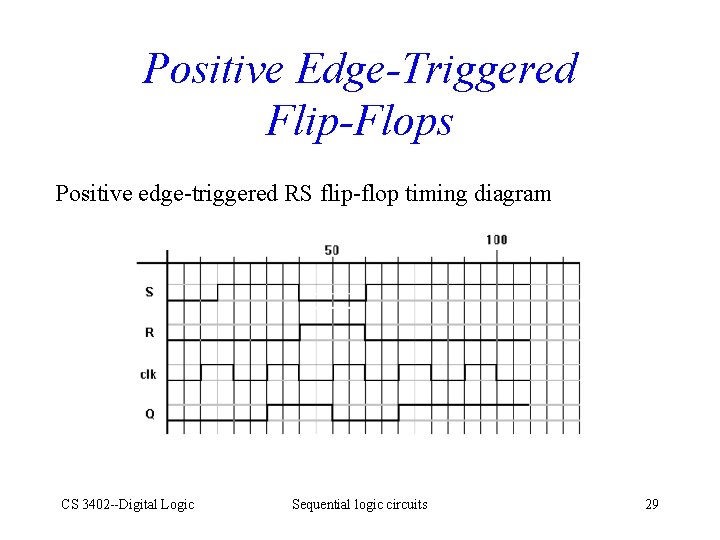

Positive Edge-Triggered Flip-Flops Positive edge-triggered RS flip-flop timing diagram CS 3402 --Digital Logic Sequential logic circuits 29

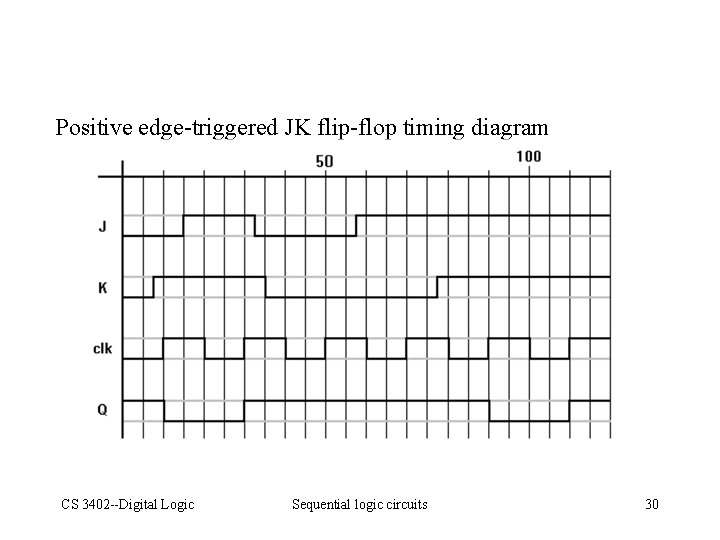

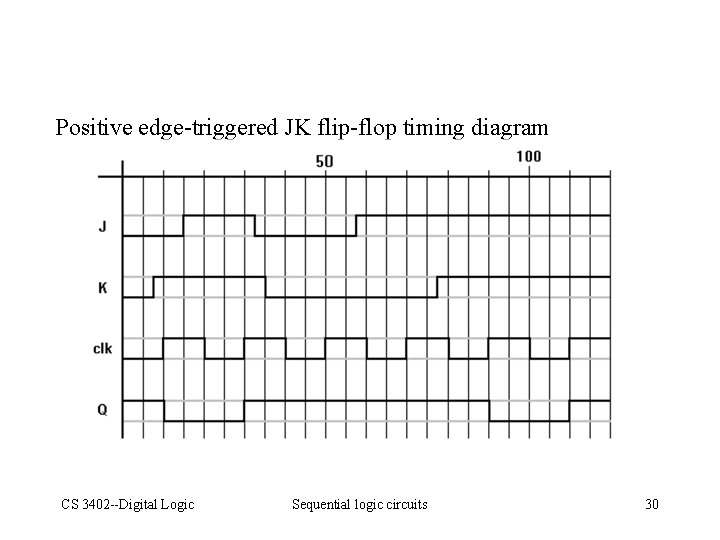

Positive edge-triggered JK flip-flop timing diagram CS 3402 --Digital Logic Sequential logic circuits 30

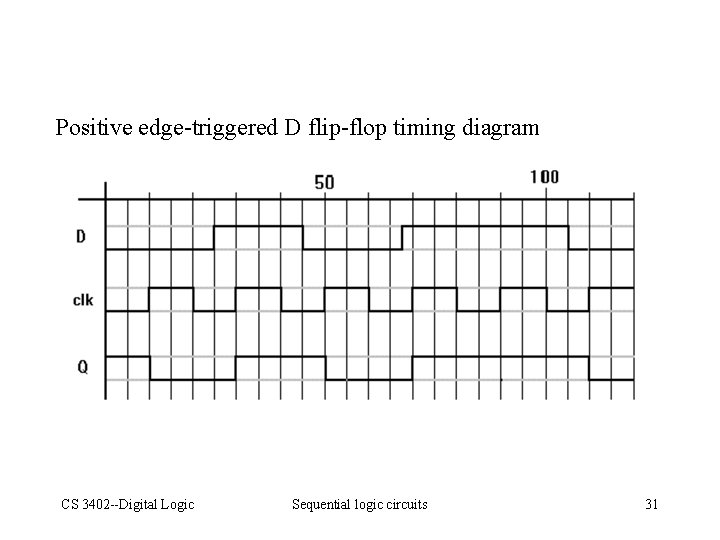

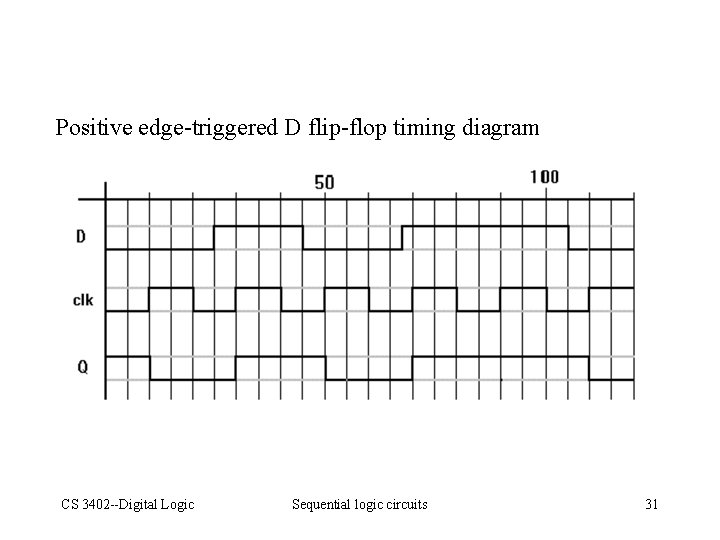

Positive edge-triggered D flip-flop timing diagram CS 3402 --Digital Logic Sequential logic circuits 31

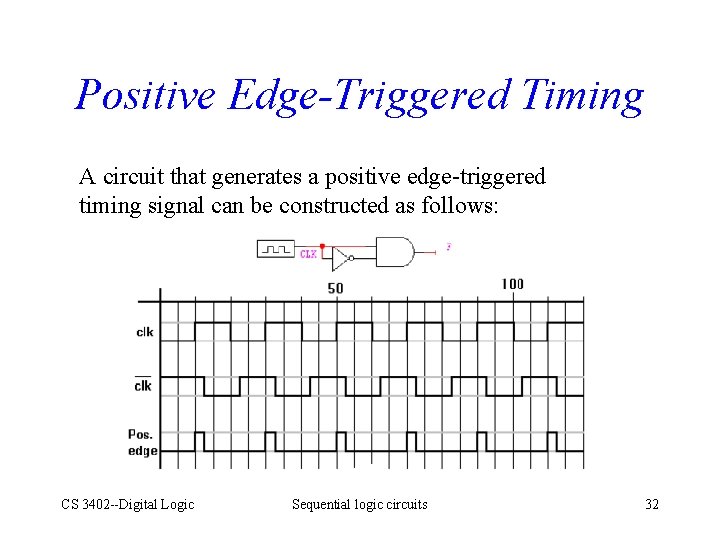

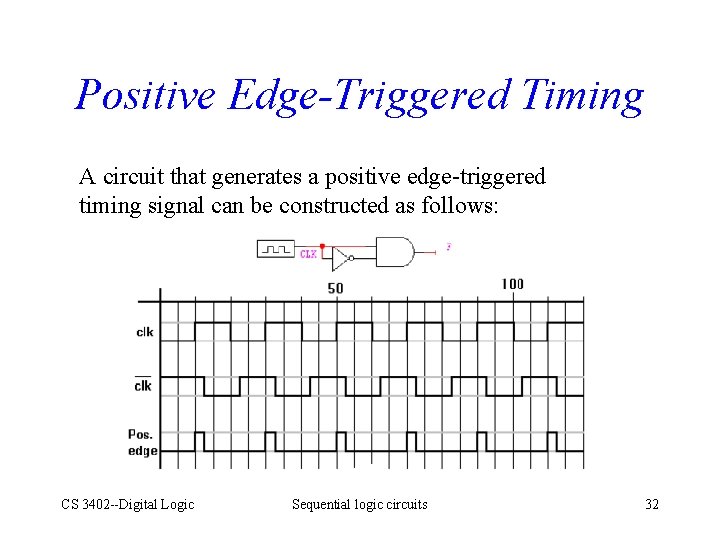

Positive Edge-Triggered Timing A circuit that generates a positive edge-triggered timing signal can be constructed as follows: CS 3402 --Digital Logic Sequential logic circuits 32

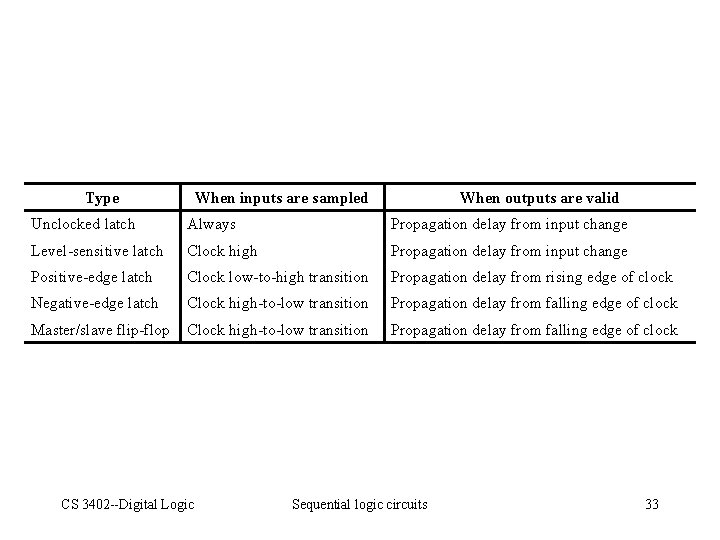

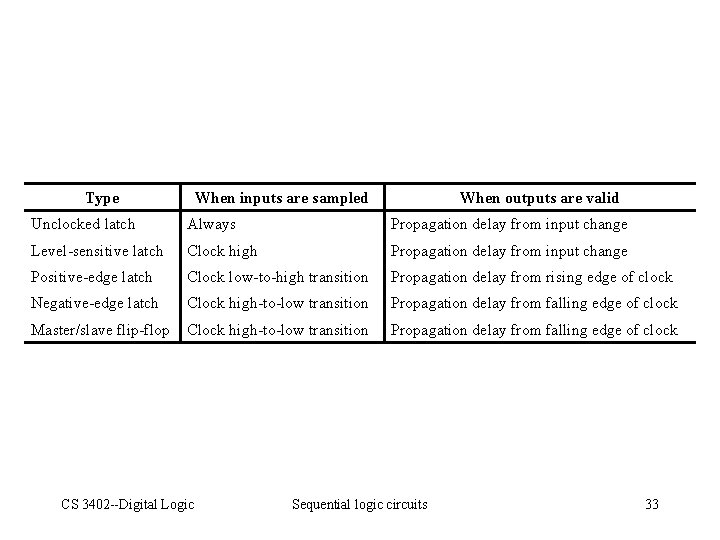

Type When inputs are sampled When outputs are valid Unclocked latch Always Propagation delay from input change Level-sensitive latch Clock high Propagation delay from input change Positive-edge latch Clock low-to-high transition Propagation delay from rising edge of clock Negative-edge latch Clock high-to-low transition Propagation delay from falling edge of clock Master/slave flip-flop Clock high-to-low transition Propagation delay from falling edge of clock CS 3402 --Digital Logic Sequential logic circuits 33

Exercises page 425, 6. 1 -6. 6, 6. 9, 6. 10, 6. 12, 6. 13, 6. 14, 6. 17, 6. 24, 6. 25 CS 3402 --Digital Logic Sequential logic circuits 34