COE 405 Sequential Circuit Design Dr Aiman H

- Slides: 53

COE 405 Sequential Circuit Design Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

Outline n Sequential Circuit Model n Timing of Sequential Circuits n Latches and Flip flops n Sequential Circuit Design Procedure n Sequential Circuit Design Examples n State Minimization n State Encoding n Sequential Circuit Timing 1 -2

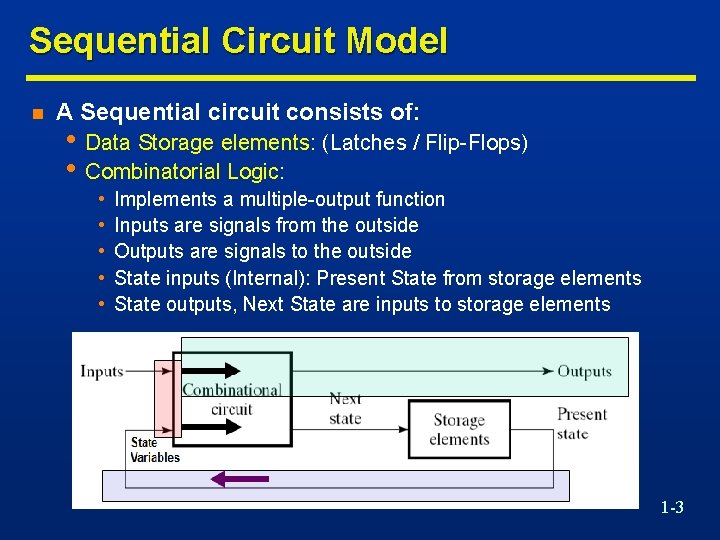

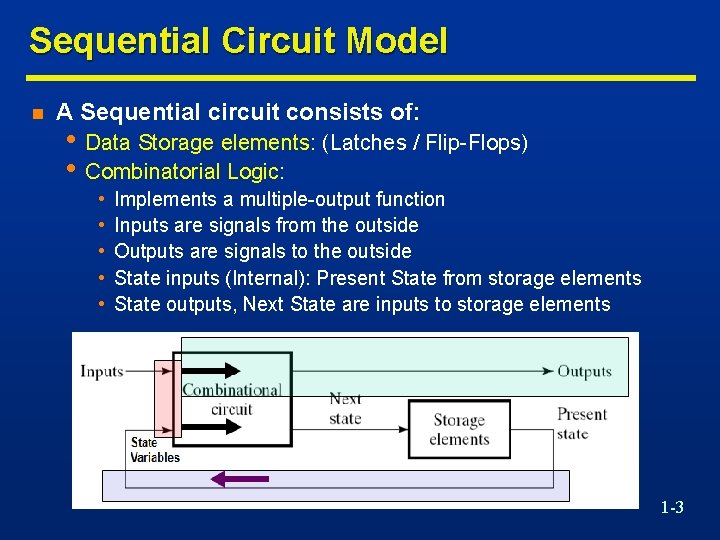

Sequential Circuit Model n A Sequential circuit consists of: • Data Storage elements: (Latches / Flip-Flops) • Combinatorial Logic: • • • Implements a multiple-output function Inputs are signals from the outside Outputs are signals to the outside State inputs (Internal): Present State from storage elements State outputs, Next State are inputs to storage elements 1 -3

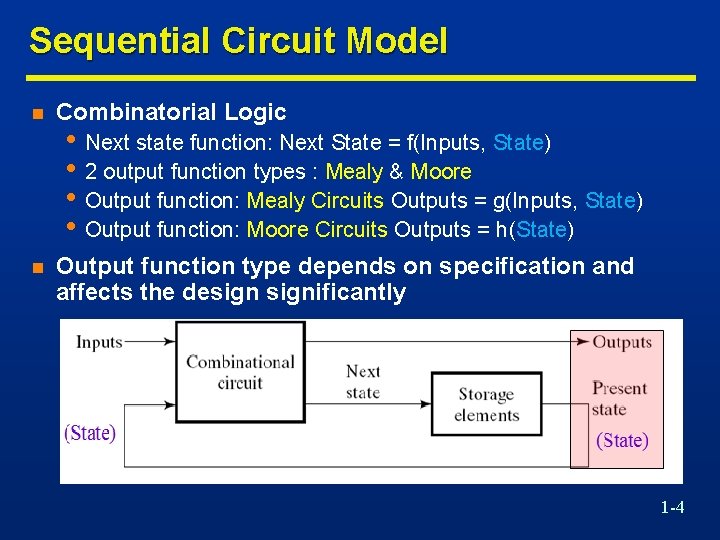

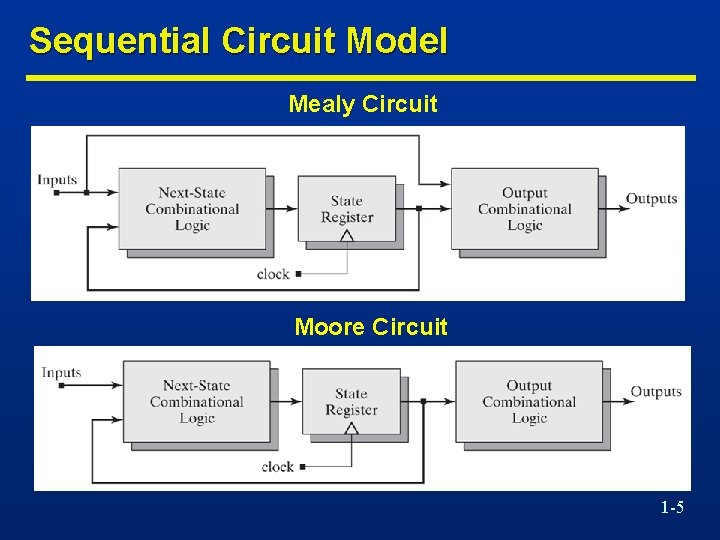

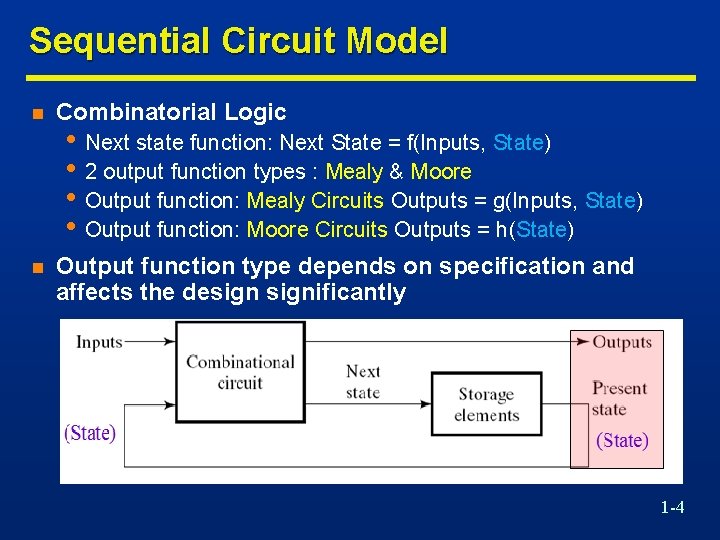

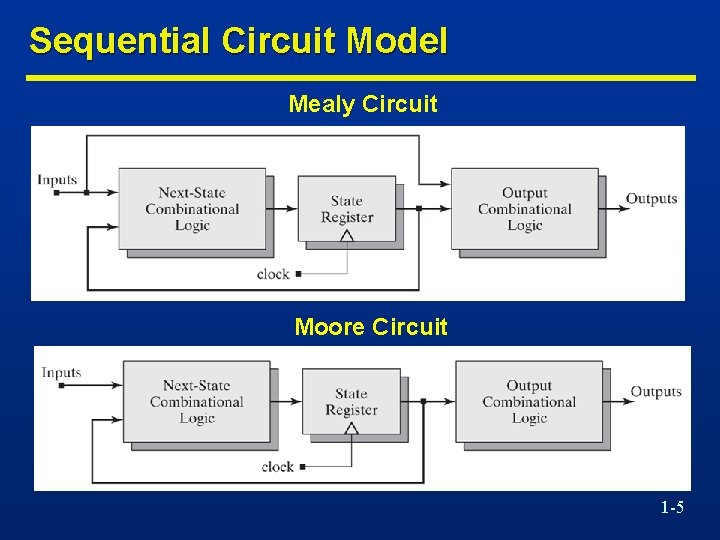

Sequential Circuit Model n Combinatorial Logic n Output function type depends on specification and affects the designificantly • Next state function: Next State = f(Inputs, State) • 2 output function types : Mealy & Moore • Output function: Mealy Circuits Outputs = g(Inputs, State) • Output function: Moore Circuits Outputs = h(State) 1 -4

Sequential Circuit Model Mealy Circuit Moore Circuit 1 -5

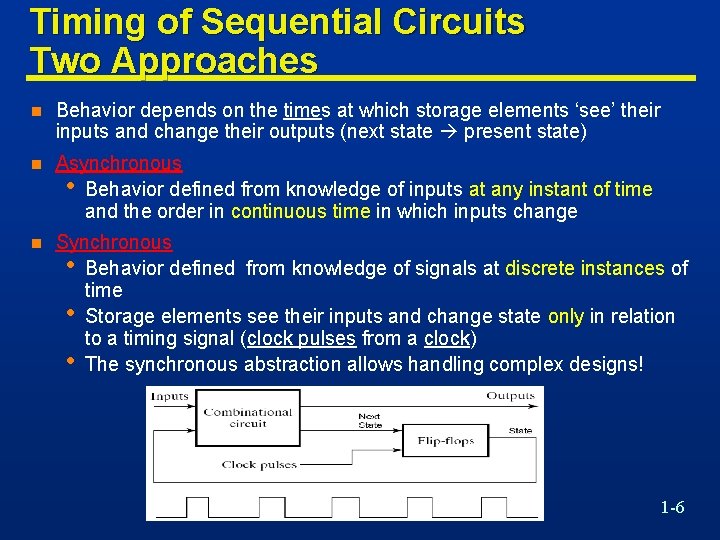

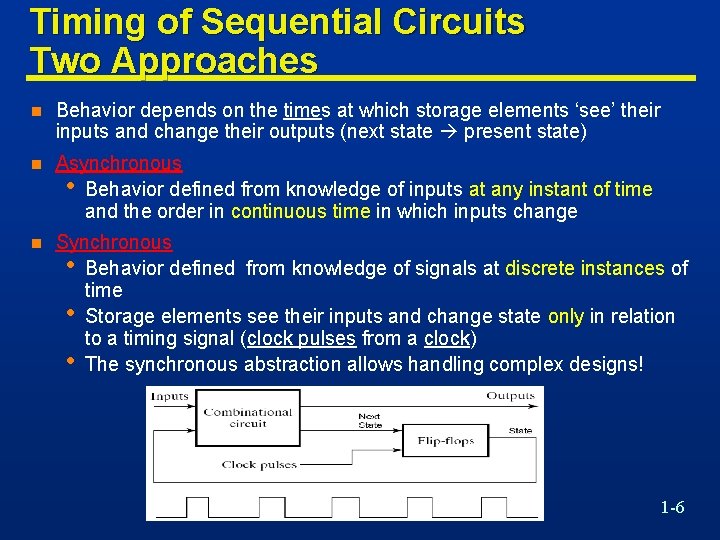

Timing of Sequential Circuits Two Approaches n Behavior depends on the times at which storage elements ‘see’ their inputs and change their outputs (next state present state) n Asynchronous • Behavior defined from knowledge of inputs at any instant of time and the order in continuous time in which inputs change n Synchronous • Behavior defined from knowledge of signals at discrete instances of time • Storage elements see their inputs and change state only in relation to a timing signal (clock pulses from a clock) • The synchronous abstraction allows handling complex designs! 1 -6

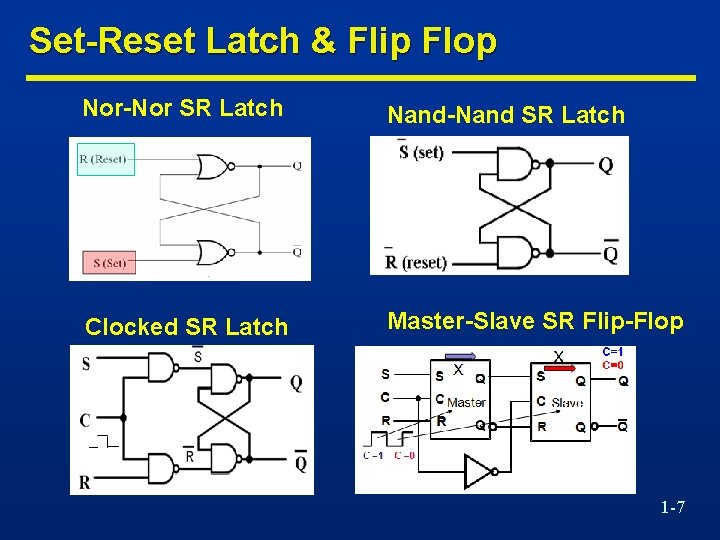

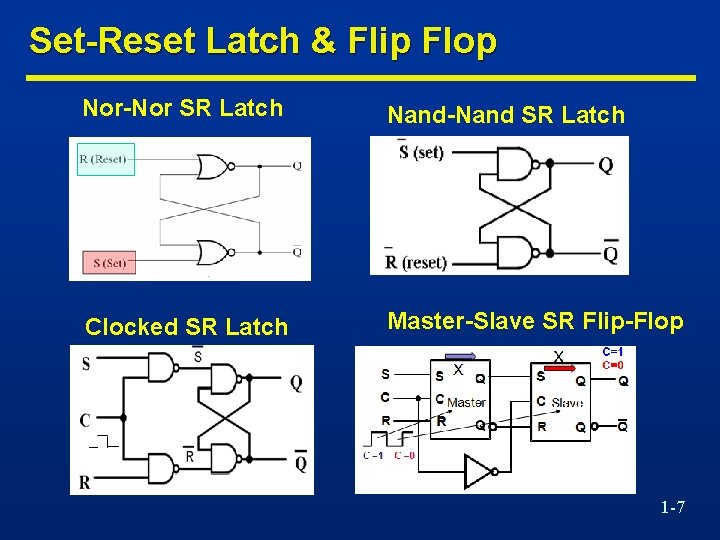

Set-Reset Latch & Flip Flop Nor-Nor SR Latch Nand-Nand SR Latch Clocked SR Latch Master-Slave SR Flip-Flop 1 -7

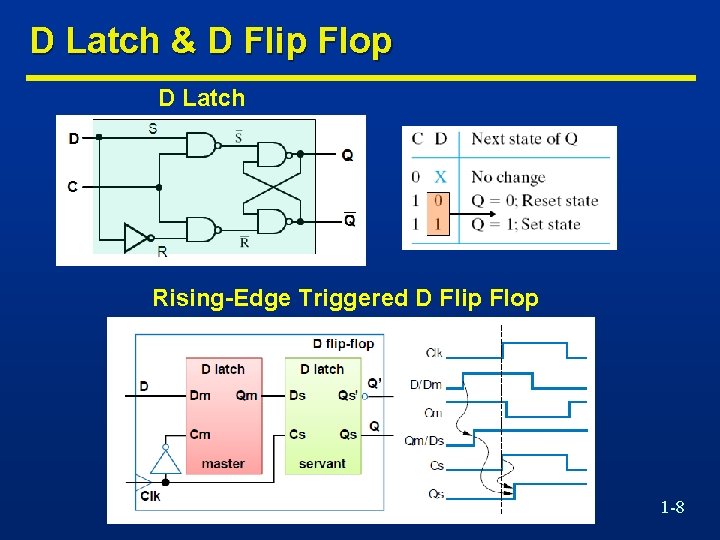

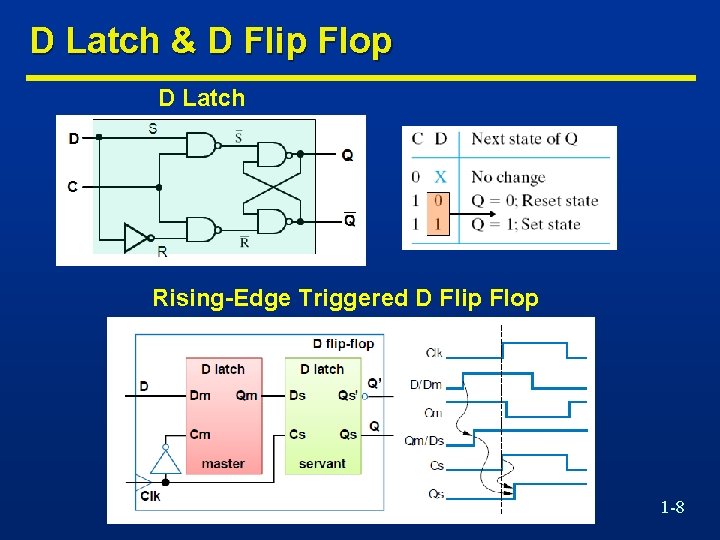

D Latch & D Flip Flop D Latch Rising-Edge Triggered D Flip Flop 1 -8

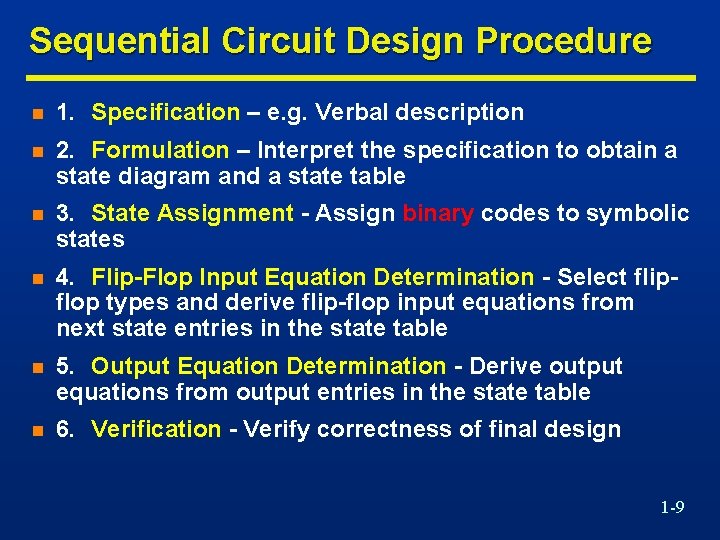

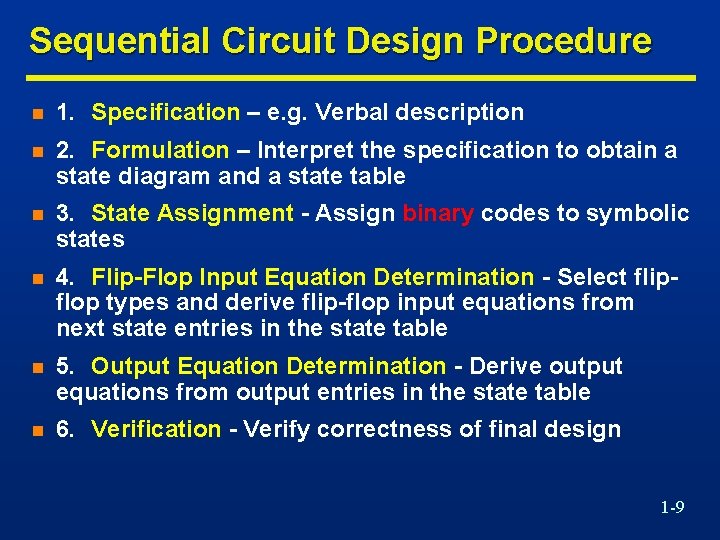

Sequential Circuit Design Procedure n 1. Specification – e. g. Verbal description n 2. Formulation – Interpret the specification to obtain a state diagram and a state table n 3. State Assignment - Assign binary codes to symbolic states n 4. Flip-Flop Input Equation Determination - Select flipflop types and derive flip-flop input equations from next state entries in the state table n 5. Output Equation Determination - Derive output equations from output entries in the state table n 6. Verification - Verify correctness of final design 1 -9

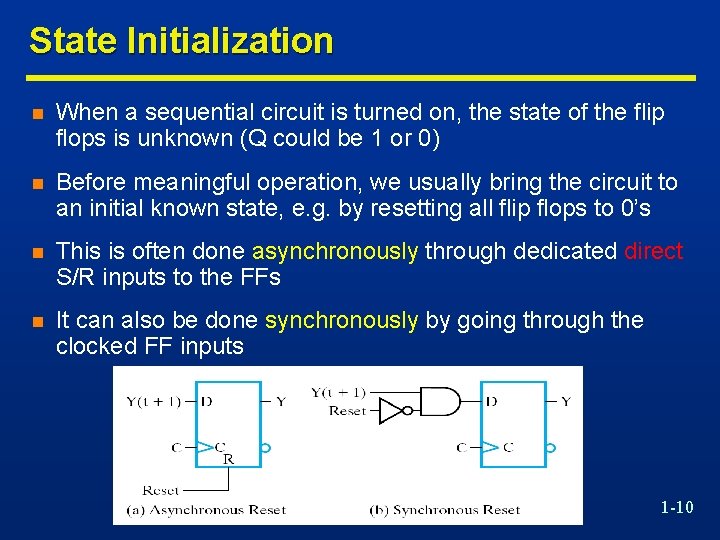

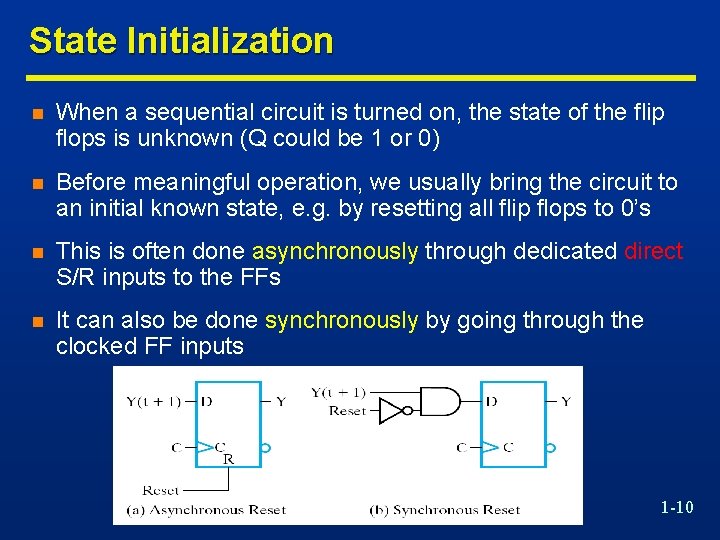

State Initialization n When a sequential circuit is turned on, the state of the flip flops is unknown (Q could be 1 or 0) n Before meaningful operation, we usually bring the circuit to an initial known state, e. g. by resetting all flip flops to 0’s n This is often done asynchronously through dedicated direct S/R inputs to the FFs n It can also be done synchronously by going through the clocked FF inputs 1 -10

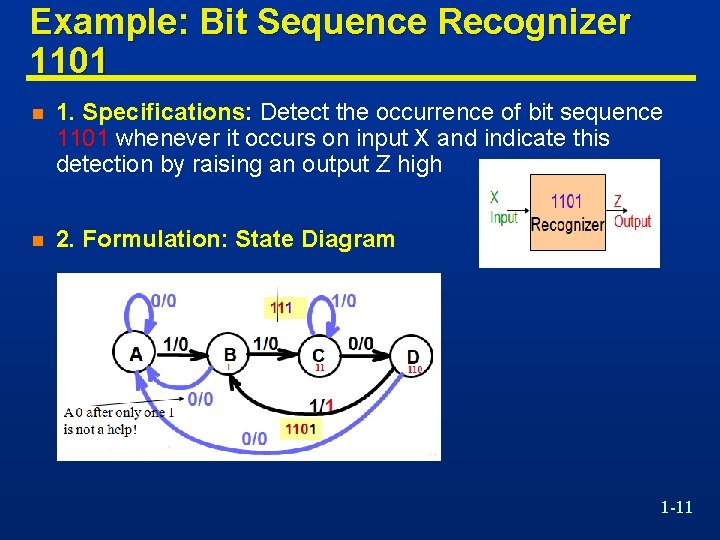

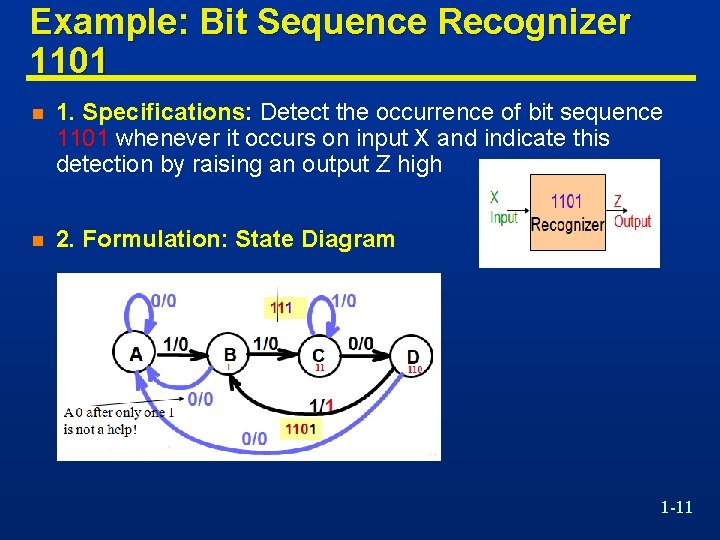

Example: Bit Sequence Recognizer 1101 n 1. Specifications: Detect the occurrence of bit sequence 1101 whenever it occurs on input X and indicate this detection by raising an output Z high n 2. Formulation: State Diagram 1 -11

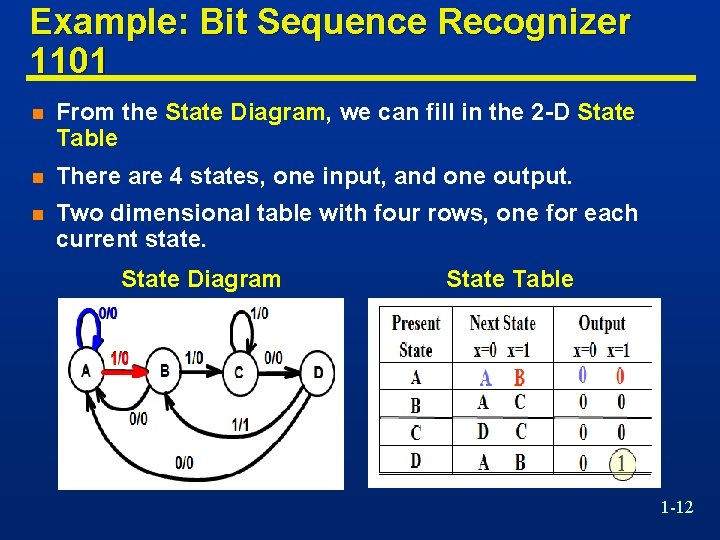

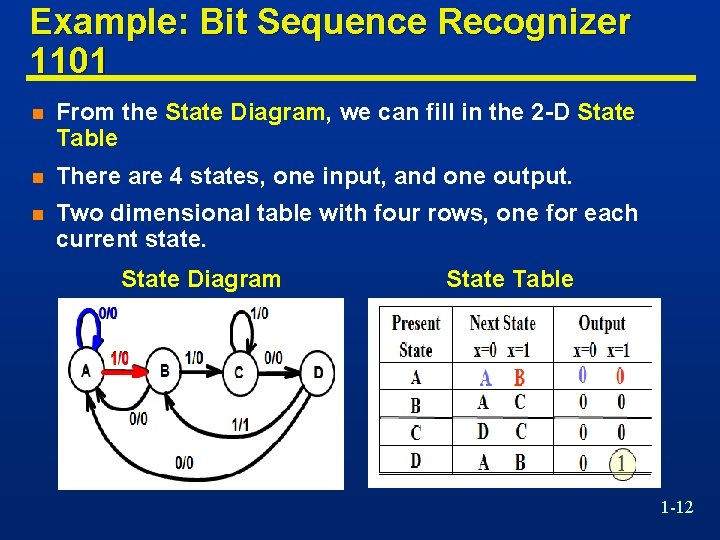

Example: Bit Sequence Recognizer 1101 n From the State Diagram, we can fill in the 2 -D State Table n There are 4 states, one input, and one output. n Two dimensional table with four rows, one for each current state. State Diagram State Table 1 -12

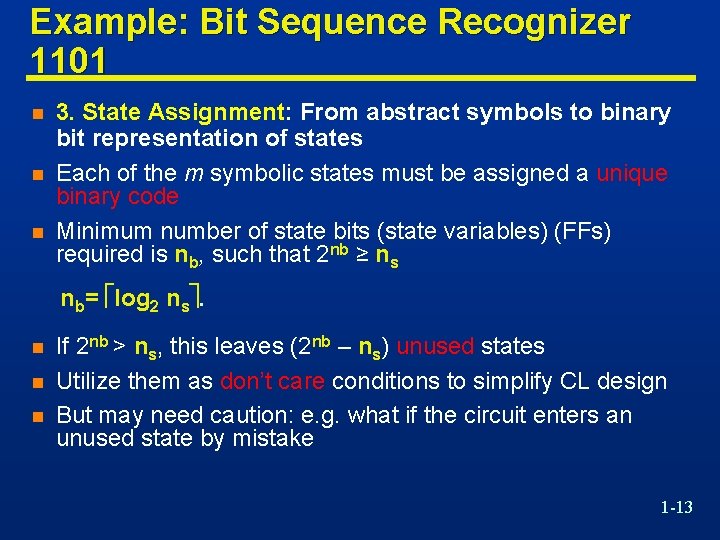

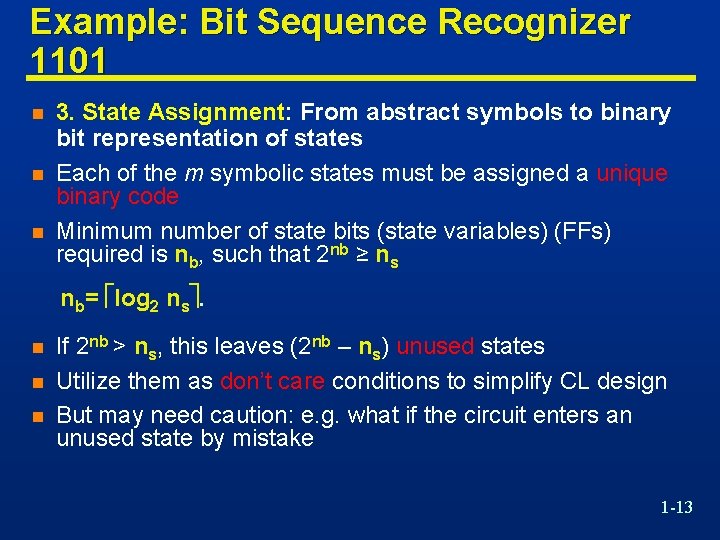

Example: Bit Sequence Recognizer 1101 n n n 3. State Assignment: From abstract symbols to binary bit representation of states Each of the m symbolic states must be assigned a unique binary code Minimum number of state bits (state variables) (FFs) required is nb, such that 2 nb ≥ ns nb= log 2 ns. n n n If 2 nb > ns, this leaves (2 nb – ns) unused states Utilize them as don’t care conditions to simplify CL design But may need caution: e. g. what if the circuit enters an unused state by mistake 1 -13

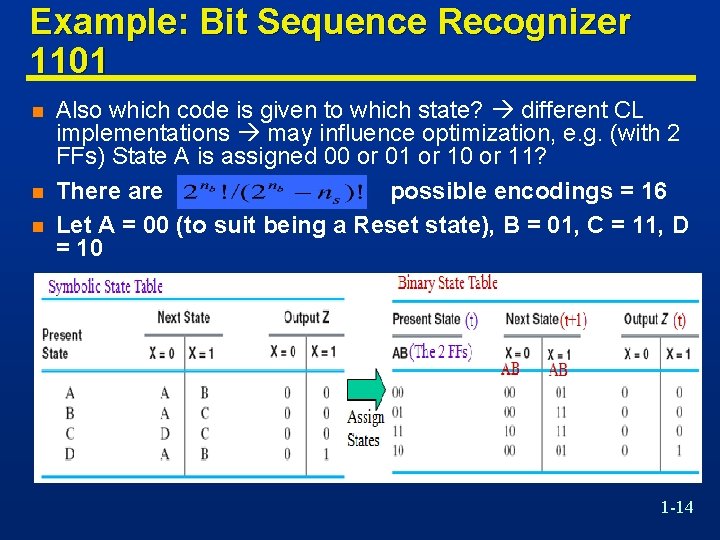

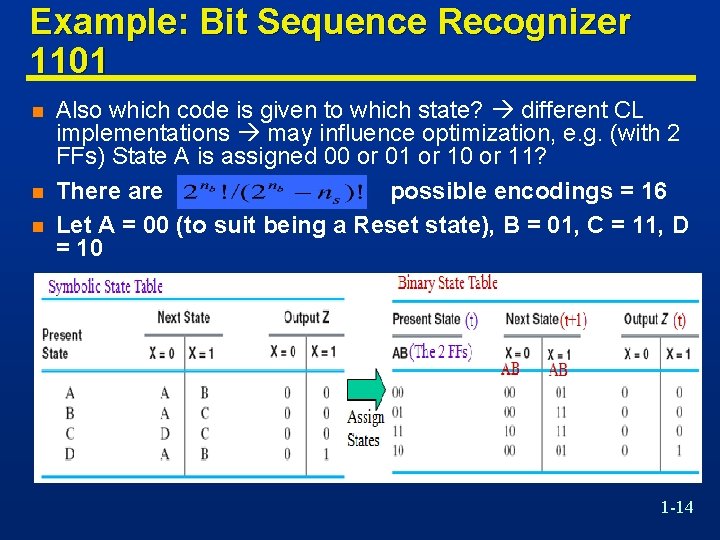

Example: Bit Sequence Recognizer 1101 n n n Also which code is given to which state? different CL implementations may influence optimization, e. g. (with 2 FFs) State A is assigned 00 or 01 or 10 or 11? There are possible encodings = 16 Let A = 00 (to suit being a Reset state), B = 01, C = 11, D = 10 1 -14

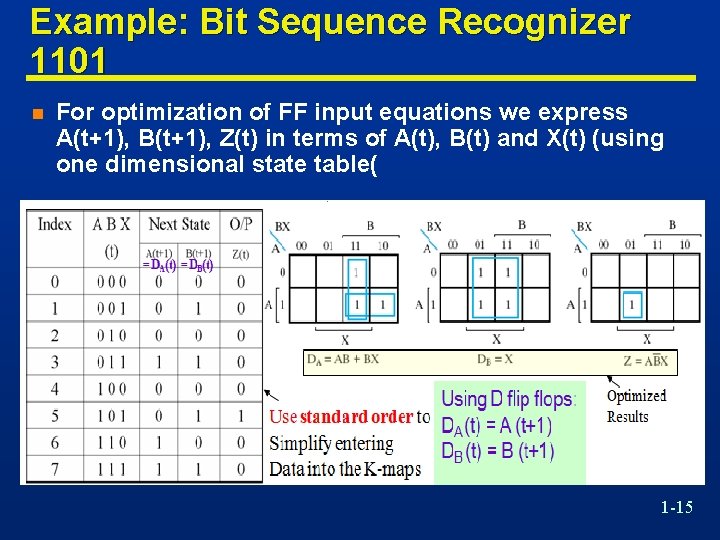

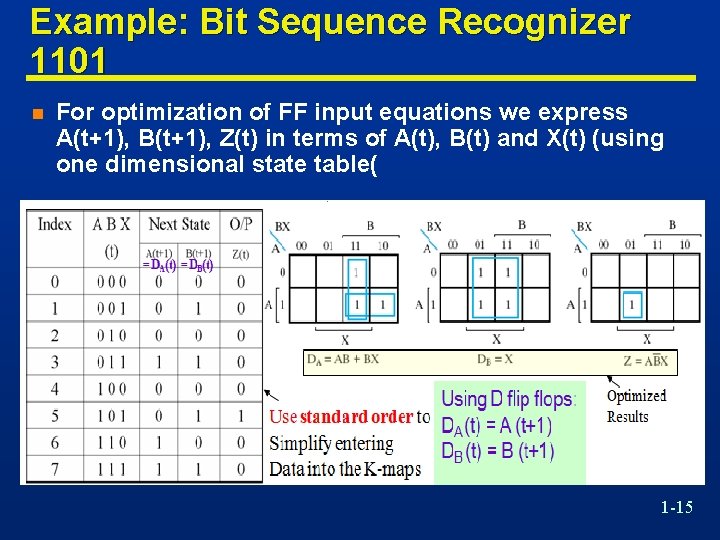

Example: Bit Sequence Recognizer 1101 n For optimization of FF input equations we express A(t+1), B(t+1), Z(t) in terms of A(t), B(t) and X(t) (using one dimensional state table( 1 -15

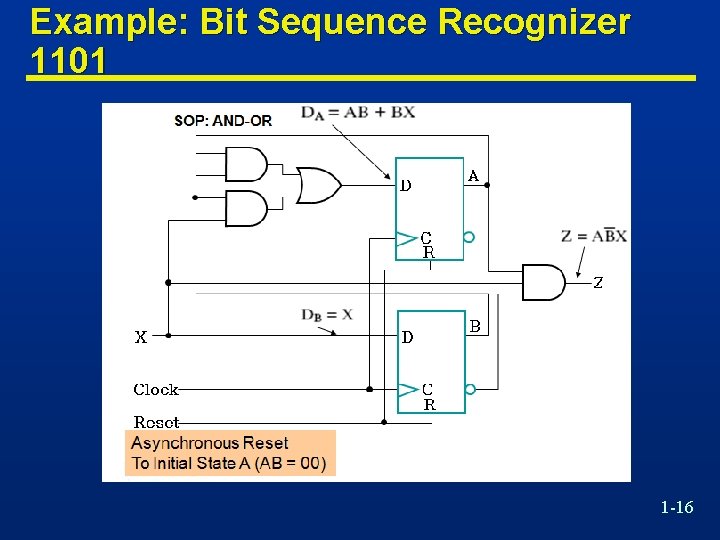

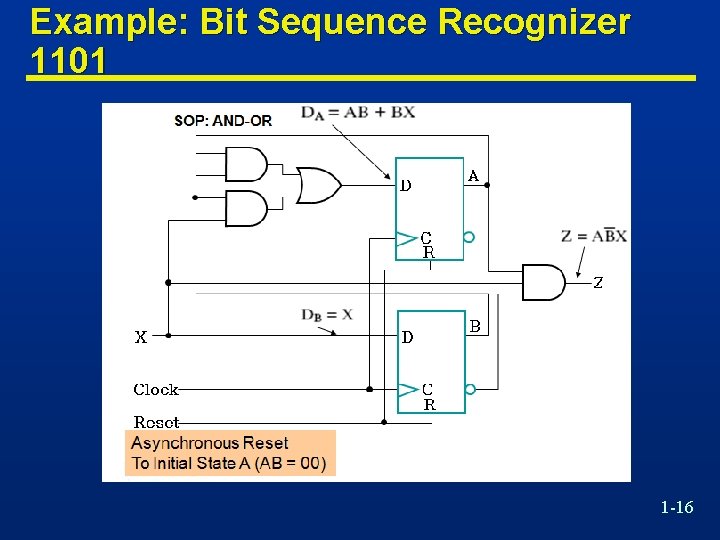

Example: Bit Sequence Recognizer 1101 1 -16

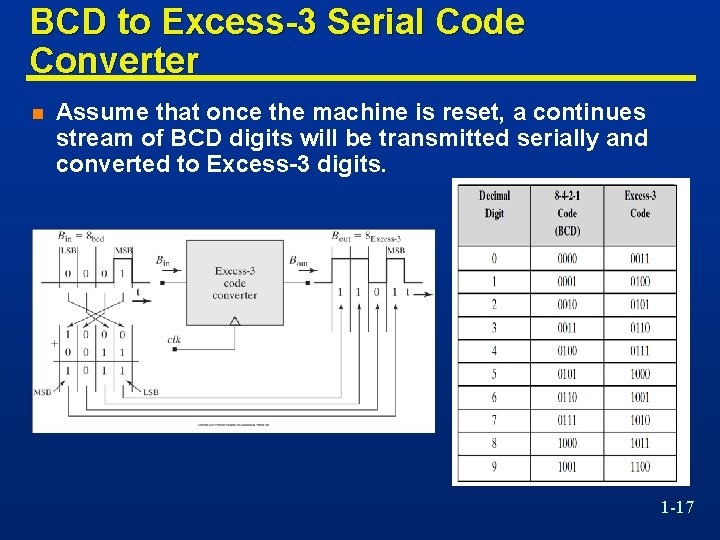

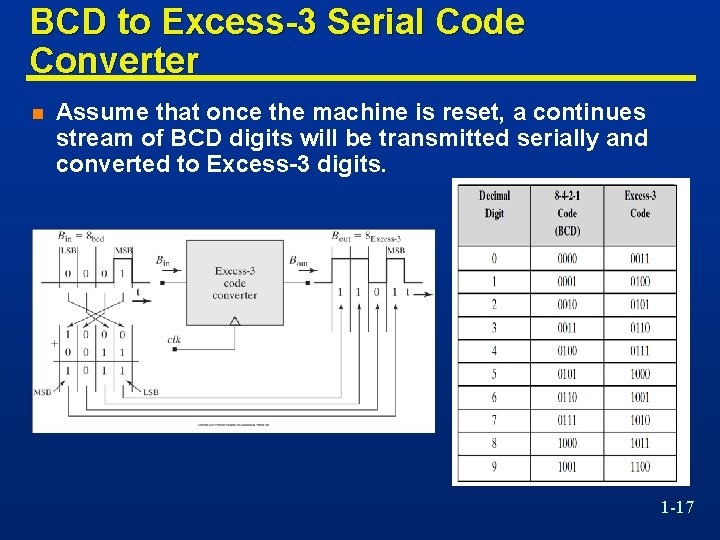

BCD to Excess-3 Serial Code Converter n Assume that once the machine is reset, a continues stream of BCD digits will be transmitted serially and converted to Excess-3 digits. 1 -17

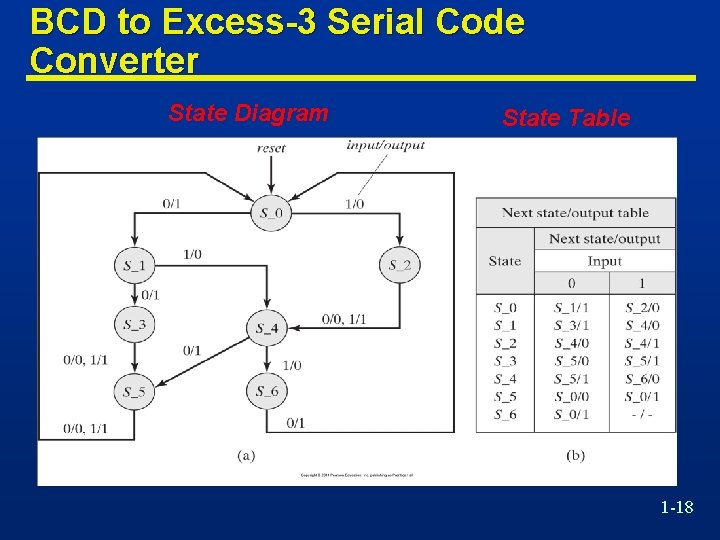

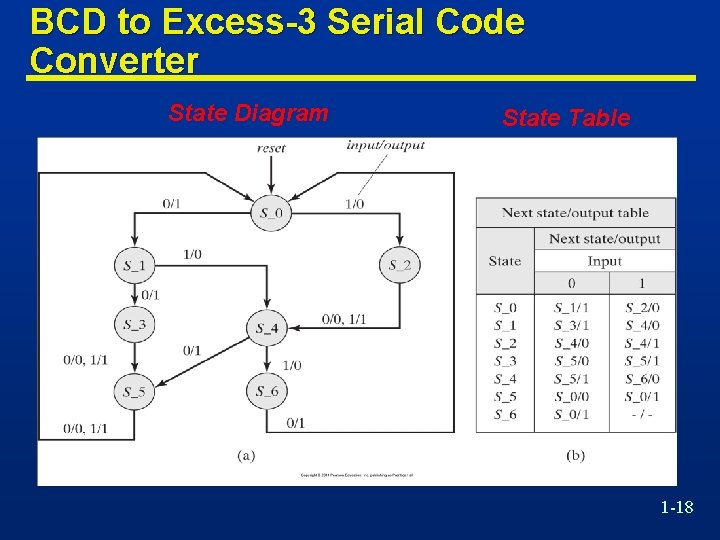

BCD to Excess-3 Serial Code Converter State Diagram State Table 1 -18

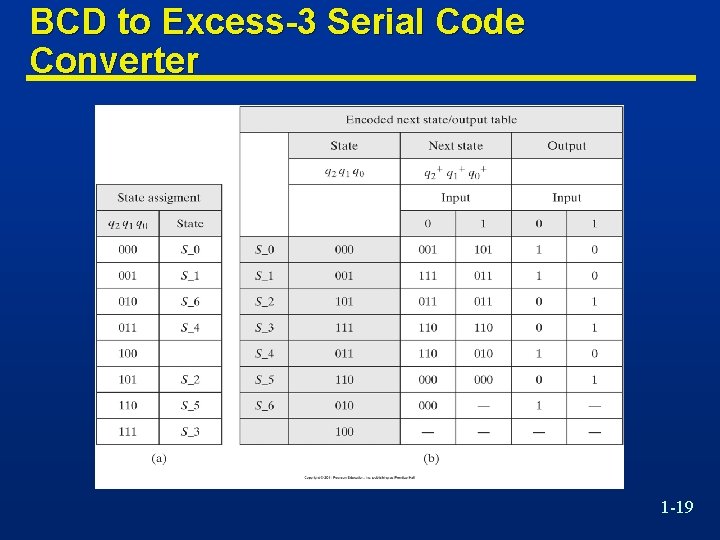

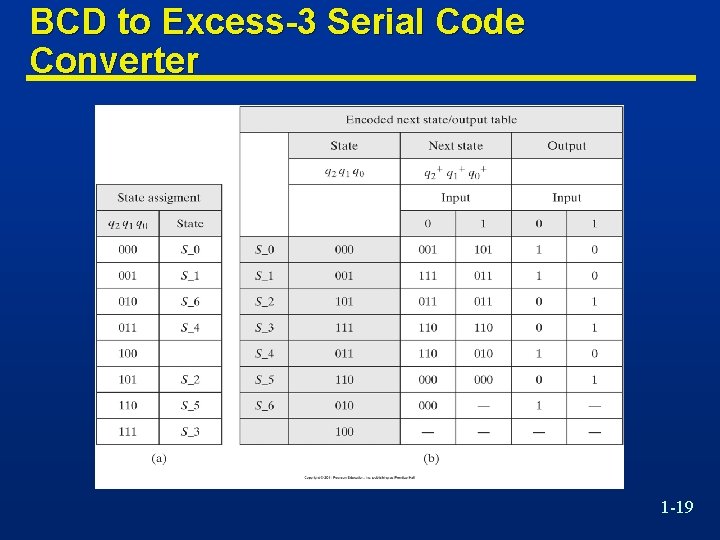

BCD to Excess-3 Serial Code Converter 1 -19

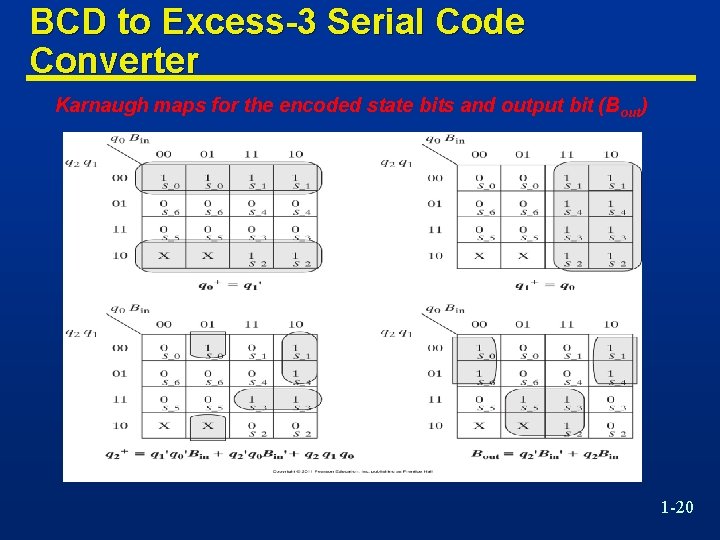

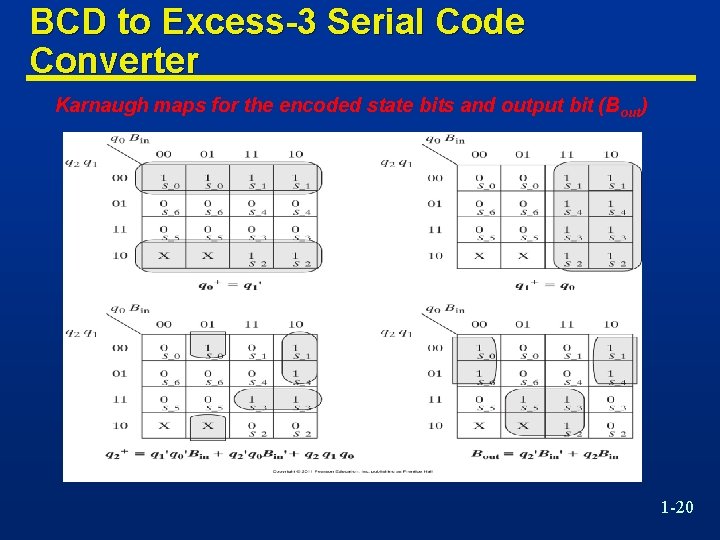

BCD to Excess-3 Serial Code Converter Karnaugh maps for the encoded state bits and output bit (Bout) 1 -20

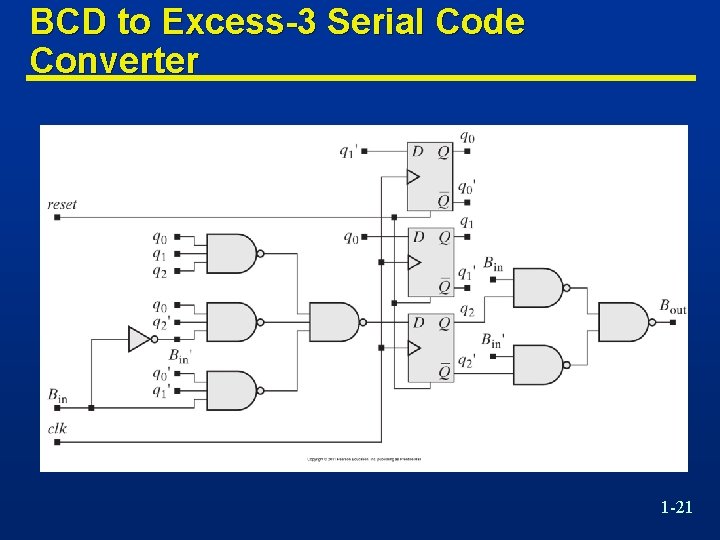

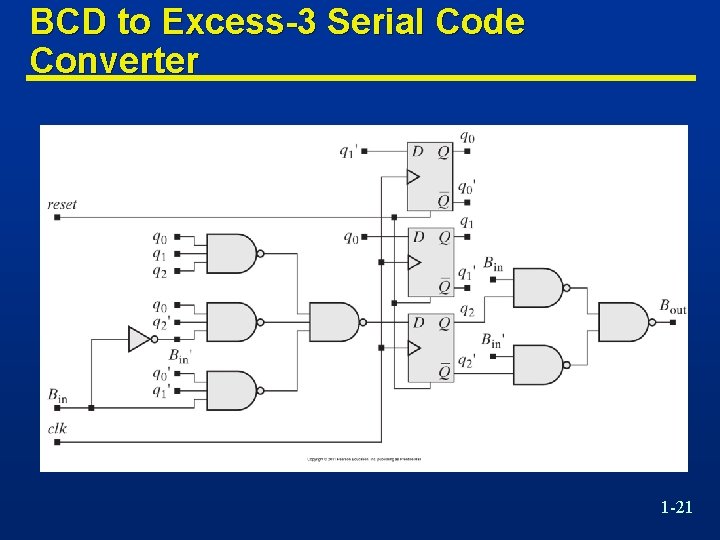

BCD to Excess-3 Serial Code Converter 1 -21

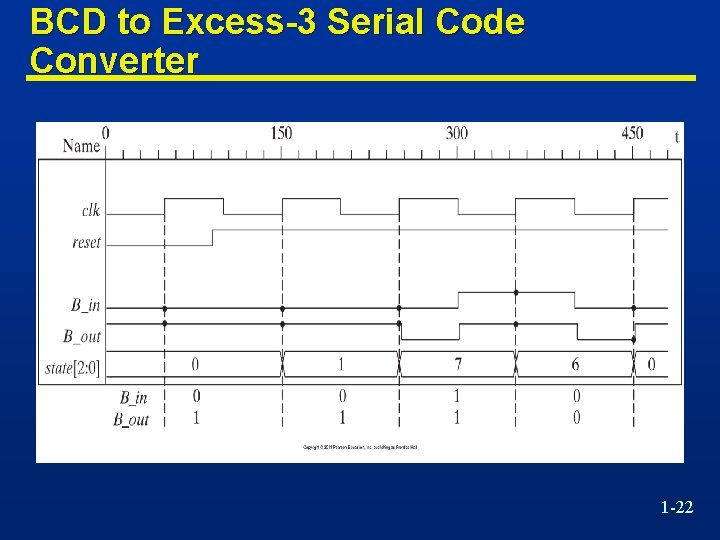

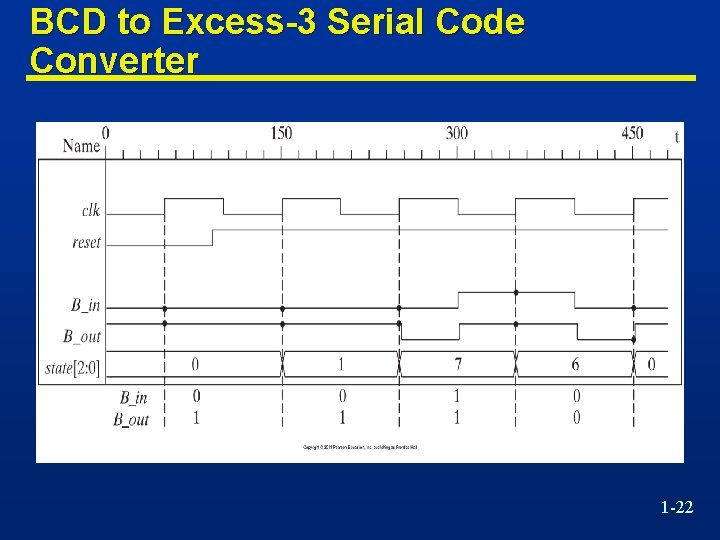

BCD to Excess-3 Serial Code Converter 1 -22

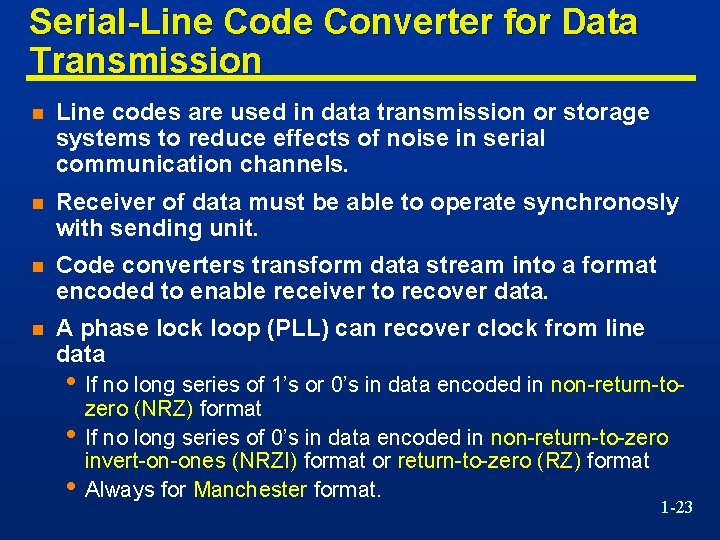

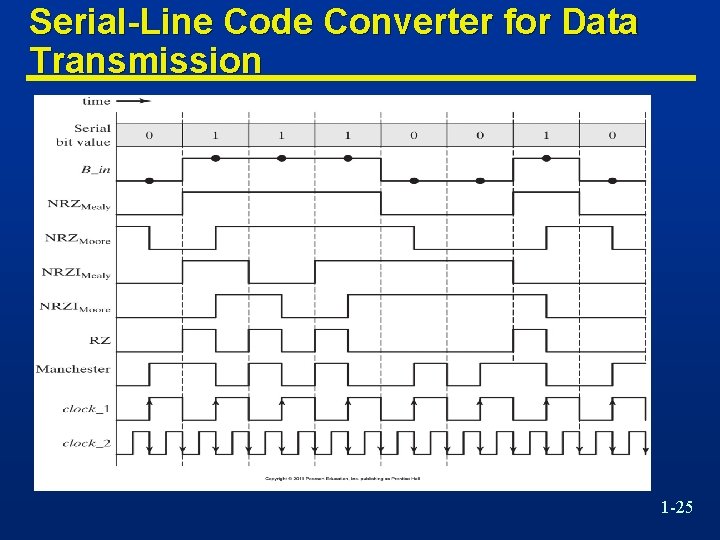

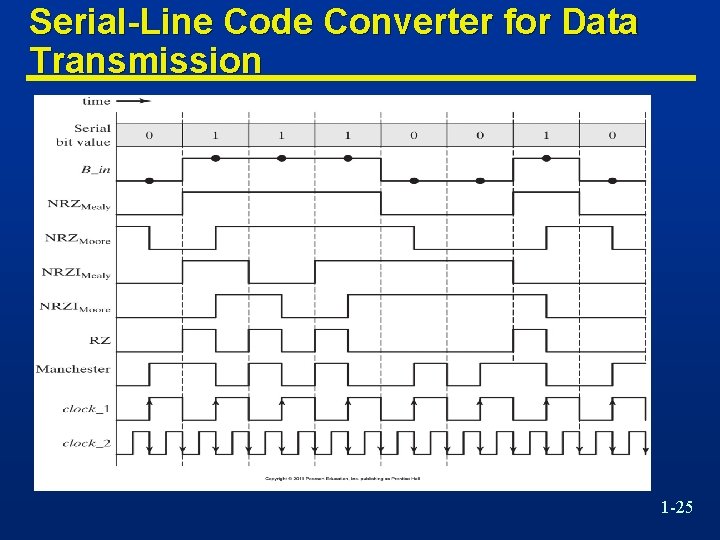

Serial-Line Code Converter for Data Transmission n Line codes are used in data transmission or storage systems to reduce effects of noise in serial communication channels. n Receiver of data must be able to operate synchronosly with sending unit. n Code converters transform data stream into a format encoded to enable receiver to recover data. n A phase lock loop (PLL) can recover clock from line data • If no long series of 1’s or 0’s in data encoded in non-return-to • • zero (NRZ) format If no long series of 0’s in data encoded in non-return-to-zero invert-on-ones (NRZI) format or return-to-zero (RZ) format Always for Manchester format. 1 -23

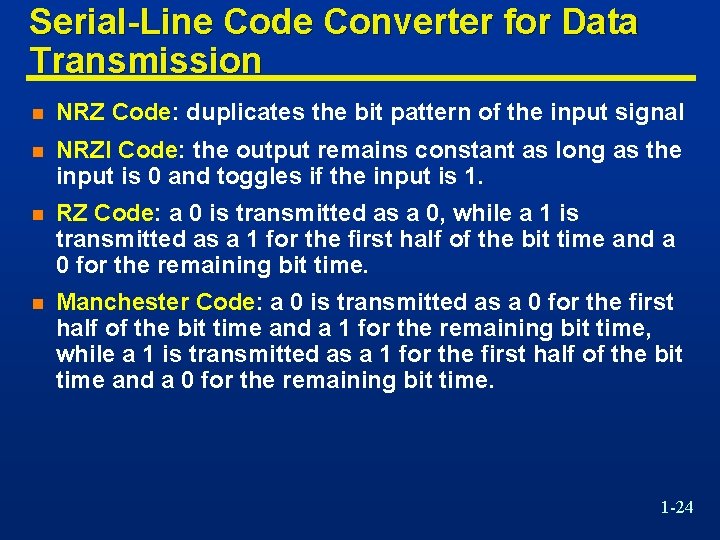

Serial-Line Code Converter for Data Transmission n NRZ Code: duplicates the bit pattern of the input signal n NRZI Code: the output remains constant as long as the input is 0 and toggles if the input is 1. n RZ Code: a 0 is transmitted as a 0, while a 1 is transmitted as a 1 for the first half of the bit time and a 0 for the remaining bit time. n Manchester Code: a 0 is transmitted as a 0 for the first half of the bit time and a 1 for the remaining bit time, while a 1 is transmitted as a 1 for the first half of the bit time and a 0 for the remaining bit time. 1 -24

Serial-Line Code Converter for Data Transmission 1 -25

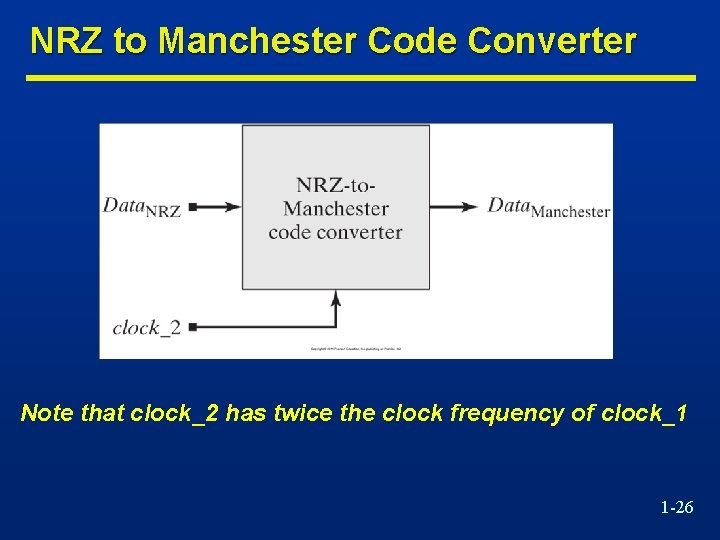

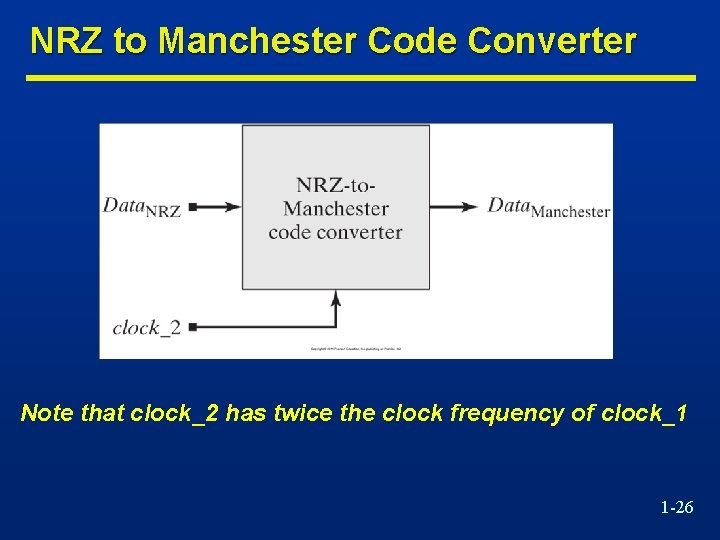

NRZ to Manchester Code Converter Note that clock_2 has twice the clock frequency of clock_1 1 -26

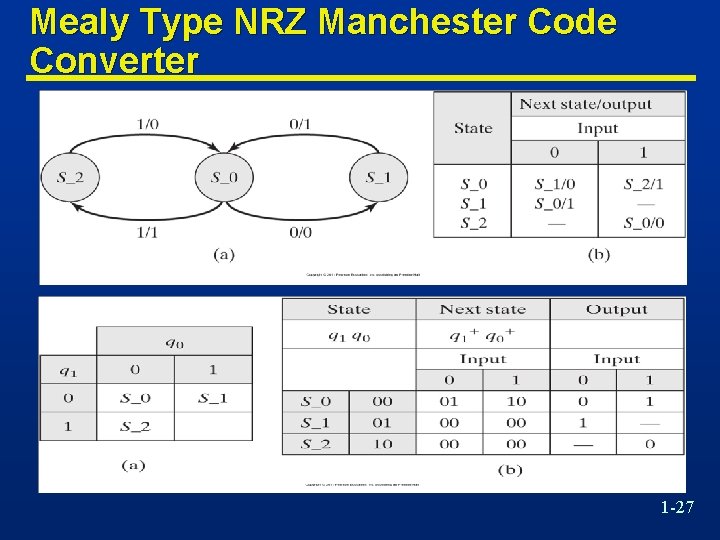

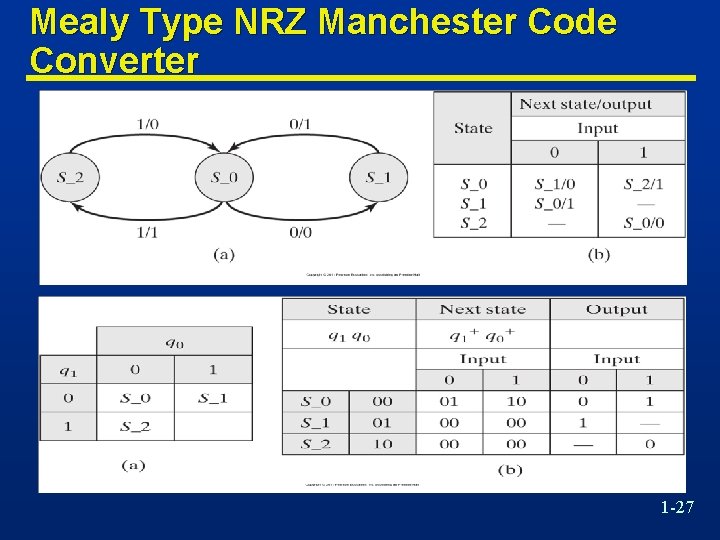

Mealy Type NRZ Manchester Code Converter 1 -27

Mealy-Type NRZ Manchester Code Converter 1 -28

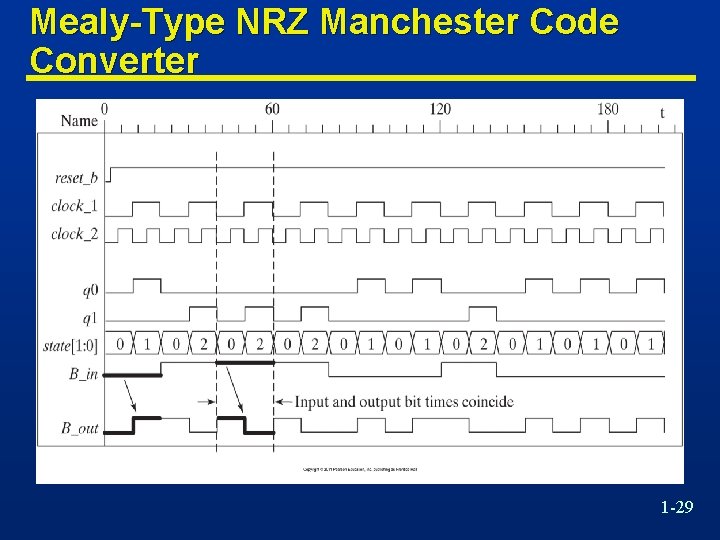

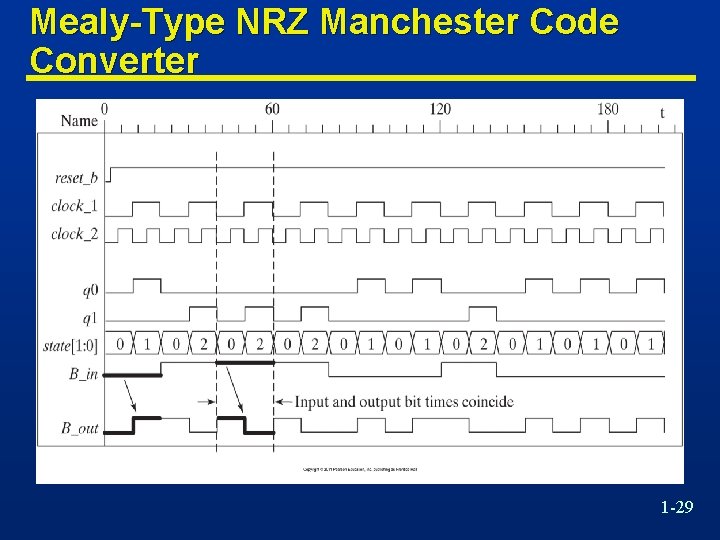

Mealy-Type NRZ Manchester Code Converter 1 -29

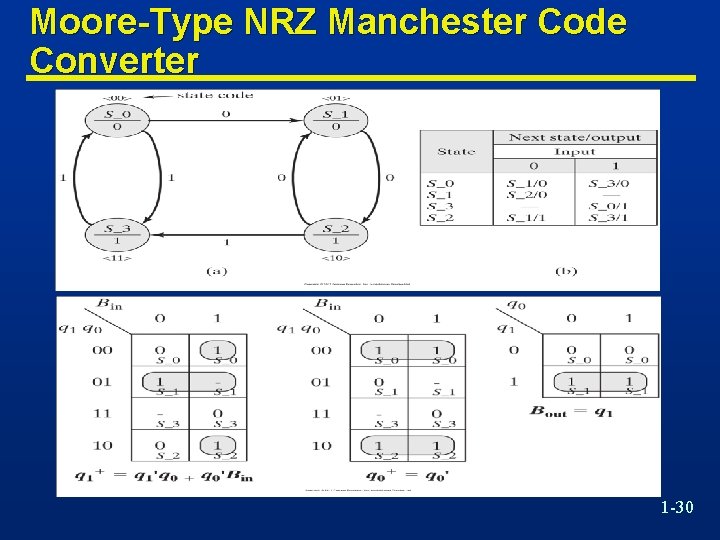

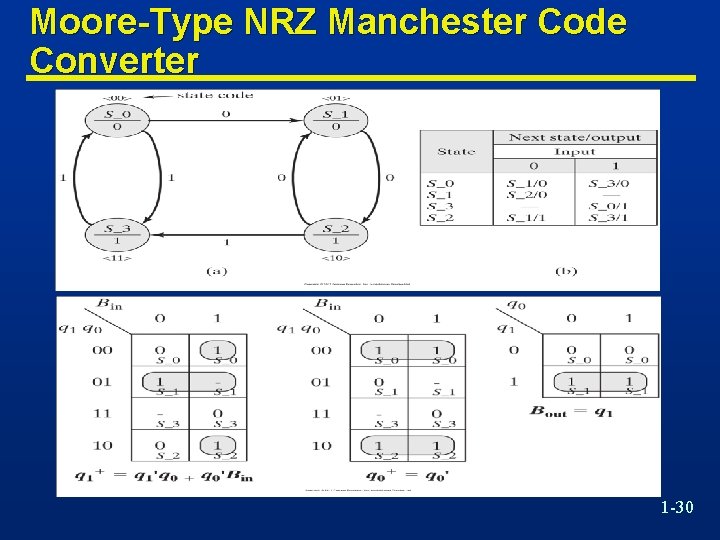

Moore-Type NRZ Manchester Code Converter 1 -30

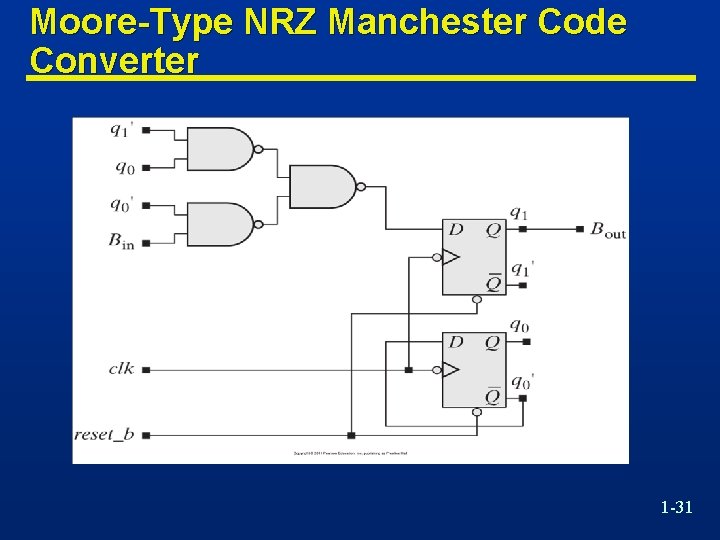

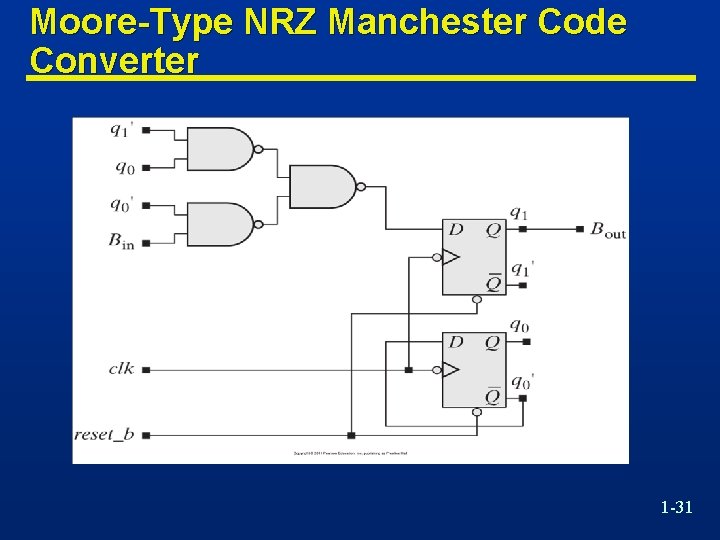

Moore-Type NRZ Manchester Code Converter 1 -31

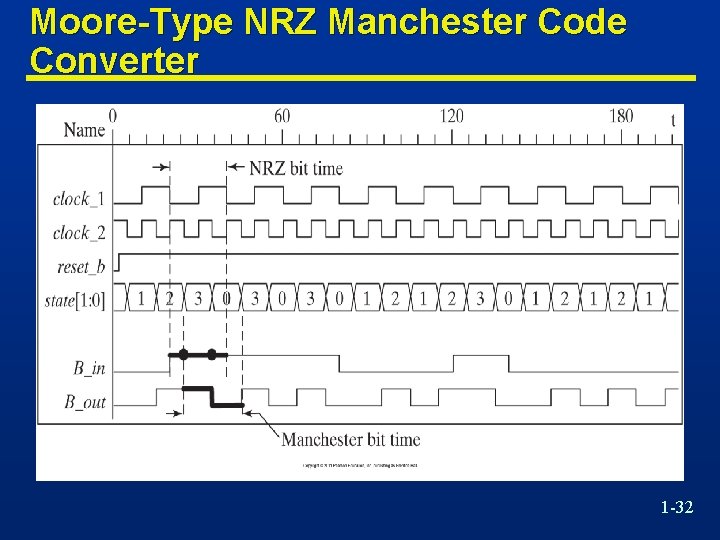

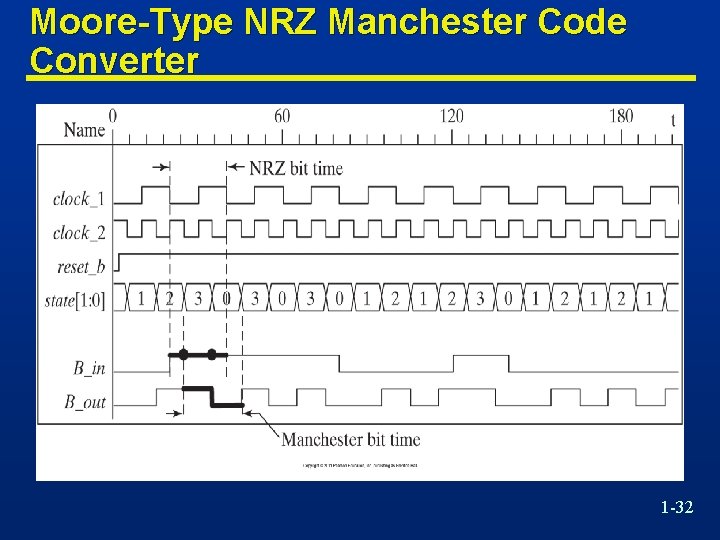

Moore-Type NRZ Manchester Code Converter 1 -32

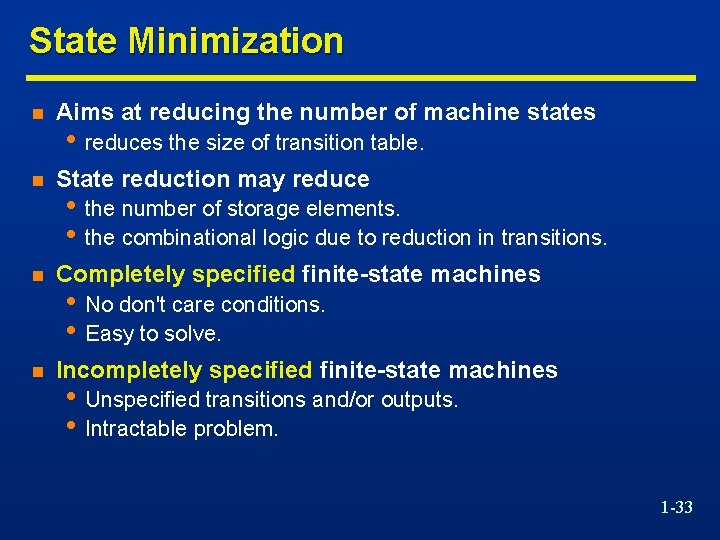

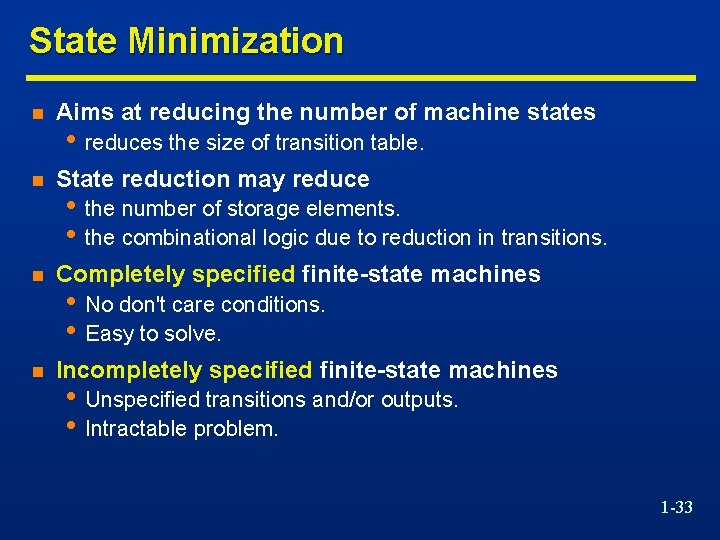

State Minimization n Aims at reducing the number of machine states n State reduction may reduce n Completely specified finite-state machines n Incompletely specified finite-state machines • reduces the size of transition table. • the number of storage elements. • the combinational logic due to reduction in transitions. • No don't care conditions. • Easy to solve. • Unspecified transitions and/or outputs. • Intractable problem. 1 -33

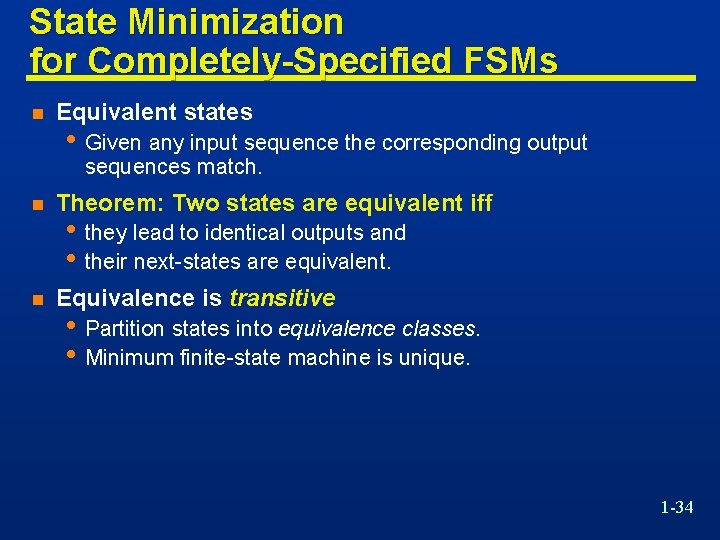

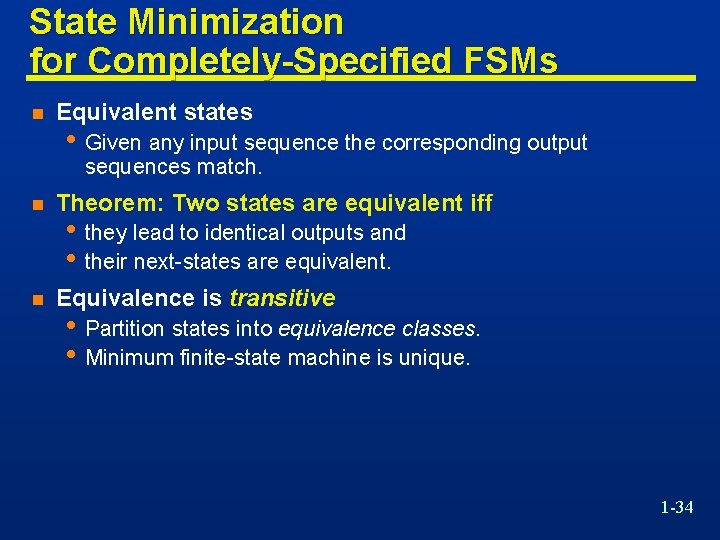

State Minimization for Completely-Specified FSMs n Equivalent states • Given any input sequence the corresponding output sequences match. n Theorem: Two states are equivalent iff n Equivalence is transitive • they lead to identical outputs and • their next-states are equivalent. • Partition states into equivalence classes. • Minimum finite-state machine is unique. 1 -34

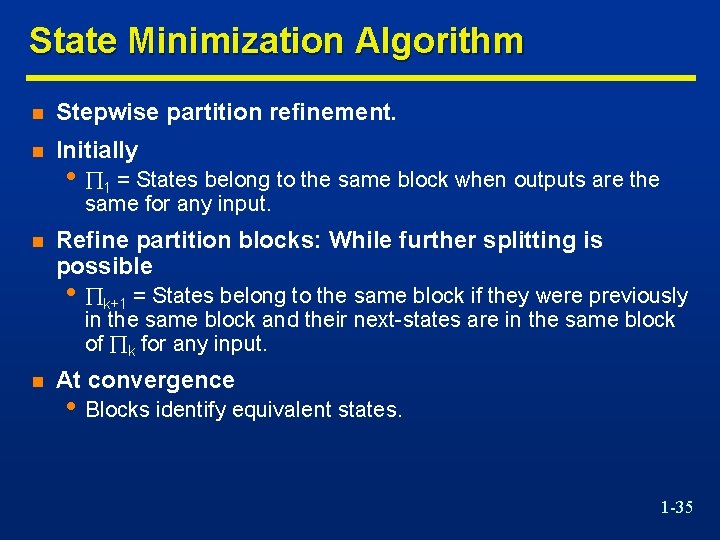

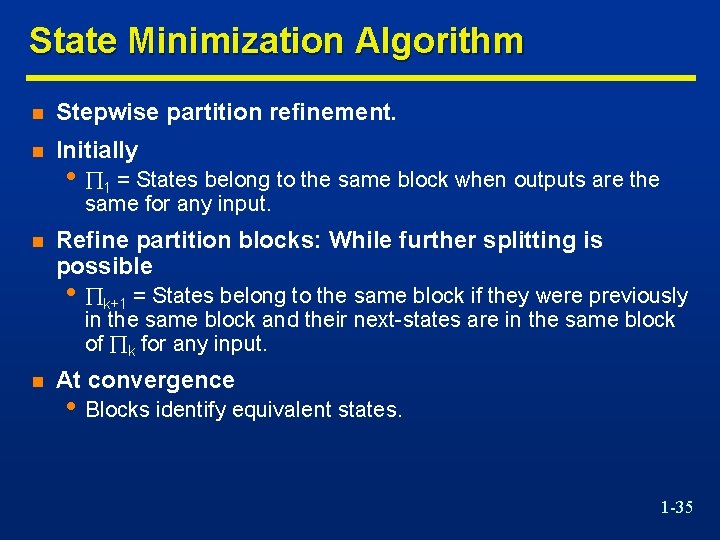

State Minimization Algorithm n Stepwise partition refinement. n Initially • 1 = States belong to the same block when outputs are the same for any input. n Refine partition blocks: While further splitting is possible • k+1 = States belong to the same block if they were previously in the same block and their next-states are in the same block of k for any input. n At convergence • Blocks identify equivalent states. 1 -35

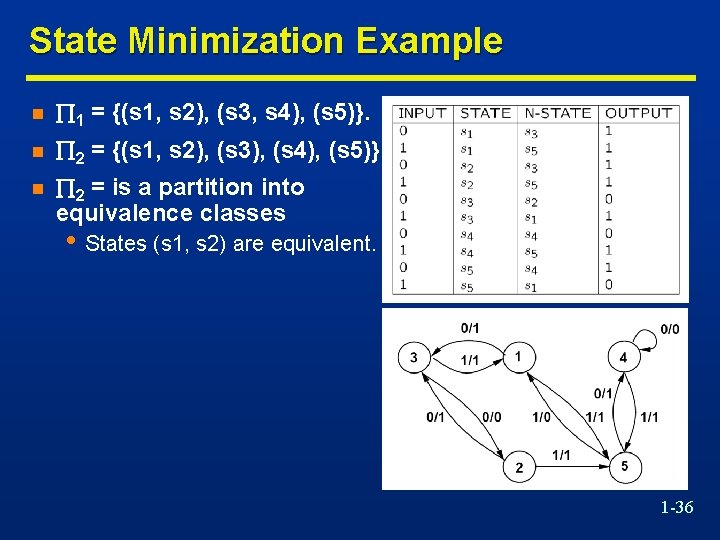

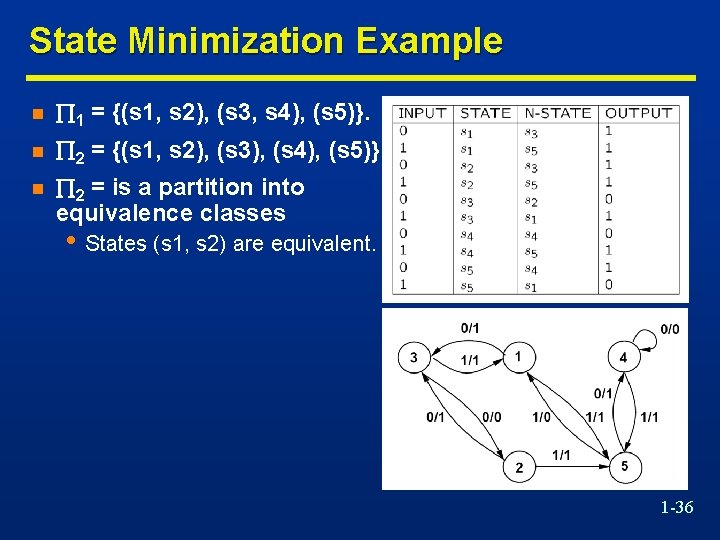

State Minimization Example n 1 = {(s 1, s 2), (s 3, s 4), (s 5)}. n 2 = {(s 1, s 2), (s 3), (s 4), (s 5)}. n 2 = is a partition into equivalence classes • States (s 1, s 2) are equivalent. 1 -36

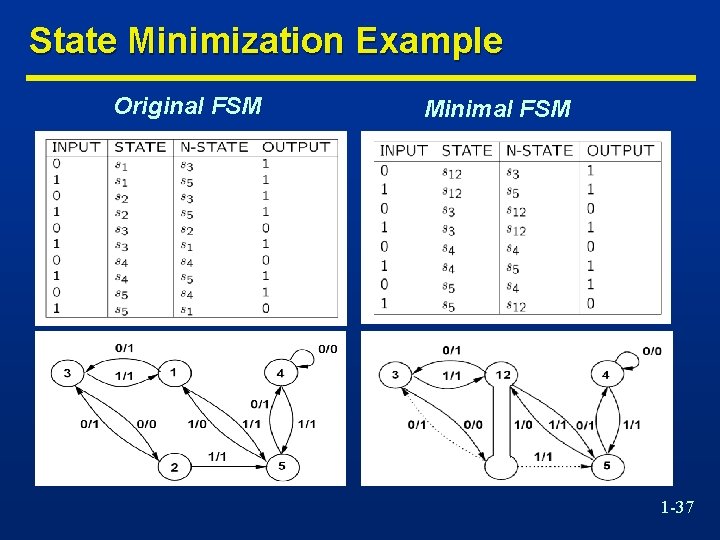

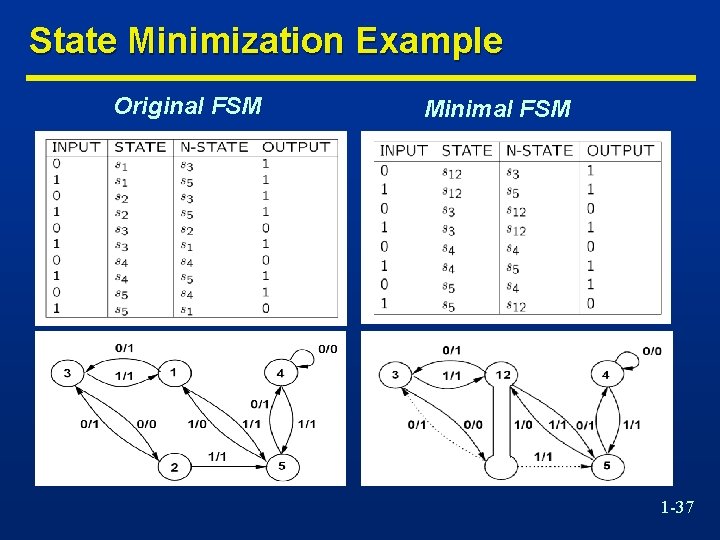

State Minimization Example Original FSM Minimal FSM 1 -37

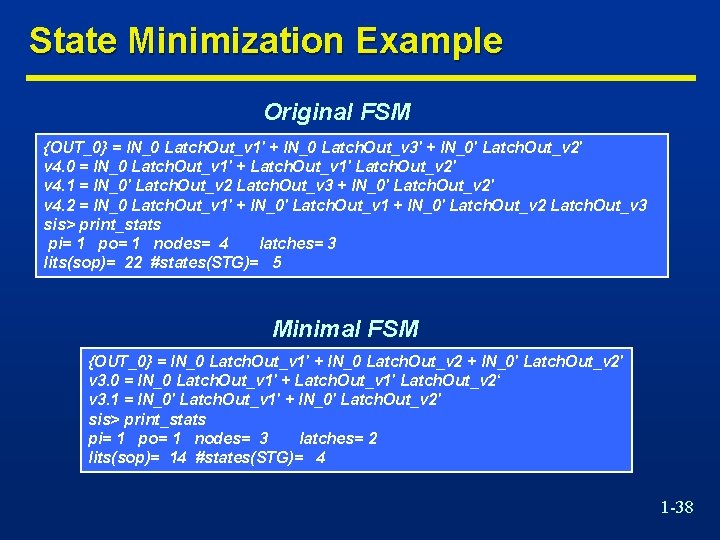

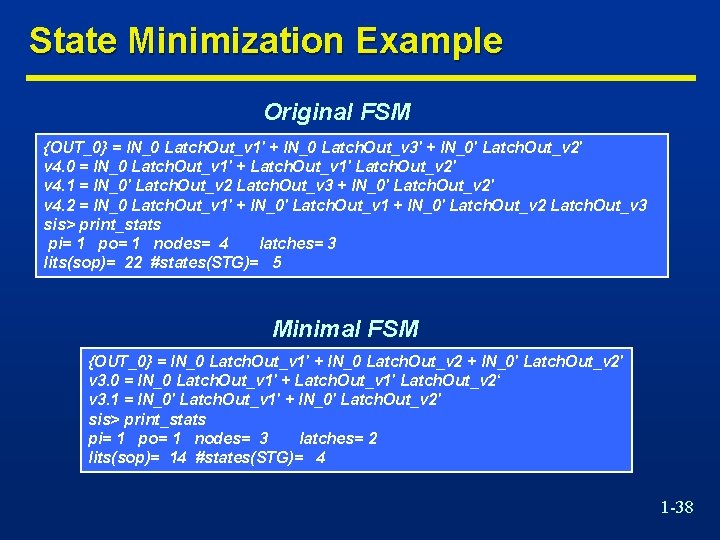

State Minimization Example Original FSM {OUT_0} = IN_0 Latch. Out_v 1' + IN_0 Latch. Out_v 3' + IN_0' Latch. Out_v 2' v 4. 0 = IN_0 Latch. Out_v 1' + Latch. Out_v 1' Latch. Out_v 2' v 4. 1 = IN_0' Latch. Out_v 2 Latch. Out_v 3 + IN_0' Latch. Out_v 2' v 4. 2 = IN_0 Latch. Out_v 1' + IN_0' Latch. Out_v 1 + IN_0' Latch. Out_v 2 Latch. Out_v 3 sis> print_stats pi= 1 po= 1 nodes= 4 latches= 3 lits(sop)= 22 #states(STG)= 5 Minimal FSM {OUT_0} = IN_0 Latch. Out_v 1' + IN_0 Latch. Out_v 2 + IN_0' Latch. Out_v 2' v 3. 0 = IN_0 Latch. Out_v 1' + Latch. Out_v 1' Latch. Out_v 2‘ v 3. 1 = IN_0' Latch. Out_v 1' + IN_0' Latch. Out_v 2' sis> print_stats pi= 1 po= 1 nodes= 3 latches= 2 lits(sop)= 14 #states(STG)= 4 1 -38

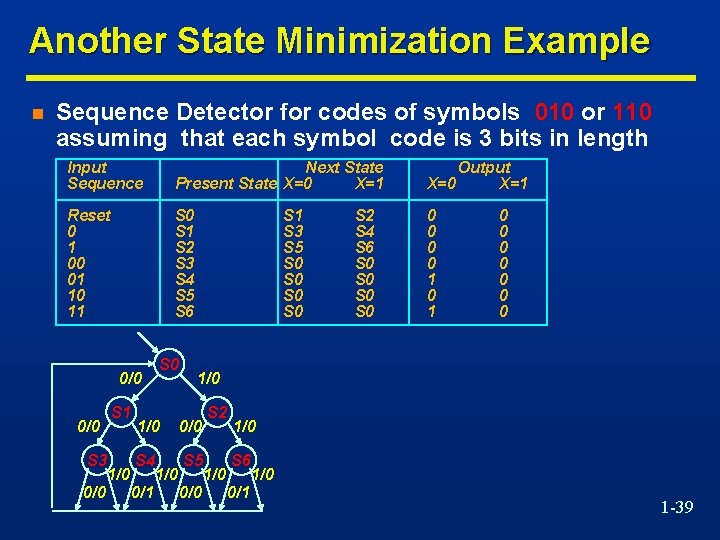

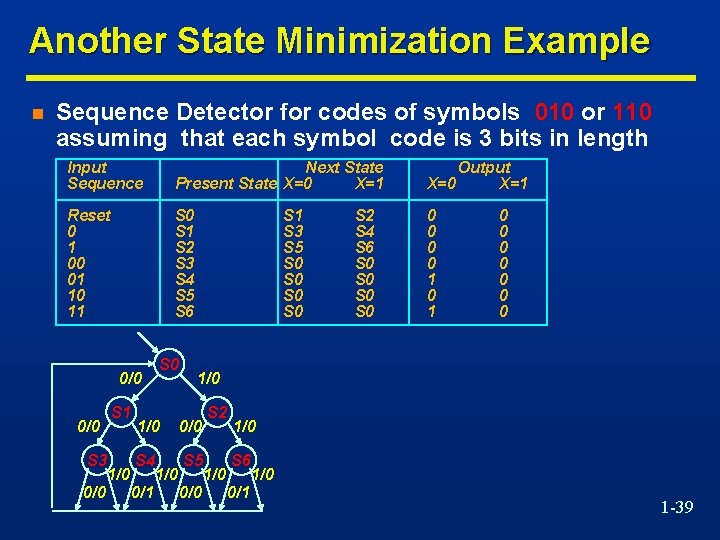

Another State Minimization Example n Sequence Detector for codes of symbols 010 or 110 assuming that each symbol code is 3 bits in length Input Sequence Next State Present State X=0 X=1 Output X=0 X=1 Reset 0 1 00 01 10 11 S 0 S 1 S 2 S 3 S 4 S 5 S 6 0 0 1 0/0 0/0 S 3 0/0 S 1 1/0 S 1 S 3 S 5 S 0 S 0 0/0 S 4 S 5 0/1 0 0 0 0 1/0 1/0 S 2 S 4 S 6 S 0 S 0 0/0 S 2 1/0 S 6 0/1 1/0 1 -39

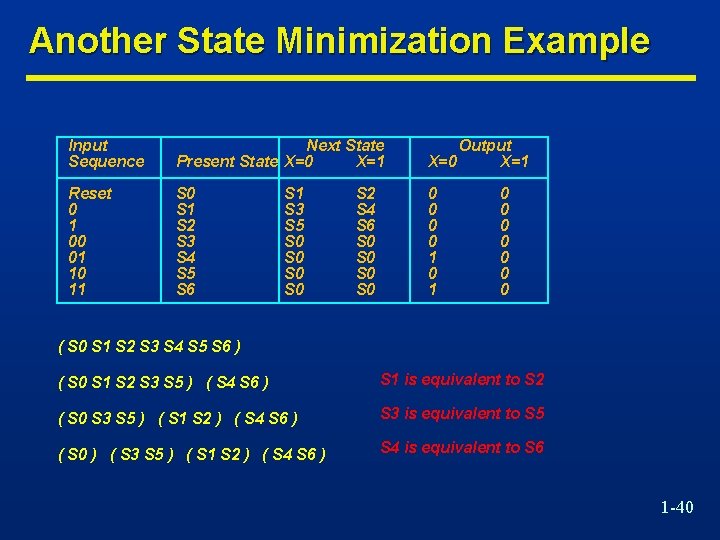

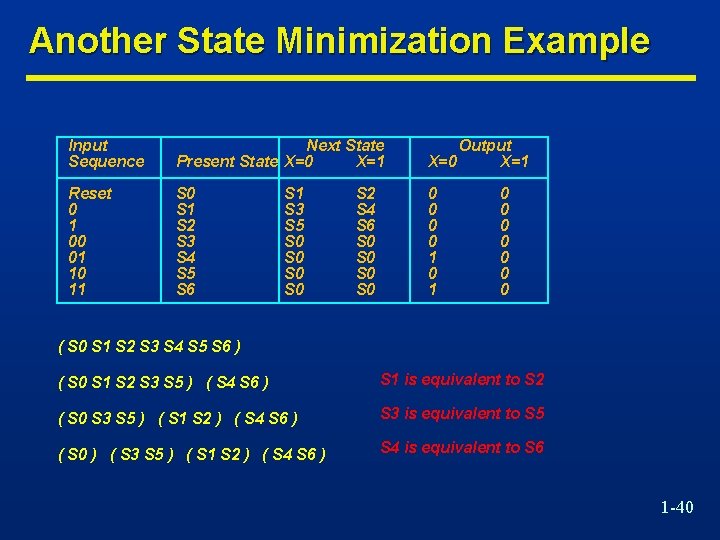

Another State Minimization Example Input Sequence Next State Present State X=0 X=1 Output X=0 X=1 Reset 0 1 00 01 10 11 S 0 S 1 S 2 S 3 S 4 S 5 S 6 0 0 1 0 1 S 3 S 5 S 0 S 0 S 2 S 4 S 6 S 0 S 0 0 0 0 0 ( S 0 S 1 S 2 S 3 S 4 S 5 S 6 ) ( S 0 S 1 S 2 S 3 S 5 ) ( S 4 S 6 ) S 1 is equivalent to S 2 ( S 0 S 3 S 5 ) ( S 1 S 2 ) ( S 4 S 6 ) S 3 is equivalent to S 5 ( S 0 ) ( S 3 S 5 ) ( S 1 S 2 ) ( S 4 S 6 ) S 4 is equivalent to S 6 1 -40

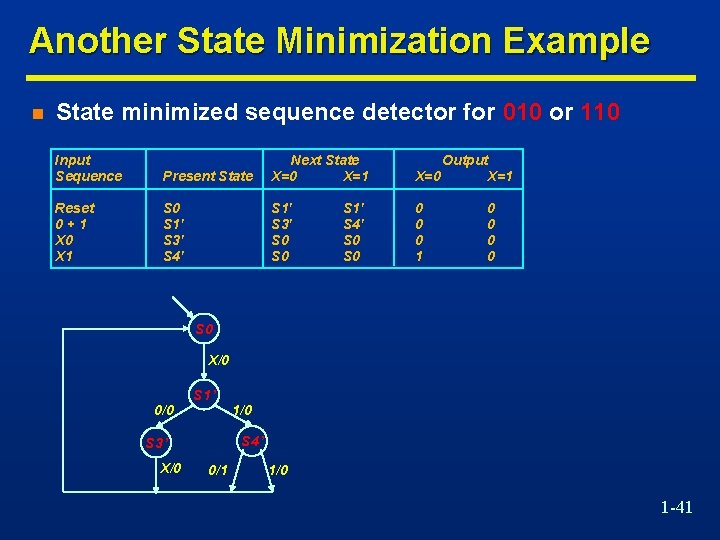

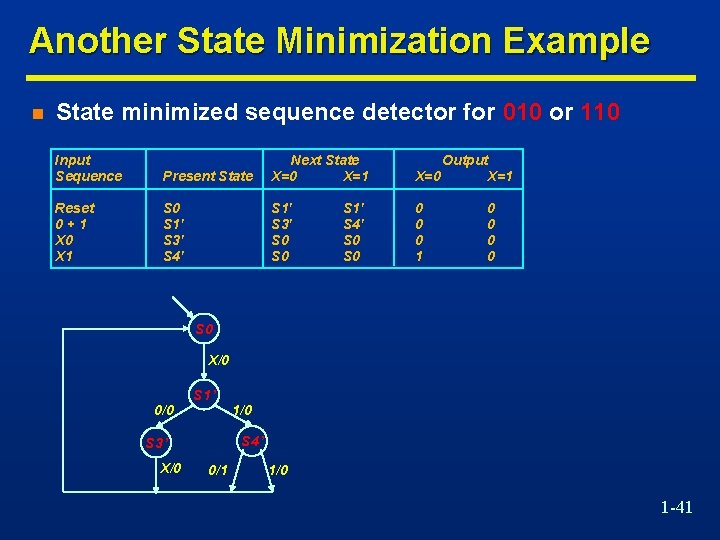

Another State Minimization Example n State minimized sequence detector for 010 or 110 Input Sequence Reset 0+1 X 0 X 1 Present State Next State X=0 X=1 Output X=0 X=1 S 0 S 1' S 3' S 4' S 1' S 3' S 0 0 0 0 1 S 1' S 4' S 0 0 0 S 0 X/0 0/0 S 1’ S 4’ S 3’ X/0 1/0 0/1 1/0 1 -41

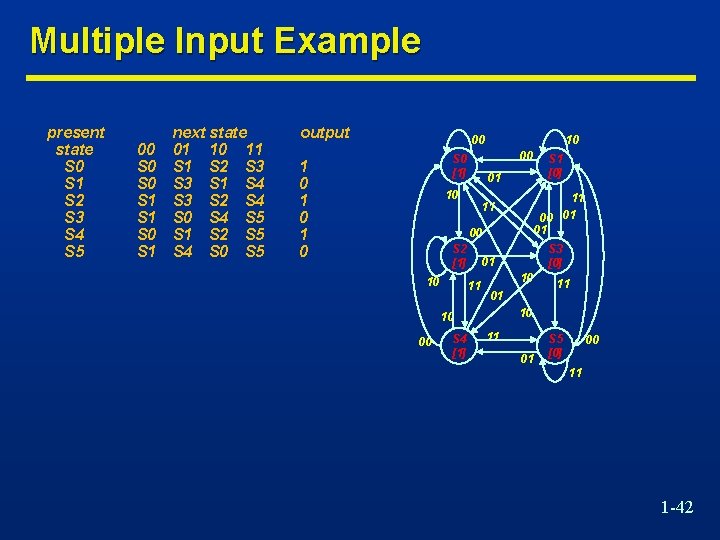

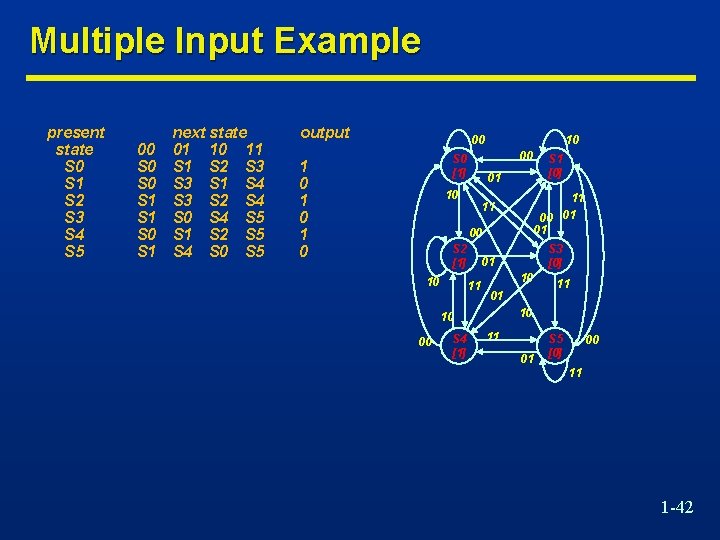

Multiple Input Example present state S 0 S 1 S 2 S 3 S 4 S 5 00 S 0 S 1 next state 01 10 11 S 2 S 3 S 1 S 4 S 3 S 2 S 4 S 0 S 4 S 5 S 1 S 2 S 5 S 4 S 0 S 5 output 00 00 S 0 [1] 1 0 1 0 10 01 10 11 00 01 01 11 00 S 2 [1] 10 11 S 4 [1] S 3 [0] 01 10 01 11 10 10 00 S 1 [0] 11 01 S 5 [0] 00 11 1 -42

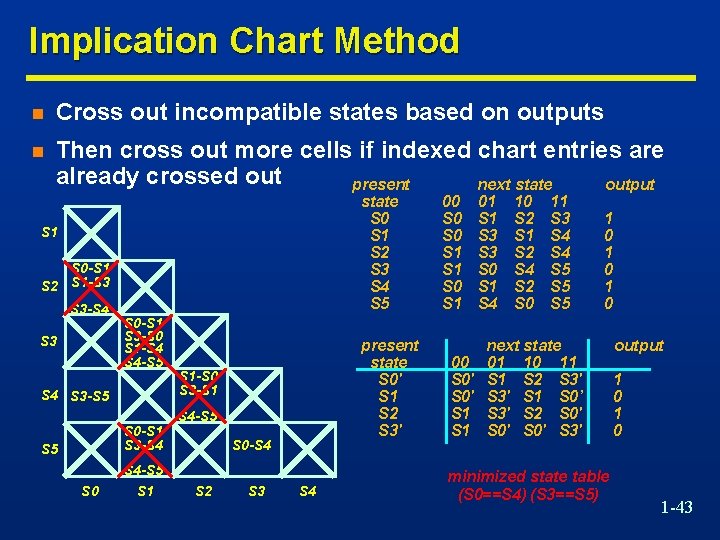

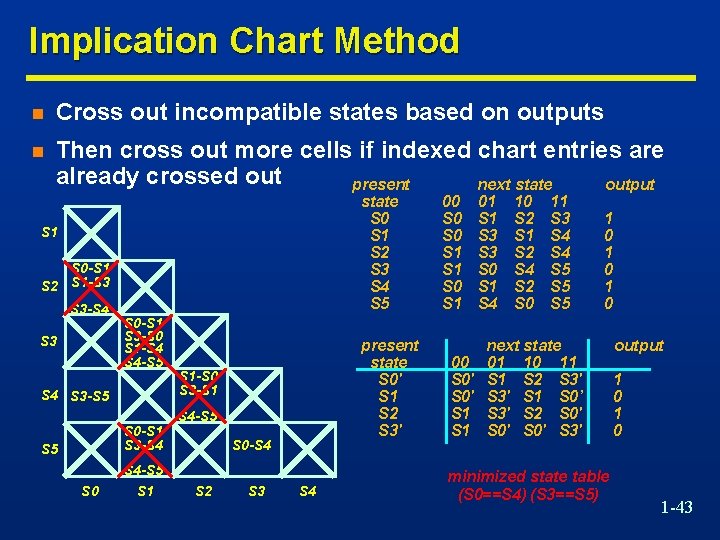

Implication Chart Method n Cross out incompatible states based on outputs n Then cross out more cells if indexed chart entries are already crossed out present next state output state S 0 S 1 S 2 S 3 S 4 S 5 S 1 S 0 -S 1 S 2 S 1 -S 3 S 3 -S 4 S 3 S 0 -S 1 S 3 -S 0 S 1 -S 4 S 4 -S 5 S 4 S 3 -S 5 S 0 -S 1 S 3 -S 4 S 5 present state S 0' S 1 S 2 S 3' S 1 -S 0 S 3 -S 1 S 4 -S 5 S 0 -S 4 S 4 -S 5 S 0 S 1 S 2 S 3 S 4 00 S 0 S 1 00 S 0' S 1 01 S 3 S 0 S 1 S 4 10 S 2 S 1 S 2 S 4 S 2 S 0 11 S 3 S 4 S 5 S 5 1 0 1 0 next state 01 10 11 S 2 S 3' S 1 S 0’ S 3' S 2 S 0' S 3' minimized state table (S 0==S 4) (S 3==S 5) output 1 0 1 -43

State Minimization Computational Complexity n Polynomially-bound algorithm. n There can be at most |S| partition refinements. n Each refinement requires considering each state n Actual time may depend upon • Complexity O(|S|2). • Data-structures. • Implementation details. 1 -44

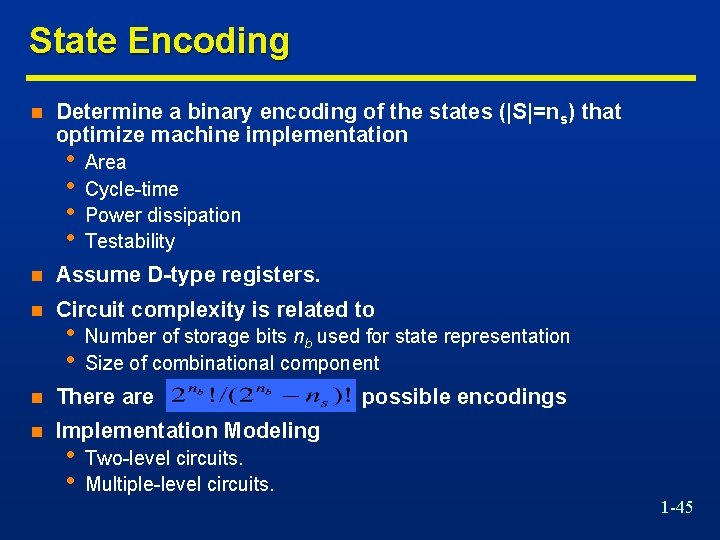

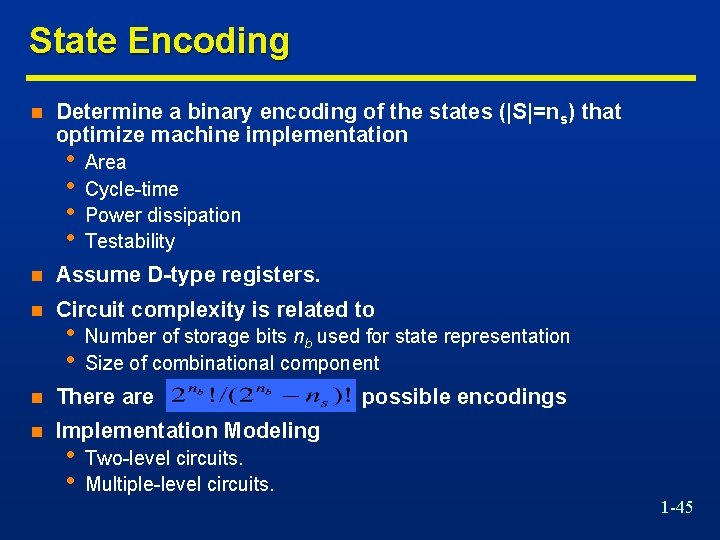

State Encoding n Determine a binary encoding of the states (|S|=ns) that optimize machine implementation • • Area Cycle-time Power dissipation Testability n Assume D-type registers. n Circuit complexity is related to • • Number of storage bits nb used for state representation Size of combinational component n There are n Implementation Modeling • • possible encodings Two-level circuits. Multiple-level circuits. 1 -45

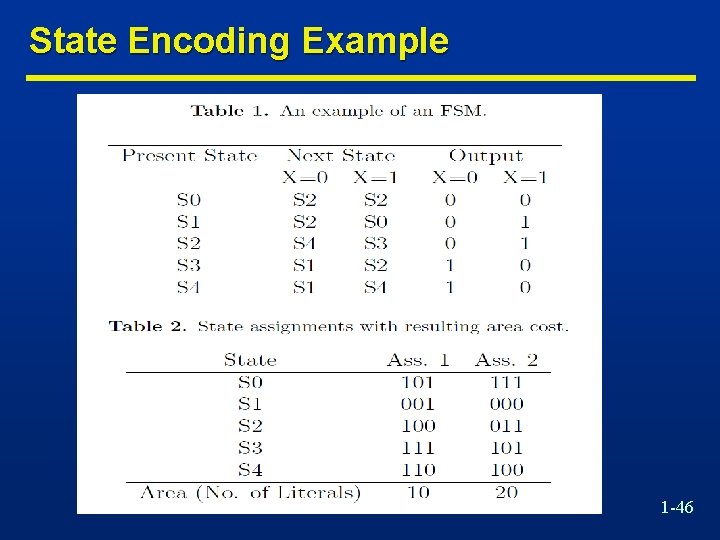

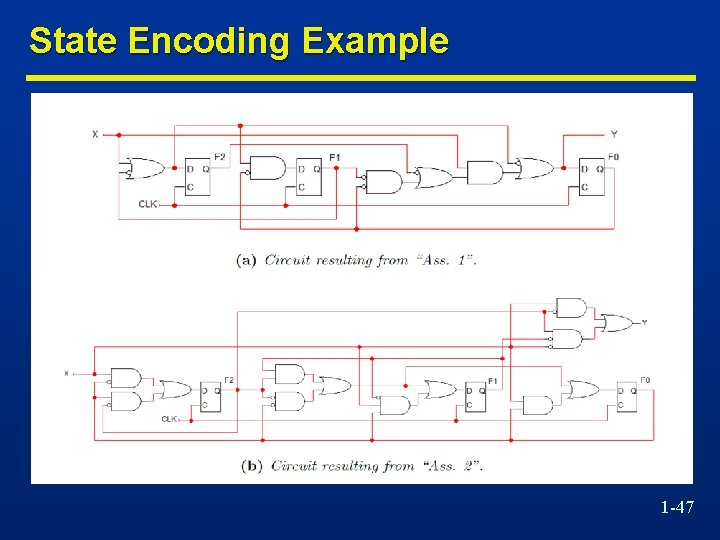

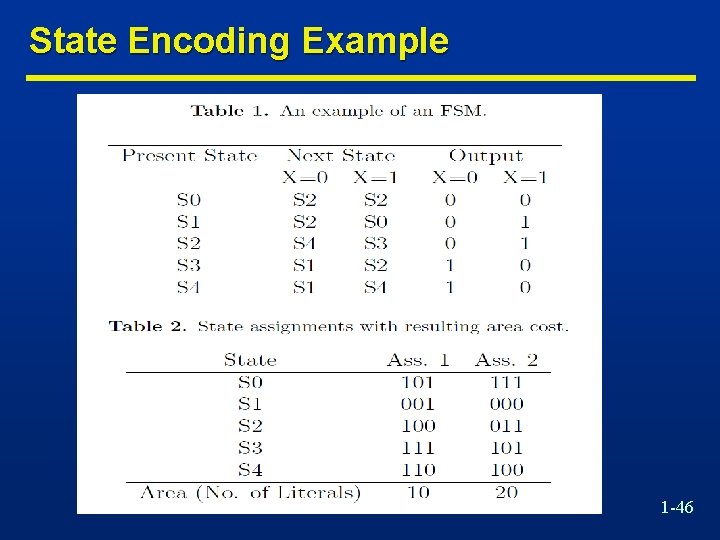

State Encoding Example 1 -46

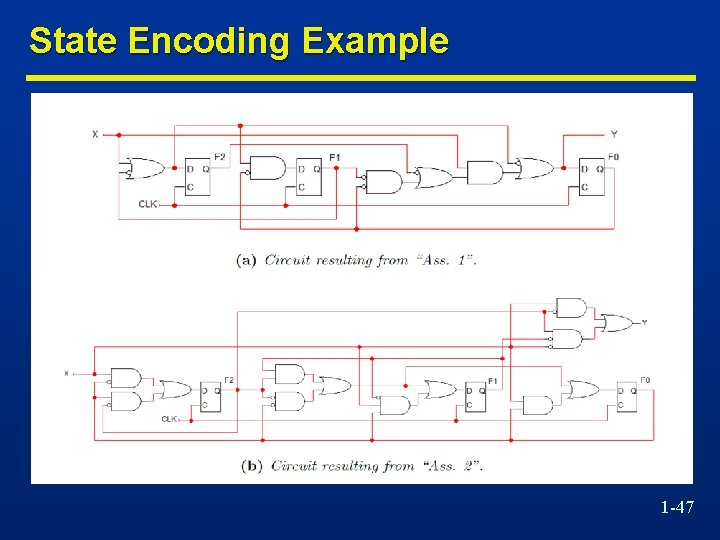

State Encoding Example 1 -47

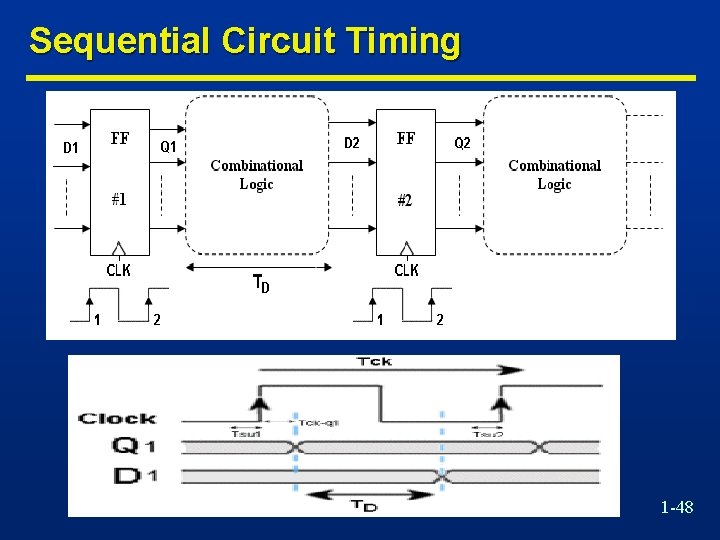

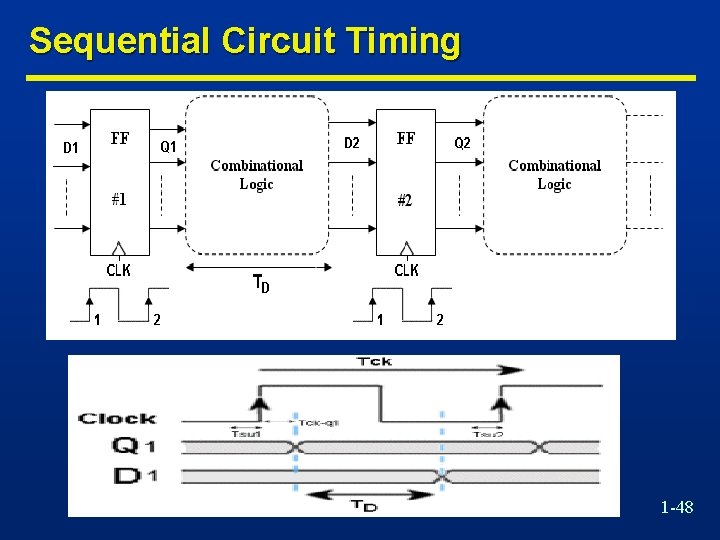

Sequential Circuit Timing 1 -48

Timing Constraints n TD = worst case delay through combinational logic n TSU = FF set up time – Minimum time before the clock edge where the input data must be ready and stable n Tclk Q = Clock to Q delay – Time between clock edge and data appearing at the output of the FF n THold = FF hold time – Minimum time after the clock edge where data has to remain stable (held stable) n Based on the FF & combinational logic timing parameters, the following timing constraints are obtained for correct operation of the circuit: Tclk ≥ Tclk q 1 + TD + Tsu 1 -49

Timing Constraints n The previous equation assumes that the clock arrives at all FFs, at exactly the same time! n Clock Skew (Tskew) is the delay between clocks at different chip locations. n To take Clock Skew into account: Tclk ≥ Tclk q 1 + TD + Tsu + Tskew n Clock Signals will have random variations in their Periods and Frequencies, called Jitter. n The latest arrival time minus the earliest arrival time during an observed period of time is called the "peak to peak jitter amplitude". n We have to take the Peak to Peak Jitter (TP-P Jitter) into account Tclk ≥ T clk q 1 + TD + Tsu + Tskew + TP-P Jitter 1 -50

Timing Constraints n Another Timing Constraint arises in situations where TD is "Zero" or very small when the output of a FF is fed directly to the input of another (e. g. in Shift Registers). n In such situation, we need to make sure that the data does not pass through two FFs (during the transparency window of the FF where both master and slave are enabled). n Hence to avoid Hold Time violation: Tskew + TP-P Jitter + Thold 2 ≤ Tck q 1 + TD where Thold 2 is the hold time of the 2 nd FF 1 -51

Metastability n Whenever there are setup and hold time violations in any flip-flop, it enters a state where its output is unpredictable: this state is known as metastable state (quasi stable state) n At the end of metastable state, the flip-flop settles down to either '1' or '0'. This whole process is known as metastability. n When a flip-flop is in metastable state, its output oscillates between '0' and '1‘. How long it takes to settle down, depends on the technology of the flip-flop. n Metastability occurs when the input signal is an asynchronous signal. 1 -52

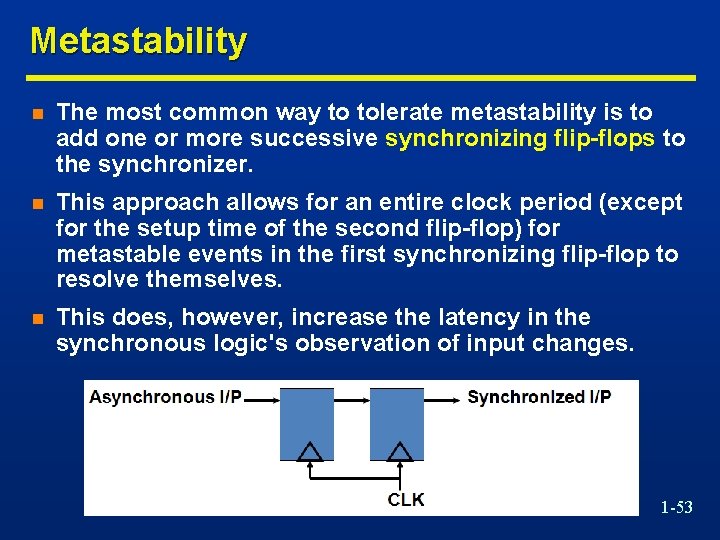

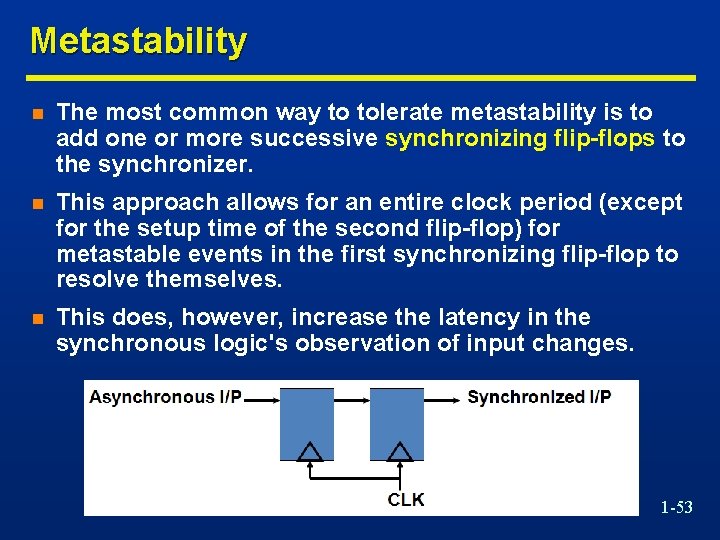

Metastability n The most common way to tolerate metastability is to add one or more successive synchronizing flip-flops to the synchronizer. n This approach allows for an entire clock period (except for the setup time of the second flip-flop) for metastable events in the first synchronizing flip-flop to resolve themselves. n This does, however, increase the latency in the synchronous logic's observation of input changes. 1 -53