Lecture 24 More Sequential Circuit Analysis and Design

- Slides: 53

Lecture 24 More Sequential Circuit Analysis and Design 1

Analysis by Signal Tracing We can analyze clocked sequential circuits to find the output sequence resulting from a given input sequence by tracing 0 and 1 signals through the circuit. The basic procedure is: 1. Assume an initial state of the flip-flops (all flip-flops reset to 0 unless otherwise specified). 2. For the first input in the given sequence, determine the circuit output(s) and flip-flop inputs. 3. Determine the new set of flip-flop states after the next active clock edge. 4. Determine the output(s) that corresponds to the new states. 5. Repeat 2, 3, and 4 for each input in the given sequence. 2

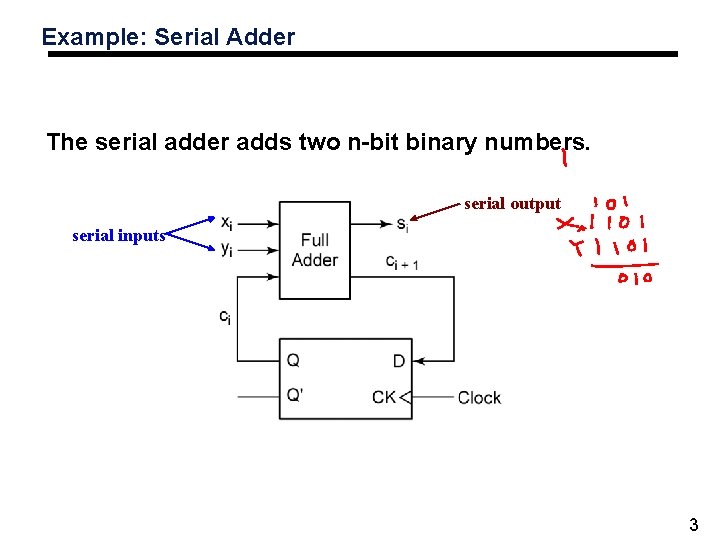

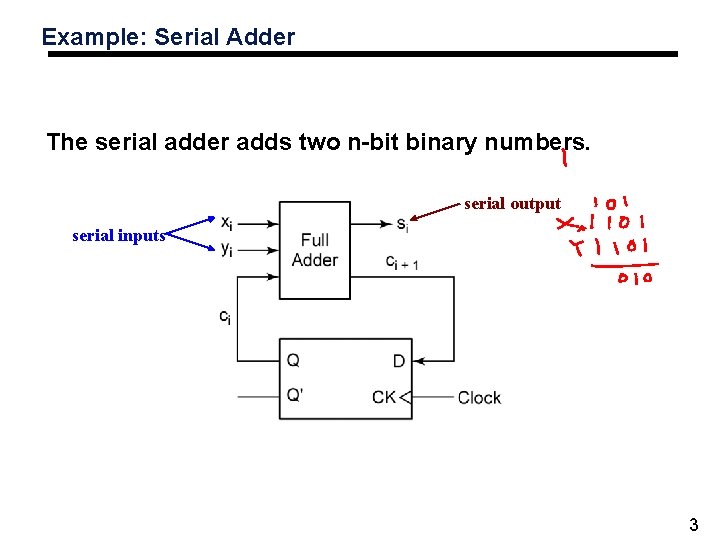

Example: Serial Adder The serial adder adds two n-bit binary numbers. serial output serial inputs 3

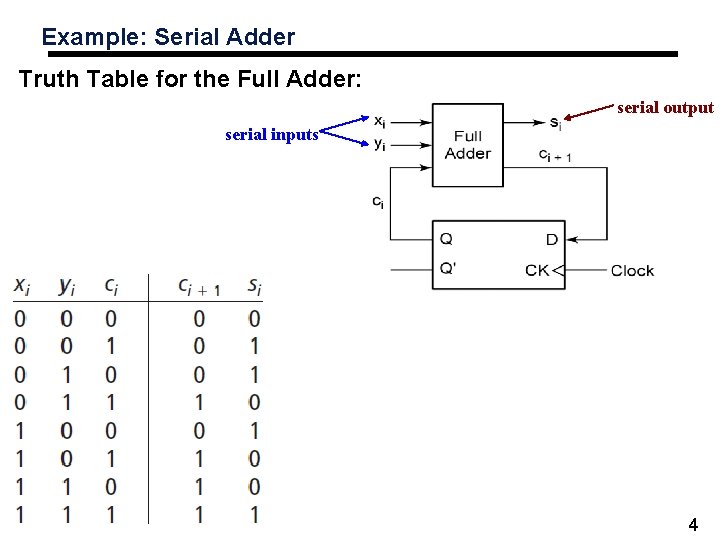

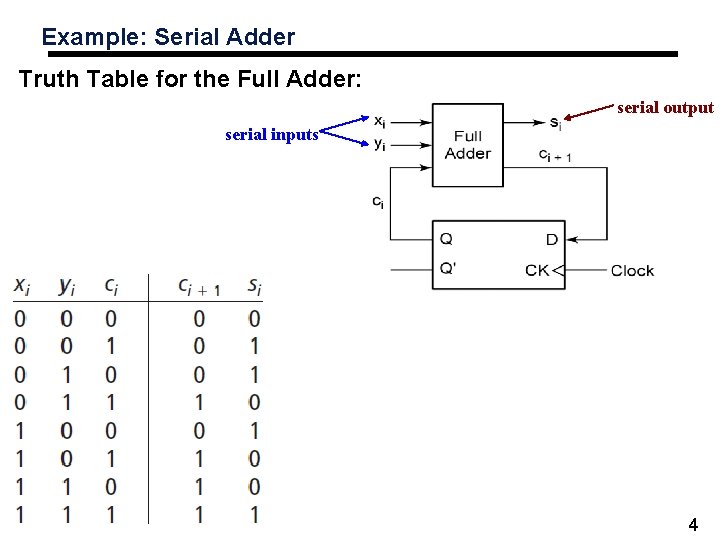

Example: Serial Adder Truth Table for the Full Adder: serial output serial inputs 4

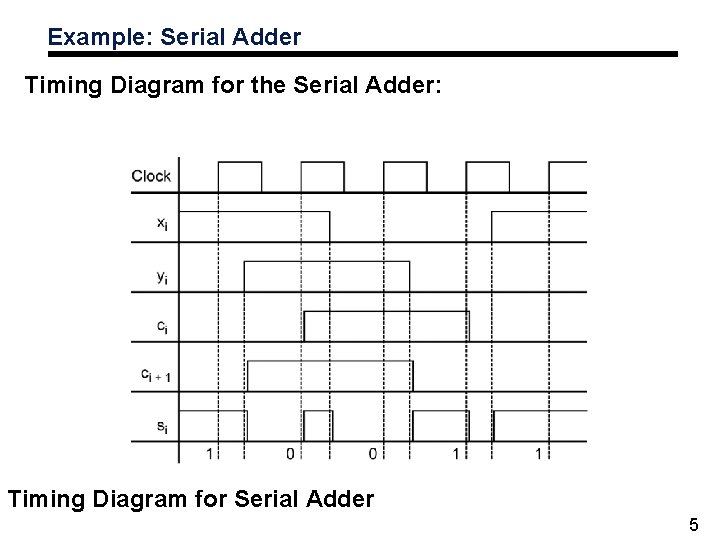

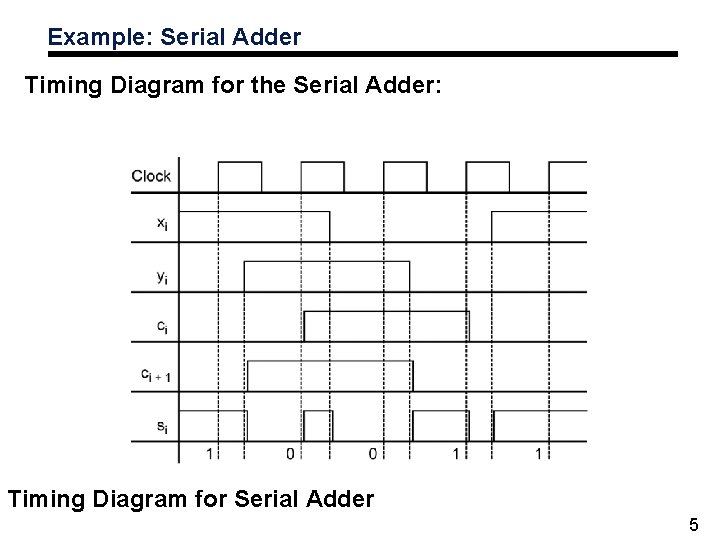

Example: Serial Adder Timing Diagram for the Serial Adder: Timing Diagram for Serial Adder 5

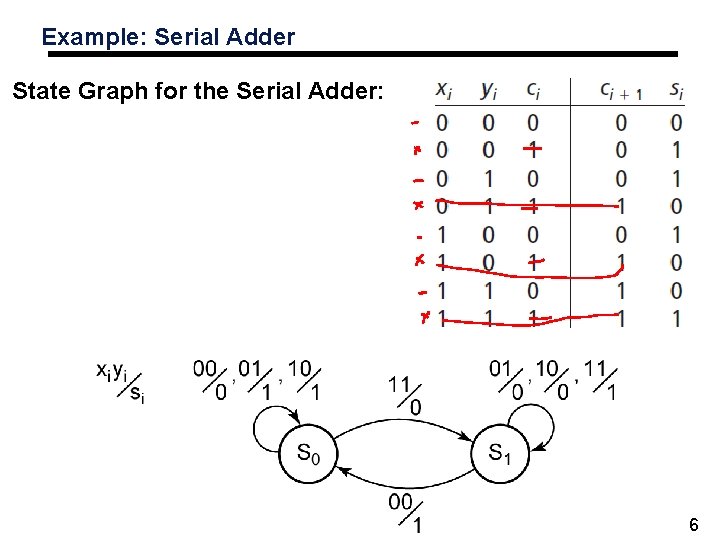

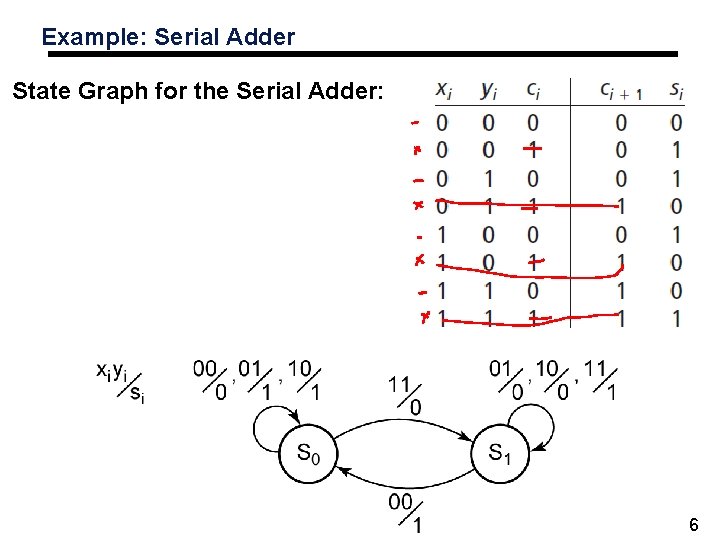

Example: Serial Adder State Graph for the Serial Adder: 6

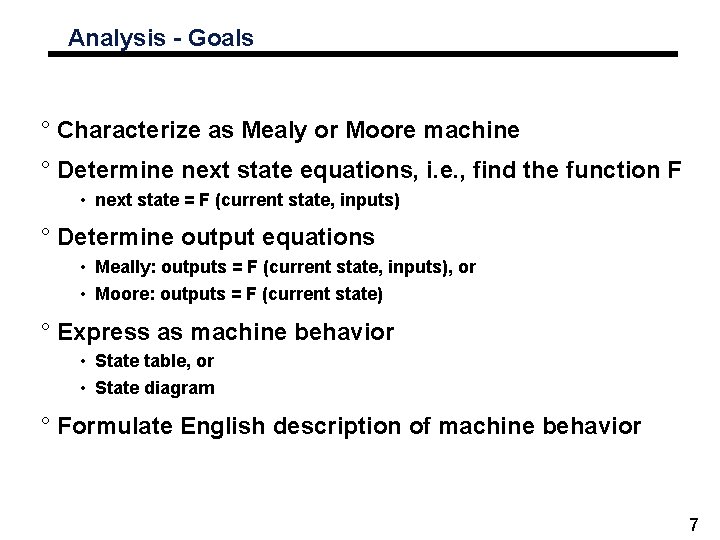

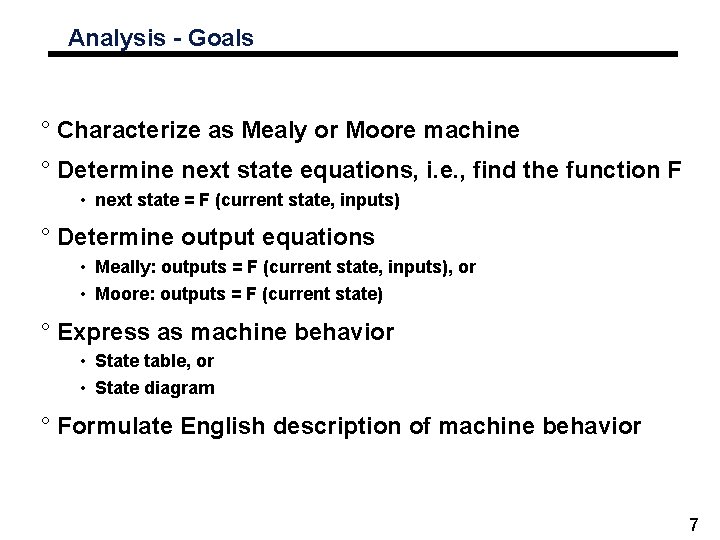

Analysis - Goals ° Characterize as Mealy or Moore machine ° Determine next state equations, i. e. , find the function F • next state = F (current state, inputs) ° Determine output equations • Meally: outputs = F (current state, inputs), or • Moore: outputs = F (current state) ° Express as machine behavior • State table, or • State diagram ° Formulate English description of machine behavior 7

8

State Reduction and Assignment ° Analysis of sequential circuits starts from a circuit diagram and culminates in a state table or diagram. ° Design of a sequential circuit starts from a set of specifications and culminates in a logic diagram ° Any design process must consider the problem of minimizing the cost of the final circuit ° Two most obvious cost reductions are • Reductions in the number of flip-flops • Reductions in the number of gates ° Reduction of the number of flip-flops in a sequential circuit is referred to as the state-reduction problem ° State-reduction algorithms are concerned with procedures for reducing the number of states in a state table while keeping the external input-output requirements unchanged 9

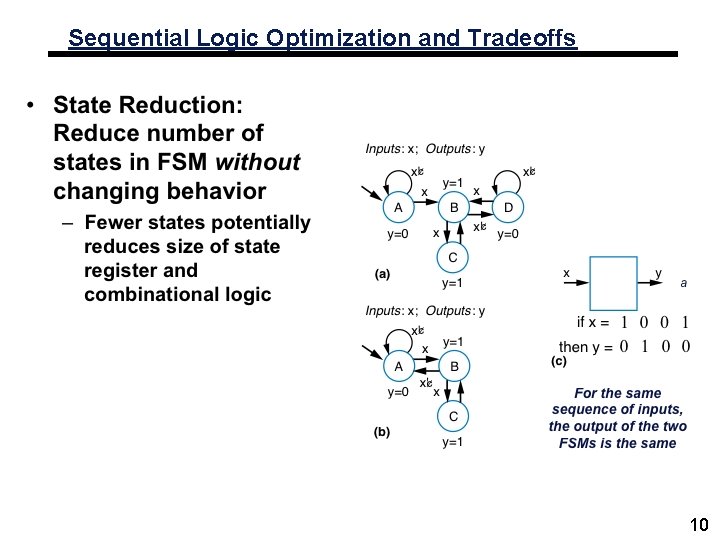

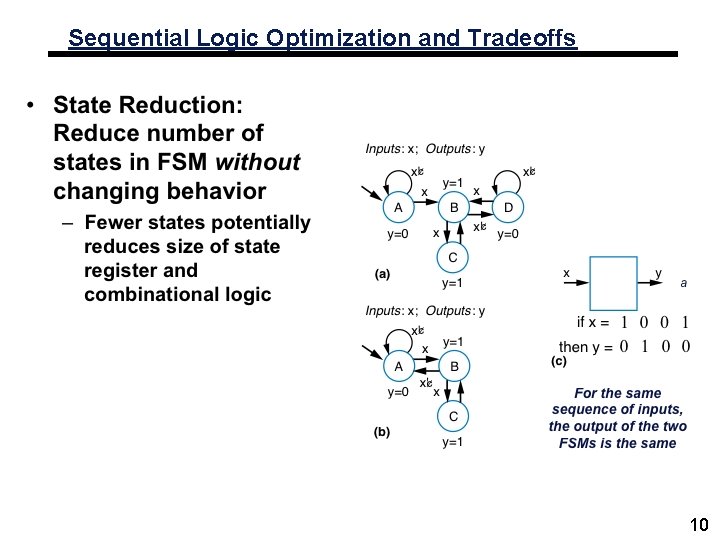

Sequential Logic Optimization and Tradeoffs 10

State Reduction and Assignment ° Pros and Cons of State Reduction Pros ° Since m flip-flops produce 2 m states, a reduction in the number of states may (or may not) result in a reduction in the number of flip-flops. Cons ° Sometimes the reduction in the number of Flip Flops results in the additional number of combinational gates, so the combinational logic may increase 11

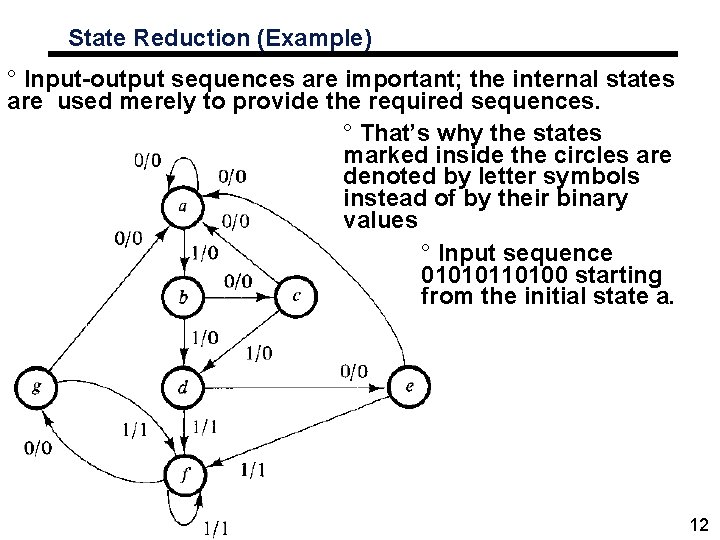

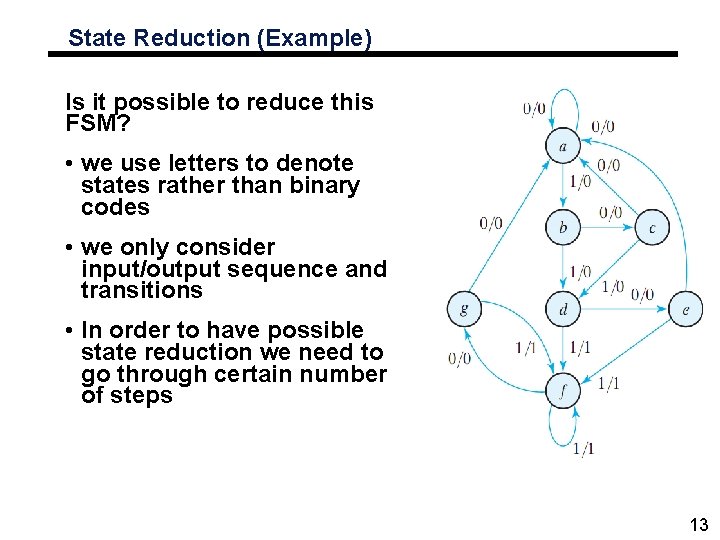

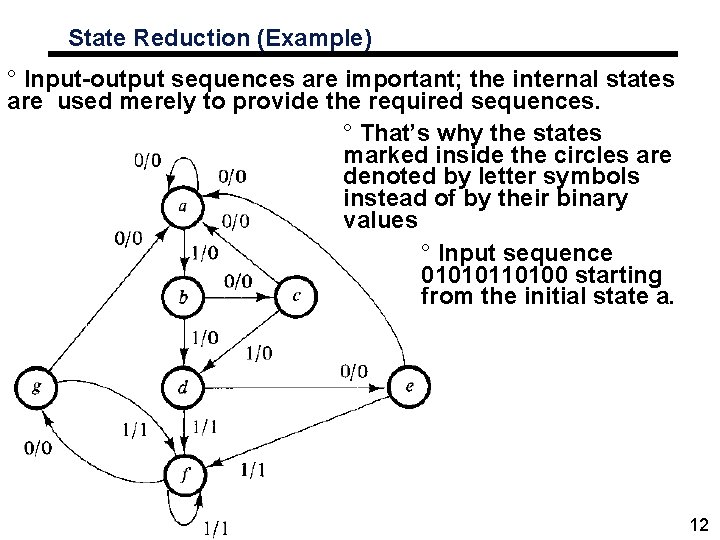

State Reduction (Example) ° Input-output sequences are important; the internal states are used merely to provide the required sequences. ° That’s why the states marked inside the circles are denoted by letter symbols instead of by their binary values ° Input sequence 01010110100 starting from the initial state a. 12

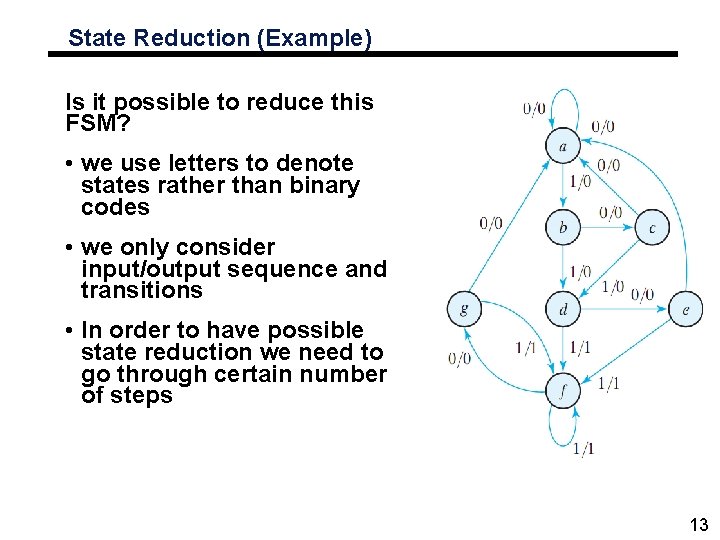

State Reduction (Example) Is it possible to reduce this FSM? • we use letters to denote states rather than binary codes • we only consider input/output sequence and transitions • In order to have possible state reduction we need to go through certain number of steps 13

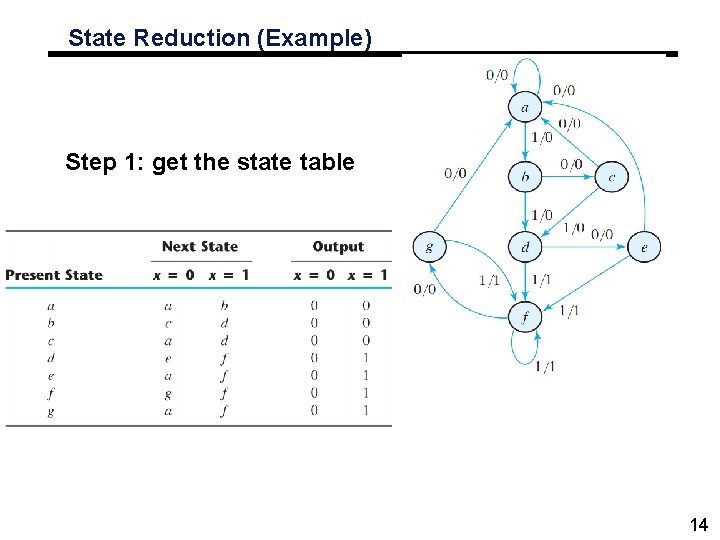

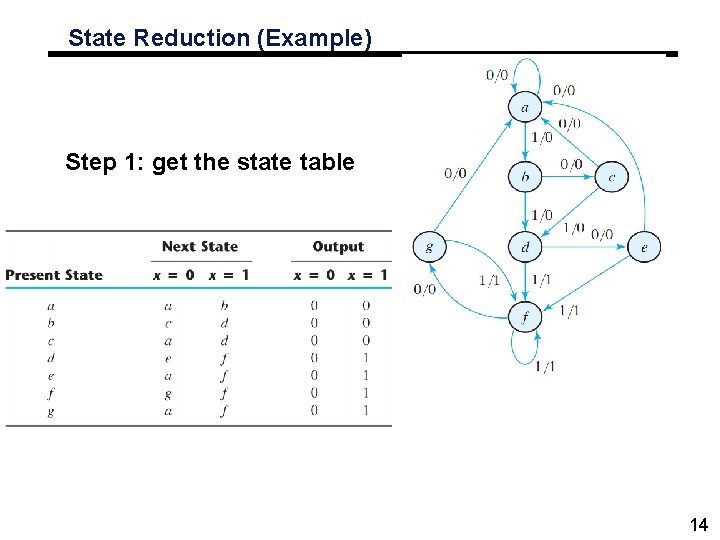

State Reduction (Example) Step 1: get the state table 14

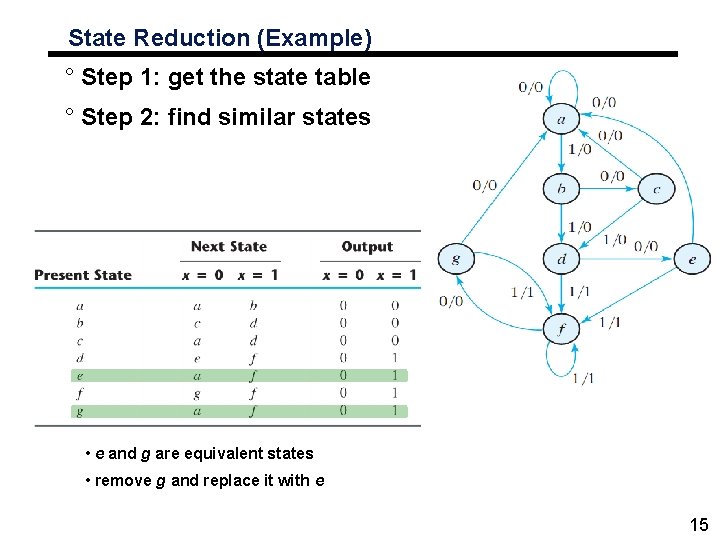

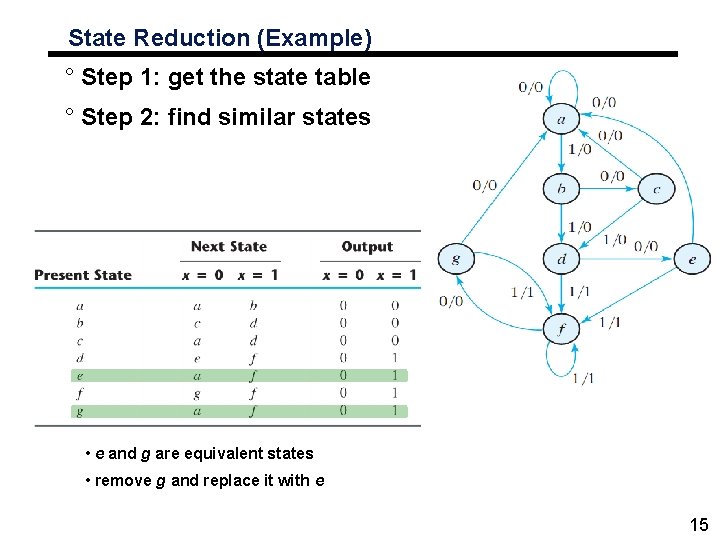

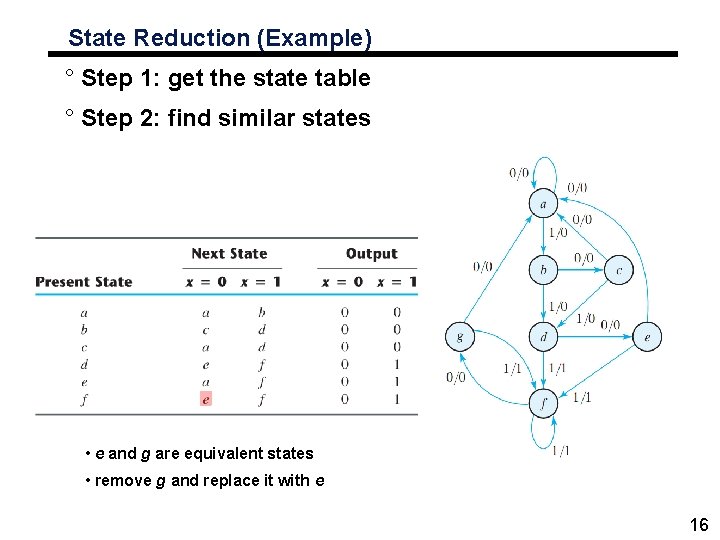

State Reduction (Example) ° Step 1: get the state table ° Step 2: find similar states • e and g are equivalent states • remove g and replace it with e 15

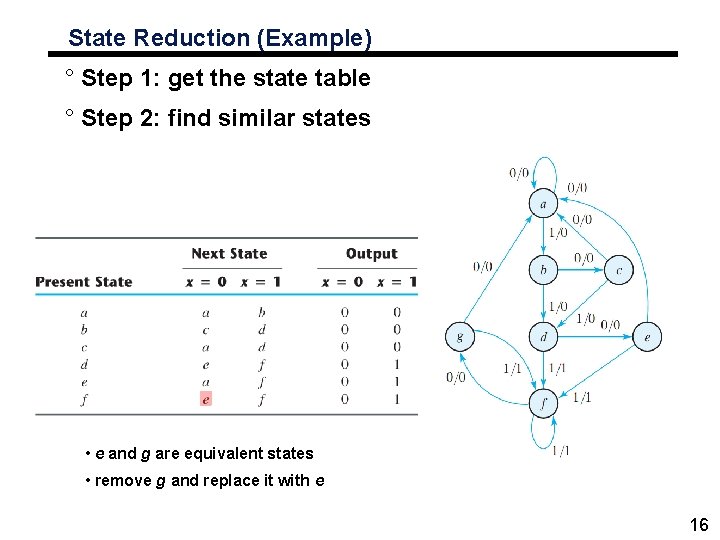

State Reduction (Example) ° Step 1: get the state table ° Step 2: find similar states • e and g are equivalent states • remove g and replace it with e 16

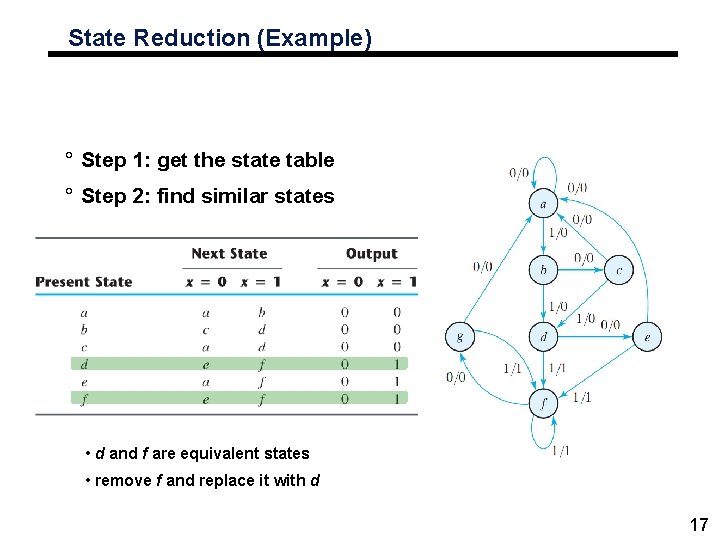

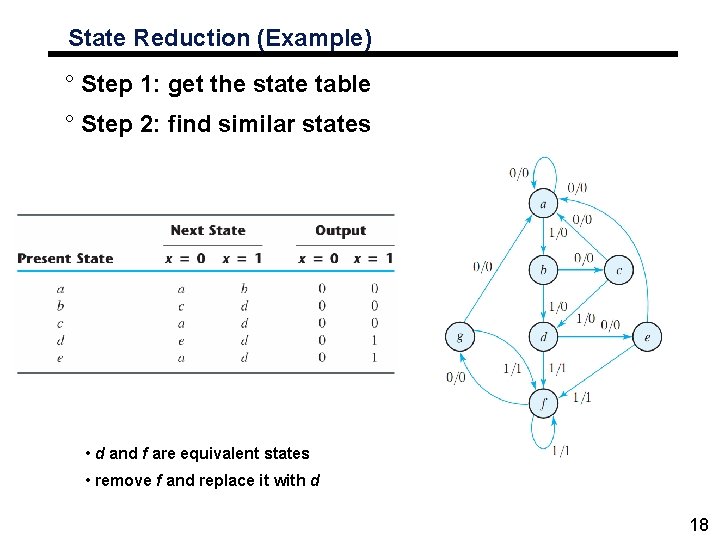

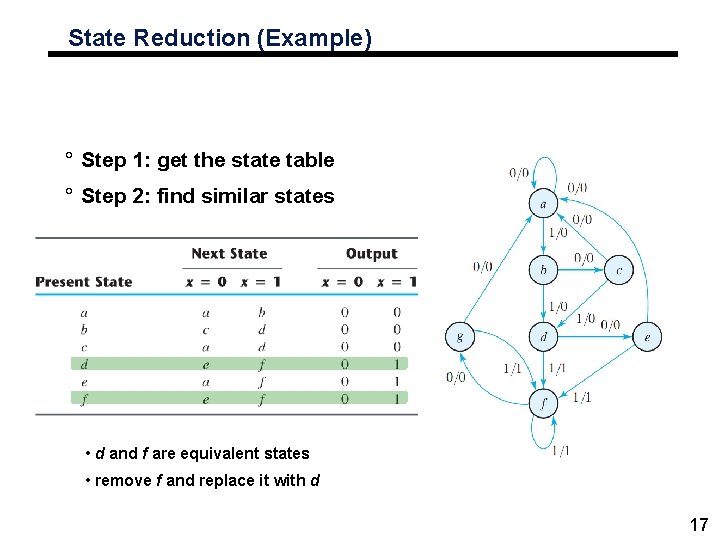

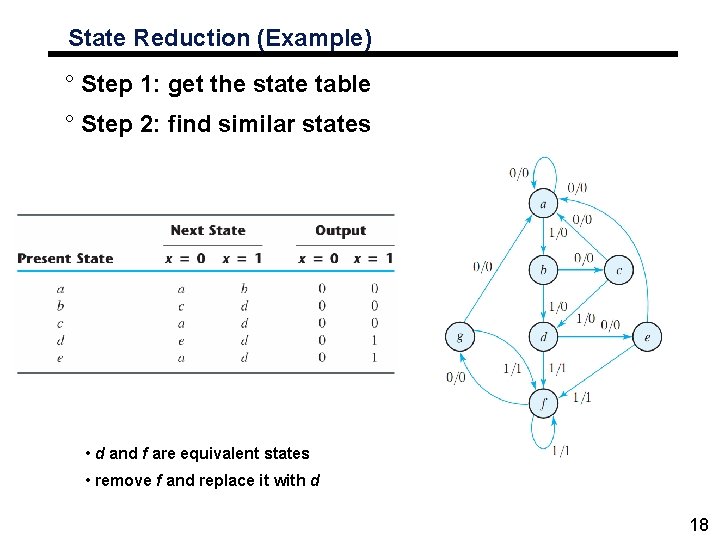

State Reduction (Example) ° Step 1: get the state table ° Step 2: find similar states • d and f are equivalent states • remove f and replace it with d 17

State Reduction (Example) ° Step 1: get the state table ° Step 2: find similar states • d and f are equivalent states • remove f and replace it with d 18

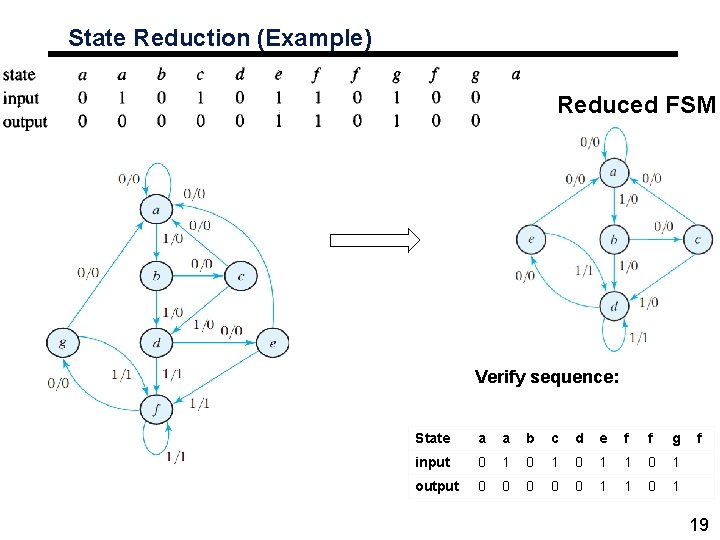

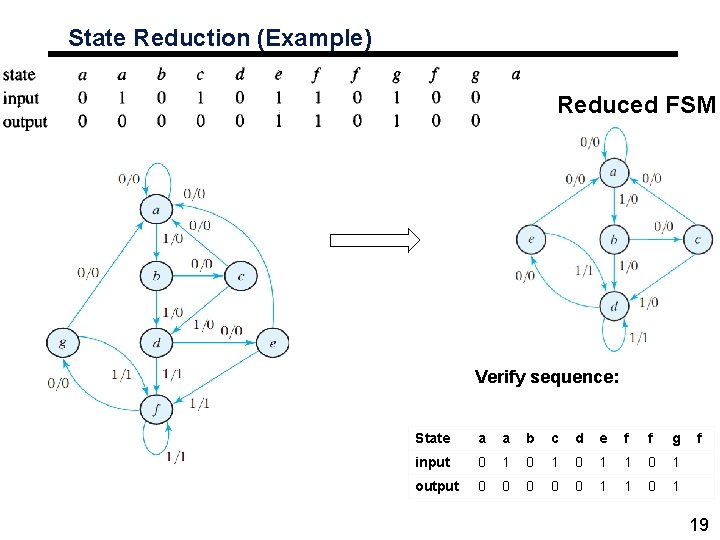

State Reduction (Example) Reduced FSM Verify sequence: State a a b c d e f f g input 0 1 0 1 output 0 0 0 1 1 0 1 f 19

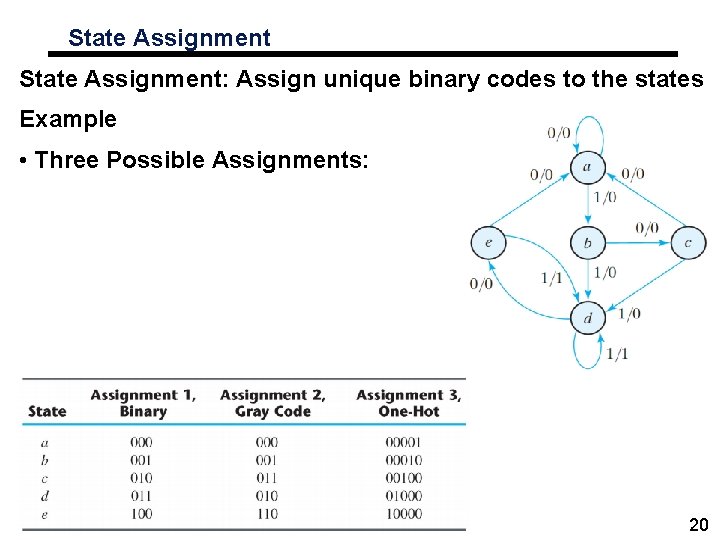

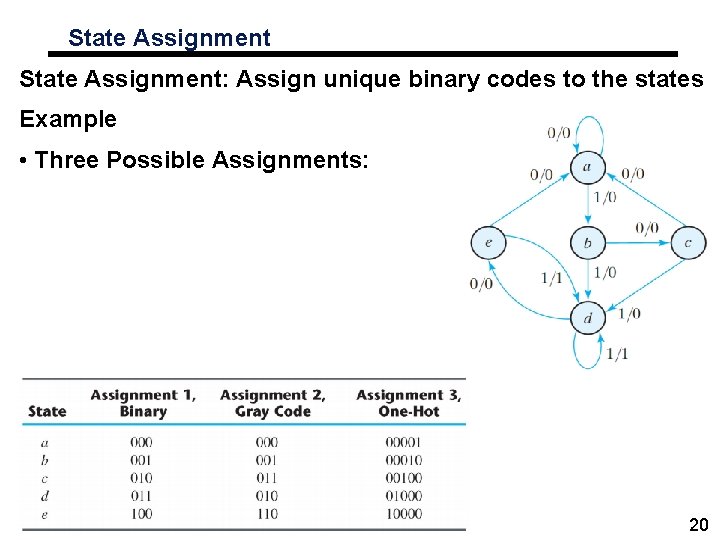

State Assignment: Assign unique binary codes to the states Example • Three Possible Assignments: 20

Design of Synchronous Sequential Circuits • Obtain a state diagram • State reduction if necessary • Obtain State Table • State Assignment • Choose type of flip-flops • Use FF’s excitation table to complete the table • Derive state equations • Use K-Maps • Obtain the FF input equations and the output equations • Draw the circuit diagram 21

22

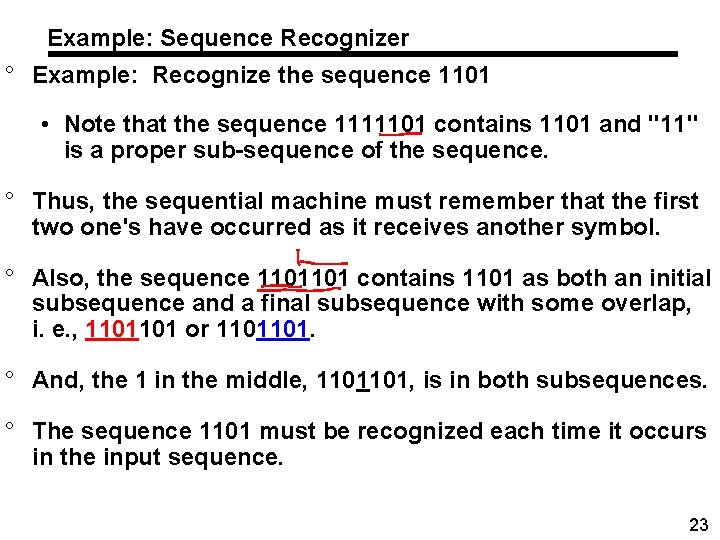

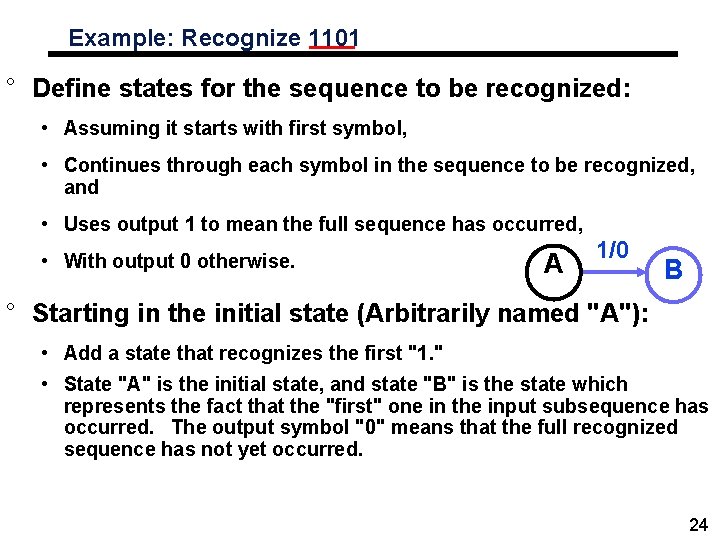

Example: Sequence Recognizer ° Example: Recognize the sequence 1101 • Note that the sequence 1111101 contains 1101 and "11" is a proper sub-sequence of the sequence. ° Thus, the sequential machine must remember that the first two one's have occurred as it receives another symbol. ° Also, the sequence 1101101 contains 1101 as both an initial subsequence and a final subsequence with some overlap, i. e. , 1101101 or 1101101. ° And, the 1 in the middle, 1101101, is in both subsequences. ° The sequence 1101 must be recognized each time it occurs in the input sequence. 23

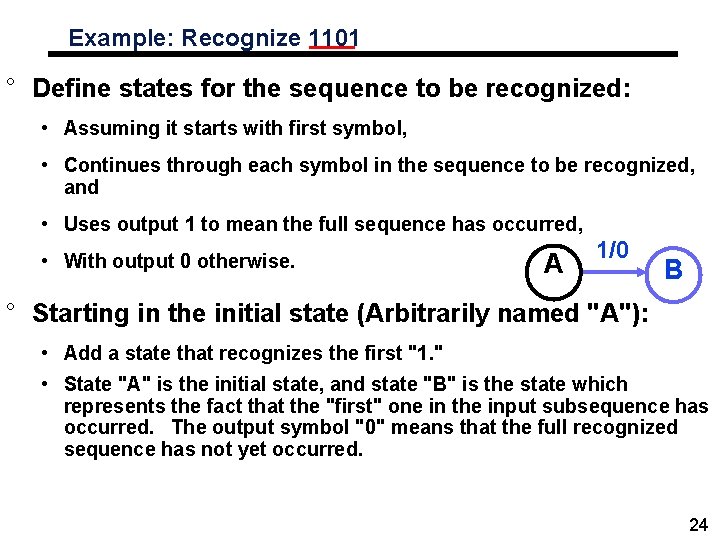

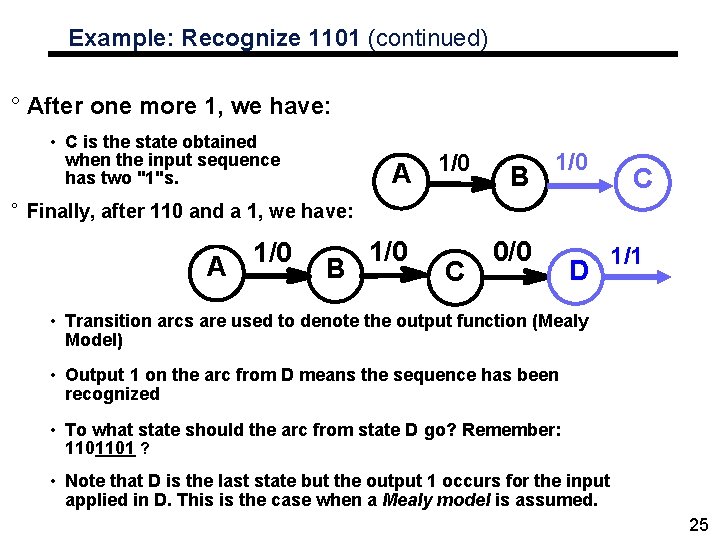

Example: Recognize 1101 ° Define states for the sequence to be recognized: • Assuming it starts with first symbol, • Continues through each symbol in the sequence to be recognized, and • Uses output 1 to mean the full sequence has occurred, • With output 0 otherwise. A 1/0 B ° Starting in the initial state (Arbitrarily named "A"): • Add a state that recognizes the first "1. " • State "A" is the initial state, and state "B" is the state which represents the fact that the "first" one in the input subsequence has occurred. The output symbol "0" means that the full recognized sequence has not yet occurred. 24

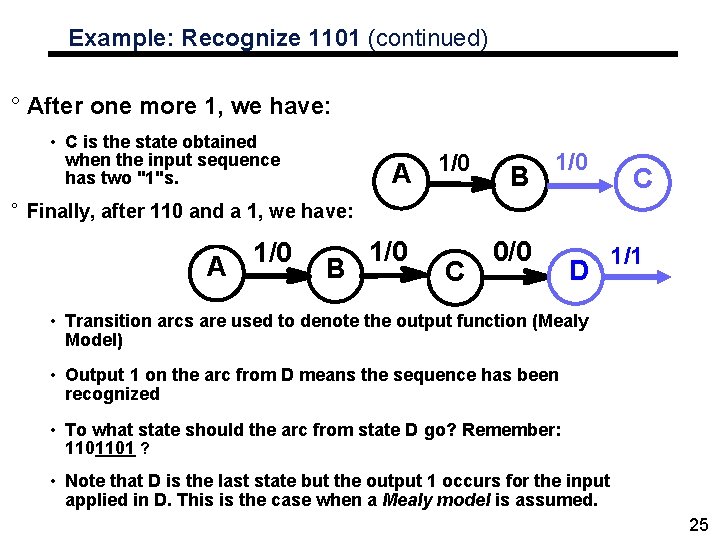

Example: Recognize 1101 (continued) ° After one more 1, we have: • C is the state obtained when the input sequence has two "1"s. A 1/0 B 1/0 C ° Finally, after 110 and a 1, we have: A 1/0 B 1/0 C 0/0 D 1/1 • Transition arcs are used to denote the output function (Mealy Model) • Output 1 on the arc from D means the sequence has been recognized • To what state should the arc from state D go? Remember: 1101101 ? • Note that D is the last state but the output 1 occurs for the input applied in D. This is the case when a Mealy model is assumed. 25

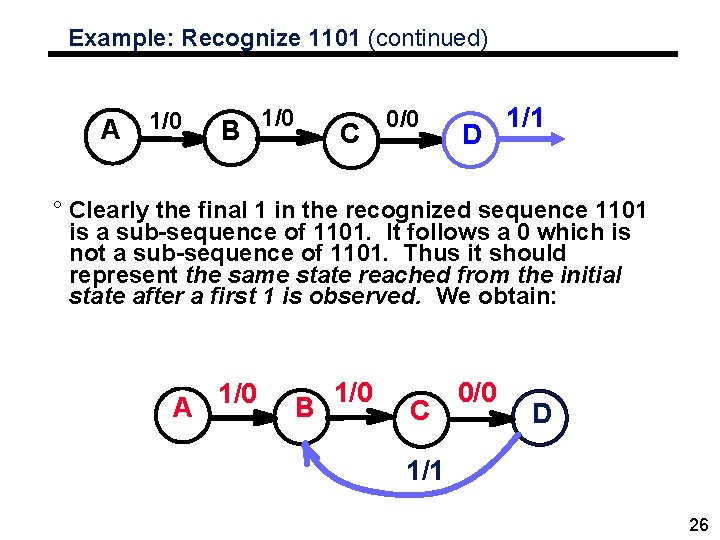

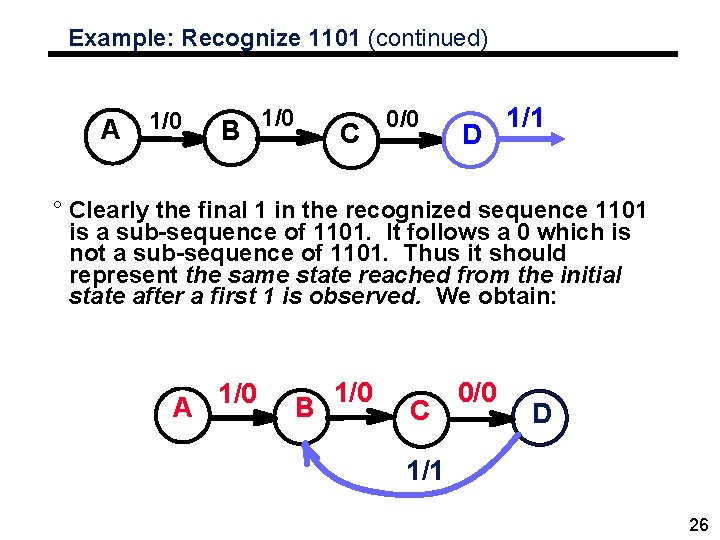

Example: Recognize 1101 (continued) A 1/0 B 1/0 C 0/0 D 1/1 ° Clearly the final 1 in the recognized sequence 1101 is a sub-sequence of 1101. It follows a 0 which is not a sub-sequence of 1101. Thus it should represent the same state reached from the initial state after a first 1 is observed. We obtain: 1/0 A B 1/0 C 0/0 D 1/1 26

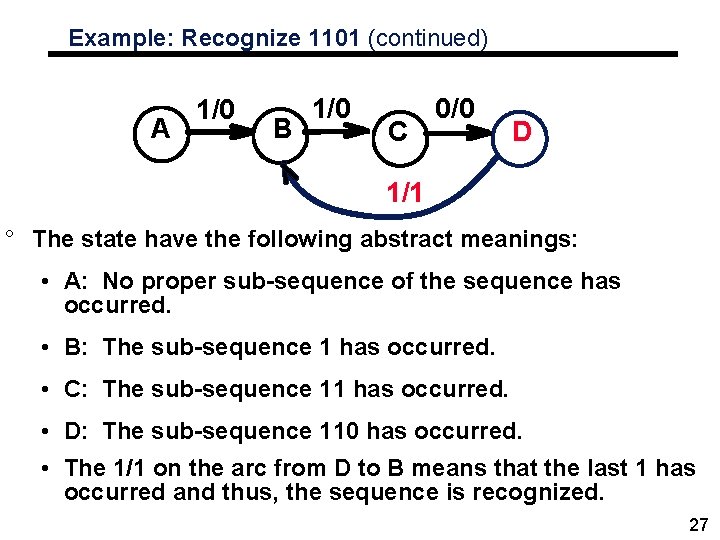

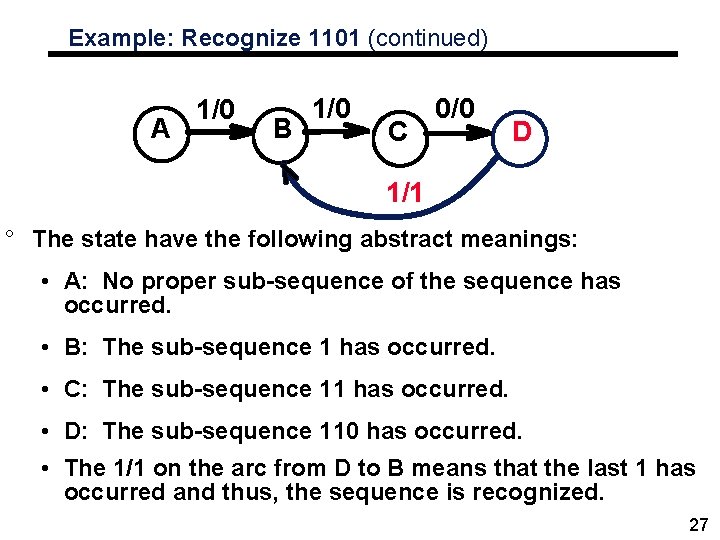

Example: Recognize 1101 (continued) A 1/0 B 1/0 C 0/0 D 1/1 ° The state have the following abstract meanings: • A: No proper sub-sequence of the sequence has occurred. • B: The sub-sequence 1 has occurred. • C: The sub-sequence 11 has occurred. • D: The sub-sequence 110 has occurred. • The 1/1 on the arc from D to B means that the last 1 has occurred and thus, the sequence is recognized. 27

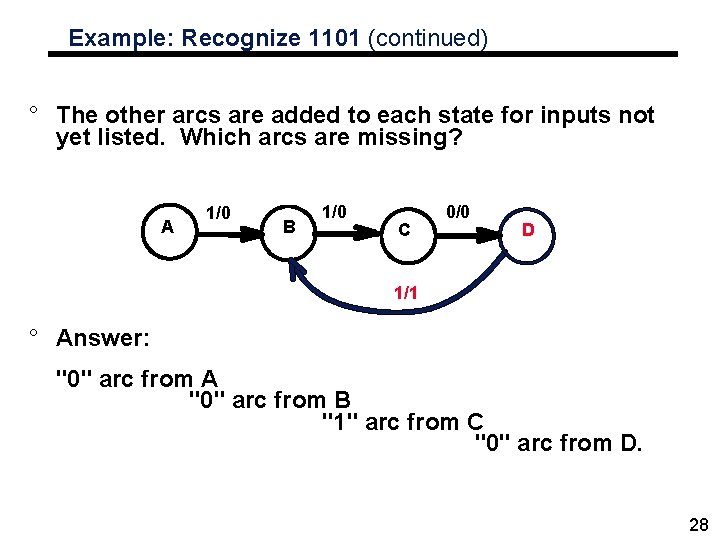

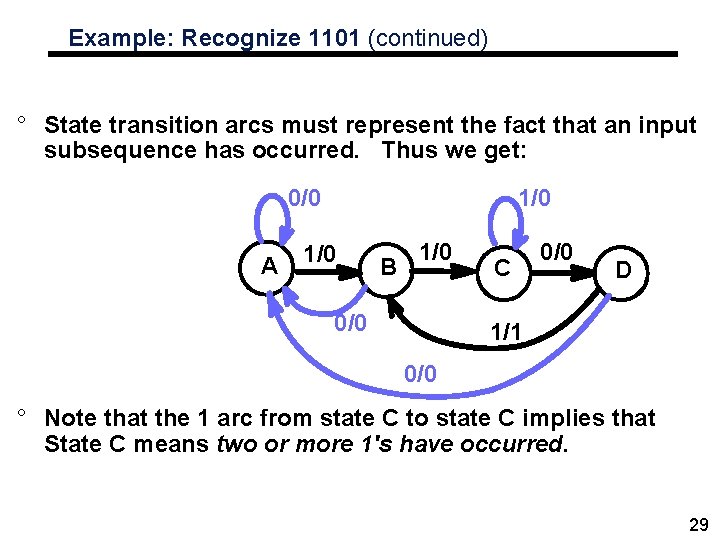

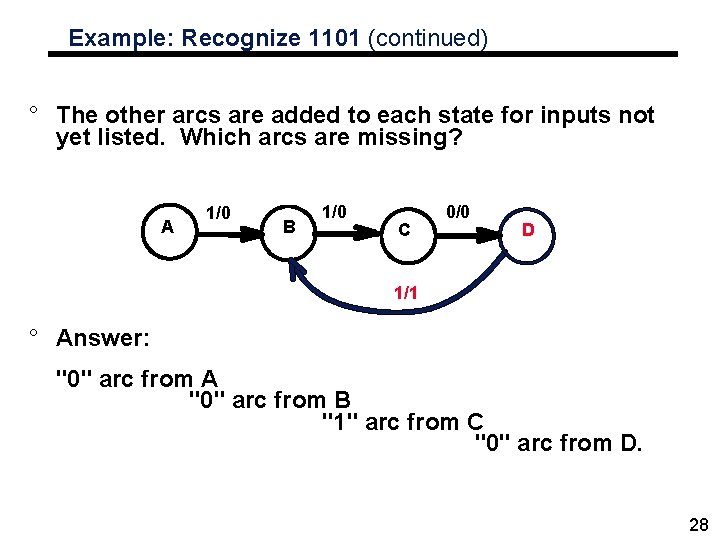

Example: Recognize 1101 (continued) ° The other arcs are added to each state for inputs not yet listed. Which arcs are missing? A 1/0 B 1/0 C 0/0 D 1/1 ° Answer: "0" arc from A "0" arc from B "1" arc from C "0" arc from D. 28

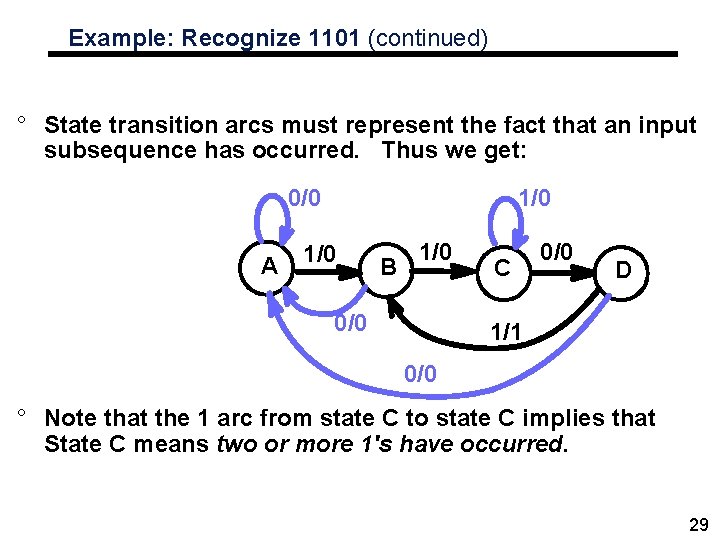

Example: Recognize 1101 (continued) ° State transition arcs must represent the fact that an input subsequence has occurred. Thus we get: 0/0 A 1/0 B 1/0 0/0 C 0/0 D 1/1 0/0 ° Note that the 1 arc from state C to state C implies that State C means two or more 1's have occurred. 29

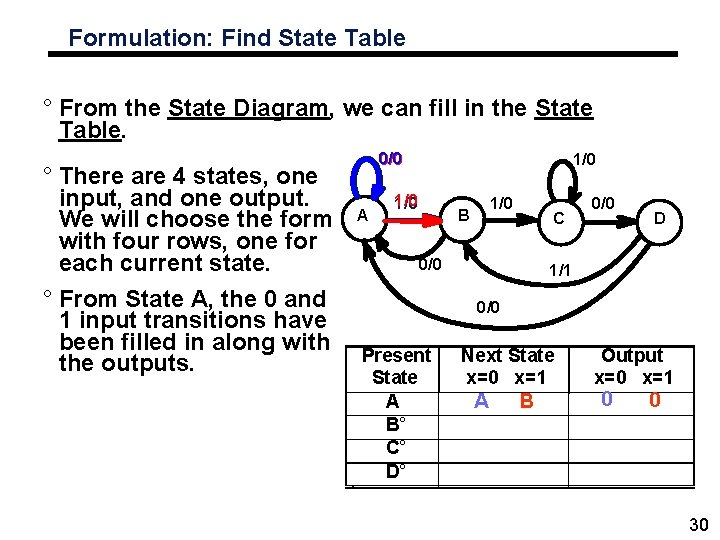

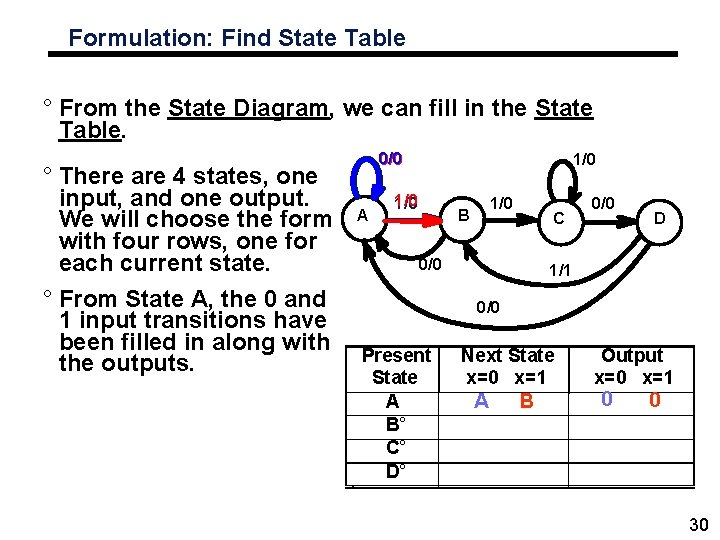

Formulation: Find State Table ° From the State Diagram, we can fill in the State Table. 0/0 ° There are 4 states, one input, and one output. We will choose the form with four rows, one for each current state. ° From State A, the 0 and 1 input transitions have been filled in along with the outputs. A 1/0 1/0 B C 0/0 D 1/1 0/0 Present State A B° C° D° Next State x=0 x=1 A B Output x=0 x=1 0 0 ° 30

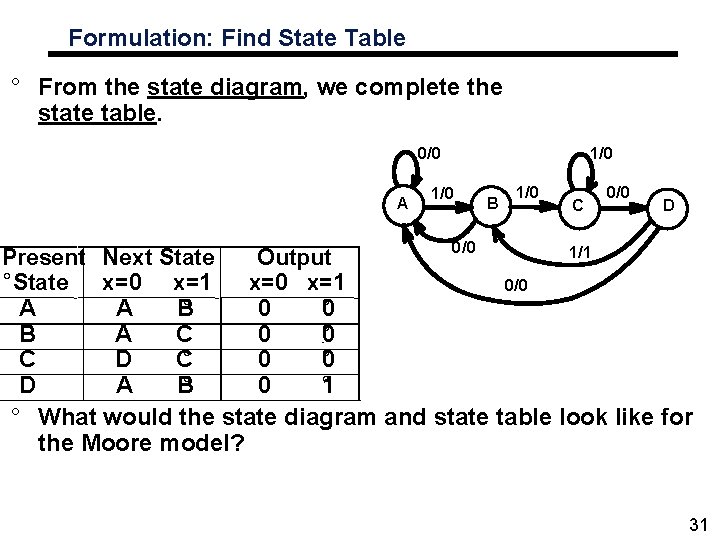

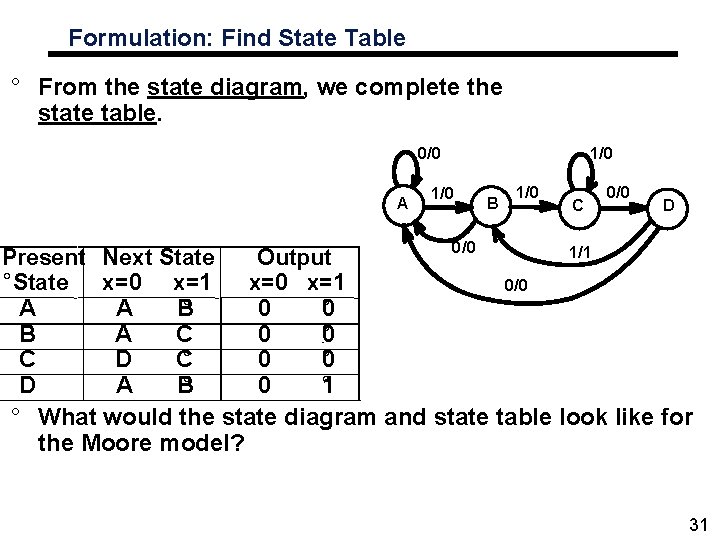

Formulation: Find State Table ° From the state diagram, we complete the state table. 0/0 A 1/0 B 1/0 C 0/0 D 0/0 1/1 °Present Next State Output °State x=0 x=1 0/0 A A B° 0 0 ° B A C 0 0 ° C D C° 0 0 ° D A B° 0 1 ° ° What would the state diagram and state table look like for the Moore model? 31

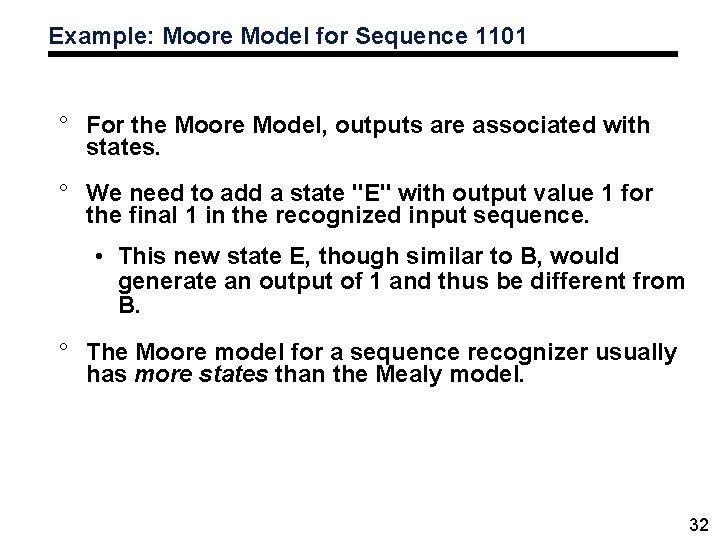

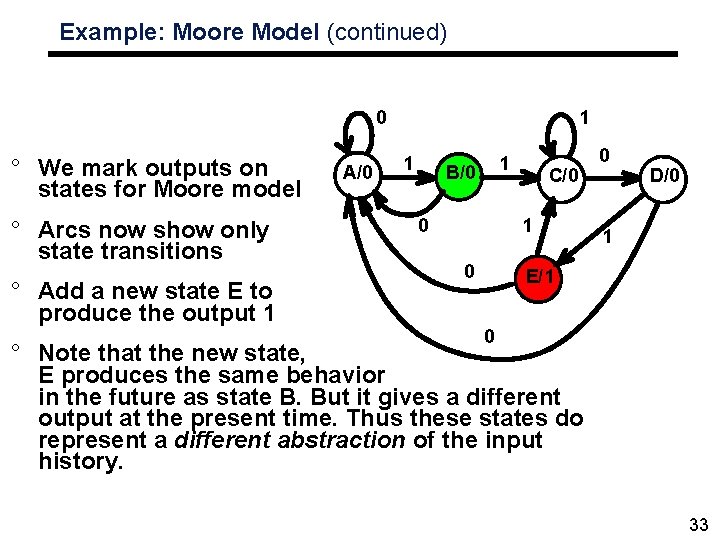

Example: Moore Model for Sequence 1101 ° For the Moore Model, outputs are associated with states. ° We need to add a state "E" with output value 1 for the final 1 in the recognized input sequence. • This new state E, though similar to B, would generate an output of 1 and thus be different from B. ° The Moore model for a sequence recognizer usually has more states than the Mealy model. 32

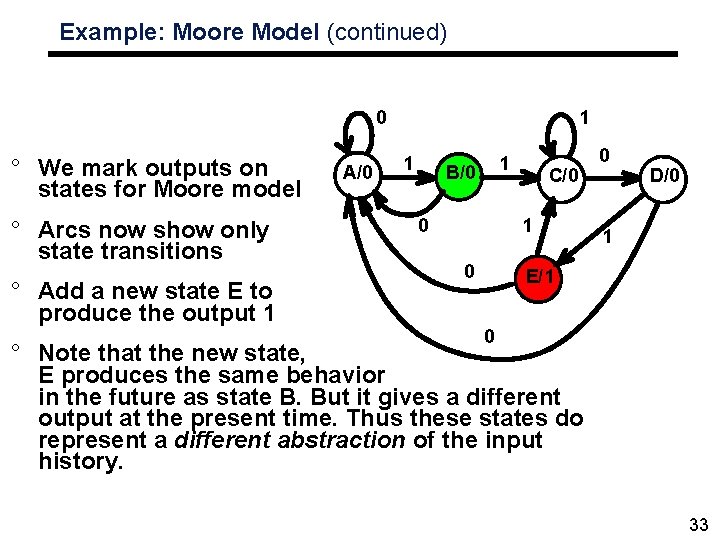

Example: Moore Model (continued) 0 ° We mark outputs on states for Moore model ° Arcs now show only state transitions ° Add a new state E to produce the output 1 A/0 1 1 1 B/0 0 C/0 1 0 0 D/0 1 E/1 0 ° Note that the new state, E produces the same behavior in the future as state B. But it gives a different output at the present time. Thus these states do represent a different abstraction of the input history. 33

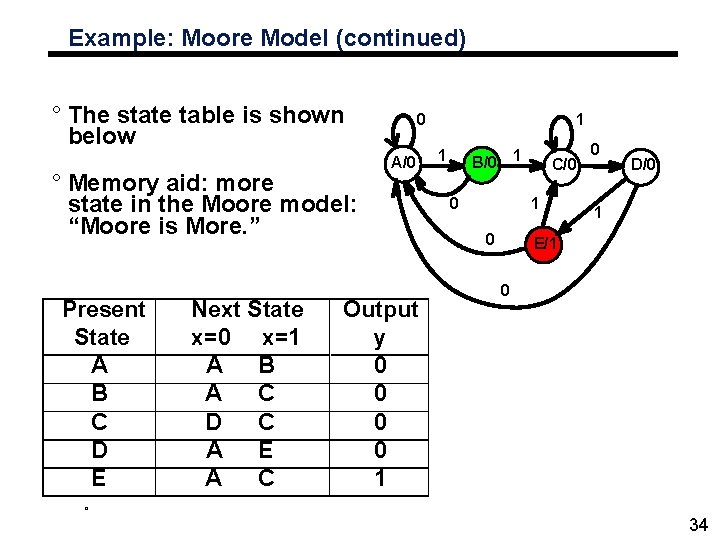

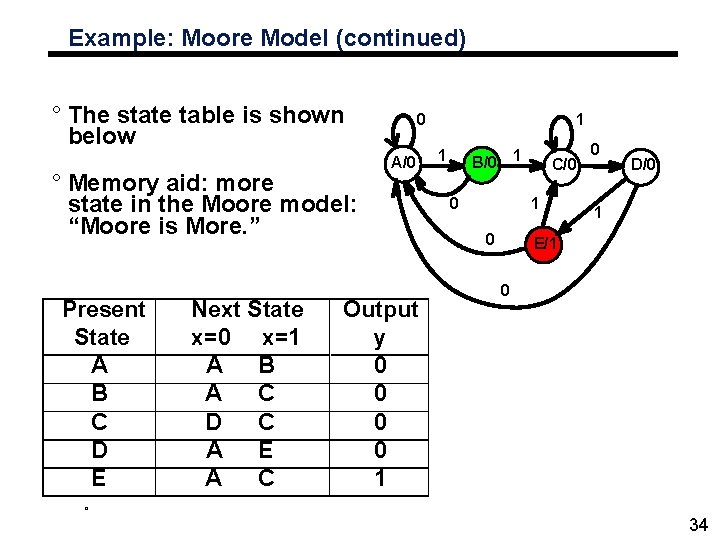

Example: Moore Model (continued) ° The state table is shown below ° Memory aid: more state in the Moore model: “Moore is More. ” Present State A B C D E ° Next State x=0 x=1 A B A C D C A E A C 0 A/0 Output y 0 0 1 1 1 B/0 1 0 C/0 1 0 0 D/0 1 E/1 0 34

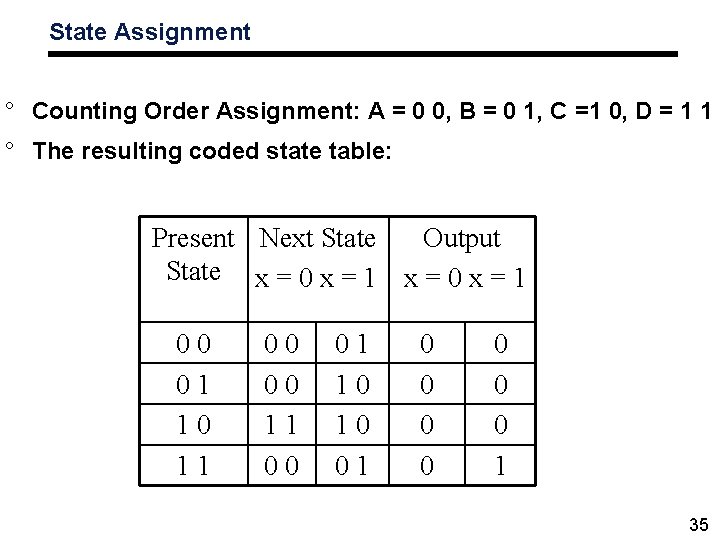

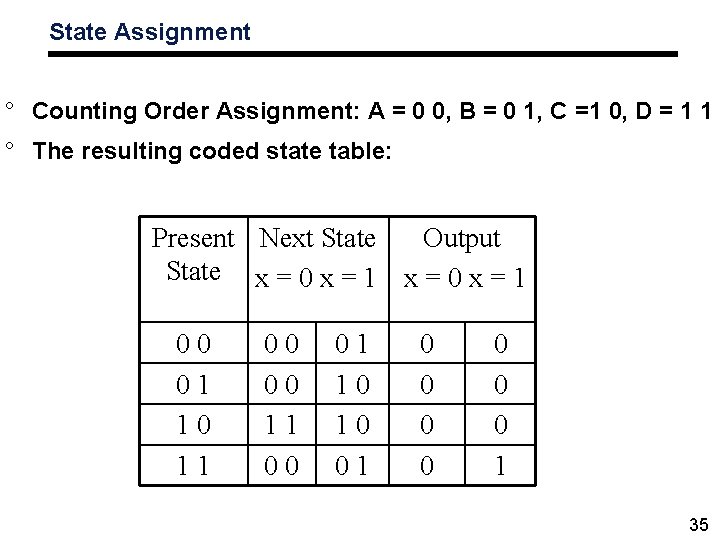

State Assignment ° Counting Order Assignment: A = 0 0, B = 0 1, C =1 0, D = 1 1 ° The resulting coded state table: Present Next State Output State x = 0 x = 1 00 01 10 11 00 01 10 10 01 0 0 0 0 1 35

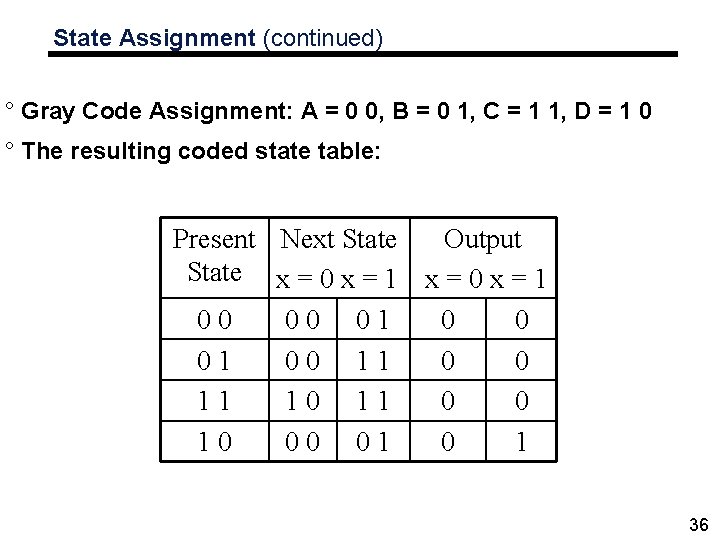

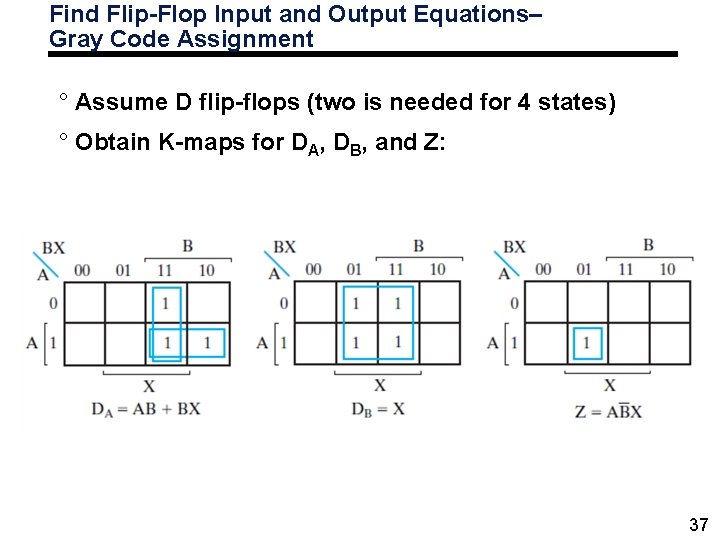

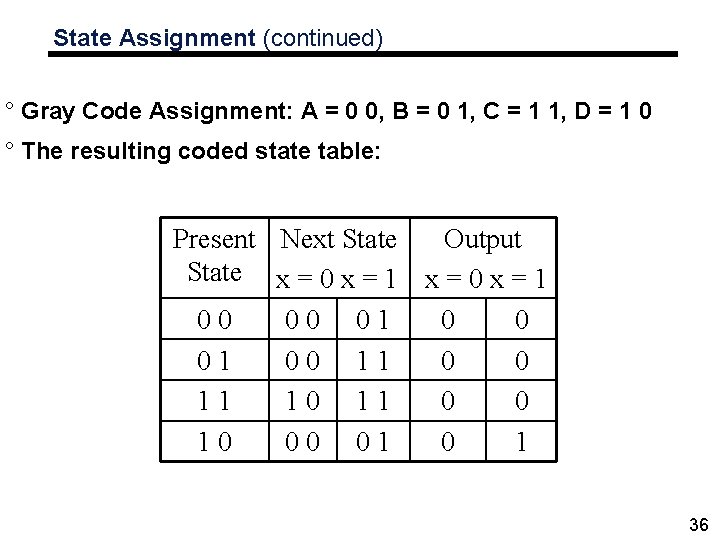

State Assignment (continued) ° Gray Code Assignment: A = 0 0, B = 0 1, C = 1 1, D = 1 0 ° The resulting coded state table: Present Next State Output State x = 0 x = 1 00 00 01 00 11 0 0 11 10 11 0 0 10 00 01 0 1 36

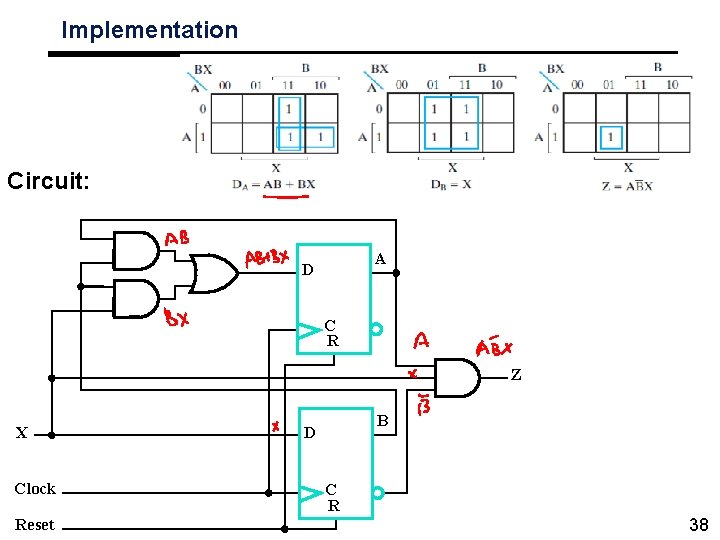

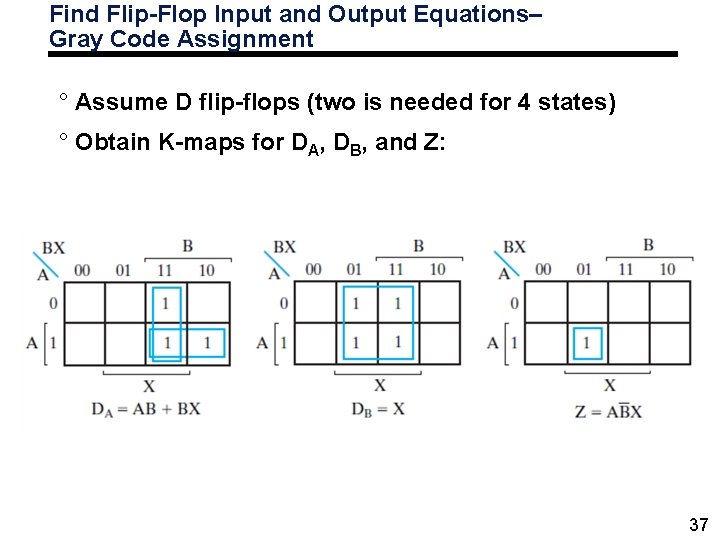

Find Flip-Flop Input and Output Equations– Gray Code Assignment ° Assume D flip-flops (two is needed for 4 states) ° Obtain K-maps for DA, DB, and Z: 37

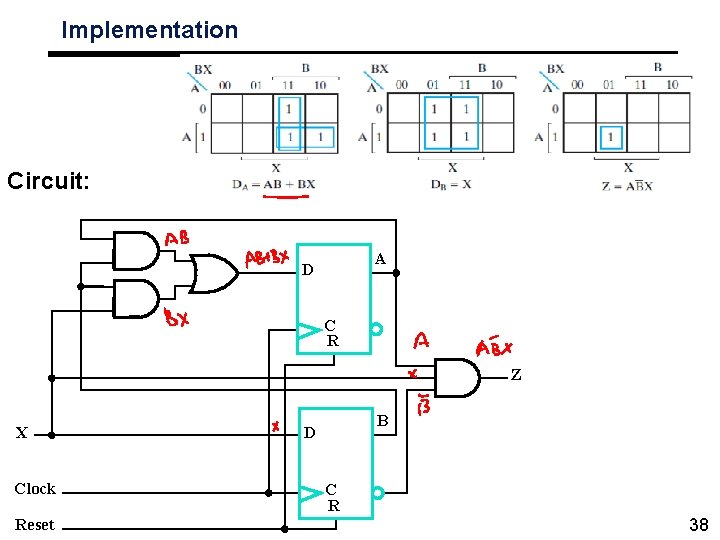

Implementation Circuit: A D C R Z X Clock Reset B D C R 38

39

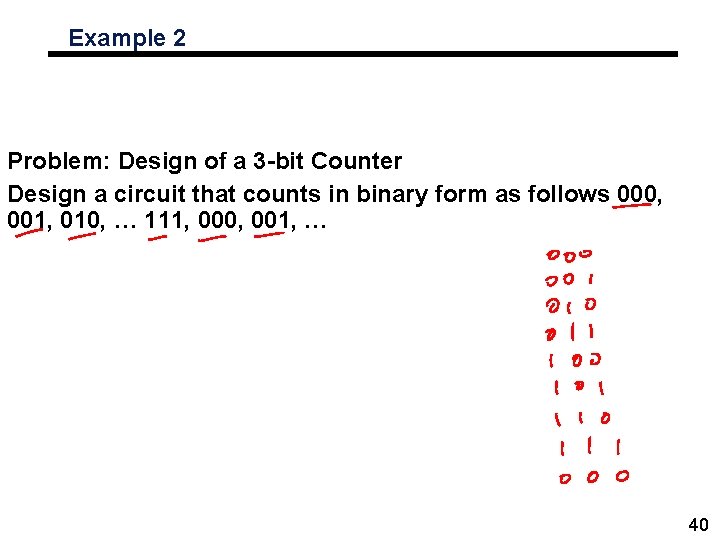

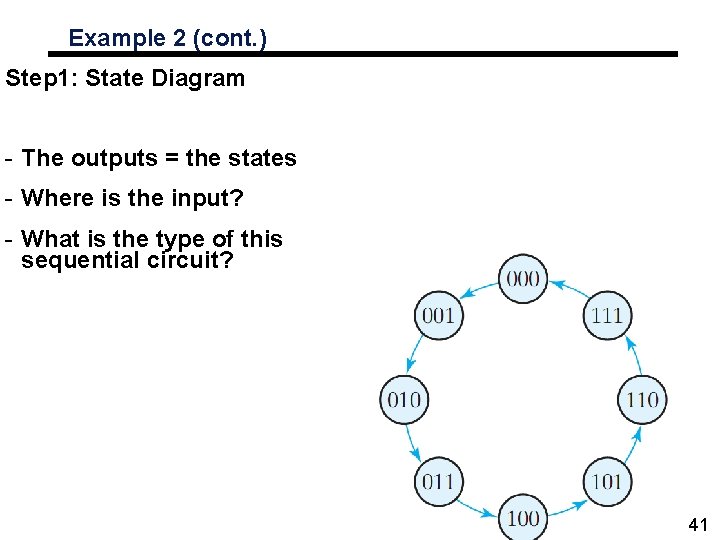

Example 2 Problem: Design of a 3 -bit Counter Design a circuit that counts in binary form as follows 000, 001, 010, … 111, 000, 001, … 40

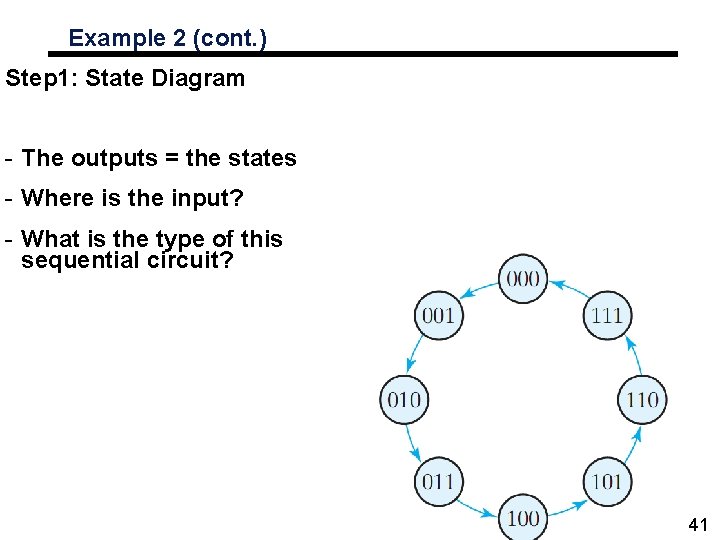

Example 2 (cont. ) Step 1: State Diagram - The outputs = the states - Where is the input? - What is the type of this sequential circuit? 41

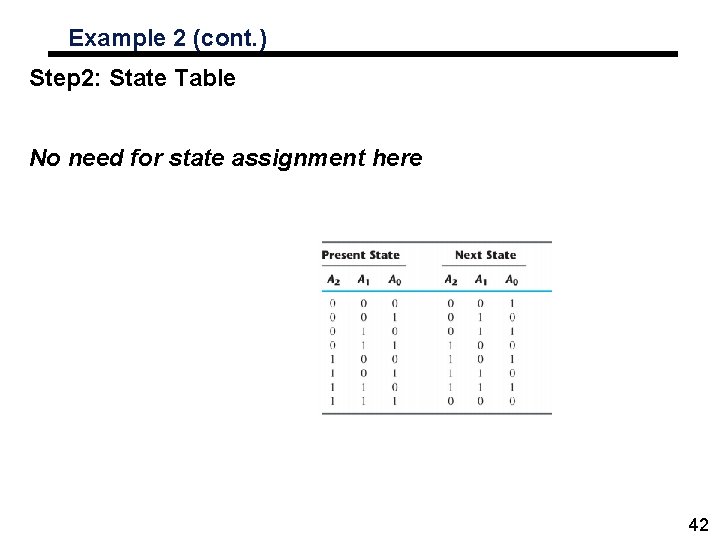

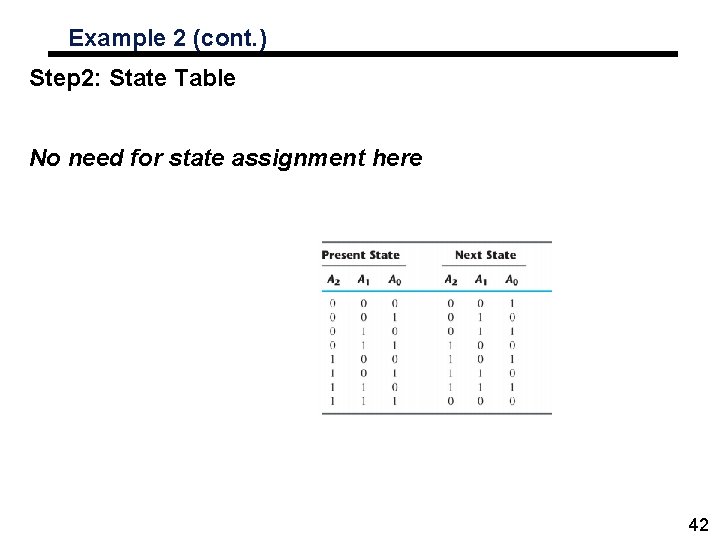

Example 2 (cont. ) Step 2: State Table No need for state assignment here 42

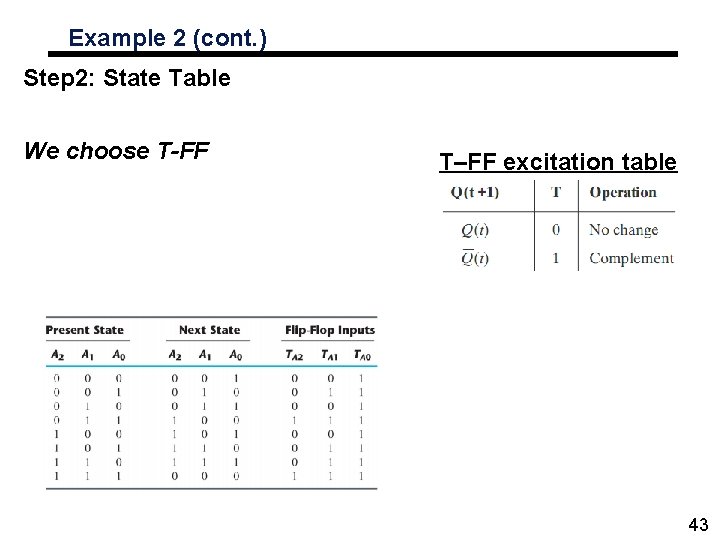

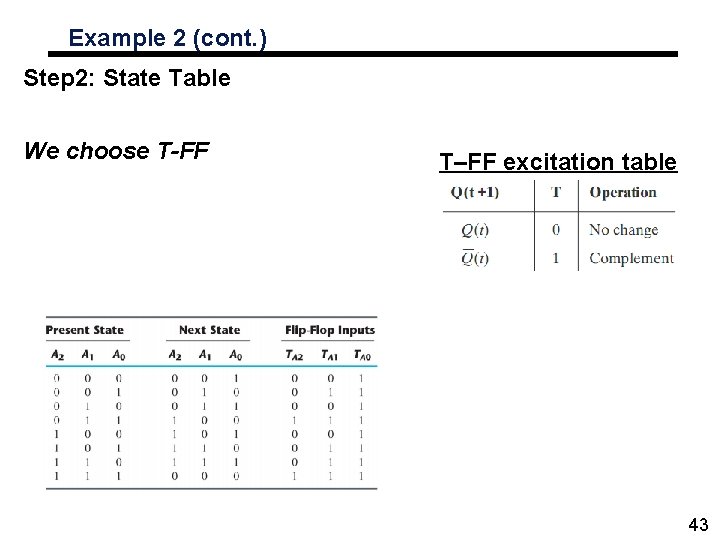

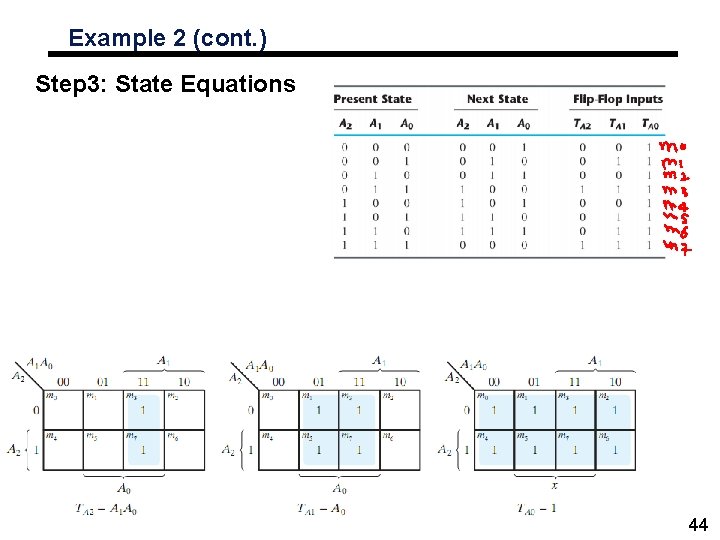

Example 2 (cont. ) Step 2: State Table We choose T-FF T–FF excitation table 43

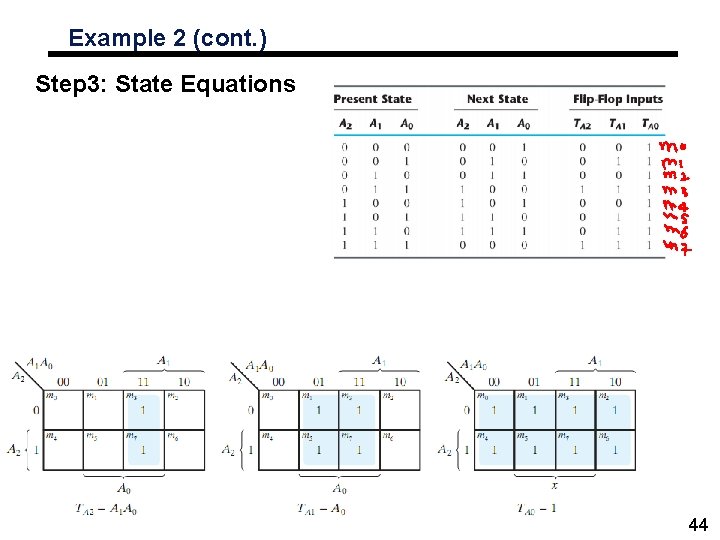

Example 2 (cont. ) Step 3: State Equations 44

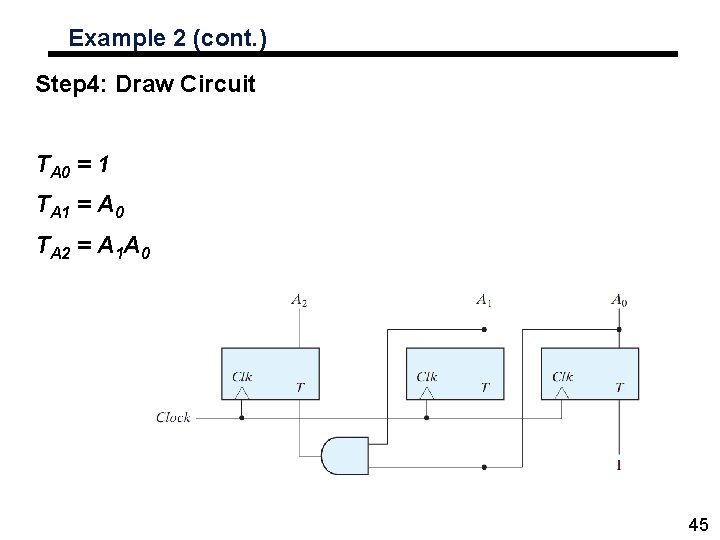

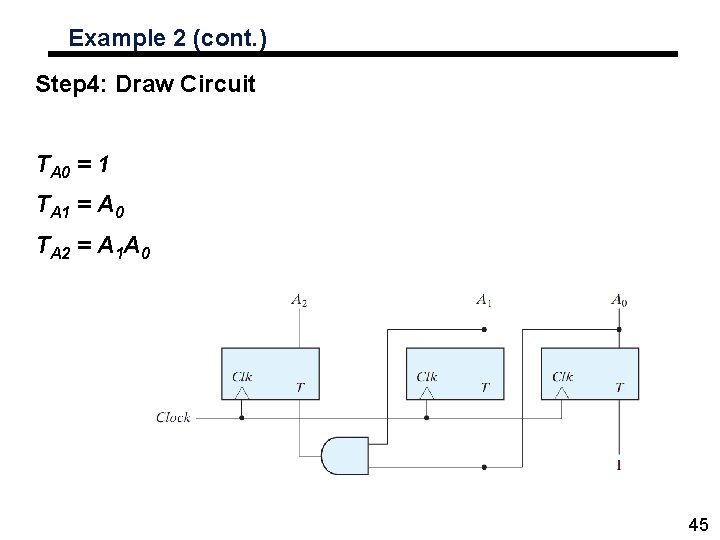

Example 2 (cont. ) Step 4: Draw Circuit TA 0 = 1 TA 1 = A 0 TA 2 = A 1 A 0 45

46

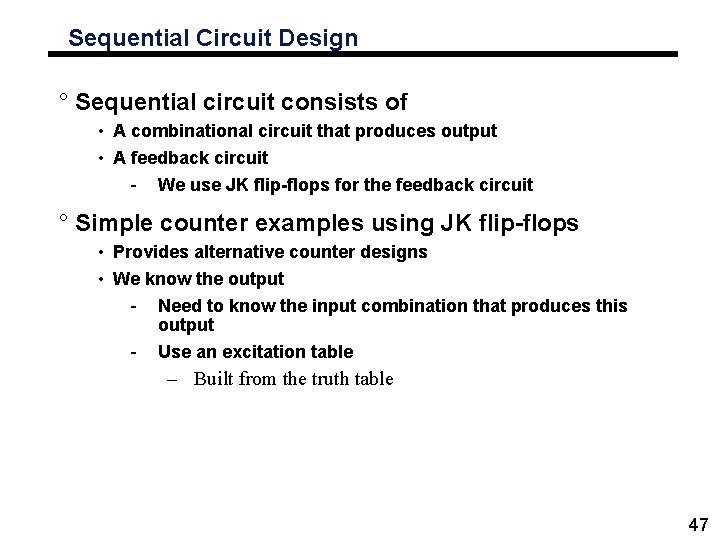

Sequential Circuit Design ° Sequential circuit consists of • A combinational circuit that produces output • A feedback circuit - We use JK flip-flops for the feedback circuit ° Simple counter examples using JK flip-flops • Provides alternative counter designs • We know the output - Need to know the input combination that produces this output - Use an excitation table – Built from the truth table 47

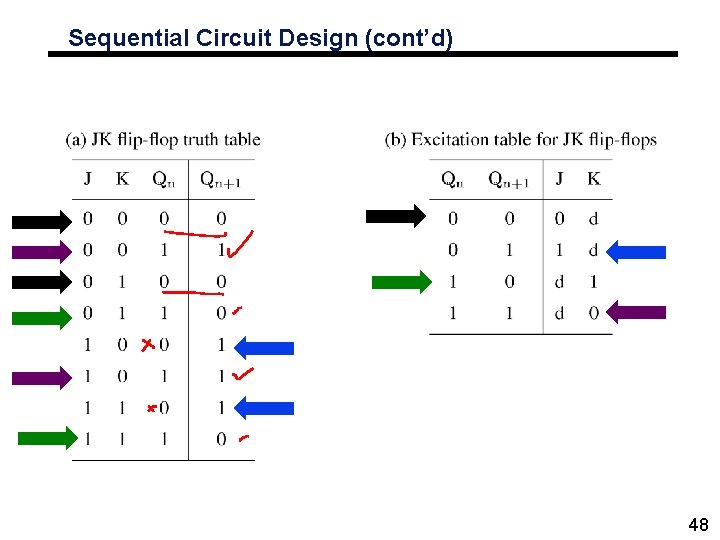

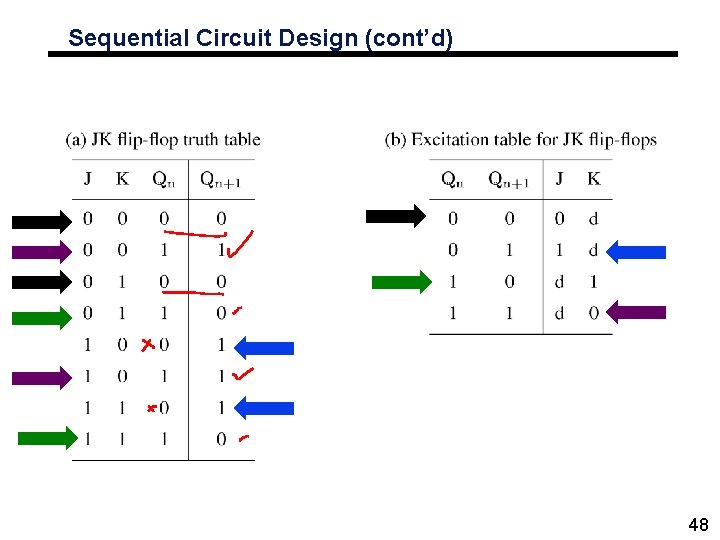

Sequential Circuit Design (cont’d) 48

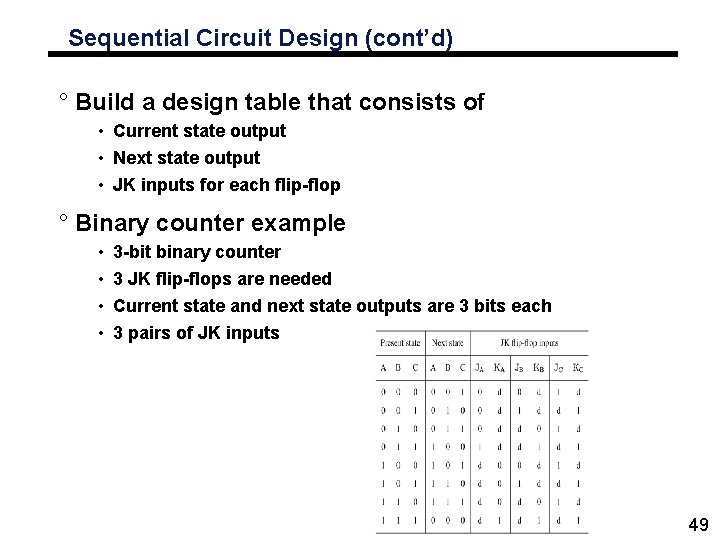

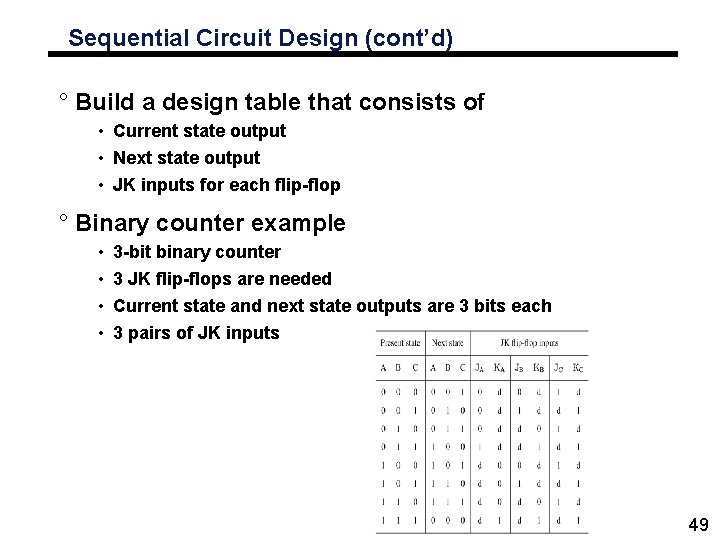

Sequential Circuit Design (cont’d) ° Build a design table that consists of • Current state output • Next state output • JK inputs for each flip-flop ° Binary counter example • • 3 -bit binary counter 3 JK flip-flops are needed Current state and next state outputs are 3 bits each 3 pairs of JK inputs 49

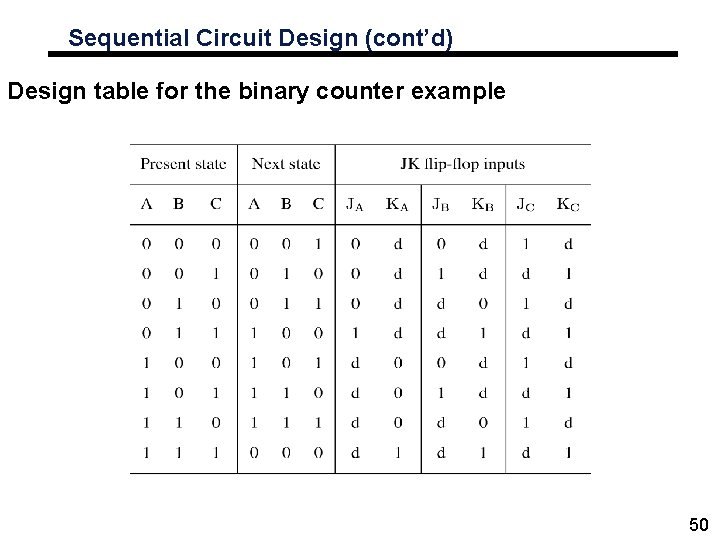

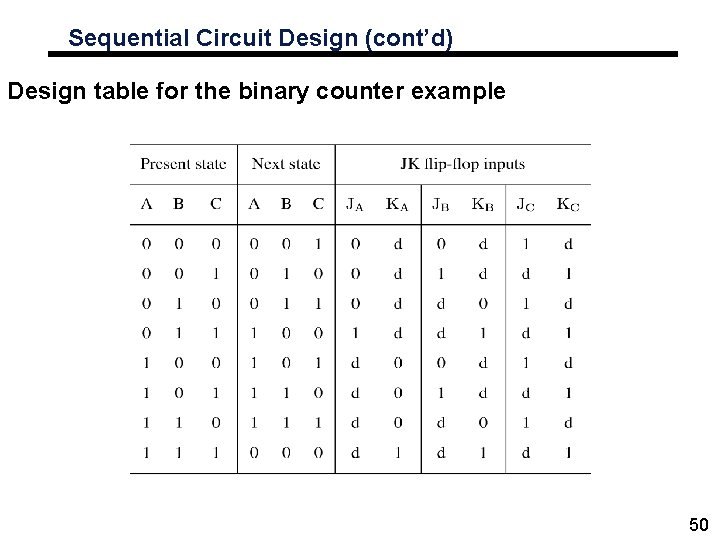

Sequential Circuit Design (cont’d) Design table for the binary counter example 50

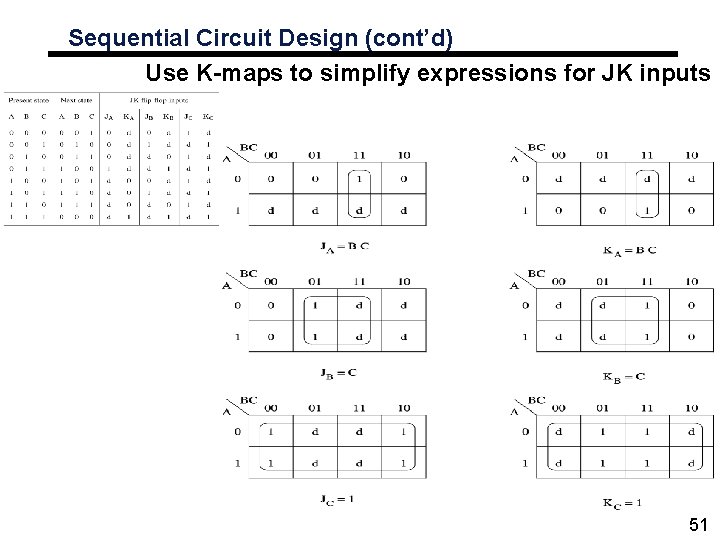

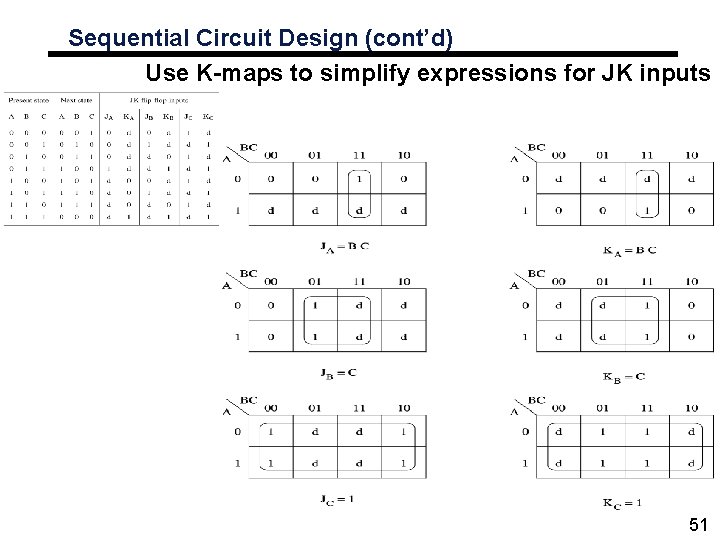

Sequential Circuit Design (cont’d) Use K-maps to simplify expressions for JK inputs 51

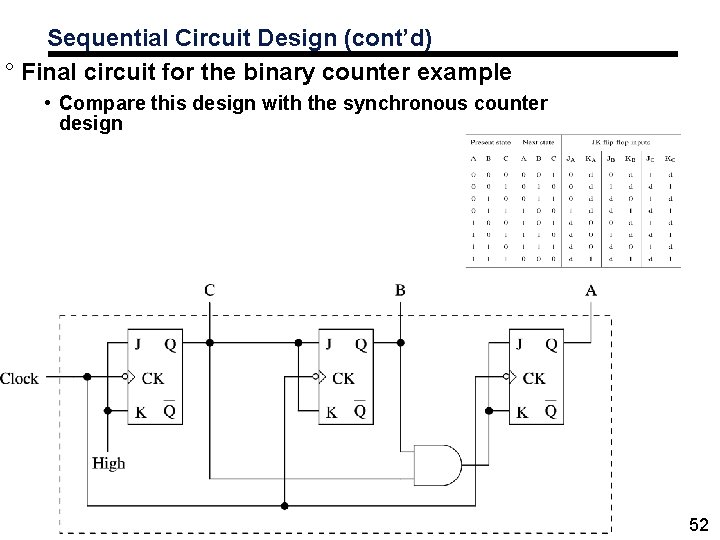

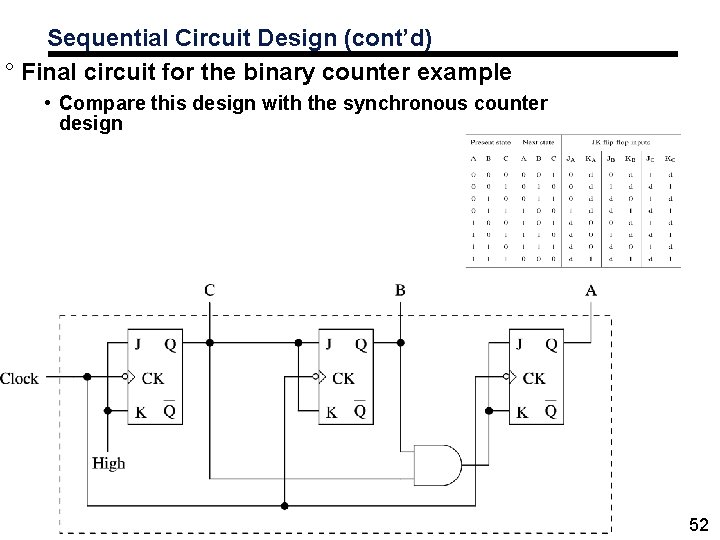

Sequential Circuit Design (cont’d) ° Final circuit for the binary counter example • Compare this design with the synchronous counter design 52

Summary Analysis by signal tracing Sequential Design State Reduction Design Examples Thanks 53