Design of Combinational Logic Using CMOS Combinational Logic

Design of Combinational Logic Using CMOS

Combinational Logic with CMOS l Representation l Structure l Design l of Binary variable of CMOS gates of Combinational logic Using CMOS

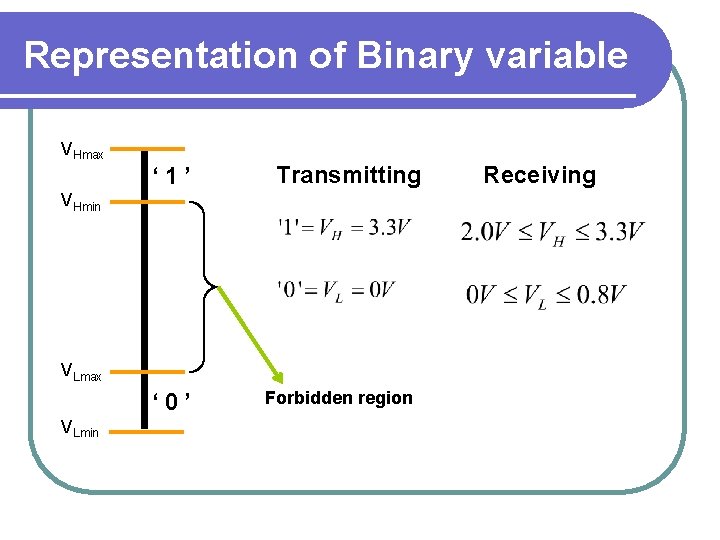

Representation of Binary variable VHmax ‘ 1’ Transmitting VHmin VLmax ‘ 0’ VLmin Forbidden region Receiving

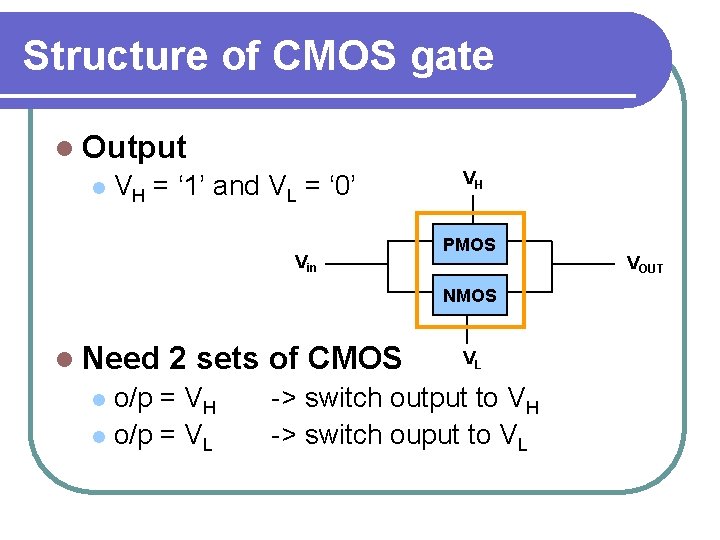

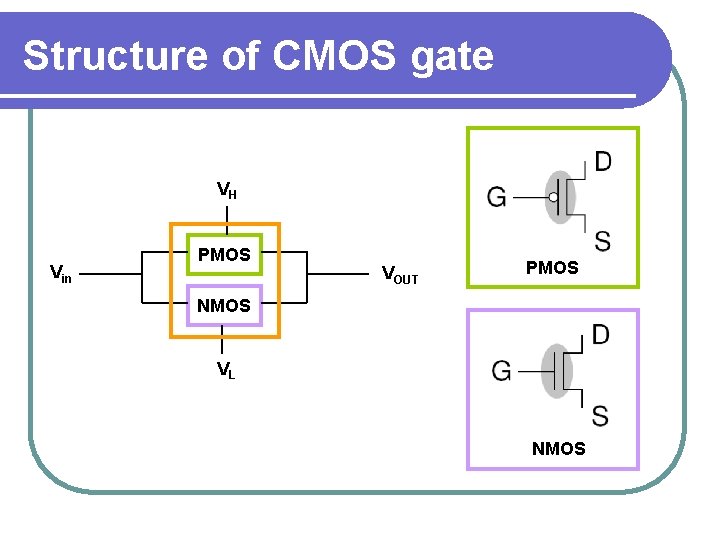

Structure of CMOS gate l Output l VH = ‘ 1’ and VL = ‘ 0’ Vin VH PMOS NMOS l Need 2 sets of CMOS o/p = VH l o/p = VL l VL -> switch output to VH -> switch ouput to VL VOUT

Structure of CMOS gate VH Vin PMOS VOUT PMOS NMOS VL NMOS

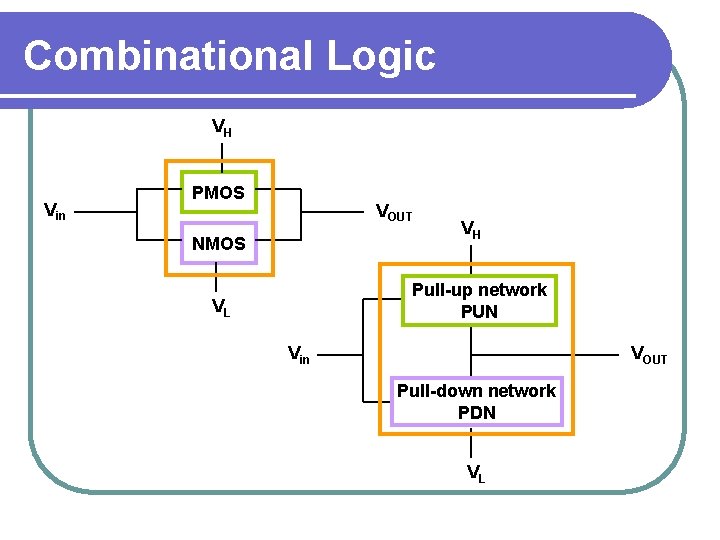

Combinational Logic VH Vin PMOS VOUT NMOS VH Pull-up network PUN VL Vin VOUT Pull-down network PDN VL

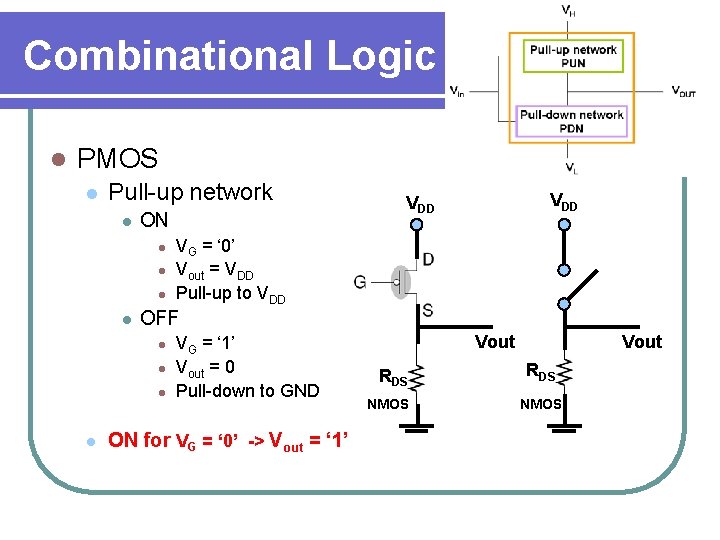

Combinational Logic l PMOS l Pull-up network l ON l l VG = ‘ 0’ Vout = VDD Pull-up to VDD OFF l l VDD VG = ‘ 1’ Vout = 0 Pull-down to GND ON for VG = ‘ 0’ -> Vout = ‘ 1’ Vout RDS NMOS

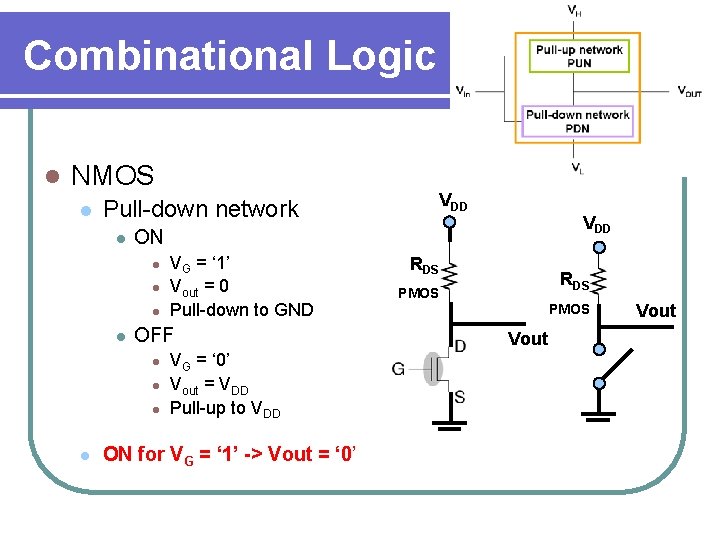

Combinational Logic l NMOS l l l VDD ON l VG = ‘ 1’ Vout = 0 Pull-down to GND OFF l l VDD Pull-down network VG = ‘ 0’ Vout = VDD Pull-up to VDD ON for VG = ‘ 1’ -> Vout = ‘ 0’ RDS PMOS Vout

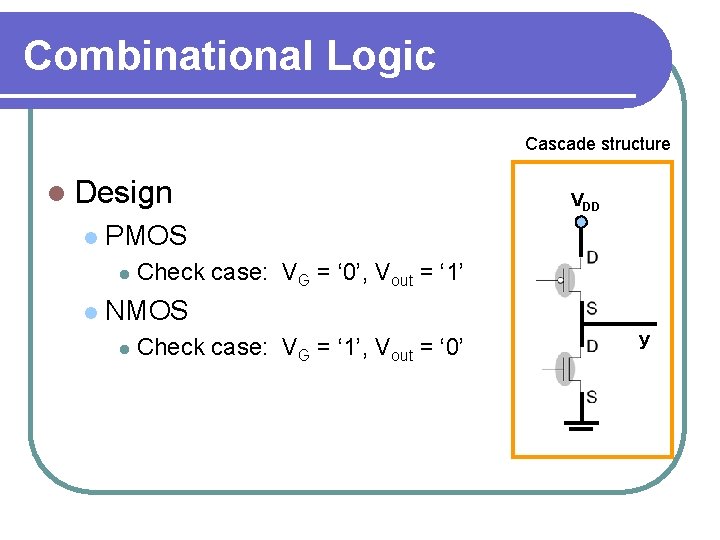

Combinational Logic Cascade structure l Design l PMOS l l VDD Check case: VG = ‘ 0’, Vout = ‘ 1’ NMOS l Check case: VG = ‘ 1’, Vout = ‘ 0’ y

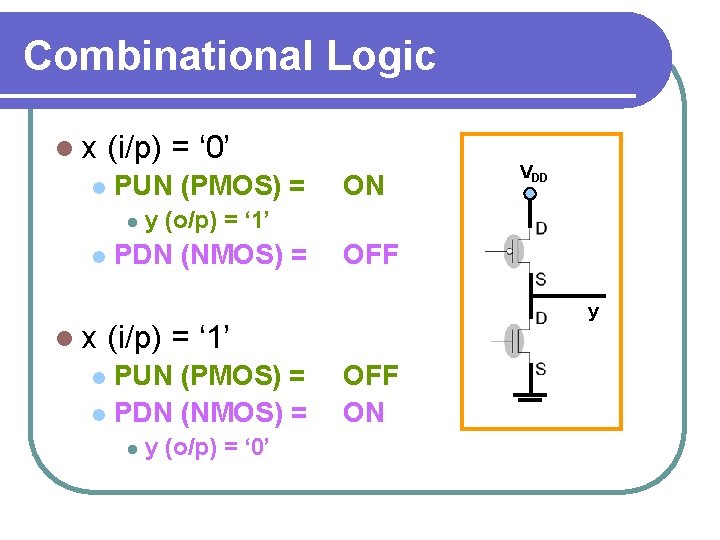

Combinational Logic lx l (i/p) = ‘ 0’ PUN (PMOS) = l l lx ON y (o/p) = ‘ 1’ PDN (NMOS) = OFF y (i/p) = ‘ 1’ PUN (PMOS) = l PDN (NMOS) = l l VDD y (o/p) = ‘ 0’ OFF ON

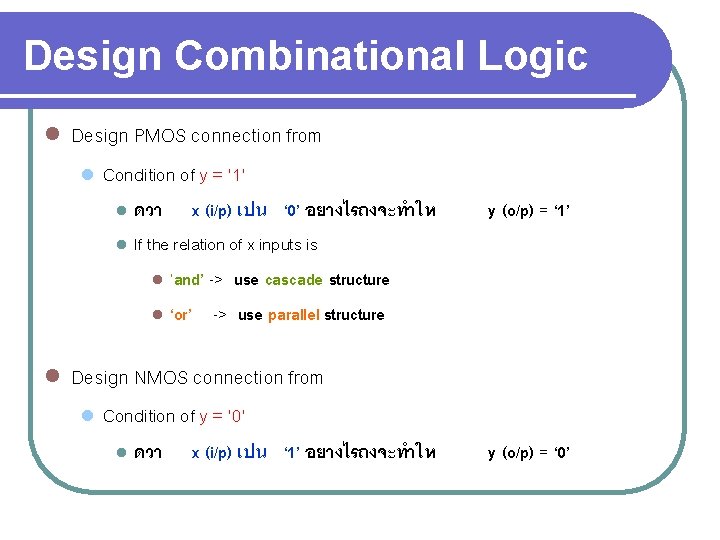

Design Combinational Logic l Design PMOS connection from l Condition of y = ‘ 1’ ดวา x (i/p) เปน ‘ 0’ อยางไรถงจะทำให l If the relation of x inputs is l ‘and’ -> use cascade structure l ‘or’ -> use parallel structure l l y (o/p) = ‘ 1’ Design NMOS connection from l Condition of y = ‘ 0’ l ดวา x (i/p) เปน ‘ 1’ อยางไรถงจะทำให y (o/p) = ‘ 0’

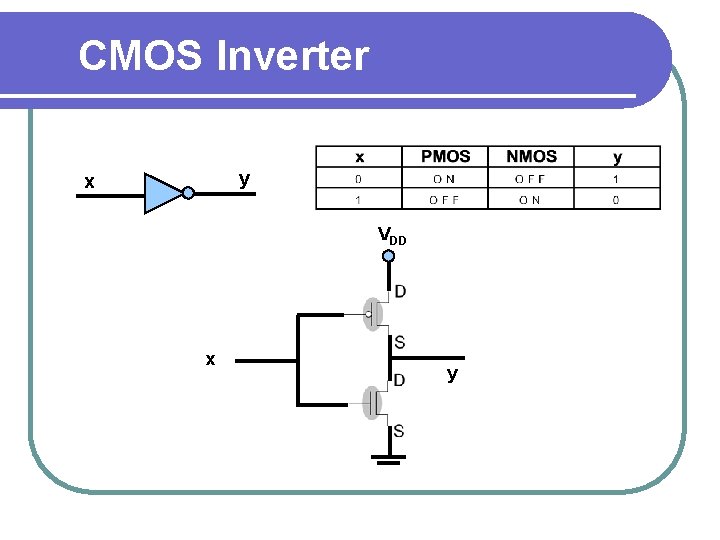

CMOS Inverter y x VDD x y

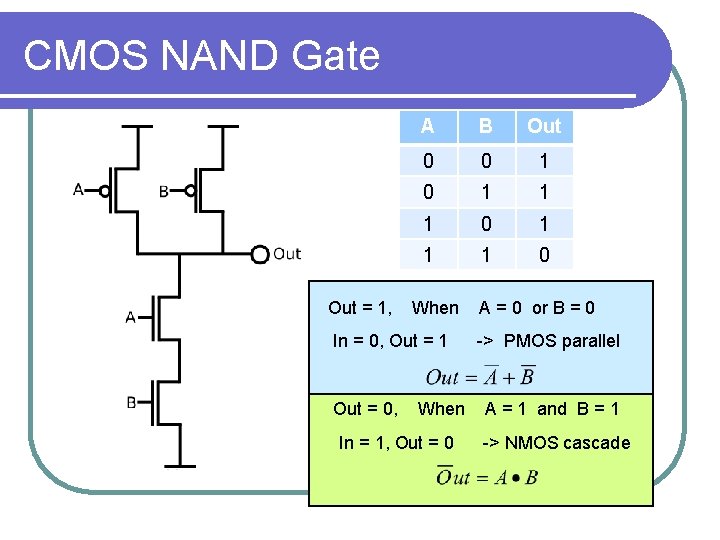

CMOS NAND Gate Out = 1, A B Out 0 0 1 1 1 0 When In = 0, Out = 1 Out = 0, When In = 1, Out = 0 A = 0 or B = 0 -> PMOS parallel A = 1 and B = 1 -> NMOS cascade

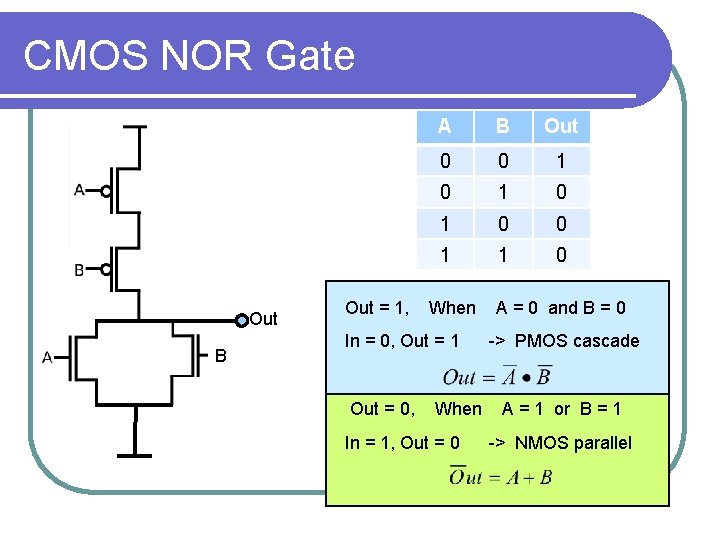

CMOS NOR Gate Out B Out = 1, A B Out 0 0 1 0 1 0 0 1 1 0 When In = 0, Out = 1 Out = 0, When In = 1, Out = 0 A = 0 and B = 0 -> PMOS cascade A = 1 or B = 1 -> NMOS parallel

- Slides: 14