TIMERS COUNTERS Two 16 bit timercounters Can be

TIMERS / COUNTERS - Two 16 bit timer/counters - Can be programmed independently as – timer or event counter. - Four-SFR’s connected with TIMER/COUNTER operation - TMOD – Timer Mode Register - TCON – Timer Control Register - TH 0, TL 0 – Timer/Counter - 0 - TH 1, TL 1 – Timer/Counter - 1 - Two pins of 8051 connected with Timer/counter. T 0 – Timer 0 external input – P 3. 4 T 1 – Timer 1 external input – P 3. 5 - INT 0 and INT 1 are also used for controlling the timer/counters.

Timer Operation Timer Register (TH 0, TL 0 or TH 1, TL 1) incremented every m/c cycle. Thus working at increment frequency of 1/12 of oscillator frequency ( for 12 oscillator machine cycle ). Any preset value i. e. initial count can be loaded to TH 0, TL 0 or TH 1, TL 1. For Example – Clock frequency = 12 MHZ Clock period = 1/12 µ sec Machine cycle time = 1 µ sec Thus timer register will be incremented every microsecond. - If timer is initialized to 0000 H Max. count = FFFFH max. time measured = 216 µ sec = 26 x 210 µ sec ≈ 26 millisecond ≈ 64 millisecond = 65. 5 millisecond

Counter Operation - Counts pulses occurring at T 0 pin (Timer/Counter 0) and/or T 1 pin (Timer/counter 1). - May correspond to event like • Passing of railway coach from a point – axle counter • Rotation of speedometer cable – speedometer of vehicle • No. of persons visiting exhibition. - T 0, T 1 scanned every m/c cycle • nth m/c cycle – T 1 or T 0 = High • (n+1)th m/c – T 1 or T 0 = Low • Timer 0 or timer 1 incremented in (n+1)th m/c cycle - Count frequency = min 2 m/c cycle per count - T 0 - P 3. 4, T 1 - P 3. 5

2 m/c cycle In 12 MHz 8051 – m/c cycle = 1 µ sec - 8051 can count at the rate of 2 µ sec per count or higher - Any event when takes less than 2 µ sec may go unnoticed - C/T bit of TMOD selects Timer or counter operation for Timer 0 or Timer 1. - Timer/Counter operations are controlled by - Gate bit of TMOD - TR 0 bit of TCON When Gate = 0 then TR 0, TR 1 act as Timer run control bits.

- Thus make Gate = 0 in TMOD By making TR 0 (TCON. 4) or TR 1 (TCON. 6) = 1. through instruction, Timer/Counter 0 or Timer/Counter 1 may be started. - For starting and stopping the Timer/Counter from outside through hardware. § Make Gate = 1, TR 0 = 1 through software. - By making INT 0 or INT 1 pin High will start Timer/Counter 0 or Timer/Counter 1 § Make INT 0 or INT 1 Low to stop the Timer/Counter. § INT 0 - P 3. 2 § INT 1 - P 3. 3

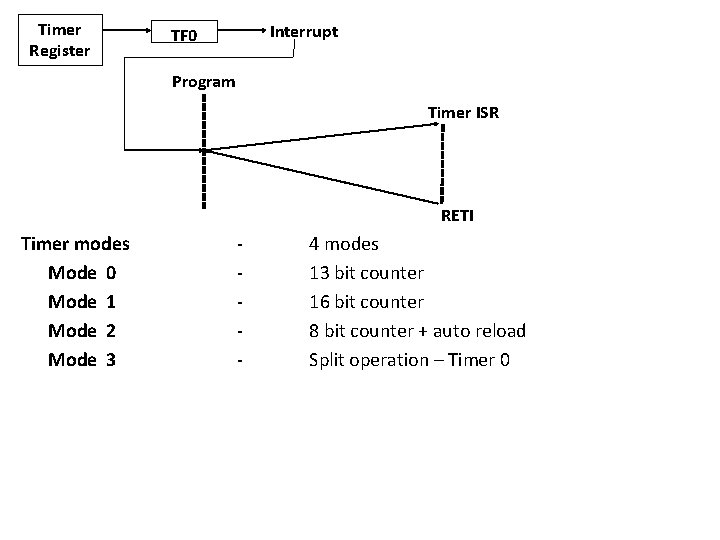

As value in Timer register rolls from all ones (i. e. FFFFH) to all zero’s (i. e. 0000 H) interrupt flag (TF 0 or TF 1) will be set. - TF 0 (for Timer 0) and TF 1 (for Timer 1) are bits of TCON SFR. § IF Timer 0 or Timer 1 interrupt is enabled then program control will branch to interrupt servicing routine.

Timer Register Interrupt TF 0 Program Timer ISR RETI Timer modes Mode 0 Mode 1 Mode 2 Mode 3 - 4 modes 13 bit counter 16 bit counter 8 bit counter + auto reload Split operation – Timer 0

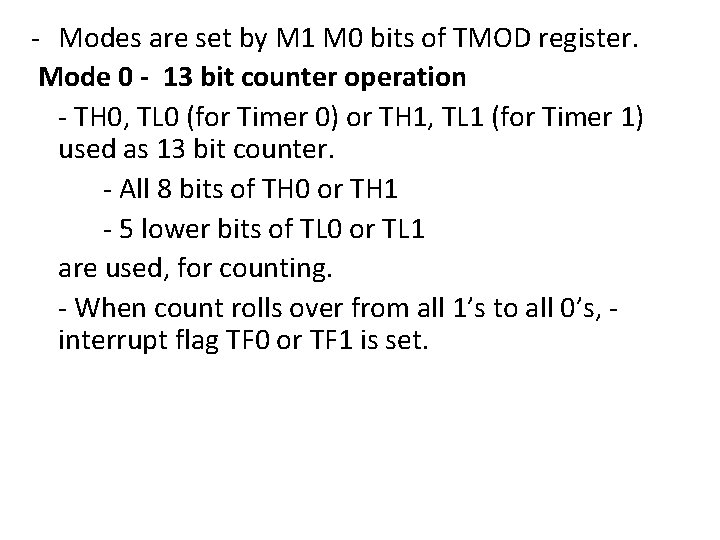

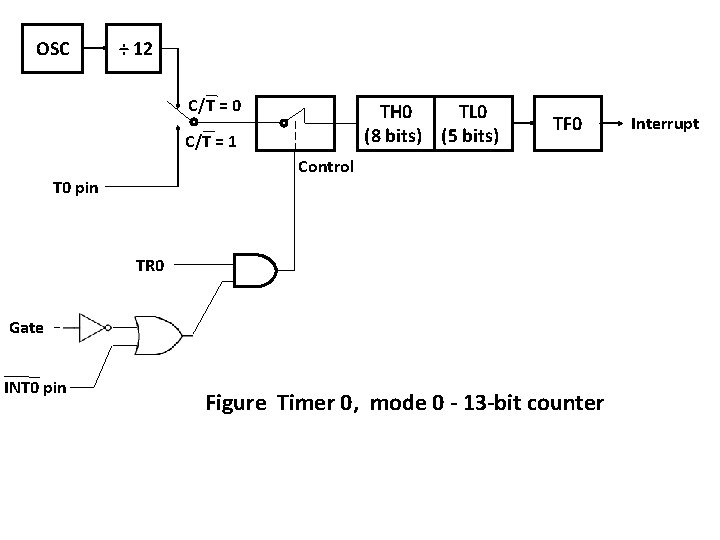

- Modes are set by M 1 M 0 bits of TMOD register. Mode 0 - 13 bit counter operation - TH 0, TL 0 (for Timer 0) or TH 1, TL 1 (for Timer 1) used as 13 bit counter. - All 8 bits of TH 0 or TH 1 - 5 lower bits of TL 0 or TL 1 are used, for counting. - When count rolls over from all 1’s to all 0’s, interrupt flag TF 0 or TF 1 is set.

OSC ÷ 12 C/T = 0 TH 0 TL 0 (8 bits) (5 bits) C/T = 1 TF 0 Control T 0 pin TR 0 Gate INT 0 pin Figure Timer 0, mode 0 - 13 -bit counter Interrupt

In above figure when C/T = 0 - timer operation count incremented every m/c cycle. provided TR 0 (TCON. 4) or TR 1 (TCON. 6) = 1 and Gate (TMOD. 3) or (TMOD. 7) = 0 Other way is- TR 0 or TR 1 =1 - Gate = 1 and INT 0 or INT 1 = 1 - Thus by sending Logic High signal on INT 0 (or INT 1) pins Timer 0 or Timer 1 can be started.

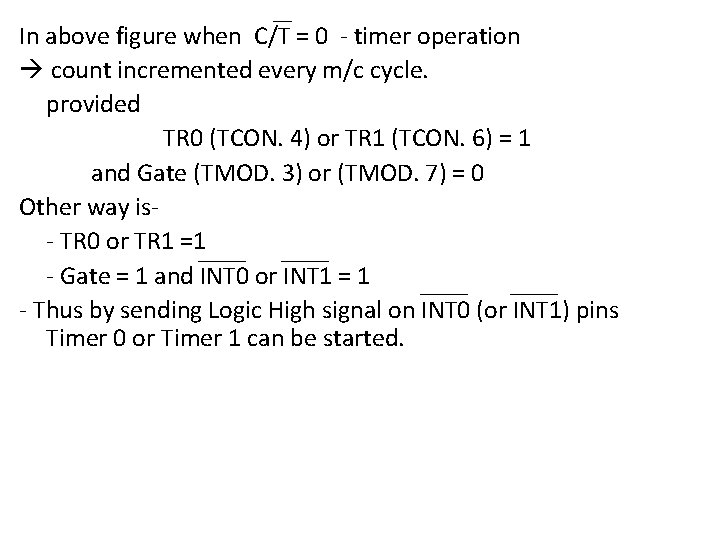

- This can be used for finding pulse width in the following way. C/T = 0 – Timer operation TR 0 or TR 1 = 1 Gate = 1 Source of pulse connected to INT 0 or INT 1 pin - When pulse goes high timer starts counting at the rate 1/12 clock frequency - Which pulse goes low – Timer stops. INT 0 or INT 1 = Low - causes interrupt.

Timer Starts Timer Stops + Interrupt Generated - ISR can read the timer value. - ISR can store the timer value and process it as required by the application.

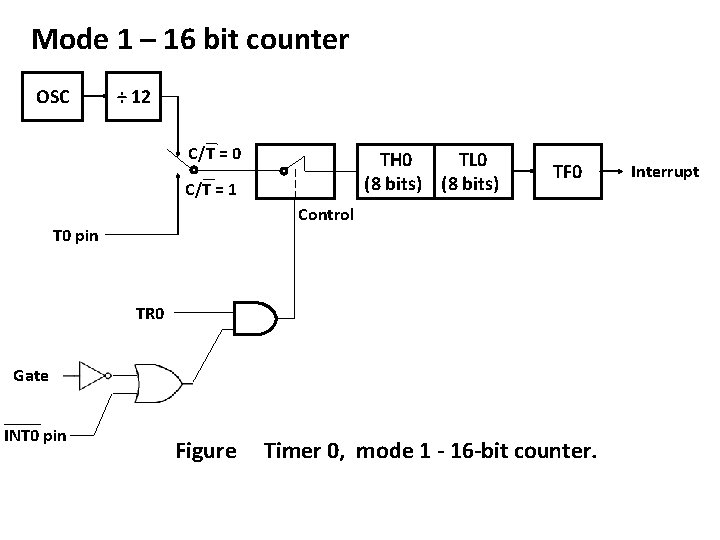

Mode 1 – 16 bit counter OSC ÷ 12 C/T = 0 TH 0 TL 0 (8 bits) C/T = 1 TF 0 Control T 0 pin TR 0 Gate INT 0 pin Figure Timer 0, mode 1 - 16 -bit counter. Interrupt

- Operation same as mode 0 except that all bits of TH 0, TL 0 or TH 1, TL 1 are used. When count rolls over from all 1’s to all 0’s – TF 0 or TF 1 interrupt flag is set. - Causes interrupt if enabled.

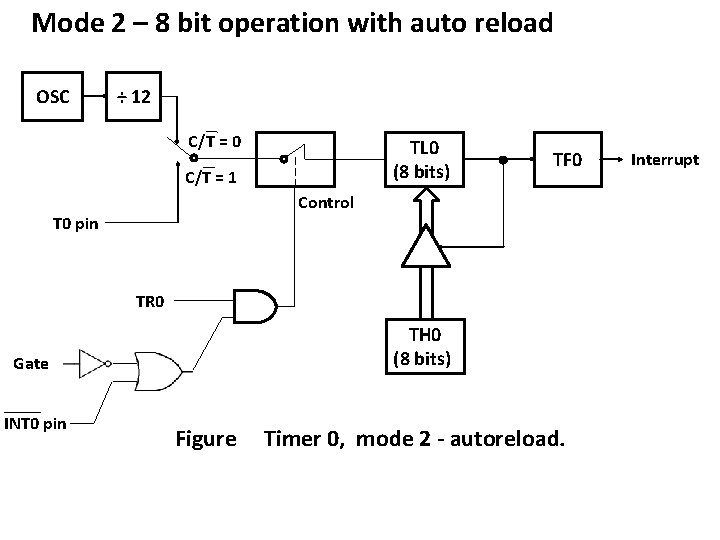

Mode 2 – 8 bit operation with auto reload OSC ÷ 12 C/T = 0 TL 0 (8 bits) C/T = 1 TF 0 Control T 0 pin TR 0 TH 0 (8 bits) Gate INT 0 pin Figure Timer 0, mode 2 - autoreload. Interrupt

- Only TL 0 or TL 1 are used i. e. 8 bit counting. - Initial preset value is loaded to TH 0 or TH 1 by software. - The value is loaded to TL 0 or TL 1 by hardware automatically before starts of counting. - When count rolls from all 1’s (i. e. FFH) to all 0’s (i. e. 00 H) - TF 0 or TF 1 flag is set - Preset value in TH 0 or TH 1 is reloaded to TL 0 or TL 1 - Operation i. e. Counting starts automatically.

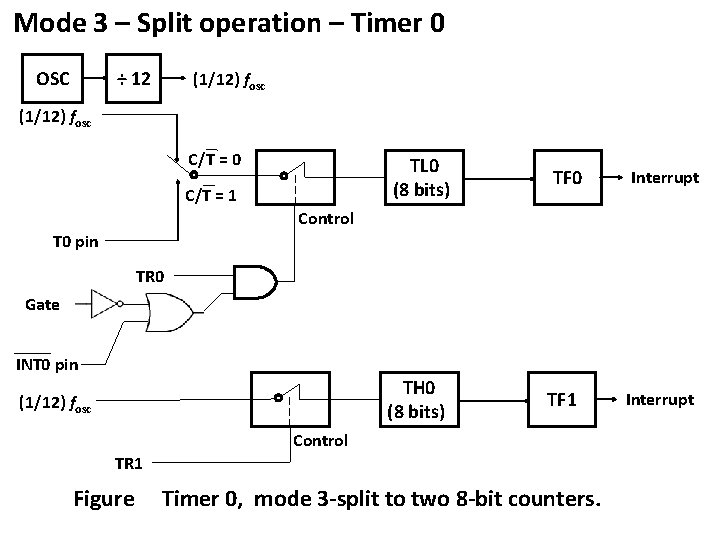

Mode 3 – Split operation – Timer 0 OSC ÷ 12 (1/12) fosc C/T = 0 C/T = 1 TL 0 (8 bits) TF 0 TH 0 (8 bits) TF 1 Interrupt Control T 0 pin TR 0 Gate INT 0 pin (1/12) fosc Control TR 1 Figure Timer 0, mode 3 -split to two 8 -bit counters. Interrupt

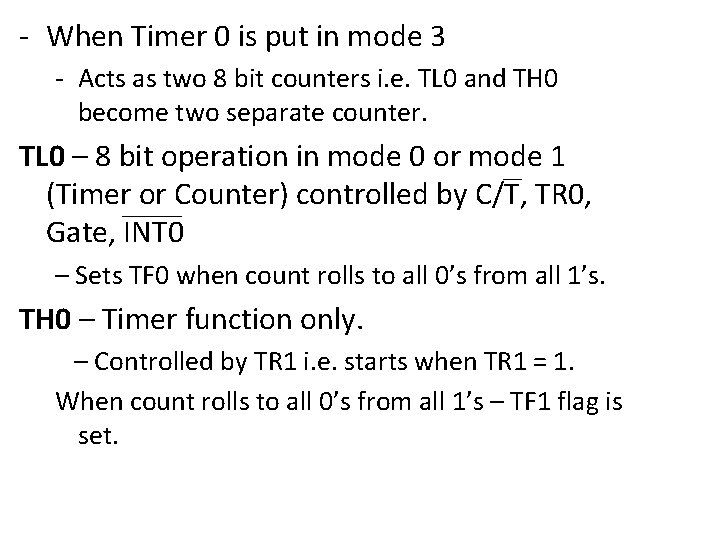

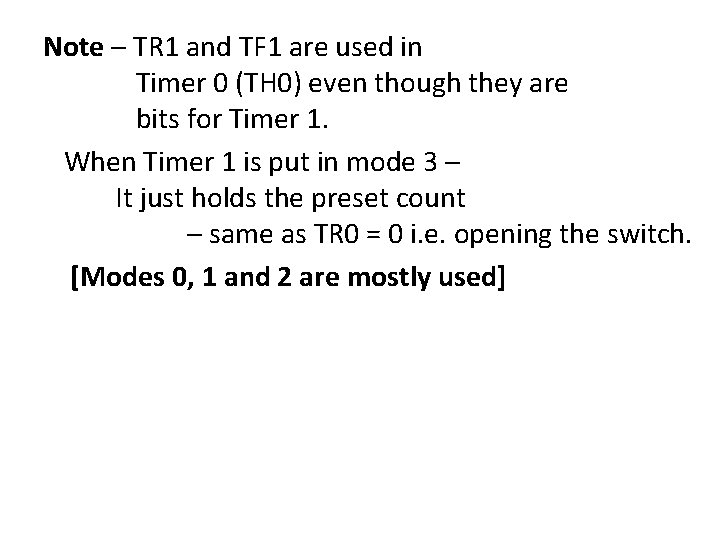

- When Timer 0 is put in mode 3 - Acts as two 8 bit counters i. e. TL 0 and TH 0 become two separate counter. TL 0 – 8 bit operation in mode 0 or mode 1 (Timer or Counter) controlled by C/T, TR 0, Gate, INT 0 – Sets TF 0 when count rolls to all 0’s from all 1’s. TH 0 – Timer function only. – Controlled by TR 1 i. e. starts when TR 1 = 1. When count rolls to all 0’s from all 1’s – TF 1 flag is set.

Note – TR 1 and TF 1 are used in Timer 0 (TH 0) even though they are bits for Timer 1. When Timer 1 is put in mode 3 – It just holds the preset count – same as TR 0 = 0 i. e. opening the switch. [Modes 0, 1 and 2 are mostly used]

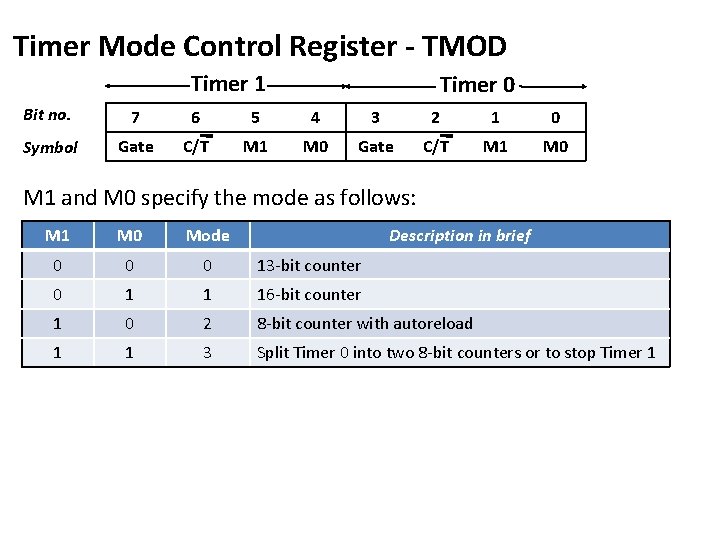

Timer Mode Control Register - TMOD Timer 1 Timer 0 Bit no. 7 6 5 4 3 2 1 0 Symbol Gate C/T M 1 M 0 M 1 and M 0 specify the mode as follows: M 1 M 0 Mode Description in brief 0 0 0 13 -bit counter 0 1 1 16 -bit counter 1 0 2 8 -bit counter with autoreload 1 1 3 Split Timer 0 into two 8 -bit counters or to stop Timer 1

If C/T = 1, the timers function as counters to count the negative transitions at T 0 or T 1 pins. If C/T = 0, the timers function as timers, that is, they basically count the number of machine cycles. Gate = 0 means that the timer is controlled by TR 1 or TR 0 only, irrespective of INT 0 or INT 1. Gate = 1 means that the timer control will depend on INT 0 or INT 1 and also on TR 0 or TR 1 bits

When data is written it gets latched. TMOD is used for setting mode bits M 1, M 0, Gate bit and C/T for Timer 0 and Timer 1. Bit 0 to 3 for Timer 0. Bit 4 to 7 for Timer 1.

Timer Control Register - TCON Bit 0 to 3 – used for interrupt functions Bit 4 to 7 – used for setting TR 0, TR 1 by software - Setting TF 0, TF 1 by counter i. e. hardware When count rolls from all 1’s to all 0’s.

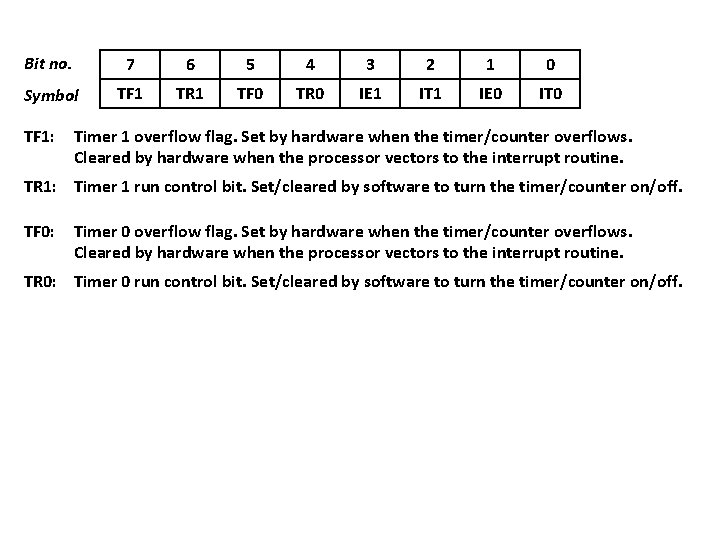

Bit no. 7 6 5 4 3 2 1 0 Symbol TF 1 TR 1 TF 0 TR 0 IE 1 IT 1 IE 0 IT 0 TF 1: Timer 1 overflow flag. Set by hardware when the timer/counter overflows. Cleared by hardware when the processor vectors to the interrupt routine. TR 1: Timer 1 run control bit. Set/cleared by software to turn the timer/counter on/off. TF 0: Timer 0 overflow flag. Set by hardware when the timer/counter overflows. Cleared by hardware when the processor vectors to the interrupt routine. TR 0: Timer 0 run control bit. Set/cleared by software to turn the timer/counter on/off.

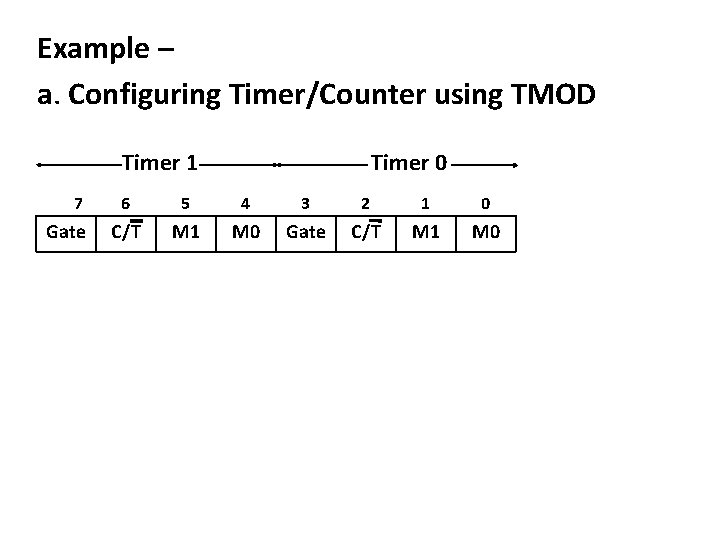

Example – a. Configuring Timer/Counter using TMOD Timer 1 7 Gate Timer 0 6 5 4 3 2 1 0 C/T M 1 M 0 Gate C/T M 1 M 0

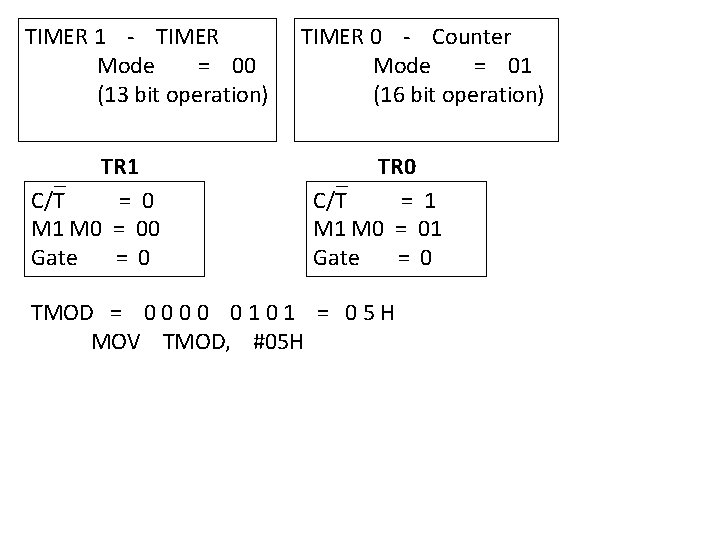

TIMER 1 - TIMER Mode = 00 (13 bit operation) TR 1 C/T = 0 M 1 M 0 = 00 Gate = 0 TIMER 0 - Counter Mode = 01 (16 bit operation) TR 0 C/T = 1 M 0 = 01 Gate = 0 TMOD = 0 0 0 1 = 0 5 H MOV TMOD, #05 H

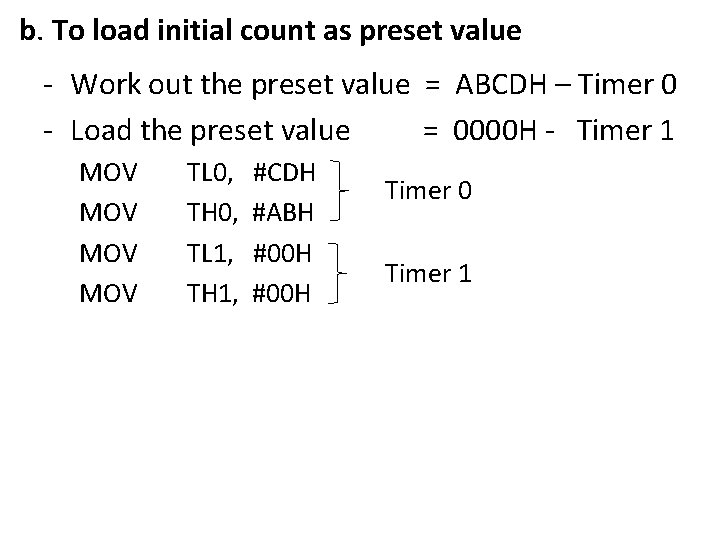

b. To load initial count as preset value - Work out the preset value = ABCDH – Timer 0 - Load the preset value = 0000 H - Timer 1 MOV MOV TL 0, TH 0, TL 1, TH 1, #CDH #ABH #00 H Timer 0 Timer 1

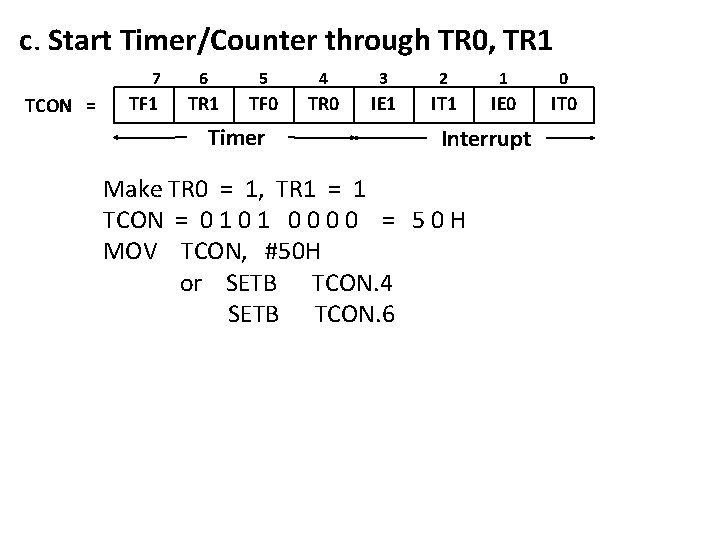

c. Start Timer/Counter through TR 0, TR 1 7 TCON = TF 1 6 5 4 3 2 1 0 TR 1 TF 0 TR 0 IE 1 IT 1 IE 0 IT 0 Timer Interrupt Make TR 0 = 1, TR 1 = 1 TCON = 0 1 0 0 = 5 0 H MOV TCON, #50 H or SETB TCON. 4 SETB TCON. 6

d. When count value in Timer Register transits from all 1’s to all 0’s - Following tasks need to be done. ØPreset value to be loaded to Timer Register ØTimer interrupt flag (TF 0 or TF 1) to be cleared For continuous operation of Timer/Counter ØTime clock ØPulse train generation etc.

- Can be achieved in 2 ways: 1. - Check Timer interrupt flag in loop. JNB TCON. 5, $ or JNB TCON. 7, $ - When interrupt flag is set then clear the flag. CLR TCON. 5 or CLR TCON. 7 - Load the preset count and restart SJMP to b

2. Write ISR for Timer 0 or Timer 1 and store at location 000 BH (for Timer 0) or 001 BH (for Timer 1) - Enable Timer 0 or Timer 1 interrupt by making bits ET 0 (IE. 1) or ET 1(IE. 3) = 1. SETB IE. 1 or SETB IE. 3 - When TF 0 or TF 1 is set - Interrupt will occur and program will branch to ISR location (000 BH for Timer 0) or (001 BH for Timer 1).

- ISR - clear flag TF 0 or TF 1 - load preset value - Restart timer/counter RETI Step d will be different for different applications. Example -1 - Generate a square wave of 50% duty cycle at pin p 1. 7. Use Timer 1 to generate time delay. Clock frequency = 12 MHz, 12 oscillator clock. Pulse width = 50 millisecond. - Let us work out the initial preset value.

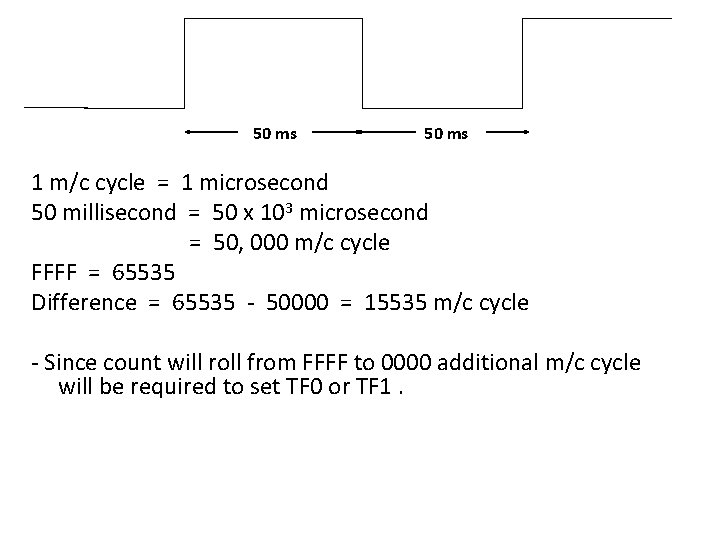

50 ms 1 m/c cycle = 1 microsecond 50 millisecond = 50 x 103 microsecond = 50, 000 m/c cycle FFFF = 65535 Difference = 65535 - 50000 = 15535 m/c cycle - Since count will roll from FFFF to 0000 additional m/c cycle will be required to set TF 0 or TF 1.

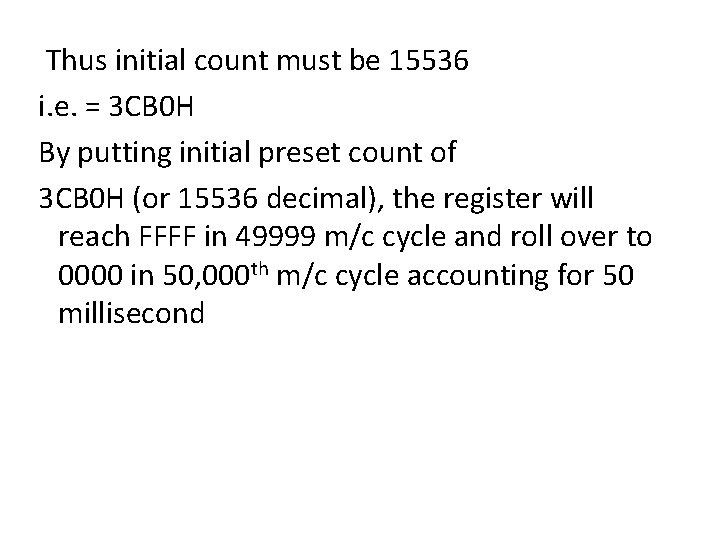

Thus initial count must be 15536 i. e. = 3 CB 0 H By putting initial preset count of 3 CB 0 H (or 15536 decimal), the register will reach FFFF in 49999 m/c cycle and roll over to 0000 in 50, 000 th m/c cycle accounting for 50 millisecond

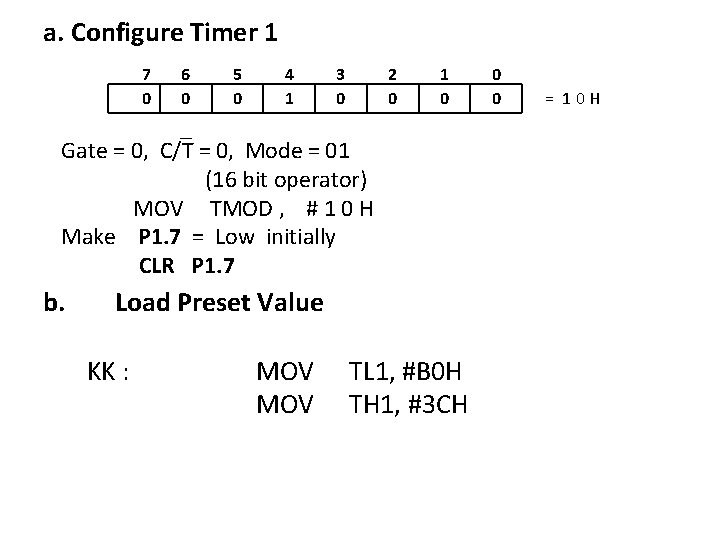

a. Configure Timer 1 7 0 6 0 5 0 4 1 3 0 2 0 1 0 Gate = 0, C/T = 0, Mode = 01 (16 bit operator) MOV TMOD , # 1 0 H Make P 1. 7 = Low initially CLR P 1. 7 b. Load Preset Value KK : MOV TL 1, #B 0 H TH 1, #3 CH 0 0 = 10 H

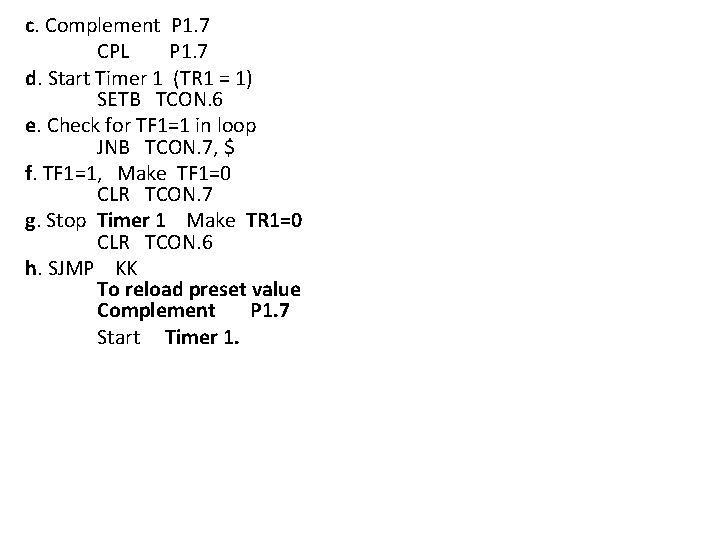

c. Complement P 1. 7 CPL P 1. 7 d. Start Timer 1 (TR 1 = 1) SETB TCON. 6 e. Check for TF 1=1 in loop JNB TCON. 7, $ f. TF 1=1, Make TF 1=0 CLR TCON. 7 g. Stop Timer 1 Make TR 1=0 CLR TCON. 6 h. SJMP KK To reload preset value Complement P 1. 7 Start Timer 1.

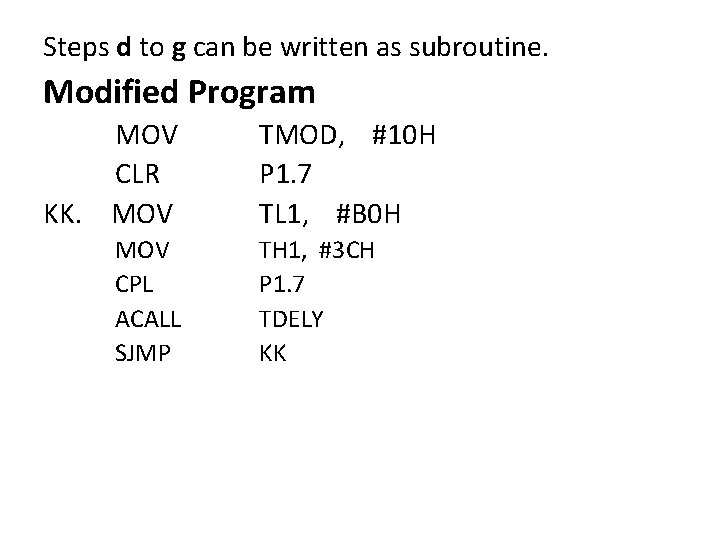

Steps d to g can be written as subroutine. Modified Program MOV CLR KK. MOV CPL ACALL SJMP TMOD, #10 H P 1. 7 TL 1, #B 0 H TH 1, #3 CH P 1. 7 TDELY KK

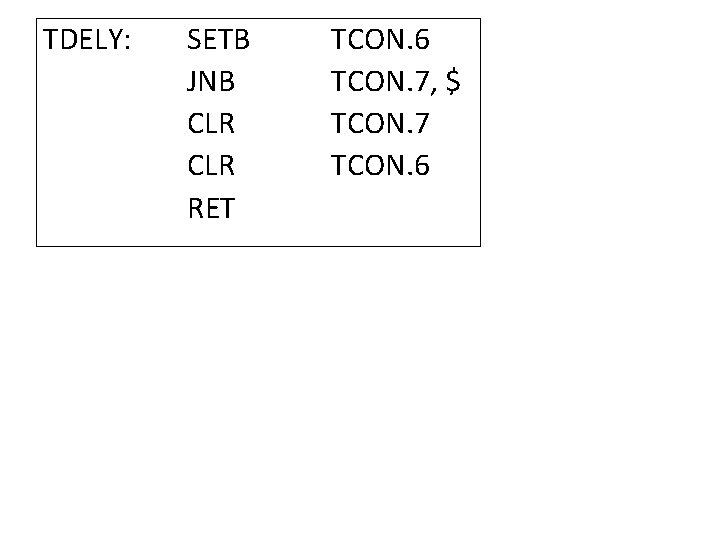

TDELY: SETB JNB CLR RET TCON. 6 TCON. 7, $ TCON. 7 TCON. 6

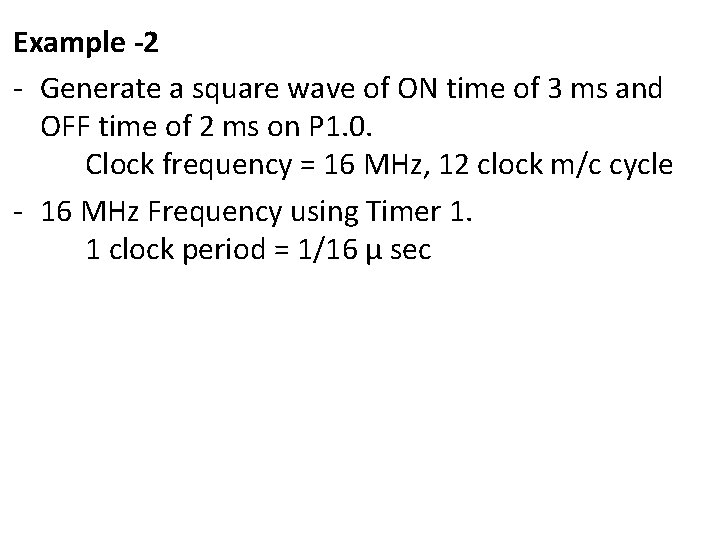

Example -2 - Generate a square wave of ON time of 3 ms and OFF time of 2 ms on P 1. 0. Clock frequency = 16 MHz, 12 clock m/c cycle - 16 MHz Frequency using Timer 1. 1 clock period = 1/16 µ sec

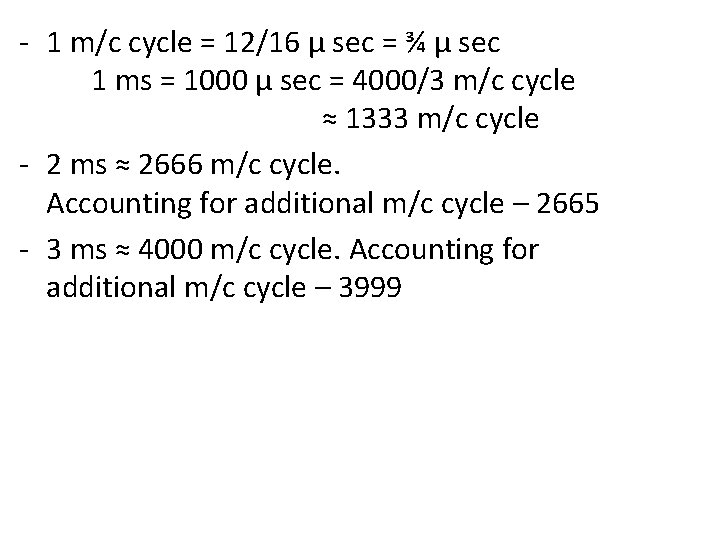

- 1 m/c cycle = 12/16 µ sec = ¾ µ sec 1 ms = 1000 µ sec = 4000/3 m/c cycle ≈ 1333 m/c cycle - 2 ms ≈ 2666 m/c cycle. Accounting for additional m/c cycle – 2665 - 3 ms ≈ 4000 m/c cycle. Accounting for additional m/c cycle – 3999

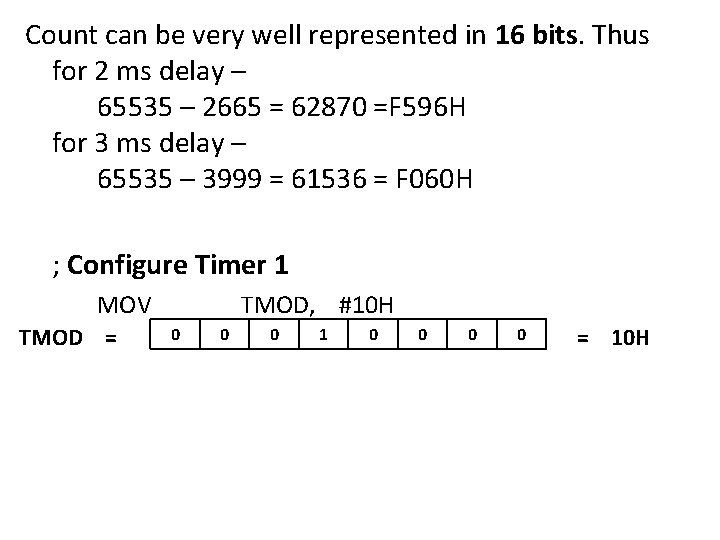

Count can be very well represented in 16 bits. Thus for 2 ms delay – 65535 – 2665 = 62870 =F 596 H for 3 ms delay – 65535 – 3999 = 61536 = F 060 H ; Configure Timer 1 MOV TMOD = TMOD, #10 H 0 0 0 1 0 0 = 10 H

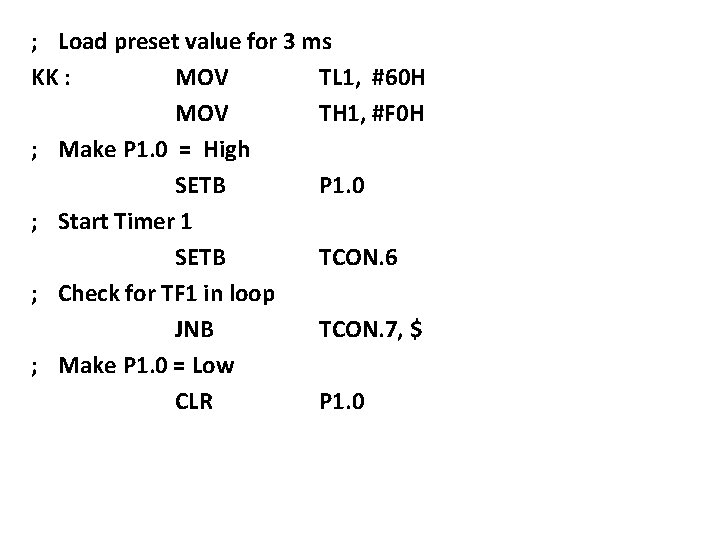

; Load preset value for 3 ms KK : MOV TL 1, #60 H MOV TH 1, #F 0 H ; Make P 1. 0 = High SETB P 1. 0 ; Start Timer 1 SETB TCON. 6 ; Check for TF 1 in loop JNB TCON. 7, $ ; Make P 1. 0 = Low CLR P 1. 0

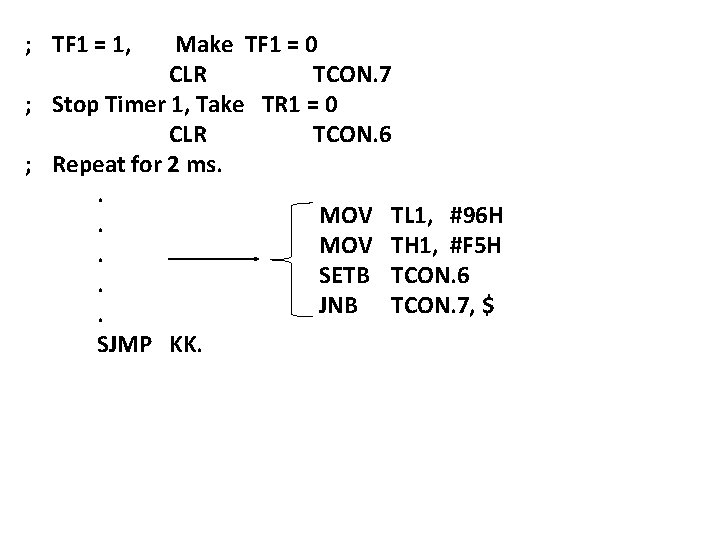

; TF 1 = 1, Make TF 1 = 0 CLR TCON. 7 ; Stop Timer 1, Take TR 1 = 0 CLR TCON. 6 ; Repeat for 2 ms. . MOV TL 1, #96 H. MOV TH 1, #F 5 H. SETB TCON. 6. JNB TCON. 7, $. SJMP KK.

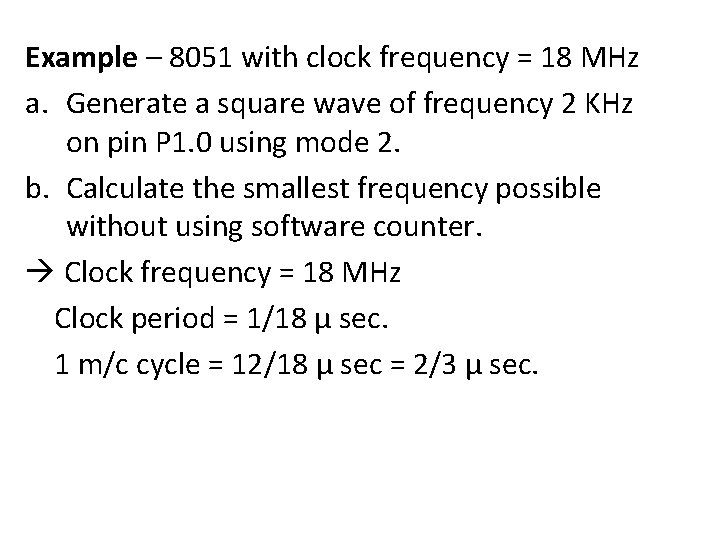

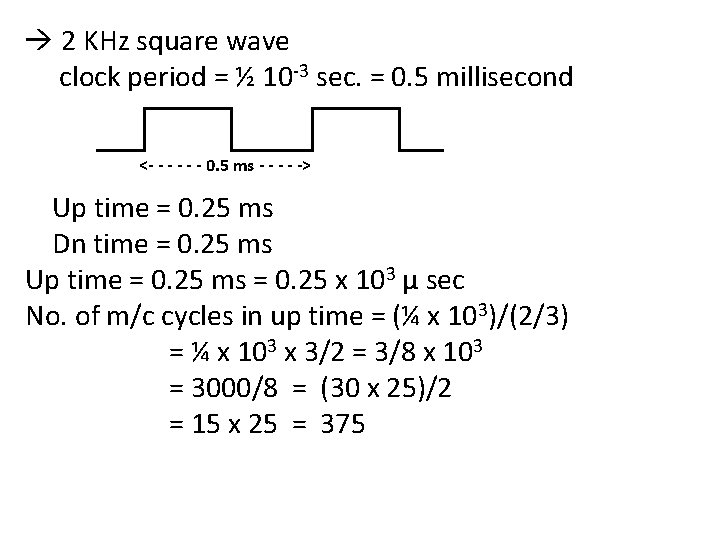

Example – 8051 with clock frequency = 18 MHz a. Generate a square wave of frequency 2 KHz on pin P 1. 0 using mode 2. b. Calculate the smallest frequency possible without using software counter. Clock frequency = 18 MHz Clock period = 1/18 µ sec. 1 m/c cycle = 12/18 µ sec = 2/3 µ sec.

2 KHz square wave clock period = ½ 10 -3 sec. = 0. 5 millisecond <- - - 0. 5 ms - - -> Up time = 0. 25 ms Dn time = 0. 25 ms Up time = 0. 25 ms = 0. 25 x 103 µ sec No. of m/c cycles in up time = (¼ x 103)/(2/3) = ¼ x 103 x 3/2 = 3/8 x 103 = 3000/8 = (30 x 25)/2 = 15 x 25 = 375

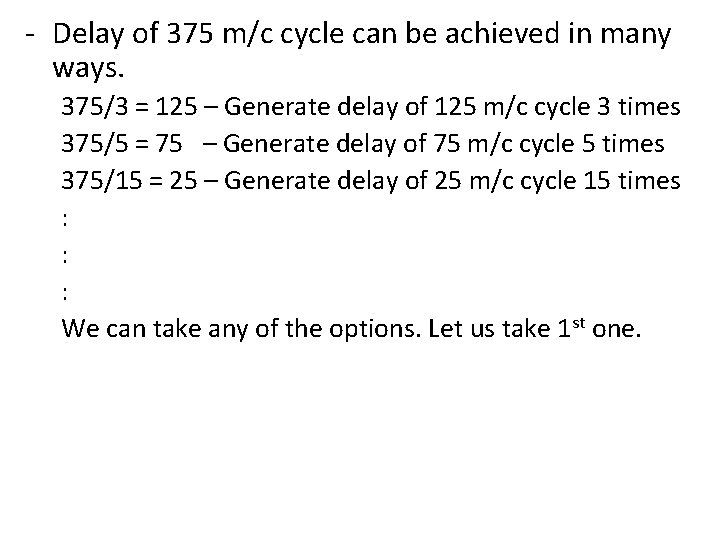

- Delay of 375 m/c cycle can be achieved in many ways. 375/3 = 125 – Generate delay of 125 m/c cycle 3 times 375/5 = 75 – Generate delay of 75 m/c cycle 5 times 375/15 = 25 – Generate delay of 25 m/c cycle 15 times : : : We can take any of the options. Let us take 1 st one.

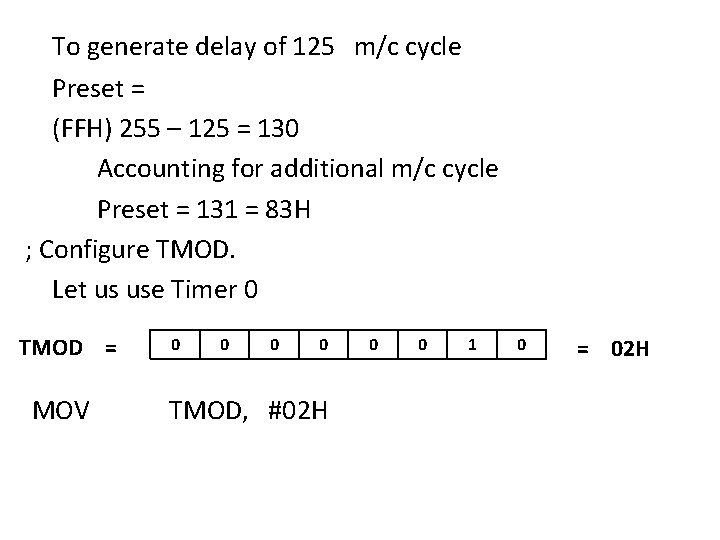

To generate delay of 125 m/c cycle Preset = (FFH) 255 – 125 = 130 Accounting for additional m/c cycle Preset = 131 = 83 H ; Configure TMOD. Let us use Timer 0 TMOD = MOV 0 0 TMOD, #02 H 0 0 1 0 = 02 H

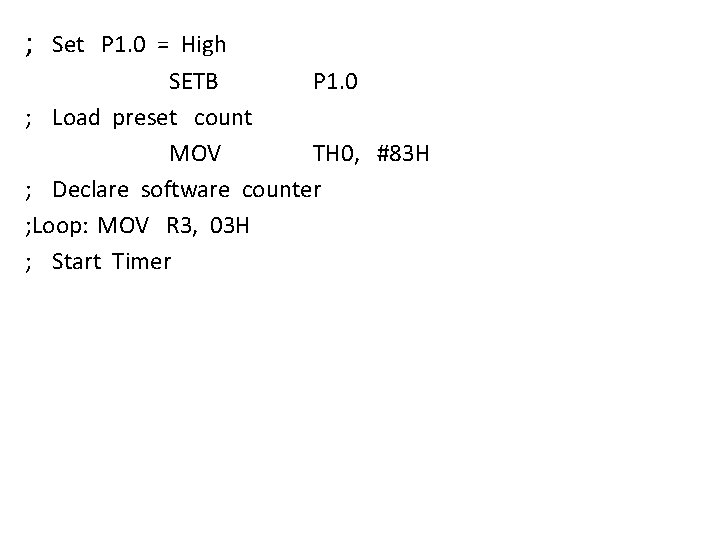

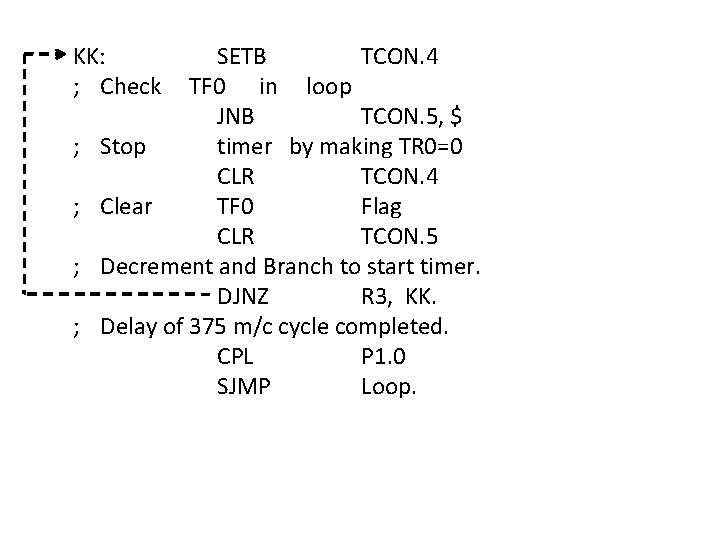

; Set P 1. 0 = High SETB P 1. 0 ; Load preset count MOV TH 0, #83 H ; Declare software counter ; Loop: MOV R 3, 03 H ; Start Timer

KK: ; Check ; ; SETB TCON. 4 TF 0 in loop JNB TCON. 5, $ Stop timer by making TR 0=0 CLR TCON. 4 Clear TF 0 Flag CLR TCON. 5 Decrement and Branch to start timer. DJNZ R 3, KK. Delay of 375 m/c cycle completed. CPL P 1. 0 SJMP Loop.

b. – Frequency is smallest when clock period = maximum i. e. Up time and Down time = maximum i. e. Delay is maximum when preset value =0 i. e. No. of m/c cycles in Up time = FF+1 No. of m/c cycles in Dn time = FF+1 Up time = 256 x 2/3 µ sec = 512/3 ≈ 170 µ sec Clock period = 341 µ sec. Frequency = 1/341 MHz = 1000/341 KHz = 2. 92 KHz

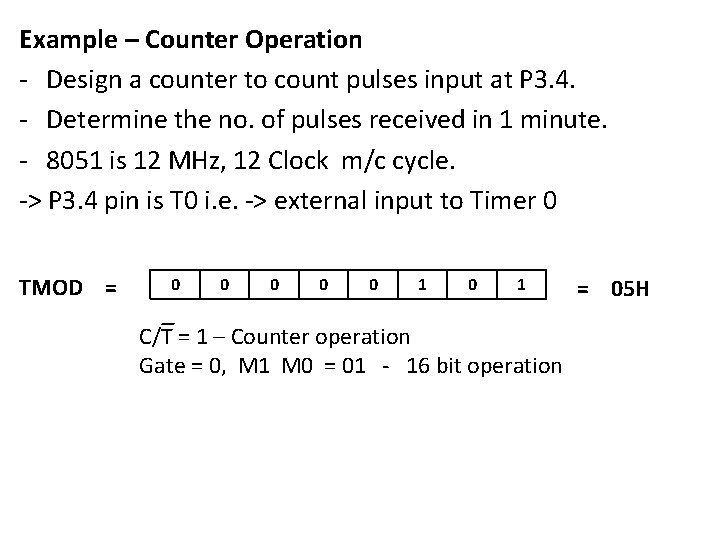

Example – Counter Operation - Design a counter to count pulses input at P 3. 4. - Determine the no. of pulses received in 1 minute. - 8051 is 12 MHz, 12 Clock m/c cycle. -> P 3. 4 pin is T 0 i. e. -> external input to Timer 0 TMOD = 0 0 0 1 C/T = 1 – Counter operation Gate = 0, M 1 M 0 = 01 - 16 bit operation = 05 H

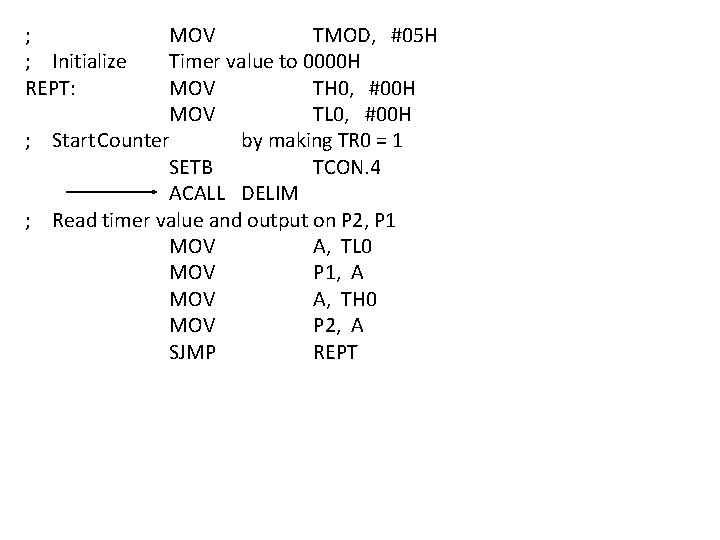

; ; Initialize REPT: MOV TMOD, #05 H Timer value to 0000 H MOV TH 0, #00 H MOV TL 0, #00 H ; Start. Counter by making TR 0 = 1 SETB TCON. 4 ACALL DELIM ; Read timer value and output on P 2, P 1 MOV A, TL 0 MOV P 1, A MOV A, TH 0 MOV P 2, A SJMP REPT

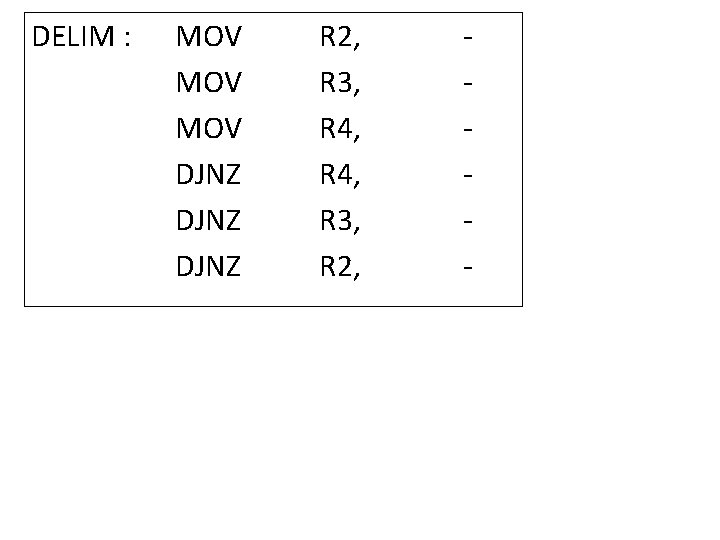

DELIM : MOV MOV DJNZ R 2, R 3, R 4, R 3, R 2, -

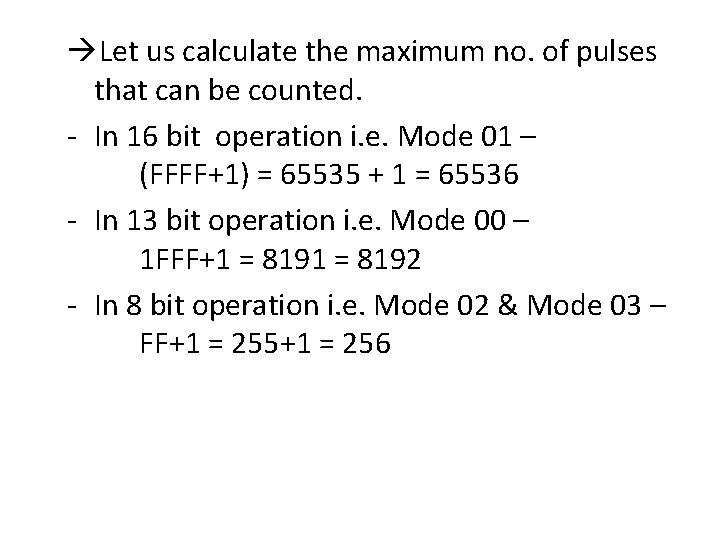

Let us calculate the maximum no. of pulses that can be counted. - In 16 bit operation i. e. Mode 01 – (FFFF+1) = 65535 + 1 = 65536 - In 13 bit operation i. e. Mode 00 – 1 FFF+1 = 8192 - In 8 bit operation i. e. Mode 02 & Mode 03 – FF+1 = 255+1 = 256

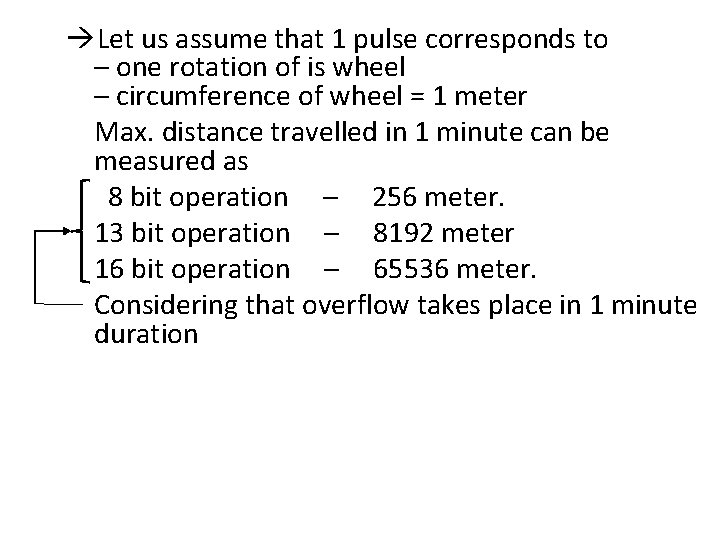

Let us assume that 1 pulse corresponds to – one rotation of is wheel – circumference of wheel = 1 meter Max. distance travelled in 1 minute can be measured as 8 bit operation – 256 meter. 13 bit operation – 8192 meter 16 bit operation – 65536 meter. Considering that overflow takes place in 1 minute duration

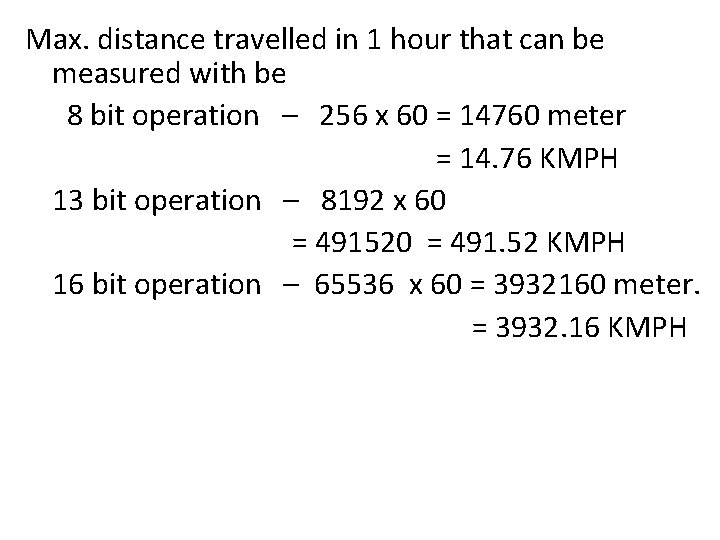

Max. distance travelled in 1 hour that can be measured with be 8 bit operation – 256 x 60 = 14760 meter = 14. 76 KMPH 13 bit operation – 8192 x 60 = 491520 = 491. 52 KMPH 16 bit operation – 65536 x 60 = 3932160 meter. = 3932. 16 KMPH

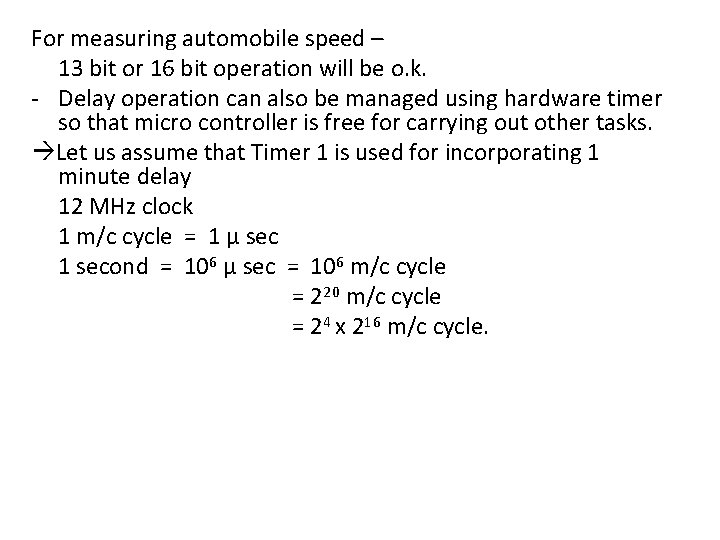

For measuring automobile speed – 13 bit or 16 bit operation will be o. k. - Delay operation can also be managed using hardware timer so that micro controller is free for carrying out other tasks. Let us assume that Timer 1 is used for incorporating 1 minute delay 12 MHz clock 1 m/c cycle = 1 µ sec 1 second = 106 µ sec = 106 m/c cycle = 220 m/c cycle = 24 x 216 m/c cycle.

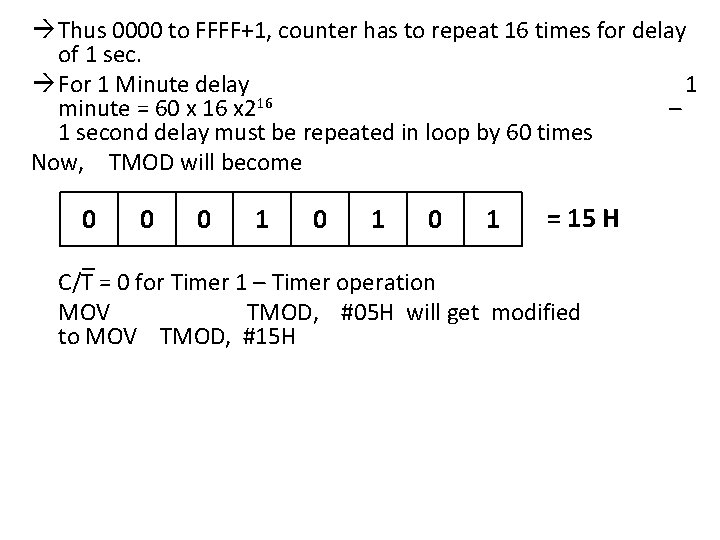

Thus 0000 to FFFF+1, counter has to repeat 16 times for delay of 1 sec. For 1 Minute delay 1 minute = 60 x 16 x 216 – 1 second delay must be repeated in loop by 60 times Now, TMOD will become 0 0 0 1 0 1 = 15 H C/T = 0 for Timer 1 – Timer operation MOV TMOD, #05 H will get modified to MOV TMOD, #15 H

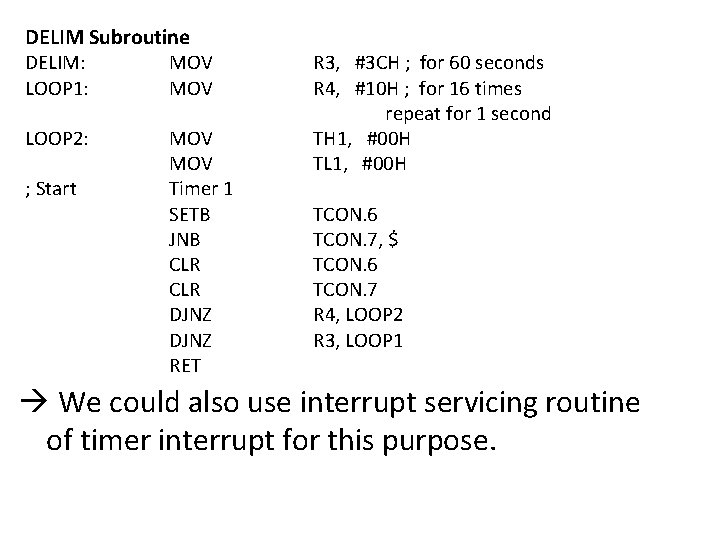

DELIM Subroutine DELIM: MOV LOOP 1: MOV LOOP 2: ; Start MOV Timer 1 SETB JNB CLR DJNZ RET R 3, #3 CH ; for 60 seconds R 4, #10 H ; for 16 times repeat for 1 second TH 1, #00 H TL 1, #00 H TCON. 6 TCON. 7, $ TCON. 6 TCON. 7 R 4, LOOP 2 R 3, LOOP 1 We could also use interrupt servicing routine of timer interrupt for this purpose.

THE END

- Slides: 60