Microprocessors I 8051 Addressing Modes CS00871 Prof Msc

- Slides: 19

Microprocessors I 8051 Addressing Modes CS-00871 Prof. Msc. Ivan A. Escobar iescobar@itesm. mx

Introduction l l Assembly language is machine dependant. Each family of microprocessors or microncontrollers has its own instruction set. Each instruction has an 8 bit op-code with an associated mnemonic. Some instructions have one or two additional bytes for operand (data or addresses).

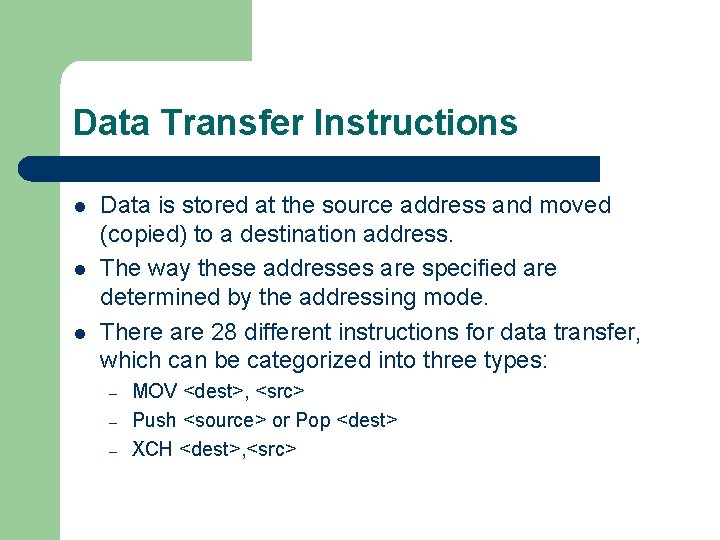

Data Transfer Instructions l l l Data is stored at the source address and moved (copied) to a destination address. The way these addresses are specified are determined by the addressing mode. There are 28 different instructions for data transfer, which can be categorized into three types: – – – MOV <dest>, <src> Push <source> or Pop <dest> XCH <dest>, <src>

Addressing Modes l When operating with data, where does it reside? – – l As part of the instruction? In a register? In general memory? In external memory? The 8051 has numerous modes of addressing data.

Available Modes l l l l Immediate Register Direct Indirect Relative Absolute Long Indexed

Immediate Addressing l l The data is numeric constant in the operand. Indicated by a # sign. MOV A, #34 h Moves the value of 34 hex into the Acc. 2 byte instruction: – l Opcode | Data Useful for getting constants into registers

Immediate Addressing – The immediate value is a maximum of 8 -bits. l One exception, when dealing with the DPTR register it can be 16 -bits. l MOV DPTR, #2000 H ; Load the value 2000 H into the DPTR register MOV R 0, #0 F 0 H ; Load R 0 with the value F 0 H l

Register Addressing l Direct access to eight registers – R 0 through R 7. l MOV A, R 0 MOV R 1, A ADD A, R 1 l Not all combinations are valid. l l – MOV R 2, R 1 ; Invalid

Register Addressing l There are 4 banks of registers accessible through register addressing. – Only one bank can be accessed at a time controllable through bit RS 0 and RS 1 of the PSW l l MOV PSW, #00011000 B Set RS 0: RS 1 to 11, therefore, accessing register bank 3.

Register Addressing l The register is part of the Op-code. Allows for a 1 byte instruction. – – – Op-code uses 3 bits for Rn MOV A, R 3 Moves the contents of R 3 into the Acc.

Direct Addressing l l Access any on-chip RAM location General purpose registers. Control registers. May be addressed by location or name – – l MOV E 0 h, #33 h Moves the hex value of 33 into memory location E 0 h. MOV P 0, #85 h Moves the hex value 85 into P 0 register port. 2 byte instruction + possible data – Opcode | Direct Address | Data

Direct Addressing – All on-chip memory locations and registers have 8 -bit addresses. – Can use the 8 -bit address in the instruction. l – ; A mem[04 H] Or can use the register name. l – MOV A, 4 H MOV A, R 4 Don’t get confused with Immediate mode. l No “#” sign.

Indirect Addressing l l l R 0 or R 1 hold the location of the internal RAM location. Indicated by the @ sign. MOV A, @R 1 Moves the contents of the memory address indicated by R 1 to the Acc. Example: If R 1 contains 23 h, the contents of address 23 h will be moved to the Acc. One byte instruction: – Opcode using 1 bit for R 0 or R 1.

Indirect Addressing l Example: l MOV R 1, #40 H MOV A, @R 1 ; Make R 1 point to location 40 ; Move the contents of 40 H to A l MOV @R 0, R 1 ; Move contents of R 1 into the memory location pointed to by R 0. l

Indirect Addressing l Can also be used for accessing external memory: – Can use R 0 and R 1 to point to external memory locations 00 H to FFH. l – MOVX A, @R 1 ; Move contents of external memory location whose address is in R 1 into A Can also use DPTR to point to all 64 k of external memory. l MOVX A, @DPTR

Relative Addressing l l l Used with certain jumps. A jump is made from current address to a +127 or -128 memory location. SJMP #20 h – l PC = PC + 20 (jump ahead 20 addresses). 2 Byte instruction: – Opcode | Relative offset

Absolute Addressing l l Used with ACALL (Absolute call) and AJMP (Absolute Jump). Allows a call within a 2 K page of memory. The op-code contains 3 of the 11 bits of the address, the operand contains lower 8 bits. 2 bytes instruction: – l 3 bits+op-code | lower 8 -bit address. The address being called must be with the same 2 K page.

Long Addressing l l l Used with LCALL (Long Call) and LJMP (Long Jump) instructions. Allows jumping to any 16 -bit address. 3 bytes instruction: – Opcode | High order | Low order

Indexed Addressing l Use a register for storing a pointer to memory and another register for storing an offset. – The effective address is the sum of the two: l EA = Pointer + Offset l MOVC A, @A+DPTR ; Move byte from memory located at DPTR+A to A.