Registers Counters Registers Shift Registers Serial in serial

- Slides: 23

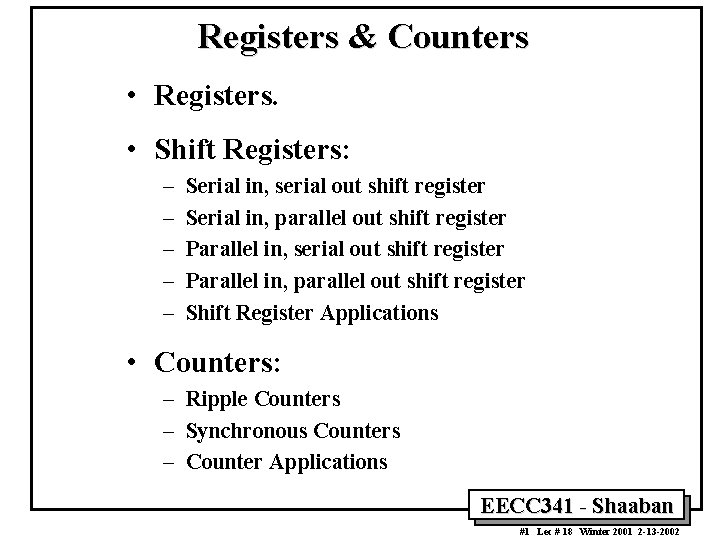

Registers & Counters • Registers. • Shift Registers: – – – Serial in, serial out shift register Serial in, parallel out shift register Parallel in, serial out shift register Parallel in, parallel out shift register Shift Register Applications • Counters: – Ripple Counters – Synchronous Counters – Counter Applications EECC 341 - Shaaban #1 Lec # 18 Winter 2001 2 -13 -2002

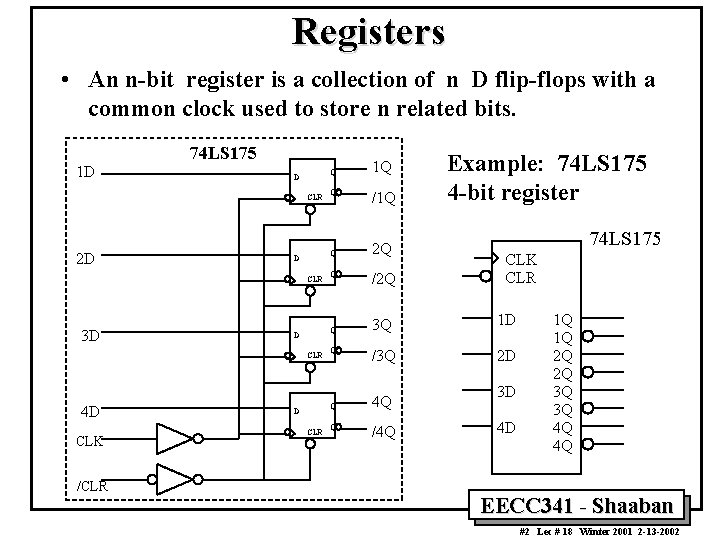

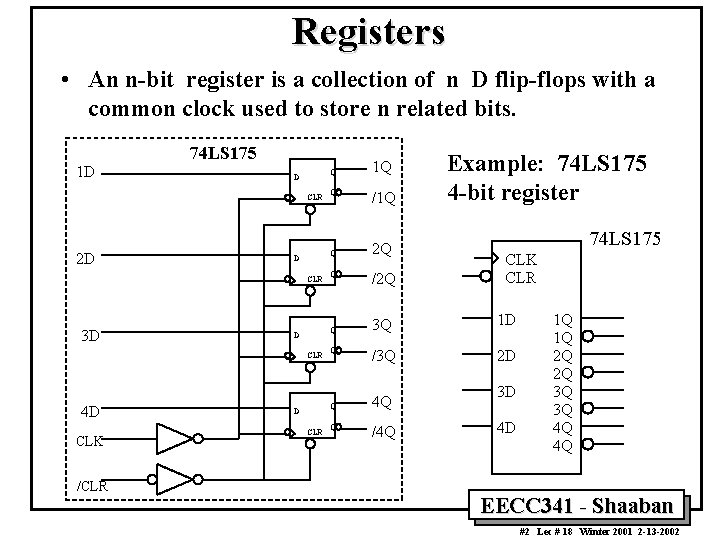

Registers • An n-bit register is a collection of n D flip-flops with a common clock used to store n related bits. 74 LS 175 1 D Q D CLR 2 D Q D CLR 3 D CLK /CLR Q Q D CLR 4 D Q Q Q D CLR Q 1 Q /1 Q 2 Q /2 Q Example: 74 LS 175 4 -bit register 74 LS 175 CLK CLR 3 Q 1 D /3 Q 2 D 4 Q /4 Q 3 D 4 D 1 Q 1 Q 2 Q 2 Q 3 Q 3 Q 4 Q 4 Q EECC 341 - Shaaban #2 Lec # 18 Winter 2001 2 -13 -2002

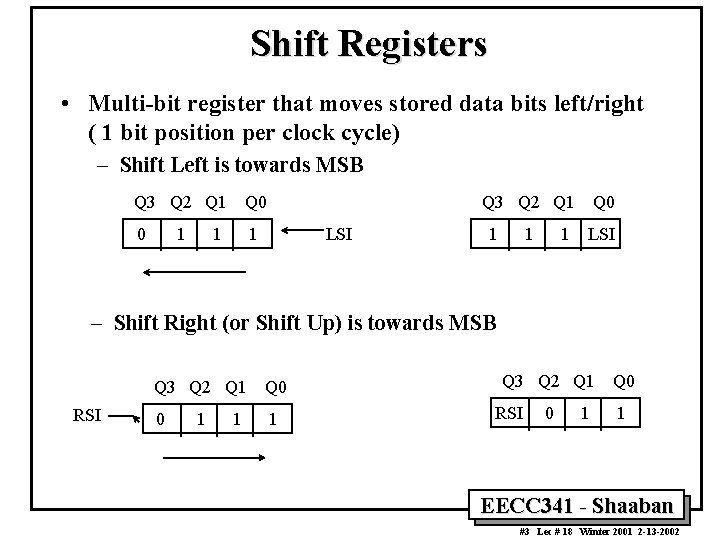

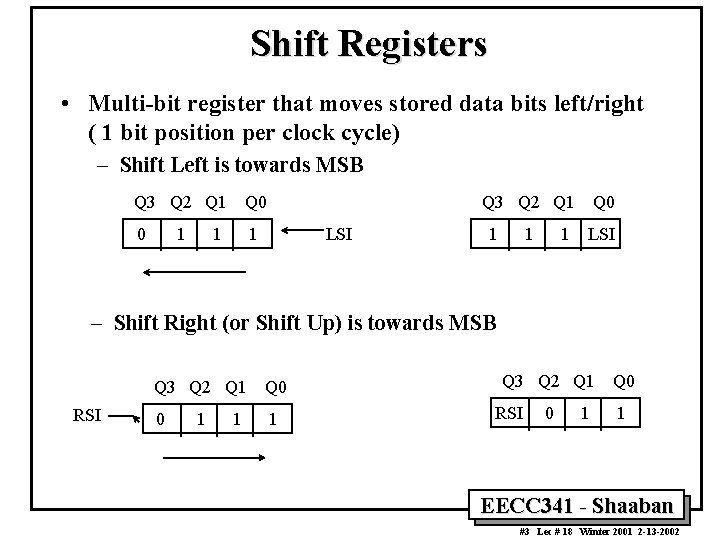

Shift Registers • Multi-bit register that moves stored data bits left/right ( 1 bit position per clock cycle) – Shift Left is towards MSB Q 3 Q 2 Q 1 Q 0 0 1 1 1 Q 3 Q 2 Q 1 LSI 1 1 1 Q 0 LSI – Shift Right (or Shift Up) is towards MSB RSI Q 3 Q 2 Q 1 Q 0 0 1 1 1 Q 3 Q 2 Q 1 RSI 0 1 Q 0 1 EECC 341 - Shaaban #3 Lec # 18 Winter 2001 2 -13 -2002

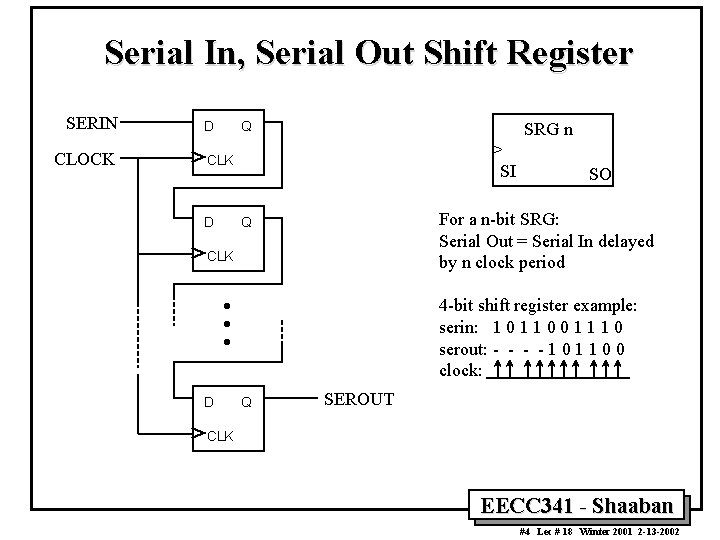

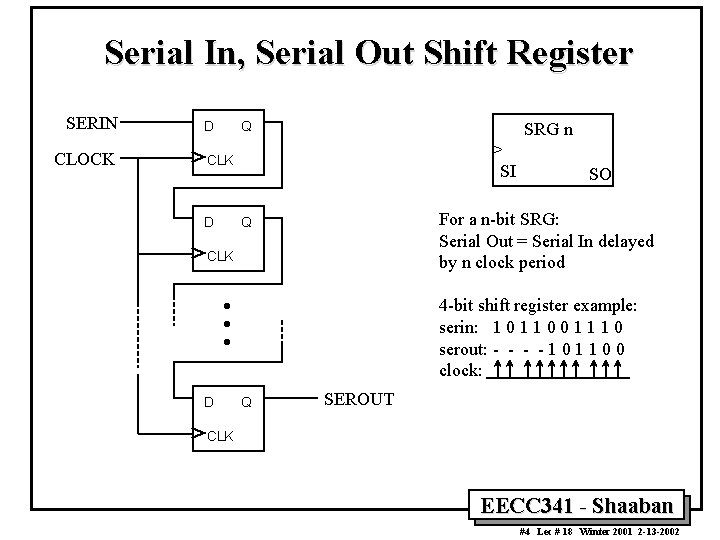

Serial In, Serial Out Shift Register SERIN CLOCK D Q SRG n > SI CLK D For a n-bit SRG: Serial Out = Serial In delayed by n clock period Q CLK · · · D SO 4 -bit shift register example: serin: 1 0 1 1 0 0 1 1 1 0 serout: - - 1 0 1 1 0 0 clock: Q SEROUT CLK EECC 341 - Shaaban #4 Lec # 18 Winter 2001 2 -13 -2002

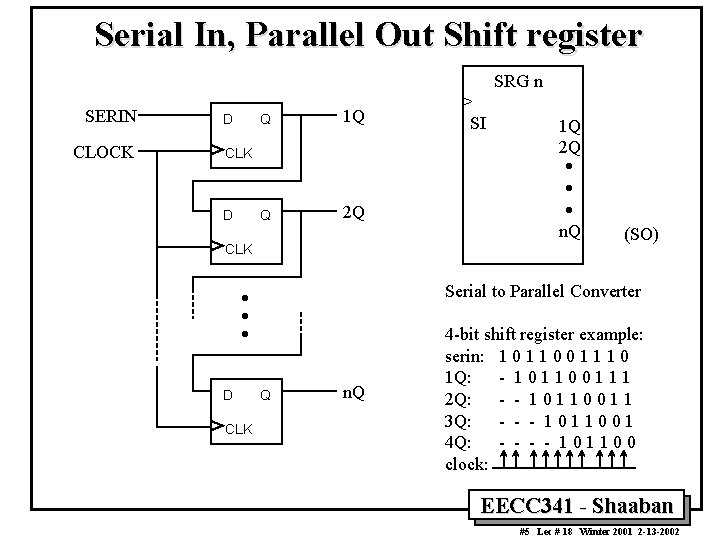

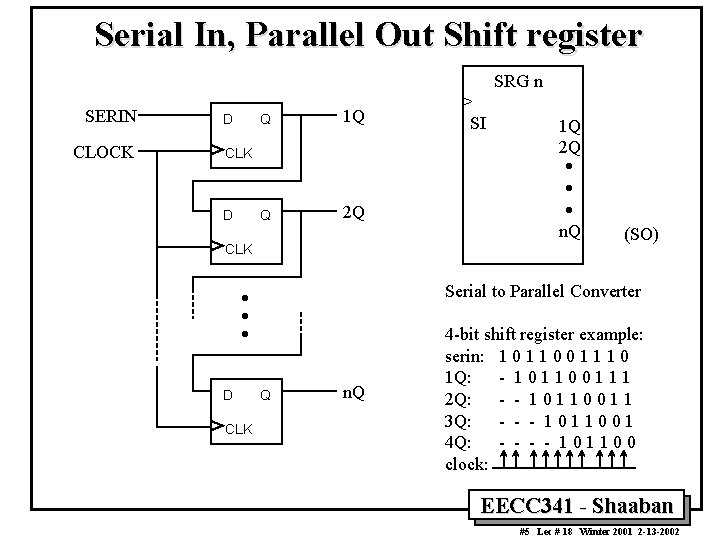

Serial In, Parallel Out Shift register SRG n SERIN CLOCK D Q 1 Q Q 2 Q CLK D CLK 1 Q 2 Q · · · n. Q (SO) Serial to Parallel Converter · · · D > SI Q n. Q 4 -bit shift register example: serin: 1 0 1 1 0 0 1 1 1 0 1 Q: - 101100111 2 Q: - - 10110011 3 Q: - - - 1011001 4 Q: - - 101100 clock: EECC 341 - Shaaban #5 Lec # 18 Winter 2001 2 -13 -2002

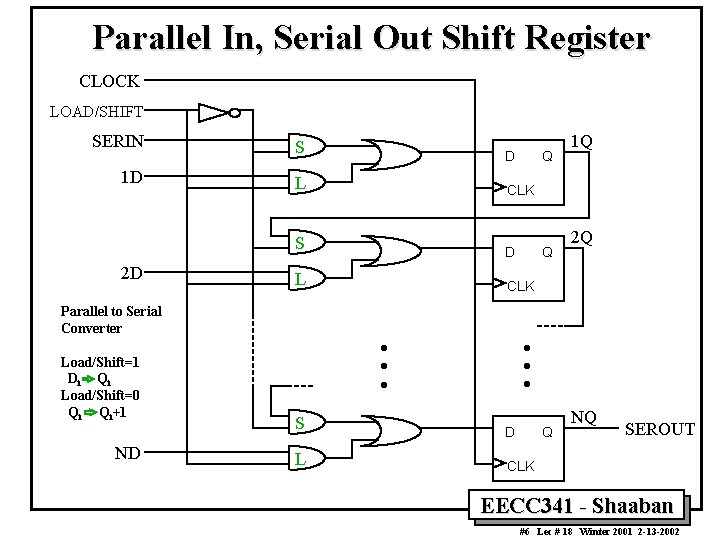

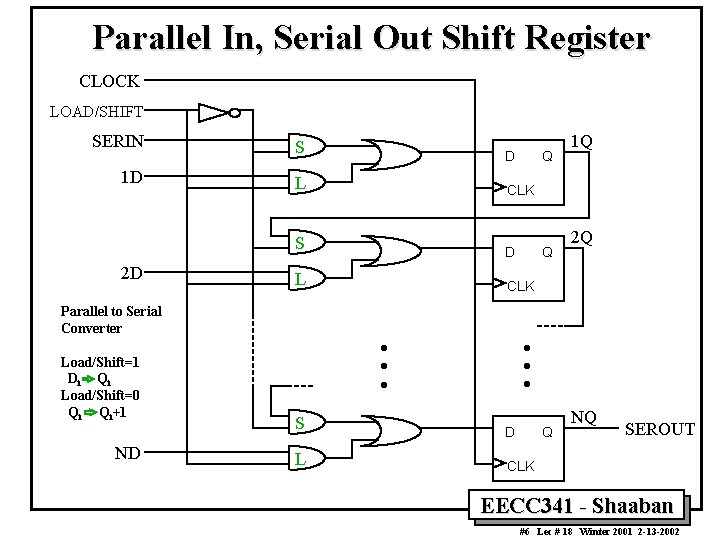

Parallel In, Serial Out Shift Register CLOCK LOAD/SHIFT SERIN S 1 D L D CLK S 2 D Load/Shift=1 Di Q i Load/Shift=0 Qi Qi+1 ND D L Parallel to Serial Converter L Q 2 Q CLK · · · S Q 1 Q · · · D Q NQ SEROUT CLK EECC 341 - Shaaban #6 Lec # 18 Winter 2001 2 -13 -2002

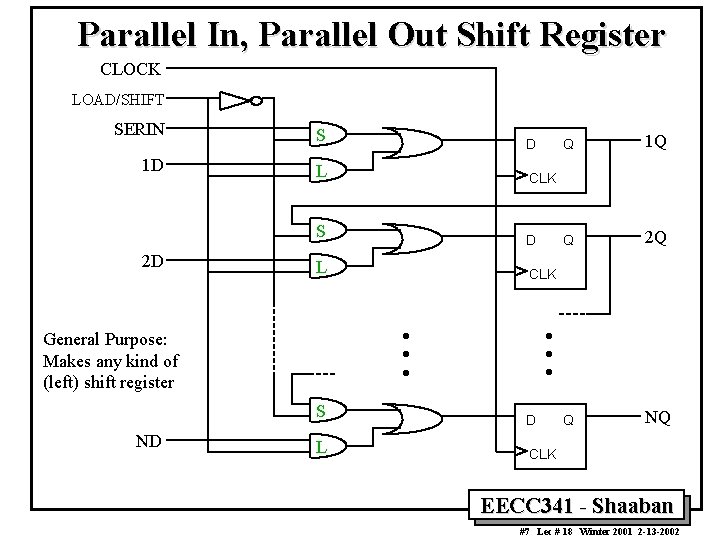

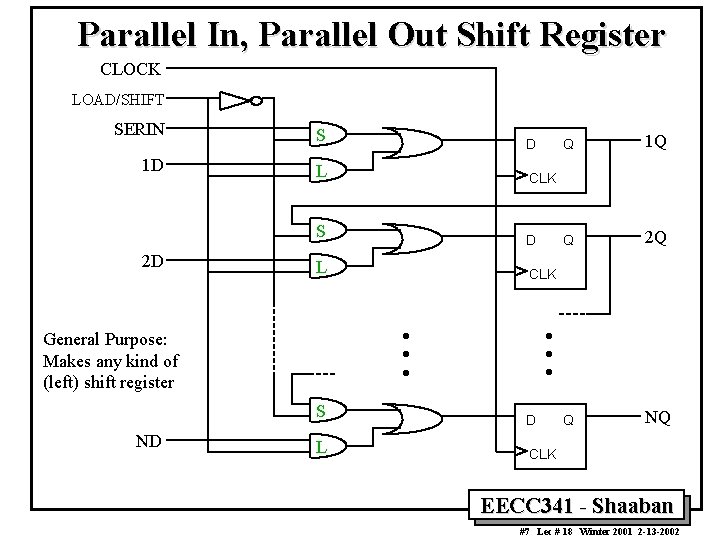

Parallel In, Parallel Out Shift Register CLOCK LOAD/SHIFT SERIN S 1 D L Q 2 Q Q NQ CLK · · · S ND D L General Purpose: Makes any kind of (left) shift register 1 Q CLK S 2 D Q · · · D CLK EECC 341 - Shaaban #7 Lec # 18 Winter 2001 2 -13 -2002

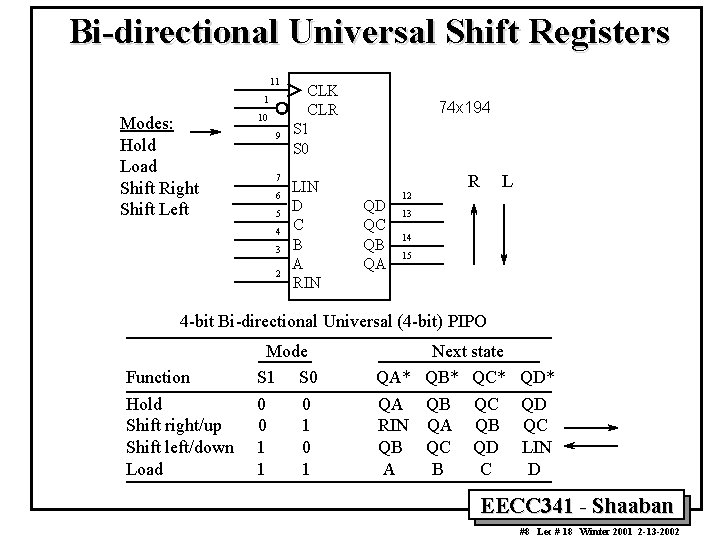

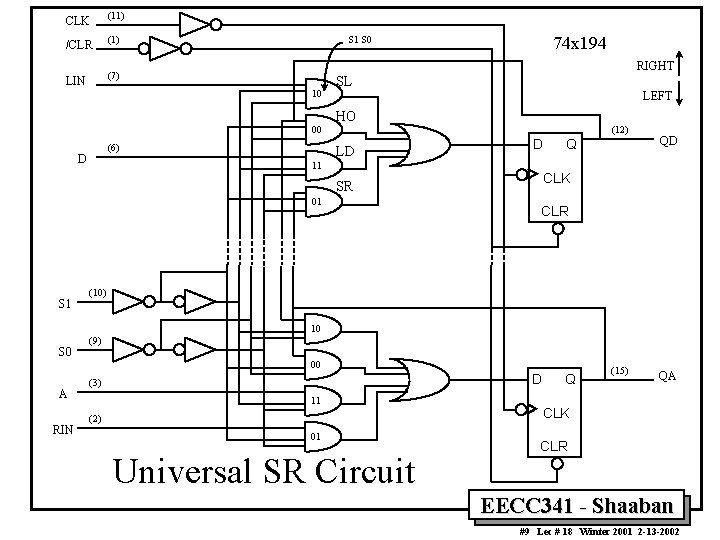

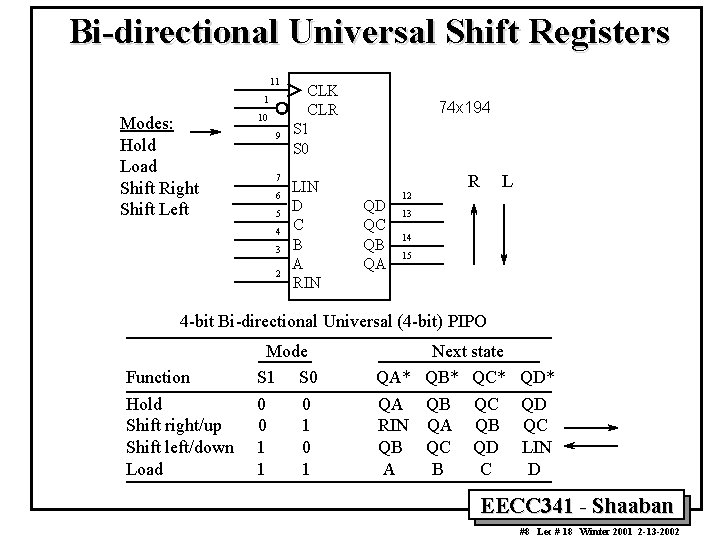

Bi-directional Universal Shift Registers 11 1 Modes: Hold Load Shift Right Shift Left 10 9 7 6 5 4 3 2 CLK CLR S 1 S 0 LIN D C B A RIN 74 x 194 QD QC QB QA 12 R L 13 14 15 4 -bit Bi-directional Universal (4 -bit) PIPO Function Hold Shift right/up Shift left/down Load Mode S 1 S 0 0 1 1 Next state QA* QB* QC* QA QB QC RIN QA QB QB QC QD A B C QD* QD QC LIN D EECC 341 - Shaaban #8 Lec # 18 Winter 2001 2 -13 -2002

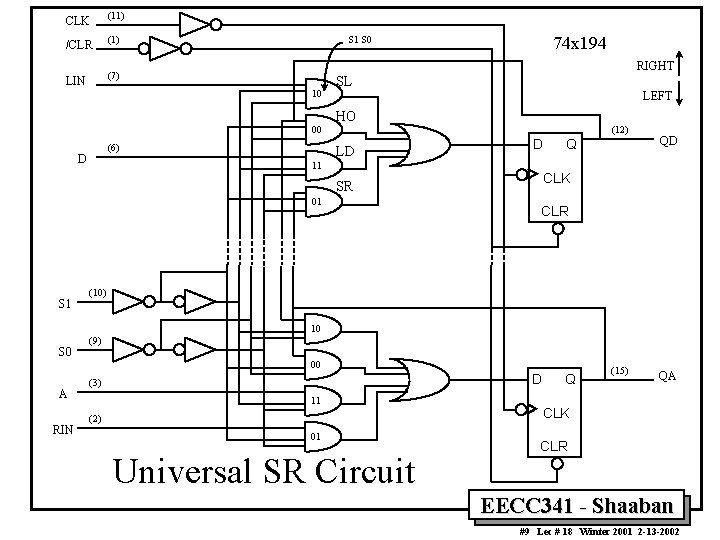

CLK (11) /CLR (1) LIN (7) 74 x 194 S 1 S 0 RIGHT 10 SL LEFT HO 00 (6) D (12) LD D 11 S 1 QD CLK SR 01 Q CLR (10) 10 S 0 (9) 00 A RIN D (3) 11 (2) 01 Universal SR Circuit Q (15) QA CLK CLR EECC 341 - Shaaban #9 Lec # 18 Winter 2001 2 -13 -2002

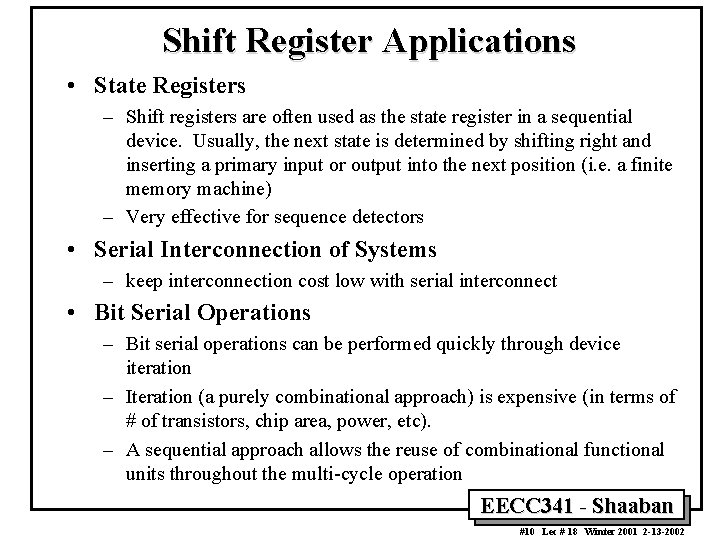

Shift Register Applications • State Registers – Shift registers are often used as the state register in a sequential device. Usually, the next state is determined by shifting right and inserting a primary input or output into the next position (i. e. a finite memory machine) – Very effective for sequence detectors • Serial Interconnection of Systems – keep interconnection cost low with serial interconnect • Bit Serial Operations – Bit serial operations can be performed quickly through device iteration – Iteration (a purely combinational approach) is expensive (in terms of # of transistors, chip area, power, etc). – A sequential approach allows the reuse of combinational functional units throughout the multi-cycle operation EECC 341 - Shaaban #10 Lec # 18 Winter 2001 2 -13 -2002

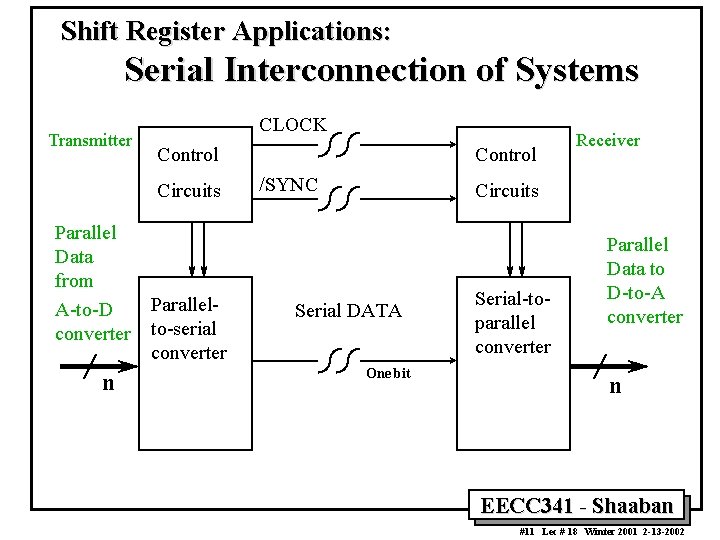

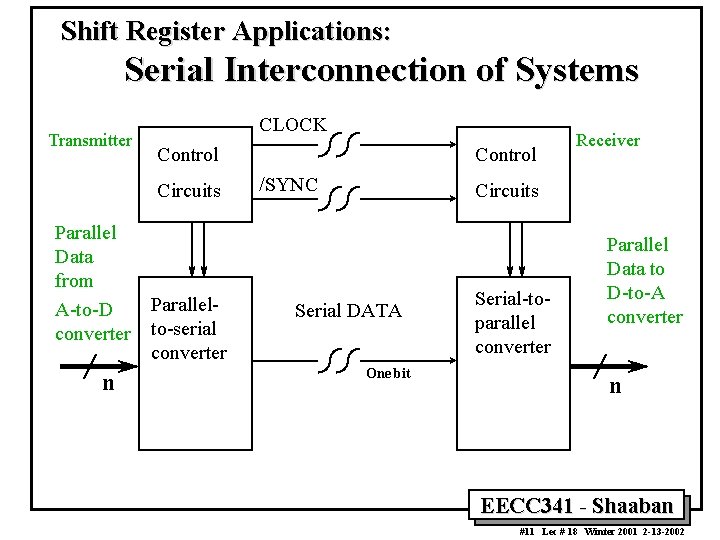

Shift Register Applications: Serial Interconnection of Systems Transmitter CLOCK Control Circuits Parallel Data from A-to-D converter n Parallelto-serial converter Control /SYNC Receiver Circuits Serial DATA One bit Serial-toparallel converter Parallel Data to D-to-A converter n EECC 341 - Shaaban #11 Lec # 18 Winter 2001 2 -13 -2002

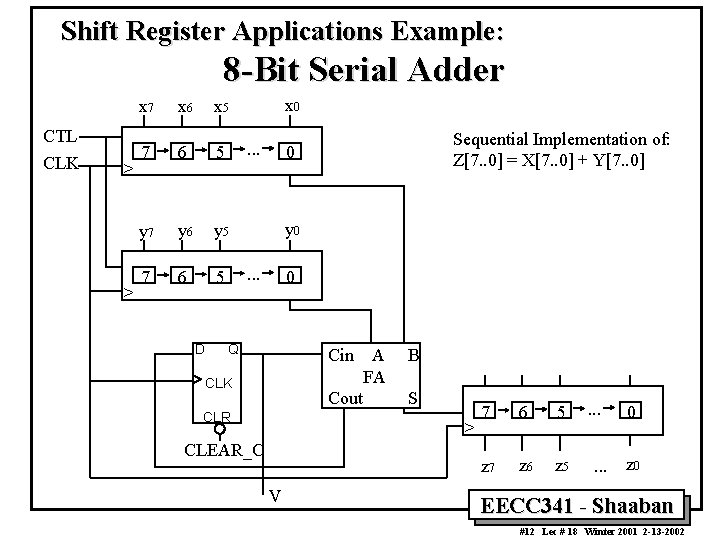

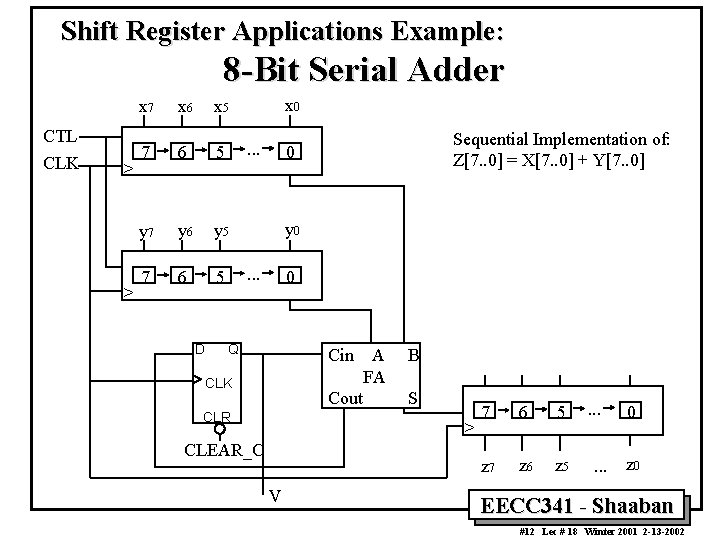

Shift Register Applications Example: 8 -Bit Serial Adder CTL CLK > > x 7 x 6 x 5 7 6 5 y 7 y 6 y 5 7 6 5 D x 0. . . Sequential Implementation of: Z[7. . 0] = X[7. . 0] + Y[7. . 0] 0 y 0. . . 0 Q Cin A FA Cout CLK CLR B S > CLEAR_C V 7 6 5 z 7 z 6 z 5 . . . 0 z 0 EECC 341 - Shaaban #12 Lec # 18 Winter 2001 2 -13 -2002

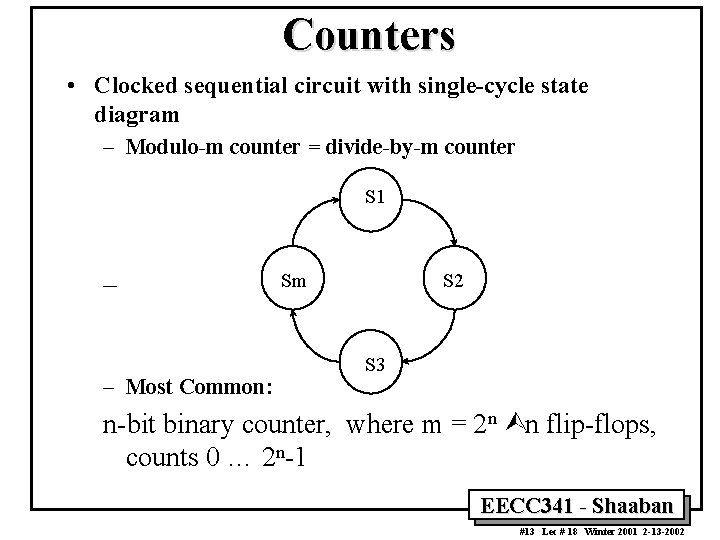

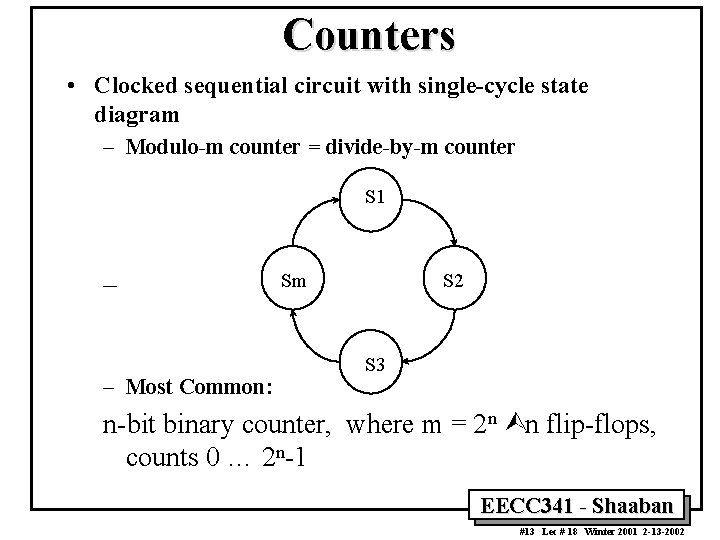

Counters • Clocked sequential circuit with single-cycle state diagram – Modulo-m counter = divide-by-m counter S 1 – – Most Common: Sm S 2 S 3 n-bit binary counter, where m = 2 n Ùn flip-flops, counts 0 … 2 n-1 EECC 341 - Shaaban #13 Lec # 18 Winter 2001 2 -13 -2002

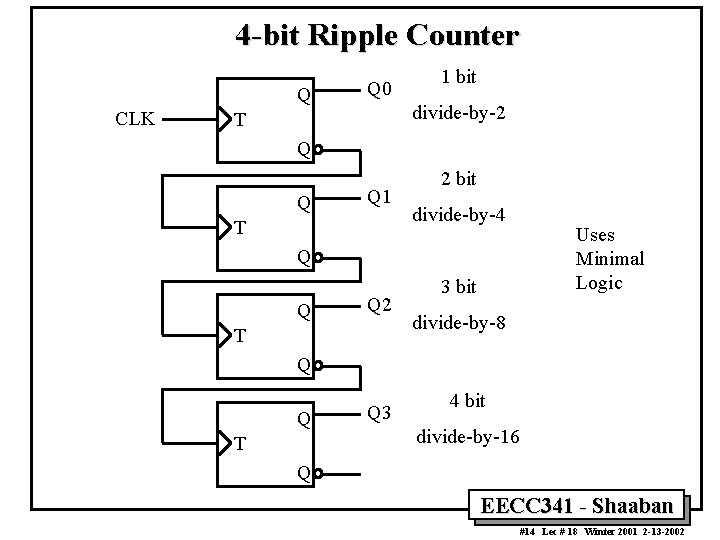

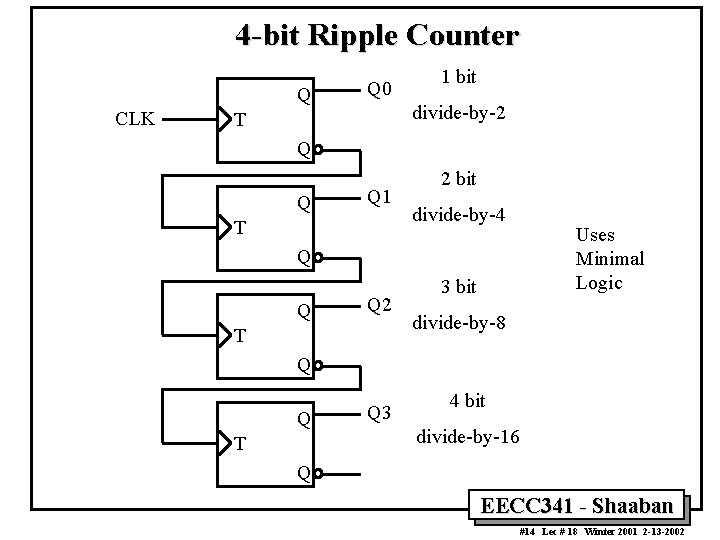

4 -bit Ripple Counter Q CLK Q 0 1 bit divide-by-2 T Q Q Q 1 T 2 bit divide-by-4 Q Q Q 2 T 3 bit Uses Minimal Logic divide-by-8 Q Q T Q 3 4 bit divide-by-16 Q EECC 341 - Shaaban #14 Lec # 18 Winter 2001 2 -13 -2002

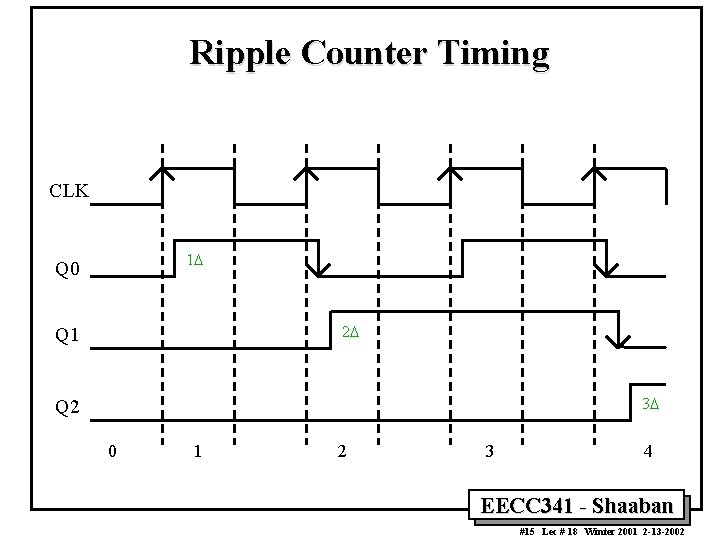

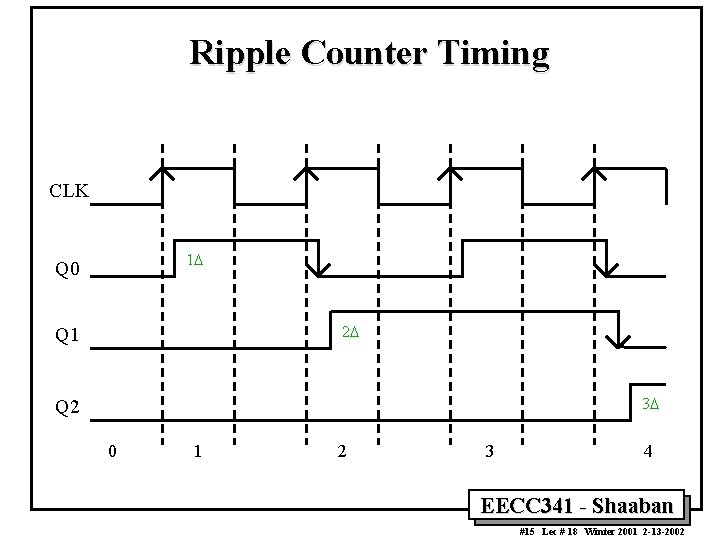

Ripple Counter Timing CLK 1 D Q 0 2 D Q 1 3 D Q 2 0 1 2 3 4 EECC 341 - Shaaban #15 Lec # 18 Winter 2001 2 -13 -2002

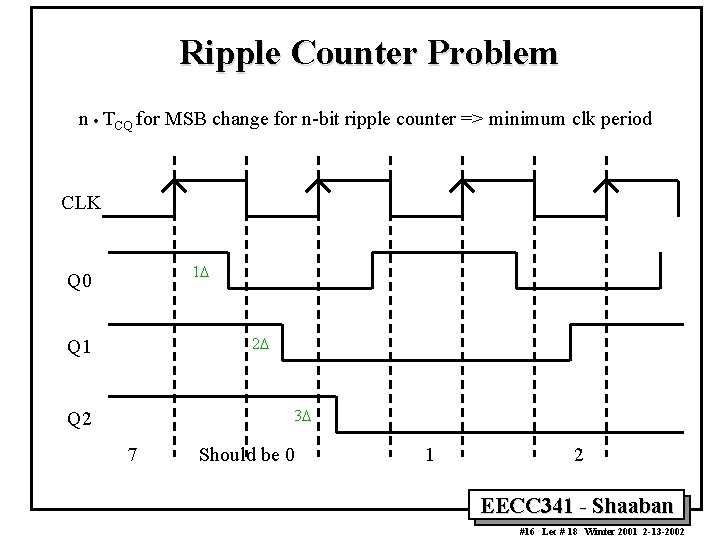

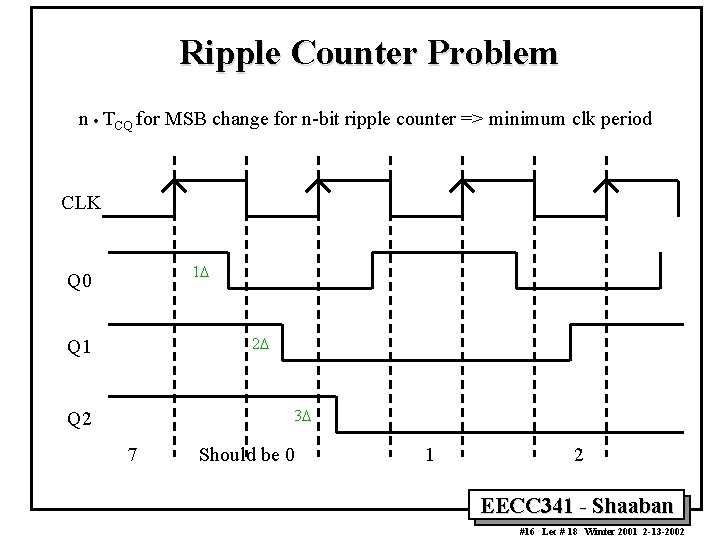

Ripple Counter Problem n · TCQ for MSB change for n-bit ripple counter => minimum clk period CLK 1 D Q 0 2 D Q 1 3 D Q 2 7 Should be 0 1 2 EECC 341 - Shaaban #16 Lec # 18 Winter 2001 2 -13 -2002

Synchronous Counters • All clock inputs connected to common CLK signal – All flip-flop outputs change simultaneously t. CQ after CLK – Faster than ripple counters – More complex logic – Most frequently used type of counter EECC 341 - Shaaban #17 Lec # 18 Winter 2001 2 -13 -2002

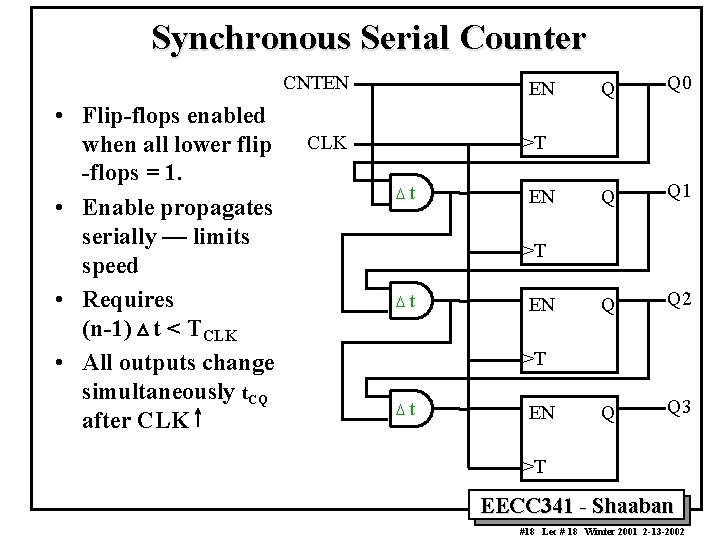

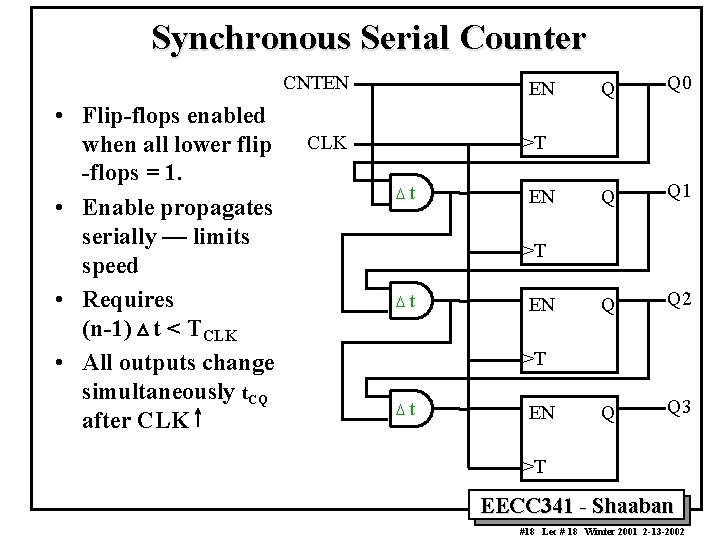

Synchronous Serial Counter CNTEN • Flip-flops enabled when all lower flip -flops = 1. • Enable propagates serially — limits speed • Requires (n-1) D t < TCLK • All outputs change simultaneously t. CQ after CLK EN CLK Q Q 0 Q Q 1 Q Q 2 Q Q 3 >T Dt EN >T EECC 341 - Shaaban #18 Lec # 18 Winter 2001 2 -13 -2002

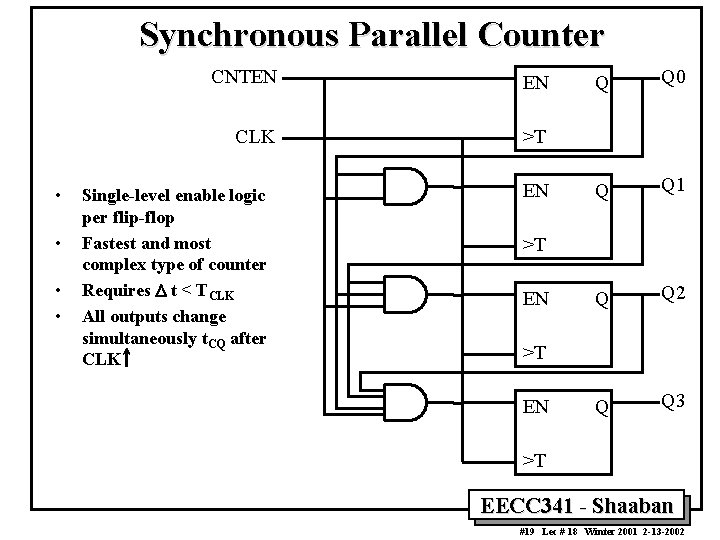

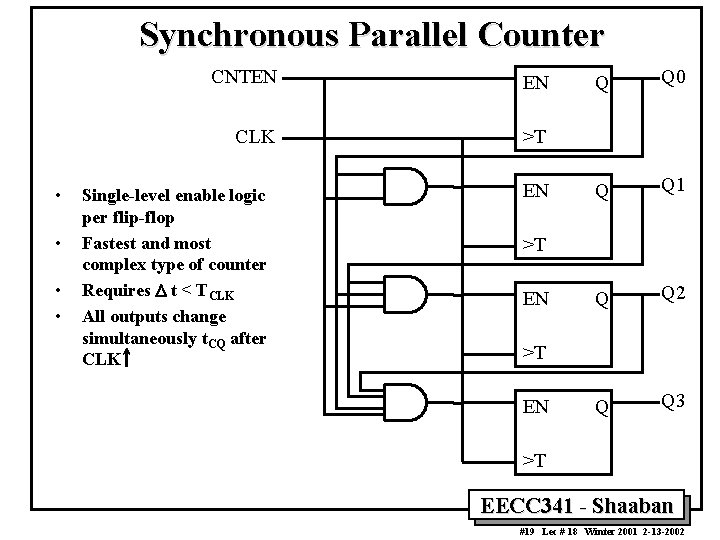

Synchronous Parallel Counter • • CNTEN EN CLK >T Single-level enable logic per flip-flop Fastest and most complex type of counter Requires D t < TCLK All outputs change simultaneously t. CQ after CLK EN Q Q 0 Q Q 1 Q Q 2 Q Q 3 >T EN >T EECC 341 - Shaaban #19 Lec # 18 Winter 2001 2 -13 -2002

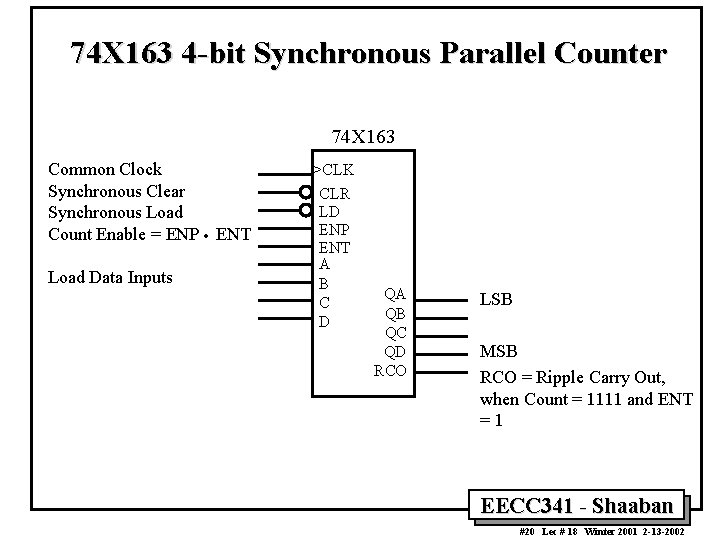

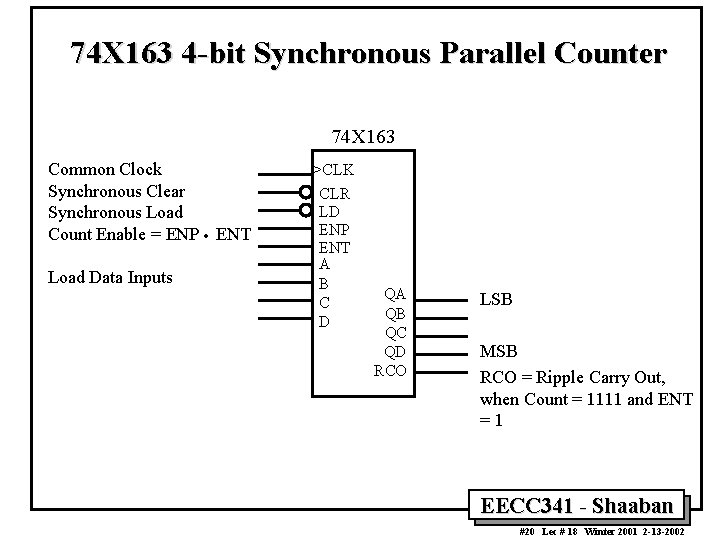

74 X 163 4 -bit Synchronous Parallel Counter 74 X 163 Common Clock Synchronous Clear Synchronous Load Count Enable = ENP · ENT Load Data Inputs >CLK CLR LD ENP ENT A B C D QA QB QC QD RCO LSB MSB RCO = Ripple Carry Out, when Count = 1111 and ENT =1 EECC 341 - Shaaban #20 Lec # 18 Winter 2001 2 -13 -2002

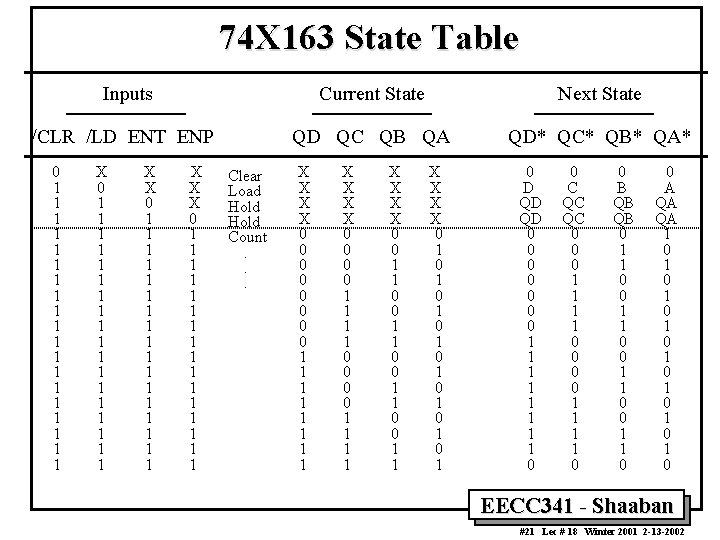

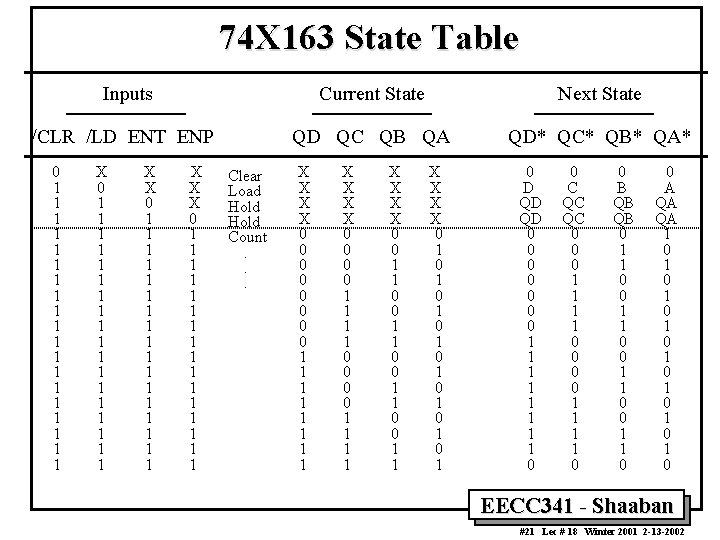

74 X 163 State Table Inputs Current State Next State /CLR /LD ENT ENP QD QC QB QA QD* QC* QB* QA* 0 1 1 1 1 1 X 0 1 1 1 1 1 1 1 1 1 X X X 0 1 1 1 1 Clear Load Hold Count. . . X X 0 0 0 0 1 1 1 1 X X 0 0 1 1 X X 0 1 0 1 0 D QD QD 0 0 0 0 1 1 1 1 0 0 C QC QC 0 0 0 1 1 1 1 0 0 B QB QB 0 1 1 0 0 A QA QA 1 0 1 0 EECC 341 - Shaaban #21 Lec # 18 Winter 2001 2 -13 -2002

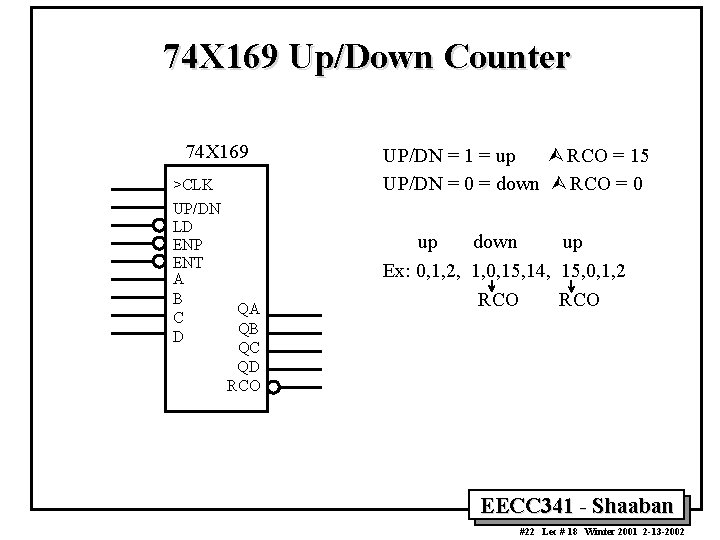

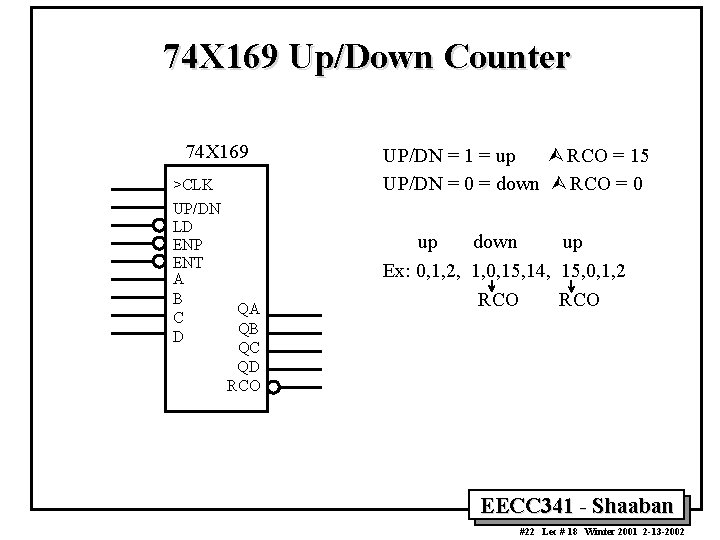

74 X 169 Up/Down Counter 74 X 169 >CLK UP/DN LD ENP ENT A B C D QA QB QC QD RCO UP/DN = 1 = up Ù RCO = 15 UP/DN = 0 = down Ù RCO = 0 up down up Ex: 0, 1, 2, 1, 0, 15, 14, 15, 0, 1, 2 RCO EECC 341 - Shaaban #22 Lec # 18 Winter 2001 2 -13 -2002

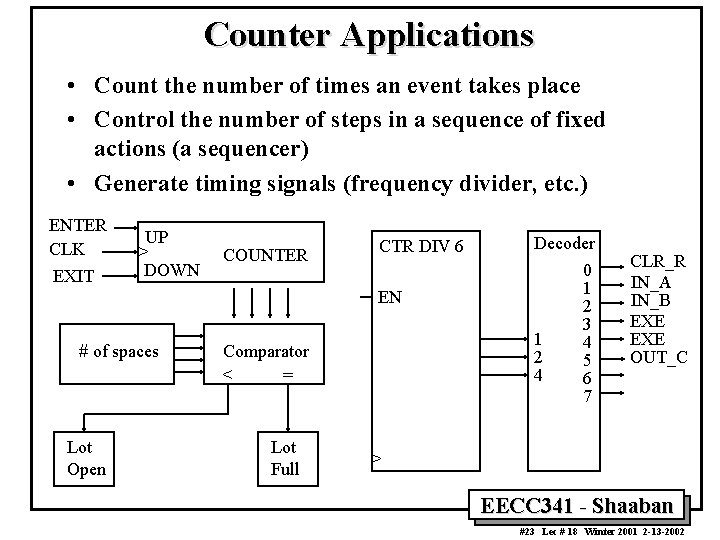

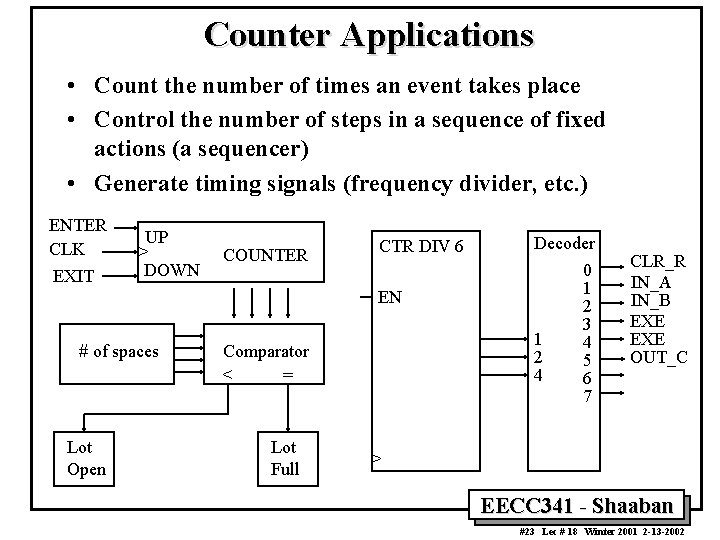

Counter Applications • Count the number of times an event takes place • Control the number of steps in a sequence of fixed actions (a sequencer) • Generate timing signals (frequency divider, etc. ) ENTER CLK EXIT UP > DOWN COUNTER CTR DIV 6 Decoder EN # of spaces Lot Open 1 2 4 Comparator < = Lot Full 0 1 2 3 4 5 6 7 CLR_R IN_A IN_B EXE OUT_C > EECC 341 - Shaaban #23 Lec # 18 Winter 2001 2 -13 -2002