Registers Counters Mantksal Tasarm BBM 231 M nder

Registers & Counters Mantıksal Tasarım – BBM 231 M. Önder Efe onderefe@cs. hacettepe. edu. tr 1

Registers • Registers are clocked sequential circuits • A register is a group of flip-flops – Each flip-flop capable of storing one bit of information – An n-bit register • consists of n flip-flops • capable of storing n bits of information – besides flip-flops, a register usually contains combinational logic to perform some simple tasks – In summary • flip-flops to hold information • combinational logic to control the state transition 2

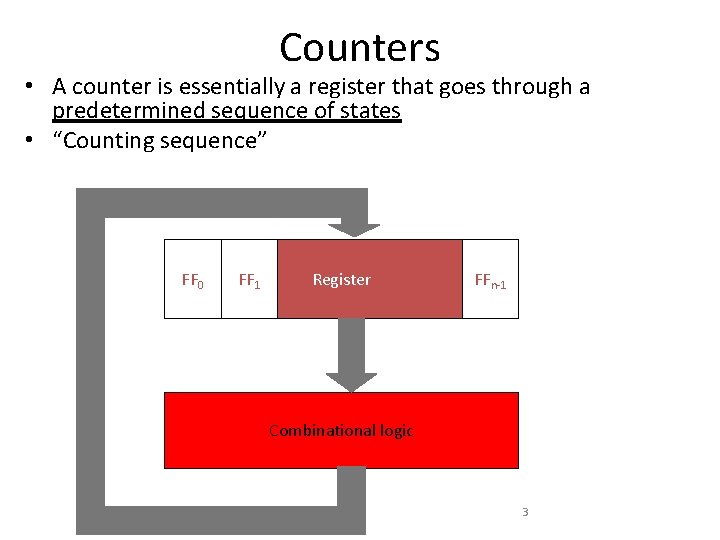

Counters • A counter is essentially a register that goes through a predetermined sequence of states • “Counting sequence” FF 0 FF 1 Register FFn-1 Combinational logic 3

Uses of Registers and Counters • Registers are useful for storing and manipulating information – internal registers in microprocessors to manipulate data • Counters are extensively used in control logic – PC (program counter) in microprocessors 4

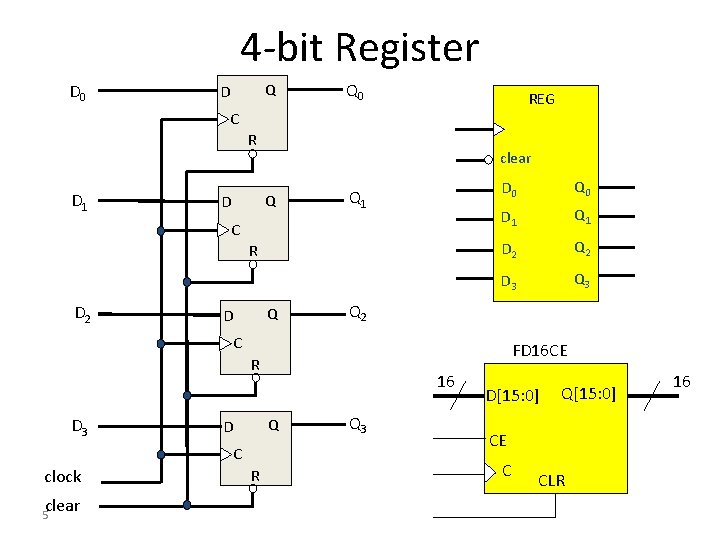

4 -bit Register D 0 Q D Q 0 REG C R D 1 clear Q D Q 1 C R D 2 Q D D 0 Q 0 D 1 Q 1 D 2 Q 2 D 3 Q 2 C FD 16 CE R D 3 Q D C clock clear 5 16 R Q 3 D[15: 0] Q[15: 0] CE C CLR 16

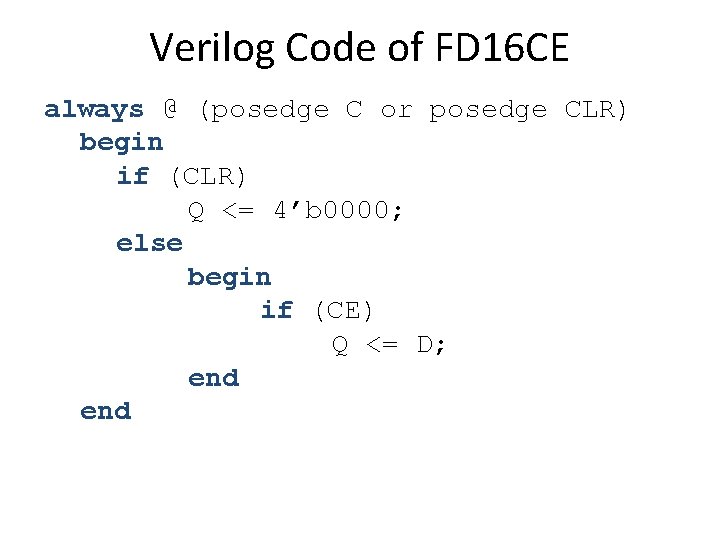

Verilog Code of FD 16 CE always @ (posedge C or posedge CLR) begin if (CLR) Q <= 4’b 0000; else begin if (CE) Q <= D; end

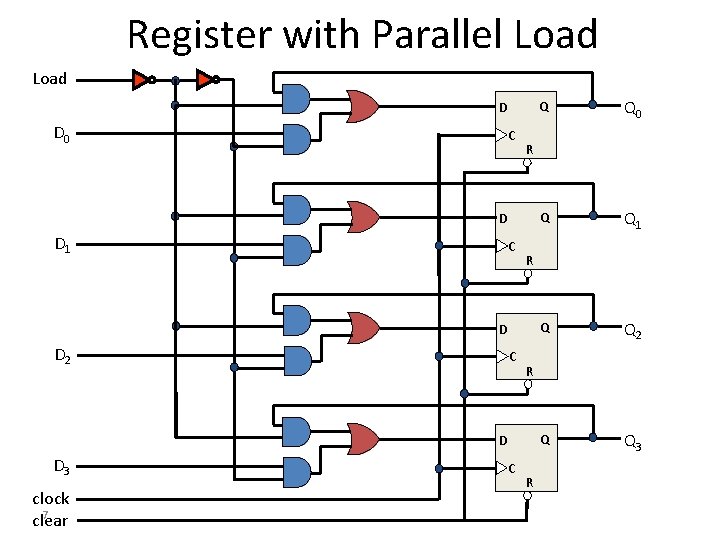

Register with Parallel Load D D 0 C C C clock 7 clear C Q 1 Q Q 2 Q Q 3 R D D 3 Q R D D 2 Q 0 R D D 1 Q R

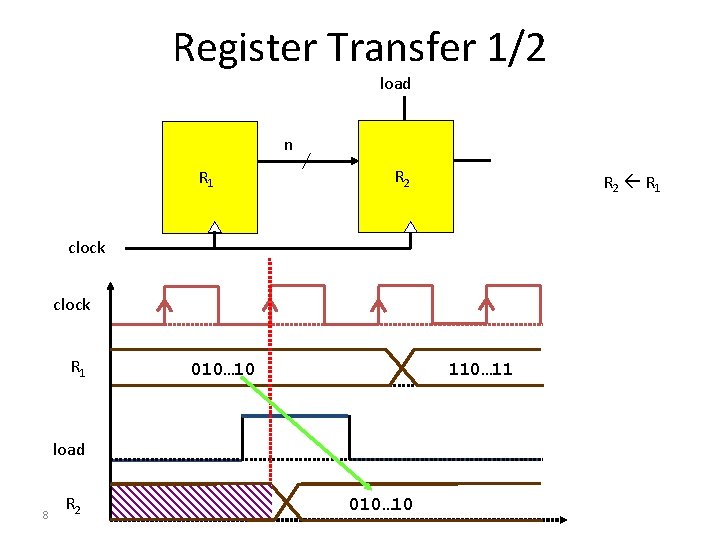

Register Transfer 1/2 load n R 1 R 2 R 1 clock R 1 010… 10 110… 11 load 8 R 2 010… 10

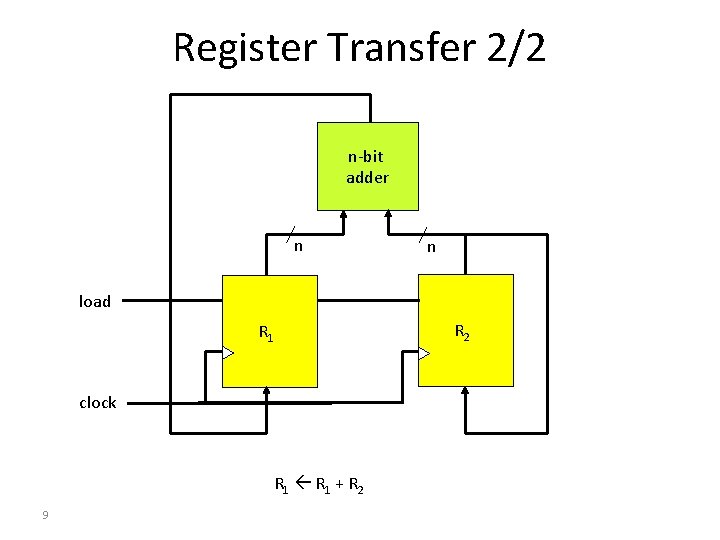

Register Transfer 2/2 n-bit adder n n load R 1 clock R 1 + R 2 9 R 2

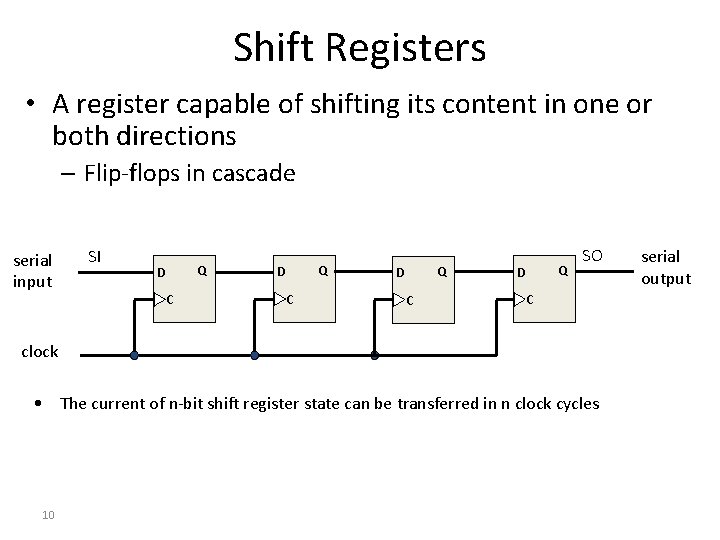

Shift Registers • A register capable of shifting its content in one or both directions – Flip-flops in cascade serial input SI Q D C Q D SO C clock • The current of n-bit shift register state can be transferred in n clock cycles 10 serial output

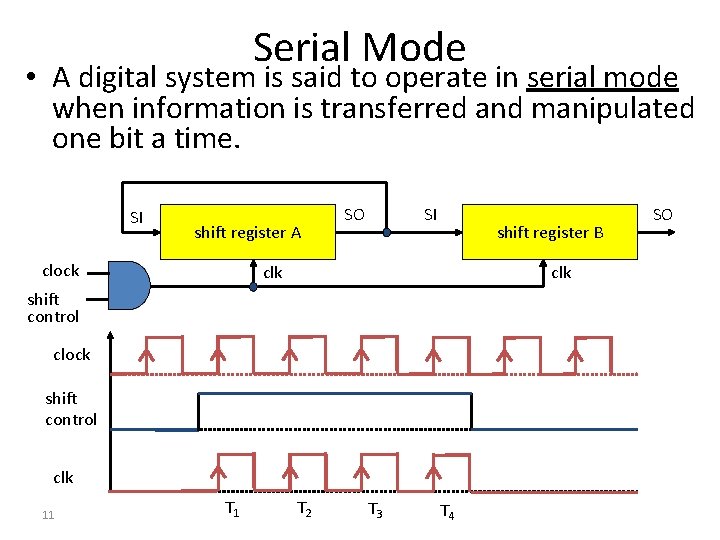

Serial Mode • A digital system is said to operate in serial mode when information is transferred and manipulated one bit a time. SI shift register A clock SO SI shift register B clk shift control clock shift control clk 11 T 2 T 3 T 4 SO

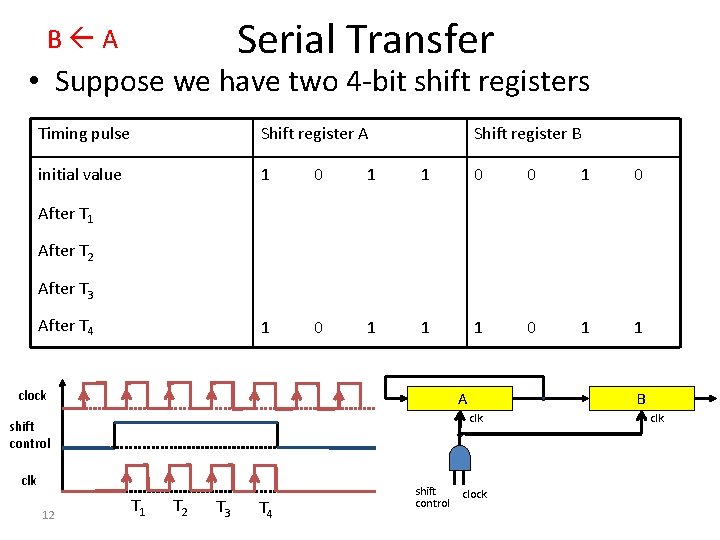

Serial Transfer B A • Suppose we have two 4 -bit shift registers Timing pulse Shift register A Shift register B initial value 1 0 1 1 0 0 1 0 1 1 After T 2 After T 3 After T 4 clock clk shift control clk 12 B A T 1 T 2 T 3 T 4 shift control clock clk

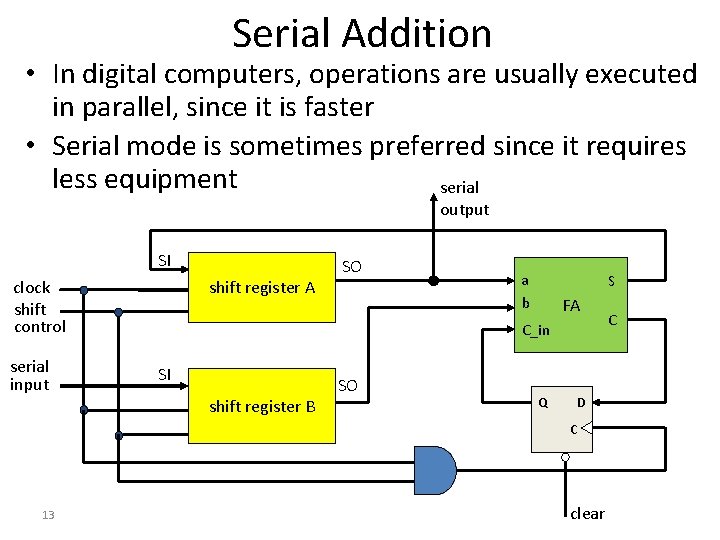

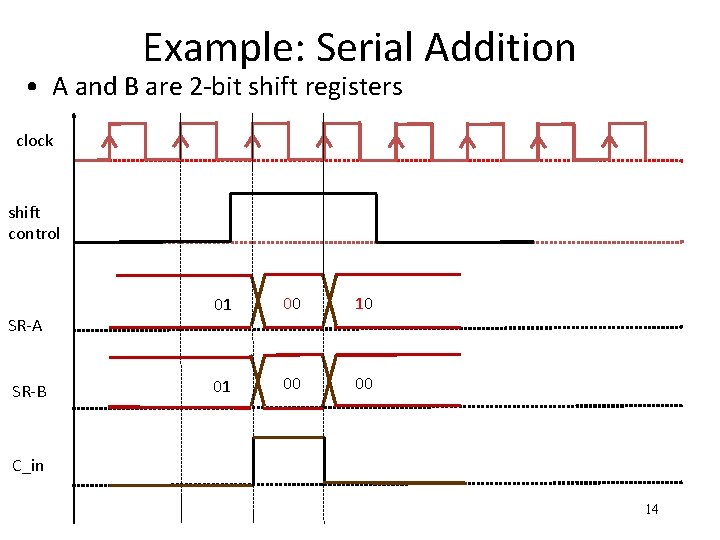

Serial Addition • In digital computers, operations are usually executed in parallel, since it is faster • Serial mode is sometimes preferred since it requires less equipment serial output SI clock shift control serial input shift register A SO a b S FA C_in SI shift register B SO Q D C 13 clear C

Example: Serial Addition • A and B are 2 -bit shift registers clock shift control SR-A SR-B 01 00 10 01 00 00 C_in 14

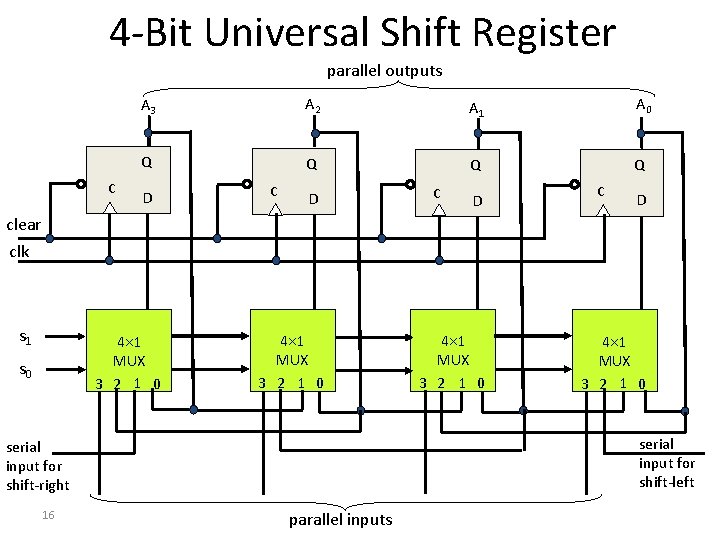

Universal Shift Register • Capabilities: 1. 2. 3. 4. 5. 6. 15 A “clear” control to set the register to 0. A “clock” input A “shift-right” control A “shift-left” control n input lines & a “parallel-load” control n parallel output lines

4 -Bit Universal Shift Register parallel outputs C A 3 A 2 A 1 A 0 Q Q D C D C D clear clk s 1 4 1 MUX 3 2 1 0 s 0 4 1 MUX 3 2 1 0 serial input for shift-left serial input for shift-right 16 4 1 MUX 3 2 1 0 parallel inputs

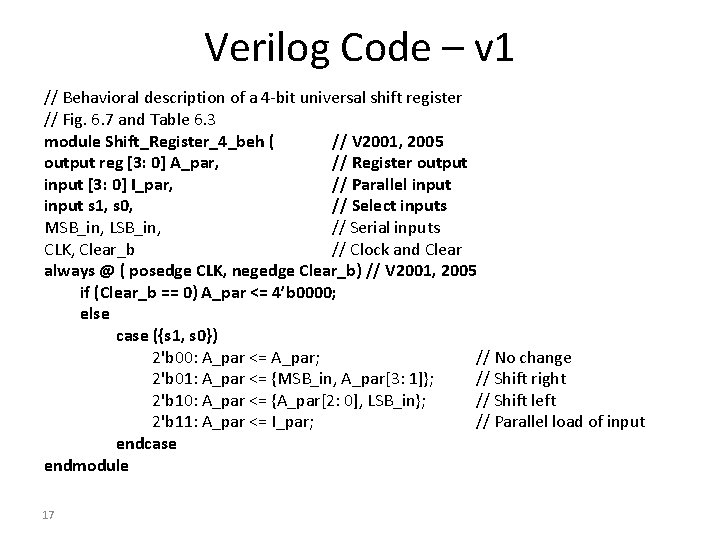

Verilog Code – v 1 // Behavioral description of a 4 -bit universal shift register // Fig. 6. 7 and Table 6. 3 module Shift_Register_4_beh ( // V 2001, 2005 output reg [3: 0] A_par, // Register output input [3: 0] I_par, // Parallel input s 1, s 0, // Select inputs MSB_in, LSB_in, // Serial inputs CLK, Clear_b // Clock and Clear always @ ( posedge CLK, negedge Clear_b) // V 2001, 2005 if (Clear_b == 0) A_par <= 4’b 0000; else case ({s 1, s 0}) 2'b 00: A_par <= A_par; // No change 2'b 01: A_par <= {MSB_in, A_par[3: 1]}; // Shift right 2'b 10: A_par <= {A_par[2: 0], LSB_in}; // Shift left 2'b 11: A_par <= I_par; // Parallel load of input endcase endmodule 17

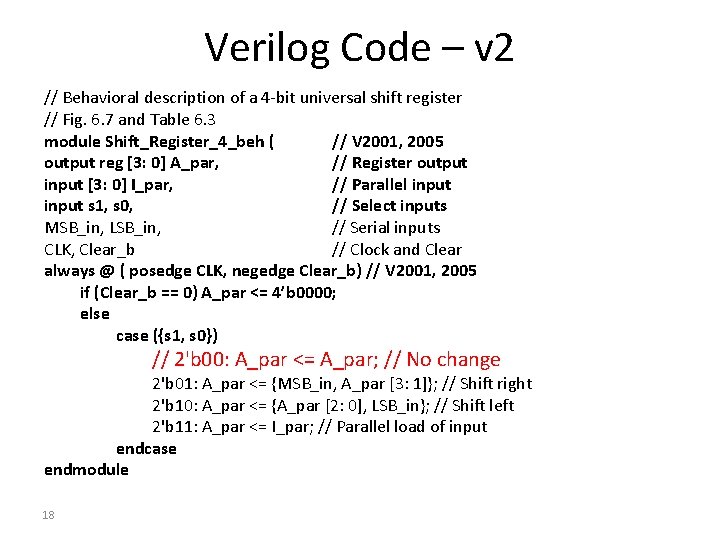

Verilog Code – v 2 // Behavioral description of a 4 -bit universal shift register // Fig. 6. 7 and Table 6. 3 module Shift_Register_4_beh ( // V 2001, 2005 output reg [3: 0] A_par, // Register output input [3: 0] I_par, // Parallel input s 1, s 0, // Select inputs MSB_in, LSB_in, // Serial inputs CLK, Clear_b // Clock and Clear always @ ( posedge CLK, negedge Clear_b) // V 2001, 2005 if (Clear_b == 0) A_par <= 4’b 0000; else case ({s 1, s 0}) // 2'b 00: A_par <= A_par; // No change 2'b 01: A_par <= {MSB_in, A_par [3: 1]}; // Shift right 2'b 10: A_par <= {A_par [2: 0], LSB_in}; // Shift left 2'b 11: A_par <= I_par; // Parallel load of input endcase endmodule 18

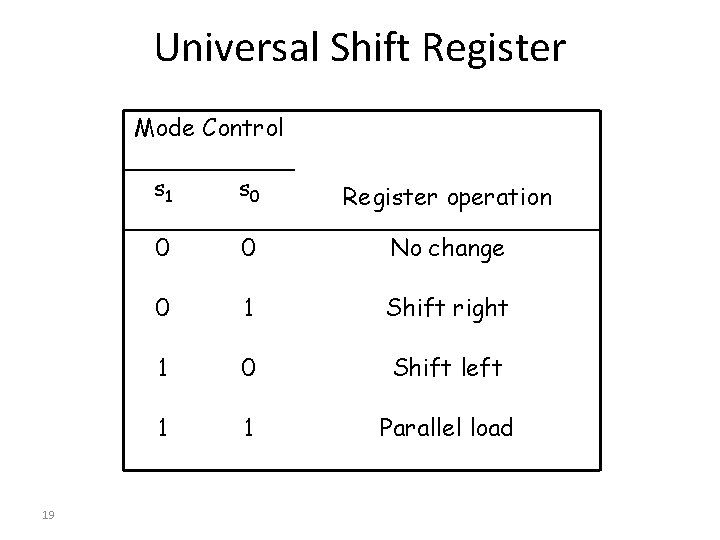

Universal Shift Register Mode Control 19 s 1 s 0 Register operation 0 0 No change 0 1 Shift right 1 0 Shift left 1 1 Parallel load

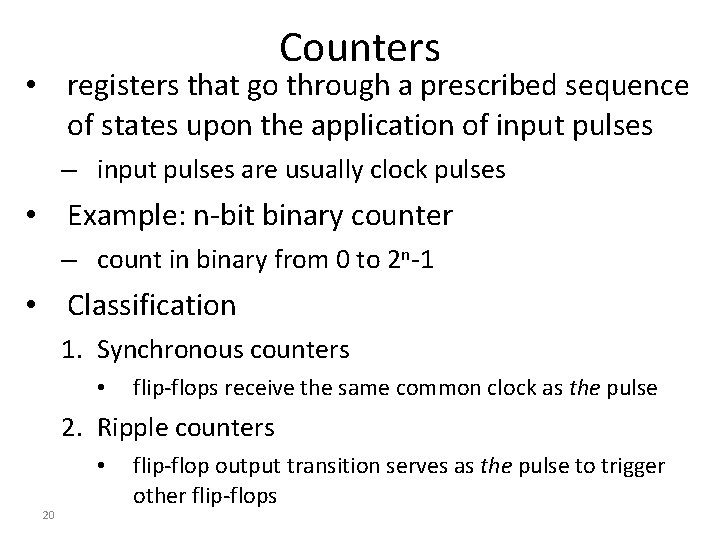

Counters • registers that go through a prescribed sequence of states upon the application of input pulses – input pulses are usually clock pulses • Example: n-bit binary counter – count in binary from 0 to 2 n-1 • Classification 1. Synchronous counters • flip-flops receive the same common clock as the pulse 2. Ripple counters • 20 flip-flop output transition serves as the pulse to trigger other flip-flops

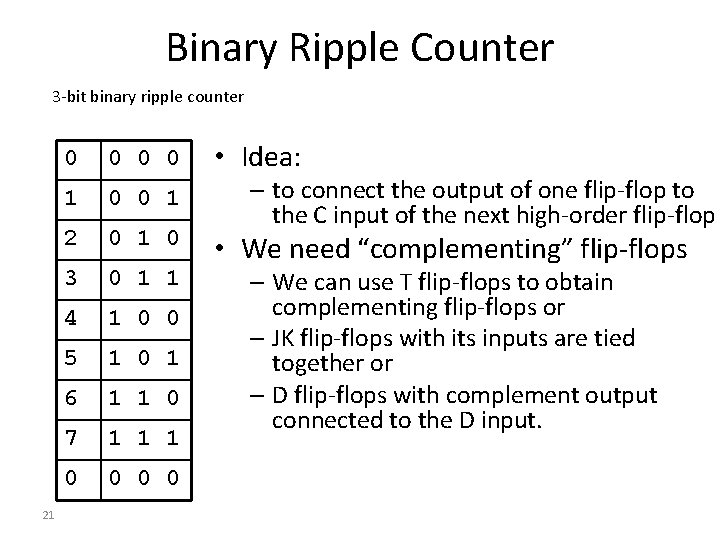

Binary Ripple Counter 3 -bit binary ripple counter 21 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 0 0 • Idea: – to connect the output of one flip-flop to the C input of the next high-order flip-flop • We need “complementing” flip-flops – We can use T flip-flops to obtain complementing flip-flops or – JK flip-flops with its inputs are tied together or – D flip-flops with complement output connected to the D input.

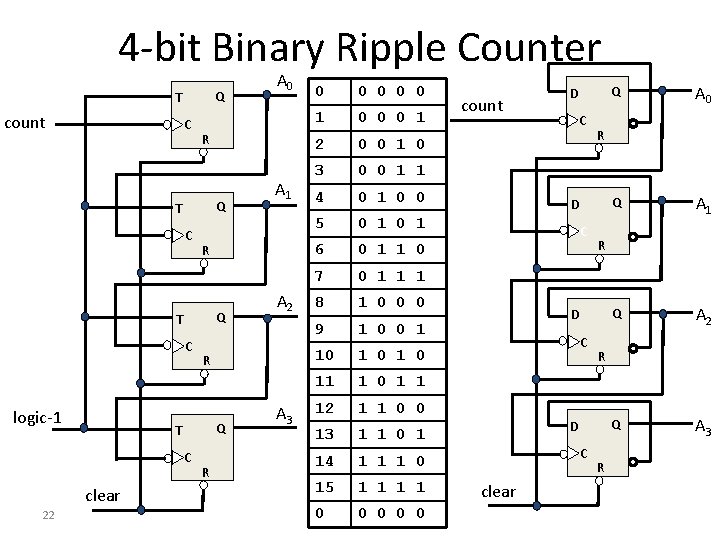

4 -bit Binary Ripple Counter Q T count C R Q T C logic-1 Q clear 22 A 2 R Q T C A 1 R T C A 0 R A 3 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 1 0 11 1 0 1 1 12 1 1 0 0 13 1 1 0 1 14 1 1 1 0 15 1 1 0 0 0 count D C clear A 1 Q A 2 Q A 3 R D C Q R D C A 0 R D C Q R

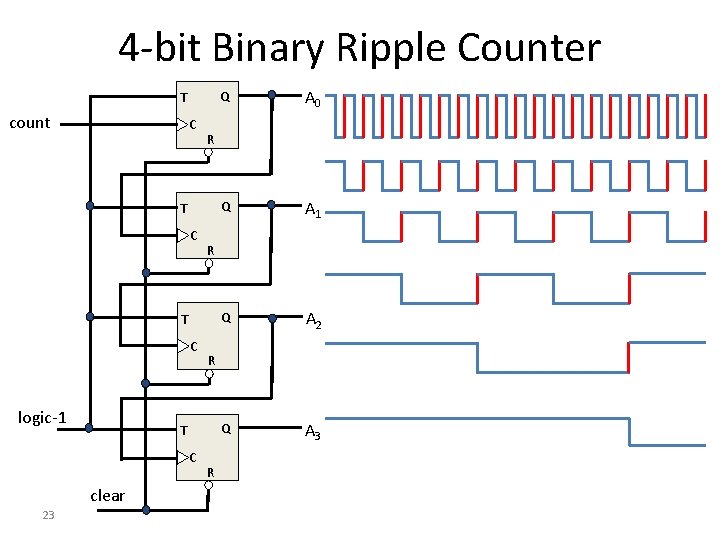

4 -bit Binary Ripple Counter T count C logic-1 clear 23 A 1 Q A 2 Q A 3 R T C Q R T C A 0 R T C Q R

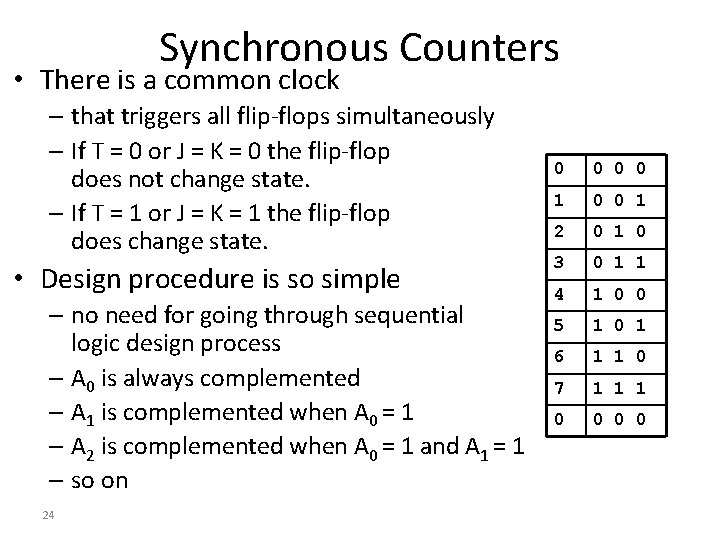

Synchronous Counters • There is a common clock – that triggers all flip-flops simultaneously – If T = 0 or J = K = 0 the flip-flop does not change state. – If T = 1 or J = K = 1 the flip-flop does change state. • Design procedure is so simple – no need for going through sequential logic design process – A 0 is always complemented – A 1 is complemented when A 0 = 1 – A 2 is complemented when A 0 = 1 and A 1 = 1 – so on 24 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 0 0

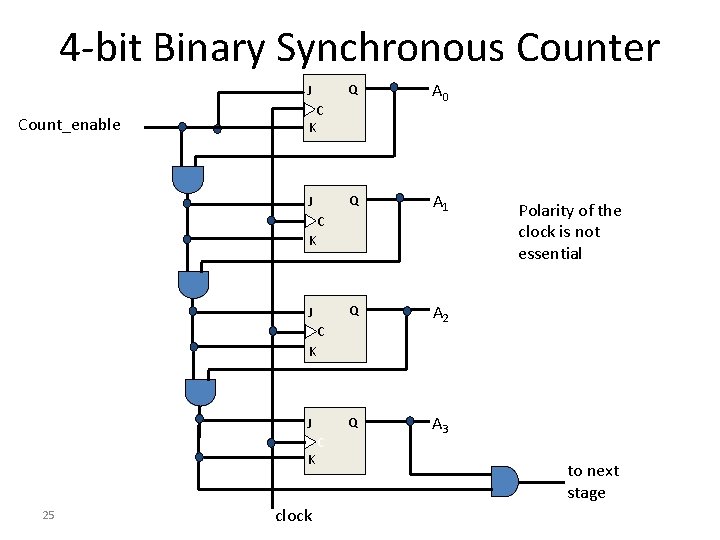

4 -bit Binary Synchronous Counter J Count_enable Q A 0 Q A 1 Q A 2 Q A 3 C K J C Polarity of the clock is not essential K J C K 25 clock to next stage

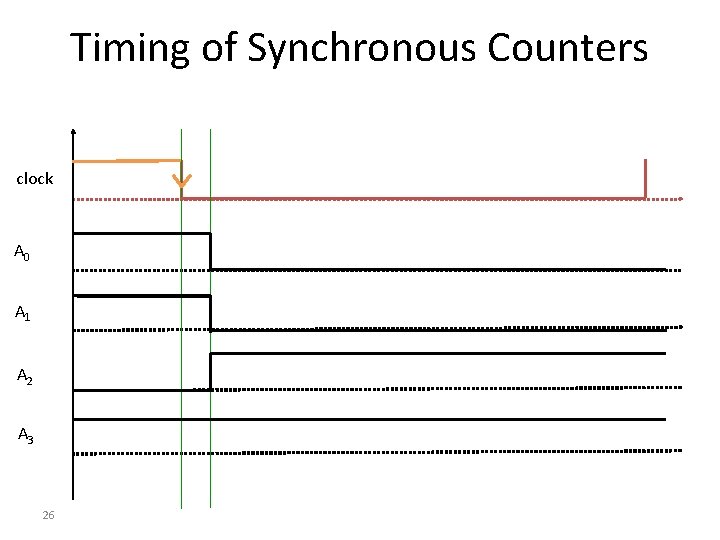

Timing of Synchronous Counters clock A 0 A 1 A 2 A 3 26

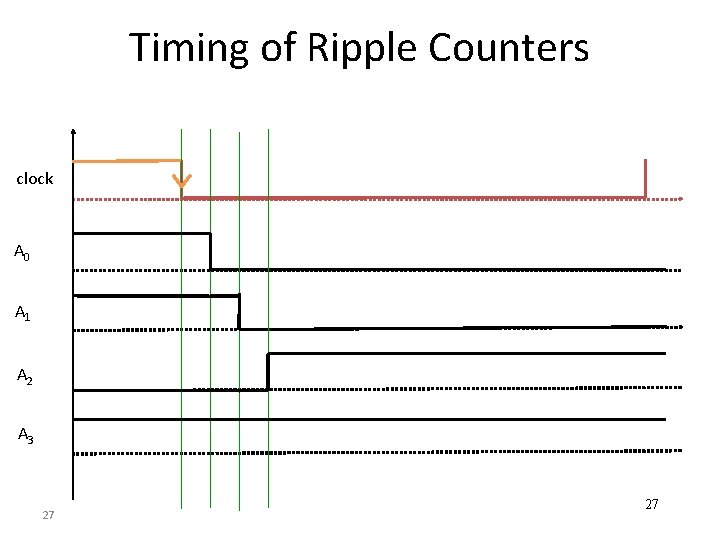

Timing of Ripple Counters clock A 0 A 1 A 2 A 3 27 27

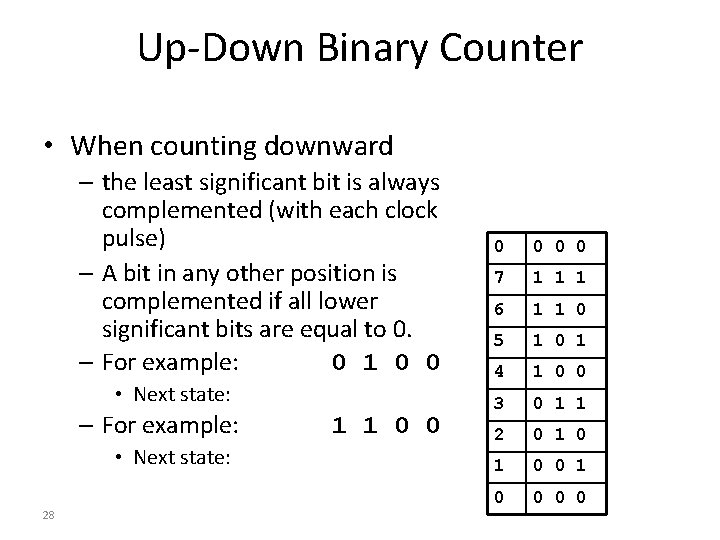

Up-Down Binary Counter • When counting downward – the least significant bit is always complemented (with each clock pulse) – A bit in any other position is complemented if all lower significant bits are equal to 0. – For example: 0 1 0 0 • Next state: – For example: • Next state: 28 1 1 0 0 0 7 1 1 1 6 1 1 0 5 1 0 1 4 1 0 0 3 0 1 1 2 0 1 0 0

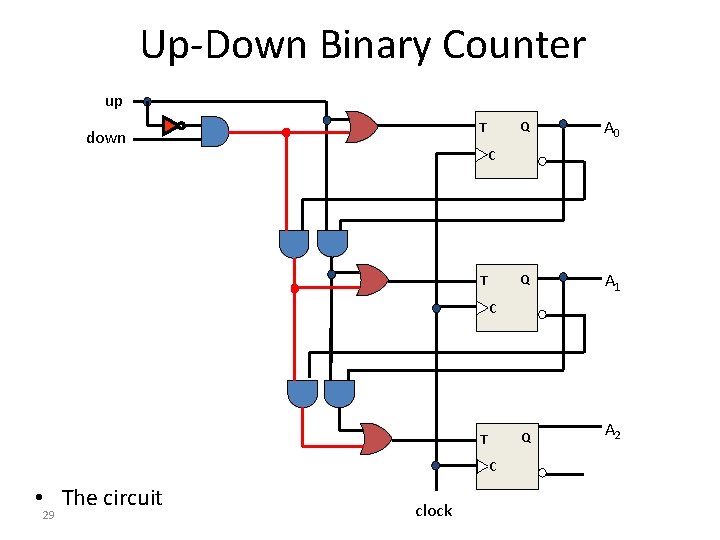

Up-Down Binary Counter up T down Q A 0 Q A 1 Q A 2 C T C • The circuit 29 clock C

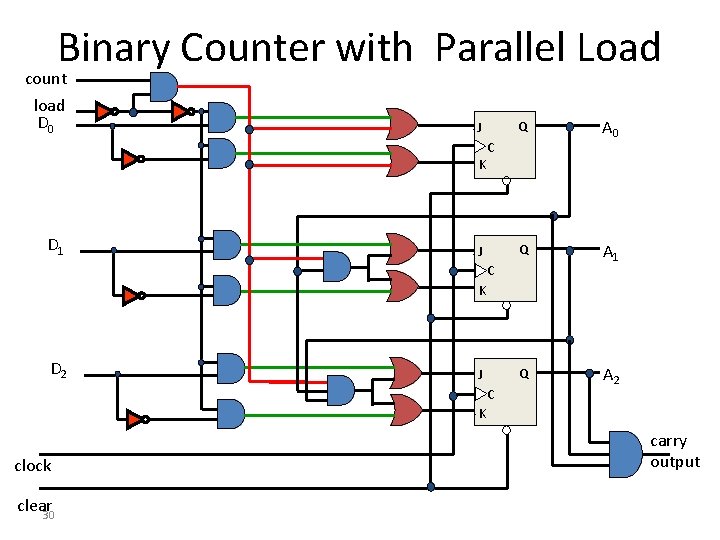

Binary Counter with Parallel Load count load D 0 J Q A 0 Q A 1 Q A 2 C K D 1 J C K D 2 J C K clock clear 30 carry output

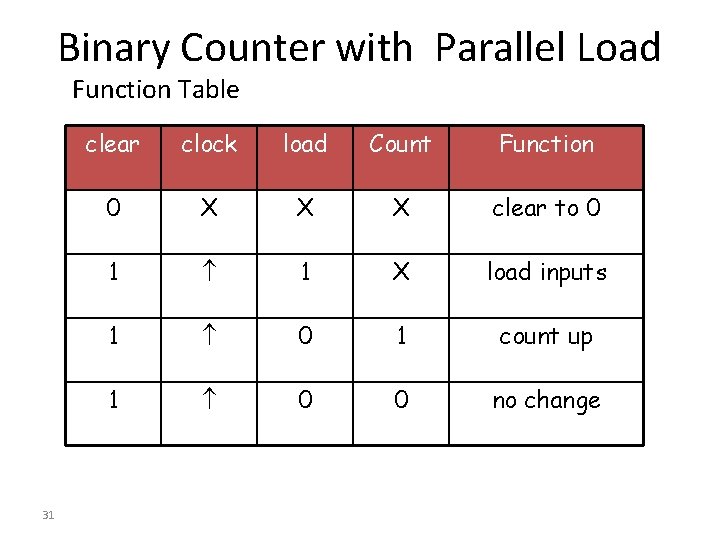

Binary Counter with Parallel Load Function Table 31 clear clock load Count Function 0 X X X clear to 0 1 1 X load inputs 1 0 1 count up 1 0 0 no change

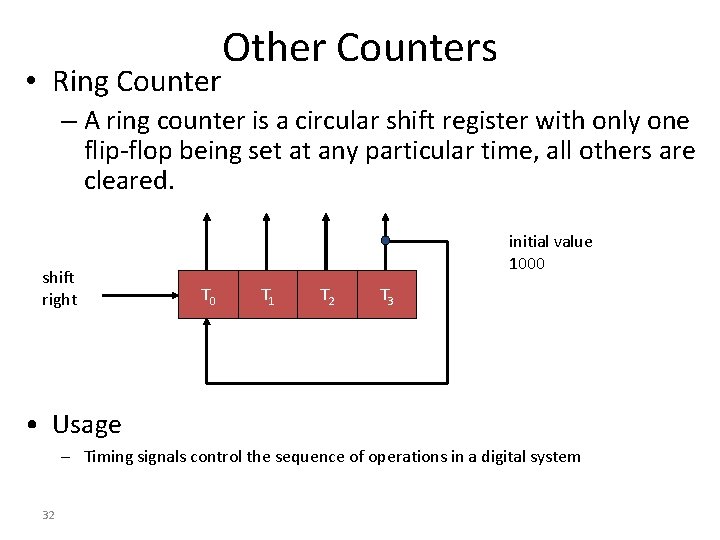

• Ring Counter Other Counters – A ring counter is a circular shift register with only one flip-flop being set at any particular time, all others are cleared. shift right initial value 1000 T 1 T 2 T 3 • Usage – Timing signals control the sequence of operations in a digital system 32

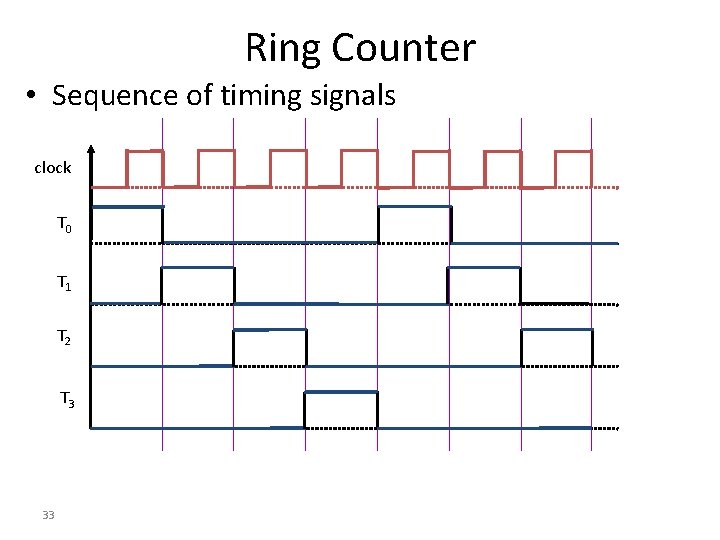

Ring Counter • Sequence of timing signals clock T 0 T 1 T 2 T 3 33

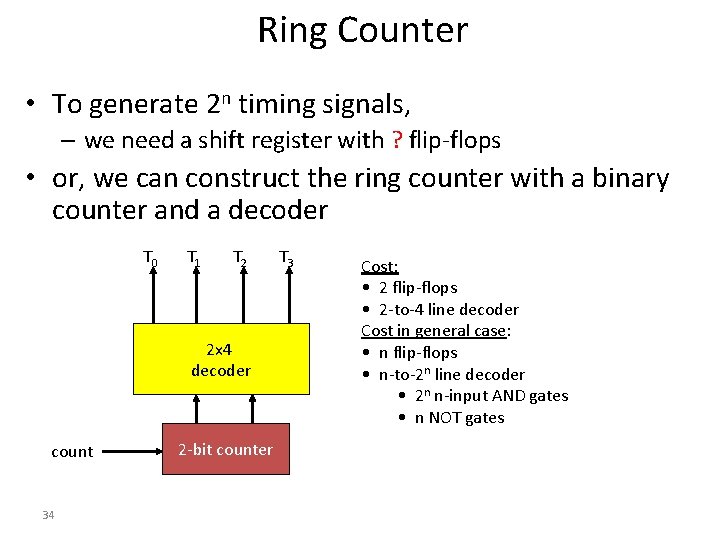

Ring Counter • To generate 2 n timing signals, – we need a shift register with ? flip-flops • or, we can construct the ring counter with a binary counter and a decoder T 0 T 1 T 2 2 x 4 decoder count 34 2 -bit counter T 3 Cost: • 2 flip-flops • 2 -to-4 line decoder Cost in general case: • n flip-flops • n-to-2 n line decoder • 2 n n-input AND gates • n NOT gates

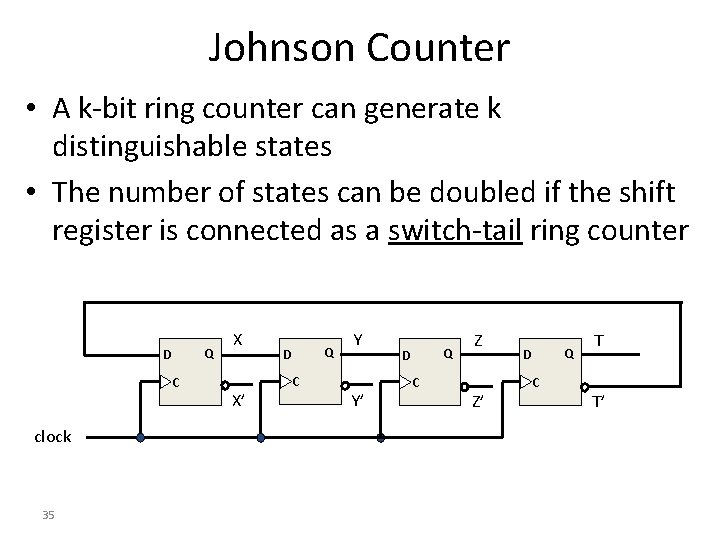

Johnson Counter • A k-bit ring counter can generate k distinguishable states • The number of states can be doubled if the shift register is connected as a switch-tail ring counter Q D C clock 35 X X’ Q D C Y Y’ Q D C Z Z’ Q D C T T’

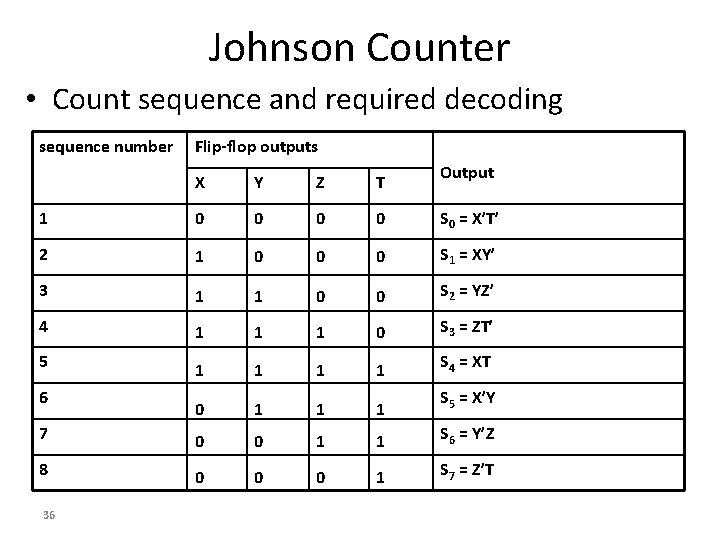

Johnson Counter • Count sequence and required decoding sequence number Flip-flop outputs Output X Y Z T 1 0 0 S 0 = X’T’ 2 1 0 0 0 S 1 = XY’ 3 1 1 0 0 S 2 = YZ’ 4 1 1 1 0 S 3 = ZT’ 1 1 S 4 = XT 0 1 1 1 7 0 0 1 1 S 6 = Y’Z 8 0 0 0 1 S 7 = Z’T 5 6 36 S 5 = X’Y

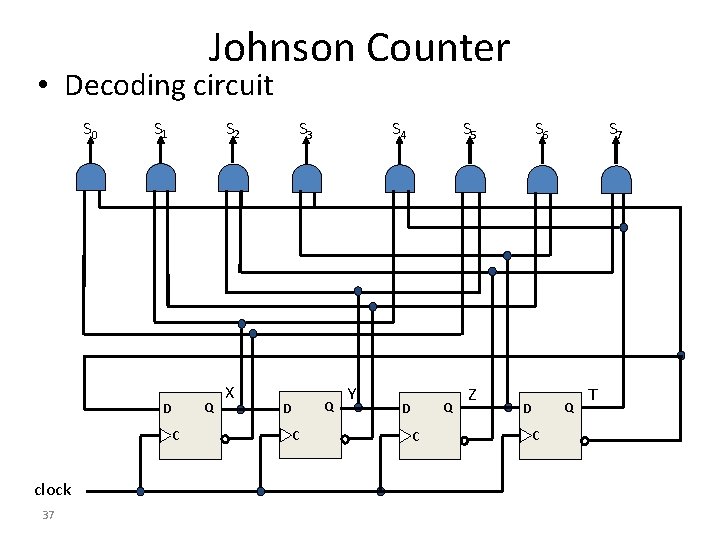

Johnson Counter • Decoding circuit S 0 S 1 S 2 Q D C clock 37 X S 3 S 4 Q D C Y S 5 Q D C Z S 6 S 7 Q D C T

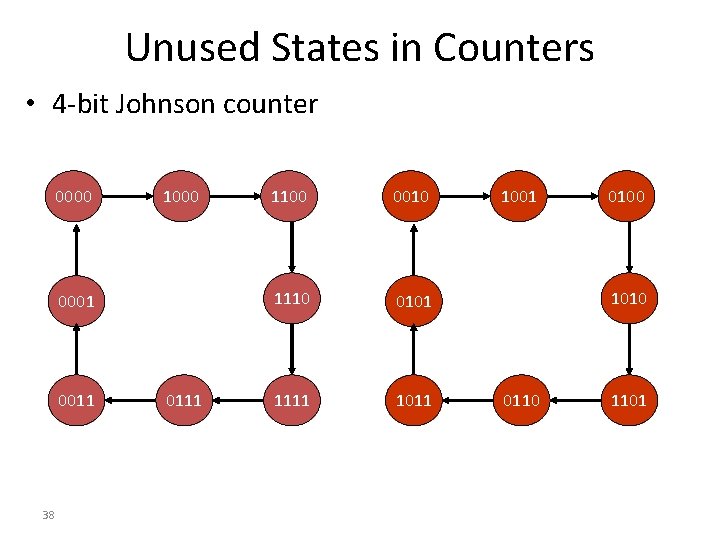

Unused States in Counters • 4 -bit Johnson counter 0000 1000 0001 0011 38 0111 1100 0010 1110 0101 1111 1001 0100 1010 0110 1101

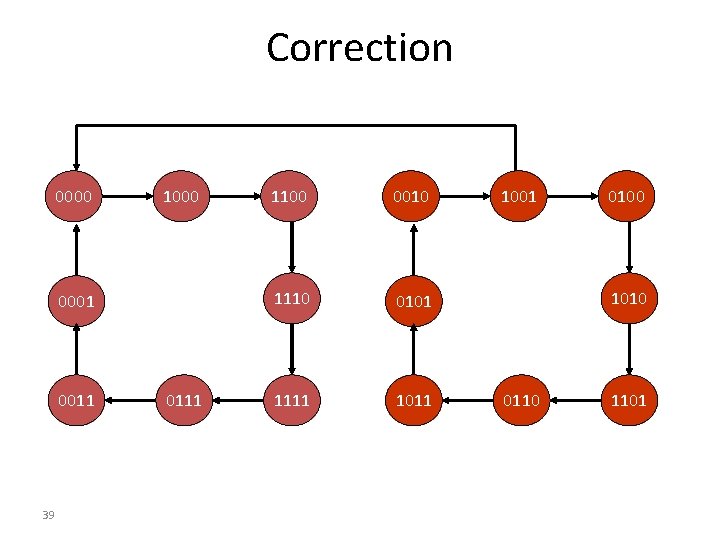

Correction 0000 1000 0001 0011 39 0111 1100 0010 1110 0101 1111 1001 0100 1010 0110 1101

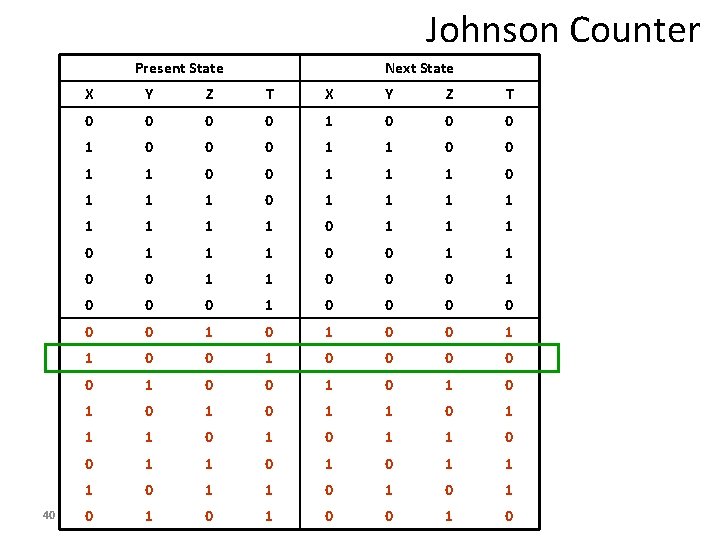

Johnson Counter Present State 40 Next State X Y Z T 0 0 1 0 0 0 1 1 1 0 1 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 0 0 0 0 1 0 1 0 1 1 1 0 0 1 1 1 0 1 0 1 0

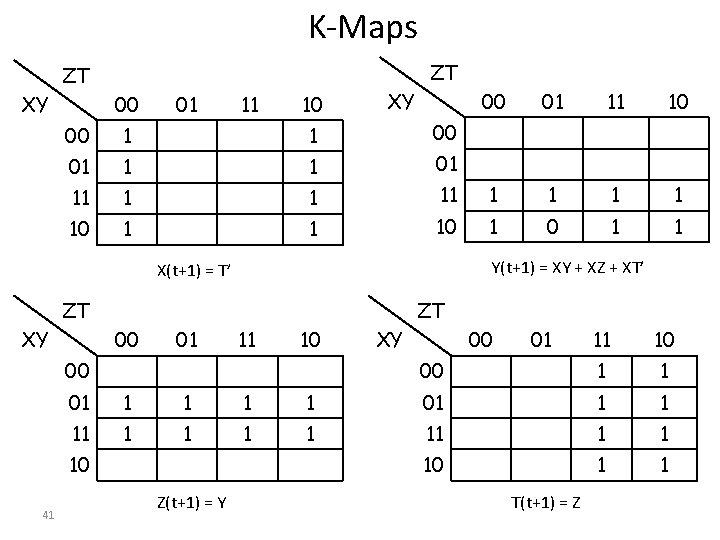

K-Maps ZT ZT XY 00 01 11 10 XY 01 11 10 00 1 1 00 01 1 1 01 11 1 10 1 0 1 1 Y(t+1) = XY + XZ + XT’ X(t+1) = T’ ZT XY ZT 00 01 11 10 00 XY 00 01 11 10 00 1 1 01 1 1 11 1 1 10 41 00 Z(t+1) = Y T(t+1) = Z

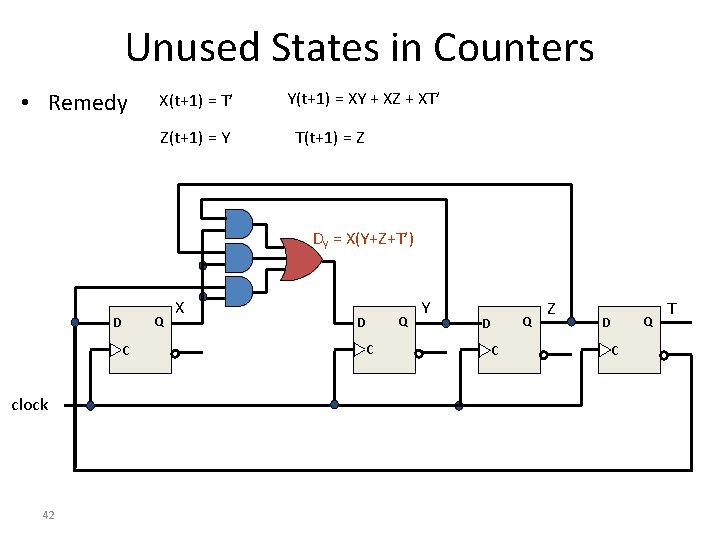

Unused States in Counters • Remedy X(t+1) = T’ Z(t+1) = Y Y(t+1) = XY + XZ + XT’ T(t+1) = Z DY = X(Y+Z+T’) Q D C clock 42 X Q D C Y Q D C Z Q D C T

- Slides: 42