Blackfin Timers Independent timers build into the Blackfin

Blackfin Timers Independent timers build into the Blackfin Watchdog Timer can be used to prevent the TTCOS system from locking up with one Task hogging all the CPU time

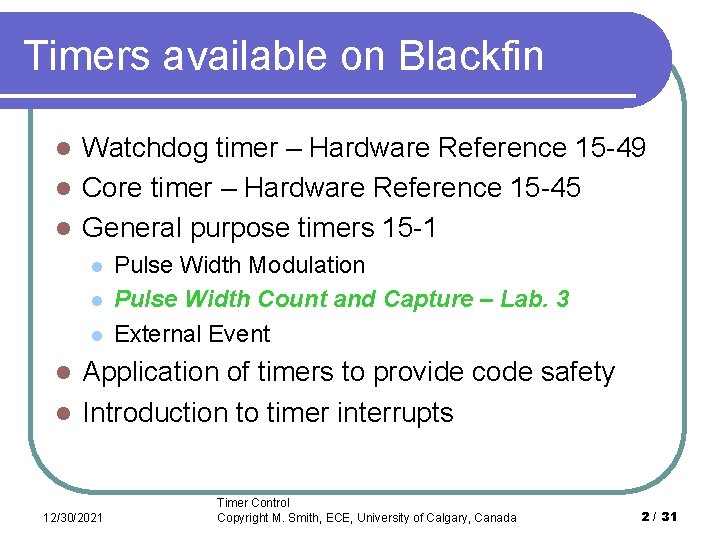

Timers available on Blackfin Watchdog timer – Hardware Reference 15 -49 l Core timer – Hardware Reference 15 -45 l General purpose timers 15 -1 l l Pulse Width Modulation Pulse Width Count and Capture – Lab. 3 External Event Application of timers to provide code safety l Introduction to timer interrupts l 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 2 / 31

Basic concept – watchdog timer Your code is on an embedded system that is running in the field l Something goes unexpectedly wrong with your program, and one piece of code (a subroutine) keeps running, and running l l l Other parts of the system self-destruct as there are no control signals send to them Fix this issue with a “Watch. Dog Timer” l 12/30/2021 The use of software and haradware watch dog timers are the subject on one TTCOS article Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 3 / 31

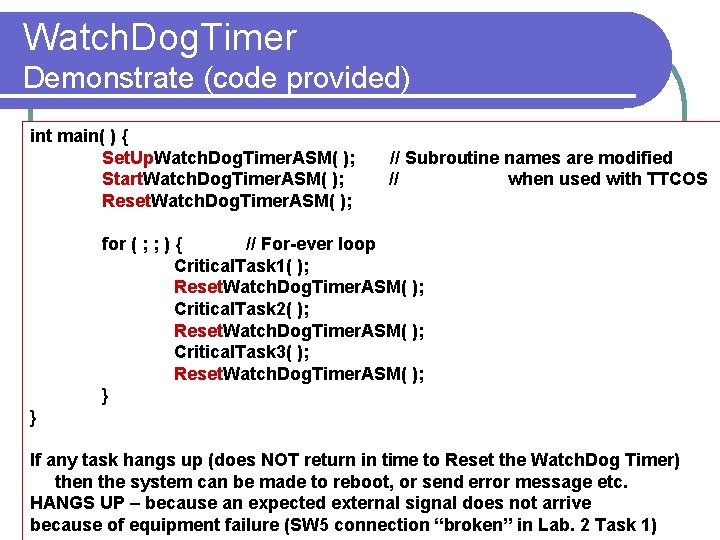

Watch. Dog. Timer Demonstrate (code provided) int main( ) { Set. Up. Watch. Dog. Timer. ASM( ); Start. Watch. Dog. Timer. ASM( ); Reset. Watch. Dog. Timer. ASM( ); // Subroutine names are modified // when used with TTCOS for ( ; ; ) { // For-ever loop Critical. Task 1( ); Reset. Watch. Dog. Timer. ASM( ); Critical. Task 2( ); Reset. Watch. Dog. Timer. ASM( ); Critical. Task 3( ); Reset. Watch. Dog. Timer. ASM( ); } } If any task hangs up (does NOT return in time to Reset the Watch. Dog Timer) then the system can be made to reboot, or send error message etc. Control HANGS UP – because. Timer an expected external signal does not arrive 4 / 31 12/30/2021 Copyright M. Smith, ECE, University of Calgary, Canada because of equipment failure (SW 5 connection “broken” in Lab. 2 Task 1)

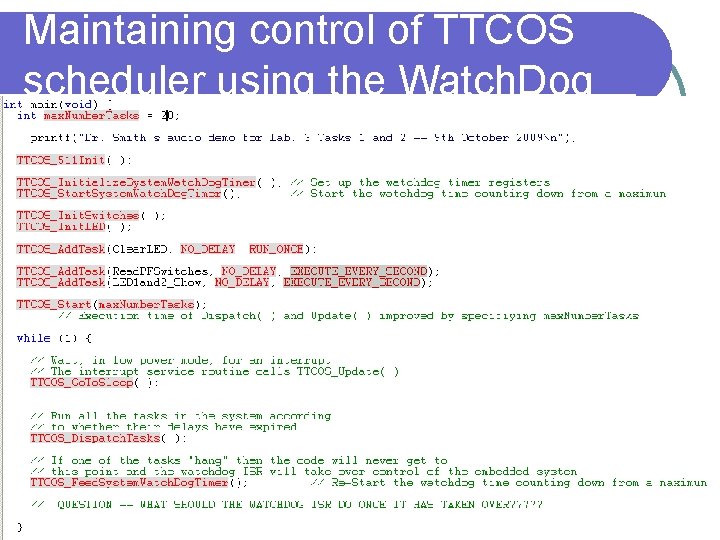

Maintaining control of TTCOS scheduler using the Watch. Dog 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 5 / 31

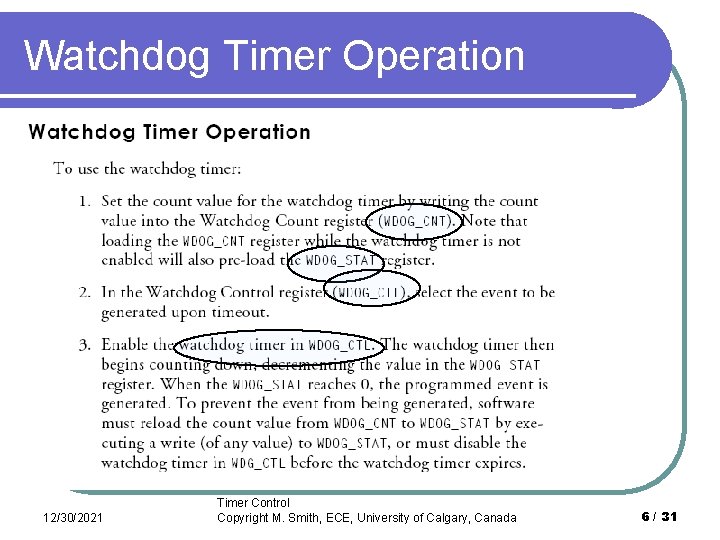

Watchdog Timer Operation 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 6 / 31

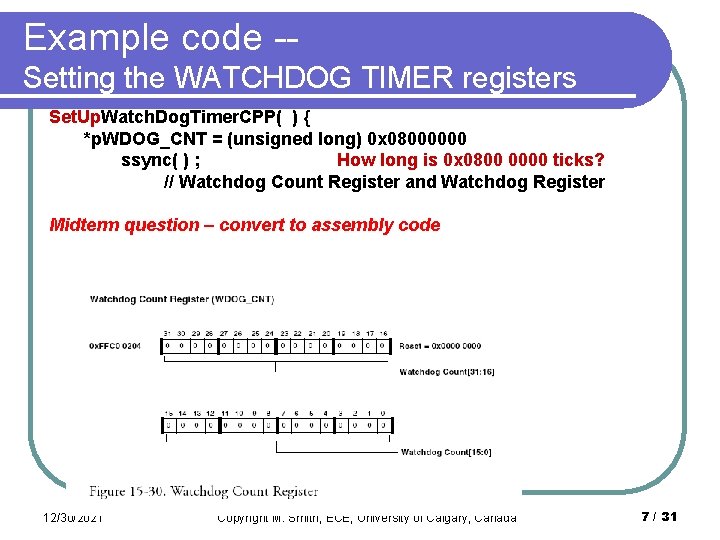

Example code -Setting the WATCHDOG TIMER registers Set. Up. Watch. Dog. Timer. CPP( ) { *p. WDOG_CNT = (unsigned long) 0 x 08000000 ssync( ) ; How long is 0 x 0800 0000 ticks? // Watchdog Count Register and Watchdog Register Midterm question – convert to assembly code 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 7 / 31

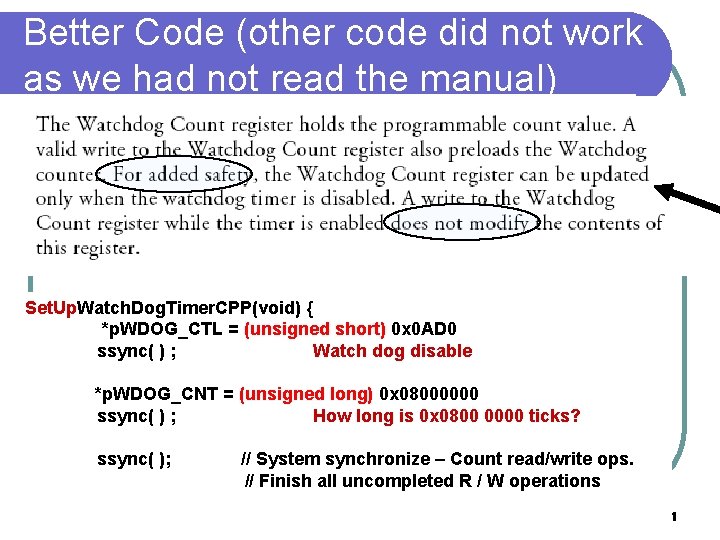

Better Code (other code did not work as we had not read the manual) Set. Up. Watch. Dog. Timer. CPP(void) { *p. WDOG_CTL = (unsigned short) 0 x 0 AD 0 ssync( ) ; Watch dog disable *p. WDOG_CNT = (unsigned long) 0 x 08000000 ssync( ) ; How long is 0 x 0800 0000 ticks? ssync( ); 12/30/2021 // System synchronize – Count read/write ops. // Finish all uncompleted R / W operations Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 8 / 31

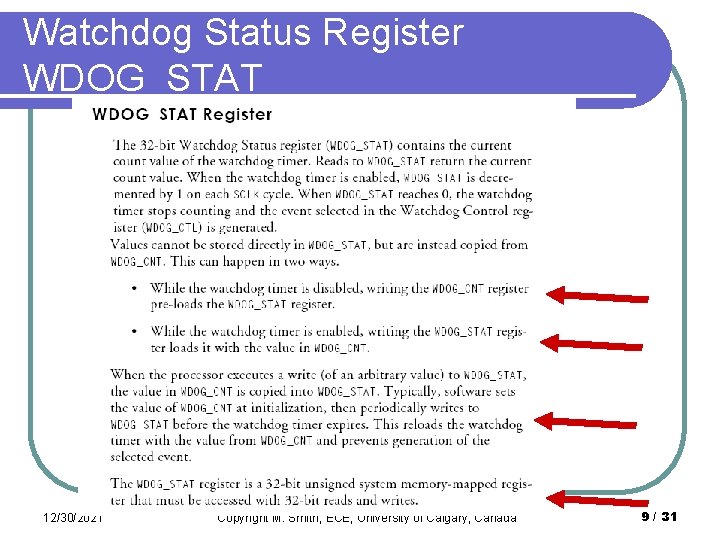

Watchdog Status Register WDOG_STAT 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 9 / 31

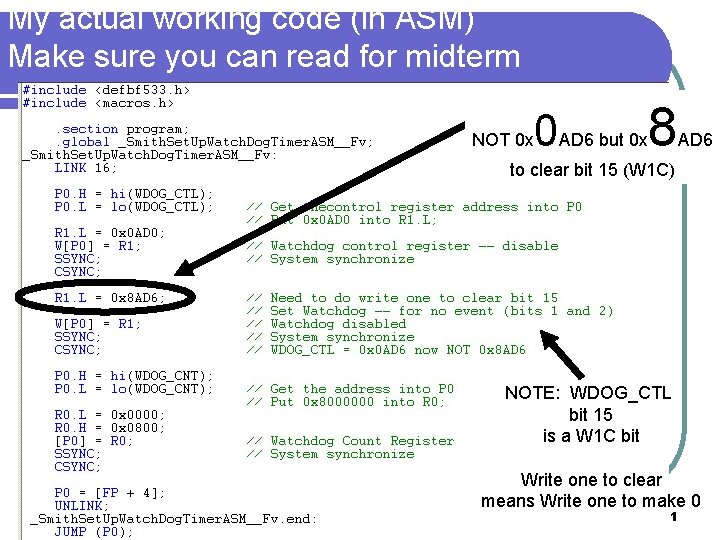

My actual working code (in ASM) Make sure you can read for midterm NOT 0 x 0 AD 6 but 0 x 8 AD 6 to clear bit 15 (W 1 C) NOTE: WDOG_CTL bit 15 is a W 1 C bit 12/30/2021 Write one to clear means Write one to make 0 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 10 / 31

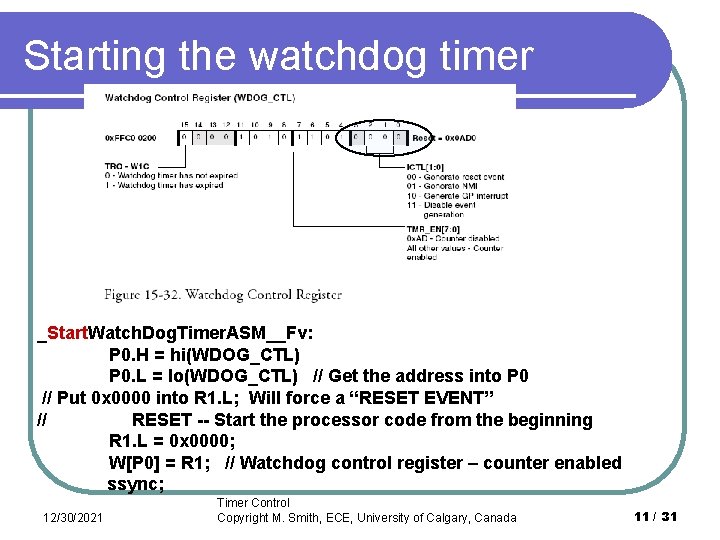

Starting the watchdog timer _Start. Watch. Dog. Timer. ASM__Fv: P 0. H = hi(WDOG_CTL) P 0. L = lo(WDOG_CTL) // Get the address into P 0 // Put 0 x 0000 into R 1. L; Will force a “RESET EVENT” // RESET -- Start the processor code from the beginning R 1. L = 0 x 0000; W[P 0] = R 1; // Watchdog control register – counter enabled ssync; 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 11 / 31

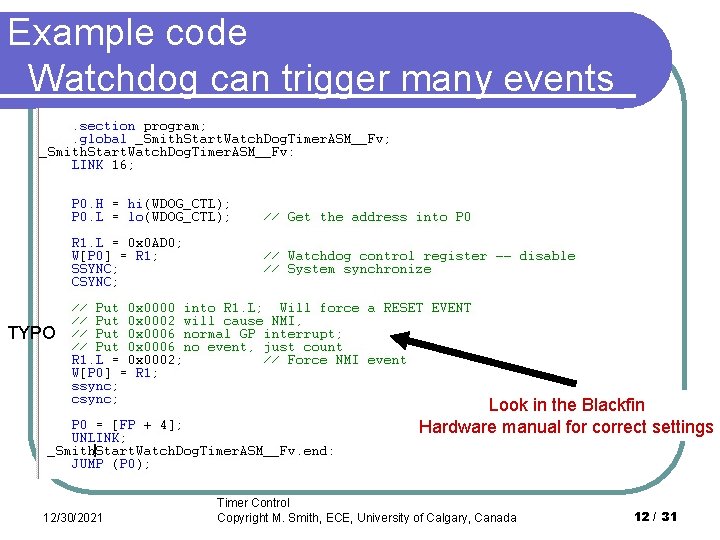

Example code Watchdog can trigger many events TYPO Look in the Blackfin Hardware manual for correct settings 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 12 / 31

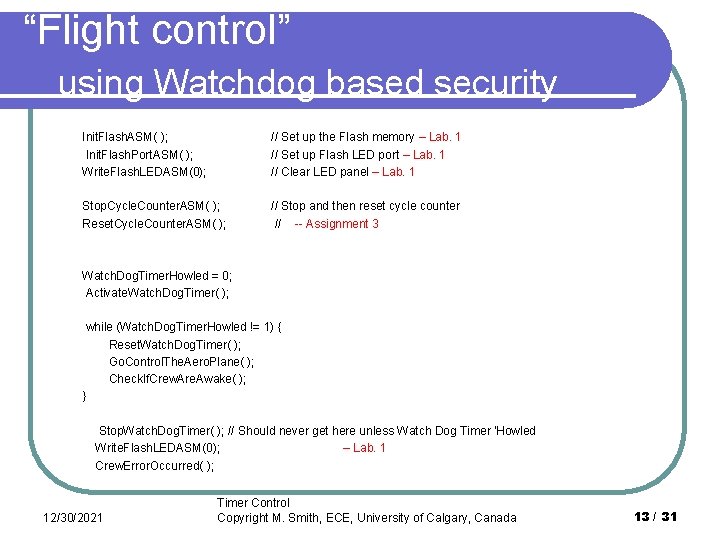

“Flight control” using Watchdog based security Init. Flash. ASM( ); Init. Flash. Port. ASM( ); Write. Flash. LEDASM(0); // Set up the Flash memory – Lab. 1 // Set up Flash LED port – Lab. 1 // Clear LED panel – Lab. 1 Stop. Cycle. Counter. ASM( ); Reset. Cycle. Counter. ASM( ); // Stop and then reset cycle counter // -- Assignment 3 Watch. Dog. Timer. Howled = 0; Activate. Watch. Dog. Timer( ); while (Watch. Dog. Timer. Howled != 1) { Reset. Watch. Dog. Timer( ); Go. Control. The. Aero. Plane( ); Check. If. Crew. Are. Awake( ); } Stop. Watch. Dog. Timer( ); // Should never get here unless Watch Dog Timer 'Howled Write. Flash. LEDASM(0); – Lab. 1 Crew. Error. Occurred( ); 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 13 / 31

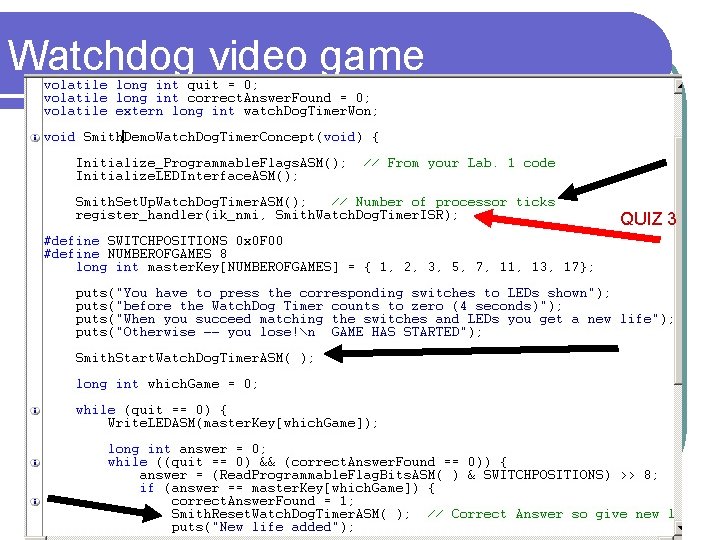

Watchdog video game QUIZ 3 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 14 / 31

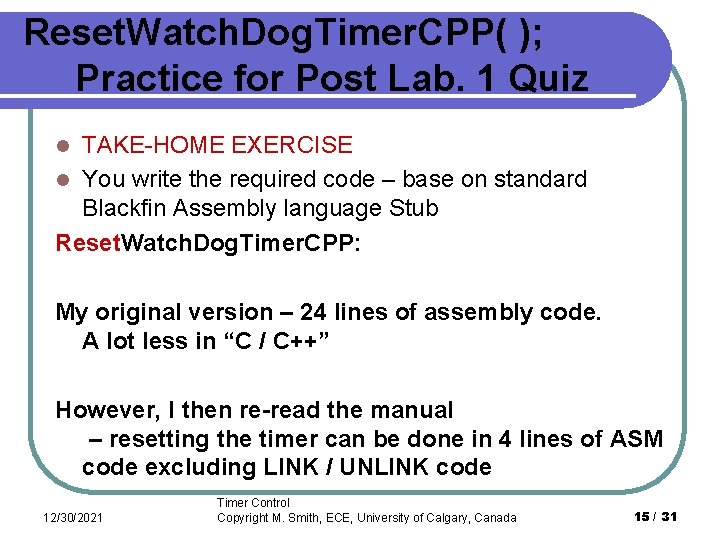

Reset. Watch. Dog. Timer. CPP( ); Practice for Post Lab. 1 Quiz TAKE-HOME EXERCISE l You write the required code – base on standard Blackfin Assembly language Stub Reset. Watch. Dog. Timer. CPP: l My original version – 24 lines of assembly code. A lot less in “C / C++” However, I then re-read the manual – resetting the timer can be done in 4 lines of ASM code excluding LINK / UNLINK code 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 15 / 31

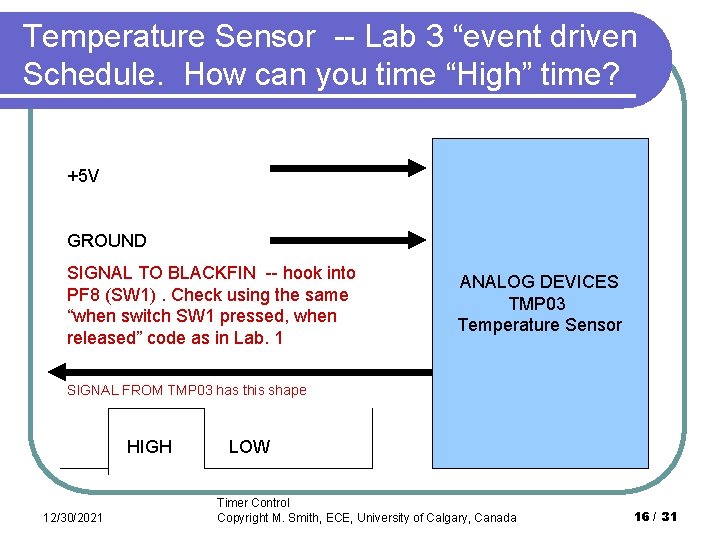

Temperature Sensor -- Lab 3 “event driven Schedule. How can you time “High” time? +5 V GROUND SIGNAL TO BLACKFIN -- hook into PF 8 (SW 1). Check using the same “when switch SW 1 pressed, when released” code as in Lab. 1 ANALOG DEVICES TMP 03 Temperature Sensor SIGNAL FROM TMP 03 has this shape HIGH 12/30/2021 LOW Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 16 / 31

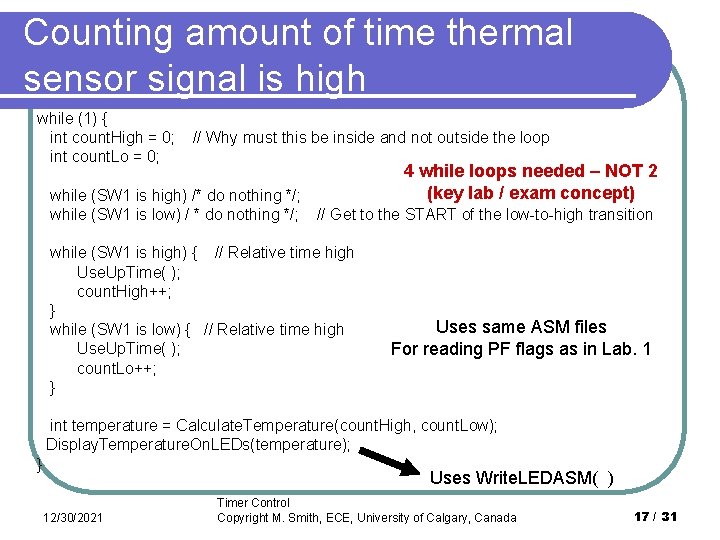

Counting amount of time thermal sensor signal is high while (1) { int count. High = 0; int count. Lo = 0; // Why must this be inside and not outside the loop 4 while loops needed – NOT 2 (key lab / exam concept) while (SW 1 is high) /* do nothing */; while (SW 1 is low) / * do nothing */; // Get to the START of the low-to-high transition while (SW 1 is high) { // Relative time high Use. Up. Time( ); count. High++; } while (SW 1 is low) { // Relative time high Use. Up. Time( ); count. Lo++; } Uses same ASM files For reading PF flags as in Lab. 1 int temperature = Calculate. Temperature(count. High, count. Low); Display. Temperature. On. LEDs(temperature); } Uses Write. LEDASM( ) 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 17 / 31

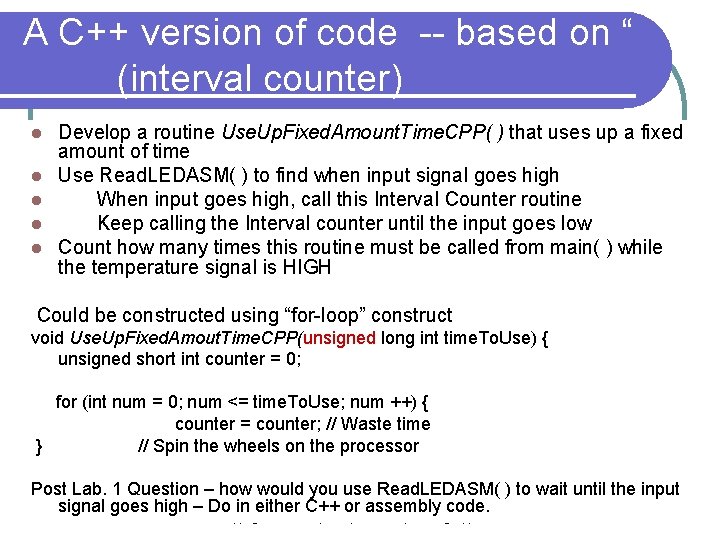

A C++ version of code -- based on “ (interval counter) l l l Develop a routine Use. Up. Fixed. Amount. Time. CPP( ) that uses up a fixed amount of time Use Read. LEDASM( ) to find when input signal goes high When input goes high, call this Interval Counter routine Keep calling the Interval counter until the input goes low Count how many times this routine must be called from main( ) while the temperature signal is HIGH Could be constructed using “for-loop” construct void Use. Up. Fixed. Amout. Time. CPP(unsigned long int time. To. Use) { unsigned short int counter = 0; for (int num = 0; num <= time. To. Use; num ++) { counter = counter; // Waste time } // Spin the wheels on the processor Post Lab. 1 Question – how would you use Read. LEDASM( ) to wait until the input Timer signal goes high – Do in Control either C++ or assembly code. 12/30/2021 Copyright M. Smith, ECE, University of Calgary, Canada 18 / 31

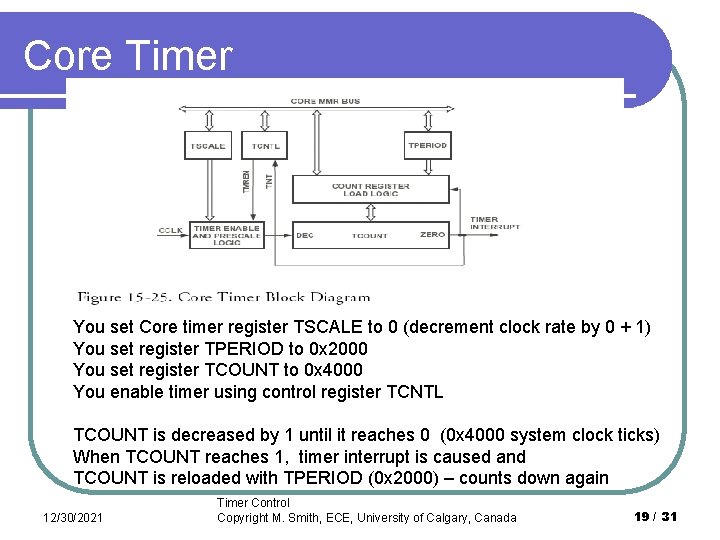

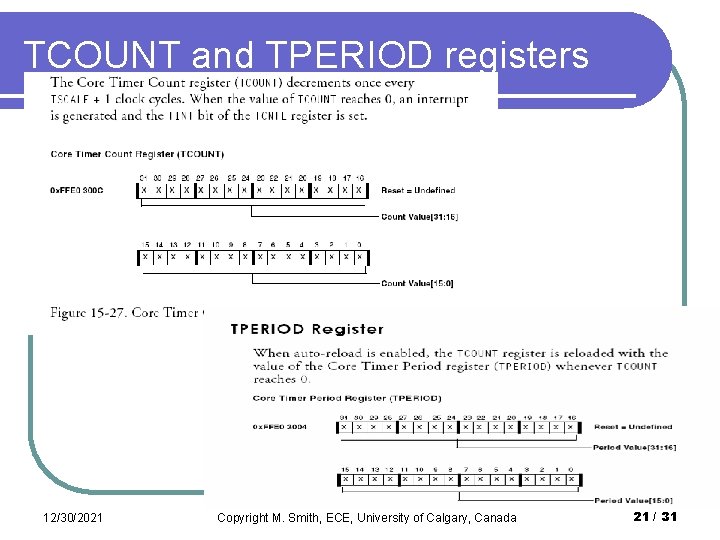

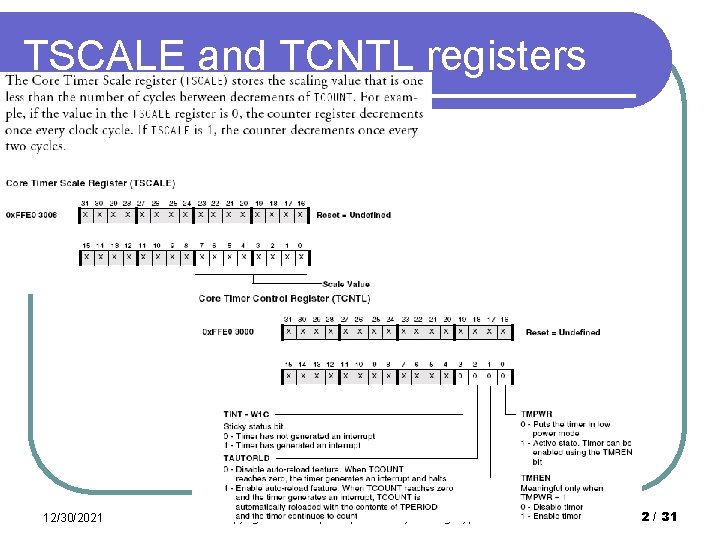

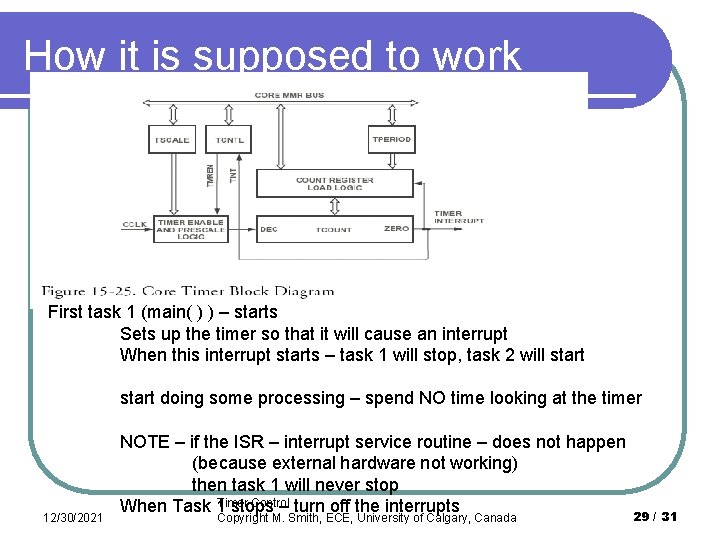

Core Timer You set Core timer register TSCALE to 0 (decrement clock rate by 0 + 1) You set register TPERIOD to 0 x 2000 You set register TCOUNT to 0 x 4000 You enable timer using control register TCNTL TCOUNT is decreased by 1 until it reaches 0 (0 x 4000 system clock ticks) When TCOUNT reaches 1, timer interrupt is caused and TCOUNT is reloaded with TPERIOD (0 x 2000) – counts down again 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 19 / 31

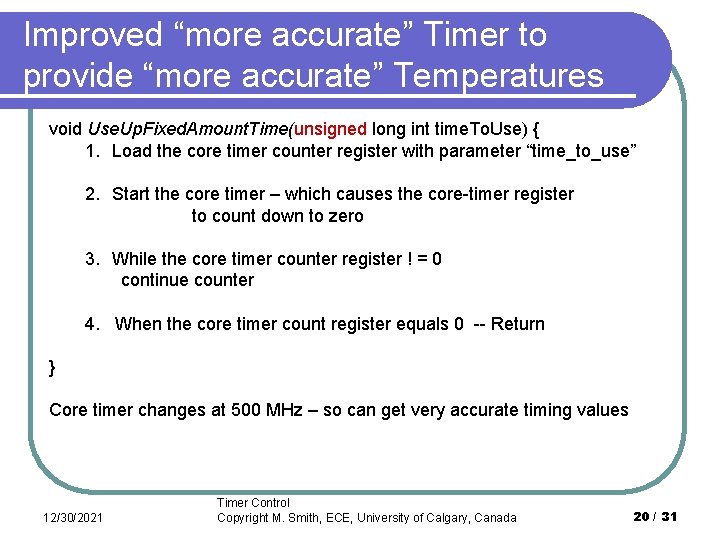

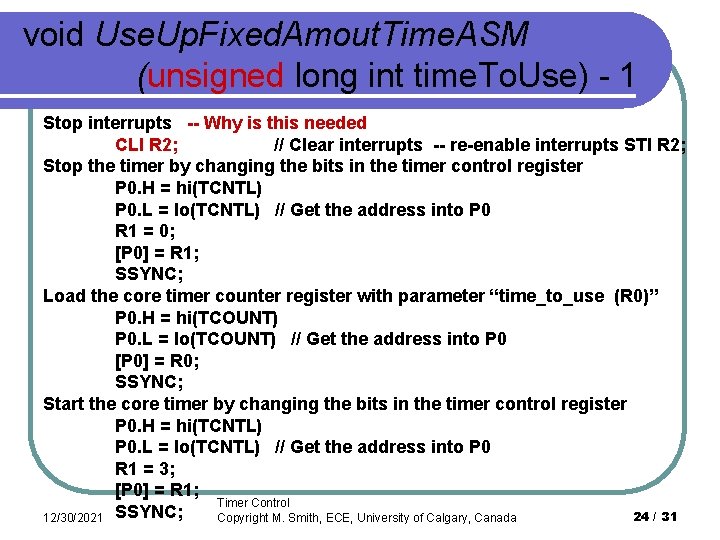

Improved “more accurate” Timer to provide “more accurate” Temperatures void Use. Up. Fixed. Amount. Time(unsigned long int time. To. Use) { 1. Load the core timer counter register with parameter “time_to_use” 2. Start the core timer – which causes the core-timer register to count down to zero 3. While the core timer counter register ! = 0 continue counter 4. When the core timer count register equals 0 -- Return } Core timer changes at 500 MHz – so can get very accurate timing values 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 20 / 31

TCOUNT and TPERIOD registers 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 21 / 31

TSCALE and TCNTL registers 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 22 / 31

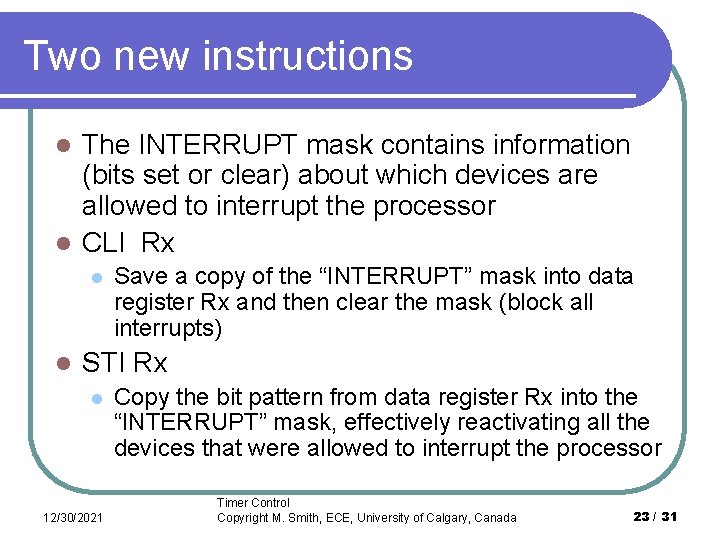

Two new instructions The INTERRUPT mask contains information (bits set or clear) about which devices are allowed to interrupt the processor l CLI Rx l l l Save a copy of the “INTERRUPT” mask into data register Rx and then clear the mask (block all interrupts) STI Rx l 12/30/2021 Copy the bit pattern from data register Rx into the “INTERRUPT” mask, effectively reactivating all the devices that were allowed to interrupt the processor Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 23 / 31

void Use. Up. Fixed. Amout. Time. ASM (unsigned long int time. To. Use) - 1 Stop interrupts -- Why is this needed CLI R 2; // Clear interrupts -- re-enable interrupts STI R 2; Stop the timer by changing the bits in the timer control register P 0. H = hi(TCNTL) P 0. L = lo(TCNTL) // Get the address into P 0 R 1 = 0; [P 0] = R 1; SSYNC; Load the core timer counter register with parameter “time_to_use (R 0)” P 0. H = hi(TCOUNT) P 0. L = lo(TCOUNT) // Get the address into P 0 [P 0] = R 0; SSYNC; Start the core timer by changing the bits in the timer control register P 0. H = hi(TCNTL) P 0. L = lo(TCNTL) // Get the address into P 0 R 1 = 3; [P 0] = R 1; Timer Control SSYNC; 24 / 31 12/30/2021 Copyright M. Smith, ECE, University of Calgary, Canada

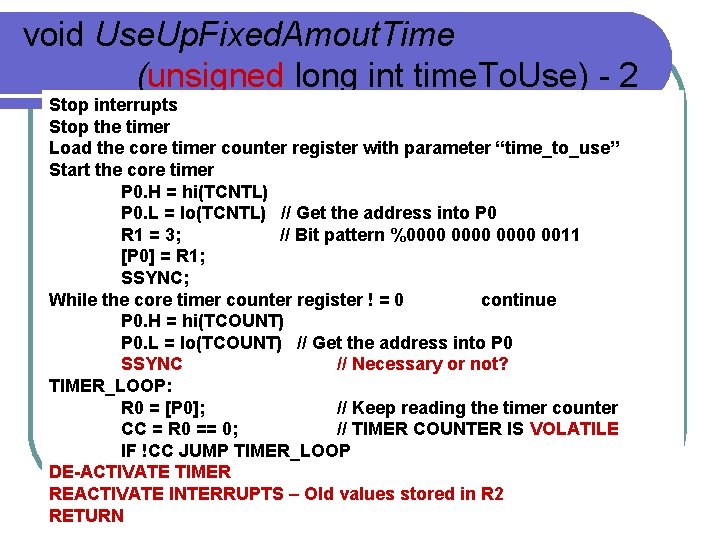

void Use. Up. Fixed. Amout. Time (unsigned long int time. To. Use) - 2 Stop interrupts Stop the timer Load the core timer counter register with parameter “time_to_use” Start the core timer P 0. H = hi(TCNTL) P 0. L = lo(TCNTL) // Get the address into P 0 R 1 = 3; // Bit pattern %0000 0011 [P 0] = R 1; SSYNC; While the core timer counter register ! = 0 continue P 0. H = hi(TCOUNT) P 0. L = lo(TCOUNT) // Get the address into P 0 SSYNC // Necessary or not? TIMER_LOOP: R 0 = [P 0]; // Keep reading the timer counter CC = R 0 == 0; // TIMER COUNTER IS VOLATILE IF !CC JUMP TIMER_LOOP DE-ACTIVATE TIMER REACTIVATE INTERRUPTS – Old values stored in R 2 Timer Control RETURN 12/30/2021 Copyright M. Smith, ECE, University of Calgary, Canada 25 / 31

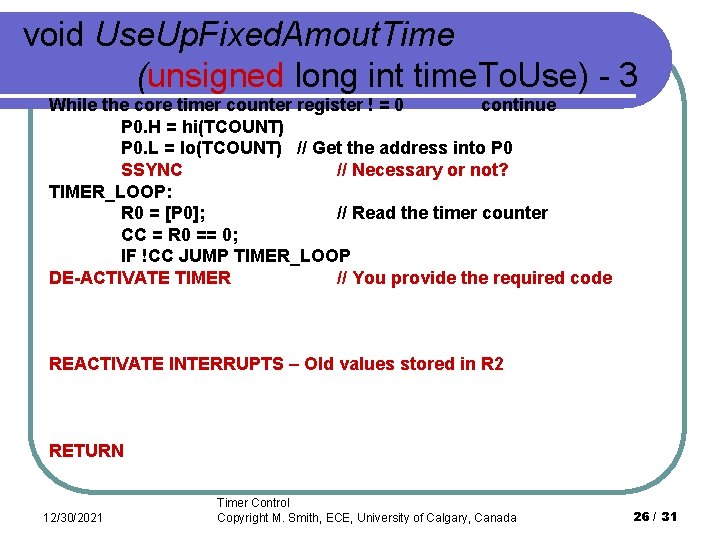

void Use. Up. Fixed. Amout. Time (unsigned long int time. To. Use) - 3 While the core timer counter register ! = 0 continue P 0. H = hi(TCOUNT) P 0. L = lo(TCOUNT) // Get the address into P 0 SSYNC // Necessary or not? TIMER_LOOP: R 0 = [P 0]; // Read the timer counter CC = R 0 == 0; IF !CC JUMP TIMER_LOOP DE-ACTIVATE TIMER // You provide the required code REACTIVATE INTERRUPTS – Old values stored in R 2 RETURN 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 26 / 31

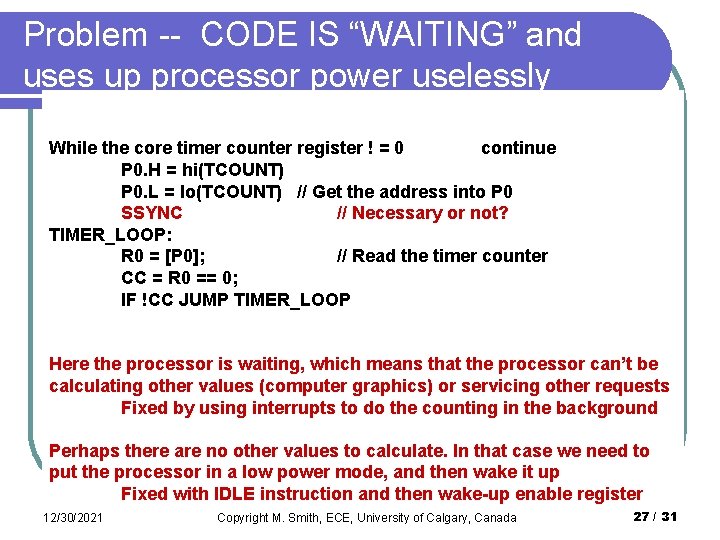

Problem -- CODE IS “WAITING” and uses up processor power uselessly While the core timer counter register ! = 0 continue P 0. H = hi(TCOUNT) P 0. L = lo(TCOUNT) // Get the address into P 0 SSYNC // Necessary or not? TIMER_LOOP: R 0 = [P 0]; // Read the timer counter CC = R 0 == 0; IF !CC JUMP TIMER_LOOP Here the processor is waiting, which means that the processor can’t be calculating other values (computer graphics) or servicing other requests Fixed by using interrupts to do the counting in the background Perhaps there are no other values to calculate. In that case we need to put the processor in a low power mode, and then wake it up Fixed with IDLE instruction and then wake-up enable register Timer Control 12/30/2021 Copyright M. Smith, ECE, University of Calgary, Canada 27 / 31

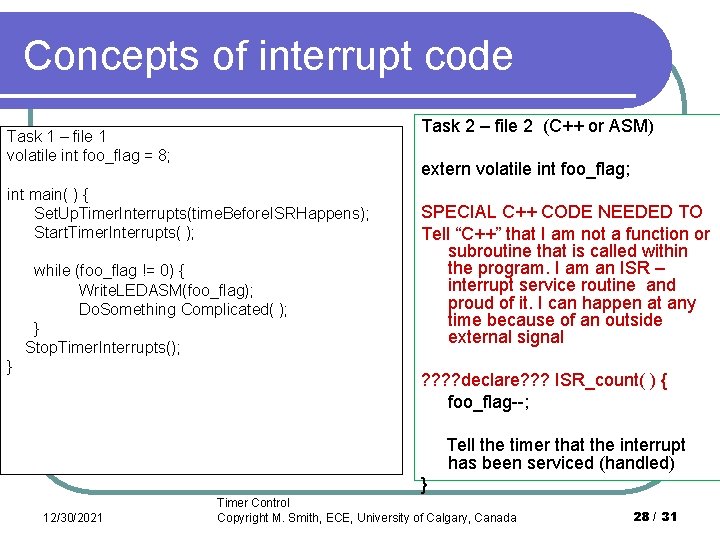

Concepts of interrupt code Task 2 – file 2 (C++ or ASM) Task 1 – file 1 volatile int foo_flag = 8; extern volatile int foo_flag; int main( ) { Set. Up. Timer. Interrupts(time. Before. ISRHappens); Start. Timer. Interrupts( ); while (foo_flag != 0) { Write. LEDASM(foo_flag); Do. Something Complicated( ); } Stop. Timer. Interrupts(); } SPECIAL C++ CODE NEEDED TO Tell “C++” that I am not a function or subroutine that is called within the program. I am an ISR – interrupt service routine and proud of it. I can happen at any time because of an outside external signal ? ? declare? ? ? ISR_count( ) { foo_flag--; Tell the timer that the interrupt has been serviced (handled) } 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 28 / 31

How it is supposed to work First task 1 (main( ) ) – starts Sets up the timer so that it will cause an interrupt When this interrupt starts – task 1 will stop, task 2 will start doing some processing – spend NO time looking at the timer 12/30/2021 NOTE – if the ISR – interrupt service routine – does not happen (because external hardware not working) then task 1 will never stop Control When Task 1 Timer stops – turn off the interrupts Copyright M. Smith, ECE, University of Calgary, Canada 29 / 31

Task 2 and Task 1 in this code (Not Lab. 2 Tasks 1 and 2) l Task 1 and Task 2 communicate via the “volatile foo_flag” variable – “message” l Every time the timer counts down to zero The TCOUNTER register is reloaded with TPERIOD register value l The timer counts down again l An interrupt is issued and latched l 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 30 / 31

Unanswered questions 1. 2. 3. 4. 5. 6. 7. What does “volatile” mean? Why will “optimized code” probably not work if volatile is not used? How do you tell C++ that this function is an ISR and not a standard function? Why do you need to tell C++ that this function is an ISR and not a standard function? What is the difference (in coding) between an ISR and a standard function? How does an interupt get latched, why and where? Why do I have to tell the timer that the interrupt has been serviced, and how do I do it? 12/30/2021 Task 2 – file 2 (C++ or ASM) extern volatile int foo_flag; Tell “C++” that I am not a function but I am an ISR – interrupt service routine ? ? declare as ISR? ? ? ISR_count( ) { foo_flag--; Tell the timer that the interrupt has been serviced } Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 31 / 31

Tackled today Watchdog timer – Hardware Reference 15 -49 l Core timer – Hardware Reference 15 -45 l General purpose timers 15 -1 l l Pulse Width Modulation Pulse Width Count and Capture External Event Application of timers to provide code safety and improved version of Use. Fixed. Amount. Time. ASM( ) l Introduction to timer interrupts l 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 32 / 31

l Information taken from Analog Devices On-line Manuals with permission http: //www. analog. com/processors/resources/technical. Library/manuals/ l Information furnished by Analog Devices is believed to be accurate and reliable. However, Analog Devices assumes no responsibility for its use or for any infringement of any patent other rights of any third party which may result from its use. No license is granted by implication or otherwise under any patent or patent right of Analog Devices. Copyright Analog Devices, Inc. All rights reserved. 12/30/2021 Timer Control Copyright M. Smith, ECE, University of Calgary, Canada 33 / 31

- Slides: 33