CPRE 583 Reconfigurable Computing Lecture 4 9032010 VHDL

CPRE 583 Reconfigurable Computing Lecture 4: 9/03/2010 (VHDL Overview 2 ) Instructor: Dr. Phillip Jones (phjones@iastate. edu) Reconfigurable Computing Laboratory Iowa State University Ames, Iowa, USA http: //class. ece. iastate. edu/cpre 583/ 1 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Overview • Mini Literary Survey • VHDL review 2 2 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

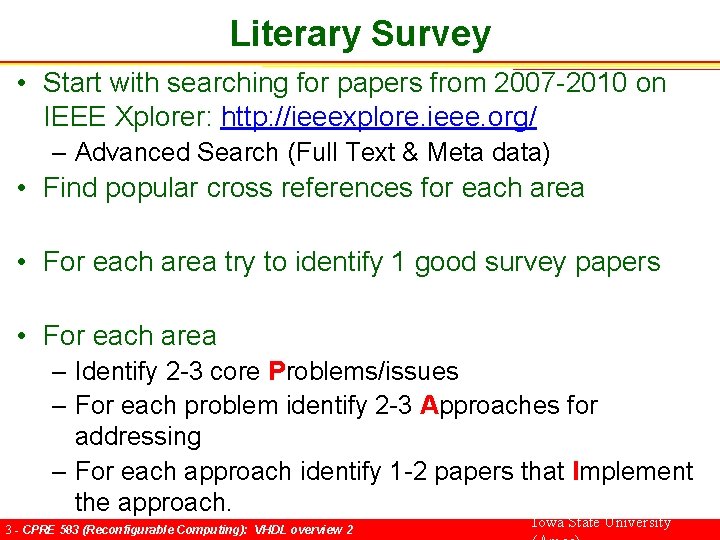

Literary Survey • Start with searching for papers from 2007 -2010 on IEEE Xplorer: http: //ieeexplore. ieee. org/ – Advanced Search (Full Text & Meta data) • Find popular cross references for each area • For each area try to identify 1 good survey papers • For each area – Identify 2 -3 core Problems/issues – For each problem identify 2 -3 Approaches for addressing – For each approach identify 1 -2 papers that Implement the approach. 3 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

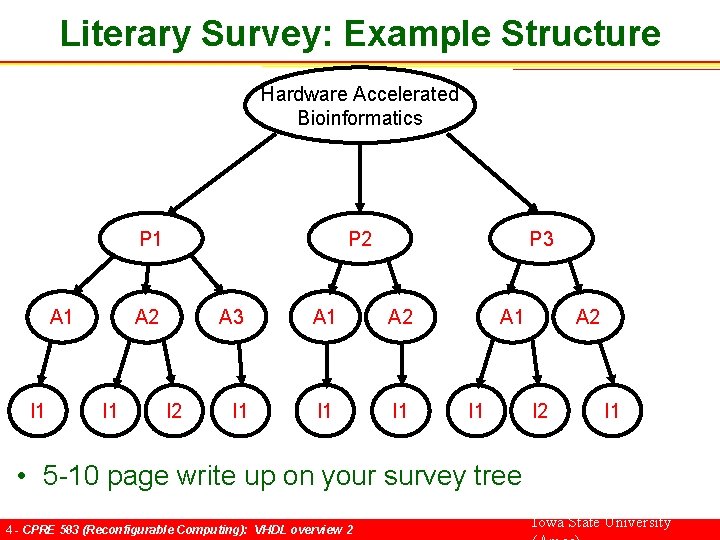

Literary Survey: Example Structure Hardware Accelerated Bioinformatics P 2 P 1 A 1 I 1 A 2 I 1 I 2 P 3 A 1 A 2 I 1 I 1 A 2 I 1 • 5 -10 page write up on your survey tree 4 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Literature Survey: Bioinformatics Date: 6/11/2010 Name : Pooja Mhapsekar 5 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

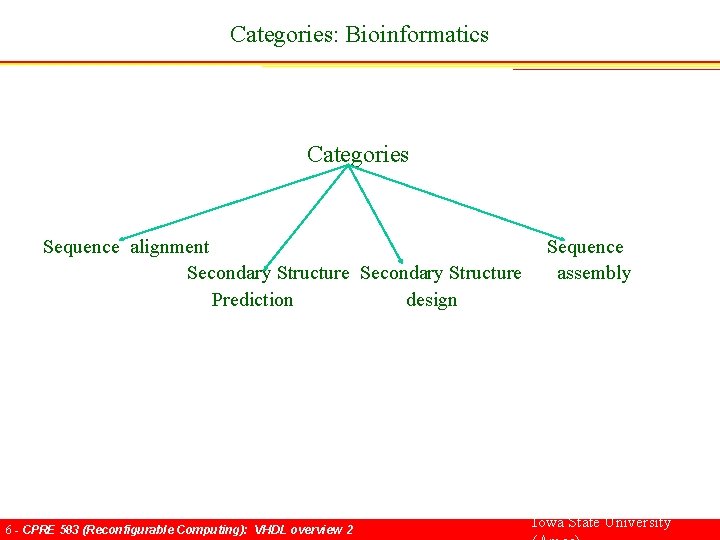

Categories: Bioinformatics Categories Sequence alignment Sequence Secondary Structure assembly Prediction design 6 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

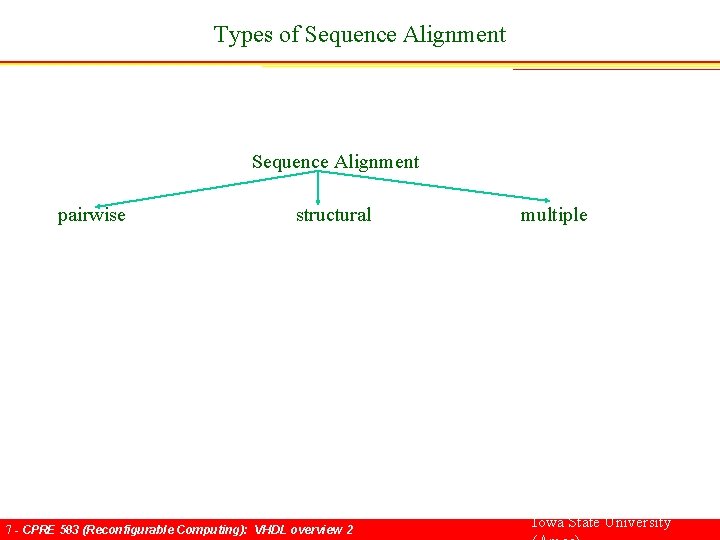

Types of Sequence Alignment Sequence Alignment pairwise structural multiple 7 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

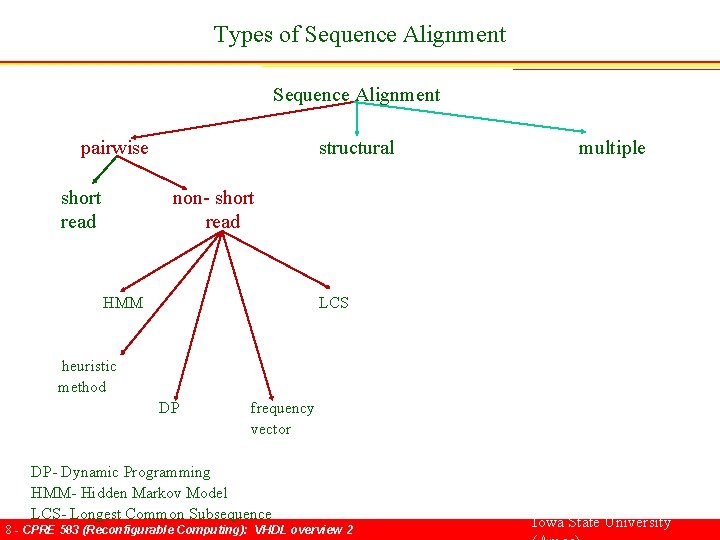

Types of Sequence Alignment pairwise structural multiple short non- short read HMM LCS heuristic method DP frequency vector DP- Dynamic Programming HMM- Hidden Markov Model LCS- Longest Common Subsequence 8 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

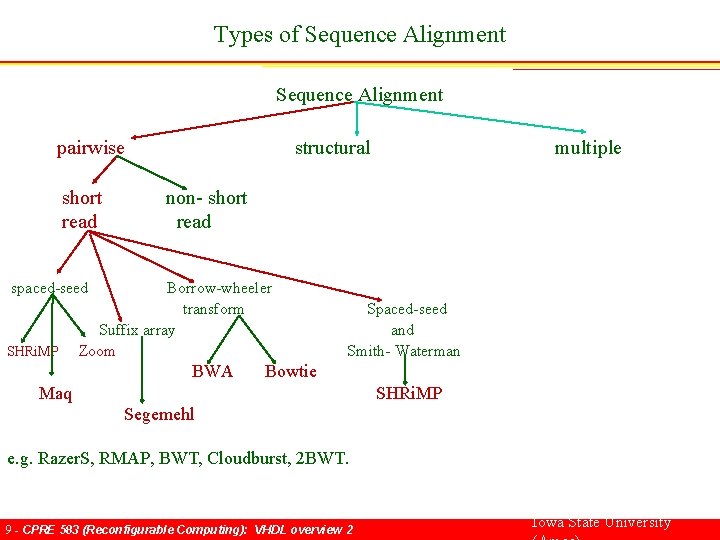

Types of Sequence Alignment pairwise structural multiple short non- short read spaced-seed Borrow-wheeler transform Suffix array SHRi. MP Zoom Spaced-seed and Smith- Waterman BWA Bowtie Maq SHRi. MP Segemehl e. g. Razer. S, RMAP, BWT, Cloudburst, 2 BWT. 9 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

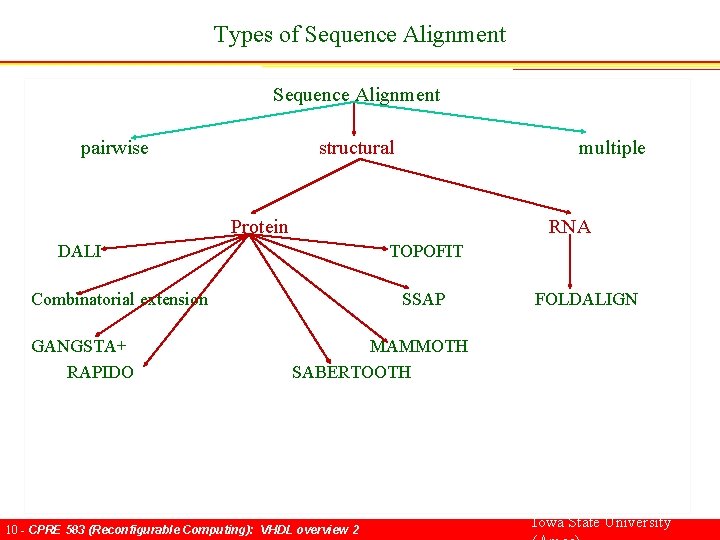

Types of Sequence Alignment pairwise structural multiple Protein RNA DALI TOPOFIT Combinatorial extension SSAP FOLDALIGN GANGSTA+ MAMMOTH RAPIDO SABERTOOTH 10 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

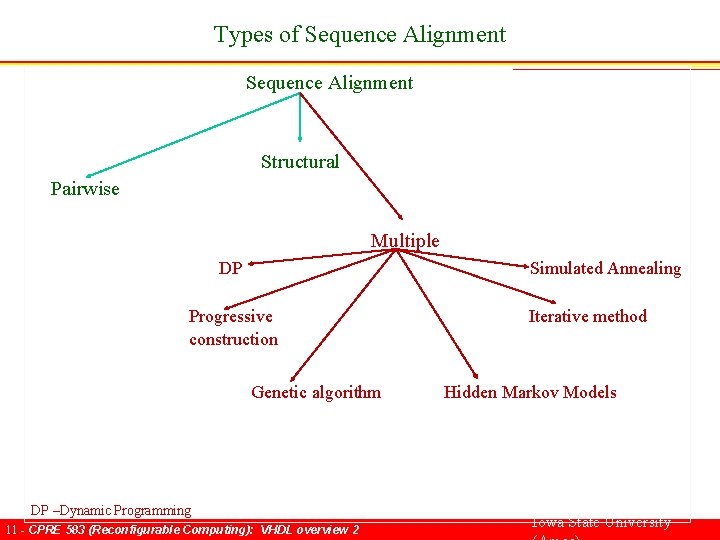

Types of Sequence Alignment Structural Pairwise Multiple DP Simulated Annealing Progressive Iterative method construction Genetic algorithm Hidden Markov Models DP –Dynamic Programming 11 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

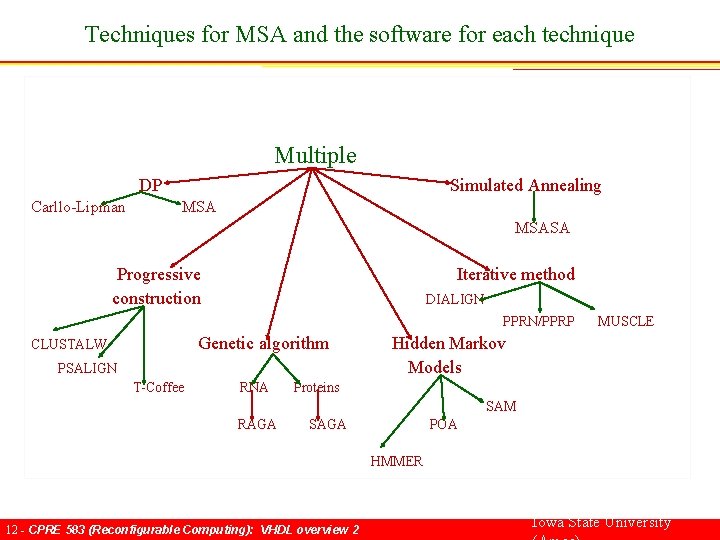

Techniques for MSA and the software for each technique Multiple DP Simulated Annealing Carllo-Lipman MSA MSASA Progressive Iterative method construction DIALIGN PPRN/PPRP MUSCLE CLUSTALW Genetic algorithm Hidden Markov PSALIGN Models T-Coffee RNA Proteins SAM RAGA SAGA POA HMMER 12 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

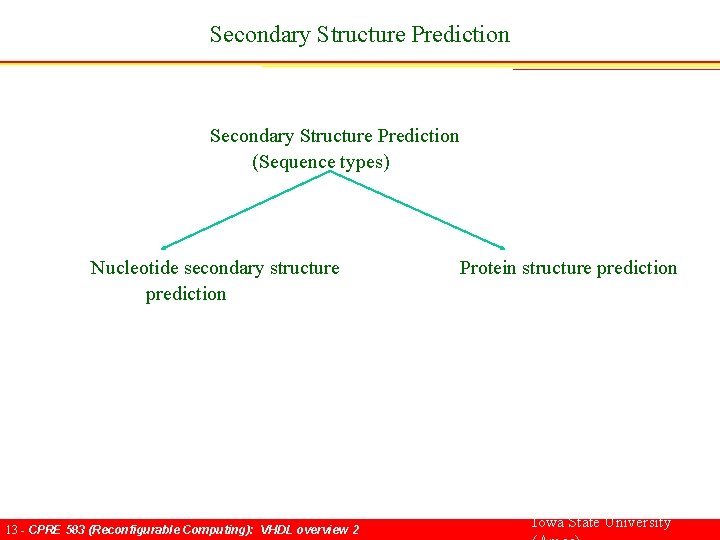

Secondary Structure Prediction Secondary Structure Prediction (Sequence types) Nucleotide secondary structure Protein structure prediction 13 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

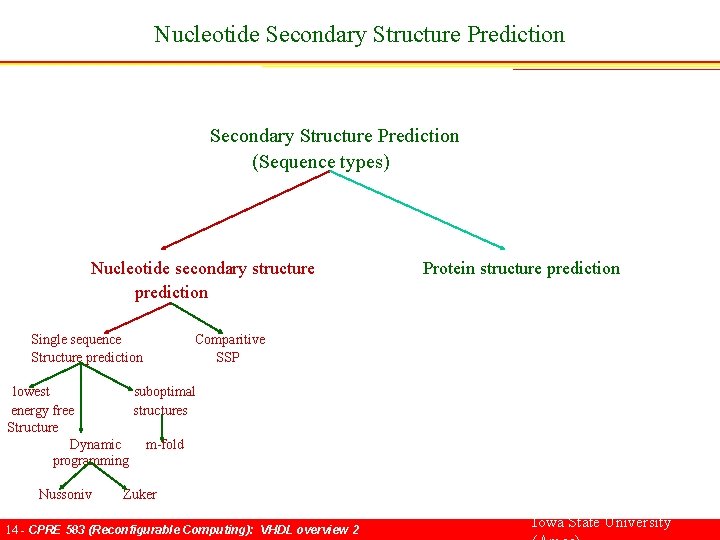

Nucleotide Secondary Structure Prediction Secondary Structure Prediction (Sequence types) Nucleotide secondary structure Protein structure prediction prediction Single sequence Comparitive Structure prediction SSP lowest suboptimal energy free structures Structure Dynamic m-fold programming Nussoniv Zuker 14 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

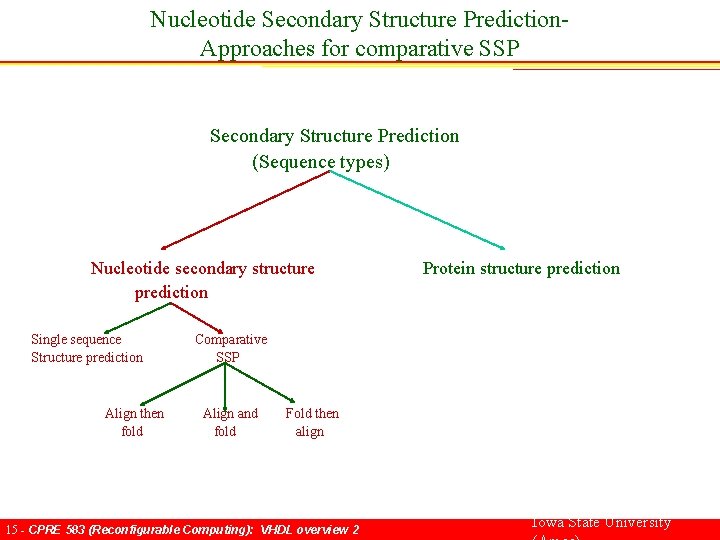

Nucleotide Secondary Structure Prediction. Approaches for comparative SSP Secondary Structure Prediction (Sequence types) Nucleotide secondary structure Protein structure prediction prediction Single sequence Comparative Structure prediction SSP Align then Align and Fold then fold align 15 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

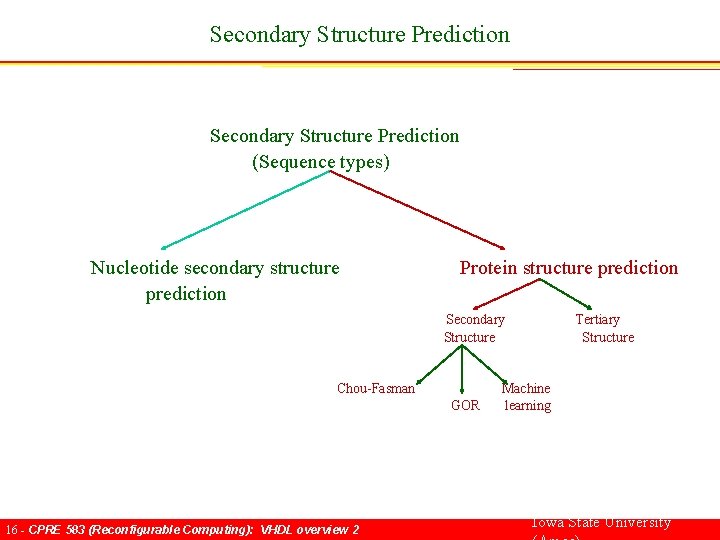

Secondary Structure Prediction Secondary Structure Prediction (Sequence types) Nucleotide secondary structure Protein structure prediction Secondary Tertiary Structure Chou-Fasman Machine GOR learning 16 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

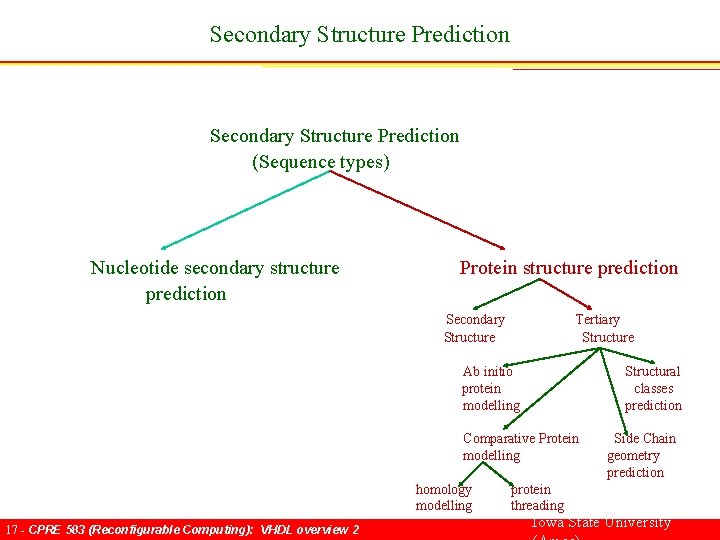

Secondary Structure Prediction Secondary Structure Prediction (Sequence types) Nucleotide secondary structure Protein structure prediction Secondary Tertiary Structure Ab initio Structural protein classes modelling prediction 17 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Comparative Protein Side Chain modelling geometry prediction homology protein modelling threading Iowa State University

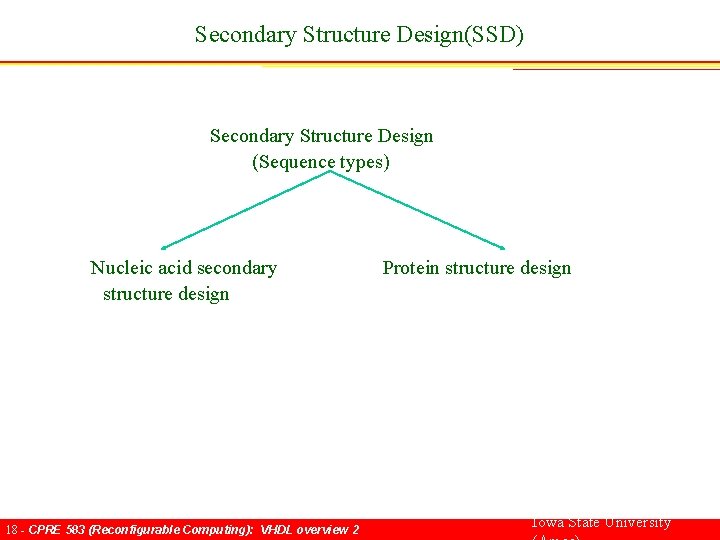

Secondary Structure Design(SSD) Secondary Structure Design (Sequence types) Nucleic acid secondary Protein structure design 18 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

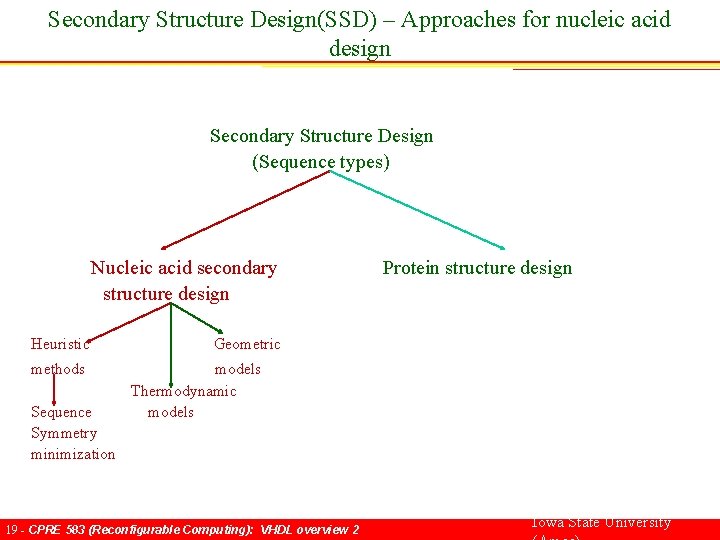

Secondary Structure Design(SSD) – Approaches for nucleic acid design Secondary Structure Design (Sequence types) Nucleic acid secondary Protein structure design Heuristic Geometric methods models Thermodynamic Sequence models Symmetry minimization 19 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

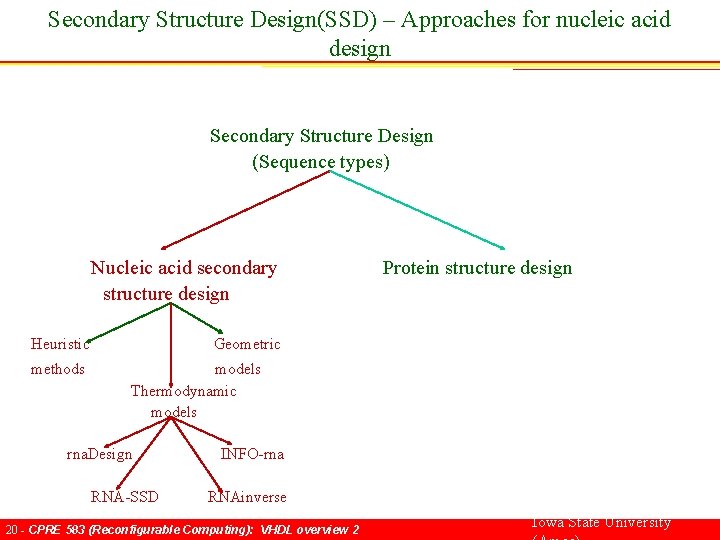

Secondary Structure Design(SSD) – Approaches for nucleic acid design Secondary Structure Design (Sequence types) Nucleic acid secondary Protein structure design Heuristic Geometric methods models Thermodynamic models rna. Design INFO-rna RNA-SSD RNAinverse 20 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

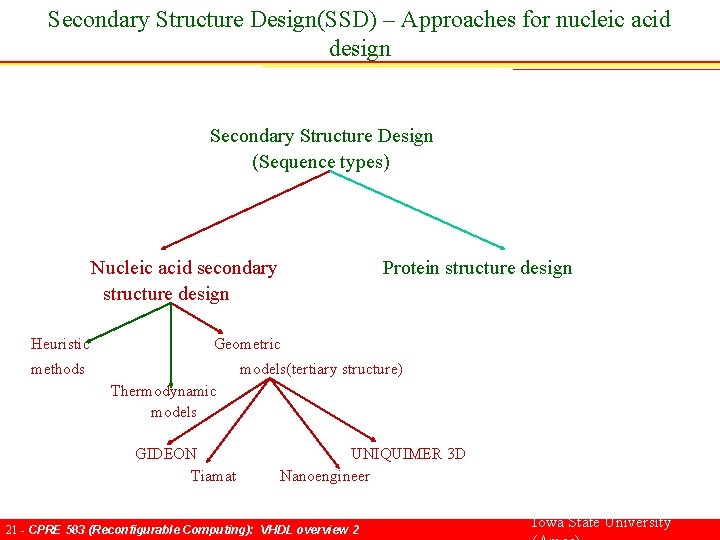

Secondary Structure Design(SSD) – Approaches for nucleic acid design Secondary Structure Design (Sequence types) Nucleic acid secondary Protein structure design Heuristic Geometric methods models(tertiary structure) Thermodynamic models GIDEON UNIQUIMER 3 D Tiamat Nanoengineer 21 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

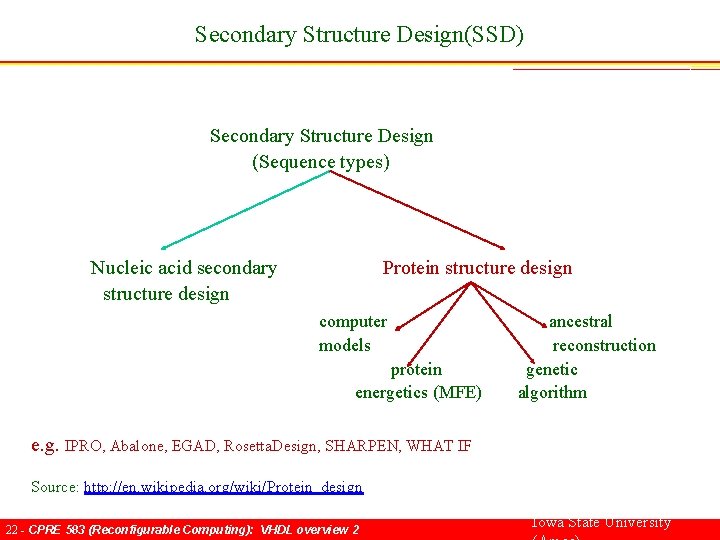

Secondary Structure Design(SSD) Secondary Structure Design (Sequence types) Nucleic acid secondary Protein structure design computer ancestral models reconstruction protein genetic energetics (MFE) algorithm e. g. IPRO, Abalone, EGAD, Rosetta. Design, SHARPEN, WHAT IF Source: http: //en. wikipedia. org/wiki/Protein_design 22 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

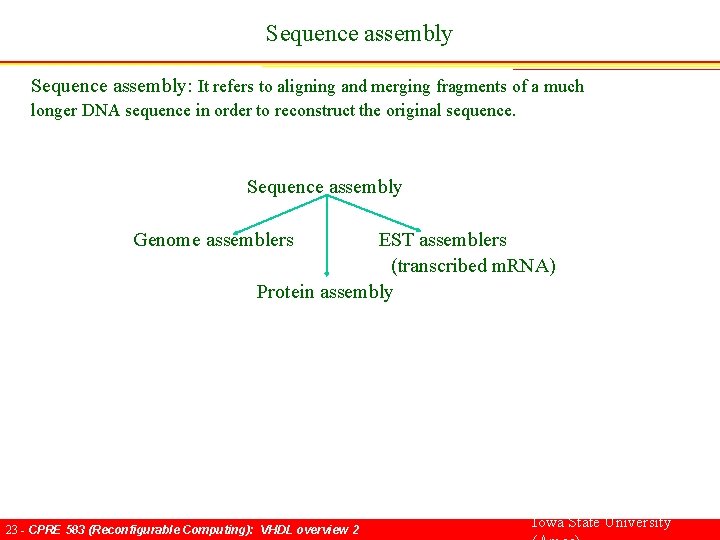

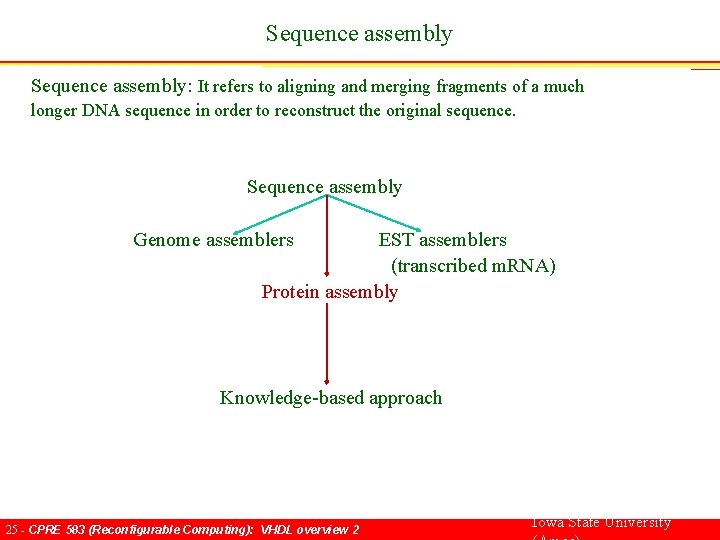

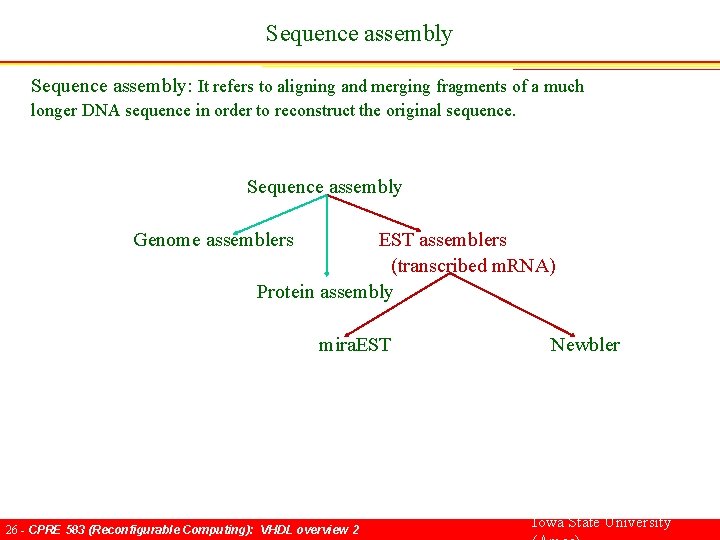

Sequence assembly: It refers to aligning and merging fragments of a much longer DNA sequence in order to reconstruct the original sequence. Sequence assembly Genome assemblers EST assemblers (transcribed m. RNA) Protein assembly 23 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

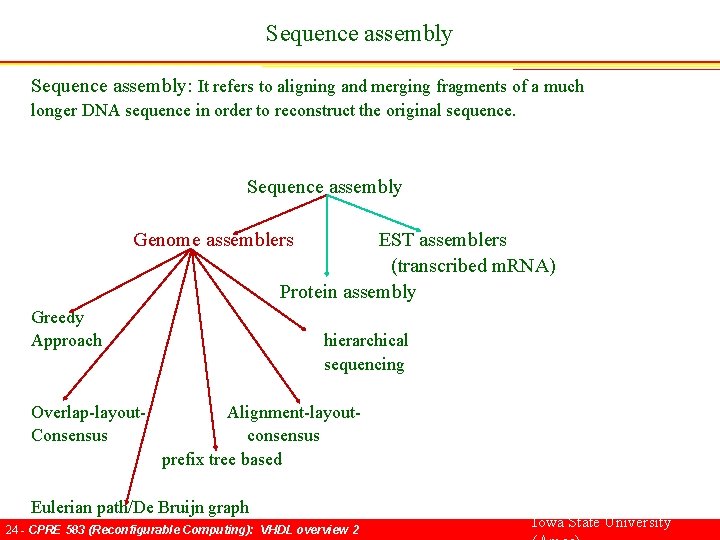

Sequence assembly: It refers to aligning and merging fragments of a much longer DNA sequence in order to reconstruct the original sequence. Sequence assembly Genome assemblers EST assemblers (transcribed m. RNA) Protein assembly Greedy Approach hierarchical sequencing Overlap-layout- Alignment-layout. Consensus consensus prefix tree based Eulerian path/De Bruijn graph 24 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Sequence assembly: It refers to aligning and merging fragments of a much longer DNA sequence in order to reconstruct the original sequence. Sequence assembly Genome assemblers EST assemblers (transcribed m. RNA) Protein assembly Knowledge-based approach 25 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Sequence assembly: It refers to aligning and merging fragments of a much longer DNA sequence in order to reconstruct the original sequence. Sequence assembly Genome assemblers EST assemblers (transcribed m. RNA) Protein assembly mira. EST Newbler 26 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

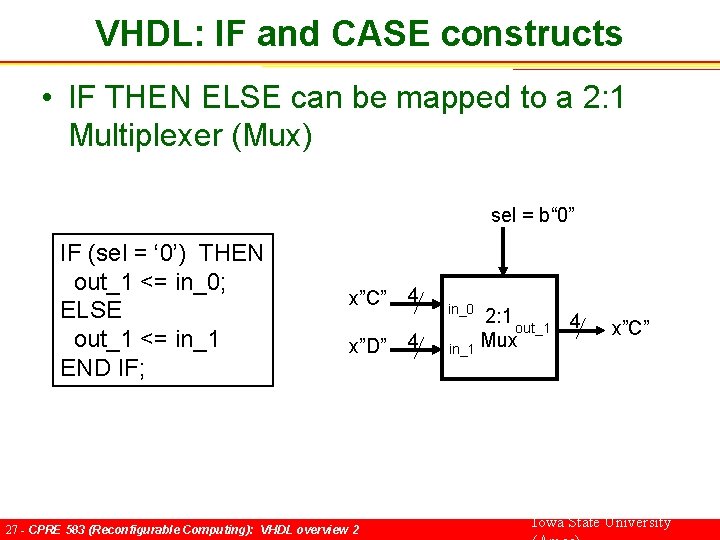

VHDL: IF and CASE constructs • IF THEN ELSE can be mapped to a 2: 1 Multiplexer (Mux) sel = b“ 0” IF (sel = ‘ 0’) THEN out_1 <= in_0; ELSE out_1 <= in_1 END IF; x”C” 4 x”D” 4 27 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 in_0 2: 1 out_1 4 Mux in_1 x”C” Iowa State University

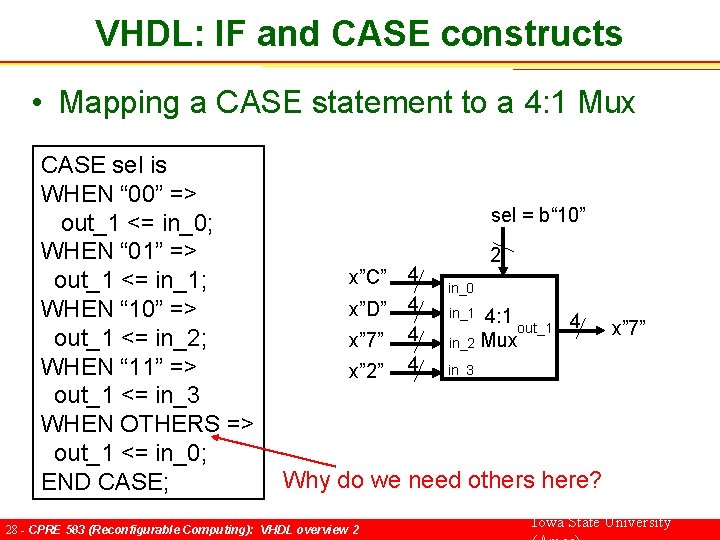

VHDL: IF and CASE constructs • Mapping a CASE statement to a 4: 1 Mux CASE sel is WHEN “ 00” => out_1 <= in_0; WHEN “ 01” => out_1 <= in_1; WHEN “ 10” => out_1 <= in_2; WHEN “ 11” => out_1 <= in_3 WHEN OTHERS => out_1 <= in_0; END CASE; sel = b“ 10” x”C” 4 x”D” 4 x” 7” 4 4 x” 2” 2 in_0 4: 1 out_1 4 in_2 Mux in_1 x” 7” in_3 Why do we need others here? 28 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

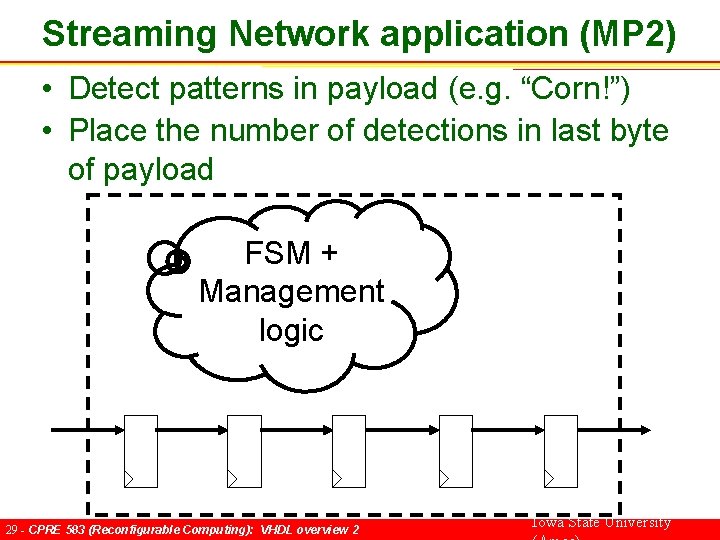

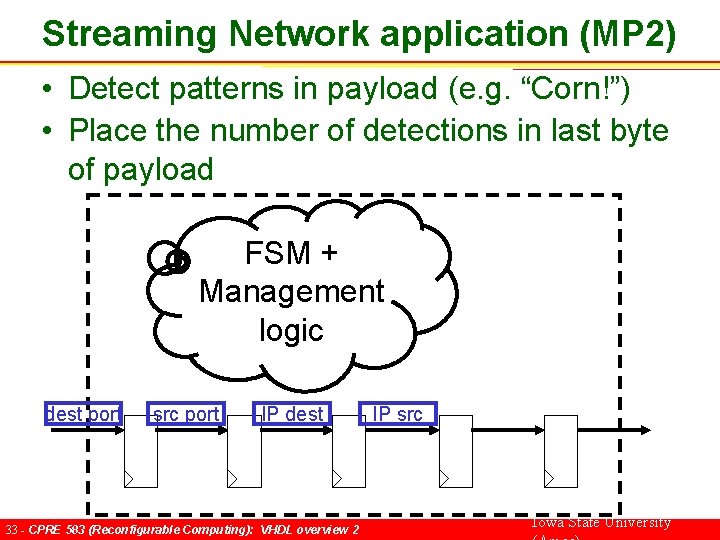

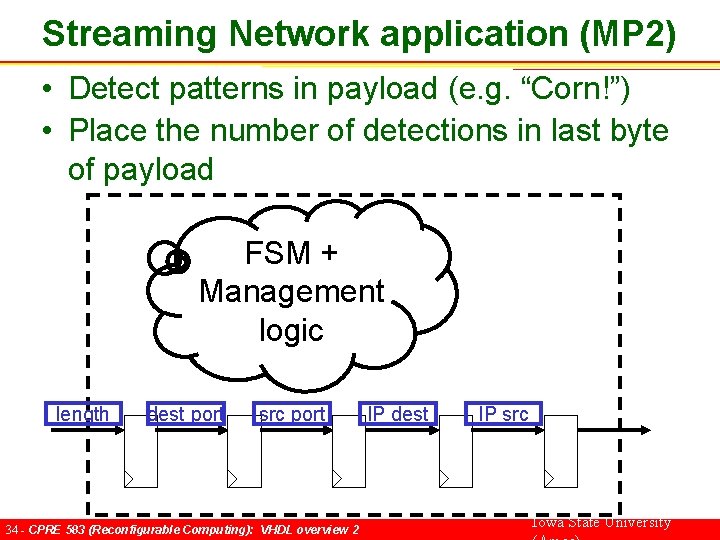

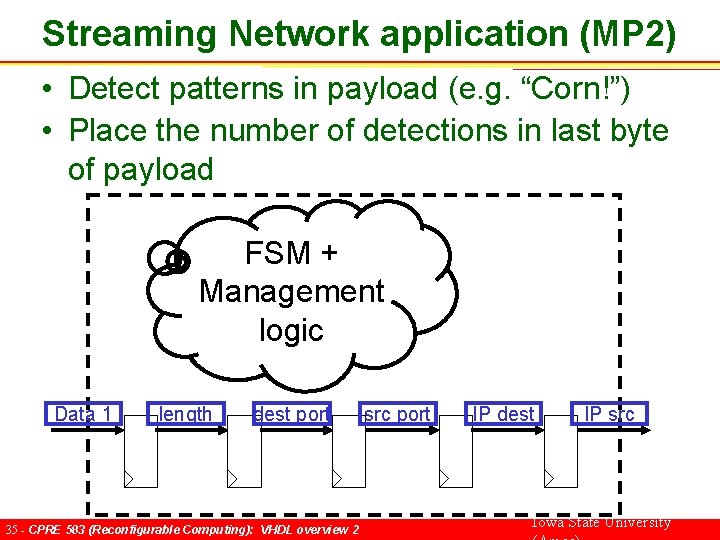

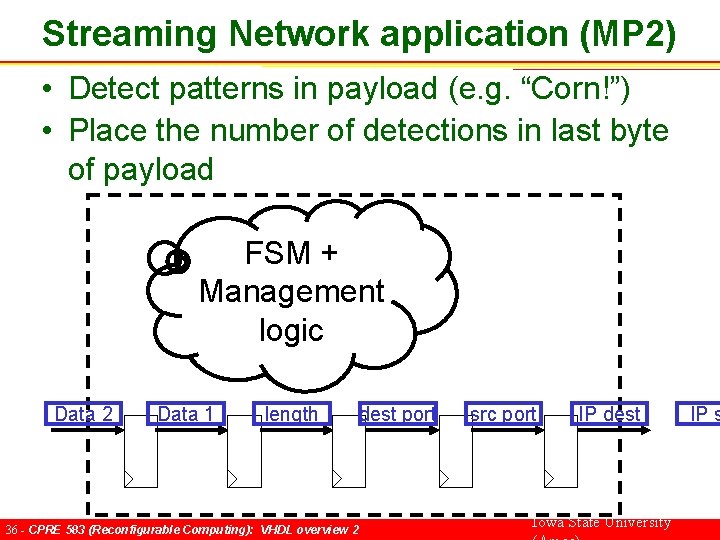

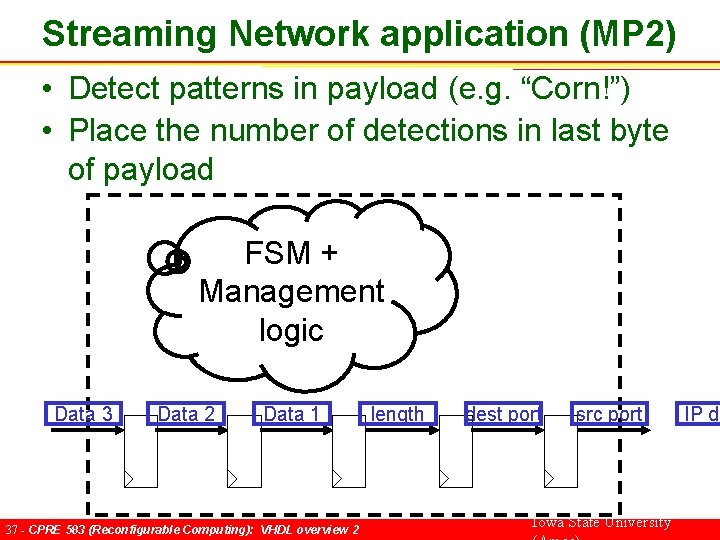

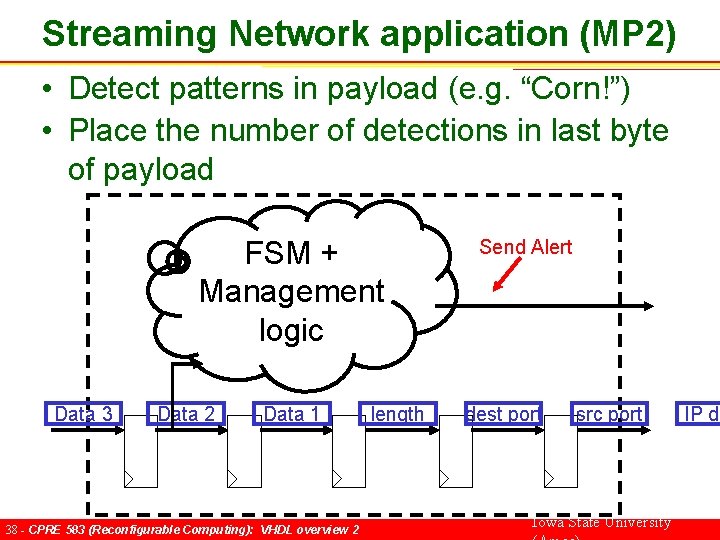

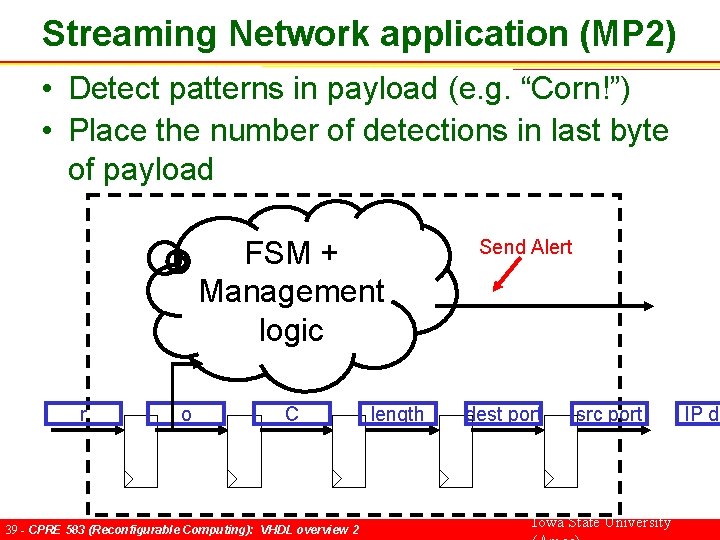

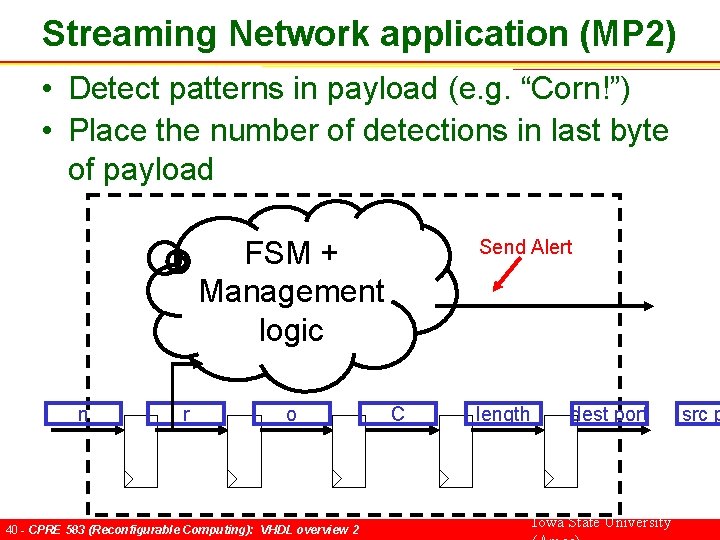

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic 29 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

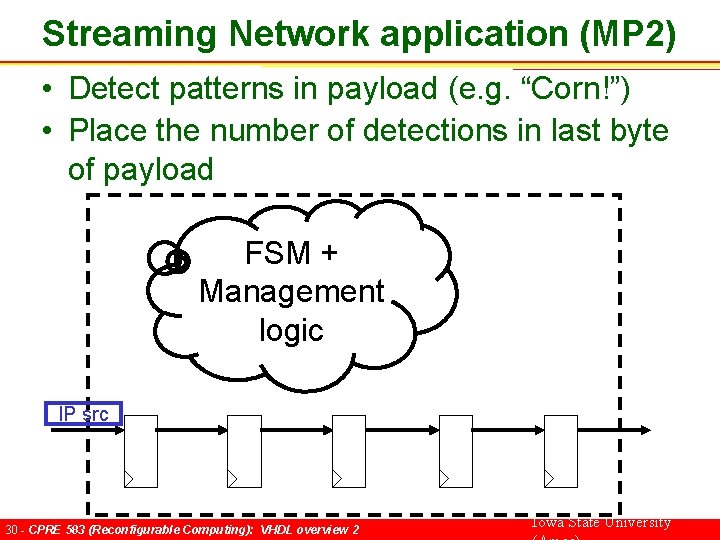

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic IP src 30 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

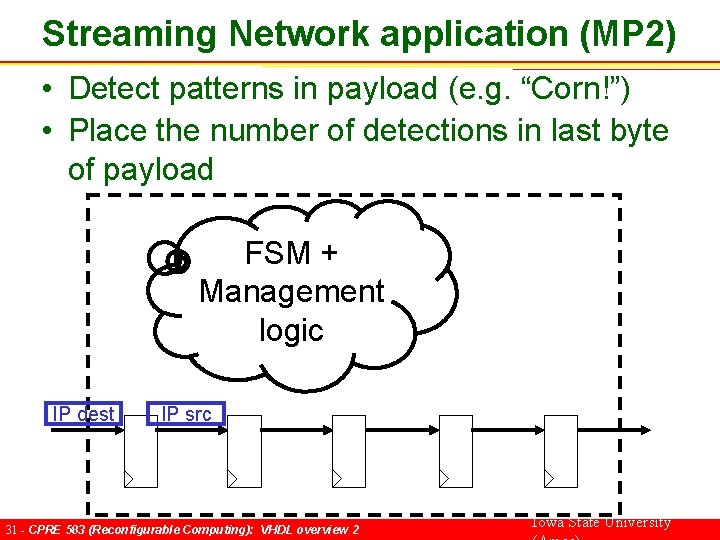

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic IP dest IP src 31 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

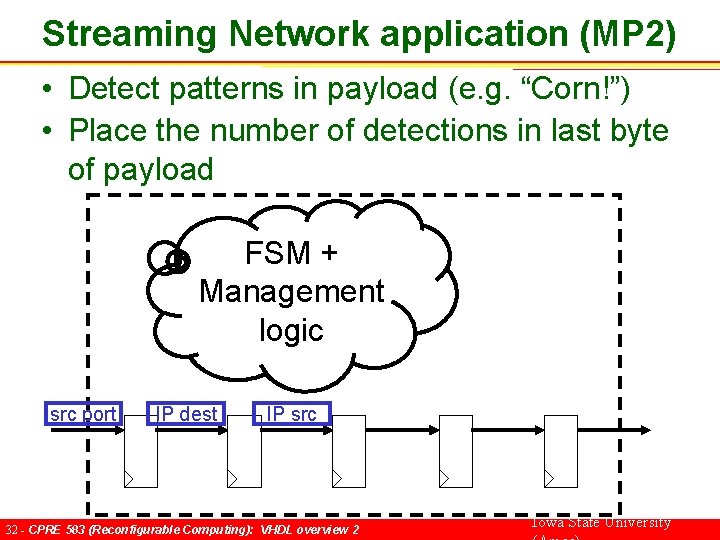

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic src port IP dest IP src 32 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic dest port src port IP dest 33 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 IP src Iowa State University

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic length dest port src port 34 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 IP dest IP src Iowa State University

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic Data 1 length dest port 35 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 src port IP dest IP src Iowa State University

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic Data 2 Data 1 length 36 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 dest port src port IP dest Iowa State University IP s

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic Data 3 Data 2 Data 1 37 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 length dest port src port Iowa State University IP de

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic Data 3 Data 2 Data 1 38 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 length Send Alert dest port src port Iowa State University IP de

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic r o C 39 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 length Send Alert dest port src port Iowa State University IP de

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic n r o 40 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Send Alert C length dest port Iowa State University src p

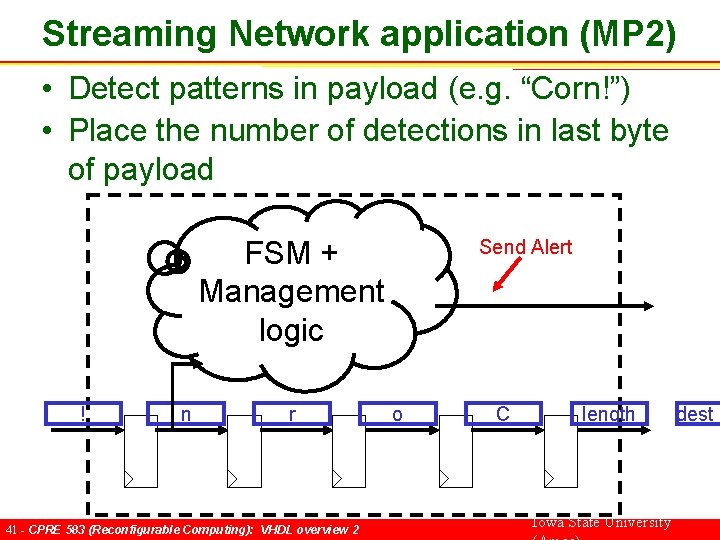

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic ! n r 41 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Send Alert o C length Iowa State University dest p

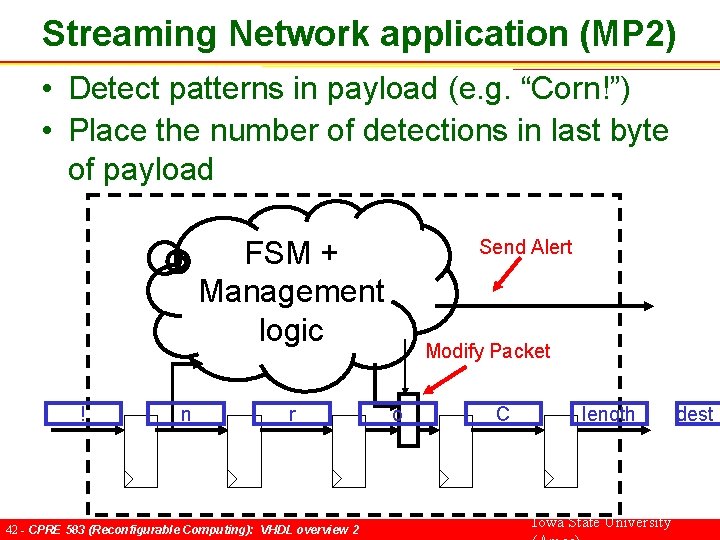

Streaming Network application (MP 2) • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload FSM + Management logic ! n r 42 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Send Alert Modify Packet o C length Iowa State University dest p

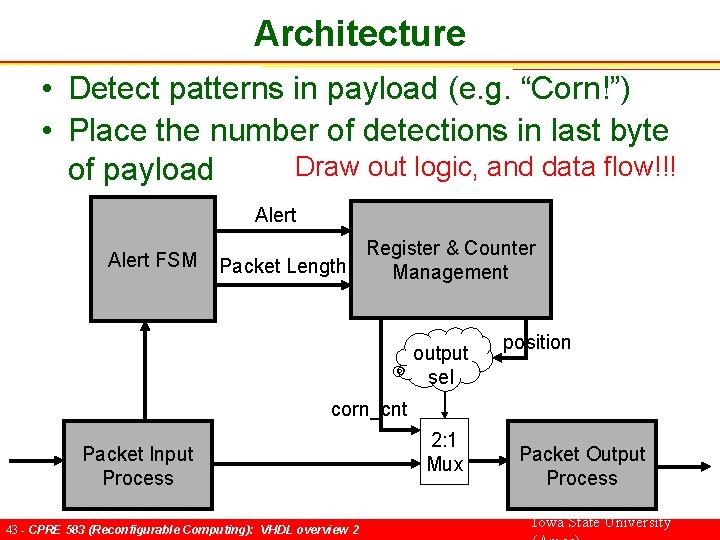

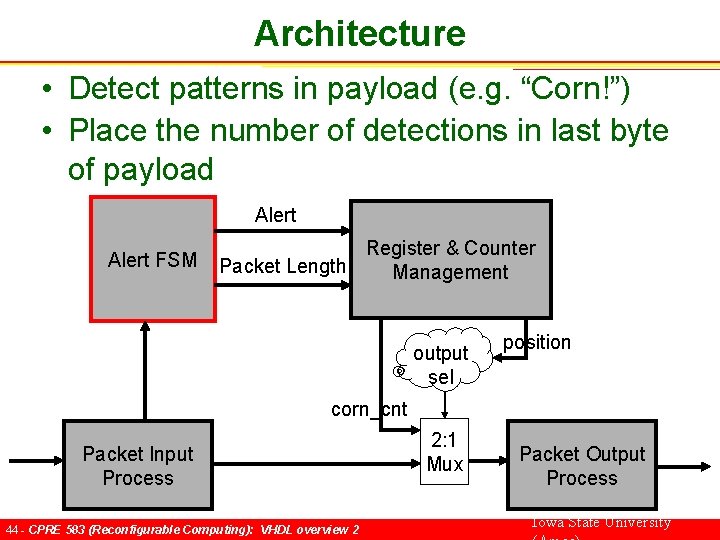

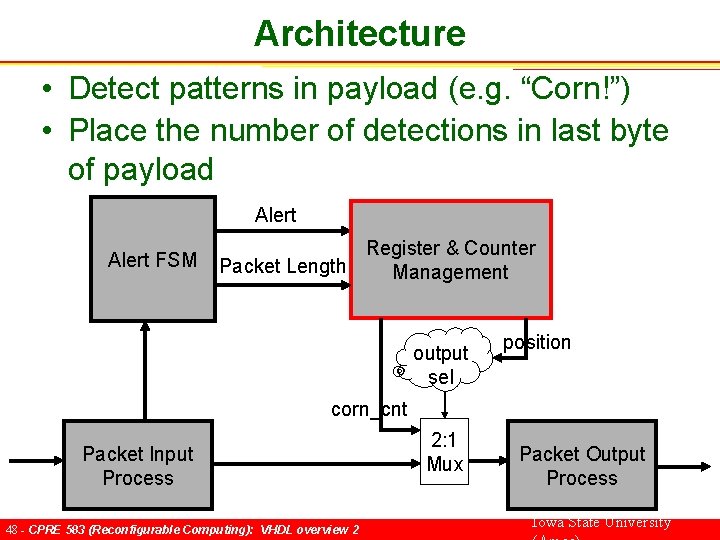

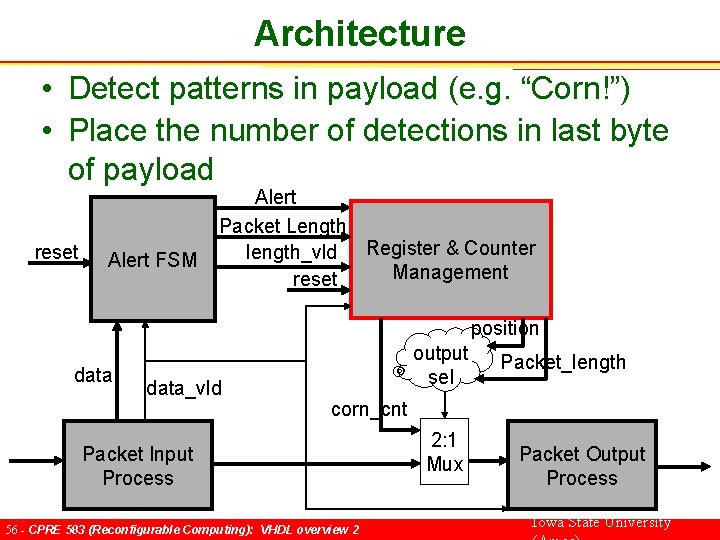

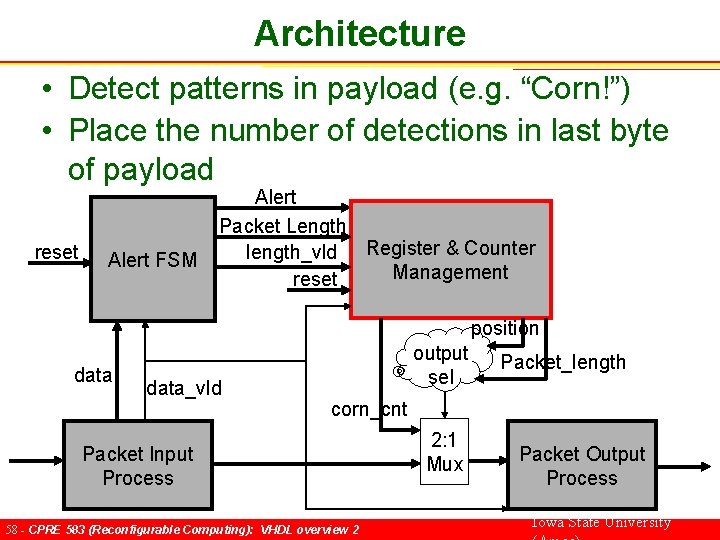

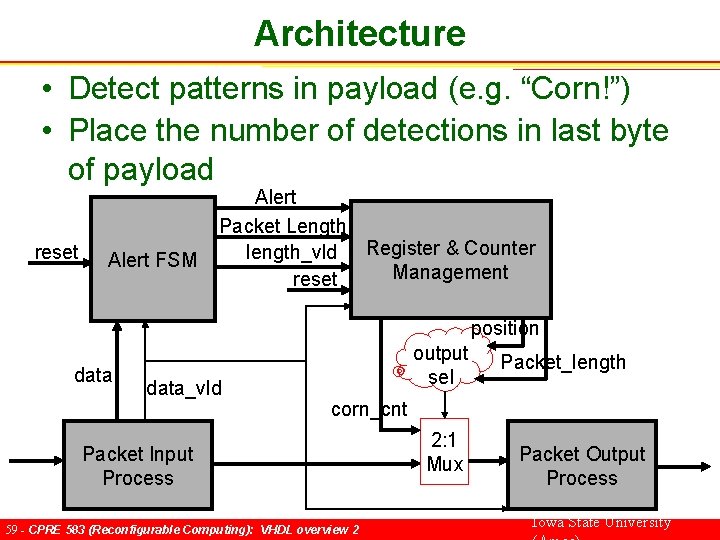

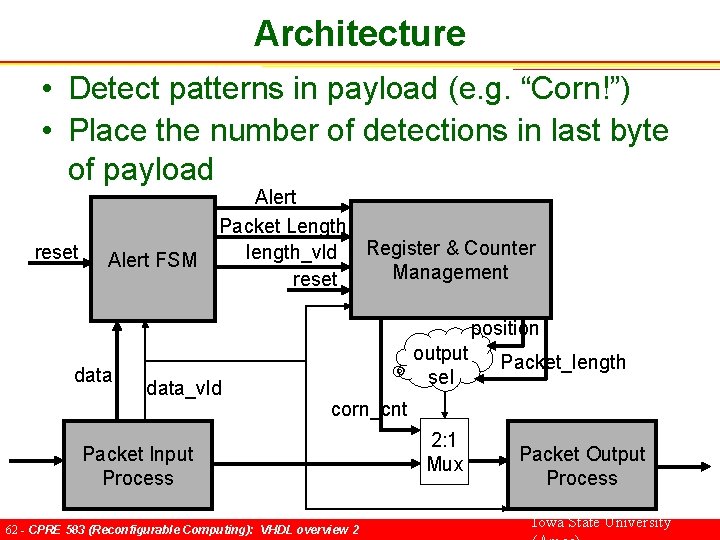

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte Draw out logic, and data flow!!! of payload Alert FSM Register & Counter Packet Length Management output sel position corn_cnt Packet Input Process 43 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload Alert FSM Register & Counter Packet Length Management output sel position corn_cnt Packet Input Process 44 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

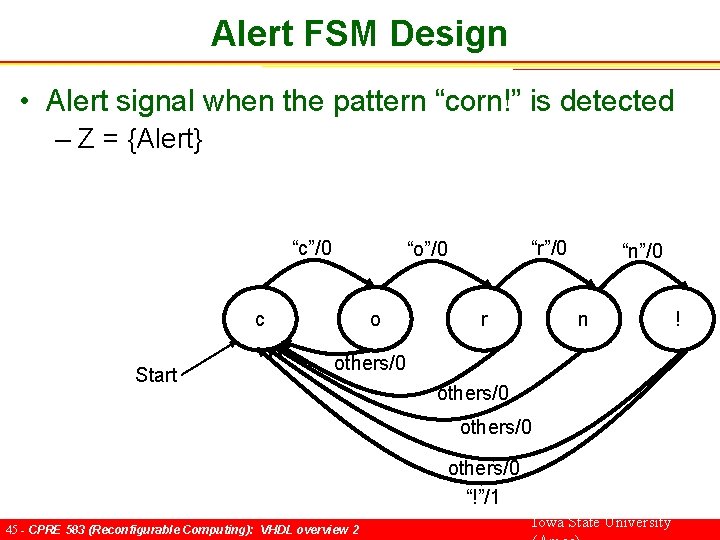

Alert FSM Design • Alert signal when the pattern “corn!” is detected – Z = {Alert} “c”/0 c Start “r”/0 “o”/0 o r “n”/0 n ! others/0 45 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 others/0 “!”/1 Iowa State University

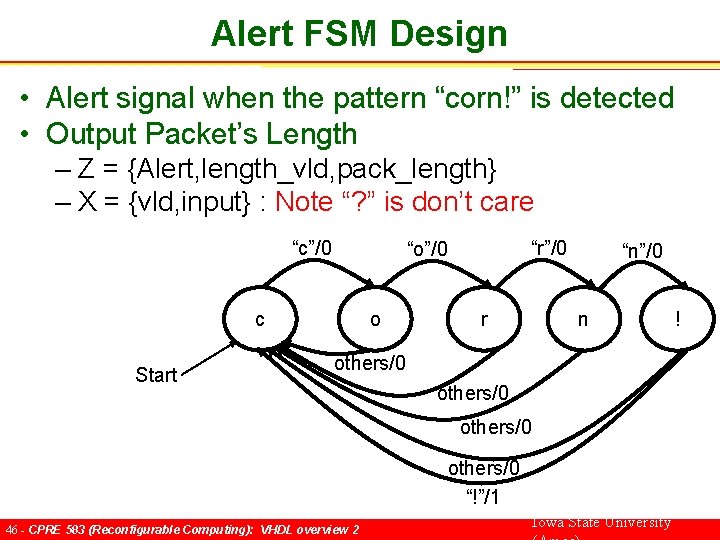

Alert FSM Design • Alert signal when the pattern “corn!” is detected • Output Packet’s Length – Z = {Alert, length_vld, pack_length} – X = {vld, input} : Note “? ” is don’t care “c”/0 c Start “r”/0 “o”/0 o r “n”/0 n ! others/0 46 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 others/0 “!”/1 Iowa State University

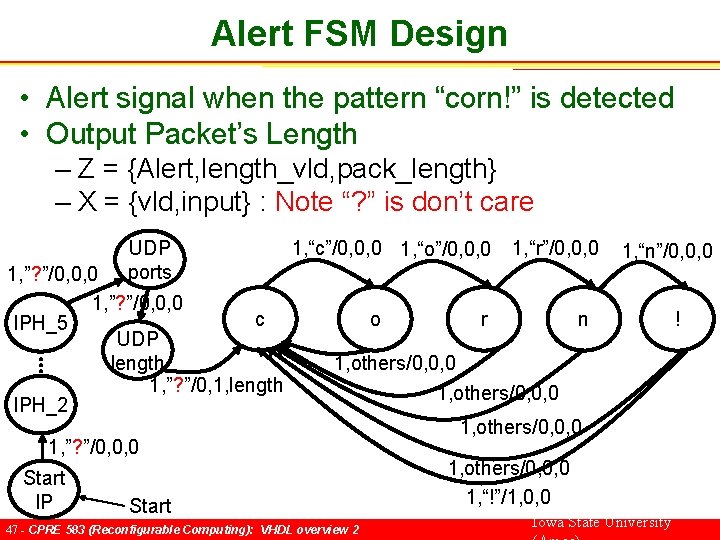

Alert FSM Design • Alert signal when the pattern “corn!” is detected • Output Packet’s Length – Z = {Alert, length_vld, pack_length} – X = {vld, input} : Note “? ” is don’t care UDP ports 1, ”? ”/0, 0, 0 c IPH_5 UDP length 1, ”? ”/0, 1, length IPH_2 1, “c”/0, 0, 0 1, “o”/0, 0, 0 o r n 1, “n”/0, 0, 0 ! 1, others/0, 0, 0 1, ”? ”/0, 0, 0 Start IP 1, “r”/0, 0, 0 Start 47 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 1, others/0, 0, 0 1, “!”/1, 0, 0 Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload Alert FSM Register & Counter Packet Length Management output sel position corn_cnt Packet Input Process 48 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

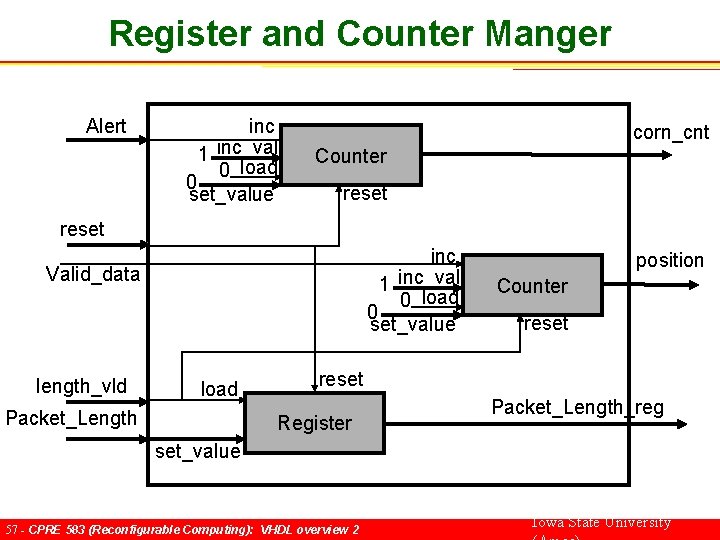

Register & Counter Manager • Register & Counter Components • Design of Manager 49 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

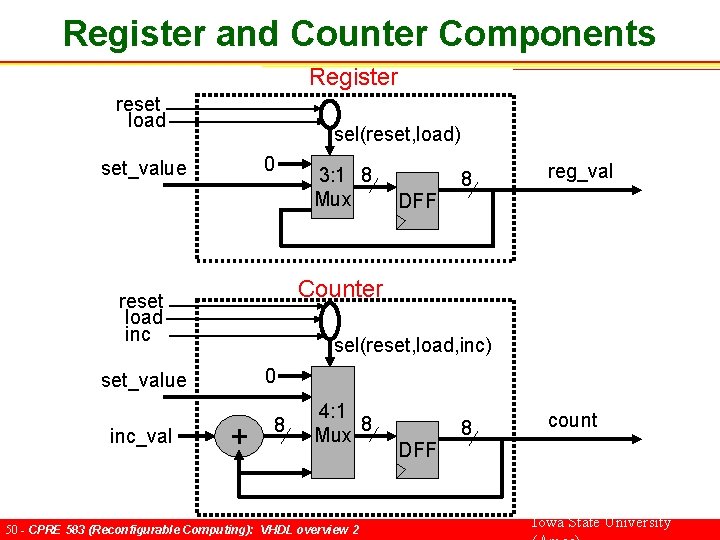

Register and Counter Components Register reset load sel(reset, load) 0 set_value DFF 8 reg_val Counter reset load inc sel(reset, load, inc) 0 set_value inc_val 3: 1 8 Mux + 8 4: 1 8 Mux 50 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 DFF 8 count Iowa State University

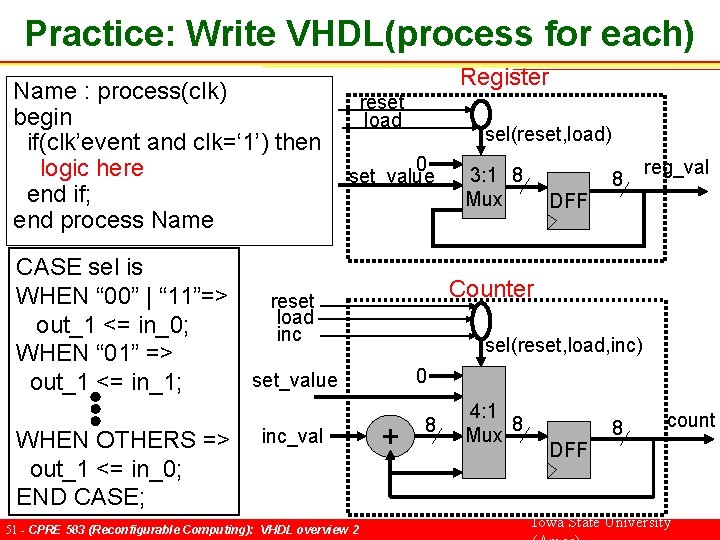

Practice: Write VHDL(process for each) Name : process(clk) begin if(clk’event and clk=‘ 1’) then logic here end if; end process Name Register reset load 0 set_value CASE sel is WHEN “ 00” | “ 11”=> reset load out_1 <= in_0; inc WHEN “ 01” => set_value out_1 <= in_1; WHEN OTHERS => out_1 <= in_0; END CASE; sel(reset, load) inc_val 51 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 3: 1 8 Mux DFF 8 reg_val Counter sel(reset, load, inc) 0 + 8 4: 1 8 Mux DFF 8 count Iowa State University

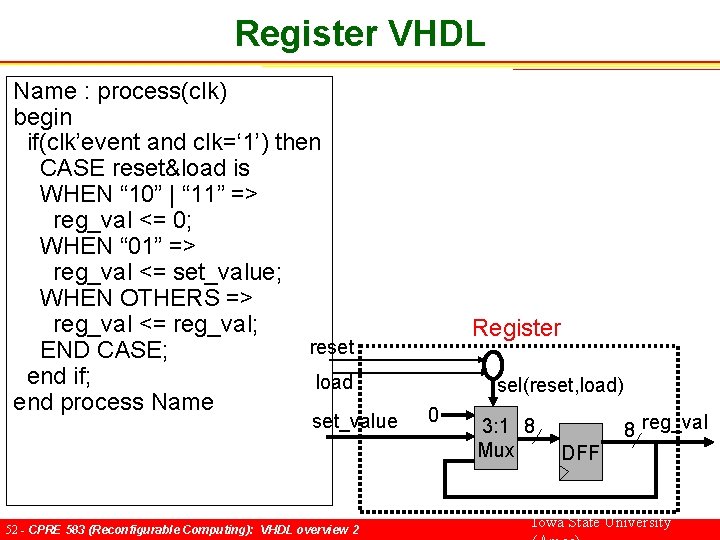

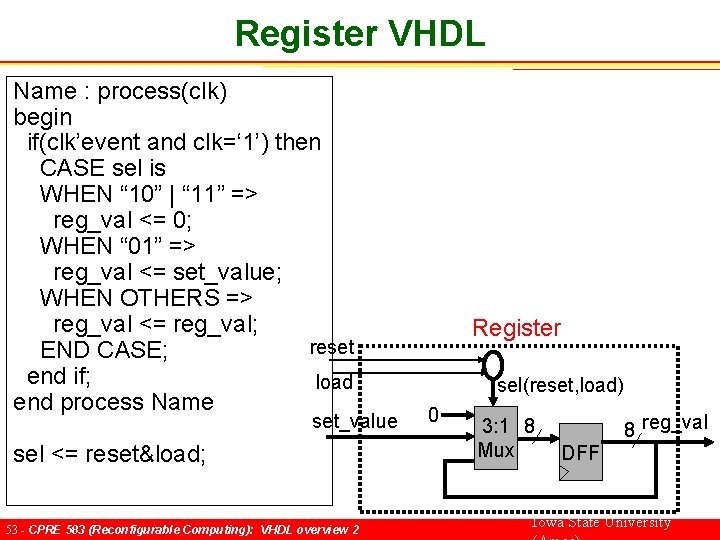

Register VHDL Name : process(clk) begin if(clk’event and clk=‘ 1’) then CASE reset&load is WHEN “ 10” | “ 11” => reg_val <= 0; WHEN “ 01” => reg_val <= set_value; WHEN OTHERS => reg_val <= reg_val; reset END CASE; end if; load end process Name set_value 52 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Register sel(reset, load) 0 3: 1 8 Mux DFF 8 reg_val Iowa State University

Register VHDL Name : process(clk) begin if(clk’event and clk=‘ 1’) then CASE sel is WHEN “ 10” | “ 11” => reg_val <= 0; WHEN “ 01” => reg_val <= set_value; WHEN OTHERS => reg_val <= reg_val; reset END CASE; end if; load end process Name set_value sel <= reset&load; 53 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Register sel(reset, load) 0 3: 1 8 Mux DFF 8 reg_val Iowa State University

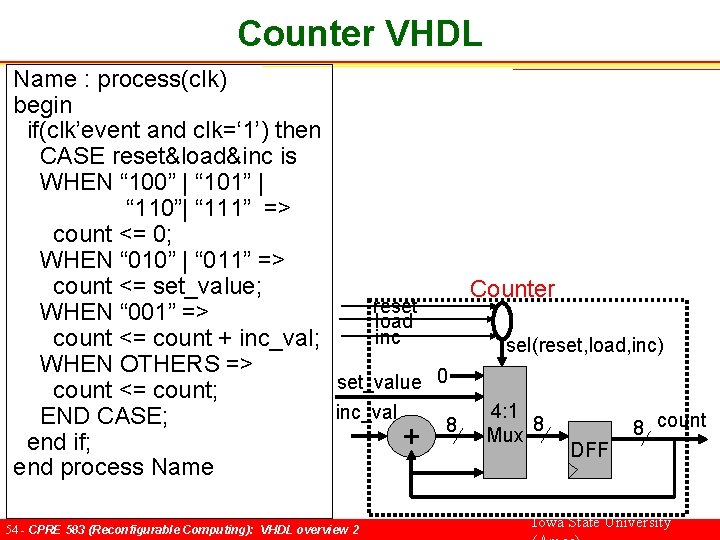

Counter VHDL Name : process(clk) begin if(clk’event and clk=‘ 1’) then CASE reset&load&inc is WHEN “ 100” | “ 101” | “ 110”| “ 111” => count <= 0; WHEN “ 010” | “ 011” => count <= set_value; Counter reset WHEN “ 001” => load inc count <= count + inc_val; sel(reset, load, inc) WHEN OTHERS => 0 set_value count <= count; 4: 1 inc_val END CASE; 8 Mux 8 8 count + end if; DFF end process Name 54 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

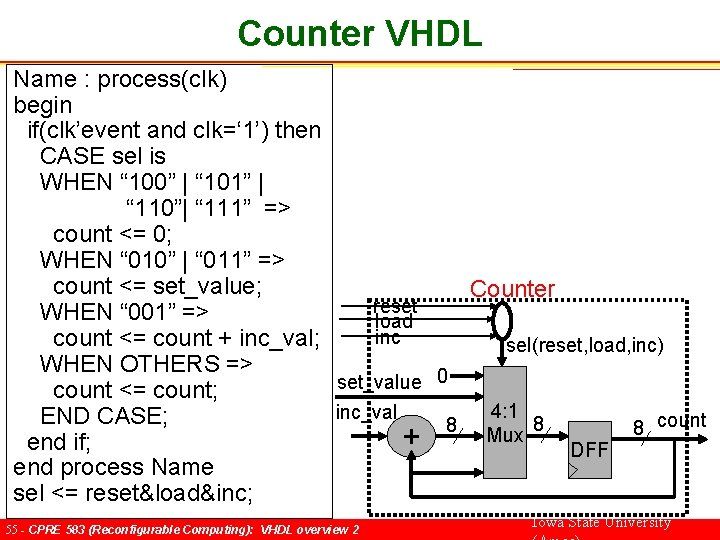

Counter VHDL Name : process(clk) begin if(clk’event and clk=‘ 1’) then CASE sel is WHEN “ 100” | “ 101” | “ 110”| “ 111” => count <= 0; WHEN “ 010” | “ 011” => count <= set_value; Counter reset WHEN “ 001” => load inc count <= count + inc_val; sel(reset, load, inc) WHEN OTHERS => 0 set_value count <= count; 4: 1 inc_val END CASE; 8 Mux 8 8 count + end if; DFF end process Name sel <= reset&load&inc; 55 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload reset Alert FSM Alert Packet Length length_vld Register & Counter Management reset position data_vld output sel Packet_length corn_cnt Packet Input Process 56 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

Register and Counter Manger Alert inc 1 inc_val 0 load 0 set_value corn_cnt Counter reset inc 1 inc_val 0 load 0 set_value Valid_data length_vld load Packet_Length position Counter reset Register Packet_Length_reg set_value 57 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload reset Alert FSM Alert Packet Length length_vld Register & Counter Management reset position data_vld output sel Packet_length corn_cnt Packet Input Process 58 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload reset Alert FSM Alert Packet Length length_vld Register & Counter Management reset position data_vld output sel Packet_length corn_cnt Packet Input Process 59 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

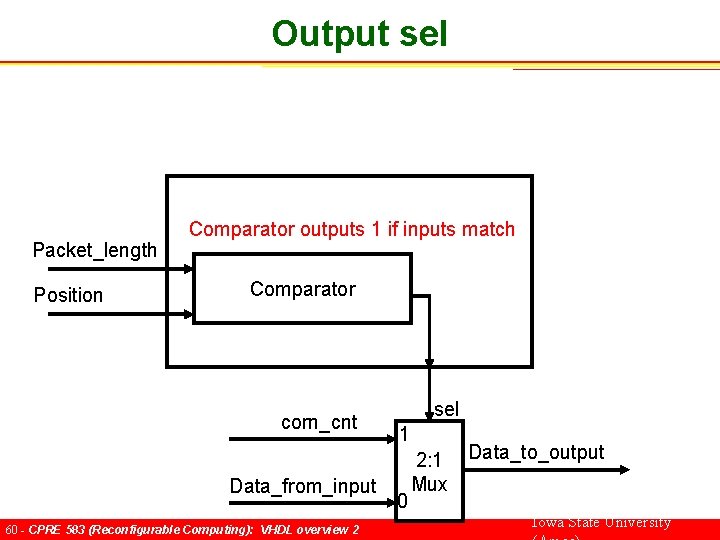

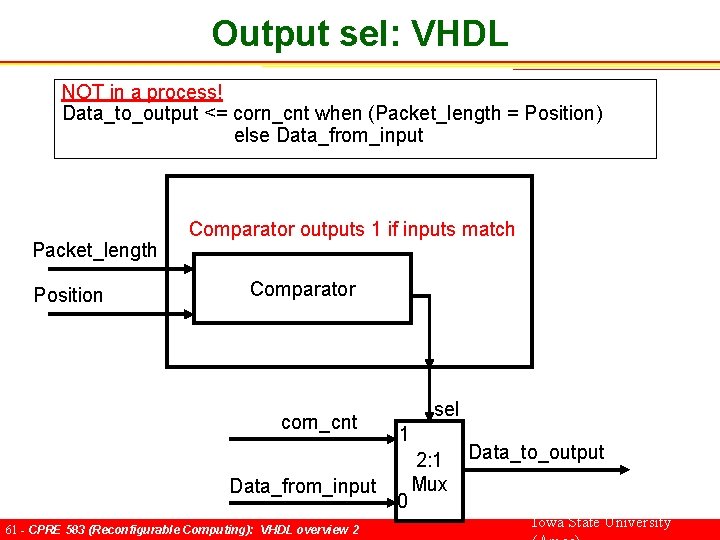

Output sel Packet_length Position Comparator outputs 1 if inputs match Comparator corn_cnt Data_from_input 60 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 sel 1 0 2: 1 Data_to_output Mux Iowa State University

Output sel: VHDL NOT in a process! Data_to_output <= corn_cnt when (Packet_length = Position) else Data_from_input Packet_length Position Comparator outputs 1 if inputs match Comparator corn_cnt Data_from_input 61 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 sel 1 0 2: 1 Data_to_output Mux Iowa State University

Architecture • Detect patterns in payload (e. g. “Corn!”) • Place the number of detections in last byte of payload reset Alert FSM Alert Packet Length length_vld Register & Counter Management reset position data_vld output sel Packet_length corn_cnt Packet Input Process 62 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 2: 1 Mux Packet Output Process Iowa State University

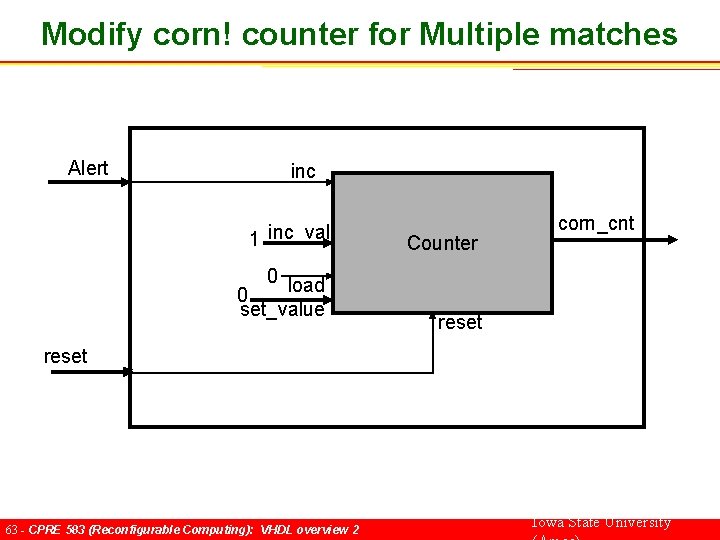

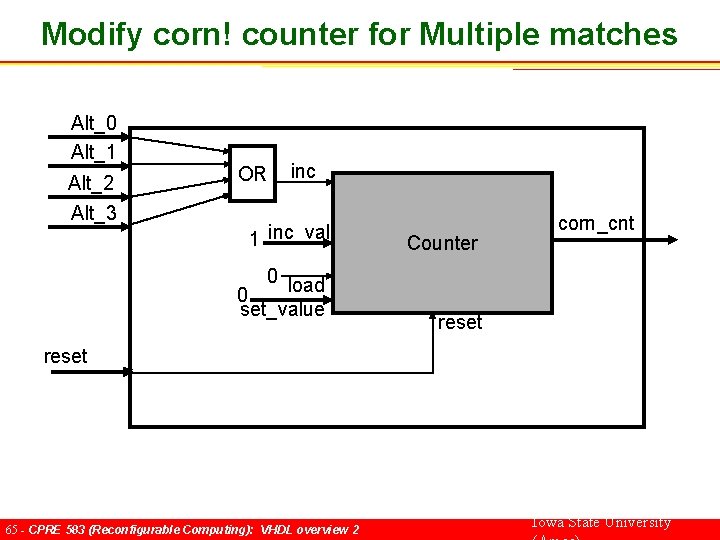

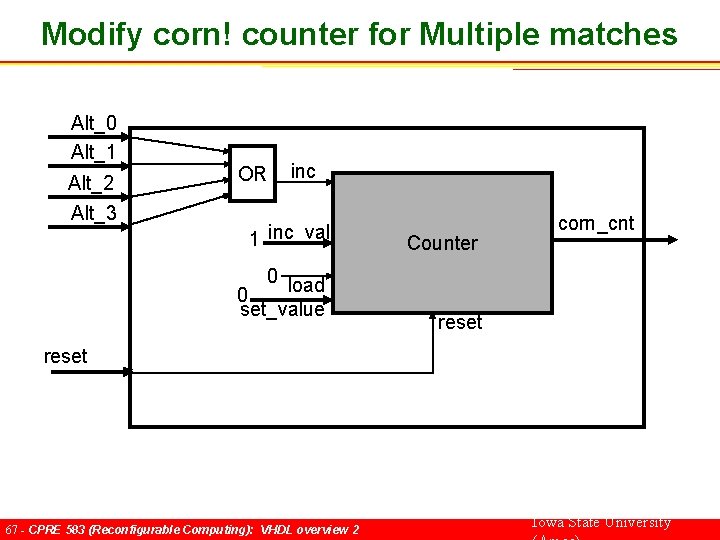

Modify corn! counter for Multiple matches Alert inc 1 inc_val 0 load 0 set_value Counter corn_cnt reset 63 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

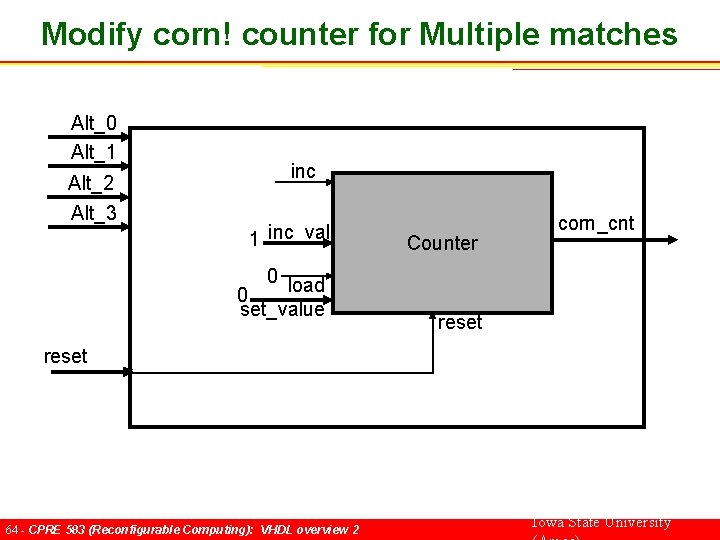

Modify corn! counter for Multiple matches Alt_0 Alt_1 Alt_2 Alt_3 inc 1 inc_val 0 load 0 set_value Counter corn_cnt reset 64 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Modify corn! counter for Multiple matches Alt_0 Alt_1 Alt_2 Alt_3 OR inc 1 inc_val 0 load 0 set_value Counter corn_cnt reset 65 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Modify corn! counter for Multiple characters Alt_0 Alt_1 OR Alt_2 Alt_3 1 2 3 4 sel(Alt 0, Alt 1, Alt 2, Alt 3) 4: 1 Mux inc_val 0 load 0 set_value Counter corn_cnt reset NOT in a process! Alt_merge <= Alt 0 & Alt 1 & Alt 2 & Alt 3; inc_val <= 4 when (Alt_merge = “ 1111”) 3 when (Alt_merge = “ 0111” or Alt_merge = “ 1011”. . . ) 2 when (Alt_merge = “ 0011” or Alt_merge = “ 0110”. . . ) else 0 66 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Modify corn! counter for Multiple matches Alt_0 Alt_1 Alt_2 Alt_3 OR inc 1 inc_val 0 load 0 set_value Counter corn_cnt reset 67 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

State Machine design next Friday 68 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

Questions/Comments/Concerns 69 - CPRE 583 (Reconfigurable Computing): VHDL overview 2 Iowa State University

- Slides: 69