CPRE 583 Reconfigurable Computing Lecture 7 9152010 Common

CPRE 583 Reconfigurable Computing Lecture 7: 9/15/2010 (Common VHDL Mistakes: “It works perfect in simulation, but not in the hardware!” ) Instructor: Dr. Phillip Jones (phjones@iastate. edu) Reconfigurable Computing Laboratory Iowa State University Ames, Iowa, USA http: //class. ece. iastate. edu/cpre 583/ 1 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Announcements/Reminders • MP 1/HW 1 Due midnight tonight • MP 2: Make sure to get started by Thursday (tomorrow • HW 2: Delayed Thur/Fri release, due date will be appropriated adjusted. • Mini literary survey – Power. Point tree due: Fri 9/17 by class, so try to have to me by 9/16 night. My current plan is to summarize some of the classes findings during class. – Final 5 -10 page write up on your tree due: Fri 9/24 midnight. 2 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Literary Survey • Start with searching for papers from 2007 -2010 on IEEE Xplorer: http: //ieeexplore. ieee. org/ – Advanced Search (Full Text & Meta data) • Find popular cross references for each area • For each area try to identify 1 good survey papers • For each area – Identify 2 -3 core Problems/issues – For each problem identify 2 -3 Approaches for addressing – For each approach identify 1 -2 papers that Implement the approach. 3 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

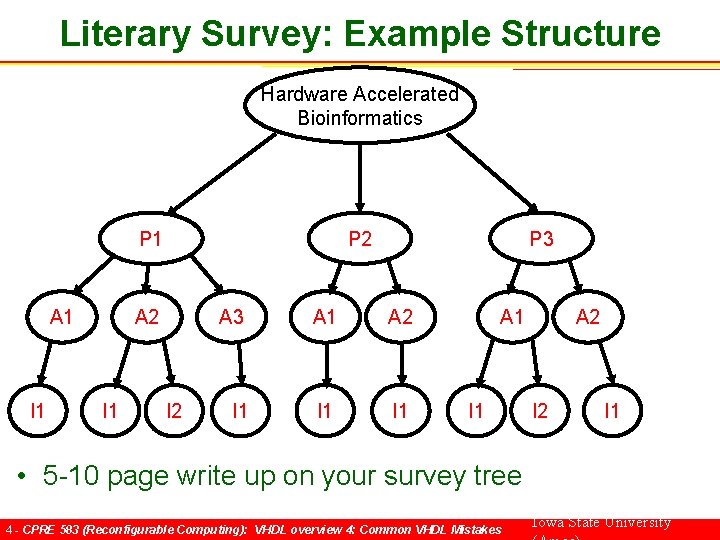

Literary Survey: Example Structure Hardware Accelerated Bioinformatics P 2 P 1 A 1 I 1 A 2 I 1 I 2 P 3 A 1 A 2 I 1 I 1 A 2 I 1 • 5 -10 page write up on your survey tree 4 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Questions 5 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Questions 6 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

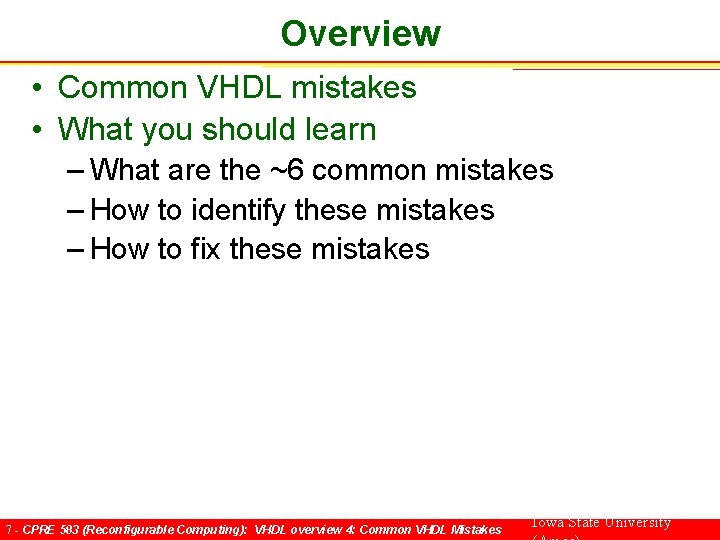

Overview • Common VHDL mistakes • What you should learn – What are the ~6 common mistakes – How to identify these mistakes – How to fix these mistakes 7 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

My design works in simulation, but not in hardware!! • Clocked and non-clock processes common issues. • Clean Statemachine design, using best know practices • Common Mistakes pdf document 8 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

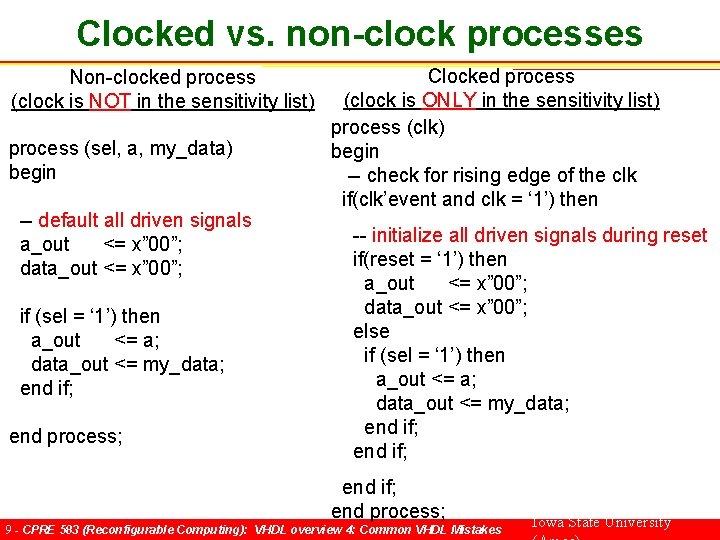

Clocked vs. non-clock processes Non-clocked process (clock is NOT in the sensitivity list) process (sel, a, my_data) begin -- default all driven signals a_out <= x” 00”; data_out <= x” 00”; if (sel = ‘ 1’) then a_out <= a; data_out <= my_data; end if; end process; Clocked process (clock is ONLY in the sensitivity list) process (clk) begin -- check for rising edge of the clk if(clk’event and clk = ‘ 1’) then -- initialize all driven signals during reset if(reset = ‘ 1’) then a_out <= x” 00”; data_out <= x” 00”; else if (sel = ‘ 1’) then a_out <= a; data_out <= my_data; end if; end process; 9 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

State Machine Structure -- Assign STATE to next state process (clk) begin -- check for rising edge of the clk if(clk’event and clk = ‘ 1’) then -- initialize all driven signals during reset if(reset = ‘ 1’) then STATE <= S 1; else STATE <= Next_STATE; end if; end process; Has memory (e. g. flip-flops) No memory!!!! -- Compute next state process (STATE, x) begin -- defaults next_state <= STATE; case STATE is when S 1 => if(x = ‘ 0’) then Next_STATE <= S 1; else Next_STATE <= S 2; end if; when S 2 => Next_State <= S 1; end if; end process; 10 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

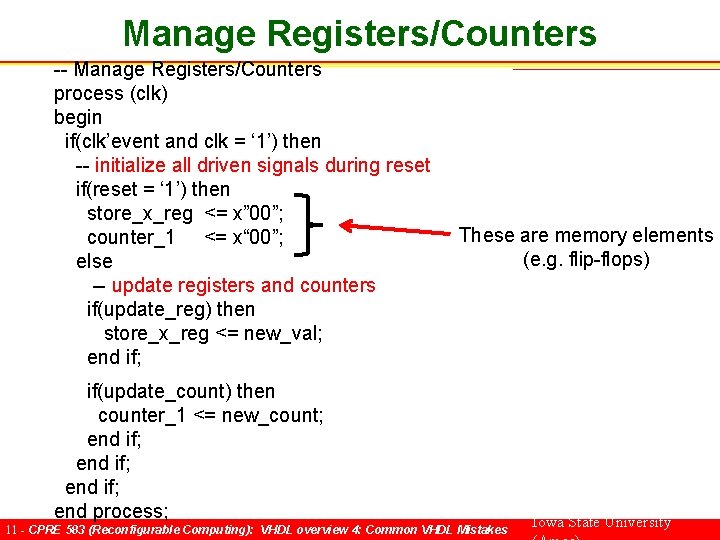

Manage Registers/Counters -- Manage Registers/Counters process (clk) begin if(clk’event and clk = ‘ 1’) then -- initialize all driven signals during reset if(reset = ‘ 1’) then store_x_reg <= x” 00”; counter_1 <= x“ 00”; else -- update registers and counters if(update_reg) then store_x_reg <= new_val; end if; These are memory elements (e. g. flip-flops) if(update_count) then counter_1 <= new_count; end if; end process; 11 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Good papers on state machine design – FSM “good practices” paper (Note: in. Verilog) – http: //www. sunburst-design. com/papers/ • The Fundamentals of Efficient Synthesizable Finite State Machine (2002) • Synthesizable Finite State Machine Design Techniques (2003) 12 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

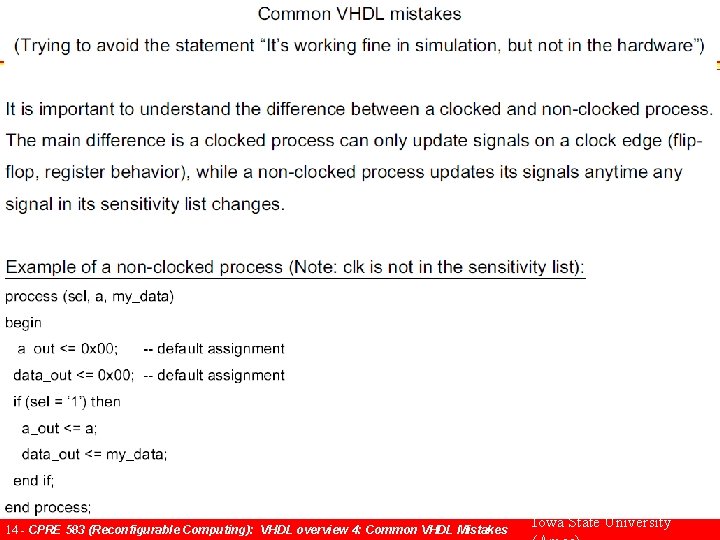

Common Mistakes in more detail – See Common VHDL mistakes pdf on course web 13 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Mistakes in more detail 14 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

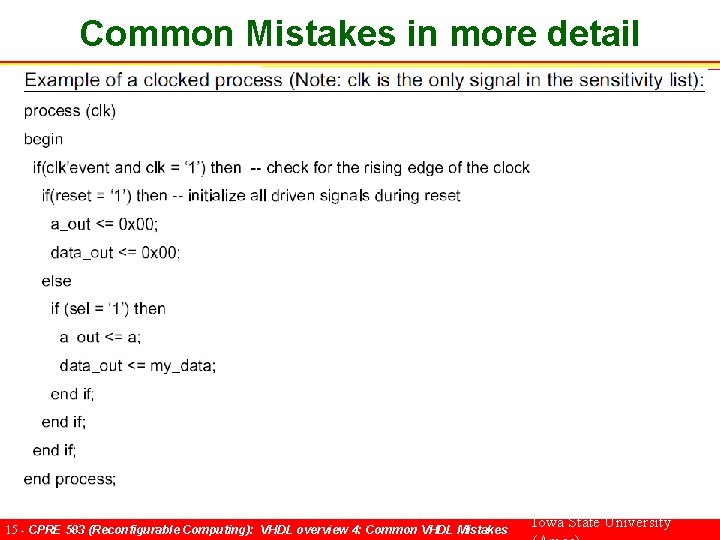

Common Mistakes in more detail 15 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

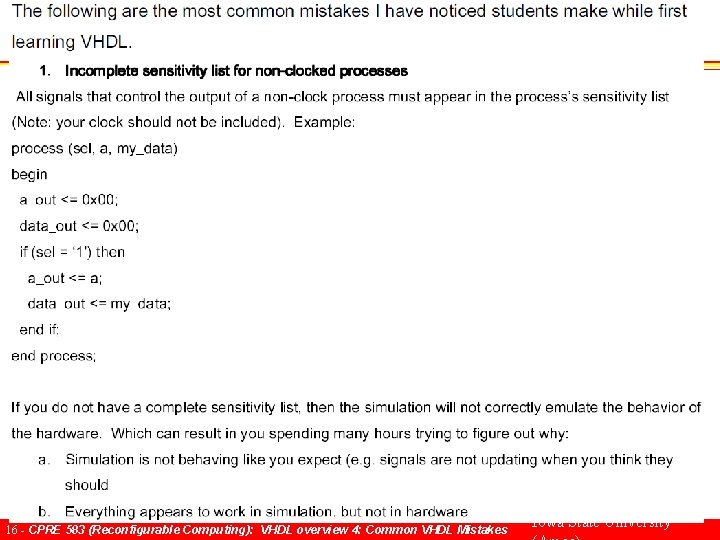

Common Mistakes in more detail 16 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Mistakes in more detail 17 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Mistakes in more detail 18 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

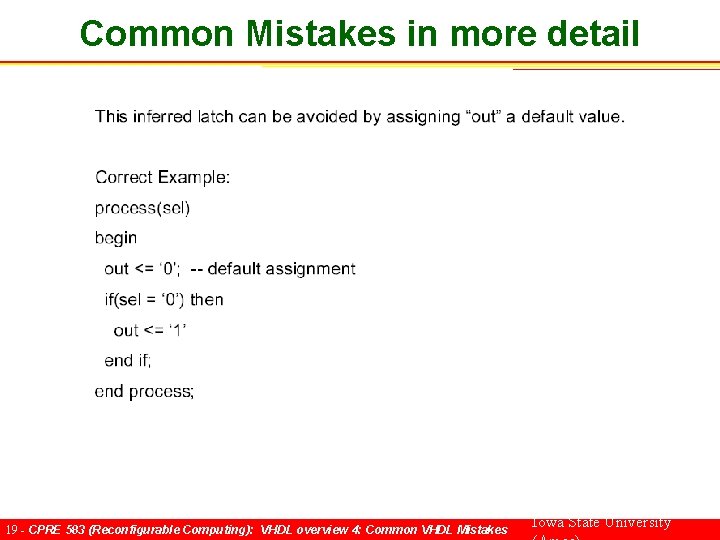

Common Mistakes in more detail 19 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Mistakes in more detail 20 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

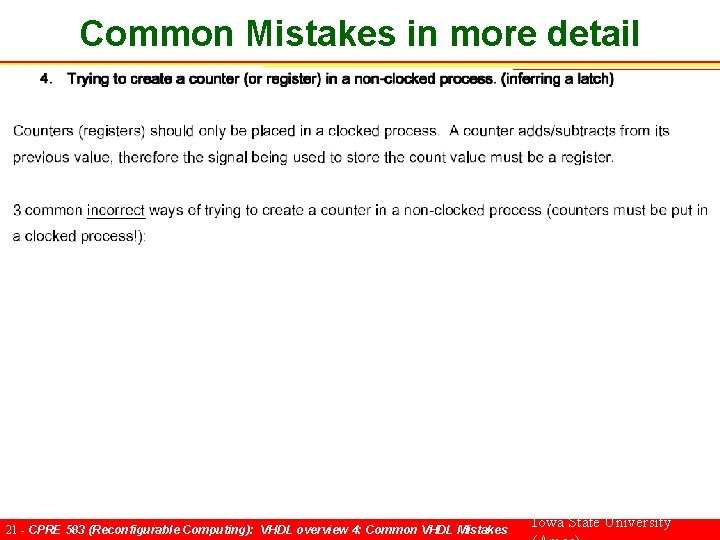

Common Mistakes in more detail 21 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

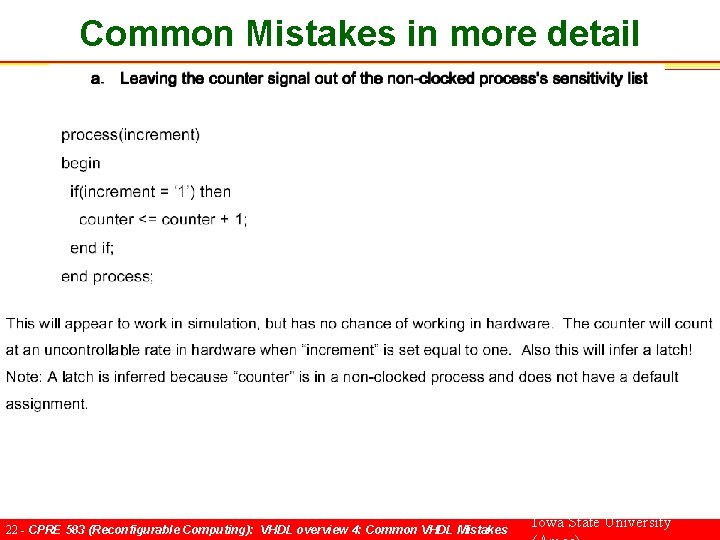

Common Mistakes in more detail 22 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

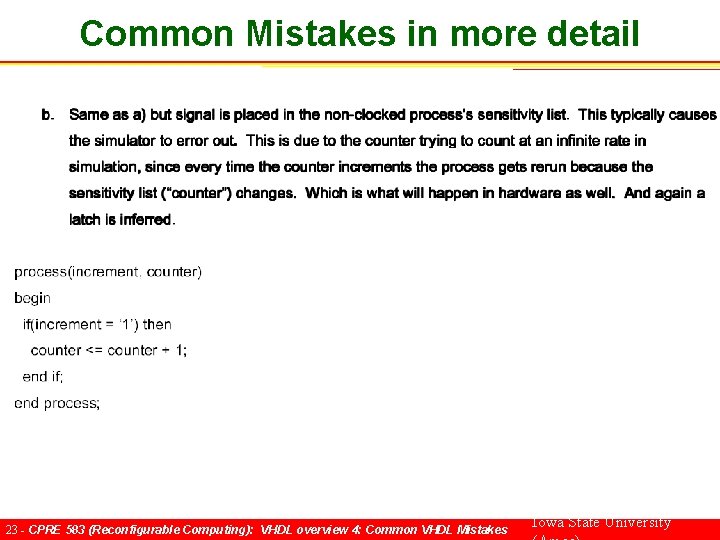

Common Mistakes in more detail 23 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

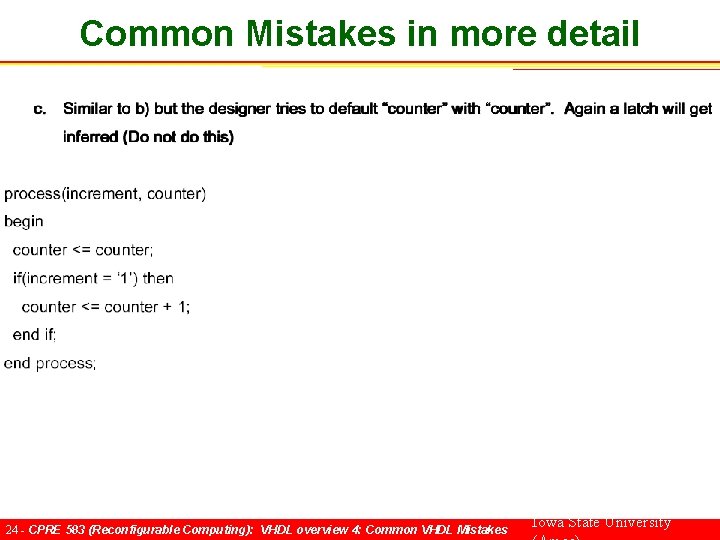

Common Mistakes in more detail 24 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

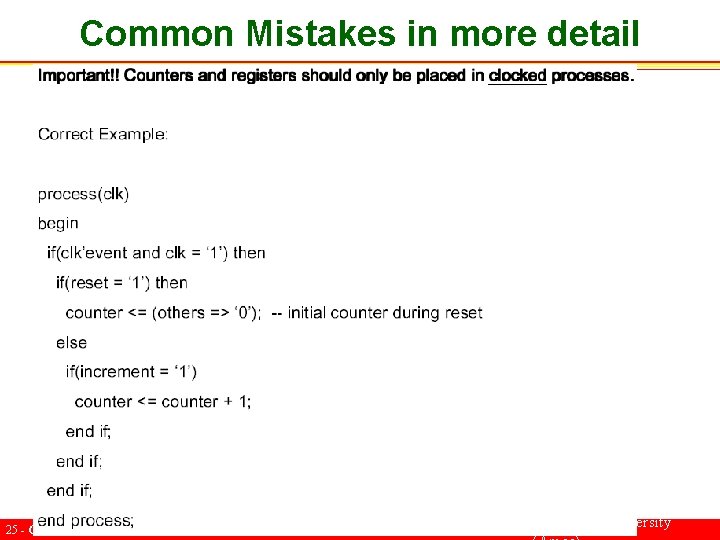

Common Mistakes in more detail 25 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Common Mistakes in more detail 26 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

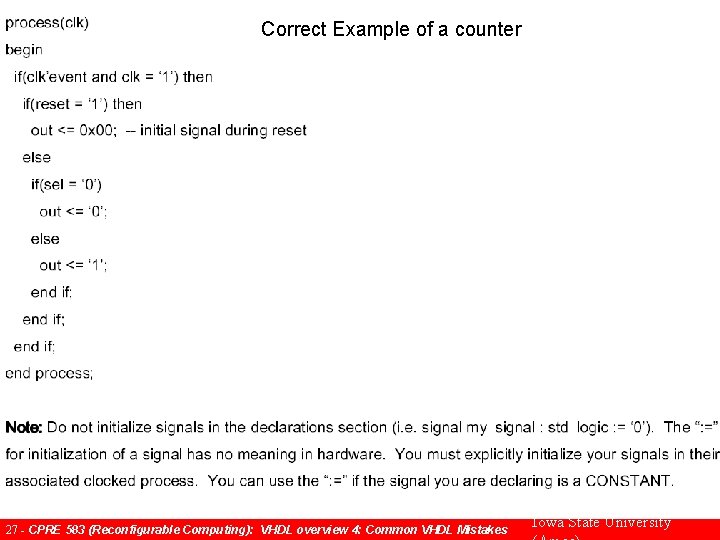

Correct Example of a counter Common Mistakes in more detail 27 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

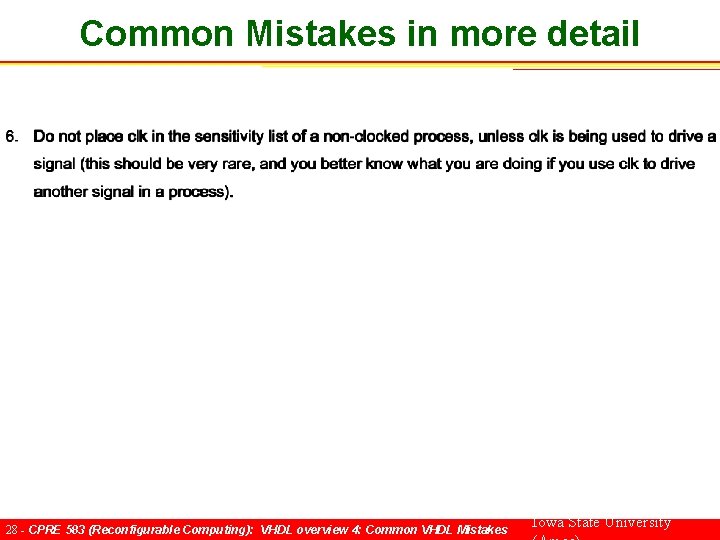

Common Mistakes in more detail 28 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

MP 2 overview 29 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

MP 2 overview 30 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

MP 2 overview 31 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

MP 2 overview 32 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

MP 2 overview 33 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Next Class • VHDL -> FPGA, or • Short History of Reconfigurable computing 34 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

Questions/Comments/Concerns 35 - CPRE 583 (Reconfigurable Computing): VHDL overview 4: Common VHDL Mistakes Iowa State University

- Slides: 35