CPRE 583 Reconfigurable Computing Lecture 9 Wed 922009

CPRE 583 Reconfigurable Computing Lecture 9: Wed 9/2/2009 (Reconfigurable Computing Systems: History) Instructor: Dr. Phillip Jones (phjones@iastate. edu) Reconfigurable Computing Laboratory Iowa State University Ames, Iowa, USA http: //class. ee. iastate. edu/cpre 583/ 1 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Announcements/Reminders • HW 2: will be released today • MP 2: You should have started (you can work in pairs) – Make sure to read the README file in the MP 2 distribution • Contains info on how to fix a Gigabit core licensing issue ISE has • Mini literary survey – Final 5 -10 page write up on your tree & tree due: Fri 9/24 midnight. • Should tell the story of your literary tree 2 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Literary Survey • Start with searching for papers from 2007 -2010 on IEEE Xplorer: http: //ieeexplore. ieee. org/ – Advanced Search (Full Text & Meta data) • Find popular cross references for each area • For each area try to identify 1 good survey papers • For each area – Identify 2 -3 core Problems/issues – For each problem identify 2 -3 Approaches for addressing – For each approach identify 1 -2 papers that Implement the approach. 3 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

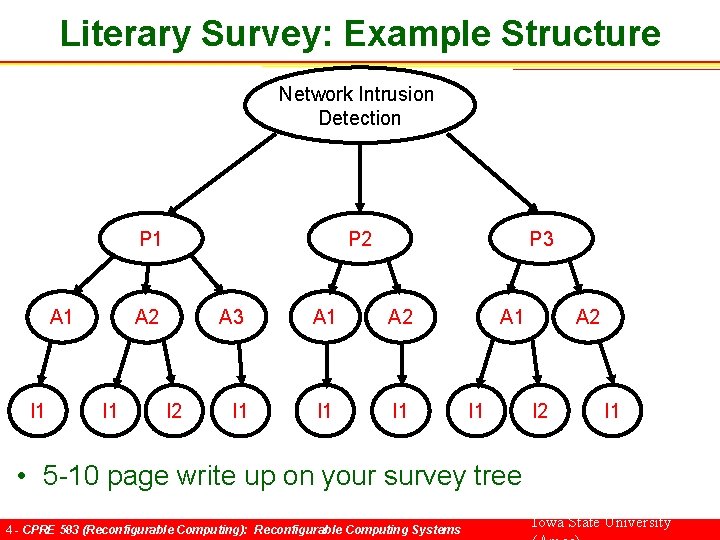

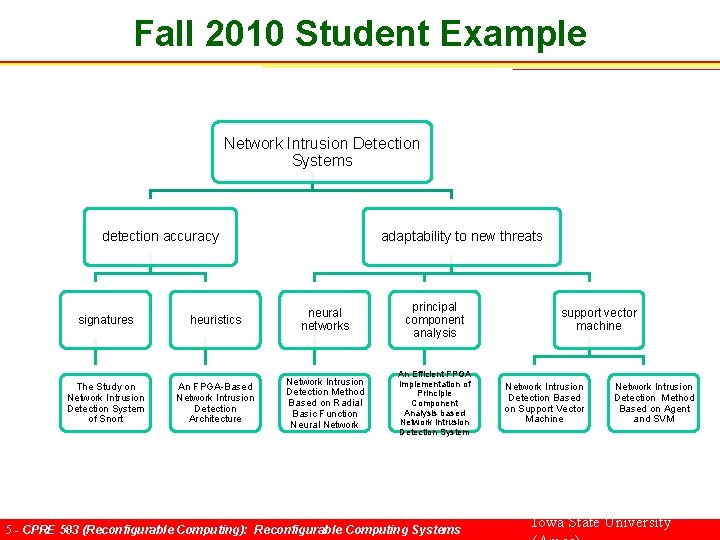

Literary Survey: Example Structure Network Intrusion Detection P 2 P 1 A 1 I 1 A 2 I 1 I 2 P 3 A 1 A 2 I 1 I 1 A 2 I 1 • 5 -10 page write up on your survey tree 4 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Fall 2010 Student Example Network Intrusion Detection Systems detection accuracy adaptability to new threats signatures heuristics neural networks principal component analysis The Study on Network Intrusion Detection System of Snort An FPGA-Based Network Intrusion Detection Architecture Network Intrusion Detection Method Based on Radial Basic Function Neural Network An Efficient FPGA Implementation of Principle Component Analysis based Network Intrusion Detection System 5 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems support vector machine Network Intrusion Detection Based on Support Vector Machine Network Intrusion Detection Method Based on Agent and SVM Iowa State University

Overview • Chapter 3 of text 6 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

What you should learn • Basic history and some applications of Reconfigurable Computing Systems 7 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Reconfigurable Computing System (RCS) • Examples of Characteristics – – – Composed of reconfigurable devices Devices are reprogrammed Give hardware-level of performance Give orders of Magnitude speed up over standard CPUs Can perform a range of applications Spatially Reprogrammed (Heterogeneous Computing) • Great talk about the benefits of Heterogeneous Computing • http: //video. google. com/videoplay? docid=-4969729965240981475# • SIMD (Single Instruction Multiple Data) not a RCS – A key difference typical all units are homogenous, and follow instructions from a central issuing unit 8 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Early Systems • 1960’s: Fixed-Plus-Variable (F+V) – University of California Los Angeles (UCLA) – “Reconfigurable Computer Origins: The UCLA Fixed-Plus-Variable (F+V) Structure Computer”, 2002, IEEE Annals of the History of Computing. • 1980’s: (low logic density devices) – Xilinx, Altera, Atmel, Actel • FPGA devices used as interface glue logic • 10 K gates only!! – Host Processor + Multiple FPGAs • Programmable Active Memories (PAM): 25 FPGAs • Virtual Computer Corporation (VCC): ~48 FPGAs • Splash: ~32 FPGAs (Cryptology, Pattern Matching) 9 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

More Modern Systems • 1990’s: Increasing logic densities – PRISM: Brown University • One of the first uses of a FPGA as a true coprocessor / off loading functional unit – CAL (Configurable Logic Array) and XC 6200 • CAL developed by Algotronix • XC 6200 developed by Xilinx based off CAL after acquiring Algotronix – Dynamic (run-time) Partial Reconfiguration!!! 10 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Circuit Emulation • The use of FPGAs to emulate ASICs (Application Specific Integrated Circuits), e. g. Xeon/Optiron Processors. Example platforms – Pi. E – Quick. Turn – In. CA • Why – Bugs in a large processor is expensive!!! – Simulation slow (days -> weeks to run 1 ms) – Early testing of SW (e. g. boot Windows in one day) 11 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Circuit Emulation • Virtual Wires (Work at M. I. T) 12 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Accelerating Technology (Mid-Late 1990’s) • FPGAs more generally used, Why? – Increased logic density (single device systems) – Increasing the performance of standard CPUs becoming more difficult. • Memory Bandwidth issues • Power/Thermal issues – Adaptive Computing Systems (ACS) • ~$100 million invested by the department of defense for research over a 5 year period • Perhaps motivated England Japan to push research 13 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Accelerating Technology (Mid-Late 1990’s) • New trends – Single FPGA devices on standard interface boards (e. g. PCI) – Many low coast platforms emerged (10’ -100’s) • Issue: No standard tools for programming – SW/HW codesign not cleanly supported • Tool chain for developing HW (from vendor) • Tool chain for developing SW (more standard, e. g. gcc) • No clean way to bring the HW and SW design process together – Still an on going open research issue today 14 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Reconfigurable Supercomputing (2000’s) • A typical architecture composed of many commercial CPUs each paired with a large FPGA • Produced by major supercomputing players – Cray: 100’s of processing nodes (XD 1) – SRC: – Silicon Graphics: • Reconfigurable Application Specific Processor (RASP) • Newer supercomputing players: Motherboard FPGA/CPU (Personal Supercomputers) – – Xtreme. Data Nallatec DRC Convey 15 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Next Class • Accelerating Applications 16 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

Questions/Comments/Concerns • Write down – Main point of lecture – One thing that’s still not quite clear OR – If everything is clear, then give an example of how to apply something from lecture 17 - CPRE 583 (Reconfigurable Computing): Reconfigurable Computing Systems Iowa State University

- Slides: 17