CPRE 583 Reconfigurable Computing Lecture 18 Fri 10272010

CPRE 583 Reconfigurable Computing Lecture 18: Fri 10/27/2010 (Floating Point) Instructor: Dr. Phillip Jones (phjones@iastate. edu) Reconfigurable Computing Laboratory Iowa State University Ames, Iowa, USA http: //class. ee. iastate. edu/cpre 583/ 1 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Announcements/Reminders • Midterm: – Take home portion (40%) given Friday 10/29 (released today by 5 pm), due Tue 11/2 (midnight) – In class portion (60%) Wed 11/3 • Distance students will have in class portion given via a timed Web. CT (2 hour) session (take on Wed, Thur or Friday). • Problem 2 of HW 2 (released soon) 2 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Initial Project Proposal Slides (5 -10 slides) • Project team list: Name, Responsibility (who is project leader) – Team size: 3 -4 (5 case-by-case) • Project idea • Motivation (why is this interesting, useful) • What will be the end result • High-level picture of final product • High-level Plan – Break project into mile stones • Provide initial schedule: I would initially schedule aggressively to have project complete by Thanksgiving. Issues will pop up to cause the schedule to slip. – System block diagrams – High-level algorithms (if any) – Concerns • Implementation • Conceptual • Research papers related to you project idea 3 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Projects Ideas: Relevant conferences • • • FPL FPT FCCM FPGA DAC ICCAD Reconfig RTSS RTAS ISCA • • Micro Super Computing HPCA IPDPS 4 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Initial Project Proposal Slides (5 -10 slides) • Project team list: Name, Responsibility (who is project leader) • Project idea • Motivation (why is this interesting, useful) • What will be the end result • High-level picture of final product • High-level Plan – Break project into mile stones • Provide initial schedule: I would initially schedule aggressively to have project complete by Thanksgiving. Issues will pop up to cause the schedule to slip. – System block diagrams – High-level algorithms (if any) – Concerns • Implementation • Conceptual • Research papers related to you project idea 5 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Weekly Project Updates • The current state of your project write up – Even in the early stages of the project you should be able to write a rough draft of the Introduction and Motivation section • The current state of your Final Presentation – Your Initial Project proposal presentation (Due Fri 10/22). Should make for a starting point for you Final presentation • What things are work & not working • What roadblocks are you running into 6 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Projects: Target Timeline • Teams Formed and Idea: Mon 10/11 – Project idea in Power Point 3 -5 slides • Motivation (why is this interesting, useful) • What will be the end result • High-level picture of final product – Project team list: Name, Responsibility • High-level Plan/Proposal: Fri 10/22 – Power Point 5 -10 slides • System block diagrams • High-level algorithms (if any) • Concerns – Implementation – Conceptual • Related research papers (if any) 7 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Projects: Target Timeline • Work on projects: 10/22 - 12/8 – Weekly update reports • More information on updates will be given • Presentations: Last Wed/Fri of class – Present / Demo what is done at this point – 15 -20 minutes (depends on number of projects) • Final write up and Software/Hardware turned in: Day of final (TBD) 8 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Project Grading Breakdown • 50% Final Project Demo • 30% Final Project Report – 30% of your project report grade will come from your 5 -6 project updates. Friday’s midnight • 20% Final Project Presentation 9 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Common Questions 10 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Common Questions 11 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Overview • Floating Point on FPGAs (Chapter 21. 4 and 31) – Why is it viewed as difficult? ? – Options for mitigating issues 12 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

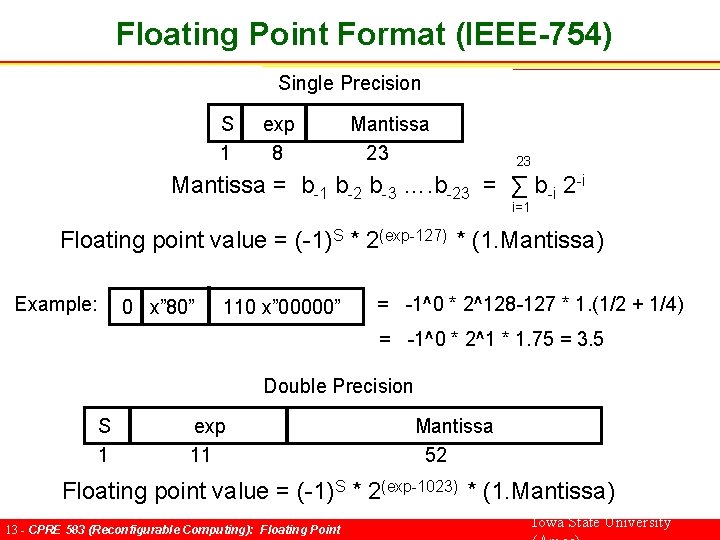

Floating Point Format (IEEE-754) Single Precision S 1 exp 8 Mantissa 23 23 Mantissa = b-1 b-2 b-3 …. b-23 = ∑ b-i 2 -i i=1 Floating point value = (-1)S * 2(exp-127) * (1. Mantissa) Example: 0 x” 80” 110 x” 00000” = -1^0 * 2^128 -127 * 1. (1/2 + 1/4) = -1^0 * 2^1 * 1. 75 = 3. 5 Double Precision S 1 exp 11 Mantissa 52 Floating point value = (-1)S * 2(exp-1023) * (1. Mantissa) 13 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

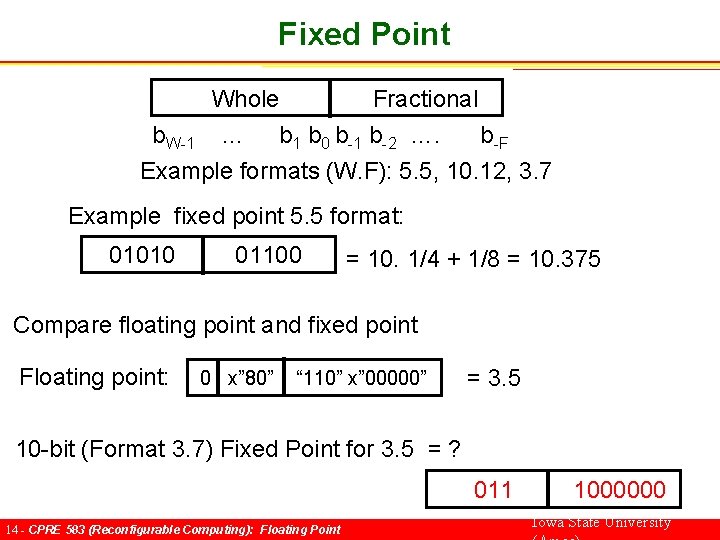

Fixed Point Whole b. W-1 … Fractional b 1 b 0 b-1 b-2 …. b-F Example formats (W. F): 5. 5, 10. 12, 3. 7 Example fixed point 5. 5 format: 01010 01100 = 10. 1/4 + 1/8 = 10. 375 Compare floating point and fixed point Floating point: 0 x” 80” “ 110” x” 00000” = 3. 5 10 -bit (Format 3. 7) Fixed Point for 3. 5 = ? 011 14 - CPRE 583 (Reconfigurable Computing): Floating Point 1000000 Iowa State University

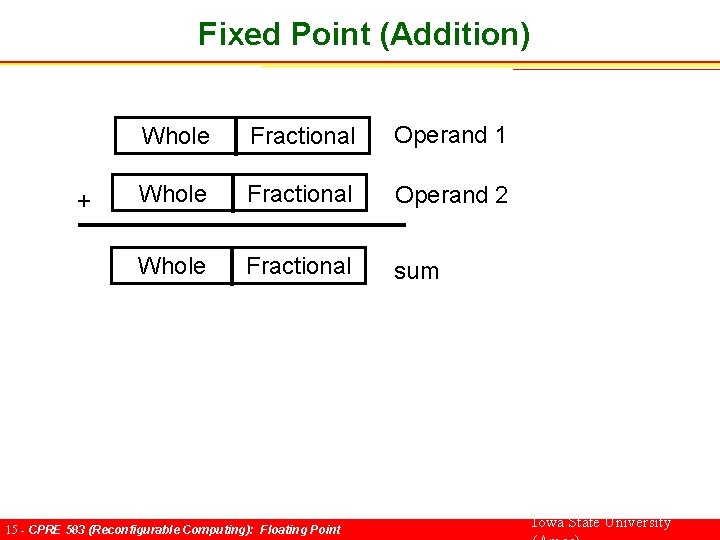

Fixed Point (Addition) + Whole Fractional Operand 1 Whole Fractional Operand 2 Whole Fractional sum 15 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

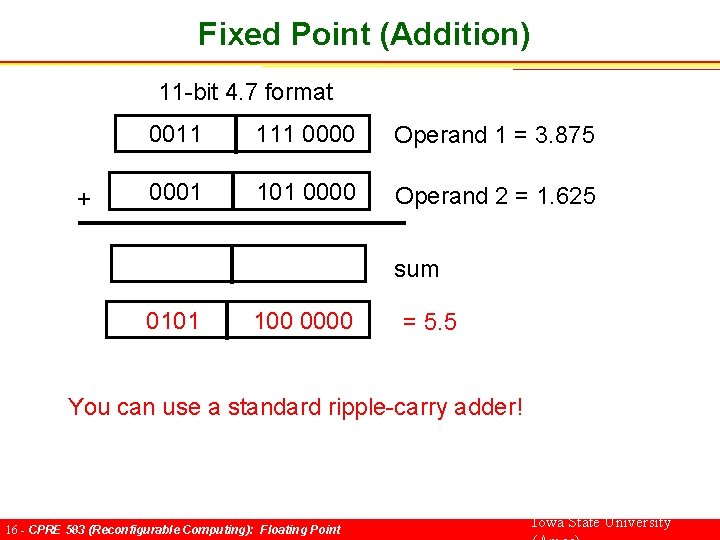

Fixed Point (Addition) 11 -bit 4. 7 format + 0011 111 0000 Operand 1 = 3. 875 0001 101 0000 Operand 2 = 1. 625 sum 0101 100 0000 = 5. 5 You can use a standard ripple-carry adder! 16 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

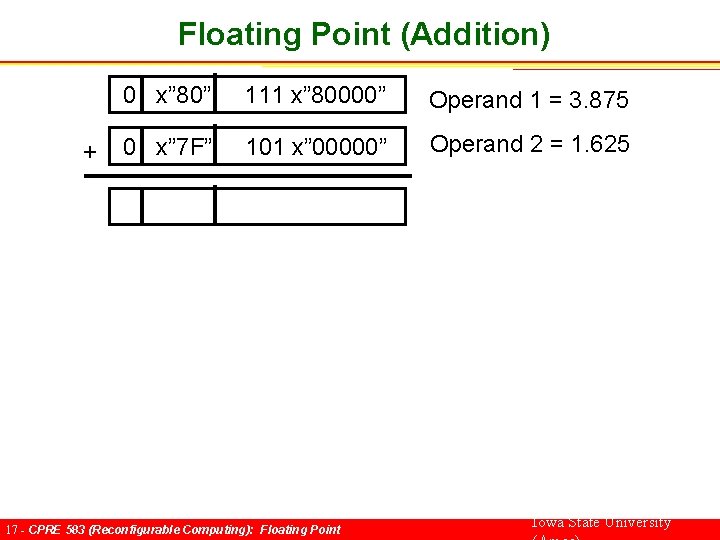

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 17 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

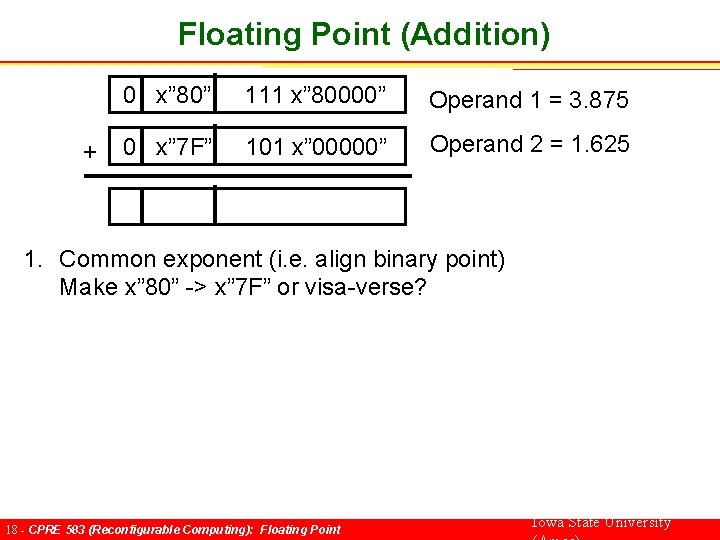

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 1. Common exponent (i. e. align binary point) Make x” 80” -> x” 7 F” or visa-verse? 18 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

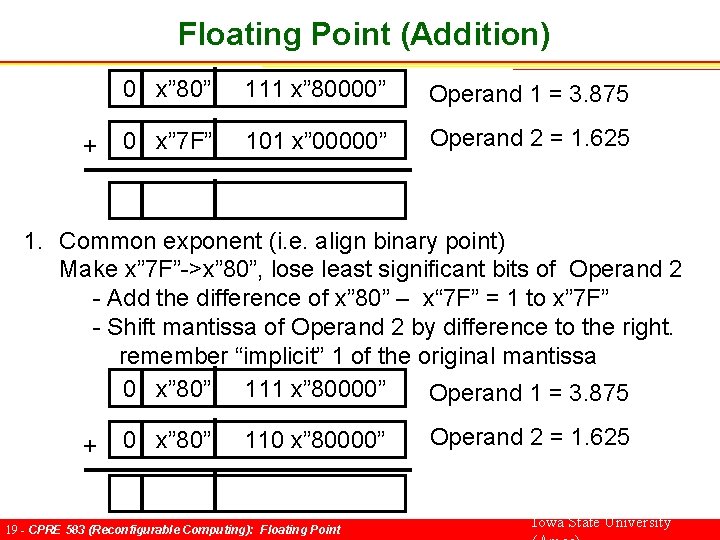

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 1. Common exponent (i. e. align binary point) Make x” 7 F”->x” 80”, lose least significant bits of Operand 2 - Add the difference of x” 80” – x“ 7 F” = 1 to x” 7 F” - Shift mantissa of Operand 2 by difference to the right. remember “implicit” 1 of the original mantissa 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 + 0 x” 80” 110 x” 80000” 19 - CPRE 583 (Reconfigurable Computing): Floating Point Operand 2 = 1. 625 Iowa State University

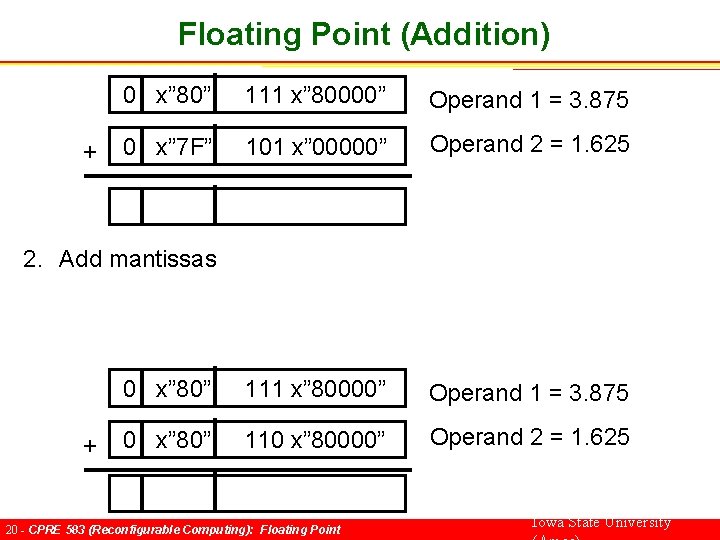

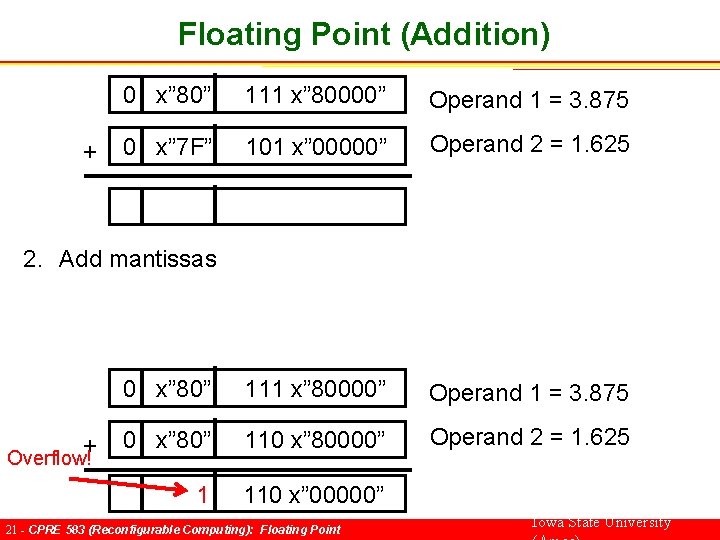

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 80” 110 x” 80000” Operand 2 = 1. 625 2. Add mantissas + 20 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

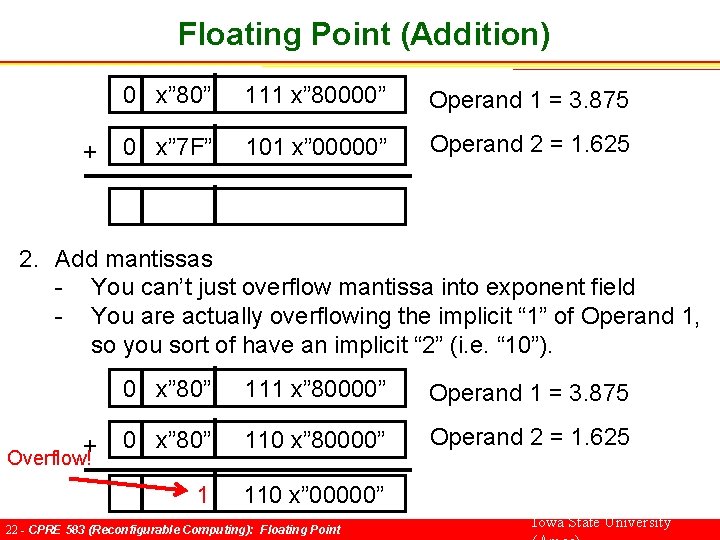

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 80” 110 x” 80000” Operand 2 = 1. 625 1 110 x” 00000” 2. Add mantissas + Overflow! 21 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 2. Add mantissas - You can’t just overflow mantissa into exponent field - You are actually overflowing the implicit “ 1” of Operand 1, so you sort of have an implicit “ 2” (i. e. “ 10”). + Overflow! 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 80” 110 x” 80000” Operand 2 = 1. 625 1 110 x” 00000” 22 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

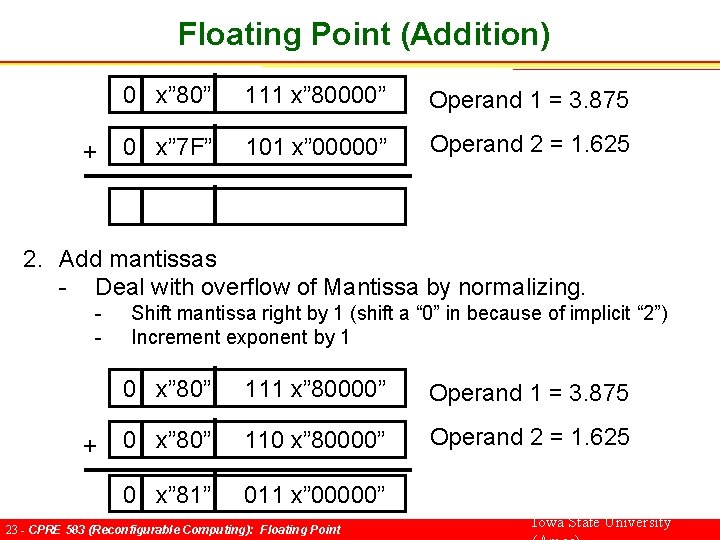

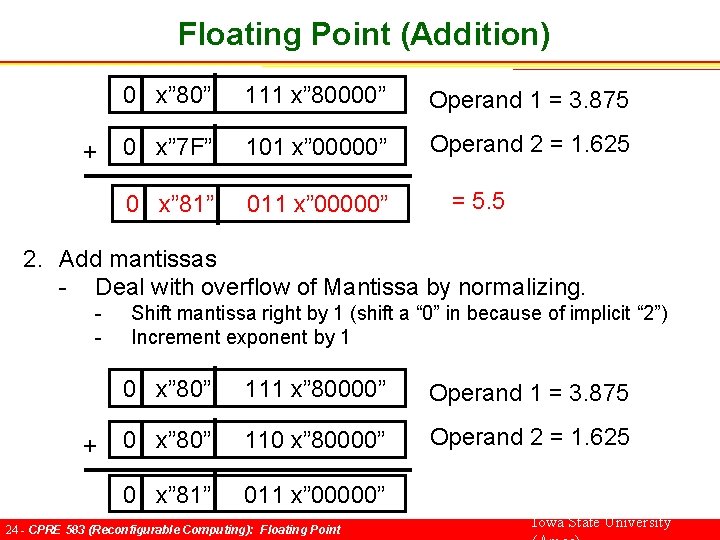

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 2. Add mantissas - Deal with overflow of Mantissa by normalizing. - + Shift mantissa right by 1 (shift a “ 0” in because of implicit “ 2”) Increment exponent by 1 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 80” 110 x” 80000” Operand 2 = 1. 625 0 x” 81” 011 x” 00000” 23 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Floating Point (Addition) + 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 7 F” 101 x” 00000” Operand 2 = 1. 625 0 x” 81” 011 x” 00000” = 5. 5 2. Add mantissas - Deal with overflow of Mantissa by normalizing. - + Shift mantissa right by 1 (shift a “ 0” in because of implicit “ 2”) Increment exponent by 1 0 x” 80” 111 x” 80000” Operand 1 = 3. 875 0 x” 80” 110 x” 80000” Operand 2 = 1. 625 0 x” 81” 011 x” 00000” 24 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

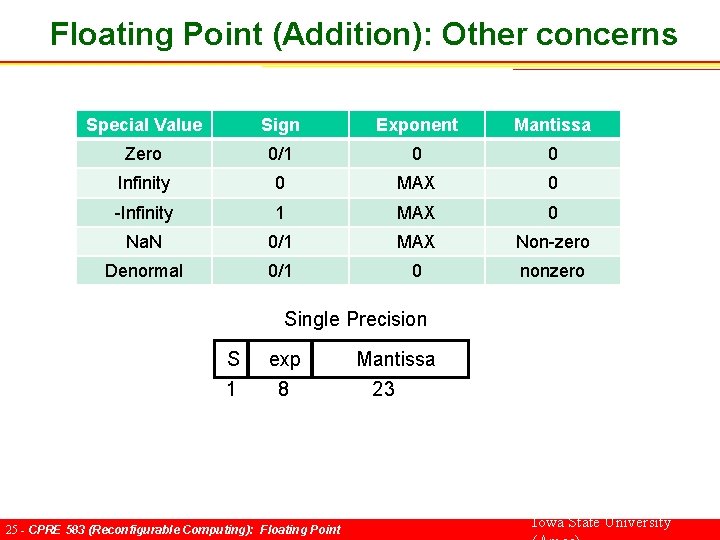

Floating Point (Addition): Other concerns Special Value Sign Exponent Mantissa Zero 0/1 0 0 Infinity 0 MAX 0 -Infinity 1 MAX 0 Na. N 0/1 MAX Non-zero Denormal 0/1 0 nonzero Single Precision S 1 exp 8 25 - CPRE 583 (Reconfigurable Computing): Floating Point Mantissa 23 Iowa State University

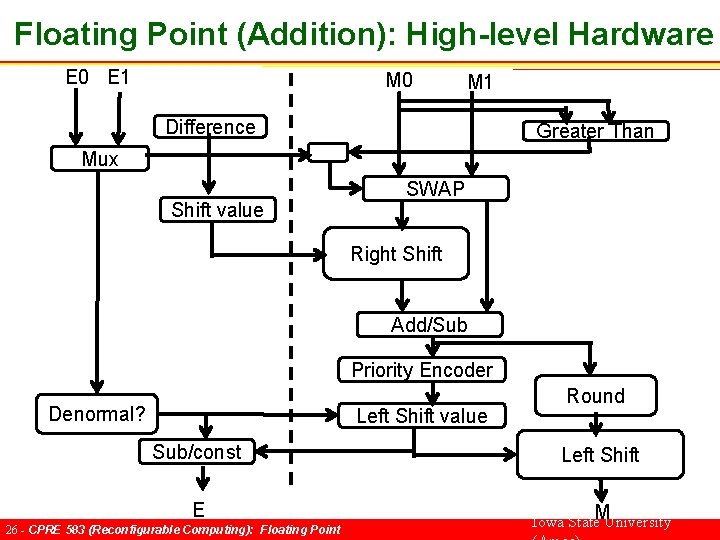

Floating Point (Addition): High-level Hardware E 0 E 1 M 0 M 1 Difference Greater Than Mux Shift value SWAP Right Shift Add/Sub Priority Encoder Denormal? Left Shift value Sub/const E 26 - CPRE 583 (Reconfigurable Computing): Floating Point Round Left Shift M Iowa State University

Floating Point • Both Xilinx and Altera supply floating point soft-cores (which I believe are IEEE-754 compliant). So don’t get too afraid if you need floating point in your class projects • Also there should be floating point open cores that are freely available. 27 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

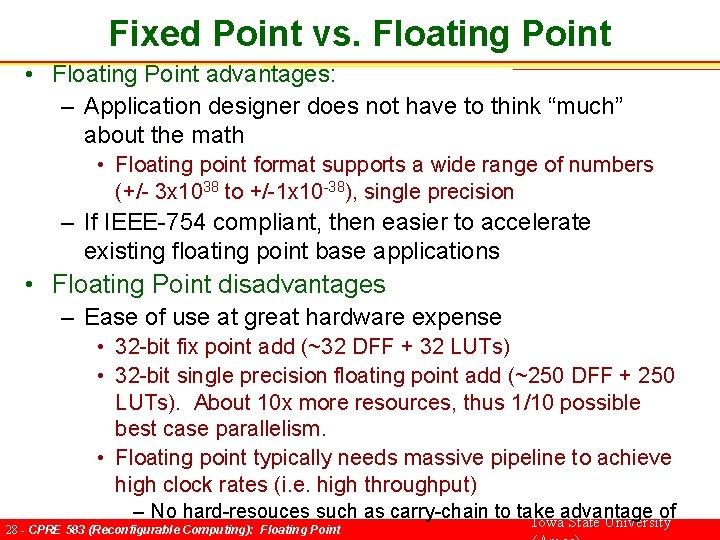

Fixed Point vs. Floating Point • Floating Point advantages: – Application designer does not have to think “much” about the math • Floating point format supports a wide range of numbers (+/- 3 x 1038 to +/-1 x 10 -38), single precision – If IEEE-754 compliant, then easier to accelerate existing floating point base applications • Floating Point disadvantages – Ease of use at great hardware expense • 32 -bit fix point add (~32 DFF + 32 LUTs) • 32 -bit single precision floating point add (~250 DFF + 250 LUTs). About 10 x more resources, thus 1/10 possible best case parallelism. • Floating point typically needs massive pipeline to achieve high clock rates (i. e. high throughput) – No hard-resouces such as carry-chain to take advantage of Iowa State University 28 - CPRE 583 (Reconfigurable Computing): Floating Point

Fixed Point vs. Floating Point • Range example: • Floating Point vs. Fixed Point advantages: Some exception with respect to precision 29 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Mitigating Floating Point Disadvantages • Only support a subset of the IEEE-754 standard – Could use software to off-load special cases • Modify floating point format to support a smaller data type (e. g. 18 -bit instead of 32 -bit) – Link to Cornell class: • http: //instruct 1. cit. cornell. edu/courses/ece 576/Floating. Point/index. html • Add hardware support in the FPGA for floating point – Hardcore multipliers: Added by companies early 2000’s – Altera: Hard shared paths for floating point (Stratix-V 2011) • How to get 1 -TFLOP throughput on FPGAs article – http: //www. eetimes. com/design/programmable-logic/4207687/How-toachieve-1 -trillion-floating-point-operations-per-second-in-an-FPGA 30 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Mitigating Fixed Point Disadvantages (21. 4) • Block Floating Point (mitigating range issue) 31 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

CPU/FPGA/GPU reported FLOPs • Block Floating Point (mitigating range issue) 32 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Next Lecture • Mid-term • Then on Friday: Evolvable Hardware 33 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Questions/Comments/Concerns • Write down – Main point of lecture – One thing that’s still not quite clear OR – If everything is clear, then give an example of how to apply something from lecture 34 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

Lecture Notes Altera App Notes on computing FLOPs for Stratix-III Altera old app Notes on floating point add/mult 35 - CPRE 583 (Reconfigurable Computing): Floating Point Iowa State University

- Slides: 35