VHDL Ernest Jamro Pawe Russek C 3 p

![Process Składnia: [etykieta: ] process [(lista sygnałów aktywujących)] [is] [podprogram] [typ] [stała] [zmienna] [inne Process Składnia: [etykieta: ] process [(lista sygnałów aktywujących)] [is] [podprogram] [typ] [stała] [zmienna] [inne](https://slidetodoc.com/presentation_image_h/11fe46740c03a3b178fb73b42f22f202/image-22.jpg)

- Slides: 63

VHDL Ernest Jamro, Paweł Russek C 3 p. 504 jamro@agh. edu. pl russek@agh. edu. pl www. fpga. agh. edu. pl

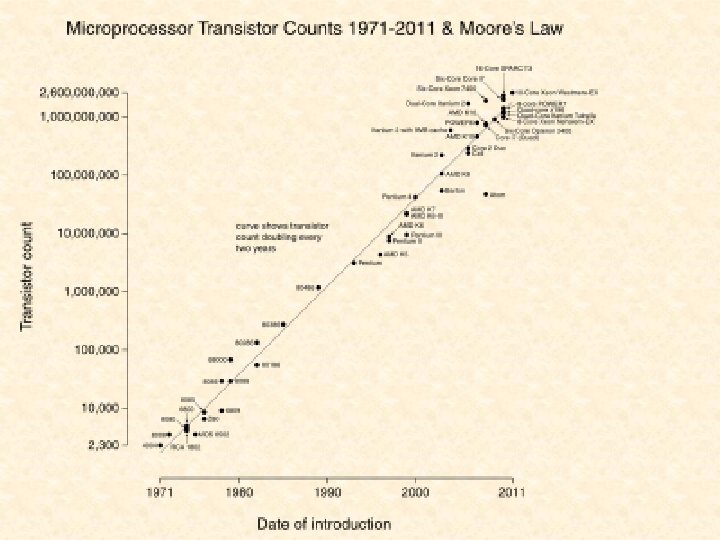

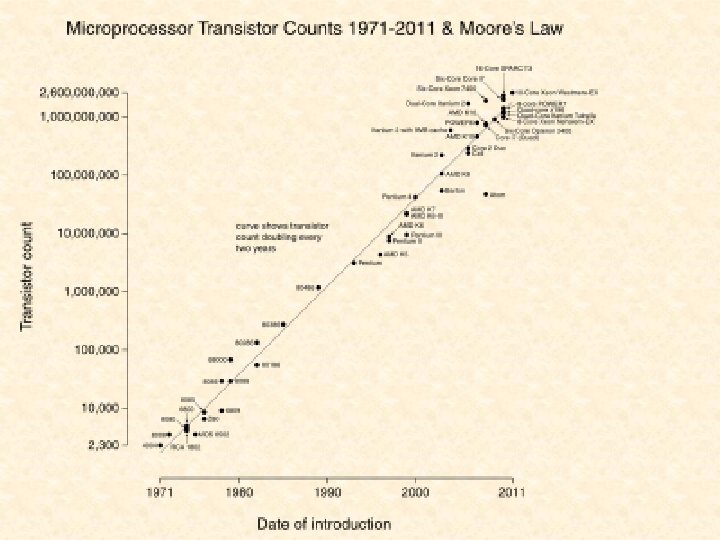

Języki Opisu Sprzętu – po co? Potrzeba narzędzia: • 1970 - INTEL 4004 4 projektantów 1 tys. tranzystorów • 1982 - INTEL 80286 20 projektantów 100 tys. tranzystorów 100 projektantów 3 mln tranzystorów 1000 projektantów 150 mln tranzystorów • 1992 - INTEL PENTIUM • 2008 • 200? ? ? ? ? projektantów ? ? mln tranzystorów Współczesne wymagania: hardware-software codesign !!! E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

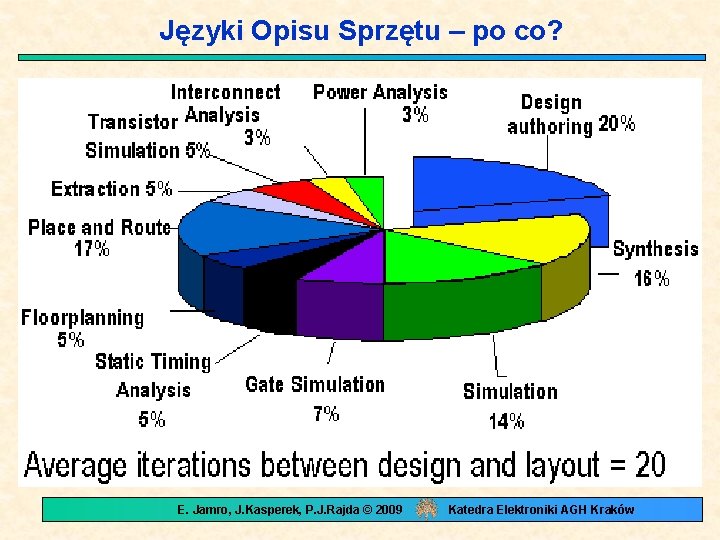

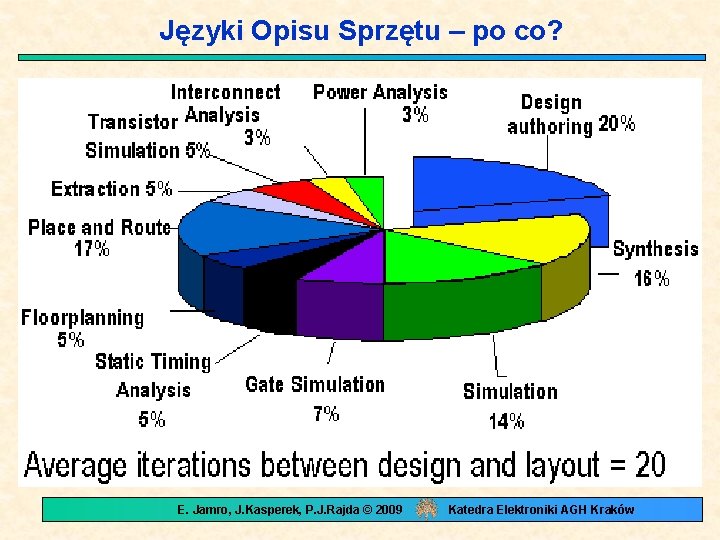

Języki Opisu Sprzętu – po co? E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

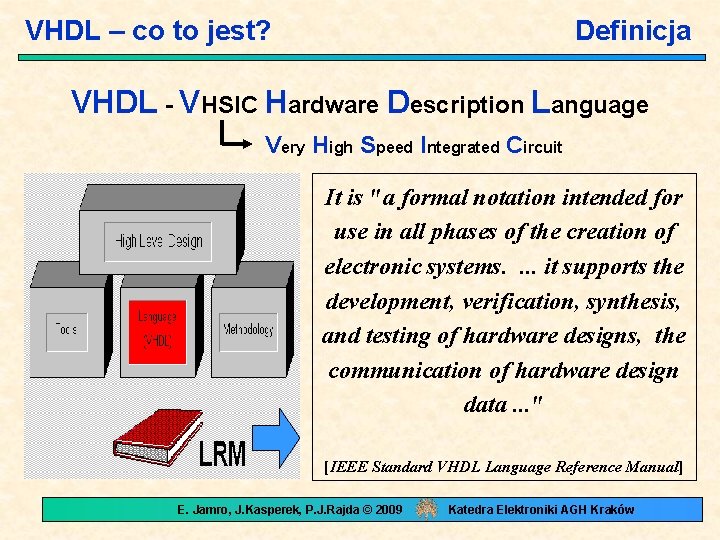

VHDL – co to jest? Definicja VHDL - VHSIC Hardware Description Language Very High Speed Integrated Circuit It is "a formal notation intended for use in all phases of the creation of electronic systems. . it supports the development, verification, synthesis, and testing of hardware designs, the communication of hardware design data. . . " [IEEE Standard VHDL Language Reference Manual] E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

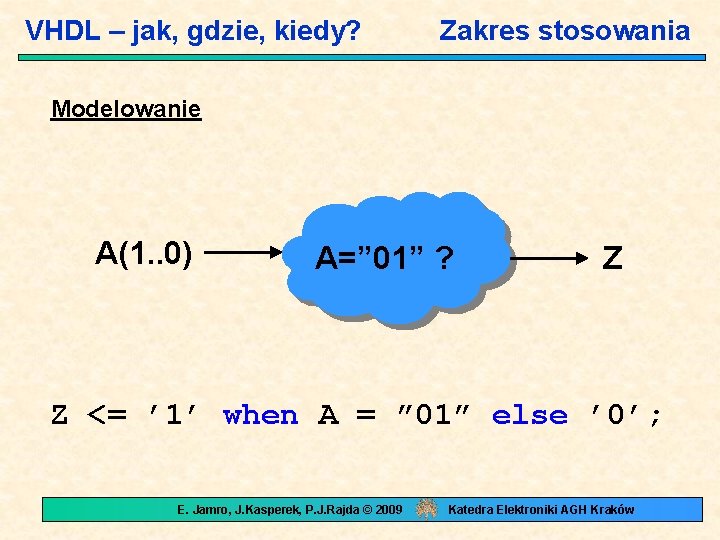

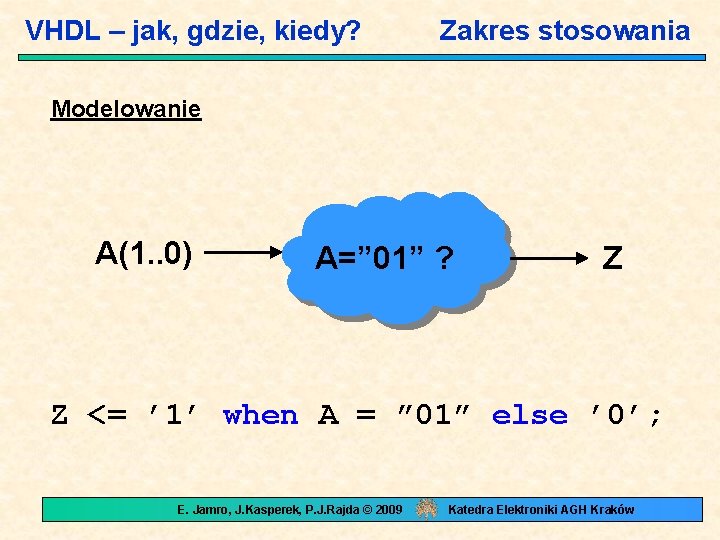

VHDL – jak, gdzie, kiedy? Zakres stosowania Modelowanie A(1. . 0) A=” 01” ? Z Z <= ’ 1’ when A = ” 01” else ’ 0’; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

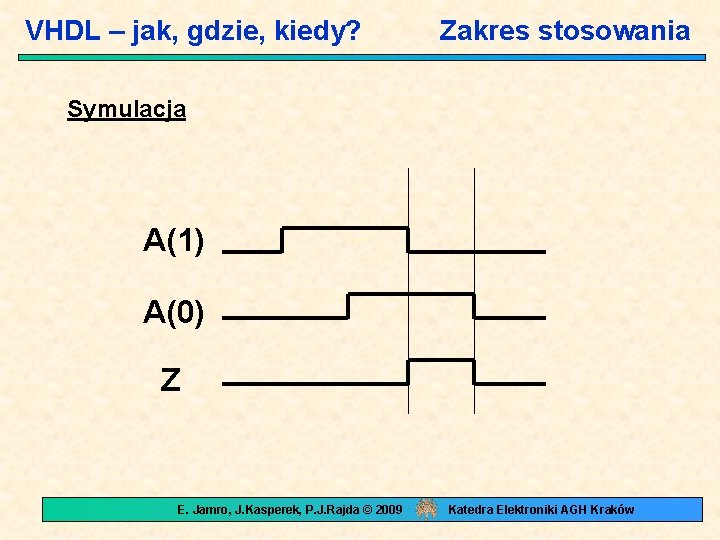

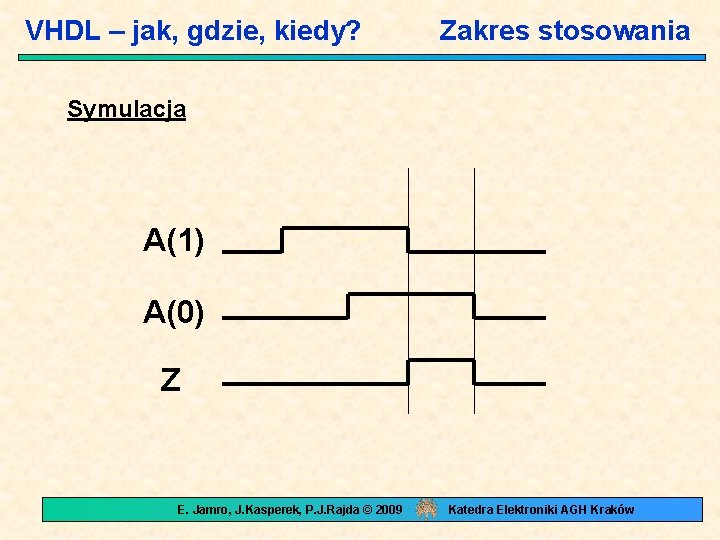

VHDL – jak, gdzie, kiedy? Zakres stosowania Symulacja A(1) A(0) Z E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

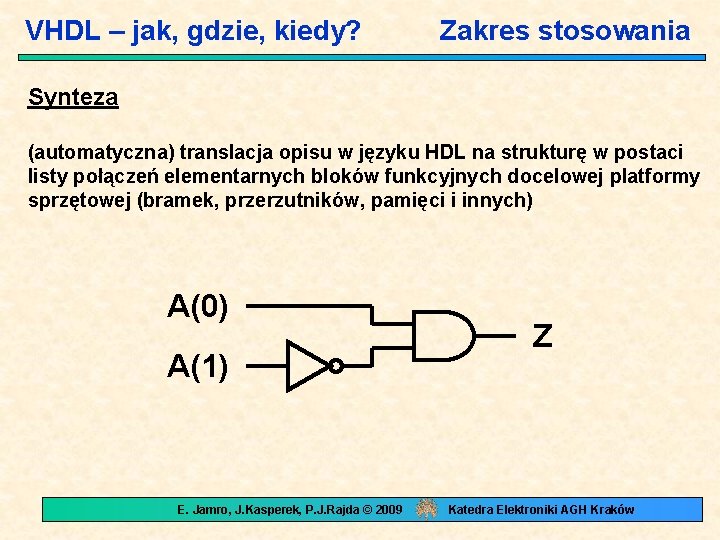

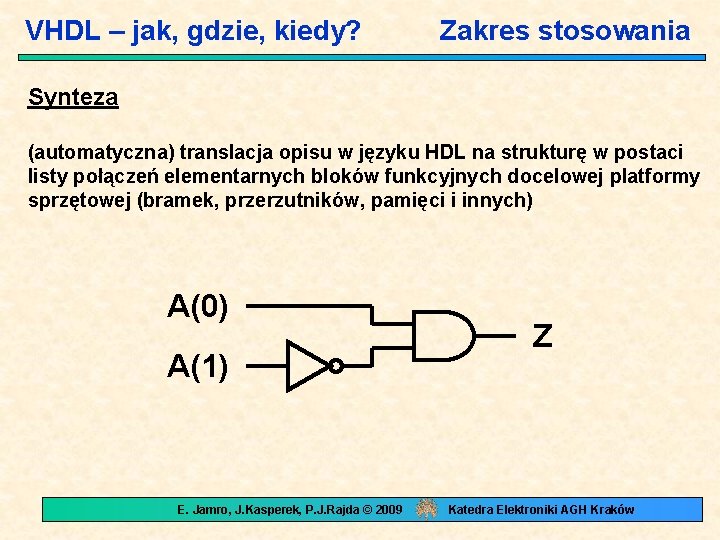

VHDL – jak, gdzie, kiedy? Zakres stosowania Synteza (automatyczna) translacja opisu w języku HDL na strukturę w postaci listy połączeń elementarnych bloków funkcyjnych docelowej platformy sprzętowej (bramek, przerzutników, pamięci i innych) A(0) A(1) E. Jamro, J. Kasperek, P. J. Rajda © 2009 Z Katedra Elektroniki AGH Kraków

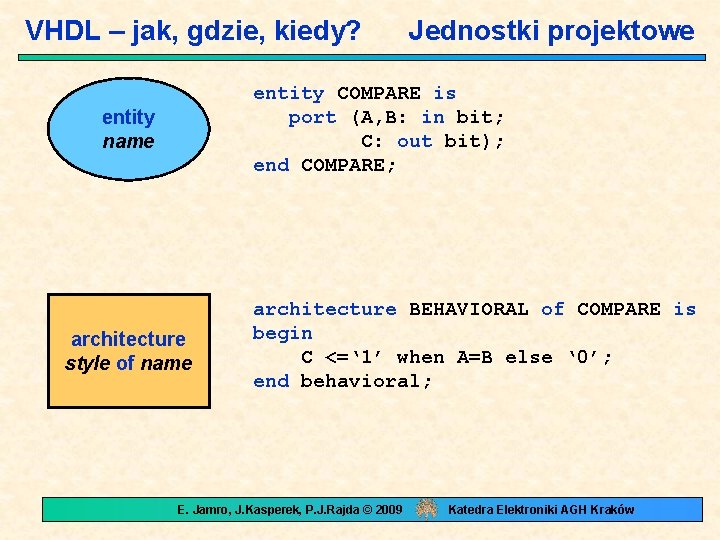

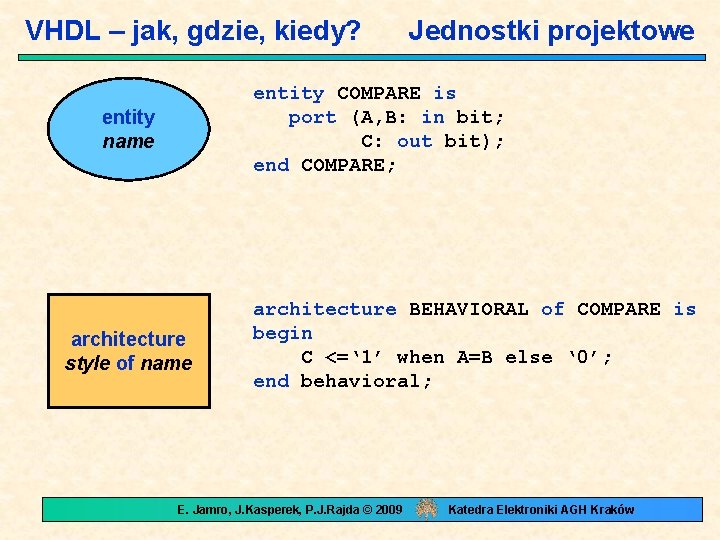

VHDL – jak, gdzie, kiedy? Jednostki projektowe entity COMPARE is port (A, B: in bit; C: out bit); end COMPARE; entity name architecture style of name architecture BEHAVIORAL of COMPARE is begin C <=‘ 1’ when A=B else ‘ 0’; end behavioral; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

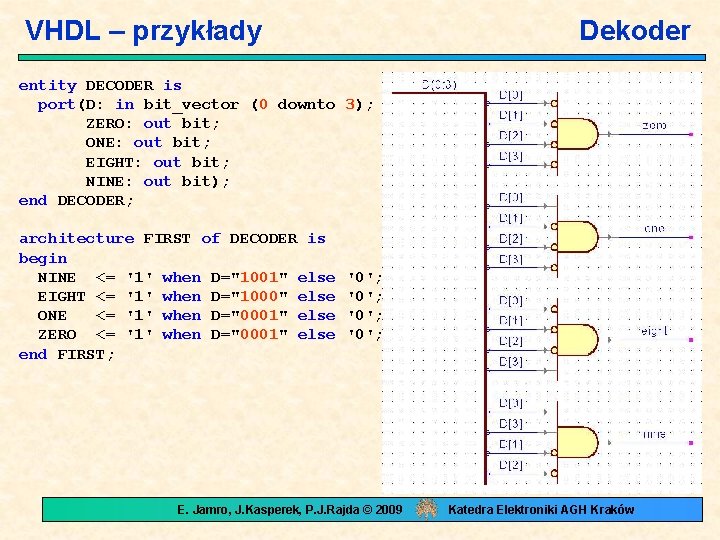

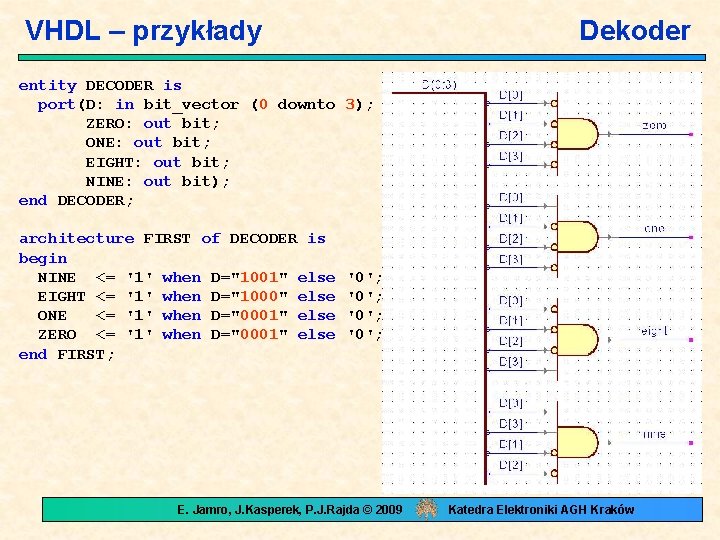

VHDL – przykłady Dekoder entity DECODER is port(D: in bit_vector (0 downto 3); ZERO: out bit; ONE: out bit; EIGHT: out bit; NINE: out bit); end DECODER; architecture FIRST of DECODER is begin NINE <= '1' when D="1001" else EIGHT <= '1' when D="1000" else ONE <= '1' when D="0001" else ZERO <= '1' when D="0001" else end FIRST; '0'; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

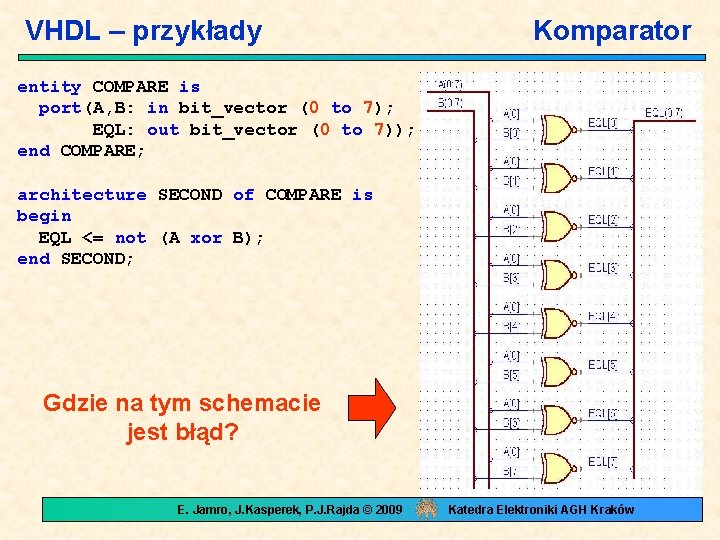

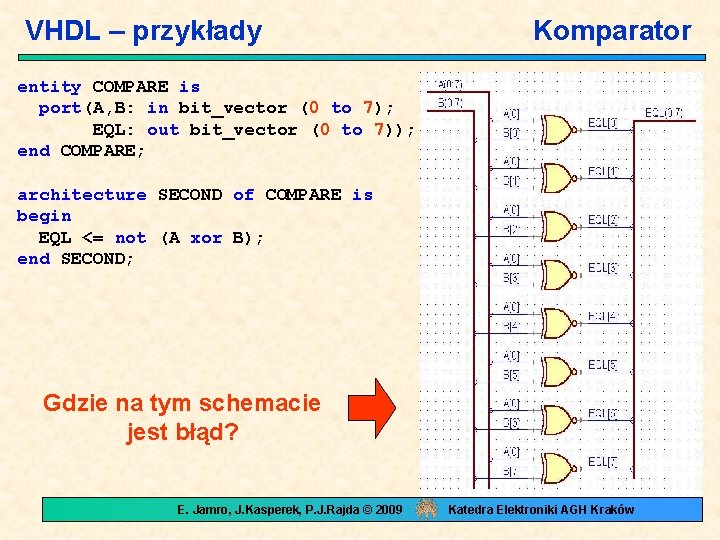

VHDL – przykłady Komparator entity COMPARE is port(A, B: in bit_vector (0 to 7); EQL: out bit_vector (0 to 7)); end COMPARE; architecture SECOND of COMPARE is begin EQL <= not (A xor B); end SECOND; Gdzie na tym schemacie jest błąd? E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

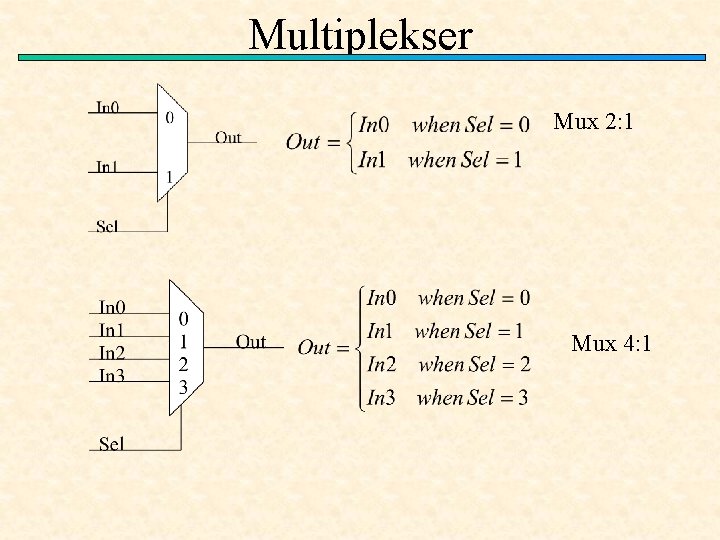

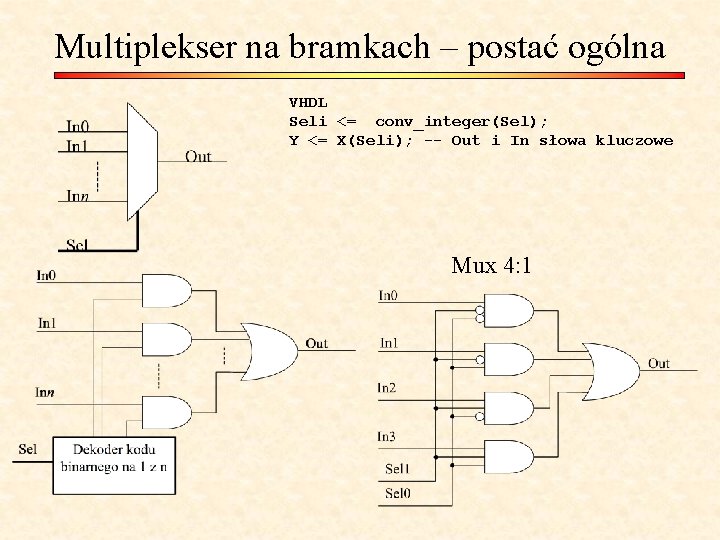

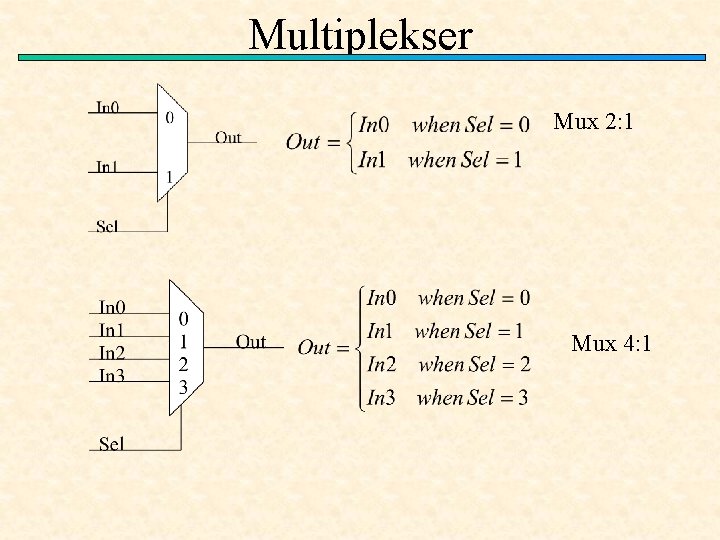

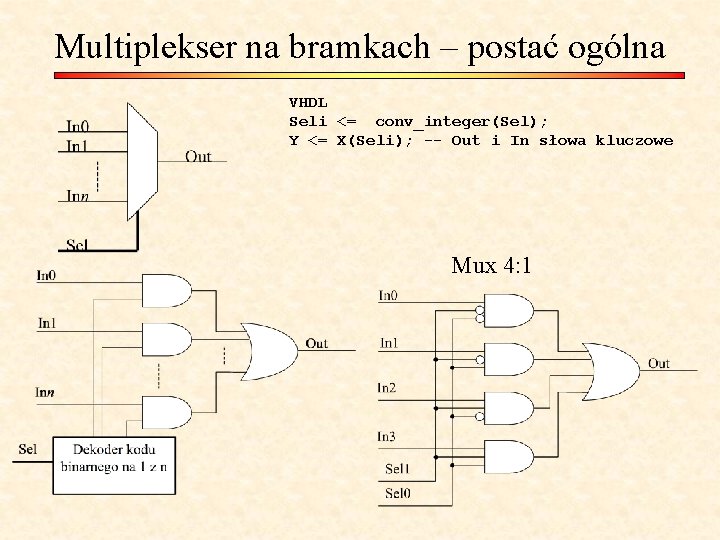

Multiplekser Mux 2: 1 Mux 4: 1

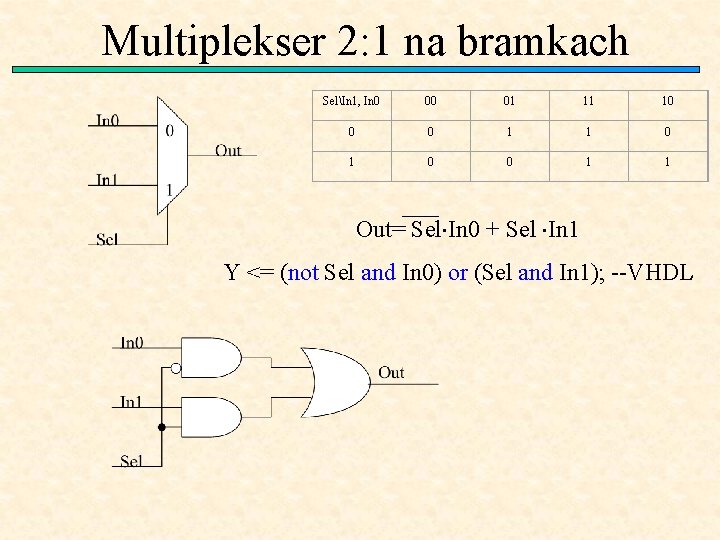

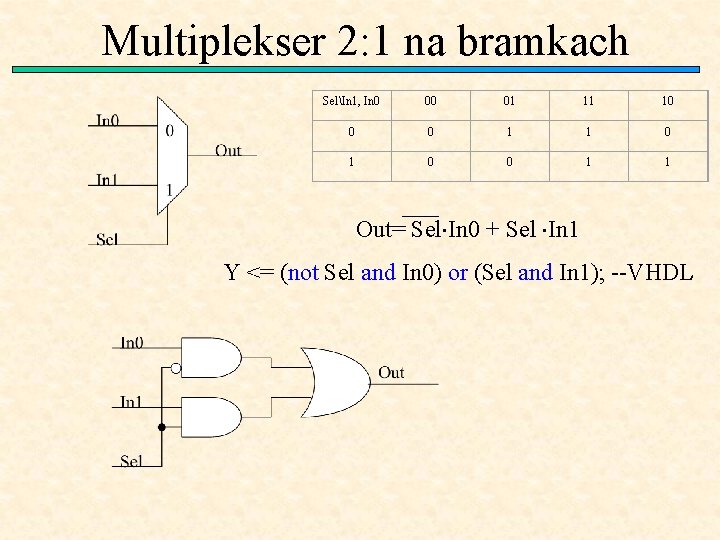

Multiplekser 2: 1 na bramkach SelIn 1, In 0 00 01 11 10 0 0 1 1 Out= Sel In 0 + Sel In 1 Y <= (not Sel and In 0) or (Sel and In 1); --VHDL

Multiplekser na bramkach – postać ogólna VHDL Seli <= conv_integer(Sel); Y <= X(Seli); -- Out i In słowa kluczowe Mux 4: 1

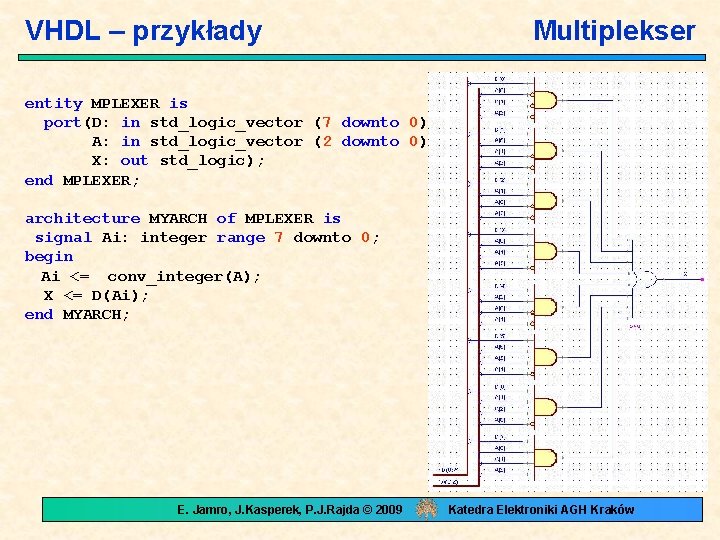

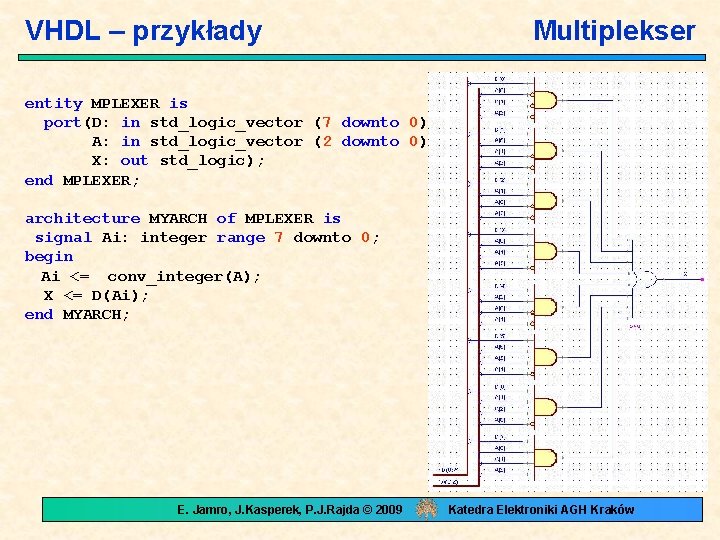

VHDL – przykłady Multiplekser entity MPLEXER is port(D: in std_logic_vector (7 downto 0); A: in std_logic_vector (2 downto 0); X: out std_logic); end MPLEXER; architecture MYARCH of MPLEXER is signal Ai: integer range 7 downto 0; begin Ai <= conv_integer(A); X <= D(Ai); end MYARCH; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

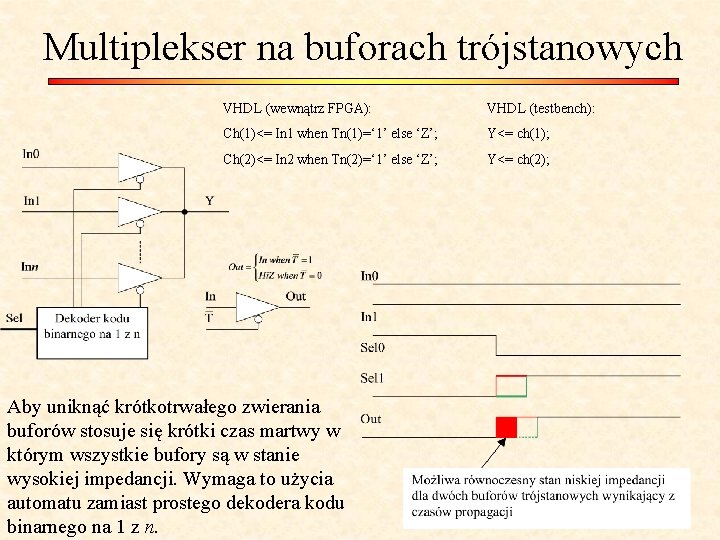

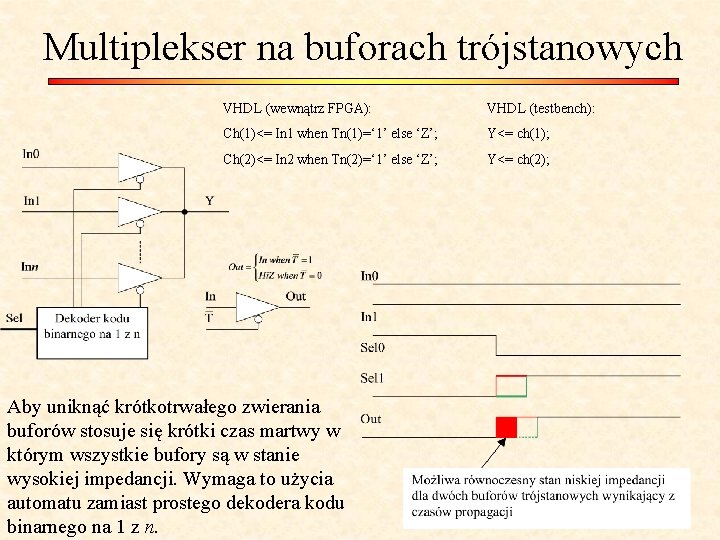

Multiplekser na buforach trójstanowych VHDL (wewnątrz FPGA): VHDL (testbench): Ch(1)<= In 1 when Tn(1)=‘ 1’ else ‘Z’; Y<= ch(1); Ch(2)<= In 2 when Tn(2)=‘ 1’ else ‘Z’; Y<= ch(2); Aby uniknąć krótkotrwałego zwierania buforów stosuje się krótki czas martwy w którym wszystkie bufory są w stanie wysokiej impedancji. Wymaga to użycia automatu zamiast prostego dekodera kodu binarnego na 1 z n.

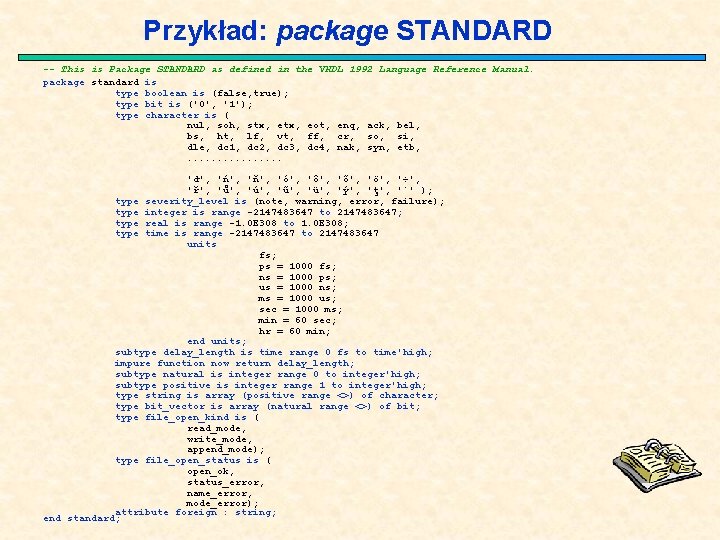

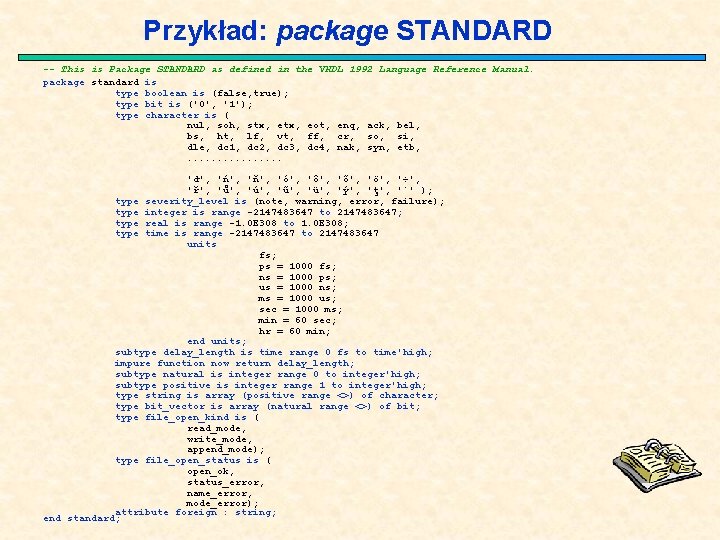

Przykład: package STANDARD -- This is Package STANDARD as defined in the VHDL 1992 Language Reference Manual. package standard is type boolean is (false, true); type bit is ('0', '1'); type character is ( nul, soh, stx, eot, enq, ack, bel, bs, ht, lf, vt, ff, cr, so, si, dle, dc 1, dc 2, dc 3, dc 4, nak, syn, etb, . . . . 'đ', 'ń', 'ň', 'ó', 'ô', 'ő', 'ö', '÷', 'ř', 'ů', 'ú', 'ű', 'ü', 'ý', 'ţ', '˙' ); type severity_level is (note, warning, error, failure); type integer is range -2147483647 to 2147483647; type real is range -1. 0 E 308 to 1. 0 E 308; type time is range -2147483647 to 2147483647 units fs; ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 us; sec = 1000 ms; min = 60 sec; hr = 60 min; end units; subtype delay_length is time range 0 fs to time'high; impure function now return delay_length; subtype natural is integer range 0 to integer'high; subtype positive is integer range 1 to integer'high; type string is array (positive range <>) of character; type bit_vector is array (natural range <>) of bit; type file_open_kind is ( read_mode, write_mode, append_mode); type file_open_status is ( open_ok, status_error, name_error, mode_error); attribute foreign : string; end standard;

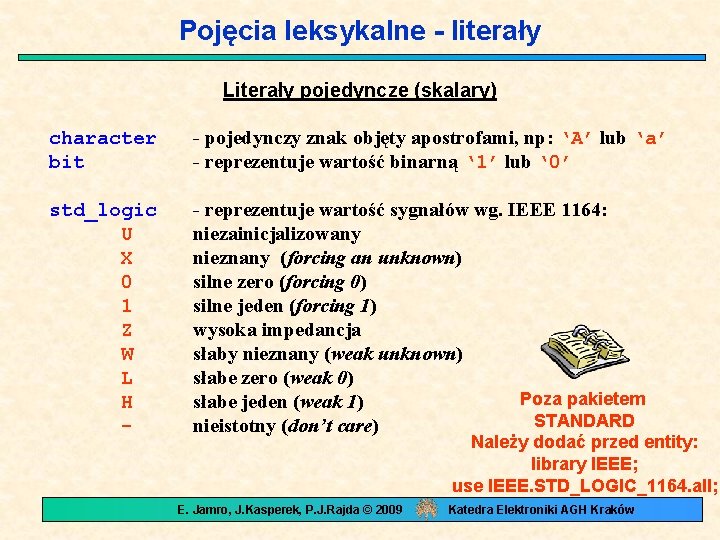

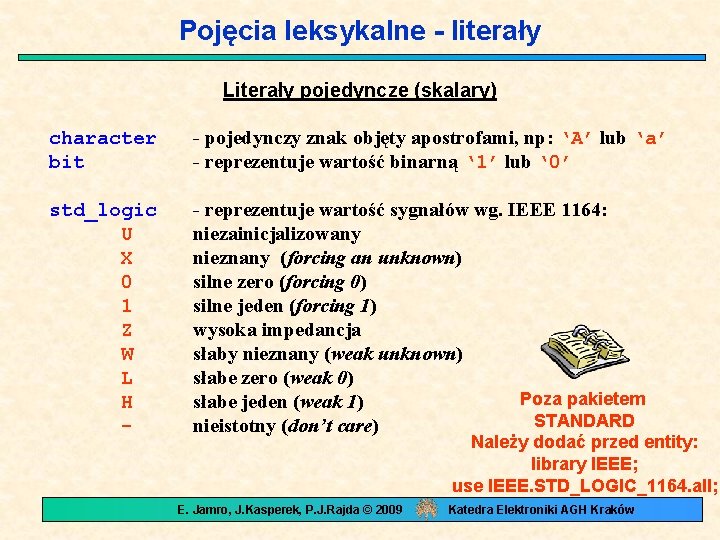

Pojęcia leksykalne - literały Literały pojedyncze (skalary) character bit - pojedynczy znak objęty apostrofami, np: ‘A’ lub ‘a’ - reprezentuje wartość binarną ‘ 1’ lub ‘ 0’ std_logic U X 0 1 Z W L H - - reprezentuje wartość sygnałów wg. IEEE 1164: niezainicjalizowany nieznany (forcing an unknown) silne zero (forcing 0) silne jeden (forcing 1) wysoka impedancja słaby nieznany (weak unknown) słabe zero (weak 0) Poza pakietem słabe jeden (weak 1) STANDARD nieistotny (don’t care) Należy dodać przed entity: library IEEE; use IEEE. STD_LOGIC_1164. all; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

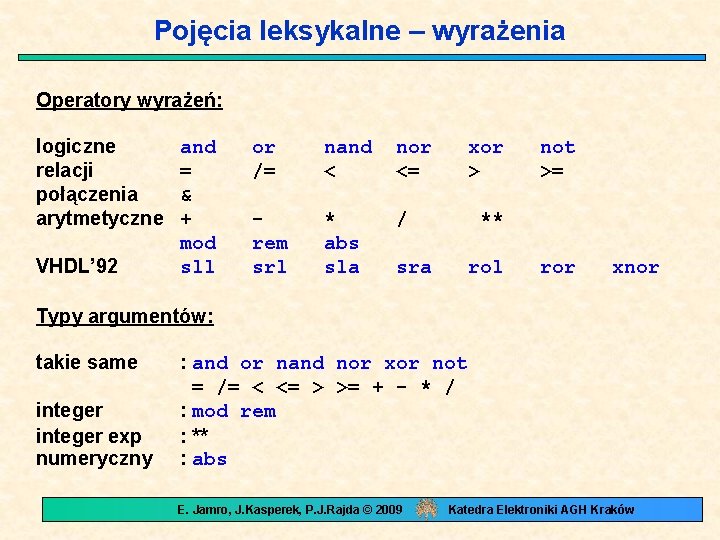

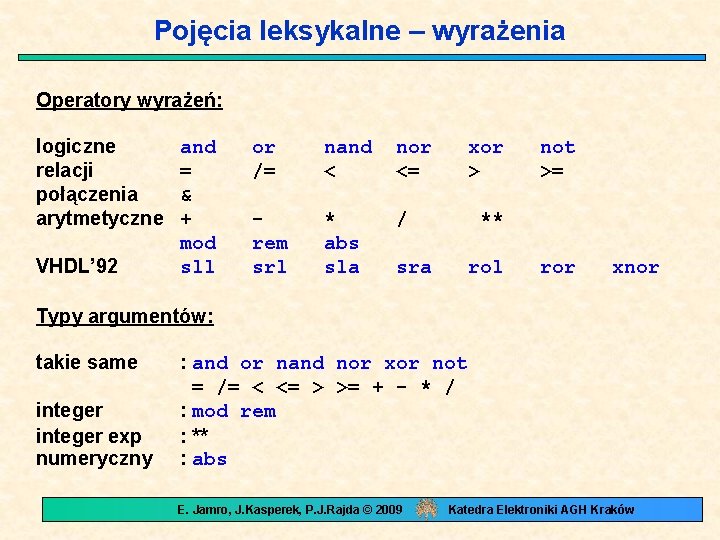

Pojęcia leksykalne – wyrażenia Operatory wyrażeń: logiczne relacji połączenia arytmetyczne VHDL’ 92 and = & + mod sll or /= nand < nor <= rem srl * abs sla / sra xor > not >= ** rol ror xnor Typy argumentów: takie same integer exp numeryczny : and or nand nor xor not = /= < <= > >= + - * / : mod rem : ** : abs E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

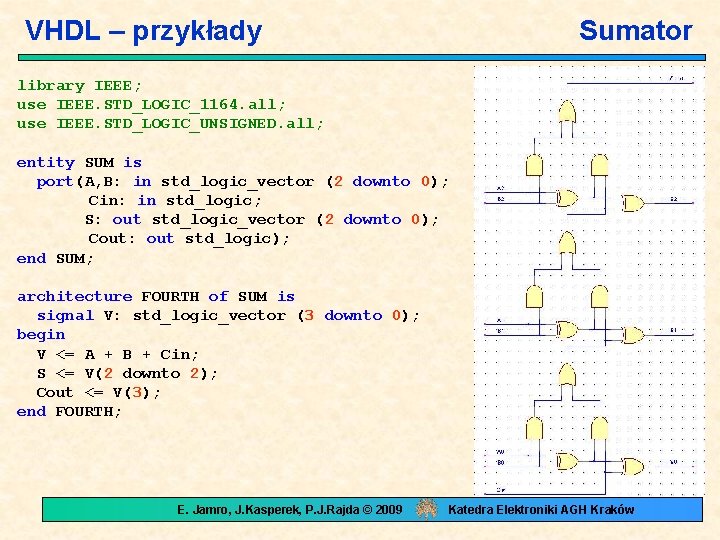

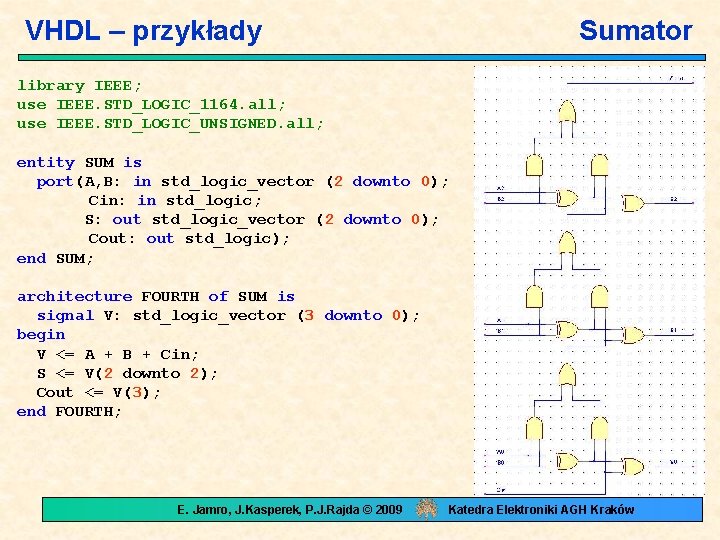

VHDL – przykłady Sumator library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_UNSIGNED. all; entity SUM is port(A, B: in std_logic_vector (2 downto 0); Cin: in std_logic; S: out std_logic_vector (2 downto 0); Cout: out std_logic); end SUM; architecture FOURTH of SUM is signal V: std_logic_vector (3 downto 0); begin V <= A + B + Cin; S <= V(2 downto 2); Cout <= V(3); end FOURTH; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

![Process Składnia etykieta process lista sygnałów aktywujących is podprogram typ stała zmienna inne Process Składnia: [etykieta: ] process [(lista sygnałów aktywujących)] [is] [podprogram] [typ] [stała] [zmienna] [inne](https://slidetodoc.com/presentation_image_h/11fe46740c03a3b178fb73b42f22f202/image-22.jpg)

Process Składnia: [etykieta: ] process [(lista sygnałów aktywujących)] [is] [podprogram] [typ] [stała] [zmienna] [inne deklaracje] begin instrukcje sekwencyjne end process [etykieta]; Instrukcja przypisania wartości dla zmiennych zmienna : = wyrażenie; Instrukcja przypisania wartości dla sygnałów sygnał <= wyrażenie [after delay]; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

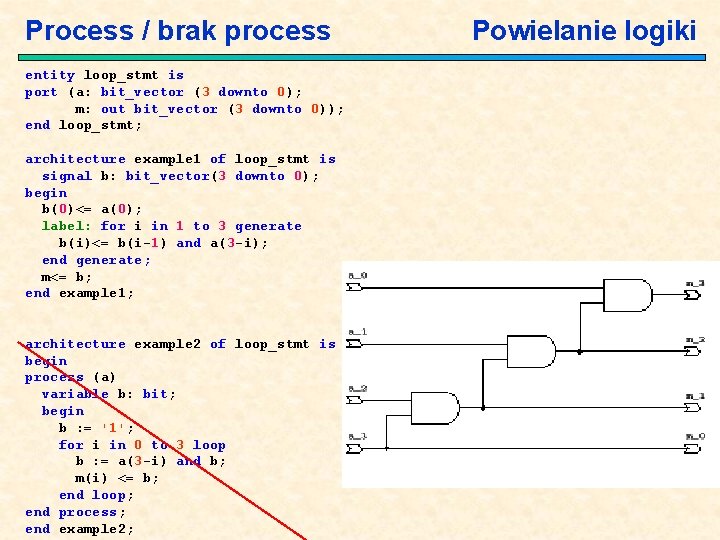

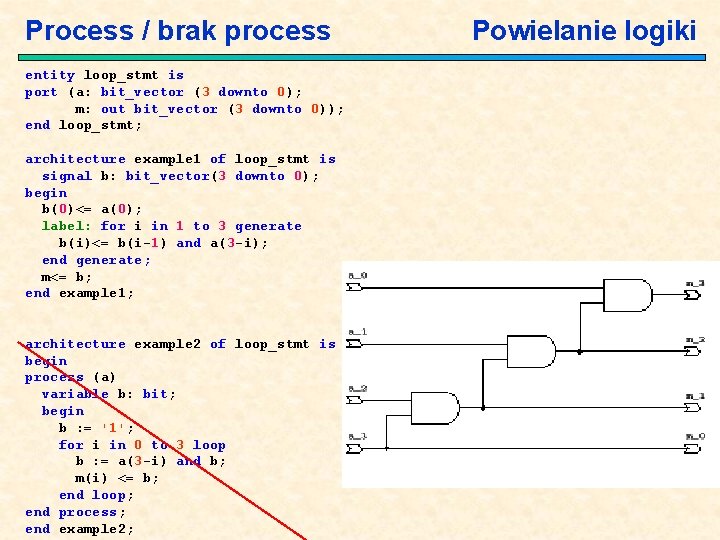

Process / brak process entity loop_stmt is port (a: bit_vector (3 downto 0); m: out bit_vector (3 downto 0)); end loop_stmt; architecture example 1 of loop_stmt is signal b: bit_vector(3 downto 0); begin b(0)<= a(0); label: for i in 1 to 3 generate b(i)<= b(i-1) and a(3 -i); end generate; m<= b; end example 1; architecture example 2 of loop_stmt is begin process (a) variable b: bit; begin b : = '1'; for i in 0 to 3 loop b : = a(3 -i) and b; m(i) <= b; end loop; end process; end example 2; Powielanie logiki

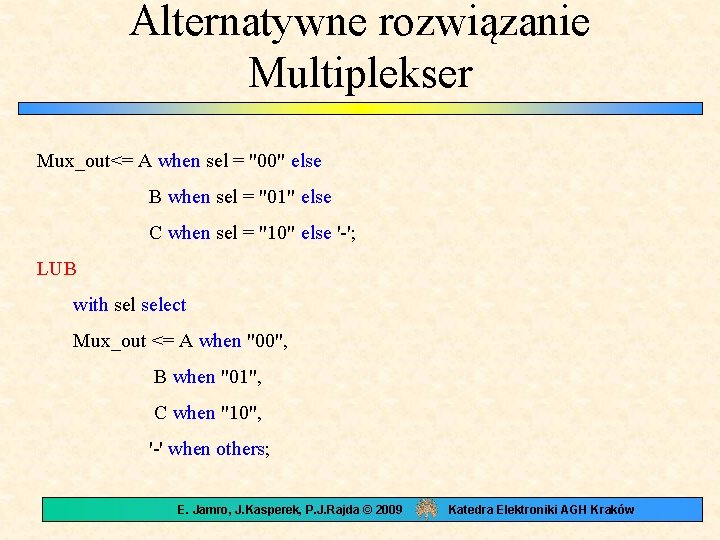

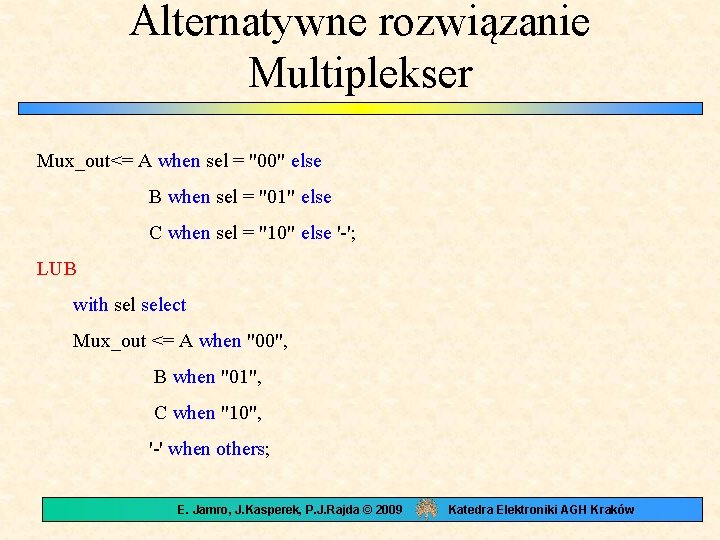

Alternatywne rozwiązanie Multiplekser Mux_out<= A when sel = "00" else B when sel = "01" else C when sel = "10" else '-'; LUB with select Mux_out <= A when "00", B when "01", C when "10", '-' when others; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

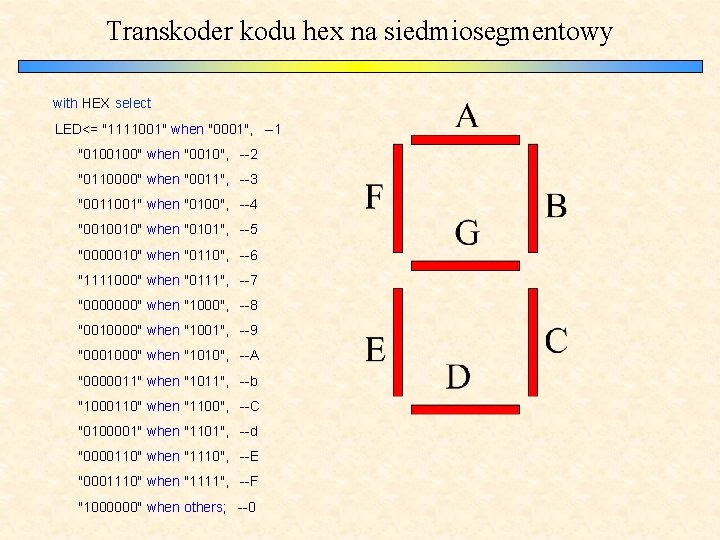

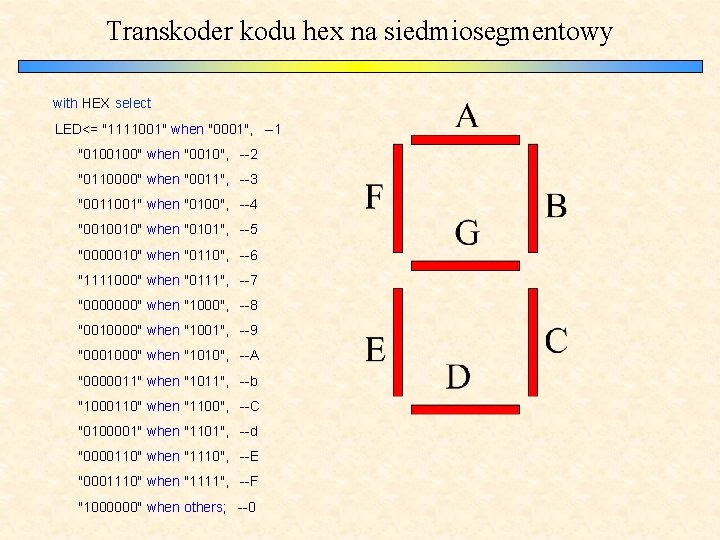

Transkoder kodu hex na siedmiosegmentowy with HEX select LED<= "1111001" when "0001", --1 "0100100" when "0010", --2 "0110000" when "0011", --3 "0011001" when "0100", --4 "0010010" when "0101", --5 "0000010" when "0110", --6 "1111000" when "0111", --7 "0000000" when "1000", --8 "0010000" when "1001", --9 "0001000" when "1010", --A "0000011" when "1011", --b "1000110" when "1100", --C "0100001" when "1101", --d "0000110" when "1110", --E "0001110" when "1111", --F "1000000" when others; --0

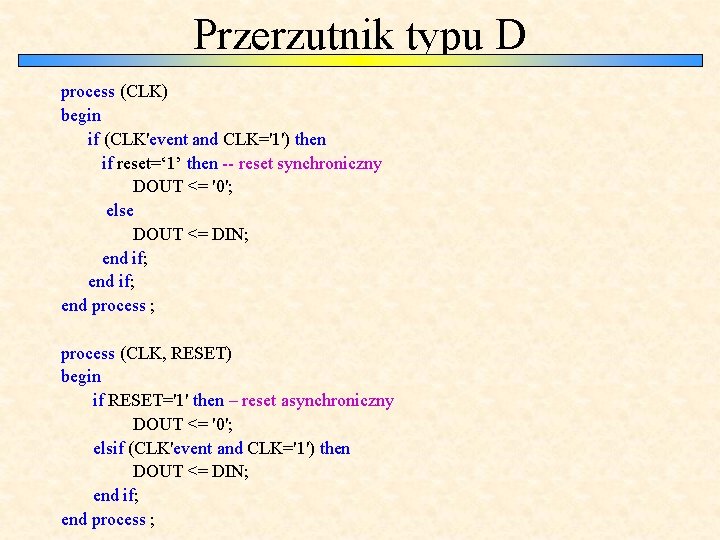

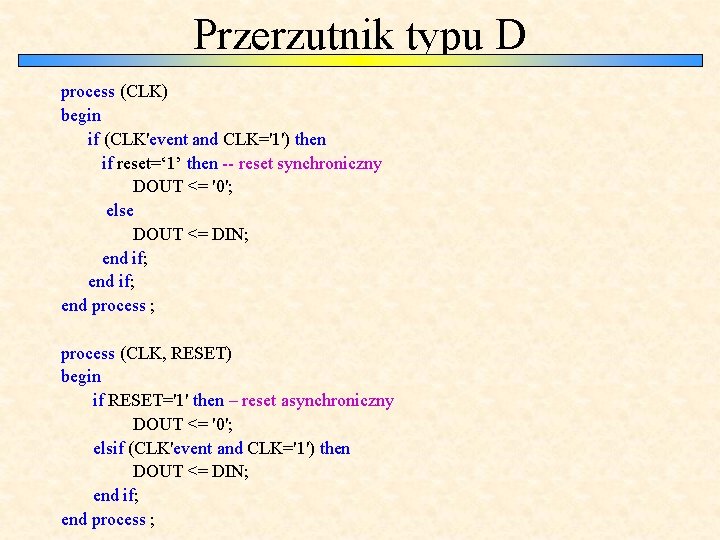

Przerzutnik typu D process (CLK) begin if (CLK'event and CLK='1') then if reset=‘ 1’ then -- reset synchroniczny DOUT <= '0'; else DOUT <= DIN; end if; end process ; process (CLK, RESET) begin if RESET='1' then – reset asynchroniczny DOUT <= '0'; elsif (CLK'event and CLK='1') then DOUT <= DIN; end if; end process ;

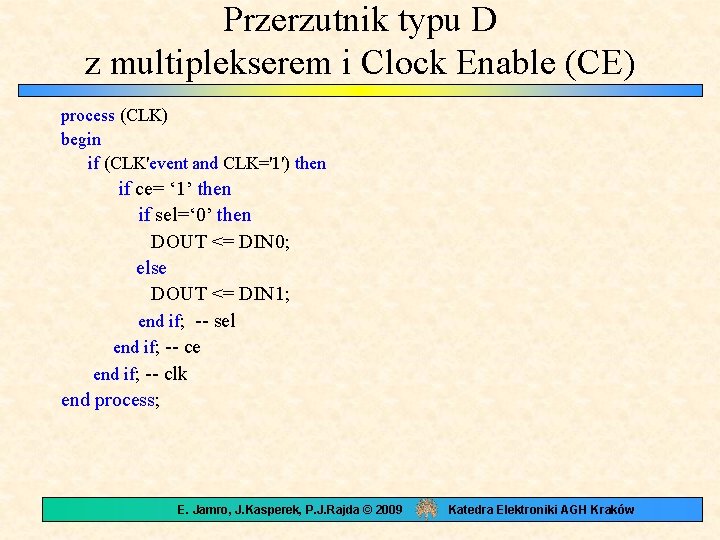

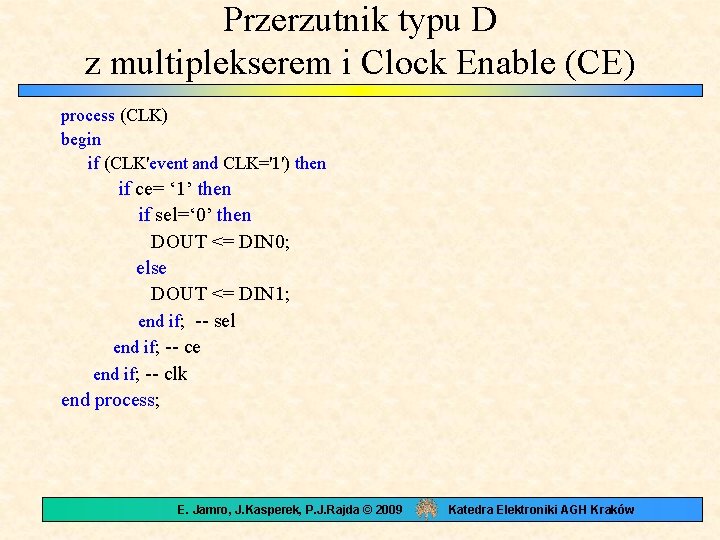

Przerzutnik typu D z multiplekserem i Clock Enable (CE) process (CLK) begin if (CLK'event and CLK='1') then if ce= ‘ 1’ then if sel=‘ 0’ then DOUT <= DIN 0; else DOUT <= DIN 1; end if; -- sel end if; -- ce end if; -- clk end process; E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

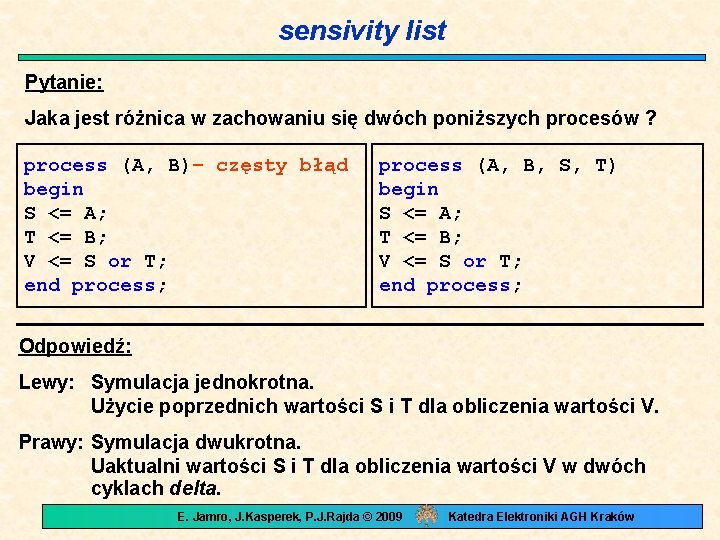

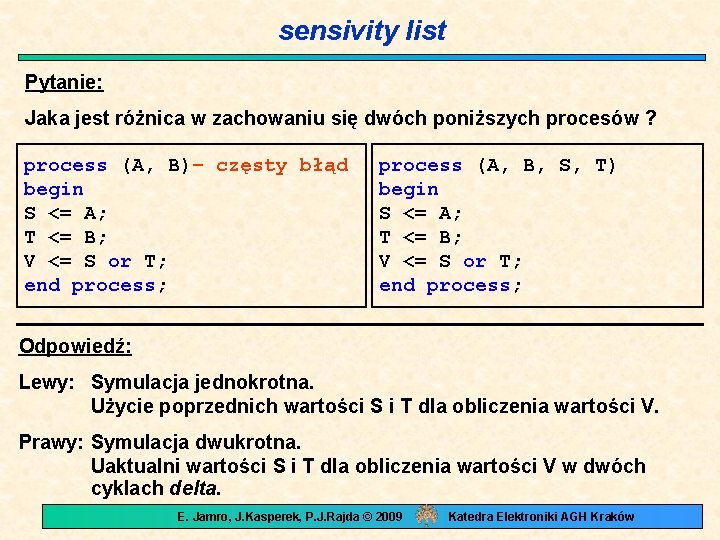

sensivity list Pytanie: Jaka jest różnica w zachowaniu się dwóch poniższych procesów ? process (A, B)– częsty błąd begin S <= A; T <= B; V <= S or T; end process; process (A, B, S, T) begin S <= A; T <= B; V <= S or T; end process; Odpowiedź: Lewy: Symulacja jednokrotna. Użycie poprzednich wartości S i T dla obliczenia wartości V. Prawy: Symulacja dwukrotna. Uaktualni wartości S i T dla obliczenia wartości V w dwóch cyklach delta. E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

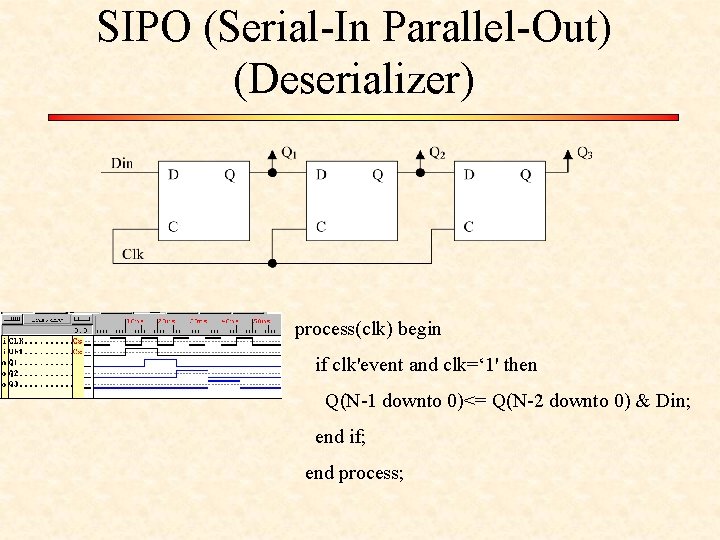

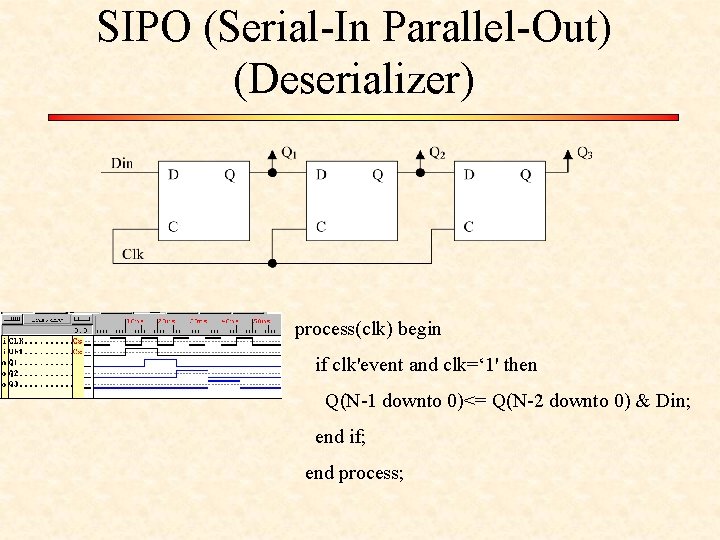

SIPO (Serial-In Parallel-Out) (Deserializer) process(clk) begin if clk'event and clk=‘ 1' then Q(N-1 downto 0)<= Q(N-2 downto 0) & Din; end if; end process;

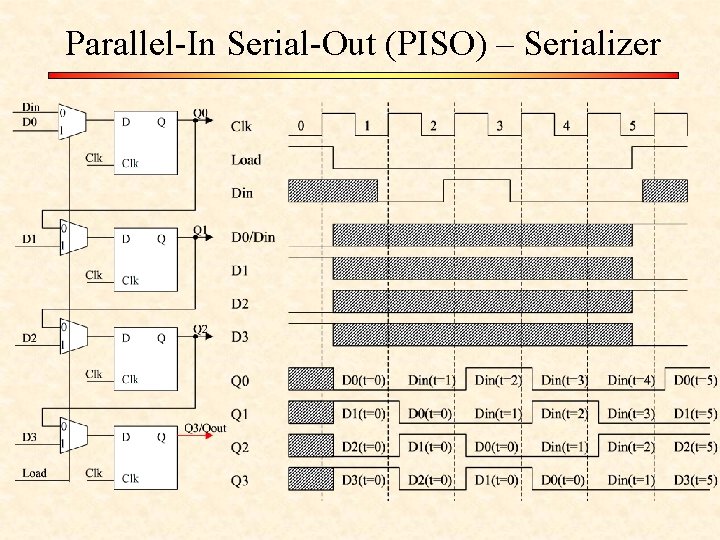

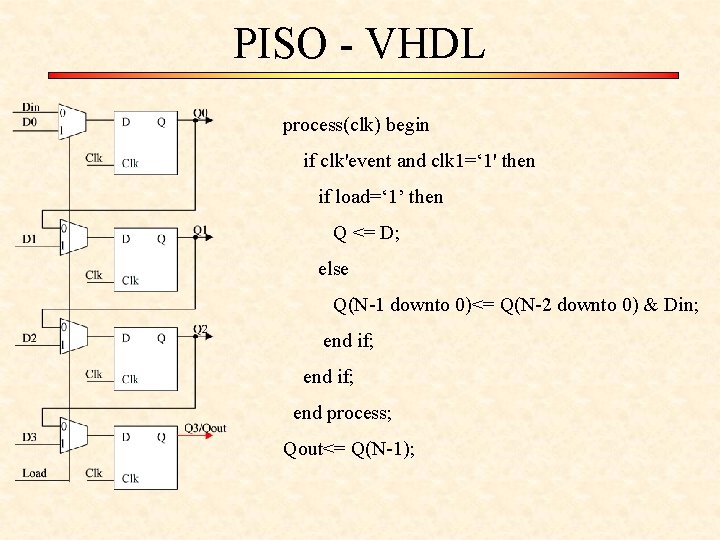

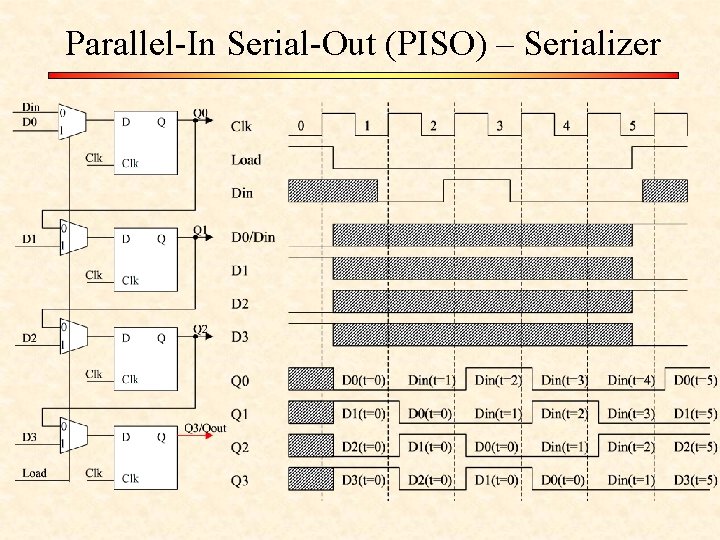

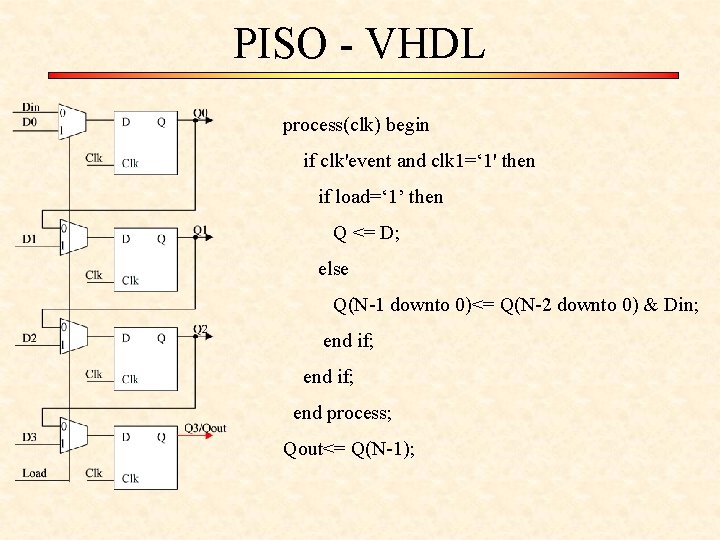

Parallel-In Serial-Out (PISO) – Serializer

PISO - VHDL process(clk) begin if clk'event and clk 1=‘ 1' then if load=‘ 1’ then Q <= D; else Q(N-1 downto 0)<= Q(N-2 downto 0) & Din; end if; end process; Qout<= Q(N-1);

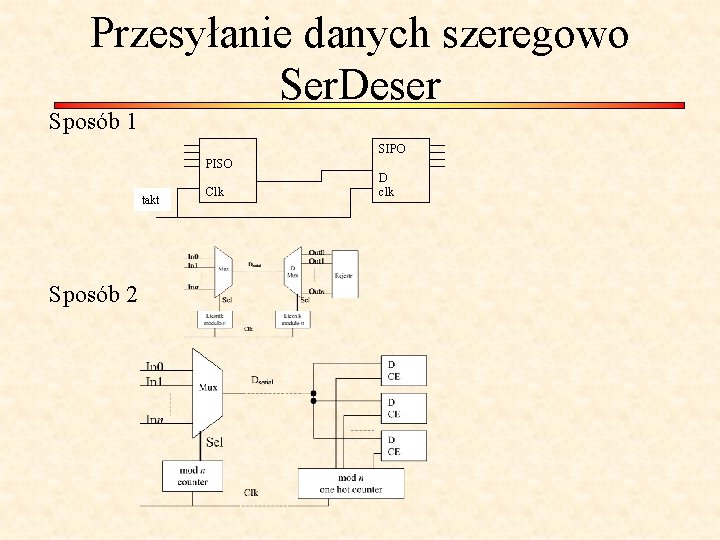

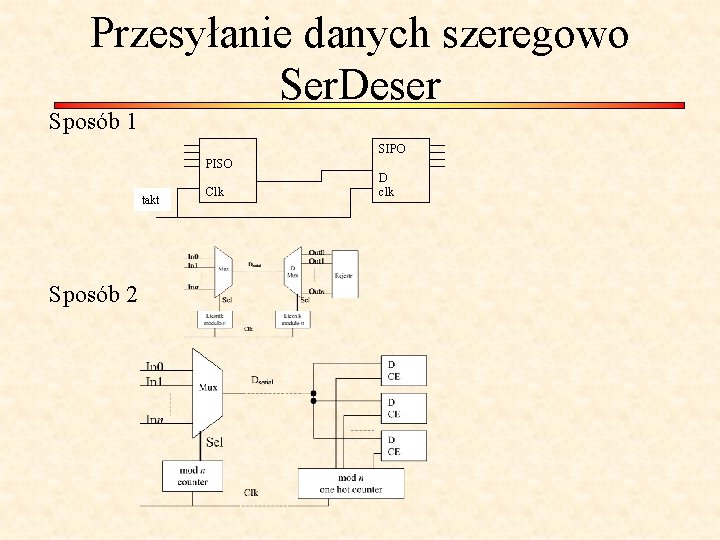

Przesyłanie danych szeregowo Ser. Deser Sposób 1 SIPO PISO takt Sposób 2 Clk D clk

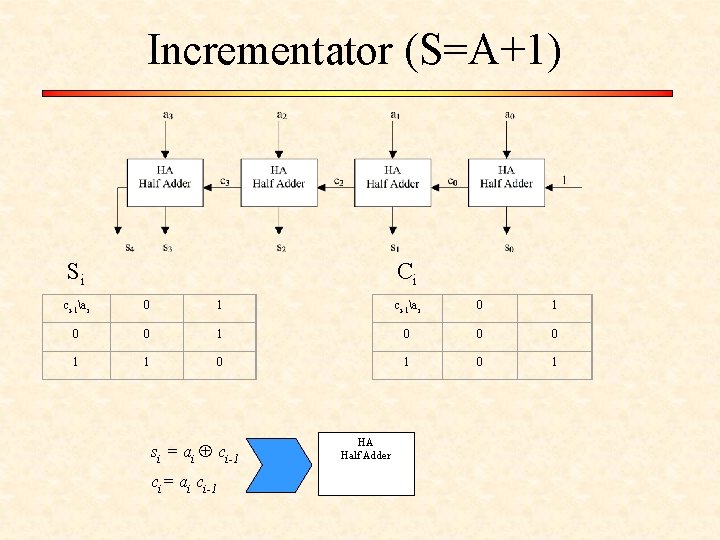

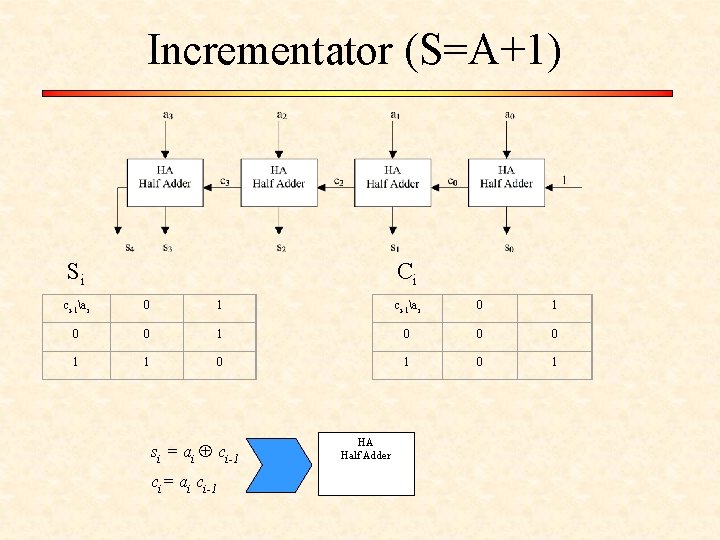

Incrementator (S=A+1) Si Ci ci-1ai 0 1 0 0 0 1 1 0 1 si = ai ci-1 ci= ai ci-1 HA Half Adder

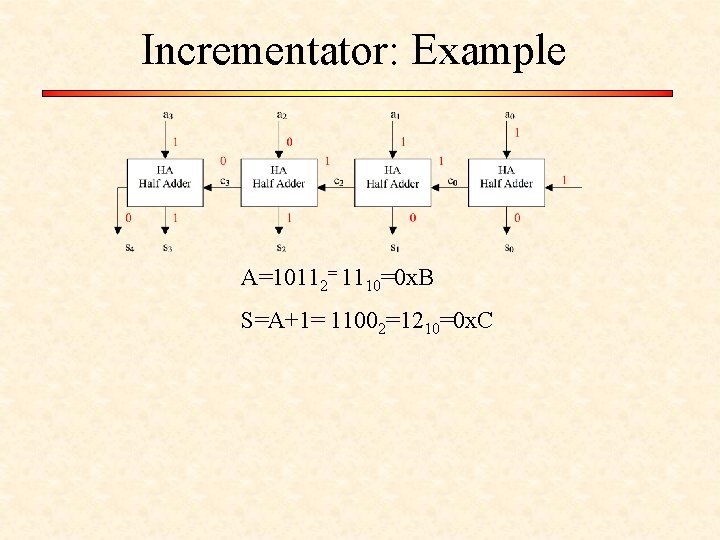

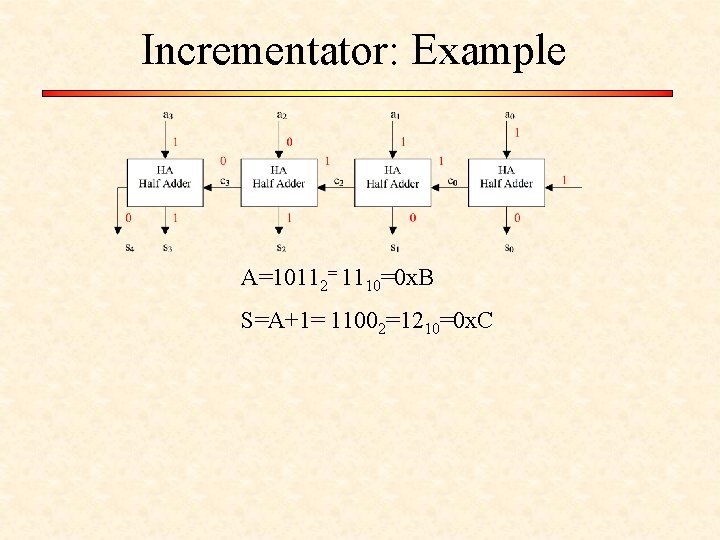

Incrementator: Example A=10112= 1110=0 x. B S=A+1= 11002=1210=0 x. C

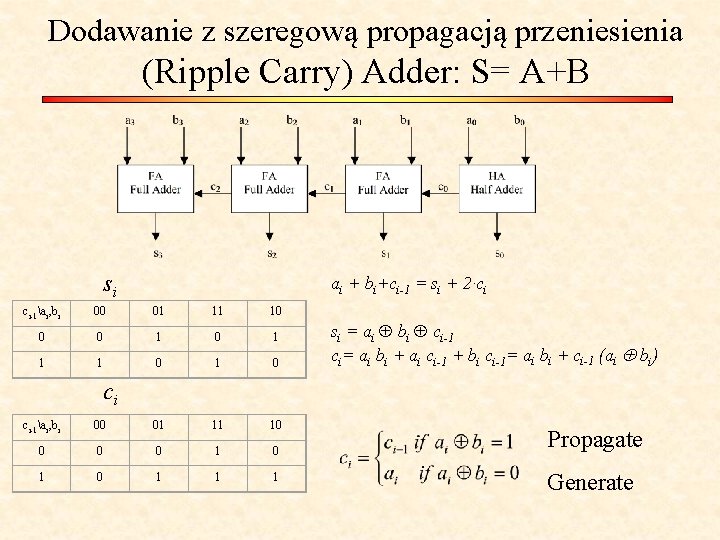

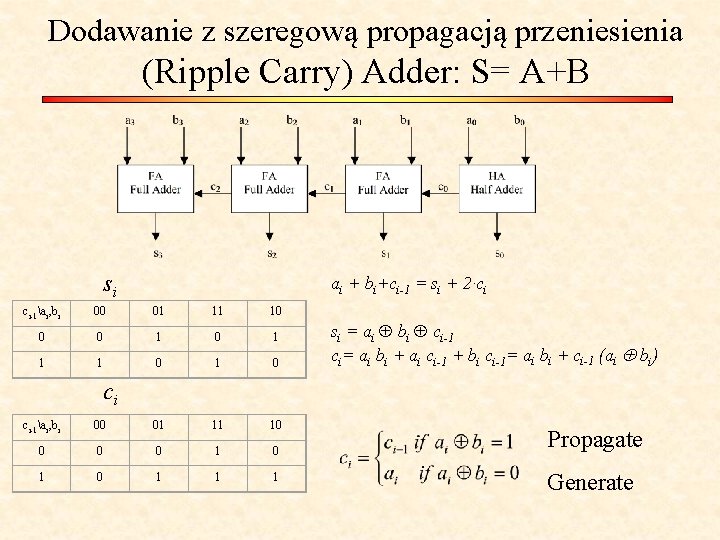

Dodawanie z szeregową propagacją przeniesienia (Ripple Carry) Adder: S= A+B si ai + bi+ci-1 = si + 2·ci ci-1ai, bi 00 01 11 10 0 0 1 1 1 0 si = ai bi ci-1 ci= ai bi + ai ci-1 + bi ci-1= ai bi + ci-1 (ai bi) ci ci-1ai, bi 00 01 11 10 0 1 0 1 1 1 Propagate Generate

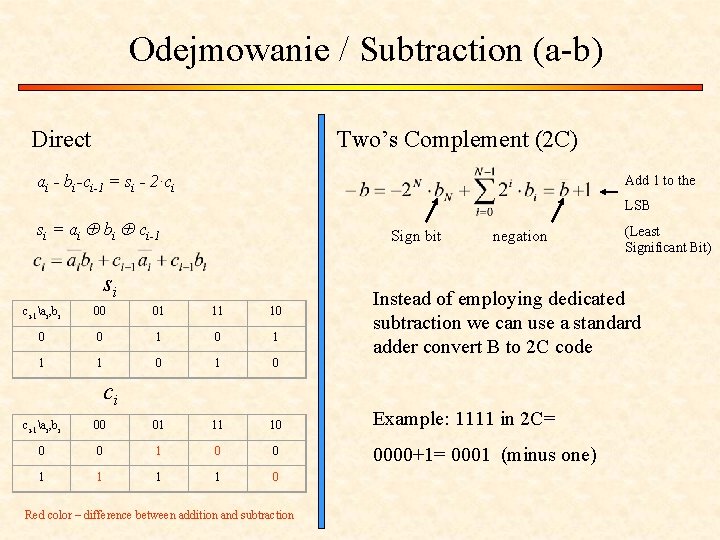

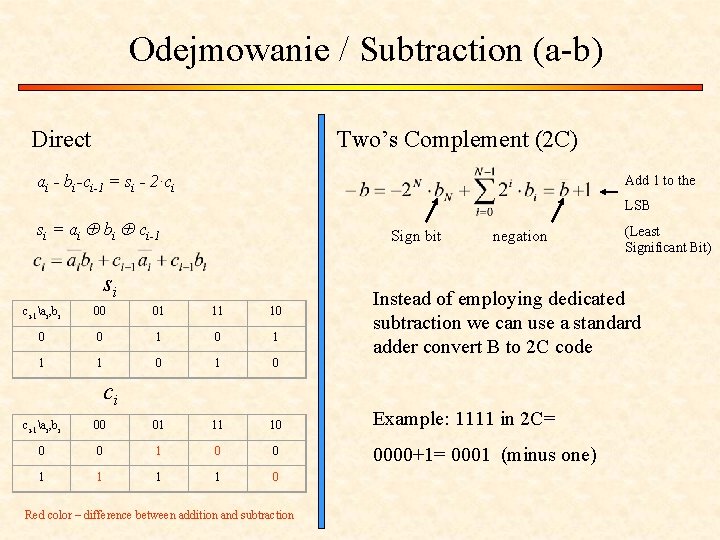

Odejmowanie / Subtraction (a-b) Direct Two’s Complement (2 C) ai - bi-ci-1 = si - 2·ci Add 1 to the LSB si = ai bi ci-1 Sign bit si ci-1ai, bi 00 01 11 10 0 0 1 1 1 0 ci ci-1ai, bi 00 01 11 10 0 0 1 1 1 1 0 Red color – difference between addition and subtraction negation (Least Significant Bit) Instead of employing dedicated subtraction we can use a standard adder convert B to 2 C code Example: 1111 in 2 C= 0000+1= 0001 (minus one)

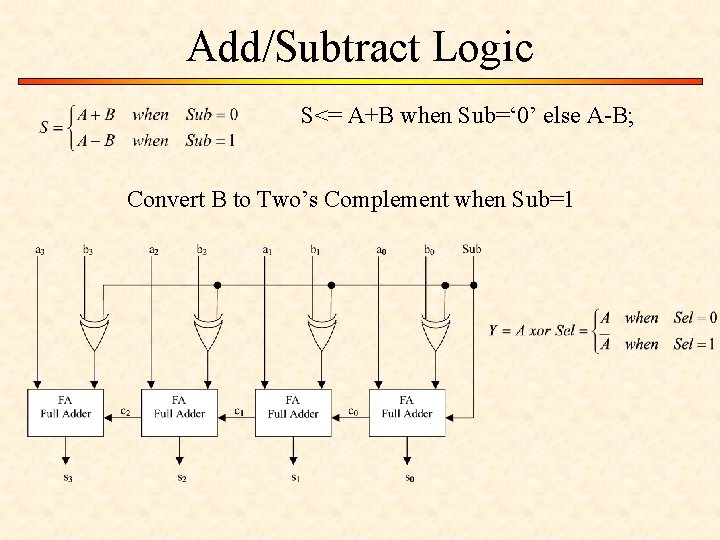

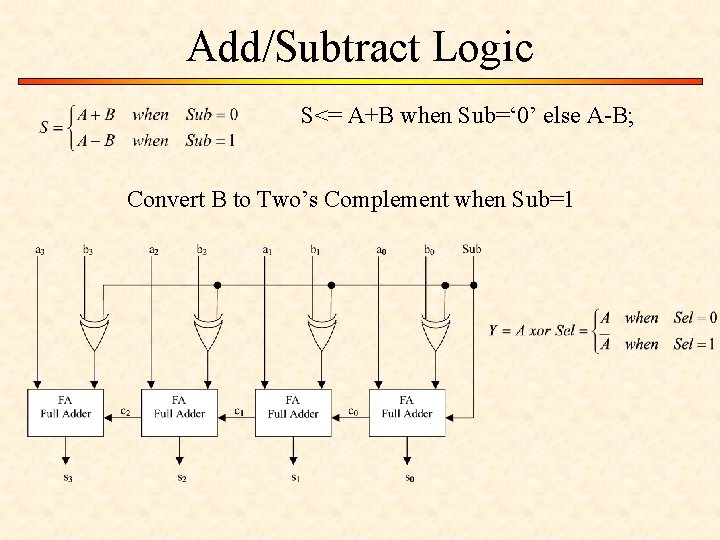

Add/Subtract Logic S<= A+B when Sub=‘ 0’ else A-B; Convert B to Two’s Complement when Sub=1

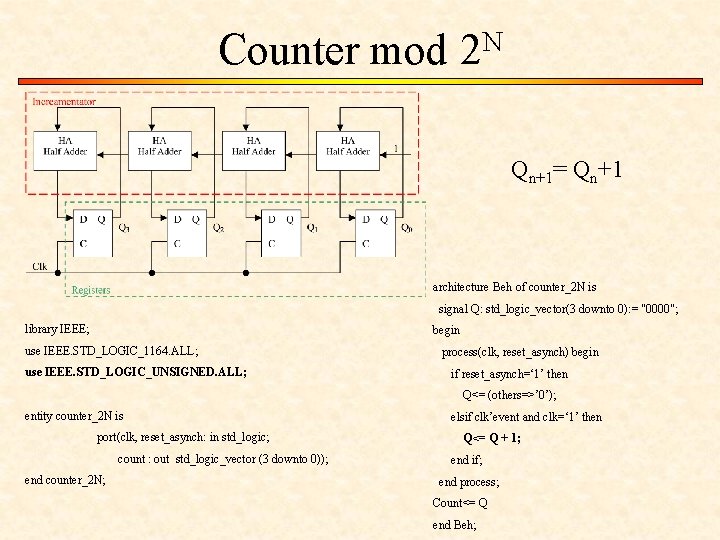

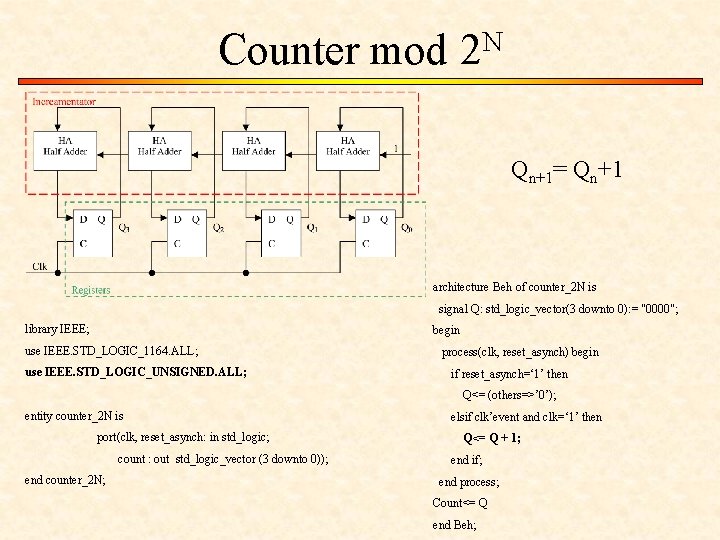

Counter mod N 2 Qn+1= Qn+1 architecture Beh of counter_2 N is signal Q: std_logic_vector(3 downto 0): = "0000"; library IEEE; begin use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; process(clk, reset_asynch) begin if reset_asynch=‘ 1’ then Q<= (others=>’ 0’); entity counter_2 N is port(clk, reset_asynch: in std_logic; count : out std_logic_vector (3 downto 0)); end counter_2 N; elsif clk’event and clk=‘ 1’ then Q<= Q + 1; end if; end process; Count<= Q end Beh;

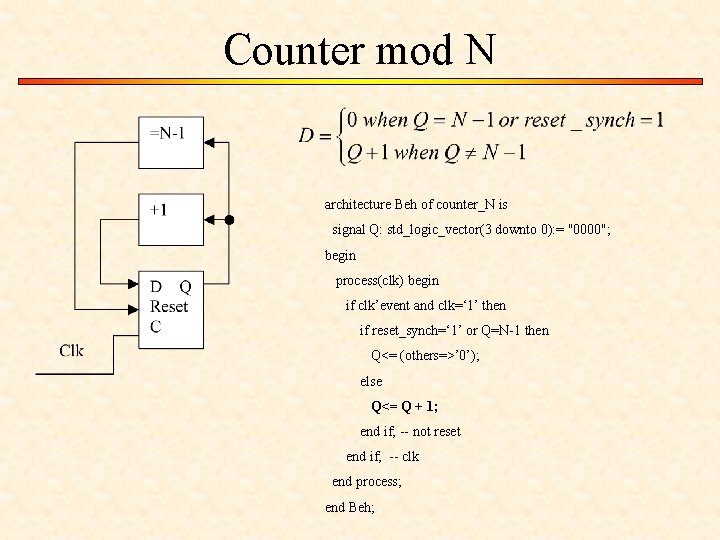

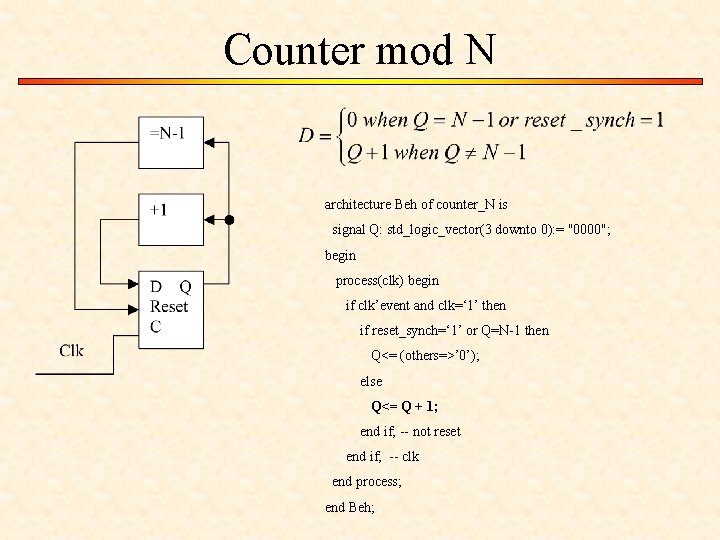

Counter mod N architecture Beh of counter_N is signal Q: std_logic_vector(3 downto 0): = "0000"; begin process(clk) begin if clk’event and clk=‘ 1’ then if reset_synch=‘ 1’ or Q=N-1 then Q<= (others=>’ 0’); else Q<= Q + 1; end if; -- not reset end if; -- clk end process; end Beh;

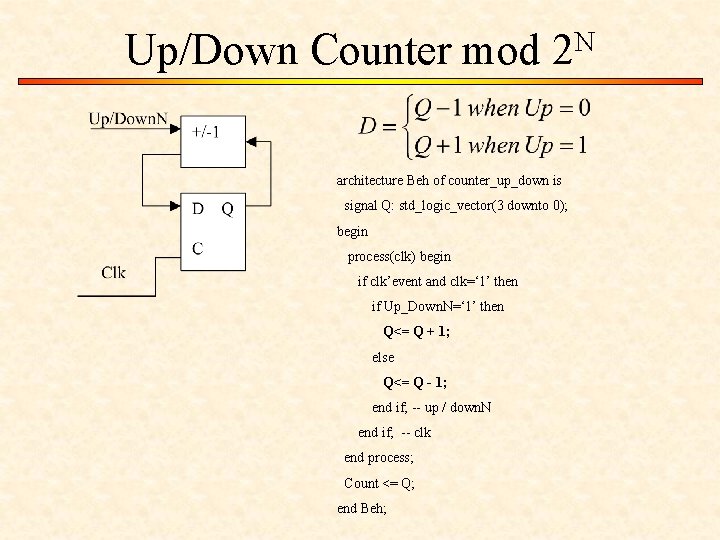

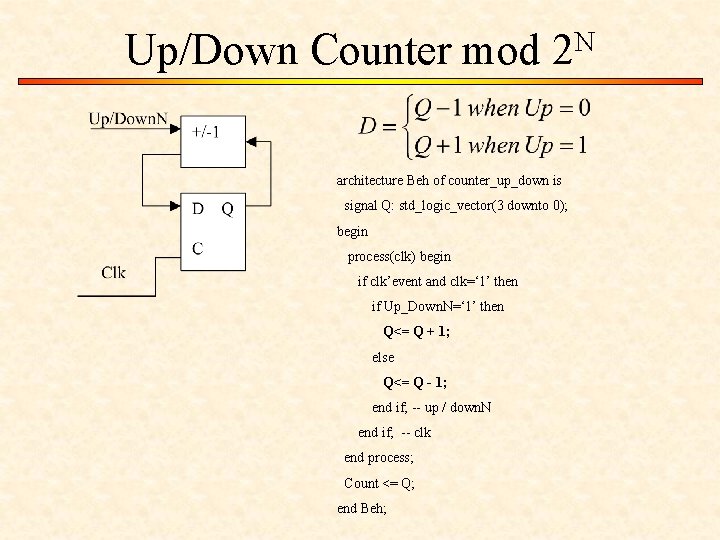

Up/Down Counter mod N 2 architecture Beh of counter_up_down is signal Q: std_logic_vector(3 downto 0); begin process(clk) begin if clk’event and clk=‘ 1’ then if Up_Down. N=‘ 1’ then Q<= Q + 1; else Q<= Q - 1; end if; -- up / down. N end if; -- clk end process; Count <= Q; end Beh;

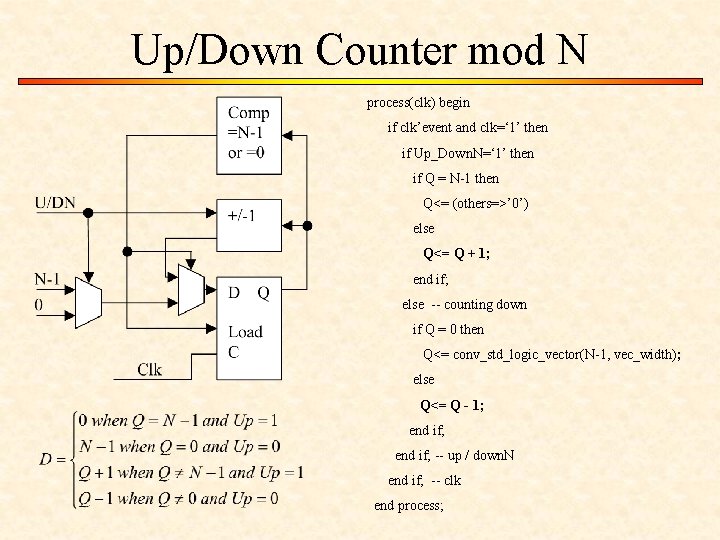

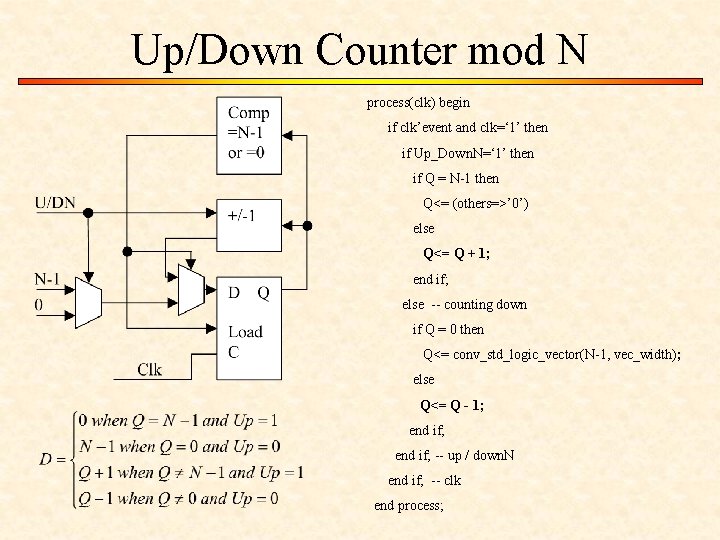

Up/Down Counter mod N process(clk) begin if clk’event and clk=‘ 1’ then if Up_Down. N=‘ 1’ then if Q = N-1 then Q<= (others=>’ 0’) else Q<= Q + 1; end if; else -- counting down if Q = 0 then Q<= conv_std_logic_vector(N-1, vec_width); else Q<= Q - 1; end if; -- up / down. N end if; -- clk end process;

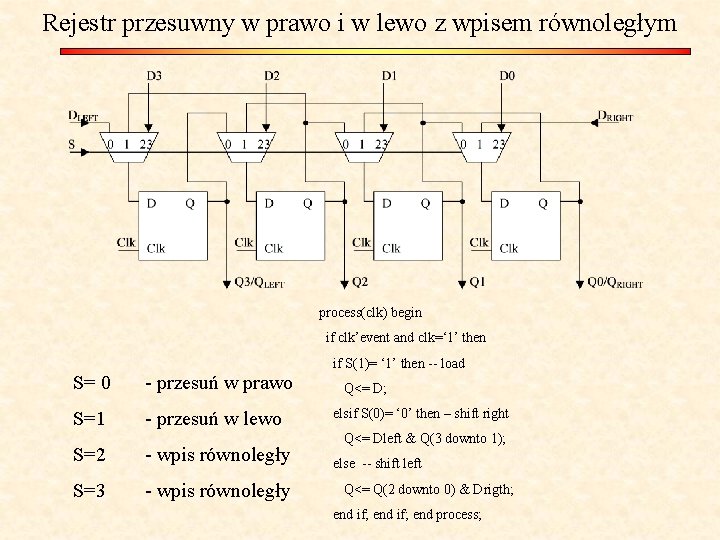

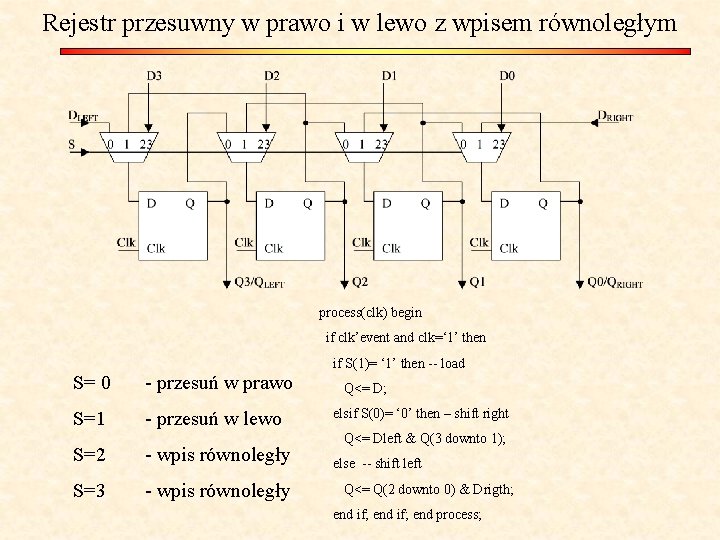

Rejestr przesuwny w prawo i w lewo z wpisem równoległym process(clk) begin if clk’event and clk=‘ 1’ then if S(1)= ‘ 1’ then -- load S= 0 - przesuń w prawo S=1 - przesuń w lewo S=2 - wpis równoległy S=3 - wpis równoległy Q<= D; elsif S(0)= ‘ 0’ then – shift right Q<= Dleft & Q(3 downto 1); else -- shift left Q<= Q(2 downto 0) & Drigth; end if; end process;

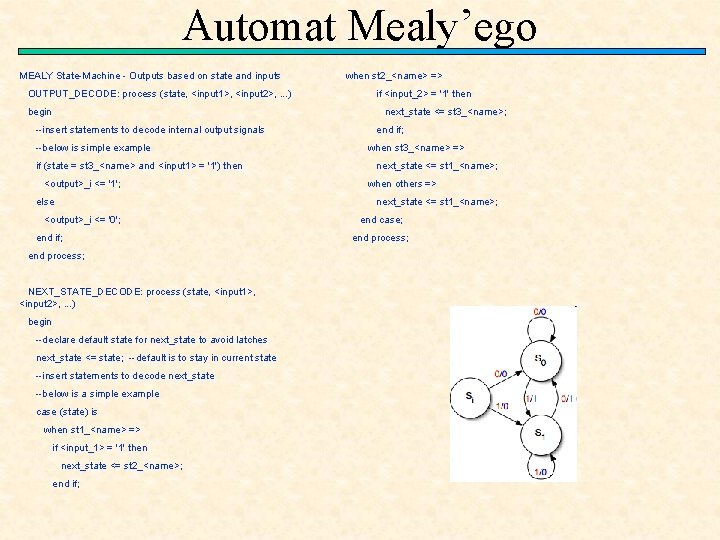

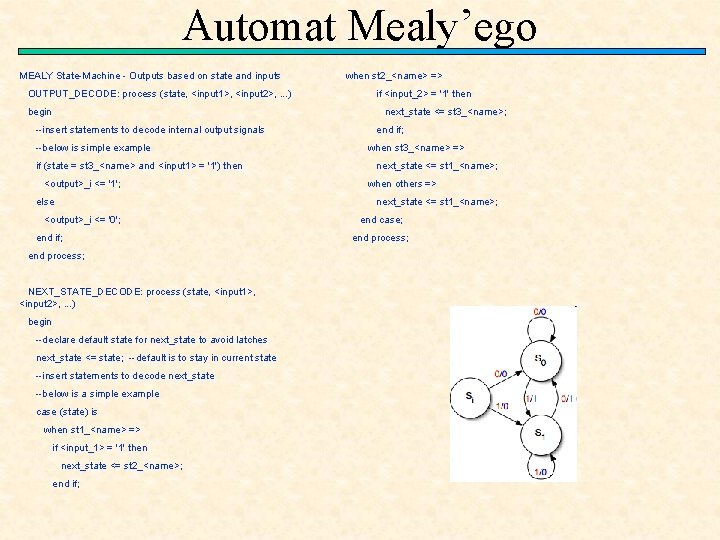

Automat Moore’a --Insert the following in the architecture before the begin keyword --Use descriptive names for the states, like st 1_reset, st 2_search type state_type is (st 1_<name_state>, st 2_<name_state>, . . . ); signal state, next_state : state_type; --Declare internal signals for all outputs of the state-machine signal <output>_i : std_logic; -- example output signal --other outputs --Insert the following in the architecture after the begin keyword SYNC_PROC: process (<clock>) begin if (<clock>'event and <clock> = '1') then if (<reset> = '1') then state <= st 1_<name_state>; <output> <= '0'; else state <= next_state; <output> <= <output>_i; -- assign other outputs to internal signals end if; end process;

Automat Mealy’ego MEALY State-Machine - Outputs based on state and inputs OUTPUT_DECODE: process (state, <input 1>, <input 2>, . . . ) when st 2_<name> => if <input_2> = '1' then next_state <= st 3_<name>; begin --insert statements to decode internal output signals --below is simple example if (state = st 3_<name> and <input 1> = '1') then <output>_i <= '1'; end if; when st 3_<name> => next_state <= st 1_<name>; when others => next_state <= st 1_<name>; else <output>_i <= '0'; end if; end process; NEXT_STATE_DECODE: process (state, <input 1>, <input 2>, . . . ) begin --declare default state for next_state to avoid latches next_state <= state; --default is to stay in current state --insert statements to decode next_state --below is a simple example case (state) is when st 1_<name> => if <input_1> = '1' then next_state <= st 2_<name>; end if; end case; end process;

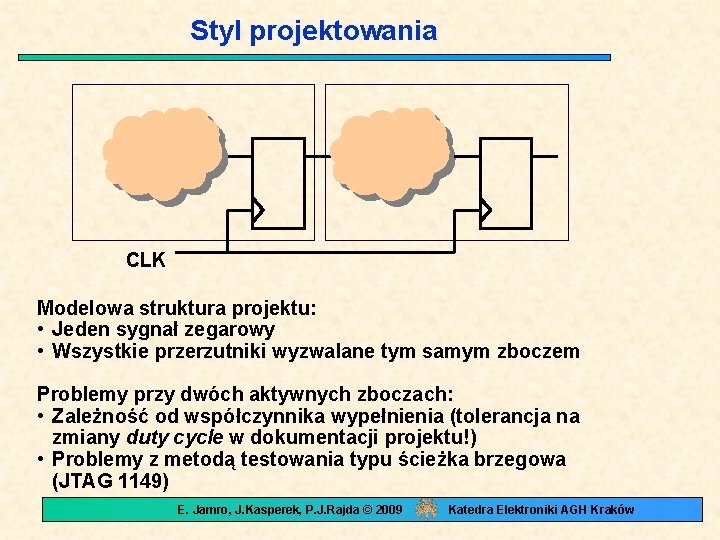

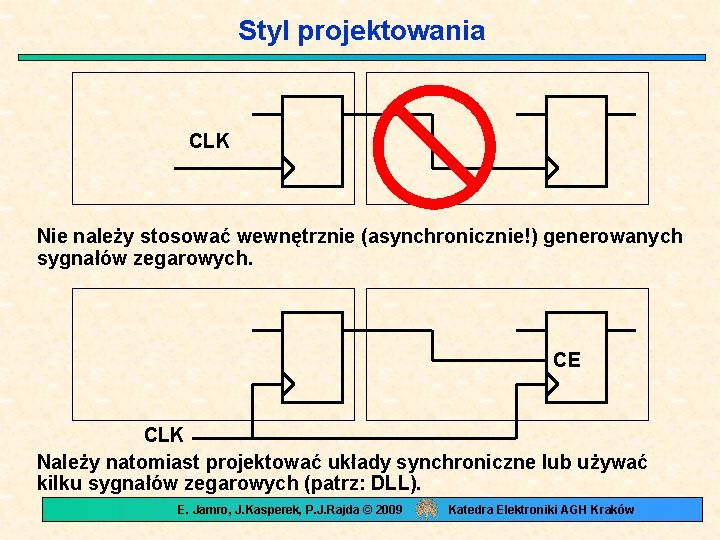

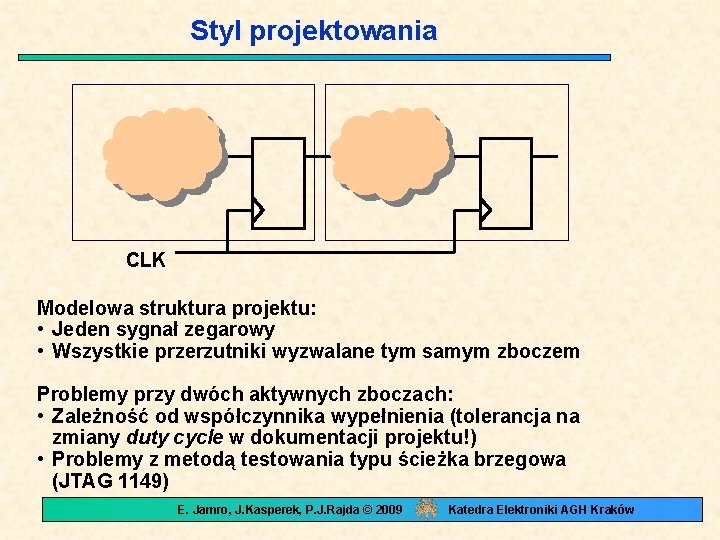

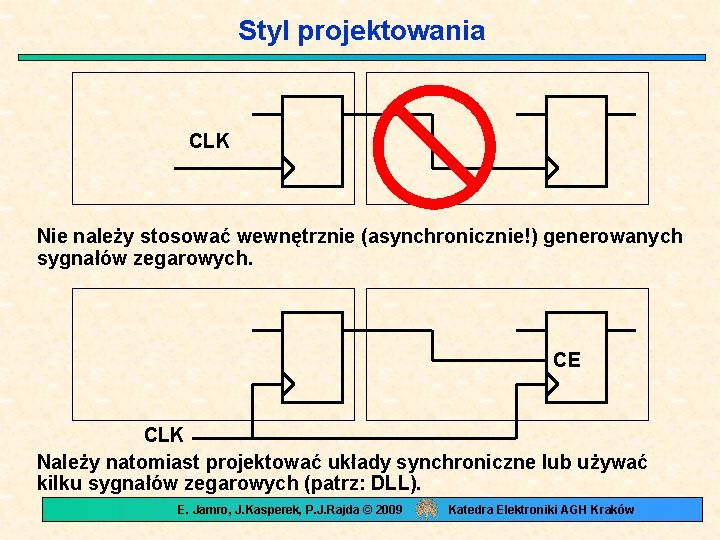

Styl projektowania CLK Modelowa struktura projektu: • Jeden sygnał zegarowy • Wszystkie przerzutniki wyzwalane tym samym zboczem Problemy przy dwóch aktywnych zboczach: • Zależność od współczynnika wypełnienia (tolerancja na zmiany duty cycle w dokumentacji projektu!) • Problemy z metodą testowania typu ścieżka brzegowa (JTAG 1149) E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

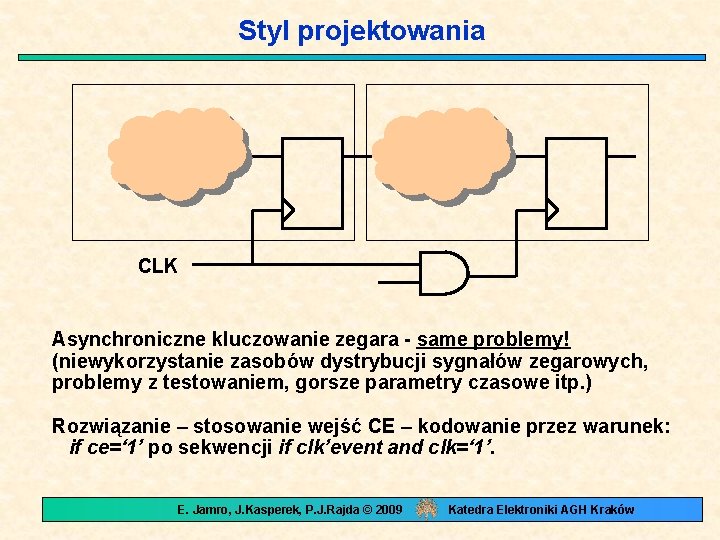

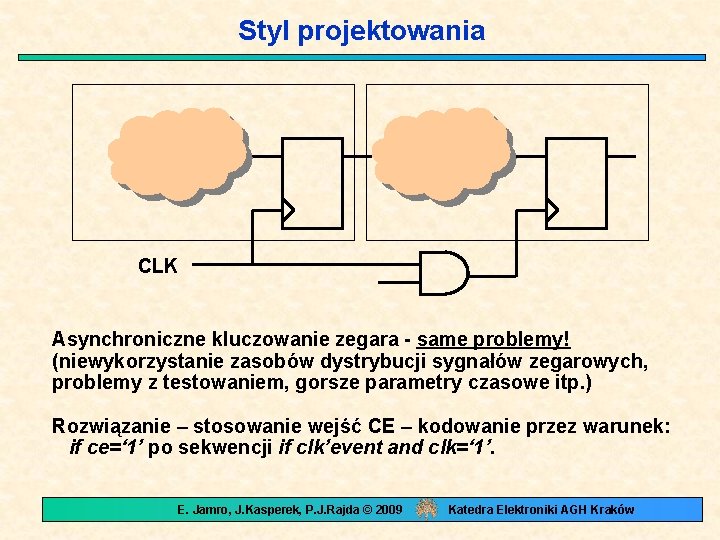

Styl projektowania CLK Asynchroniczne kluczowanie zegara - same problemy! (niewykorzystanie zasobów dystrybucji sygnałów zegarowych, problemy z testowaniem, gorsze parametry czasowe itp. ) Rozwiązanie – stosowanie wejść CE – kodowanie przez warunek: if ce=‘ 1’ po sekwencji if clk’event and clk=‘ 1’. E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

Styl projektowania CLK Nie należy stosować wewnętrznie (asynchronicznie!) generowanych sygnałów zegarowych. CE CLK Należy natomiast projektować układy synchroniczne lub używać kilku sygnałów zegarowych (patrz: DLL). E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

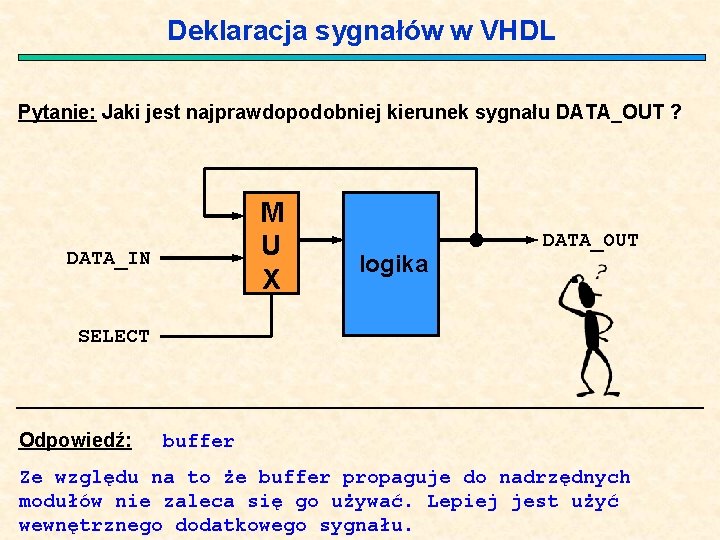

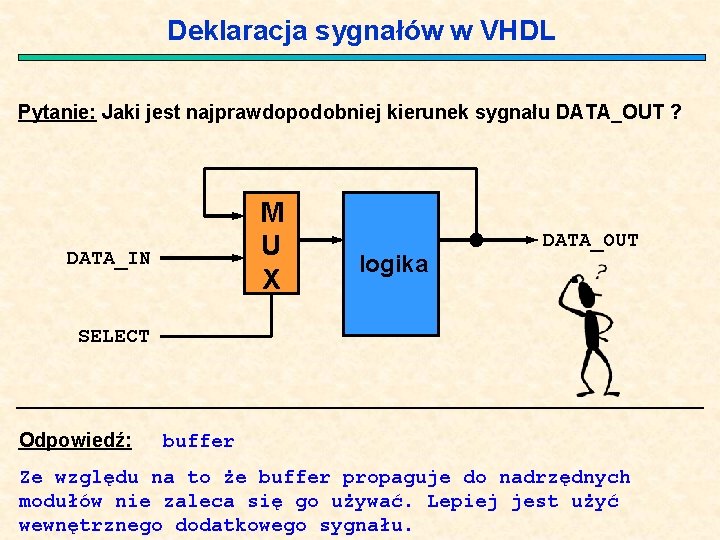

Deklaracja sygnałów w entity W deklaracji sygnału jako portu dla entity należy wyszczególnić: nazwę sygnału, jego kierunek, typ i opcjonalnie jego wartość początkową. Składnia: port (names: direction type [: = expression] [; more_ports]); Przykład: port (DATA_IN: in bit: = ‘ 0’; DATA_OUT: out bit); port (B, A: in std_logic_vector);

Deklaracja sygnałów w VHDL Pytanie: Jaki jest najprawdopodobniej kierunek sygnału DATA_OUT ? M U X DATA_IN logika DATA_OUT SELECT Odpowiedź: buffer Ze względu na to że buffer propaguje do nadrzędnych modułów nie zaleca się go używać. Lepiej jest użyć wewnętrznego dodatkowego sygnału.

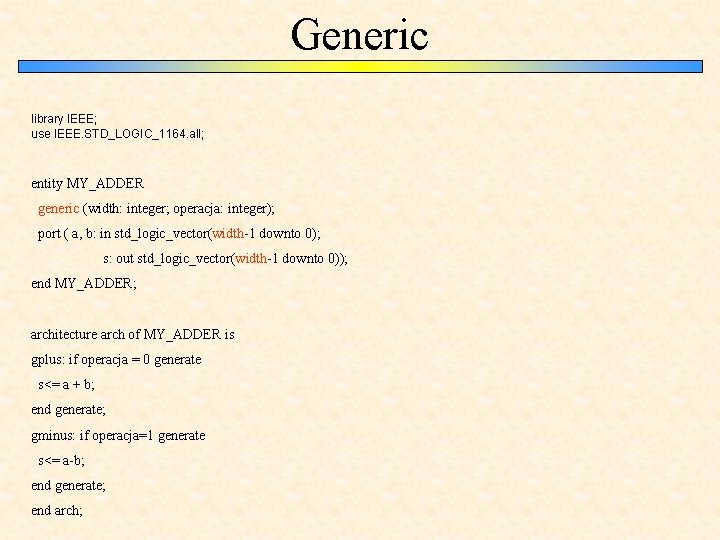

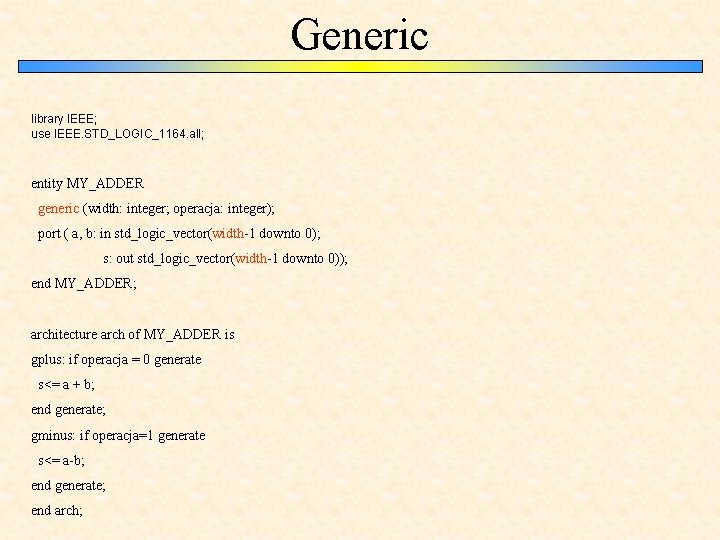

Generic library IEEE; use IEEE. STD_LOGIC_1164. all; entity MY_ADDER generic (width: integer; operacja: integer); port ( a, b: in std_logic_vector(width-1 downto 0); s: out std_logic_vector(width-1 downto 0)); end MY_ADDER; architecture arch of MY_ADDER is gplus: if operacja = 0 generate s<= a + b; end generate; gminus: if operacja=1 generate s<= a-b; end generate; end arch;

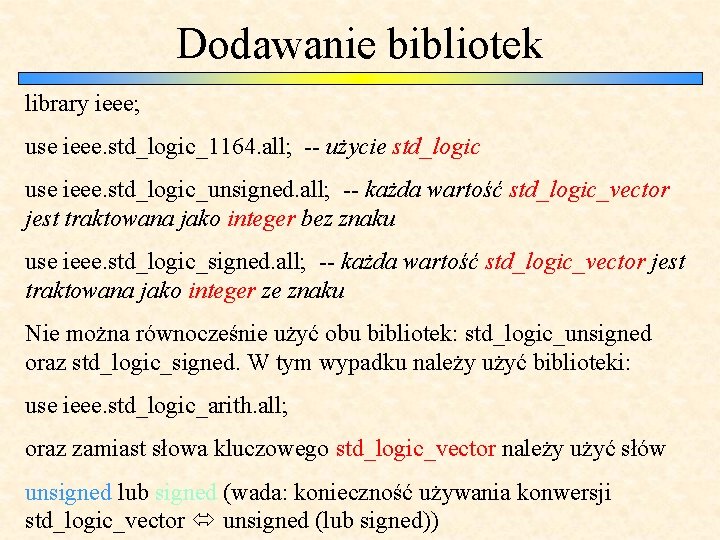

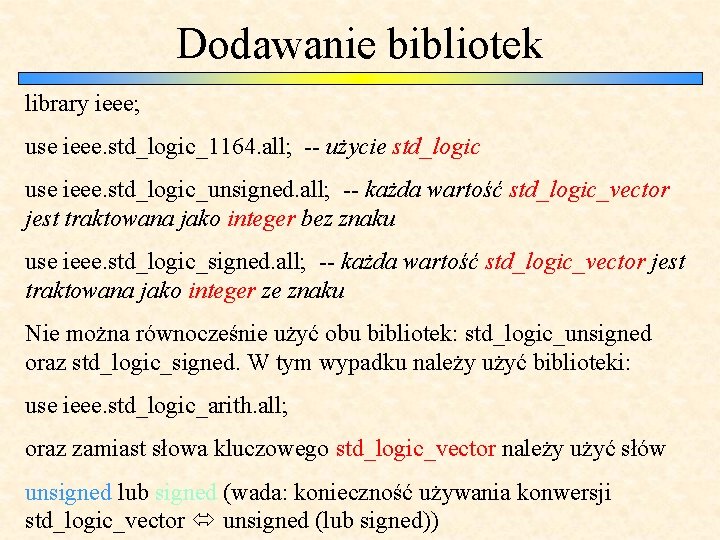

Dodawanie bibliotek library ieee; use ieee. std_logic_1164. all; -- użycie std_logic use ieee. std_logic_unsigned. all; -- każda wartość std_logic_vector jest traktowana jako integer bez znaku use ieee. std_logic_signed. all; -- każda wartość std_logic_vector jest traktowana jako integer ze znaku Nie można równocześnie użyć obu bibliotek: std_logic_unsigned oraz std_logic_signed. W tym wypadku należy użyć biblioteki: use ieee. std_logic_arith. all; oraz zamiast słowa kluczowego std_logic_vector należy użyć słów unsigned lub signed (wada: konieczność używania konwersji std_logic_vector unsigned (lub signed))

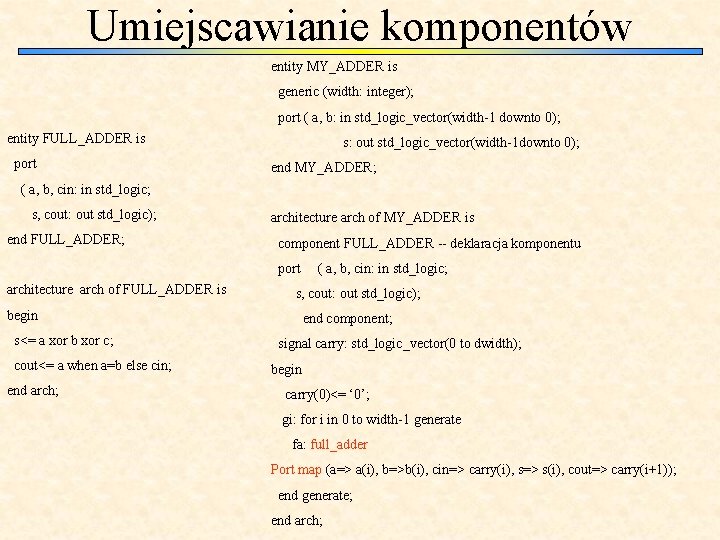

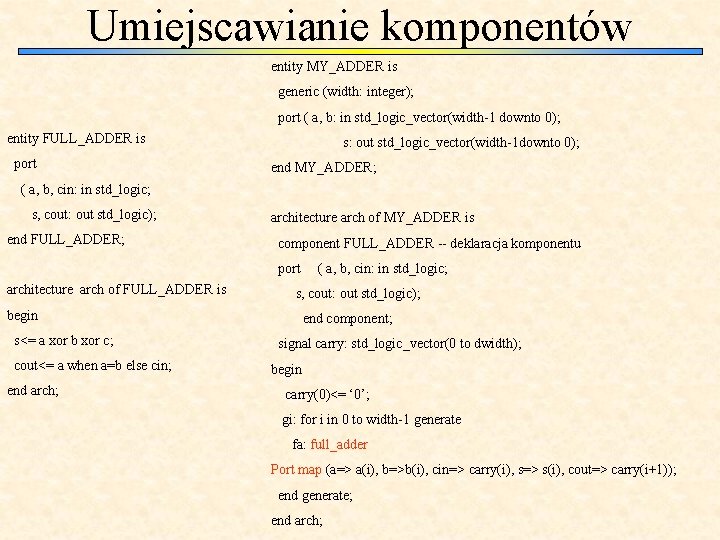

Umiejscawianie komponentów entity MY_ADDER is generic (width: integer); port ( a, b: in std_logic_vector(width-1 downto 0); entity FULL_ADDER is port s: out std_logic_vector(width-1 downto 0); end MY_ADDER; ( a, b, cin: in std_logic; s, cout: out std_logic); end FULL_ADDER; architecture arch of MY_ADDER is component FULL_ADDER -- deklaracja komponentu port architecture arch of FULL_ADDER is s, cout: out std_logic); begin s<= a xor b xor c; cout<= a when a=b else cin; end arch; ( a, b, cin: in std_logic; end component; signal carry: std_logic_vector(0 to dwidth); begin carry(0)<= ‘ 0’; gi: for i in 0 to width-1 generate fa: full_adder Port map (a=> a(i), b=>b(i), cin=> carry(i), s=> s(i), cout=> carry(i+1)); end generate; end arch;

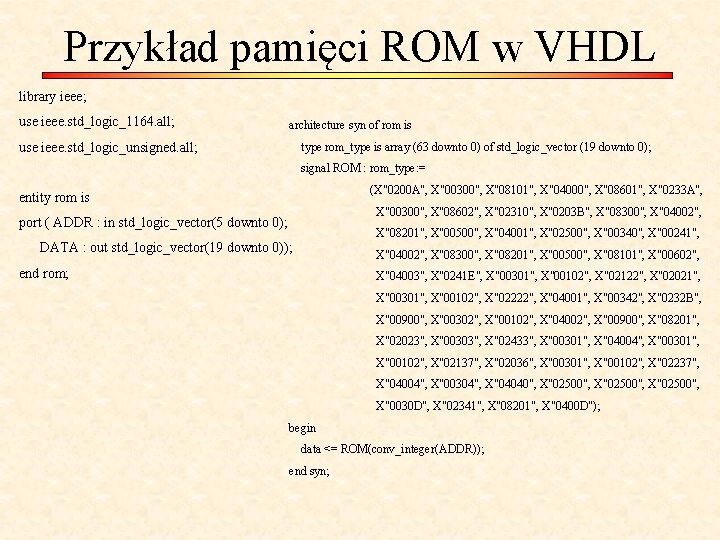

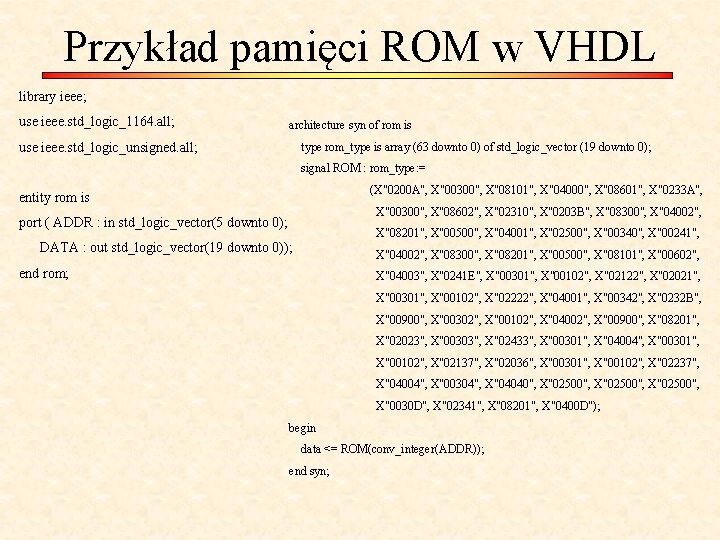

Przykład pamięci ROM w VHDL library ieee; use ieee. std_logic_1164. all; architecture syn of rom is use ieee. std_logic_unsigned. all; type rom_type is array (63 downto 0) of std_logic_vector (19 downto 0); signal ROM : rom_type: = (X"0200 A", X"00300", X"08101", X"04000", X"08601", X"0233 A", entity rom is X"00300", X"08602", X"02310", X"0203 B", X"08300", X"04002", port ( ADDR : in std_logic_vector(5 downto 0); X"08201", X"00500", X"04001", X"02500", X"00340", X"00241", DATA : out std_logic_vector(19 downto 0)); X"04002", X"08300", X"08201", X"00500", X"08101", X"00602", end rom; X"04003", X"0241 E", X"00301", X"00102", X"02122", X"02021", X"00301", X"00102", X"02222", X"04001", X"00342", X"0232 B", X"00900", X"00302", X"00102", X"04002", X"00900", X"08201", X"02023", X"00303", X"02433", X"00301", X"04004", X"00301", X"00102", X"02137", X"02036", X"00301", X"00102", X"02237", X"04004", X"00304", X"04040", X"02500", X"0030 D", X"02341", X"08201", X"0400 D"); begin data <= ROM(conv_integer(ADDR)); end syn;

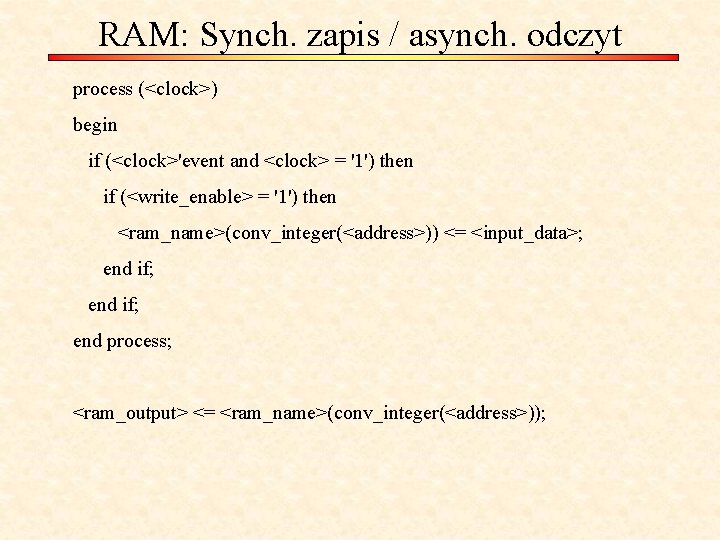

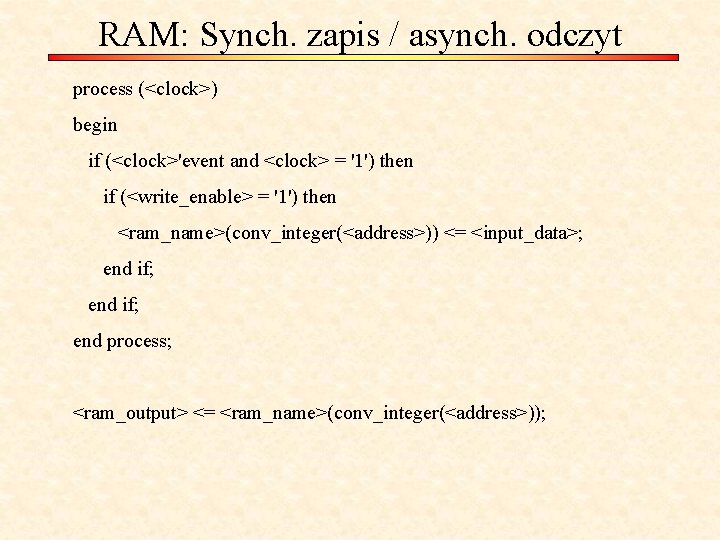

RAM: Synch. zapis / asynch. odczyt process (<clock>) begin if (<clock>'event and <clock> = '1') then if (<write_enable> = '1') then <ram_name>(conv_integer(<address>)) <= <input_data>; end if; end process; <ram_output> <= <ram_name>(conv_integer(<address>));

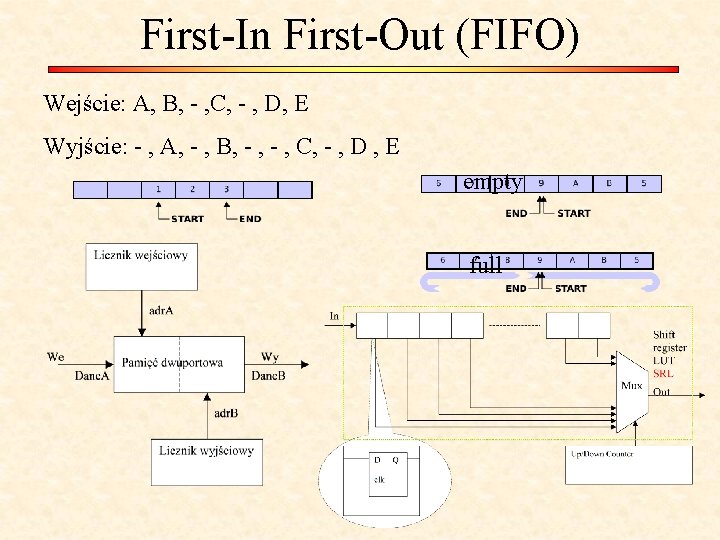

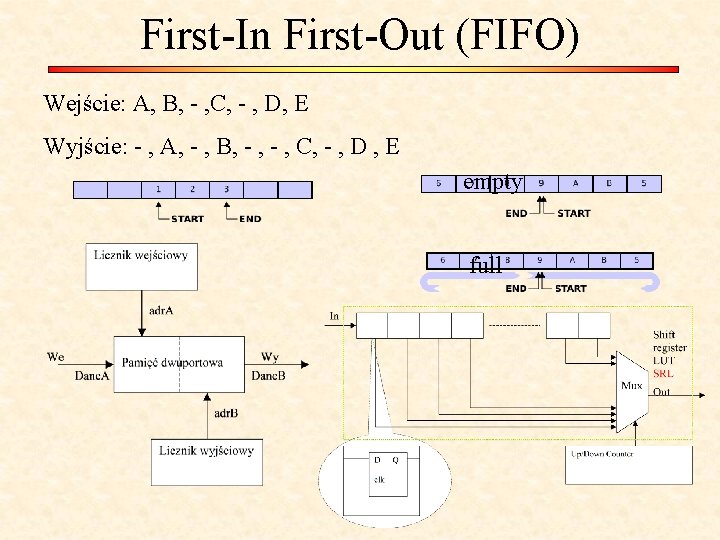

First-In First-Out (FIFO) Wejście: A, B, - , C, - , D, E Wyjście: - , A, - , B, - , C, - , D , E empty full

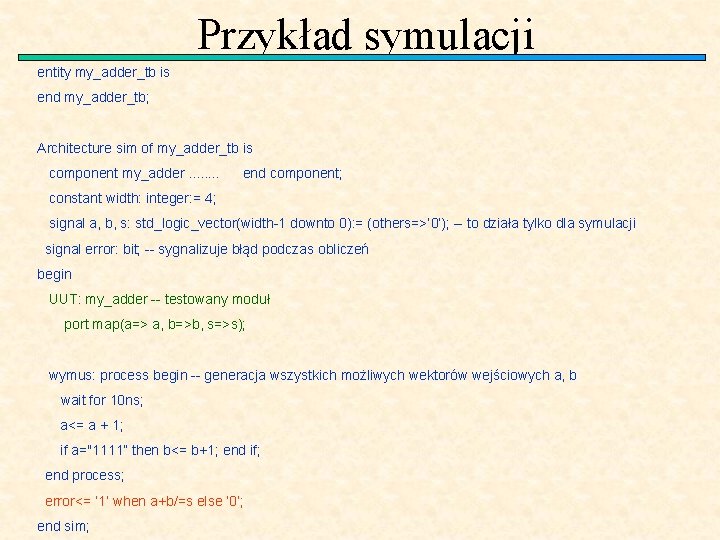

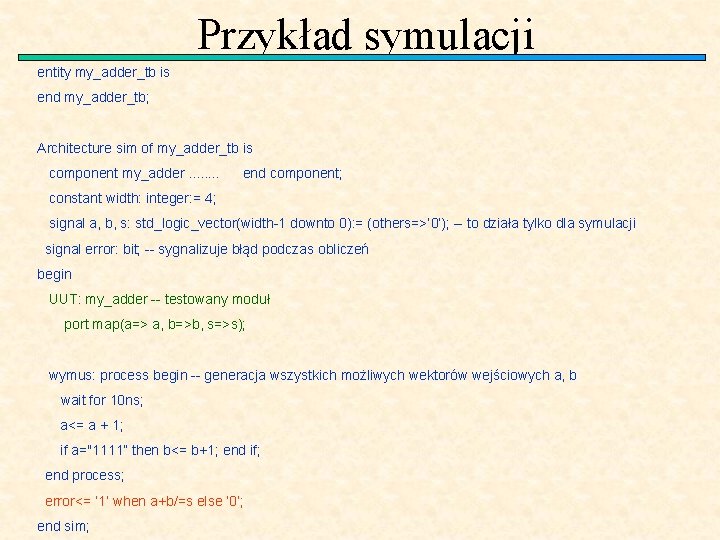

TESTBENCH – połączenie Process/Component Process Test. Bench Component Signals UUT Rodzaje procesów testujących • Ad Hoc Zbiór wektorów testowych do podstawowych testów funkcjonalnych. • Algorytmiczny Prosty algorytm generujący wymuszenia, np. pętla zwiększająca zmienną przez cały jej zakres do testowania dekodera lub ALU. • Plik wektorów Rozwiązanie strukturalne: proces czytający plik z wektorami do testowania. E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

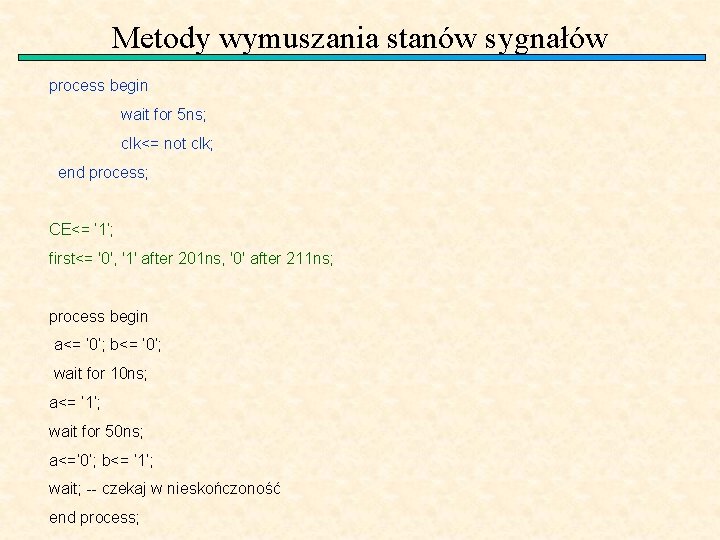

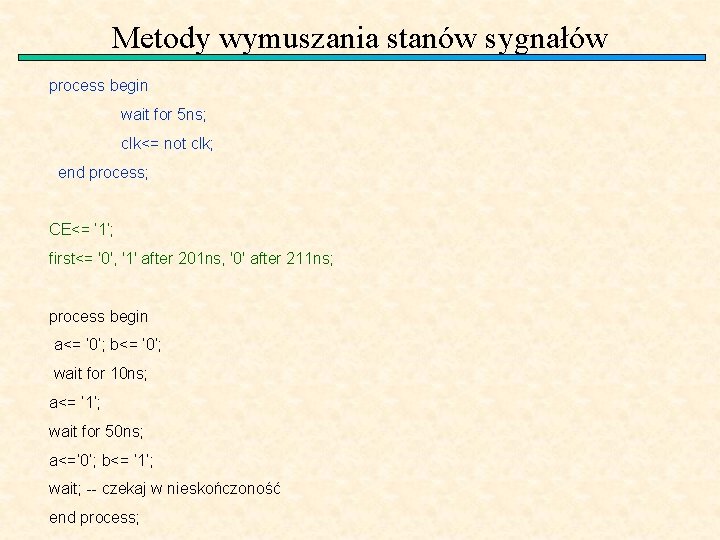

Przykład symulacji entity my_adder_tb is end my_adder_tb; Architecture sim of my_adder_tb is component my_adder. . . . end component; constant width: integer: = 4; signal a, b, s: std_logic_vector(width-1 downto 0): = (others=>’ 0’); -- to działa tylko dla symulacji signal error: bit; -- sygnalizuje błąd podczas obliczeń begin UUT: my_adder -- testowany moduł port map(a=> a, b=>b, s=>s); wymus: process begin -- generacja wszystkich możliwych wektorów wejściowych a, b wait for 10 ns; a<= a + 1; if a="1111” then b<= b+1; end if; end process; error<= ‘ 1’ when a+b/=s else ‘ 0’; end sim;

Metody wymuszania stanów sygnałów process begin wait for 5 ns; clk<= not clk; end process; CE<= ‘ 1’; first<= '0', '1' after 201 ns, '0' after 211 ns; process begin a<= ‘ 0’; b<= ‘ 0’; wait for 10 ns; a<= ‘ 1’; wait for 50 ns; a<=‘ 0’; b<= ‘ 1’; wait; -- czekaj w nieskończoność end process;

VHDL – literatura „A Guide to VHDL”, S. Mazor, P. Langstraat „VHDL Analysis and Modelling of Digital Systems”, Z. Navabi „VHDL Hardware Description and Design”, R. Lipsett, C. Schaefer, C. Ussery „The VHDL Cookbook”, P. J. Ashenden „VHDL programming: with advanced topics”, L. Baker „VHDL starter's guide”, S. Yalamanchili „VHDL for designers”, S. Sjoholm, L. Lindh „VHDL made easy!”, D. Pellerin, D. Taylor „VHDL answers to frequently asked questions”, B. Cohen „VHDL and AHDL digital systems implementation”, F. A. Scarpino „VHDL: język opisu i projektowania układów cyfrowych”, W. Wrona „Active-VHDL Series BOOK#2 – EVITA Interactive Tutorial”, J. Mirkowski, M. Kapustka, Z. Skowroński, A. Biniszkiewicz „VHDL: a logic synthesis approach”, D. Naylor, S. Jones E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

VHDL – literatura Kevin Skahill Marek Zwoliński E. Jamro, J. Kasperek, P. J. Rajda © 2009 Józef Kalisz Włodzimierz Wrona Katedra Elektroniki AGH Kraków

VHDL – zasoby w Internecie • http: //fpga. elektro. agh. edu. pl • • • VHDL: http: //www. vhdl. org/ Grupa dyskusyjna: comp. lang. vhdl (FAQ - 4 części) Accellera: http: //www. accellera. org/ EDA Industry Working Groups homepage: http: //www. eda. org/ FPGA Journal http: //www. fpgajournal. com/ - (ładne lekcje Chalk. Talk ) Design Automation Cafe: http: //www. dacafe. com/ Doulos High Level Design Web site: http: //www. doulos. com/ VHDL-online, University of Erlangen-Nürnberg: http: //www. vhdl-online. de/ VHDL info pages of the Microelectronics Department (University of Ulm, Germany): http: //mikro. e-technik. uni-ulm. de/vhdl_infos. html E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

VHDL – tutoriale • Evita Interactive VHDL Tutorial from Aldec, Inc. : • http: //www. aldec. com • • • Doulos High Level Design Web site; A Hardware Engineers Guide to VHDL: http: //www. doulos. com/hegv/index. htm An Introductory VHDL Tutorial, Green Mountain Computing Systems: http: //www. gmvhdl. com/VHDL. html VHDL Tutorial by Ulrich Heinkel, Thomas Bürner and Martin Padeffke (in English and German): http: //www. vhdl-online. de/~vhdl/TUTORIAL/ VHDL-FSM-Tutorial by Martin Padeffke: http: //www. vhdl-online. de/FSM/ VHDL Verification Course by Stefan Doll: http: //www. stefan. VHDL. com/ E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków

VHDL – free IP cores • • Open. IP home page: http: //www. opencores. org System On Chip http: //www. soccentral. com/ • Free behavioral models from Alatek: http: //www. alatek. com/ • • • The Hamburg VHDL archive: http: //tams-www. informatik. uni-hamburg. de/research/vlsi/vhdl/ Rapid Prototyping of Application Specific Signal Processors (RASSP) www site: http: //www. eda. org/rassp/ Doulos High Level Design Web site; Monthly-updated Original Models (developed by Doulos): http: //www. doulos. com/fi/ A VHDL synthesizable model for the MICROCHIP PIC 16 C 5 X microcontroller by Tom Coonan: http: //www. mindspring. com/~tcoonan/ VHDL Library of Arithmetic Units developed by R. Zimmermann: http: //www. iis. ee. ethz. ch/~zimmi/arith_lib. html E. Jamro, J. Kasperek, P. J. Rajda © 2009 Katedra Elektroniki AGH Kraków