Nonlinear Neural Networks LAB CHAPTER 20 VHDL FOR

Nonlinear & Neural Networks LAB. CHAPTER 20 VHDL FOR DIGITAL SYSYEM DESIGN 20. 1 20. 2 20. 3 20. 4 20. 5 VHDL Code for a Serial Adder VHDL Code for a Binary Multiplier VHDL Code for a Binary Divider VHDL Code for a Dice Game Simulator Concluding Remarks

Objectives 1. Given a block diagram and state graph for a digital system’s control unit. Write behavioral VHDL code for system. Use one clocked process 2. Compile and simulate VHDL code you wrote for step 1 3. Write synthesizable VHDL code for the system using control signals. Use two processes, one for combinational logic and one for updating registers 4. Compile, simulate, and synthesize the VHDL code for step. 3 5. Write a VHDL test bench to test a VHDL module Nonlinear & Neural Networks LAB.

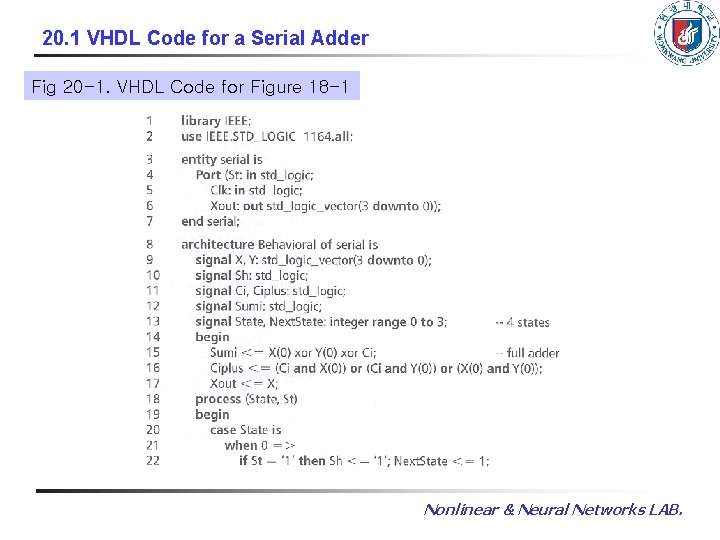

20. 1 VHDL Code for a Serial Adder Fig 20 -1. VHDL Code for Figure 18 -1 Nonlinear & Neural Networks LAB.

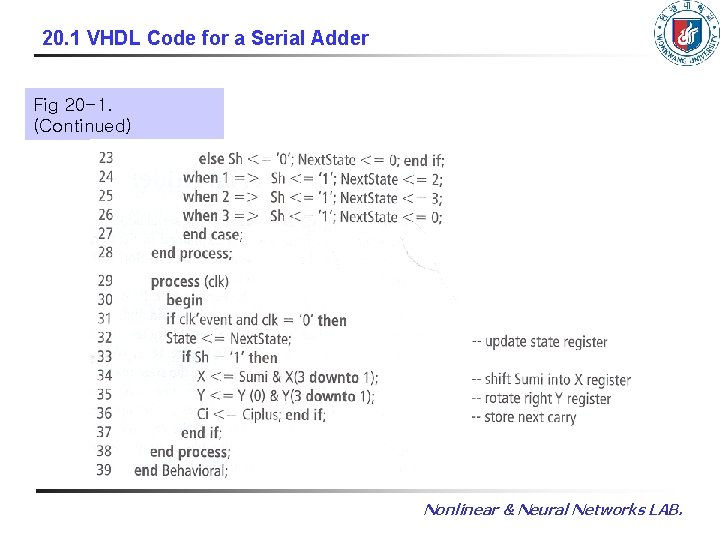

20. 1 VHDL Code for a Serial Adder Fig 20 -1. (Continued) Nonlinear & Neural Networks LAB.

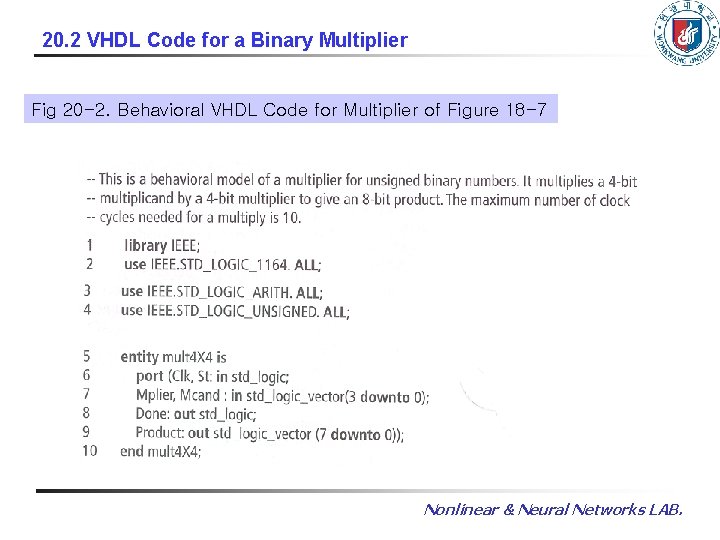

20. 2 VHDL Code for a Binary Multiplier Fig 20 -2. Behavioral VHDL Code for Multiplier of Figure 18 -7 Nonlinear & Neural Networks LAB.

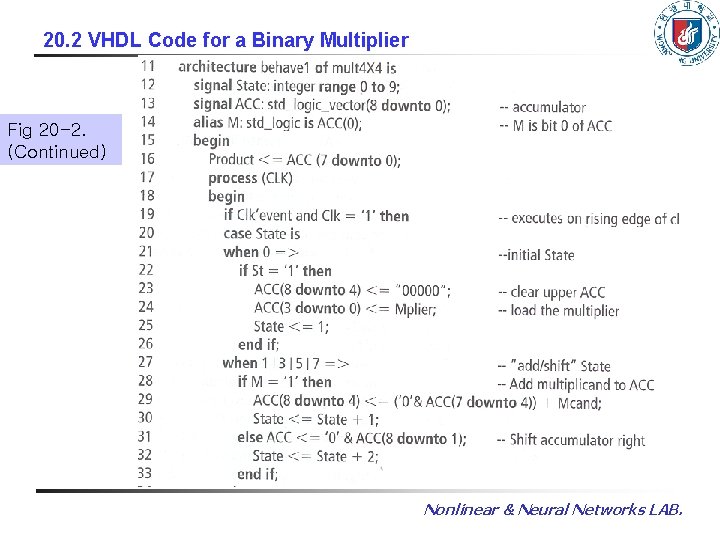

20. 2 VHDL Code for a Binary Multiplier Fig 20 -2. (Continued) Nonlinear & Neural Networks LAB.

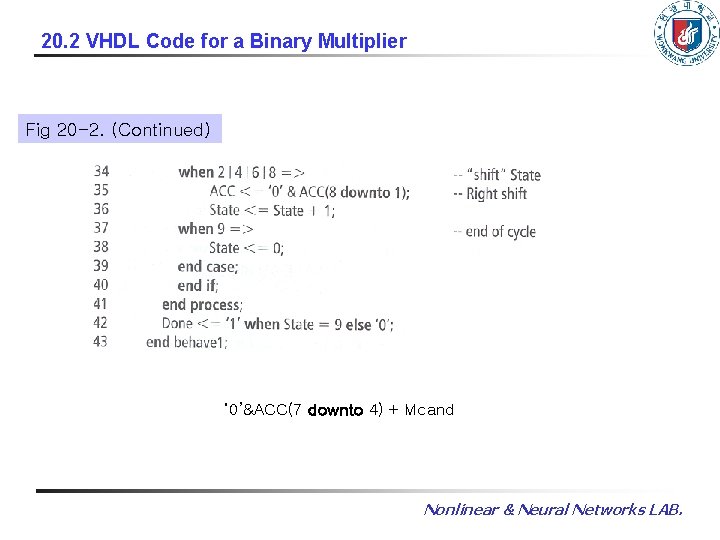

20. 2 VHDL Code for a Binary Multiplier Fig 20 -2. (Continued) ‘ 0’&ACC(7 downto 4) + Mcand Nonlinear & Neural Networks LAB.

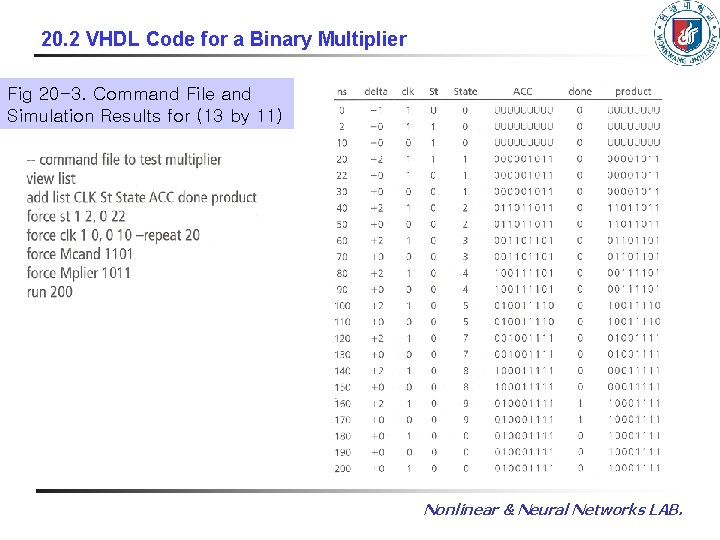

20. 2 VHDL Code for a Binary Multiplier Fig 20 -3. Command File and Simulation Results for (13 by 11) Nonlinear & Neural Networks LAB.

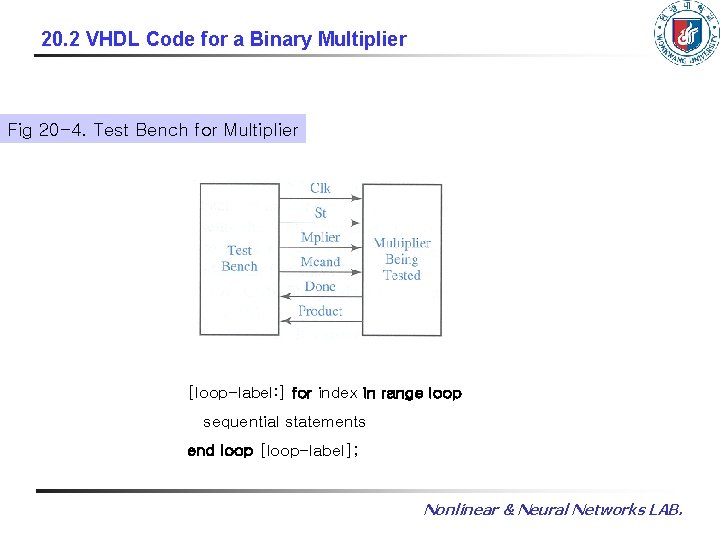

20. 2 VHDL Code for a Binary Multiplier Fig 20 -4. Test Bench for Multiplier [loop-label: ] for index in range loop sequential statements end loop [loop-label]; Nonlinear & Neural Networks LAB.

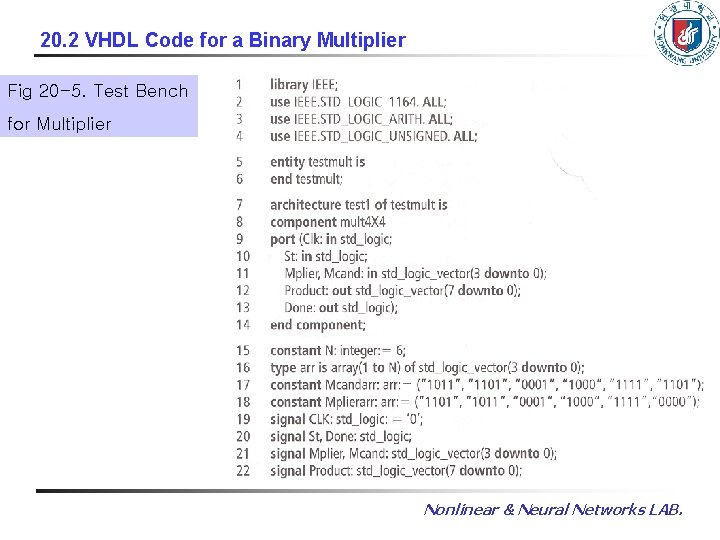

20. 2 VHDL Code for a Binary Multiplier Fig 20 -5. Test Bench for Multiplier Nonlinear & Neural Networks LAB.

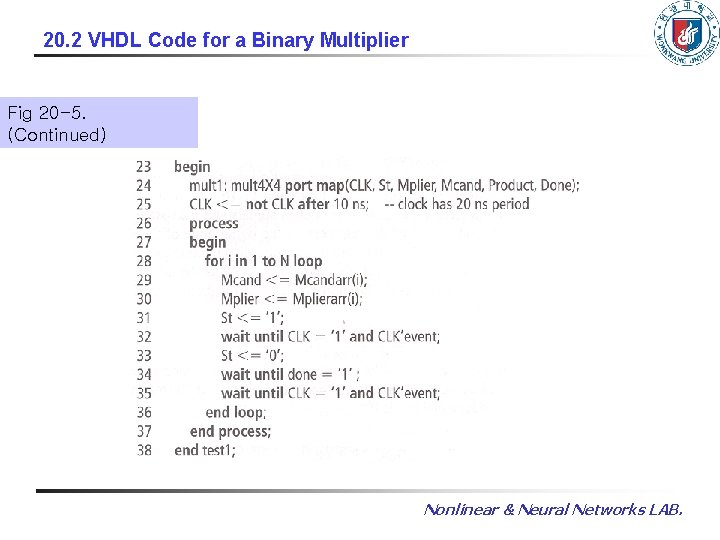

20. 2 VHDL Code for a Binary Multiplier Fig 20 -5. (Continued) Nonlinear & Neural Networks LAB.

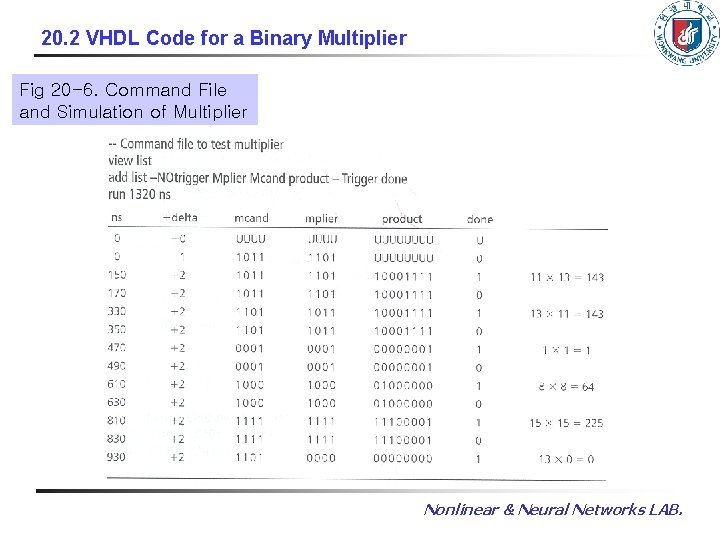

20. 2 VHDL Code for a Binary Multiplier Fig 20 -6. Command File and Simulation of Multiplier Nonlinear & Neural Networks LAB.

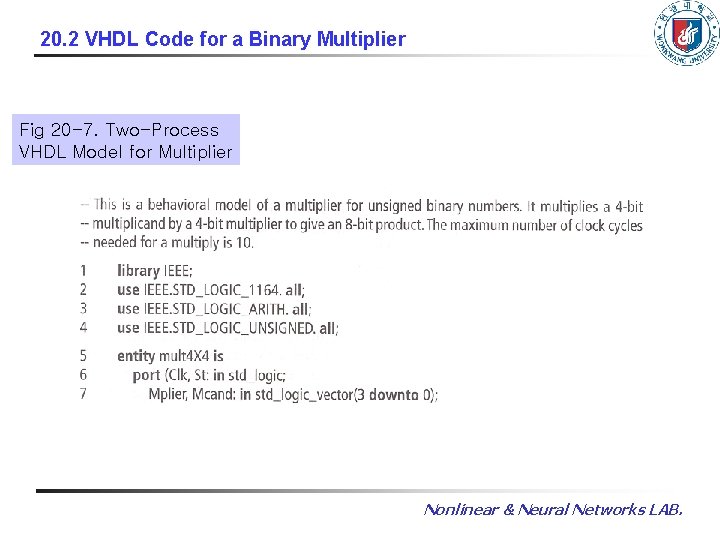

20. 2 VHDL Code for a Binary Multiplier Fig 20 -7. Two-Process VHDL Model for Multiplier Nonlinear & Neural Networks LAB.

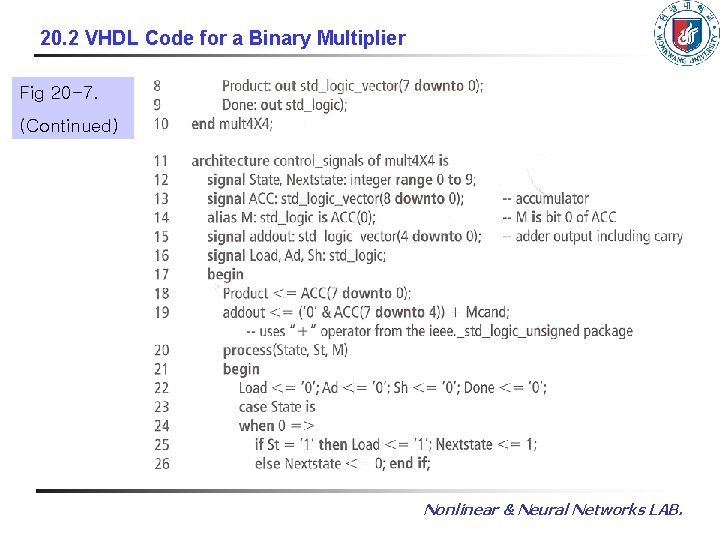

20. 2 VHDL Code for a Binary Multiplier Fig 20 -7. (Continued) Nonlinear & Neural Networks LAB.

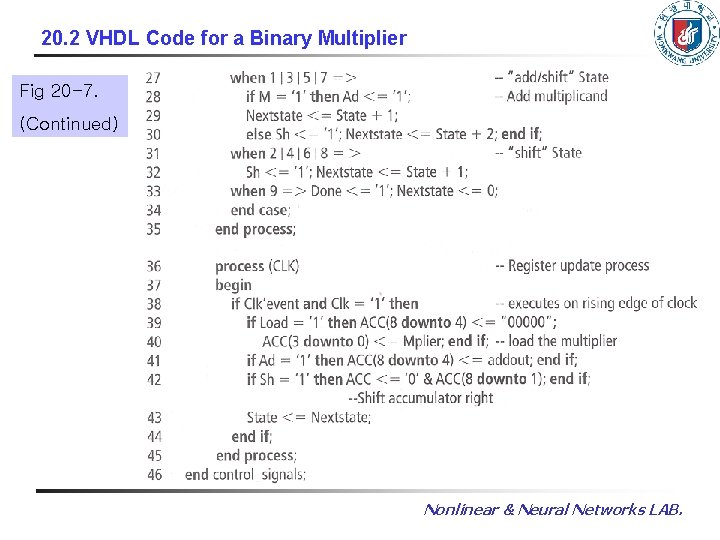

20. 2 VHDL Code for a Binary Multiplier Fig 20 -7. (Continued) Nonlinear & Neural Networks LAB.

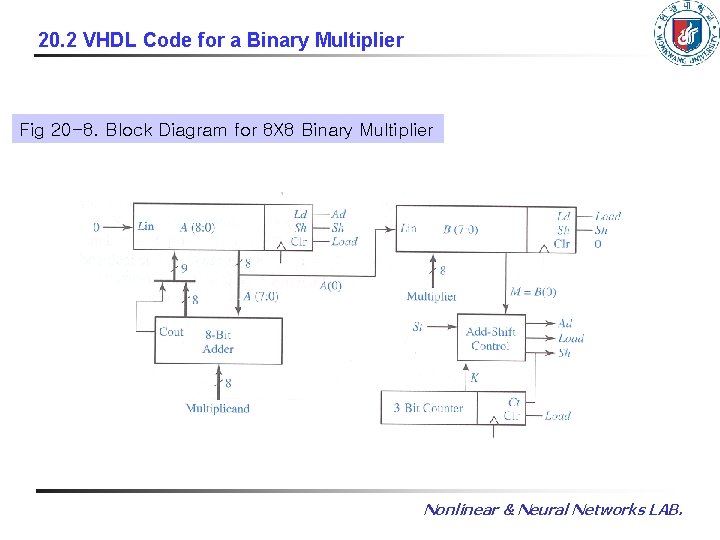

20. 2 VHDL Code for a Binary Multiplier Fig 20 -8. Block Diagram for 8 X 8 Binary Multiplier Nonlinear & Neural Networks LAB.

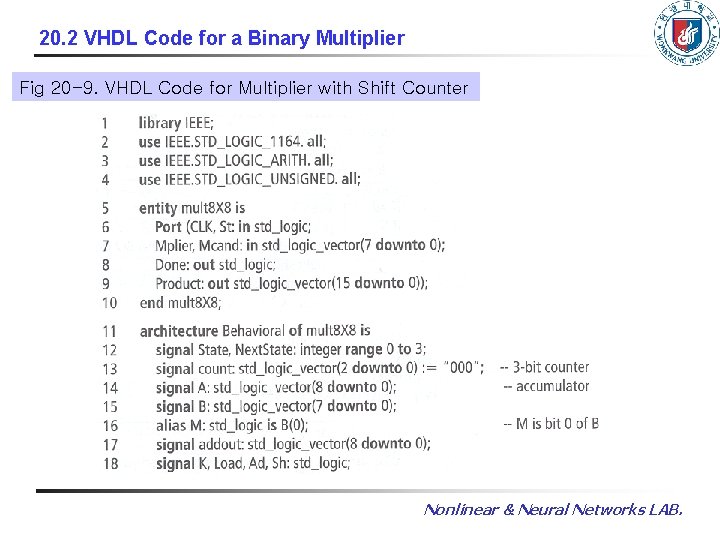

20. 2 VHDL Code for a Binary Multiplier Fig 20 -9. VHDL Code for Multiplier with Shift Counter Nonlinear & Neural Networks LAB.

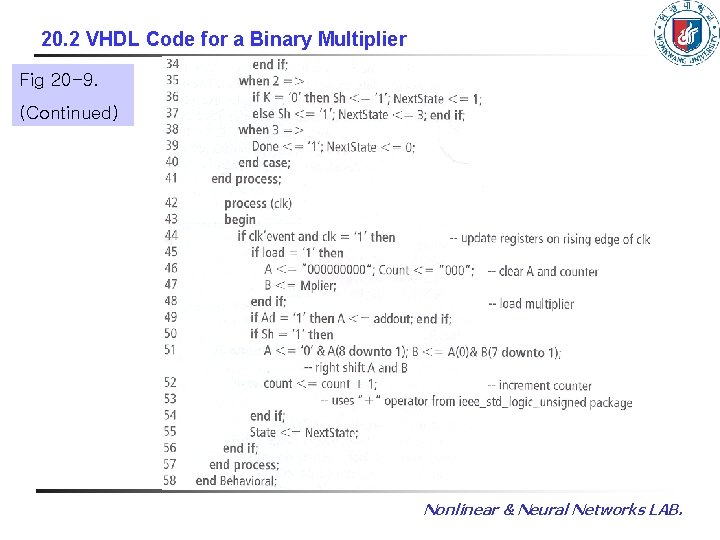

20. 2 VHDL Code for a Binary Multiplier Fig 20 -9. (Continued) Nonlinear & Neural Networks LAB.

20. 2 VHDL Code for a Binary Multiplier Fig 20 -9. (Continued) Nonlinear & Neural Networks LAB.

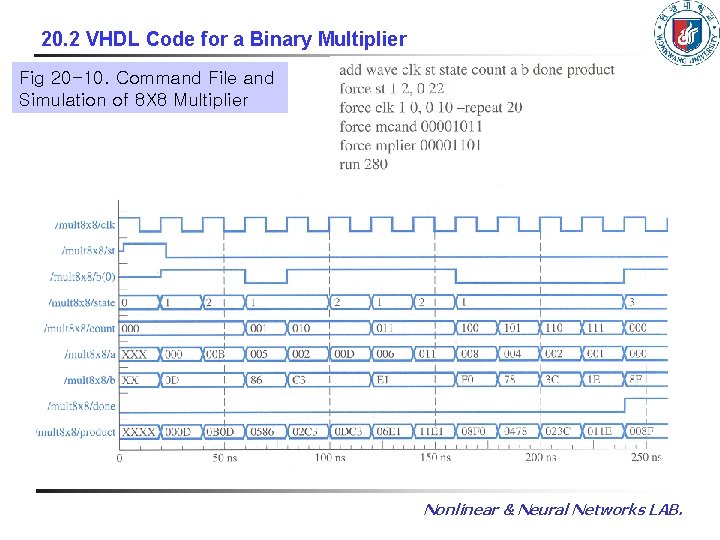

20. 2 VHDL Code for a Binary Multiplier Fig 20 -10. Command File and Simulation of 8 X 8 Multiplier Nonlinear & Neural Networks LAB.

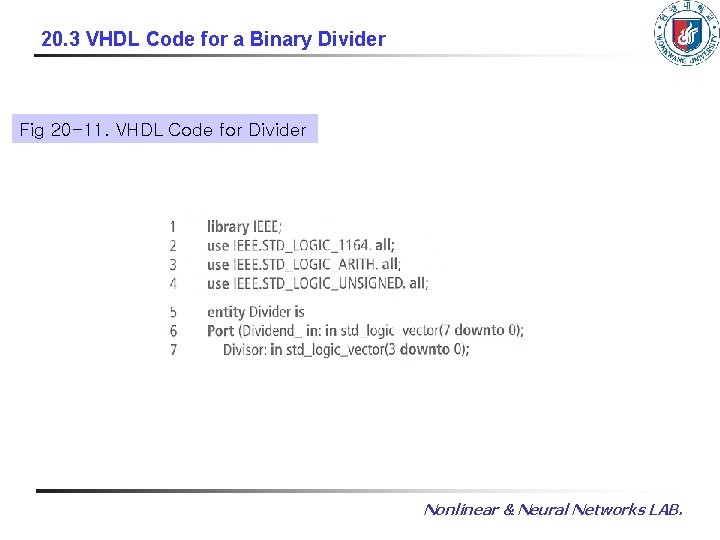

20. 3 VHDL Code for a Binary Divider Fig 20 -11. VHDL Code for Divider Nonlinear & Neural Networks LAB.

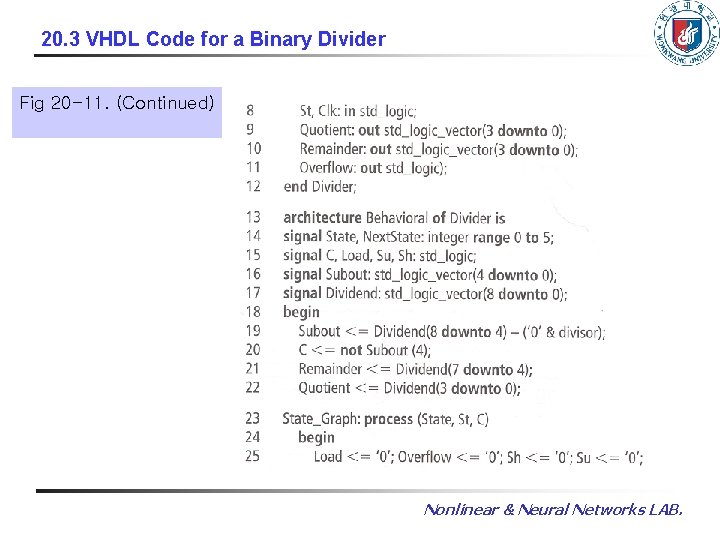

20. 3 VHDL Code for a Binary Divider Fig 20 -11. (Continued) Nonlinear & Neural Networks LAB.

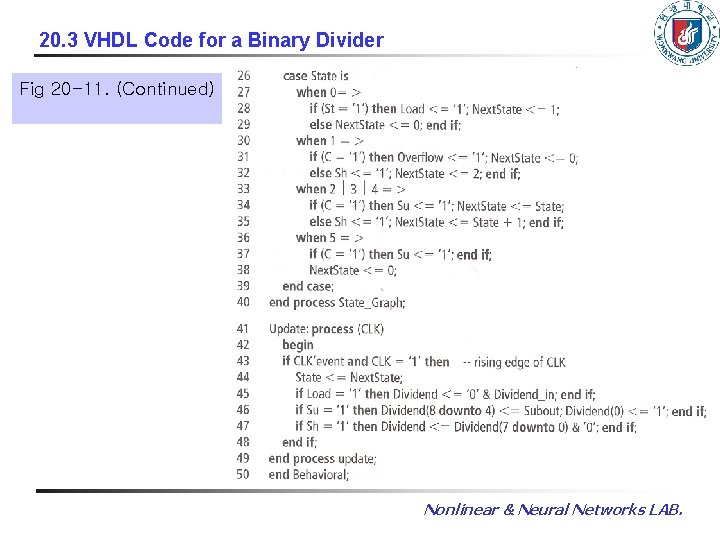

20. 3 VHDL Code for a Binary Divider Fig 20 -11. (Continued) Nonlinear & Neural Networks LAB.

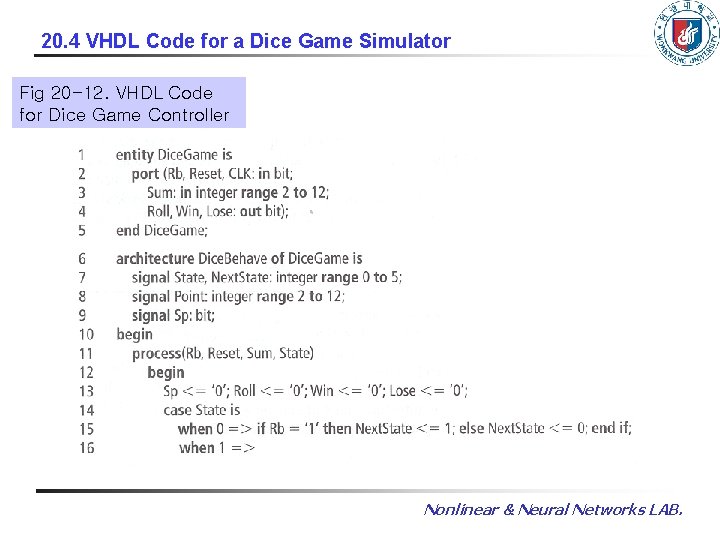

20. 4 VHDL Code for a Dice Game Simulator Fig 20 -12. VHDL Code for Dice Game Controller Nonlinear & Neural Networks LAB.

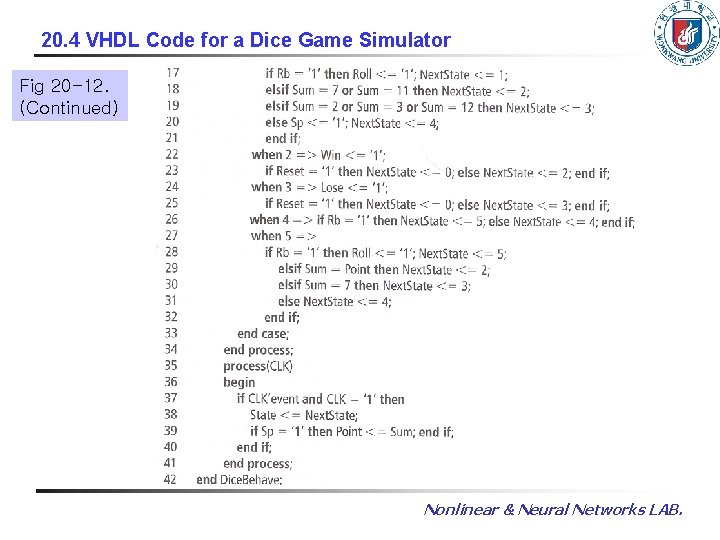

20. 4 VHDL Code for a Dice Game Simulator Fig 20 -12. (Continued) Nonlinear & Neural Networks LAB.

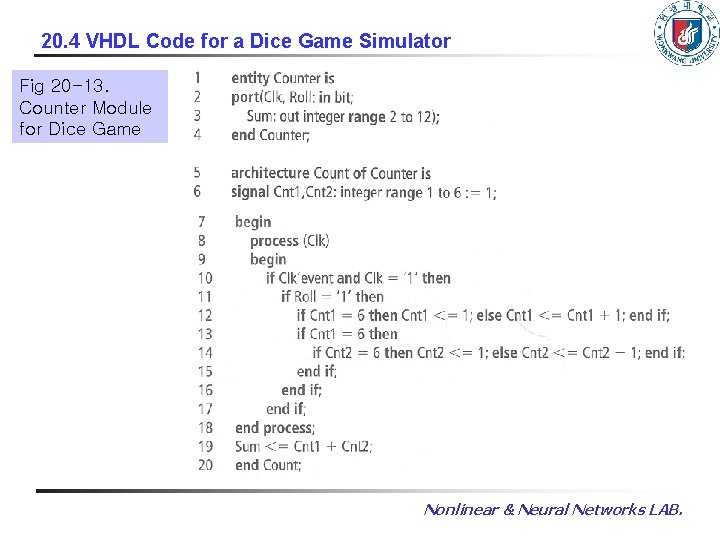

20. 4 VHDL Code for a Dice Game Simulator Fig 20 -13. Counter Module for Dice Game Nonlinear & Neural Networks LAB.

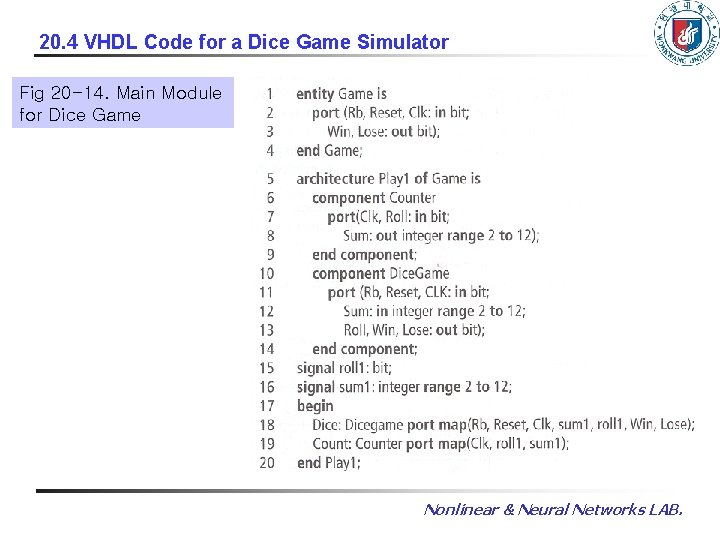

20. 4 VHDL Code for a Dice Game Simulator Fig 20 -14. Main Module for Dice Game Nonlinear & Neural Networks LAB.

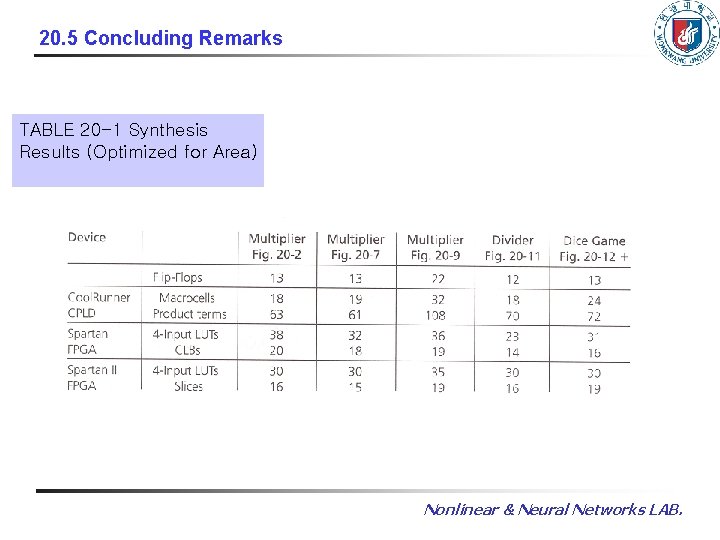

20. 5 Concluding Remarks TABLE 20 -1 Synthesis Results (Optimized for Area) Nonlinear & Neural Networks LAB.

- Slides: 28