Construccin de multiplicadores sobre campos finitos GF2 m

Construcción de multiplicadores sobre campos finitos GF(2 m) para el tratamiento de la información Presenta: Mario Alberto García-Martínez Asesor: Guillermo Morales-Luna 1

Contenido n n n Antecedentes Motivación y planteamiento del problema Soluciones propuestas n n n El divisor y el multiplicador El exponenciador para GF(2 m) Resultados mas importantes Publicaciones Trabajo inmediato y conclusiones 2

Antecedentes n El antecedente principal para este trabajo es el diseño de un divisor para campos finitos GF(24) que se realizó como tesis para el grado de maestría. n n n Esquemático PLD´s Altera 3

Motivación y planteamiento. . . n n Las operaciones aritméticas sobre GF(2 m) son intensamente usadas en los algoritmos criptográficos, de códigos de corrección de errores y procesamiento digital de señales. Esto presenta la necesidad de que tales operaciones puedan ser desarrolladas a altas velocidades. 4

Motivación y planteamiento. . . n Frente a los desarrollos en software de estos algoritmos, proponemos en este trabajo la implementación en hardware de tales operaciones básicas. 5

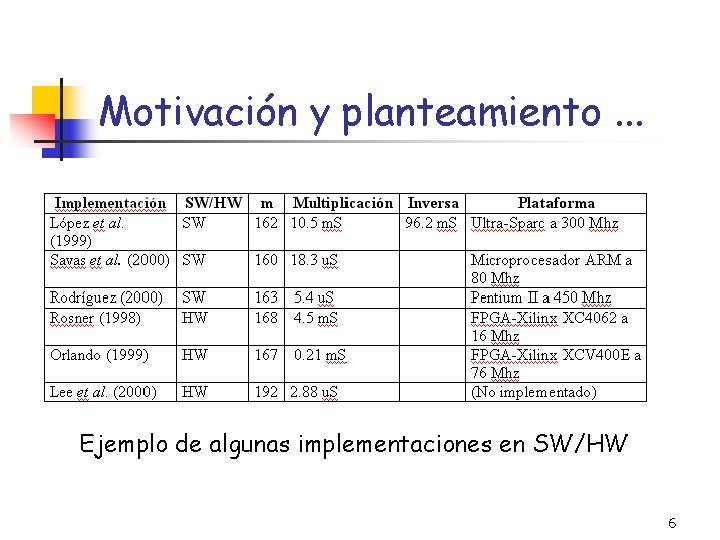

Motivación y planteamiento. . . Ejemplo de algunas implementaciones en SW/HW 6

Objetivo principal: n La implementación en lógica reconfigurable de arquitecturas funcionales para las operaciones básicas sobre GF(2 m). 7

Operaciones en campos finitos Aquí se ubica principalmente nuestro trabajo 8

Porqué FPGA’s? n Su característica de reprogramación permite: n n n Menor tiempo de desarrollo y fabricación que un ASIC Muchas facilidades para verificación y corrección de fallas. Se adaptan muy bien a las arquitecturas sistólicas. 9

Soluciones propuestas n Se ha realizado el diseño de tres circuitos: n Un divisor serial y sistólico de 4 bits n n (Descripción VHDL, síntesis, simulación, implementación) Un multiplicador serial y sistólico de 64 bits n (Descripción VHDL, síntesis, simulación) 10

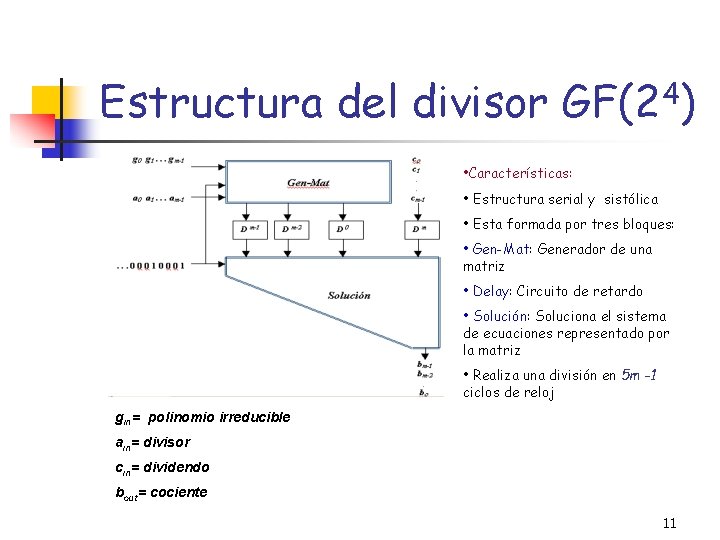

Estructura del divisor GF(24) • Características: • Estructura serial y sistólica • Esta formada por tres bloques: • Gen-Mat: Generador de una matriz • Delay: Circuito de retardo • Solución: Soluciona el sistema de ecuaciones representado por la matriz • Realiza una división en 5 m -1 ciclos de reloj gin= polinomio irreducible ain= divisor cin= dividendo bout= cociente 11

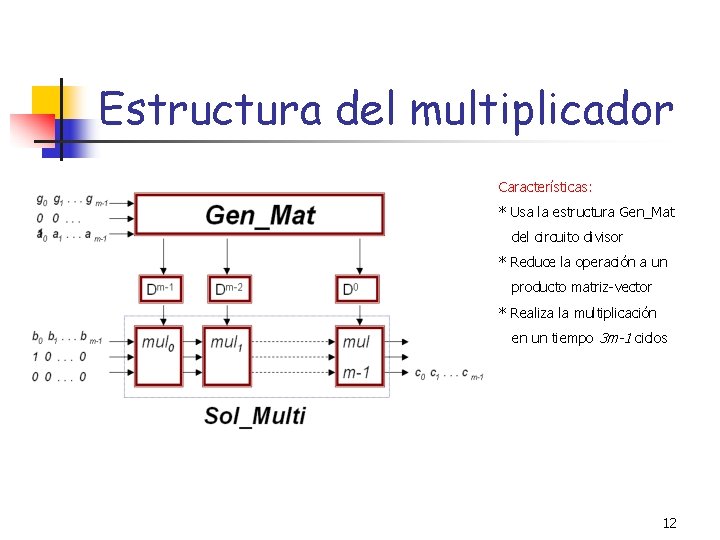

Estructura del multiplicador Características: * Usa la estructura Gen_Mat del circuito divisor * Reduce la operación a un producto matriz-vector * Realiza la multiplicación en un tiempo 3 m-1 ciclos 12

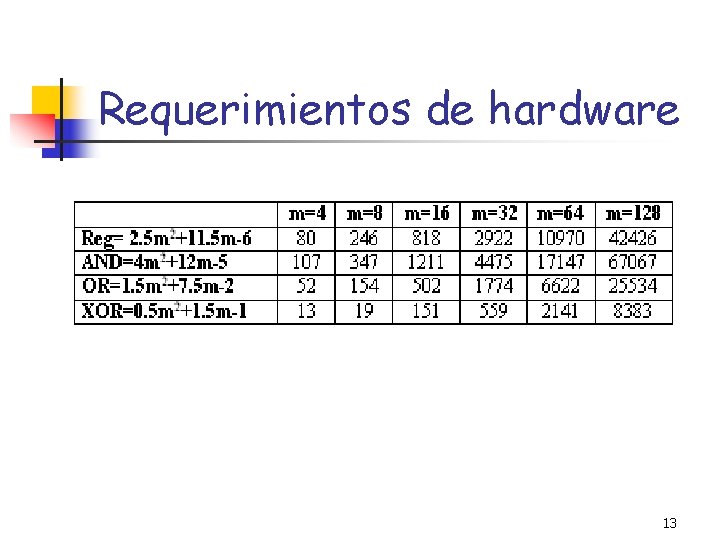

Requerimientos de hardware 13

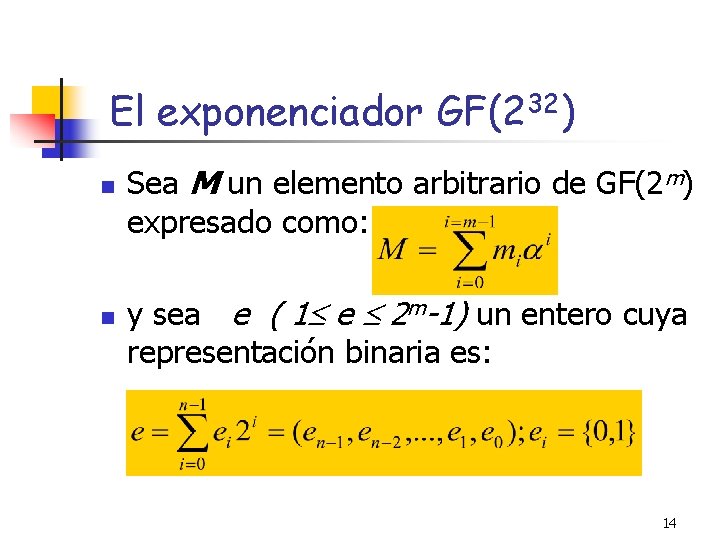

El exponenciador GF(232) n n Sea M un elemento arbitrario de GF(2 m) expresado como: y sea e ( 1 e 2 m-1) un entero cuya representación binaria es: 14

El exponenciador GF(232) n Entonces la potencia R= Me modulo el polinomio irreducible G, está también en GF(2 m) y, según el método binario, se calcula mediante el siguiente algoritmo: 15

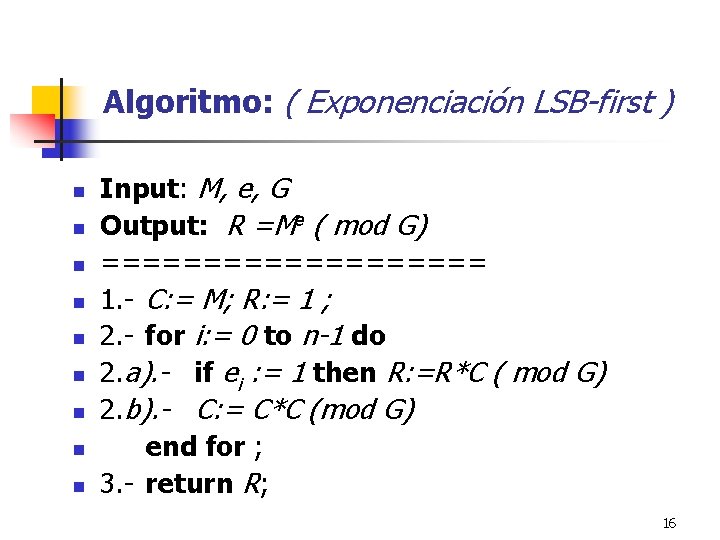

Algoritmo: ( Exponenciación LSB-first ) n n n n n Input: M, e, G Output: R =Me ( mod G) ========== 1. - C: = M; R: = 1 ; 2. - for i: = 0 to n-1 do 2. a). - if ei : = 1 then R: =R*C ( mod G) 2. b). - C: = C*C (mod G) end for ; 3. - return R; 16

Ejemplo: e = 11111010 = 250 17

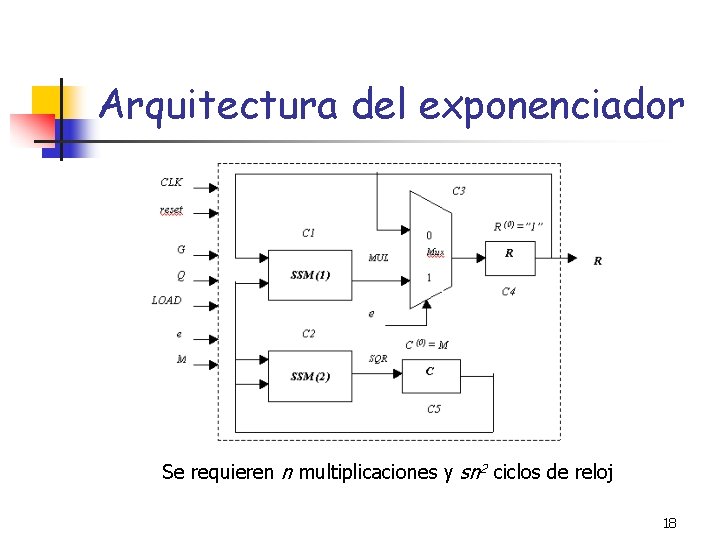

Arquitectura del exponenciador Se requieren n multiplicaciones y sn 2 ciclos de reloj 18

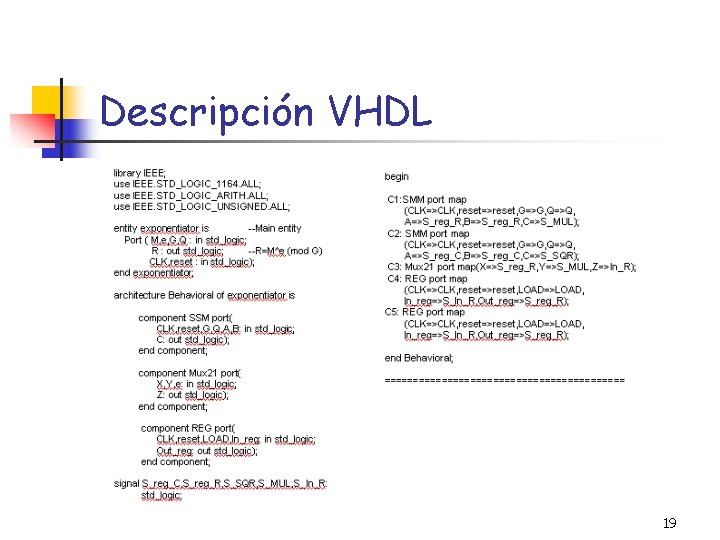

Descripción VHDL 19

Implementación y resultados Se ha realizado una implementación inicial de 32 bits en un FPGA Virtex XCV 300 de Xilinx: Layout de conexiones Layout del uso de CLB´s 20

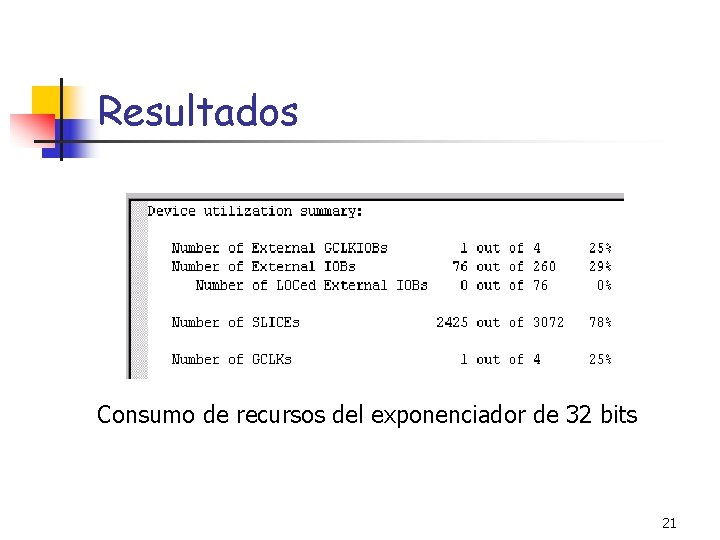

Resultados Consumo de recursos del exponenciador de 32 bits 21

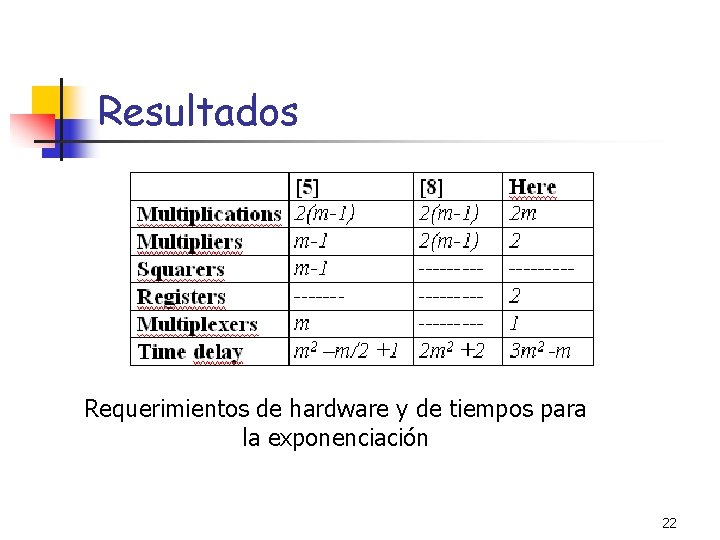

Resultados Requerimientos de hardware y de tiempos para la exponenciación 22

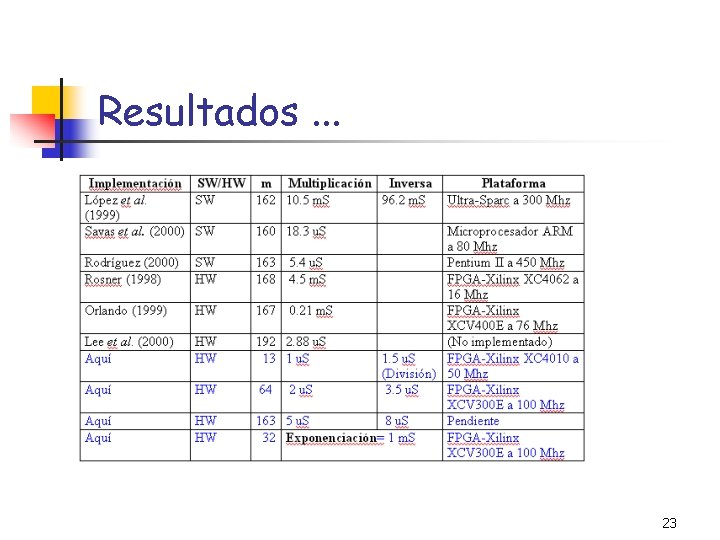

Resultados. . . 23

Publicaciones 1. Mario Alberto García Martínez, Guillermo Morales Luna y José Antonio Moreno Cadenas. “Procesador de División sobre Campos de Galois en un PLD”. CIE 2000. CINVESTAV, IPN. México D. F. Septiembre de 2000. 2. Mario Alberto García Martínez y Guillermo Morales Luna. “Implantación en un Circuito Lógico del procedimiento de Reducción Gaussiana para matrices en Campos Finitos” GF(2 m). Congreso de la Sociedad Matemática Mexicana 2000. Saltillo Coahuila. Octubre de 2000 3. Mario Alberto García Martínez y Guillermo Morales Luna. “Estructura Lógica para el procedimiento matricial de Reducción Gaussiana en Campos Finitos GF(2 m)”. CONAGOLFO 2000, Instituto Tecnológico de Orizaba Ver. Noviembre de 2000. 4. Mario Alberto García Martínez y Guillermo Morales Luna. “VHDL specification of a FPGA to divide and multiply in GF(2 m)”. Sixth International Conference on Finite Fields and Applications. Oaxaca, México. Mayo de 2001. 24

Publicaciones 5. Mario Alberto García Martínez y Guillermo Morales Luna. “VHDL specification of a FPGA to perform division over Galois Fields”. 3 er. Encuentro Internacional de Ciencias de la Computación. ENC´ 01. Aguascalientes, Ags. México. Septiembre de 2001. 6. Mario Alberto García Martínez y Guillermo Morales Luna. “Descripción en VHDL de un multiplicador serial y sistólico para campos de Galois GF(2 m)”. VIII International Workshop Iber. Chip 2002. Guadalajara Jal. México. Abril 2002. 7. Mario Alberto García Martínez, Guillermo Morales Luna y Francisco Rodríguez Enríquez. “ Descripción con VHDL de un exponenciador para campos finitos GF(2 m)”. IX International Workshop Iberchip 2003. La Habana, Cuba. Marzo 2003. 8. Mario Alberto García Martínez, Guillermo Morales Luna y Francisco Rodríguez Enríquez. “ Hardware Implementation of Binary Method for Exponentiation in GF(2 m)”. 4 o. Encuentro Internacional de Ciencias de la Computación. ENC´ 03. Tlaxcala, Tlax. Septiembre de 2003. 25

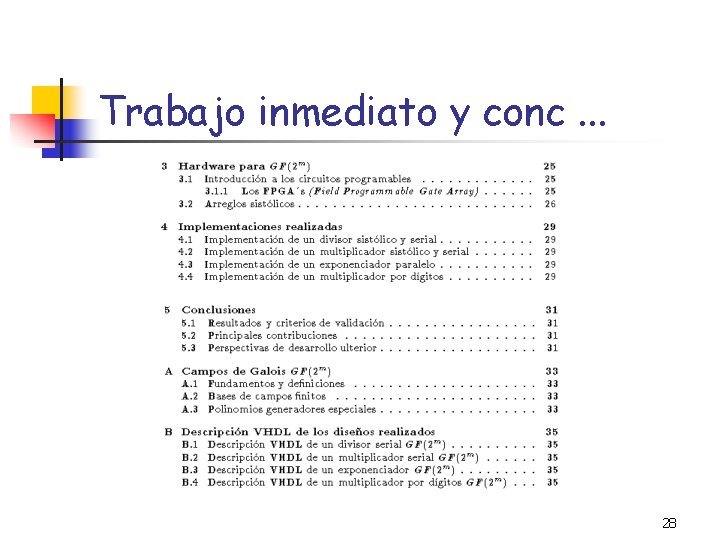

Trabajo inmediato y conclusiones n n Se ha de concluír el diseño del multiplicador por dígitos durante los próximos dos meses. Se han escrito ya los dos primeros capítulos de la tesis, cuyo contenido se presenta enseguida. 26

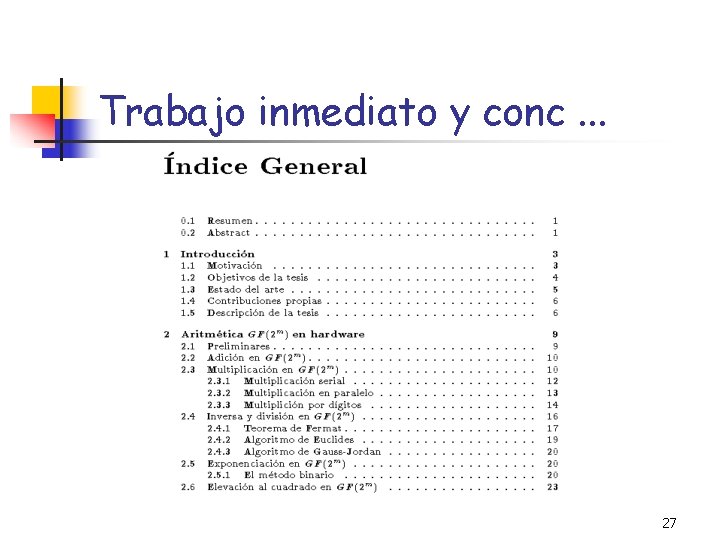

Trabajo inmediato y conc. . . 27

Trabajo inmediato y conc. . . 28

Trabajo inmediato y conc. . . n Esperamos la conclusión del programa doctoral para finales del presente año. 29

- Slides: 29