Behavioral Modeling in Combinational Design with VHDL Dataflow

Behavioral Modeling in Combinational Design with VHDL. Dataflow Style Coding IAS 0600 Digital Systems Design Alexander Sudnitson Tallinn University of Technology 1

Combinational systems n n 2 Combinational systems have no memory. A combinational system's outputs are a function of only its present input values. No latches/FFs or closed feedback loop Combinational system description can be in dataflow, behavioral, or structioral styles. Concurrent signal assignment signal is basic for dataflow style combinational design.

Order of evaluation For example, if we want to form the XOR of a and b using only AND, OR, and NOT operations and assign the result to c, the following statement is sufficient in many high-level languages: c = a and not b or not a and b However, in VHDL, since the and operator does not have higher precedence than the or operator, the previous expression is interpreted as: c = ((a and (not b)) or (not a)) and b We must use parentheses to ensure that our expressions are interpreted as we intend. Accordingly, the previous assignment statement must be written in VHDL as: c <= (a and not b) or (not a and b); Because the predefined versions of the operators AND, OR, XOR, and XNOR are defined as associative, a sequence of any one of these operators is allowed. Thus, to create a three-input AND using the and operator, we can write: f <= a and b and c; In contrast, a sequence of either nand or nor operators is not allowed. Accordingly, the following attempt to produce a three-input NAND using the nand operator creates a compiler error: g <= a nand b nand c; -- invalid Instead, we could write: g <= not (a and b and c); -- valid 3

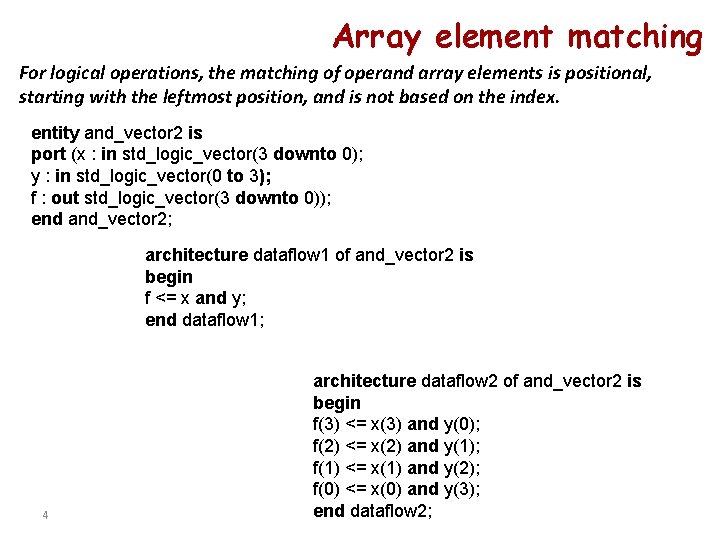

Array element matching For logical operations, the matching of operand array elements is positional, starting with the leftmost position, and is not based on the index. entity and_vector 2 is port (x : in std_logic_vector(3 downto 0); y : in std_logic_vector(0 to 3); f : out std_logic_vector(3 downto 0)); end and_vector 2; architecture dataflow 1 of and_vector 2 is begin f <= x and y; end dataflow 1; 4 architecture dataflow 2 of and_vector 2 is begin f(3) <= x(3) and y(0); f(2) <= x(2) and y(1); f(1) <= x(1) and y(2); f(0) <= x(0) and y(3); end dataflow 2;

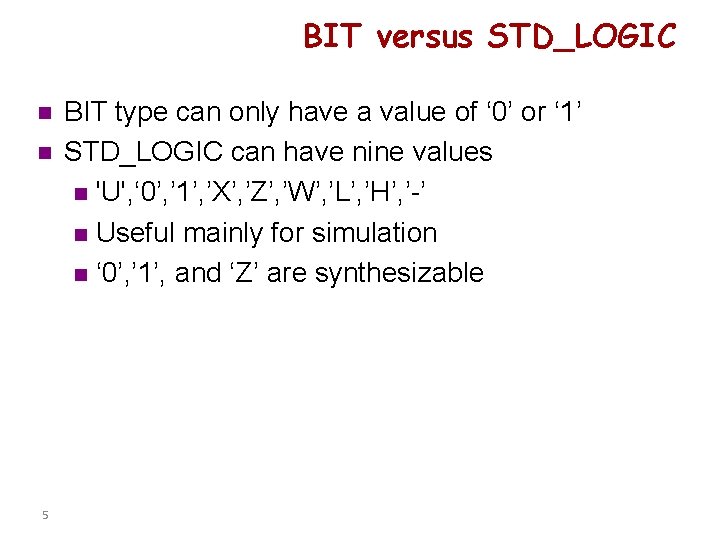

BIT versus STD_LOGIC n n 5 BIT type can only have a value of ‘ 0’ or ‘ 1’ STD_LOGIC can have nine values n 'U', ‘ 0’, ’ 1’, ’X’, ’Z’, ’W’, ’L’, ’H’, ’-’ n Useful mainly for simulation n ‘ 0’, ’ 1’, and ‘Z’ are synthesizable

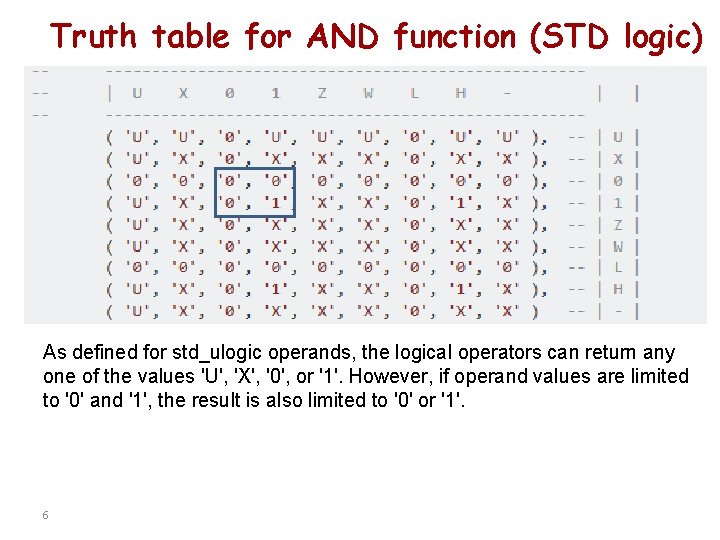

Truth table for AND function (STD logic) As defined for std_ulogic operands, the logical operators can return any one of the values 'U', 'X', '0', or '1'. However, if operand values are limited to '0' and '1', the result is also limited to '0' or '1'. 6

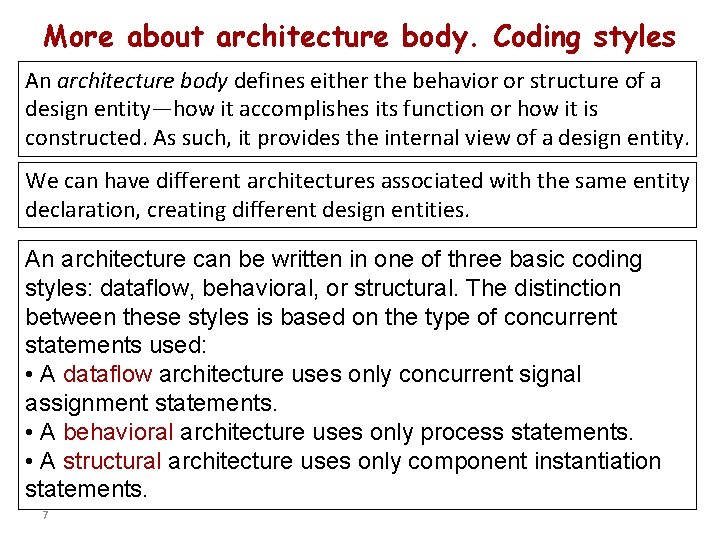

More about architecture body. Coding styles An architecture body defines either the behavior or structure of a design entity—how it accomplishes its function or how it is constructed. As such, it provides the internal view of a design entity. We can have different architectures associated with the same entity declaration, creating different design entities. An architecture can be written in one of three basic coding styles: dataflow, behavioral, or structural. The distinction between these styles is based on the type of concurrent statements used: • A dataflow architecture uses only concurrent signal assignment statements. • A behavioral architecture uses only process statements. • A structural architecture uses only component instantiation statements. 7

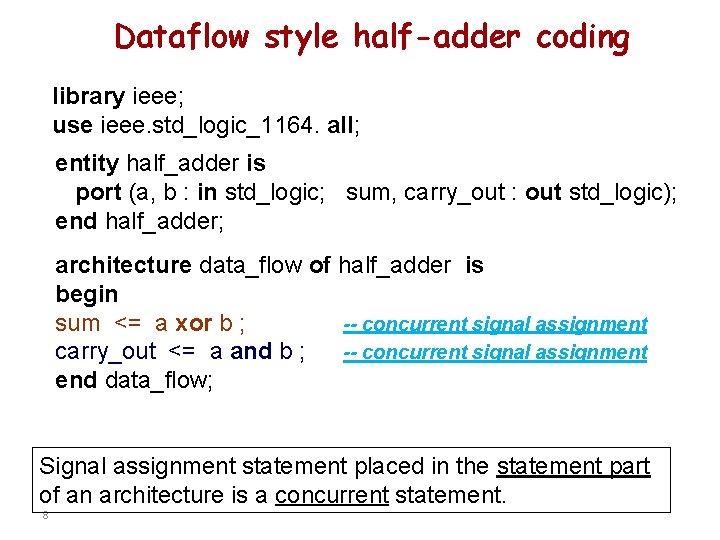

Dataflow style half-adder coding library ieee; use ieee. std_logic_1164. all; entity half_adder is port (a, b : in std_logic; sum, carry_out : out std_logic); end half_adder; architecture data_flow of half_adder is begin sum <= a xor b ; -- concurrent signal assignment carry_out <= a and b ; -- concurrent signal assignment end data_flow; Signal assignment statement placed in the statement part of an architecture is a concurrent statement. 8

Signal assignment statement placed in the statement part of an architecture is a concurrent statement. Concurrent signal assignment statements assigns a new value to the signal on the left-hand side of the signal assignment symbol (<=) whenever there is an event on one of the signals on the right-hand side of the assignment symbol. The signal assignment statement is said to be sensitive to the signals on the right-hand side of the statement. The symbol <= is read as “gets. ” We consider three kinds of concurrent signal assignment: ØConcurrent signal assignment statement using a Boolean expression ØSelected signal assignment statement ØConditional signal assignment statement 9

Concurrent signal assignment with a closed feedback loop Signal assignment statement with a closed feedback loop: Øa signal appears in both sides of a concurrent assignment statement, For example, q <= ((not q) and (not en)) or (d and en); üSyntactically correct üBut form a closed feedback loop üShould be avoided 10

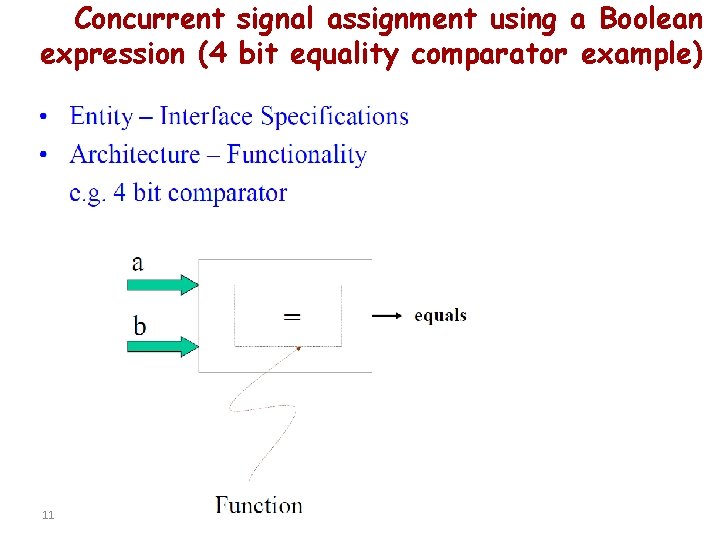

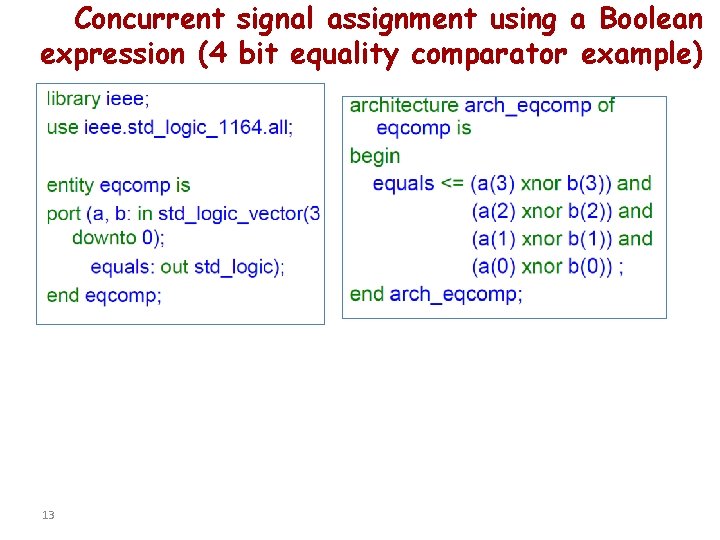

Concurrent signal assignment using a Boolean expression (4 bit equality comparator example) 11

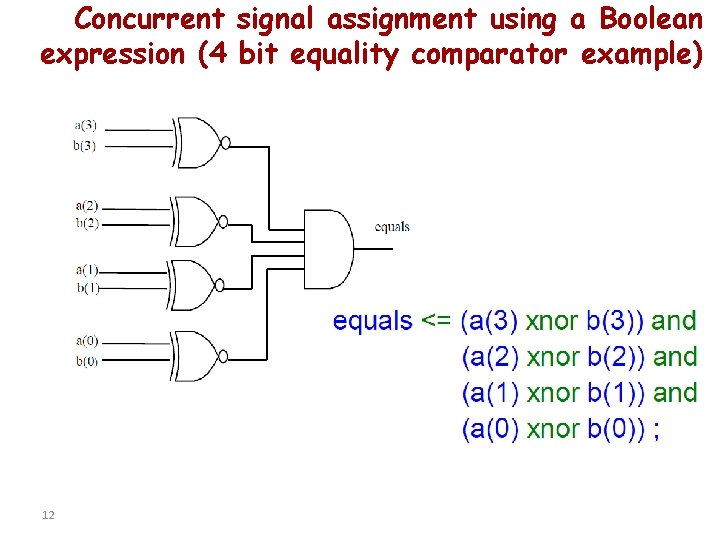

Concurrent signal assignment using a Boolean expression (4 bit equality comparator example) 12

Concurrent signal assignment using a Boolean expression (4 bit equality comparator example) 13

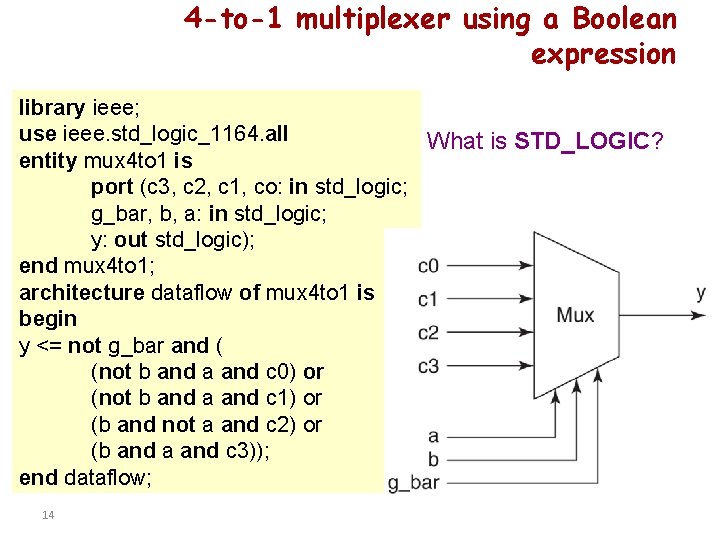

4 -to-1 multiplexer using a Boolean expression library ieee; use ieee. std_logic_1164. all What is STD_LOGIC? entity mux 4 to 1 is port (c 3, c 2, c 1, co: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture dataflow of mux 4 to 1 is begin y <= not g_bar and ( (not b and a and c 0) or (not b and a and c 1) or (b and not a and c 2) or (b and a and c 3)); end dataflow; 14

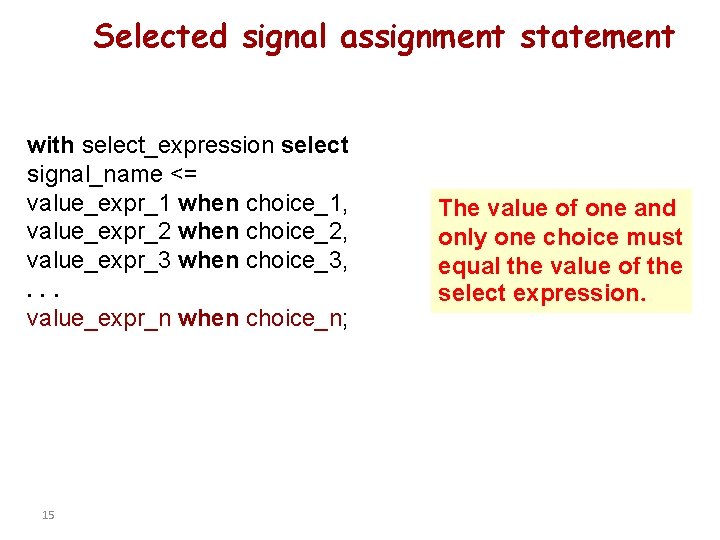

Selected signal assignment statement with select_expression select signal_name <= value_expr_1 when choice_1, value_expr_2 when choice_2, value_expr_3 when choice_3, . . . value_expr_n when choice_n; 15 The value of one and only one choice must equal the value of the select expression.

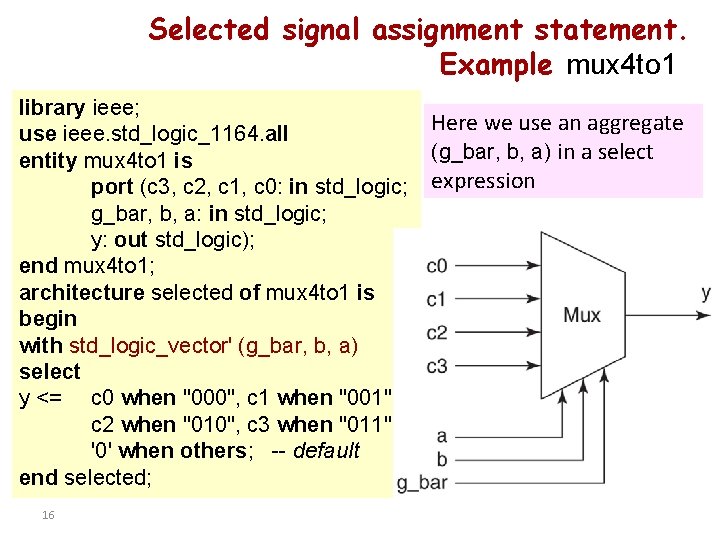

Selected signal assignment statement. Example mux 4 to 1 library ieee; use ieee. std_logic_1164. all entity mux 4 to 1 is port (c 3, c 2, c 1, c 0: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture selected of mux 4 to 1 is begin with std_logic_vector' (g_bar, b, a) select y <= c 0 when "000", c 1 when "001", c 2 when "010", c 3 when "011" '0' when others; -- default end selected; 16 Here we use an aggregate (g_bar, b, a) in a select expression

Type qualification. Choices’ completeness We must explicitly specify the aggregat's (g_bar, b, a) type. This is accomplished using a type qualification ('): std_logic_vector' (g_bar, b, a). If we use this aggregate alone, the compiler cannot tell the aggregate’s type from the context. The compiler does not simply assume that an aggregate of std_logic elements is type std_logic_vector, since there are other array types, such as unsigned, that have std_logic elements (lect. 7) 17

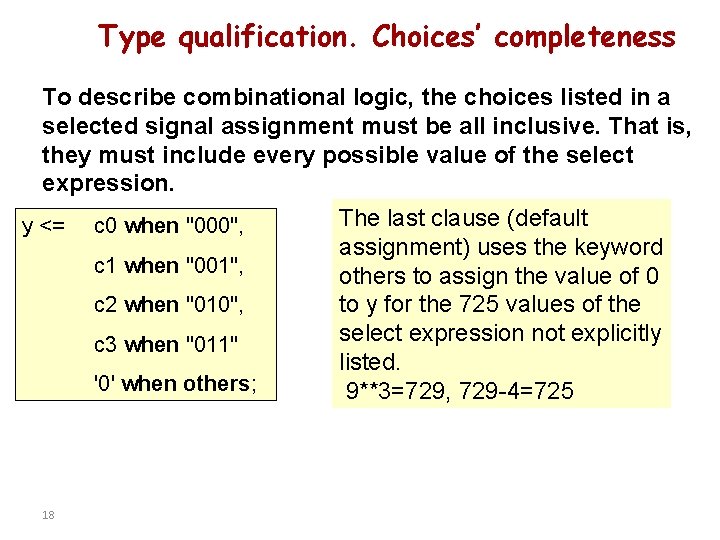

Type qualification. Choices’ completeness To describe combinational logic, the choices listed in a selected signal assignment must be all inclusive. That is, they must include every possible value of the select expression. The last clause (default y <= c 0 when "000", assignment) uses the keyword c 1 when "001", others to assign the value of 0 c 2 when "010", to y for the 725 values of the select expression not explicitly c 3 when "011" listed. '0' when others; 9**3=729, 729 -4=725 18

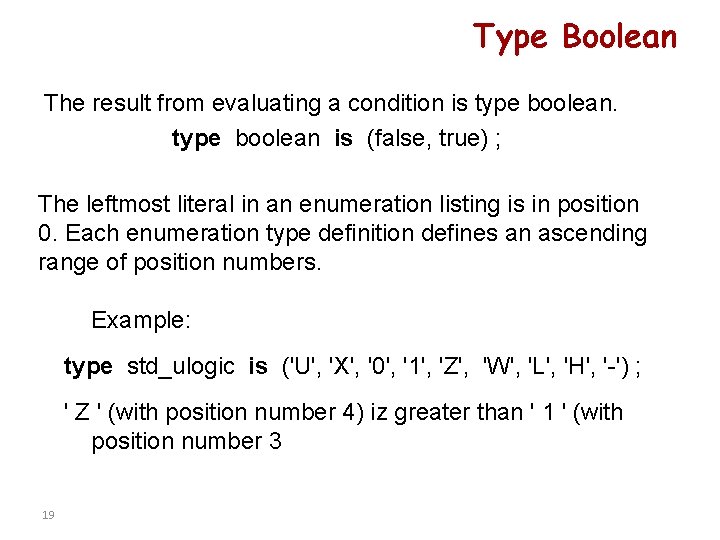

Type Boolean The result from evaluating a condition is type boolean is (false, true) ; The leftmost literal in an enumeration listing is in position 0. Each enumeration type definition defines an ascending range of position numbers. Example: type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-') ; ' Z ' (with position number 4) iz greater than ' 1 ' (with position number 3 19

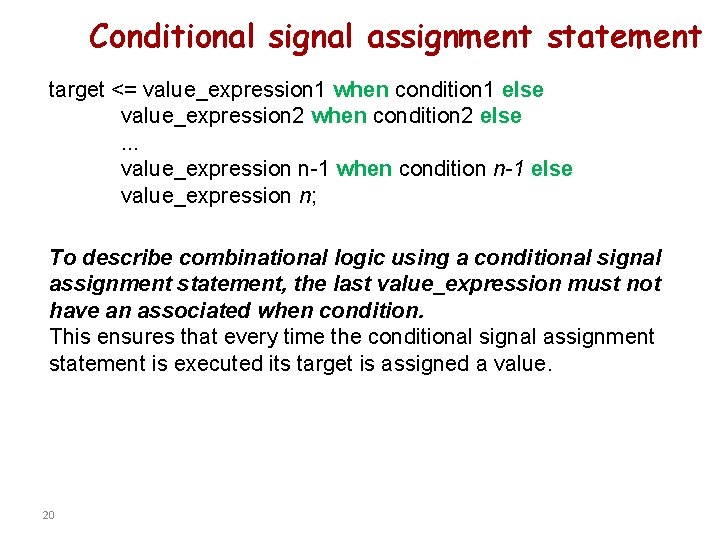

Conditional signal assignment statement target <= value_expression 1 when condition 1 else value_expression 2 when condition 2 else. . . value_expression n-1 when condition n-1 else value_expression n; To describe combinational logic using a conditional signal assignment statement, the last value_expression must not have an associated when condition. This ensures that every time the conditional signal assignment statement is executed its target is assigned a value. 20

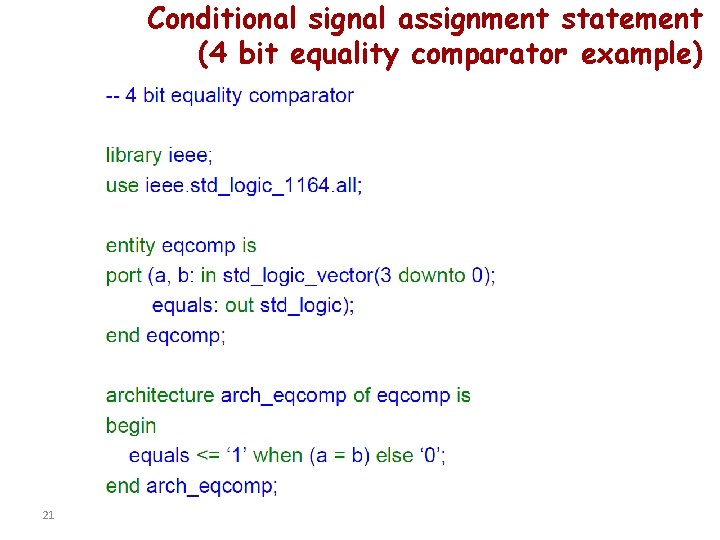

Conditional signal assignment statement (4 bit equality comparator example) 21

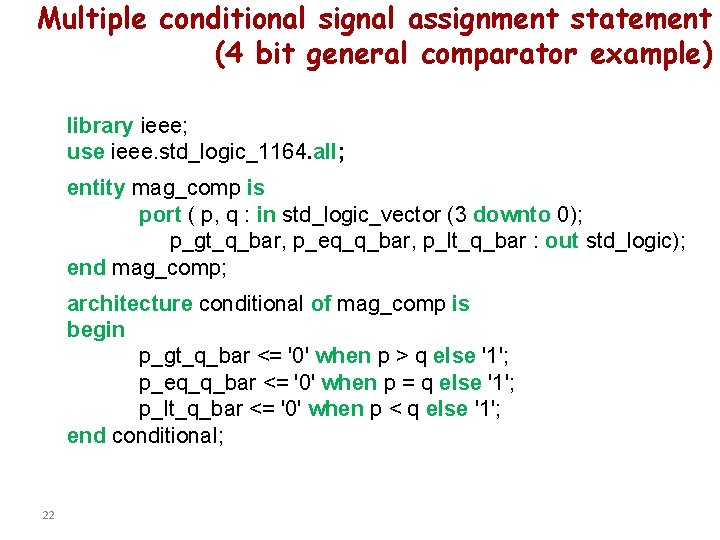

Multiple conditional signal assignment statement (4 bit general comparator example) library ieee; use ieee. std_logic_1164. all; entity mag_comp is port ( p, q : in std_logic_vector (3 downto 0); p_gt_q_bar, p_eq_q_bar, p_lt_q_bar : out std_logic); end mag_comp; architecture conditional of mag_comp is begin p_gt_q_bar <= '0' when p > q else '1'; p_eq_q_bar <= '0' when p = q else '1'; p_lt_q_bar <= '0' when p < q else '1'; end conditional; 22

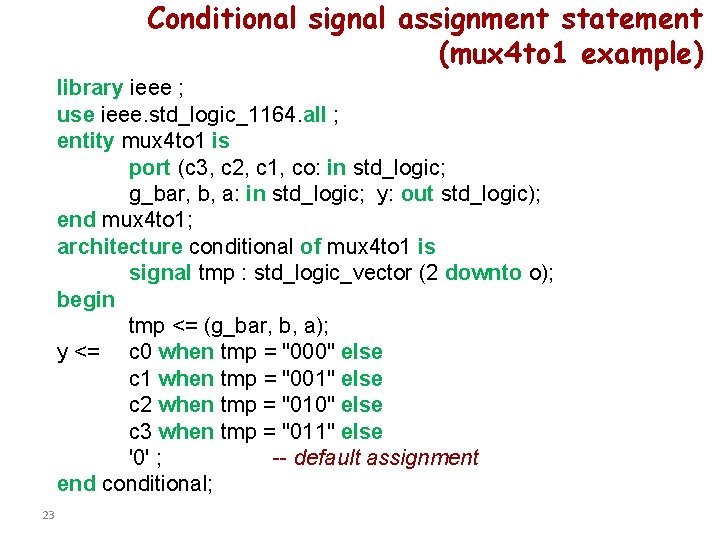

Conditional signal assignment statement (mux 4 to 1 example) library ieee ; use ieee. std_logic_1164. all ; entity mux 4 to 1 is port (c 3, c 2, c 1, co: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture conditional of mux 4 to 1 is signal tmp : std_logic_vector (2 downto o); begin tmp <= (g_bar, b, a); y <= c 0 when tmp = "000" else c 1 when tmp = "001" else c 2 when tmp = "010" else c 3 when tmp = "011" else '0' ; -- default assignment end conditional; 23

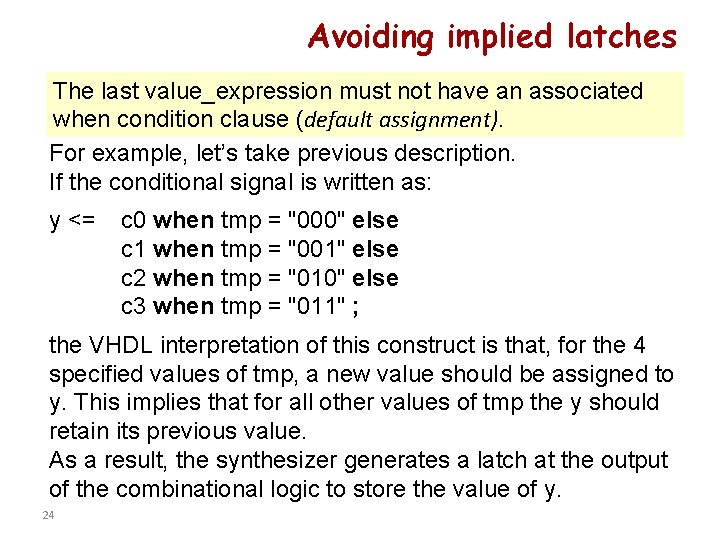

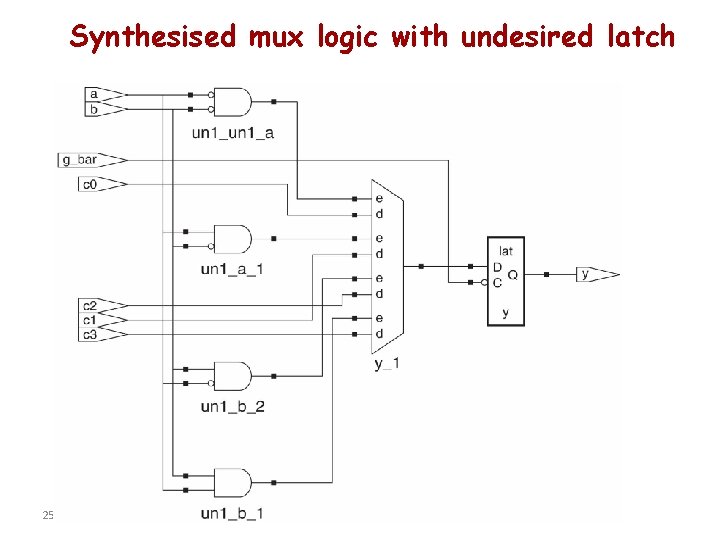

Avoiding implied latches The last value_expression must not have an associated when condition clause (default assignment). For example, let’s take previous description. If the conditional signal is written as: y <= c 0 when tmp = "000" else c 1 when tmp = "001" else c 2 when tmp = "010" else c 3 when tmp = "011" ; the VHDL interpretation of this construct is that, for the 4 specified values of tmp, a new value should be assigned to y. This implies that for all other values of tmp the y should retain its previous value. As a result, the synthesizer generates a latch at the output of the combinational logic to store the value of y. 24

Synthesised mux logic with undesired latch 25

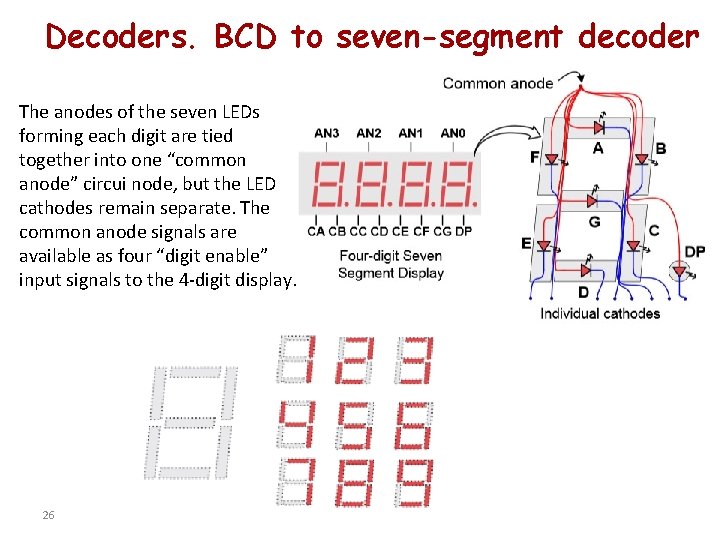

Decoders. BCD to seven-segment decoder The anodes of the seven LEDs forming each digit are tied together into one “common anode” circui node, but the LED cathodes remain separate. The common anode signals are available as four “digit enable” input signals to the 4 -digit display. 26

27

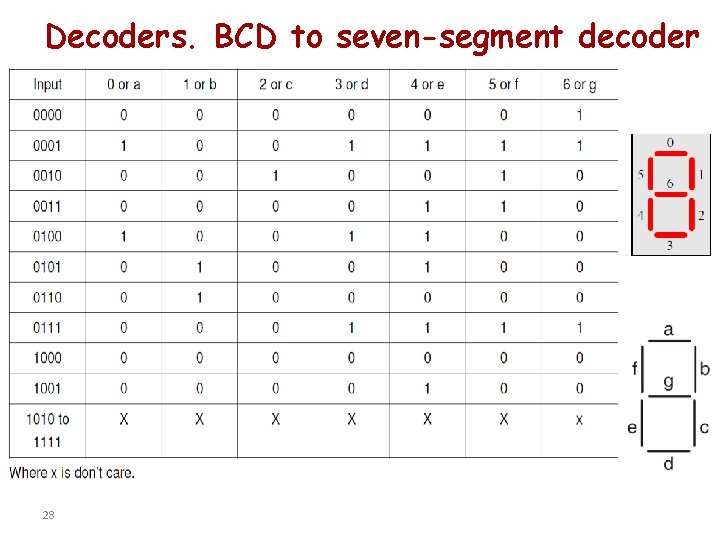

Decoders. BCD to seven-segment decoder 28

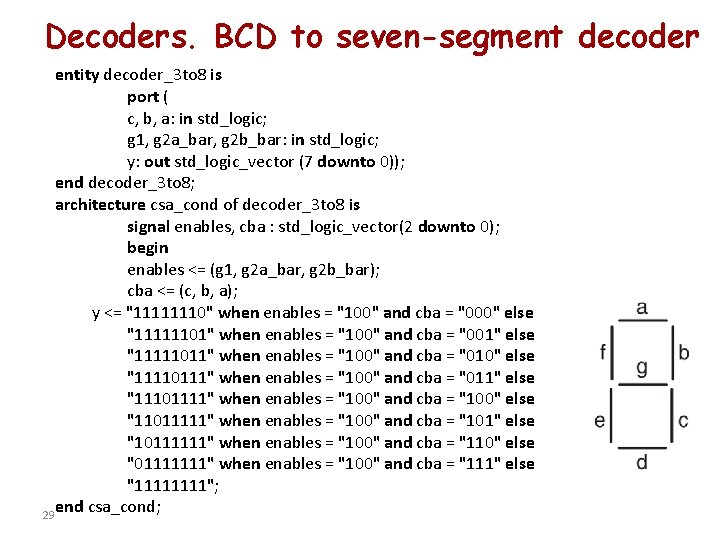

Decoders. BCD to seven-segment decoder entity decoder_3 to 8 is port ( c, b, a: in std_logic; g 1, g 2 a_bar, g 2 b_bar: in std_logic; y: out std_logic_vector (7 downto 0)); end decoder_3 to 8; architecture csa_cond of decoder_3 to 8 is signal enables, cba : std_logic_vector(2 downto 0); begin enables <= (g 1, g 2 a_bar, g 2 b_bar); cba <= (c, b, a); y <= "11111110" when enables = "100" and cba = "000" else "11111101" when enables = "100" and cba = "001" else "11111011" when enables = "100" and cba = "010" else "11110111" when enables = "100" and cba = "011" else "11101111" when enables = "100" and cba = "100" else "11011111" when enables = "100" and cba = "101" else "10111111" when enables = "100" and cba = "110" else "01111111" when enables = "100" and cba = "111" else "1111"; end csa_cond; 29

- Slides: 29