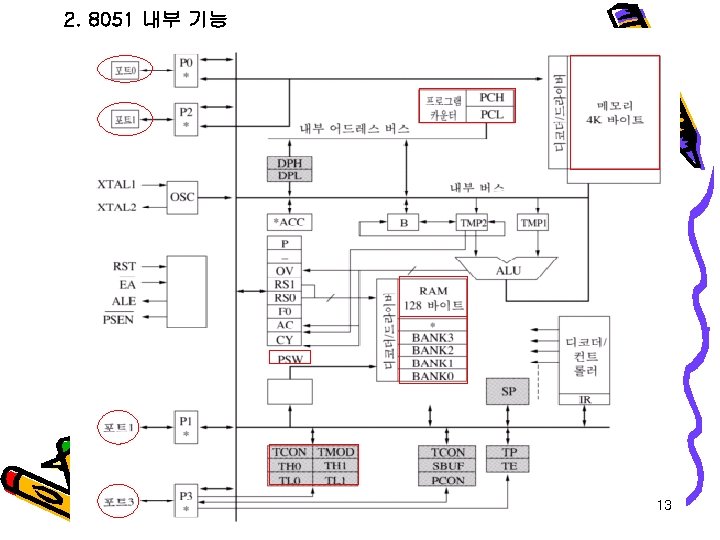

2 8051 2 1 8051 Family 2 1

- Slides: 55

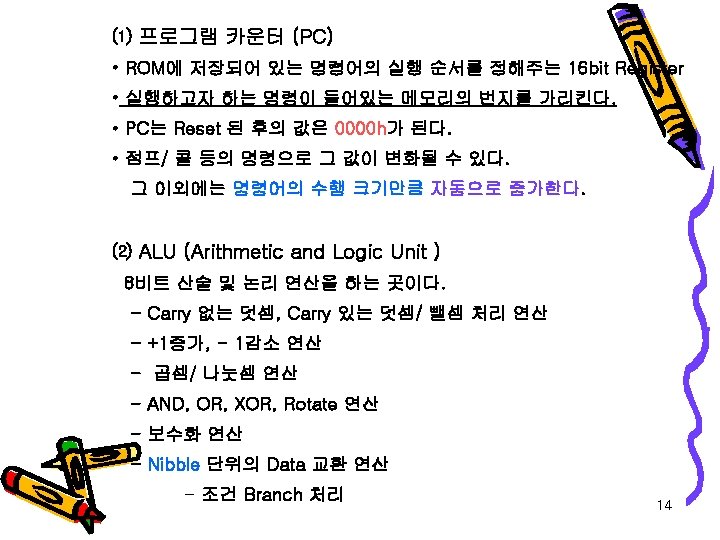

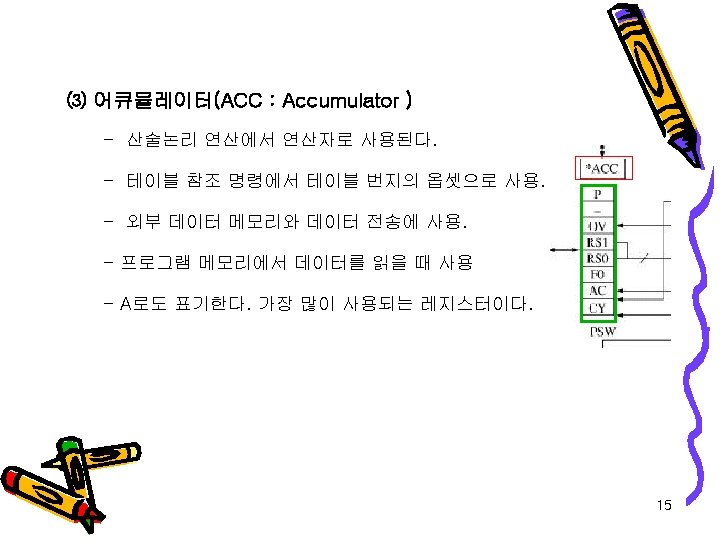

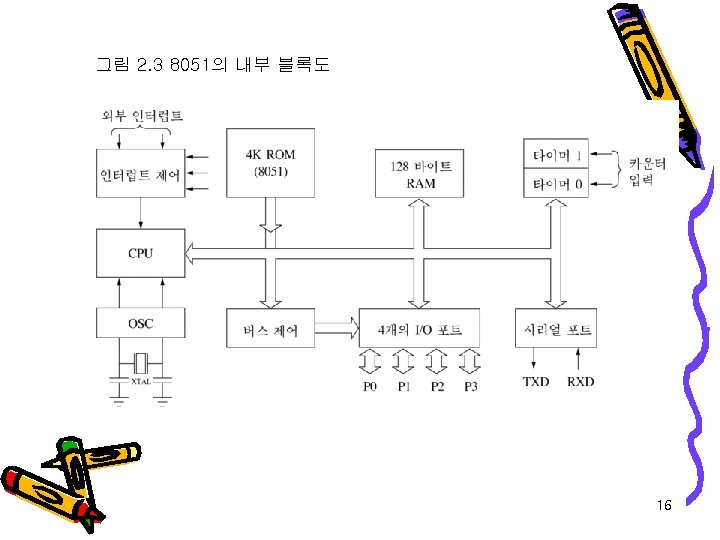

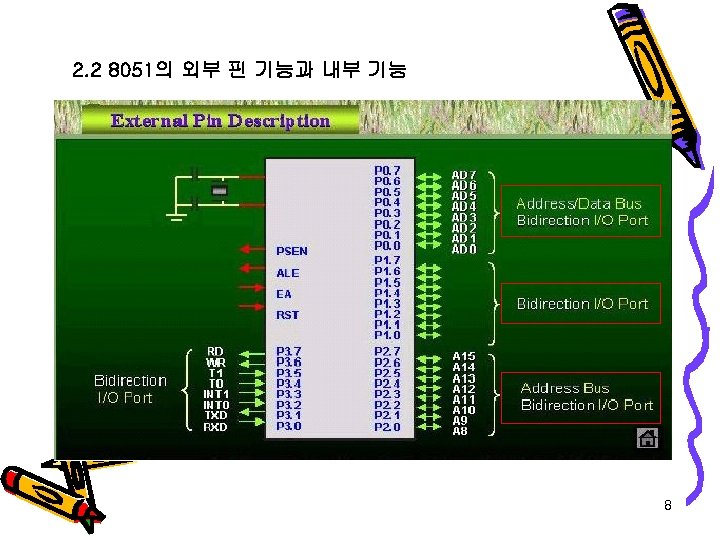

2장 8051의 구조 2. 1 8051 Family의 개요 2. 1 8051의 외부 Pin 기능과 내부 기능 2. 3 8051 Memory 구조 2. 4 8051 Timing 1

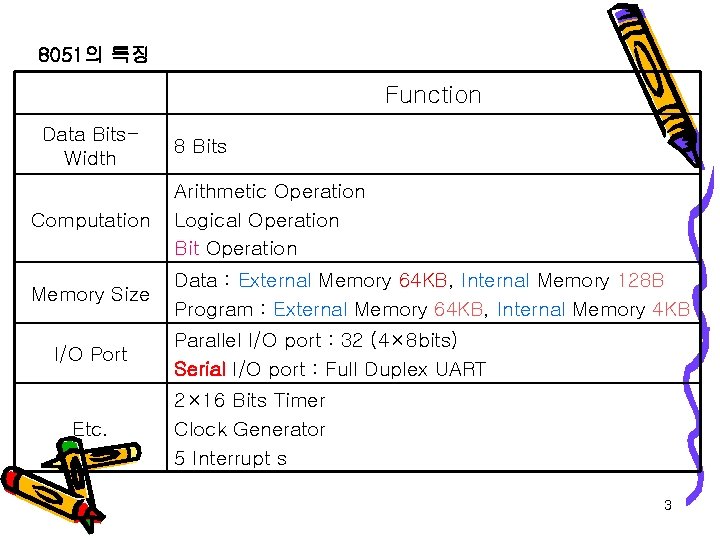

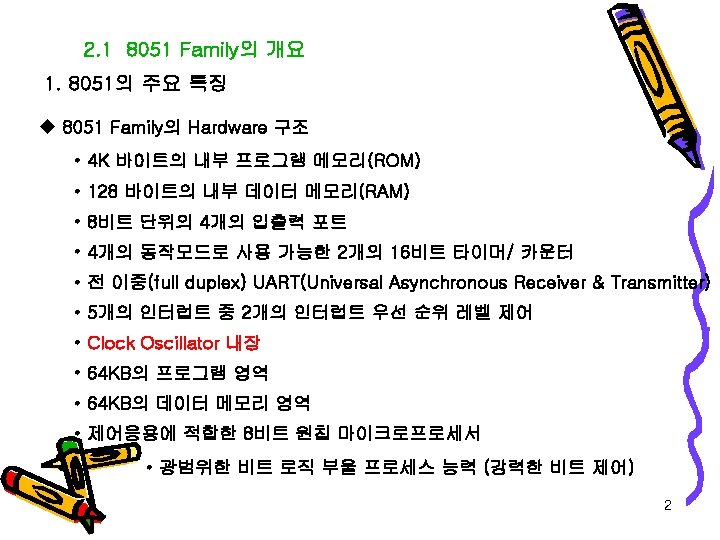

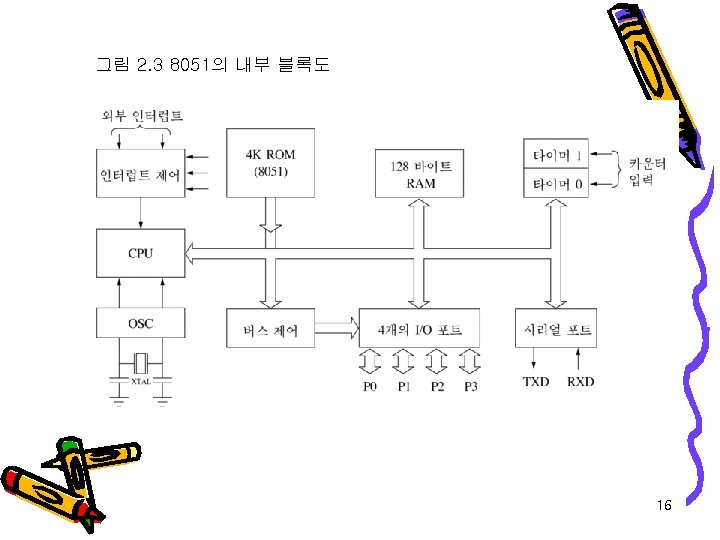

8051의 특징 Function Data Bits. Width 8 Bits Computation Arithmetic Operation Logical Operation Bit Operation Memory Size Data : External Memory 64 KB, Internal Memory 128 B Program : External Memory 64 KB, Internal Memory 4 KB I/O Port Etc. Parallel I/O port : 32 (4× 8 bits) Serial I/O port : Full Duplex UART 2× 16 Bits Timer Clock Generator 5 Interrupt s 3

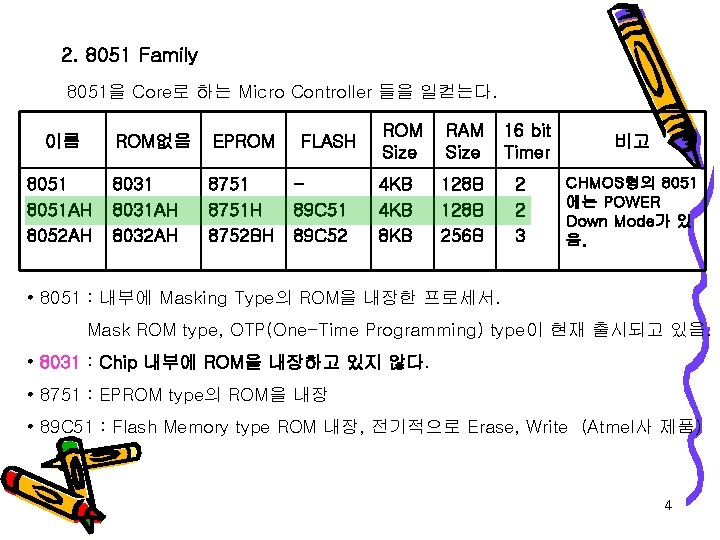

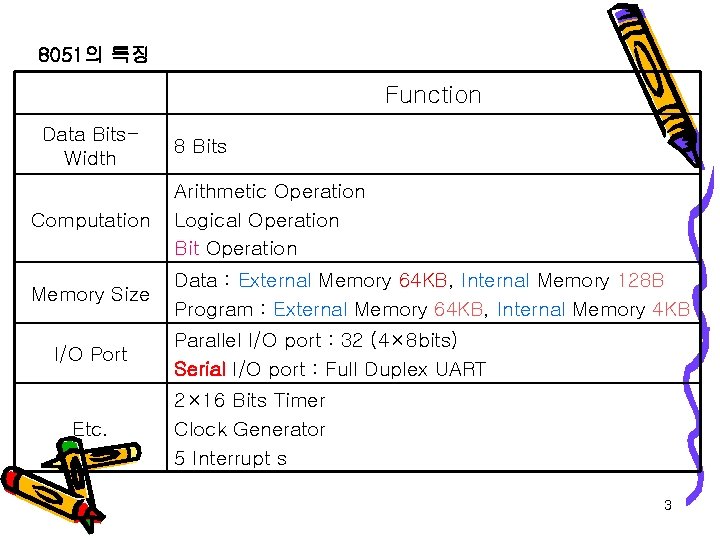

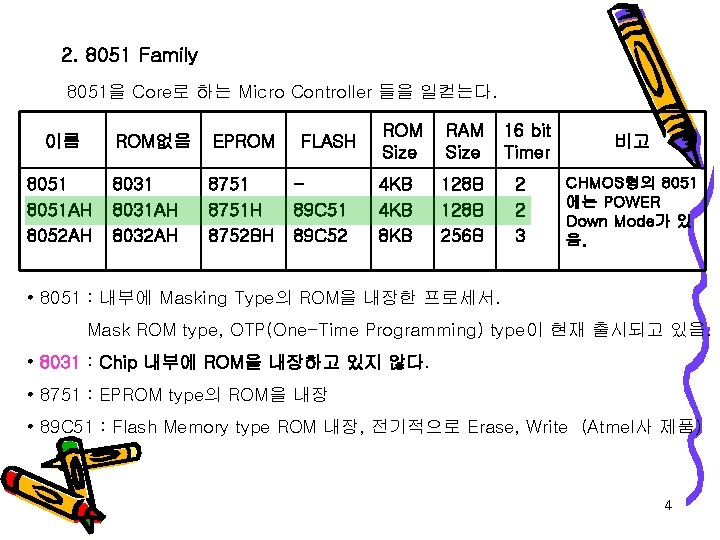

2. 8051 Family 8051을 Core로 하는 Micro Controller 들을 일컫는다. 이름 8051 AH 8052 AH ROM없음 EPROM 8031 AH 8032 AH 8751 H 8752 BH FLASH 89 C 51 89 C 52 ROM Size RAM Size 4 KB 8 KB 128 B 256 B 16 bit Timer 2 2 3 비고 CHMOS형의 8051 에는 POWER Down Mode가 있 음. • 8051 : 내부에 Masking Type의 ROM을 내장한 프로세서. Mask ROM type, OTP(One-Time Programming) type이 현재 출시되고 있음. • 8031 : Chip 내부에 ROM을 내장하고 있지 않다. • 8751 : EPROM type의 ROM을 내장 • 89 C 51 : Flash Memory type ROM 내장, 전기적으로 Erase, Write (Atmel사 제품) 4

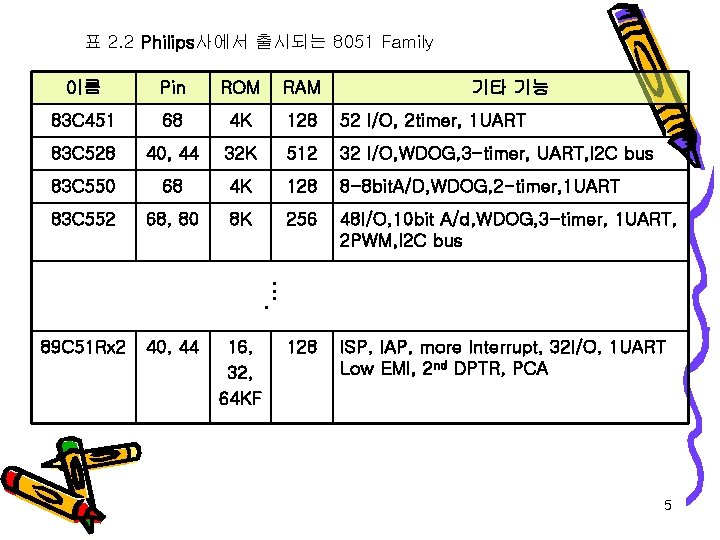

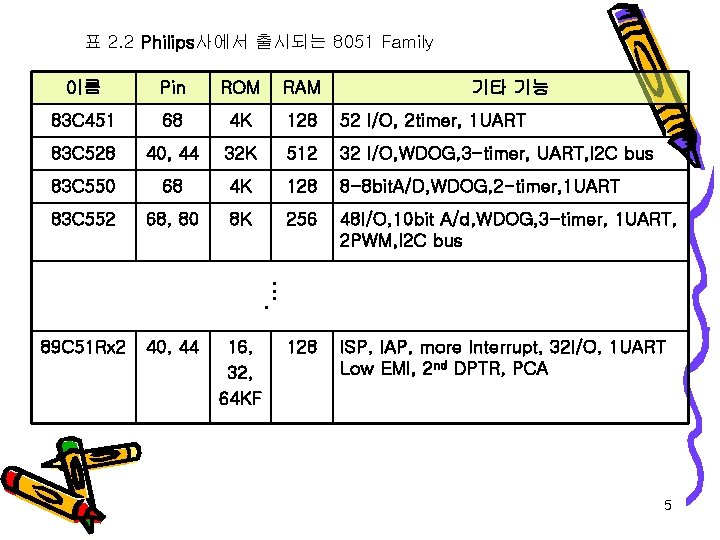

표 2. 2 Philips사에서 출시되는 8051 Family Pin ROM RAM 기타 기능 83 C 451 68 4 K 128 52 I/O, 2 timer, 1 UART 83 C 528 40, 44 32 K 512 32 I/O, WDOG, 3 -timer, UART, I 2 C bus 83 C 550 68 4 K 128 8 -8 bit. A/D, WDOG, 2 -timer, 1 UART 83 C 552 68, 80 8 K 256 48 I/O, 10 bit A/d, WDOG, 3 -timer, 1 UART, 2 PWM, I 2 C bus 89 C 51 Rx 2 40, 44 16, 32, 64 KF 128 ISP, IAP, more Interrupt, 32 I/O, 1 UART Low EMI, 2 nd DPTR, PCA …. 이름 5

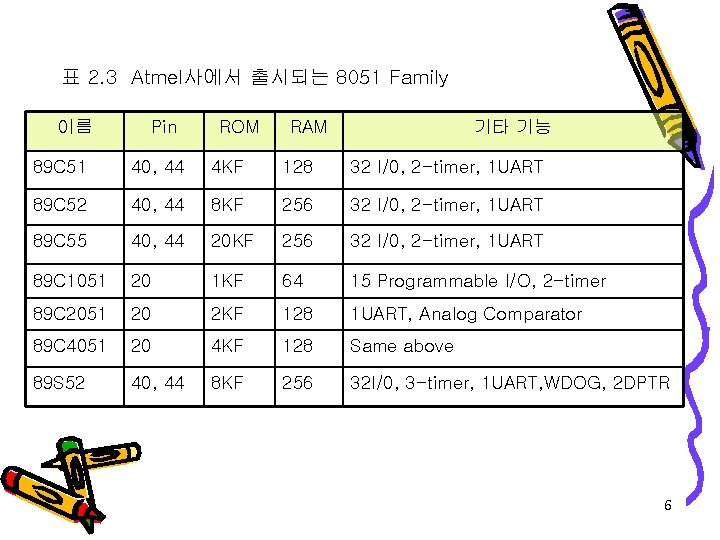

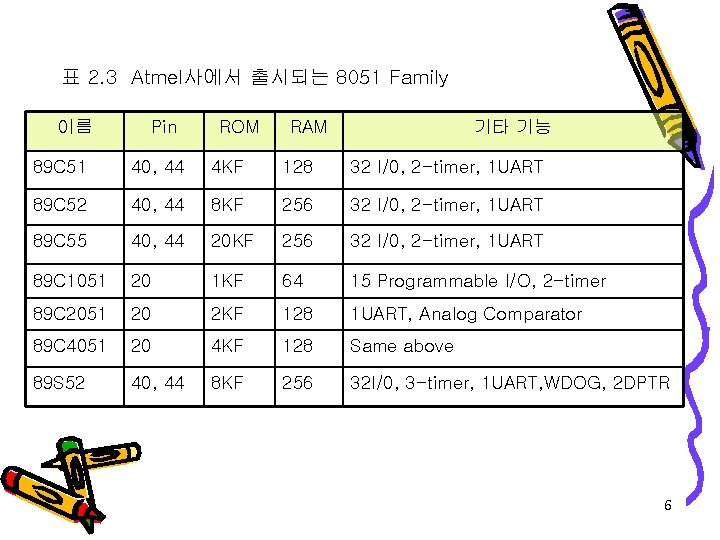

표 2. 3 Atmel사에서 출시되는 8051 Family 이름 Pin ROM RAM 기타 기능 89 C 51 40, 44 4 KF 128 32 I/0, 2 -timer, 1 UART 89 C 52 40, 44 8 KF 256 32 I/0, 2 -timer, 1 UART 89 C 55 40, 44 20 KF 256 32 I/0, 2 -timer, 1 UART 89 C 1051 20 1 KF 64 15 Programmable I/O, 2 -timer 89 C 2051 20 2 KF 128 1 UART, Analog Comparator 89 C 4051 20 4 KF 128 Same above 89 S 52 40, 44 8 KF 256 32 I/0, 3 -timer, 1 UART, WDOG, 2 DPTR 6

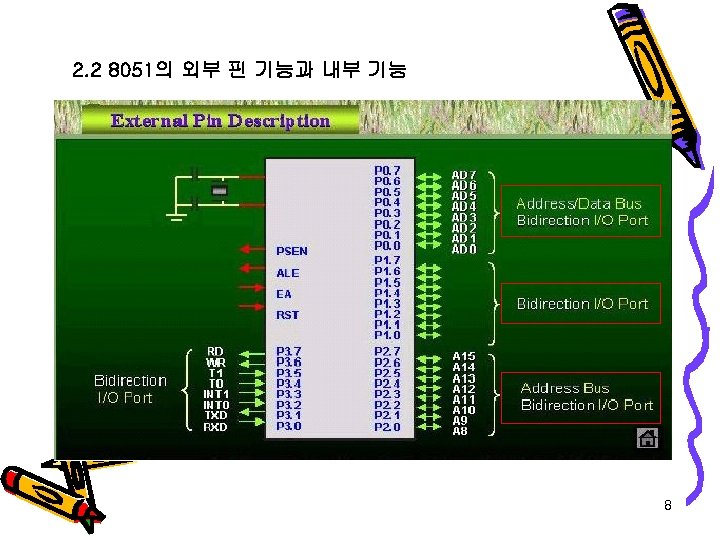

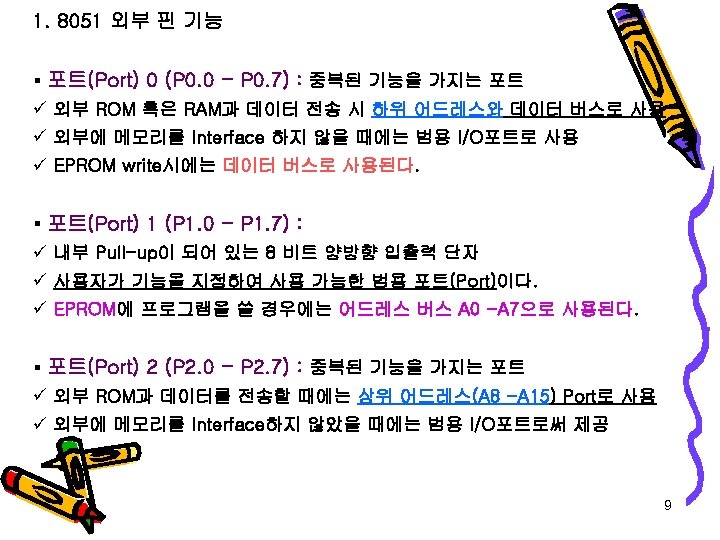

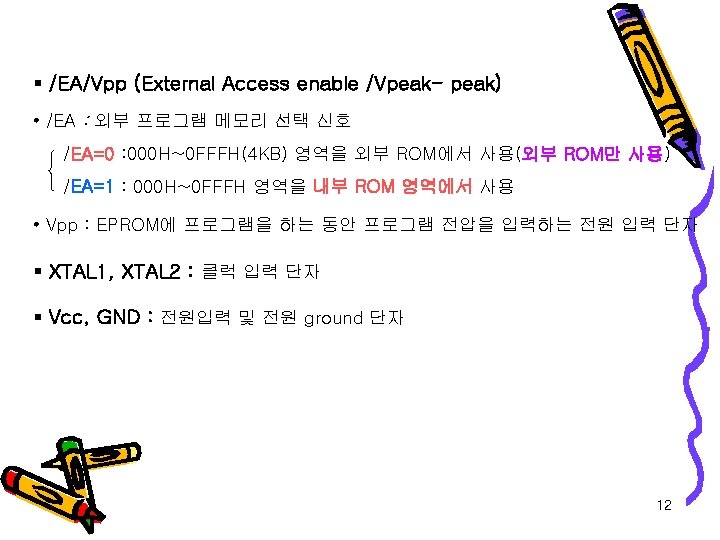

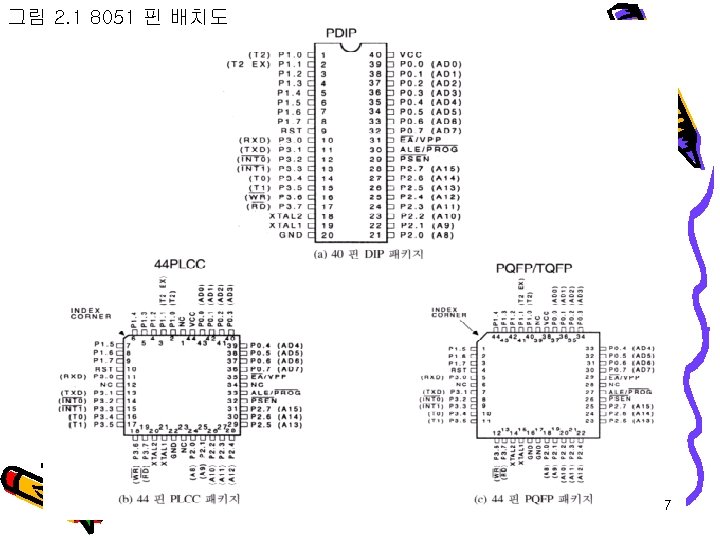

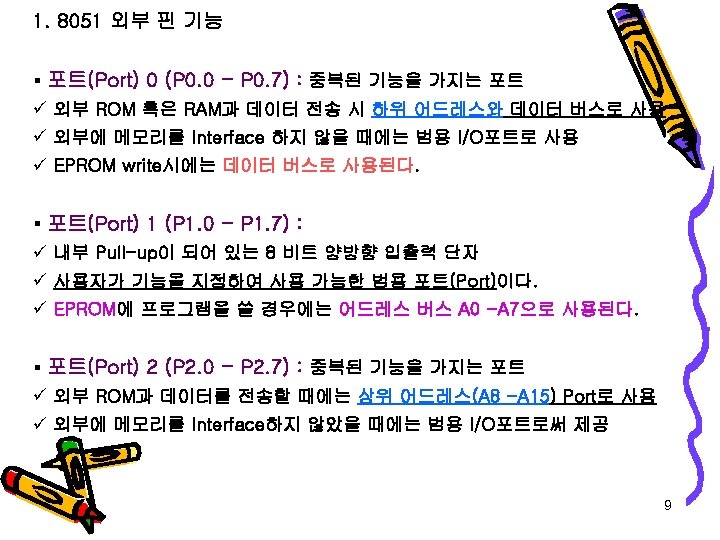

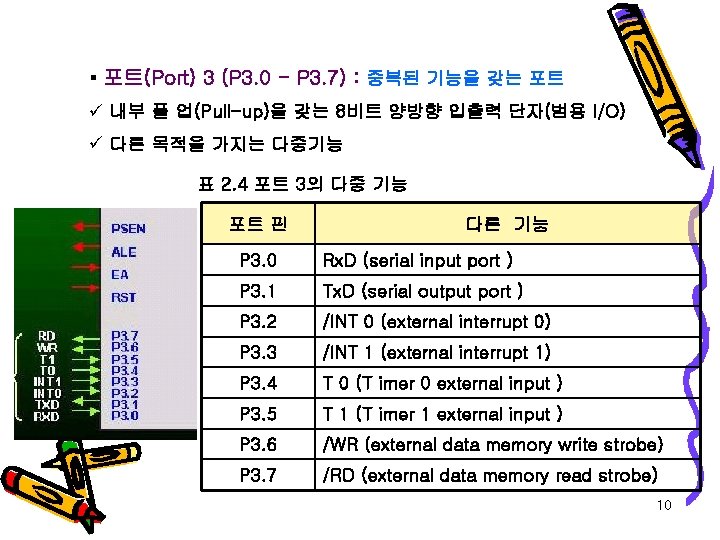

§ 포트(Port) 3 (P 3. 0 - P 3. 7) : 중복된 기능을 갖는 포트 ü 내부 풀 업(Pull-up)을 갖는 8비트 양방향 입출력 단자(범용 I/O) ü 다른 목적을 가지는 다중기능 표 2. 4 포트 3의 다중 기능 포트 핀 다른 기능 P 3. 0 Rx. D (serial input port ) P 3. 1 Tx. D (serial output port ) P 3. 2 /INT 0 (external interrupt 0) P 3. 3 /INT 1 (external interrupt 1) P 3. 4 T 0 (T imer 0 external input ) P 3. 5 T 1 (T imer 1 external input ) P 3. 6 /WR (external data memory write strobe) P 3. 7 /RD (external data memory read strobe) 10

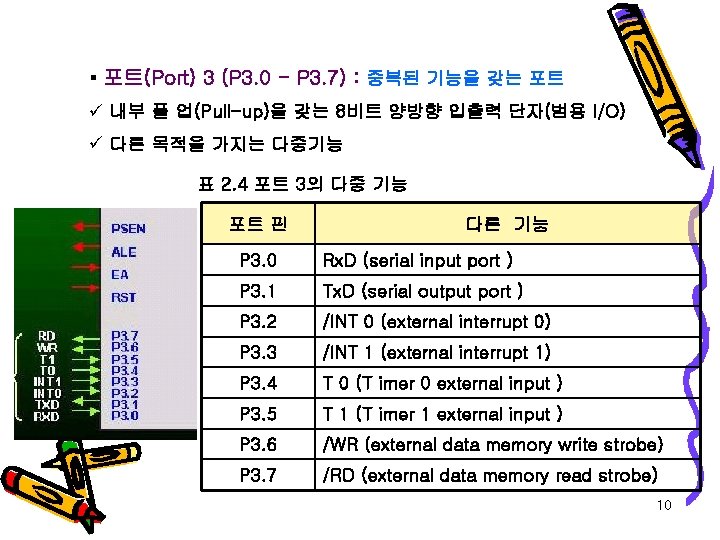

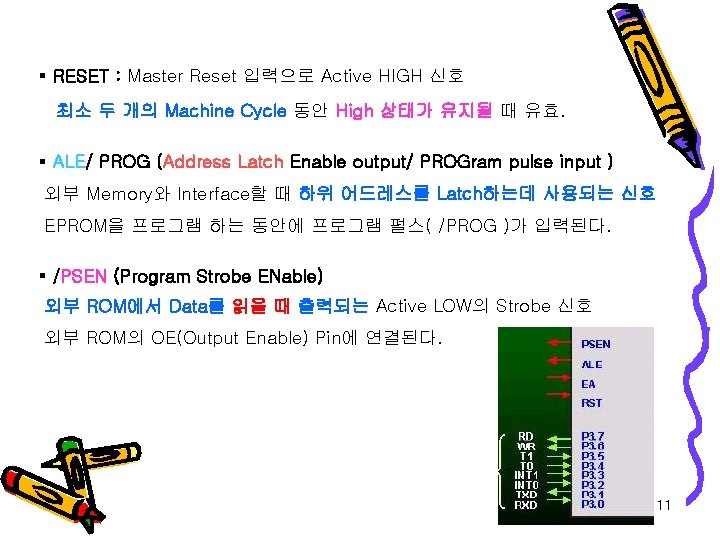

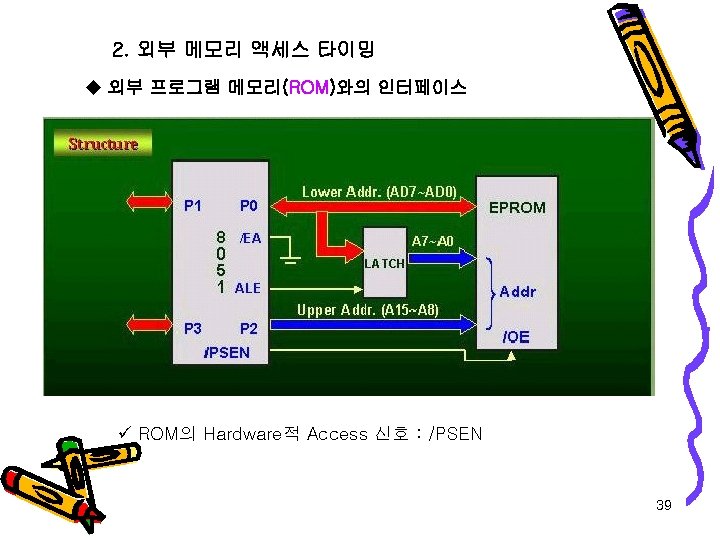

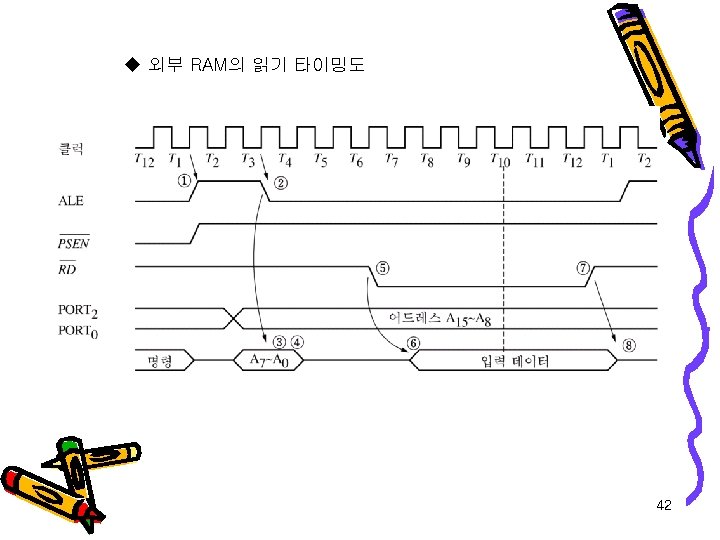

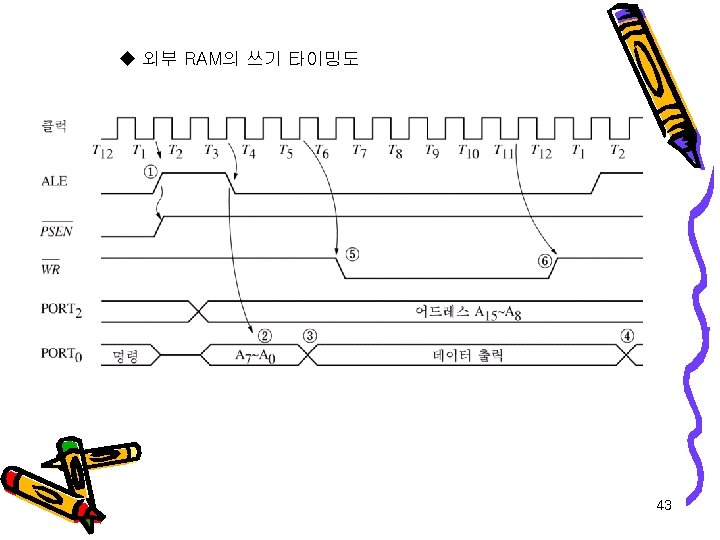

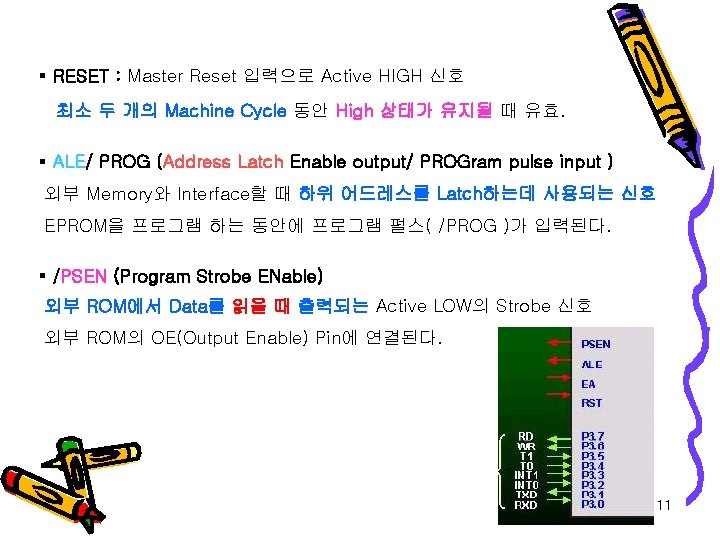

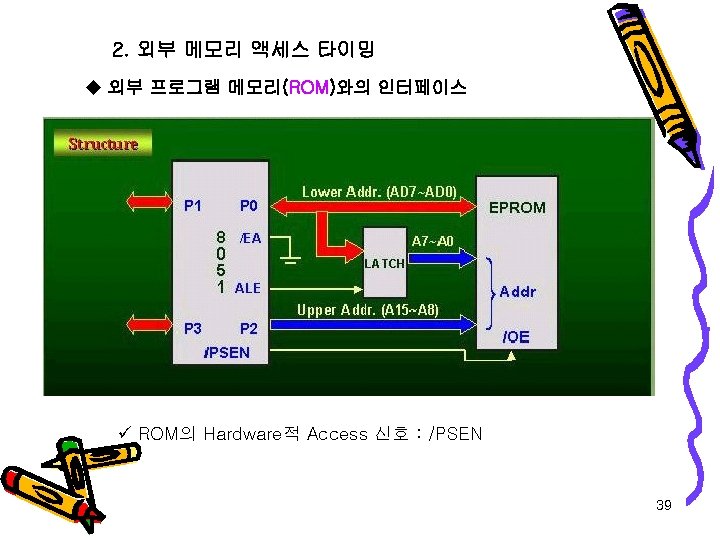

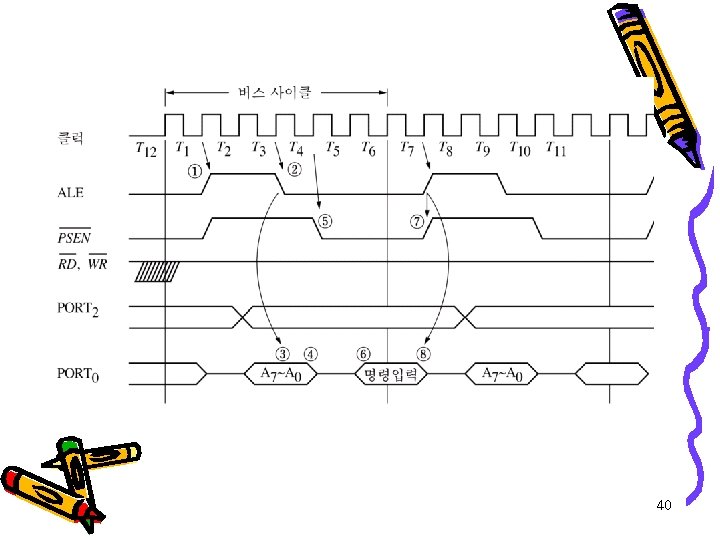

§ RESET : Master Reset 입력으로 Active HIGH 신호 최소 두 개의 Machine Cycle 동안 High 상태가 유지될 때 유효. § ALE/ PROG (Address Latch Enable output/ PROGram pulse input ) 외부 Memory와 Interface할 때 하위 어드레스를 Latch하는데 사용되는 신호 EPROM을 프로그램 하는 동안에 프로그램 펄스( /PROG )가 입력된다. § /PSEN (Program Strobe ENable) 외부 ROM에서 Data를 읽을 때 출력되는 Active LOW의 Strobe 신호 외부 ROM의 OE(Output Enable) Pin에 연결된다. 11

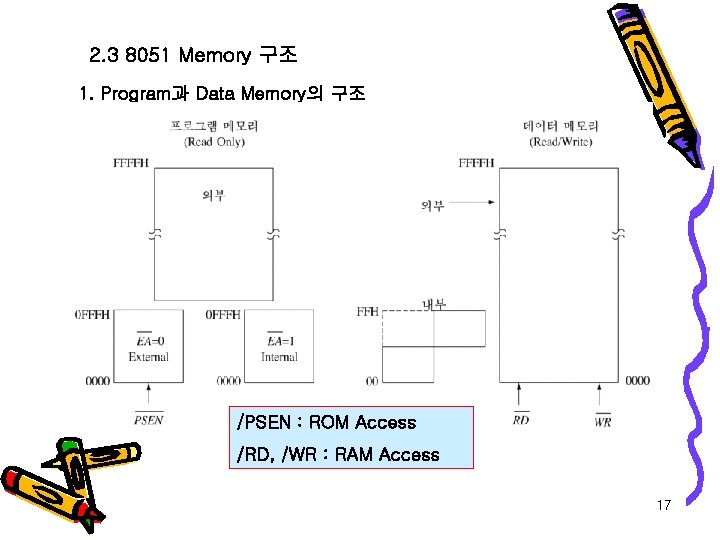

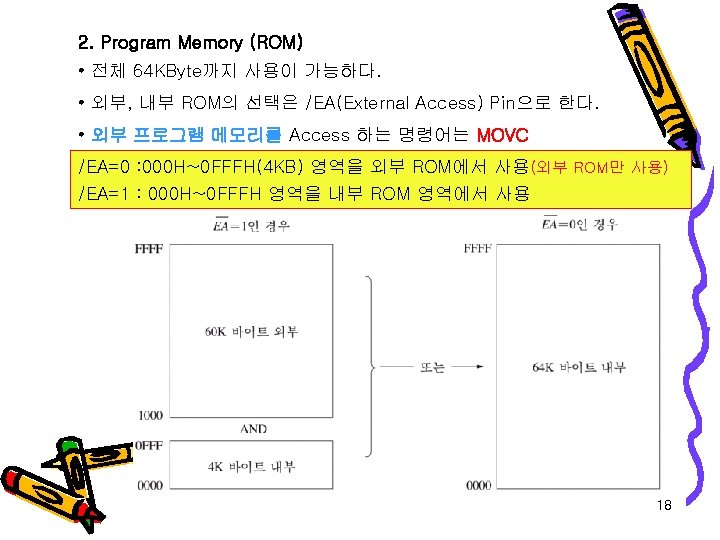

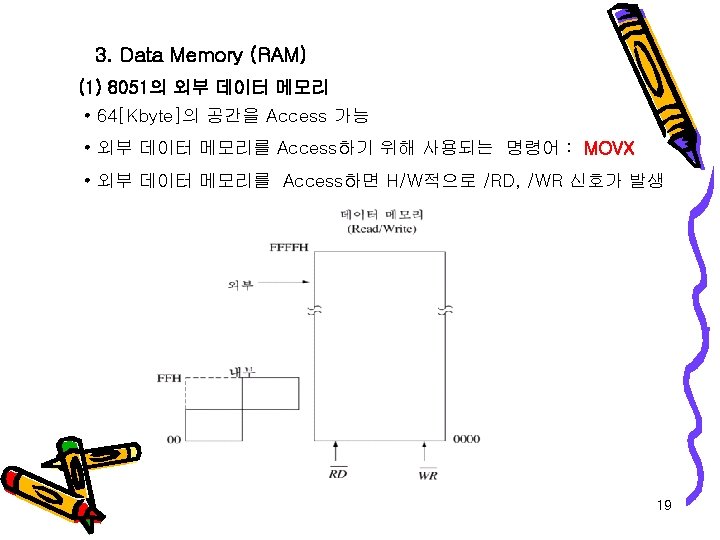

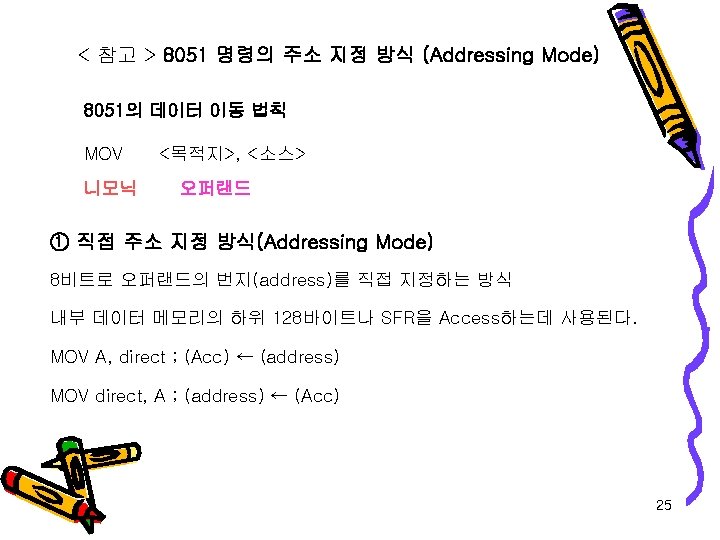

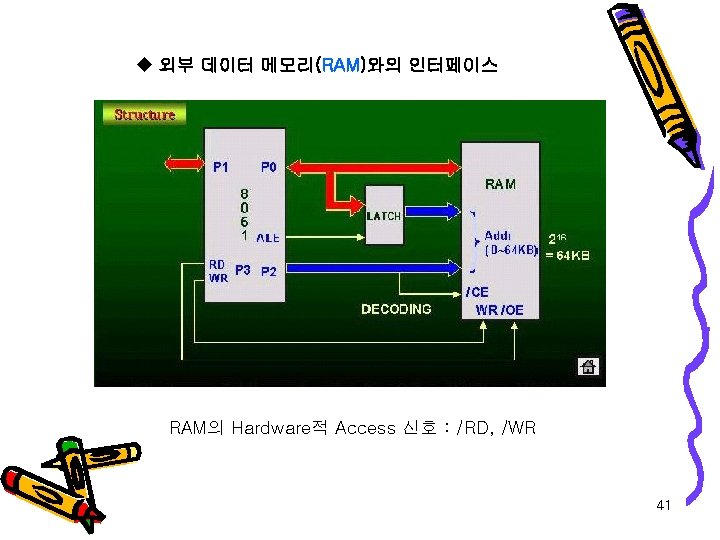

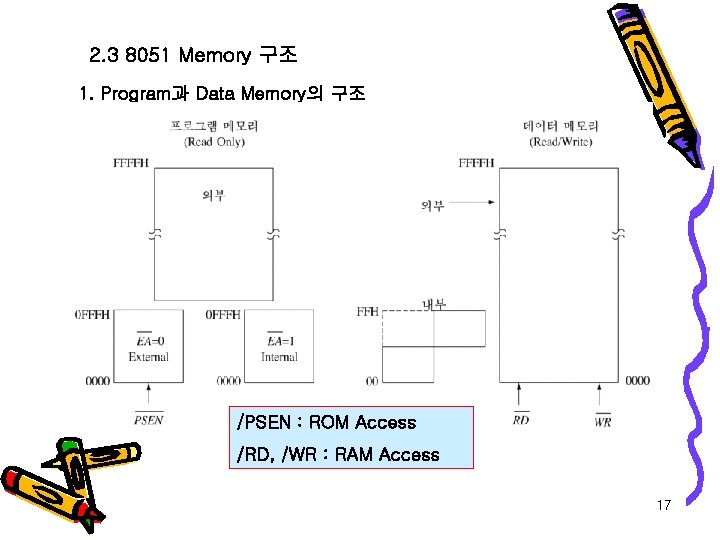

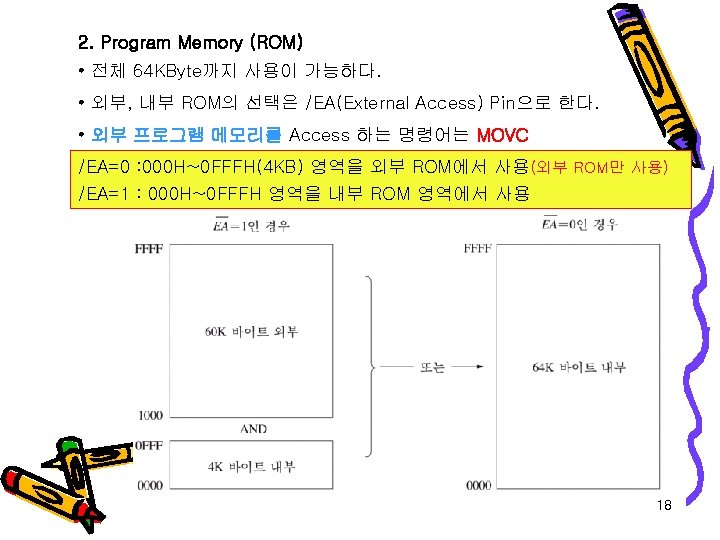

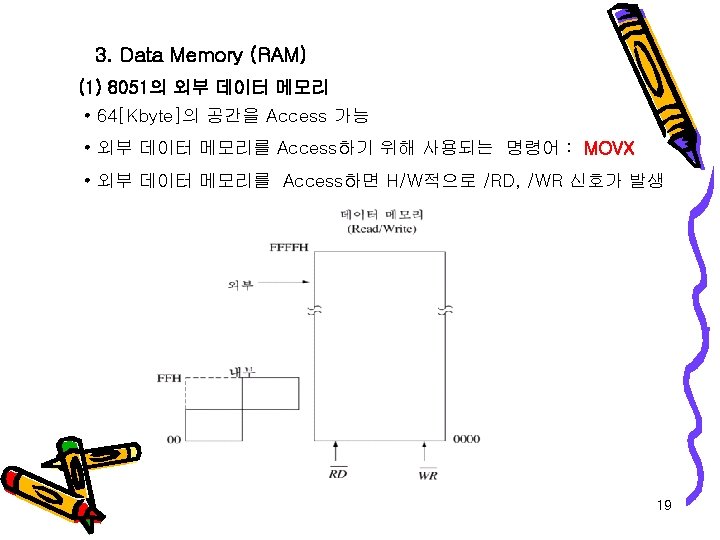

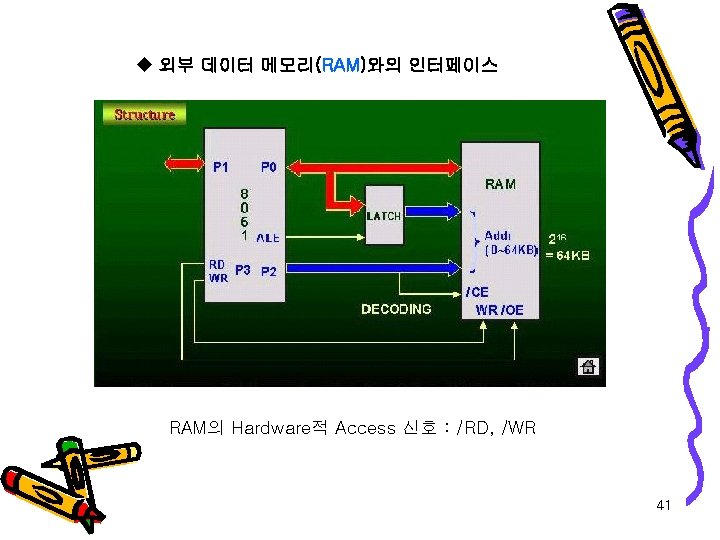

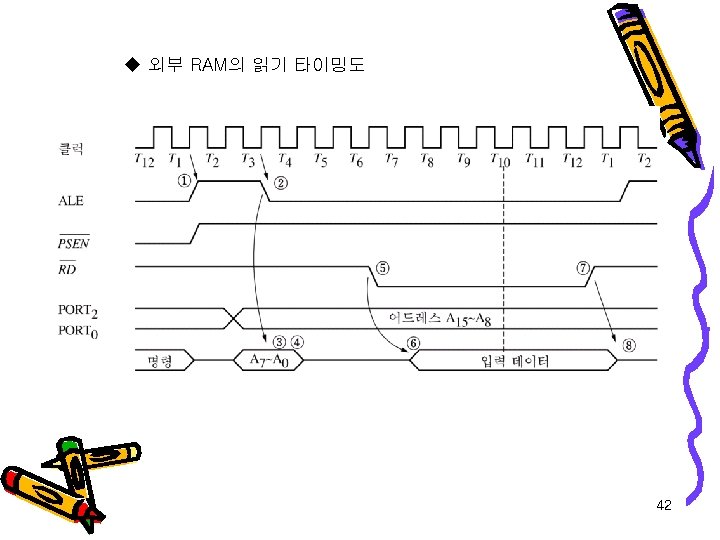

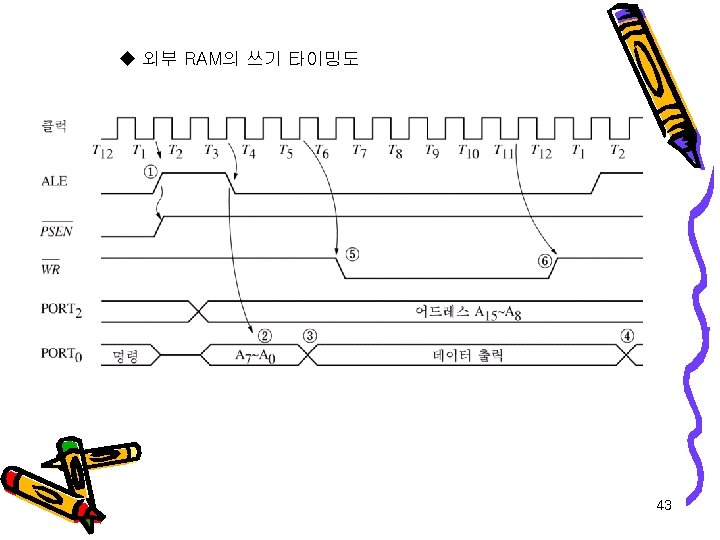

2. 3 8051 Memory 구조 1. Program과 Data Memory의 구조 /PSEN : ROM Access /RD, /WR : RAM Access 17

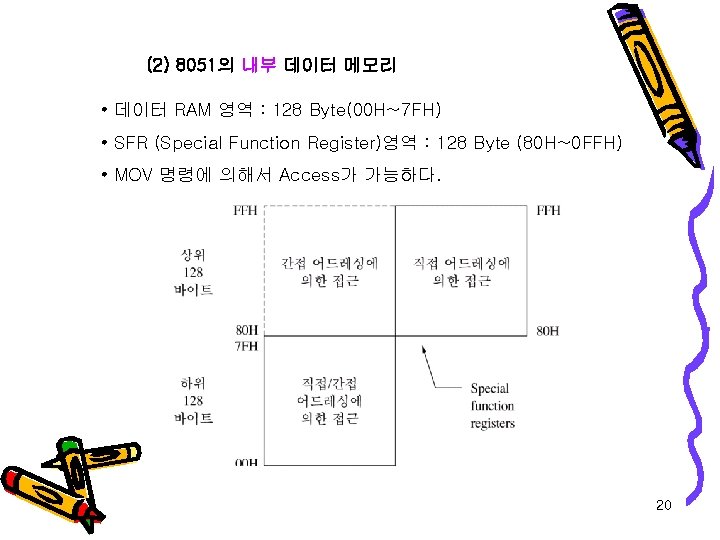

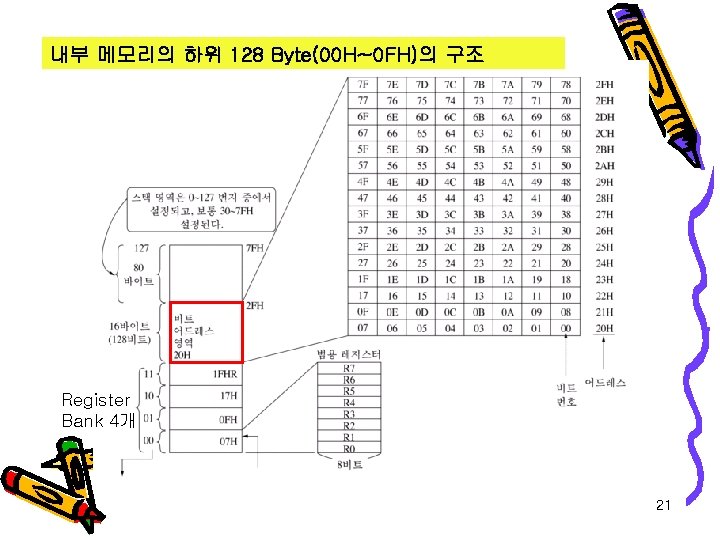

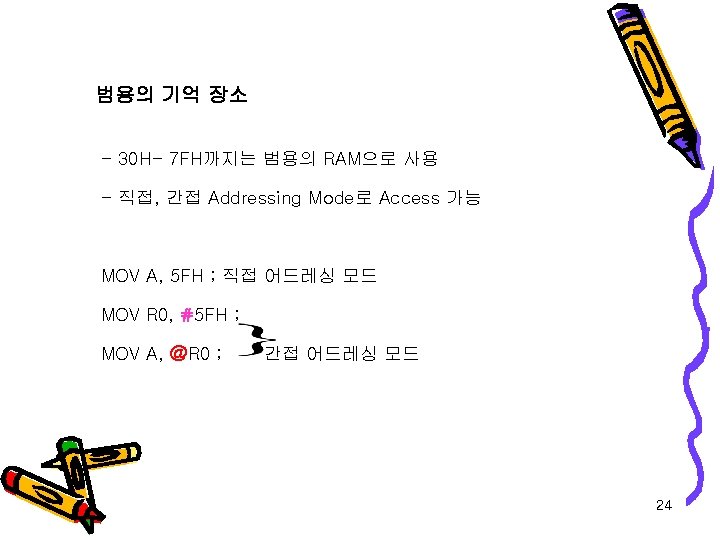

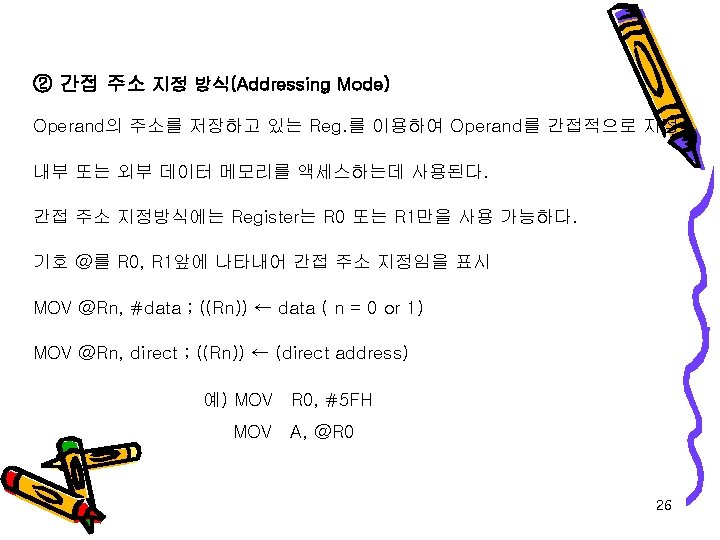

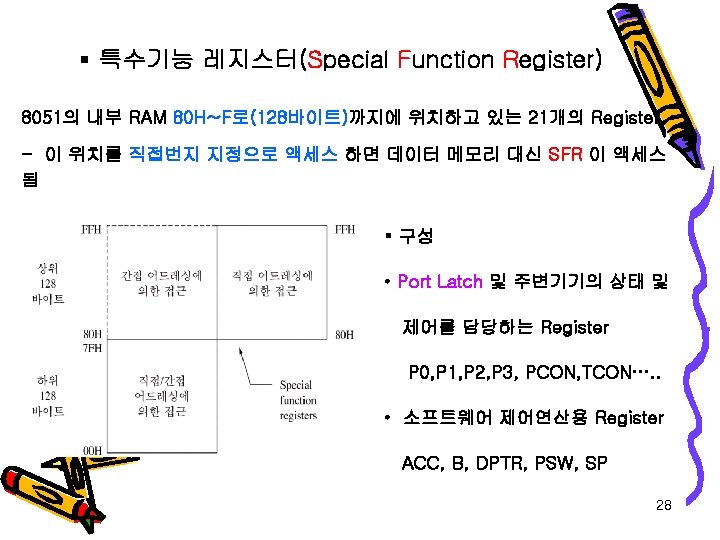

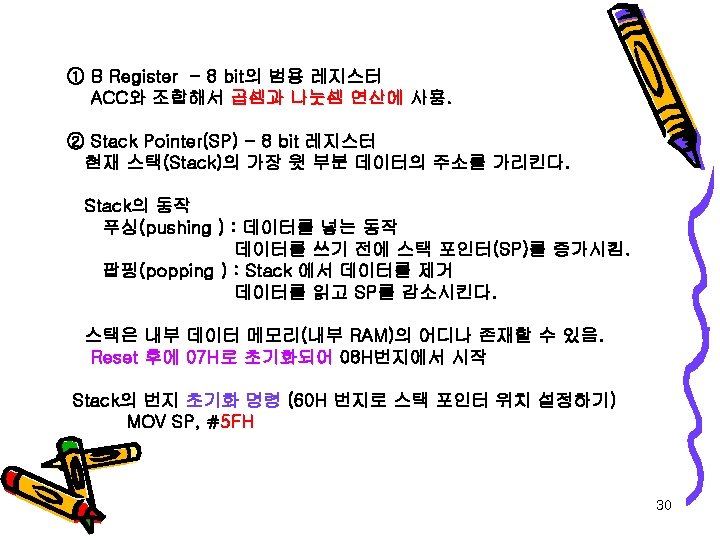

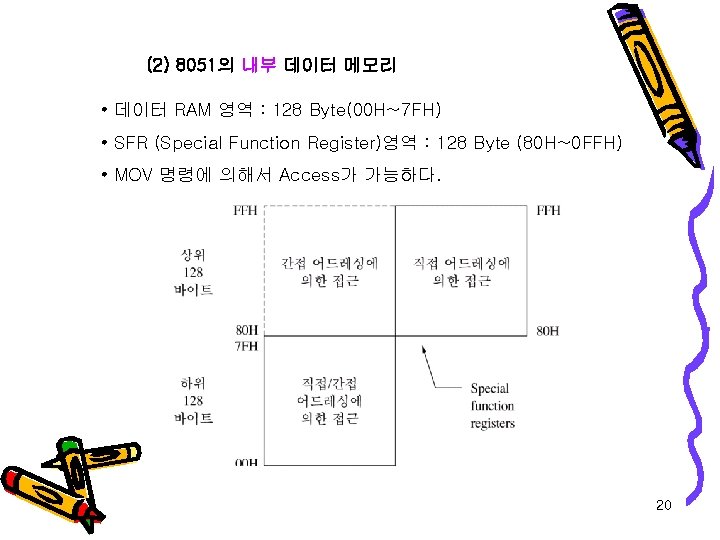

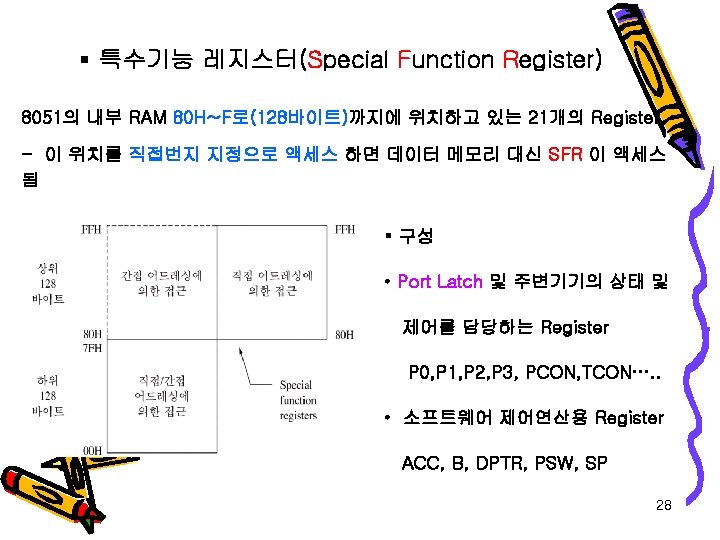

(2) 8051의 내부 데이터 메모리 • 데이터 RAM 영역 : 128 Byte(00 H~7 FH) • SFR (Special Function Register)영역 : 128 Byte (80 H~0 FFH) • MOV 명령에 의해서 Access가 가능하다. 20

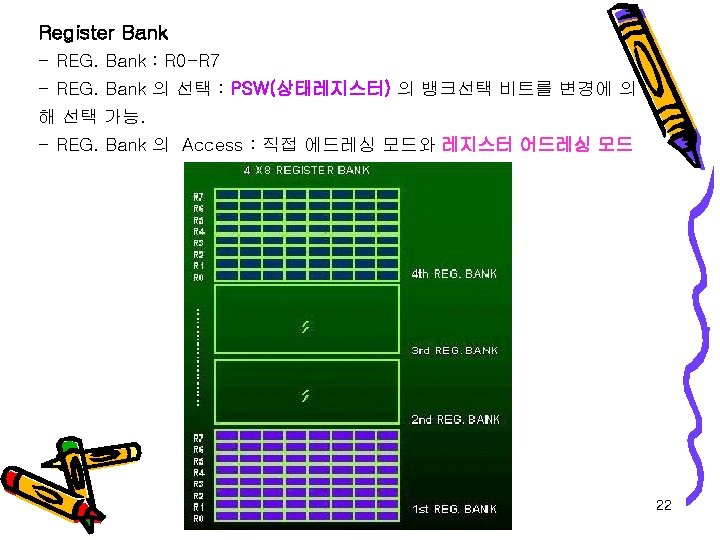

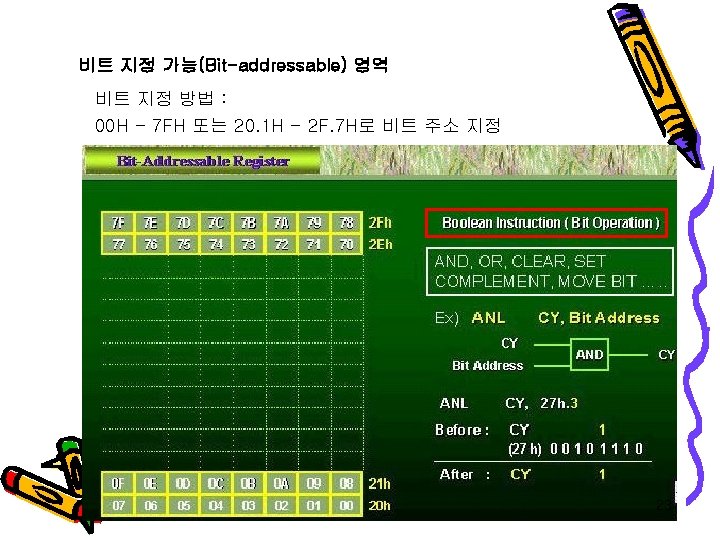

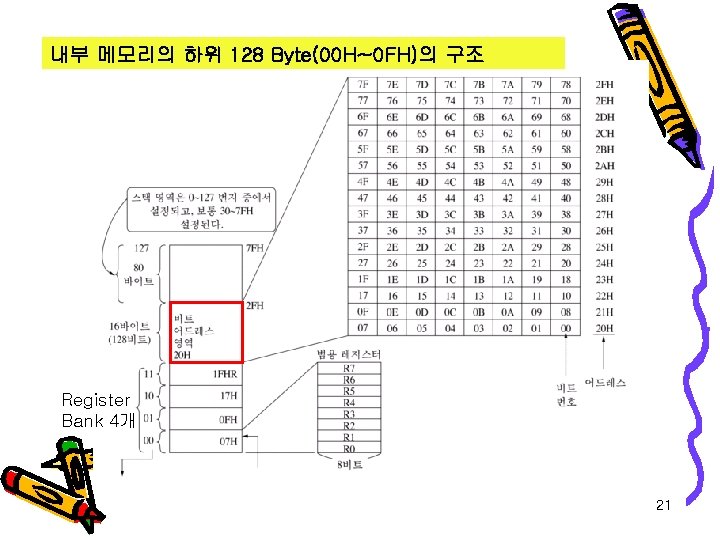

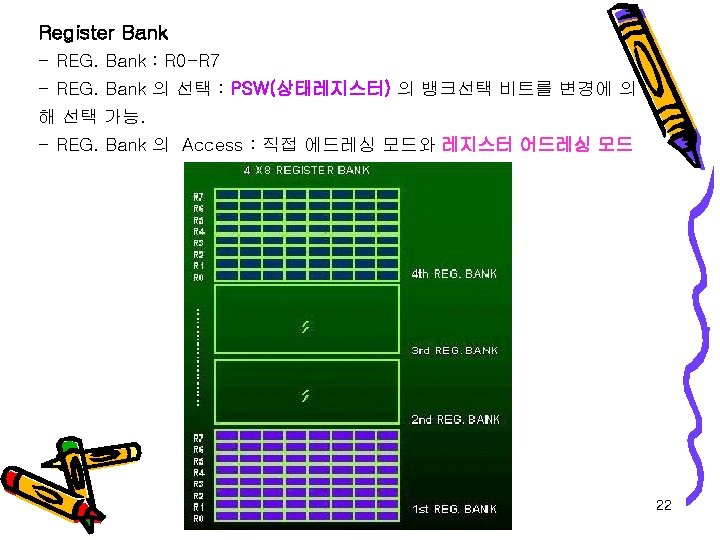

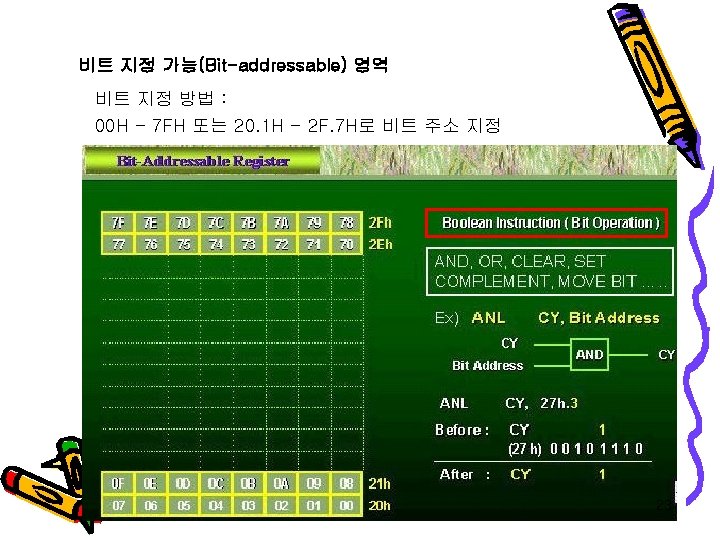

내부 메모리의 하위 128 Byte(00 H~0 FH)의 구조 Register Bank 4개 21

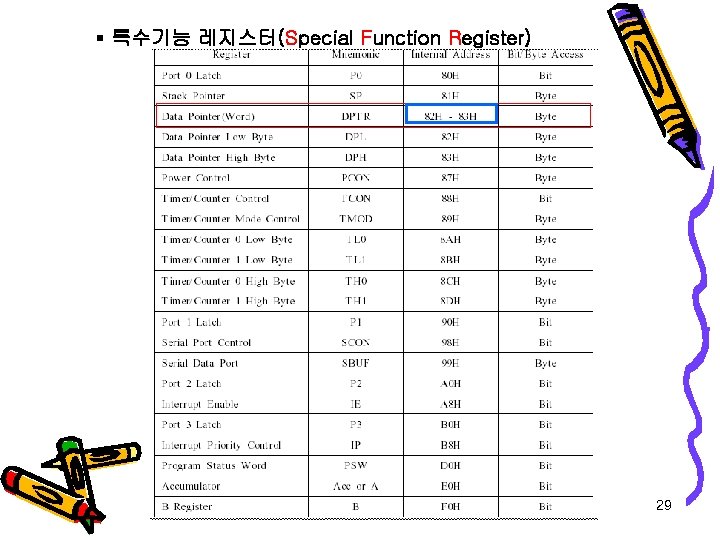

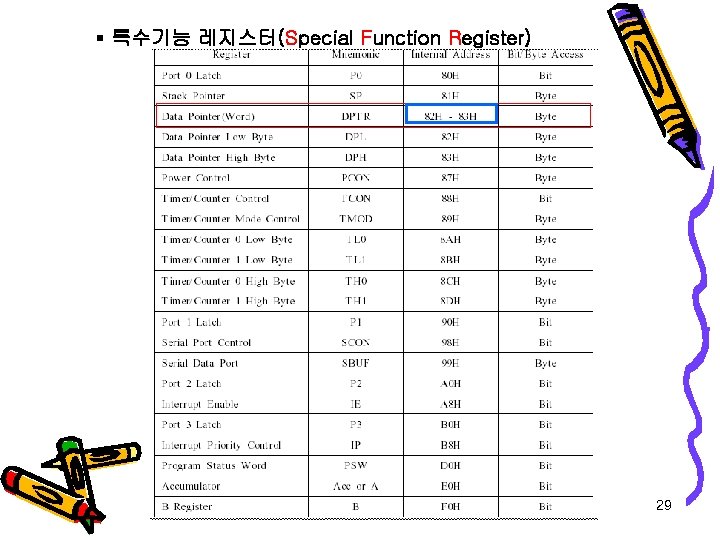

§ 특수기능 레지스터(Special Function Register) 29

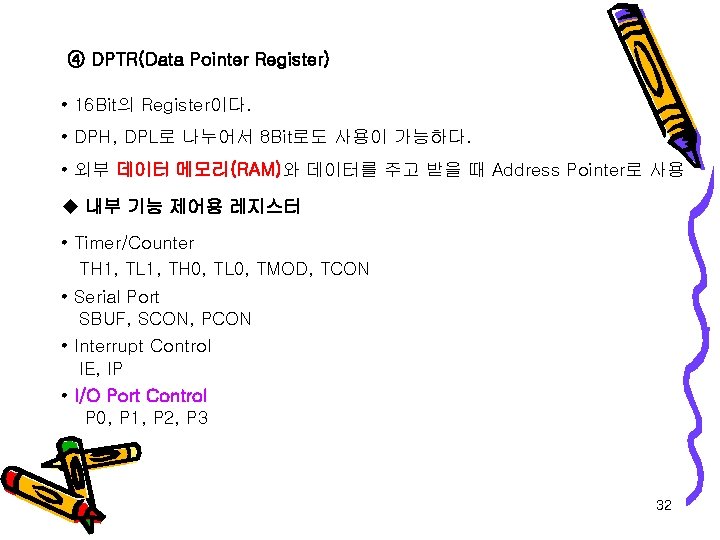

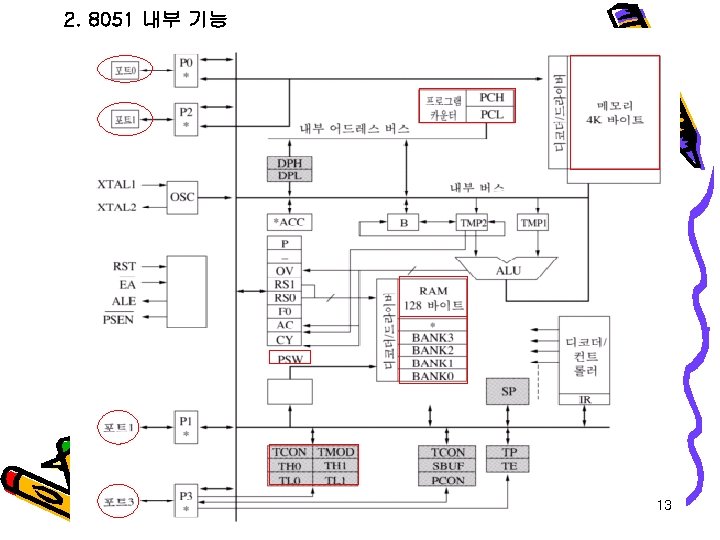

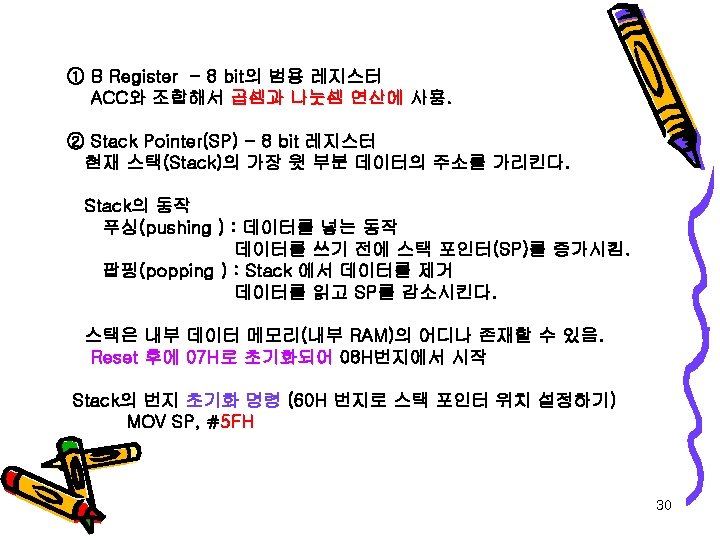

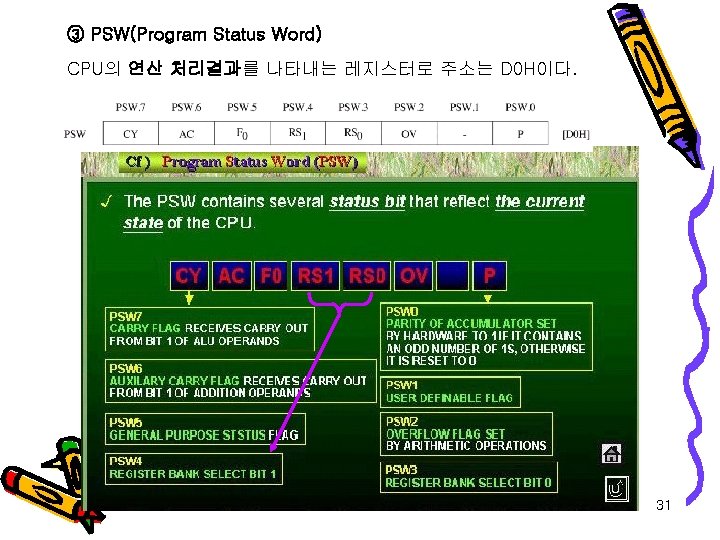

④ DPTR(Data Pointer Register) • 16 Bit의 Register이다. • DPH, DPL로 나누어서 8 Bit로도 사용이 가능하다. • 외부 데이터 메모리(RAM)와 데이터를 주고 받을 때 Address Pointer로 사용 u 내부 기능 제어용 레지스터 • Timer/Counter TH 1, TL 1, TH 0, TL 0, TMOD, TCON • Serial Port SBUF, SCON, PCON • Interrupt Control IE, IP • I/O Port Control P 0, P 1, P 2, P 3 32

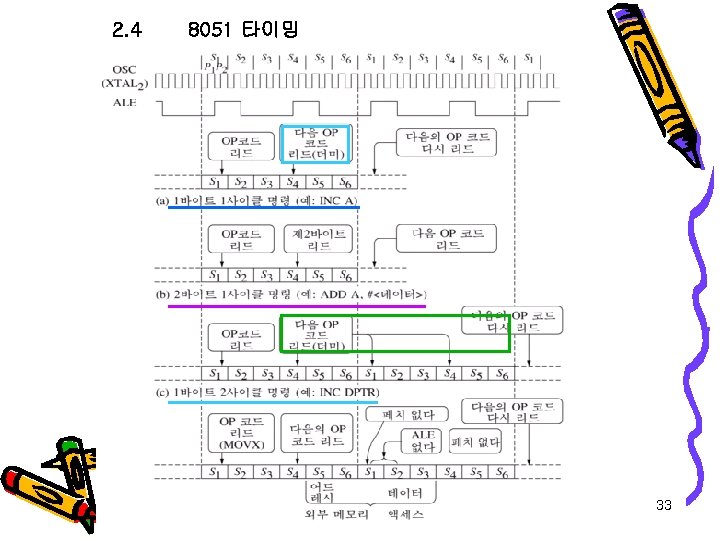

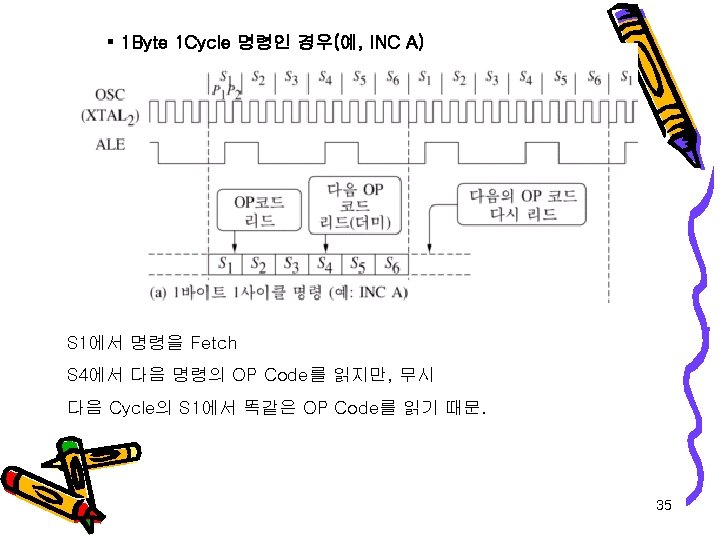

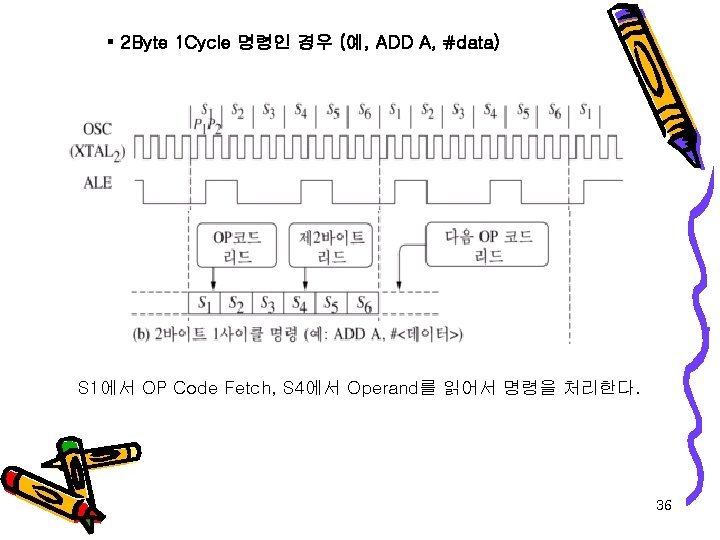

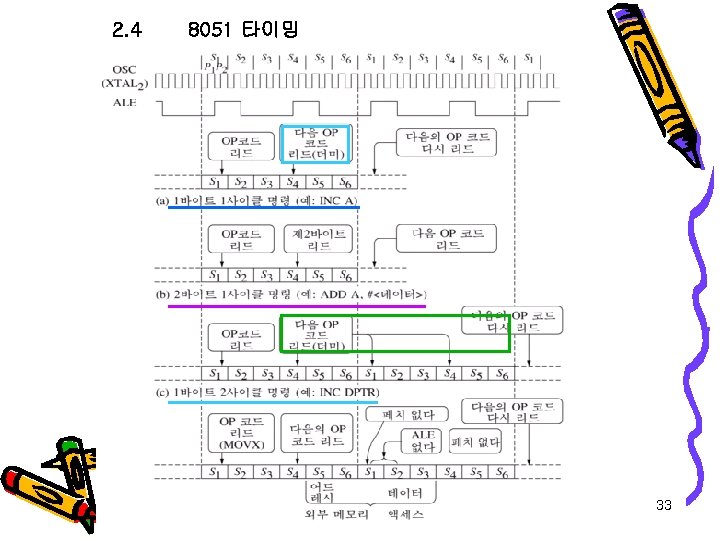

2. 4 8051 타이밍 33

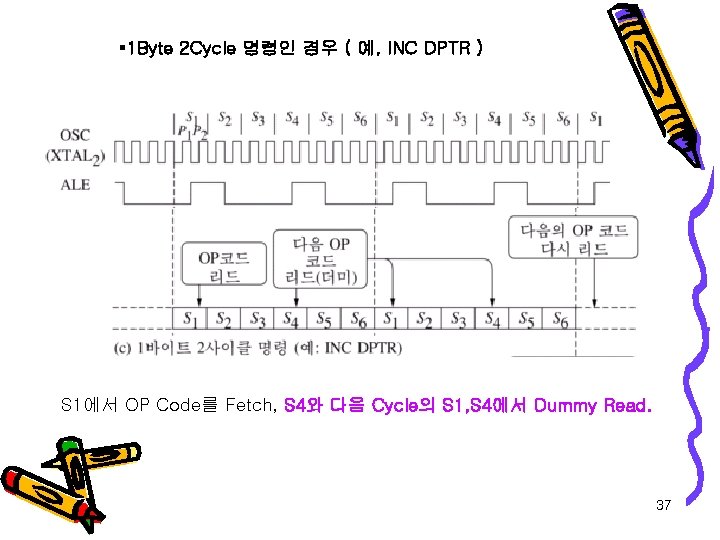

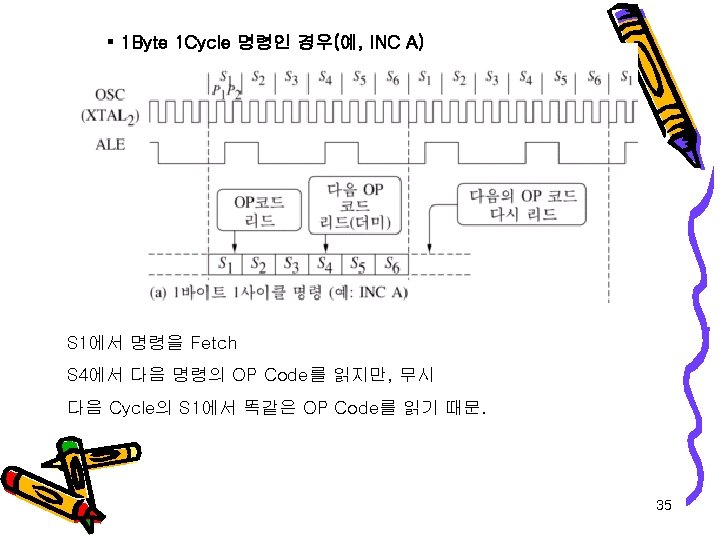

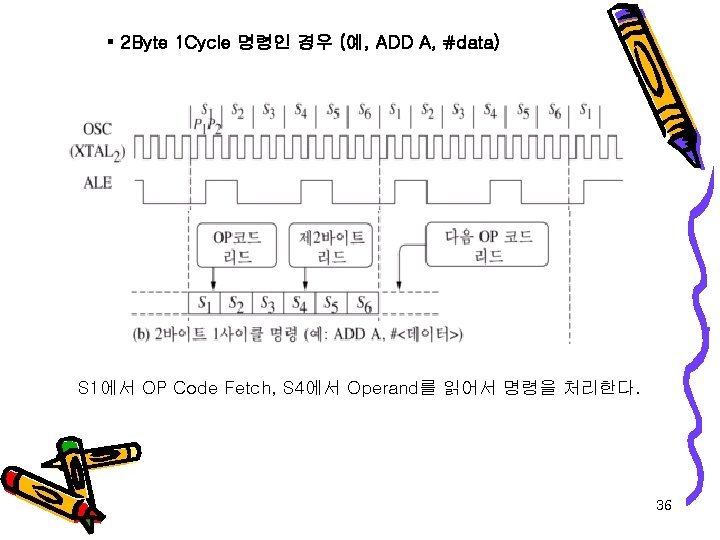

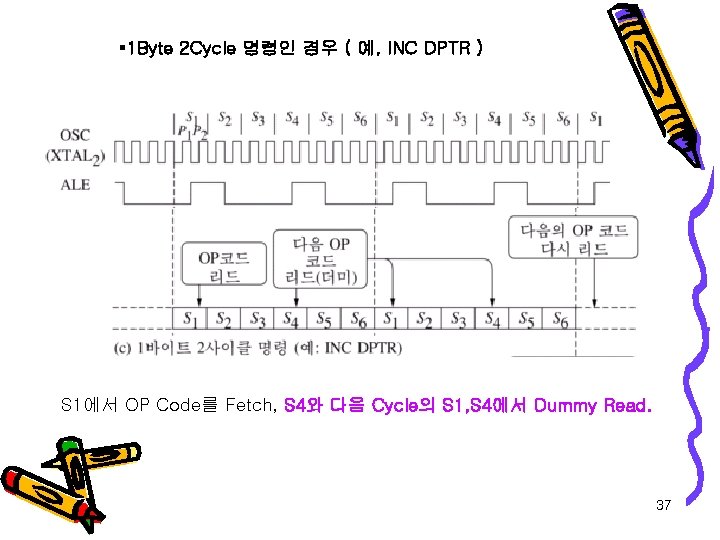

§ 1 Byte 2 Cycle 명령인 경우 ( 예, INC DPTR ) S 1에서 OP Code를 Fetch, S 4와 다음 Cycle의 S 1, S 4에서 Dummy Read. 37

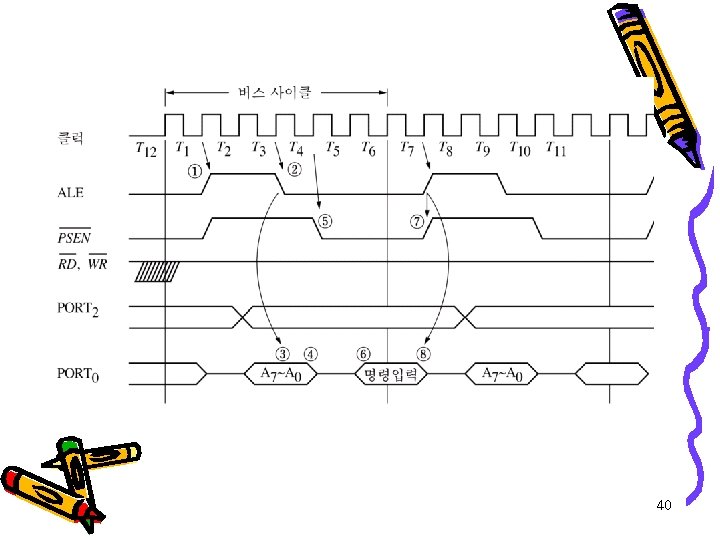

40

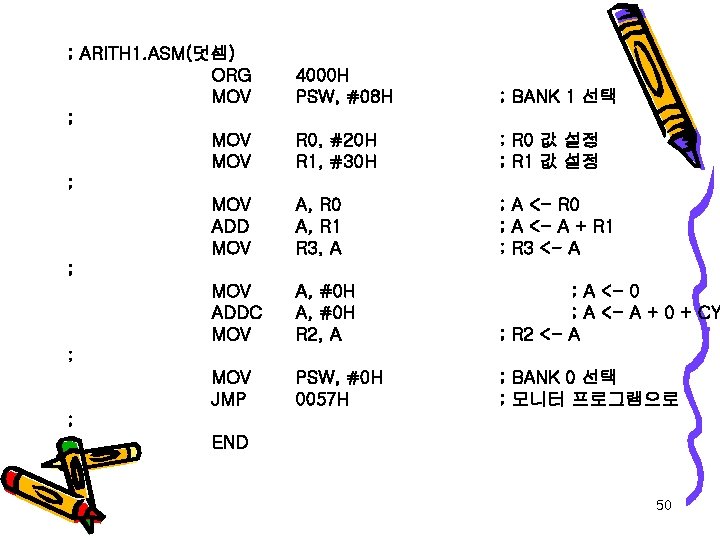

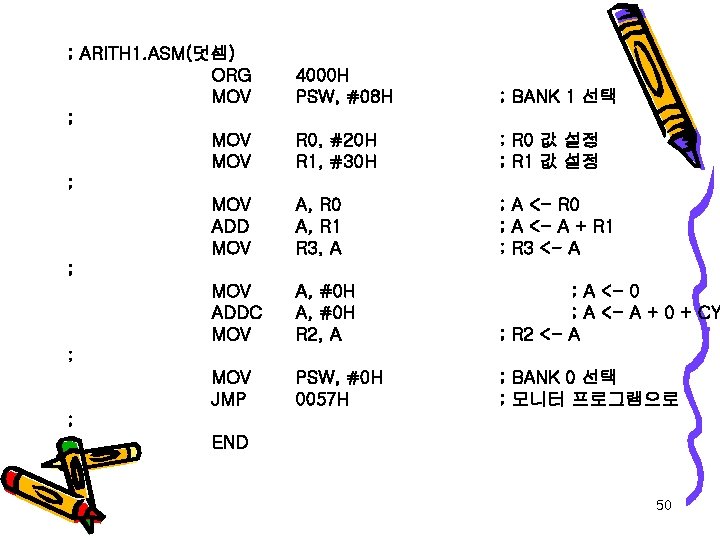

; ARITH 1. ASM(덧셈) ORG MOV ; MOV ADDC MOV ; MOV JMP ; END 4000 H PSW, #08 H ; BANK 1 선택 R 0, #20 H R 1, #30 H ; R 0 값 설정 ; R 1 값 설정 A, R 0 A, R 1 R 3, A ; A <- R 0 ; A <- A + R 1 ; R 3 <- A A, #0 H R 2, A ; A <- 0 ; A <- A + 0 + CY ; R 2 <- A PSW, #0 H 0057 H ; BANK 0 선택 ; 모니터 프로그램으로 50

• • • • • • ; ARITH 2. ASM(뺄셈) ORG MOV ; MOV MOV ; CLR MOV SUBB MOV ; MOV JMP 로 END 4000 H PSW, #08 H ; BANK 1 선택 R 2, R 3, R 4, R 5, ; ; R 2 R 3 R 4 R 5 C A, R 3 A, R 5 R 7, A ; ; CY <- 0 A <- R 3 A <- A - R 3 - CY R 7 <- A A, R 2 A, R 4 R 6, A ; A <- R 2 ; A <- A - R 4 - CY ; R 6 <- A PSW, #0 H 0057 H ; BANK 0 선택 ; 모니터 프로그램으 #34 H #56 H #12 H #34 H 값 값 설정 설정 51

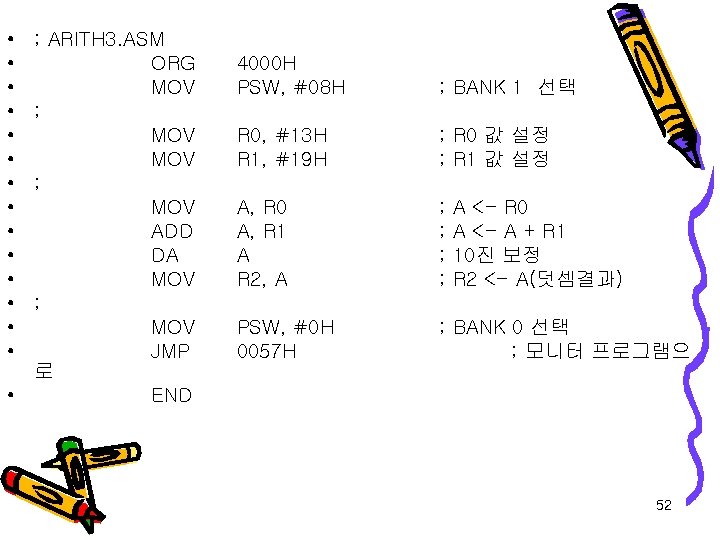

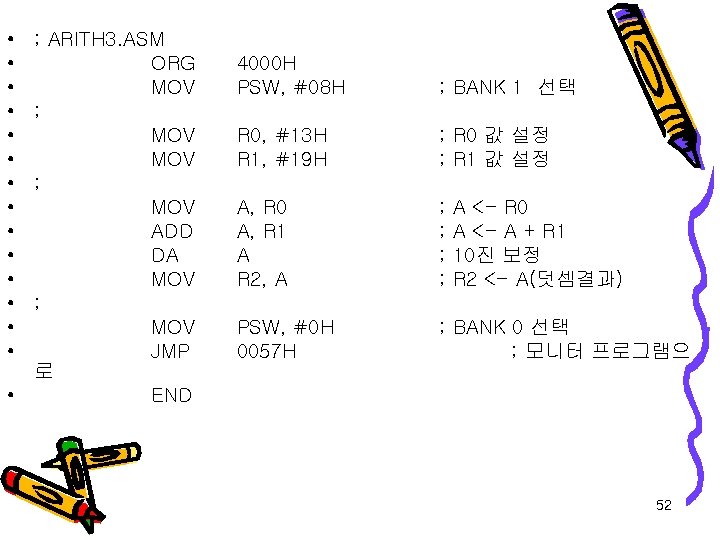

• • • • ; ARITH 3. ASM ORG MOV ; MOV ADD DA MOV ; MOV JMP 로 • END 4000 H PSW, #08 H ; BANK 1 선택 R 0, #13 H R 1, #19 H ; R 0 값 설정 ; R 1 값 설정 A, R 0 A, R 1 A R 2, A ; ; PSW, #0 H 0057 H ; BANK 0 선택 ; 모니터 프로그램으 A <- R 0 A <- A + R 1 10진 보정 R 2 <- A(덧셈결과) 52

• • • • ; ARITH 4. ASM(곱셈) ORG MOV ; MOV MOV MUL ; MOV JMP 로 • END 4000 H PSW, #08 H ; BANK 1 선택 R 0, #9 R 1, #11 B, R 0 A, R 1 AB R 3, A R 2, B PSW, #0 H 0057 H ; BANK 0 선택 ; 모니터 프로그램으 53

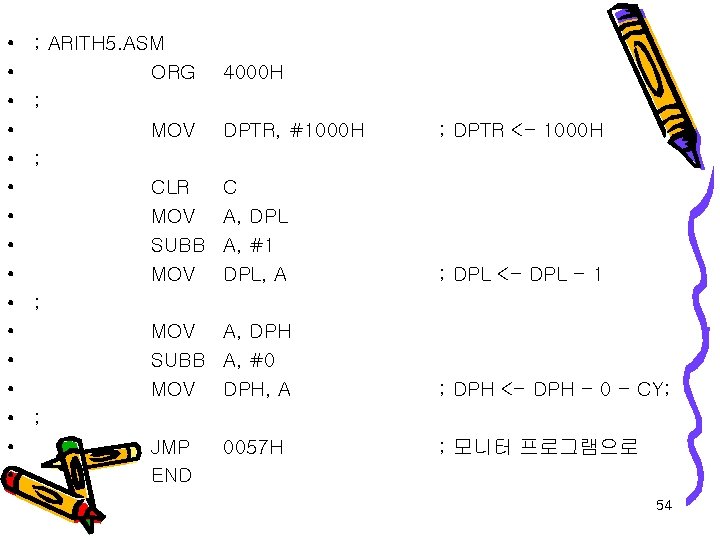

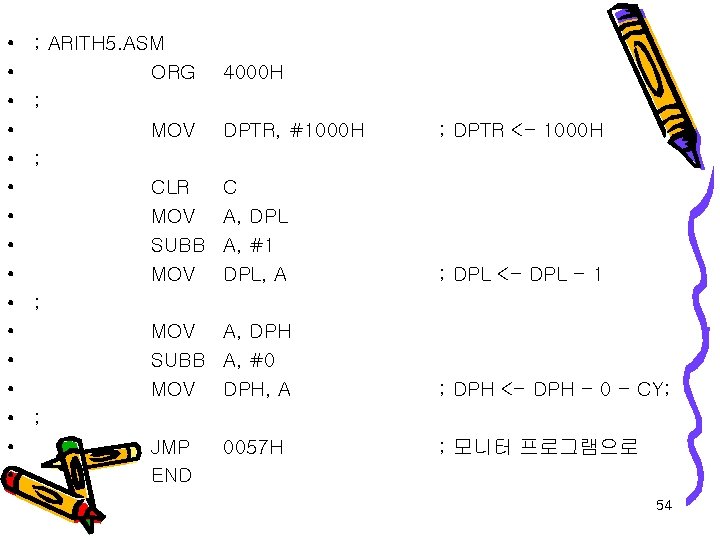

• • • • ; ARITH 5. ASM ORG ; MOV ; CLR MOV SUBB MOV ; JMP END 4000 H DPTR, #1000 H ; DPTR <- 1000 H C A, DPL A, #1 DPL, A ; DPL <- DPL - 1 A, DPH A, #0 DPH, A ; DPH <- DPH - 0 - CY; 0057 H ; 모니터 프로그램으로 54

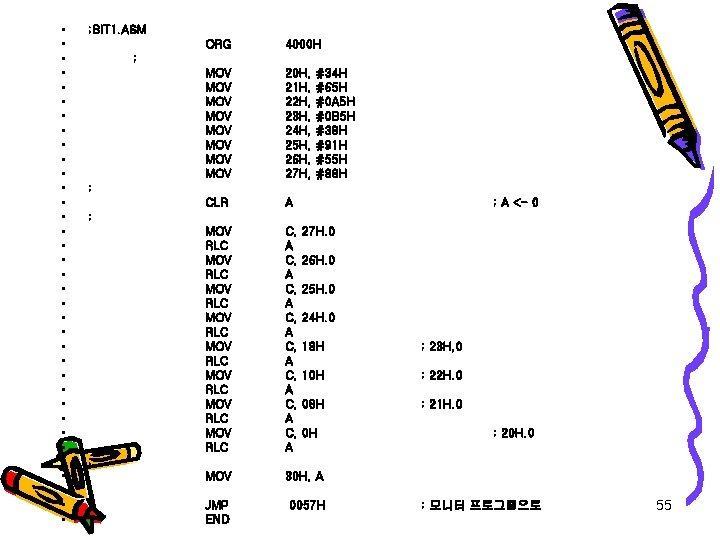

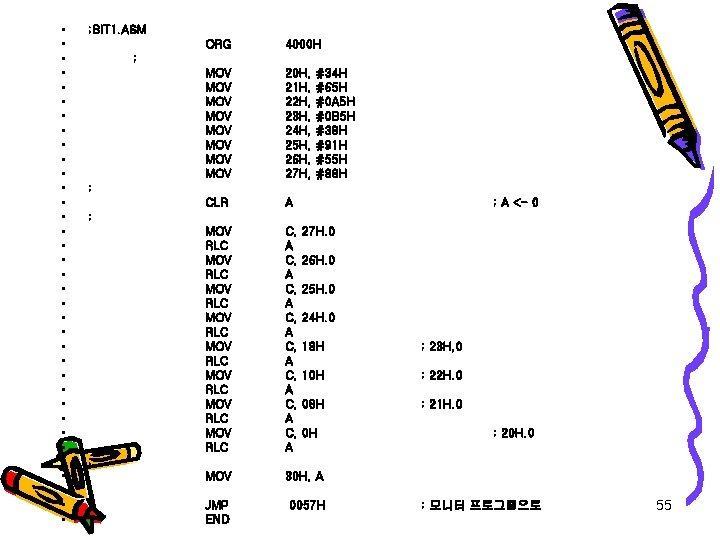

• • • • • • • • • ; BIT 1. ASM ORG 4000 H MOV MOV 20 H, 21 H, 22 H, 23 H, 24 H, 25 H, 26 H, 27 H, CLR A MOV RLC MOV RLC C, A C, A MOV 30 H, A JMP END 0057 H ; #34 H #65 H #0 A 5 H #0 B 5 H #38 H #91 H #55 H #88 H ; ; A <- 0 ; 27 H. 0 26 H. 0 25 H. 0 24 H. 0 18 H ; 23 H, 0 10 H ; 22 H. 0 08 H ; 21 H. 0 0 H ; 20 H. 0 ; ; ; 모니터 프로그램으로 55