8051 Programming Addressing ModeInstruction Set Lec note 5

- Slides: 81

8051 Programming (Addressing Mode-Instruction Set) Lec note 5 hsabaghianb @ kashanu. ac. ir Microprocessors 5 -1

Outline q Data transfer instructions q Addressing modes q Data processing (arithmetic and logic) q Program flow instructions hsabaghianb @ kashanu. ac. ir Microprocessors 5 -2

Data Transfer Instructions q MOV dest, source q Stack instructions PUSH byte POP byte dest source ; increment stack ; move byte ; move from stack ; decrement pointer, on stack to byte, stack pointer q Exchange instructions XCH a, byte XCHD a, byte hsabaghianb @ kashanu. ac. ir ; exchange accumulator and byte ; exchange low nibbles of ; accumulator and byte Microprocessors 5 -3

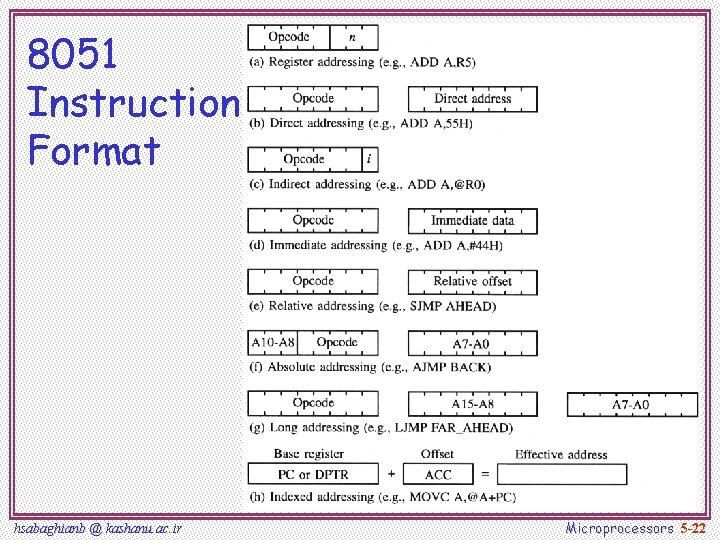

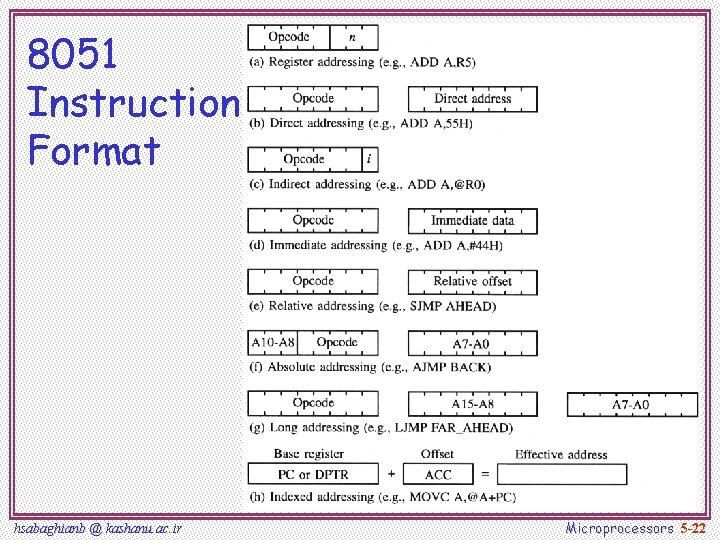

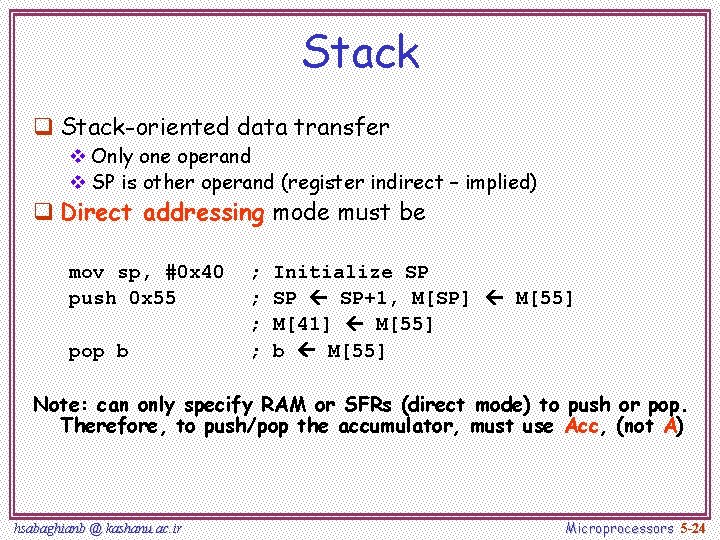

Addressing Modes q Ways of accessing data q 8051 has different addressing mode: v. Immediate (constant data) v. Register (register data) v. Direct (RAM data) v. Register indirect (RAM data) v. Indexed (ROM data) vrelative addressing v. Absolute addressing v. Long addressing hsabaghianb @ kashanu. ac. ir Microprocessors 5 -4

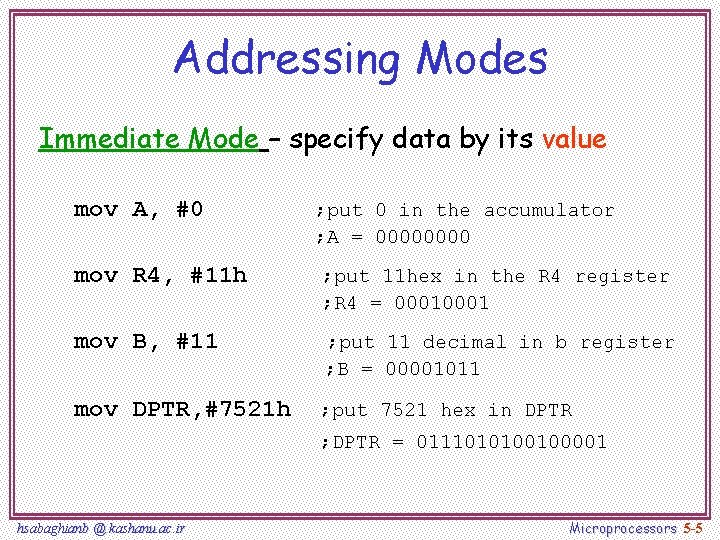

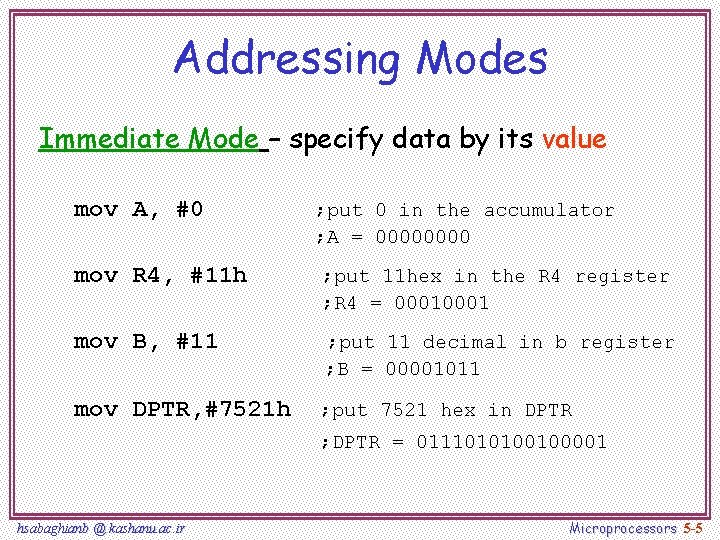

Addressing Modes Immediate Mode – specify data by its value mov A, #0 ; put 0 in the accumulator ; A = 0000 mov R 4, #11 h ; put 11 hex in the R 4 register ; R 4 = 0001 mov B, #11 ; put 11 decimal in b register ; B = 00001011 mov DPTR, #7521 h ; put 7521 hex in DPTR ; DPTR = 0111010100100001 hsabaghianb @ kashanu. ac. ir Microprocessors 5 -5

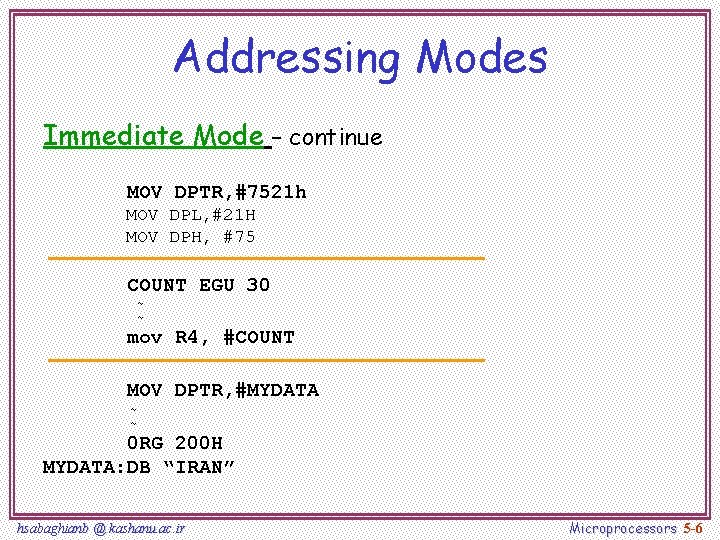

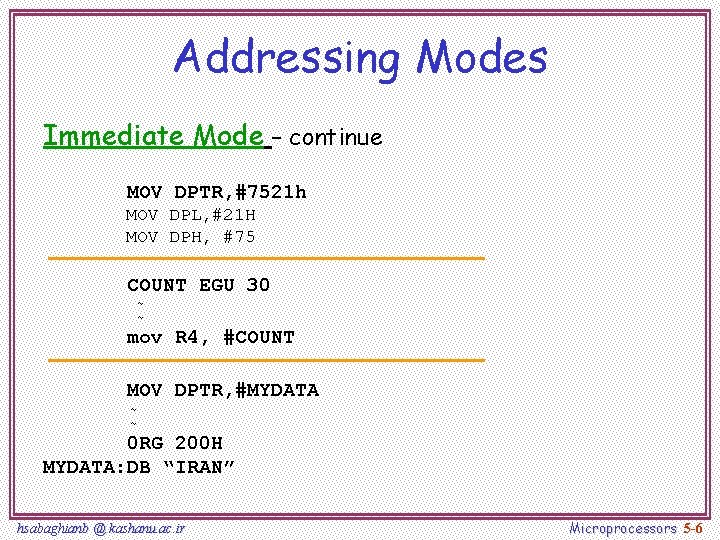

Addressing Modes Immediate Mode – continue MOV DPTR, #7521 h MOV DPL, #21 H MOV DPH, #75 COUNT EGU 30 ~ ~ mov R 4, #COUNT MOV DPTR, #MYDATA ~ ~ 0 RG 200 H MYDATA: DB “IRAN” hsabaghianb @ kashanu. ac. ir Microprocessors 5 -6

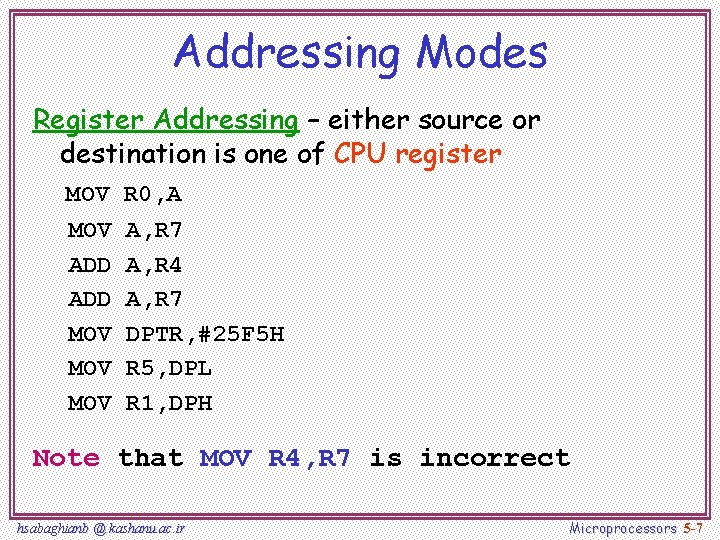

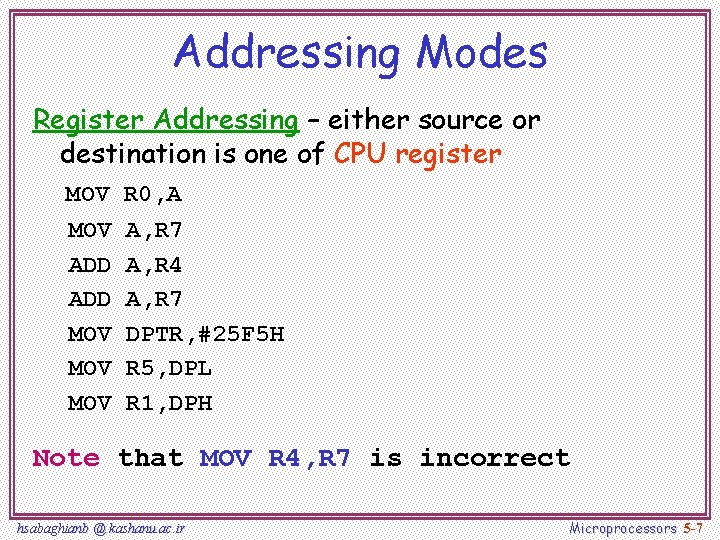

Addressing Modes Register Addressing – either source or destination is one of CPU register MOV ADD MOV MOV R 0, A A, R 7 A, R 4 A, R 7 DPTR, #25 F 5 H R 5, DPL R 1, DPH Note that MOV R 4, R 7 is incorrect hsabaghianb @ kashanu. ac. ir Microprocessors 5 -7

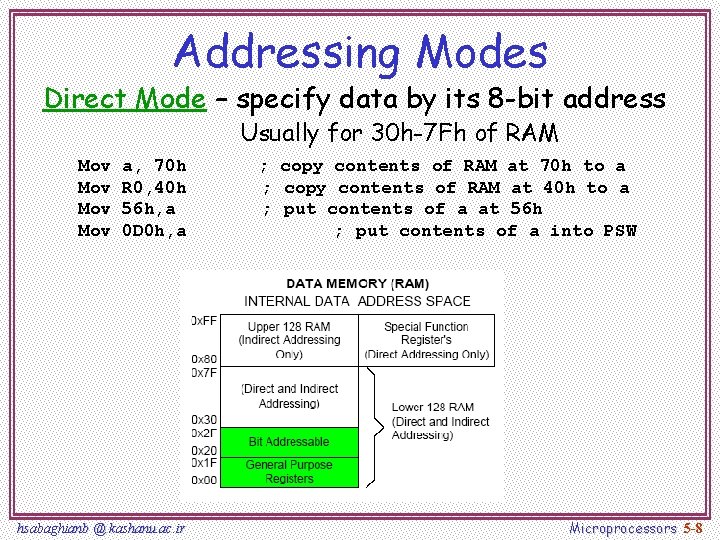

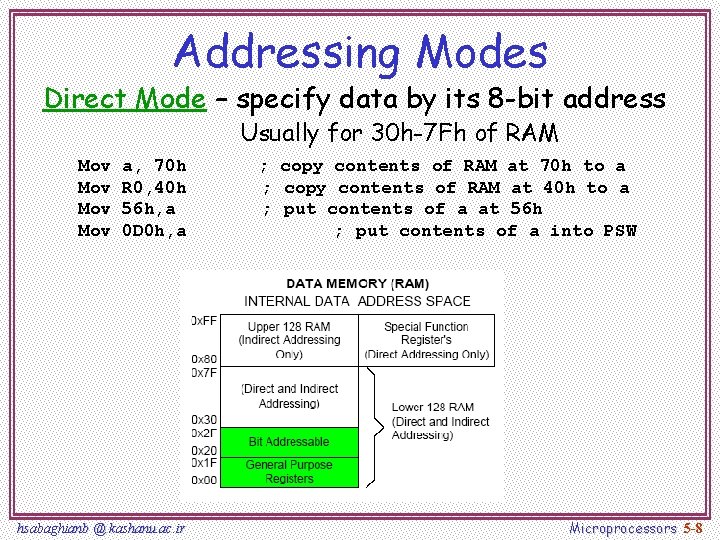

Addressing Modes Direct Mode – specify data by its 8 -bit address Usually for 30 h-7 Fh of RAM Mov Mov a, 70 h R 0, 40 h 56 h, a 0 D 0 h, a hsabaghianb @ kashanu. ac. ir ; copy contents of RAM at 70 h to a ; copy contents of RAM at 40 h to a ; put contents of a at 56 h ; put contents of a into PSW Microprocessors 5 -8

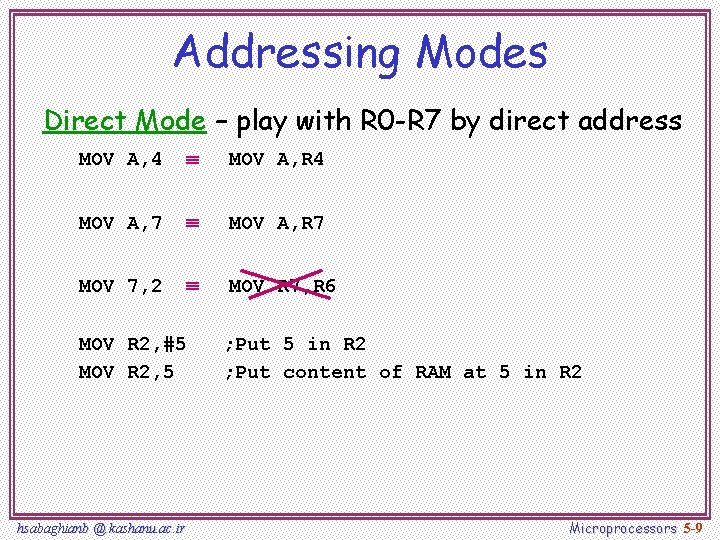

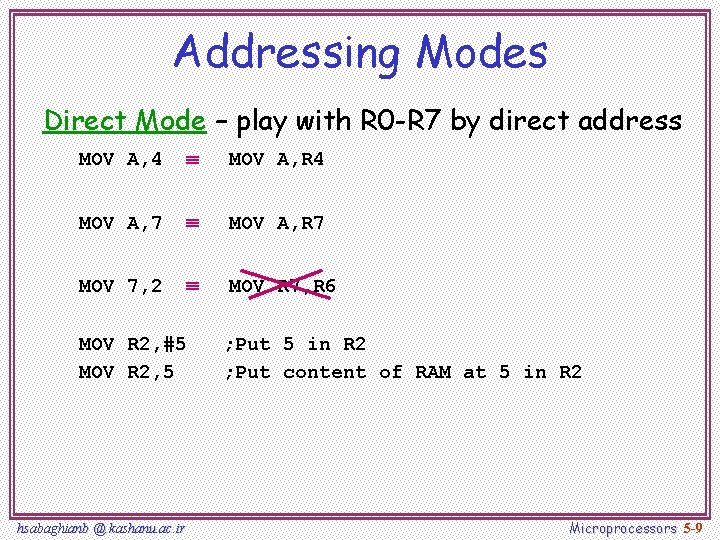

Addressing Modes Direct Mode – play with R 0 -R 7 by direct address MOV A, 4 MOV A, R 4 MOV A, 7 MOV A, R 7 MOV 7, 2 MOV R 7, R 6 MOV R 2, #5 MOV R 2, 5 hsabaghianb @ kashanu. ac. ir ; Put 5 in R 2 ; Put content of RAM at 5 in R 2 Microprocessors 5 -9

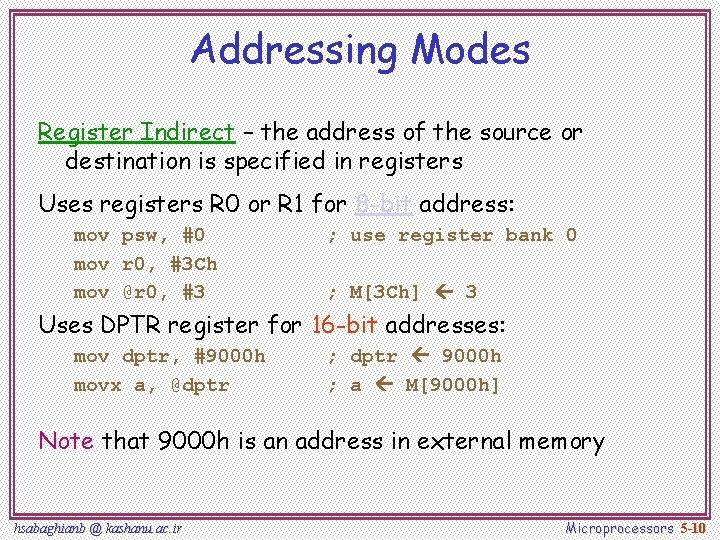

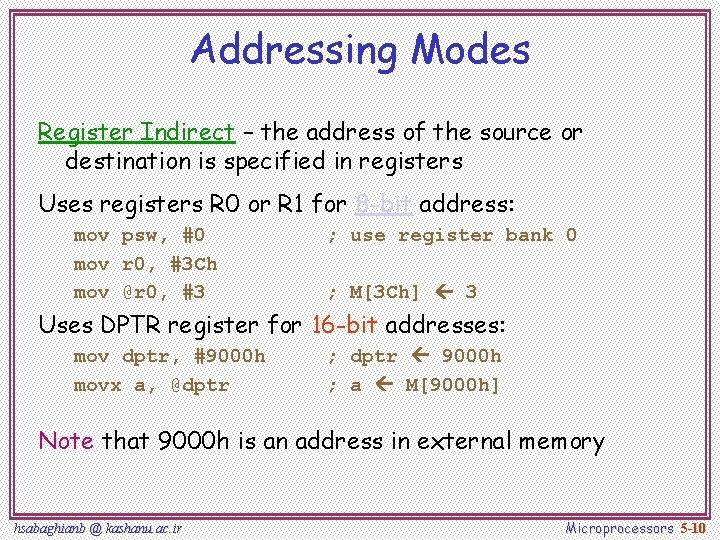

Addressing Modes Register Indirect – the address of the source or destination is specified in registers Uses registers R 0 or R 1 for 8 -bit address: mov psw, #0 mov r 0, #3 Ch mov @r 0, #3 ; use register bank 0 ; M[3 Ch] 3 Uses DPTR register for 16 -bit addresses: mov dptr, #9000 h movx a, @dptr ; dptr 9000 h ; a M[9000 h] Note that 9000 h is an address in external memory hsabaghianb @ kashanu. ac. ir Microprocessors 5 -10

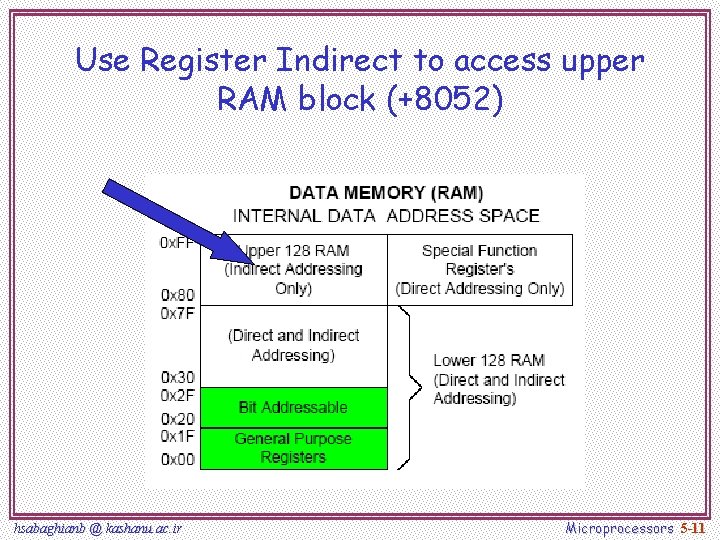

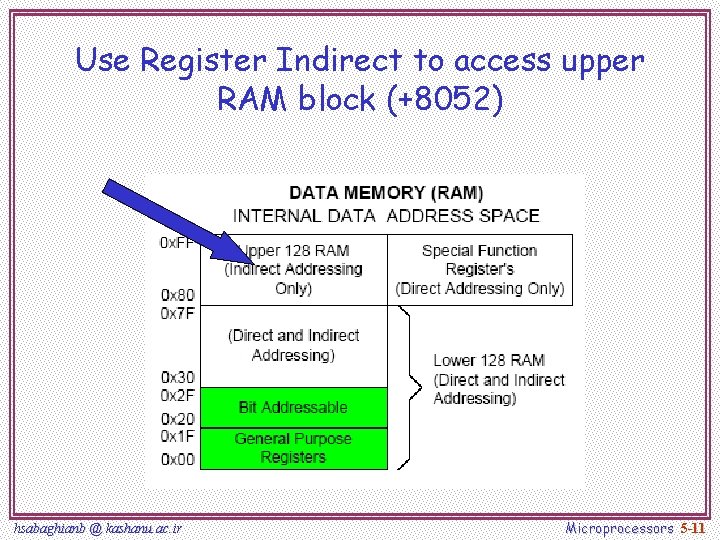

Use Register Indirect to access upper RAM block (+8052) hsabaghianb @ kashanu. ac. ir Microprocessors 5 -11

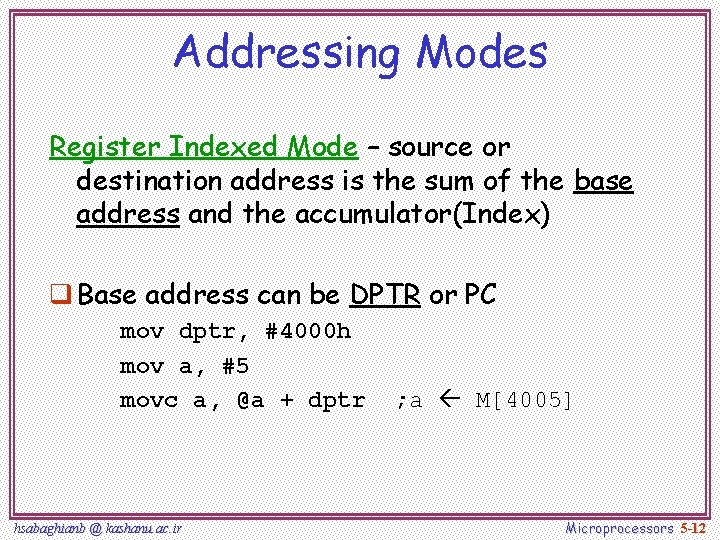

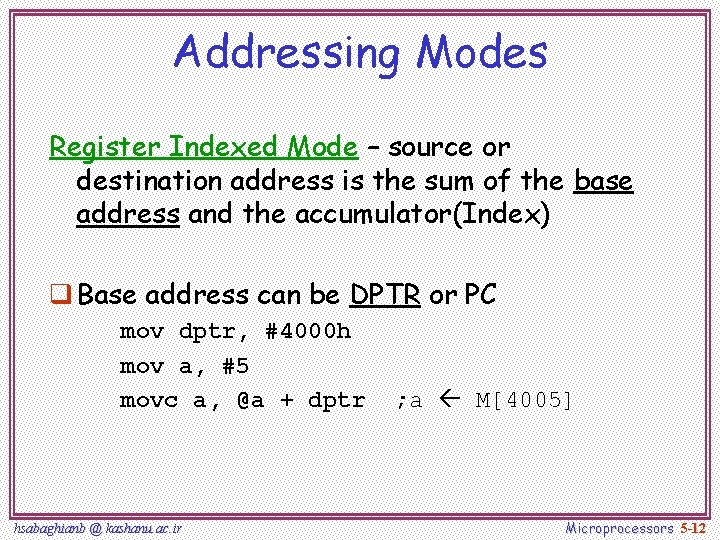

Addressing Modes Register Indexed Mode – source or destination address is the sum of the base address and the accumulator(Index) q Base address can be DPTR or PC mov dptr, #4000 h mov a, #5 movc a, @a + dptr hsabaghianb @ kashanu. ac. ir ; a M[4005] Microprocessors 5 -12

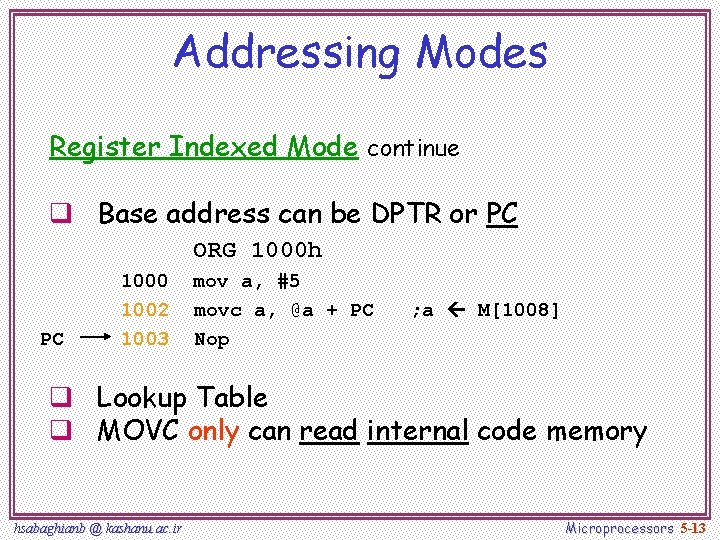

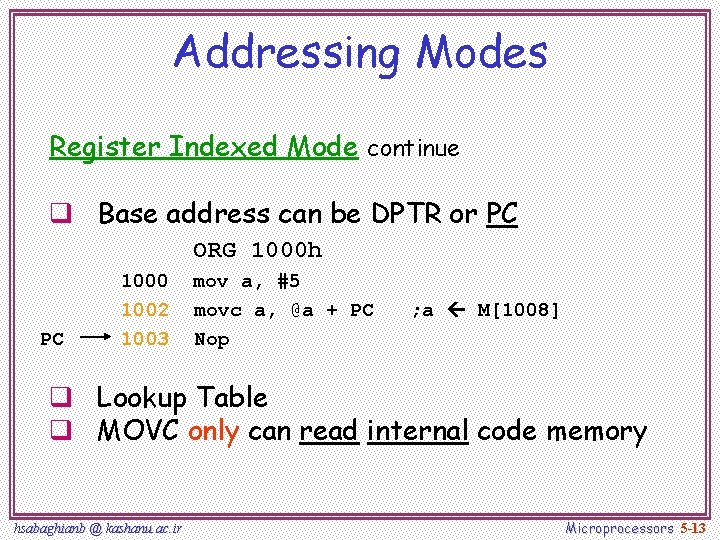

Addressing Modes Register Indexed Mode continue q Base address can be DPTR or PC ORG 1000 h PC 1000 1002 1003 mov a, #5 movc a, @a + PC Nop ; a M[1008] q Lookup Table q MOVC only can read internal code memory hsabaghianb @ kashanu. ac. ir Microprocessors 5 -13

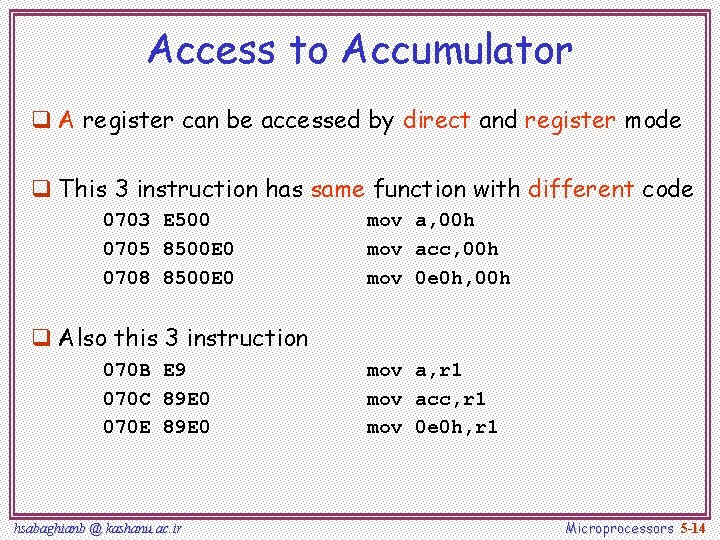

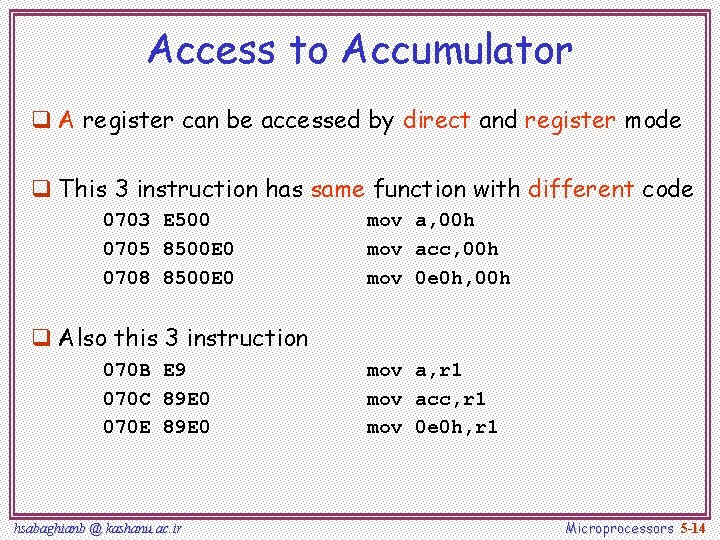

Access to Accumulator q A register can be accessed by direct and register mode q This 3 instruction has same function with different code 0703 E 500 0705 8500 E 0 0708 8500 E 0 mov a, 00 h mov acc, 00 h mov 0 e 0 h, 00 h q Also this 3 instruction 070 B E 9 070 C 89 E 0 070 E 89 E 0 hsabaghianb @ kashanu. ac. ir mov a, r 1 mov acc, r 1 mov 0 e 0 h, r 1 Microprocessors 5 -14

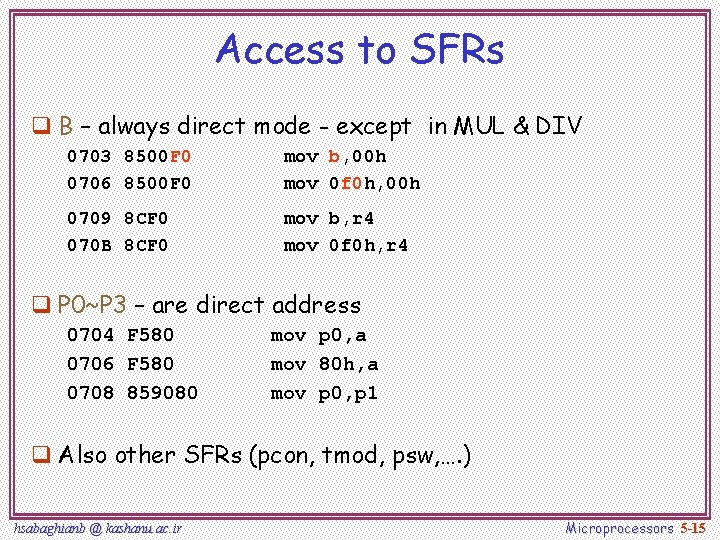

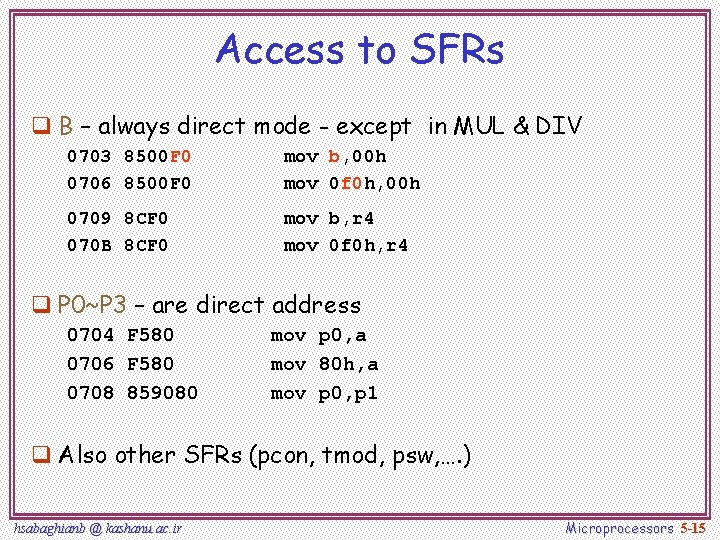

Access to SFRs q B – always direct mode - except in MUL & DIV 0703 8500 F 0 0706 8500 F 0 mov b, 00 h mov 0 f 0 h, 00 h 0709 8 CF 0 070 B 8 CF 0 mov b, r 4 mov 0 f 0 h, r 4 q P 0~P 3 – are direct address 0704 F 580 0706 F 580 0708 859080 mov p 0, a mov 80 h, a mov p 0, p 1 q Also other SFRs (pcon, tmod, psw, …. ) hsabaghianb @ kashanu. ac. ir Microprocessors 5 -15

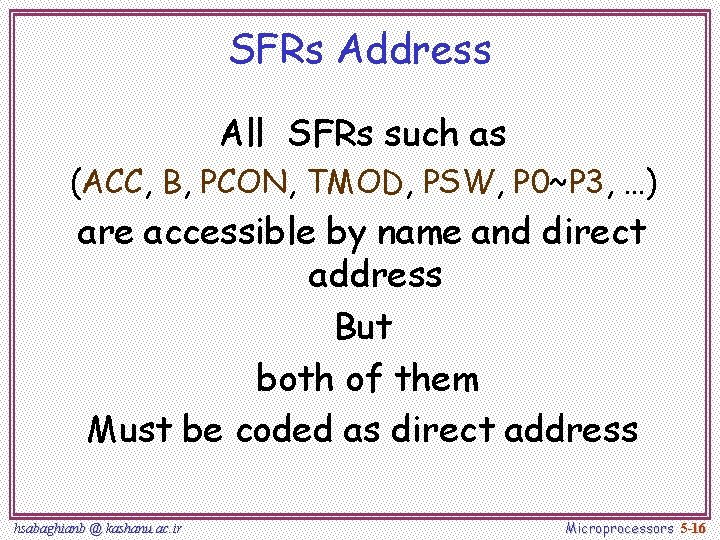

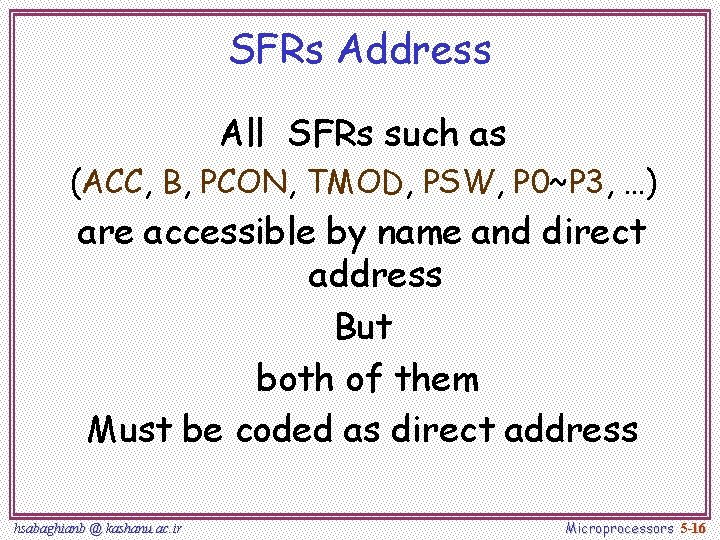

SFRs Address All SFRs such as (ACC, B, PCON, TMOD, PSW, P 0~P 3, …) are accessible by name and direct address But both of them Must be coded as direct address hsabaghianb @ kashanu. ac. ir Microprocessors 5 -16

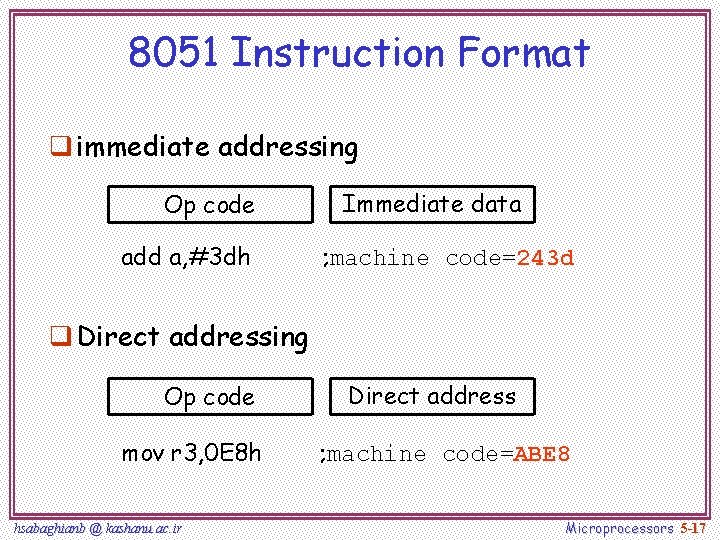

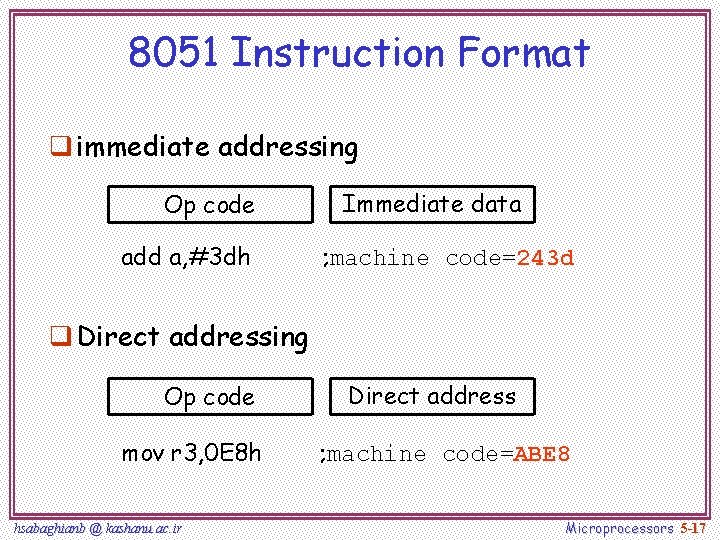

8051 Instruction Format q immediate addressing Op code add a, #3 dh Immediate data ; machine code=243 d q Direct addressing Op code mov r 3, 0 E 8 h hsabaghianb @ kashanu. ac. ir Direct address ; machine code=ABE 8 Microprocessors 5 -17

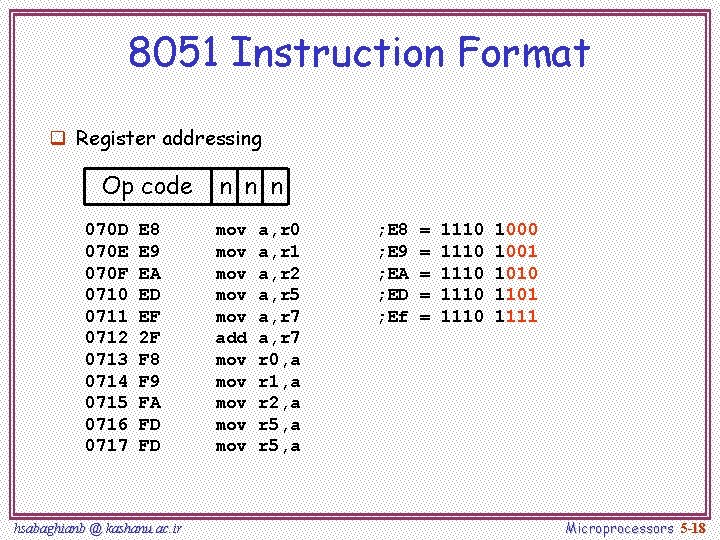

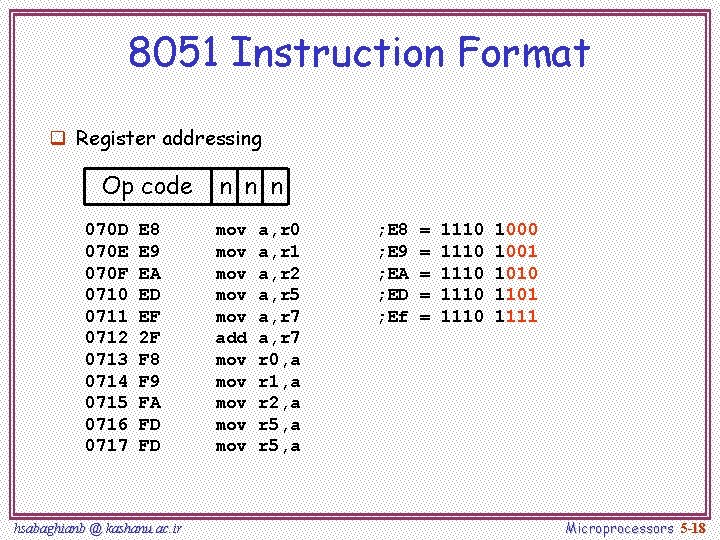

8051 Instruction Format q Register addressing Op code 070 D 070 E 070 F 0710 0711 0712 0713 0714 0715 0716 0717 E 8 E 9 EA ED EF 2 F F 8 F 9 FA FD FD hsabaghianb @ kashanu. ac. ir n n n mov mov mov add mov mov mov a, r 0 a, r 1 a, r 2 a, r 5 a, r 7 r 0, a r 1, a r 2, a r 5, a ; E 8 ; E 9 ; EA ; ED ; Ef = = = 1110 1110 1001 1010 1101 1111 Microprocessors 5 -18

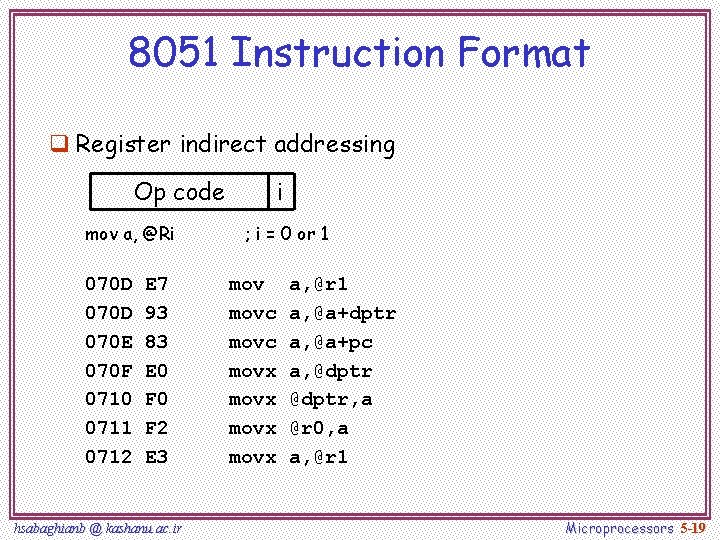

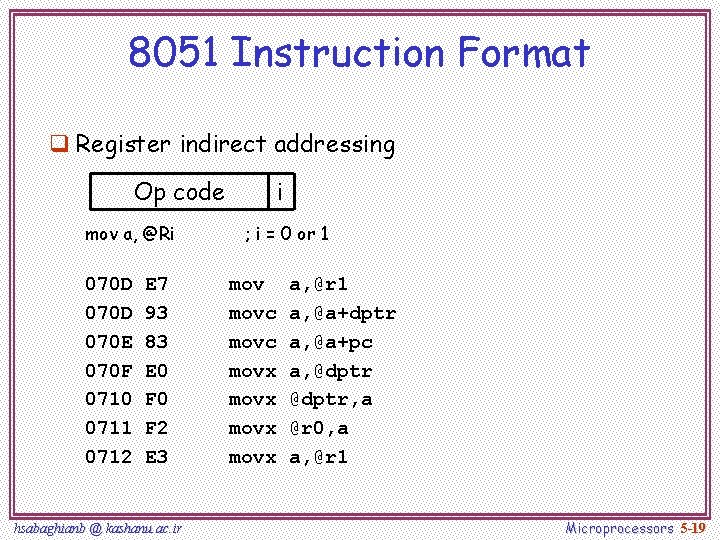

8051 Instruction Format q Register indirect addressing Op code mov a, @Ri 070 D 070 E 070 F 0710 0711 0712 E 7 93 83 E 0 F 2 E 3 hsabaghianb @ kashanu. ac. ir i ; i = 0 or 1 movc movx movx a, @r 1 a, @a+dptr a, @a+pc a, @dptr, a @r 0, a a, @r 1 Microprocessors 5 -19

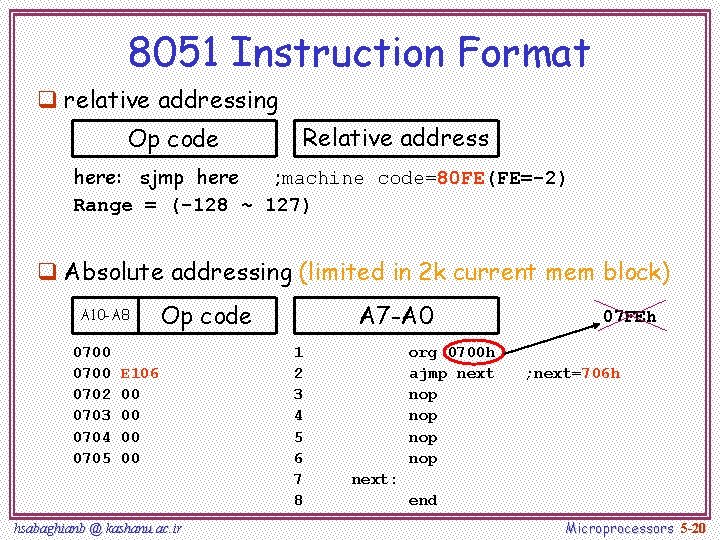

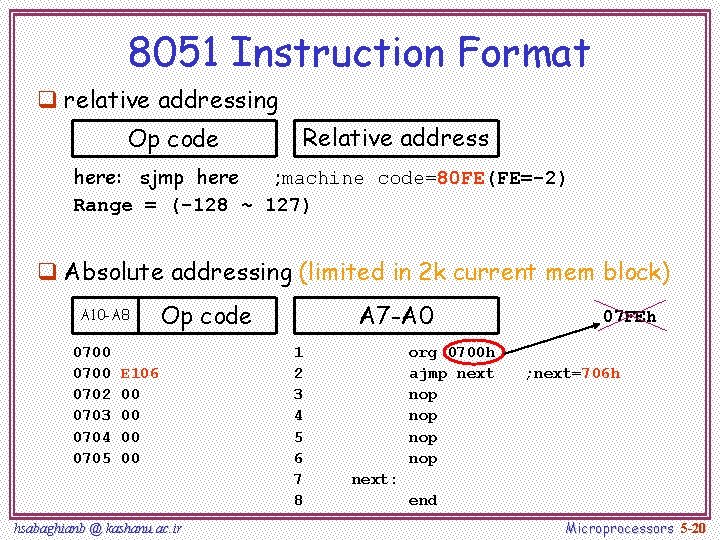

8051 Instruction Format q relative addressing Op code Relative address here: sjmp here ; machine code=80 FE(FE=-2) Range = (-128 ~ 127) q Absolute addressing (limited in 2 k current mem block) A 10 -A 8 0700 0702 0703 0704 0705 Op code E 106 00 00 hsabaghianb @ kashanu. ac. ir A 7 -A 0 1 2 3 4 5 6 7 8 org 0700 h ajmp next nop nop 07 FEh ; next=706 h next: end Microprocessors 5 -20

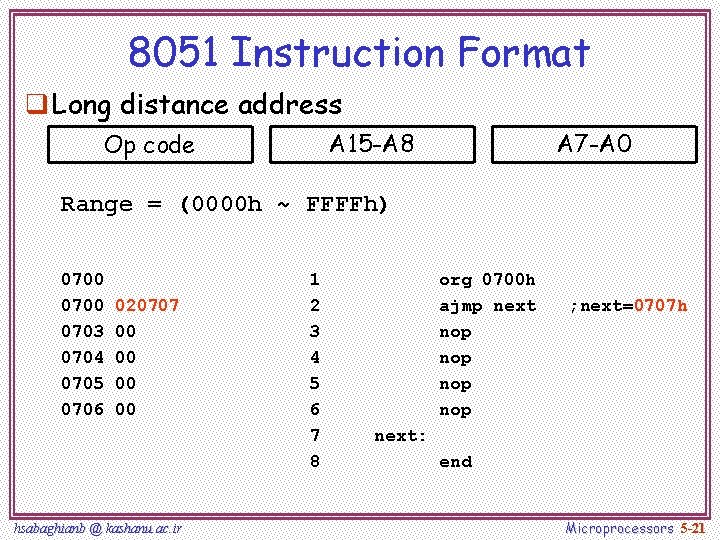

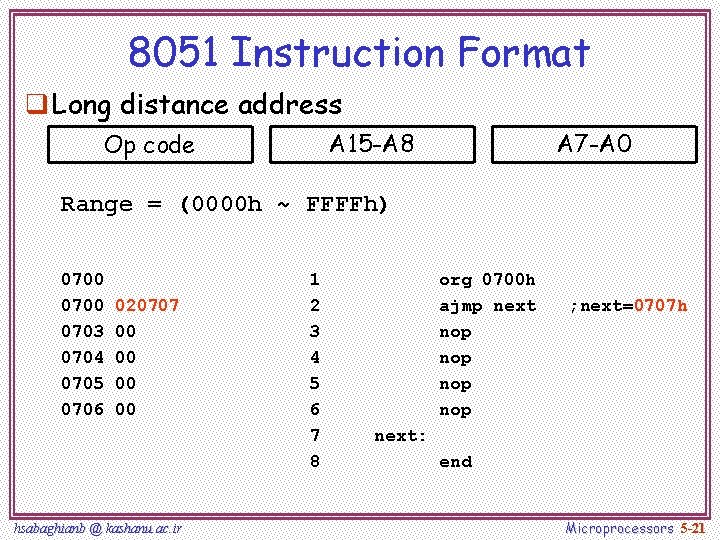

8051 Instruction Format q Long distance address A 15 -A 8 Op code A 7 -A 0 Range = (0000 h ~ FFFFh) 0700 0703 0704 0705 0706 020707 00 00 hsabaghianb @ kashanu. ac. ir 1 2 3 4 5 6 7 8 org 0700 h ajmp next nop nop ; next=0707 h next: end Microprocessors 5 -21

8051 Instruction Format hsabaghianb @ kashanu. ac. ir Microprocessors 5 -22

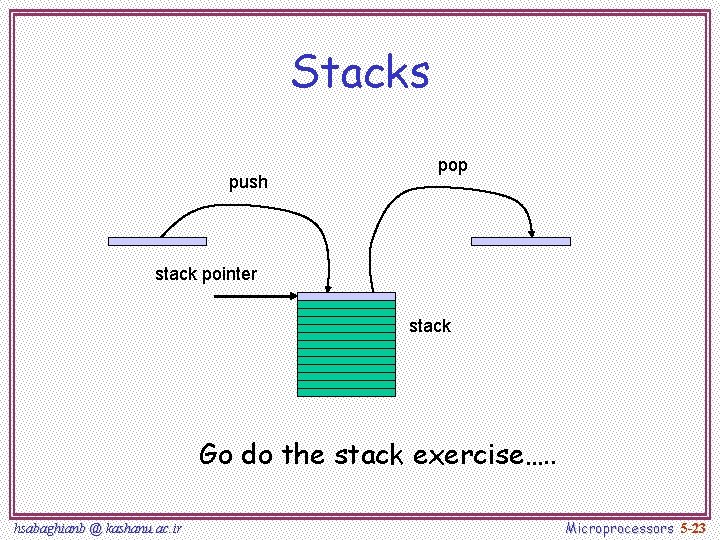

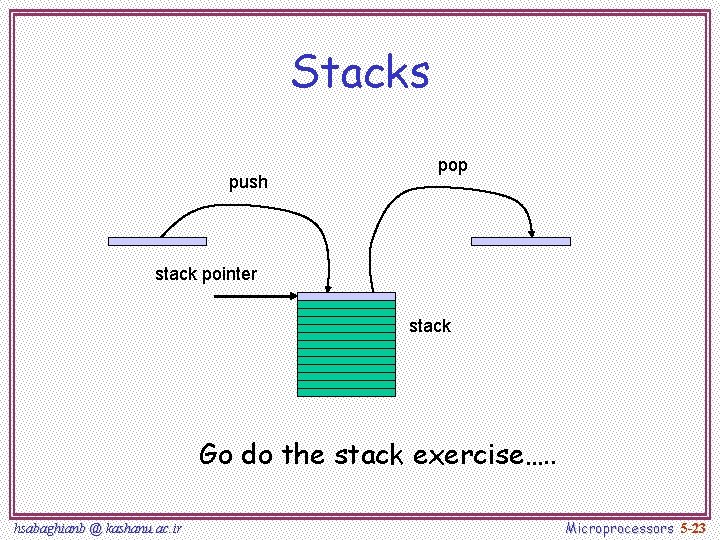

Stacks push pop stack pointer stack Go do the stack exercise…. . hsabaghianb @ kashanu. ac. ir Microprocessors 5 -23

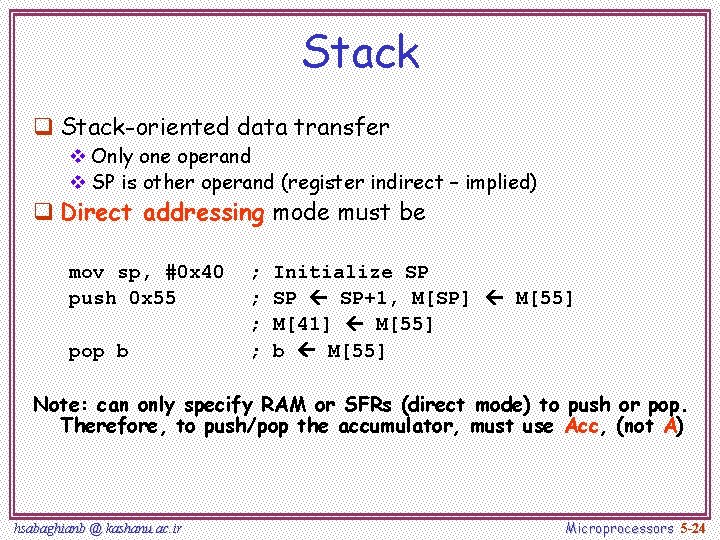

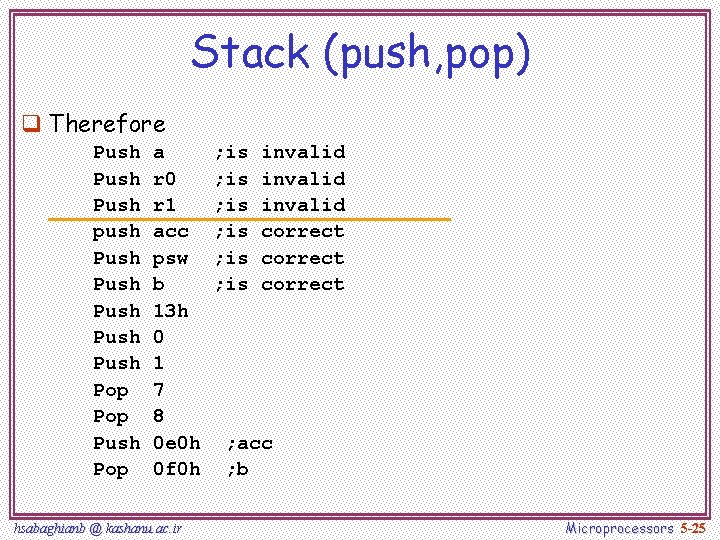

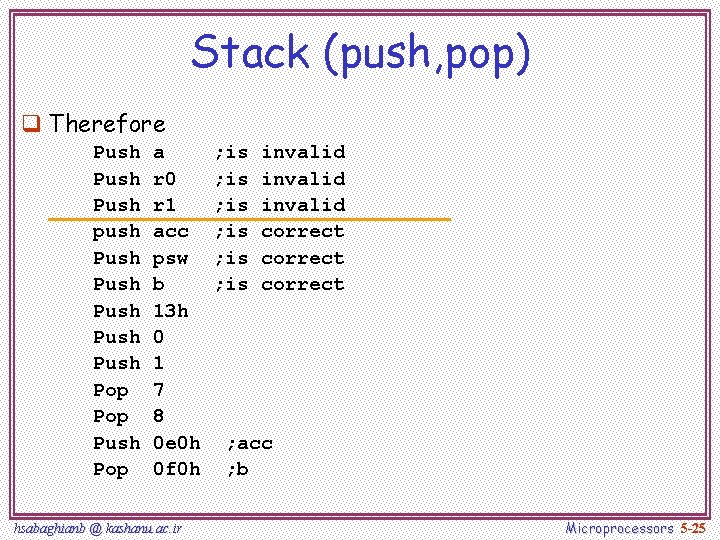

Stack q Stack-oriented data transfer v Only one operand v SP is other operand (register indirect – implied) q Direct addressing mode must be mov sp, #0 x 40 push 0 x 55 pop b ; ; Initialize SP SP SP+1, M[SP] M[55] M[41] M[55] b M[55] Note: can only specify RAM or SFRs (direct mode) to push or pop. Therefore, to push/pop the accumulator, must use Acc, (not A) hsabaghianb @ kashanu. ac. ir Microprocessors 5 -24

Stack (push, pop) q Therefore Push push Push Pop Push Pop a r 0 r 1 acc psw b 13 h 0 1 7 8 0 e 0 h 0 f 0 h hsabaghianb @ kashanu. ac. ir ; is ; is invalid correct ; acc ; b Microprocessors 5 -25

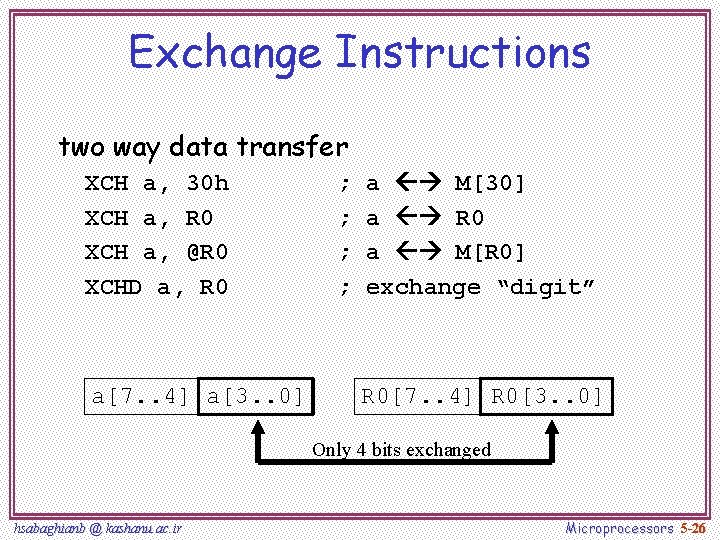

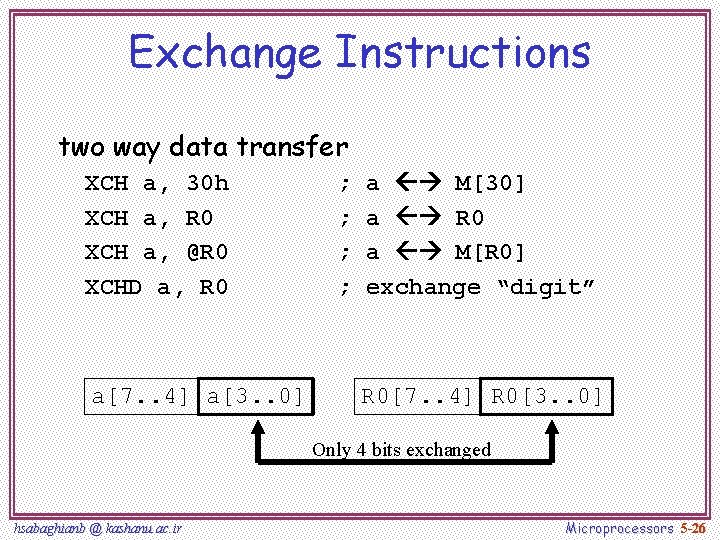

Exchange Instructions two way data transfer XCH a, 30 h XCH a, R 0 XCH a, @R 0 XCHD a, R 0 a[7. . 4] a[3. . 0] ; ; a M[30] a R 0 a M[R 0] exchange “digit” R 0[7. . 4] R 0[3. . 0] Only 4 bits exchanged hsabaghianb @ kashanu. ac. ir Microprocessors 5 -26

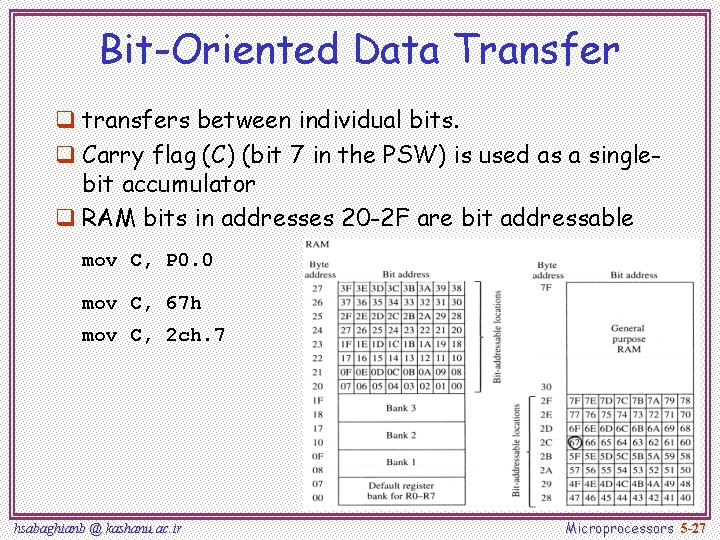

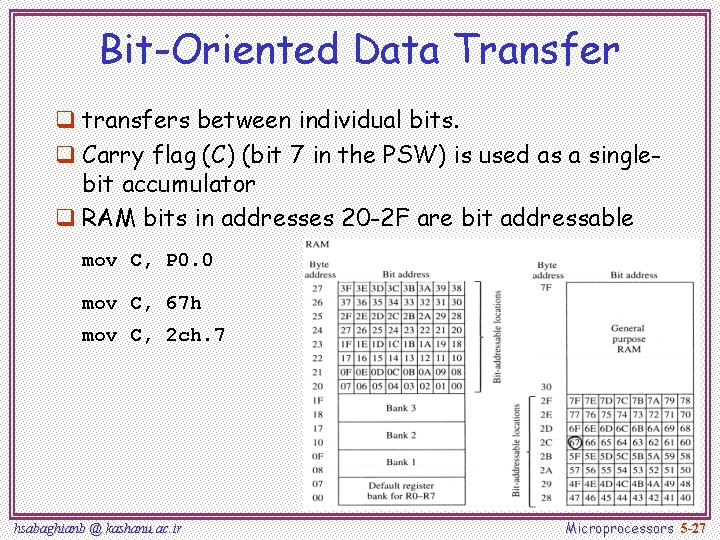

Bit-Oriented Data Transfer q transfers between individual bits. q Carry flag (C) (bit 7 in the PSW) is used as a singlebit accumulator q RAM bits in addresses 20 -2 F are bit addressable mov C, P 0. 0 mov C, 67 h mov C, 2 ch. 7 hsabaghianb @ kashanu. ac. ir Microprocessors 5 -27

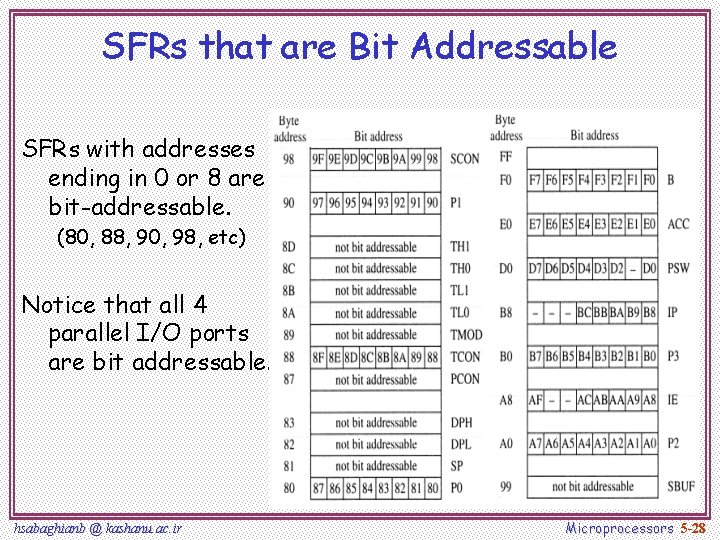

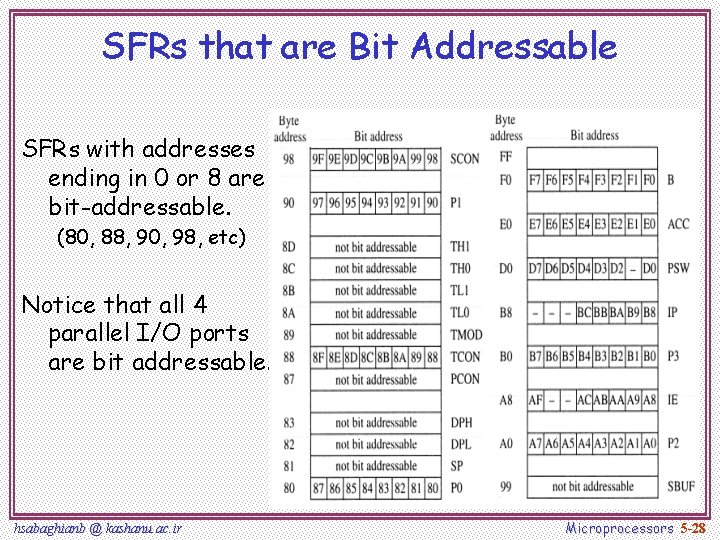

SFRs that are Bit Addressable SFRs with addresses ending in 0 or 8 are bit-addressable. (80, 88, 90, 98, etc) Notice that all 4 parallel I/O ports are bit addressable. hsabaghianb @ kashanu. ac. ir Microprocessors 5 -28

Data Processing Instructions Arithmetic Instructions Logic Instructions hsabaghianb @ kashanu. ac. ir Microprocessors 5 -29

Arithmetic Instructions q Add q Subtract q Increment q Decrement q Multiply q Divide q Decimal adjust hsabaghianb @ kashanu. ac. ir Microprocessors 5 -30

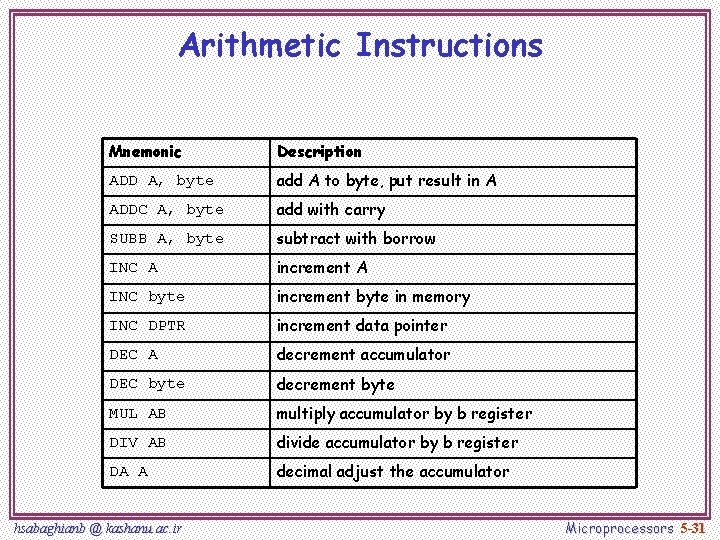

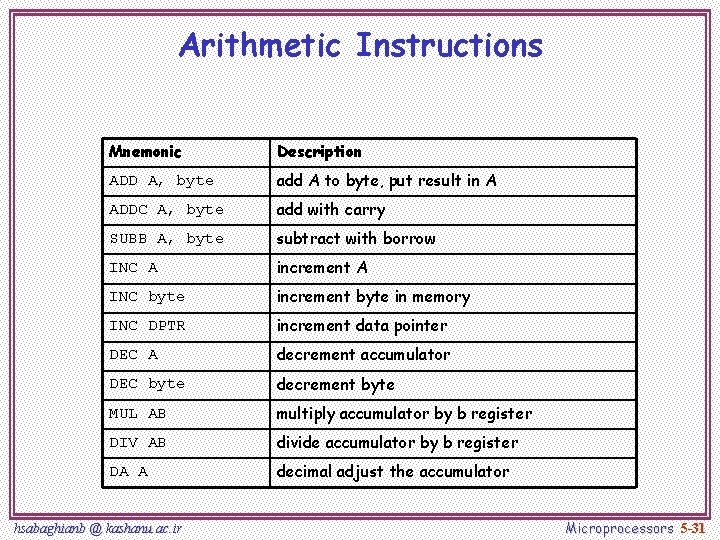

Arithmetic Instructions Mnemonic Description ADD A, byte add A to byte, put result in A ADDC A, byte add with carry SUBB A, byte subtract with borrow INC A increment A INC byte increment byte in memory INC DPTR increment data pointer DEC A decrement accumulator DEC byte decrement byte MUL AB multiply accumulator by b register DIV AB divide accumulator by b register DA A decimal adjust the accumulator hsabaghianb @ kashanu. ac. ir Microprocessors 5 -31

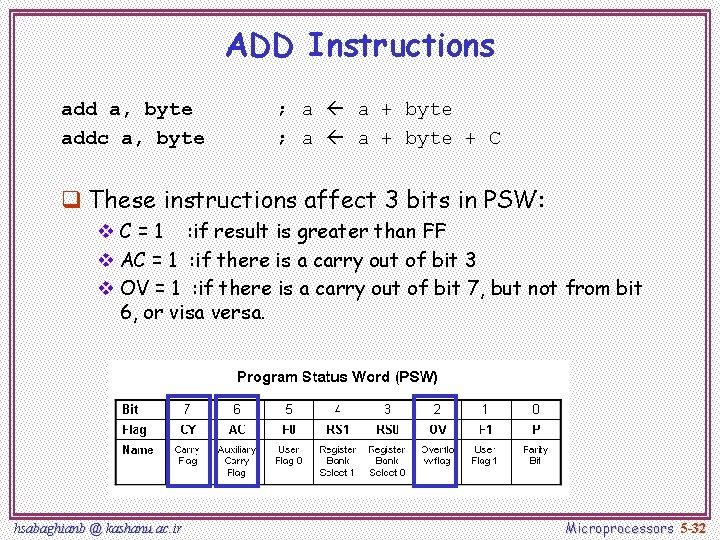

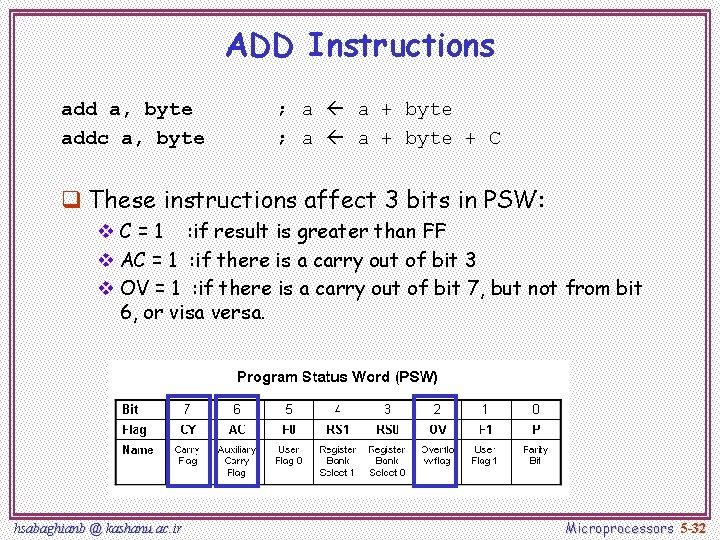

ADD Instructions add a, byte addc a, byte ; a a + byte + C q These instructions affect 3 bits in PSW: v C = 1 : if result is greater than FF v AC = 1 : if there is a carry out of bit 3 v OV = 1 : if there is a carry out of bit 7, but not from bit 6, or visa versa. hsabaghianb @ kashanu. ac. ir Microprocessors 5 -32

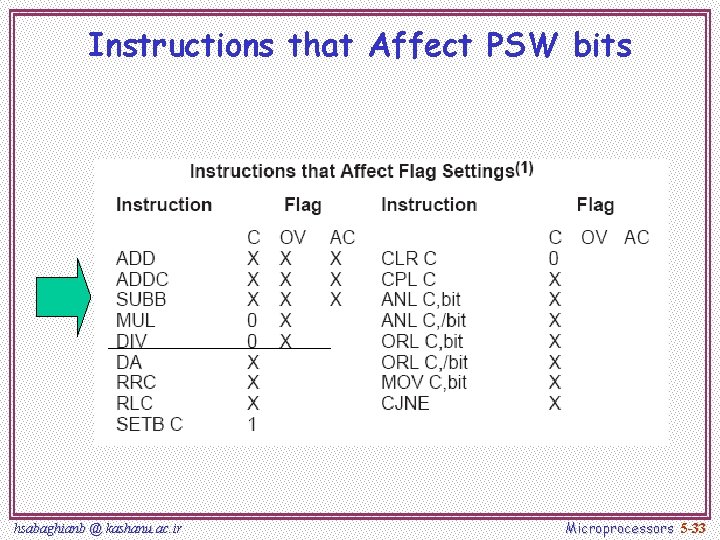

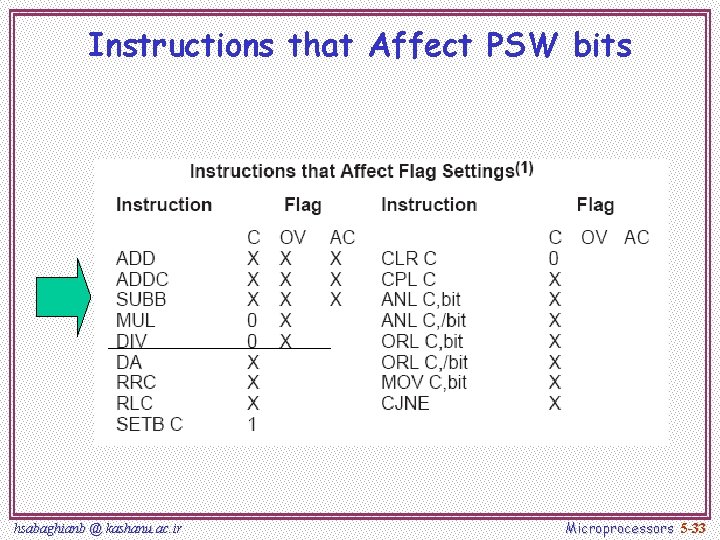

Instructions that Affect PSW bits hsabaghianb @ kashanu. ac. ir Microprocessors 5 -33

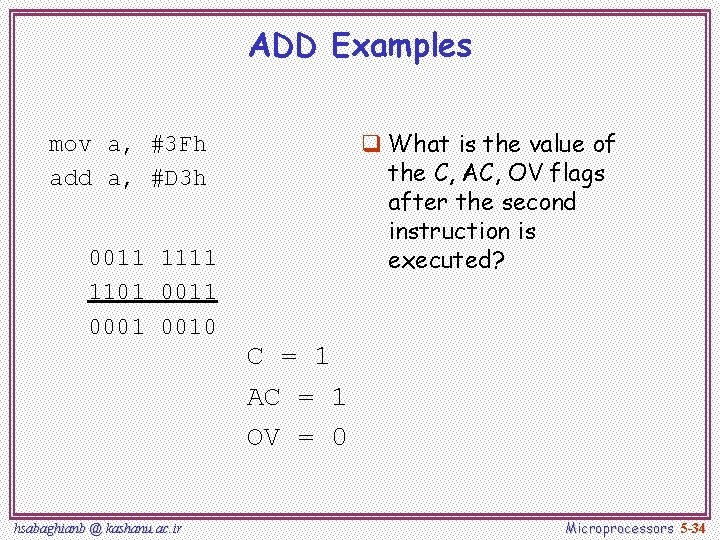

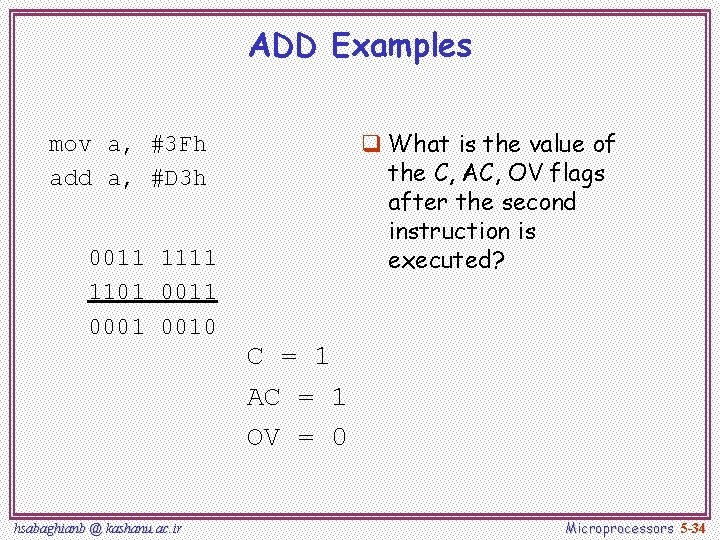

ADD Examples q What is the value of the C, AC, OV flags after the second instruction is executed? mov a, #3 Fh add a, #D 3 h 0011 1101 0011 0001 0010 hsabaghianb @ kashanu. ac. ir C = 1 AC = 1 OV = 0 Microprocessors 5 -34

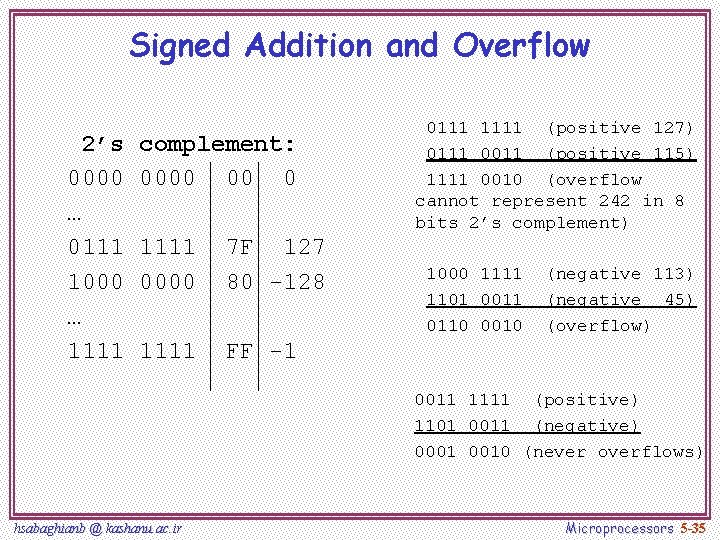

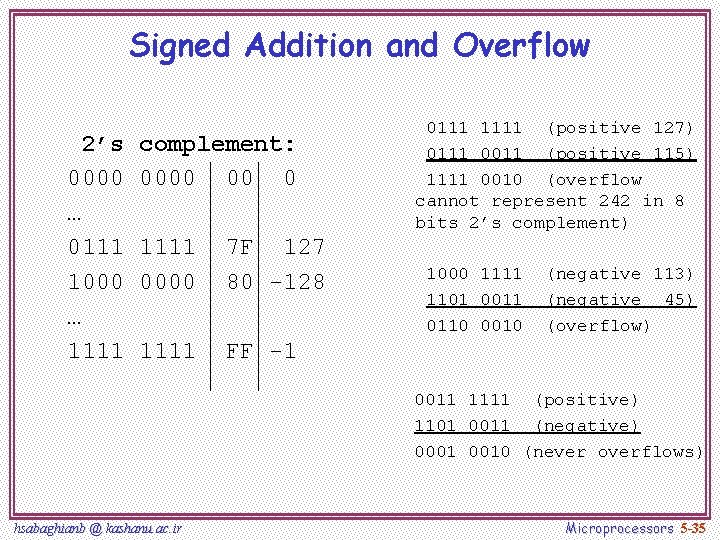

Signed Addition and Overflow 2’s 0000 … 0111 1000 … 1111 complement: 0000 00 0 1111 0000 7 F 127 80 -128 1111 FF -1 0111 1111 (positive 127) 0111 0011 (positive 115) 1111 0010 (overflow cannot represent 242 in 8 bits 2’s complement) 1000 1111 1101 0011 0110 0010 (negative 113) (negative 45) (overflow) 0011 1111 (positive) 1101 0011 (negative) 0001 0010 (never overflows) hsabaghianb @ kashanu. ac. ir Microprocessors 5 -35

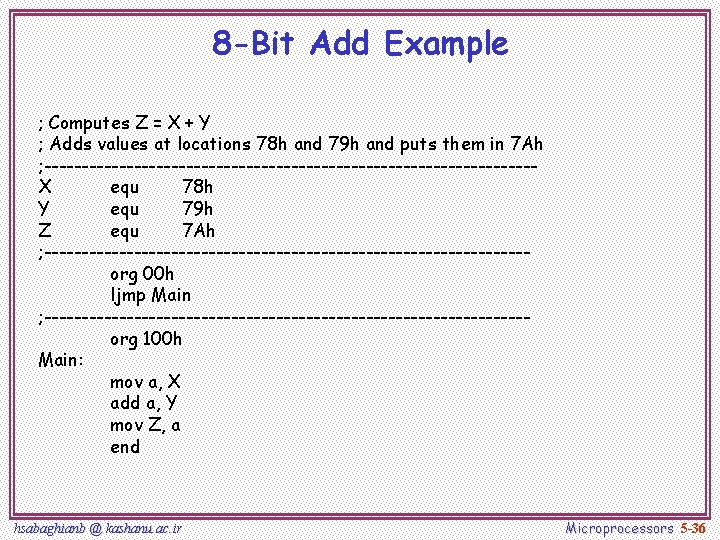

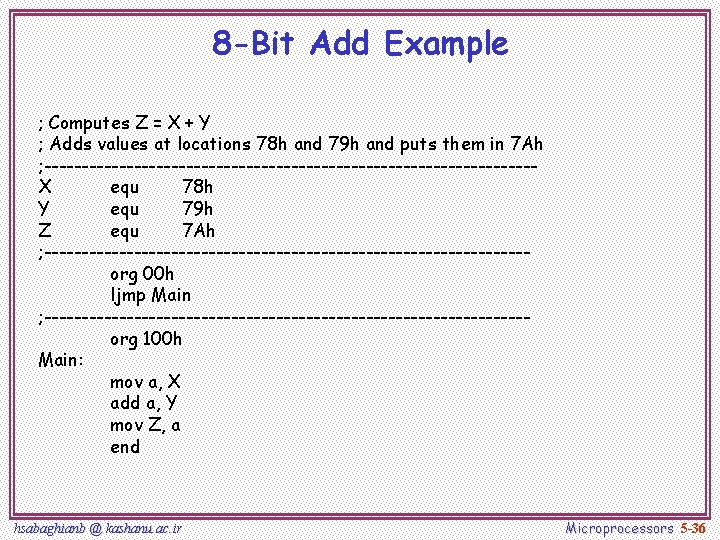

8 -Bit Add Example ; Computes Z = X + Y ; Adds values at locations 78 h and 79 h and puts them in 7 Ah ; ---------------------------------X equ 78 h Y equ 79 h Z equ 7 Ah ; --------------------------------org 00 h ljmp Main ; --------------------------------org 100 h Main: mov a, X add a, Y mov Z, a end hsabaghianb @ kashanu. ac. ir Microprocessors 5 -36

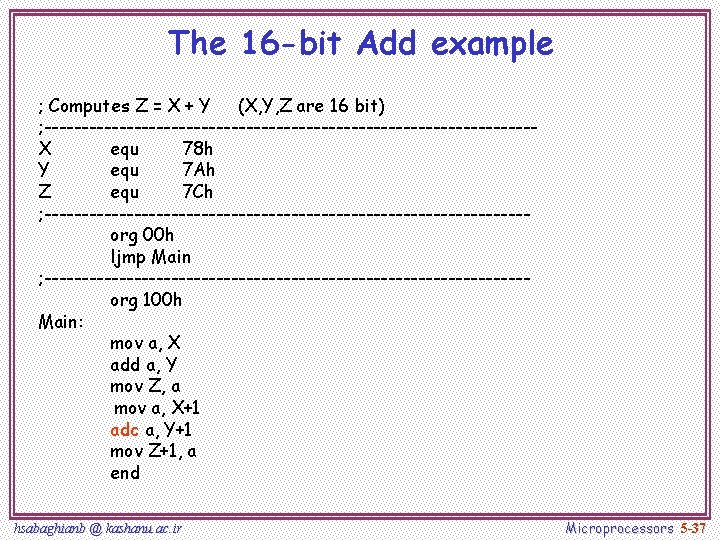

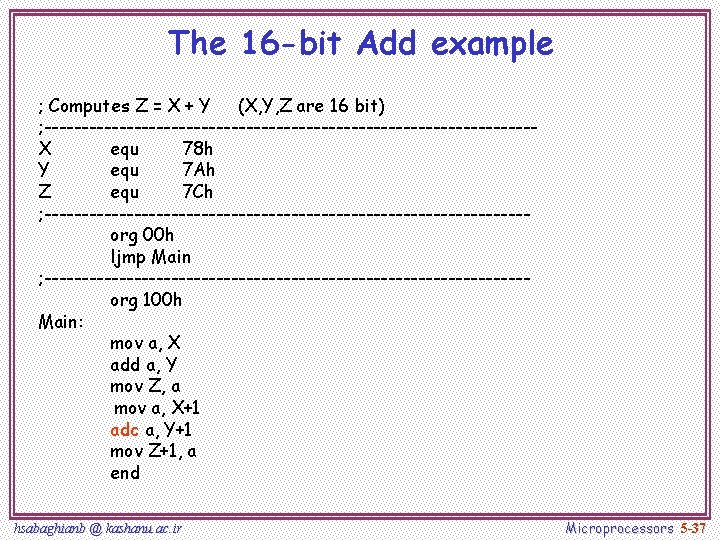

The 16 -bit Add example ; Computes Z = X + Y (X, Y, Z are 16 bit) ; ---------------------------------X equ 78 h Y equ 7 Ah Z equ 7 Ch ; --------------------------------org 00 h ljmp Main ; --------------------------------org 100 h Main: mov a, X add a, Y mov Z, a mov a, X+1 adc a, Y+1 mov Z+1, a end hsabaghianb @ kashanu. ac. ir Microprocessors 5 -37

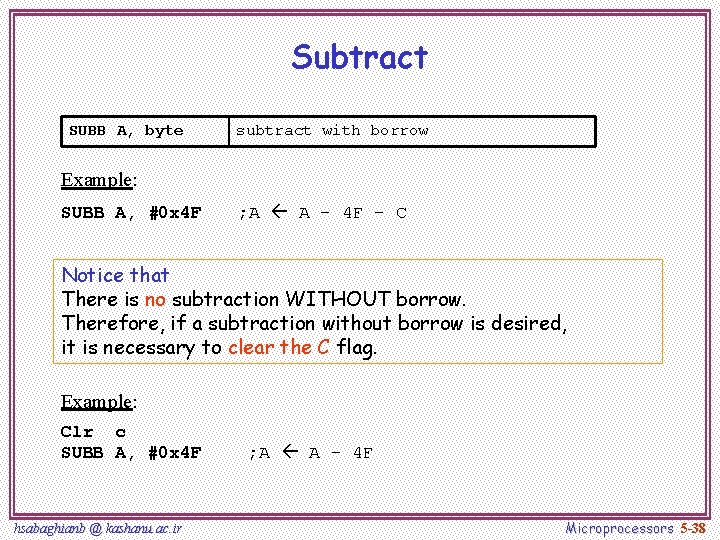

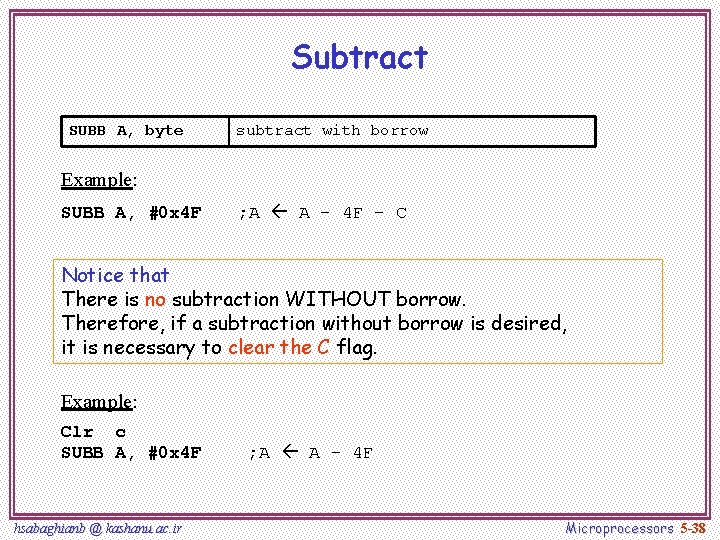

Subtract SUBB A, byte subtract with borrow Example: SUBB A, #0 x 4 F ; A A – 4 F – C Notice that There is no subtraction WITHOUT borrow. Therefore, if a subtraction without borrow is desired, it is necessary to clear the C flag. Example: Clr c SUBB A, #0 x 4 F hsabaghianb @ kashanu. ac. ir ; A A – 4 F Microprocessors 5 -38

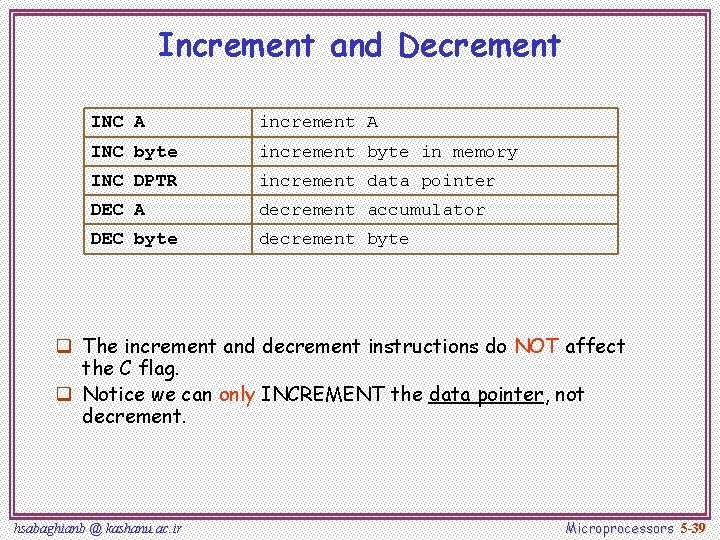

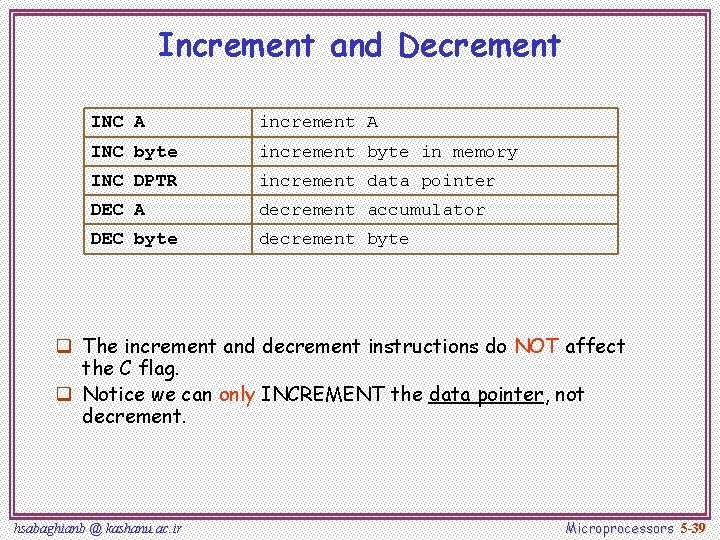

Increment and Decrement INC A increment A INC byte increment byte in memory INC DPTR increment data pointer DEC A decrement accumulator DEC byte decrement byte q The increment and decrement instructions do NOT affect the C flag. q Notice we can only INCREMENT the data pointer, not decrement. hsabaghianb @ kashanu. ac. ir Microprocessors 5 -39

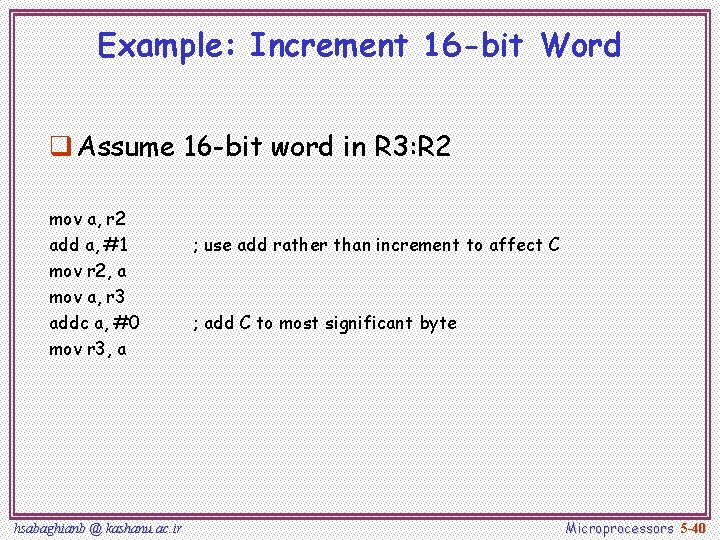

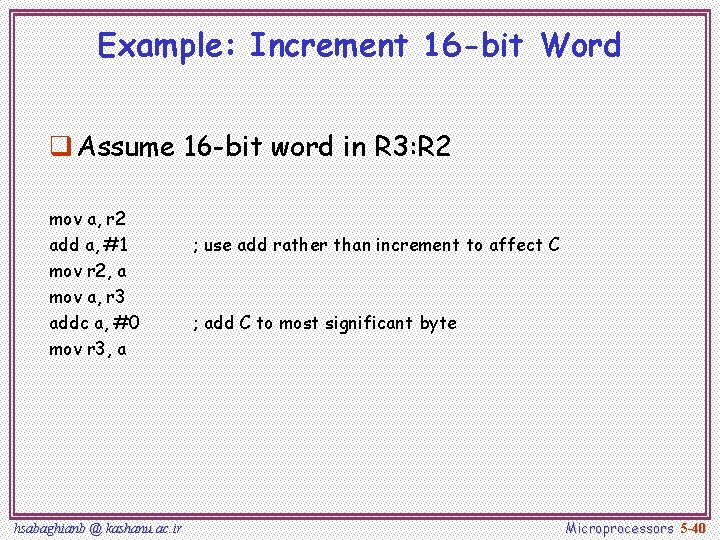

Example: Increment 16 -bit Word q Assume 16 -bit word in R 3: R 2 mov a, r 2 add a, #1 mov r 2, a mov a, r 3 addc a, #0 mov r 3, a hsabaghianb @ kashanu. ac. ir ; use add rather than increment to affect C ; add C to most significant byte Microprocessors 5 -40

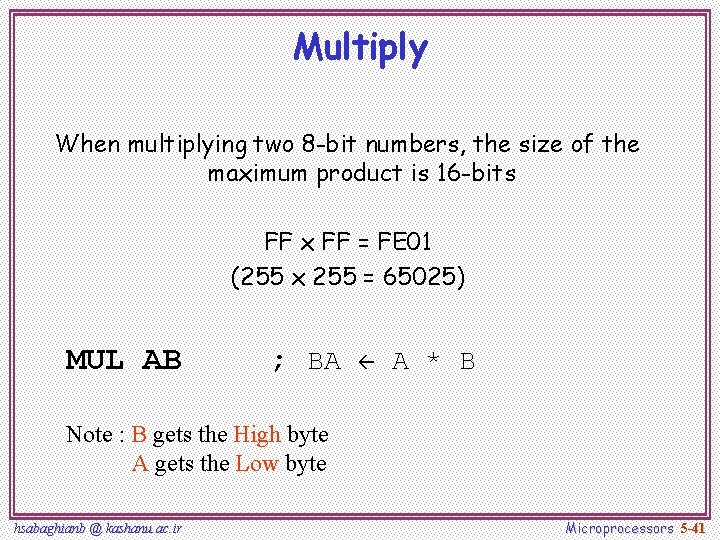

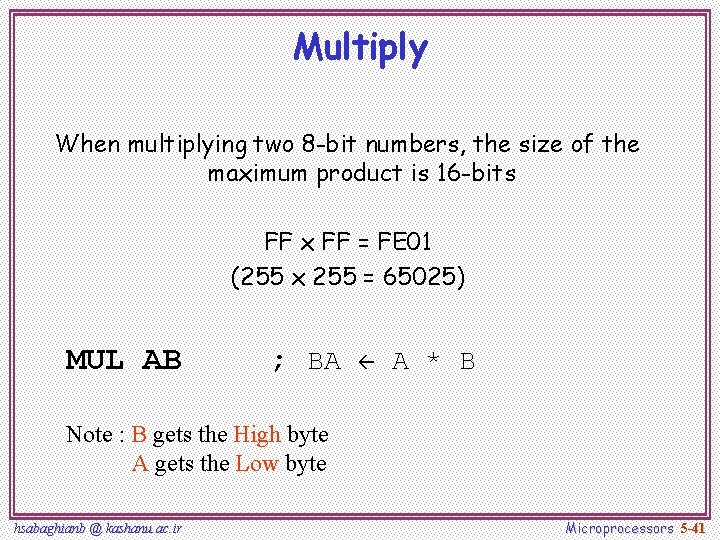

Multiply When multiplying two 8 -bit numbers, the size of the maximum product is 16 -bits FF x FF = FE 01 (255 x 255 = 65025) MUL AB ; BA A * B Note : B gets the High byte A gets the Low byte hsabaghianb @ kashanu. ac. ir Microprocessors 5 -41

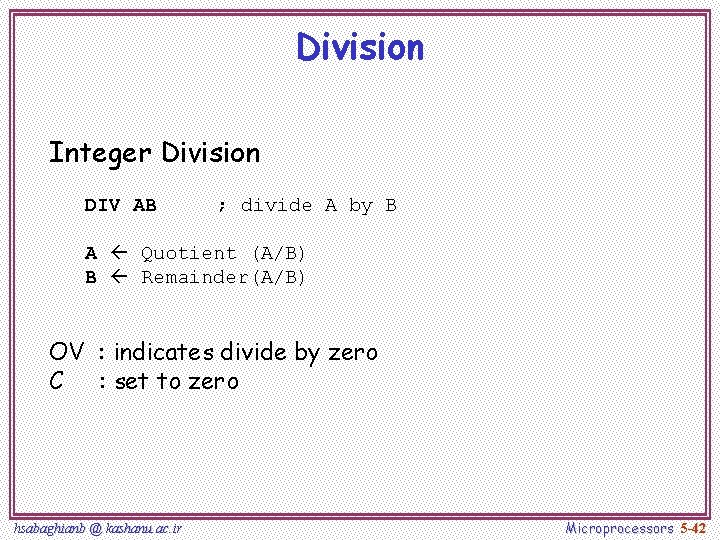

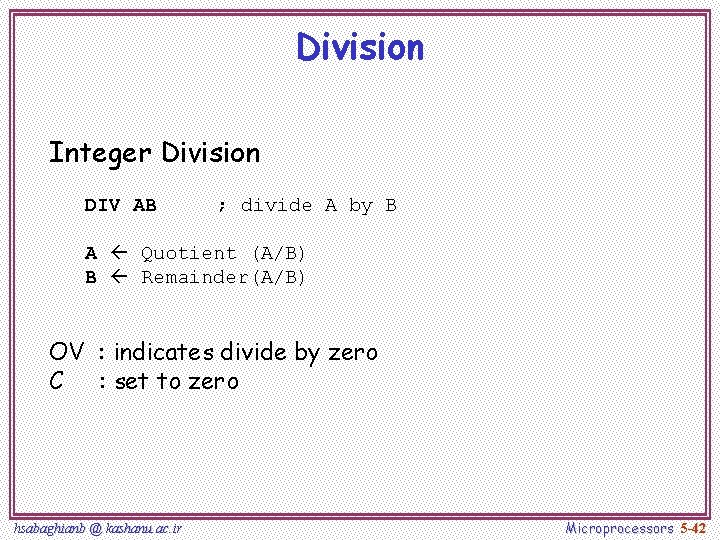

Division Integer Division DIV AB ; divide A by B A Quotient (A/B) B Remainder(A/B) OV : indicates divide by zero C : set to zero hsabaghianb @ kashanu. ac. ir Microprocessors 5 -42

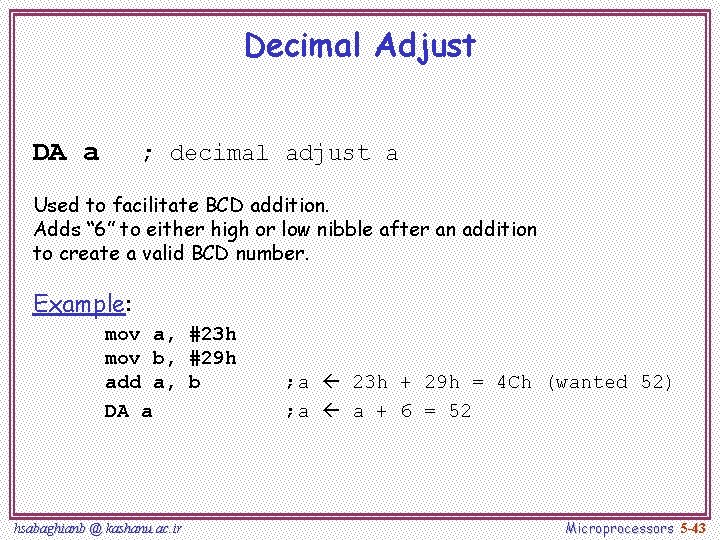

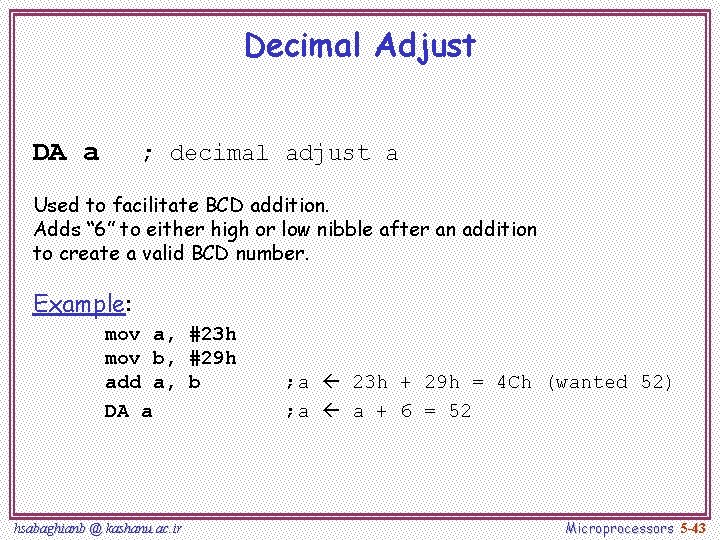

Decimal Adjust DA a ; decimal adjust a Used to facilitate BCD addition. Adds “ 6” to either high or low nibble after an addition to create a valid BCD number. Example: mov a, #23 h mov b, #29 h add a, b DA a hsabaghianb @ kashanu. ac. ir ; a 23 h + 29 h = 4 Ch (wanted 52) ; a a + 6 = 52 Microprocessors 5 -43

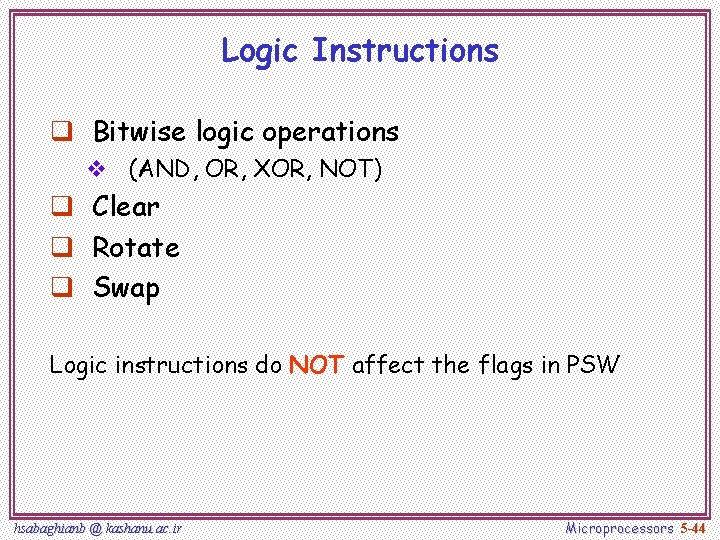

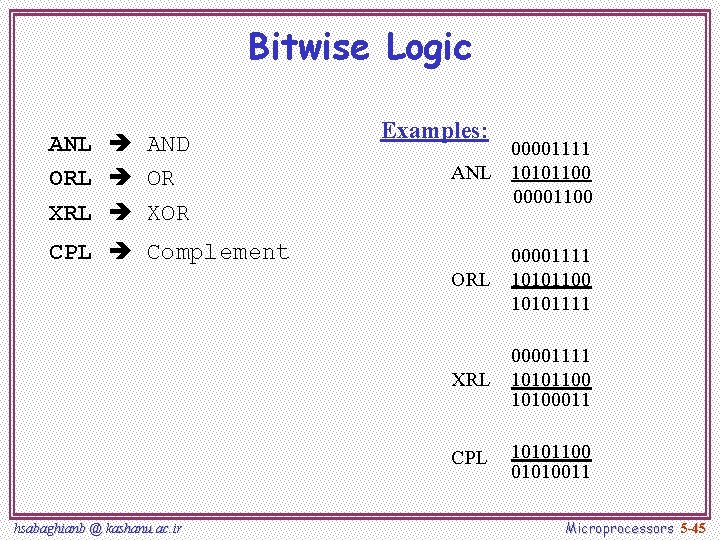

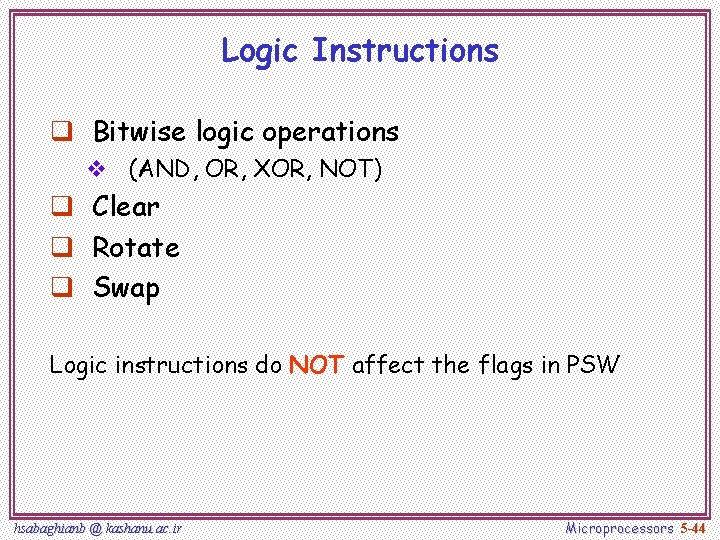

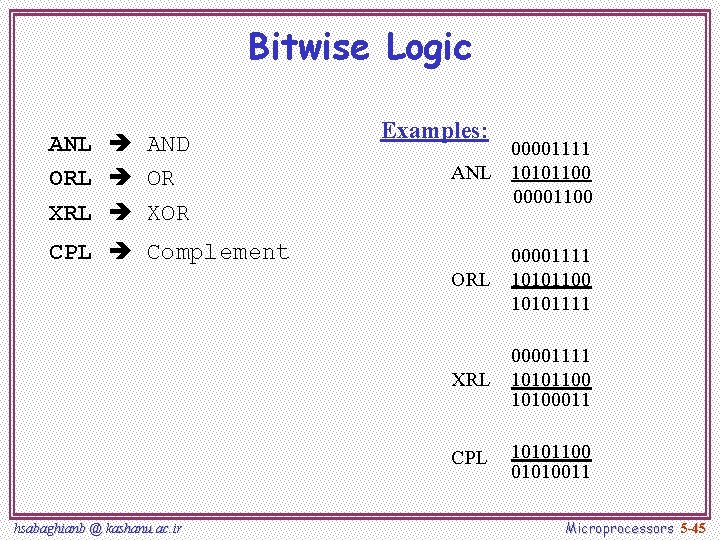

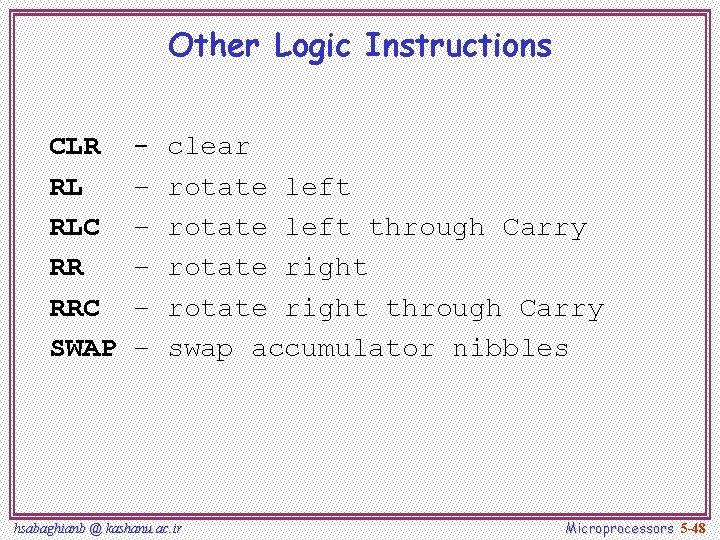

Logic Instructions q Bitwise logic operations v (AND, OR, XOR, NOT) q Clear q Rotate q Swap Logic instructions do NOT affect the flags in PSW hsabaghianb @ kashanu. ac. ir Microprocessors 5 -44

Bitwise Logic ANL AND ORL OR XRL XOR Examples: 00001111 ANL 10101100 00001100 CPL Complement hsabaghianb @ kashanu. ac. ir ORL 00001111 10101100 10101111 XRL 00001111 10101100 10100011 CPL 10101100 01010011 Microprocessors 5 -45

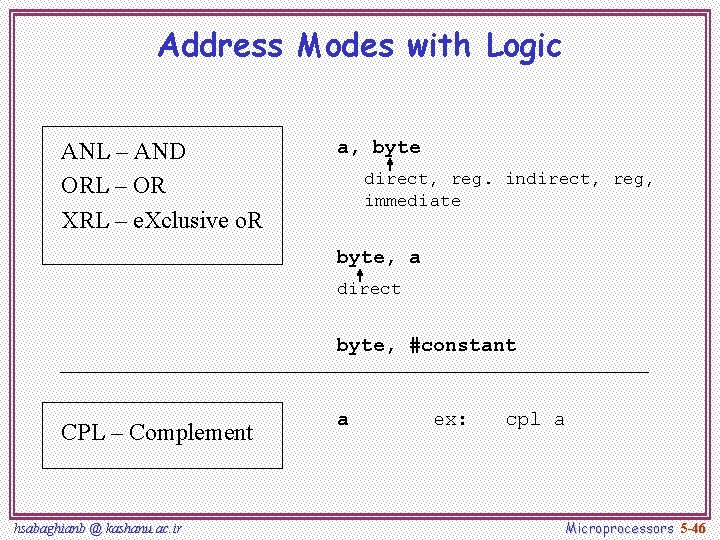

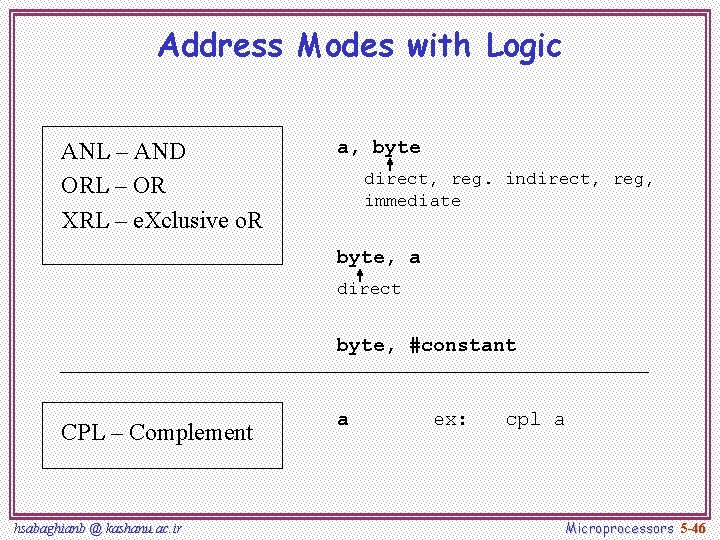

Address Modes with Logic ANL – AND ORL – OR XRL – e. Xclusive o. R a, byte direct, reg. indirect, reg, immediate byte, a direct byte, #constant CPL – Complement hsabaghianb @ kashanu. ac. ir a ex: cpl a Microprocessors 5 -46

Uses of Logic Instructions q Force individual bits low, without affecting other bits. anl PSW, #0 x. E 7 ; PSW AND 11100111 q Force individual bits high. orl PSW, #0 x 18 ; PSW OR 00011000 q Complement individual bits xrl P 1, #0 x 40 hsabaghianb @ kashanu. ac. ir ; P 1 XRL 01000000 Microprocessors 5 -47

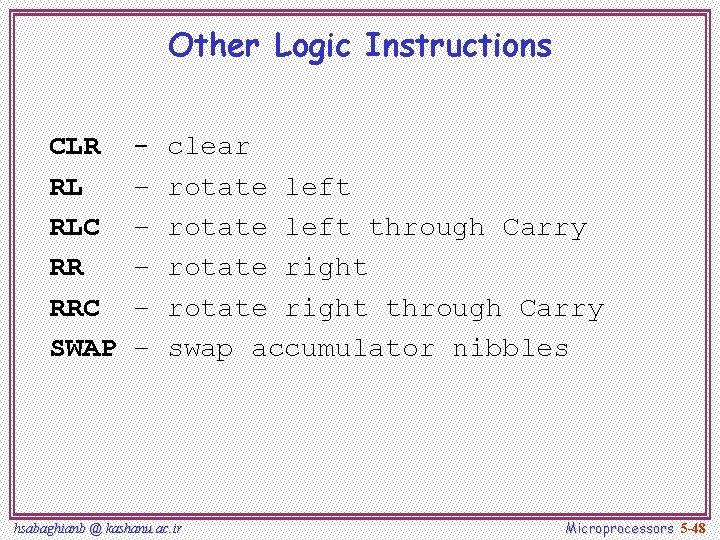

Other Logic Instructions CLR RL RLC RR RRC SWAP – – – clear rotate left through Carry rotate right through Carry swap accumulator nibbles hsabaghianb @ kashanu. ac. ir Microprocessors 5 -48

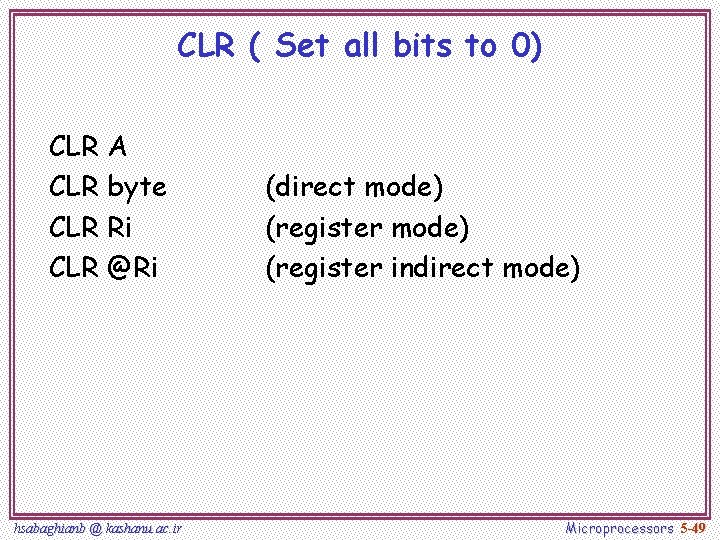

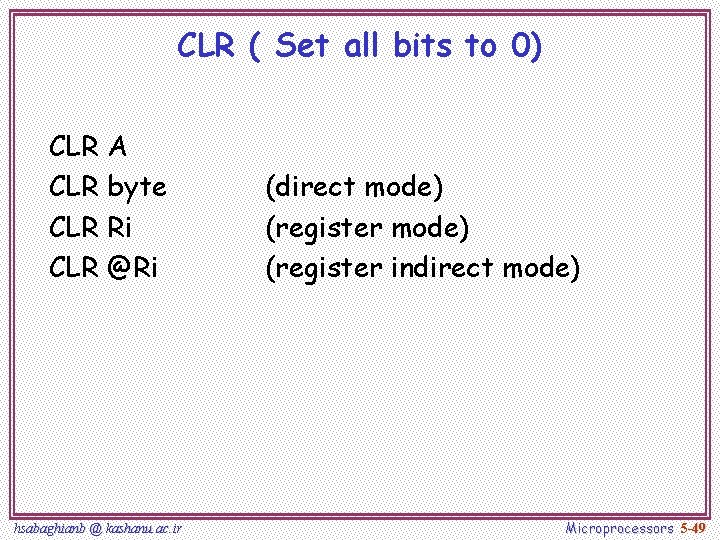

CLR ( Set all bits to 0) CLR A CLR byte CLR Ri CLR @Ri hsabaghianb @ kashanu. ac. ir (direct mode) (register indirect mode) Microprocessors 5 -49

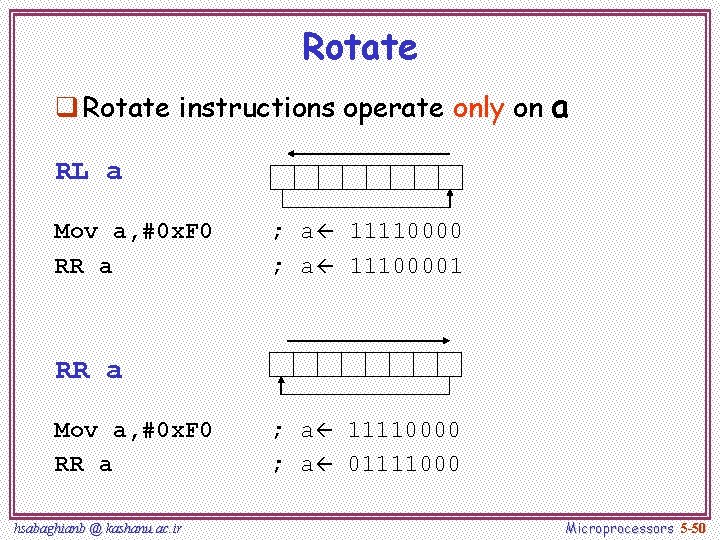

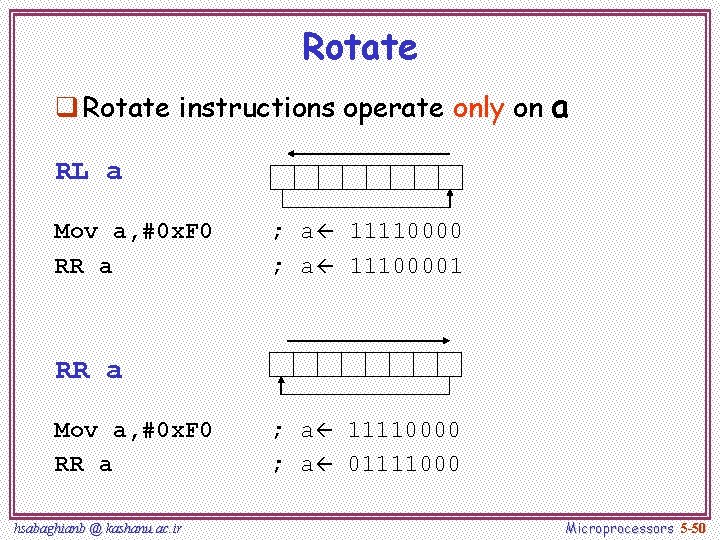

Rotate q Rotate instructions operate only on a RL a Mov a, #0 x. F 0 RR a ; a 11110000 ; a 11100001 RR a Mov a, #0 x. F 0 RR a hsabaghianb @ kashanu. ac. ir ; a 11110000 ; a 01111000 Microprocessors 5 -50

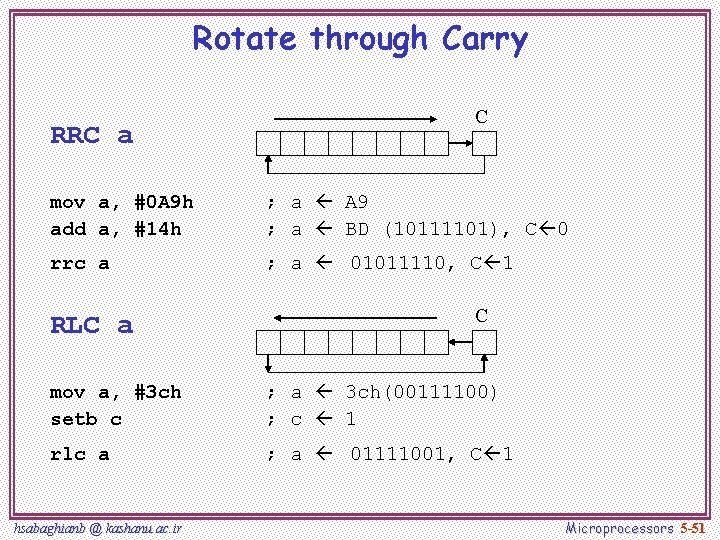

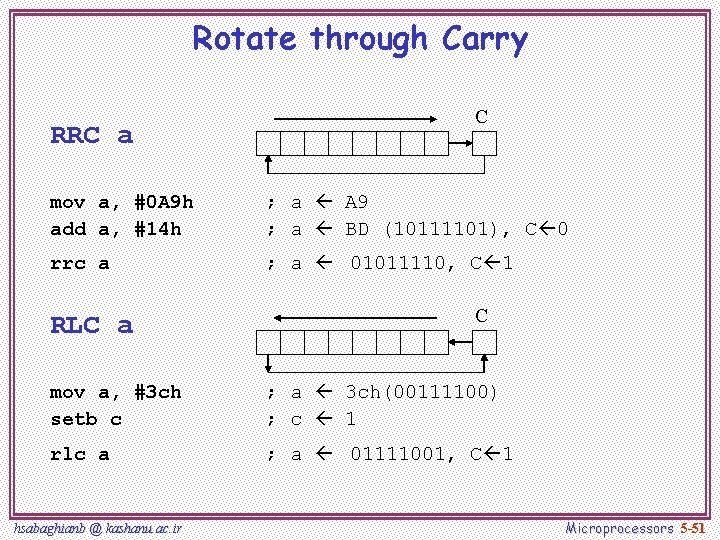

Rotate through Carry RRC a C mov a, #0 A 9 h add a, #14 h ; a A 9 ; a BD (10111101), C 0 rrc a ; a 01011110, C 1 RLC a C mov a, #3 ch setb c ; a 3 ch(00111100) ; c 1 rlc a ; a 01111001, C 1 hsabaghianb @ kashanu. ac. ir Microprocessors 5 -51

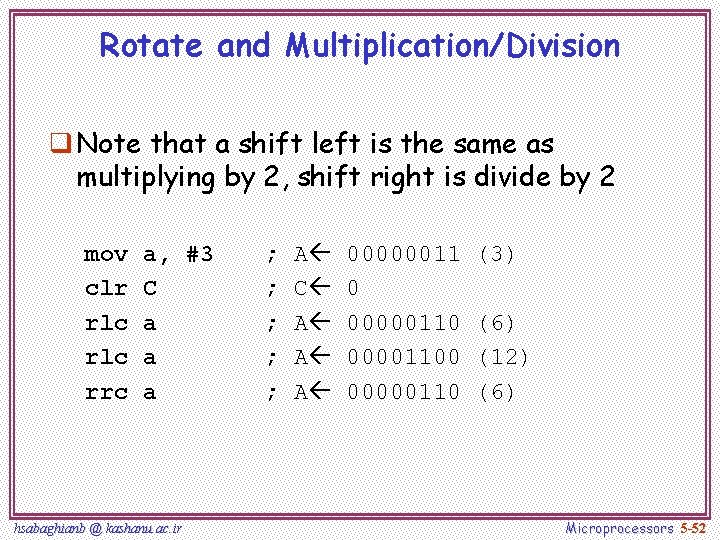

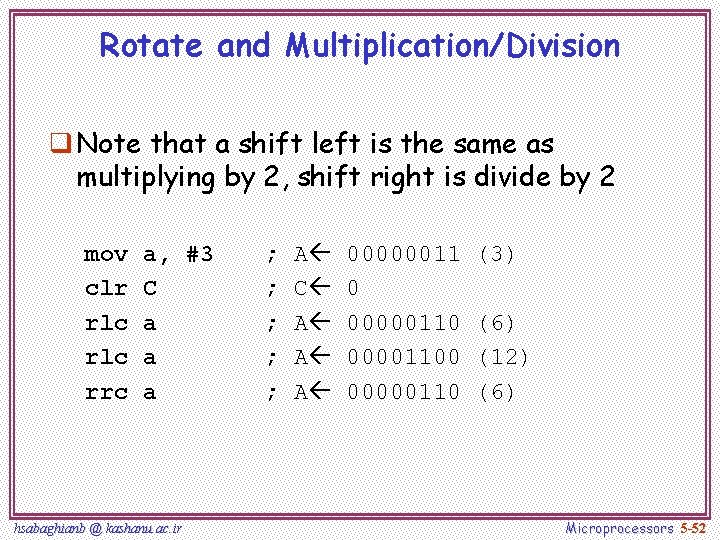

Rotate and Multiplication/Division q Note that a shift left is the same as multiplying by 2, shift right is divide by 2 mov clr rlc rrc a, #3 C a a a hsabaghianb @ kashanu. ac. ir ; ; ; A C A A A 00000011 0 000001100 00000110 (3) (6) (12) (6) Microprocessors 5 -52

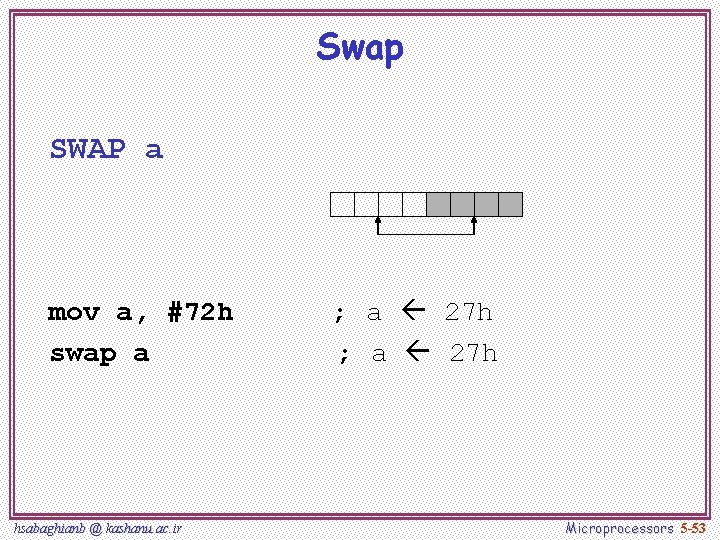

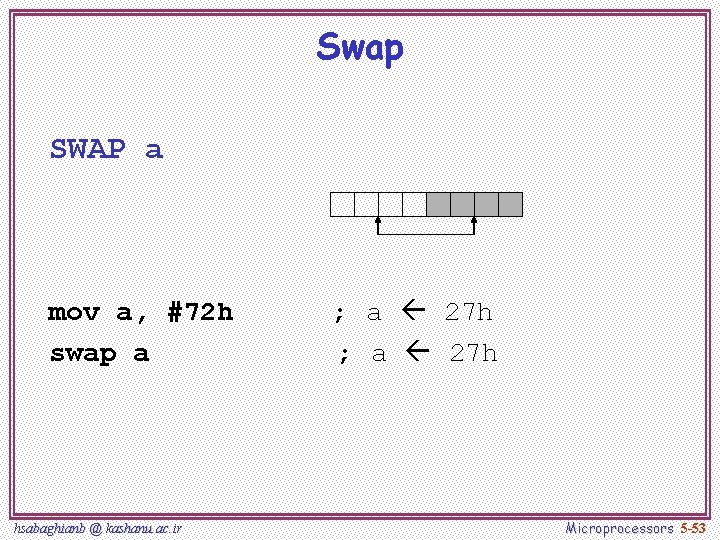

Swap SWAP a mov a, #72 h swap a hsabaghianb @ kashanu. ac. ir ; a 27 h Microprocessors 5 -53

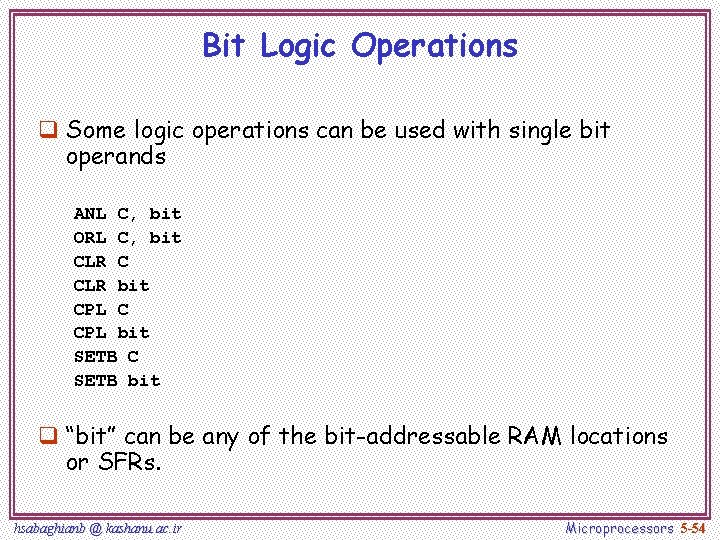

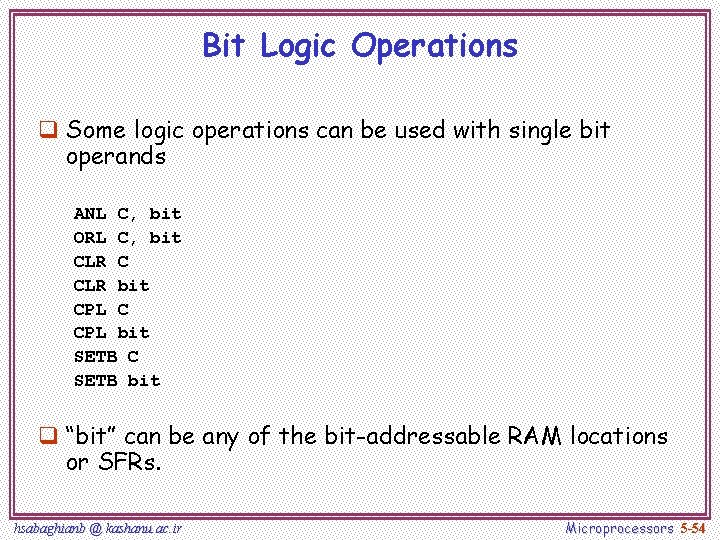

Bit Logic Operations q Some logic operations can be used with single bit operands ANL C, bit ORL C, bit CLR C CLR bit CPL C CPL bit SETB C SETB bit q “bit” can be any of the bit-addressable RAM locations or SFRs. hsabaghianb @ kashanu. ac. ir Microprocessors 5 -54

Program Flow Control q Unconditional jumps (“go to”) q Conditional jumps q Call and return hsabaghianb @ kashanu. ac. ir Microprocessors 5 -55

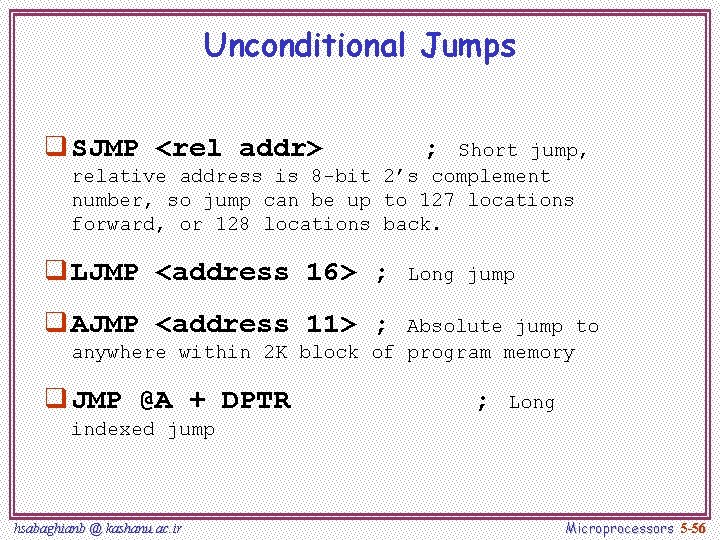

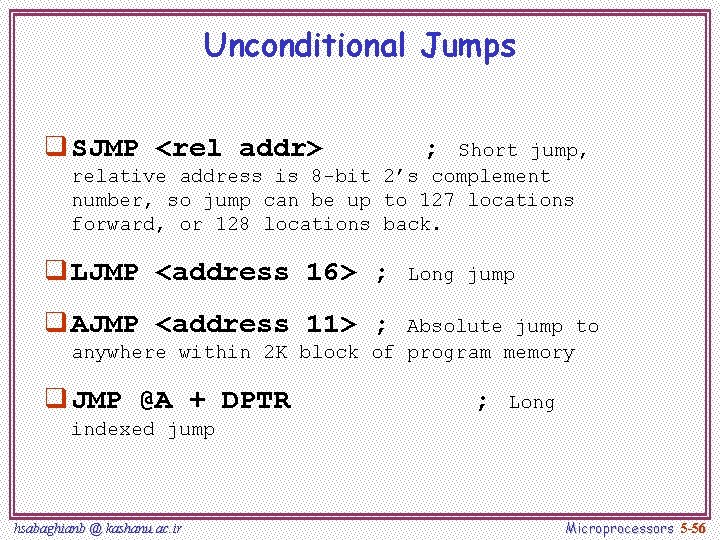

Unconditional Jumps q SJMP <rel addr> ; Short jump, relative address is 8 -bit 2’s complement number, so jump can be up to 127 locations forward, or 128 locations back. q LJMP <address 16> ; Long jump q AJMP <address 11> ; Absolute jump to anywhere within 2 K block of program memory q JMP @A + DPTR ; Long indexed jump hsabaghianb @ kashanu. ac. ir Microprocessors 5 -56

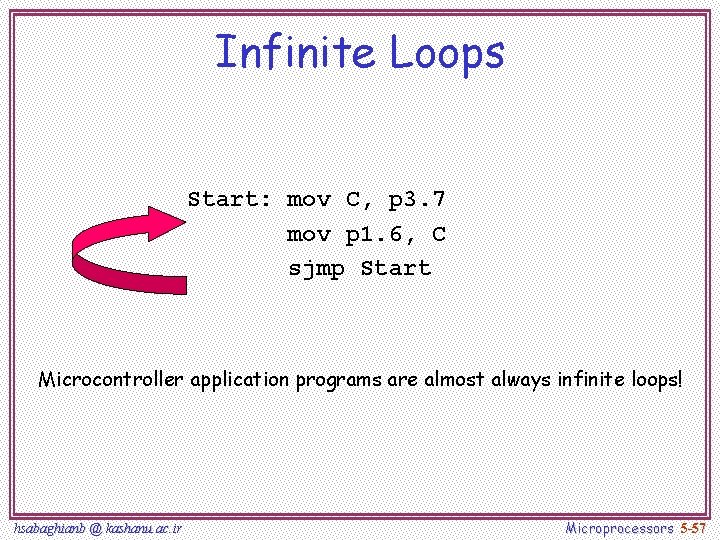

Infinite Loops Start: mov C, p 3. 7 mov p 1. 6, C sjmp Start Microcontroller application programs are almost always infinite loops! hsabaghianb @ kashanu. ac. ir Microprocessors 5 -57

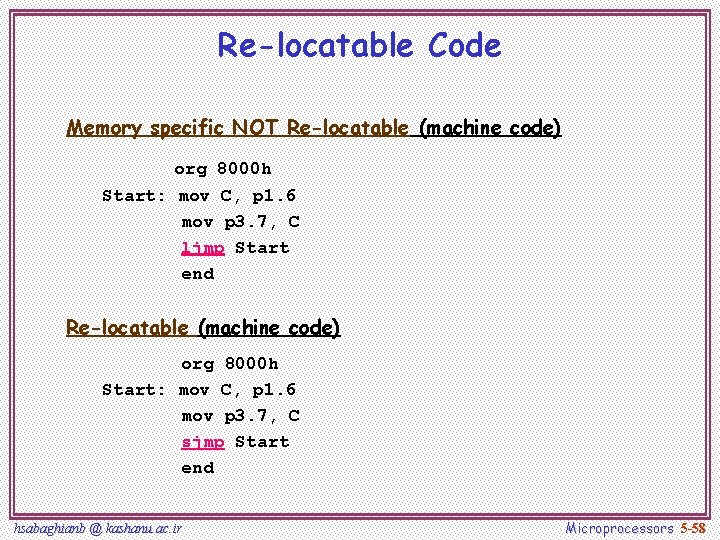

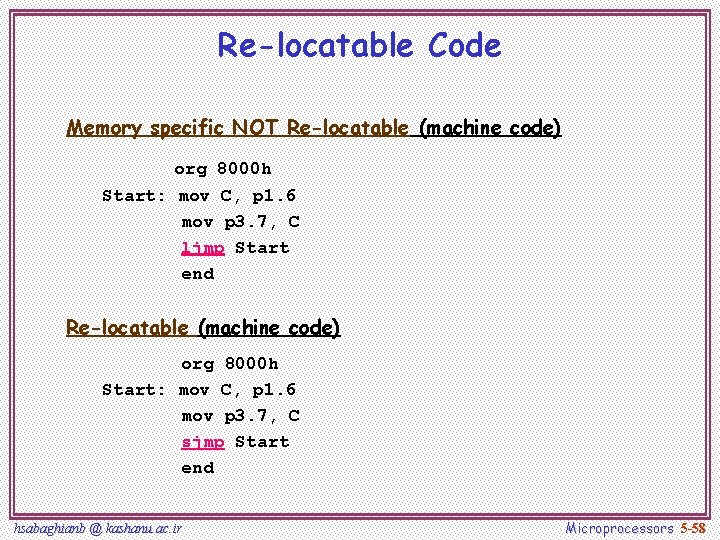

Re-locatable Code Memory specific NOT Re-locatable (machine code) org 8000 h Start: mov C, p 1. 6 mov p 3. 7, C ljmp Start end Re-locatable (machine code) org 8000 h Start: mov C, p 1. 6 mov p 3. 7, C sjmp Start end hsabaghianb @ kashanu. ac. ir Microprocessors 5 -58

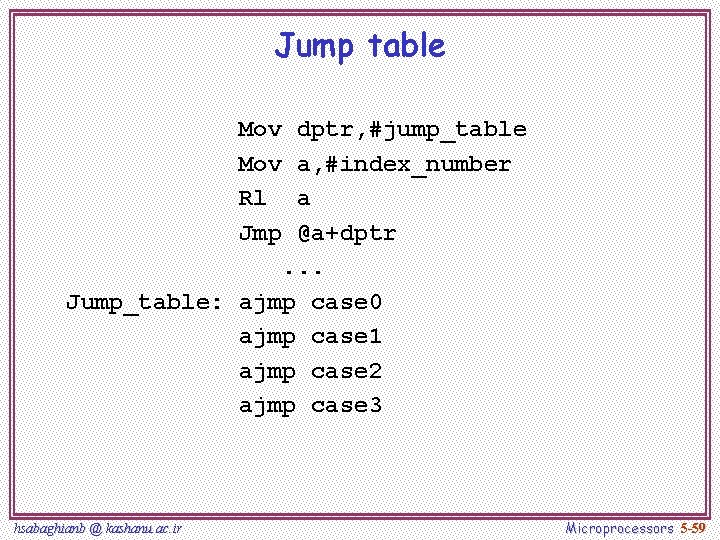

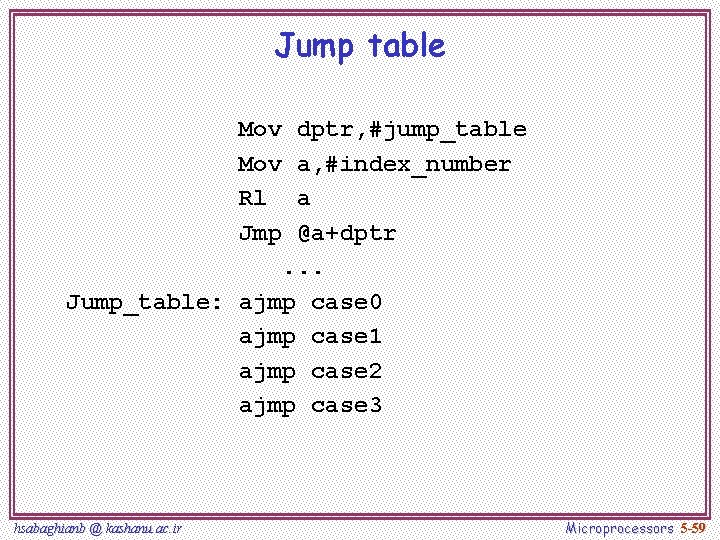

Jump table Mov dptr, #jump_table Mov a, #index_number Rl a Jmp @a+dptr. . . Jump_table: ajmp case 0 ajmp case 1 ajmp case 2 ajmp case 3 hsabaghianb @ kashanu. ac. ir Microprocessors 5 -59

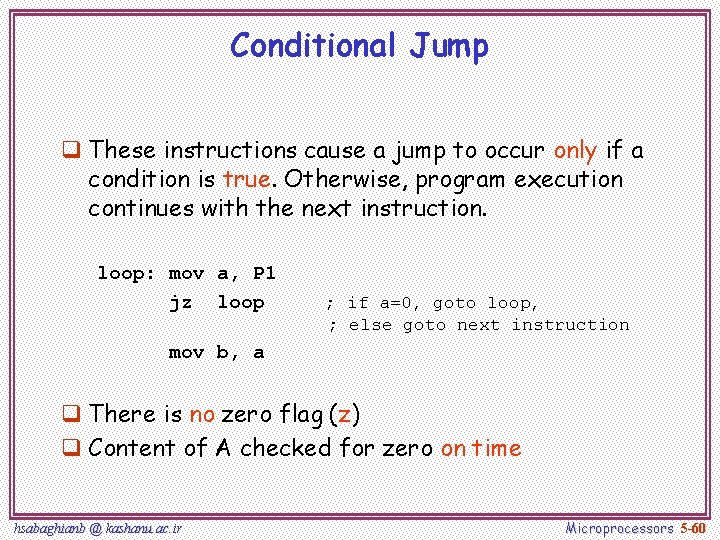

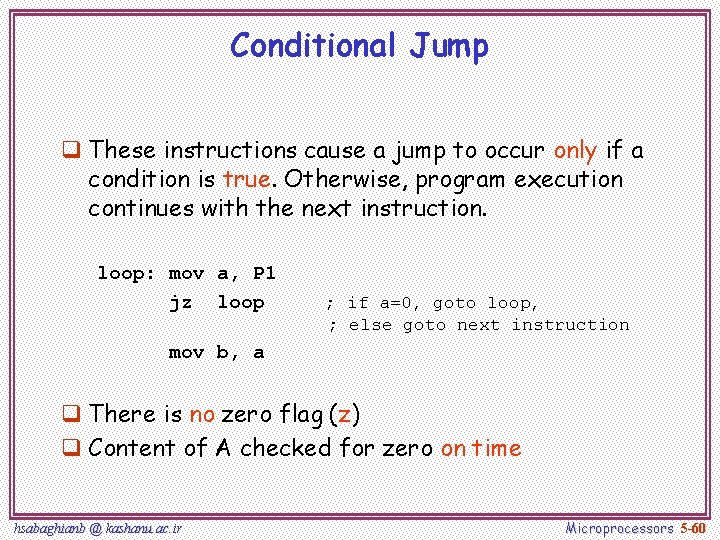

Conditional Jump q These instructions cause a jump to occur only if a condition is true. Otherwise, program execution continues with the next instruction. loop: mov a, P 1 jz loop ; if a=0, goto loop, ; else goto next instruction mov b, a q There is no zero flag (z) q Content of A checked for zero on time hsabaghianb @ kashanu. ac. ir Microprocessors 5 -60

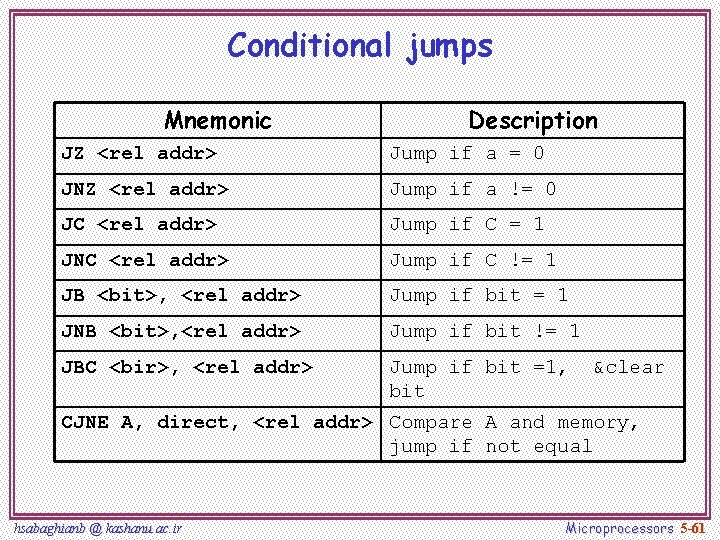

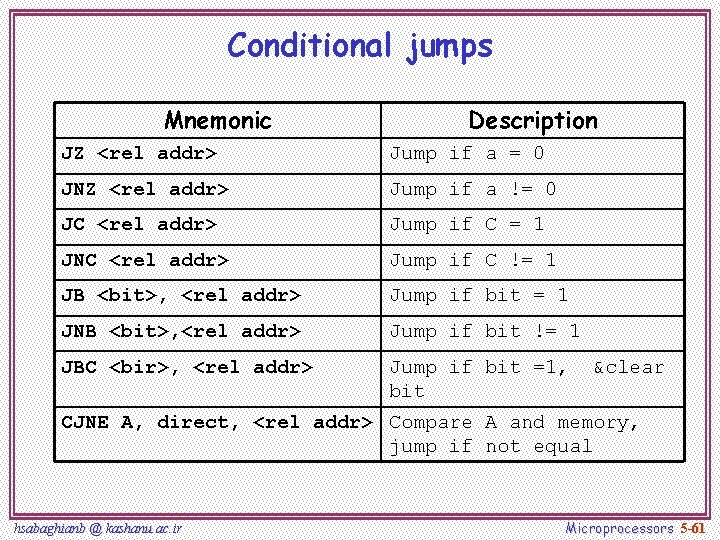

Conditional jumps Mnemonic Description JZ <rel addr> Jump if a = 0 JNZ <rel addr> Jump if a != 0 JC <rel addr> Jump if C = 1 JNC <rel addr> Jump if C != 1 JB <bit>, <rel addr> Jump if bit = 1 JNB <bit>, <rel addr> Jump if bit != 1 JBC <bir>, <rel addr> Jump if bit =1, bit &clear CJNE A, direct, <rel addr> Compare A and memory, jump if not equal hsabaghianb @ kashanu. ac. ir Microprocessors 5 -61

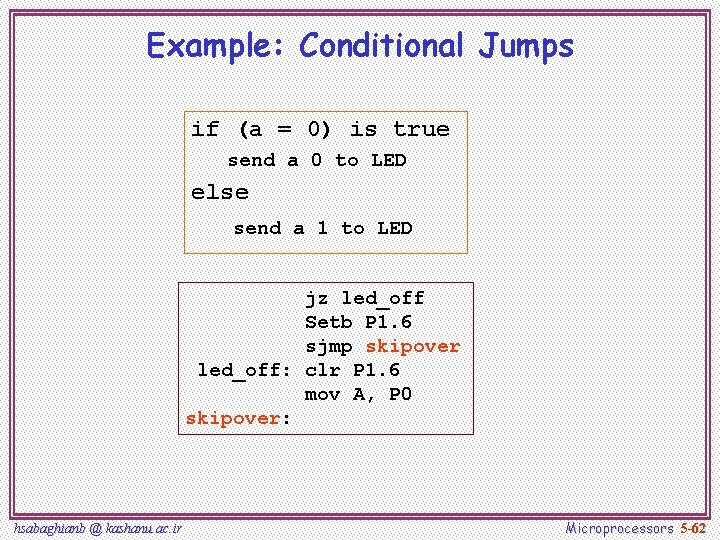

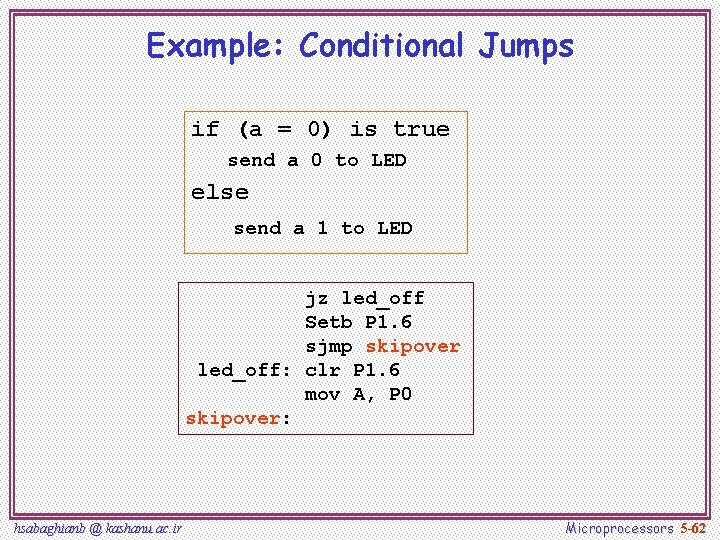

Example: Conditional Jumps if (a = 0) is true send a 0 to LED else send a 1 to LED jz led_off Setb P 1. 6 sjmp skipover led_off: clr P 1. 6 mov A, P 0 skipover: hsabaghianb @ kashanu. ac. ir Microprocessors 5 -62

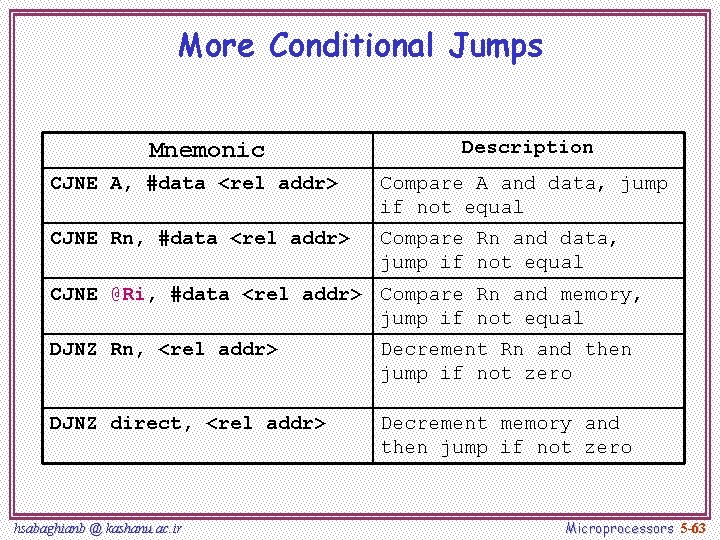

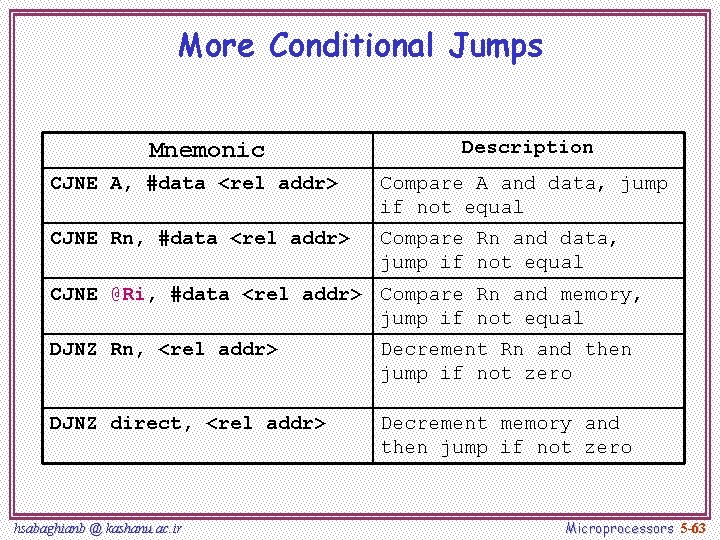

More Conditional Jumps Mnemonic Description CJNE A, #data <rel addr> Compare A and data, jump if not equal CJNE Rn, #data <rel addr> Compare Rn and data, jump if not equal CJNE @Ri, #data <rel addr> Compare Rn and memory, jump if not equal DJNZ Rn, <rel addr> Decrement Rn and then jump if not zero DJNZ direct, <rel addr> Decrement memory and then jump if not zero hsabaghianb @ kashanu. ac. ir Microprocessors 5 -63

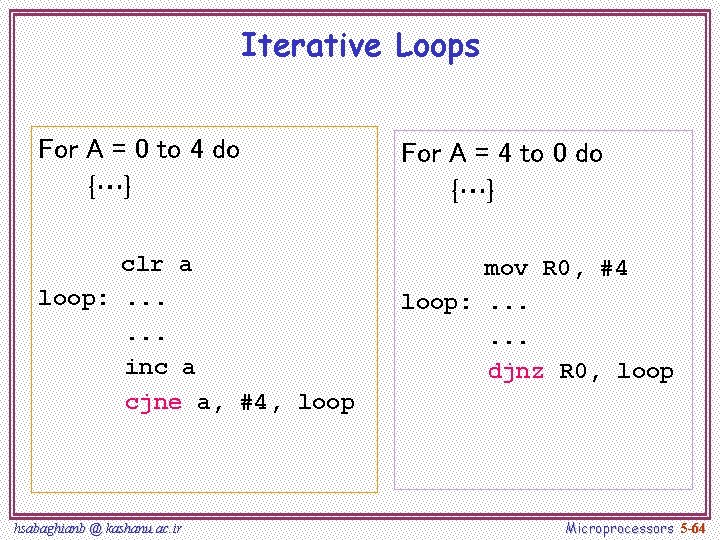

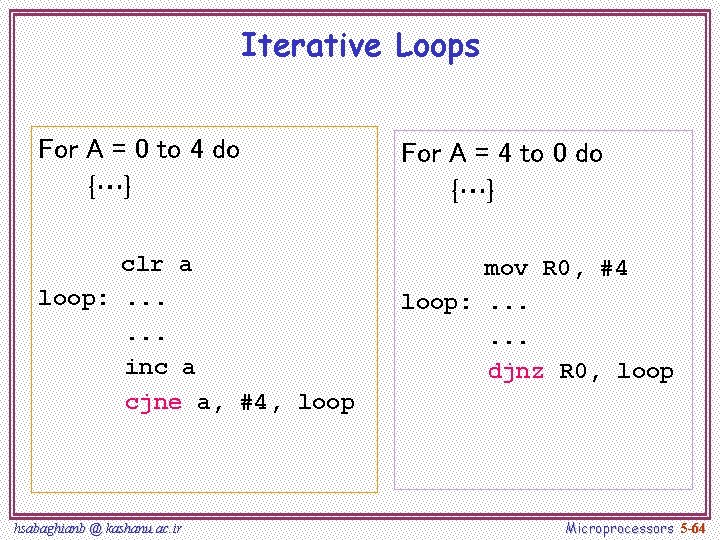

Iterative Loops For A = 0 to 4 do {…} For A = 4 to 0 do {…} clr a loop: . . . inc a cjne a, #4, loop mov R 0, #4 loop: . . . djnz R 0, loop hsabaghianb @ kashanu. ac. ir Microprocessors 5 -64

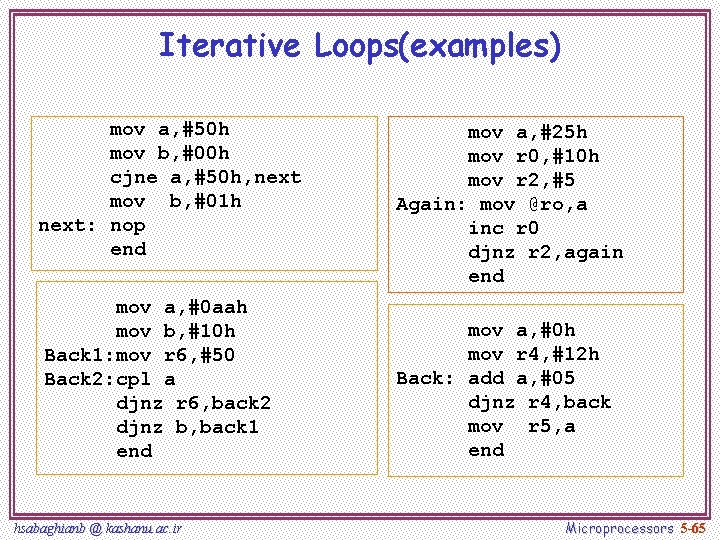

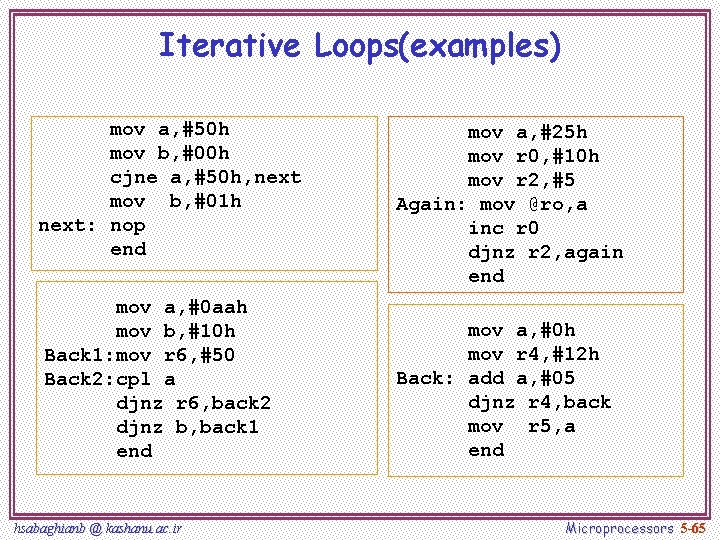

Iterative Loops(examples) mov a, #50 h mov b, #00 h cjne a, #50 h, next mov b, #01 h next: nop end mov a, #0 aah mov b, #10 h Back 1: mov r 6, #50 Back 2: cpl a djnz r 6, back 2 djnz b, back 1 end hsabaghianb @ kashanu. ac. ir mov a, #25 h mov r 0, #10 h mov r 2, #5 Again: mov @ro, a inc r 0 djnz r 2, again end mov a, #0 h mov r 4, #12 h Back: add a, #05 djnz r 4, back mov r 5, a end Microprocessors 5 -65

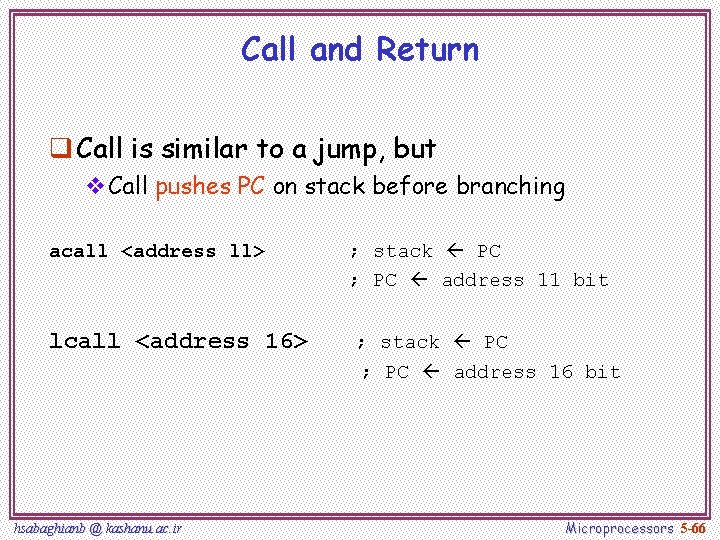

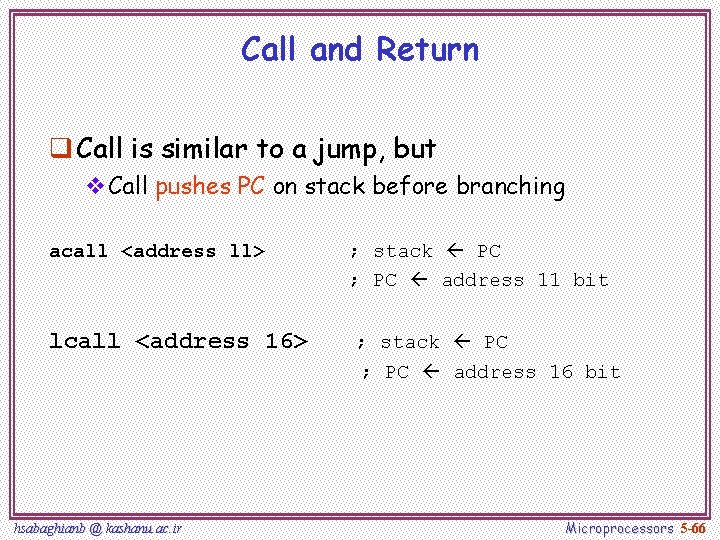

Call and Return q Call is similar to a jump, but v. Call pushes PC on stack before branching acall <address ll> lcall <address 16> ; stack PC ; PC address 11 bit ; stack PC ; PC address 16 bit hsabaghianb @ kashanu. ac. ir Microprocessors 5 -66

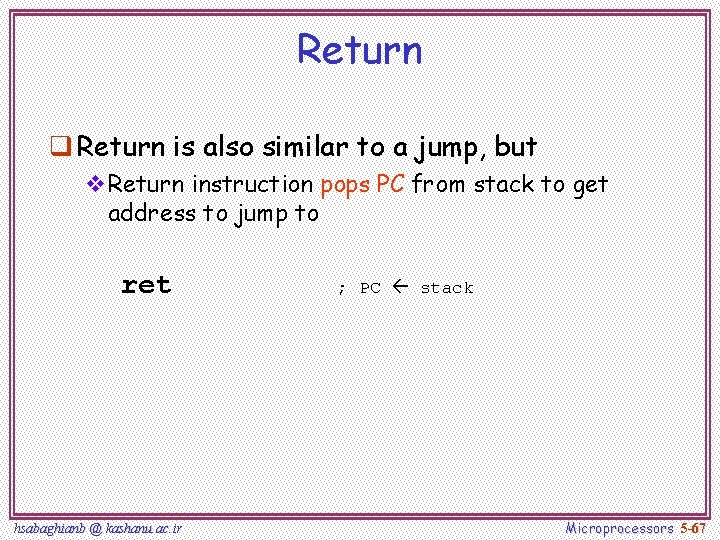

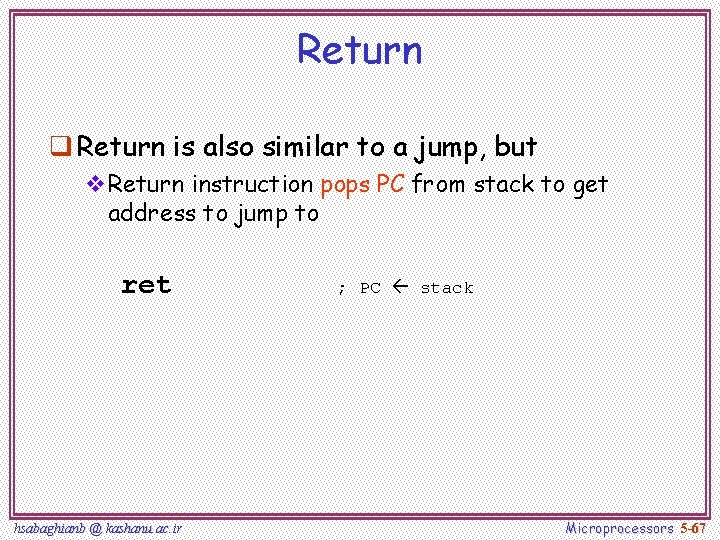

Return q Return is also similar to a jump, but v. Return instruction pops PC from stack to get address to jump to ret hsabaghianb @ kashanu. ac. ir ; PC stack Microprocessors 5 -67

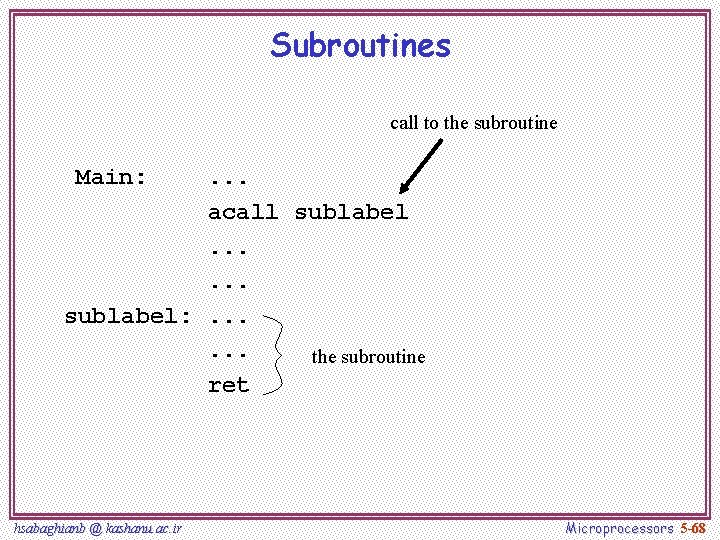

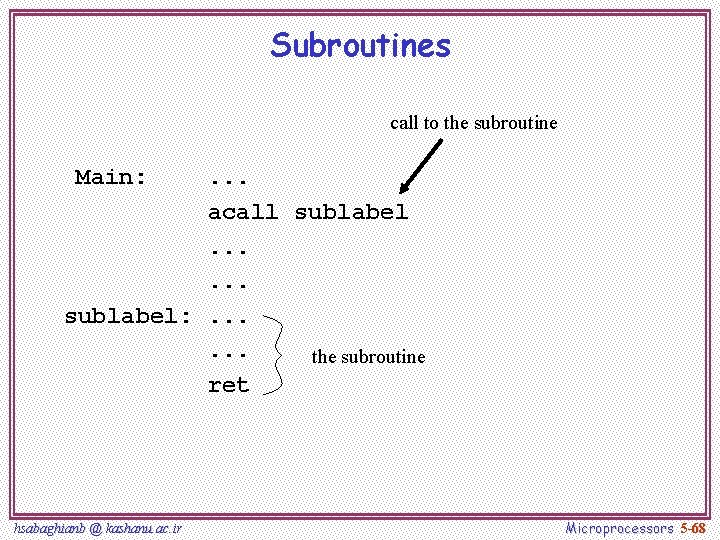

Subroutines call to the subroutine Main: . . . acall sublabel. . . sublabel: . . . the subroutine ret hsabaghianb @ kashanu. ac. ir Microprocessors 5 -68

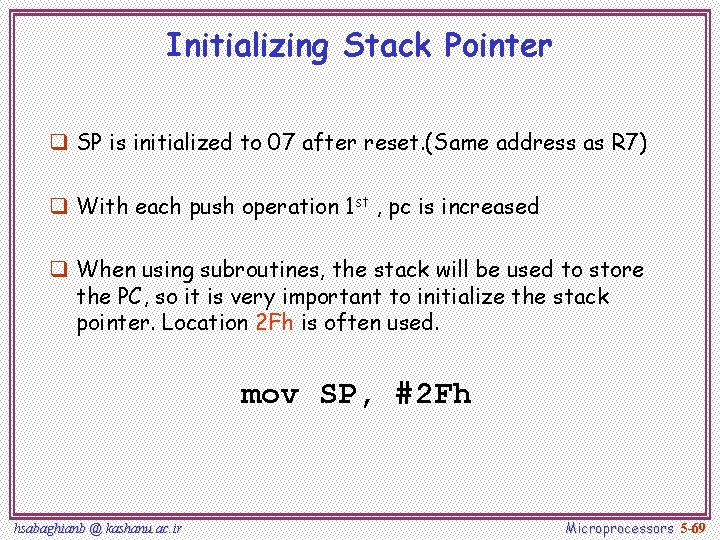

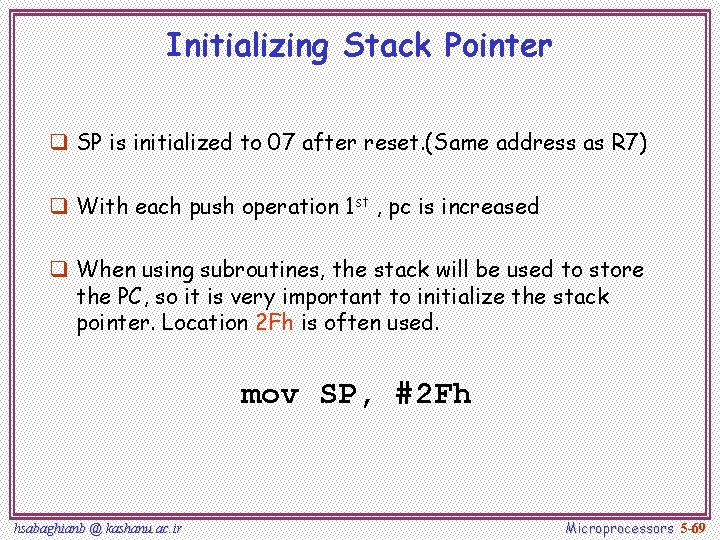

Initializing Stack Pointer q SP is initialized to 07 after reset. (Same address as R 7) q With each push operation 1 st , pc is increased q When using subroutines, the stack will be used to store the PC, so it is very important to initialize the stack pointer. Location 2 Fh is often used. mov SP, #2 Fh hsabaghianb @ kashanu. ac. ir Microprocessors 5 -69

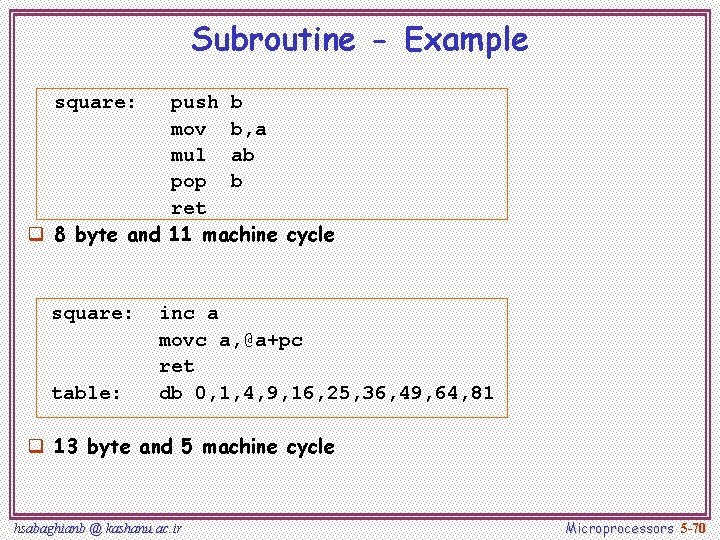

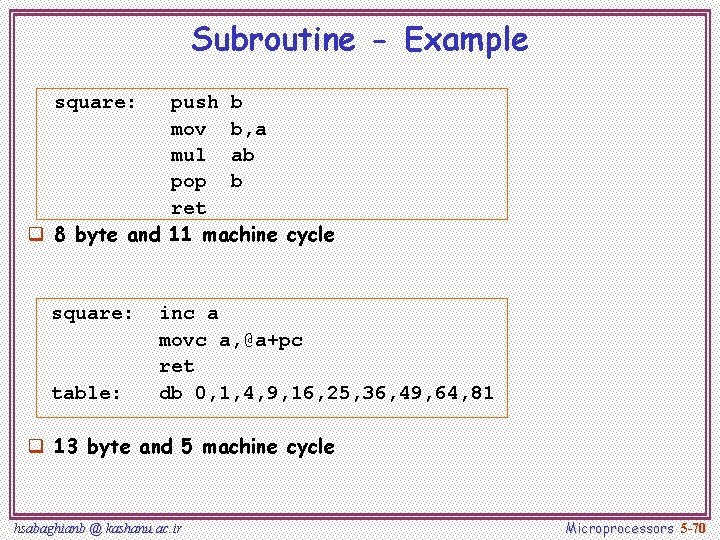

Subroutine - Example square: push b mov b, a mul ab pop b ret q 8 byte and 11 machine cycle square: table: inc a movc a, @a+pc ret db 0, 1, 4, 9, 16, 25, 36, 49, 64, 81 q 13 byte and 5 machine cycle hsabaghianb @ kashanu. ac. ir Microprocessors 5 -70

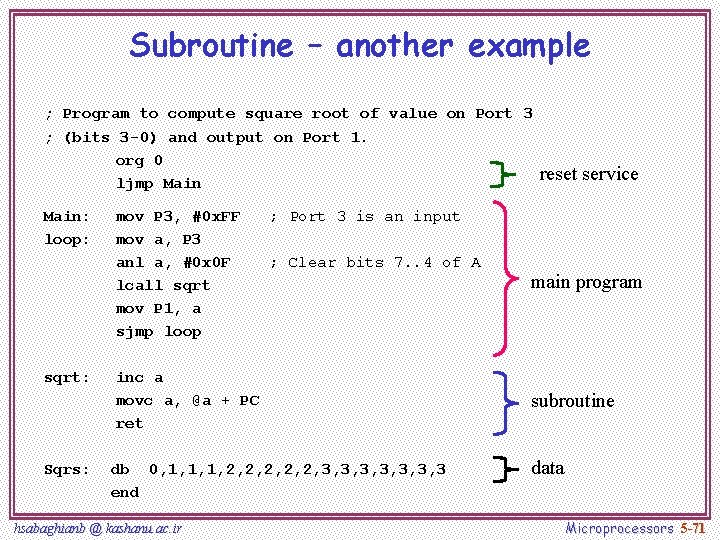

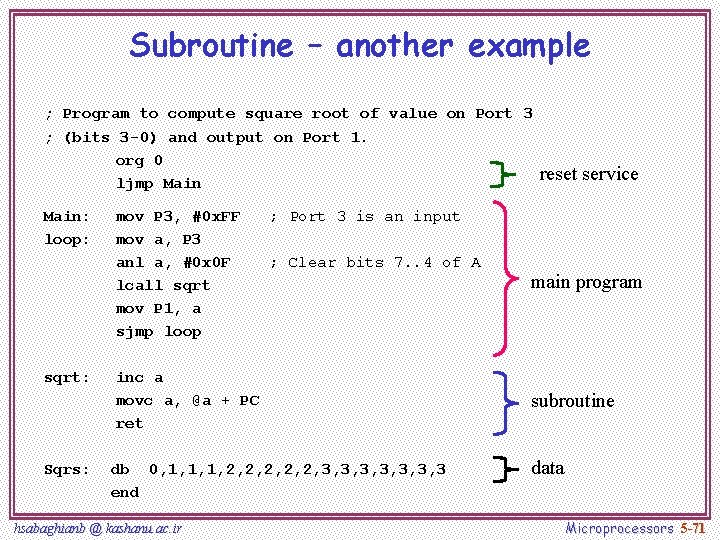

Subroutine – another example ; Program to compute square root of value on Port 3 ; (bits 3 -0) and output on Port 1. org 0 ljmp Main: loop: sqrt: Sqrs: mov P 3, #0 x. FF mov a, P 3 anl a, #0 x 0 F lcall sqrt mov P 1, a sjmp loop ; Port 3 is an input ; Clear bits 7. . 4 of A inc a movc a, @a + PC ret db 0, 1, 1, 1, 2, 2, 2, 3, 3, 3, 3 end hsabaghianb @ kashanu. ac. ir reset service main program subroutine data Microprocessors 5 -71

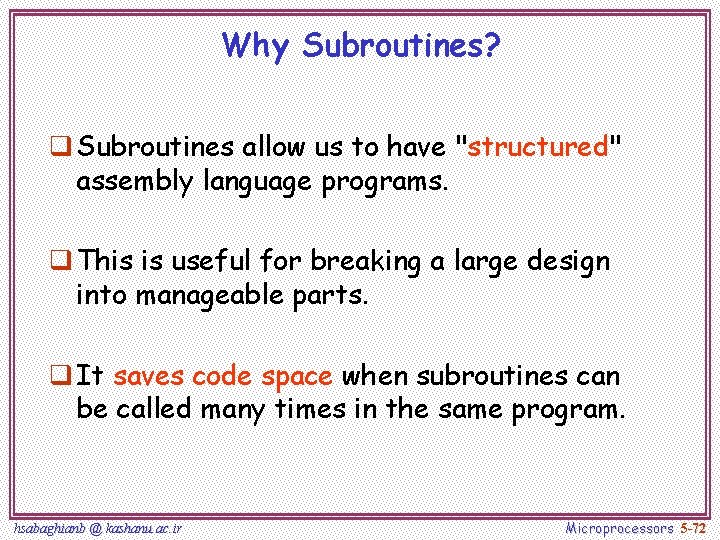

Why Subroutines? q Subroutines allow us to have "structured" assembly language programs. q This is useful for breaking a large design into manageable parts. q It saves code space when subroutines can be called many times in the same program. hsabaghianb @ kashanu. ac. ir Microprocessors 5 -72

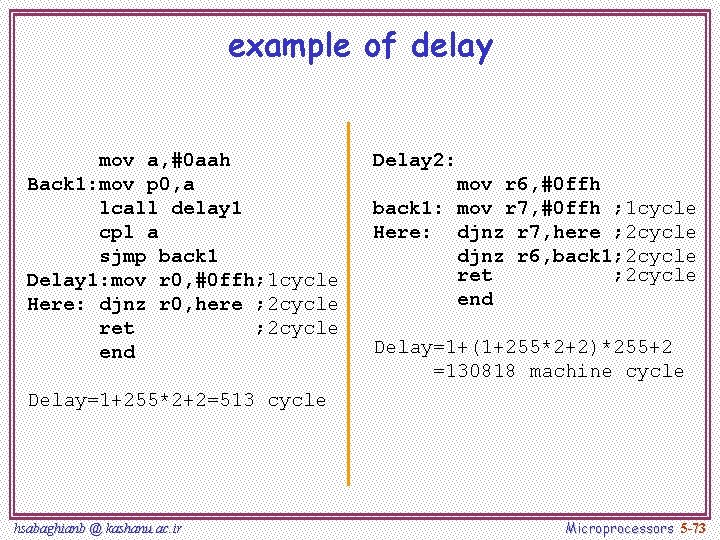

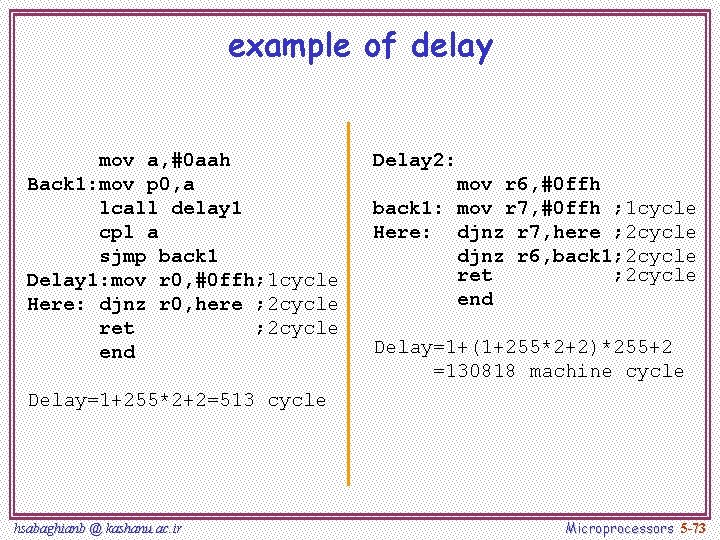

example of delay mov a, #0 aah Back 1: mov p 0, a lcall delay 1 cpl a sjmp back 1 Delay 1: mov r 0, #0 ffh; 1 cycle Here: djnz r 0, here ; 2 cycle ret ; 2 cycle end Delay 2: mov r 6, #0 ffh back 1: mov r 7, #0 ffh ; 1 cycle Here: djnz r 7, here ; 2 cycle djnz r 6, back 1; 2 cycle ret ; 2 cycle end Delay=1+(1+255*2+2)*255+2 =130818 machine cycle Delay=1+255*2+2=513 cycle hsabaghianb @ kashanu. ac. ir Microprocessors 5 -73

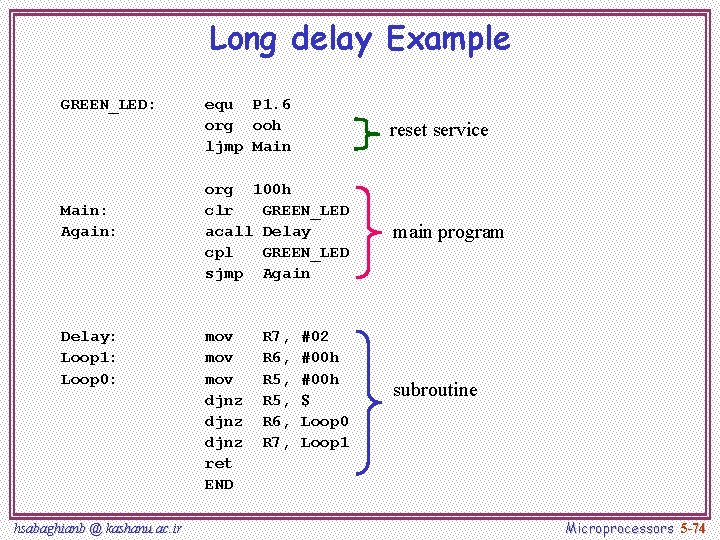

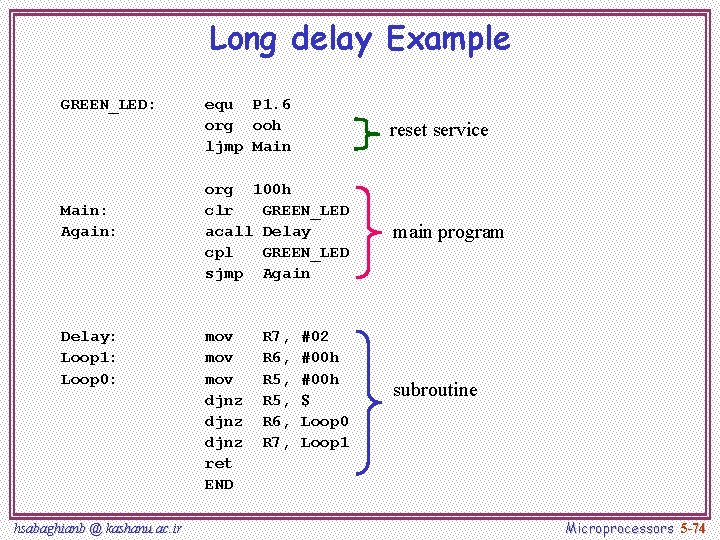

Long delay Example GREEN_LED: Main: Again: Delay: Loop 1: Loop 0: hsabaghianb @ kashanu. ac. ir equ P 1. 6 org ooh ljmp Main reset service org 100 h clr GREEN_LED acall Delay cpl GREEN_LED sjmp Again main program mov mov djnz ret END R 7, R 6, R 5, R 6, R 7, #02 #00 h $ Loop 0 Loop 1 subroutine Microprocessors 5 -74

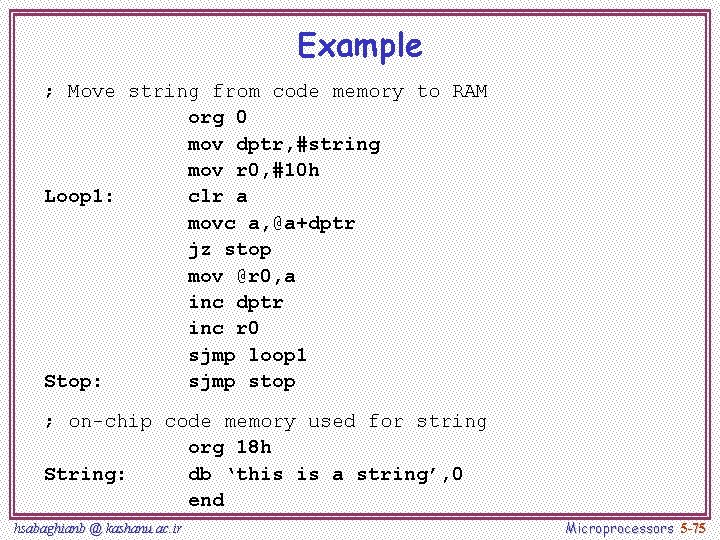

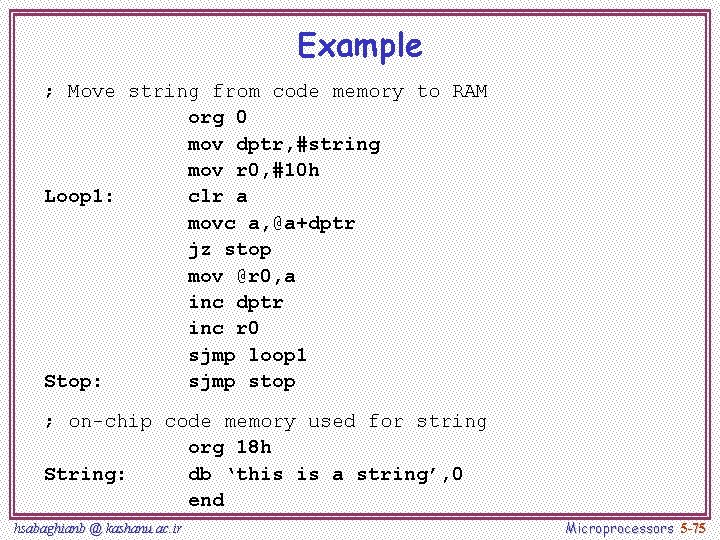

Example ; Move string from code memory to RAM org 0 mov dptr, #string mov r 0, #10 h Loop 1: clr a movc a, @a+dptr jz stop mov @r 0, a inc dptr inc r 0 sjmp loop 1 Stop: sjmp stop ; on-chip code memory used for string org 18 h String: db ‘this is a string’, 0 end hsabaghianb @ kashanu. ac. ir Microprocessors 5 -75

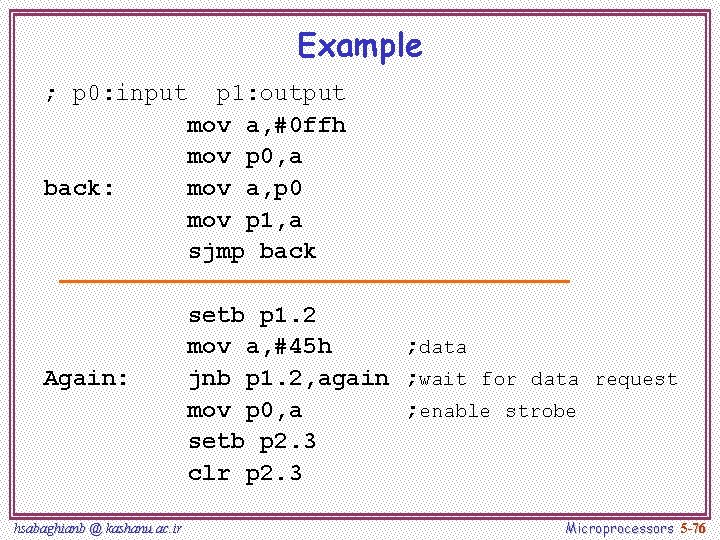

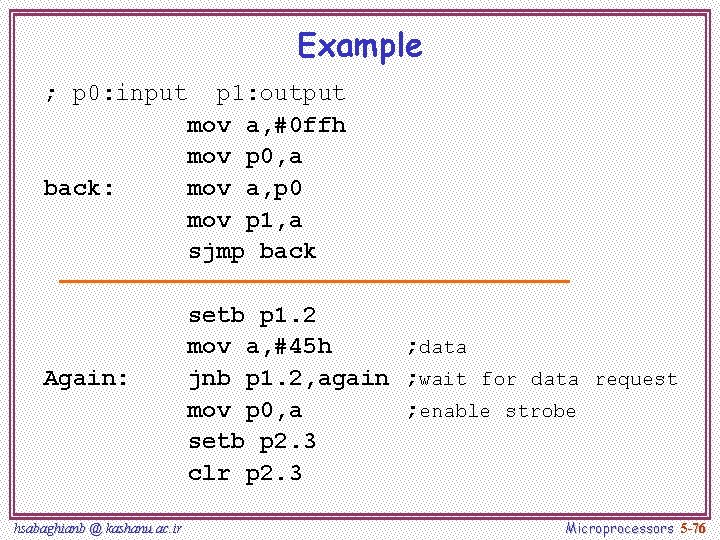

Example ; p 0: input p 1: output mov a, #0 ffh mov p 0, a back: mov a, p 0 mov p 1, a sjmp back Again: hsabaghianb @ kashanu. ac. ir setb p 1. 2 mov a, #45 h ; data jnb p 1. 2, again ; wait for data request mov p 0, a ; enable strobe setb p 2. 3 clr p 2. 3 Microprocessors 5 -76

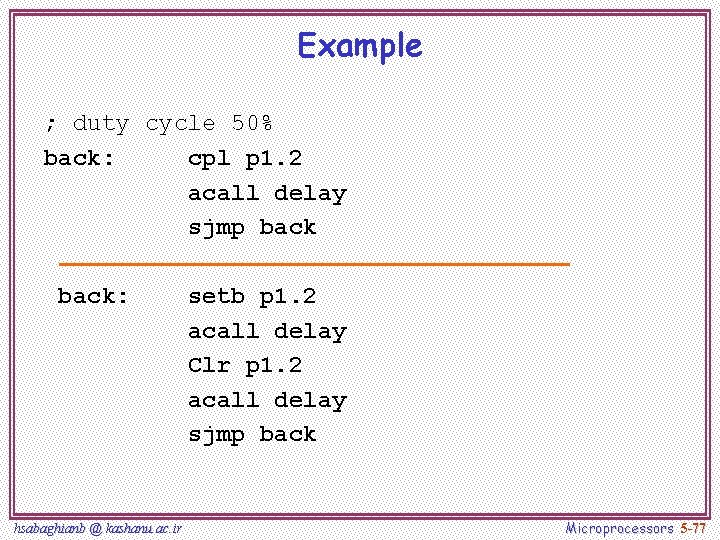

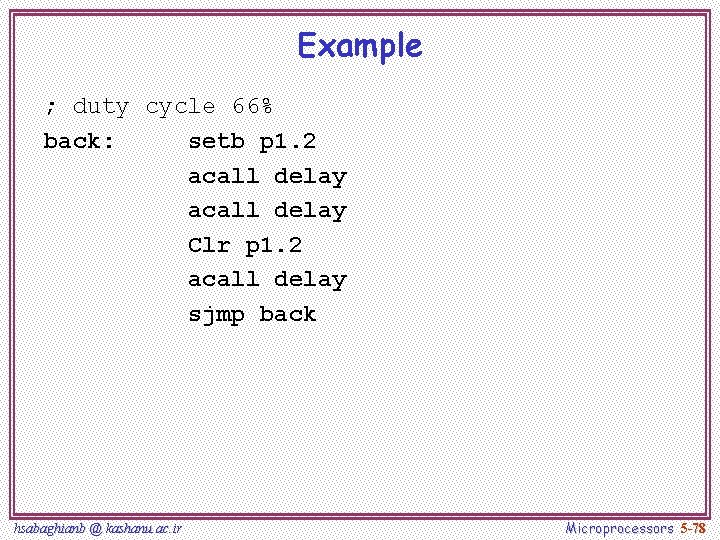

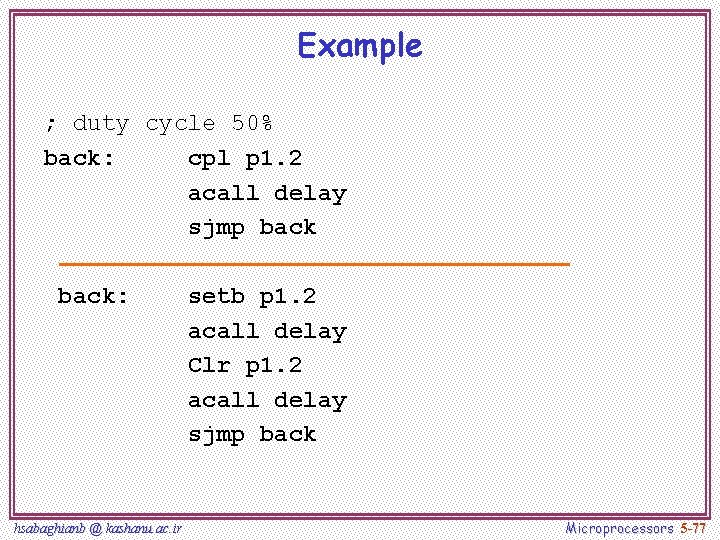

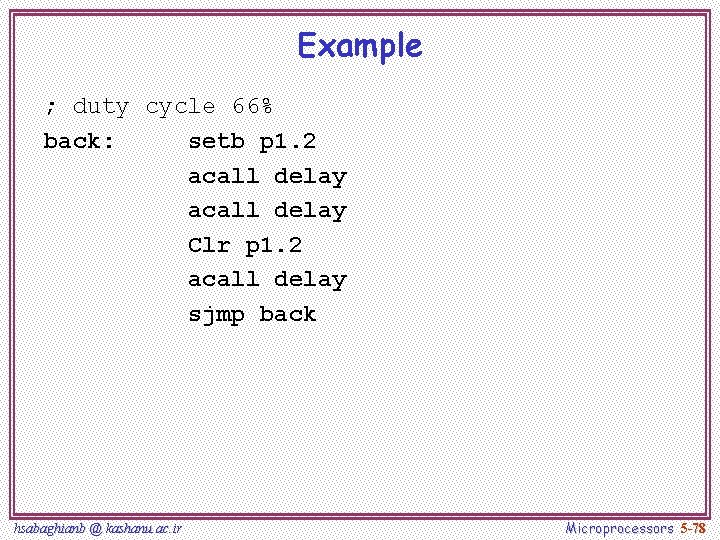

Example ; duty cycle 50% back: cpl p 1. 2 acall delay sjmp back: hsabaghianb @ kashanu. ac. ir setb p 1. 2 acall delay Clr p 1. 2 acall delay sjmp back Microprocessors 5 -77

Example ; duty cycle 66% back: setb p 1. 2 acall delay Clr p 1. 2 acall delay sjmp back hsabaghianb @ kashanu. ac. ir Microprocessors 5 -78

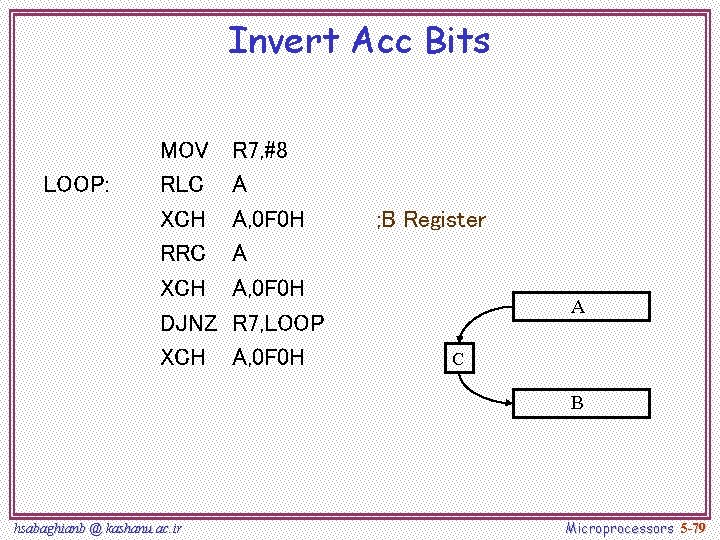

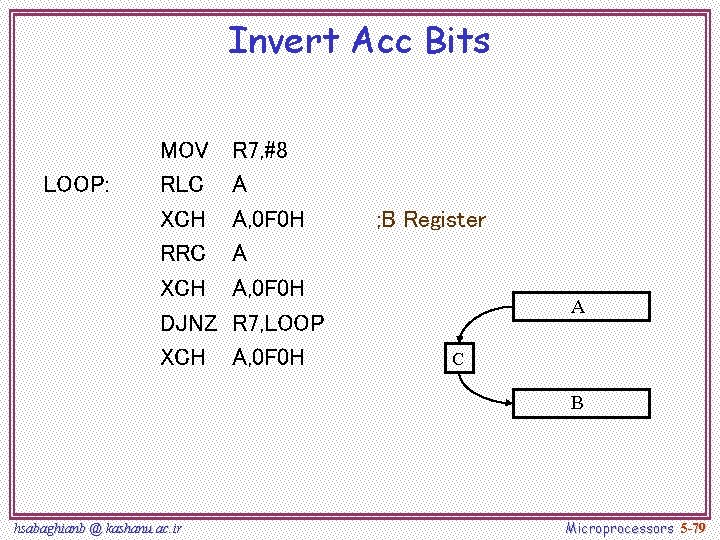

Invert Acc Bits LOOP: MOV RLC XCH RRC XCH DJNZ XCH R 7, #8 A A, 0 F 0 H R 7, LOOP A, 0 F 0 H ; B Register A C B hsabaghianb @ kashanu. ac. ir Microprocessors 5 -79

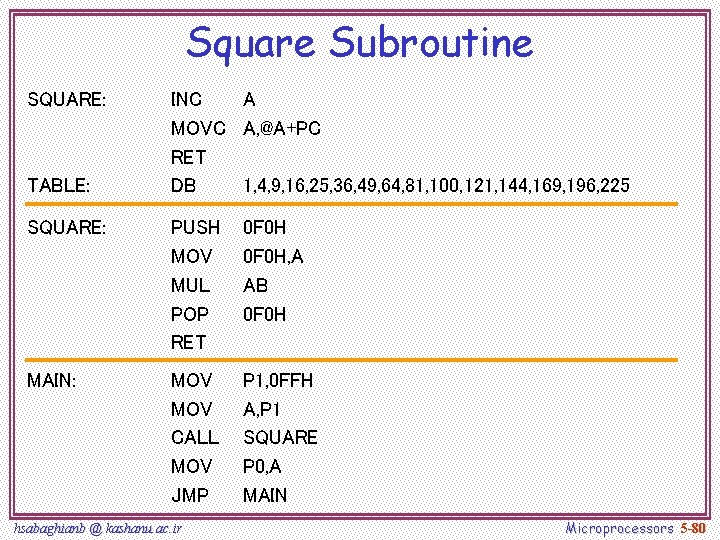

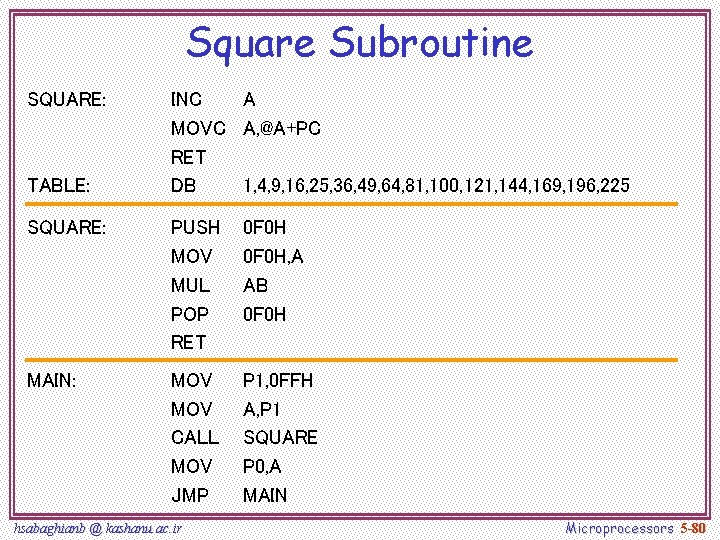

Square Subroutine SQUARE: TABLE: INC A MOVC A, @A+PC RET DB 1, 4, 9, 16, 25, 36, 49, 64, 81, 100, 121, 144, 169, 196, 225 SQUARE: PUSH MOV MUL POP RET 0 F 0 H, A AB 0 F 0 H MAIN: MOV CALL MOV JMP P 1, 0 FFH A, P 1 SQUARE P 0, A MAIN hsabaghianb @ kashanu. ac. ir Microprocessors 5 -80

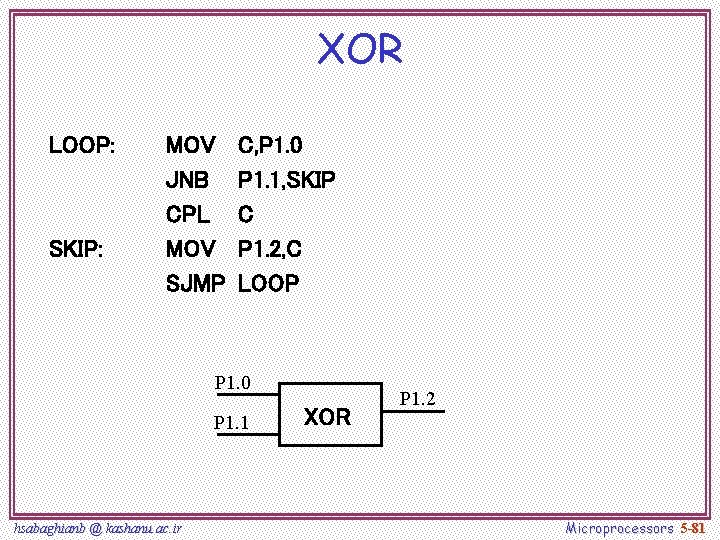

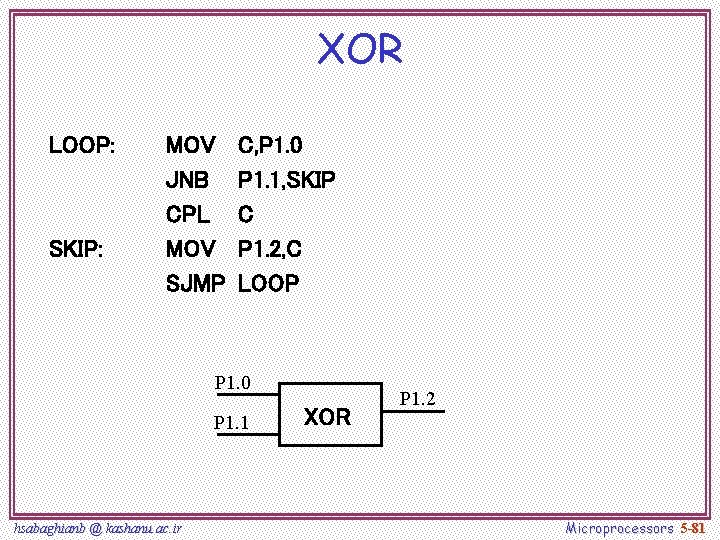

XOR LOOP: SKIP: MOV JNB CPL MOV SJMP C, P 1. 0 P 1. 1, SKIP C P 1. 2, C LOOP P 1. 0 P 1. 1 hsabaghianb @ kashanu. ac. ir XOR P 1. 2 Microprocessors 5 -81